## New Jersey Institute of Technology Digital Commons @ NJIT

#### Dissertations

Theses and Dissertations

Spring 1995

## Investigation of hybrid message-passing and sharedmemory architectures for parallel computer : a case study : turbonet

Xi Li New Jersey Institute of Technology

Follow this and additional works at: https://digitalcommons.njit.edu/dissertations Part of the <u>Electrical and Electronics Commons</u>

#### **Recommended** Citation

Li, Xi, "Investigation of hybrid message-passing and shared-memory architectures for parallel computer : a case study : turbonet" (1995). *Dissertations*. 1119. https://digitalcommons.njit.edu/dissertations/1119

This Dissertation is brought to you for free and open access by the Theses and Dissertations at Digital Commons @ NJIT. It has been accepted for inclusion in Dissertations by an authorized administrator of Digital Commons @ NJIT. For more information, please contact digitalcommons@njit.edu.

# **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

## **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps. Each original is also photographed in one exposure and is included in reduced form at the back of the book.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

A Bell & Howell Information Company 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 313/761-4700 800/521-0600 UMI Number: 9539583

Copyright 1995 by Li, Xi All rights reserved.

UMI Microform 9539583 Copyright 1995, by UMI Company. All rights reserved.

This microform edition is protected against unauthorized copying under Title 17, United States Code.

## UMI

300 North Zeeb Road Ann Arbor, MI 48103

#### ABSTRACT

### INVESTIGATION OF HYBRID MESSAGE-PASSING AND SHARED-MEMORY ARCHITECTURES FOR PARALLEL COMPUTERS. A CASE STUDY: TURBONET

#### by Xi Li

Several DSP (Digital Signal Processing) algorithms are developed for the NJIT TurboNet parallel computer. In contrast to other parallel computers that implement exclusively in hardware either the message-passing or the shared-memory communication paradigm, or employ distributed shared-memory architectures characterized by inefficient implementation of the shared-memory paradigm, the hybrid architecture of TurboNet supports direct, efficient implementation of both paradigms. Three versions of each algorithm are developed, if possible, corresponding to message-passing, shared-memory, and hybrid communications, respectively. Theoretical and experimental comparisons of algorithms are employed in the analysis of performance. The results prove that the hybrid versions generally achieve better performance than the other two versions. The main conclusion of this research is that small-scale and medium-scale parallel computers should implement directly in hardware both communication paradigms, for high performance, robustness in relation to the application space, and ease of algorithm development. To facilitate theoretical comparisons, a methodology is developed for highly accurate prediction of algorithm performance. The success of this methodology proves that such prediction is possible for complex parallel computers, such as TurboNet, if enough information is provided by the data dependence graphs.

## INVESTIGATION OF HYBRID MESSAGE-PASSING AND SHARED-MEMORY ARCHITECTURES FOR PARALLEL COMPUTERS. A CASE STUDY: TURBONET

by Xi Li

A Dissertation Submitted to the Faculty of New Jersey Institute of Technology in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

.

Department of Electrical and Computer Engineering

May 1995

Copyright © 1995 by Xi Li ALL RIGHTS RESERVED

#### **APPROVAL PAGE**

## INVESTIGATION OF HYBRID MESSAGE-PASSING AND SHARED-MEMORY ARCHITECTURES FOR PARALLEL COMPUTERS. A CASE STUDY: TURBONET

## Xi Li

| Dr. Sotirios G. Ziavras, Thesis Advisor                                                                 | Date |

|---------------------------------------------------------------------------------------------------------|------|

| Assistant Professor of Electrical and Computer Engineering, NJIT                                        |      |

| Dr. Constantine N. Manikopoulos, Thesis Advisor                                                         | Date |

| Associate Professor of Electrical and Computer Engineering, NJIT                                        |      |

| Dr. Edwin Hou, Committee Member<br>Assistant Professor of Computer and Information Science, NJIT        | Date |

| Dr. Michael Palis, Committee Member<br>Associate Professor of Electrical and Computer Engineering, NJIT | Date |

| Dr. Huifang Sun, Committee Member<br>Member of Technical Staff, David Sarnoff Research Laboratories     | Date |

| Dr. Mengchu Zhou, Committee Member                                                                      | Date |

Assistant Professor of Electrical and Computer Engineering, NJIT

## **BIOGRAPHICAL SKETCH**

Author: Xi Li

**Degree:** Doctor of Philosophy in Electrical Engineering

**Date:** May 1995

#### **Undergraduate and Graduate Education:**

- Doctor of Philosophy in Electrical Engineering, New Jersey Institute of Technology, Newark, NJ, 1995

- Master of Science in Computer Engineering, Florida Institute of Technology, Melbourne, FL, 1989

- Bachelor of Science in Electrical Engineering, South-China Institute of Technology, Guangzhou, P.R.China, 1983

### Major: Electrical Engineering

#### **Presentation and Publications:**

- X. Li, S. G. Ziavras and C. N. Manikopoulos, "Parallel DSP Algorithms on TurboNet: An Experimental System with Hybrid Message-Passing and Shared-Memory Architecture," *Concurrency: Practice and Experience*, accepted for publication, 1995.

- 2. X. Li, S. G. Ziavras and C. N. Manikopoulos, "Parallel Generation of Adaptive Multiresolution Structures for Image Processing," *Concurrency: Practice and Experience*, submitted for publication.

- R. Hross, S. G. Ziavras, C. N. Manikopoulos, N. J. Lad and X. Li, "A Defect Identification Algorithm for Sequential and Parallel Computers," *IEEE International Symposium on Industrial Electronics*, Athens, Greece, July 10-14, 1995, to appear.

This thesis is dedicated to my parents, my sister and Catherine Cai

#### ACKNOWLEDGMENT

The author would like to express his sincere gratitude to his advisors, Professors Ziavras and Manikopoulos, for their guidance, insight and support throughout the process of producing this thesis.

My thanks are due to the other members of my thesis committee, Drs. E. Hou, M. Palis, H. Sun, and M. Zhou.

I am thankful to Catherine Cai for her support and encouragement.

The work presented in this research was supported in part by the National Science Foundation under Grants CDA-9121475 and DMI-9500260.

## TABLE OF CONTENTS

| Chapter Page                                                           |  |

|------------------------------------------------------------------------|--|

| 1 INTRODUCTION                                                         |  |

| 1.1 Parallel Processing Systems1                                       |  |

| 1.1.1 Shared-Memory Multiprocessors2                                   |  |

| 1.1.2 Message-Passing Multicomputers                                   |  |

| 1.2 Message-Passing Versus Shared-Memory5                              |  |

| 1.3 Motivation, Objectives, and Contributions8                         |  |

| 1.4 Outline                                                            |  |

| 2 TURBONET: A MESSAGE-PASSING AND SHARED-MEMORY<br>HYBRID ARCHITECTURE |  |

| 2.1 The Texas Instruments TMS320C40 Processor10                        |  |

| 2.2 Hydra Boards11                                                     |  |

| 2.3 The Host System14                                                  |  |

| 2.4 The Hybrid Architecture of the TurboNet System14                   |  |

| 3 MULTIDIMENSIONAL CONVOLUTION                                         |  |

| 3.1 One-Dimensional Convolution Algorithms18                           |  |

| 3.2 Two-Dimensional Convolution Algorithm20                            |  |

| 3.3 Theoretical Analysis27                                             |  |

| 3.3.1 1-D Convolution27                                                |  |

| 3.3.2 2-D Convolution                                                  |  |

## TABLE OF CONTENTS (Continued)

| Chapter Page                                                    |

|-----------------------------------------------------------------|

| 3.4 Performance Results on TurboNet                             |

| 3.4.1 1-D Convolution                                           |

| 3.4.2 2-D Convolution                                           |

| 4 FAST FOURIER TRANSFORM                                        |

| 4.1 One-Dimensional FFT50                                       |

| 4.2 Two-Dimensional FFT54                                       |

| 4.3 Theoretical Analysis                                        |

| 4.3.1 1-D FFT                                                   |

| 4.3.2 2-D FFT                                                   |

| 4.4 Performance Results on TurboNet65                           |

| 4.4.1 1-D FFT65                                                 |

| 4.4.2 2-D FFT                                                   |

| 5 MATRIX MULTIPLICATION                                         |

| 5.1 Matrix Multiplication Algorithm77                           |

| 5.2 Theoretical Analysis                                        |

| 5.3 Performance Results on TurboNet95                           |

| 6 ADAPTIVE MULTIRESOLUTION STRUCTURES<br>FOR IMAGE SEGMENTATION |

## TABLE OF CONTENTS (Continued)

| Chapter Page                                       |     |

|----------------------------------------------------|-----|

| 6.1 Introduction                                   | 103 |

| 6.2 Algorithm to Generate RAG Pyramids on TurboNet | 105 |

| 6.3 Implementation on TurboNet                     | 108 |

| 6.4 Performance Results                            | 113 |

| 7 CONCLUSIONS                                      | 123 |

| APPENDIX A DSP ALGORITHMS                          | 125 |

| REFERENCES                                         | 130 |

## LIST OF TABLES

| Table   Page |                                                                                         |   |

|--------------|-----------------------------------------------------------------------------------------|---|

| 3.1          | Estimated running time for 1-D convolution with method 12                               | 9 |

| 3.2          | Estimated running time for 1-D convolution with method 22                               | 9 |

| 3.3          | The time ucal-1 (in nsecs) for 1-D convolution with method 1                            | 0 |

| 3.4          | The time ucal-2 (in nsecs) for 1-D convolution with method 2                            | 0 |

| 3.5          | The estimated running time of the hybrid version of the binary-tree algorithm3          | 6 |

| 3.6          | The estimated running time of the message-passing version of the binary-tree algorithm  | 7 |

| 3.7          | The estimated running time of the shared-memory version<br>of the binary-tree algorithm | 7 |

| 3.8          | The time u <sub>1</sub> (in nsecs) for the binary-tree algorithm                        | 7 |

| 3.9          | The time $u_{xx2}$ (in nsecs) for the binary-tree algorithm                             | 8 |

| 3.10         | The time $u_{xx3}$ (in nsecs) for the binary-tree algorithm                             | 8 |

| 3.11         | The time $u_{xx4}$ (in nsecs) for the binary-tree algorithm                             | 8 |

| 3.12         | Execution time for 1-D convolution with method 140                                      | 0 |

| 3.13         | Speedup of 1-D convolution with method 14                                               | 0 |

| 3.14         | Efficiency of 1-D convolution with method 14                                            | 0 |

| 3.15         | Execution time for 1-D convolution with method 24                                       | 0 |

| 3.16         | Speedup of 1-D convolution with method 24                                               | 1 |

| 3.17         | Efficiency of 1-D convolution with method 24                                            | 1 |

| 3.18         | Execution time for the hybrid version of the binary-tree algorithm                      | 4 |

| Tabl | e Page                                                                                         |

|------|------------------------------------------------------------------------------------------------|

| 3.19 | Speedup of the hybrid version of the binary-tree algorithm                                     |

| 3.20 | Efficiency of the hybrid version of the binary-tree algorithm                                  |

| 3.21 | Execution time for the message-passing version of the binary-tree algorithm44                  |

| 3.22 | Speedup of the message-passing version of the binary-tree algorithm45                          |

| 3.23 | Efficiency of the message-passing version of the binary-tree algorithm45                       |

| 3.24 | Execution time for the shared-memory version of the binary-tree algorithm45                    |

| 3.25 | Speedup of the shared-memory version of the binary-tree algorithm45                            |

| 3.26 | Efficiency of the shared-memory version of the binary-tree algorithm45                         |

| 3.27 | The communication time (in $\mu$ sec) between P <sub>i</sub> and P <sub>i+1</sub> in stage 249 |

| 3.28 | The communication time (in $\mu$ sec) between P <sub>i</sub> and P <sub>i-2</sub> in stage 349 |

| 3.29 | The communication time (in $\mu$ sec) between P <sub>i</sub> and P <sub>i-4</sub> in stage 449 |

| 4.1  | The estimated running time for 1-D FFT with message-passing61                                  |

| 4.2  | The estimated running time for 1-D FFT with shared-memory61                                    |

| 4.3  | The sequential time u (in nsecs) of 1-D FFT                                                    |

| 4.4  | The time ump (in nsecs) of 1-D FFT with message-passing61                                      |

| 4.5  | The time usm (in nsecs) of 1-D FFT with shared-memory                                          |

| 4.6  | The estimated running time for 2-D FFT for $2k < (N/P)$ with shared-memory64                   |

| 4.7  | The sequential time u (in nsecs) of 2-D FFT                                                    |

| 4.8  | The time uDRAM (in nsecs) for matrix transposition of 2-D FFT                                  |

| Tabl | Table   Page                                                                                          |  |

|------|-------------------------------------------------------------------------------------------------------|--|

| 4.9  | Execution time for 1-D FFT with message-passing                                                       |  |

| 4.10 | Speedup of 1-D FFT with message-passing                                                               |  |

| 4.11 | Efficiency of 1-D FFT with message-passing67                                                          |  |

| 4.12 | Execution time for 1-D FFT with shared-memory67                                                       |  |

| 4.13 | Speedup of 1-D FFT with shared-memory67                                                               |  |

| 4.14 | Efficiency of 1-D FFT with shared-memory                                                              |  |

| 4.15 | Execution time for 2-D FFT (without matrix transposition)71                                           |  |

| 4.16 | Speedup of 2-D FFT (without matrix transposition)71                                                   |  |

| 4.17 | Efficiency of 2-D FFT (without matrix transposition)71                                                |  |

| 4.18 | Execution time for 2-D FFT (with matrix transposition)71                                              |  |

| 4.19 | Speedup of 2-D FFT (with matrix transposition)72                                                      |  |

| 4.20 | Efficiency of 2-D FFT (with matrix transposition)72                                                   |  |

| 4.21 | Execution time for 2-D FFT with the improved method74                                                 |  |

| 4.22 | Speedup of 2-D FFT with the improved method75                                                         |  |

| 4.23 | Efficiency of 2-D FFT with the improved method75                                                      |  |

| 5.1  | Estimated running time for matrix multiplication on 0-D and 1-D hypercubes87                          |  |

| 5.2  | The times u <sub>(2p, xx)</sub> (in nsecs) for matrix multiplication<br>on the 0-D and 1-D hypercubes |  |

| 5.3  | The times $u_{xx}$ (in nsecs) for matrix multiplication on the 1-D hypercube                          |  |

..

| Tab  | le Page                                                                                                                                                   |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.4  | Estimated running time for matrix multiplication with the 2-D hypercube90                                                                                 |

| 5.5  | The times $u_{(4p, xx)}$ (in nsecs) for matrix multiplication with the 2-Dhypercube90                                                                     |

| 5.6  | Estimated running time for matrix multiplication with the 3-D hypercube                                                                                   |

| 5.7  | The times $u_{(8p. xx)}$ (in nsecs) for matrix multiplication with the 3-D hypercube94                                                                    |

| 5.8  | Execution time of matrix multiplication on the 1-D hypercube                                                                                              |

| 5.9  | Speedup of matrix multiplication for the 1-D hypercube                                                                                                    |

| 5.10 | Efficiency of matrix multiplication for the 1-D hypercube                                                                                                 |

| 5.11 | Execution time of matrix multiplication on the 2-D hypercube                                                                                              |

| 5.12 | Speedup of matrix multiplication for the 2-D hypercube                                                                                                    |

| 5.13 | Efficiency of matrix multiplication for the 2-D hypercube                                                                                                 |

| 5.14 | Execution time of matrix multiplication on the 3-D hypercube100                                                                                           |

| 5.15 | Speedup of matrix multiplication for the 3-D hypercube                                                                                                    |

| 5.16 | Efficiency of matrix multiplication for the 3-D hypercube100                                                                                              |

| 5.17 | Two implementation results of matrix multiplication on the 0-D hypercube.<br>Cal.: calculation time only, Inp. & Cal.: data input and calculation time102 |

| 6.1  | Function codes for communication operations111                                                                                                            |

| 6.2  | Execution time and numbers of pyramid levels for a single processor115                                                                                    |

| 6.3  | Execution time for the message-passing version with $P = 2$ 116                                                                                           |

| 6.4  | Execution time for the shared-memory version with $P = 2$                                                                                                 |

| Tab  | le I                                                                            | <b>Page</b> |

|------|---------------------------------------------------------------------------------|-------------|

| 6.5  | Execution time for the hybrid version with $P = 2$                              | .117        |

| 6.6  | Execution time for the hybrid version with P = 2 and separate<br>Phases 4 and 5 | .117        |

| 6.7  | Execution time for the message-passing version with $P = 4$                     | .118        |

| 6.8  | Execution time for the shared-memory version with $P = 4$                       | .119        |

| 6.9  | Execution time for the hybrid version with $P = 4$                              | .119        |

| 6.10 | Execution time for the hybrid version with P = 4 and separate<br>Phases 4 and 5 | .119        |

| 6.11 | Execution time for the message-passing version with $P = 8$                     | .120        |

| 6.12 | Execution time for the shared-memory version with $P = 8$                       | .120        |

| 6.13 | Execution time for the hybrid version with $P = 8$                              | .121        |

## LIST OF FIGURES

| Figu | Figure Page                                                                                                      |  |  |

|------|------------------------------------------------------------------------------------------------------------------|--|--|

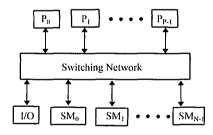

| 1.1  | The UMA multiprocessor model2                                                                                    |  |  |

| 1.2  | The NUMA multiprocessor model                                                                                    |  |  |

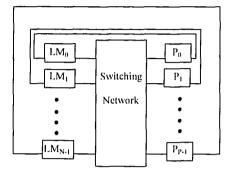

| 1.3  | A multicomputer                                                                                                  |  |  |

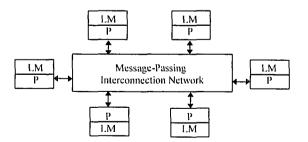

| 1.4  | Examples of common network topologies5                                                                           |  |  |

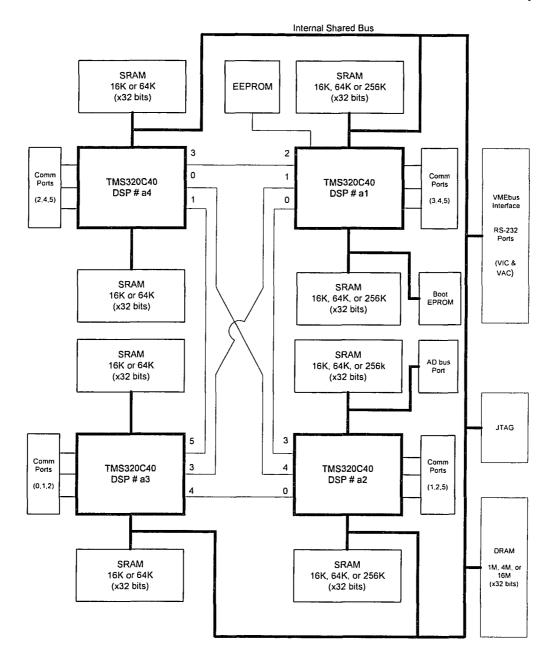

| 2.1  | The Hydra block diagram13                                                                                        |  |  |

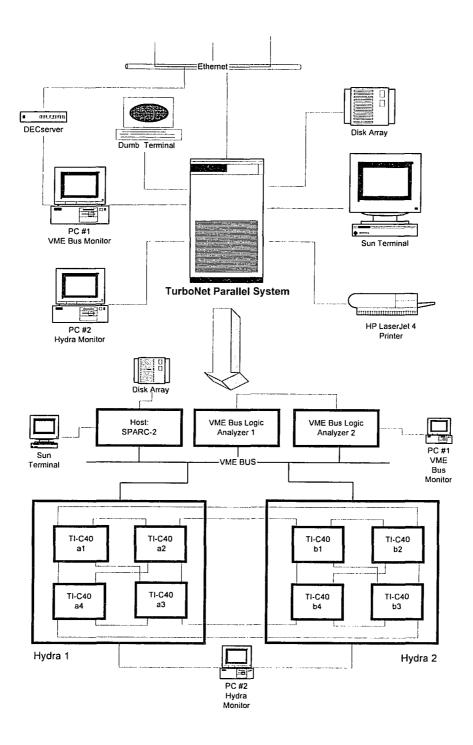

| 2.2  | The interconnection diagram of TurboNet16                                                                        |  |  |

| 3.1  | An example of one-dimensional convolution19                                                                      |  |  |

| 3.2  | An example of 2-D convolution                                                                                    |  |  |

| 3.3  | The data dependencies for convolution of two 4x4 matrices                                                        |  |  |

| 3.4  | An example of the binary-tree method23                                                                           |  |  |

| 3.5  | An example of the grid method25                                                                                  |  |  |

| 3.6  | An example of the triangle method                                                                                |  |  |

| 3.7  | DDG of the binary-tree algorithm with 8 processors                                                               |  |  |

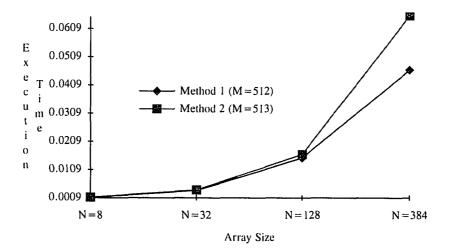

| 3.8  | Execution time of 1-D convolution (method 1 Vs method 2), with $P = 8$ 41                                        |  |  |

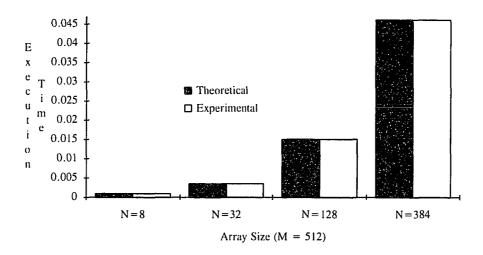

| 3.9  | A comparison of theoretical and experimental running times for method 142                                        |  |  |

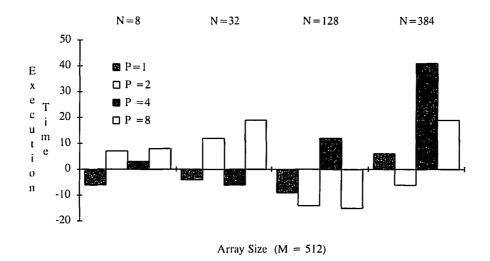

| 3.10 | The difference between theoretical and experimental running times<br>for method 1                                |  |  |

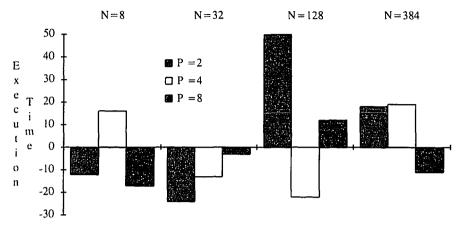

| 3.11 | The difference of theoretical and experimental running times from method 243                                     |  |  |

| 3.12 | The difference in execution times between the message-passing<br>and hybrid versions, in this order, for $P = 8$ |  |  |

## LIST OF FIGURES (Continued)

| Figu | Figure Page                                                                                                    |  |

|------|----------------------------------------------------------------------------------------------------------------|--|

| 3.13 | A comparison of theoretical and experimental running times<br>of the hybrid version for $P = 8$                |  |

| 3.14 | The difference of theoretical and experimental running times<br>from the hybrid version                        |  |

| 3.15 | The difference of theoretical and experimental running times<br>for the message -passing version47             |  |

| 3.16 | The difference of theoretical and experimental running times<br>for the shared-memory version                  |  |

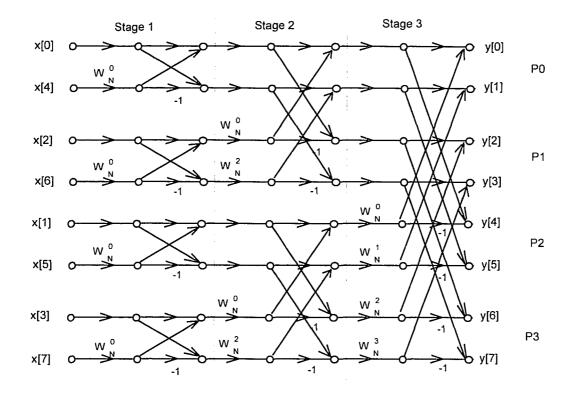

| 4.1  | Data flow graph of an 8-point decimation-in-time DFT52                                                         |  |

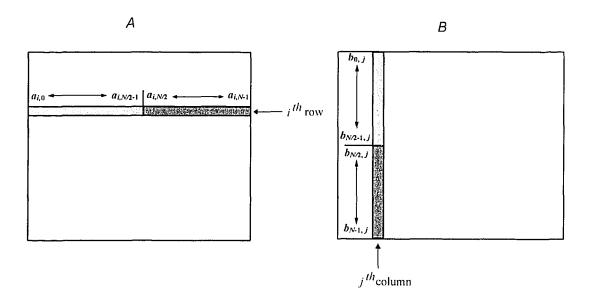

| 4.2  | An example of accessing row data for the FFT, with $P = 4$ and $2k < (N/P)$                                    |  |

| 4.3  | An example of transferring data for the FFT, with $P = 4$ and $2k \ge (N/P)$                                   |  |

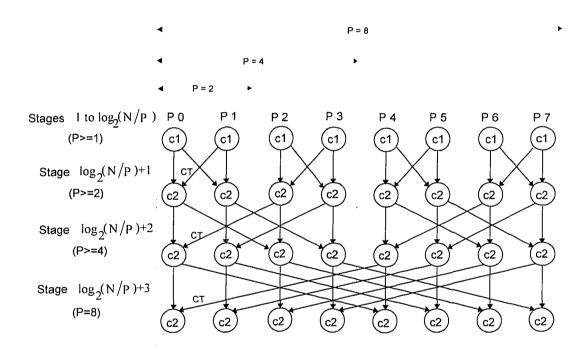

| 4.4  | DDG of the 1-D FFT with $P = 8$                                                                                |  |

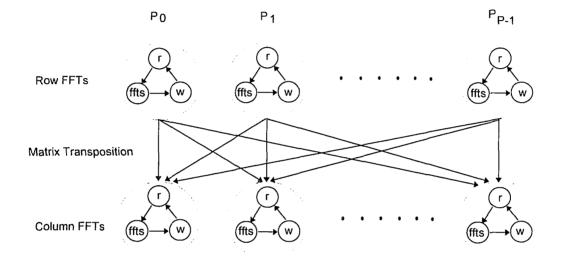

| 4.5  | DDG of the 2-D FFT algorithm for $2k < (N/P)$                                                                  |  |

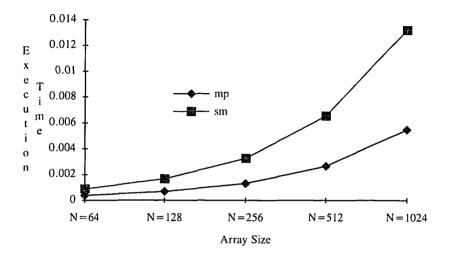

| 4.6  | Execution time for 1-D FFT Vs array size, with $P = 8$                                                         |  |

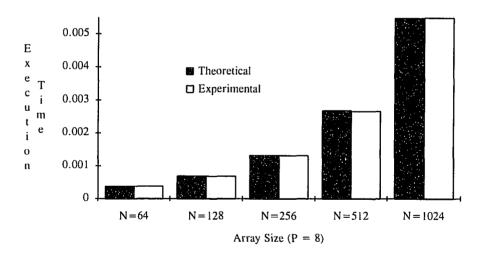

| 4.7  | Comparison of theoretical and experimental running times<br>for 1-D FFT with message-passing                   |  |

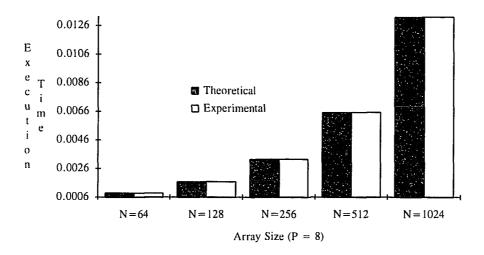

| 4.8  | Comparison of theoretical and experimental running times<br>for 1-D FFT with shared-memory                     |  |

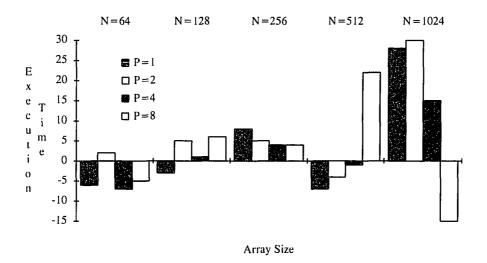

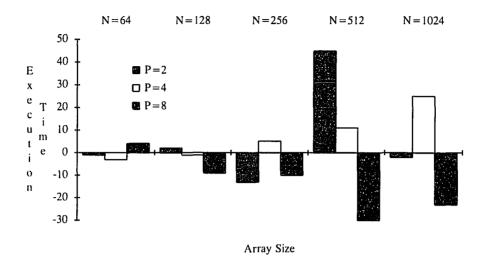

| 4.9  | The difference of theoretical and experimental running times<br>for the message-passing version of 1-D FFT69   |  |

| 4.10 | The difference of theoretical and experimental running times<br>for the shared-memory version of the 1-D FFT70 |  |

## LIST OF FIGURES (Continued)

| Figu | Figure Page                                                                                  |  |  |

|------|----------------------------------------------------------------------------------------------|--|--|

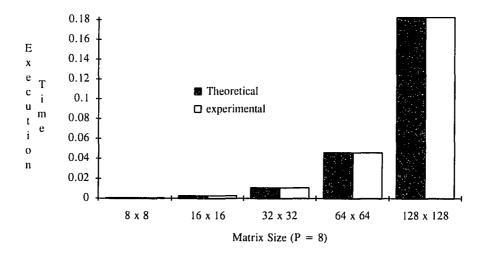

| 4.11 | Comparison of theoretical and experimental running times<br>for 2-D FFT with shared-memory72 |  |  |

| 4.12 | The difference of theoretical and experimental running times for 2-D FFT73                   |  |  |

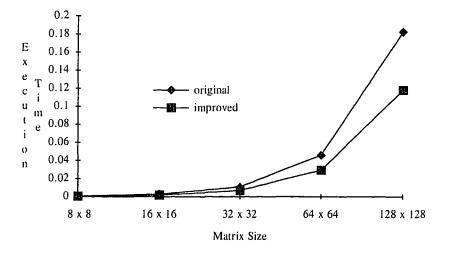

| 4.13 | Execution time for 2-D FFT vs matrix size, with $P = 8$                                      |  |  |

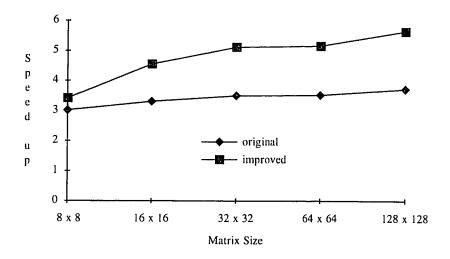

| 4.14 | Speed up of 2-D FFT vs matrix size, with $P = 8$                                             |  |  |

| 5.1  | The decomposition for c <sub>ij</sub>                                                        |  |  |

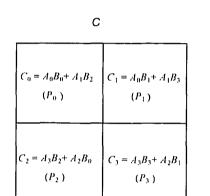

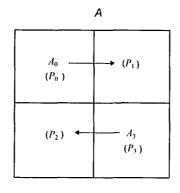

| 5.2  | The decomposition of the matrices A, B and C for four processors                             |  |  |

| 5.3  | The communication scheme according to Equation 5.3                                           |  |  |

| 5.4  | The decomposition of the matrices A and B for the 3-D hypercube                              |  |  |

| 5.5  | The decomposition of matrices A, B and C for the 1-D hypercube83                             |  |  |

| 5.6  | DDG of matrix multiplication for the 1-D hypercube                                           |  |  |

| 5.7  | DDG of matrix multiplication for the 2-D hypercube                                           |  |  |

| 5.8  | DDG of matrix multiplication for $P_0$ of the 3-D hypercube91                                |  |  |

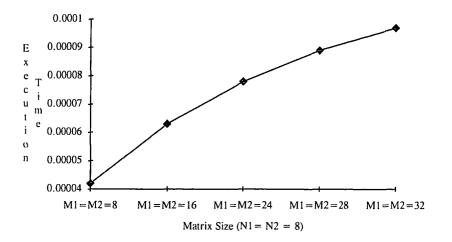

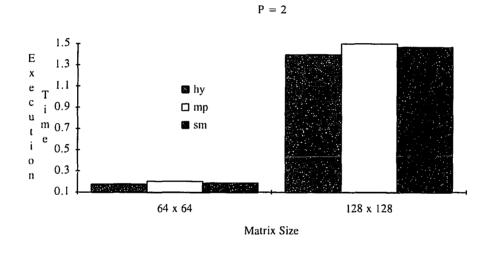

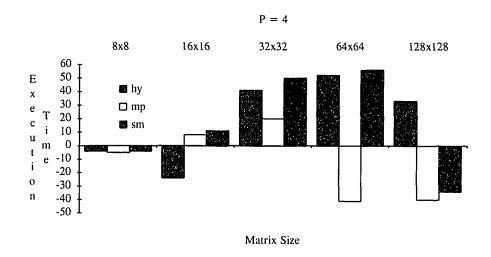

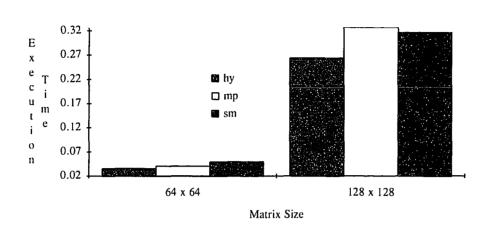

| 5.9  | Performance comparision of the three versions for the 1-D hypercube96                        |  |  |

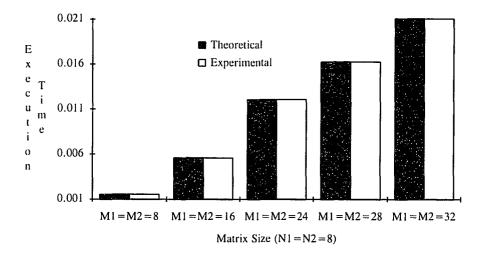

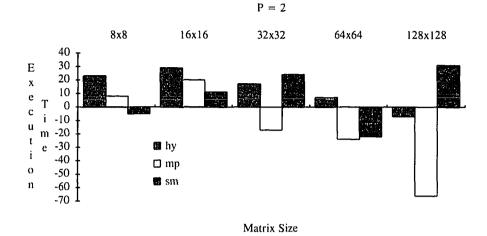

| 5.10 | The difference of theoretical and experimental timings for the 1-D hypercube97               |  |  |

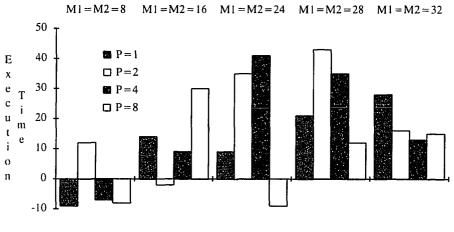

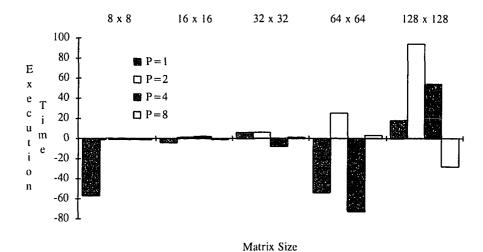

| 5.11 | Performance comparision of the three versions for the 2-D hypercube                          |  |  |

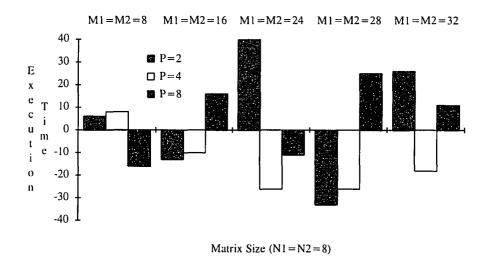

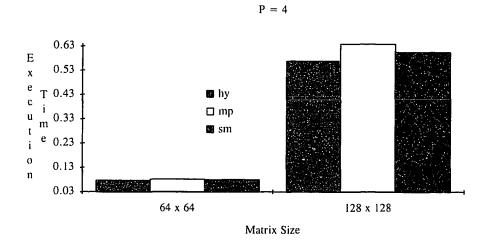

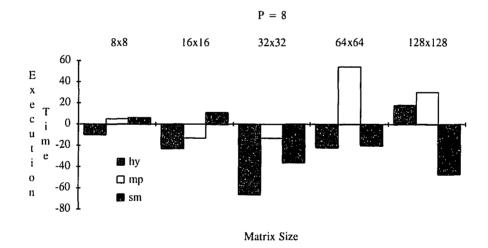

| 5.12 | Difference of theoretical and experimental timings for the 2-D hypercube                     |  |  |

| 5.13 | Derformance comparision of the three versions for the 3-D hypercube101                       |  |  |

| 5.14 | Difference of theoretical and experimental timings for the 3-D hypercube101                  |  |  |

## LIST OF FIGURES (Continued)

| Figure     Page |                                                                                                                                                 |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.1             | An example for Phases 4 and 5107                                                                                                                |

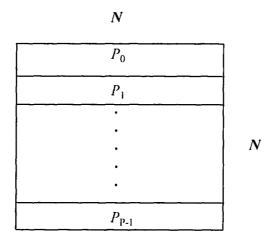

| 6.2             | Assignment of data for an NxN input image110                                                                                                    |

| 6.3             | A 32-bit long communication package                                                                                                             |

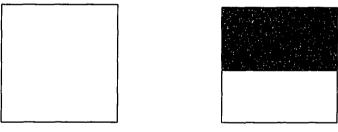

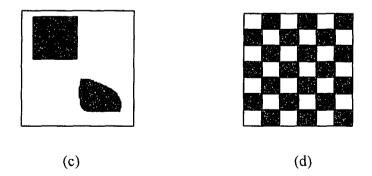

| 6.4             | Four types of images used in testing: (a) Uniform, (b) Horizontal half,<br>(c) Three objects, including the background, and (d) Checkerboard114 |

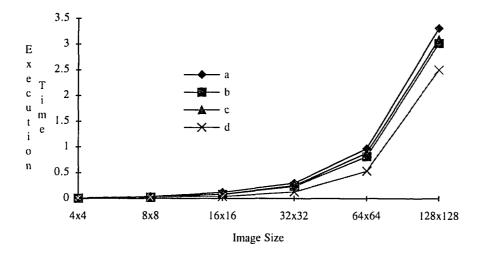

| 6.5             | Execution time vs. image types for the hybrid version with $P = 4$ 120                                                                          |

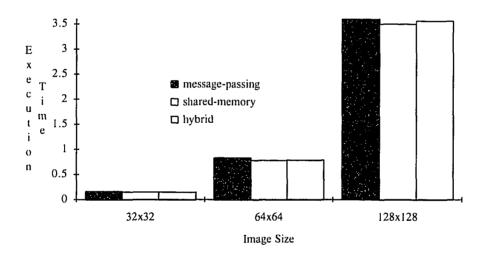

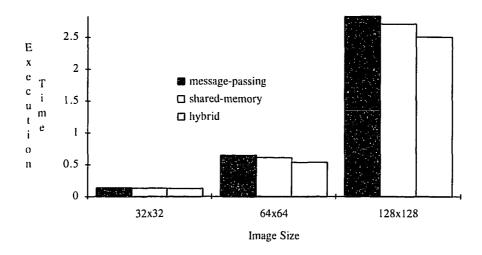

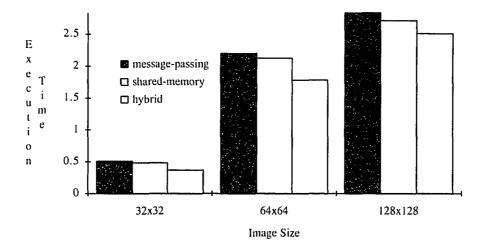

| 6.6             | Performance comparison of the three versions with image d and $P = 2$ 121                                                                       |

| 6.7             | Performance comparison of the three versions with image d and $P = 4$ 122                                                                       |

| 6.8             | Performance comparison of the three versions with image d and $P = 8$                                                                           |

#### **CHAPTER 1**

#### **INTRODUCTION**

Parallel processing has become the most prominent technology in achieving high performance computational power. One of the key problems to be solved with this technology is to determine how individual processes cooperate with each other efficiently when carrying out a task together. In general, message-passing and shared-memory are two techniques parallel computer systems use for coordination and communication, and they will be the focus of this dissertation. This chapter provides an introductory background in this fast growing research area. The motivations and objectives of our research, as well as an overview of its contributions, are also presented. An outline of the thesis is presented at the end.

#### **1.1 Parallel Processing Systems**

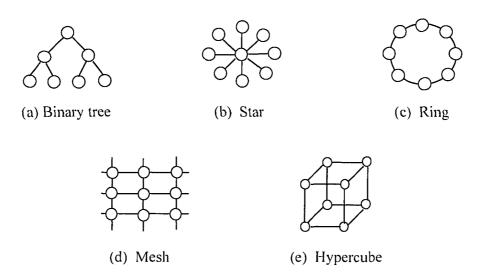

A parallel processing system consists of multiple processors (or nodes), memory modules, peripherals, and a switching or interconnection network. There are two major categories in classifying parallel processing systems: *shared-memory multiprocessors* and *message-passing multicomputers* [24]. The difference between them lies in how communication among nodes is carried out. The following two subsections give more details about these two categories.

-

#### 1.1.1 Shared-Memory Multiprocessors

In a shared-memory multiprocessor multiple processors share a common memory and some peripherals, and communication is performed through the shared memory by writing and reading it. Two shared-memory multiprocessor models are primarily used: the *uniform-memory-access* (UMA) model and the *nonuniform-memory-access* (NUMA) model [36]. They differ in the way the memory and other resources are distributed. In the UMA model, as shown in Figure 1.1, all processors have equal access time to all memory locations in all shared-memory modules (marked as SM) under the condition of no network congestion, and that is why it is called uniform-memory-access model. In the NUMA model in Figure 1.2, however, accessing the local shared memory (marked as LM) is faster than accessing a remote one, because there is no need for a processor to go through the switching network when accessing the former.

Figure 1.1 The UMA multiprocessor model.

The most popular switching networks are single bus, crossbar, and multistage. The single bus can only handle one transaction at a time, employing a single source. The crossbar and multistage networks, built with extra hardware, can have more than one ongoing transaction. Hence, the single bus has low cost and low performance while the other two provide high bandwidth with higher cost.

Figure 1.2 The NUMA multiprocessor model.

#### 1.1.2 Message-Passing Multicomputers

$< \frac{1}{2}$

A message-passing multicomputer consists of multiple computers (or nodes) interconnected by a point-to-point network, and each node is an autonomous computer including a processor, a private local memory, and possibly disks or I/O peripherals, as modeled in Figure 1.3. Internode communication is carried out by passing messages through the network while observing certain communication protocols. Such actions may involve multiple links (i.e. physical connections between nodes) and nodes, if the source is not directly connected to the destination.

Some common network topologies in constructing interconnection networks for multicomputers are, as shown in Figure 1.4, binary tree, star, ring, mesh, hypercube, etc. They are also called static connection networks because all links between nodes are fixed after a network is built. Among these topologies, the hypercube has very high hardware complexity but it is very popular [38]. A *d*-dimensional hypercube consists of  $2^d$  nodes. each of which is connected to one other node in each dimension. For example, a 0dimensional hypercube, a 0-cube for short, has a single node with no communication channels, i.e. it is a standard sequential computer. A 1-cube is constructed from two 0cubes by connecting them with a single communication channel, and a 2-cube is formed with two 1-cubes by connecting their corresponding nodes via an additional channel. Figure 1.4(e) shows a 3-cube, containing two 2-cubes, and each node in each 2-cube has a connection to the corresponding node in the other 2-cube. Hence, in general, a *d*-cube is constructed by connecting corresponding pairs of nodes in two (*d*-1)-cubes with an additional channel. The number of nodes is  $P = 2^{d}$ . The number of connections per node and the maximum distance between two nodes are  $d = \log_2 P$ . The node number (i.e. its identification) is chosen to be a *d*-bit binary code where its *i*<sup>th</sup> bit represents the coordinate of the node in the *i*<sup>th</sup> dimension of the hypercube. The binary addresses of any two neighboring nodes differ in a single bit. The number of bits that differ between the addresses of two nodes gives the distance between them.

Figure 1.3 A multicomputer.

Figure 1.4 Examples of common network topologies.

#### 1.2 Message-Passing Versus Shared-Memory

In a general sense, the message-passing architecture is efficient for communicating small amounts of data in small distance. On the other hand, shared-memory is primarily used for I/O with the host, and for otherwise distant communications with large amounts of data. Additionally, the shared-memory paradigm simplifies the development of algorithms.

Chandra et. al. [10] studied the strengths and weaknesses of these two fundamental mechanisms of message-passing and shared-memory by comparing the performance of equivalent, well-written message-passing and shared-memory programs running on similar hardware. Each application program was produced in two versions and its performance was measured on closely-related simulators of a message-passing and a shared-memory machine. They found that three of the four shared-memory programs ran at roughly the same speed as their message-passing equivalents, even though their communication patterns were different. Therefore, the advantage of message-passing over shared-memory, or vice-versa, is not clear-cut, and this strongly suggests that parallel computers should support, if possible, both communication mechanisms.

Many parallel computer systems have been developed since the early 1980's, such as the nCUBE, Intel iPSC, Wavetracer, Cray Y-MP, MultiMax, Symmetry, and Connection-Machines CM-2 and CM-5. They primarily implement either the messagepassing or the shared-memory parallel processing paradigm. For example, the nCUBE, iPSC, and Connection Machine CM-2 [9] are message-passing machines, whereas the Cray Y-MP employs a shared-memory architecture. Many parallel Digital Signal Processing (DSP) algorithms have also been developed for either one of the two paradigms. For instance, Cvetanovic [7] analyzed the performance of a Fast Fourier Transform (FFT) algorithm for a shared-memory parallel architecture, and Fox [4] developed a matrix multiplication algorithm and an FFT algorithm targeting a messagepassing architecture.

Recently, the complementary nature of the shared-memory and message-passing communication mechanisms, together with the advance of underlying hardware technologies have led to a growing interest in hybrid architectures supporting both paradigms within a single parallel system. Emphasis has been given to the creation of distributed shared-memory systems, where all local memories of all processors in a message-passing system form a global address space. The underlying message-passing architecture is chosen because it supports system scalability. The Stanford FLASH Multiprocessor [11] is one of the few hybrid architectures of this kind that appeared in recent years. It integrates message-passing with shared-memory in a single architecture by using a programmable node controller, called MAGIC, to efficiently support both communication paradigms. MAGIC provides a tight coupling with the network and memory, and allows for efficient protocol handling through parallel implementation of control processing and data movement. Cache coherence for the shared memory can be carried out even during message transfer. Alewife [12] is another example of a hybrid architecture. Each Alewife node has a hardware controller to handle cache coherence, and a DMA unit (within the controller) to facilitate message passing. In addition, the main processor has an efficient memory-mapped interface to the controller that is used for controlling message sends. However, both systems are based on a message-passing architecture; shared-memory transactions are simulated by software.

In related work, Dowling et. al. [3] introduced and analyzed the Hybrid Array Ring Processor (HARP) architecture. HARP is an application specific architecture centered around a host processor, shared memory, and a set of memory-mapped processors connected into both an open backplane and a bidirectional systolic ring. The architecture implements both the message-passing and shared-memory paradigms and has been benchmarked through simulation of matrix multiplication, FFT, QR Decomposition, and Singular Value Decomposition algorithms, assuming the TMS34082 floating point RISC processor. The HARP system has not been built. In these simulations, the shared memory is used only for the purpose of distributing input data and collecting final results; data transfers during the execution of algorithms are all done through the systolic links of HARP. Thus, the HARP project does not integrate the message-passing and shared-memory paradigms during the execution of algorithms.

#### 1.3 Motivation, Objectives, and Contributions

It is our vision that a hardware combination of message-passing with shared-memory has potential advantages for many applications, and therefore should be investigated extensively for small-scale and medium-scale parallel computers. The current version of our TurboNet system, the target system in this dissertation, is an asynchronous three-dimensional hypercube system composed of eight powerful Texas Instruments TMS320C40 (C40 in brevity) DSP processor chips. We have built this system with two VME Hydra boards of Ariel Corp., where each board contains four C40's and shared-memory, in addition to local memory attached to each C40. The shared-memory of each board is also global so that it can be accessed by any of the eight processors via the shared VME bus. TurboNet has a more general architecture that implements directly in hardware both communication paradigms, in contrast to the proposed FLASH, Alewife, and HARP systems. Details about TurboNet follow in the next section.

The objectives of this dissertation are: (1) to employ simultaneously both the message-passing and shared-memory paradigms in the development of parallel DSP algorithms, such as one-dimensional (1-D) and two-dimensional (2-D) FFT and convolution, matrix multiplication, and image segmentation; (2) to develop highly accurate methodology for the theoretical assessment of algorithms during their design; (3)

to compare the performance of our algorithms that employ the hybrid communication paradigm (i.e. both the message-passing and shared-memory paradigms) with the performance of algorithms supporting only one of the two basic paradigms, in order to illustrate the superiority of the former.

Our results prove that several algorithms can take advantage of the hybrid architecture of our target system in order to achieve very impressive speedups. Therefore the main conclusion of this dissertation is that small-scale and medium-scale parallel computers should support directly in hardware, if possible, both the message-passing and shared-memory paradigms for good performance and versatility in algorithm development.

#### 1.4 Outline

This dissertation is organized as follows. Following this introduction, Chapter 2 provides a brief overview of our target TurboNet system, including a overview of the C40 and the Hydra architecture, and the main characteristics of the TurboNet system. In Chapters 3, 4, 5, and 6, algorithms for convolution, FFT, matrix multiplication, and image segmentation are introduced, and relevant performance analysis and experimental results are included. Chapter 7 presents the conclusions and further research objectives.

#### **CHAPTER 2**

#### TURBONET: A MESSAGE-PASSING AND SHARED-MEMORY HYBRID ARCHITECTURE

The TurboNet system is presented in this chapter. Three main aspects of the system are discussed here: the TMS320C40 DSP's, the Hydra boards, and the host board. From the architecture point of view, the TurboNet system implements in hardware both the message-passing and shared-memory paradigms, and this is what distinguishes it from other systems.

#### 2.1 The Texas Instruments TMS320C40 Processor

The TurboNet system currently contains eight C40's. The C40 has the following key features [32]:

- 1. Six 8-bit bidirectional half-duplex communication ports for high speed interprocessor communication.

- Six-channel DMA coprocessor for concurrent I/O and CPU operation, thereby maximizing sustained CPU performance by alleviating the CPU of burdensome I/O.

- High-performance DSP CPU capable of 275 MOPS and 320 Mbytes/sec of data-transfer rate.

- 4. Two identical external data and address buses supporting shared-memory systems and high data rate, single-cycle transfers. The 32 bit data buses are called the Global Bus and the Local Bus. Each bus is capable of addressing 2 Gwords (x32 bits) of address space for a total of 4 Gwords addressable by each C40.

- 5. On-chip analysis module supporting efficient, state of the art parallel processing debugging.

- On-chip program cache and dual-access/single-cycle RAM (2 KWords) for increased memory access performance.

- Separate internal program, data, and DMA coprocessor buses for support of massive concurrent I/O of program and data throughput, thereby maximizing sustained CPU performance.

#### 2.2 Hydra Boards

Hydra[31] is a single-slot 6U VME-based multi-digital signal processor (DSP) board, consisting of a base card and a daughter card, each one containing two C40 chips. Its block diagram is shown in Figure 2.1.

The global or local bus of each C40 is connected to a bank of fast zero-wait-state static memory which is private to the specific C40, that is, any of the DSP's can access its own SRAM without affecting the operations in any of the other DSP's. Each of the DSP's is, in fact, an independent processing node. Each of the DSP's can have 16 Kwords, 64 Kwords, or 256 Kwords (x32 bits) of SRAM in each of its two banks. In our system, the

SRAM's in Hydra 1 all contain 64 Kwords while there are 16 Kword SRAM's in Hydra 2.

Hydra has an Internal Shared Bus (ISB) to which the VME bus and the Global bus of each DSP are attached. The ISB provides access to a bank of DRAM (1 Mwords, 4 Mwords, or 16 Mwords in size; 1 Mwords in our system) and other shared resources. Any external VME master can also access the ISB. Isolation transceivers have been utilized to isolate all DSP modules and the VME bus from the ISB when they are not currently granted the ISB.

ISB requests from the VME bus always take higher priority over local DSP requests. ISB requests from the Hydra DSP's are arbitrated on a rotating priority scheme to make it impossible for one internal master to lock-out or 'starve' the other devices of the ISB. The ownership of the ISB is determined on a cycle-by-cycle basis. If the current master is a local DSP, ownership is challenged after that DSP completes its current ISB cycle. If that DSP is accessing DRAM or any ISB facility, the arbiter will test for new requesters between each access, even if the current owner is operating the DRAM in page mode.

Each C40 has six communication ports. Three of them are used within the board to implement a fully-connected system with four C40's. The remaining three communication ports are brought out to the front panel of Hydra for connections with multiple Hydra boards via microminiature, 25-pin D-sub connectors.

A monitor program, including a bootstrap, is stored in the EPROM attached to DSP1. The bootstrap will set up the VME interface, including the VME memory window

as seen by the internal ISB masters and the base offset of Hydra as seen by another VME bus master. In addition to the VME interface, the monitor also initializes the RS-232 port.

Figure 2.1 The Hydra block diagram.

After DSP1 is boot up by bootstrap, it will boot up the other three DSP's through their parallel communication ports. All the necessary configuration information for Hydra is stored in an EEPROM that is also attached to DSP1.

In our system, the Hydra device driver and the utility library are both made available to users. The former is a traditional UNIX device driver while the latter is a resource-mapping library, and they both are independent to each other. The driver can be a loadable one or it can be configured into the SunOS kernel.

## 2.3 The Host System

The host system, a SPARC CPU-2CE board, is a complete VME-based SPARCstation 2 architecture with Sbus expansion. It offers the same I/O interface as the SPARCstation 2, including DMA supported SCSI and Ethernet ports, along with audio, keyboard/mouse, and two serial channels with full modem support. Two Sbus sockets allow the installation of standard Sbus modules, such as graphics frame buffers, or accelerators, or any other of over 300 Sbus cards available. In our case, these two sockets are used for a monitor and a cache memory expansion card.

# 2.4 The Hybrid Architecture of the TurboNet System

The TurboNet system comprises a VME backplane, a SPARC CPU-2CE [29] host board, two Hydra boards, two hard disk drives, a floppy drive, a CDROM, a VME bus logic analyzer, and a dumb terminal, as depicted in Figure 2.2. There are four bidirectional links between the two Hydra boards, each of them connecting two C40's together in the two different boards. As mentioned earlier, three of the six communication ports of each DSP are dedicated to the interconnection of the four DSP's inside Hydra. A fourth port is used for an interboard connection. Ignoring the diagonal intraboard connections, the processors form a 3-dimensional hypercube. It is our intention to build a larger hypercube system with up to 64 C40's, thus the diagonal intraboard connections will be removed in the future in order to facilitate this goal. Therefore, these diagonal connections are ignored in this research.

As shown in Figure 2.1, each Hydra board has a shared memory (the DRAM) connected to all four DSP's by a single bus, the ISB. It can be accessed by the DSP's from inside and outside the board. The DSP's, however, when accessing the shared memory from the other board, would have to go through the VME bus before reaching it, i.e. the access time will be longer compared to accessing the local shared memory. This indicates that we have a UMA shared-memory model when dealing with one board and a NUMA shared-memory model when using both boards. And let us not forget that all these coexist with the message-passing hypercube connection in our TurboNet system. Both communication mechanisms (paradigms) can perform their functions at the same time, so that DSP's can talk to each other through communication ports and have their DMA controllers competing for the shared memory via their ISB's and/or VME bus. This hybrid architecture is like adding a new communication media to a system which has only one overcrowded communication space. It also provides options of communication paradigms to applications that may have interconnection bias in performance, such as 1-D FFT, as explained in Chapter 4.

Figure 2.2 The interconnection diagram of TurboNet.

In the course of the system integration, two major problems occurred. The two Hydra boards are different versions, and the older one can take only the low base address in the VME bus while the recent version can use any base address available. The other problem is the malfunction of three communication ports in DSP7 (b3) of the second Hydra board. Due to this reason, its connection with DSP4 (a4) of the first Hydra board goes through DSP5 (b1) of the second Hydra board instead of going to a4 directly. This is not shown in Figure 2.2.

## **CHAPTER 3**

## MULTIDIMENSIONAL CONVOLUTION

In this chapter algorithms are presented for 1-D and 2-D convolution on the TurboNet system. Theoretical analysis of the algorithms and performance results of their implementation are also included. All running times in this thesis are expresses in seconds unless specified otherwise. There are two algorithms for 1-D convolution. They do not require any communication between processors. For 2-D convolution, all three communication paradigms have been implemented, namely message-passing, shared-memory and a combination of both (the hybrid paradigm).

### 3.1 One-Dimensional Convolution Algorithms

Given two sequences of numbers f[0], f[1], ..., f[N-1] and g[0], g[1], ..., g[M-1], 1-D convolution produces a sequence y of length N+M-1, where

$$y[i] = \sum_{j=0}^{N-1} f[j]g[i-j]$$

(3.1)

for i = 0, 1, ..., N+M-2. Let us consider an example of this convolution with  $f = \{1,4,2\}$ and  $g = \{1,2,3,1\}$ . The result of convolution is shown in Figure 3.1.

From the figure we can see that each element of y is generated by one or more multiplications of some elements from f and g, and zero or more subsequent additions. Suppose we have two processors to perform this convolution. One way to implement this

is to let processor  $P_0$  calculate y[0], y[1], y[4] and y[5], while let processor  $P_1$  calculate y[2] and y[3]. Another way is to let processor  $P_0$  calculate y[0], y[1] and y[2], while let processor  $P_1$  calculate y[3], y[4] and y[5]. In *method* 1, if there are P processors, where 1  $< P \le M$ , each one of them calculates M/P results in the first phase. For example,  $P_0$  calculates y[0], y[1], ..., y[M/P-1],  $P_1$  calculates y[M/P], y[M/P+1], ..., y[2M/P-1], etc. In the second phase, each of the first  $\lceil (N-1)P/M \rceil$  processors calculates up to M/P results from y[M] to y[M+N-2]. In *method* 2,  $P_0$  calculates the first (M+N-1)/P results while  $P_1$  calculates the second (M+N-1)/P results, and so on; we assume that M/P and (M+N-1)/P are integer numbers. In method 1 each processor has almost the same amount of computation, but in method 2 processors that generate the central portion of the output array have more calculation load than the others, and therefore good load balancing is rarely accomplished. As a result, method 1 will generally have better performance than method 2. In both methods, as the algorithms were designed, no communication is necessary between processors.

$$y[0] = f[0]g[0] = 1x1$$

$$y[1] = f[0]g[1] + f[1]g[0] = 1x2 + 4x1$$

$$y[2] = f[0]g[2] + f[1]g[1] + f[2]g[0] = 1x3 + 4x2 + 2x1$$

$$y[3] = f[0]g[3] + f[1]g[2] + f[2]g[1] = 1x1 + 4x3 + 2x2$$

$$y[4] = f[1]g[3] + f[2]g[2] = 4x1 + 2x3$$

$$y[5] = f[2]g[3] = 2x1$$

Figure 3.1 An example of one-dimensional convolution.

#### 3.2 Two-Dimensional Convolution Algorithm

The basic definition of two-dimensional convolution is

$$c[x,y] = \sum_{i=0}^{N_{1}-1} \sum_{j=0}^{N_{2}-1} f[i,j]g[x-i,y-j]$$

(3.2)

where  $x = 0, 1, 2, ..., N_1 + M_1 - 2, y = 0, 1, 2, ..., N_2 + M_2 - 2$ , and the lengths of  $f[n_1, n_2]$  and  $g[m_1, m_2]$  in the first dimension are  $N_1$  and  $M_1$ , respectively, whereas they are  $N_2$  and  $M_2$ , respectively, in the second dimension. In the following discussion we assume that  $N_1$  and  $M_1$  are powers of 2.

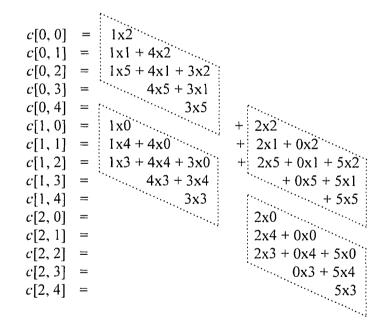

As an example, let us consider two-dimensional convolution with  $f = \begin{cases} 1,4,3\\2,0,5 \end{cases}$

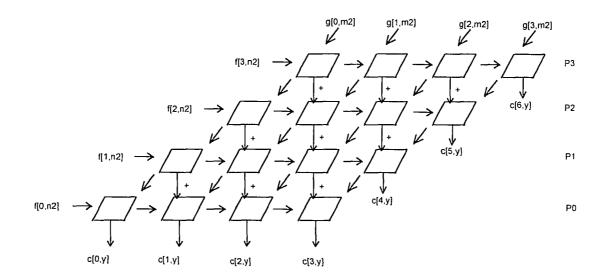

and  $g = \begin{cases} 2,1,5\\0,4,3 \end{cases}$ . Figure 3.2 (a) shows the operations to be performed. If operations involving distinct pairs of rows from *f* and *g*, respectively, are grouped together with distinct parallelograms, then four such parallelograms are obtained, as in Figure 3.2 (b). If we rotate this figure counter-clockwise by 90 degrees, then the parallelograms derived for the convolution of two 4x4 matrices and the data dependencies for obtaining the resulting matrix are shown in Figure 3.3. Again each parallelogram in Figure 3.3 represents the convolution of a pair of rows from *f* and *g*, respectively.

| c[0, 0] = f[0, 0]g[0, 0]  |                               |                                                          |                                     |

|---------------------------|-------------------------------|----------------------------------------------------------|-------------------------------------|

| c[0, 1] = f[0,0] g[0,1] + | f[0,1]g[0,0]                  |                                                          |                                     |

| c[0, 2] = f[0,0] g[0,2] + | f[0,1]g[0,1]+f[0,2]g[0,0]     | ]                                                        |                                     |

| c[0, 3] =                 | f[0,1]g[0,2]+f[0,2]g[0,1]     | -                                                        |                                     |

| c[0, 4] =                 | f[0,2]g[0,2]                  | ]                                                        |                                     |

| c[1, 0] = f[0, 0] g[1, 0] |                               | + f[1,0]g[0,0]                                           |                                     |

| c[1, 1] = f[0,0] g[1,1] + | <i>f</i> [0,1] <i>g</i> [1,0] | + f[1,0]g[0,1]+f[1,1]g                                   | [0,0]                               |

| c[1, 2] = f[0,0] g[1,2]+  | f[0,1]g[1,1]+f[0,2]g[1,0]     | ] + f[1,0]g[0,2] + f[1,1]g                               | [0,1]+f[1,2]g[0,0]                  |

| c[1, 3] =                 | f[0,1]g[1,2]+f[0,2]g[1,1]     | +f[1,1]g                                                 | [0,2]+f[1,2]g[0,1]                  |

| c[1, 4] =                 | <i>f</i> [0,2] <i>g</i> [1,2] | ]                                                        | +f[1,2]g[0,2]                       |

| c[2, 0] =                 |                               | <i>f</i> [1,0] <i>g</i> [1,0]                            |                                     |

| c[2, 1] =                 |                               | f[1,0]g[1,1]+f[1,1]g[                                    | [1,0]                               |

| c[2, 2] =                 |                               | <i>f</i> [1,0] <i>g</i> [1,2]+ <i>f</i> [1,1] <i>g</i> [ | 1,1]+ <i>f</i> [1,2] <i>g</i> [1,0] |

| c[2, 3] =                 |                               | <i>f</i> [1,1] <i>g</i>                                  | [1,2]+f[1,2]g[1,1]                  |

| c[2, 4] =                 |                               |                                                          | <i>f</i> [1,2] <i>g</i> [1,2]       |

|                           |                               |                                                          |                                     |

(a) An expansion of Equation 3.2 with the data arrays f and g.

(b) The convolution parallelograms.

Figure 3.2 An example of 2-D convolution.

Figure 3.3 The data dependencies for convolution of two 4x4 matrices.

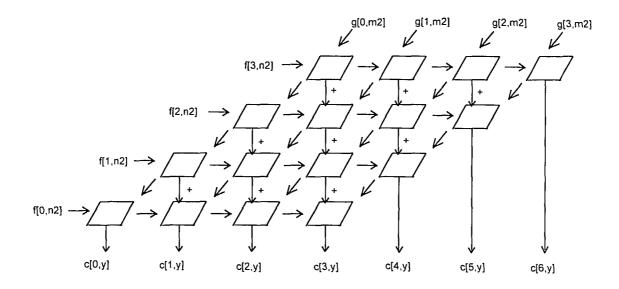

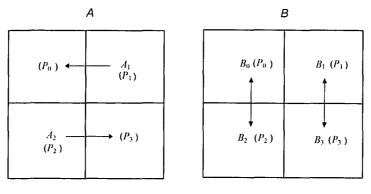

Suppose we have a hypercube system of four processors to perform this convolution. Each processor could be responsible for the calculations in one row of parallelograms in Figure 3.3. The final result will spread unevenly among the processors, so that processor  $P_0$  will have c[0,y], c[1,y], c[2,y] and c[3,y], whereas processors  $P_1$ ,  $P_2$  and  $P_3$  will have c[4,y], c[5,y] and c[6,y], respectively. This is shown in Figure 3.4. In the first stage of this algorithm, each processor performs the operations of all the parallelograms assigned to it. In the second stage, processors  $P_1$  and  $P_3$  send the results of their first three parallelograms to processors  $P_0$  and  $P_2$ , respectively, and the receivers add them to their corresponding results. In the final stage, processor  $P_2$  sends the results of its first two parallelograms to processor  $P_0$  and the third one to processor  $P_1$ , and again the

receivers add them to their corresponding results. We call this method of parallel convolution the *binary-tree method* because of the pairwise additions in rows.

Figure 3.4 An example of the binary-tree method.

It is important to mention that data transfers can be avoided altogether by combining pairs of columns, so that the number of parallelograms in each column becomes  $N_1$  (similar to method 1 of 1-D convolution). This is accomplished in Figure 3.3 by combining the linear arrays that produce the pairs (c[0,y], c[4,y]), (c[1,y], c[5,y]) and (c[2,y], c[6,y]). However, such an implementation is neglected here because programming such a task is more difficult in the general case. Also such an implementation could not be used to investigate the capabilities of TurboNet's hybrid communication architecture.

With P processors (P > 1), where P is assumed to be a power of 2, the binary-tree algorithm will have  $\log_2 P + 1$  stages, and each processor will have  $N_1/P$  rows of

parallelograms  $(N_1/P \text{ is an integer})$ .  $P_0$  will have c[0,y], c[1,y], ...,  $c[M_1-2+N_1/P, y]$  of the final result, and  $P_i$  will have  $c[M_1-1+i N_1/P, y]$ , ...,  $c[M_1-2+(i+1)N_1/P, y]$ , for i = 1, 2, ..., P-1.

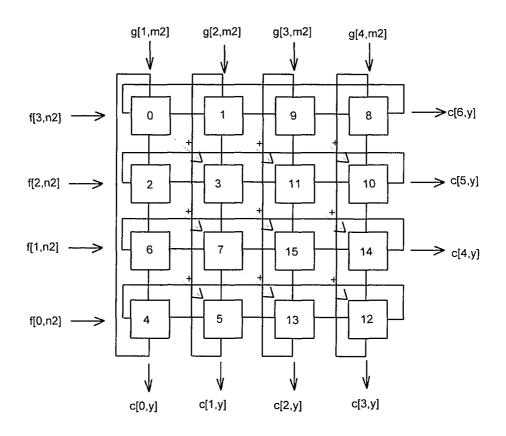

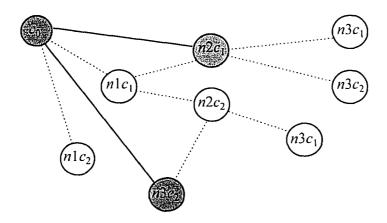

Now suppose we have a 4-dimensional hypercube with 16 processors. To perform the two-dimensional convolution, we can assign each of the 16 parallelograms in Figure 3.3 to a processor in the hypercube, so that the convolution of  $f[3, n_2]$  and  $g[0, m_2]$  goes to processor  $P_0$ , the convolution of  $f[3, n_2]$  and  $g[1, m_2]$  goes to processor  $P_1$  and so on, as shown in Figure 3.5. The arrows for values of f and g do not represent systolic array processing as in [37, 38, 39]. Each arrow implies that all processors on the corresponding row or column initially obtain the same values of f or g. After each processor finishes its 1-D convolution, except for those processors on the south and east borders, it has to send the result to its south-east neighbor, and the final result will be distributed among the processors on the south and east borders. We call this the *grid method*.

In the grid method, all communications are non-local, and they are most likely done efficiently through shared-memory. A binary Gray code is used for the assignment of parallelograms to processors, and each communication is between processors whose distance is equal to 2. The Gray codes for rows and columns are chosen, so that each set of four processors in each quadrant belong to the same Hydra board. This scheme minimizes the number of VME bus accesses.

Figure 3.5 An example of the grid method.

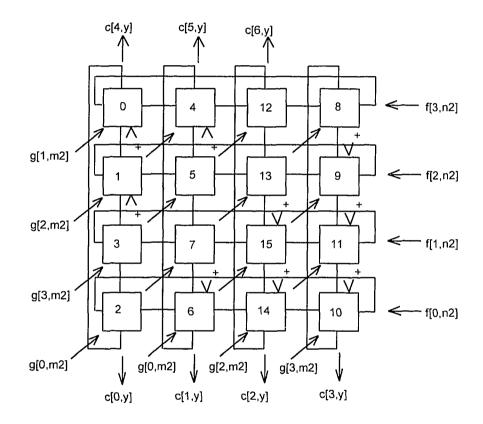

To also make efficient use of the message-passing capability of our target system, we invent another method, called the *triangle method*. The profile in Figure 3.3 is also a parallelogram. If we cut its right angle along the dashed line and paste it in the left side of the parallelogram, we have a square configuration. We then assign each parallelogram to a processor of the hypercube as shown in Figure 3.6. In the figure each row and column number is transformed according to the binary reflected Gray code. To obtain the address of a hypercube processor, we concatenate the corresponding transformed column and row numbers. This process results in optimal mapping of a mesh to the hypercube. Again, the

address assignment in this algorithm intents to let all the processors in the same column of Figure 3.6 share the same-board DRAM, and therefore avoid going through the VME bus.

Figure 3.6 An example of the triangle method.

After each processor is done with its 1-D convolution, all processors in the lowerright triangle (including the diagonal processors) transfer their results to their lowervertical neighbors, while the processors in the upper-left triangle send theirs to their upper neighbors, as indicated in Figure 3.6. The final result will be distributed among the processors in the upper and lower sides of the mesh. All data transfers are between neighbors.

In general, for both the grid and triangle methods each processor might be assigned more than one parallelogram. In this case, after calculating the convolutions of its assigned parallelograms, the processor has to transfer different parallelograms to different processors. We did not implement these two methods. Only the binary-tree method was implemented on TurboNet because of its simplicity in programming. We, however, consider these as interesting problems for further research. Algorithms for all methods are shown in Appendix A.

### 3.3 Theoretical Analysis

Theoretical analysis for 1-D and 2-D convolution is presented in this section. Since the algorithms for 1-D convolution do not need any communication, no Data Dependence Graph (DDG) is presented. For the algorithm of 2-D convolution, three communication strategies are discussed and the DDG is also provided for theoretical estimation of the algorithm's performance.

# 3.3.1 1-D Convolution

1-D convolution of two arrays is as defined in Equation 3.1. Its running time on a single processor is

$$t_{\rm sq1}(M) = 2 MN t_{\rm cal} = O(M^2)$$

(3.3)

for  $M \ge N$ , where *M* and *N* are the sizes of the two data arrays, and  $t_{cal}$  is the time for one multiplication or one addition. Since no communication is involved, the execution times of both methods for 1-D convolution consist of calculation times only. In both methods, let *P*, the number of processors, be a power of 2,  $P \le M$  and  $M \ge N$ . In method 1, let M/P be an integer. Because the workload is balanced among the processors, each one of them performs MN/P multiplications and additions. The total running time is therefore

$$t_{m1}(M) = 2MN/Pt_{cal} = O(M^2/P)$$

(3.4)

In method 2, n = (M + N - 1)/P is assumed to be an integer. Here each processor calculates *n* consecutive elements of the result. Since the numbers of operations required for different output elements may differ, this method does not generally balance the workload among the processors. The processor(s) that produces the central portion of the output array *y* corresponds to the longest running time. The maximum number of multiplications/additions the processor might have to perform is

Nn - ((P/2+1)n - M)((P/2+1)n - M+1)/2 if (P/2-1)n < N < nP/2, or Nn if N < (P/2-1)n. Then the running time of method 2 is

$$t_{m2}(M) = \begin{cases} 2(Nn - ((P/2 + 1)n - M)((P/2 + 1)n - M + 1)/2)t_{cal} \\ 2Nnt_{cal} \end{cases}$$

$$= \begin{cases} O(M^2/P) & \text{if } (P/2 - 1)n < N < nP/2 \\ O(M^2/P) & \text{if } N < (P/2 - 1)n \end{cases}$$

(3.5)

In Tables 3.1 and 3.2 the calculated running times for both methods of 1-D convolution are presented. They are estimated from the following two equations

$$t_{\rm E-m1}(M) = MN/P u_{\rm cal-1}(N, P)$$

(3.6)

and

$$t_{\text{E-m2}}(M) = \begin{cases} (Nn - ((P/2 + 1)n - M)((P/2 + 1)n - M + 1)/2) u_{\text{cal}-2}(N, P) \\ & \text{if } (P/2 - 1)n < N < nP/2 \\ Nn u_{\text{cal}-2}(N, P) & \text{if } N < (P/2 - 1)n \end{cases}$$

(3.7)

where  $u_{cal-1}(N, P)$  and  $u_{cal-2}(N, P)$ , obtained from experiment, represent the amount of time for one multiplication and one addition, including the time to load and store the input and output data in methods 1 and 2, respectively. Due to the pipelined structure of the C40 [33], the unit time may change according to the number of operations needed to be performed. This is why the *u* parameters are functions of *N* and *P*. Their values are derived from experiment and are listed in Tables 3.3 and 3.4.

**Table 3.1** Estimated running time for 1-D convolution with method 1.

| <i>M</i> =512    | N=8      | N=32     | N=128    | N=384    |

|------------------|----------|----------|----------|----------|

| <i>P</i> =1      | 0.005132 | 0.020509 | 0.082040 | 0.246151 |

| P=2              | 0.003689 | 0.013160 | 0.053300 | 0.174860 |

| $\overline{P}=4$ | 0.001861 | 0.006710 | 0.028462 | 0.090753 |

| <i>P</i> =8      | 0.000954 | 0.003519 | 0.015033 | 0.046197 |

**Table 3.2** Estimated running time for 1-D convolution with method 2.

| <i>M</i> =513 | N=8      | N=32     | N=128    | N=384    |

|---------------|----------|----------|----------|----------|

| <i>P</i> =1   | 0.005132 | 0.020509 | 0.082040 | 0.246151 |

| <i>P</i> =2   | 0.004470 | 0.014063 | 0.052554 | 0.154966 |

| <i>P</i> =4   | 0.002266 | 0.007400 | 0.032507 | 0.114776 |

| <i>P</i> =8   | 0.001112 | 0.003708 | 0.016281 | 0.065480 |

| u <sub>cal-1</sub> | N=8    | N=32   | <i>N</i> =128 | N=384  |

|--------------------|--------|--------|---------------|--------|

| <i>P</i> =1        | 1250.7 | 1251.8 | 1251.8        | 1252.0 |

| <i>P</i> =2        | 1801.3 | 1606.5 | 1626.6        | 1778.8 |

| <i>P</i> =4        | 1817.4 | 1638.2 | 1737.2        | 1846.4 |

| <i>P</i> =8        | 1863.3 | 1718.3 | 1835.1        | 1879.8 |

**Table 3.3** The time  $u_{cal-1}$  (in nsecs) for 1-D convolution with method 1.

**Table 3.4** The time  $u_{cal-2}$  (in nsecs) for 1-D convolution with method 2.

| <i>u</i> <sub>cal-2</sub> | N=8    | N=32   | <i>N</i> =128 | N=384  |

|---------------------------|--------|--------|---------------|--------|

| <i>P</i> =2               | 2178.4 | 1720.0 | 1600.7        | 1573.3 |

| <i>P</i> =4               | 2178.9 | 1700.4 | 1587.3        | 1566.0 |

| <i>P</i> =8               | 2138.5 | 1704.0 | 1590.0        | 1563.5 |

## 3.3.2 2-D Convolution

The 2-D convolution of two matrices performed on a uniprocessor has running time

$$t_{sq2}(M_1) = 2N_1N_2M_1M_2t_{cal} = O(M_1^4)$$

(3.8)

where  $N_1$ ,  $N_2$ ,  $M_1$  and  $M_2$  are as defined in Section 3.2, and  $M_1$  is assumed to be the largest among them. The binary-tree algorithm for 2-D convolution, as described in the previous section, has

$$s = \log_2 P + 1 \tag{3.9}$$

stages.

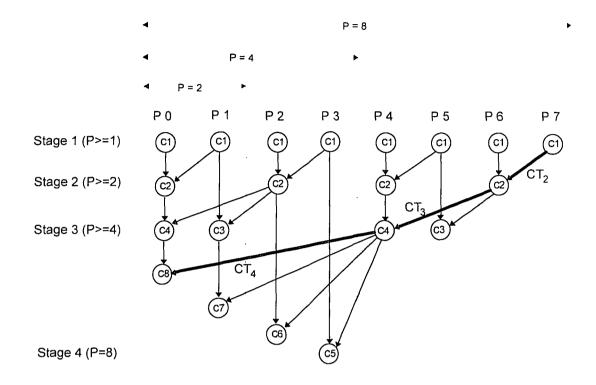

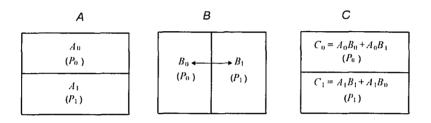

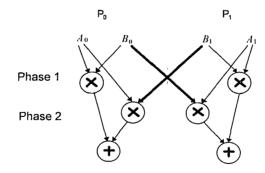

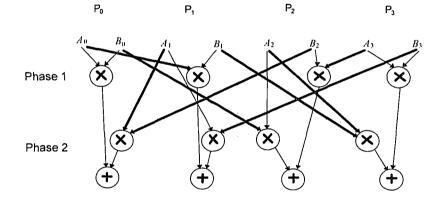

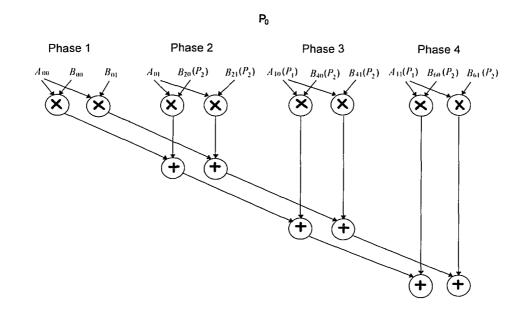

Figure 3.7 DDG of the binary-tree algorithm with 8 processors.

Although the only restriction of the algorithm is that the number of processors P be a power of 2, the DDG in Figure 3.7 is for 8 processors, the number of processors available in TurboNet. This diagram also includes the data dependence information for P = 2 and P = 4. From Equation 3.9, there are 4 stages in the algorithm for P = 8. In stage 1 each processor computes the convolution for each parallelogram assigned to it. As indicated in Section 3.2, each processor has  $N_1/P$  rows of parallelograms, and from Figure 3.2 it can be seen that each row contains  $M_1$  parallelograms, i.e. each processor is assigned  $M_1N_1/P$  parallelograms. Inside each one of them, it is simply a convolution of

two rows from the two input matrices, with lengths of  $N_2$  and  $M_2$ , respectively, as seen in Figure 3.1. Hence, there are  $N_2M_2M_1N_1/P$  multiplications and the same number of additions in stage 1 for each processor. With the same assumption as in Equation 3.8, we have the running time of stage 1 as

$$c_1(M_1) = 2N_2M_2M_1N_1/Pt_{cal} = O(M_1^4/P)$$

(3.10)

The convolution result in each processor is then treated locally as a 1-D array of length  $(N_1/P + M_1 - 1)(N_2 + M_2 - 1)$ , where  $N_2 + M_2 - 1$  is the number of elements of the result in the 1-D convolution of vectors (i.e. one parallelogram) having length  $N_2$  and  $M_2$ .

In stage 2, each processor  $P_i$  whose LSB of its binary address *i* is 0 (i.e.  $P_0$ ,  $P_2$ ,  $P_4$ or  $P_6$ ) receives from  $P_{i+1}$  (i.e.  $P_1$ ,  $P_3$ ,  $P_5$  or  $P_7$ ) the first  $(M_1-1)(N_2+M_2-1)$  elements of the array that resulted in stage 1 in  $P_{i+1}$ , and adds them to the last  $(M_1-1)(N_2+M_2-1)$  elements of its own array from stage 1. Since the binary addresses of  $P_i$  and  $P_{i+1}$  differ in a single bit, they are neighbors if TurboNet is viewed as a hypercube, and therefore their communications can be easily carried out through direct links between them. This is true only for the hybrid and message-passing versions of the algorithm. In the shared-memory version, because each pair of  $P_i$  and  $P_{i+1}$  are located in the same board, no accessing of the shared memory through the VME bus is necessary. But the shared memory in each Hydra board is shared by two pairs of  $P_i$  and  $P_{i+1}$  for  $P \ge 4$ , therefore delay due to congestion on the ISB occurs (no delay for P = 2). As described in Section 2.2, the ownership of the ISB is determined on a cycle-by-cycle basis, so the maximum delay for  $P \ge 4$  is about  $(M_1-1)(N_2+M_2-1)$  cycles. The running times of the three versions in stage 2 are

$$c_{(2,\text{hy})}(M_1) = (M_1 - 1)(N_2 + M_2 - 1)(t_{\text{cal}} + t_{\text{com}}) = O(M_1^2)$$

(3.11)

$$c_{(2,\text{mp})}(M_1) = (M_1 - 1)(N_2 + M_2 - 1)(t_{\text{cal}} + t_{\text{com}}) = O(M_1^2)$$

(3.12)

$$c_{(2,\text{sm})}(M_{1}) = \begin{cases} (M_{1} - 1)(N_{2} + M_{2} - 1)(t_{\text{cal}} + t_{\text{DRAM}}) = O(M_{1}^{2}) & \text{for } P = 2\\ (M_{1} - 1)(N_{2} + M_{2} - 1)(t_{\text{cal}} + t_{\text{DRAM}} + t_{\text{del}}) = O(M_{1}^{2}) & \text{for } P \ge 4 \end{cases}$$

(3.13)

where hy, mp and sm mean hybrid, message-passing and shared-memory, respectively. Also,  $t_{com}$  is the time to transfer a single word between neighbors in the hypercube via the direct link that connects them, and  $t_{del} = t_{DRAM}$  is the time to transfer the same word but through the shared memory (the DRAM).

In stage 3 each processor  $P_i$  whose LSB of its *i* is 0 and the next bit is 1 (i.e.  $P_2$  or  $P_6$ ) sends to  $P_{i,1}$  (i.e.  $P_1$  or  $P_5$ )  $N_1/P(N_2+M_2-1)$  elements of its resulting array from stage 2 (starting at element  $(M_1-N_1/P-1)(N_2+M_2-1)$ ) and to  $P_{i,2}$  (i.e.  $P_0$  or  $P_4$ ) the first  $(M_1-N_1/P-1)(N_2+M_2-1)$  elements.  $P_{i,1}$  and  $P_{i,2}$  will then add the received data to their own arrays. The communication process in this stage can be carried out in three ways. In the hybrid way, the communication between  $P_i$  and  $P_{i,1}$  is done through the shared memory while  $P_i$  sends data to  $P_{i,2}$  via a direct link between them, and the later is assumed to dominate the running time in this stage. In this case, there is no communication congestion in either the link or the shared memory. In using message-passing, data being sent from  $P_i$  to  $P_{i,1}$  may need to go through  $P_{i,2}$ , that is  $P_{i,2}$  is an intermediate node in the path between  $P_i$  and  $P_{i,1}$ . It is assumed that this is the dominant time. In the shared-memory implementation  $P_i$ ,  $P_{i,1}$ .

and  $P_{i-2}$  are all in the same board, therefore there will be no accessing to out-board shared memory. The ISB delay due to congestion exists when  $P_{i-1}$  and  $P_{i-2}$  try to read data at the same time from the on-board shared memory through the ISB bus. Since  $P_i$  starts sending data to  $P_{i-2}$  only after it finishes with  $P_{i-1}$ ,  $P_{i-2}$  will finish last with a maximum delay of  $N_1/P(N_2+M_2-1) t_{del}$ . The running times for this stage are

$$c_{(4,\text{hy})}(M_{1}) = (M_{1} - N_{1}/P - 1)(N_{2} + M_{2} - 1)(t_{\text{cal}} + t_{\text{com}}) = O(M_{1}^{2})$$

$$(3.14)$$

$$c_{(4,\text{mp})}(M_{1}) = (M_{1} - N_{1}/P - 1)(N_{2} + M_{2} - 1)(t_{\text{cal}} + t_{\text{com}}) + N_{1}/P(N_{2} + M_{2} - 1)t_{\text{com}}$$

$$= O(M_{1}^{2}) + O(M_{2}^{2}/P)$$

(3.15)

$$c_{(4,\text{sm})}(M_1) = (M_1 - N_1/P - 1)(N_2 + M_2 - 1)(t_{\text{cal}} + t_{\text{DRAM}}) + N_1/P(N_2 + M_2 - 1)t_{\text{DRAM}}$$

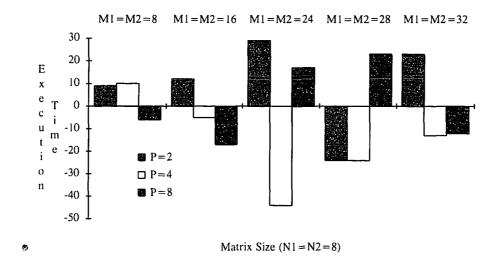

$$= O(M_1^2) + O(M_2^2/P)$$