## New Jersey Institute of Technology

# **Digital Commons @ NJIT**

**Dissertations**

**Electronic Theses and Dissertations**

Spring 5-31-1997

# Efficient parallel processing with optical interconnections

Lili Hai New Jersey Institute of Technology

Follow this and additional works at: https://digitalcommons.njit.edu/dissertations

Part of the Computer Sciences Commons

#### **Recommended Citation**

Hai, Lili, "Efficient parallel processing with optical interconnections" (1997). Dissertations. 1044. https://digitalcommons.njit.edu/dissertations/1044

This Dissertation is brought to you for free and open access by the Electronic Theses and Dissertations at Digital Commons @ NJIT. It has been accepted for inclusion in Dissertations by an authorized administrator of Digital Commons @ NJIT. For more information, please contact digitalcommons@njit.edu.

# **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

#### ABSTRACT

# EFFICIENT PARALLEL PROCESSING WITH OPTICAL INTERCONNECTIONS

## by Lili Hai

With the advances in VLSI technology, it is now possible to build chips which can each contain thousands of processors. The efficiency of such chips in executing parallel algorithms heavily depends on the interconnection topology of the processors. It is not possible to build a fully interconnected network of processors with constant fan-in/fan-out using electrical interconnections. Free space optics is a remedy to this limitation. Qualities exclusive to the optical medium are its ability to be directed for propagation in free space and the property that optical channels can cross in space without any interference. In this thesis, we present an electro-optical interconnected architecture named Optical Reconfigurable Mesh (ORM). It is based on an existing optical model of computation. There are two layers in the architecture. The processing layer is a reconfigurable mesh and the deflecting layer contains optical devices to deflect light beams. ORM provides three types of communication mechanisms. The first is for arbitrary planar connections among sets of locally connected processors using the reconfigurable mesh. The second is for arbitrary connections among N of the processors using the electrical buses on the processing layer and  $N^2$  fixed passive deflecting units on the deflection layer. The third is for arbitrary connections among any of the  $N^2$  processors using the  $N^2$  mechanically reconfigurable deflectors in the deflection layer. The third type of communication mechanisms is significantly slower than the other two. Therefore, it is desirable to avoid reconfiguring this type of communication during the execution of the algorithms. Instead, the optical reconfiguration can be done before the execution of each algorithm begins. Determining a right configuration that would be suitable for the entire configuration of a task execution is studied in this thesis. The basic data movements for each of the mechanisms are studied. Finally, to show the power of ORM, we use all three types of communication mechanisms in the first O(logN) time algorithm for finding the convex hulls of all figures in an  $N \times N$  binary image presented in this thesis.

# EFFICIENT PARALLEL PROCESSING WITH OPTICAL INTERCONNECTIONS

by Lili **H**ai

A Dissertation

Submitted to the Faculty of

New Jersey Institute of Technology

in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

Department of Computer and Information Science

May 1997

Copyright © 1997 by Lili Hai ALL RIGHTS RESERVED

# APPROVAL PAGE

# Efficient Parallel Processing with Optical Interconnections

| Dr. Mary M. Eshaghian, Dissertation Advisor                      | Date                  |

|------------------------------------------------------------------|-----------------------|

| Director of Advanced Computer Architecture and                   |                       |

| Parallel Processing Laboratory                                   |                       |

| Assistant Professor of Computer and Information Science          |                       |

| Assistant Professor of Electrical and Computer Engineering, NJIT |                       |

|                                                                  |                       |

|                                                                  |                       |

|                                                                  |                       |

|                                                                  |                       |

| Dr. John D. Carpinelli, Committee Member                         | Date                  |

| Associate Professor of Electrical and Computing Engineering      |                       |

| Associate Professor of Computer and Information Science, NJIT    |                       |

|                                                                  |                       |

|                                                                  |                       |

|                                                                  |                       |

|                                                                  | . , . ,               |

| Dr. Kurfess, Committee Member                                    | Date                  |

| Co-Director of Software Engineering Laboratory                   |                       |

| Assistant Professor of Computer and Information Science, NJIT    |                       |

|                                                                  |                       |

|                                                                  |                       |

|                                                                  |                       |

|                                                                  | <u> </u>              |

| Dr. Peter A. Ng, Committee Member                                | $\operatorname{Date}$ |

| Chairperson of CIS Department                                    |                       |

| Full Professor of Computer Science, NJIT                         |                       |

|                                                                  |                       |

|                                                                  |                       |

|                                                                  |                       |

|                                                                  | ··                    |

| Dr. Muhammad Shaaban, Committee Member                           | Date                  |

| Assistant Professor of Computer Engineering,                     |                       |

| Rochester Institute of Technology                                |                       |

#### BIOGRAPHICAL SKETCH

Author: Lili Hai

Degree: Doctor of Philosophy

Date: May 1997

#### Undergraduate and Graduate Education:

- Doctor of Philosophy in Computer Science,

New Jersey Institute of Technology, Newark, New Jersey, 1997

- Master of Application and Engineering in Computer Science, North China Institute of Technology, Beijing, China, 1983

- Bachelor of Science in Computer Science, Beijing University, Beijing, China, 1978

Major: Computer Science

#### Publications:

M. Eshaghian and L. Hai,

"An Efficient Electro-Optical Parallel Architecture",

To appear in Proceeding of International Symposium on Automotive Technology and Automation, Florence, Italy, June, 1997.

M. Eshaghian and L. Hai,

"A Fast Parallel Image Convexity Algorithm",

To appear in Proceeding of International Symposium on Automotive Technology and Automation, Florence, Italy, June, 1997.

M.Eshaghian and L. Hai,

"Application Specific Design of the Optical Communication Topology in ORM",

To appear in Proceeding of International Symposium on Automotive Technology and Automation, Florence, Italy, June, 1997.

M.Eshaghian and L. Hai,

"Efficient Parallel Computing with an Optically Interconnected Reconfigurable Mesh",

Submitted to Journal of Parallel Distributed Computing

To my beloved family

#### ACKNOWLEDGMENT

I would like to express my deepest appreciation to my advisor Dr. Mary Eshaghian, who not only served as my research supervisor, providing valuable and countless guidances, but also constant support, encouragement, reassurance and friendship.

Special thanks are given to Dr. Peter Ng, Dr. John Carpinelli, Dr. Franz Kurfess and Dr. Muhammad Shaaban for serving as members in my committee and offering invaluable suggestions to this dissertation.

Special recognition to many of my fellow graduate students in the CIS department, colleagues in my department of LUCENT Technologies Inc. and especially Dr. Song Chen and Dr. Jay Y. Wu for their support. In addition, I appreciate the works done by Amanda Haseltine for English editing on this thesis. I also wish to thank all the secretaries in CIS department for their assistance over the years.

# TABLE OF CONTENTS

| $\mathbf{C}$ | hapte | er                                                                                                                 | Page |

|--------------|-------|--------------------------------------------------------------------------------------------------------------------|------|

| 1            | INT   | RODUCTION                                                                                                          | . 1  |

|              | 1.1   | VLSI Interconnection Topologies                                                                                    | . 2  |

|              | 1.2   | Ideal Parallel Computational Model                                                                                 | . 4  |

|              | 1.3   | Optical Interconnection Networks                                                                                   | . 5  |

|              |       | 1.3.1 Why Optics in VLSI                                                                                           | . 5  |

|              |       | 1.3.2 Previous Work                                                                                                | . 7  |

|              |       | 1.3.3 Overview of the Thesis                                                                                       | . 12 |

| 2            | AN    | OPTICAL MODEL OF COMPUTATION                                                                                       | . 14 |

|              | 2.1   | OMC                                                                                                                | . 14 |

|              |       | 2.1.1 Definition                                                                                                   | . 14 |

|              |       | 2.1.2 Implementations                                                                                              | . 16 |

|              | 2.2   | Applications                                                                                                       | . 21 |

|              |       | 2.2.1 Optimal Geometric Algorithms                                                                                 | . 21 |

|              |       | 2.2.2 Distance Problems                                                                                            | . 23 |

|              |       | 2.2.3 Constant Time Geometric Algorithms                                                                           | . 24 |

|              |       | 2.2.4 A Special Purpose Design for Parallel Implementation of Iterative Methods for Higher Level Vision Processing |      |

|              |       | 2.2.5 Conclusion                                                                                                   | . 25 |

| 3            | OPT   | ΓICAL RECONFIGURABLE MESH                                                                                          | . 26 |

|              | 3.1   | Introduction                                                                                                       | . 26 |

|              | 3.2   | The ORM Architecture                                                                                               | . 28 |

|              |       | 3.2.1 The Processing Unit                                                                                          | . 29 |

|              |       | 3.2.2 The Deflection Unit                                                                                          | . 30 |

|              | 3.3   | Data Movement in ORM                                                                                               | . 31 |

|              |       | 3.3.1 Electrical Routing                                                                                           | . 31 |

| Chapter |      |        | Page                                         | 3    |   |

|---------|------|--------|----------------------------------------------|------|---|

|         |      | 3.3.2  | Optical Routing                              | . 31 | L |

|         |      | 3.3.3  | Electro-Optical Routing                      | . 32 | 2 |

|         | 3.4  | Concl  | usion                                        | . 37 | ī |

| 4       | A F  | AST PA | ARALLEL IMAGE CONVEXITY ALGORITHM            | . 39 | ) |

|         | 4.1  | Introd | luction                                      | . 39 | ) |

|         | 4.2  | O(log) | N) Convexity Algorithm                       | . 40 | ) |

|         |      | 4.2.1  | The Algorithm                                | . 41 | l |

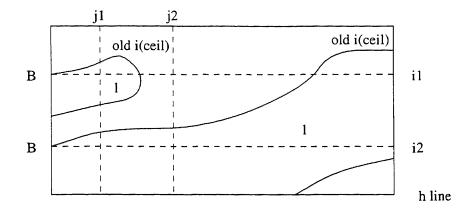

|         |      | 4.2.2  | CONNECT: The Method to Find $i_{ceil}$       | . 53 | 3 |

| •       | 4.3  | Concl  | usion                                        | . 56 | 3 |

| 5       |      |        | TION SPECIFIC DESIGN OF THE OPTICAL COMMUNI- |      | 7 |

|         | 5.1  | Introd | luction                                      | . 57 | 7 |

|         | 5.2  | Prelin | ninaries                                     | . 59 | 3 |

|         | 5.3  | The C  | CONST Methodology                            | . 62 | 2 |

|         |      | 5.3.1  | Phase 1: (Declustering)                      | . 62 | 2 |

|         |      | 5.3.2  | Phase 2: (Assigning)                         | . 62 | 2 |

|         | 5.4  | Concl  | usion                                        | . 68 | 3 |

| 6       | COI  | NCLUS  | ION AND FUTURE WORKS                         | . 69 | 9 |

| A.      | PPEN | NDIX A | CLUSTER-M PRELIMINARIES                      | . 72 | 2 |

| R.      | EFEF | RENCE  | s                                            | . 8' | 7 |

# LIST OF FIGURES

| Figu | ire .                                                                  | Pag | ge |

|------|------------------------------------------------------------------------|-----|----|

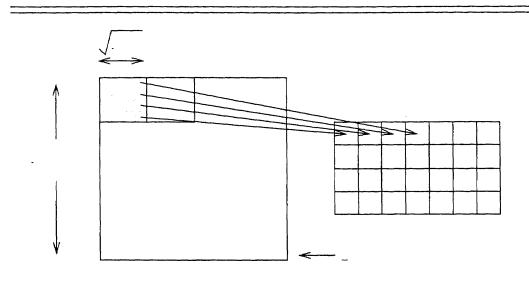

| 1.1  | Optical crossbar system                                                |     | 9  |

| 2.1  | The OMC model                                                          |     | 15 |

| 2.2  | An optical mesh using mirrors                                          |     | 18 |

| 2.3  | Reconfiguration using acousto-optic devices                            |     | 19 |

| 2.4  | Reconfiguration using an electro-optical crossbar                      | •   | 20 |

| 2.5  | Merging of blocks and processor assignment                             | •   | 23 |

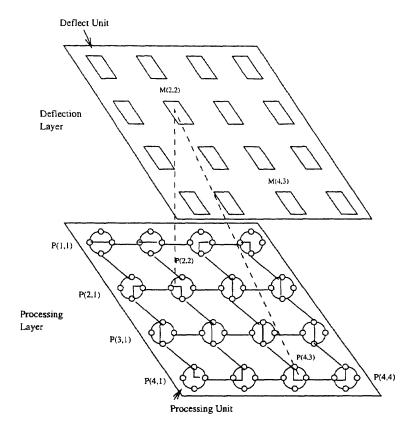

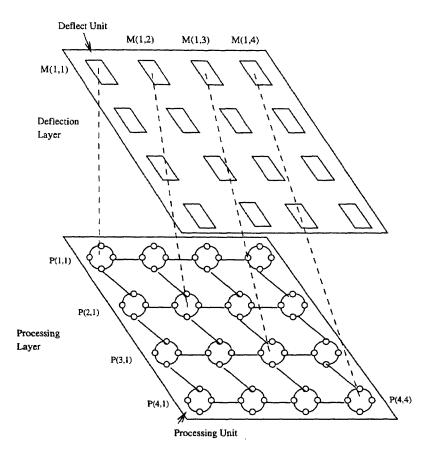

| 3.1  | The ORM architecture                                                   | •   | 29 |

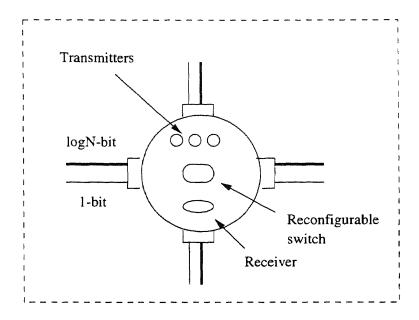

| 3.2  | The detailed structure of a processing element                         |     | 30 |

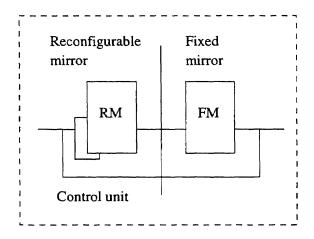

| 3.3  | The detailed structure of a deflector                                  |     | 30 |

| 3.4  | The optical interconnections for electro-optical routing of ORM        |     | 33 |

| 3.5  | Concurrent read on ORM                                                 | -   | 37 |

| 4.1  | Convexity Algorithm                                                    |     | 42 |

| 4.2  | Function $REGION_2(i)$                                                 |     | 43 |

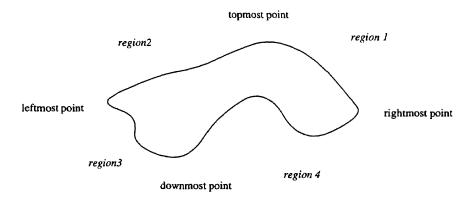

| 4.3  | The region divisions                                                   |     | 44 |

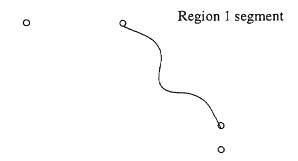

| 4.4  | The region 1 in the figure with multi-most points                      |     | 45 |

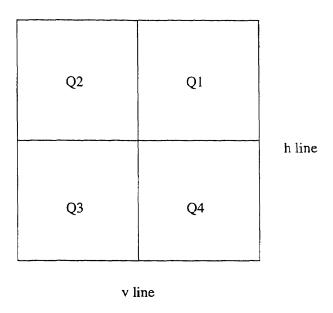

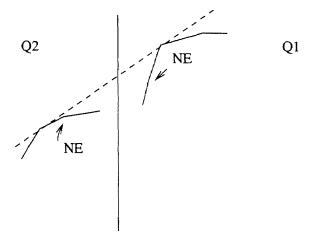

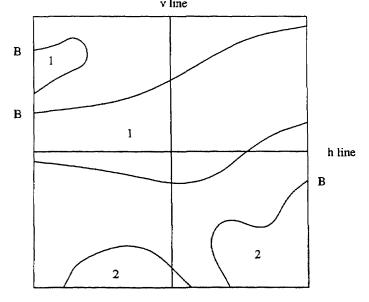

| 4.5  | Quadrants, the $v$ line and the $h$ line in a submesh of ORM           |     | 47 |

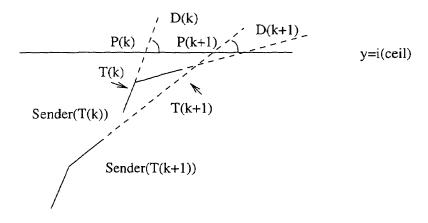

| 4.6  | P nodes: the cross points of tangents and line $y \dots \dots \dots$ . |     | 49 |

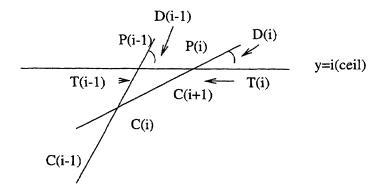

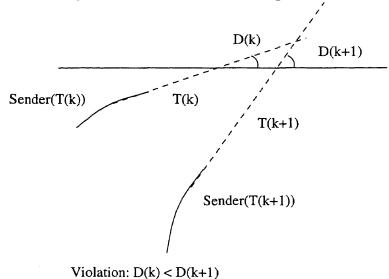

| 4.7  | The example of the rule violation: $D(k) \ge D(k+1) \dots \dots$       |     | 50 |

| 4.8  | The example of the rule violation: $D(k) \leq D(k+1) \dots \dots$      |     | 51 |

| 4.9  | Drop the nonextreme points depending on $LN$ and $RN$ nodes $\ldots$   |     | 52 |

| 4.10 | Two pieces of figure 1 and two pieces of figure 2 in one submesh       |     | 53 |

| 4.11 | Find the route for each figure                                         |     | 56 |

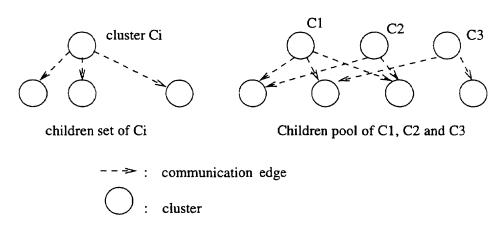

| 5.1  | A children set and a children pool                                     | •   | 61 |

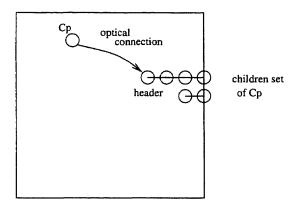

| 5.2  | The optical connection to the header of children set                   |     | 64 |

| F'igu | Figure                                                   |   | Page |  |  |

|-------|----------------------------------------------------------|---|------|--|--|

| 5.3   | The example of the conflict                              | • | 65   |  |  |

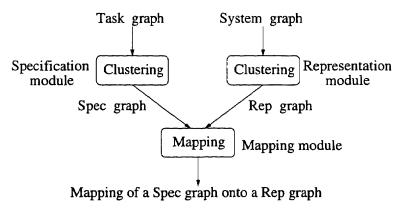

| A.1   | Cluster-M mapping process                                | • | 73   |  |  |

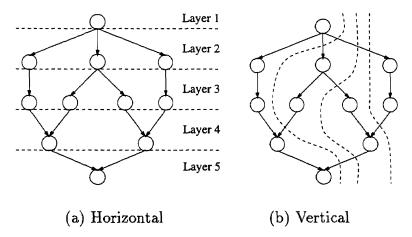

| A.2   | Horizontal and vertical partitioning of a task graph     |   | 74   |  |  |

| A.3   | Clustering Nonuniform Directed Graphs (CNDG) algorithm   |   | 78   |  |  |

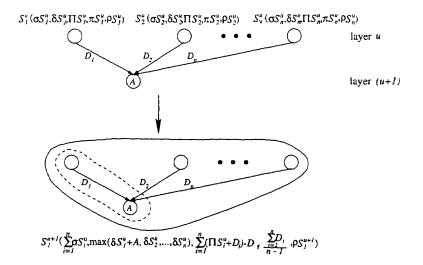

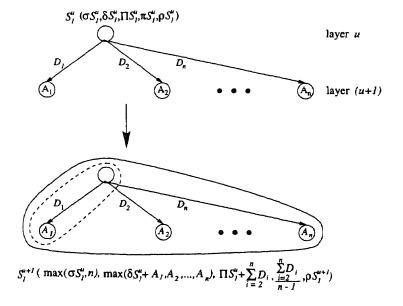

| A.4   | Clustering on a join-node: a general case                |   | 81   |  |  |

| A.5   | Clustering on a fork-node: a general case                |   | 81   |  |  |

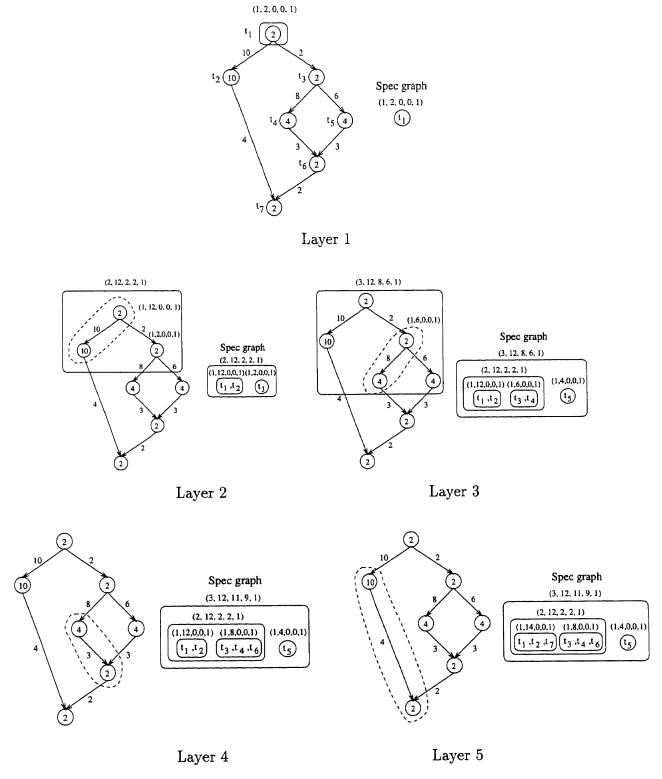

| A.6   | A task graph and steps for obtaining the Spec graph      |   | 82   |  |  |

| A.7   | Clustering Nonuniform Undirected Graphs (CNUG) algorithm | • | 85   |  |  |

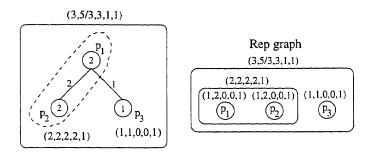

| A.8   | A nonuniform system graph and its Rep graph              |   | 85   |  |  |

#### CHAPTER 1

#### INTRODUCTION

Speedups due to technological advances in solid state electronic design are reaching theoretical limits. To get around these limits, researchers have considered concurrent processing of data as a promising alternative for achieving speedups proportional to the level of concurrency. Since the late 1970's, many multiprocessor architectures have been proposed to obtain such speedups. However, the desired speedups have not been realized because of a limited understanding of issues in designing efficient parallel algorithms and in designing interconnection networks and their interactions. During the last decade, many parallel algorithms have been designed based on a theoretical shared memory model, the Parallel Random Access Machine (PRAM) [66], in which a unit-delay interconnection network is assumed. Unfortunately, a realization of this machine does not exist.

Traditionally electronic interconnects have dominated the interconnection methods in parallel computers. In practice, electronic interconnection networks introduce a delay factor in the implementation of parallel algorithms. The main issues in the design of such interconnection networks have been routing delay, communication bandwidth, hardware cost and ease of control. However, a new technique for interconnecting processing elements in massively parallel computers is emerging: optical interconnection. Over the last ten years, various optical interconnection systems have been developed. The advantages of optical technology are realized and studied. This promising technique is playing a more and more important role in parallel computations. An introduction to the above issues is discussed in this chapter.

#### 1.1 VLSI Interconnection Topologies

Research in the design of interconnection networks can be divided into two topological classes: static and dynamic [19]. In a static network, links between any two processors are passive and direct connections cannot be reconfigured between processors. In a dynamic network, links can be reconfigured by setting the switching elements in the network. Among many static topologies, those having smaller diameters are most attractive. The diameter of a network is the maximum distance between any pair of processors. The distance between a pair of processors is the smallest number of nodes that have to be traversed in order to get from one processor to the other. The diameter of an architecture represents a lower bound on worst case communication delay between any two processors. A fully connected network has unit diameter. However, when an N-processor system is implemented in electronic technology such as VLSI, its diameter becomes  $\Omega(\log N)$  due to pin-out limitations of processors if N is large. Also, the VLSI layout area becomes too large to be practically implemented. A balance has to be found among various network parameters, such as the node degree, the switching complexity, and the network latency. Therefore, an appropriate alternative is to consider area efficient architectures which have some degree of communication delay. The typical example is the hypercube topology in which there are  $\log N$  interconnections from each node to others such that the diameter is  $\log N$ . Pyramid and Mesh of Trees are other examples of such architectures [50, 34, 44].

Dynamic networks are categorized in three topological classes: single-stage, multistage, and crossbar [19]. The switches in an  $N \times N$  crossbar can be set in  $O(\log N)$  time so that every input port can be connected to a free output port. An N input crossbar requires  $\Omega(N^2)$  VLSI area, using the usual two dimensional VLSI model [59]. Several N input N output multistage networks are known which require  $O(N \log N)$  switching elements, significantly fewer than a crossbar network [56].

Multistage networks can be divided into two major classes: rearrangeable and non-rearrangeable [5]. Non-rearrangeable networks can realize only a proper subset of all permutations. A Butterfly network is a widely used non-rearrangeable network. The well known Omega network is a non-rearrangeable multistage network. It has  $O(N \log N)$  switching elements and requires  $\Omega(N^2/\log^2 N)$  VLSI area [34]. Rearrangeable networks support any arbitrary permutation using appropriate switch settings. However, finding a switch setting to realize a permutation on a rearrangeable network can be time consuming; for example it can take as much as  $O(\log^4 N)$  time using a cube connected computer or a perfect shuffle computer with N processors [46]. Their layout area in the two-dimensional VLSI model is not significantly superior compared to the area requirement of the N input crossbar. Therefore, realizing multistage interconnection networks in  $O(N \log N)$  area does not seem possible unless one assumes that wires do not occupy any area.

From the theoretical computational point of view, for a given problem, there is a lower bound on the VLSI circuit area A on which the problem is run, and its computational time T. The lower bound in the VLSI model, called " $AT^2$  bound", is represented by the formula  $AT^2 = \Omega(I^2)$ , where I is the information content of the problem [59]. Through this lower bound, we can see that if the time T is fixed, the required VLSI area grows with the problem size. We will see in section 1.3 that this problem is overcome by using optical interconnection.

In this thesis, we study parallel architectures that use free space optics as a means of interprocessor communications. Replacing electrical interconnects with optical beams has a significant impact on the performance of VLSI architectures [12, 26]. This fact arises from the following two important properties of free space optics. First, free space optical beams can cross each other without any interference. Second, the connections need not be fixed and can be redirected [6].

#### 1.2 Ideal Parallel Computational Model

From the point of view of the parallel algorithm people, the design issue of an algorithm depends more on the number of usable processors, the data accessing mode and the routing method in the system than on the circuit layout design. The computational model affects the algorithms design directly. The ideal model or the best algorithm design environment is that no mater what kind of computational architecture is used, the detail of the routing method does not reflect into the algorithm.

One of the widely used models of parallel computation is the Parallel Random Access Machine (PRAM). The basic assumption in this model is that in unit time each of N processors can simultaneously access any one memory location [66]. Unfortunately, it is unlikely that a PRAM model will ever faithfully represent any "real" parallel machine. A real parallel computer will most likely consist of a large number of simple processors, each connected to a small number of other processors. Each processor in this network has its own local memory, and processors communicate by sending messages over links to neighboring processors. To reconcile the convenience of a PRAM with the limitations of a real computer, it is simulated on a real network.

One of the first randomized simulations is given in [61], where it is shown that there exists an N-processor realistic computer that can simulate an idealistic N processor PRAM with only a factor of  $O(\log N)$  loss of run time efficiency. In [51], this was improved by obtaining similar bounds but requiring only bounded queue size. The deterministic simulation takes the longer time. The deterministic simulation of EREW (exclusive read exclusive write) or CRCW (concurrent read concurrent write) PRAM on an N-processor butterfly needs  $O(\log M \log N \log \log N)$  steps, where M is the number of memory cells and  $M > N^2$ . A similar performance can be obtained from an N-node hypercube [35].

Since the end of the 1980's, there has been an emerging interest in the design of models of parallel computation which more closely simulate a realistic

machine. In [24], a more restricted PRAM model called Distributed Random Access Machine (DRAM) is introduced, which reflects an assumption of limited communication bandwidth in the underlying network. All memory in DRAM is local to the processors, and is accessed by routing messages through a communication network. A stronger model called local memory PRAM was introduced in [2]. Like the DRAM, the memory is distributed. However, there is no restriction on the underlying communication network and hence it is assumed to have a unit time delay. Such a communication medium is feasible with fixed connection architectures of unbounded degree, or those with reconfigurable optical interconnects.

#### 1.3 Optical Interconnection Networks

A considerable amount of research has been done on exploring the features of optics. The theoretical and experimental results support a point that the optical interconnection could be an ideal substitution of the electronic interconnection in parallel computers or networks. The significance of this on computer science may be deeper than expected.

#### 1.3.1 Why Optics in VLSI

Several characteristics of present hardware techniques limit the density of electrical interconnects. One limitation is that the edge of the chip is reserved for I/O functions. Another is that electrical interconnects are confined to pseudo-planar structures (e.g., printed wiring boards, backplanes). The phenomenon of crosstalk is a fundamental limitation on spacing between individual interconnects. This density issue is aggravated with increases in speed in individual devices. As speeds increase, sensitivity to crosstalk through the electrical interconnect also increases and the required distance between devices decreases to ensure that the signal propagation time is less than the clock period. Obviously, as density increases, the spacing between lines

decreases and it is necessary to reduce the cross-sectional area of the conductors in order to place more interconnections in a given volume.

It has been demonstrated that optical techniques provide a much higher density for a given bandwidth than electronic techniques. Using free space or wavelength propagation, it is possible to take advantage of the high density bandwidth product available in the optical domain. In addition, using integration of opto-electronic devices, it is possible to communicate with the interior of the chip rather than confining I/O to the chip boundary.

The system implemented by electronic computers and optical interconnection among the computers is called opto-electronic system. In section 1.1, the VLSI model and computational time of the electronic computer was discussed. In a three dimensional electro-optical model called VLSIO [3], which is the generalization of the VLSI model into three dimensional opto-electronic systems, a similar lower bound can be expressed as  $VT^{3/2} = \Omega(I^{3/2})$  where V is the circuit volume. This overcomes the problem caused by the two-dimension electronic wire interconnection limitation. This advantage is not gained by the optical versions of existing electronic architectures implemented by replacing wires on a VLSI chip with optical waveguides [21, 27]. The reason is that by using waveguides, the communication bandwidth can be increased but the interconnection topology is still the same as before which is two-dimensional while the optical free space technique uses the third dimension to transfer data.

An even better lower bound for the optical free space interconnection system is given in [18]. It is based on the fact that the distance of the free space between two planes of such kind of system is a constant. In some systems, each plane contains processors and the processors on one plane can communicate with the processors on another plane [45] through free space. Another typical optical free space interconnection is that one plane contains processors and another plane consists of light deflection devices. The data is sent from the processor plane and is received by the

processors on the same plane. The lights go to the deflection layer, and are redirected back to the processor plane through free space. For an optimal lower bound of optical free space interconnection system, please refer to [18].

#### 1.3.2 Previous Work

There are two approaches to define the optical interconnection medium: guided-wave interconnect and free space coupling. Although many efficient models using wavelength division multiplexing (WDM) have been developed in recent years [57, 13, 62], they are outside the focus of this thesis. The work based on using free space interconnection methods are examined more closely in this section.

Some qualities of the optical medium are its abilities to be directed for propagation in free space and to have two optical channels cross in space with out interaction. These properties allow optical interconnects to utilize all three dimensions of space. Such a capability will allow optical interconnection to improve upon many of the functions presently implemented on a limited scale with electronics, such as routing data between processing elements based on data dependent decisions, as well as multiplexing and demultiplexing information. Another widely used advantage of optical free space is that the node-to-node interconnection can be changed freely and quickly. In the other words, the interconnection topology of an optical free space system can be reconfigured during the computation even though the reconfiguring takes time.

One of the first attempts in using free space optics as a means of data-communications is [23]. In their hybrid GaAs/Si approach to data communication, a GaAs chip with optical sources was connected in a hybrid fashion (with conventional wire bond techniques) to a Si chip such that light was generated only along the edges of the Si chip. The sources were of the edge-emitting or surface emitting type. The optical signals were routed to the appropriate locations on the Si chip using

conventional and/or holographic optical elements. The Si chip contained detectors to receive the optical data streams generated by the sources. Since the detector-amplifier combinations were fabricated in Si, every computational component on the Si chip was capable of receiving data.

To explore this promising concept, it was extended to support efficient interconnection networks for massively parallel computing.

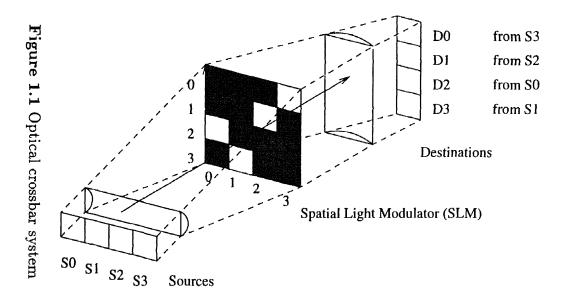

One idea is to make optical crossbar networks by using optical matrix-vector multiplication [22, 41, 47]. In the late 80's, Sawchuck et al. [55] described several possible bulk optical systems for implementing optical crossbar networks. Unlike electrical crossbar, these crossbars provided unit time interconnectivity and had a slow switching rate. A typical N-node optical crossbar system is shown in the figure 1.1 [53]. An  $N \times N$  switch array consists of  $N \times N$  optical switchs, or some kind of optical devices. This matrix is called spatial light modulator (SLM) and modulates the cross-section of a light beam. The  $N \times N$  array corresponds to the permutation matrix that represents the interconnection among N processors. Once the switches are set, the messages can be transmitted at optical transmission rates, which can be several Gigahertz. But the switch array is not energy efficient and the switch setting is slow.

To avoid the above problems, the holographic technique is used. A hologram can be written dynamically and the recorded information can be retrieved later. So, it is used to remember the address pattern. The holograms can be dynamicly recorded [68, 11], or can be fixed [15, 65, 40, 52] in the system. The time for recording a hologram is also long. Using fixed holograms to implement dynamic routing schemes is an important research topic on optical free space interconnection computers.

Many application of optical systems using the free space technique are emerging. A model for a data flow based processor is given in [8]. The concept is to set the interconnection dynamically among processors of the optoelectric network

to match the dynamically abstracted data flow graph. The interconnection network is an optical implementation of a rearrangeably non-blocking Clos network, which is a three-stage permutation network. Several possible ways to realize the system are given. One way is to use the optical crossbar developed in [7]. Ferroelectric liquid crystal (FLC) devices are used, in which beam-blocking mask patterns are written similar to the way that an image is produced on a liquid crystal display screen. By the feature of the data flow system, the reconfiguration is needed. For a static data flow graph which does not need to change frequently, this approach is realistic.

A similar optical reconfigurable parallel architecture [25] supports advanced multiple functions. It provides a set of instructions to allow users to configure both the topology and the behavior of the architecture. The topology means the interconnection pattern (mesh, cube, etc.) and the behaviour means the style of the data processing (pipeline, dataflow, etc). This system adopts the SLM-based crossbar switch matrix which we introduced before. The SLM is situated between two banks of I/Os from the processors: outputs on one side, inputs on the other. The outputs are placed vertically and the inputs horizontally, thus each output illuminates a row of the SLM and each input reads from the column. The data transfer is through the optical free space. Since the switching time on the SLM frame in such a system dominates the system performance, the fast electronically controlled matrix-addressed ferroelectric liquid crystal (FLC) SLM is chosen.

The earlier work based on the similar idea is [62]. But the architecture is not an optical free space one; the model named Multiple Channel Architecture (MCA) can support large numbers of users with vastly different computing requirements through a fact that the large amount of independent, selectable channels (or virtual buses) can be provided by a single optical fiber. Depending on different computation requirement, different channels can be chosen by a computer to connect to some new neighbors, so that new interconnection topology can be built.

In recent years, there have been many experimental works done in optoelectronic computer systems supported by universities, governments and international organizations. These efforts are supported by theoretical research and they

pace the commercialization of the opto-electric computers. One is ESPRIT II

OLIVERS [49]. This is a three year collaborative project under the European

Strategic Program for Research in Information Technology (ESPRIT). OLIVES

means Optical Interconnections for VLSI and Electronic Systems. Four demonstrators of optical interconnections at the module, backplane, multichip module

and chip levels were constructed. Various optical techniques were used in different

demonstrators led by theoretical investigations. Among them, the optical free space

technique is used to implement the mastercard for backplane interconnections. Its

slab is provided with holograms which perform beam directing splitting and possibly

focusing functions.

Another project of an optoelectronic 3-D system is [45]. The free space optically interconnected system with internal feedback loop based on the concept of [29] was presented. Two optoelectronic arrays (also know as smart-pixel arrays) each containing  $8\times8$  one-bit processors optically connected face-to-face through free space using a bidirectional holographic element. Optical sources are vertical-cavity surface-emitting lasers (VCSELs) which is an important research topic in the project. The goal of this experimental work is to find the parameters of the optical scheme such as the hologram and detector dimensions, their spacing and the Fourier objective diameter.

Free space optical interconnections are classified according to the degree of space variance [38], which determines the network's complexity and regularity. A totally *space-variant* network allows a completely arbitrary interconnection between components, whereas a totally *space-invariant* network has a definite, regular structure so that all the nodes in a system have the same connection patterns.

Most optical free space interconnection architectures mentioned above are space-variant. For the features of space-invariant system claimed in [39] and the interconnection simplicity, many space-invariant networks are researched [32, 39]. The typical method is to simulate an existing electric multistage network by assigning each node the regular connection to other nodes through optical components such as lenses, mirrors and holograms. Another optical space-invariant system is [37]. As in OLIVERS, it combines free space and waveguide technologies into one system even though each uses them in different system levels.

#### 1.3.3 Overview of the Thesis

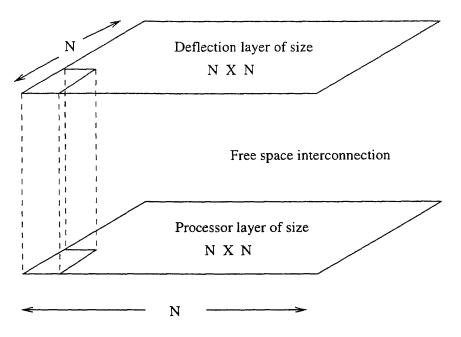

In this thesis, there are six chapters. In Chapter 2, we introduce an optical model of computations, OMC, and several implementations for the model. In Chapter 3, we present an electro-optical parallel architecture called the Optical Reconfigurable Mesh (ORM). It is an implementation of an existing optical model of computation (OMC) [15]. The ORM has two layers, the deflection layer and the processing layer. The processing layer is an  $N \times N$  reconfigurable mesh. The deflection layer is situated directly above the processing layer to provide unit-time free space optical interconnections for the processors. Three types of unit-time communication mechanisms supported by the architecture are introduced in the thesis. The first is for arbitrary planar connections among sets of locally connected processors using the reconfigurable mesh. The second is for arbitrary connections among N of the processors using the electrical buses on the processing layer and  $N^2$  fixed passive deflecting units on the deflection layer. The third is for arbitrary connections among any of the  $N^2$  processors using the  $N^2$  mechanically reconfigurable deflectors in the deflection layer. A set of basic data movement algorithms for those mechanisms are presented. To show the power of ORM, we use all three types of communication mechanisms in the first O(log N) time algorithm for finding the convex hulls of all figures in an

$N \times N$  0/1 image presented in Chapter 4. The optical reconfiguration in the third type of communication mechanisms is significantly slower than the other two. It is desirable to avoid using this type of communication during the execution of the algorithms. Instead, we do the optical reconfiguration before the execution of each algorithm begins. Determining a right configuration that would be suitable for the entire configuration of a task execution is studied in Chapter 5. The conclusion and future works are discussed in Chapter 6. An appendix in this thesis includes some preliminary that used in the methodology studied in Chapter 5.

### CHAPTER 2

#### AN OPTICAL MODEL OF COMPUTATION

In this chapter, the optical computational model OMC [15] is introduced and the implementations are reviewed.

#### 2.1 OMC

The OMC model (Optical Model of Computation) was first introduced by Eshaghian [15] in 1988. Its inherent EREW PRAM capability makes it very powerful to be used for various existing application parallel algorithms.

#### 2.1.1 Definition

The OMC model is shown in Figure 2.1. Formally, this model is defined as follows:

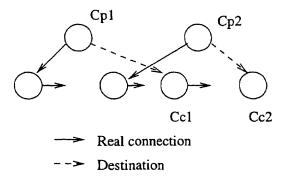

An optical model of computation represents a network of N processors each associated with a memory module and a deflecting unit capable of establishing direct optical connection to another processor. The interprocessor communication is performed satisfying the following rules similar to [2]:

- 1. At any time a processor can send at most one message. Its destination is another processor.

- 2. The message will succeed in reaching the processor if it is the only message with that processor as its destination, within that step.

- 3. All messages succeed or fail (and thus are discarded) in unit time.

To insure that every processor knows when its message succeeds we assume that the OMC is run in two phases. In the first phase, read/write messages are sent and in the second, values are returned to successful readers and acknowledgements are

14

Figure 2.1 The OMC model

returned to successful writers. It assumes that the operation mode is synchronous, and all processors are connected to a central control unit. The above definition is supplemented with the following set of assumptions for accurate analysis.

- 1. Processors are embedded in the Euclidean plane. This is referred to as the processing layer.

- 2. Each of the processing/memory elements occupies unit area.

- 3. Deflectors are embedded in the Euclidean plane. This is referred to as the deflecting layer.

- 4. Each deflecting unit occupies one unit area.

- 5. The deflecting layer is collinear to the processing layer.

- 6. I/O is performed at I/O pads. Each I/O pad occupies unit area.

- 7. The total volume is the sum of the volume occupied by the processing layer, the deflecting layer and the space for optical beams.

- 8. The intercommunication is done through free space optical beams.

- 9. Time is measured in terms of number of units of clock cycles.

- 10. An optical beam carries a constant amount of information in one unit of time, independent of the distance to be covered.

- 11. A deflector is capable of redirecting an incident beam in one unit of time.

- 12. A processor can perform a simple arithmetic/logic operation in one unit of time.

- 13. The time T for computation is the time between the arrival of the first input and the departure of the last output.

Compared with an electronic VLSI computation model, the following result can be stated:

**Proposition 1** Any computation performed by a three dimensional VLSI organization having N processors with degree d, in time T, and volume V can be performed on OMC in volume v, and time t, where  $dT/N \le t \le T$ , and  $Nd \le v$ .

Its lower bound can be simply obtained by multiplying T by d/N which is the maximum speed up factor that can be obtained due to its unit time interconnection medium. The lower bound on v is obtained by the minimum area requirement for having d deflectors for each of the processing elements. In the next sections three different parallel architectures are presented as possible efficient upper bounds for v.

#### 2.1.2 Implementations

In this section, a class of optical interconnection networks as a realization of the OMC introduced in [15] are reviewed. Each of the designs uses a different optical device technology for redirection of the optical beams to establish a new topology at any clock cycle, and represents an upper bound on the volume requirement of OMC.

Optical Mesh Using Mirrors: In this design, there are N processors on the processing layer of area N. Similarly, the deflecting layer has area N and holds N mirrors, each with its own arithmetic unit.. These layers are aligned so that each of the mirrors is located directly above its associated processor (see Figure 2.2). Each processor has two lasers. One of these is directed up towards the arithmetic unit of the mirror and the other is directed towards the mirror's surface. A connection phase would consist of two cycles. In the first cycle, each processor sends the address of its desired destination processor to the arithmetic unit of its associated mirror using its dedicated laser. The arithmetic unit of the mirror computes a rotation degree such that both the origin and destination processors have equal angle with the line perpendicular to the surface of the mirror in the plane formed by the mirror, the source processor, and the destination processor. Once the angle is computed, the mirror is rotated to point to the desired destination. In the second cycle, a connection is established by the laser beam carrying the data from the source to the mirror and from the mirror being reflected towards the destination. Since the connection is done through a mechanical movement of the mirror, with the current technology this leads to an order of milli-second reconfiguration time. Therefore this architecture is suitable for applications where the interconnection topology does not have to be changed frequently. In [33], the design of various topologies has been studied to minimize the time complexity of several problems for a fixed period of computation.

The space requirement of this architecture is O(N) under the following assumption. Each mirror is attached to a simple electro-mechanical device which takes one unit of space and can rotate to any position in one unit of time. The assumptions are as valid as those in VLSI such that the constant propagation delay assumption regardless of the wire length. Other assumptions can also be made based on the following arguments. Many mirrors have a reconfiguration delay

proportional to their rotation angle, O(N). More complex mirrors on the other hand, can rotate faster for a larger angle (unit time rotation delay) but their size can grow proportional to the number of angles they can realize (O(N)).

Figure 2.2 An optical mesh using mirrors

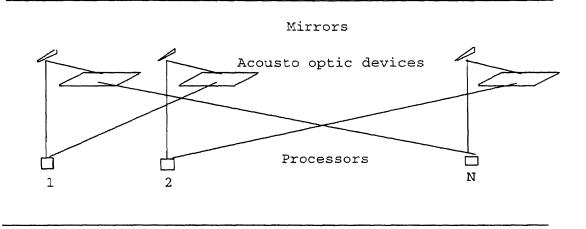

2.1.2.2 Reconfiguration Using Acousto-Optic Devices: In this organization, N processors are arranged to form a one-dimensional processing layer and the corresponding acousto-optic devices are similarly located on a one-dimensional deflecting layer (see Figure 2.3).

The size of each of the acousto-optic devices is proportional to the size of the processing array, leading to an  $O(N^2)$  area deflection layer. Similar to the design using the mirrors, every processor has two lasers, and each connection phase consists of two cycles. In the first cycle, each processor sends the address of its desired destination processor to the arithmetic unit of its associated acousto-optic unit using its dedicated laser beam. The acousto-optic cell's arithmetic unit

Figure 2.3 Reconfiguration using acousto-optic devices

computes the frequency of the wave to be applied to the crystal for redirection of the incoming optical beam to the destination processor. The acousto-optic device then redirects the incident beam from the source to the destination processor. One of the advantages of this architecture over the previous design is its order of micro-seconds reconfiguration time, which is dominated by the speed of sound waves. The other advantage is its broadcasting capability, which is due to the possibility of generating multiple waves through a crystal at a given time.

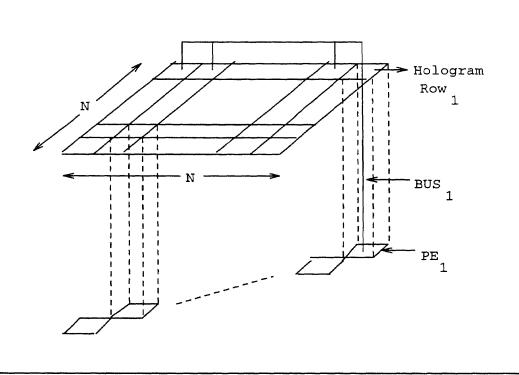

2.1.2.3 Electro-Optical Crossbar: This design uses a hybrid reconfiguration technique for interconnecting processors. There are N processors, each located in a distinct row and column of the  $N \times N$  processing layer. For each processor, there is a hologram module having N units, such that the  $i^{th}$  unit has a grating plate with a frequency leading to a deflection angle corresponding to the processor located at the grid point (i, i). In addition, each unit has a simple controller and a laser beam. To establish or reconfigure to a new connection pattern, each processor broadcasts the address of the desired destination processor to the controller of each of N units of its hologram module using an electrical bus (see Figure 2.4). The controller activates a laser (for conversion of the electrical input to optical signal), if its ID matches the

broadcast address of the destination processor. The connection is made when the laser beams are passed through the predefined gratings. Therefore, since the grating angles are predefined, the reconfiguration time of this design is bounded by the laser switching time which is in the order of nanoseconds using Gallium Arsenide (GaAs) technology [30].

Figure 2.4 Reconfiguration using an electro-optical crossbar

This architecture is faster than the previous designs and, further, it compares well with the clock cycle of current supercomputers. One of the advantages of this simple design is its implementability in VLSI, using GaAs technology. Due to the above advantages, it gives the flexible usage of the  $N^2 - N$  vacant areas on the processing layer, the extension on this architecture leads to a new implementation of OMC.

#### 2.2 Applications

In this section, using OMC, we present several parallel algorithms for fine grain image computation. We categorize the results in the following order. We present a set of processor efficient optimal O(logN) algorithms and a set of constant time algorithms for finding geometric properties of digitized images. Finally, we focus on special purpose designs tailored to meet both the computation and communication needs of problems such as those involving irregular sparse matrices.

#### 2.2.1 Optimal Geometric Algorithms

In this section, we present  $O(\log N)$  algorithms for problems such as labeling figures and finding the nearest neighbor figure to each figure in an  $N \times N$  image. The input to our algorithms is a digitized picture with PE(i,j) storing the pixel (i,j),  $0 \le i,j, \le N-1$  in the plane, where the black pixels are 1-valued, and white pixels are 0-valued.

Connectivity among pixels can be defined in terms of their adjacency. Two black pixels  $(i_1, j_1)$  and  $(i_2, j_2)$  are 8-neighbors if  $\max\{|i_1 - i_2|, |j_1 - j_2|\} \le 1$ , and 4-neighbors if  $|i_1 - i_2| + |j_1 - j_2| \le 1$ . Two black pixels  $(i_1, j_1)$  and  $(i_k, j_k)$  are said to be connected by a 8-path(4-path) if there exists a sequence of black pixels  $(i_p, j_p)$ ,  $2 \le p \le k$ , such that each pair of pixels  $(i_{p-1}, j_{p-1})$  and  $(i_p, j_p)$  are 8-neighbors(4-neighbors). A maximal connected region of black pixels is called a connected component.

2.2.1.1 Labeling Digitized Images: An early step in image processing is identifying figures in the image. Figures correspond to connected 1's in the image. An  $N \times N$  digitized picture may contain more than one connected region of black pixels. The problem is to identify which figure (label) each "1" belongs to.

**Lemma 1** Given an  $N \times N$  0/1 image, all figures can be labeled in  $O(\log N)$  time using an  $(N \times N)$ -optical mesh.

**Proof:** The basic idea of the algorithm is to identify the outer and inner boundaries of each figure and then to uniquely label all of the connected figures surrounded by each of these boundaries [1]. To assure circular boundaries, the input image is magnified by a factor of two along each dimension. Each pixel then locally determines whether or not it is a boundary pixel by checking if at least one of its four adjacent pixels along the x and y axis, hold a "0". The pixels along each boundary are linked to form a circular list.

From now on, only the boundary PEs take part in the computation to identify the least numbered PE in their list. Each PE during iteration i+1, sets its pointer to the pointer of the PE it was pointing to at the end of iteration i. This technique is called pointer jumping and is commonly used in parallel algorithms now. Since this has the effect of doubling the distance "jumped" during each iteration, in  $O(\log N)$  time all the PEs in each list know the least numbered PE in their list. The final step is the propagation of the unique IDs of each of the outer boundaries to its inner region. Broadcasting of IDs is done in parallel along each row of the image. It is easy to see that since the figures do not cross there is always a unique ID broadcasted to each of the inner PEs.  $\square$

In the following, we use fewer processors to lead to the optimal solution.

**Theorem 1** Given a  $N \times N$  0/1 image, all figures can be labeled in  $O(\log N)$  time using an  $(N/\log^{1/2} N \times N/\log^{1/2} N)$ -optical mesh.

**Proof:** In the first step, we assign a  $\log^{1/2} N \times \log^{1/2} N$  block of image to each processor, and we sequentially label the figures within these regions. This is accomplished using a serial graph traversal technique.

In the second step, these blocks are merged together until the block size becomes  $\log N \times \log N$  (see Figure 2.5). During each iteration, four blocks of size

Figure 2.5 Merging of blocks and processor assignment

$k \times k$  are merged to obtain a block of size  $2k \times 2k$ . This is performed by assigning the available PEs to block boundary pixels, and then applying the algorithm of lemma 1 to merge each pair of blocks. Since there are not enough processors available to hold all the block boundary points, they are processed by groups of  $\log N$  at a time. Hence, the total time to simulate each of  $\log \log N$  iterations is  $O(\log^{1/2} N)$ . This leads to a total of  $O(\log^{1/2} N \log \log N)$  time complexity for the second reduction step. Using Lemma 1, the remaining pixels are labeled.

#### 2.2.2 Distance Problems

Another interesting problem is to identify and to compute the distance to the nearest figure to each figure in a digitized image. In the following, we use the  $l_1$  metric. However, it can be modified to operate for any  $l_k$  metric.

**Theorem 2** Given an  $N \times N$  0/1 image, the nearest figure to all figures can be computed in  $O(\log N)$  time using an  $(N/\log^{1/2} N \times N/\log^{1/2} N)$ -optical mesh.

**Proof:** This algorithm consists of two steps. In the first step, each black pixel finds its nearest neighboring black pixel which belongs to a different figure. In the second step, each figure finds its nearest neighboring figure by finding the minimum among all those values obtained for the PEs at the boundaries. This can be done in  $O(\log N)$  time, using the techniques of [50], once the input has been reduced to match the number of processors. Reduction is possible by assigning  $O(\log^{1/2} N \times \log^{1/2} N)$  pixels to a single processor.

# 2.2.3 Constant Time Geometric Algorithms

One of the most attractive properties of optics is superposition [28]. This property suggests that the resultant disturbance at any point in a medium is the algebraic sum of the separate constituent waves. Hence, it enables many optical signals to pass through the same point in space at the same time without causing mutual interference or crosstalk. Using this property, in [31] it is shown how a single memory element can be read by many processors at the same time. In this section, we employ this characteristic to allow concurrent writes if all the requesting processors want to write a "1". This leads to constant running time of the following geometric algorithms, under the assumption that broadcasting can be done in unit time:

**Lemma 2** Given an  $(N^{1/2} \times N^{1/2})$  image, using an  $(N \times N)$  optical mesh, in O(1) time,

- 1. For a single figure, its convex hull and a smallest enclosing box can be determined.

- 2. For each figure, the nearest neighboring figure can be identified.

# 2.2.4 A Special Purpose Design for Parallel Implementation of Iterative Methods for Higher Level Vision Processing

Solutions to many problems in image understanding can be posed in terms of iterative improvement to an initial configuration. For example, discrete relaxation-based approaches to scene labeling can be viewed as an iterative improvement process. In such problems, the underlying graph is usually sparse. But this sparsity is not regular. Efficient parallel implementations of such relaxation methods are possible with OMC.

Any iterative matrix structure can be realized by OMC using devices such as holograms (or those described in Chapter 1). Although the reconfiguration time for the holograms can be in the order of seconds, it only has to be set once during the processing phase. The structure of the coefficient matrix is used to define the holographic connections. This interconnection pattern remains the same throughout the computation. An optimal O(logm) time can be achieved by this design where m is the number of nonzero elements in the matrix. This method is attractive when many computations are to be performed in which the structure of the coefficiet matrix is fixed, such as iterative methods.

#### 2.2.5 Conclusion

The Optical Model of Computation, OMC, was introduced in this chapter. The optical parallel architecture ORM presented in the next chapter is based on this model.

# CHAPTER 3 OPTICAL RECONFIGURABLE MESH

In this chapter, we will present a new electro-optical parallel architecture which is an implementation of the OMC model. This architecture is called the Optical Reconfigurable Mesh (ORM). The ORM has two layers, the deflection layer and the processing layer. The processing layer is an  $N \times N$  reconfigurable mesh. The deflection layer situated directly above the processing layer, provides unit-time free space optical interconnections for the processors. The three types of unit-time communication mechanisms supported by the architecture are introduced. A set of basic data movement algorithms for those mechanisms is discussed.

#### 3.1 Introduction

The ORM has two layers, the deflection layer and the processing layer. Each processor has a corresponding deflection unit situated above it. A reconfigurable mesh is used to build the processing layer so each processor can communicate with other processors either through an optical interconnection or electrical buses. Reconfigurable bus systems have been studied extensively in the past few years. Many different models of reconfigurable systems have been designed since the end of the 1980's [43, 4, 48, 58, 60, 36, 63]. Typically, a reconfigurable-bus architecture consists of a multi-dimensional array of processing elements (PEs). Those PEs are connected to buses through a fixed number of I/O ports. Each PE can locally control the I/O port connection to the bus in each machine communication cycle. The bus reconfiguration can then be made by a different connection style. A reconfigurable mesh is a two dimensional reconfigurable bus system. The most general and powerful reconfigurable mesh model is PARBS [63].

Since we want to concentrate on the optical interconnection in the architecture, we will not describe the reconfigurable mesh and its applications in detail. What we discuss here are its major advantages and disadvantages, how it is served in our optical computation model and how the combination of the traditional reconfigurable mesh and optical interconnections makes an even more powerful architecture. The reconfigurable mesh has a simple and uniform VLSI layout. For those applications in which most computations need to be done through communication with local neighbors by each processor (directly or indirectly connected through the bus segments), it is a very powerful computation architecture. However, for global communications, for example, when large amounts of data need to be transferred among different electrical bus segments, the reconfigurable mesh becomes very inefficient. On the other hand, a free space optical architecture is very good for the global data communications due to the free connections among processors. If fixed deflecting units (e.g. fixed holograms) are used in a free space interconnection, we usually need  $N \times N$  deflecting units to implement the random permutation for only O(N) processors. If reconfigurable deflecting units are used, we may have N deflecting units for N processors. However, this use of the VLSI area is paid off by the time used for reconfiguration of optical deflecting units. Since the computation pattern could be changed very often in an application algorithm, this can be very time consuming for a pure optical reconfigurable interconnection system. Here, "pure" means all interconnections among processors are optical.

ORM provides three types of communication mechanisms. The first is for arbitrary planar connections among sets of locally connected processors using the reconfigurable mesh. The second is for arbitrary connections among N of the processors using the electrical buses on the processing layer and  $N^2$  fixed passive deflecting units on the deflection layer. The third is for arbitrary connections among any of the  $N^2$  processors using the  $N^2$  mechanically reconfigurable deflectors in the deflection layer. The reconfiguration time of the first two communication mechanisms is on the order of nanoseconds, while for the third it is on the order

of milliseconds. One method to avoid the third type of reconfiguration during the execution is to set it up to an efficient topology before the execution starts. A good topology would be one which matches the data flow requirement of the problem being solved. Butrym, Craft, Guise, Murdocca and Sauer [8] and Guan, Barros [25] studied this problem recently.

The rest of the chapter is organized as follows. In Section 3.2, we introduce the ORM architecture in detail. In Section 3.3, the read/write and data movement operations on three communication mechanisms of ORM are described. The conclusion is given in Section 3.4.

# 3.2 The ORM Architecture

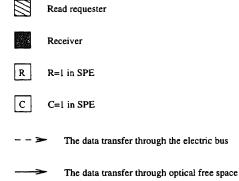

A  $4 \times 4$  optical reconfigurable mesh (ORM) is shown in Figure 3.1. There are two layers in ORM: the deflection layer and the processing layer. The deflection layer consists of  $N^2$  deflecting units and the processing layer has  $N^2$  processing units. The processors on the processing layer are interconnected as a reconfigurable mesh and can also intercommunicate optically using the deflection layer. The reconfigurable mesh model used here is similar to PARBS [63]. The reconfigurable mesh of size  $N^2$  consists of an  $N \times N$  array of processors connected to a grid-shaped reconfigurable broadcast bus, where each processor has a locally controllable bus switch. The switchs allow the broadcast bus to be divided into subbuses, providing smaller reconfigurable meshes or reconfigurable bus segments. Figure 3.2 shows the detailed structure of a processing unit in the processing layer and Figure 3.3 shows the detailed structure of a deflecting unit in the deflection layer. In the following we describe each of those components.

Figure 3.1 The ORM architecture

# 3.2.1 The Processing Unit

There are  $N \times N$  processing units on the processing layer. There are three optical transmitters and one receiver residing in each processing unit. One of the transmitters, TR(1), is directed towards the control unit of the deflection unit. The second one, TR(2), is directed towards the reconfigurable mirror (RM) of the deflection unit and the third one, TR(3), is directed towards the fixed mirror (FM) of the deflection unit. Each processing unit has a constant number of  $\log N$  bit memory cells and simple computation capabilities. It is connected to other processing units in the mesh by the electrical reconfigurable buses. Each processing unit controls the internal reconfigurable switches and is responsible for sending and receiving data to and from other processing units. We index the processing unit in the ith row and the jth column of the mesh on the processing layer as P(i,j) in which,  $1 \le i, j \le N$ .

Figure 3.2 The detailed structure of a processing element

Figure 3.3 The detailed structure of a deflector

# 3.2.2 The Deflection Unit

The deflecting layer contains  $N \times N$  deflecting units. Each deflecting unit consists of two mirrors and an arithmetic control unit. One of the mirrors, called FM (fixed mirror), is fixed which transfers data from the processor under it to a fixed address whenever it is used. Another mirror, called RM (reconfigurable mirror), is reconfigurable. The control unit receives an address from the processor under it, translates the address and controls the direction of the RM. Since the angle of the FM is fixed, the processor can send data directly from one of dedicated transmitters to the desti-

nation without any need to go through the control unit. We define each deflecting unit located directly above P(i,j) (a mirror and the related control unit) as M(i,j).

#### 3.3 Data Movement in ORM

The data can be routed in three different styles in this architecture. In the first method, routing is done only through electric buses. This is called *electrical routing*. The second one is called *optical routing* which uses free space optics. The third type uses electrical and optical free space connections to allow a complete connections among N processors, and is called *electro-optical routing*. Each of the movements is described below.

#### 3.3.1 Electrical Routing

The electric routing in ORM is similar to that of the PARBS system [63]. The electric routing in ORM is any routing from one node to another or a broadcast which uses electric buses in the reconfigurable mesh only. An example for reconfiguration is shown in Figure 3.1. This type of communication is suitable for providing arbitrary connections in the processing layer. For example, see the processing layer of Figure 3.1. There are three groups of processors. Each group has one common bus it can use for intercommunications.

- P(1,1) and P(1,2) are connected to each other.

- P(2,1), P(3,1), P(4,1), P(4,2), P(3,2) and P(2,2) are connected as a circle.

- P(1,3), P(2,3), P(3,3), P(4,3), P(4,4), P(3,4), P(2,4) and P(1,4) are connected as a circle.

# 3.3.2 Optical Routing

The optical routing in ORM is the routing through optical free space interconnections only. The data transfer would not use any electric bus in the system. All  $N^2$

processors can intercommunicate in unit time delay, as long as there is only one read or write from or to each location. In the following, we describe how such an optical connections is established between two processors through the RM (Reconfigurable Mirror).

A connection phase consists of two cycles. In the first cycle, each processor sends the address of its desired destination processor to the arithmetic control unit of its associated mirror using its dedicated laser TR(1). The arithmetic control unit of the mirror computes a rotation degree such that both the origin and destination processors have equal angle with the line perpendicular to the surface of the mirror in the plane formed by the mirror, the source processor and the destination processor. Once the angle is computed, the mirror is rotated to point to the desired destination. In the second cycle, the connection is established by the laser beam TR(2) carrying the data from the source to the mirror and from the mirror being reflected towards the destination. An example of an optical routing from processor P(2,2) to processor P(4,3) is shown in figure 3.1.

The read operation has two phases. In the first phase, the read requirement and the reader's address are sent to the processor which stores the desired data. In the second phase, the data is sent back to the reader depending on the reader's address. Both phases use the two-cycle write routing method.

# 3.3.3 Electro-Optical Routing

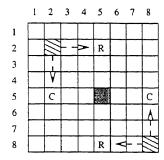

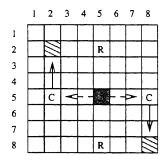

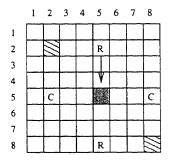

This communication mechanic establishes an efficient full connectivity among only N processors of  $N^2$  processors of ORM situated diagonally in the processing layer as show in Figure 3.4. (i.e. for processors P(j,j) where  $1 \leq j \leq N$ ). The routing technique uses electric buses on the processing layer and the fixed mirrors on the deflection layer. This type of connection is implemented in the following way as shown in Figure 3.4. Each processor P(j,j) is associated with the jth row of the

Figure 3.4 The optical interconnections for electro-optical routing of ORM

deflection unit, where the row contains N fixed mirrors. The ith fixed mirror in that row for  $1 \le i \le N$  is directed to the processing unit P(i,i). The Figure 3.4 shows this communication mechanism. The ith fixed mirror in the first row which is directed to the processing unit P(i,i),  $1 \le i \le 4$ , is displayed in the figure. The other rows have the same type of optical interconnections which are not shown in the figure for the sake of clarity. There are two types of routing possible; Exclusive Read Exclusive Write (EREW) and Concurrent Read Concurrent Write (CRCW). We explain both methodologies below (The other two techniques described earlier, electrical and optical routings, are EREW).

- **3.3.3.1 EREW:** Any processor P(i,i) sends data to P(k,k) in the following way.

- 1. P(i,i) sends the data to P(i,k) through the electrical row bus;

2. P(i,k) sends data to P(k,k) through transmitter TR(3) and its deflector M(i,k).

#### 3.3.3.2 CRCW

**Definition 1** The CRCW access model for N diagonal processors on ORM is defined as follows:

- In one write step, each P(i,i) can send one write request to another PE in the diagonal. If there is more than one write request to P(i,i), P(i,i) will receive only one of them.

- In one read step, each P(i,i) can send one read request to P(k,k),  $k \neq i$ . The reader (multiple readers are allowed) can get the requested data back in the same step.

Now, we prove the following theorem.

**Theorem 3** The concurrent write and the concurrent read of N PEs can be done on ORM in O(1) time.

**Proof:** The proof is done by giving the following constant time algorithm. We assume that the read or write operation signal (operation command) is known by all PEs. The following steps are executed in constant time.

#### Write Operation

There are three steps in this operation. In step 1, the destination address for a write request is broadcast to the row i by each P(i,i). The processor (in row i, for each i) with a j index matching the destination address is an active processor in the step. This processor will be responsible to send data to the destination and its optical light beam is activated. In step 2, a unique data is chosen among multiple write requests to write to a processor. In this step, the losers will become inactive. In step 3, the

unique writing data is sent to each destination. The implementation details of each step are as follows.

- 1. Initially, the ORM performs the row bus connection. Each P(i,i) sends a write request destination address j to the row i. The address can be received by all PEs through the row buses of the mesh. Each PE compares the address with its own column index. The P(i, j) will mark itself as an active PE if the address j is matched to its column index. The others in row i do nothing.

- 2. All PEs of ORM performs the column bus connection except that each active PE disconnects its north port from the south port. Each active PE sends a signal to the south and check the north port. If an active PE does not receive any signal from its north, means that it is a northmost active PE in the column, it activates the light beam. All the other active PEs will not be active any more. The data in P(i, i) for which the P(i, j) is active will be the chosen one writing data to P(j, j).

- 3. Each P(i,i) sends the writing data to the row again. The data will be received by active P(i,j) and sent to P(j,j) through the activated laser beam. Since there is only one sender left in each column after step 2, each P(j,j) will receive at most one data from the free space in the step.

#### Read Operation

The concurrent read operation contains two phases. In the first phase, the readers send read requests to the destination P(j,j). During this step, the electrical and optical route for a P(j,j) to send the data back to multiple readers has been established. In the second phase, the data is sent to the readers by P(j,j). Two variables R and C are used in each PE to implement the operation.

The implementation is as follows:

- 1. The ORM does the row buses connection. Each P(i,i) sends the destination processor address j and the read request (requested memory cell address) to the row i. When j is matched to the column index of a PE, P(i,j) saves the read request and sets the variable R = 1.

- 2. The ORM does the column buses connection. Each P(i,i) sends the address of the destination processor j, to the column i. Each PE compares j with its row index. If they match, the PE sets the variable C = 1.

- 3. The ORM keeps the column buses connection. The PE whose R=1 is an active PE in this step. Find the northmost active PE in each column. This PE activates the light beam and sends the read request to P(j,j) using transmitter TR(3). This can be done because the read request has been saved in this PE in step 1 and the active P(i,j) has its M(i,j) connect the optical path to P(j,j).

- 4. The ORM does the row buses connection. Each PE with C = 1 is an active PE now. It activates the light beam using transmitter TR(3). The requested data is retrieved by each P(j,j) and broadcast to row j. Then the data is sent to the requester P(i,i) through the bus and the light beam of P(j,i) using transmitter TR(3) as shown in the subfigure 3 in Figure 3.5.

#### Examples

In this subsection, we give examples of concurrent write and concurrent read operations in electro-optical routing communication mechanism. The following is an example of a concurrent writing on an  $8 \times 8$  ORM. Assume that the requests for writing values to a variable stored in P(2,2) are made by P(1,1) and P(6,6) in the same step. The value received by P(2,2) is the value sent by P(1,1) since P(1,2) is the northmost active PE in column 2. In Figure 3.5, we use an N=8 ORM system to explain the read operation. Assume that we view the architecture from the top.

Transparent top view of processing layer and deflection layer in step 2 and 3.

Step 5: the receiver sends the data back to the requesters.

Step 4: the representative sends the read request to MPE(5) which stored the requested data.

Figure 3.5 Concurrent read on ORM

We can see PEs in the bottom layer transparently through the deflection layer. Except for senders and receivers, other PEs are not indicated. In this example, we assume that P(2,2) and P(8,8) need to read data from P(5,5). P(2,5) is chosen as the representative to send the required data address to P(5,5) in step 3. In step 4, P(5,5) sends data back. Since the light beams in P(5,2) and P(5,8) are activated, when the data is sent to the bus of row 5, it is redirected by P(5,2) and P(5,3) are P(5,3) and P(5,3) and P(5,3) are activated, when the data is sent to the bus of row 5, it is redirected by P(5,3) and P(5,3) are activated.

# 3.4 Conclusion