New Jersey Institute of Technology Digital Commons @ NJIT

## Dissertations

**Electronic Theses and Dissertations**

Spring 5-31-1997

# Design fabrication and characterization of high performance in GaAs/InP focal plane array in the 1-2.6 µm wavelength region

Krishna R. Linga New Jersey Institute of Technology

Follow this and additional works at: https://digitalcommons.njit.edu/dissertations

Part of the Electrical and Electronics Commons

### **Recommended Citation**

Linga, Krishna R., "Design fabrication and characterization of high performance in GaAs/InP focal plane array in the 1-2.6 µm wavelength region" (1997). *Dissertations*. 1037. https://digitalcommons.njit.edu/dissertations/1037

This Dissertation is brought to you for free and open access by the Electronic Theses and Dissertations at Digital Commons @ NJIT. It has been accepted for inclusion in Dissertations by an authorized administrator of Digital Commons @ NJIT. For more information, please contact digitalcommons@njit.edu.

## **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

#### ABSTRACT

## DESIGN, FABRICATION AND CHARACTERIZATION OF HIGH PERFORMANCE InGaAs/InP FOCAL PLANE ARRAYS IN THE 1-2.6 µm WAVELENGTH REGION

## by Krishna R. Linga

This research thesis describes a new In<sub>v</sub>Ga<sub>1-v</sub>As/InA<sub>v</sub>sP<sub>1-v</sub>/InP technology for long wavelength photodetectors and photodetector arrays. A unique and novel detector structure was designed and fabricated using Hydride Vapor Phase Epitaxy, for low leakage current photodetector arrays in the 1-2.6 µm wavelength region. Potential applications of InGaAs focal plane arrays include near-infrared spectroscopy, fluorescence, remote sensing, environmental sensing, space and astronomical applications. The unique design concepts included the step grading of InAsP layers, lower lattice mismatch between the two InAsP graded layers, lattice matched InAsP cap layer and InGaAs absorption layer, sulphur doping of InGaAs absorption layer and InAsP layers. Improved device fabrication techniques including rapid thermal annealing and precisely controlled diffusion were implemented during the processing of 1024 element linear photodetector arrays to reduce the dislocation density. An analysis of dark current, which is the critical parameter was required and is described in detail. The dark current analysis and the experimental results showed that the dark current is bulk dominated and is due to the crystal defects and dislocation density.

Each element of the focal plane array consisted of a 13 X 500 um<sup>2</sup> active area with an element to element spacing (pitch) of 25 um. The focal plane architecture designed had two 512 element (left and right) multiplexers and a 1024 element detector array and was integrated in a 24 pin dual-in-line package.

A unique and novel Si read-out multiplexer was designed and fabricated using radiation hardened N-well CMOS process. Each multiplexer unit cell consisted of a capacitive transimpedance amplifier, correlated double sampling circuit, threshold non uniformity correction circuit and an output buffer stage.

Integration and testing of InGaAs focal plane arrays with cut-off wavelengths of  $1.7 \mu m$ ,  $2.2 \mu m$  and  $2.6 \mu m$  are described. The performance of the focal plane arrays was analyzed in detail and the results showed that the 10 fA dark current levels could be achievable with 1024 element InGaAs/InP focal plane arrays in the 1-2.6 um wavelength region. The dark current achieved from the test focal plane arrays was < 1 fA for 1.7 um, < 20 fA for 2.2 um and < 50 fA for 2.6 um cut-off wavelength. Radiation testing using proton, gamma and electron particle radiation on InGaAs photodetectors and photodetector arrays showed that InGaAs/InP focal plane arrays can with stand upto 15 Krad (Si) particle radiation. Comparison of the results achieved with published results of other technology (HgCdTe) operating at the same temperature shows that InGaAs/InP Focal Plane Arrays have lower dark current by a factor of 10-100.

## DESIGN, FABRICATION AND CHARACTERIZATION OF HIGH PERFORMANCE InGaAs/InP FOCAL PLANE ARRAYS IN THE 1-2.6 μm WAVELENGTH REGION

by Krishna R. Linga

A Dissertation Submitted to the Faculty of New Jersey Institute of Technology in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

Department of Electrical and Computer Engineering

May 1997

Copyright © 1997 by Krishna Linga ALL RIGHTS RESERVED

## APPROVAL PAGE

## DESIGN, FABRICATION AND CHARACTERIZATION OF HIGH PERFORMANCE InGaAs/InP FOCAL PLANE ARRAYS IN THE 1-2.6 μm WAVELENGTH REGION

Krishna R. Linga

| Dr. Durga M. Misra, Dissertation Advisor                         | Date |

|------------------------------------------------------------------|------|

| Associate Professor of Electrical and Computer Engineering, NJIT |      |

|                                                                  |      |

|                                                                  |      |

|                                                                  |      |

| $\sim$                                                           | -    |

| Dr. Roy Cornely, Committee Member                                | Date |

| Professor of Electrical and Computer Engineering, NJIT           |      |

|                                                                  |      |

|                                                                  |      |

|                                                                  |      |

|                                                                  |      |

| Dr. Kenneth Sohn, Committee Member                               | Date |

| Associate Chairman of Electrical and Computer Engineering, NJIT  |      |

|                                                                  |      |

|                                                                  |      |

|                                                                  |      |

|                                                                  |      |

| Dr. N. M. Ravindra, Committee Member                             | Date |

| Associate Professor of Physics Department, NJIT                  |      |

|                                                                  |      |

|                                                                  |      |

|                                                                  |      |

| <u></u>                                                          |      |

Dr. C. S. Wang, Committee Member Vice President, Advanced Research, Epitaxx, Inc., W. Trenton, NJ Date

## **BIOGRAPHICAL SKETCH**

Author: Krishna Rao Linga

Degree: Doctor of Philosophy

**Date:** May 1997

## Undergraduate and Graduate Education:

- Doctor of Philosophy in Electrical Engineering, New Jersey Institute of Technology, Newark, NJ 1997

- Master of Science in Electrical Engineering, New Jersey Institute of Technology, Newark, NJ 1990

- Bachelor of Science in Electrical Engineering, University of Mysore, Mysore, India, 1987

Major: Electrical Engineering

## Presentations and Publications:

- G.H. Olsen, S. Mason, G. Gasparian, A. M. Joshi, K. Woodruff, K. Linga, D. Rodefeld, M. Lange, F. Speer, V. S. Ban and G. Erickson, "Room temperature properties of Indium Gallium Arsenide detectors optimized for 1.8, 2.1 and 2.5 um," in Proc. IEEE LEOS Conf., Boston, Nov. 1990.

- K.R. Linga, G.H. Olsen, V.S. Ban, A.M. Joshi and W.F. Kosonocky, "Dark current analysis and characterization of In<sub>x</sub>Ga<sub>1-x</sub>As/InAs<sub>y</sub>P<sub>1-y</sub> graded photodiodes with x > 0.53 for response to longer wavelength (> 1.7 um)," IEEE Journal of Lightwave Technology, Vol. 10, No. 8, pp. 1050-1055, Aug. 1992.

- K.R. Linga, A.M. Joshi, V.S. Ban and S. Mason, "1024 element In<sub>x</sub>Ga<sub>1-x</sub>As/InAs<sub>y</sub>P<sub>1-y</sub> detector arrays for environmental sensing from 1 um to 2.6 um," Proc. SPIE, Vol. 2021, pp. 90-97, July 1993.

- 4. N.B. Urli, V.S. Ban and K. Linga, "Defects in infrared detectors based on In-Ga-As alloys," Proc. 4th International Conf. on New Tech., pp. 88-94, Pula, Oct. 1993.

- 5. W.F. Kosonocky, W. Kleinhans, C. Lau, K.R. Linga and M. Lourie, "Low-Bias CTIA Multiplexer for 1024-Element InGaAs Line Sensors," Pro. SPIE, Vol. 2226, pp. 152-171, Apr. 1994.

- K. R. Linga, C.S. Wang, Y. Dzialowski, M. Lourie, S. Mason and W.F. Kosonocky, "High performance 1024 element InGaAs hybrid focal plane arrays from 1 to 2.6 um," Proc. Of OPTO94 Conf., pp. 1024-1030, Paris Apr. 1994.

- 7. A.S. Kanofsky and K. Linga, "Effects of radiation on long wavelength devices," Proc. SPIE, Vol. 2074, pp. 214-220, Aug. 1994.

- 8. R. McKee, D. Lampe, J. Halvis, T. Henricks, T. Wilson, W. Kleinhans, K. Linga, M. Lange, "Near room temperature performance of a SWIR InGaAs/Si hybrid 96X25 element TDI performance FPA," Proc. SPIE, Vol. 2746, pp. 152-161, Apr. 1996.

- 9. K. Linga, C.S. Wang, M. Lourie, W. Xu and W.F. Kosonocky, "High Performance InGaAs/InP Focal Plane Arrays," POEM Annual Review Meeting, Princeton University, March 1997.

- 10. K. Linga, C.S. Wang, W.F. Kosonocky and D. Misra, "Noise Sources in Long Wavelength InGaAs/InP Focal Plane Arrays," To be published, 1997.

In memory of Walter Kosonocky

.

#### ACKNOWLEDGMENT

I wish to express my sincere gratitude to Dr. Walter F. Kosonocky and Dr. Durga Misra for their valuable guidance, inspiration and encouragement during the entire course of this research. I am very thankful to Dr. Durga Misra for accepting to be my advisor during the difficult times and providing valuable guidance, support and reassurance. I am also thankful to Dr. Roy Cornely, Dr. Kenneth Sohn and Dr. Ravindra of New Jersey Institute of Technology and Dr. C.S. Wang of Epitaxx, Inc. for accepting to be in my committee. I am very thankful to Epitaxx, Inc. and Dr. Kosonocky for supporting me financially through out my graduate study.

I also express my sincere thanks to Ken Fujiwara, Nobu Hiraguri, Dr. Yves Dzialowski, Dr. C.S. Wang and Epitaxx, Inc. management and staff who has provided me with an excellent environment and resources for the research work. I would especially like to acknowledge the help provided by my colleagues Suzanne McCoy for epitaxial layer growth using Hydride Vapor Phase Epitaxy reactor, Hisao Nagata and Krys Slomkowski for detector fabrication and Mark Lourie, Wei Xu and Doug Nelson for focal plane array testing development and data collection. I would also like to acknowledge the help provided by Dr. Walter Kosonocky and W. Kleinhans of Valley Oak Semiconductors for the design and layout and Honeywell Semiconductors for the fabrication of the multiplexers. I am very thankful to Dr. Mike Scott of Epitaxial Products International and Dr. Y. Miura of Sumitomo Electric Industries for valuable discussions on the Organo Metallic and Chloride Vapor Phase Epitaxial growth of InAsP layers on InP substrate. I gratefully acknowledge the encouragement and support of Dr. W. Fricke and D. Schink of Dornier GmbH, Dr. R. Hoogeveen, Dr. J. de Vries and T. Kamperman of Space Research Organization of Netherlands(SRON), R. Van Aalst of Fokker Space & Systems, Dr. B. Burmester of Ball Aerospace, Dr. J. Geary of Smithsonian and Dr. J. Burrows of University of Bremen. This work was supported by Dornier GmbH, Germany under the contract "Channel 8 InGaAs Detector Array Sliver Breadboard Phase" and Fokker Space & Systems, Netherlands under the contract "Focal Plane Arrays for NIR channels of SCIAMACHY".

Finally, I thank my wife Sujaya and my brother Rao N. Linga for their support and understanding through out my graduate study.

| Chapter |                | Page                                              |    |

|---------|----------------|---------------------------------------------------|----|

| 1       | 1 INTRODUCTION |                                                   |    |

| 2       | BACK           | GROUND                                            | 5  |

|         | 2.1            | Research Objective                                | 7  |

|         | 2.2            | Main Problems                                     | 8  |

|         | 2.3            | Performance Requirements                          | 11 |

| 3       | OVER           | RVIEW OF TECHNOLOGY                               | 13 |

|         | 3.1            | Crystal Growth Techniques                         | 14 |

|         | 3.2            | Device Design and Cross-section                   | 18 |

|         | 3.3            | Device Fabrication                                | 29 |

|         | 3.4            | Device Results                                    | 35 |

| 4       | DARK           | CURRENT ANALYSIS                                  | 43 |

|         | 4.1            | Theory of Dark Current                            | 43 |

|         | 4.2            | Parameter Interpolation                           | 46 |

|         | 4.3            | Simulation Results                                | 49 |

| 5       | FOCA           | L PLANE ARRAY (FPA) ARCHITECTURE                  | 62 |

|         | 5.1            | Focal Plane Architecture                          | 62 |

|         | 5.2            | Focal Plane Array Integration and Testing         | 62 |

| 6       | READ           | D-OUT ELECTRONICS                                 | 68 |

|         | 6.1            | Introduction                                      | 69 |

|         | 6.2            | Multiplexer Performance and Design Specifications | 69 |

|         | 6.3            | Design of the Multiplexer                         | 76 |

## TABLE OF CONTENTS

## TABLE OF CONTENTS (Continued)

•

| Chapter |        | Page                                                   |     |

|---------|--------|--------------------------------------------------------|-----|

|         | 6.4    | Multiplexer Chip Layout                                | 89  |

|         | 6.5    | Multiplexer Fabrication                                | 91  |

|         | 6.6    | Multiplexer Testing and Performance Results            | 94  |

| 7       | FOCA   | L PLANE ARRAY TESTING AND RESULTS                      | 108 |

|         | 7.1    | Focal Plane Array Results and Analysis                 | 108 |

|         | 7.2    | Radiation Hardness Results and Analysis                | 126 |

|         | 7.3    | Focal Plane Array Noise Analysis                       | 127 |

|         | 7.4    | Comparison with Other Technology                       | 132 |

| 8       | CONC   | CLUSIONS                                               | 134 |

|         | 8.1    | Future Direction                                       | 136 |

| APPE    | NDIX A | A DISLOCATION DENSITY USING DIFFUSION<br>APPROXIMATION | 137 |

| REFE    | RENCE  | ES                                                     | 141 |

## LIST OF TABLES

| Table |                                                                       | Page |

|-------|-----------------------------------------------------------------------|------|

| 3.1   | Effect of RTA on dark current                                         | 27   |

| 3.2   | Dark current as a function of InGaAs and InP layer doping             | 36   |

| 4.1   | Interpolated parameters of $In_xG_{1-x}As$ absorption layer           | 49   |

| 6.1   | Performance and design specifications of InGaAs multiplexer           | 70   |

| 6.2   | Calculated Readout Noise of InGaAs Multiplexers                       | 74   |

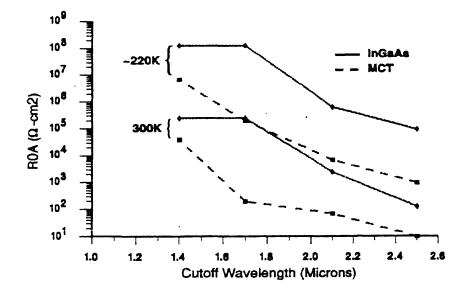

| 7.1   | Comparison of HgCdTe and InGaAs detector R <sub>o</sub> A performance | 133  |

.

## LIST OF FIGURES

| Figure | Figure Page                                                                                                                                                                                                                                                                                     |    |  |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

| 2.1    | Energy bandgap, cut-off wavelength and lattice constant for a variety of semiconductor material                                                                                                                                                                                                 | 9  |  |

| 3.1    | Cross-section and energy band diagram of a p-i-n diode                                                                                                                                                                                                                                          | 17 |  |

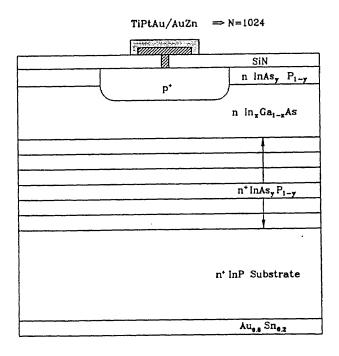

| 3.2    | Schematic cross-section of 1.7 um cut-off InGaAs detector                                                                                                                                                                                                                                       | 20 |  |

| 3.3    | Band diagram of the planar lattice matched $In_{0.53}Ga_{0.47}As$ photodiode                                                                                                                                                                                                                    | 20 |  |

| 3.4    | Schematic cross-section of 2.2 um and 2.6 um cut-off wavelength<br>InGaAs detector                                                                                                                                                                                                              | 21 |  |

| 3.5    | Schematic cross-section of the 2.6 um photodiode                                                                                                                                                                                                                                                | 22 |  |

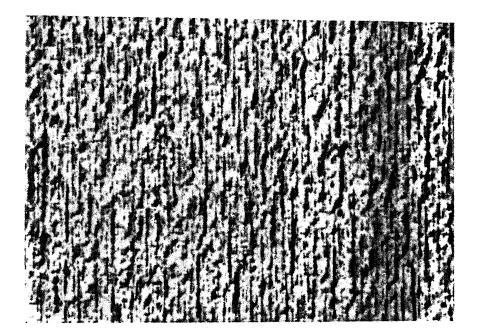

| 3.6    | Optical micrograph showing surface morphology of an $In_xGa_{1-x}As/InAs_yP_{1-y}$<br>2.6 um photodetector structure on a (100)-2° InP substrate with a lattice<br>mismatch of 0.33% between consecutive mismatched InAsP graded layers<br>(100X magnification)                                 | 24 |  |

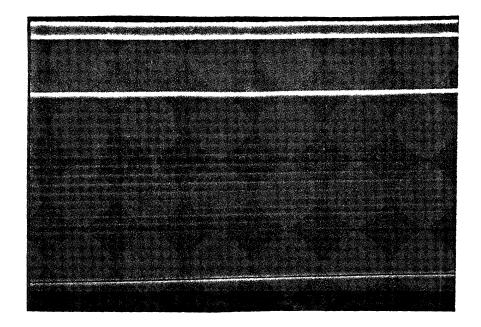

| 3.7    | Optical micrograph showing surface morphology of an In <sub>x</sub> Ga <sub>1-x</sub> As/InAs <sub>y</sub> P <sub>1-y</sub> 2.6 um photodetector structure on a (100)-2° InP substrate with a lattice mismatch of 0.13% between consecutive mismatched InAsP graded layers (100X magnification) | 24 |  |

| 3.8    | SEM cross-section of an $In_xGa_{1-x}As/InAs_yP_{1-y}$ 2.6 um photodiode structure on a (100)-2° InP substrate                                                                                                                                                                                  | 25 |  |

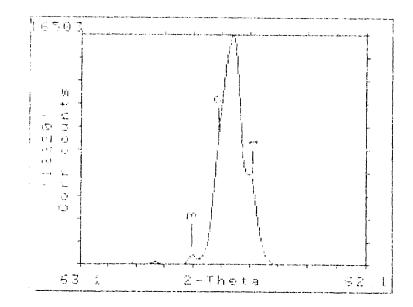

| 3.9    | X-ray diffraction spectra of an $In_{0.82}Ga_{0.18}As$ photodiode structure                                                                                                                                                                                                                     | 26 |  |

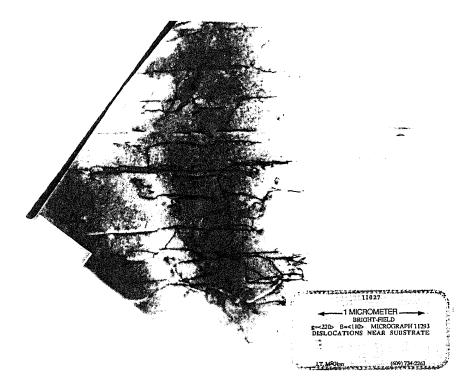

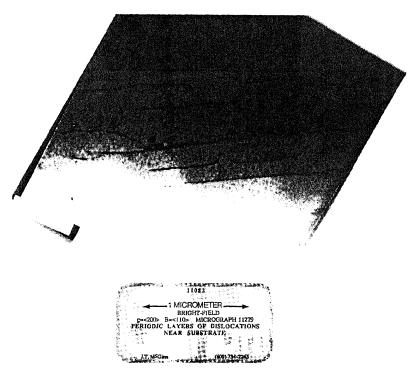

| 3.10   | TEM micro graph showing the cross section of an In <sub>0.82</sub> Ga <sub>0.18</sub> As photodiode structure before thermal annealing                                                                                                                                                          | 28 |  |

| 3.11   | TEM micro graph showing the cross section of an $In_{0.82}Ga_{0.18}As$ photodiode structure after thermal annealing                                                                                                                                                                             | 28 |  |

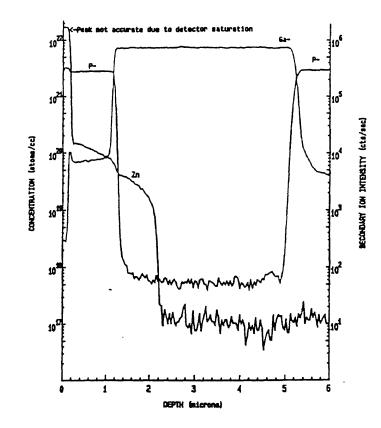

| 3.12   | SIMS profile of an In <sub>0.82</sub> Ga <sub>0.18</sub> As photodetector structure                                                                                                                                                                                                             | 30 |  |

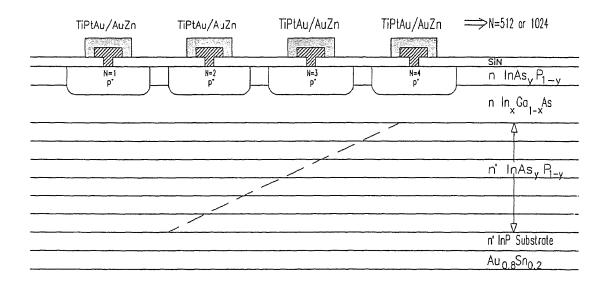

| 3.13   | Cross-section of 1024 element $In_xGa_{1-x}As/InAs_yP_{1-y}$ photodetector array                                                                                                                                                                                                                | 31 |  |

| 3.14   | Wafer Surface(coated with silicon nitride) after annealing                                                                                                                                                                                                                                      | 33 |  |

| Figure | e P                                                                                                                                                | age |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.15   | Wafer surface(coated with silicon nitride) before annealing                                                                                        | 33  |

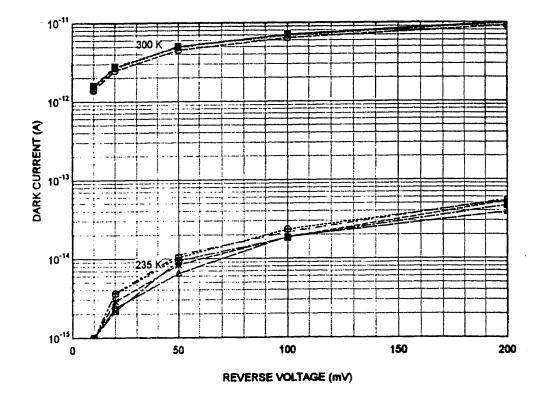

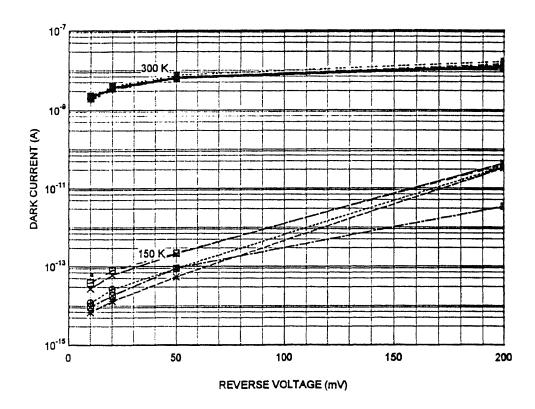

| 3.16   | Dark current-voltage characteristics of 1.7 um cut-off InGaAs detector                                                                             | 36  |

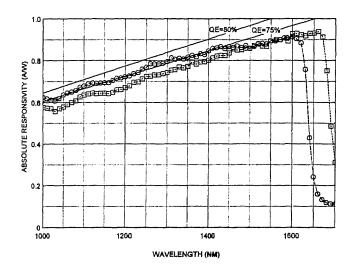

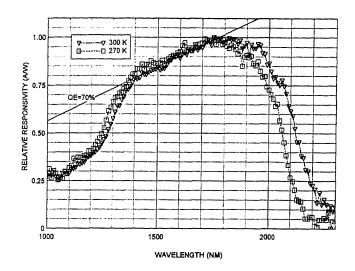

| 3.17   | Spectral response of 1.7 um cut-off InGaAs detector                                                                                                | 37  |

| 3.18   | Dark current-voltage characteristics of 2.2 um cut-off InGaAs detector                                                                             | 38  |

| 3.19   | Spectral response of 2.2 um cut-off InGaAs detector                                                                                                | 39  |

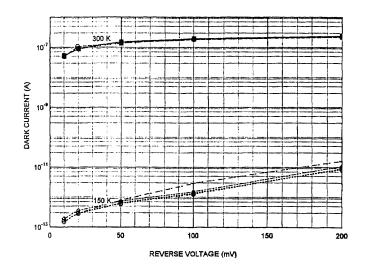

| 3.20   | Dark current-voltage characteristics of 2.6 um cut-off InGaAs detector                                                                             | 40  |

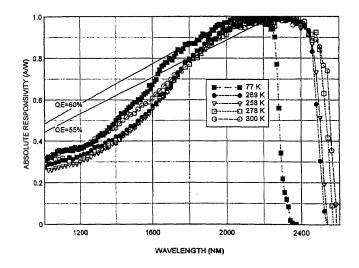

| 3.21   | Spectral response of 2.6 um cut-off InGaAs detector                                                                                                | 40  |

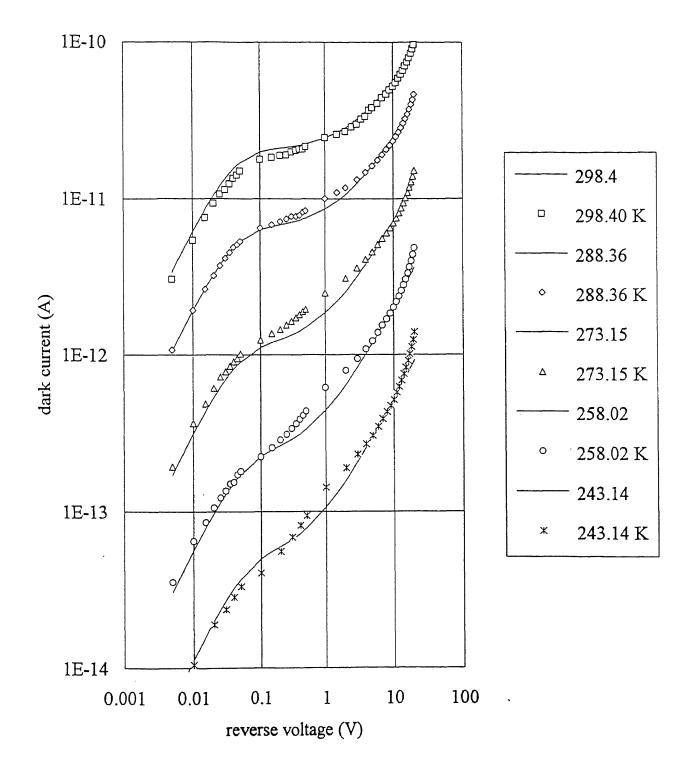

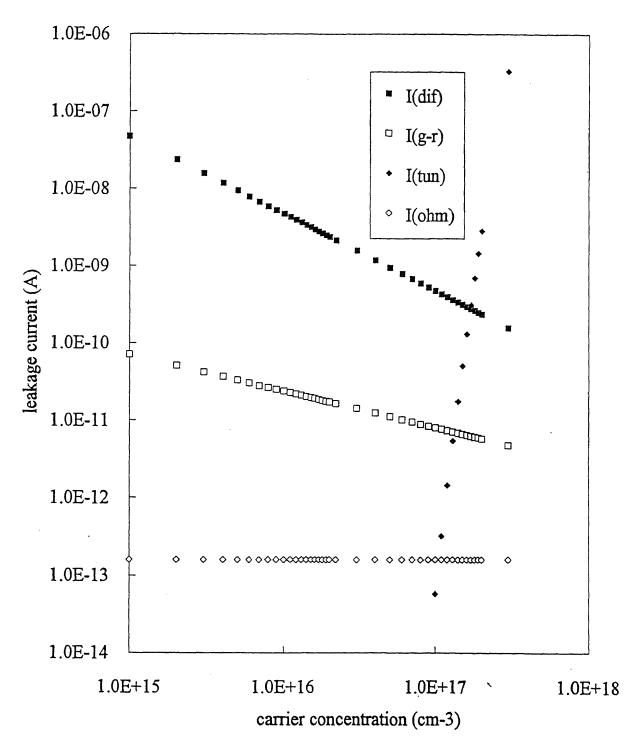

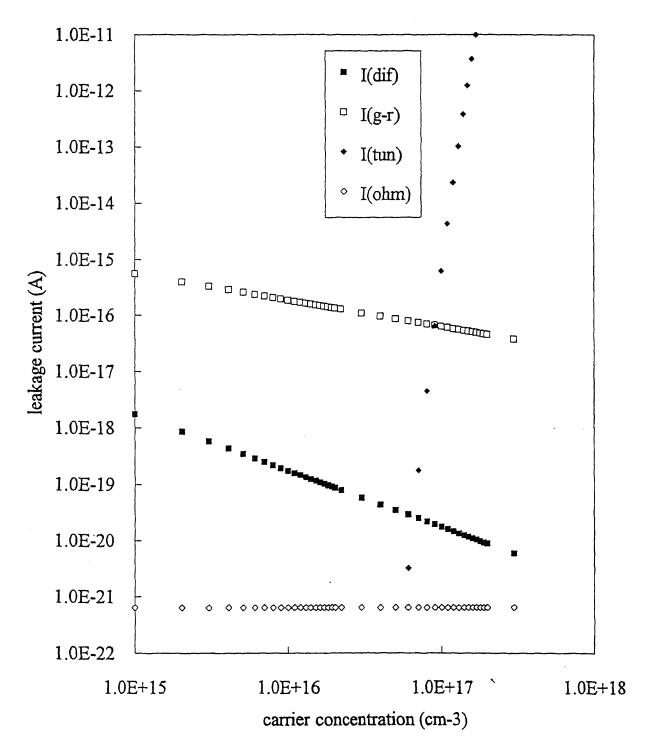

| 4.1    | Measured and simulated results of dark current as a function of reverse voltage                                                                    | 52  |

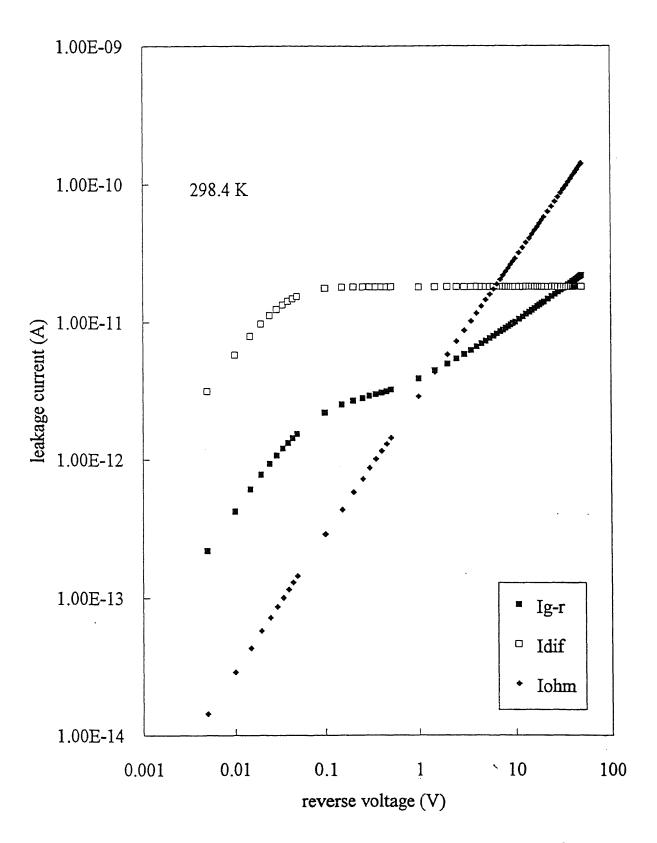

| 4.2(a) | Simulated results of dark current contributions as a function of reverse voltage at room-temperature                                               | 53  |

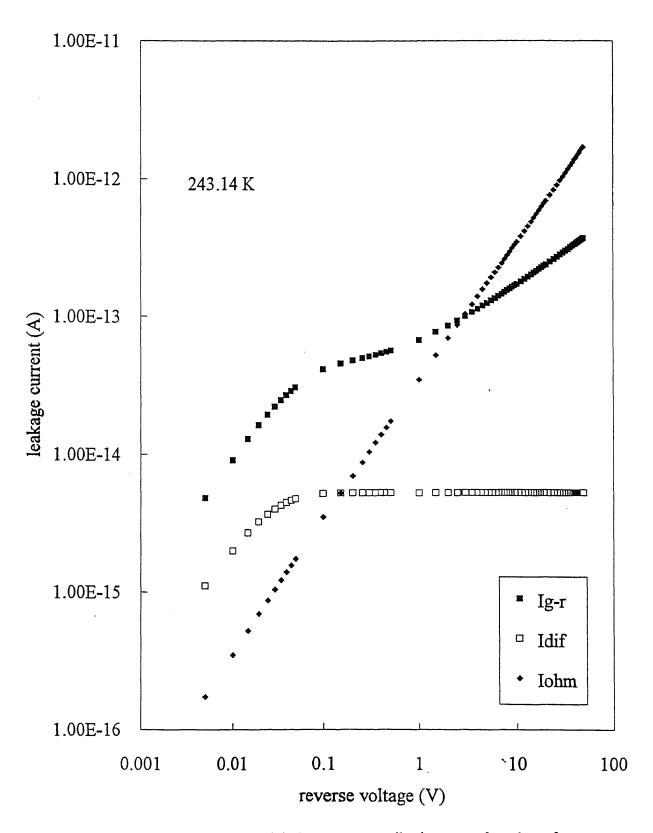

| 4.2(b) | Simulated results of dark current contributions as a function of reverse voltage at 243 K                                                          | 54  |

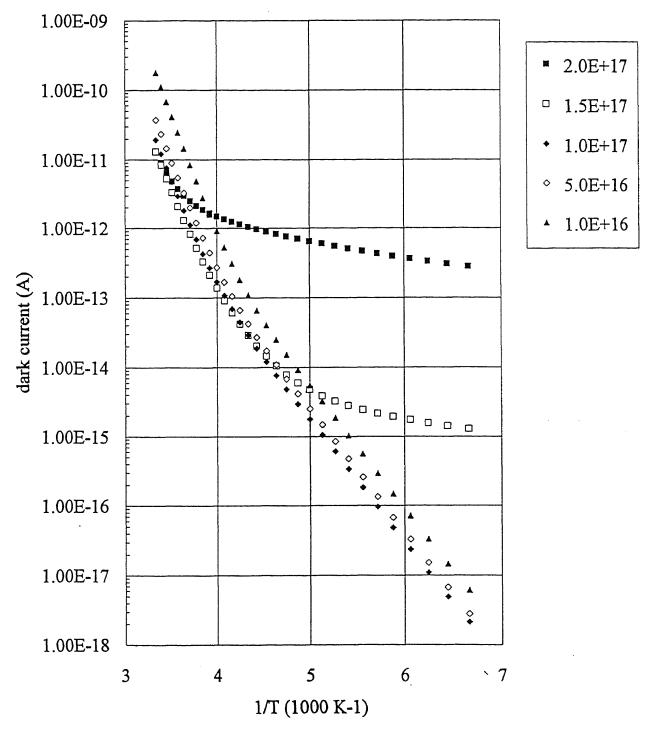

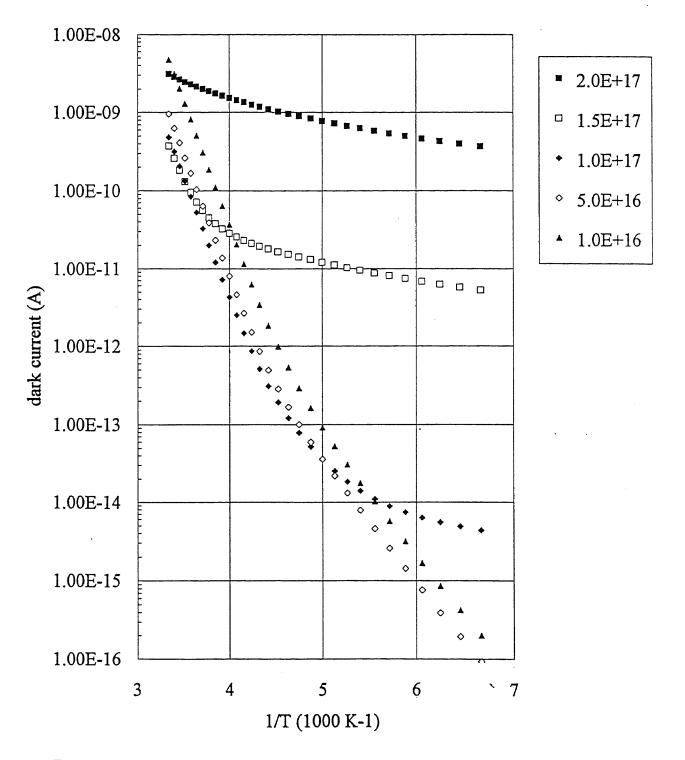

| • • •  | Simulated results of dark current as a function of temperature and In <sub>0.72</sub> Ga <sub>0.28</sub> As layer (2.2 um cut-off) doping          | 55  |

| 4.3(b) | Simulated results of dark current as a function of temperature and $In_{0.82}Ga_{0.18}As$ (2.6 um cut-off) layer doping                            | 56  |

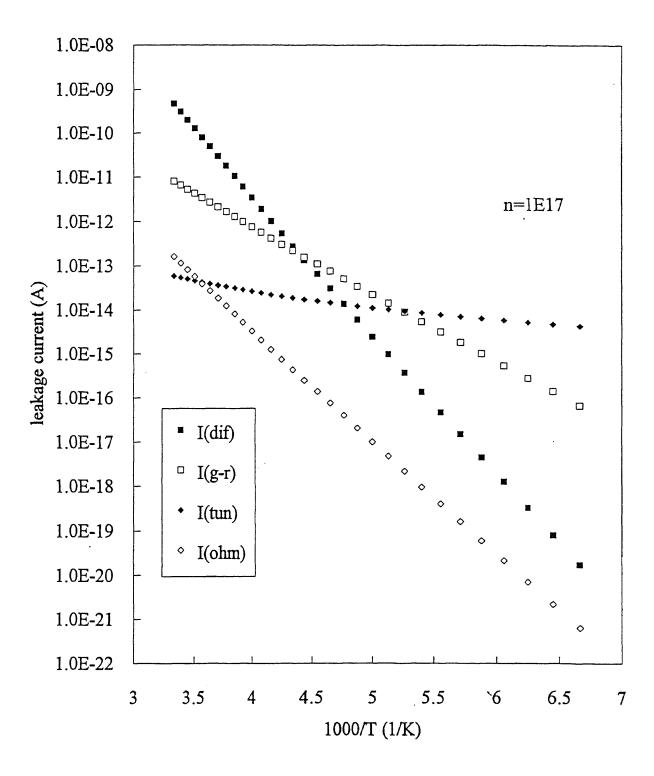

| 4.4    | Simulated results of dark current contributions as a function of temperature for $In_{0.82}Ga_{0.18}As$ (2.6 um cut-off) detector                  | 57  |

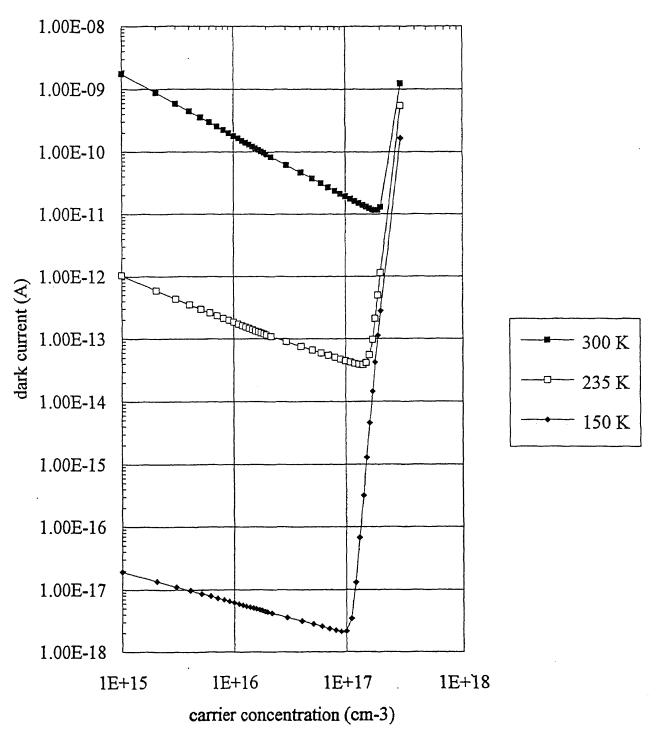

| 4.5(a) | Simulated results of dark current as a function of temperature and $In_{0.72}Ga_{0.28}As$ (2.2 um cut-off) absorption layer doping                 | 58  |

| 4.5(b) | Simulated results of dark current as a function of temperature and $In_{0.82}Ga_{0.18}As$ (2.6 um cut-off) absorption layer doping                 | 59  |

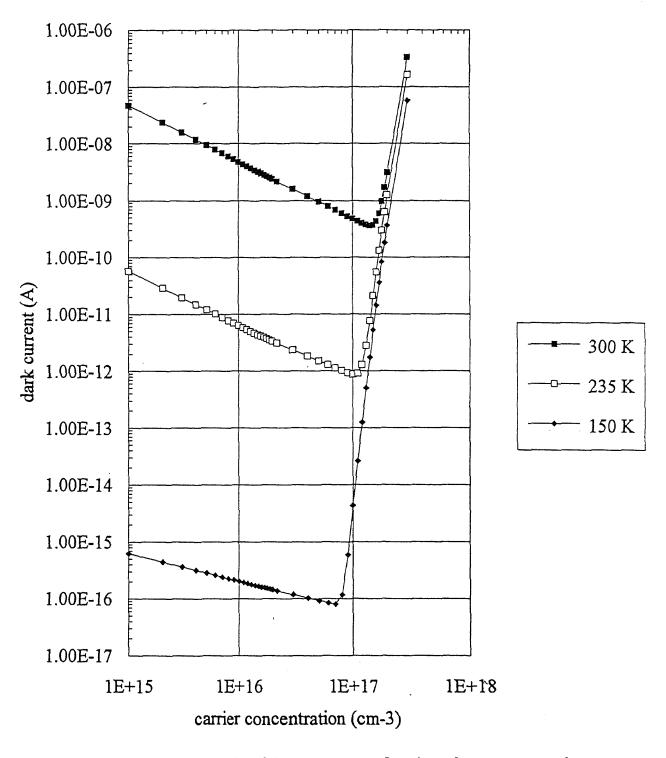

| 4.6(a) | Simulated results of dark current components as a function of $In_{0.82}Ga_{0.18}As$ (2.6 um cut-off) absorption layer doping at 300 K temperature | 60  |

| Figur  | e ]                                                                                                                                                | Page       |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 4.6(b) | Simulated results of dark current components as a function of $In_{0.82}Ga_{0.18}As$ (2.6 um cut-off) absorption layer doping at 150 K temperature | 61         |

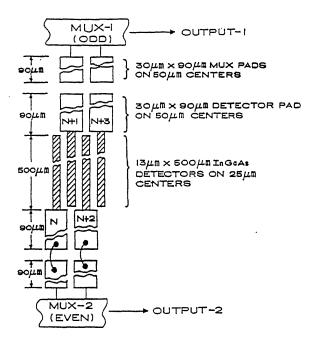

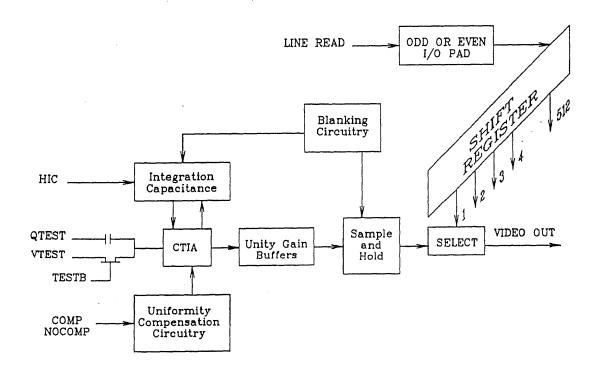

| 5.1    | Focal Plane Array architecture                                                                                                                     | 63         |

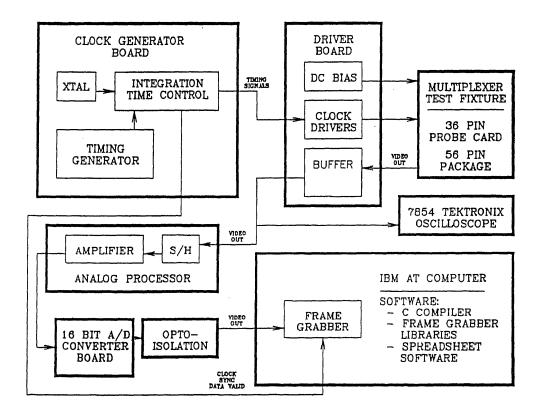

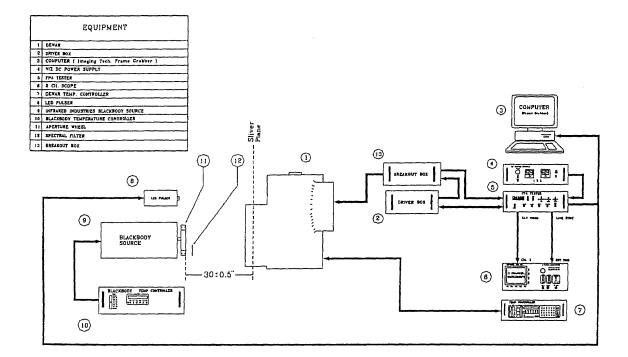

| 5.2    | Block diagram of the multiplexer test setup                                                                                                        | 65         |

| 5.3    | Functional block diagram of the multiplexer test setup                                                                                             | 66         |

| 5.4    | Block diagram of the InGaAs Focal Plane Array test setup                                                                                           | 67         |

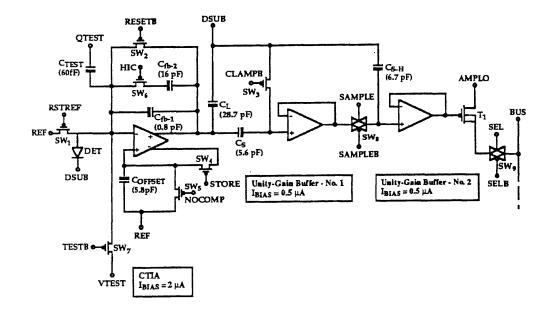

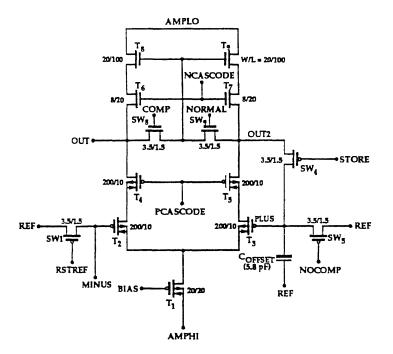

| 6.1    | Schematic of the multiplexer input circuit                                                                                                         | 7 <b>7</b> |

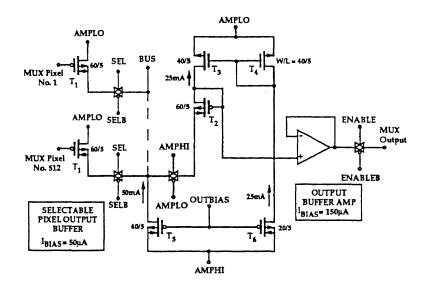

| 6.2    | Selectable MUX pixel buffer                                                                                                                        | 79         |

| 6.3    | CTIA of the MUX input circuit                                                                                                                      | 79         |

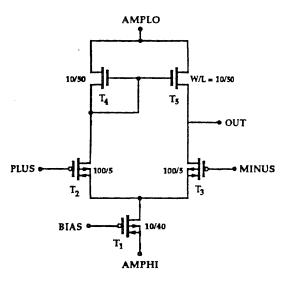

| 6.4    | Opamp for unity-gain-buffer No.1 and No.2                                                                                                          | 80         |

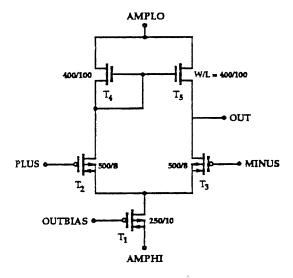

| 6.5    | Opamp for output buffer                                                                                                                            | 80         |

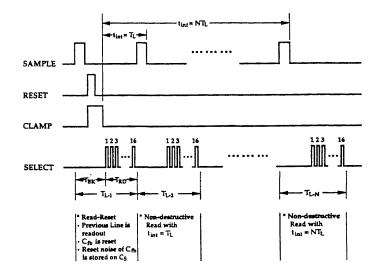

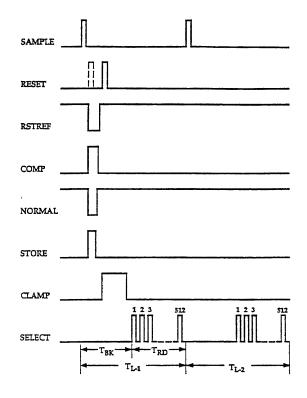

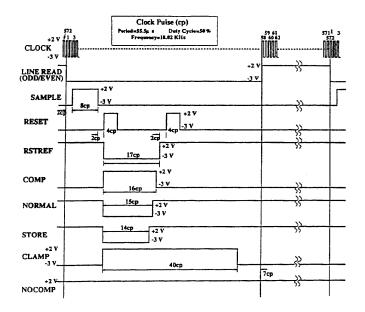

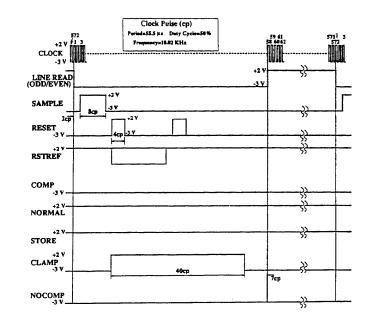

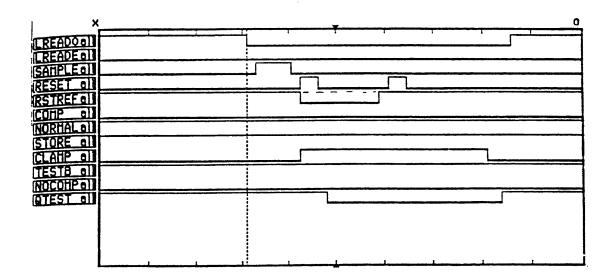

| 6.6    | Clock waveforms for operation of multiplexer without non-uniformity correction                                                                     | 83         |

| 6.7    | Clock waveforms for operation of multiplexer with non-uniformity correction                                                                        | ı 86       |

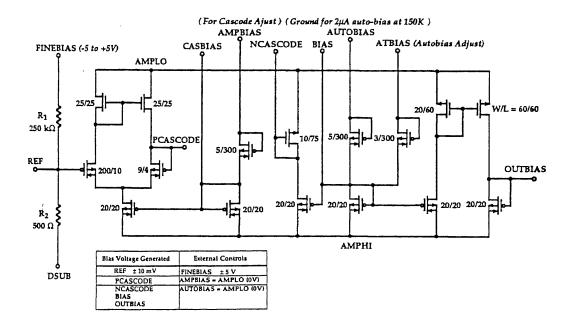

| 6.8    | Auto-bias generators                                                                                                                               | 87         |

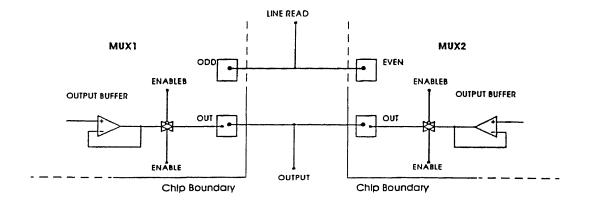

| 6.9    | Output connection of ODD MUX and EVEN MUX                                                                                                          | 89         |

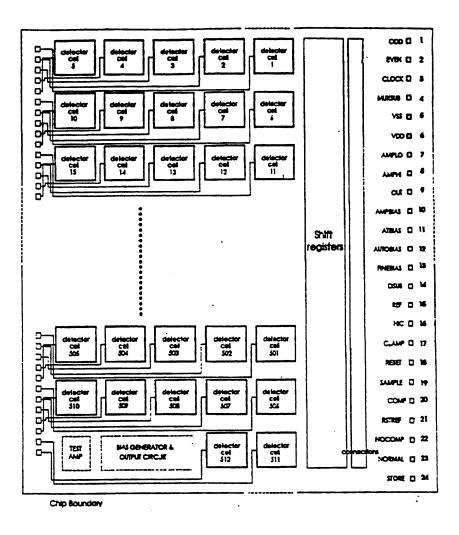

| 6.10   | Schematic of the MUX chip layout                                                                                                                   | 90         |

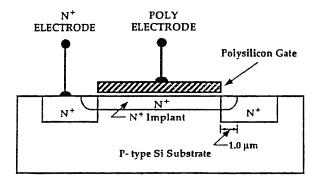

| 6.11   | Cross-sectional view of linear capacitor                                                                                                           | 93         |

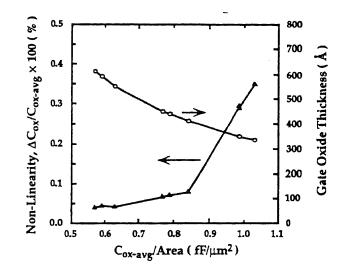

| 6.12   | Tradeoff of non-linearity Vs capacitance for polysilicon-on $N^+$ capacitors                                                                       | 94         |

| 6.13   | Clock waveforms for operation with periodic non-uniformity correction                                                                              | . 95       |

| 6.14   | Clock waveforms for operation without non-uniformity correction                                                                                    | 96         |

| Figur | re                                                                                                                         | Page |

|-------|----------------------------------------------------------------------------------------------------------------------------|------|

| 6.15  | Clock waveforms for MUX normal (NOCOMP) mode with QTEST                                                                    | 99   |

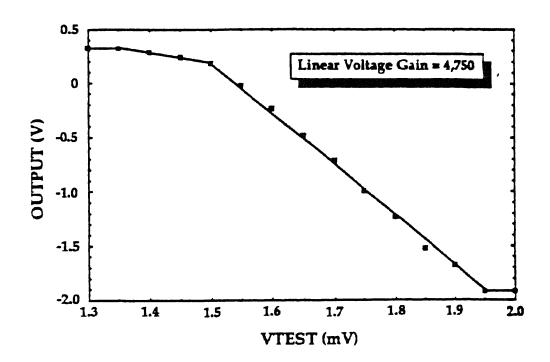

| 6.16  | Multiplexer transfer characteristics                                                                                       | 100  |

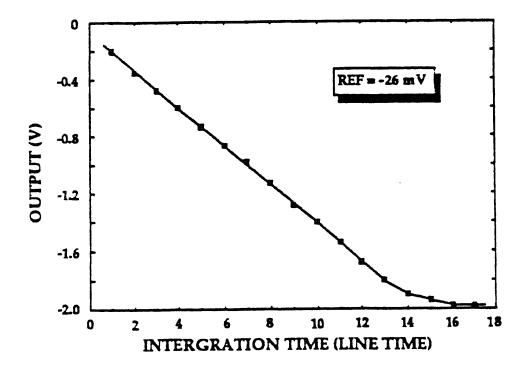

| 6.17  | MUX output linearity with integration of dark current in NOCOMP mode                                                       | 101  |

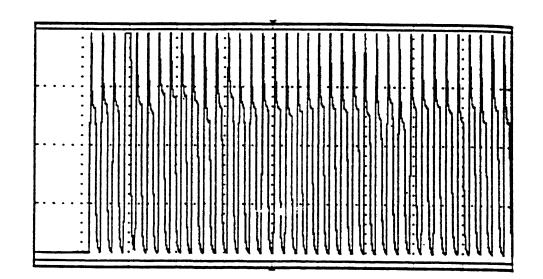

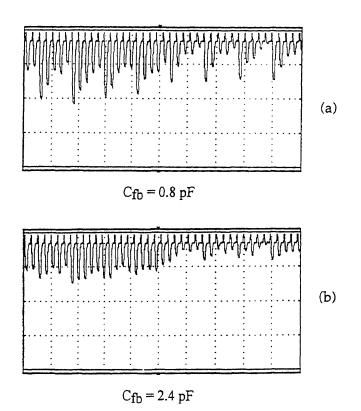

| 6.18  | ODD MUX output waveforms for COMP mode with VTEST=DSUB for Cfb=0.8 pF (scale: 20 mV/div)                                   | 103  |

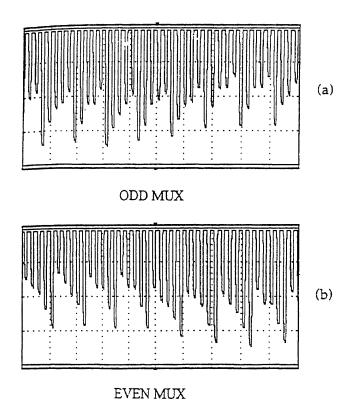

| 6.19  | MUX output waveforms for QTEST=+3V step input for ODD MUX in (a) and EVEN MUX in (b) (scale: 15 mV/div)                    | 106  |

| 6.20  | MUX output waveforms for ODD MUX with QTEST=0 V for $C_{fb}$ =0.8 pF in (a) and $C_{fb}$ =0.8 pF in (b) (scale: 15 mV/div) | 107  |

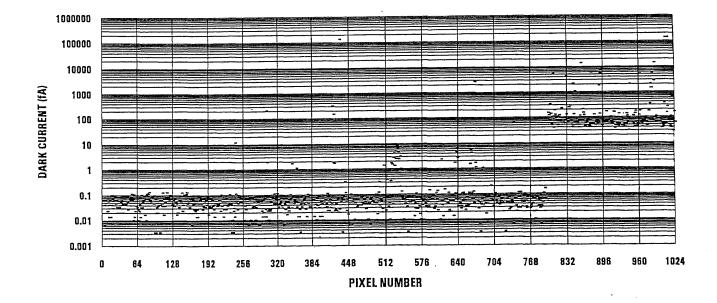

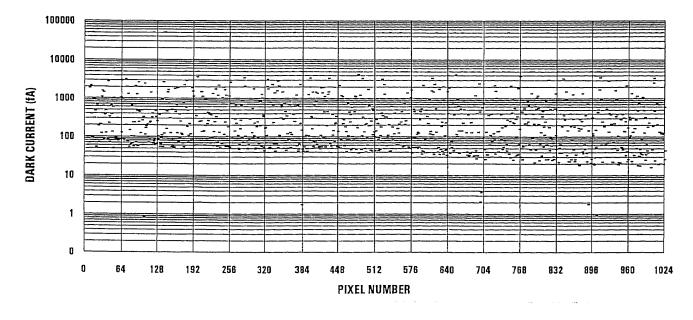

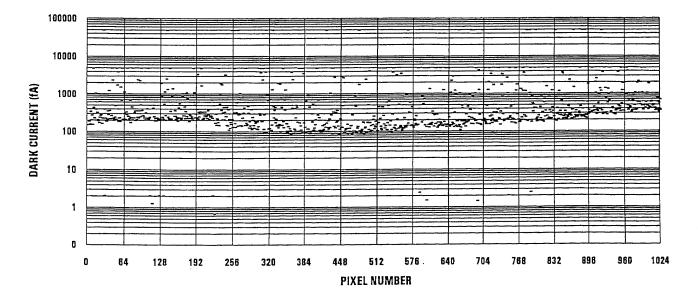

| 7.1   | Dark current vs. pixel number of 1.7 um InGaAs focal plane array                                                           | 108  |

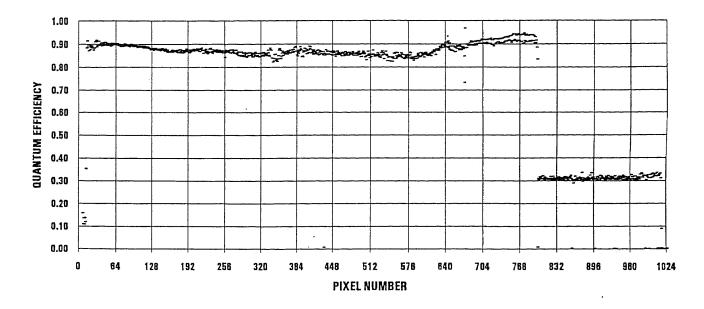

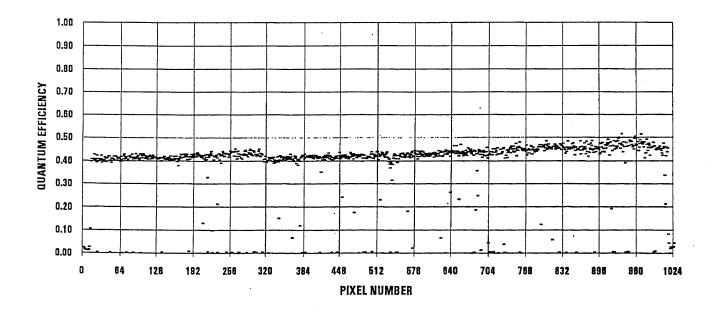

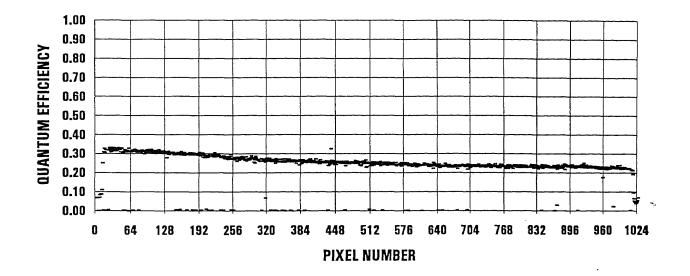

| 7.2   | Flat-field optical response of 1.7 um InGaAs focal plane array                                                             | 111  |

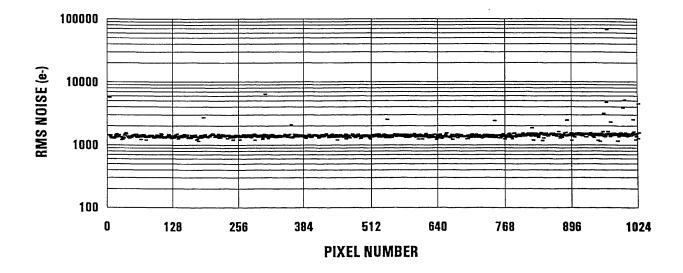

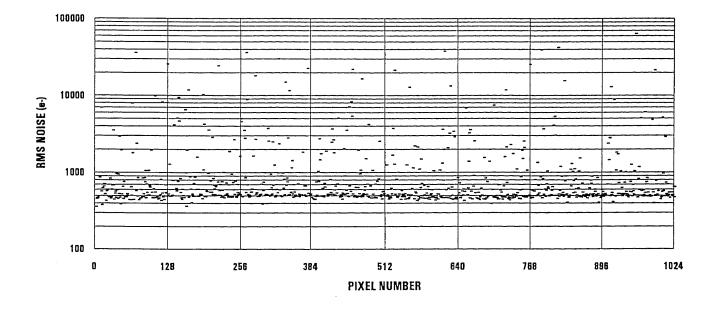

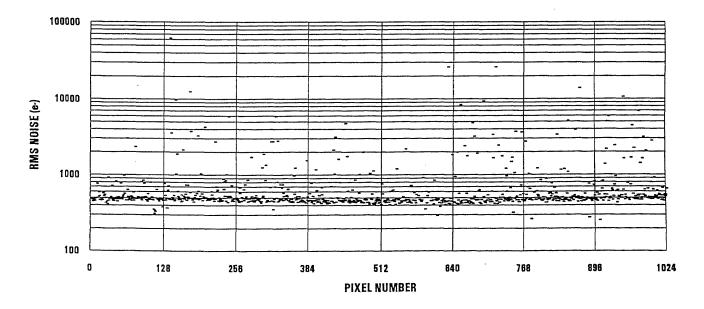

| 7.3   | Measured noise results of 1.7 um InGaAs focal plane array                                                                  | 111  |

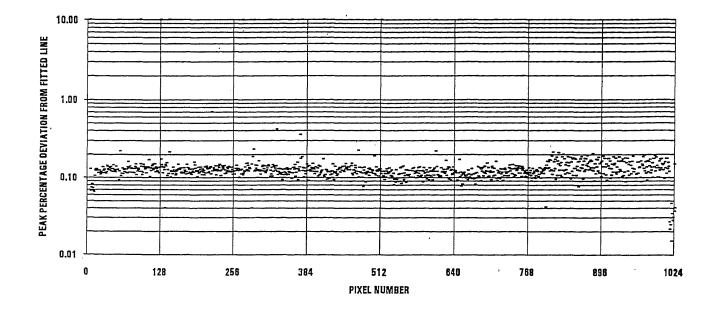

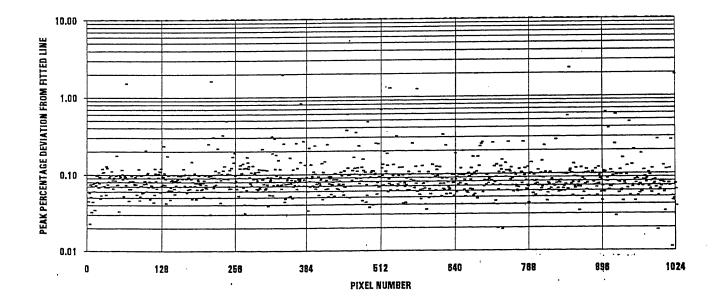

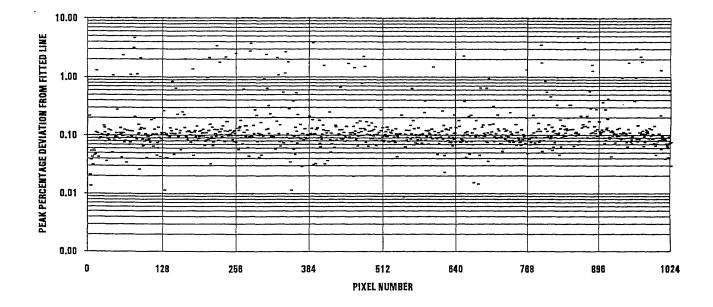

| 7.4   | Measured linearity results of 1.7 um InGaAs focal plane array                                                              | 112  |

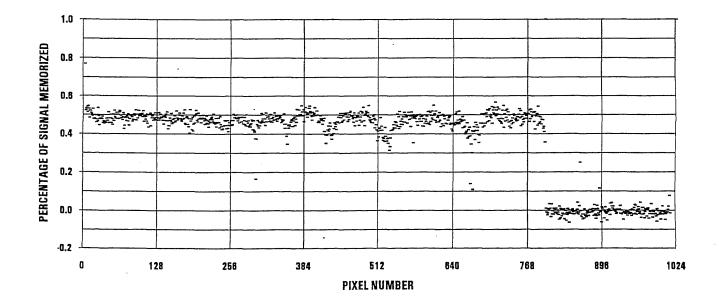

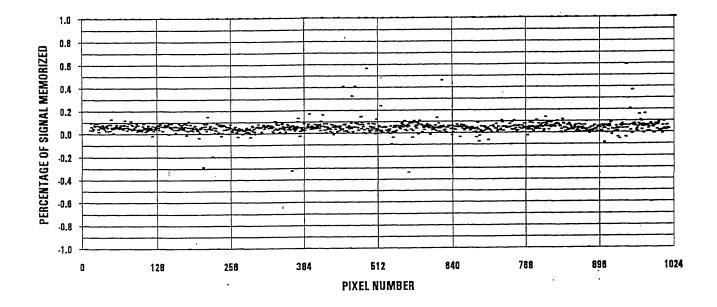

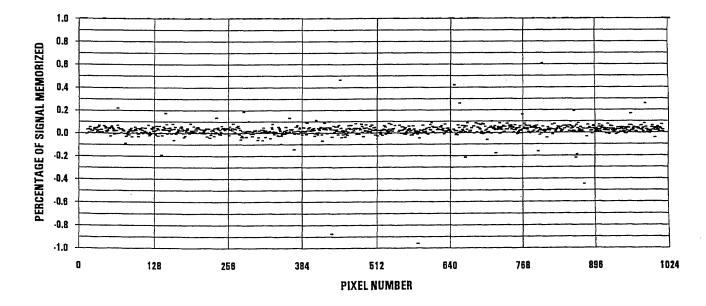

| 7.5   | Measured memory effect results of 1.7 um InGaAs focal plane array                                                          | 112  |

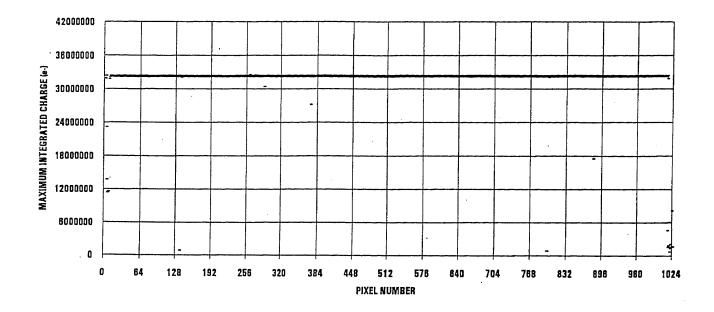

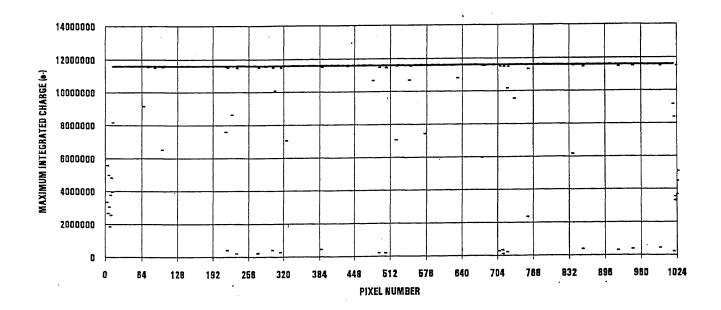

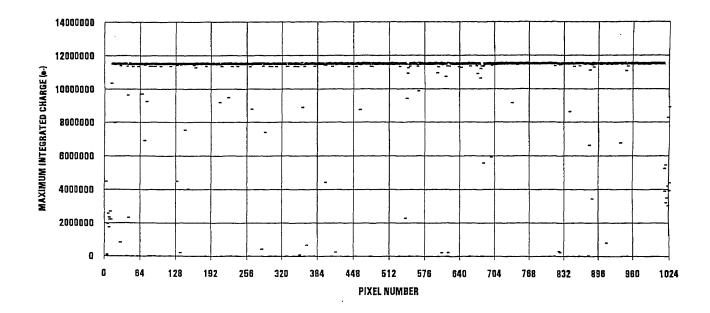

| 7.6   | Measured maximum charge results of 1.7 um InGaAs focal plane array                                                         | 113  |

| 7.7   | Dark current vs. pixel number of 2.2 um InGaAs focal plane array                                                           | 117  |

| 7.8   | Flat-field optical response of 2.2 um InGaAs focal plane array                                                             | 117  |

| 7.9   | Measured noise results of 2.2 um InGaAs focal plane array                                                                  | 118  |

| 7.10  | Measured linearity results of 2.2 um InGaAs focal plane array                                                              | 118  |

| 7.11  | Measured memory effect results of 2.2 um InGaAs focal plane array                                                          | 119  |

| 7.12  | Measured maximum charge results of 2.2 um InGaAs focal plane array                                                         | 119  |

| Figure |                                                                                                  | Page |

|--------|--------------------------------------------------------------------------------------------------|------|

| 7.13   | Dark current vs. pixel number of 2.6 um InGaAs focal plane array                                 | 123  |

| 7.14   | Flat-field optical response of 2.6 um InGaAs focal plane array                                   | 124  |

| 7.15   | Measured noise results of 2.6 um InGaAs focal plane array                                        | 124  |

| 7.16   | Measured linearity results of 2.6 um InGaAs focal plane array                                    | 125  |

| 7.17   | Measured memory effect results of 2.6 um InGaAs focal plane array                                | 125  |

| 7.18   | Measured maximum charge results of 2.6 um InGaAs focal plane array                               | 126  |

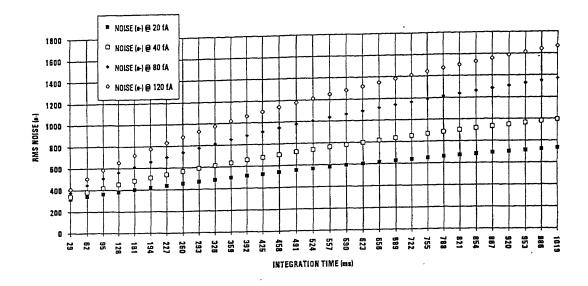

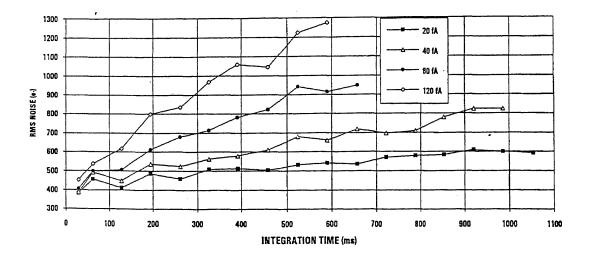

| 7.19   | Simulated rms. noise electrons as a function of integration time                                 | 130  |

| 7.20   | Measured rms. noise electrons as a function of integration time                                  | 130  |

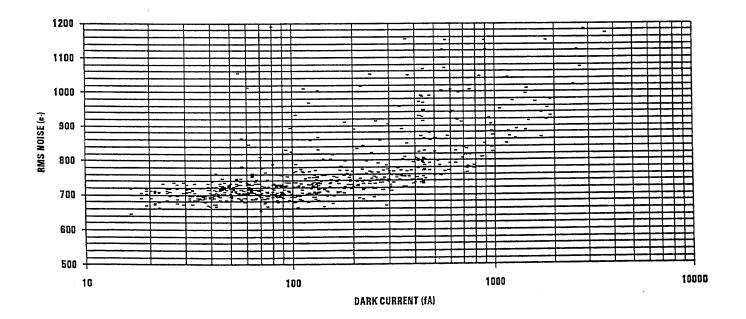

| 7.21   | Measured rms. noise electrons as a function of dark current                                      | 131  |

| 7.22   | Comparison of InGaAs and HgCdTe detector performance as a function of wavelength and temperature | 133  |

#### CHAPTER 1

#### INTRODUCTION

Indium gallium arsenide is finding an important role in the 1-2.6  $\mu$ m spectrum because of its unsurpassed performance and high reliability. Environmental remote sensing missions such as SCIAMACHY designed to measure the atmospheric trace gas abundance's on a global scale in the stratosphere as well as in the troposphere will require a high signal to noise ratio in the near infra-red channel focal plane arrays because of very low photon signal (< 2.2X10<sup>10</sup> Photons/(cm<sup>2</sup>-nm-s)<sup>1/2</sup>. In InGaAs detectors, the major noise contribution is from the shot noise due to leakage current. Therefore, especially low leakage current InGaAs photodiodes is highly desirable in order to detect the atmospheric constituents in the 1-2.6  $\mu$ m spectral region. To realize such challenging technological applications, a detector array of several thousand pixels having an average leakage currents as low as 10 fA is required for the spectral region 2.265 - 2.385  $\mu$ m.

This research investigates the possibility of achieving leakage currents of less than 50 fA using InGaAs/InP technology by designing a novel and unique InGaAs/InAsP/InP p-i-n detector structure, growth of uniform InGaAs/InAsP layers with abrupt interfaces using Hydride Vapor Phase Epitaxy (HVPE), Chloride Vapor Phase Epitaxy (CVPE) and Metal Organic Chemical Vapor Deposition (MOCVD) techniques. To achieve these objectives, comparison and analysis of the detector results from the three wafer growth methods mentioned above will be presented. Also described are the post wafer growth fabrication techniques to reduce number of defects, design and fabrication of 1024 element detector arrays and design and development of a capacitive transimpedance amplifier (CTIA) multiplexer for the readout of InGaAs detector arrays to operate at near zero-bias voltage. Testing, measurement and analysis of the 1024 element focal plane array results will be described in detail.

Chapter 2 describes the previous research work done on the development of InGaAs/InP detectors and detector arrays in the 1 to 2.6  $\mu$ m wavelength region, the research objectives of this thesis describing the major problems that had to be addressed in order to achieve leakage currents of < 50 fA for the InGaAs/InP p-i-n detectors and detector arrays in the wavelength spectrum of 1 to 2.6  $\mu$ m. Also described in this chapter are the general requirements or specifications of InGaAs/InP focal plane arrays for environmental sensing applications.

Chapter 3 describes the technology overview used to fabricate InP, InGaAs and InAsP materials for the wavelength of operation, device design and architecture of p-i-n detector using InP/InGaAs/InAsP material system and the growth of InAsP/InGaAs/InAsP/InP layers using the three most advanced material growth techniques, the Hydride Vapor Phase Epitaxy (HVPE), Chloride Vapor Phase Epitaxy (CVPE) and Metal Organic Chemical Vapor Deposition (MOCVD). The device fabrication and device electro-optical results are described. Also described in this chapter are the radiation hardness testing and results of proton, gamma and electron radiation on InGaAs detectors.

Dark current which is the important parameter in the operation of a Focal Plane Array for high signal to noise requirements or to integrate low optical signals is analyzed in Chapter 4. The mechanisms and origin of dark current in InGaAs/InP p-i-n photodetectors is explained in this chapter. The dark current model used to simulate the dark current behavior was developed and described in this chapter. The measured device dark current results are compared with the the simulated values.

Chapter 5 describes the 1024 element InGaAs Focal Plane Array architecture using the Si read out multiplexer and InP/InGaAs detector arrays. This chapter also describes the pixel layout and hybridization of detector arrays and Si readout multiplexer using wire bonding and advanced mounting techniques that were used. Testing and test setup development for the electro-optical characterization of Si read-out multiplexer and InGaAs Focal Plane Arrays are also described in this chapter.

Chapter 6 describes the readout electronics developed for the read-out of InGaAs detector arrays. The design of read-out electronics consists of 512 element Capacitive Transimpedance Amplifier (CTIA) multiplexer for the readout of 1024 element InGaAs detector arrays. The fabrication method and testing results of the multiplexer are also described in this chapter.

Chapter 7 describes the 1024 element InP/InGaAs/InAsP Focal Plane Array test results and analysis of the test results. This chapter includes the detailed analysis of the electro-optical test results of InP/InGaAs/InAsP Focal Plane Arrays with cut-off wavelengths of 1.7, 1.9, 2.2 and 2.6  $\mu$ m. Noise and quantum efficiency, the two important parameters for the signal to noise ratio requirements are analyzed, simulated and compared the simulated and measured results with great detail in this chapter. The radiation hardness testing and test results of gamma radiation on InGaAs Focal Plane Arrays with a cut-off wavelength of 2.6  $\mu$ m is described in this chapter.

Chapter 8 describes the conclusions of this research thesis and future directions for the InGaAs Focal Plane Arrays development. Major conclusions achieved in this thesis are the long wavelength Focal Plane Arrays with a detector noise < 400 rms e<sup>-</sup> can be achieved with InGaAs/InP technology. Also described in this chapter are the proposed ideas to further overcome the difficulties of dark current generation in the lattice mismatched devices.

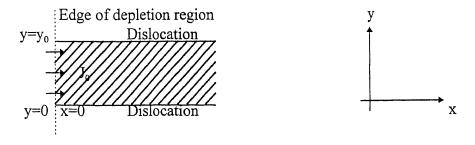

In Appendix A, theoretical equation was derived for the dislocation density using two dimensional Poisson's equation based on the diffusion approximation. This equation was used to estimate the defect density in the 1.7, 2.2 and 2.6  $\mu$ m cut-off InGaAs photodetectors.

The research reported in this thesis was done as part of a joint research of the New Jersey Institute of Technology and Epitaxx, Inc., in support of a contract from Dornier, GmbH and Fokker Space & Systems, Holland. All of the wafers, devices, fabrication and the experimental facilities for this work were provided by Epitaxx, Inc., West Trenton, NJ.

#### CHAPTER 2

#### BACKGROUND

Optical communication is expected to play an important role in the upcoming information technology. The requirement for infrared detectors for low-loss, low dispersion silica fibers in the 1.0 - 1.6  $\mu$ m wavelength range has been readily satisfied by the PIN photo diodes fabricated from Ga<sub>0.47</sub>In<sub>0.53</sub>As, which can be grown lattice matched to InP substrates. For future communication systems based on novel fluoride fibers, for which losses of <= 0.01 dB/km have been predicted[1], detectors operating at longer wavelengths will be required.

Indium gallium arsenide is finding an important role in the 1-2.6  $\mu$ m spectrum because of its unsurpassed performance and high reliability[2]. Environmental remote sensing missions such as SCIAMACHY designed to measure the atmospheric trace gas abundance's on a global scale in the stratosphere as well as in the troposphere[3] requires challenging task of high signal to noise ratio in the near infra-red channel focal plane arrays[4]. In InGaAs detectors, the major noise contribution is from the shot noise due to leakage current. Therefore, reduction of leakage current in InGaAs photodiodes is an important task in order to detect the atmospheric constituents in the 1-2.6  $\mu$ m spectral region. Leakage currents as low as 7 fA is required for the spectral region 2.265 - 2.385  $\mu$ m detector array[5].

In order to satisfy the high signal to noise ratio, it is necessary to use low noise, near zero-bias multiplexers[6] and to cool the detector array to lower temperatures. Since a major portion of an instrument's mass and power is consumed by the focal plane cooler, detector technologies that require only modest cooling can contribute significantly to the realization of a miniature infrared instrument[7]. The scientific space programs are in continuing trend towards smaller and more affordable missions. The advantage of an infrared detector that operates at lower temperatures (150 K - 200 K) will reduce the cooling requirement which is a key ingredient in the design and construction of scientific instruments such as SCIAMACHY. The 1024 element focal plane array consists of an InGaAs detector array connected to a CMOS multiplexer using wire bonding.

Potential applications of such a device include NIR spectroscopy, fluorescence, remote sensing, environmental sensing, space and astronomical applications. The InGaAs detector arrays are especially appropriate device since sensitive absorption, luminescence, emission and Raman spectroscopies require focal plane arrays with high quantum efficiency, low dark current and low noise.

Lattice mismatched  $In_xGa_{1-x}As/InAs_yP_{1-y}(x>0.53, y>0)$  hetero-structures are suitable for the fabrication of photodiode arrays with spectral response up to 2.6  $\mu$ m. Most applications require high uniformity of device performance as well as process reproducibility. However, InGaAs hetero-structures are extremely sensitive to defects and non-uniformity's existing in epitaxial growth of layers and those defects introduced in the processing. This thesis describes a novel and unique detector structure, growth of uniform InGaAs/InAsP layers with abrupt interfaces using Hydride Vapor Phase Epitaxy (HVPE), Chloride Vapor Phase Epitaxy (CVPE) and Metal Organic Chemical Vapor Deposition (MOCVD) techniques, post wafer growth fabrication techniques to reduce number of defects, design and development of a capacitive transimpedance amplifier (CTIA) multiplexer for the readout of InGaAs detector arrays to operate at near zero-bias voltage, measurement and analysis of the focal plane array results.

#### 2.1 Research Objective

Several authors have proposed different growth techniques, different detector structures and different fabrication methods aimed at developing the long wavelength indium gallium arsenide photodetectors [8]-[20]. Past work was aimed at achieving the InGaAs detector arrays with cut-off wavelengths of 1.7  $\mu$ m with 256 eleement pixels. The aim of this thesis is to explore the technological limitations of long wavelength (> 1.7  $\mu$ m) InGaAs photodetectors and photodetector arrays and to design, fabricate, test and analyze the results of a proposed novel detector structure aimed at minimizing the dark current due to excessive defect densities because of the lattice mismatch between the epitaxial layers and the substrate. To achieve the objective of low dark current novel material processing techniques are implemented. The results of the proposed device structures demonstrates that InGaAs/InP technology is suitable for the fabrication of 1024 element linear arrays with long cut-off wavelengths.

One of the main draw back of any near-infrared focal plane arrays is the read-out circuit. The read-out circuit has to be designed and developed depending on the requirements to limit the noise contribution and also depends on the signal requirements. To achieve the objective of low noise (400 rms e<sup>-</sup>), it is necessary to design and develop a novel and unique 512 element Si read-out multiplexer for the read out of 1024 element InGaAs detector arrays. This include the design, development, fabrication, testing and

analysis of the results of Capacitive Transimpedance Amplifier (CTIA) multiplexer for the readout of 1024 element linear InGaAs detector arrays to operate at near zero bias.

#### 2.2 Main Problems

#### 2.2.1 Material and Detector Design Problems

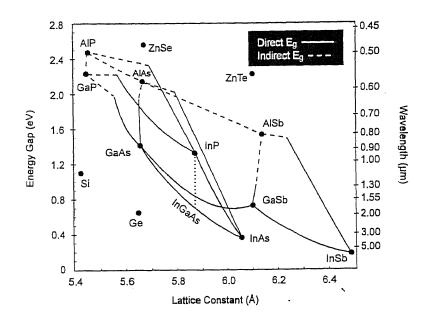

Figure 2.1 shows the bandgap energy, cutoff wavelength and lattice constant (atomic spacing) of different semiconductor elements, compounds and alloys[21]. The dots represent the binary materials (e.g. InP), the lines that connect two dots are ternary materials (e.g. InGaAs) and in between the lines are the quaternary material (e.g. InGaAsP). The binary alloys have fixed lattice parameters and bandgaps, ternary alloys have one degree of freedom and quaternary alloys have two degrees of freedom since a range of lattice parameters is available for each bandgap. Figure 2.1 aids in the selection of detector materials.

As seen from Figure 2.1, the composition of InGaAsP "quaternary" alloys can be adjusted so that their atom spacing is "lattice matched" to that of InP substrates. This enables low stress transitions from the substrate material to the active layers.  $In_{0.53}Ga_{0.47}As$  is the quaternary alloy (albeit without phosphorous) with the smallest bandgap that can still achieve lattice matching with indium phosphide.

Figure 2.1 Energy bandgap, cut-off wavelength and lattice constant for a variety of semiconductor materials.

As shown in Figure 2.1, the cut-off wavelength of InGaAs material can be extended beyond 1.7  $\mu$ m by increasing the composition of InAs content. The In<sub>x</sub>Ga<sub>1-x</sub>As layers with x>0.53, lattice mismatched to InP makes it possible to extend the absorption edge or cut-off to longer wavelengths. This necessitates the use of higher Indium content alloys which are mismatched with respect to the InP substrate with the problems of dislocation induced, junction leakage and low quantum efficiency[13]. By increasing the Indium content of the alloy, the band gap decrease and thus extends the spectral response, since

$$\lambda_{c} = 1.24 / E_{g}$$

$\lambda_{c} = cut off wavelength in \mu m$

where,

$$E_g = bandgap energy in eV.$$

An  $In_{0.82}Ga_{0.18}As$  alloy thus extends the spectral response to 2.6  $\mu m$  since it has a band gap of 0.48 eV at room temperature[22]. Since  $In_xGa_{1-x}As$  with x > 0.53 is not lattice matched to the InP substrate, the graded layer technique is used to accommodate the large mismatch between the InP substrate and the In<sub>x</sub>Ga<sub>1,x</sub>As absorption layer. There exists a critical thickness below which a lattice mismatched layer is elastically deformed and thus biaxially strained [23]. In this case the layer has the same lattice constant as the substrate in the plane parallel to the substrate-layer interface and there are no dislocations. When the layer thickness is above the critical thickness, the (biaxial) strain becomes too high and the layer will relax. The layer will take his own lattice constant which is different from that of the substrate. In a relaxed lattice mismatched layer, many dislocations are introduced and the layer will exhibit poor electrical and optical performances. The critical thickness as a function of strain was reported in [24][25]. Because of the lattice mismatch between the layers, the misfit dislocations are generated [26] [27]. These misfit dislocations are electrically active as generation and recombination centers[15]. The main effects of misfit dislocations in photodiodes are to generate excess dark current and to reduce minority carrier life time[28].

This thesis describes the design and development of  $In_{0.53}Ga_{0.47}As$ ,  $In_{0.72}Ga_{0.28}As$ and  $In_{0.82}Ga_{0.18}As$  detector arrays using the ternary compound material grown by Hydride Vapor Phase Epitaxy (HVPE), Chloride Vapor Phase Epitaxy(CVPE) and Metal Organic Chemical Vapor Deposition (MOCVD) methods. Methods of reducing the dislocation density during the epitaxial layer growth and during the fabrication of photodetectors and detector arrays are introduced. Comparison of the results of the three growth methods and performance of the long wavelength detectors and detector arrays are presented. In addition, a new detector design with improved performance of low dark current is presented. Detailed analysis of the dark current, origin of the dark current and the methods of reducing the dark current are also presented.

#### 2.2.2 Read-out Electronics

In InGaAs detector arrays, the main source of the noise is from the shot noise due to the dark current. In order to improve the signal to noise ratio, the dark current should be improved. At low bias voltages (< 100 mV) the dark current is approximately proportional to the detector reverse bias voltage. To reduce the dark current and hence the noise from the focal plane array, the detector must be operated either at zero bias voltage (photo-voltaic) or at near zero bias voltage. To operate the detector array at near zero-bias voltage, a Si read-out circuit (multiplexer) has been designed and fabricated using a Capacitive Transimpedance Amplifier (CTIA), Correlated Double Sampling (CDS) at each pixel. The multiplexer fabrication and the test results will be described and analyzed. The focal plane architecture for 1024 element linear InGaAs arrays with cut-off wavelengths of  $1.7 \mu m$ ,  $2.2 \mu m$  and  $2.6 \mu m$  will be presented.

#### 2.3 Performance Requirements

The Focal Plane Array consisting of InGaAs detector array and Si readout multiplexer was designed and developed to meet the following requirements.

| Number of pixels                | :  | 1024                                      |

|---------------------------------|----|-------------------------------------------|

| cut-off wavelength              | :  | 1.7 μm                                    |

|                                 |    | 2.2 μm                                    |

|                                 |    | 2.6 μm                                    |

| Operating temperature           | :  | 200 K for 1.7 $\mu$ m cut-off FPA         |

|                                 |    | 150 K for 2.2 & 2.6 $\mu m$ cut-off FPA   |

| Pixel size                      | :  | $500 \times 13 \ \mu m^2$                 |

| Detector pitch                  | :  | 25 μm                                     |

| Internal quantum efficiency     | :  | > 55 %                                    |

| Max. signal level               | :  | > 1E7 e <sup>-</sup>                      |

| Integration time                | :  | > 1 ms (up to several minutes)            |

| Dark current                    | :  | $< 4$ fA for 1.7 $\mu$ m cut-off detector |

|                                 |    | $< 2$ fA for 2.2 $\mu$ m cut-off detector |

|                                 |    | $<$ 7 fA for 2.6 $\mu$ m cut-off detector |

| Noise                           | :  | < 800 rms. e <sup>-</sup>                 |

| Pixel-to pixel signal variation | n: | < 5 % rms.                                |

#### CHAPTER 3

#### **OVERVIEW OF TECHNOLOGY**

In an epitaxial heterostructure, if the lattice constants (spacing between the two neighboring atoms) of the substrate and the epitaxial layer parallel to the interface are not equal, a certain misfit is present. When an epitaxial layer of lattice constant other than that of its substrate is grown, it produces strain ( $\Delta a/a$ ) in the grown layer. It requires less energy for a thin epitaxial layer to strain elastically and adopt the substrate spacing rather than form dislocation[24]. However, this energy increases with thickness and eventually a "critical thickness" is reached where it is energetically more favorable to form a dislocation, rather than remain totally strained. The critical thickness (t<sub>e</sub>) is inversely proportional to the lattice mismatch between the two adjoining epitaxial layers[29].

$$t_c = (\Delta a/a)^{-1}$$

On exceeding the critical thickness, the strain in the mismatched epitaxial layer releases through the formation of misfit dislocations[24][30][31][32]. Usually, the critical thickness is of the order of few nanometers for structures up to 4% mismatch and is mostly exceeded in the hydride vapor phase epitaxy (HVPE), which is characterized by fast epitaxial crystal growth (0.5 to 1 um/min). Thus, the InGaAs/InAsP detector structures grown for this research work exceeded their critical thickness values, thereby generating misfit dislocations.

The mismatch (or misfit) dislocations have detrimental effect on the electrical and optical characteristics of many devices like lasers, photodetectors and transmission photo cathodes[33]. The reduction of dislocation density is a key to improve the device

performance. G.H. Olsen et. al [30] and J. W. Matthews et. al [16][34] has studied the lattice mismatched layers extensively and grown heteroepitaxial lattice mismatched semiconductors with dislocation densities as low as 10<sup>5</sup>/cm<sup>2</sup>. They concluded that an abrupt interface between the mismatched layers bends most of the dislocations into the plane of the growth and prevents them from propagating into the active layer. Therefore, for the reduction of dark current in the lattice mismatched InGaAs detectors, growth of epitaxial layers with compositionally sharp and abrupt interfaces is very important.

The dislocation density in a lattice mismatched crystal is dependent on the lattice mismatch between the two adjoining epitaxial layers. In InAsP layers, the lattice mismatch between the two neighboring layers can be reduced by reducing and accurately controlling the arsenic concentration. During this research work, as many as 18 InAs<sub>y</sub>P<sub>1-y</sub> buffer layers were grown on top of InP substrate to reduce the lattice mismatch between the two layers to < 0.1%.

## 3.1 Crystal Growth Techniques

An  $In_{0.82}Ga_{0.18}As$  alloy has a band gap of 0.48 eV at 300K and thus extends the absorption of photons up to 2.6 um wavelength at room temperature. A graded layer technique is used to accommodate the large lattice mismatch between the InP substrate( $a_0 = 5.8694$ ) and the  $In_{0.82}Ga_{0.18}As$  absorption layer( $a_0 = 5.990$ ) which is about 2%. To reduce the defect density, the mismatch is accommodated by growing several  $InAs_yP_{1.y}$  layers, where the composition of As is increased from layer to layer. Step grading is very effective in decreasing dislocation density than continuous grading because most dislocations bend at the step interface and do not propagate along the growth direction[34][35]. Misfit dislocations can be electrically active as generation-recombination centers, generate excess dark current and reduce minority carrier life time. InAsP was chosen over InGaAs as the material to grade because in the hydride VPE process it is easier to adjust AsH<sub>3</sub>/PH<sub>3</sub> ratios than InCl/GaCl ratios. InAs<sub>y</sub>P<sub>1-y</sub> was also used as the "cap" layer to terminate the p-n junction because of it's high band gap which helps in reducing the dark current. About 15 layers of InAs<sub>y</sub>P<sub>1-y</sub> with y increasing from 0.0 to 0.68, each layer about 0.8 um are grown on InP substrate. This results in lattice constant change from 5.8694 to 5.9926 A° and the band gap energy change from 1.35 to 0.65 eV. The final graded layer of InAs<sub>0.68</sub>P<sub>0.32</sub> was about 1.0 um thickness to provide a good quality sub-layer for the growth of the absorption layer. The cap or window layer is InAs<sub>0.68</sub>P<sub>0.32</sub> and is about 1.5 um. The p-n junction is formed by zinc diffusion through the window layer. The 3.7 um thick absorption layer assures strong absorption of the transmitted radiation with energy slightly greater than the bandgap energy of the absorption layer.

#### 3.1.1 Hydride Vapor Phase Epitaxy (HVPE)

The group V element is introduced as a hydride (e.g.  $PH_3$ ) and HCl is passed over the group III metal to form the group III chloride[36]. The group III and group V composition can be accurately controlled[37][38]. The As and P controllability is much simpler in hydride VPE than that in other growth methods, such as MOVPE and MBE[12]. Therefore, hydride VPE is an effective method by which accurate control of the InAs<sub>y</sub>P<sub>1-y</sub> graded buffer layer is possible[39]. By controlling the AsH<sub>3</sub> with a faster

response time and smaller flow range controller helps to obtain abrupt interfaces between the graded layers. A drawback of HVPE is the need for hydrides, which are extremely toxic.

#### 3.1.2 Chloride Vapor Phase Epitaxy (CVPE)

Chloride Vapor Phase Epitaxy is one of the earliest vapor growth techniques. The group V chloride (e.g. AsCl<sub>3</sub>) passes over the group III metal, which is heated in the hottest zone of the reactor, to form a group III chlorides (e.g. GaCl). This group III chloride diffuses to a cold zone, which contains the substrate and react with a group V species to form a III-V compound. Multilayer structures are achieved by shuttling back and forth between the chambers. The disadvantage of this growth technique is that the group V chlorides are introduced by heating a liquid which means that the concentration varies exponentially with temperature and is thus difficult to control.

## 3.1.3 Metal Organic Vapor Phase Epitaxy (MOVPE)

Metal-Organic Vapor Phase Epitaxy uses a group V hydrides and group III metalorganics (e.g. TriMethylIndium or TMI or  $(CH_3)_3$ In) which are introduced in the reactor by means of a carrier gas. The source metalorganics are kept in temperature controlled bubblers in order to stabilize the vapor pressure. Carrier gas flows through the bubbler and is saturated by the vapor pressure in the bubbler. The reactants are cracked above the hot wafer surface and combine on the wafer. MOVPE growth can be performed at atmospheric pressure but also at reduced pressures (20 - 200 mbar), enabling more abrupt

interfaces. MOVPE was the first technique that was able to grow high purity layers with monolayer abruptness. The past 10 years the reactor designs have much improved resulting in uniform growth over large areas. Because of this flexibility and rather simple reactor, MOVPE is at this moment the moist widely used growth technique for basic research as wells as for large scale production. The main disadvantage of MOVPE is the high consumption of expensive and hazardous sources, which requires high investments for source materials and safety equipment. However, the past ten years a strong effort has been put in the development of alternative and less hazardous source materials.

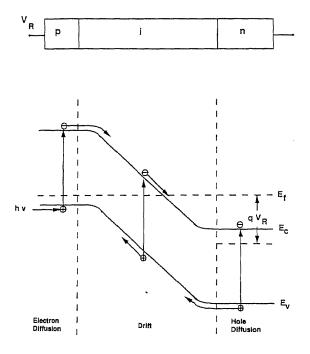

Figure 3.1 Cross-section and energy band diagram of a p-i-n diode.

#### 3.2 Device Design and Cross-section

The p-i-n photodiode is one of the most common photodetectors and is usually reverse biased, since light absorbs in the intrinsic layer, the intrinsic layer can be adjusted to optimize the quantum efficiency and frequency response. The basic schematic representation of a p-i-n diode and an energy band diagram is shown in Fig. 3.1. Light absorption in the semiconductor produces electron-hole pairs. Electron-hole pairs produced in the depletion region or within a diffusion length will eventually be separated by the electric field and hence the carriers drift across the depletion layer. The material requirement for p-i-n photodiodes with good device performance are lattice matched, dislocation free epitaxial layers with controlled doping and thickness.

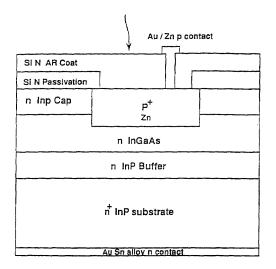

#### 3.2.1 Lattice Matched In<sub>0.53</sub>Ga<sub>0.47</sub>As/InP Device Structure and Fabrication

Figure 3.2 is a schematic cross section of standard planar  $In_{0.53}Ga_{0.47}As$  p-i-n photodiode which is lattice-matched to InP substrate[40][41]. Figure 3.3 shows it's band diagram. This device operates in the wavelength region 0.8 - 1.7 µm. As shown in figure 3.2, the device consists of several epitaxial layers on InP substrate. The substrate is sulfur (n+) doped InP. The first layer on top of the InP substrate is about 1 µm thick InP buffer layer. This layer reduces the defect migration from the InP substrate to the  $In_{0.53}Ga_{0.47}As$ absorption layer, which is the second layer. The  $In_{0.53}Ga_{0.47}As$  absorption layer is about 3.5 um thick and assures complete absorption of the incoming photons. The third layer is a 1 um thick InP cap layer. Although  $In_{0.53}Ga_{0.47}As$  has high internal absorption for photons, photo generated electrons and holes can often recombine at the top surface

thereby reducing over all quantum efficiency. Deposition of the high bandgap InP on this surface eliminates the dangling bonds at this free surface, allows free transmission of light and tends to repel carriers from the interface so they don't recombine. This large bandgap(1.34 eV) layer also acts as a cap region to passivate the small band gap(0.75 eV) InGaAs, avoiding surface leakage current of the diode. Therefore, the top cap layer reduces the surface leakage currents, and the surface recombination of photo generated carriers. This enhances the noise performance also. The doping of the three layers were optimized to reduce the dark current. The very top layer is a plasma deposited  $Si_3N_4$ dielectric coating, which provides passivation and assures the reliability of the device. This  $Si_3N_4$  also serves as an antireflection coating to enhance the responsivity of the detector. The p-n junction was formed by Zn diffusion through the opening in the  $Si_3N_4$ passivation layer. Each detector element consists of 13 um X 500 um<sup>2</sup> Zn diffusion area with a pitch of 25 um between the neighboring two pixels. The 'p' contact was made using alloyed AuZn contact. The contact was extended using the electron-beam deposited TiPtAu to reduce the diffusion area and effective dark current. The final step is the thermally evaporated AuSn 'n' contact to provide low resistance ohmic contacts. The planar structure shown in Fig. 3.2 is expected to show advantages in durability and reliability[40]41] [42].

Figure 3.2 Schematic cross-section of 1.7 um cut-off InGaAs detector.

Figure 3.3 Band diagram of the planar lattice matched  $In_{0.53}Ga_{0.47}As$  photodiode.

## 3.2.2 Lattice mis-matched In<sub>x</sub>Ga<sub>1-x</sub>As/InP Device Structure and Fabrication

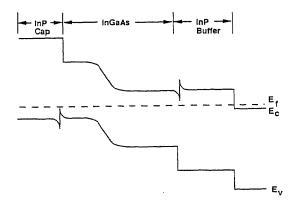

The detector cross-section for the wavelength range 1000 - 2200 nm and 1000 - 2600 nm is shown in Figure 3.4[43]. The detector structure consists of InP substrate and InAs<sub>y</sub>P<sub>1-y</sub> graded buffer layers, In<sub>x</sub>Ga<sub>1-x</sub>As absorption layer and InAs<sub>y</sub>P<sub>1-y</sub> cap layer. The composition of In (x) and the composition of As (y) is varied to get the required cut-off wavelength of 2.2 um and 2.6 um and to achieve the perfect lattice match between In<sub>x</sub>Ga<sub>1-x</sub>As and InAs<sub>y</sub>P<sub>1-y</sub> layers.

# Figure 3.4 Schematic cross-section of 2.2 um and 2.6 um cut-off wavelength InGaAs detector.

|                                    | InAs <sub>n 6</sub> P <sub>0.4</sub>     | P+             | n 1-3X10 <sup>16</sup> |

|------------------------------------|------------------------------------------|----------------|------------------------|

|                                    | In <sub>0.82</sub> Ga <sub>0.18</sub> As | n              | 1X10 <sup>17</sup>     |

| y = 0.60                           | InAs <sub>0.6</sub> P <sub>0.4</sub>     | n <sup>+</sup> | 1-2X10 <sup>18</sup>   |

| ,                                  | InAsP                                    | n <sup>+</sup> | 1-2X10 <sup>18</sup>   |

|                                    | InAsP                                    | n <sup>+</sup> | 1-2X1018               |

|                                    | InAsP                                    | n <sup>+</sup> | 1-2X10 <sup>18</sup>   |

|                                    | InAsP                                    | n*             | 1-2X10 <sup>18</sup>   |

|                                    | InAsP                                    | n+             | 1-2X10 <sup>18</sup>   |

| InAs <sub>y</sub> P <sub>1-y</sub> | InAsP                                    | n+             | 1-2X10 <sup>18</sup>   |

| , .,                               | InAsP                                    | n*             | 1-2X10 <sup>18</sup>   |

|                                    | InAsP                                    | n†             | 1-2X10 <sup>18</sup>   |

|                                    | InAsP                                    | n*             | 1-2X10 <sup>18</sup>   |

|                                    | InAsP                                    | <u>n</u> †     | 1-2X10 <sup>18</sup>   |

|                                    | InAsP                                    | n⁺             | 1-2X10 <sup>18</sup>   |

|                                    | InAsP                                    |                | 1-2X10 <sup>18</sup>   |

|                                    | InAsP                                    | n+             | 1-2X1018               |

| y = 0.015                          | InAsP                                    | <u>n+</u>      | 1-2X10 <sup>18</sup>   |

| -                                  | InP                                      | n*             | 1-3X10 <sup>18</sup>   |

Figure 3.5 Schematic cross-section of the 2.6 um photodiode.

Figure 3.5 shows the schematic cross-section of the lattice mismatched  $In_{0.82}Ga_{0.18}As$  p-i-n photodiode. A graded layer technique was used to accommodate the large lattice mismatch between the InP substrate( $a_0=5.86944$ ) and the  $In_{0.82}Ga_{0.18}As$  absorption layer( $a_0=5.990$ ). This lattice mismatch between the neighboring layers introduces the misfit dislocations. Misfit dislocations can be electrically active as generation-recombination centers, generate excess dark current and reduce minority carrier life time. The graded layer technique was used to bend the threading dislocations and reduce the dislocation density. Fifteen layers of graded InAsP layers were grown on

the InP substrate keeping the lattice mismatch between the neighboring layers to as low as 0.13%[44]. Making the lattice mismatch smaller between the neighboring layers reduces the number of misfit dislocations[45]. In addition, the surface morphology of the wafers grown with higher (0.33%) lattice mismatch between the consecutive mismatched layers was very often rough with no distinct cross hatch pattern. This rough surface reduces the number of consecutive good pixels in a long photodetector arrays in addition to increasing the dark current. The surface morphology of wafer grown with a lattice mismatch of 0.33% between the neighboring two InAsP graded layers was shown in Figure 3.6. As seen from Figure 3.6, the surface morphology was rough with no clear pattern. By reducing the flow range of AsH<sub>3</sub> mass flow controller with a faster response time allowed us to grow smaller lattice mismatched InAsP layers with a better accuracy of controlling the mismatch. Additionally, the faster response time helped to obtain the abrupt interfaces between the graded layers. Abrupt interfaces bend dislocations into the plane of growth and thus prevent their propagation into the InGaAs absorption layer[34][46]. Figure 3.7 shows the surface morphology of a wafer grown using small mismatch (<0.13%) between the neighboring InAsP graded layers. As seen from Fig. 3.7, the surface morphology was smooth with clear and distinct cross hatch pattern. The smooth surface also helps in the fabrication of photodetectors during the photolithography and alignment of 'p' metal contact.

Figure 3.6 Optical micrograph showing surface morphology of an In<sub>x</sub>Ga<sub>1-x</sub>As/InAs<sub>y</sub>P<sub>1-y</sub>

2.6 um photodetector structure on a (100)-2° InP substrate with a lattice mismatch of 0.33% between consecutive mismatched InAsP graded layers (100X magnification). The short axis of the photograph is 1.4 mm.

|                                       | and a second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                       | a the second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                       | a the set of the second of the second of the second s |

|                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |