## New Jersey Institute of Technology

## Digital Commons @ NJIT

**Dissertations**

**Electronic Theses and Dissertations**

Fall 1-31-1999

## A novel readout method for focal plane array imaging in the presence of large dark current

Changging Qiu New Jersey Institute of Technology

Follow this and additional works at: https://digitalcommons.njit.edu/dissertations

Part of the Electrical and Electronics Commons

#### **Recommended Citation**

Qiu, Changqing, "A novel readout method for focal plane array imaging in the presence of large dark current" (1999). Dissertations. 968.

https://digitalcommons.njit.edu/dissertations/968

This Dissertation is brought to you for free and open access by the Electronic Theses and Dissertations at Digital Commons @ NJIT. It has been accepted for inclusion in Dissertations by an authorized administrator of Digital Commons @ NJIT. For more information, please contact digitalcommons@njit.edu.

## **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

#### **ABSTRACT**

## A NOVEL READOUT METHOD FOR FOCAL PLANE ARRAY IMAGING IN THE PRESENCE OF LARGE DARK CURRENT

## by Changqing Qiu

This research was an investigation of a novel readout method for focal plane array (FPA) optical imaging, especially for very sensitive detectors with large dark current. The readout method is based on periodically blocking the optical input enabling the removal of the dark current integration from the output. The research demonstrated that it is feasible to modulate the optical input with the designed readout circuit and thus achieve longer signal integration time to enhance the signal-to-noise ratio.

Study of a proposed circuit model showed that in theory the correlated readout method could increase the output voltage swing and reduce the noise level by attenuating low frequency noise, thereby effectively improving the FPA dynamic range. Circuits based on standard CMOS circuitry were designed, simulated by PSpice, fabricated using Orbit 2µm n-well technology, and tested with a PI-4000 system. In the circuit evaluation, the output noise due to the clock switching phenomena, the gate signal feedthrough and the charge relaxation, was considered to be the critical problem. The most promising design for minimizing this problem had a CMOS current steering circuit at the input of a high CMRR operational amplifier. Simulation and test results showed that a modified capacitive transimpedance amplifier (CTIA) could subtract dark current output and reduce the output signal due to any difference between the frequencies of the optical input modulation signal and the switch modulation signal. In conclusion, the correlated readout circuit was shown to be a promising approach for advancing FPA technology.

## A NOVEL READOUT METHOD FOR FOCAL PLANE ARRAY IMAGING IN THE PRESENCE OF LARGE DARK CURRENT

by Changqing Qiu

A Dissertation

Submitted to the Faculty of

New Jersey Institute of Technology

in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

Department of Electrical and Computer Engineering

January 1999

Copyright © 1999 by Changqing Qiu

ALL RIGHTS RESERVED

## APPROVAL PAGE

# A Novel Readout Method for Focal Plane Array Imaging in the Presence of Large Dark Current

## Changqing Qiu

| Dr. Ken K. Chin, Dissertation Adviser<br>Professor of Physics, NJIT                                                          | Date |

|------------------------------------------------------------------------------------------------------------------------------|------|

| Dr. Roy H. Cornely, Dissertation Co-Adviser and Committee Chairman<br>Professor of Electrical and Computer Engineering, NJIT | Date |

| Dr. Kenneth S. Sohn, Committee Member Professor of Electrical and Computer Engineering, NJIT                                 | Date |

| Dr. Yun-Qing Shi, Committee Member Associate Professor of Electrical and Computer Engineering, NJIT                          | Date |

| Dr. Hongya Ge, Committee Member Assistant Professor of Electrical and Computer Engineering, NJIT                             | Date |

| Dr. Guang Yang, Committee Member<br>Senior Member Engineering Staff of Jet Propulsion Laboratory, Pasadena, CA               | Date |

## BIOGRAPHICAL SKETCH

Author: Changqing Qiu

**Degree:** Doctor of Philosophy

Date: January 1999

## **Undergraduate and Graduate Education:**

- Doctor of Philosophy in Electrical Engineering,

New Jersey Institute of Technology, Newark, NJ, 1999

- Master of Science in Applied Physics,

New Jersey Institute of Technology, Newark, NJ, 1993

- Bachelor of Science in Physics

University of Science and Technology of China, Hefei, P.R. China, 1983

Major: Electrical Engineering

### **Presentations and Publications:**

Changqing Qiu, Xinde Wang and Ken K. Chin, "Correlated readout -- a new readout method of focal plane array," *SPIE 3360*, Orlando, Florida, April 1998.

To my parents, my wife and my daughter Shela

#### **ACKNOWLEDGMENT**

I would like to express my sincere gratitude to my advisor, Professor Ken K. Chin, for his guidance, support and encouragement throughout this research. In more ways than one, he has made me realize my fullest potential. I would especially like to thank him for his teaching during my years at NJIT.

Special thanks to Professor Roy H. Cornely, the dissertation co-advisor. This dissertation would not complete without his guidance and help. His wonderful ideas and instructions helped me overcame many obstacles in dissertation organization and writing. Special thanks are also given to Dr. Kenneth Sohn, Dr. Yuen-Qing Shi, Dr. Hongya Ge and Dr. Guang Yan for actively participating in my committee.

I want also to give my gratitude to Dr. Xinde Wang, who was a visiting scholar in III-V device characterization laboratory of physics department when I started this research, for providing me valuable and countless resources, intuition, and instructions throughout this research. This dissertation could not be done without his help, especially in the circuits testing.

Finally, I want to thank all my friends and family members for their love and help throughout my years at NJIT.

## TABLE OF CONTENTS

| Ch | apte | r Pa                                                   | age |

|----|------|--------------------------------------------------------|-----|

| 1  | INT  | RODUCTION                                              | 1   |

| 2  | A R  | EVIEW OF INFRARED READOUT ELECTRONICS                  | 5   |

|    | 2.1  | Introduction                                           | 5   |

|    | 2.2  | Matured Hybrid Readout Circuits                        | 7   |

|    |      | 2.2.1 Self-Integration Readout                         | 7   |

|    |      | 2.2.2 Injection Circuits                               | 9   |

|    |      | 2.2.3 Gate Modulation                                  | 11  |

|    |      | 2.2.4 Capacitive Transimpedance Amplifier              | 12  |

|    | 2.3  | Noise in Hybrid Infrared FPA                           | 14  |

|    |      | 2.3.1 System Characterization                          | 15  |

|    |      | 2.3.2 The Dark Currents Noise                          | 17  |

|    |      | 2.3.3 Readout Noise                                    | 19  |

|    | 2.4  | The Research on Background Subtraction                 | 24  |

|    |      | 2.4.1 A Unique Current Memory Circuit                  | 24  |

|    |      | 2.4.2 Dynamic Current Mirror Buffered Direct Injection | 26  |

|    |      | 2.4.3 Buffered Gate Modulation                         | 28  |

|    | 2.5  | Conclusions                                            | 29  |

| 3  | TH   | E PRINCIPLE OF CORRELATED READOUT                      | 32  |

|    | 3.1  | Correlated Readout Methodology                         | 32  |

|    | 3.2  | Signal Processing by Correlated Readout                | 35  |

# TABLE OF CONTENTS (Continued)

| Ch | apte | r P                                                   | age |

|----|------|-------------------------------------------------------|-----|

|    |      | 3.2.1 Basic Techniques                                | 35  |

|    |      | 3.2.2 The Phase Sensitive Detector                    | 38  |

|    |      | 3.2.3 A Correlated Reset Integrator (CRI)             | 41  |

|    | 3.3  | Correlated Interface Circuits                         | 48  |

|    |      | 3.3.1 Circuits Developed from CTIA                    | 49  |

|    |      | 3.3.2 Circuits Developed from Other Methods           | 52  |

|    | 3.4  | The Applications                                      | 55  |

|    |      | 3.4.1 Passive Imaging                                 | 55  |

|    |      | 3.4.2 Solar Magnetography                             | 57  |

|    |      | 3.4.3 Active Imaging                                  | 60  |

| 4  | CO   | RRELATED READOUT CIRCUIT DESIGN IN STANDARD CMOS      | 62  |

|    | 4.1  | 4.1 CMOS Design Through MOSIS Service                 | 62  |

|    | 4.2  | Switching System Design                               | 66  |

|    |      | 4.2.1 Basic MOS Switch Model                          | 66  |

|    |      | 4.2.2 Charge Injection and Capacitive Feedthrough     | 68  |

|    |      | 4.2.3 SPICE Simulation of the Switching Feedthrough   | 71  |

|    |      | 4.2.4 Methods for Canceling the Switching Feedthrough | 75  |

|    |      | 4.2.5 Noise in the Switches                           | 77  |

|    | 4.3  | The CTIA Design                                       | 80  |

|    |      | 4.3.1 The Transimpedance Amplifier (TIA)              | 80  |

# TABLE OF CONTENTS (Continued)

| Ch | Page Page Page Page Page Page Page Page |                                                 | Page  |

|----|-----------------------------------------|-------------------------------------------------|-------|

|    |                                         | 4.3.2 Important Specifications of a CMOS Op Amp | . 83  |

|    |                                         | 4.3.3 The Design of a Two Stage CMOS Op Amp     | . 85  |

|    | 4.4                                     | A 16×16 Demo Chip Design                        | . 89  |

|    |                                         | 4.4.1 General Description                       | . 89  |

|    |                                         | 4.4.2 PSpice Simulation                         | . 91  |

|    |                                         | 4.4.3 Layout                                    | . 97  |

|    | 4.5                                     | Summary                                         | . 99  |

| 5  | TES                                     | STING OF THE CORRELATED READOUT CIRCUITS        | 101   |

|    | 5.1                                     | The Experiment Methodology                      | . 101 |

|    | 5.2                                     | Measurement System                              | . 104 |

|    | 5.3                                     | Circuit Biases and Timing                       | 108   |

|    | 5.4                                     | The Correlated Readout Circuit Characterization | . 112 |

|    |                                         | 5.4.1 The Correlated Function                   | . 112 |

|    |                                         | 5.4.2 The Frequency Response                    | 116   |

|    |                                         | 5.4.3 The Switching Feedthrough                 | . 121 |

|    | 5.5                                     | Summary                                         | . 123 |

| 6  | SU                                      | MMARY AND CONCLUSIONS                           | . 125 |

|    | 6.1                                     | Summary                                         | . 125 |

|    | 6.2                                     | Conclusions and Suggestions for Future Studies  | . 128 |

| Αŀ | PPEN                                    | NDIX A PSPICE PROGRAM FOR CIRCUITS SIMULATION   | . 131 |

# TABLE OF CONTENTS (Continued)

| Chapter    | F                             | Page |

|------------|-------------------------------|------|

| APPENDIX B | MASK LAYOUT FOR THE DEMO CHIP | 135  |

| APPENDIX C | TESTING DOCUMENTS             | 138  |

| REFERENCES |                               | 142  |

## LIST OF TABLES

| Tabl        | Table F                                                       |     |

|-------------|---------------------------------------------------------------|-----|

| 2.1         | Input-referred circuit noise in major mature readout circuits | 22  |

| 4.1         | Current CMOS process in MOSIS                                 | 62  |

| 4.2         | Major SPICE model parameters                                  | 64  |

| 4.3         | Device sizes                                                  | 91  |

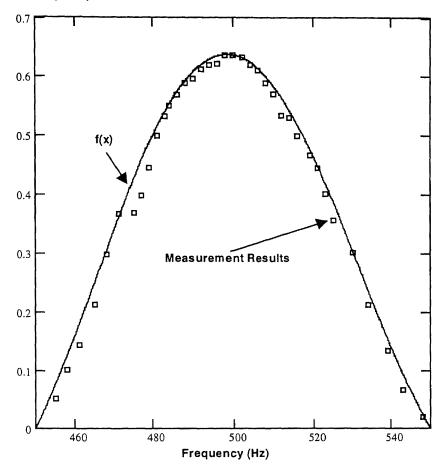

| 5.1         | Instruction program for generating Figure 5.13 for 10 cycles  | 119 |

| 5.2         | Some measurement results for the frequency response           | 119 |

| <b>C</b> .1 | Mnemonic list for the correlated readout demo chip testing    | 138 |

| C.2         | True table of analog selector                                 | 138 |

| C.3         | Pinout description for correlated readout demo chip           | 139 |

| C.4         | Measurement results in frequency response testing             | 141 |

## LIST OF FIGURES

| Figu | Page                                                                                                                                                    |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1  | Direct readout architecture consists of an array of switches and detector Interface circuits.                                                           | 6  |

| 2.2  | Topology of direct detector integration (DDI) and source follower per detector (SFD): (a) simplest circuit schematic, (b) principle of signal detection | 8  |

| 2.3  | Schematic of injection circuits                                                                                                                         | 9  |

| 2.4  | Gate modulation input structure                                                                                                                         | 11 |

| 2.5  | Circuit schematic of CTIA                                                                                                                               | 13 |

| 2.6  | Noise transfer diagram for an imaging system                                                                                                            | 15 |

| 2.7  | Correlated double sampling circuitry: (a) clamping and delay line processor; (b) differential sampling approach                                         | 21 |

| 2.8  | Schematic showing modified CDS readout data construction                                                                                                | 21 |

| 2.9  | Buffered direct injection circuit using chopper stabilization to reduce detector bias offsets and amplifier 1/f noise                                   | 23 |

| 2.10 | (a) Circuit implementation of current mode background subtraction and (b)  Circuit schematic of current memory with feedback suppression                | 25 |

| 2.11 | Detection principle of dynamic current mirror buffered direct injection                                                                                 | 27 |

| 2.12 | Input circuit and chip architecture of buffered gate modulation                                                                                         | 28 |

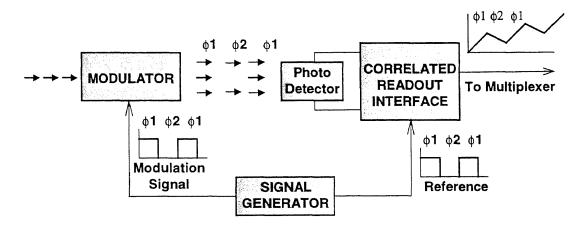

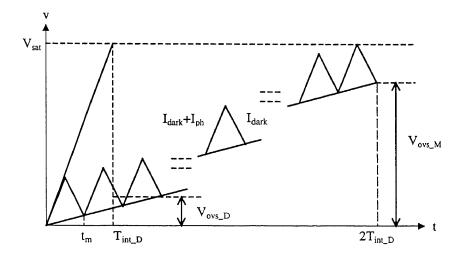

| 3.1  | The principle of correlated readout method                                                                                                              | 33 |

| 3.2  | DC model for the process of correlated interface circuits                                                                                               | 34 |

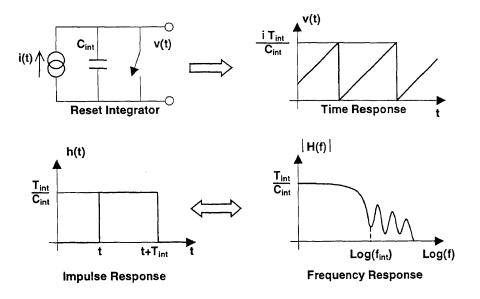

| 3.3  | The reset integrator action can be modeled as a continuous integrator that is sampled and subtracted as discrete time increment.                        | 36 |

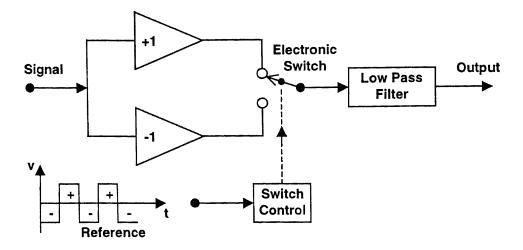

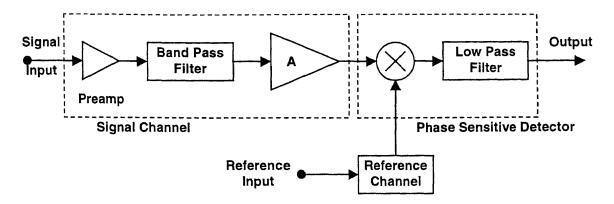

| 3.4  | The principle of phase sensitive detector                                                                                                               | 39 |

| 3.5  | A basic lock-in amplifier                                                                                                                               | 41 |

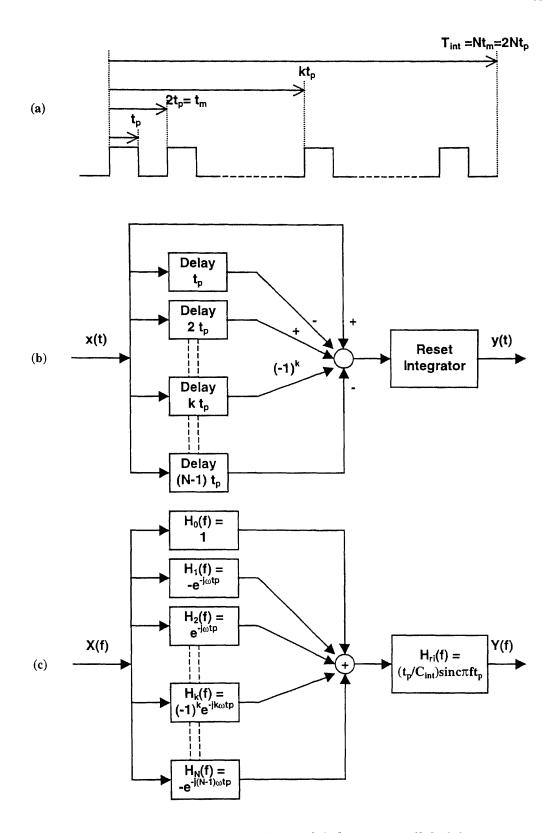

| 3.6  | The correlated reset integrator is modeled as a parallel delay processor                                                                                |    |

# LIST OF FIGURES (Continued)

| Figu | re I                                                                                                                                            | Page       |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|      | followed by a reset integrator with integration time of t: (a) Timing, (b) Simulation diagram, (c) Frequency domain block diagram.              | 43         |

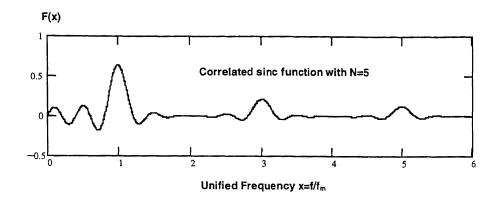

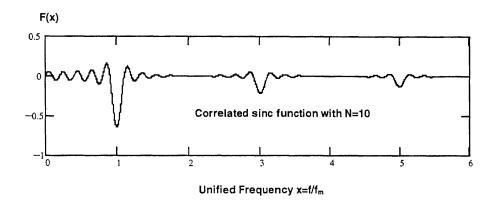

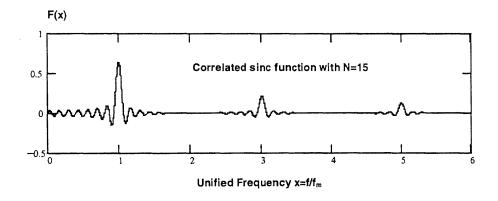

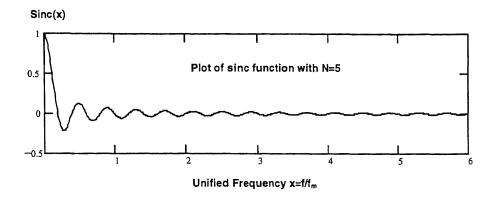

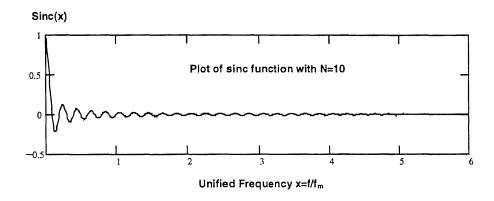

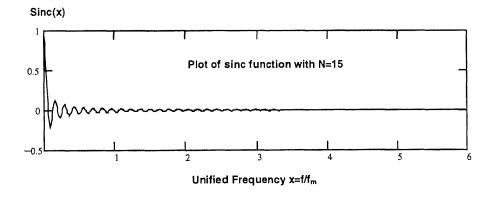

| 3.7  | The reset integrator has the frequency response as a sinc function and the correlated reset integrator has the form of correlated sinc function | 46         |

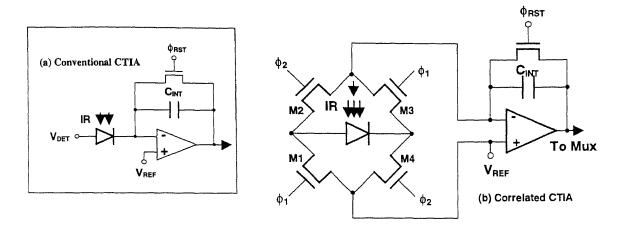

| 3.8  | Circuit schematic of correlated CTIA                                                                                                            | 50         |

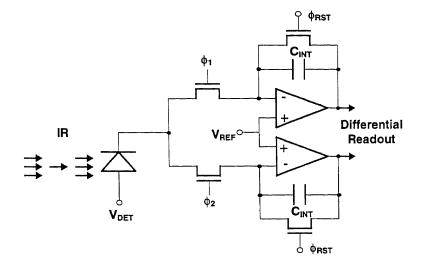

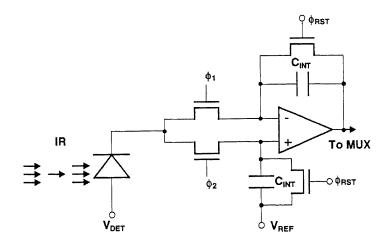

| 3.9  | Circuit schematic of twin CTIA                                                                                                                  | 51         |

| 3.10 | The circuit schematic of differential integrator                                                                                                | 51         |

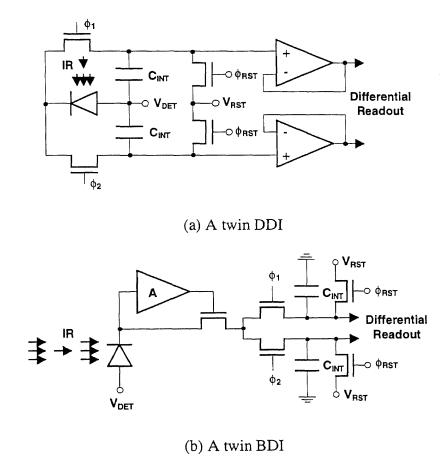

| 3.11 | Correlated readout circuits developed from DDI and BDI                                                                                          | <b>5</b> 3 |

| 3.12 | An ideal circuit for correlated gate modulation                                                                                                 | 54         |

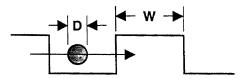

| 3.13 | Basic mechanical chopper configurations                                                                                                         | 56         |

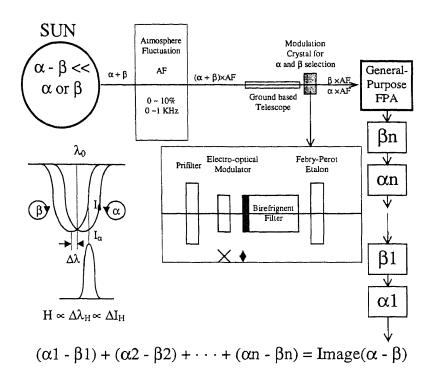

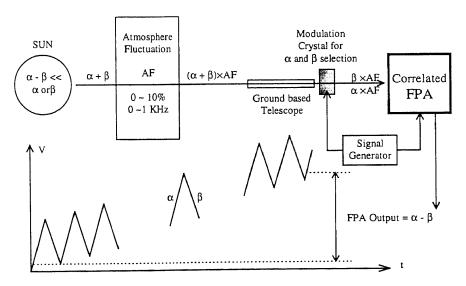

| 3.14 | Scenario of solar magnetography                                                                                                                 | 58         |

| 3.15 | Solar magnetography by correlated readout method                                                                                                | 59         |

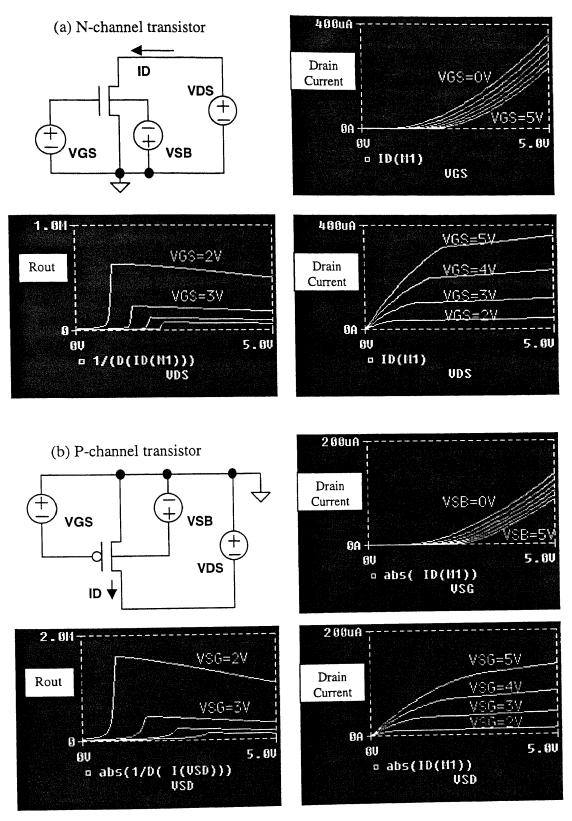

| 4.1  | Characteristic of MOSFET for Orbit 2 $\mu m$ n-well process with L and W = 4 $\mu m$                                                            | 65         |

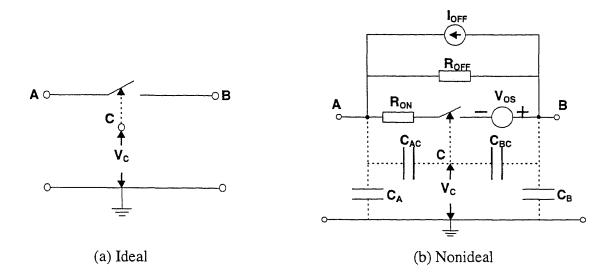

| 4.2  | A model of MOS switch                                                                                                                           | 67         |

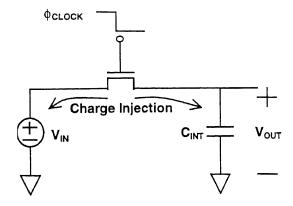

| 4.3  | Simple configuration using an NMOS to show charge injection                                                                                     | 68         |

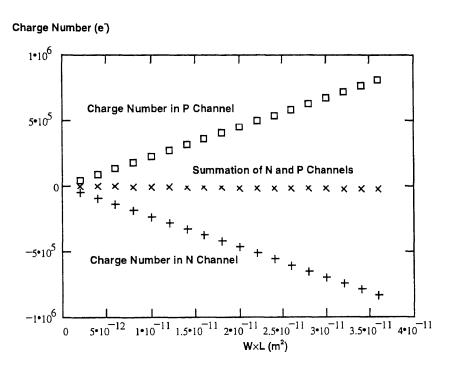

| 4.4  | The channel charge is calculated with the size of WL and converted into number of electrons.                                                    | 69         |

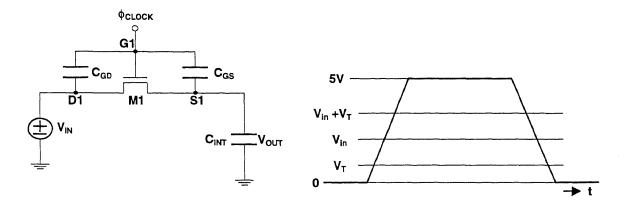

| 4.5  | Illustration of capacitive feedthrough and the clock waveform                                                                                   | 71         |

| 4.6  | Circuit model used to simulate the switching feedthrough on CTIA                                                                                | 72         |

| 4.7  | PSpice simulation to demonstrate the effect of switching feedthrough on CTIA                                                                    | 73         |

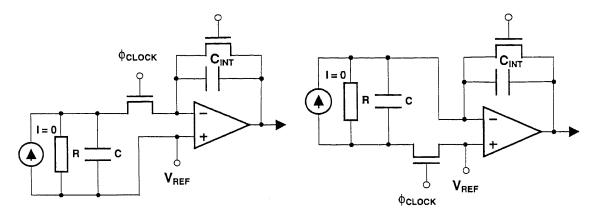

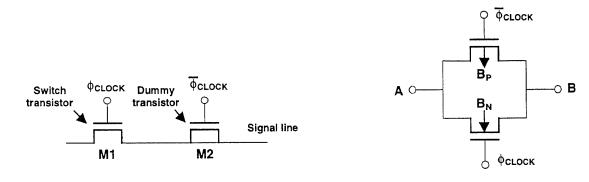

| 4.8  | Classical methods for canceling switching feedthrough                                                                                           | 75         |

| 4.9  | Minimization of switching feedthrough by a fully differential circuit                                                                           | 77         |

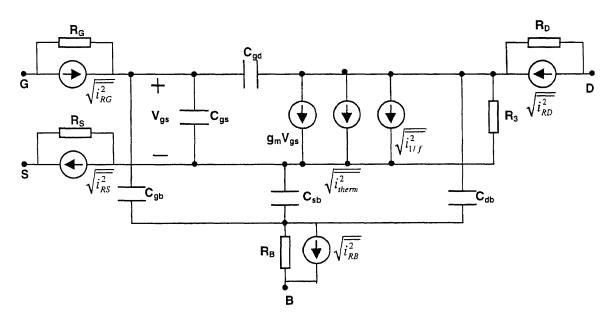

| 4.10 | Noise model for MOSFET                                                                                                                          | 78         |

# LIST OF FIGURES (Continued)

| Figu | re P                                                                                                                                                                                           | age |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

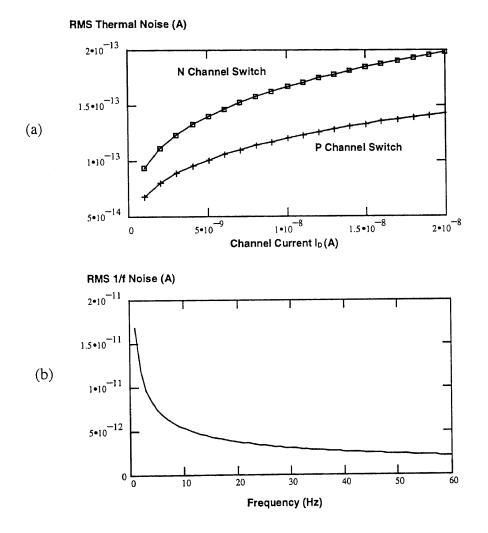

| 4.11 | Calculation of thermal and flick noise generated by switch                                                                                                                                     | 79  |

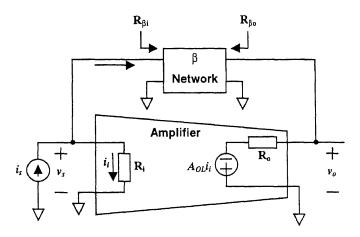

| 4.12 | An ideal transimpedance (shunt-shunt feedback) amplifier                                                                                                                                       | 81  |

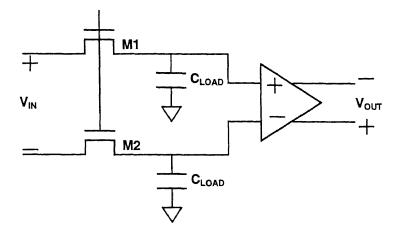

| 4.13 | Resistor transimpedance amplifier (RTIA)                                                                                                                                                       | 82  |

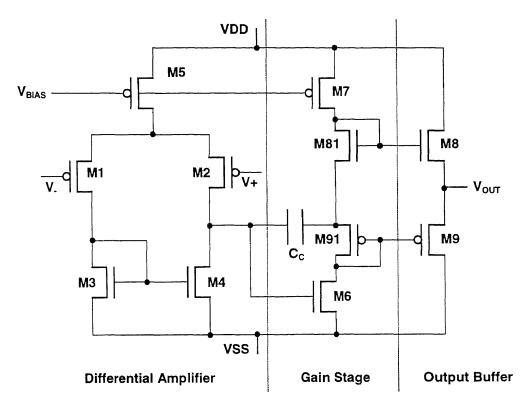

| 4.14 | A basic CMOS operational amplifier for n-well process                                                                                                                                          | 83  |

| 4.15 | Differential amplifier configuration for determining input CMRR                                                                                                                                | 85  |

| 4.16 | A two stage CMOS Op Amp can most be applied to pixel design because of area and circuitry complexity considerations.                                                                           | 86  |

| 4.17 | (a) Small signal model of a two stage Op Amp and (b) simplified model of (a)                                                                                                                   | 87  |

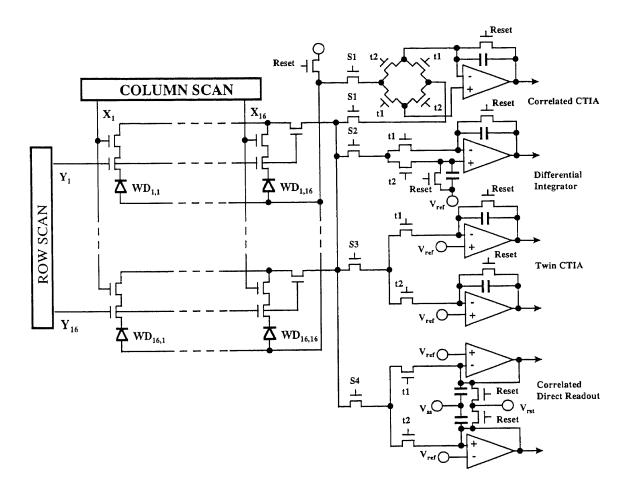

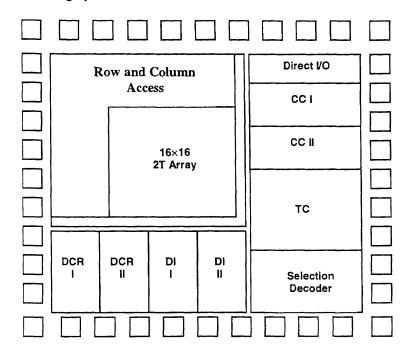

| 4.18 | First correlated readout test chip includes a 16×16 diode array, four kinds of interface circuits, two 4-input decoders for row and column access, and transmission gates as switching system. | 90  |

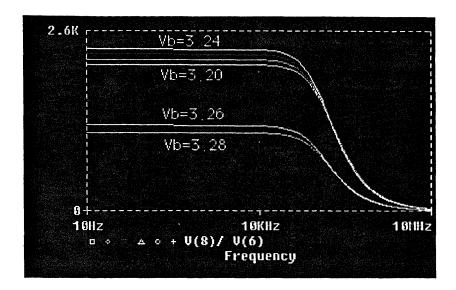

| 4.19 | The demonstration of Op Amp simulation for frequency response with the change of bias voltage. The open-loop gain is 67dB and -3dB frequency is 120KHz.                                        | 92  |

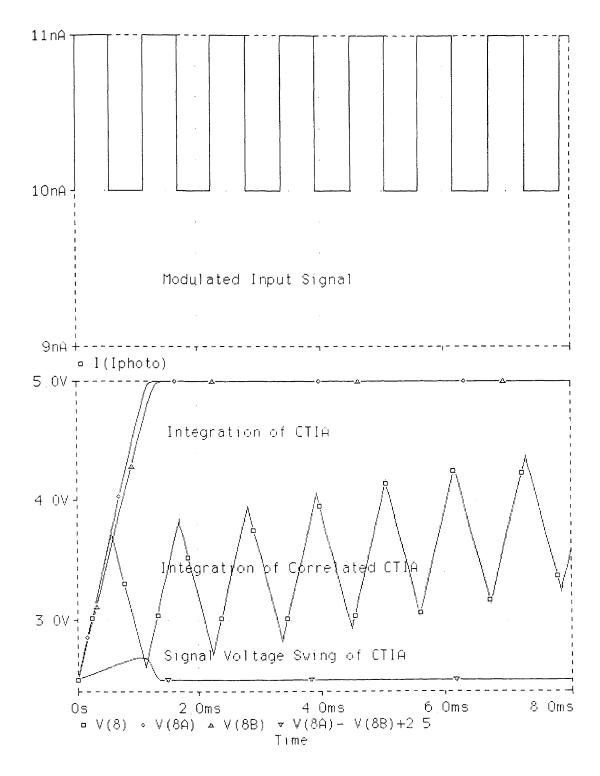

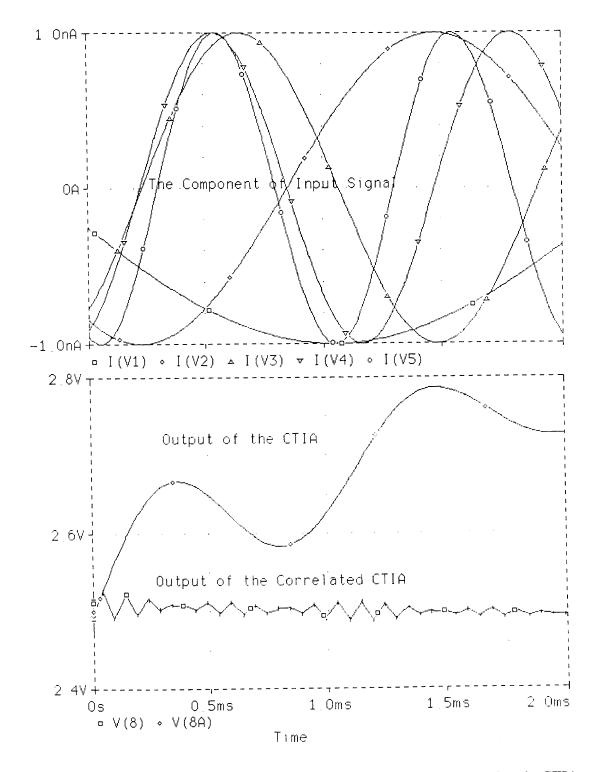

| 4.20 | The simulation of the correlated CTIA for (a) the output voltage swing and (b) The simulation of the correlated CTIA for the noise reduction                                                   | 93  |

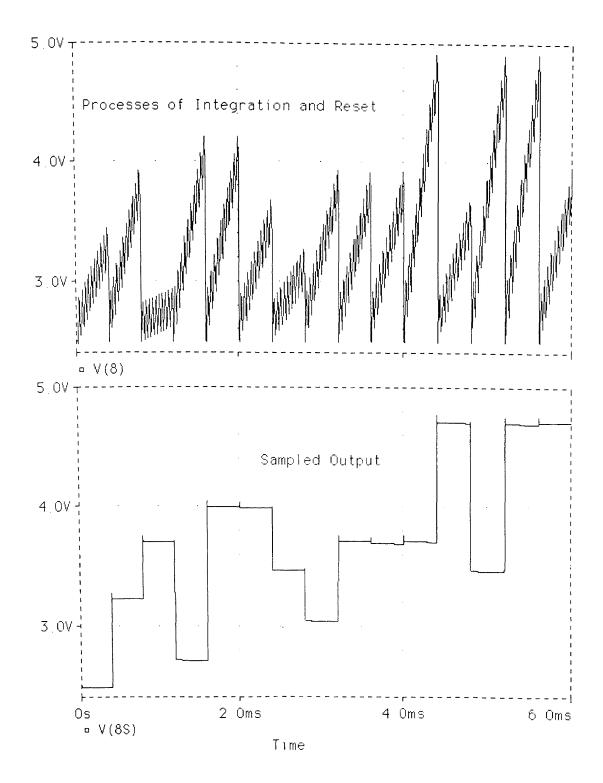

| 4.21 | PSpice simulation for the performance of the first correlated demo chip                                                                                                                        | 96  |

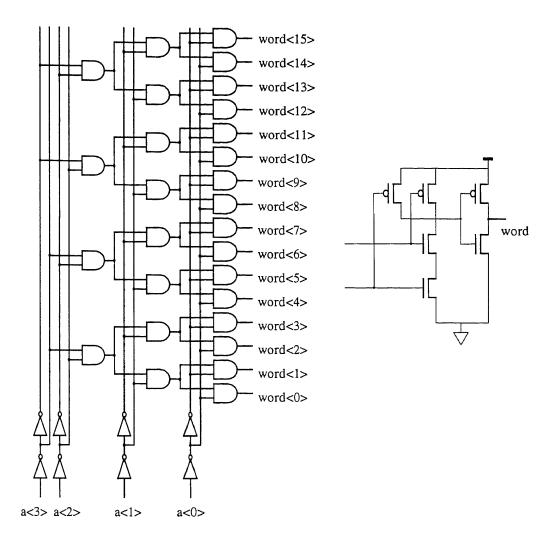

| 4.22 | (a) Circuit diagram of 4-input decoder in gate level and (b) AND gate in the 4-input decoder                                                                                                   | 97  |

| 4.23 | Floor plane of the first correlated readout demo chip                                                                                                                                          | 98  |

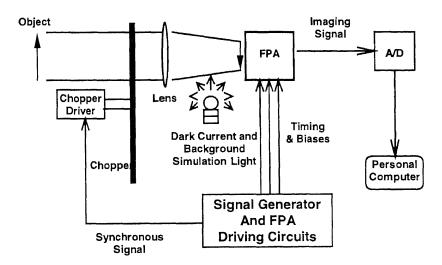

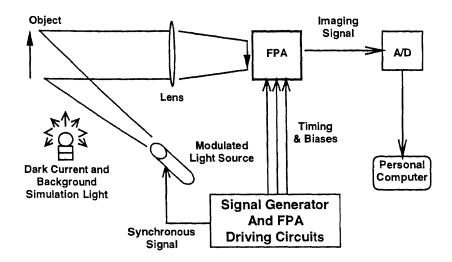

| 5.1  | In passive imaging applications, the modulation signal will control the optical modulator. Such an approach is not suggested in beginning of the research                                      | 102 |

| 5.2  | In active imaging approach, the modulation signal controls a light source instead of controlling the modulator in front of the FPA.                                                            | 103 |

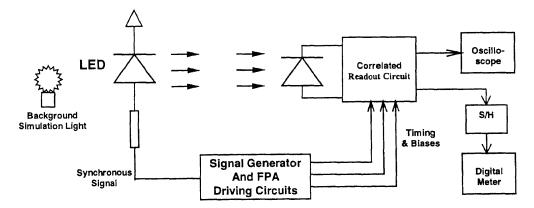

| 5.3  | A direct modulation method using light emitting diode (LED) as the object is used in this research for the correlated readout circuit characterization                                         | 103 |

# LIST OF FIGURES (Continued)

| Figu | re P                                                                                                                                                                                                                | age |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

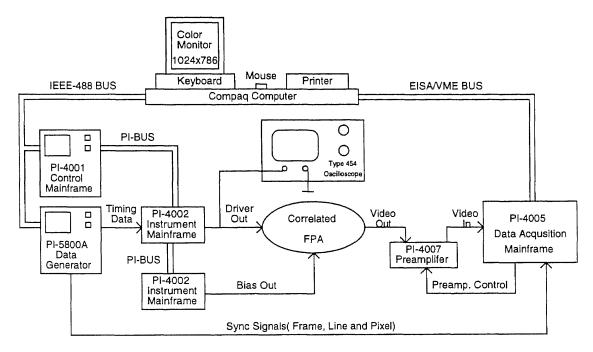

| 5.4  | The measurement system for the correlated readout circuit is based on Pulse Instruments System 4000 Series Automated FPA Test System                                                                                | 105 |

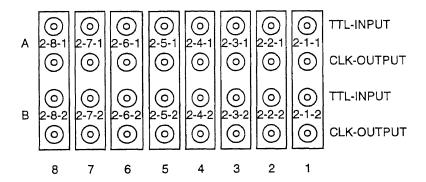

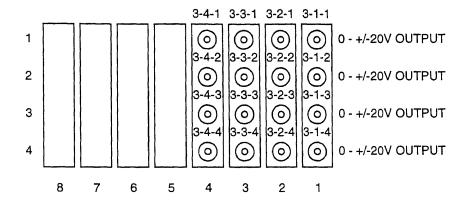

| 5.5  | Output connector of PI-5800A data generator                                                                                                                                                                         | 106 |

| 5.6  | Input/output connectors of 40460 clock driver                                                                                                                                                                       | 106 |

| 5.7  | The output connectors of 40750 bias supply card                                                                                                                                                                     | 107 |

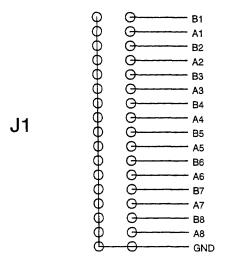

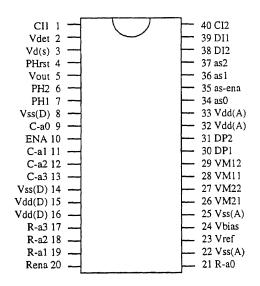

| 5.8  | The pin diagram of the first correlated readout demo chip                                                                                                                                                           | 107 |

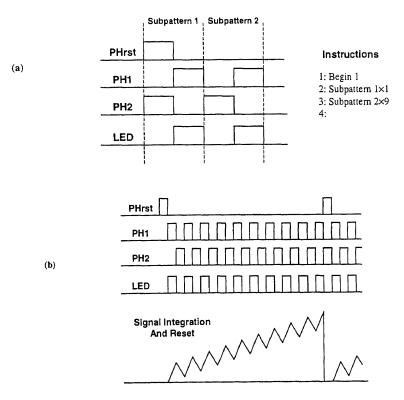

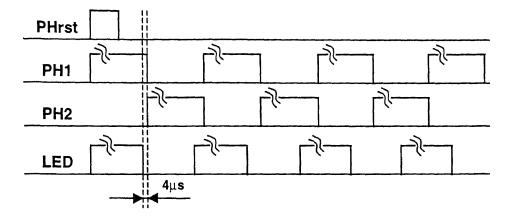

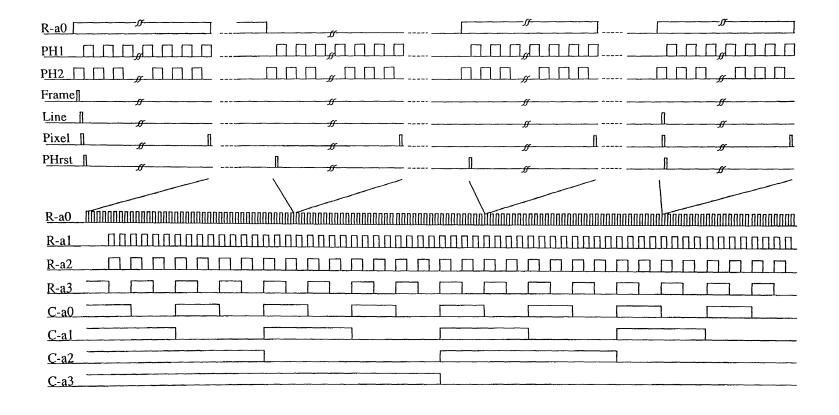

| 5.9  | The simplest subpatterns and instructions program for timing the correlated readout circuit: (a) The subpatterns and the instruction program and (b) The clock output and the expected signal integration and reset | 111 |

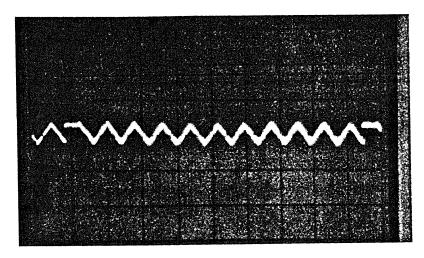

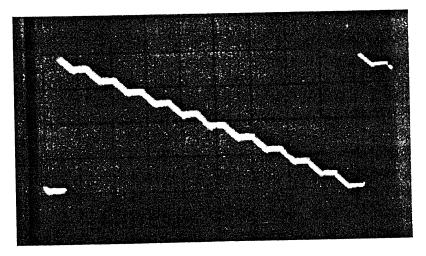

| 5.10 | Photo taken in scope for the correlated function test result                                                                                                                                                        | 113 |

| 5.11 | Photo taken for the output of each twin CTIA                                                                                                                                                                        | 115 |

| 5.12 | Photo taken to shown phase effect of the correlated CTIA                                                                                                                                                            | 117 |

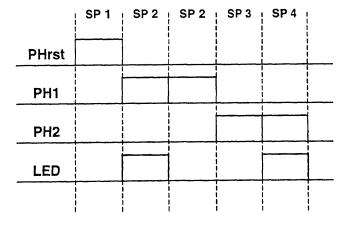

| 5.13 | The clock relationship when the switching signal is 500Hz and the LED Exciting signal is 502Hz. Only first three cycles are shown in the figure                                                                     | 118 |

| 5.14 | Basic subpatterns in Figure 5.13                                                                                                                                                                                    | 118 |

| 5.15 | The plot of frequency response from 450Hz to 550Hz                                                                                                                                                                  | 120 |

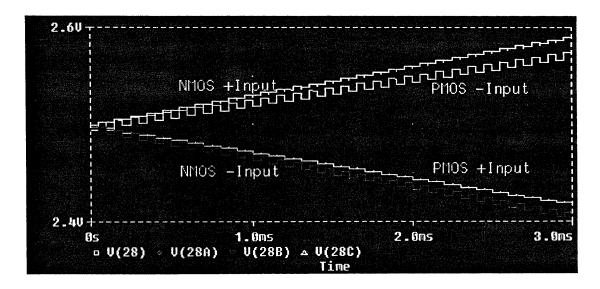

| 5.16 | The output voltages at each twin CTIA due to the switching feedthrough                                                                                                                                              | 122 |

| B.1  | Mask layout for switching system                                                                                                                                                                                    | 135 |

| B.2  | Mask layout for CTIA                                                                                                                                                                                                | 136 |

| B.3  | Mask layout for the first correlated readout demo chip                                                                                                                                                              | 138 |

| C.1  | Timing for demo chip testing                                                                                                                                                                                        | 140 |

#### CHAPTER 1

### INTRODUCTION

Infrared sensors are used to detect, measure and image the thermal radiation emitted by all objects. The possibility of mass fabrication of two-dimensional arrays, based on advances in photolithography, increased the possible application areas and performance of infrared focal plane array (FPA) [1]. Further advances will be accelerated by higher pixel density, the capability to do on-chip processing, improved materials with lower cooling requirements, and higher sensitivity. However, some FPA performance limitations can be traced to the readout electronics rather than the detectors [2], [3].

This research investigated the feasibility of a novel readout concept recently proposed for FPA optical imaging. The method discriminates against background noise due to various dark current sources and is especially useful for very sensitive detectors with large dark current. Named correlated readout, the method is based on periodically blocking the optical input enabling the subtraction of the output component of the current integration due to dark current sources such as large background photon noise that irradiates the detector circuitry and electron motion fluctuations inherent in the FPA components. State-of-the-art readout circuits developed from mature hybrid readout circuits were selected and redesigned for this research. The modified circuits were both simulated and experimentally tested. The results showed that it is feasible to modulate an optical input with the designed readout electronics and thus achieve longer signal integration time to enhance the FPA signal-to-noise ratio. The results of the thesis will be useful for long wavelength infrared (LWIR) sensing applications and particularly for

special scientific measurements, such as solar magnetography where large background is present.

Since the 1940's, photon detectors have been extensively developed. Because of their fast response time, high sensitivity and the ease of fabricating the required large 2D arrays in semiconductors, photon detectors, especially photovoltaic (PV) detectors, are expected to be used in almost all advanced infrared FPA systems. Many materials and detector structures are being developed to cover all the spectral bands, such as extrinsic silicon and germanium, Schottky-barrier photoemissive junctions, III-V, Hg<sub>1-x</sub>Cd<sub>x</sub>Te, IV-IV and multi-quantum well detector arrays [4]. The applications of the monolithic, hybrid, and monolithic heterostructure FPAs using these materials can be found in astronomy, military, environmental monitoring, law enforcement, and many other scientific research and surveillance purposes [5]. Unfortunately, photon and thermal noise sources limit the applications of infrared photon detectors. For long wavelength detection, such as the wavelength window 8 to 14µm (LWIR) and 14 to 30µm (VLWIR), background flux may become much stronger than signal flux because of black body radiation from the ambient. In detection at relatively high temperatures, such as 77°K (maintained by liquid nitrogen), 105°K (obtained in space by passive radiation cooling), and even room temperature, a detector's R<sub>o</sub>A will be decreased drastically for all the materials mentioned above [6]. In addition, the large background problem exists in other imaging applications where wavelength and temperature are not particularly important. For example, in the measurements for solar magnetograph, the signal is the difference of two circularly polarized light sources and the background is one of the primary sources. Due to the effect of Zeeman splitting this primary source can be 4 orders as high as the real signal [7]. All these detection conditions pose an important question: How does one read out the image signal in the presence of large background noise.

To design a FPA for working in the presence of large background noise which results in a large dark current, saturation of the image storage capacitors must be given primary consideration. Saturation would limit the signal integration time so that the array's signal-to-noise ratio will not be enough to reveal the image. This is because a FPA has very limited charge handling capacity [8], especially in 2D arrays. A large capacitor in each pixel is not only restricted by available real estate; it will also contribute a large reset noise that should be eliminated in the design. At the FPA level, the dynamic range, which is defined as the ratio of the maximum achievable output voltage swing to the output noise level of the imager, can be the most important device characteristic [9]. An ideal readout method would be one that both can increase the signal output voltage swing and reduce the noise level. This was the major goal of this research.

If there is not a breakthrough in detector materials or FPA architecture, conventional imaging methods will not solve the problem in the applications mentioned above, although second-generation FPA with hybridized readout electronics promise significantly higher performance and design flexibility [10-13]. Imaging an object in the presence of large dark current with a modulated source has been proposed recently [14]. The readout method developed in this thesis is the first to realize this new imaging approach [15]. The basic principle of this method is to demodulate the photon signal by charging the signal integration capacitor in one modulation phase and discharging the capacitor in the following phase to remove dark current signal. By processing the current from the detector in this way, it was shown that the correlated readout approach could

significantly subtract dark current integration and attenuate its associated noise. This results in an increase in the dynamic range and signal-to-noise ratio of the FPA.

In the next chapter, the hybrid readout method, which represents the state-of-theart of readout electronics, will be reviewed. Some newly proposed research will also be discussed. In chapter 3, the correlated readout method is presented, including the methodology, signal processing model and circuit implementation. The principle of phase sensitive detection is described to illustrate the noise reduction capability of the method. The possible application to the measurement of solar magnetograph and other imaging applications are also presented in this chapter. Chapter 4 discusses the design of correlated readout circuits using the standard CMOS process. Switching signal feedthrough is addressed as a serious problem in the correlated readout circuit design. For developing readout circuits based on the capacitive transimpedance amplifier concept a higher than normal common-mode rejection ratio of the operational amplifier is required. Finally, the design of a 16 by 16 silicon imager for the experimental study of this thesis is presented. The test chip was designed and fabricated by using Orbit 2µm n-well technology through MOSIS. Chapter 5 presents test results for the chip. The experimental methodology is discussed first, followed by a description of the test equipment. The experiments tested the correlated function, the frequency response and the switching feedthrough. The conclusions for the thesis are given in chapter 6. It was concluded that the correlated readout circuit is a promising approach for advancing FPA technology.

### CHAPTER 2

### A REVIEW OF INFRARED READOUT ELECTRONICS

#### 2.1 Introduction

Historically, the development of infrared sensors has concentrated on the growth, fabrication, measurement and optimization of IR materials and detectors. First-generation devices are fundamentally a monolithic FPA, which consists of a detector array, and the readout multiplexer integrated on the same substrate. Most of the readout techniques and device architectures were originally introduced from visible silicon imagers, such as charge coupled device (CCD) and charge injection device (CID) [16].

With the advancement in microlithography feature size reduction and the requirements of increased array size and performances, hybrid IR FPAs have developed rapidly in recent years. These second-generation FPA typically consists of a detector array chip bump-bonded on a silicon readout multiplexer. Because it allows independent optimization of the detector array and the readout, hybridized readout electronics that perform the function of detector interface, signal processing, and video multiplexing, represents the state-of-the-art for IR FPA readout technology.

Early hybrid readouts were still either CIDs or CCDs because of their success in visible imaging applications. With the Active Pixel Sensor (APS) technology stepping into the stage of scientific image acquisition [17], [18], x-y arrays addressed MOSFET switches, or direct readout (DRO) FET arrays, start to dominate today's infrared readout electronics for reasons of yield, design flexibility, and simplified interface. The APS concept is expressed as: One or more active transistors are integrated into the pixel of an

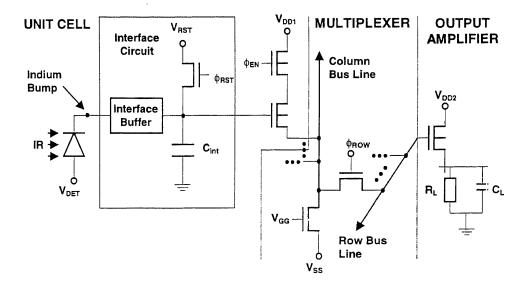

imaging detector array, and buffer the photo signal as well as drive the readout lines. The DRO architecture consists of an array of FET switches. The basic multiplexer has several source follower stages that are separated at the cell, row, and column levels by MOSFET switches which are enable and disable to perform pixel access, reset, and multiplexing (Figure 2.1).

Figure 2.1 Direct readout (DRO) architecture consists of an array of switches and detector interface circuits.

This review will concentrate on various readout methods with DRO schematic, which represent today's IR readout technology. It is well know that currently matured circuits are source follower per detector (SFD) [19], buffered direct injection (BDI) [20], gate modulation [21], and capacitive transimpedance amplifier (CTIA) [22], while many other methods are still in the conceptual stages. New proposed research on background suppression will be described in a separate section. The noise process is specially discussed, since noise figure is an important issue of focal plane array and signal-to-noise-ratio (SNR) is the prime design driver in most sensor systems. The important

conclusion is that it is the time to trade circuitry complexity with other performance characteristics. However, the existing readout methods will have difficulties to succeed for the detection conditions considered by this thesis research.

## 2.2 Matured Hybrid Readout Circuits

The general requirements of infrared FPAs fall into broad categories of array size, pixel pitch, charge handling capacity, integration time, noise, dynamic range, readout rate, operating temperature, power dissipation, radiation hardness, and detector bias control. Although many circuits can be used for interfacing discrete photon detectors, only a few have been successfully applied in FPA readout circuits, and the following four methods are matured so far.

## 2.2.1 Self-Integration Readout

To integrate charges on detector itself is a most commonly used design where the charge accumulation element is a capacitor or a CCD. Usually, this method is referred as direct detector integration (DDI), or source follower per detector (SFD) in active pixel sensor technology. The simple unit cell electronics still makes self-integration readout attractive because of the achievable small cell area and low power dissipation, although it can only be applied in low background detection.

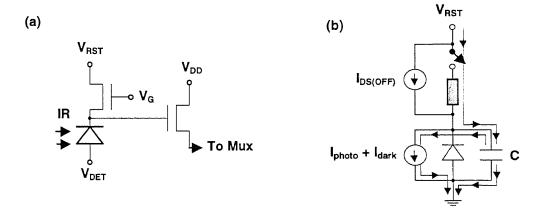

Figure 2.2 is a most simple photodiode DDI/SFD circuit with the illustration of detection principle. When the reset MOSFET is pulsed on, the photodiode capacitor, along with the sense node stray capacitor, will be charged from reset voltage ( $V_{RST}$ ) through its drain-to-source channel resistance, to approach the voltage level of  $V_{RST}$  -  $V_{T}$ ,

where  $V_T$  is the MOSFET threshold voltage for channel formation. Photo-generated minority carriers, together with the thermally generated minority carriers, will diffuse and drift across the PN junction to result in a current flow of  $I_{photo} + I_{dark}$  which acts to discharge the capacitor C. If the MOSFET is kept off for a time  $t_{OFF}$ , the change of the stored charge  $\Delta Q$  at the end of this time period will be given by the time integral of the combination of the photocurret  $I_{photo}$ , the dark current  $I_{dark}$ , and the MOSFET leakage current  $I_{DS(OFF)}$ :

$$\Delta Q = \int_0^{tOFF} (I_{photo} + I_{dark} + I_{DS(OFF)}) dt. \qquad (2.1)$$

The corresponding change in the voltage across the sense node will be  $\Delta V = \Delta Q/C$ . The voltage is buffered by the source-follower MOSFET and then multiplexed to a common bus prior to the video output amplifier.

Figure 2.2 Topology of direct detector integration (DDI) and source follower per detector (SFD): (a) simplest circuit schematic, and (b) principle of signal detection.

DDI/SFD topology is particularly susceptible to 1/f noise. This is due to the fact that the time period for which the source-follower transistor turns on during multiplexing is longer than the response time of the source-follower. This effect enhances the low frequency noise contribution, and limits the utilization of an integration capacitor for long

time integration applications. For noise figure consideration, it was concluded that the optimum sense node capacitance other than the detector capacitance occurs at the point where it is equal to the detector capacitance [3].

### 2.2.2 Injection Circuits

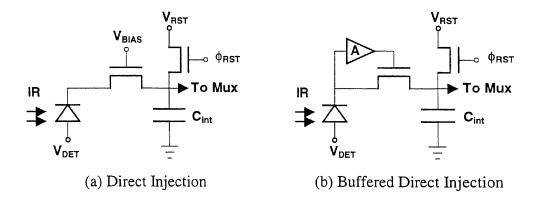

Instead of resetting the detector node directly, injection circuits accumulate charges on a separate integration capacitor  $C_{int}$ , and periodically reset the capacitor. Two popular injection circuits, direct injection (DI) and buffered direct injection (BDI), are shown in Figure 2.3. The direct injection circuit typically consists of an integration capacitor, an injection transistor, a reset transistor, and an output selection transistor (not shown in the figure). It is a widely used interface circuit because of its simplicity and high performance. The detector directly modulates the source of a MOSFET, and the photogenerated current directly couples into the storage capacitor for charge integration. This requires that detectors with N-on-P polarity interface N-type FETs (and vice versa) for carrier collection in the capacitor.

Figure 2.3 Schematic of injection circuits.

An important issue of using an integration capacitor is injection efficiency  $\eta_{\rm inj}$ , which represents the percentage of detector generated current that can be stored. It may

vary across an FPA due to FET threshold, detector bias, and detector resistance non-uniformity. For DI circuit, the injection efficiency is calculated as [1]

$$\eta_{inj,DI} = \frac{g_m R_{\text{det}}}{1 + g_m R_{\text{det}}} \left[ \frac{1}{1 + \frac{j\omega C_{\text{det}} R_{\text{det}}}{1 + g_m R_{\text{det}}}} \right],$$

(2.2)

where  $R_{det}$  and  $C_{det}$  are the detectors' dynamic resistance and capacitance, respectively, and  $g_m$  is the transconductance of the injection FET.

The advantage of using the integration capacitor is to increase the integration time so that the signal-to-noise ratio will be improved. However, poor injection efficiency makes the MOSFET noise a serious problem. One approach to improve the direct injection current is to use buffered direct injection (BDI) configuration as shown in Figure 2.3b. The detector is connected to both the input diffusion and the input of a feedback amplifier with open-loop gain  $-A_v$ . The effective  $g_m$  is increased by a factor of  $(1+A_v)$  and the injection efficiency becomes

$$\eta_{inj} = \frac{g_m R_{\text{det}} (1 + A_v)}{1 + g_m R_{\text{det}} (1 + A_v) + j \omega R_{\text{det}} [(1 + A_v) C_{amp} + C_{\text{det}}]},$$

(2.3)

where  $C_{amp}$  is the Miller capacitance of the amplifier. Apart from an improvement in the injection efficiency, the inverting gain in BDI also yields better control over the detector bias at different photocurrent levels and helps to reduce the saturation frequency compared with DI circuit, thereby allowing longer integration time. In spite of these improvements, BDI still shares the same limitation with DI in terms of low background applications. Another common drawback of injection circuits is a frame-to-frame crosstalk, since the detector is not directly reset; residual photon-induced charge from one frame time can be integrated into the next frame time.

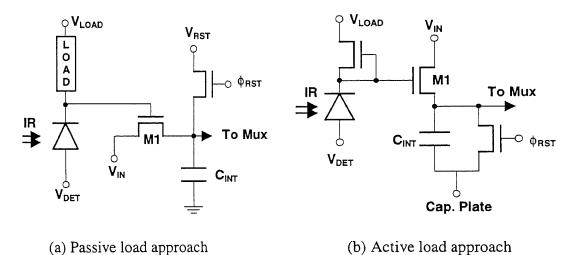

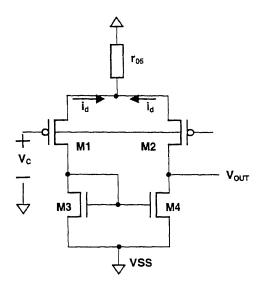

### 2.2.3 Gate Modulation

Gate modulation circuits utilize photon current to modulate the gate voltage of an input MOSFET and then induce an output current in the transistor. The principle of gate modulation input (GMI) structure is shown in Figure 2.4. The detector current, including photon current and dark current, flows through the load device. A gain-proportioned current flows into the integration capacitor from the input MOSFET (M1). The gain and dc level are adjusted by varying the source voltage  $V_{\rm IN}$  of the input MOSFET and setting the detector bias via  $V_{\rm DET}$ , so that the output is in proportion to the ac component of the signal. Good injection efficiency of the ac signal requires a high value of detector resistance with a greater load resistance value. Thereby, active load gate modulation, with a current mirror configuration, is often used in modern GMI design.

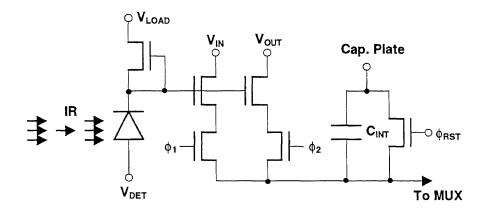

Figure 2.4 Gate modulation input structure.

In GMI circuits, the differential gate voltage applied to the input FET varies for a change in photon current ( $\Delta I_{photo}$ ) as

$$\Delta V_G = R_{LOAD} \eta_{ini,DI} \Delta I_{photo}. \tag{2.4}$$

The current injected into the integration capacitor is

$$I_{input} = g_m R_{LOAD} \eta_{inj,DI} \Delta I_{photo}. \tag{2.5}$$

The ratio of I<sub>input</sub> to I<sub>photo</sub> is the current gain, A<sub>I</sub>, which is

$$A_I = \frac{g_m}{g_{m,LOAD}} \eta_{inj,DI} \,. \tag{2.6}$$

The current gain, expressed by equation 2.6, can self-adjust depending upon the background flux by orders of magnitude. It also allows GMI to operate with a large integration capacitor compared to injection circuits, and still obtains low noise performance and high charge sensitivity. These features indicate its capability of background suppression, which leads to higher dynamic range. Unfortunately, gate modulation is only successfully applied to the detection condition when signal radiation is stronger than the background. The major problem comes from the requirement of detector bias reset as scene-induced current changes. To stabilize detector bias by using large reverse bias causes large 1/f noise and dark current non-uniformity. In addition, since the MOSFETs in gate modulation are normally operation in weak inversion, the threshold variations of the transistors become a more serious problem than injection circuits. Also from the current gain expression, GMI has a potential shortcoming for imaging application because the transfer characteristic is nonlinear, particularly when the current in the load and input FETs differ drastically.

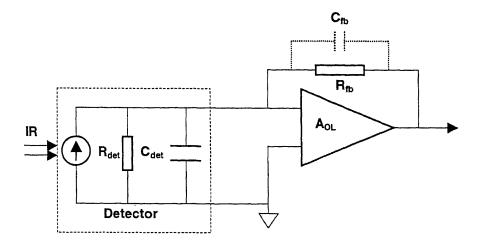

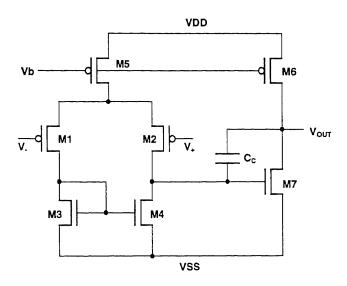

## 2.2.4 Capacitive Transimpedance Amplifier

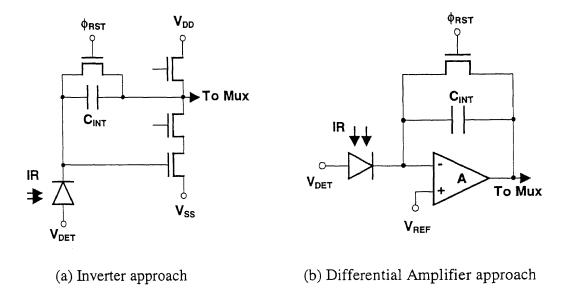

Capacitive transimpedance amplifier (CTIA) is a near ideal circuit for coupling an IR detector to a multiplexer. It consists of an inverting amplifier with a gain of A, an integration capacitor C<sub>int</sub> placed in a feedback loop, and a reset transistor in parallel with the integration capacitor, as shown in Figure 2.5. The amplifier in the circuit can be a

simple CMOS inverter as feedback amplification (Figure 2.5a), or a more elaborated differential amplifier (Figure 2.5b). The choice of the approach depends on the requirement of open-loop gain, bandwidth, power dissipation, and cell real estate.

Figure 2.5 Circuit schematic of CTIA.

In interfacing by the CTIA, when photon charge causes a slight change in voltage on the inverting input node of the amplifier, the amplifier, with open-loop gain in the hundreds to tens of thousands, responds with a sharp reduction in output voltage. This change in output is coupled back to the input node through the feedback capacitor, causing photon-induced charge to flow onto the feedback capacitor and oppose the initial effects of charge on the input node. At the end of integration process, the output voltage is sampled and multiplexed to the output video drivers, and the switch across the feedback capacitor is pulsed to reset. The CTIA gain, assuming a large open loop amplifier gain, is

$$V_{out} = \frac{I_{ph}T_{\text{int}}}{C_{fb}} \text{ [V]}, \qquad (2.7)$$

where  $C_{fb}$  is the feedback capacitor and the CTIA transimpedance is often expressed over a single frame of data as

$$Z_t = \frac{V_{out}}{I_{ph}} = \frac{T_{\text{int}}}{C_{fb}} \text{ [V/A]}.$$

(2.8)

The CTIA allows extremely small current to be integrated with high injection efficiency. It also can provide a highly stable detector bias, high gain and low noise, and ensure that the detector with low resistance can function as a current source if a well-designed differential amplifier is used. A recent report showed that the CTIA had the best overall performance characteristics compared to other readout methods at low backgrounds by state-of-the-art CMOS submicron technology [22]. Its attractiveness will continue to increase in the future.

#### 2.3 Noise in Hybrid Infrared FPA

Like all the other imaging systems, the noise sources in infrared FPAs have two general forms: temporal and spatial (or pattern) noise. Temporal noise is characterized by collecting sequential samples for each detector channel and calculating standard deviations and power spectral densities. Typical mechanisms found in FPA technology literature includes detector thermal noise, shot noise, readout noise, and flicker (1/f) noise. The measurement of pattern noise is more difficult. It requires accurate and uniform calibration sources, and often needs very long laboratory time. Therefore pattern noise has received much less attention in the literature. In most time this issue has been left to post image processing. In this section, the noise sources inside the array are reviewed in detail since large dark current is considered as the major problem for this thesis research, while many other noise sources are considered as trivial.

## 2.3.1 System Characterization

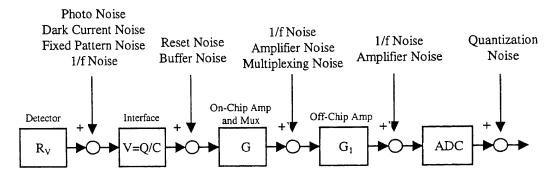

An imaging system can be considered as ideal elements with the noise introduced at appropriate locations. Figure 2.6 illustrates the noise transfer diagram. The total FPA noise consists of unit cell detector and electronic noise, and downstream noise contributed by the multiplexer and the driver.

Figure 2.6 Noise transfer diagram for an imaging system.

For single detector, specific detectivity (D\*) and noise equivalent power (NEP) offer the noise figure. D\* is the signal-to-noise ratio normalized to the electrical bandwidth and detector area. It is simply the reciprocal of the normalized NEP and has units cm-Hz/W (or Jones):

$$D^* = \frac{1}{NEP} (cm - \sqrt{Hz} / W) \tag{2.9}$$

D\* and NEP are useful specifications for finding detection limitation. At the FPA level, however, they are difficult to relate to system performance. The best description for temporal noise of a photovoltaic hybrid FPA is in terms of noise equivalent irradiance (NEI) in photons/cm<sup>2</sup>-s, which is described as FPA output noise normalized to responsivity:

$$NEI = V_n / R_v, \qquad (2.10)$$

where  $V_n$  is FPA total noise at operating background (in volts) and  $R_v$  is the responsivity in V/(photons/cm<sup>2</sup>-s):

$$R_v = \eta_m A_{opt} e \eta_{ini} T_{int} G_{elc} N_{TDI} / C_s, \qquad (2.11)$$

where  $\eta_m$  is the mean quantum efficiency,  $A_{opt}$  the detector optical area, e the electronic charge,  $\eta_{inj}$  the circuit injection efficiency,  $T_{int}$  the integration time,  $C_s$  the effective sense node capacitance,  $G_{elc}$  electronic gain past the sense node, and  $N_{TDI}$  is the number of time delay integration (TDI) stages.

For thermal imaging of the object temperature distribution, NEI is related to noise equivalent temperature difference (NE $\Delta$ T) by the relation

$$NE\Delta T = \frac{NEI}{\tau_{opt}\Omega_t \partial R_{ap}(T) / \partial T},$$

(2.12)

where  $\tau_{opt}$  is optical system transmission,  $\Omega_t$  is the projected solid angle of the telescope clear aperture with respect to the detector array, and  $\partial R_{ap}(T)/\partial T$  is the temperature derivative of the in-band source radiance, projected to the sensor aperture for a source temperature T. The detailed calculation can be found in reference [23].

NEI, along with NEAT, can give a good point of view for the consideration of temporal noise of the FPA. However, since the final output is an image, the ultimate figure of merit for an infrared imaging system should be how well the objects of varying size are resolved in the displayed image. The minimum resolvable temperature (MRT), which is a function of spatial resolution and is defined as the signal-to-noise ratio required for an observer to resolve a series of standard four-bar targets, is thus considered as a key specification for infrared FPA [1]. The inconvenience to follow MRT is that it can not be applied until the imaging system is really developed.

#### 2.3.2 The Dark Current Noise

Among the three types of noise in the photodetector, the dark current induced shot noise usually gives its limit of detection sensitivity. In most literature, the dark current is only used to describe the detector current in the dark. However, from a technical point of view, the dark current should be considered as the current inside a detector before it is exposed to a scene. Thus, the response to background radiation on the detector site should be counted as an important part of the dark current. As is well known, environment illumination can be very strong for LWIR because black body radiation peaks at 10 µm for room temperature. Therefore, the following definition is used in this thesis:

### The dark current = The detector dark current + The background photo current.

The detector dark current is the superposition of current contributions from three diode regions: bulk, depletion region and surface. The physical mechanisms include [5]:

- 1. Thermally generated current in the bulk and depletion region

- diffusion current in the bulk P and N region,

- generation-recombination current in the depletion region,

- band-to-band tunneling,

- intertrap and trap-to-band tunneling,

- anomalous avalanche current,

- ohmic leakage across the depletion region.

### 2. Surface leakage current

- surface generation current from surface states,

- generation current in a field-induced surface depletion region,]

- tunneling induced near the surface,

- ohmic or nonohmic shunt leakage,

- avalanche multiplication in a field-induced surface region.

For an ideal diode exposed to background flux density  $\phi_b$ , the dark current is the combination of thermal and shot noise, and can be expressed by [4]

$$i_n^2 = 2q\left[\frac{kT}{qR_0} + \frac{kT}{qR_0}\exp(\frac{qV}{kT}) + q\eta A\Phi_b\right]\Delta f , \qquad (2.13)$$

where k is Boltzmann constant, T absolute temperature, q the charge of electron, V bias voltage,  $\Delta f$  electronics bandwidth,  $\eta$  quantum efficiency, A the area of the diode, and  $R_0$  the dark resistance which is defined as

$$R_0 = (\frac{dI}{dV})_{|_{V}=0}^{-1}, \tag{2.14}$$

where I is the dark current and V is the diode's bias voltage. Background photo flux  $\phi_b$  can be expressed by

$$\Phi_b = \frac{\Omega}{\pi} \int_0^{\lambda_c} \frac{2\pi c}{\lambda^4 \left[ \exp(hc / \lambda kT) - 1 \right]} d\lambda$$

(2.15)

where  $\Omega$  is the field of view in radians of the detector and  $\lambda_c$  is the cutoff wavelength.

For the FPA working at short (1 to 3  $\mu$ m) and medium (3 to 5  $\mu$ m) wavelengths, the dark current noise is generally small compared to readout electronic noise, and usually is not considered in the readout circuit design. However, for the detection at LWIR and high temperature, the detection may reach two important limitations:

• background limited performance; if  $4kT/RoA \ll 2q^2\eta\Phi_b$ , then

$$D_{BLIP}^* = \frac{(A\Delta f)^{1/2}}{P_{NEP}} = \frac{\lambda}{hc} (\frac{\eta}{2\Phi_h})^{1/2}; \qquad (2.16)$$

• thermal noise limited performance; if  $4kT/RoA >> 2q^2\eta\Phi_b$ , then

$$D^* = \frac{\eta \lambda q}{2hc} (\frac{R_o A}{kT})^{1/2}.$$

(2.17)

The dark current results in fixed pattern noise (FPN). The fixed pattern noise is the variation from pixel to pixel in the camera display, but does not vary from frame to frame. It is primarily due to the dark current differences, which is caused by the differences in detector size, doping density, and foreign matter getting trapped during fabrication. Usually, it can be compensated by post imaging processing. But it may arise again because the calibration and equalization models cannot adequately model actual response, or the drift of the channels is beyond the capability of practical recalibration schemes.

The 1/f (flicker) noise level in photovoltaic detector is believed to be proportional to dark current [23], although it is also alias with biasing provided by input circuit or come from readout circuits. Whatever the source of 1/f noise in a detector or readout channel, the result is time varying offset drift. It is very nonuniform within a single chip for some narrow-bandgap detector materials. The issues in 1/f noise tend to be difficult because little theoretical basis exists for its rigorous definition. The dependency of 1/f noise with dark current indicates a background-driven 1/f drift, a less tractable process.

## 2.3.3 Readout Noise

Readout noise is usually referred as noise floor. It may include multiplexer and timing effects, reset noise, amplifier 1/f noise, and circuits nonlinearities. With the same readout architecture, the main difference for different readout method will be the noise of the interface circuit, while the reset noise may only related with storage capacitance no matter what kind of methods is used.

Reset noise (commonly referred as KTC noise) is thermal noise stored on the capacitor at the moment the switch is closed. The same as in any resistor-capacitor circuit with a resistance  $R_{on}$  and capacitance C, the rms noise on the capacitor can be calculated by integrating the thermal noise of the resistor over all frequencies through the transfer function of the RC circuit, and expressed as

$$v_c^2 = 4KTR_{on} \int_0^\infty \frac{1}{1 + (2\pi f CR_{on})^2} df \quad [V^2].$$

[2.18]

Equation 2.18 can be rewritten as

$$v_c = [4KTR_{on} \frac{\pi}{2} f(-3dB)]^{1/2} = (\frac{KT}{C})^{1/2} \text{ [volts rms]}.$$

[2.19]

The expression in terms of the noise charge stored on the capacitor is

$$q_c = (KTC)^{1/2}$$

[C]. [2.20]

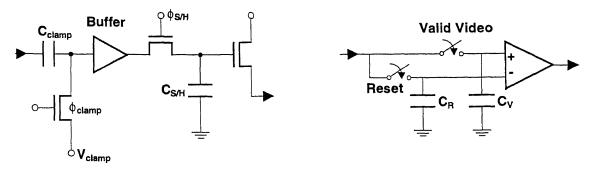

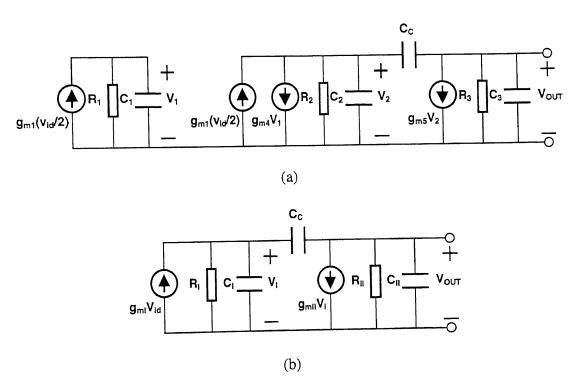

The reset noise, along with some of 1/f noise and fixed pattern noise, can be reduced via correlated double sampling (CDS). CDS may be performed by a clamping circuit with a delay line processor (Figure 2.7a), or by a differential sampling circuit illustrated in Figure 2.7b. The principle of CDS is based on correlation technique. The assumption is that the same voltage fluctuations will present on both video and reset levels. That is, the reset and video signals are correlated in that both have the same fluctuation. The performance of the CDS circuit depends on the product of the correlation time which is defined as the time interval between the two data samples, and the output amplifier cut-off frequency. Therefore, the 1/f noise reduction potential is somewhat limited, especially when the integration time is long, while the data rate is high.

- (a) Clamping and delay approach

- (b) Differential sampling approach

Figure 2.7 Correlated double sampling circuitry: (a) clamping and delay line processor; (b) differential sampling approach.

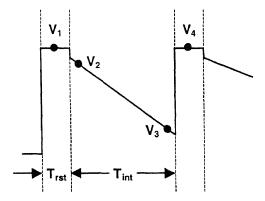

To improve the 1/f noise reduction, a modified CDS is often used. In the modified CDS circuit [24], two sets of closely spaced double samples are collected as shown in Figure 2.8. Prior to photocurrent integration, the reset noise and the offset is measured by computing the difference between the reset level before and after the reset transistor is shut off. The signal is measured at the end of the integration period by computing the difference between the data level before and after the unit cell is reset:

$$V_{mcds} = V_1 - V_2 + V_3 - V_4. (2.21)$$

As can be seen from Figure 2.8, the conventional CDS simply samples  $V_2$  and  $V_3$ , and has the output of  $(V_2 - V_3)$ .

Figure 2.8 Schematic showing modified CDS readout data construction.

After the sense node is reset to a fixed level, photocurrent is integrated on the capacitor. The voltage generated is expected to be linear with time under constant illumination. However, due to the circuit transimpedance and charge injection efficiency, combined with the integration capacitor and detector parameters, a voltage deviation will appear at the sense node. This circuit noise may be modeled by Laplace-domain small signal analysis, in which electrical transfer functions are determined for each component in the signal chain. Noise sources can be described by power spectral densities, and its propagation is described by transfer functions [25]. A more widely used technique of circuit noise analysis is to study input-referred circuit noise. The results for various readout circuits can be found in reference [1], and some of them are listed in Table 2.1.

Table 2.1 Input-referred circuit noise in mature readout circuits

| Input Circuit                          | Input-referred Circuit Noise                                                                                                                                                                             |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Direct Detector Integration            | $N_{sf} = \frac{\sqrt{2}}{S_{v}} \left[ \int_{v}^{\Delta f} V_{n}^{2}(f) \frac{(1 - \cos 2\pi f t)}{[1 + (2\pi f T_{D})]} df \right]^{1/2}$                                                              |

| Direct Injection                       | $\sigma_{input,ir}^{2} = \int \left[ \frac{1 + \omega^{2} C_{det}^{2} R_{det}^{2}}{g_{m}^{2} R_{det}^{2}} (\frac{8}{3} kTg_{m} + \frac{K_{FET}}{f^{\alpha}}) \right] df$                                 |

| Buffered Direct Injection              | $\sigma_{input}^{2} = \int_{0}^{\Delta f} \left[ \eta_{noise}^{2} \left( \frac{8}{3} kTg_{m} + \frac{K_{FET}}{f^{\alpha}} \right) + \Lambda_{amp}^{2} \left\langle e_{amp}^{2} \right\rangle \right] df$ |

| Gate Modulation                        | $\sigma_{input,ir}^2 = \int_{1}^{\Delta f} \frac{1}{A_I^2} (2qI_{input} + \frac{K_{FET,input}}{f^{\alpha}})]df$                                                                                          |

| Capacitive<br>Transimpedance Amplifier | $N_{amp,1/f} \approx \frac{C_{\text{det}} K_{amp} \sqrt{2}}{q} \left[ \ln \frac{5\tau_{\text{int}}}{\tau_{amp}} \right]$                                                                                 |

|                                        | $N_{amp,white} \approx \frac{C_{\text{det}}}{q} \sqrt{\frac{8}{3} \frac{kT}{g_m \tau_{amp} \pi}}$                                                                                                        |

The amplifiers exhibit 1/f noise because they are formed from MOSFETs. If an operational amplifier is designed as the amplifier, the input offset voltage due primarily to device and bias mismatches in the input stage would be another noise source. To

enlarge MOSFET gate area by using MOS input transistors in the lateral bipolar mode is one approach to reduce 1/f noise. The mismatch will also be reduced by increasing the input stage device geometry and size. If circuit real estate is available, chopper stabilization can be applied to reduce amplifier 1/f noise and correct the input offset voltage [26]. A simplified schematic of a chopper stabilized buffered direct injection design is shown in Figure 2.9 [27]. The chopping process shifts the amplifier's operating frequency to higher frequencies where the amplifier's noise is governed by white noise, not 1/f noise. Since the amplifier becomes ac coupled, the dc-offset components are removed and the amplifier is zero referenced. After amplification of the chopped or modulated signal, synchronous demodulation is applied to return the signal of interest to its original spectrum.

Figure 2.9 Buffered direct injection circuit using chopper stabilization to reduce detector bias offsets and amplifier 1/f noise.

The chopper stabilized unit cell circuits offer two significant improvements over conventional linear amplifiers: An effect of MOSFET threshold mismatch is vastly reduced and 1/f noise performance of the amplifier is improved. Disadvantages include high circuit complexity and the possibility of generating excess detector noise via clock feedthrough induced excitation, particularly with narrow band-gap photovoltaic detectors.

# 2.4 The Research on Background Subtraction

To image a scene in the presence of large dark current is usually referred as background suppression in the field of infrared FPA. It is an important future direction in both scientific and defense applications. Generally, to suppress background by interface circuits, two techniques, named charge domain background suppression circuit [28] and current memory based background suppression circuit [29], can be employed. However, the charge domain circuit cannot alleviate the charge handling capacity problem because it integrates both signal and background charges prior to the background suppression. On the other hand, the current memory circuit needs complicated unit cell circuit, therefore it is difficult to use in a 2D array.

# 2.4.1 A Unique Current Memory Circuit

A unique current memory circuit was proposed by NASA Jet Propulsion Laboratory. It utilizes a high accuracy current memory in the feedback loop of a BDI circuit enabling the measurement of small signals below the dark current level. Recently, a 2×130 array with 50μm×400μm unit cell size was designed for an imaging system operating in very long wavelength (VLWIR) region (12-18μm). The circuit measurements indicated an effective charge handling capacity of over 5×10<sup>9</sup> charges/pixel with less than 10<sup>5</sup> electrons of input referred noise.

Figure 2.10a shows the circuit schematic of the unit cell. The circuit performs automatic dark current suppression by first sampling and holding the dark current during the calibration cycle, and then subtracting the same during the imaging phase. A BDI input circuit is used to provide both the required bias stability for the detector and a high

input impedance enabling operation with high injection efficiency. The current mode pedestal subtracting is comprised of a cascode current memory, as shown in Figure 2.10b, with switch-feedthrough reduction and an isolation FET(M<sub>read</sub>). A double-sampled differential readout (DSDR) is employed to readout the differential infrared signal (Isig), while virtually eliminate the background. The reset noise from the current memory and integration capacitance are removed by the correlated double sampling (CDS) operation inherent in the DSDR.

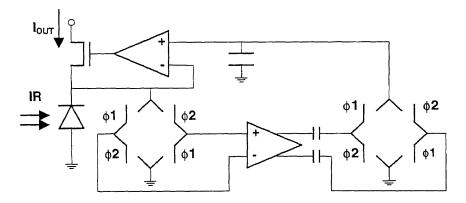

Figure 2.10 (a) Circuit implementation of current mode background subtraction and (b) Circuit schematic of current memory with feedback suppression.

The dark current memorization includes two steps. During the calibration cycle, the current memory is firstly enabled to memorize the dark current  $I_{bak}$ , which consists of the detector dark current as well as the current due to the background ( $I_{bak} = I_{dark-det} + I_{dard-bak}$ ). After the memorization is over, the current flowing through the current memory ( $I_{mem}$ ) is nearly the dark current ( $I_{bak}$ ), except for a small error current  $I_{res} = I_{bak} - I_{mem}$  that flows into the integration node. The pedestal due to the error current is then estimated in the voltage mode by integrating the error current on the integration capacitor ( $I_{cint}$ ), and sampling the resultant voltage onto one of the capacitors  $I_{cint}$ 0 of the DSDR. In imaging phase, signal current ( $I_{sig}$ 1) plus the offset current ( $I_{mem}$ 2) are integrated in integration node. After the exposure is over, the resultant voltage is sampled on the other capacitor ( $I_{cint}$ 2) in the DSDR. The difference between the potential of the two capacitors then proportional to the differential infrared signal ( $I_{sig}$ 2), while background is virtually eliminated.

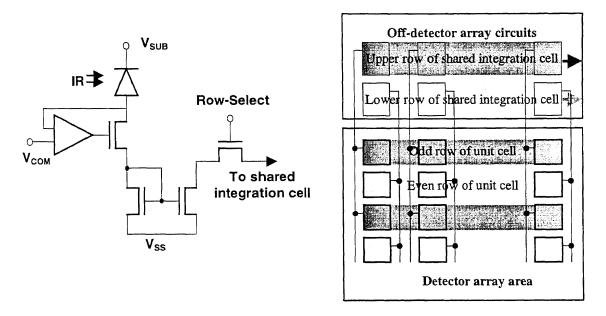

#### 2.4.2 Dynamic Current Mirror Buffered Direct Injection

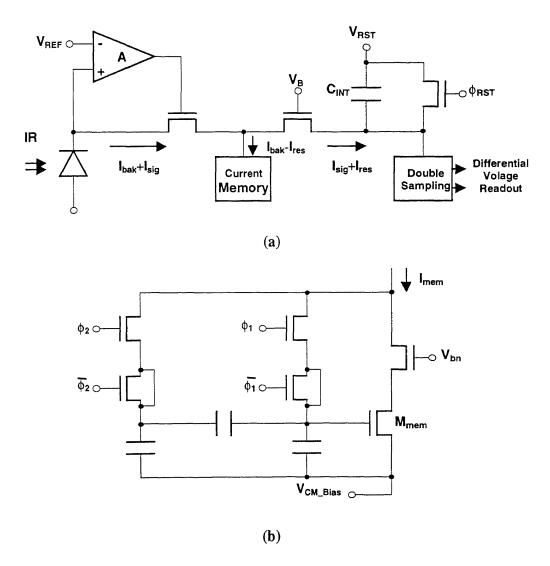

To develop a readout multiplexer for liquid nitrogen operated LWIR HgCdTe FPA, an offset-calibration current readout method was proposed [30]. The core of this readout method is a dynamic current mirror buffered direct injection (DCM-BDI). The principle of DCM-BDI can be described through Figure 2.11. When switch SI is in closing, the circuit self biases the photodiode in background (point A in Figure 2.11b) by charging the capacitor C to make the reference current  $I_{ref}$  equal to the current flowing inside the detector. During integration time with the switch is open, only the photon current ( $dI_{ph}$  in Figure 2.11b) will output to an integration capacitor. The background current is cancelled by  $I_{ref}$  since the gate voltage of the input FET is fixed by capacitor C.

Figure 2.11 Detection principle of dynamic current mirror buffered direct injection

A practical DCM-BDI circuit (not shown in the figure) had a buffer to keep the injection linear, and a capacitor to integrate the output current. A 100μm×100μm pixel had been laid out for 3-4 μm p-well CMOS process. The simulations showed that the circuit had good IR background and dark current suppression capability. The integration time, if compared with conventional BDI or CTIA, was increased by 25 times. However, this method needs forward bias of the detector to cancel out the dark current. For very high background, it was concluded that the optimum reference was about one half of the background current. Therefore, the injection efficiency became 50%.

To consider DCM-BDI as a current memory type of circuit, one can see that a forward bias on the detector offers a negative current to cancel out the background current, so that it is not integrated by the integration capacitor and the signal integration time is extended. However, when another dc current is flowing through the detector, extra shot noise will be introduced and the total noise level will be increased by square of 2, since the bias current is not correlated with the shot noise generated by the background radiation. Therefore, the improvement in FPA dynamic range and signal-to-noise ratio is limited.

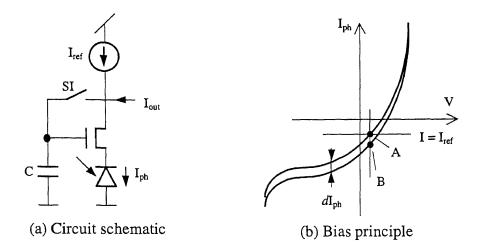

#### 2.4.3 Buffered Gate Modulation

Buffered gate modulation input (BGDI) is developed from the gate modulation input (GMI) which was discussed in chapter 2.2.3 [31]. An experimental 128×128 chip with 50µm×50µm pixel size was designed and fabricated in 0.8µm double-poly-double-metal n-well CMOS technology. Figure 2.12 is the circuit schematic and the chip architecture of BGDI. To suppress the background on chip using a shared current-mode background suppression circuit, this proposed BGDI method was concentrate on solving the problems of GMI unit cell, such as detector bias uniformity, injection efficiency and current gain stability, so that a 2D array with large FPA format could be realized.

Figure 2.12 Input circuit and chip architecture of buffered gate modulation.

As shown in Figure 2.12, the BGMI circuits integrates the buffered direct injection (BDI) technique with a GMI-like current gain configuration to form the unit cell input stage. The current gain is realized by a new unbalanced current mirror configuration. A current-mode background suppression circuit is implemented with shared integration capacitor unit to suppress the background current before integration.

Moreover, the dynamic charging output stage with CDS circuit can be included to decrease the power dissipation of the output stage and reduce noise.

Through the BDI input stage and the current mirror, the output current is sent to the shared integration cell through the row select switch. The effective current gain  $A_{LBGMI}$  of the BGMI circuit becomes

$$A_{I,BGMI} = \frac{g_{m,input}}{g_{m,load}} \eta_{inj,BDI} , \qquad (2.22)$$

and the injection efficiency is changed from  $\eta_{inj,DI}$  to  $\eta_{inj,BDI}$ . Thus, the current gain in the BGMI can be stable without the difficulties in adjusting and stabilizing the external bias voltage while keeping the circuit in low noise. The injection efficiency becomes stable because of a stable detector bias can be achieved. These improvements result in the feasibility of using the shared current-mode background suppression.

#### 2.5 Conclusions

Today's infrared FPA readout technology is still dominated by the matured readout methods. They are direct detector integration (DI) or source follower per detector (SFD), direct injection (DI) and buffered direct injection (BDI), gate modulation, and capacitive transimpedance amplifier (CTIA). The choice of the readout circuit is determined by system parameter, in which detector's characteristics play the most important role. The detector R<sub>0</sub>A so that the thermal noise, cutoff wavelength so that the background photon shot noise, and detector bias so that 1/f noise give the bottom line of the readout circuit design. A good design is expected to reduce these noise sources without introduce additional noise problems. The real difficulty of the readout circuit design is to complete

the interfacing task with minimum circuit nonlinearity, threshold voltage variation, 1/f noise, and power dissipation.

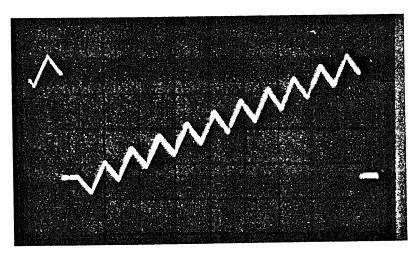

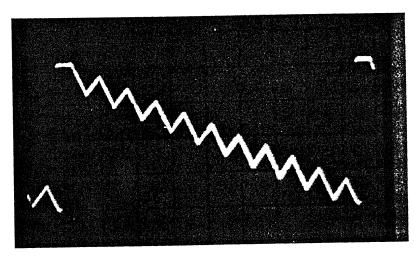

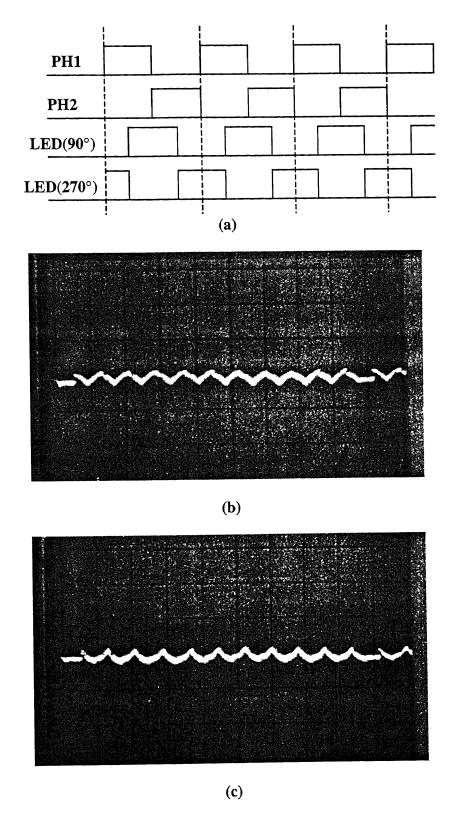

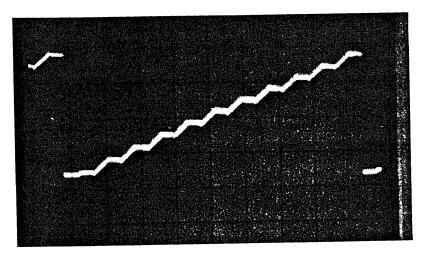

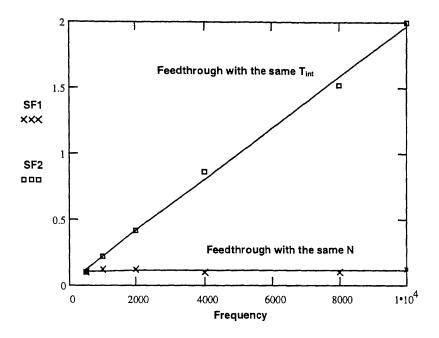

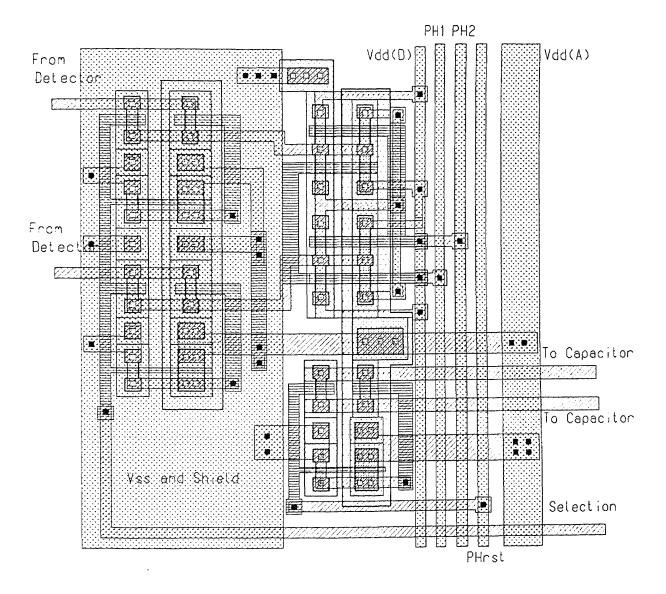

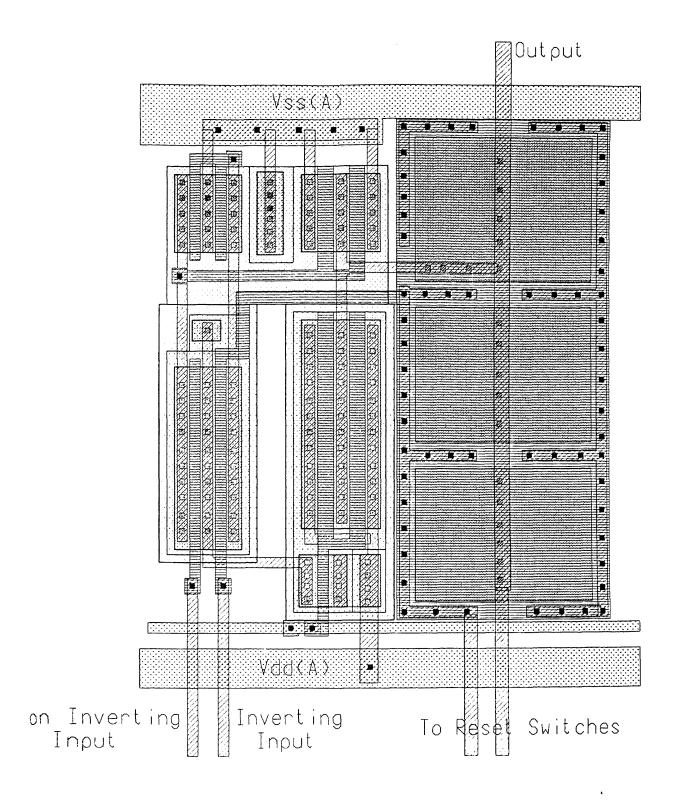

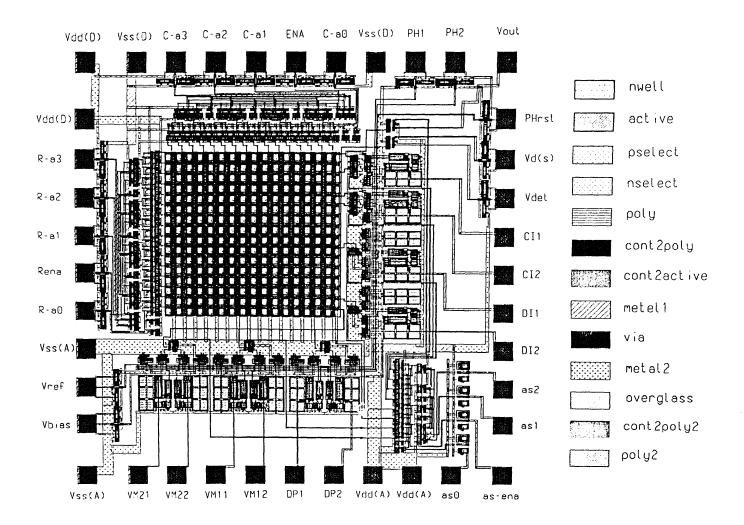

The existing literature reveals that, in lower and mid wavelength applications, it is readout circuits that limited the FPA performance. This is because matured readout methods are based on dc measurement technique, and this kind of circuit is susceptible to 1/f noise, drift, and the dark current. When the detector is near perfect, the device will be dominated by readout noise, which is usually referred as noise floor. However, for high background applications, or more generally, for the detection in the presence of large dark current, matured readout circuits will not success because the charge handling capacity is a serious problem. Simply increasing storage capacitor is not only impractical because of limited real estate, it will also cause large reset noise shown by equation 2.20 and reduce the transimpedance as equation 2.8 states. A new readout technology must be developed if there is no breakthrough in detector materials.