New Jersey Institute of Technology Digital Commons @ NJIT

Dissertations

**Electronic Theses and Dissertations**

Fall 1-31-1998

# Design and characterization of ultra high frame rate burst image sensors

Rakesh K. Kabra New Jersey Institute of Technology

Follow this and additional works at: https://digitalcommons.njit.edu/dissertations

Part of the Electrical and Electronics Commons

#### **Recommended Citation**

Kabra, Rakesh K., "Design and characterization of ultra high frame rate burst image sensors" (1998). *Dissertations*. 948. https://digitalcommons.njit.edu/dissertations/948

This Dissertation is brought to you for free and open access by the Electronic Theses and Dissertations at Digital Commons @ NJIT. It has been accepted for inclusion in Dissertations by an authorized administrator of Digital Commons @ NJIT. For more information, please contact digitalcommons@njit.edu.

## **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

#### ABSTRACT

## DESIGN AND CHARACTERIZATION OF ULTRA HIGH FRAME RATE BURST IMAGE SENSORS

#### by Rakesh K. Kabra

This thesis research was aimed at investigating and designing novel architectures required for ultra high frame rate (UHFR) imagers capable of operating at frame rates in excess of  $10^6$  frames/sec. To demonstrate the feasibility of these architectures, a  $180 \times 180$  element UHFR-I imager was designed and fabricated. The imager chip stored the latest 32 frames at its on-chip memory locations rather than performing a continuous readout. It was demonstrated that this architecture approach could achieve a frame acquisition rate of  $2 \times 10^6$  frames/sec. Additionally, other novel design features were incorporated to minimize optical cross talk and output amplifier noise, and maximize charge handling capacity.

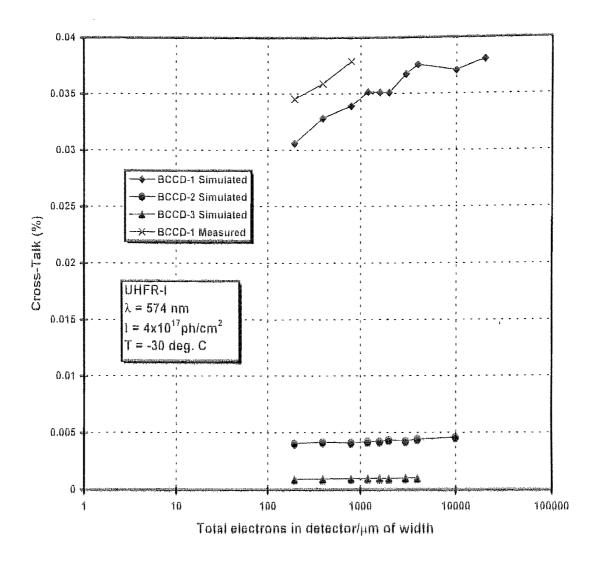

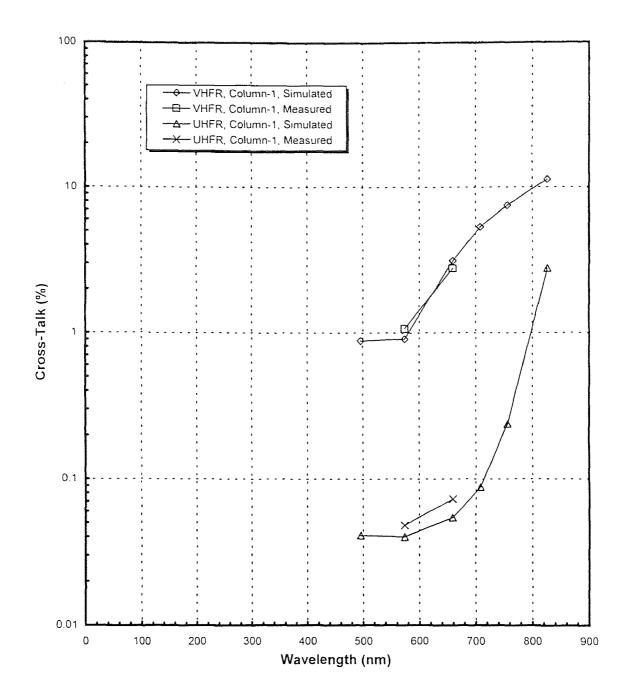

Two-dimensional (2-D) process and device simulations were performed to optimize optical cross talk and results compared favorably with experimental data of the fabricated chip. This tested imager was fabricated at the research laboratory of Sarnoff Corporation and had 4-levels of polysilicon, 3-levels of metal, eight implants and 21 photo mask levels. Simulations were also performed to characterize optical cross talk as a function of wavelength, optical shield aperture and epi-substrate doping. The measured value of optical cross talk was at least a factor of 40 times lower and maximum frame rate was a factor of 4 higher than previously published results for very high frame rate (VHFR) imager.

The experimental results were used to design a new  $64 \times 64$  element UHFR-II imager with an architecture capable of an image capture rate of  $10^7$  frames/sec. This architecture requires only 3-levels of polysilicon and 2-levels of metal and stores the latest 12 frames at its on-chip memory locations. Simulation results indicate that a frame rate of  $10^7$  frames/sec can certainly be obtained.

## DESIGN AND CHARACTERIZATION OF ULTRA HIGH FRAME RATE BURST IMAGE SENSORS

•

by Rakesh K. Kabra

A Dissertation Submitted to the Faculty of New Jersey Institute of Technology in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

Department of Electrical and Computer Engineering

January 1998

$\bigcirc$  $\langle$

Copyright © 1998 by Rakesh K. Kabra

ALL RIGHTS RESERVED

#### APPROVAL PAGE

#### DESIGN AND CHARACTERIZATION OF ULTRA HIGH FRAME RATE BURST IMAGE SENSORS

by Rakesh Kumar Kabra

/1 - 14-97 Date Dr. Kenneth Sohn. Committee Member Professor of Electrical and Computer Engineering, NJIT

Associate Professor of Electrical and Computer Engineering, NJIT

|                                                                  | (1-14-97 |

|------------------------------------------------------------------|----------|

| Dr. Edwin Hou. Committee Member                                  | Date     |

| Associate Professor of Electrical and Computer Engineering, NJIT |          |

Dr. N. M. Ravindra, Committee Member Associate Professor of Physics, NJIT

Dr. Durga Misra. Dissertation Advisor

Dr. John Tower. Committee Member Head. Sarnoff Corporation. Princeton, NJ

Dr. Vipulkumar Patel, Committee Member Technology Leader, Sarnoff Corporation, Princeton, NJ

<u>11-14-97</u> Date

11-14-97

Date

11-14-97 Date

<u>||-|4-97</u> Date

## **BIOGRAPHICAL SKETCH**

Degree: Doctor of Philosophy

Date: January, 1998

Date of Birth:

Place of Birth:

## Undergraduate and Graduate Education:

- Doctor of Philosophy in Electrical Engineering, New Jersey Institute of Technology, Newark, NJ, 1998

- Master of Engineering in Microelectronics, Birla Institute of Technology and Science, Pilani, India, 1993

- Bachelor of Engineering in Electrical and Electronics Engineering, Birla Institute of Technology and Science, Pilani, India, 1991

Major: Electrical Engineering

## **Presentations and Publications:**

- R. K. Kabra, V. Patel, J. Tower, J. L. Lowrance, V. Mastrocola and D. Misra. "180x180 Element Ultra High Frame Rate Burst Image Sensor," *Midwest Symposium* on Circuits and Systems, August 1997.

- W. F. Kosonocky, G. Yang, R. Kabra, C. Ye, Z. Toras, J. Lowrance, V. Mastrocola, F. Shallcross and V. Patel, "360x360-Element Very High Frame Rate Burst Image Sensor: Design, Operation and Performance," *IEEE Trans. Electron Devices*, VOL. 44, No. 10, pp. 1617-1624, Oct., 1997.

- W. F. Kosonocky, G. Yang, C. Ye, R. Kabra, L. Xie, J. Lowrance, V. Mastrocolla, F. Shallcross, V. Patel, "360x360-element very high frame rate burst image sensor", Proc. Of 1996 *IEEE international solid-state circuits conference*, pp. 182-183, San Fransisco, CA 1996.

Dedicated to my parents and my lovely wife Seema

#### ACKNOWLEDGMENT

First and foremost, I would like to express my deepest gratitude to Late Prof. Walter F. Kosonocky, for his guidance, friendship, and moral support. Walter's extensive experience and expertise in the Electronic Imaging area had contributed enormously towards this dissertation. Working with Walter was a great privilege and I miss him deeply.

I would like to thank my current advisor, Dr. Durga Misra, for his guidance and encouragement after Walter's demise. It has been my great pleasure to work with Dr. Misra.

I would also like to thank Dr. Kenneth Sohn, Dr. N. M. Ravindra, Dr. Edwin Hou, Dr. John Tower and Dr. Vipul Patel for serving as members of the committee. 1 am especially grateful to Vipul, for his immense help and suggestions throughout this research.

Special thanks are due to Mr. John L. Lowrance of Princeton Scientific Instrument, Inc. (PSI) for supporting this project. He provided experimental facility and guidance for doing research on High Frame Rate Burst Imagers. I am grateful to my current employer, Sarnoff Corp. for providing financial support and facilities for pursuing my research. Special thanks to Bill Mayweather, John Armer, and Laura Housel for their encouragement.

The author appreciates the timely help and suggestions from fellow graduate students Guang Yang, Jun Li, Zeynep Toras, and Chao Ye.

And finally, I would like to acknowledge the immense love, moral support and help from my wife, Seema and parents, to whom this thesis is dedicated.

vi

| TABLE | $\mathbf{OF}$ | CONT | <b>ENTS</b> |

|-------|---------------|------|-------------|

|-------|---------------|------|-------------|

| Ch | apte                                | r      | Page                                         |  |  |

|----|-------------------------------------|--------|----------------------------------------------|--|--|

| 1  | INTRODUCTION                        |        |                                              |  |  |

| 2  | FUNDAMENTALS OF SOLID-STATE IMAGING |        |                                              |  |  |

|    | 2.1                                 | Introd | uction5                                      |  |  |

|    | 2.2                                 | Funda  | mentals of CCDs and Image Sensing            |  |  |

|    |                                     | 2.2.1  | Overview of Charge-Coupled Devices           |  |  |

|    |                                     | 2.2.2  | Surface Channel CCDs and Buried Channel CCDs |  |  |

|    |                                     | 2.2.3  | Image Sensing Using CCD                      |  |  |

|    | 2.3                                 | Perfor | mance Parameters of CCD Image Sensors 10     |  |  |

|    |                                     | 2.3.1  | Fill Factor                                  |  |  |

|    |                                     | 2.3.2  | Optical Crosstalk 10                         |  |  |

|    |                                     | 2.3.3  | Dark Current                                 |  |  |

|    |                                     | 2.3.4  | Charge Handling Capacity                     |  |  |

|    |                                     | 2.3.5  | Quantum Efficiency 11                        |  |  |

|    |                                     | 2.3.6  | Dynamic Range                                |  |  |

|    |                                     | 2.3.7  | Resolution                                   |  |  |

|    |                                     | 2.3.8  | Spectral Response 14                         |  |  |

|    | 2.4                                 | Image  | r Architectures                              |  |  |

|    |                                     | 2.4.1  | Frame-Transfer CCD                           |  |  |

|    |                                     | 2.4.2  | Interline-Transfer CCD15                     |  |  |

|    |                                     | 2.4.3  | Frame-Interline-Transfer CCD 16              |  |  |

| 3  | ULT                                 | RA HI  | GH FRAME RATE BURST IMAGE SENSOR             |  |  |

## TABLE OF CONTENTS (Continued)

| Cł | napte | r       | Р                                        | age  |

|----|-------|---------|------------------------------------------|------|

|    | 3.1   | Introd  | luction                                  | 17   |

|    | 3.2   | Desig   | n of UHFR-I Image Sensor                 | . 18 |

|    |       | 3.2.1   | Specifications                           | . 18 |

|    |       | 3.2.2   | Chip Architecture                        | . 18 |

|    |       | 3.2.3   | Pixel Design                             | . 19 |

|    |       | 3.2.4   | Output Serial Register Design            | . 21 |

|    |       | 3.2.5   | Output Amplifier Design                  | . 21 |

|    | 3.3   | Proces  | ss for UHFR-I Burst Image Sensor         | . 24 |

|    |       | 3.3.1   | Process Technology                       | . 24 |

|    |       | 3.3.2   | Process Specifications                   | . 25 |

|    |       | 3.3.3   | Fabrication Sequence                     | . 26 |

|    | 3.4   | Opera   | tion of UHFR-I Imager                    | . 27 |

|    |       | 3.4.1   | Photodetector Readout                    | . 27 |

|    |       | 3.4.2   | Frame Integration and Readout            | . 28 |

|    | 3.5   | Exper   | imental Setup and Results                | . 29 |

| 4  | FRA   | ME RA   | ATE OPTIMIZATION AND DESIGN VERIFICATION | . 32 |

|    | 4.1   | Introd  | uction                                   | . 32 |

|    | 4.2   | Interco | onnection Methodology                    | . 33 |

|    |       | 4.2.1   | Macropixel Interconnection               | . 33 |

|    |       | 4.2.2   | Chip Interconnection                     | . 34 |

|    | 4.3   | Timin   | g Analysis                               | 34   |

## TABLE OF CONTENTS (Continued)

| Ch | Chapter Page |         |                                                                                                     |      |  |

|----|--------------|---------|-----------------------------------------------------------------------------------------------------|------|--|

|    |              | 4.3.1   | RC Delay of Each Driving Clock Phase in Macropixel                                                  | 35   |  |

|    |              | 4.3.2   | Metal Connection Structure and Delay Modeling                                                       | 37   |  |

|    |              | 4.3.3   | Timing Simulation                                                                                   | 40   |  |

|    | 4.4          | Verific | cation Techniques                                                                                   | 41   |  |

| 5  |              |         | ERFORMANCE OPTIMIZATION AND EXPERIMENTAL                                                            | 45   |  |

|    | 5.1          | Introdu | uction                                                                                              | 45   |  |

|    | 5.2          | Review  | w of CCD Modeling and Simulation Techniques                                                         | 46   |  |

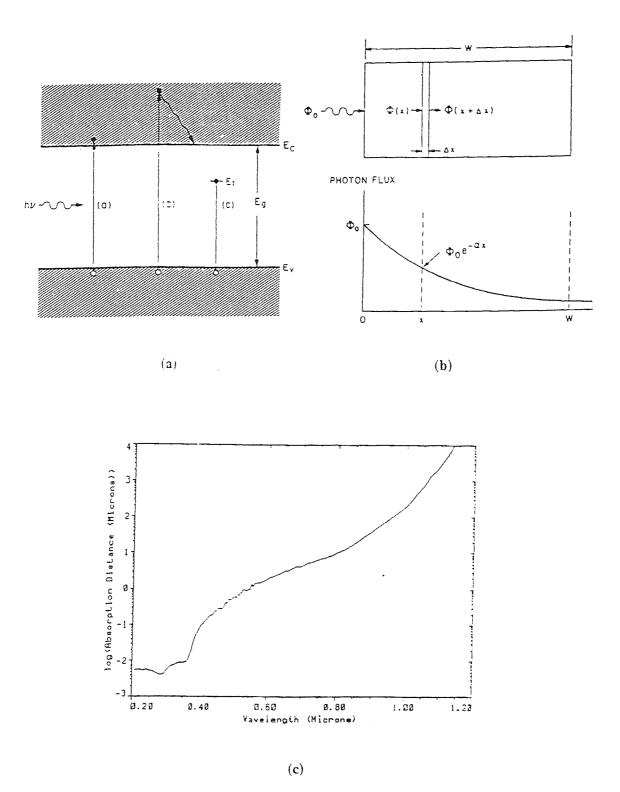

|    |              | 5.2.1   | Basics of Optical Absorption                                                                        | 49   |  |

|    |              | 5.2.2   | Model for Diffusion Crosstalk                                                                       | 51   |  |

|    | 5.3          | Crosst  | alk in UHFR-I Devices                                                                               | . 52 |  |

|    |              | 5.3.1   | One-Dimensional Simulation Model for Crosstalk                                                      | . 52 |  |

|    |              | 5.3.2   | Effects of Diffusion Crosstalk in UHFR-I Devices                                                    | . 55 |  |

|    | 5.4          | Simula  | ation and Experimental Results                                                                      | . 56 |  |

|    |              | 5.4.1   | Photocarrier Distribution and Transient Response                                                    | . 57 |  |

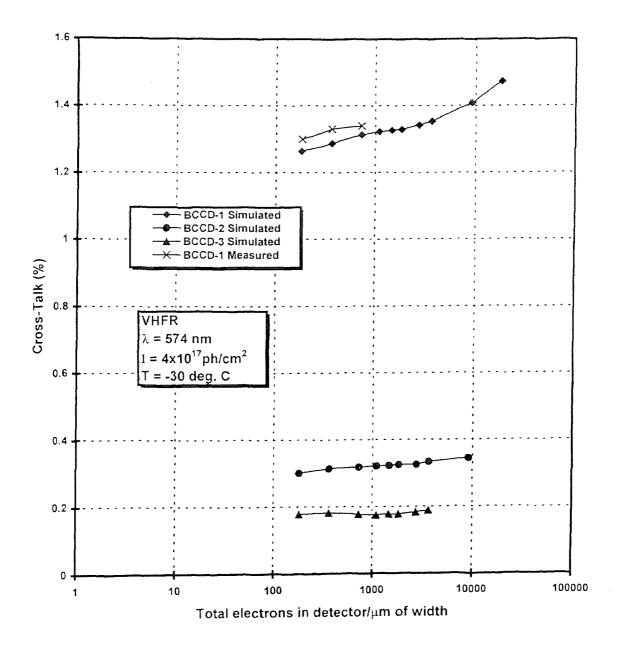

|    |              | 5.4.2   | Effect of Illumination Intensity and Wavelength on Optical<br>Crosstalk for UHFR-I and VHFR Devices | . 59 |  |

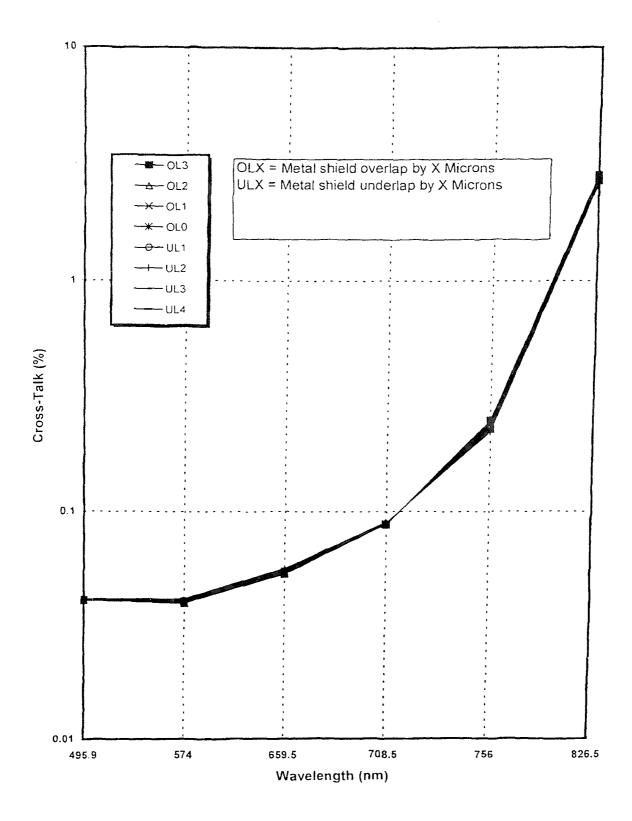

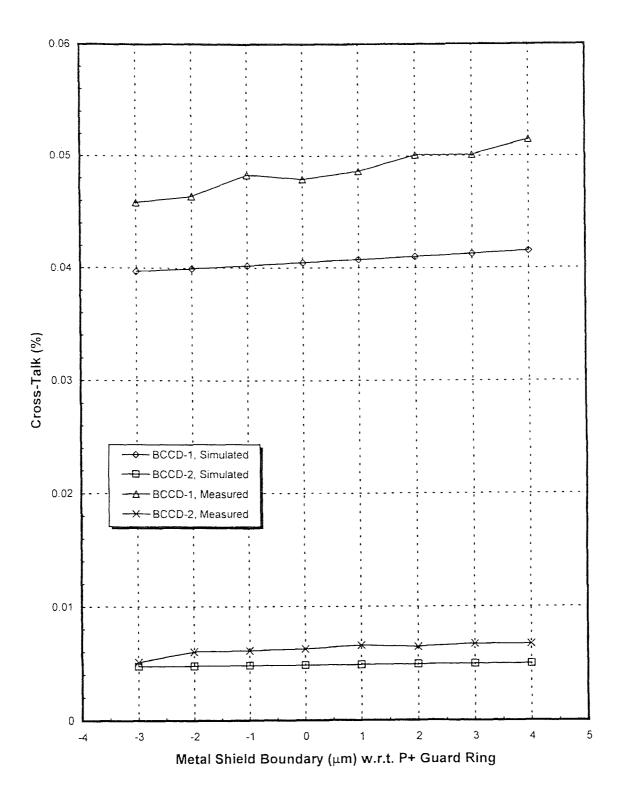

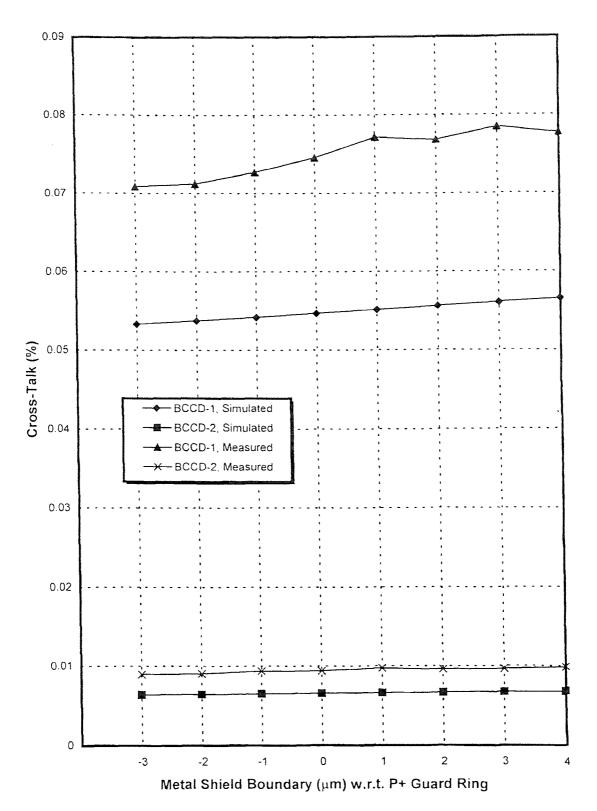

|    |              | 5.4.3   | Effect of Optical Shield Aperture on Crosstalk                                                      | . 62 |  |

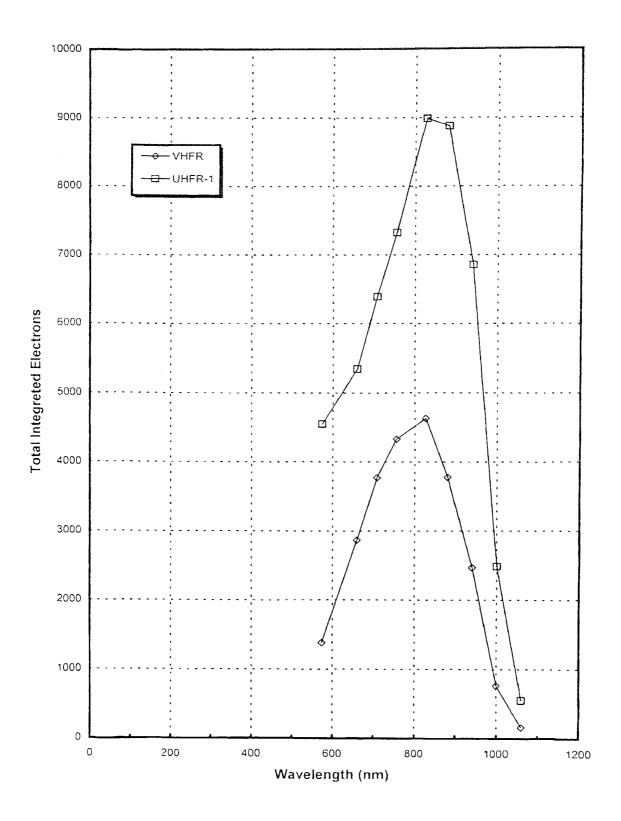

|    |              | 5.4.4   | Characterization of Photodetector as a function of Wavelength for<br>VHFR and UHFR-I Devices        | . 64 |  |

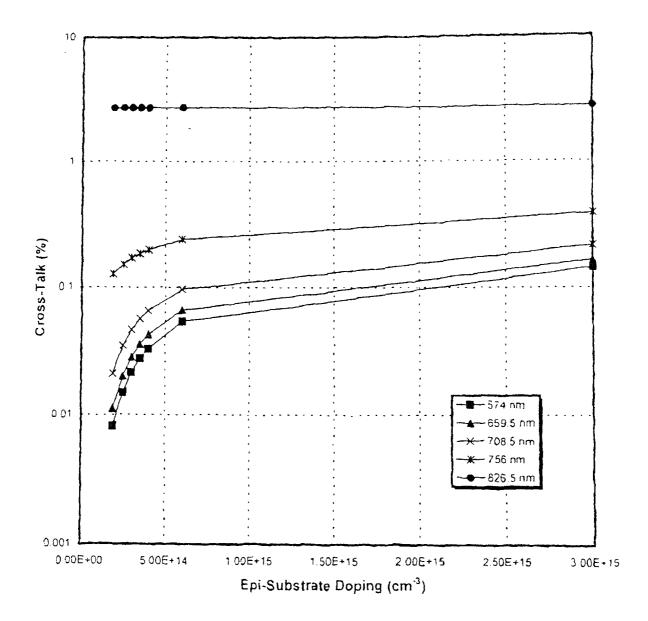

|    |              | 5.4.5   | Effect of Epi-layer Doping on Crosstalk                                                             | . 65 |  |

| 6  | TEN          | MILLI   | ON FRAME RATE UHFR-II IMAGER                                                                        | . 68 |  |

•

## TABLE OF CONTENTS (Continued)

| Ch | Chapter P |         |                                        |      |

|----|-----------|---------|----------------------------------------|------|

|    | 6.l       | Introdu | ction                                  | 68   |

|    | 6.2       | Design  | of UHFR-II Image Sensor                | . 68 |

|    |           | 6.2.1   | Specifications                         | 68   |

|    |           | 6.2.2   | Chip Architecture                      | 68   |

|    |           | 6.2.3   | Pixel Design and Operation             | 70   |

|    |           | 6.2.4   | Clock Rise Times and the Frame Rate    | 73   |

|    | 6.3       | Proces  | s for UHFR-II Burst Image Sensor       | . 74 |

|    |           | 6.3.1   | Process Technology                     | . 74 |

|    |           | 6.3.2   | Process Specifications                 | 75   |

|    |           | 6.3.3   | Fabrication Sequence                   | 76   |

| 7  | CON       | ICLUSI  | ONS AND RECOMMENDATION FOR FUTURE WORK | 79   |

| AP | PENI      | DIX     | FIGURES                                | 82   |

| RE | FERI      | ENCES   | I                                      | 136  |

## LIST OF TABLES

| Table | Pa                                                               | age  |

|-------|------------------------------------------------------------------|------|

| 3.1   | UHFR-I Imager Design Specifications                              | . 18 |

| 3.2   | Experimental Results from UHFR-I Imager                          | 30   |

| 4.l   | Unit area capacitances between layers of UHFR-I Process          | 37   |

| 4.2   | Pixel level capacitances of all clock phases                     | 37   |

| 4.3   | RC Delay Analysis for UHFR-I Clock Phases                        | 44   |

| 5.1   | Absorption length of Silicon at 300K                             | 51   |

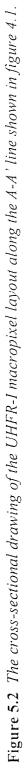

| 5.2   | Simulated and Measured potentials in UHFR-I device               | 53   |

| 5.3   | Depletion depth in the photodetector as a function of Epi-doping | 66   |

| 6.1   | Design Specification of UHFR-II Imager                           | 69   |

| 6.2   | Capacitances and delay times of the UHFR-II imager               | 74   |

## LIST OF FIGURES

| Figur | e P                                                                                                   | age  |

|-------|-------------------------------------------------------------------------------------------------------|------|

| 2.1   | Cross section of a CCD                                                                                | 83   |

| 2.2   | Charge transport in a CCD                                                                             | . 84 |

| 2.3   | (a) A metallurgical n+p junction; (b) voltage induced np junction                                     | . 85 |

| 2.4   | Readout structure for Image Sensors: (a) an MOS switch (b) CCD array                                  | . 86 |

| 2.5   | Device architecture of a frame-transfer image sensor                                                  | . 87 |

| 2.6   | Device architecture of an interline-transfer imager                                                   | . 88 |

| 2.7   | Device architecture for frame-interline-transfer imager                                               | . 89 |

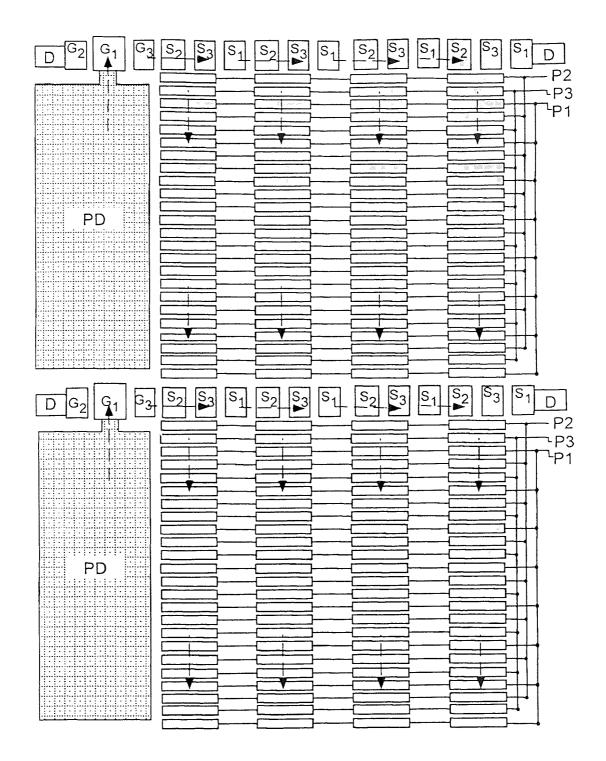

| 3.1   | Block diagram of the 180x180 element UHFR-I chip                                                      | 90   |

| 3.2   | Functional block diagram of UHFR-I burst imager                                                       | . 91 |

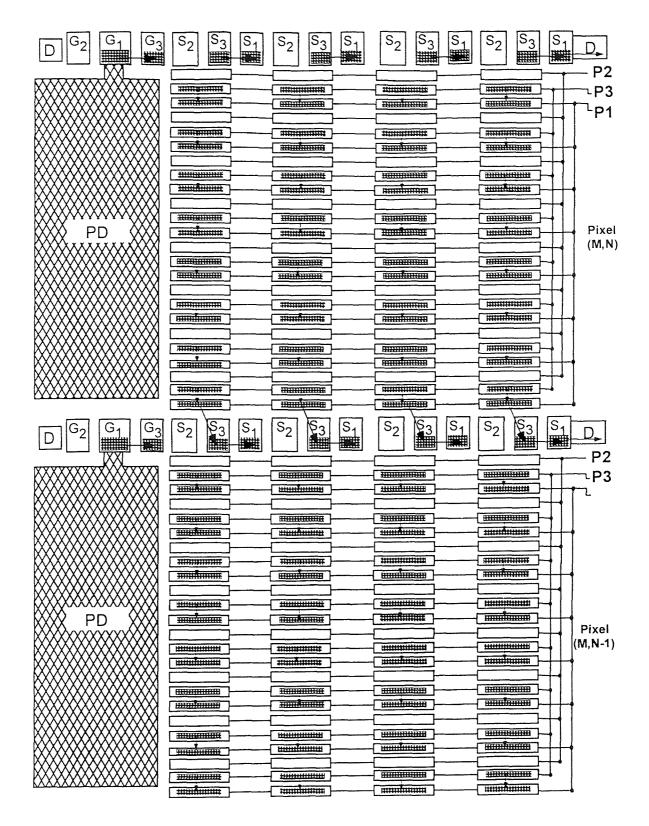

| 3.3   | Schematic diagram of two macropixels                                                                  | . 92 |

| 3.4   | SP and P Register design for 3-phase, 4-Poly CCD                                                      | . 93 |

| 3.5   | Schematic Diagram of a macropixel with OS register and output amplifier                               | . 94 |

| 3.6   | Output stage for UHFR-I imager                                                                        | . 95 |

| 3.7   | Funnel shaped output amplifier                                                                        | . 96 |

| 3.8   | Alignment of 21 mask levels and fabrication sequence                                                  | . 97 |

| 3.9   | Operation of photodetector in charge integration and readout mode                                     | . 98 |

| 3.10  | Schematic diagram of UHFR-I imager during collection of first frame charge of each 4 frames sequence. | . 99 |

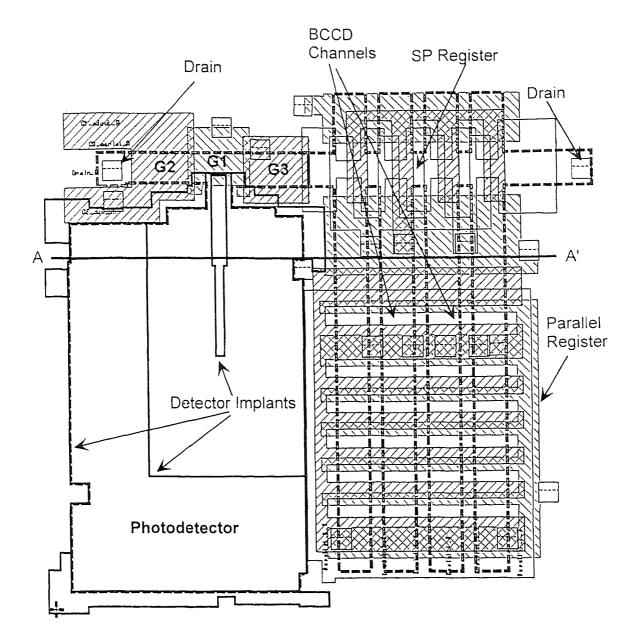

| 4.1   | Macropixel layout of UHFR-I chip                                                                      | 100  |

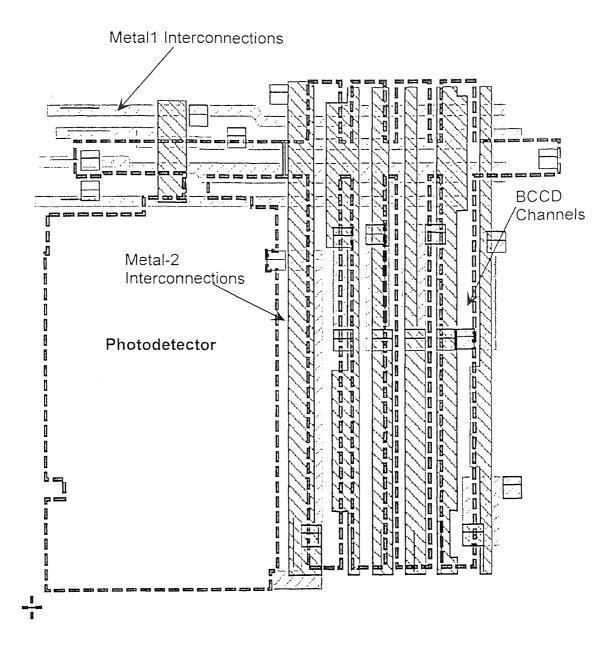

| 4.2   | Metal interconnections in a macropixel                                                                | 101  |

| 4.3   | Metal routing for non-critical clocks                                                                 | 102  |

## LIST OF FIGURES (Continued)

| Figure | 2                                                                                                                                                                                                                                            | Page  |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 4.4    | Metal routing for critical clocks                                                                                                                                                                                                            | 103   |

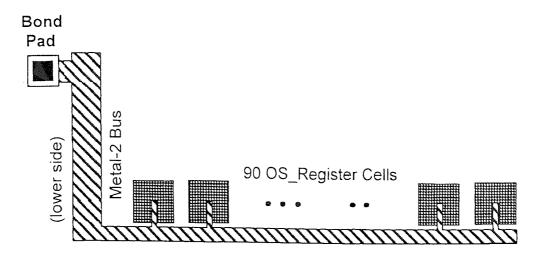

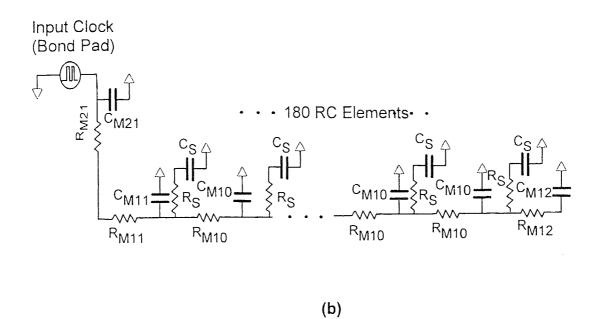

| 4.5    | Metal interconnections for structure-1 in (a), and its equivalent RC circuit in (b)                                                                                                                                                          | 104   |

| 4.6    | Metal interconnections for structure-2 in (a), and its equivalent RC circuit in (b)                                                                                                                                                          | 105   |

| 4.7    | Metal interconnections for structure-3 in (a), and its equivalent RC circuit in (b)                                                                                                                                                          | 106   |

| 4.8    | Linear CCD array and its equivalent MOS circuit                                                                                                                                                                                              | 107   |

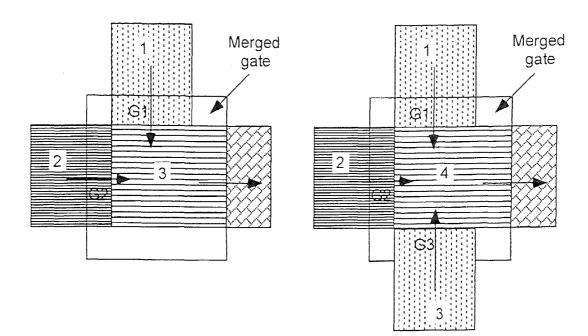

| 4.9    | Merged channel CCDs and its MOS equivalent circuits: (a) two channels merged and (b) three channels merged                                                                                                                                   | 108   |

| 4.10   | Equivalent schematic for macropixel                                                                                                                                                                                                          | . 109 |

| 5.1    | Optical absorption for $hv=E_g$ , $hv>E_g$ and $hv in (a), optical absorptionin semiconductor under illumination and exponential decay of photonflux in (b), and absorption distance of light in silicon as a function ofwavelength in (c).$ | 110   |

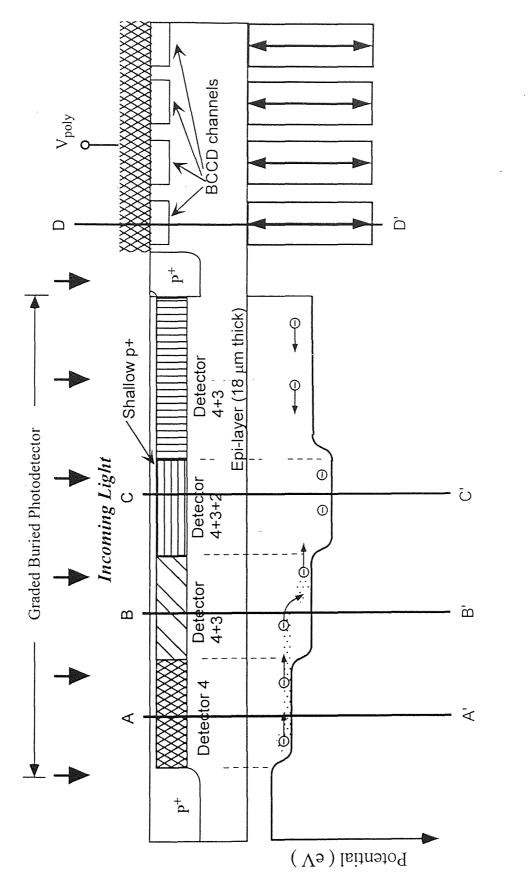

| 5.2    | The cross-sectional drawing of the UHFR-I macropixel layout along the A-A' line shown in 4.1.                                                                                                                                                | . 111 |

| 5.3    | Simulated values of maximum potential in the UHFR-I device cross-<br>section shown in 5.2 along the X-dimension                                                                                                                              | . 112 |

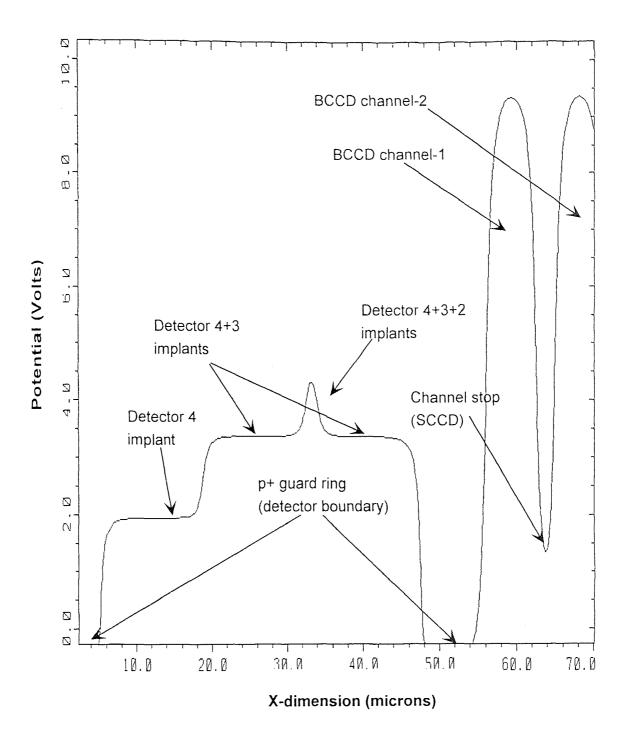

| 5.4    | Simulated values of potential in the UHFR-I macropixel regions shown in 5.2 along the depth dimension                                                                                                                                        | . 113 |

| 5.5    | Crosstalk Signal generation in a UHFR-I Macropixel                                                                                                                                                                                           | . 114 |

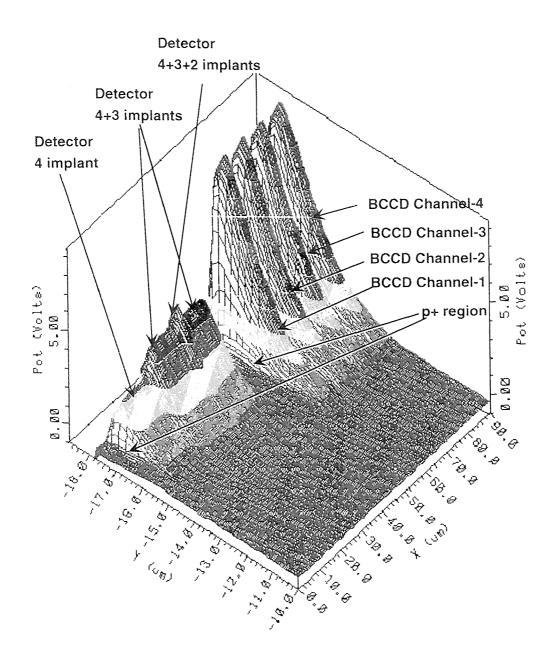

| 5.6    | Initial Potential Distribution in the macropixel region of UHFR-I device                                                                                                                                                                     | 115   |

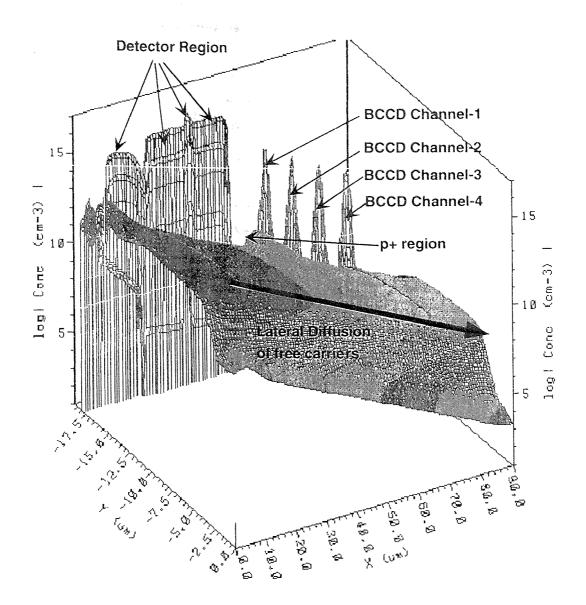

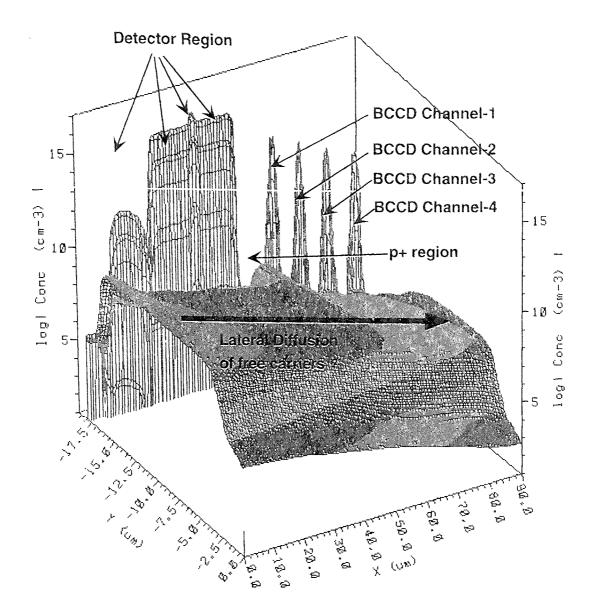

| 5.7    | Photogenerated Electron Distribution in the macropixel region after a light source of 600 nm wavelength, $4 \times 10^{20}$ photons/cm <sup>2</sup> intensity and 0.1 microsecond ON time is stopped                                         | . 116 |

## LIST OF FIGURES (Continued)

| Figu | ire Page                                                                                                                                                                               |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

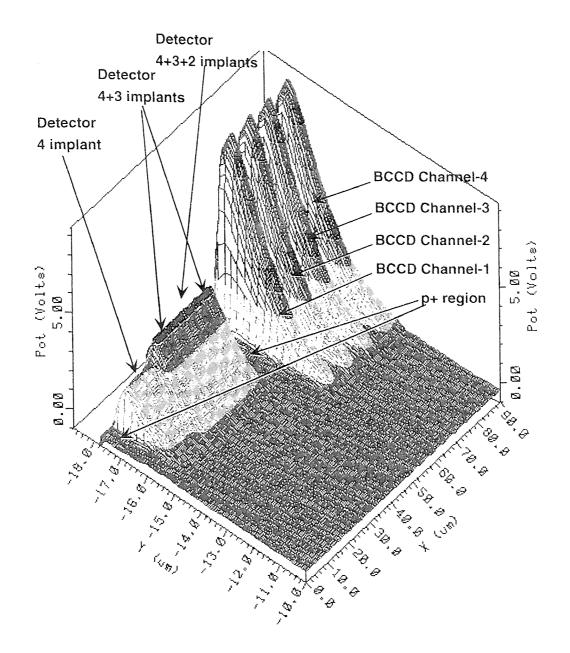

| 5.8  | Potential Distribution in the macropixel region after a light source of 600 nm wavelength, $4 \times 10^{20}$ photons/cm <sup>2</sup> intensity and 0.1 microsecond ON time is stopped |

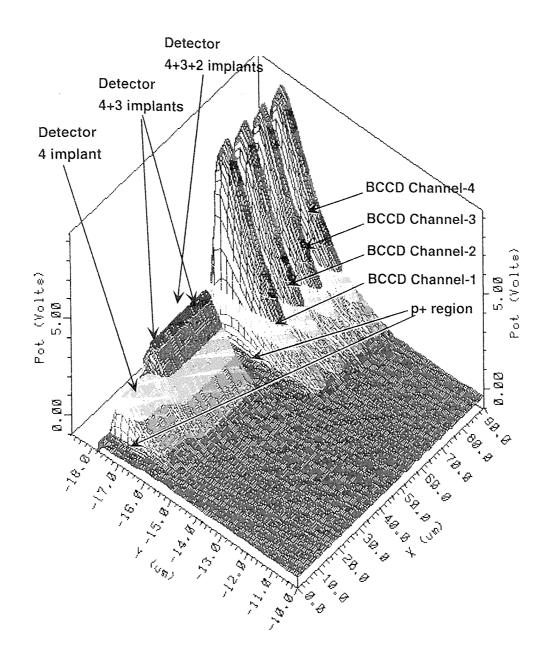

| 5.9  | Photogenerated Electron Distribution in the macropixel region after 0.4 microsecond diffusion of the carriers once the light source is turned off 118                                  |

| 5.10 | Potential Distribution in the macropixel region after 0.4 microsecond diffusion of the carriers once the light source is turned off 119                                                |

| 5.11 | Simulated and Measured values of optical cross talk for VHFR devices as a function of total integrated signal                                                                          |

| 5.12 | Simulated and Measured values of optical cross talk for UHFR-1 devices<br>as a function of total integrated signal                                                                     |

| 5.13 | Simulated and measured values of optical cross talk for VHFR and UHFR-I devices at different light source wavelengths                                                                  |

| 5.14 | Simulation results characterizing effect of metal shield aperture on the optical cross talk at different light wavelength                                                              |

| 5.15 | Simulated and measured values of optical cross talk in BCCD-1 and<br>BCCD-2 registers as a function of Metal Shield Opening at 574 nm<br>light source wavelength                       |

| 5.16 | Simulated and measured values of optical cross talk in BCCD-1 and<br>BCCD-2 registers as a function of Metal Shield Opening at 659.5 nm<br>light source wavelength                     |

| 5.17 | Simulated values of total integrated signal as a function of wavelength for VHFR and UHFR-I devices                                                                                    |

| 5.18 | Simulation results characterizing effect of epi layer doping on the optical cross talk at different light wavelength                                                                   |

| 6.1  | Block diagram of the 64 × 64 element UHFR-II chip 128                                                                                                                                  |

| 6.2  | Block diagram of the $2 \times 2$ macropixel                                                                                                                                           |

| 6.3  | Macropixel architecture                                                                                                                                                                |

.

## LIST OF FIGURES (Continued)

| Figure | e P                                             | age |

|--------|-------------------------------------------------|-----|

| 6.4    | Macropixel layout                               | 131 |

| 6.5    | Clock waveforms during image acquisition cycle  | 132 |

| 6.6    | Macropixel operation at t=t2                    | 133 |

| 6.7    | Macropixel operation at t=t4                    | 134 |

| 6.8    | Macropixel operation during frame readout cycle | 135 |

#### CHAPTER 1

#### INTRODUCTION

Many scientific applications require image acquisition at a frame rate significantly higher than 50/60 Hz required for consumer applications. Major high frame rate imaging applications include optical wavefront measurements, explosion study and hypersonic gas turbulence imaging. The required time resolution for these applications is between  $0.1 \mu s$ to  $1 \mu s$ , hence the imager should be able to capture images at the rate of  $10^6$  to  $10^7$ frames/sec.

The conventional charge coupled device (CCD) design can not achieve this speed, as the CCD transport speed and the output amplifier bandwidth is limited primarily due to gate capacitances. To overcome these limitations, various imager architectures have been devised for high frame rate imaging applications using multiport readout schemes. The maximum frame rate reported using a 32 output port design<sup>1,2</sup> is about 20,000 frames/sec. However, the use of many output ports makes the output signal processing and image reconstruction task extremely complex and the maximum achievable frame rate is still not adequate for the applications described earlier in this chapter.

In July 1991, Professor Walter F. Kosonocky and Mr. John L. Lowrance<sup>3</sup> proposed a general architecture for high frame rate CCD imaging applications. This architecture allows to capture a limited number of images at a very high speed. Subsequently, Dr. Guang Yang and Mr. Chao Ye developed an imager based on this architecture which could operate at a rate up to 500,000 frames/sec. The author led the testing team for this imager. The performance of these devices suffered from low fill

factor (~13 %), poor optical response due to large cross-talk between detector and pixel memory and limited maximum achievable frame rate of only 500,000 frames/sec.

The main objective of this dissertation is to advance the area of high frame rate imaging. There are a number of applications in numerous areas of science and engineering, which require image sensing of ultra fast transient phenomena, which would immensely benefit with the successful completion of this research.

Two new High Frame Rate Imager architectures have been invented as part of this research. First, a  $180 \times 180$  element ultra high frame rate (UHFR-I) imager has been designed to capture images at a  $2 \times 10^6$  frames/sec frame rate. This device has been fabricated at the Sarnoff Corporation and employs a process consisting of 4-layers of polysilicon, 3-layers of metal and eight implants using 21 photo mask levels. Currently, this imager is operational at Princeton Scientific Instrument Inc.(PSI), meeting all the design specifications. Second, a  $64 \times 64$  element UHFR-II imager has been designed to capture images at a  $1 \times 10^7$  frames /sec frame rate. The layout of this proposed design is complete and the devices will be fabricated at the Sarnoff Corporation using a process consisting of 3- layers of polysilicon, 2- layers of metal and eleven implants using 22 photo mask levels.

The performance of these imager structures was optimized through extensive process and device simulations. For this study, commercially available 2-D process and device simulation tools were used at the Sarnoff Corporation. The major objectives of these simulations were to minimize the optical crosstalk between the detector and pixel memory, and to achieve a very high readout speed from the photodetector structure consistent with the required frame rate for the imager. Detailed delay timing analysis was also performed using SPICE simulations to optimize the frame rate of the imager.

Princeton Scientific Instruments, Inc. (PSI) developed the hardware, software and camera electronics for UHFR-I imager. The D.C. shorts testing of the wafers was performed at Sarnoff using automated test setup. The author led the test team and obtained all the experimental results presented in this dissertation with the help of PSI and Sarnoff.

The second chapter of this dissertation gives an overview of solid-state imaging using CCDs. This chapter reviews the definition of performance parameters used to describe CCD imagers and introduces different types of imager architectures.

The third chapter describes the design, process and operational details of UHFR-I imager. It includes design and layout of imager macropixel, output serial register and output amplifier. The process steps used for fabrication of this device are also described in this chapter followed by the operational details of the UHFR imager.

The fourth chapter reviews various techniques used to achieve  $2 \times 10^6$  frames/sec frame rate and verification of layout of the UHFR-I imager. Interconnection methodology and detailed timing models are presented along with the timing delay simulation results and experimental results. Special layout versus schematic (LVS) techniques used to verify the CCD layout with its schematic are also described in the last section of this chapter.

The fifth chapter describes the process and device simulations results obtained by using TSUPREM IV and MEDICI tools for optimization of optical crosstalk. Basics of CCD modeling and simulation techniques are described first. Effect of total number of integrated carrier, optical shield aperture, wavelength and epi-substrate doping, on optical crosstalk were studied to optimize the imager performance. The simulation and experimental results of this study are described in this chapter.

The sixth chapter describes the design, process and operational details of UHFR-II imager. It includes design and layout of imager macropixel, output serial register and output amplifier as well as delay analysis results for maximum achievable frame rate calculations.

Finally, the conclusions of this dissertation and suggestions for future research work are presented in the seventh chapter.

#### CHAPTER 2

#### FUNDAMENTALS OF SOLID-STATE IMAGING

#### 2.1 Introduction

Solid-state imaging is based on the physical principle of converting quanta of light energy (photon) into a measurable quantity (voltage, electric current, etc.). The link between the photons at the input side of an imager and the voltage at the output side of the device is the collected and transported signal, which could be electrons or holes. Most fundamental operations in this chain are the generation, capture, and transport of this signal. With the invention of Charge-Coupled Devices (CCD) in 1970 by Boyle and Smith<sup>4</sup>, the classical imaging tube disappeared gradually, first from the consumer imaging applications and later from the professional broadcasting scene. The ability to detect optical signals allows CCDs to be constructed into very effective self-scanned image sensors. These sensors can store and transfer the detected charge image under the control of clock pulses, yet remain free of unwanted switching-transient pick-up noise, a unique characteristic.

There are three major sections in this chapter. The first section describes the fundamentals of CCDs and image sensing. This section also gives a brief overview of photon-conversion mechanism and the subsequent electron collection. The following section defines various specifications and performance parameters, which are used to characterize CCD imagers and are used throughout this thesis. The last section describes various imager architectures for linear and area imaging applications. This study will

conclude with an overview of the advantages and disadvantages of the various architectures.

## 2.2 Fundamentals of CCDs and Image Sensing

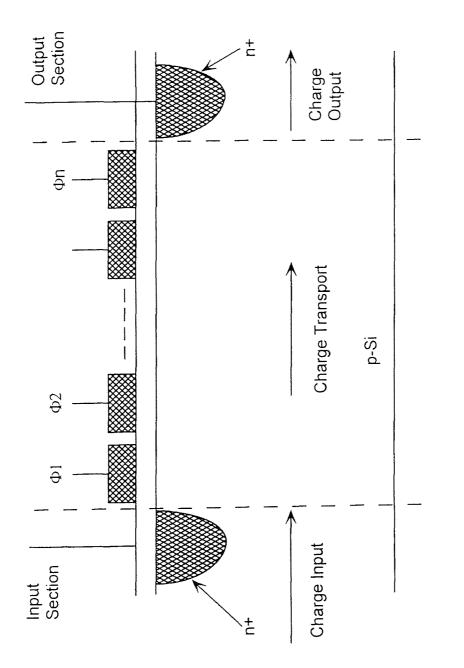

The basic concept of CCDs is a simple series connection of Metal-Oxide-Semiconductor (MOS) capacitors. The individual capacitors are physically located very close to each other. The CCD is a type of charge storage and transport device in which charge carriers are stored on the MOS capacitors and transported. The charge packets can be transported from one capacitor to its neighbor capacitor under the control of digital pulses, which are applied to the top plates of the MOS structures. The input of charge packets into CCDs, their transfer through the CCDs by means of the digital clocks on the gates and the output of charge packets is illustrated in Figure 2.1.

#### 2.2.1 Overview of Charge-Coupled Devices

The basic device physics and operation of CCDs is very well documented in several references<sup>5,6</sup>. This section reviews some of the important concepts of imaging using CCDs.

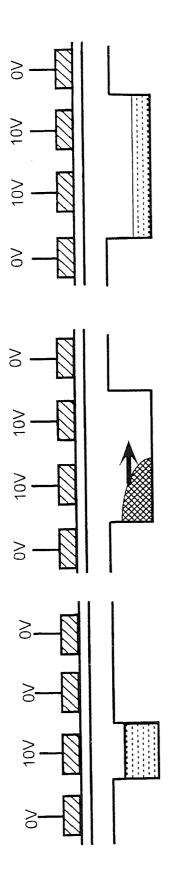

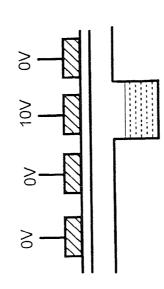

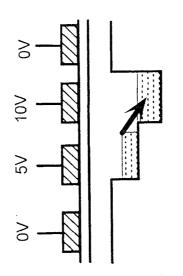

The basic working principle of a CCD rests on the theory of Metal-Oxide-Semiconductor capacitors. Depending on the gate voltage, the structure is forced into accumulation or into depletion. A CCD is just a line of these MOS capacitors spaced very closely together. The charge moves from one gate to another one, as these gates change under the control of gate clocks. Figure 2.2 illustrates the charge transport in a CCD. The charge transfer or movement of free electrons from one gate to another, along the surface of the CCD is driven by three different and independent mechanisms<sup>7</sup>:

1) The thermal diffusion of charge carriers;

2) Self induced fields; and

3) Fringing fields.

Compared with the fringing field induced transfer, the thermal diffusion and the self-induced drift are slow processes. To operate CCDs at high speeds, devices have to be designed and operated for maximizing the benefit from the presence of fringing fields. The fringing electric field generated by the voltages on the gate forces the charge to move from OFF gate to under ON gate. When the channel potential is completely flat underneath the CCD gates, the fringing field  $E_f$  are locally zero. But when the channel potential has a certain gradient, the fringing field  $E_f$  differs from zero. The substrate doping can also influence the fringing fields. When the substrate doping is lower, the thickness of the depletion layer is greater leading to higher fringing fields.

#### 2.2.2 Surface Channel CCDs and Buried Channel CCDs

In a real CCD structure, a certain level of inefficiency, which results in charge loss and noise, will degrade charge transport. The two major factors, which contribute to transfer inefficiency, are:

1) The finite time available to perform the charge transport; and

2) Charge trapping by the surface states.

If gate clocking is too fast or not enough fringing field is present, then due to the first effect mentioned above, some part of the present charge is left behind resulting in incomplete transfer. The second effect which makes the charge transport no longer perfect is the trapping of charges in bulk and surface states. These trapping states are crystalline defects present throughout the silicon but are in much higher concentration at the surface than in the bulk due to Si-SiO<sub>2</sub> interface. However, these electrons do not remain trapped in the surface states indefinitely and are subsequently released. The high transport efficiencies can only be achieved if:

- 1) The number of surface states is low;

- 2) The interaction between charge and surface states is minimized; and

- 3) The transport of the charges is faster than the time constant of surface states filling.

All these important characteristics can be obtained if the charge transport can take place in the bulk of the silicon instead of along  $Si-SiO_2$  interface. These type of devices are called Buried-Channel CCD (BCCD). In these devices, charge transport channel is designed such that the minority carriers cannot interact with the surface states and hence the charge trapping is minimized. By moving the transport channel deeper in the bulk, transport is also guided by larger fringing fields resulting in much higher charge transfer efficiency.

#### 2.2.3 Image Sensing Using CCD

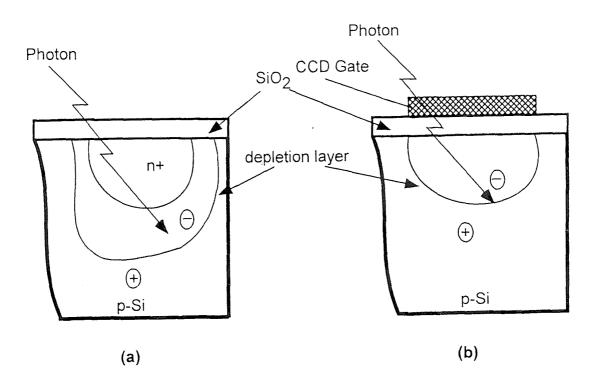

Energetic photons impinging on and penetrating into a semiconductor substrate can transfer part of their energy to the substrate. This energy transfer can take place by the generation of electron-hole pairs. If the energy content of the incoming photons is high enough, electrons will be released from the valence band to conduction band. In silicon, if incoming photons have energy higher than 1.1 eV [band gap for silicon] or their wavelength is shorter than about 1000 nm, electron-hole pairs will be created. The easiest way to separate these electrons and holes is by applying an electric field by which the electrons are captured and the holes are drained. Figure 2.3 illustrates two alternatives, a metallurgical n+p junction (reverse biased photodiode) and an externally induced np junction (MOS capacitor). The separation of the electrons and the holes is affected by the electric field across the np junction: electrons are stored as signal charge and the holes are drained to the p-type substrate.

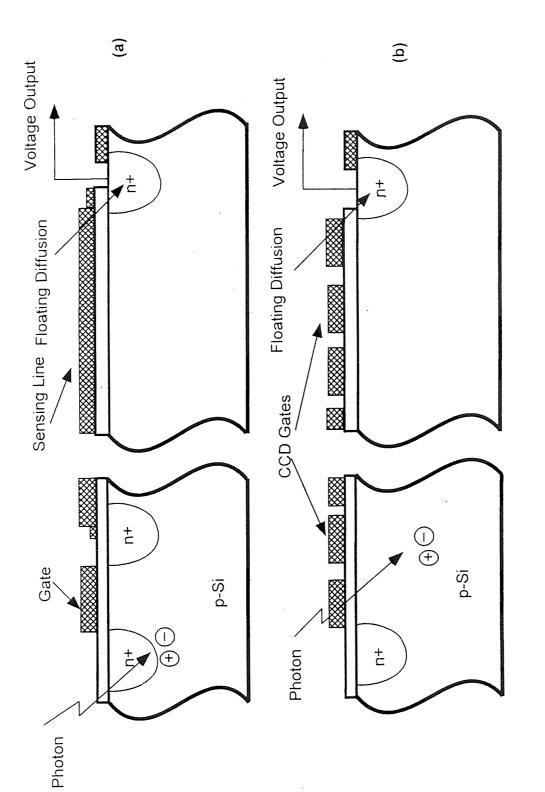

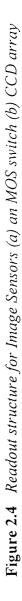

The next link in the imaging chain is the transport of the charge packets from the integrating sites toward the output of the device. Two alternatives are again possible and are shown in Figure 2.4, a MOS switch with a sensing line and a CCD shift register. In both cases the imaging cell or pixel is a photodiode built on a p-type silicon substrate. The technology of the CCD shift register is somewhat more complicated, and the transfer of the charge packet from the pixel towards the output diffusion needs appropriate clocking. The charge packet from the CCD shift register is transferred to the small capacitance of the output diffusion, which results in a relatively improved signal-to-noise performance.

The conversion from a charge packet to a voltage at the output node of the imager is typically done by sensing the voltage changes on a floating diffusion region by means of a source-follower amplifier.

#### 2.3 Performance Parameters of CCD Image Sensors

This section describes various performance parameters, used to measure, characterize and evaluate CCD image sensors. These parameters have been used throughout this thesis to evaluate and characterize the ultra high-speed CCD image sensors.

## 2.3.1 Fill Factor

Fill factor is defined as the percentage of the total pixel area, which is photosensitive. Higher fill factor results in higher photoelectron generation for a given amount of time.

#### 2.3.2 Optical Crosstalk

Optical crosstalk signal is generated in different ways in different types of imager configurations. The effect of this signal for different imager configurations is discussed in section 2.4 of this chapter. Fundamentally, all the "unwanted" optical coupling phenomena between detector-to-pixel or pixel-to-pixel is known as optical crosstalk. Optical crosstalk is also referred as "smear" in many references.

#### 2.3.3 Dark Current

Dark current is defined as the thermally generated charge during the operation of the imager, which becomes part of the signal charge. Dark current can be generated at different locations in the CCD but has, in all cases, to do with irregularities in the fundamental crystal structure of the silicon. Dark-current generation is highly temperature-dependent, doubling with approximately 8°C increase in temperature. Dark

current reduces the full well capacity and the non-uniform generation of it creates a fixedpattern noise component which is very difficult to control.

#### 2.3.4 Charge Handling Capacity

Charge handling capacity is defined as the maximum charge packet, which can be passed through the CCD without significant degradation. Buried-channel CCD can handle only about one-third of a charge packet as compared to surface-channel CCD of similar size. This is due to the fact that buried-channel CCD stores their charge in the bulk of silicon compared to at Si-SiO<sub>2</sub> interface as in surface-channel CCD.

#### 2.3.5 Quantum Efficiency

Quantum efficiency (QE) ( $\eta$ ) is a practical value for comparing output of different sensors with each other. QE is defined as the number of collected electrons ( $E_{total}$ ) divided by the number of photons ( $P_{total}$ ) impinging on the device. The total number of electrons and photons are given by:

$$E_{\text{total}} = \frac{Q_n}{qT_{\text{int}}}$$

(2.1)

$$P_{\text{total}} = \frac{\Phi_0}{h\nu} \tag{2.2}$$

hence quantum efficiency is defined as:

$$\eta = \frac{Q_n hc}{q T_{\rm int} \Phi_0 \lambda} \tag{2.3}$$

Where

$Q_n$  - is Total integrated charge;

$T_{int}$  - is Integration time;

h – is plank's constant;

c – is velocity of light;

v - is photon frequency;

$\Phi_0$  - is incoming photon flux; and

$\lambda$  - is the wavelength of the incoming photons.

For front-illuminated conventional frame transfer CCDs with polysilicon gates,<sup>5</sup> the quantum efficiency has three different regions depending upon the wavelengths.

- For wavelengths shorter than 500 nm, CCDs are somewhat insensitive. This

is due to the absorption of photons in the polysilicon gates which completely

covers the pixels of the CCD imager;

- For wavelengths larger than 1000 nm, CCDs are again insensitive. Now, the photons are rarely absorbed due to large absorption depths and are penetrated deep into the bulk;

- The region in between which is the visible spectrum, the quantum efficiency reaches its maximum of about 30% to 60%.

For Back-illuminated CCDs, the photons impinge on the silicon substrate. Hence, the quantum efficiency band is same as silicon absorption band. The maximum value of quantum efficiency could be as high as 90-100% for Si substrate with anti-reflection (AR) coating.

#### 2.3.6 Dynamic Range

The dynamic range of a CCD image sensor is expressed as the ratio of the saturation signal of the device to the r.m.s. noise measured at the output.

#### 2.3.7 Resolution

An important parameter of any image sensor is the spatial resolution that it provides, i.e., the ability to discriminate between closely spaced points in the image. This detection limit depends on the total number of pixels available, and the area of the device. Resolution is a measure for the highest spatial frequency, which can be resolved by the device taking a specific contrast in account.

The resolution of the device is assessed in terms of the modulation transfer function (MTF) of the output. The MTF is a combination of different modulation transfer functions, each of which can independently degrade the overall performance of the device. The main components are:

- The diffusion MTF which describes the degradation of the device's MTF due to the possibility of miss-diffusion of the electrons generated outside the depletion layer;

- 2) The transfer MTF which includes the non-ideal charge transfer effects; and

- The geometric MTF taking into the influence of the geometrical features of the pixels themselves.

#### 2.3.8 Spectral Response

Spectral response (R) is the output response of the imager due to an optical input signal. It is defined as the ratio of the output current ( $I_{out}$ ) of the sensor to the incoming light power ( $\Phi_0$ ).

$$R = \frac{I_{out}}{\Phi_0} = \frac{C_{FD}V_{OUT}}{A_{SF}A_{cell}T_{int}\Phi_0}$$

(2.4)

Where

$C_{FD}$  - is floating diffusion node capacitance;  $A_{SF}$  - is gain of the source-follower structure;  $A_{cell}$  - is area of a single pixel; and  $V_{OUT}$  - is output voltage measured at output amplifier.

Spectral response of an imager is closely dependent on the wavelength of the incoming light as the absorption and the collection of charges depend on the energy of the photons impinging the imager surface<sup>8</sup>. On the other hand, the spectral response for a given wavelength is linear in relation to the integration time and the incoming photon flux.

#### 2.4 Imager Architectures

Over the years, a number of different imager configurations have been developed for numerous applications<sup>9</sup>. This section describes typical architectures for area imaging. For area or two-dimensional imaging, most CCDs can be divided into frame-transfer imagers, interline transfer (IL) imagers, and frame-interline-transfer imagers.

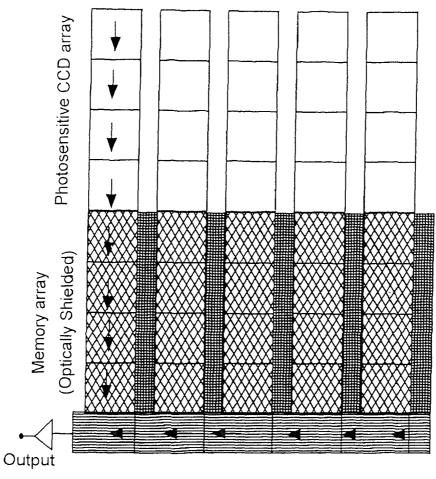

#### 2.4.1 Frame-Transfer CCD

Figure 2.5 shows a typical architecture of a frame-transfer type CCD image sensor. In the light-sensitive top part of the device or image section, all CCD cells are biased into the integration mode. Some of the CCD phases are connected to a high DC level so to collect photogenerated electrons and some are to a low DC level so to act as a barrier between pixels. At the end of the integration time, the CCD shift registers transfer their charge packets to the corresponding CCD lines in the storage section. Once the entire frame has been transported to the memory section, horizontal shift register can transfer charge towards the output amplifier.

By virtue of the basic principle of the frame-transfer CCD, smear is inevitable. Spurious signals are generated when the frame is transferred from image section to storage section. During this transfer, the imager is not shielded from the incoming light, charge-carrier generation continues and spurious signals are added to the charge packets in transport. To minimize the smear signal, transport from the image section to the storage section should be achieved as fast as possible.

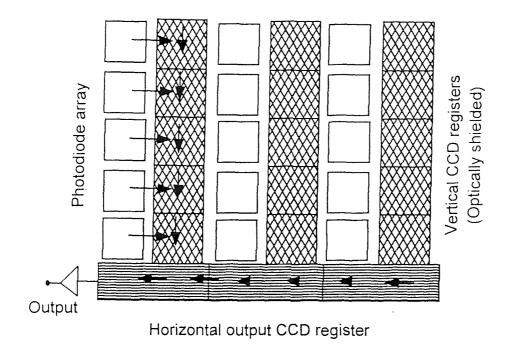

#### 2.4.2 Interline-Transfer CCD

Figure 2.6 shows the general interline-transfer type CCD image sensor. The integration of charge takes place in the pixels, which can be photodiodes or photogates. At the end of the integration time, the charge packets are shifted from the pixels into the vertical CCD shift register alongside. These registers are shielded from light and act as memory elements. After this transfer, a new integration period can begin and simultaneously the vertical shift registers are emptied into the horizontal-output register line by line. The

serial information in the horizontal output register is transferred to the output and consequently converted into an electrical voltage.

Interline-transfer device architectures are also not immune from smear signals but their generation phenomenon is completely different from frame-transfer devices. In the interline-transfer imagers, smear is caused by either:

- 1. Stray electrons generated underneath the photodiode area and diffused into the vertical CCD shift registers.

- 2. Stray photons, which arrive in the vertical CCD shift registers via, for instance multiple reflections at the Si-SiO<sub>2</sub> interface and generate electron-hole pairs locally.

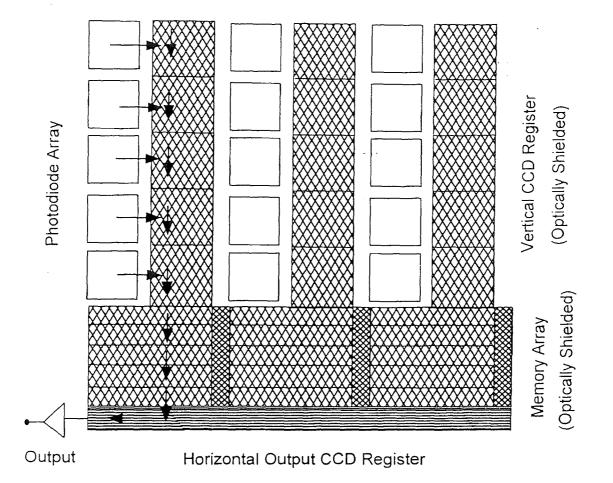

# 2.4.3 Frame-Interline-Transfer CCD

Figure 2.7 shows the frame-interline-transfer type architecture, which is a combination of frame-transfer and interline-transfer devices. The device architectures described in subsequent chapters are based on this architecture. It has the light-sensitive area of the interline-transfer device, combined with the storage area of the frame-transfer device. Its basic operation also combines these two devices: integration of the charge in the pixels, transferring the charge packets into the vertical shift register, followed by fast vertical transport toward the shielded memory part of the imager.

#### CHAPTER 3

# ULTRA HIGH FRAME RATE BURST IMAGE SENSOR

## 3.1 Introduction

This chapter describes the overall design, architecture and operation of a ultra high frame rate (UHFR-I) burst image sensor. UHFR-I is a 180 × 180 element, 3-phase CCD imager capable of capturing images at a maximum rate of  $2 \times 10^6$  frames/sec and stores the last 32 integrated frames at its on-chip storage pixels. This imager has been fabricated at Sarnoff and is operational at PSI Inc. This device design is conceptually based on a device architecture invented by Professor Walter F. Kosonocky and Mr. John L. Lowrance for high frame rate imaging applications. The previous work consists of a very high frame rate (VHFR) imager architecture with a maximum achievable frame rate of about 500,000 frames/sec. The author was extensively involved in the testing and development of the camera system for these devices<sup>10</sup>. The performance of VHFR devices was severely degraded due to high level of optical crosstalk between photodetector and storage area. The UHFR-I imager not only improves the frame rate by a factor of 4 as compared with VHFR imagers, but it also offers numerous performance enhancements of parameters such as fill-factor, charge handling capacity, noise performance and optical crosstalk.

# 3.2.1 Specifications

This UHFR-I imager was designed for adaptive optics applications. The initial specifications for this imager were:

| Maximum Frame Rate                  | $2 \times 10^6$ frames/sec           |

|-------------------------------------|--------------------------------------|

| Resolution                          | 180 x 180                            |

| Frame Storage Memory                | 32 frames                            |

| Pixel Size                          | $< 100 \text{ x} 100  \mu\text{m}^2$ |

| Fill Factor                         | > 40 %                               |

| Saturation Signal, Q <sub>max</sub> | > 40,000 e <sup>-</sup> /pixel       |

| Dynamic Range                       | 2000:1                               |

| Spectral Response                   | 250 to 900 nm                        |

| Readout Noise                       | < 10 rms e <sup>-</sup> /pixel       |

| Technology                          | 3-phase BCCD, 4-level                |

|                                     | poly, 3-level metal                  |

| Design Rules                        | 1.5 μm                               |

**Table 3.1** UHFR-I Imager Design Specifications

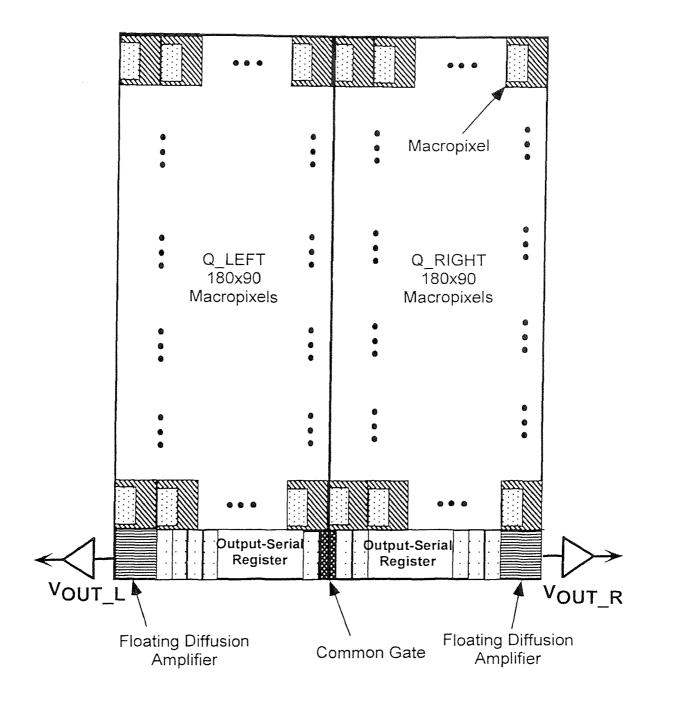

### 3.2.2 Chip Architecture

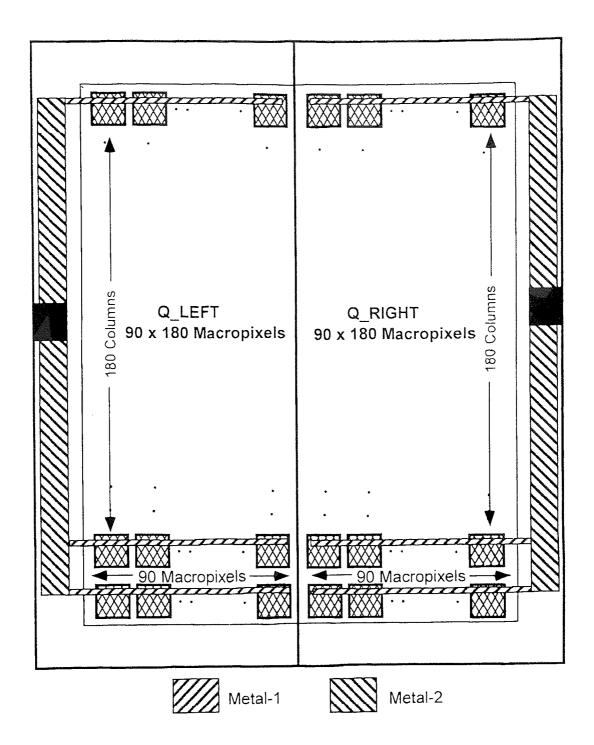

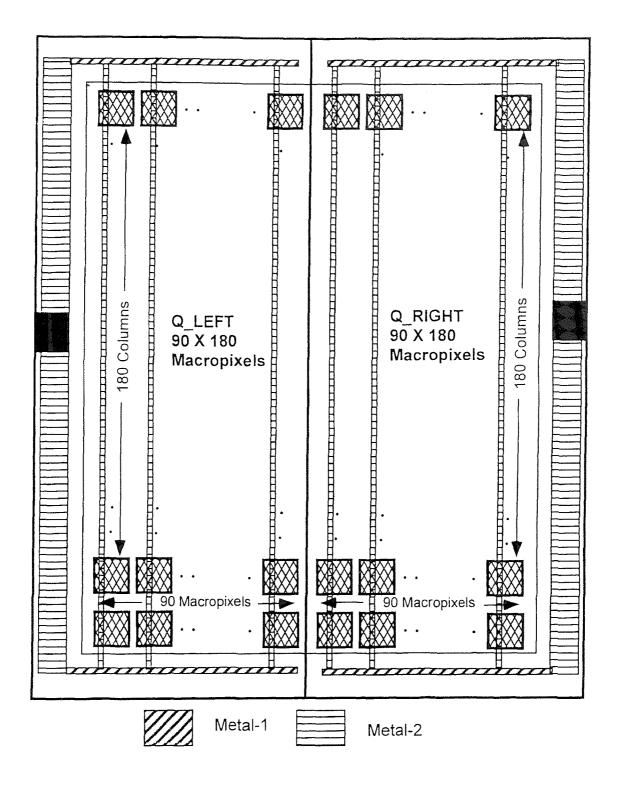

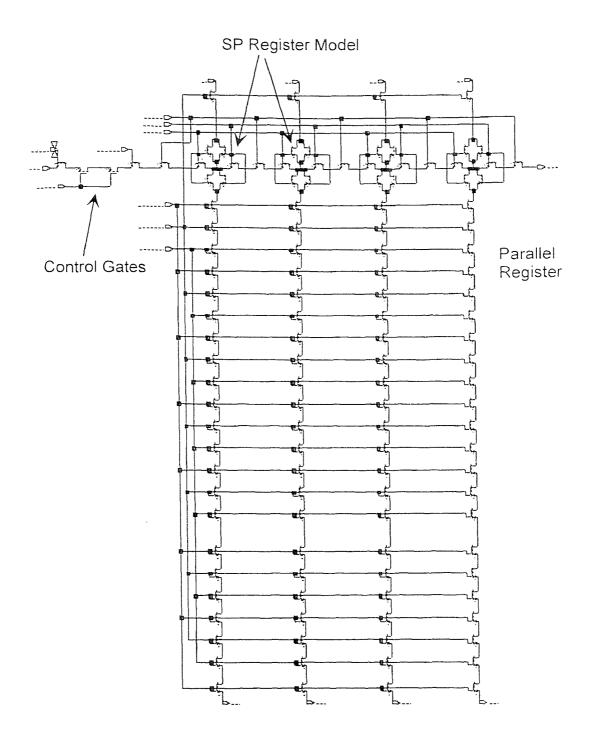

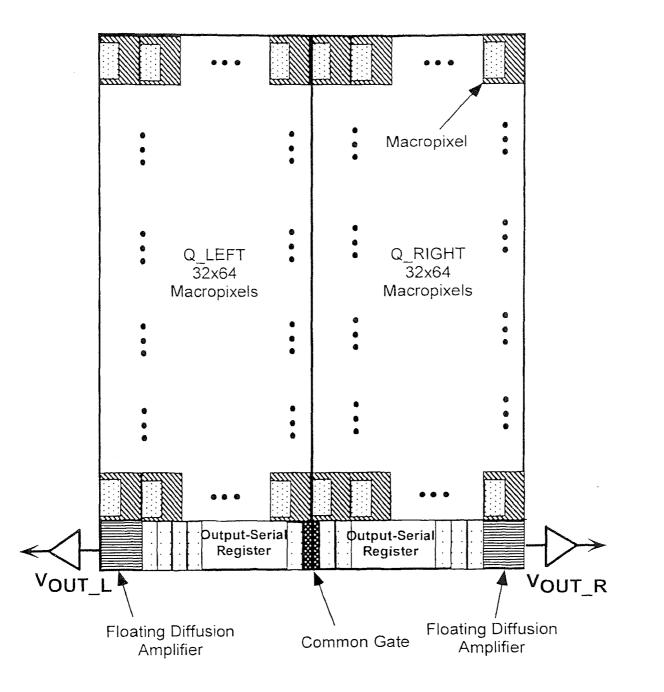

The general block diagram of the  $180 \times 180$ -element UHFR-I burst imager is shown in Figure 3.1. The chip size is approximately  $19.2 \times 19.2 \text{ mm}^2$ . Due to the large chip size, the imager was divided into two halves, (Q\_Left and Q\_Right) to improve the yield as these two halves could also be operated completely independent of each other. Each half consists of 90 x 180 macropixels, output serial register, and floating-diffusion and on-chip amplifier.

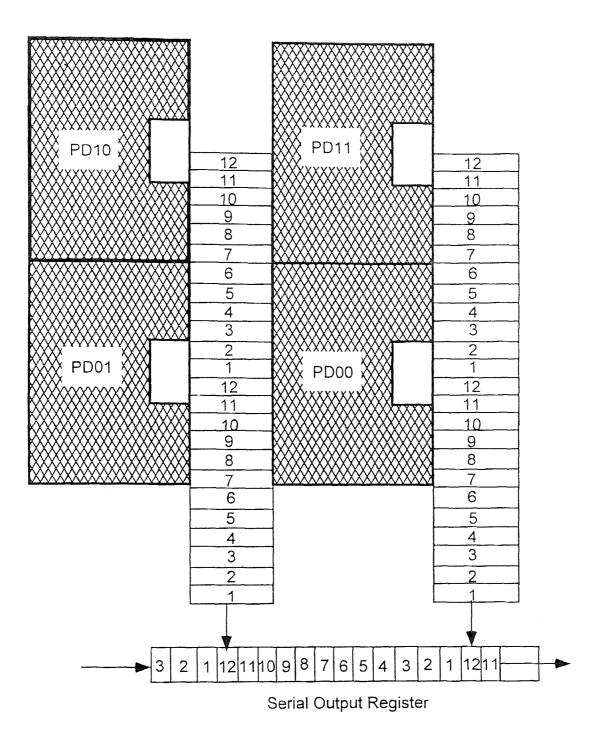

As shown in the block diagram, two halves of the imager have separate outputs and can be operated independently. The integrated frames can be reconstructed with these two outputs outside the chip. There is a common gate, which acts as a separator to two output serial registers. It is also possible to move the charge in only one direction, either left or right by applying high DC bias on common gate and appropriate clocking of serial registers. If one of the output amplifiers does not function properly, this feature of the chip allows both halves to be readout using the other output amplifier; thus further improving the yield. Each macropixel consists of a photodetector and 32 storage elements. The photodetector generates the charge, which is moved to macropixel memory at a very high speed. This operation is similar to inter-line-transfer imagers. Once the new image acquisition is stopped, imager operates as a frame transfer imager and charge moves to output serial register line-by-line. Output serial register moves the charge to floating diffusion pixel-by-pixel at a slow speed to improve signal to noise ratio, as bandwidth of the floating diffusion amplifier is limited. The operation of the imager is described in more detail in subsequent sections. Figure 3.2 illustrates the basic operation of this imager by showing charge movement in 2×2 macropixel in combination of output serial register and amplifier.

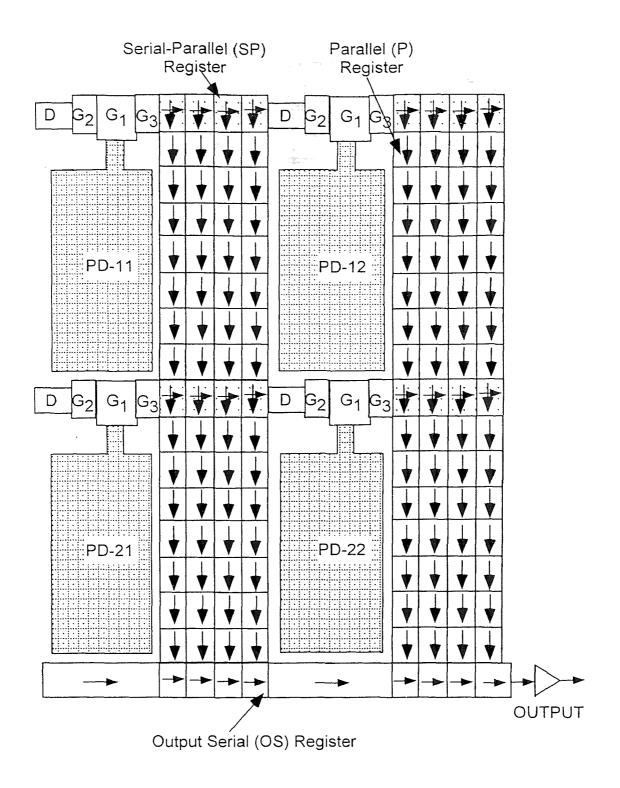

### 3.2.3 Pixel Design

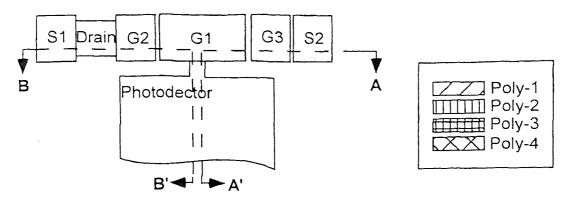

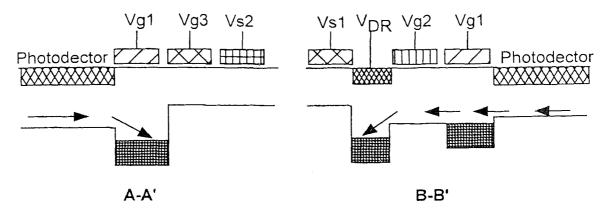

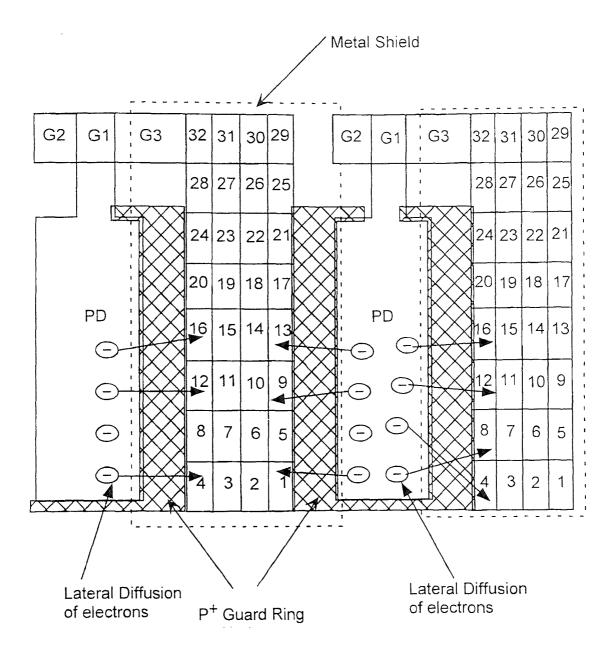

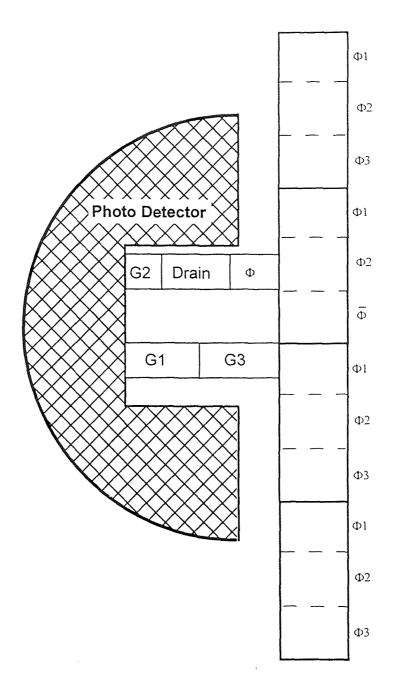

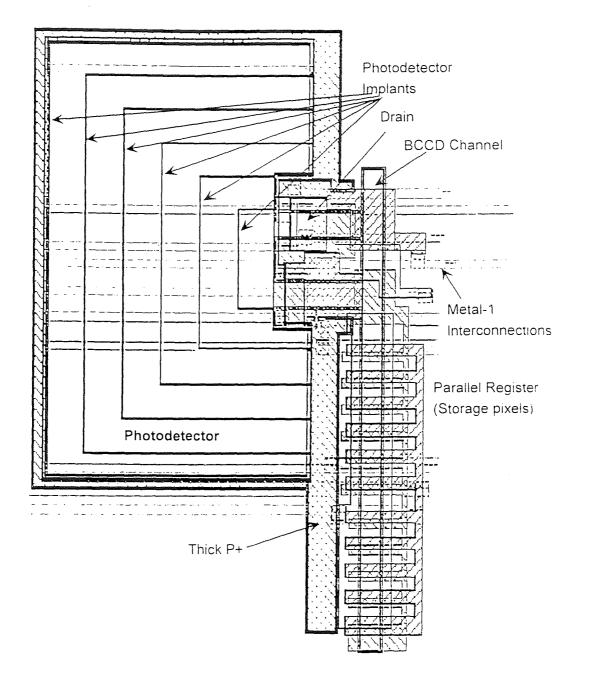

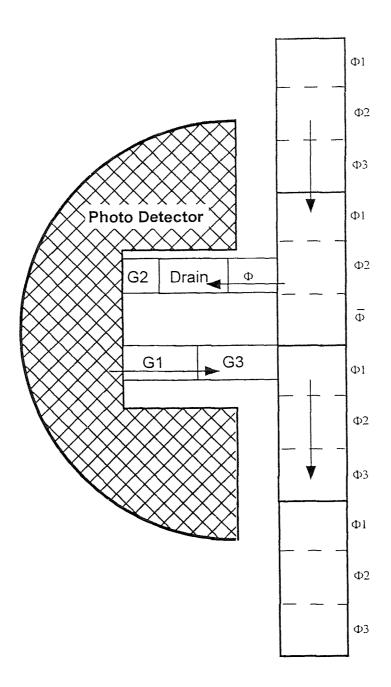

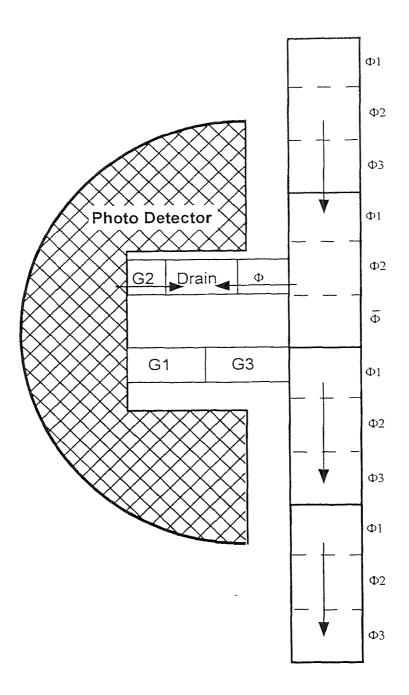

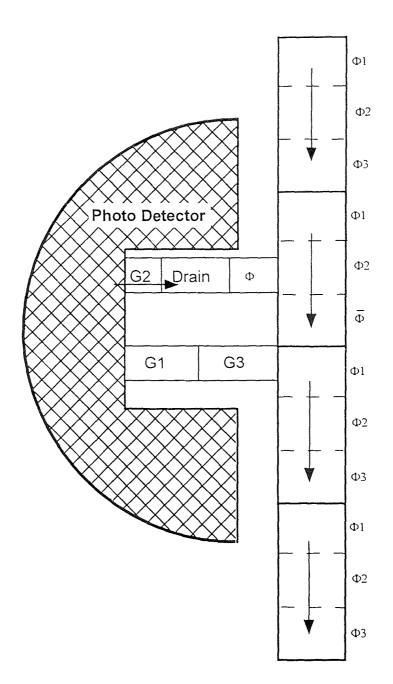

Figure 3.3 shows a schematic diagram of two macropixels. Each macropixel has a dimension of 92.2  $\mu$ m × 92.2  $\mu$ m. A macropixel consists of a photodetector PD, a charge collection gate G1, antiblooming gate G2, a drain D, charge transfer gate G3, and a storage of 32 pixel elements in the form of an array of 4×8 pixels. The first row of 4 pixels is also called serial-parallel (SP) register.

The photodetector is designed to be of 45-µm wide and 71-µm long. This design achieves a fill factor (i.e., ratio of the light sensitive area to the total area of the macropixel) of 37%. The drain D (n<sup>+</sup> diffusion) is used for control of blooming (i.e., to drain excessive charge above the saturation signal from the PD) during the integration time under the control of gate G2. During the normal frame acquisition mode, gate G1 is biased high to collect electrons generated in PD. At the end of the integration time, charge is moved from G1 to SP register via gate G3. Once the SP register is full, charge is moved to the next row of the memory. This process continues till all the 32 memory pixels are full. The drain D is also used to dump excess frames from SP register of the adjacent macropixel. Using this strategy, the imager is able to continuously store last integrated 32 frames and all previously stored frames get dumped into the macropixel drains as new frames get stored. Thus, when frame acquisition is stopped, latest 32 frames are available in macropixels memory.

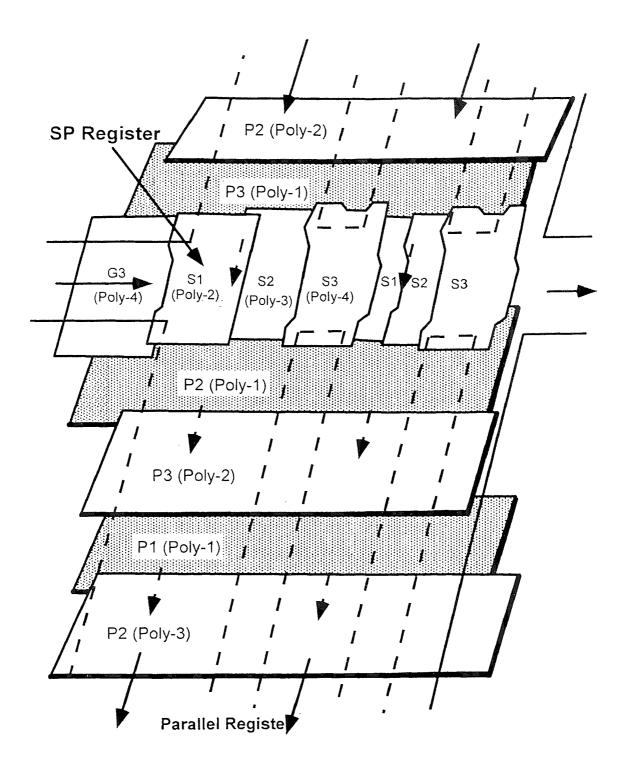

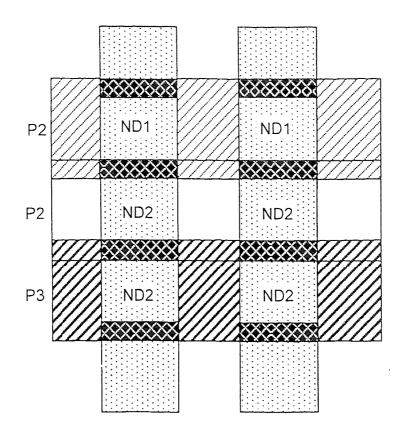

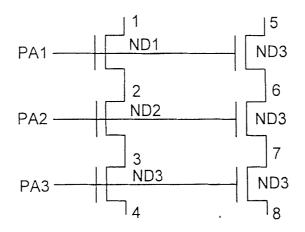

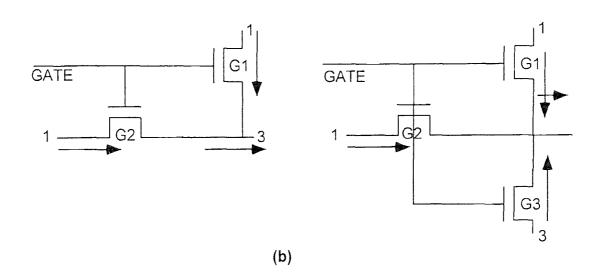

To achieve an area-efficient layout, the design of the 3-phase CCD SP register uses four levels of polysilicon. This is due to the fact that during serial transfer, SP register needs to be isolated from surrounding memory arrays and during parallel transfer, it needs to be isolated from gate G3. This could be most efficiently performed using four levels of polysilicon as shown in Figure 3.4.

The SP register phases S1, S2, and S3 are designed using poly-2, poly-3, and poly-4, respectively. During the parallel transfer, the charge is transferred in P register, phase S3 (poly-4) acts as the induced channel stop and phases S1 and S2 are clocked as phase P1 of the P register. During the horizontal transfer, phases P2 and P3 (poly-1) act as induced channel stop.

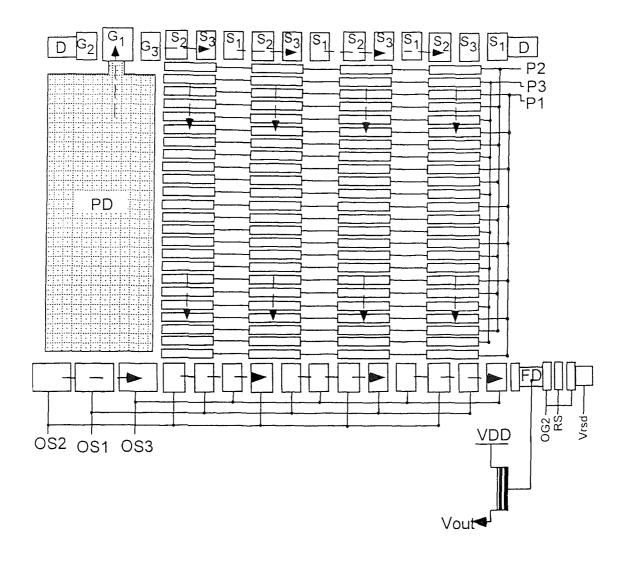

### 3.2.4 Output Serial Register Design

Output serial (OS) register is a 3-phase CCD structure, which allows the transfer of charge signal from  $90 \times 180$ -macropixel array towards a single output amplifier. Transferring in one line of information at a time and moving the charge towards the output amplifier pixel by pixel performs this operation. Figure 3.5 shows a schematic diagram of OS register along with a macropixel and output amplifier. The OS register was also designed with four levels of polysilicon, as is operationally similar to the SP register. During the vertical transfer, OS3 (poly-4) acts as induced channel stop. During horizontal transfer, phase P1 (poly-1) acts as induced channel stop.

## 3.2.5 Output Amplifier Design

Output amplifier is one of the most critical sections in a CCD imager design as its performance greatly affects the overall CCD performance. The two important parameters associated with output amplifier design are output amplifier noise and output amplifier sensitivity. Figure 3.6 is the schematic diagram of the output stage used in this UHFR-I imager. OS1 and OS3 are OS phases, OG1 and OG2 are the output control gates, RS is the reset gate,  $V_{rsd}$  is the reset drain voltage and  $V_{out}$  is the signal output voltage.

During normal operation, the output control gate OG1 is biased to a DC voltage, the output signals are periodically clocked out to the floating diffusion (FD) by controlling the voltage of OS3 to be higher and lower than OG1 bias. The clocked out signal is sensed at the FD and pre-amplified by the on-chip source follower and Vout is sampled by off-chip correlated double sampling circuitry. The FD is reset to a known voltage after each charge sampled by the reset gate RS.

### **Output Amplifier Noise**

The output stage is used to convert the charge electrons into a voltage and to buffer the output voltage towards the outside world. It also adds some uncertainty to the signals in the form of noise electrons. The overall noise from the output amplifier can be split up into various elements depending on the mechanism by which it is generated. The noise characteristics of the output stage can be separated into thermal noise, reset noise, and 1/f noise.

Inherent to the reset action of the floating-diffusion capacitance is an uncertainty about the voltage on the capacitor  $C_{FD}$ . The uncertainty or reset noise can be quantified and is equal to  $kTC_{FD}$ . The only way to deal with the reset noise is to "measure" its value and compensate for it off chip. This is done using a method known as Correlated-Double Sampling (CDS)<sup>5</sup>. The output signal of the CCD is sampled twice; once for its reset level and once for its actual signal output. One of these samples is subtracted from the other, the video signal remains, and the reset noise is canceled out. An additional component in the reset noise is the channel layer charge underneath the gate of the amplifier transistor. When the transistor is turned off, this charge has to be directed to either FD or reset drain to diminish the inversion layer. This uncertainty causes some extra voltage fluctuation from one reset operation to the other<sup>11</sup>.

#### **Output Amplifier Sensitivity**

Apart from the noise of the output amplifier, the conversion factor or sensitivity, which is expressed as  $\mu$ V/electron is a very important parameter. A large conversion factor

prevents extra signal-to-noise reduction caused by peripheral signal processing circuits. Dumping the electrons on a floating-diffusion capacitor and subsequently sensing them by means of on chip source follower performs the conversion of charge into voltage. The sensitivity is primarily determined by the value of the floating-diffusion capacitance in parallel with the parasitic capacitances associated with the source follower gate and the metal buses.

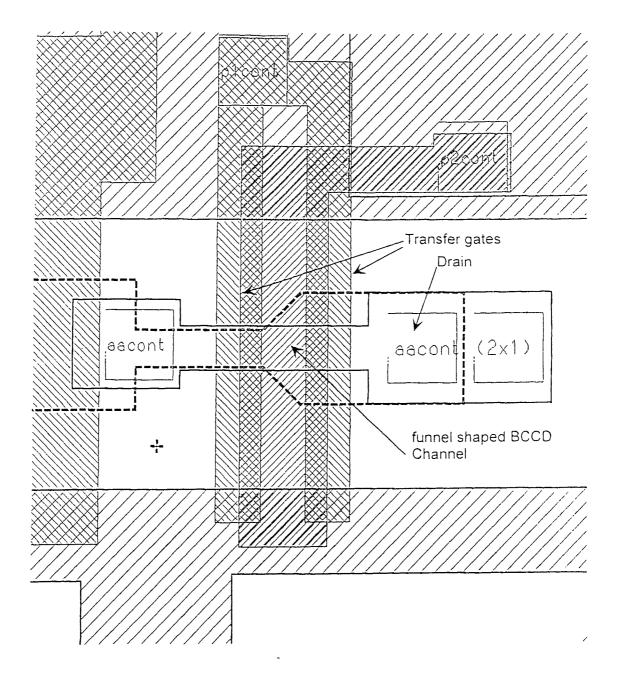

There are a number of techniques used in the design and layout of the output stage of UHFR-I imager to minimize noise and improve sensitivity. To reduce the clock pick up and readout noise at FD, the reset is achieved by keeping the gate OG2 at a DC bias and periodically resetting the FD by a minimum length gate RS. The gate OG2 shields the reset transistor from the floating-diffusion and drastically reduces the clock feed-through from RS on  $C_{FD}$ . The partitioning noise is minimized by an appropriate design of the reset transistor BCCD channel as funnel-shaped as shown in Figure 3.7. In this configuration, the narrow-channel effect pushes the electrons out of the inversion channel towards the reset-drain side during the switching-off of the reset transistor and thus reduces the partitioning noise on the floating-diffusion. The capacitance of the FD and parasitic capacitances have also been minimized by various layout techniques and optimized design achieved by using thick oxide (field oxide) around the critical areas to improve the sensitivity.

## 3.3 Process for UHFR-I Burst Image Sensor

#### 3.3.1 Process Technology

The UHFR-I burst-image sensors were fabricated by Sarnoff using a 1.5  $\mu$ m three-phase buried-channel CCD technology with four level polysilicon and three levels of aluminum. As described in sections 4.2.4 and 4.2.5, the use of fourth level of polysilicon facilitates a more efficient design and operation of serial-parallel register at macropixel and output serial register. Two levels of aluminum were used for metal interconnection and the third level of aluminum was used as an optical shield to cover the CCD pixel area. Also, SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub> channel dielectrics were used to improve the charge transfer efficiency and possibly yield.

Arsenic and phosphorus dual-implantation was used to form the BCCD channels on a p-type substrate to maximize the charge handling capacity and to achieve high fringing field for low transfer losses<sup>11</sup>. Since arsenic has a small diffusion coefficient, majority of the implanted arsenic will stay near the Si/SiO<sub>2</sub> interface and form a high concentration n-type layer. The arsenic contributes to the larger charge handling capacity of the BCCD well. On the other hand, phosphorus has a large diffusion coefficient, therefore, the implanted phosphorus forms a deep diffusion responsible for large fringing field which improves charge transfer efficiency. A modified form of pinned-buried detector was used as high-speed photodetector<sup>12</sup> at each macropixel using a thin p<sup>+</sup> implant, the BCCD implant, and three additional n-type implants to achieve less than 0.1 usec readout time.

## 3.3.2 Process Specifications

The process specifications for fabrication of the UHFR-I burst-image sensor are summarized below:

- The UHFR-I burst image sensors were fabricated using nominally 17.5-μm thick ptype epi wafer with resistivity of 43 ohm-cm on <100> CZ p<sup>+</sup> substrate with resistivity in the range of 0.008 to 0.025 ohm-cm.

- Four levels of polysilicon are used for BCCD gates.

- Three levels of metal, of which two metal levels are used for interconnections and one for optical shield of the BCCD region excluding the photo sensitive (detector) region.

- A dual dielectric of  $SiO_2/Si_3N_4$  is used.

- BCCD implants consisting of phosphorus and arsenic.

- The channel stops for BCCD channels have been defined by SCCD regions in the form of the p-type substrate without the BCCD implant.

- The pinned-buried graded photodetector was constructed by BCCD implant with three additional n-type implants and a top thin p<sup>+</sup> implant.

- The n<sup>+</sup> diffusions for blooming/dumping drain and source drains are defined by polysilicon gates surrounding the diffusion area.

- As a general design/layout procedure, the pinned-buried photodetector, the output amplifiers, and whenever possible the outside perimeter of the burst-image sensor were surrounded by a P<sup>+</sup> field implant.

#### 3.3.3 Fabrication Sequence

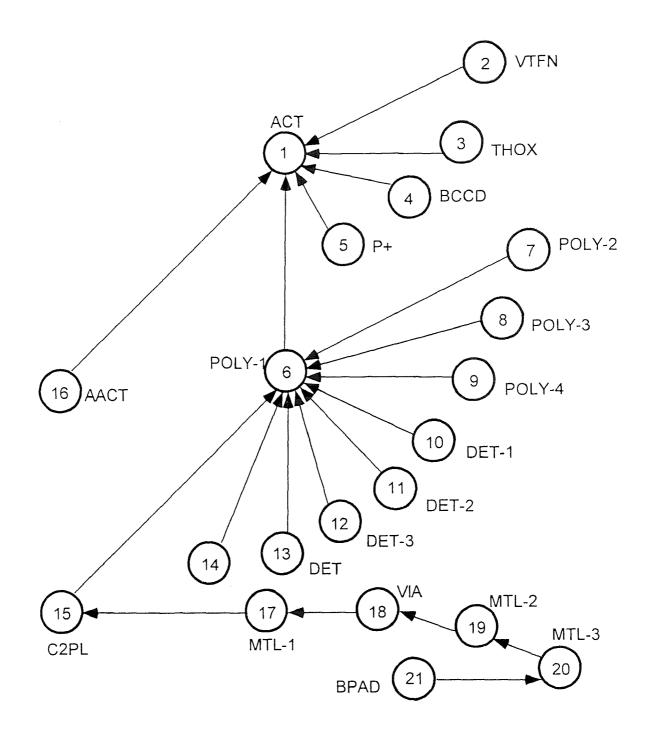

The process for fabrication of the UHFR-I burst image sensor includes four levels of polysilicon, three levels of metal, eight implants, and requires a total of 21 mask levels.

- Mask level 1: ACT, defining the active area;

- Mask level 2: VTFN, p-type implant below the recessed thick oxide;

- Mask level 3: THOX, defining the thick oxide;

- Mask level 4: BCCD, BCCD implants;

- Mask level 5:  $p^+$  field implant surrounding the photodetector, output amplifiers, and the imager perimeter;

- Mask level 6: POLY-1, BCCD polysilicon-1 gates and output source follower MOSFET gates;

- Mask level 7: POLY-2, BCCD polysilicon-2 gates;

- Mask level 8: POLY-3, BCCD polysilicon-3 gates;

- Mask level 9: POLY-4, BCCD polysilicon-4 gates;

- Mask level 10: DET-1, first photodetector additional n-type implant, covering the whole photodetector region;

- Mask level 11: DET-2, second photodetector additional n-type implant, forming the first potential step in photodetector;

- Mask level 12: DET-3, third photodetector additional n-type implant, forming the second potential step in photodetector;

- Mask level 13: DET, photodetector  $p^+$  implant, forming the pinned-buried BCCD channel photodetector;

- Mask level 14:  $N^+$ , source and drain  $N^+$  implants;

- Mask level 15: C2PL, defining contacts from metal-1 to polysilicon gates;

- Mask level 16: AACT, active area contacts, including contacts to source and drain, as well as to the substrate;

- Mask level 17: MTL-1, metal-1 interconnection lines;

- Mask level 18: VIA, VIAs between metal-1 and metal-2;

- Mask level 19: MTL-2, metal-2 interconnection lines;

- Mask level 20: MTL-3, metal-3 optical shield; and

- Mask level 21: BPAD, bonding pads.

The alignment of the 21 mask levels and fabrication sequence of the UHFR-I imager are illustrated in Figure 3.8, where the mask levels are denoted by the mask names described above, and the process sequence is given by number from 1 to 21.

### 3.4 Operation of UHFR-I Imager

### 3.4.1 Photodetector Readout

Figure 3.9 shows the photodetector and surrounding control gates of a macropixel in different states. Figure 3.9(a) shows the schematic diagram of the photodetector and surrounding control gates. Figure 3.9(b) shows the charge integration mode in which charge collecting gate G1 acts as a sink for the photodetector charge. If the generated charge is higher than the maximum charge handling capacity of the smallest BCCD storage element, the extra charge is dumped into the drain under the control of gate G2, the blooming gate. This ensures that the maximum charge collected under the gate G1 is not higher than the maximum charge, which can be stored at macropixel memory.

A periodical transfer of the charge from gate G1 to gate G3, and eventually to SP register phase S2 performs the readout of the collected charge signal. During this operation, gate G2 acts as a barrier to prevent charge transfer from G1 to drain as illustrated in Figure 3.9(c). The drain shown in Figure 3.9 is also used by the adjacent left macropixel to dump the extra signal charge when its all-32 memory pixels are full. This operation allows all the macropixels to retain latest 32 signal samples with all previous samples discarded into the drain. This charge dumping is illustrated along the B-B' line in Figures 3.9(b) and (c). As the serial clock S1 is turned on, the charge signals clocked out by the SP register of the macropixels move into the adjacent drain.

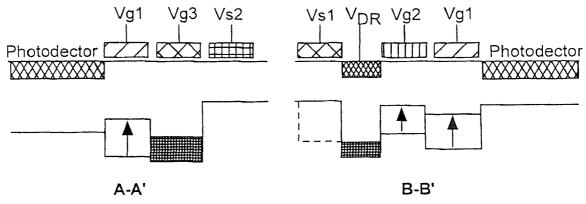

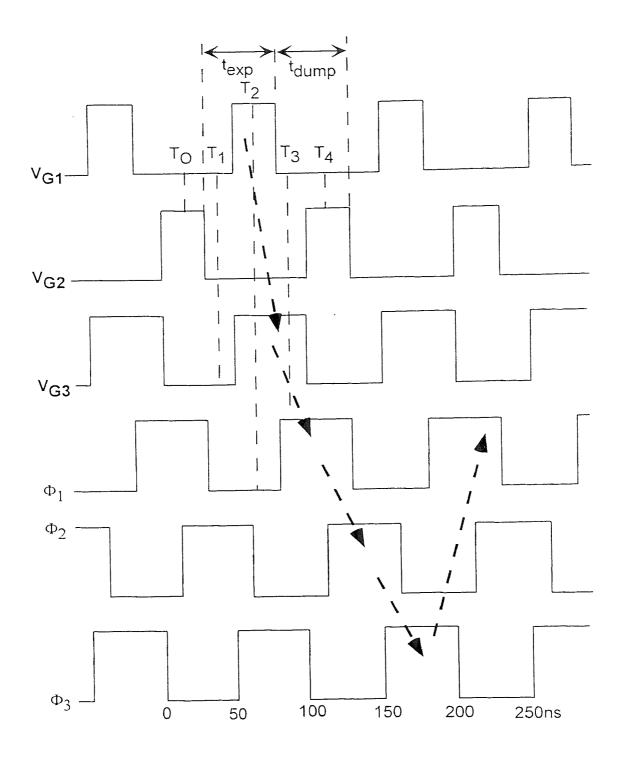

## 3.4.2 Frame Integration and Readout

During frame integration mode, imager can continuously capture images at the maximum speed of  $2 \times 10^6$  frames/sec and stores the last 32 frames at its macropixel memory locations. As the new frames are acquired, previously integrated frame charges are continuously drained in the on chip drain thus macropixel always stores the latest 32 frame signal. By virtue of the architecture of the macropixel, transfer of the first frame each time after row above SP register is full, is the most critical operation from speed point of view. This operation requires a parallel to serial transfer which is illustrated in Figure 3.10. During this operation, when the last row of signal from the upper pixel is transferred to SP register under S1 gates via S3 gates to be eventually dumped in the drain, the new integrated frame signal is entering into SP register via G3 gate. To avoid this bottleneck, these frames, i.e., 1st, 5th, 9th, 13th, 17th, 21st, 25th, and 29th frames could have subframe integration. In this mode, integration time is doubled and gate G2 is

used to empty gate G1 after half of this increased integration time. This ensures that the actual signal integration time remains the same for all frames and overall maximum frame rate could be achieved.

During the frame readout period, the frame acquisitions are stopped and gate G3 acts as a barrier between gate G1 and SP register. The entire new signal collected under gate G1 from photodetector is directly dumped into the drain. The SP register acts as one of the parallel phases and imager gets reconfigured as a large frame-transfer type imager. Signal gets transferred line by line into OS register and from OS register, and moves pixel by pixel towards output amplifier to be readout. This operation could be performed at a slow rate to improve the transfer efficiency.

### 3.5 Experimental Setup and Results

Following the completion of the design and simulation (described in Chapter 4 and 5) of the UHFR-I Imager and based on the process described in this chapter, a wafer lot was fabricated at the Sarnoff Corporation. After the successful completion of this lot, the operation of this imager was demonstrated at the Princeton Scientific Instruments (PSI), Inc. using camera electronics developed by PSI. The author led the test team and obtained the experimental data for UHFR-I imager as well as some earlier test devices and are described in this section.

## Test Setup and experimental results

The test setup developed by PSI for UHFR-I Imager demonstration used an optical test pattern, which is illuminated by a sequence LED pulses. The imager chip is cooled to -

30° C to minimize the dark current. The required control clocks for the imager as well as LED is controlled by programmable hardware/software. This set-up allows to change frame rate, voltage levels on various phases, LED ON time, and readout speed. The output of the imager is readout by an external dual-slope correlated-double sampling electronics to eliminate the reset noise. After the analog-to-digital conversion, the acquired data is stored in the host computer. The host computer does all the processing required in reformatting the acquired 32 frames and displays them on a monitor. For the imager readout rate of 120 kHz, the total readout time is about 8 seconds. An optical shutter is used to eliminate the optical smear during this readout time. The switching time of the shutter is about 20 msec. The experimental results obtained are summarized in the following table. The test results of this imager have met all of the design specifications.

| Maximum Frame Rate                  | $>2 \times 10^6$ frames /sec                  |

|-------------------------------------|-----------------------------------------------|

| Resolution                          | 180 x 180                                     |

| Frame Storage Memory                | 32 Frames                                     |

| Pixel pitch                         | 92.2 μm                                       |

| Fill Factor                         | 38 %                                          |

| Saturation Signal, Q <sub>max</sub> | ~15,000 e-/pxel                               |

| Dynamic Range                       | >2000:1                                       |

| Spectral Response                   | 400 to 900 nm                                 |

| Readout Noise                       | 9 rms e <sup>-</sup> /pixel                   |

| Optical Cross-Talk                  | Atleast 40 times improved over VHFR           |

| CTE                                 | ~2x10 <sup>-5</sup> in Output Serial Register |

| Output Amplifier Char.              | ~2.2 µV/electrons                             |

| Technology                          | 3-phase BCCD, 4-level poly, 3-level           |

|                                     | metal                                         |

| Design Rules                        | 1.5 μm                                        |

**Table 3.2** Experimental Results from UHFR-I Imager

In conclusion, the UHFR-I device can acquire images at a very high frame rate and stores the last 32 of these frames at its on-chip memory locations. Once the new image acquisitions are stopped, the stored frames could be readout at a slower speed. The operation of these devices was demonstrated at 2-million frames/sec speed and experimental results are described in this chapter. Next chapter discusses the various design techniques used to optimize the imager for its high-speed operation.

#### CHAPTER 4

## FRAME RATE OPTIMIZATION AND DESIGN VERIFICATION

### 4.1 Introduction

This chapter describes the full custom design methodology used for layout design of the UHFR-I imager chip. Large chip size (19.2 mm  $\times$  19.2 mm) and the specification of extremely high frame rate (2  $\times$  10<sup>6</sup> frames/sec) makes the layout and verification task extremely complex. At present, there is no in-built verification support available on electronic design automation (EDA) tools for CCD devices as all these tools are primarily developed for analog and digital CMOS design verification. Special techniques to verify layout against schematic were developed for CCD chips as part of this research and are described in this chapter.

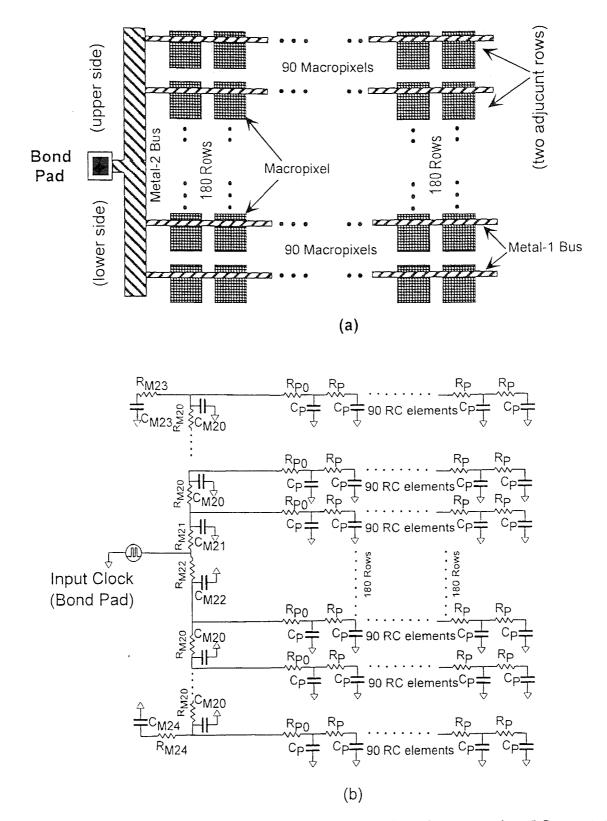

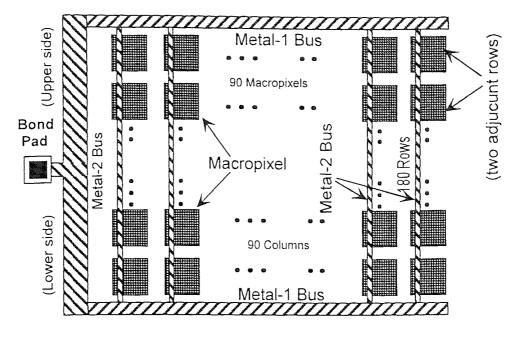

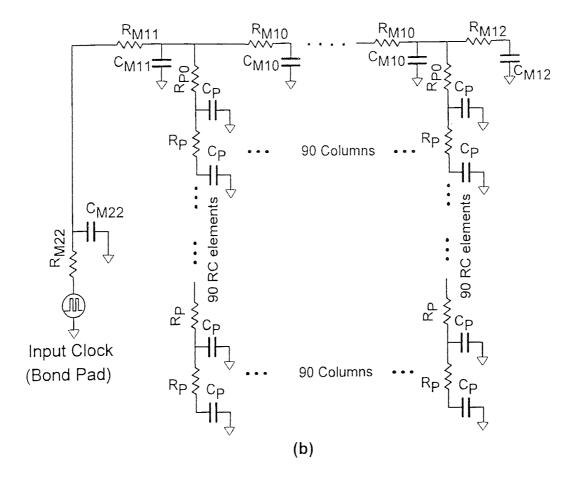

The RC time constants of different CCD phases are extremely critical in achieving  $2 \times 10^6$  frame rate. These time constants were optimized using full custom layout methodology. Two metal layers were used for interconnection purpose to give more freedom in routing and minimizing RC time constants. The  $180 \times 180$ -element UHFR-I chip has a 32-pixel memory at each macropixel, and hence the total number of pixels for the imager is 1.0368 million. Since a 3-phase BCCD technology was used, the chip has 3.11 million poly gates. To ensure that layout corresponds to the conceptually drawn schematic, automated layout versus schematic (LVS) verification tools were used. Mentor Graphics V 8.2\_5 IC design tools running on SUN Sparc 10 machine were used for this chip layout. Detailed RC delay timing analysis was performed using SPICE simulation models to ascertain target frame rate of  $2 \times 10^6$  frames/sec.

To have a systematic approach for interconnection of this complex chip, metal-1 is used for horizontal interconnection and metal-2 is used for vertical interconnection. Critical phases of this chip were separated from non-critical phases to minimize RC delay of critical phases using various layout techniques.

### 4.2.1 Macropixel Interconnection