New Jersey Institute of Technology Digital Commons @ NJIT

Theses

**Electronic Theses and Dissertations**

Spring 5-31-2000

# Programmable latching probe microstructures for wafer testing applications

Salima Taifa Sadeq New Jersey Institute of Technology

Follow this and additional works at: https://digitalcommons.njit.edu/theses

Part of the Electrical and Electronics Commons

#### **Recommended Citation**

Sadeq, Salima Taifa, "Programmable latching probe microstructures for wafer testing applications" (2000). *Theses*. 760. https://digitalcommons.njit.edu/theses/760

This Thesis is brought to you for free and open access by the Electronic Theses and Dissertations at Digital Commons @ NJIT. It has been accepted for inclusion in Theses by an authorized administrator of Digital Commons @ NJIT. For more information, please contact digitalcommons@njit.edu.

# **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

#### ABSTRACT

#### PROGRAMMABLE LATCHING PROBE MICROSTRUCTURE FOR WAFER TESTING APPLICATIONS

#### by Salmina Taifa Sadeq

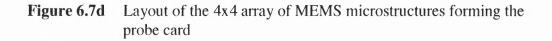

The objective of this thesis is to design a programmable wafer testing array on a single chip based on micro electromechanical systems (MEMS) and VLSI. The wafer-scale integration in this thesis is a programmable array of test probes that are used for engineering test of VLSI and ULSI silicon integrated circuits at the wafer level. This consists of two subsystems (1) the VLSI address circuits used for addressing and controlling the MEMS on the chip and (2) the latching probe MEMS microstructure array that actuates into position for testing VLSI wafers. Each of the subsystems have been designed, analyzed and simulated separately. These structures were then integrated into a demonstration 4x4 array forming a programmable probe card. A 3-micrometer critical dimension is used for both the VLSI CMOS and the MEMS physical design layouts. The fabrication technique for the MEMS microstructure is detailed. A standard 12-mask CMOS technology is used for the fabrication of the address circuits.

## PROGRAMMABLE LATCHING PROBE MICROSTRUCTURES FOR WAFER TESTING APPLICATIONS

by Salmina Taifa Sadeq

A Master's Thesis Submitted to the Faculty of New Jersey Institute of Technology in Partial Fulfillment of the Requirements for the Degree of Master of Science in Electrical Engineering

**Department of Electrical and Computer Engineering**

May 2000

#### **APPROVAL PAGE**

#### **PROGRAMMABLE LATCHING PROBE MICROSTRUCTURES FOR** FOR WAFER TESTING APPLICATIONS

#### Salmina Taifa Sadeq

Dr. William N. Carr, Thesis Advisor Professor of Electrical and Computer Engineering, NJIT Professor of Physics, NJIT

Dr. Roy H. Cornely, Committee Member Professor of Electrical and Computer Engineering, NJIT

Dr. Edip Niver, Committee Member Associate Professor of Electrical and Computer Engineering, NJIT Date

Date

Date

#### **BIOGRAPHICAL SKETCH**

Author: Salmina Taifa Sadeq

**Degree:** Master of Science in Electrical Engineering

**Date:** May, 2000

#### **Undergraduate and Graduate Education:**

- Master of Science in Electrical Engineering, New Jersey Institute of Technology, Newark, NJ, 2000

- Bachelor of Science in Electrical Engineering, Purdue University, West Lafayette, IN, 1995

Major: Electrical Engineering

This thesis is dedicated to my dear parents, my husband and my daughter Sabriya

.

#### ACKNOWLEDGMENT

I would like to express my sincere gratitude to my advisor, Professor William N. Carr for his valuable support and guidance through the entire course of this thesis. He has given me an opportunity to work him and has introduced me to the world of MEMS. I would also like to thank Professor Roy Cornely and Professor Edip Niver for taking the time to review this thesis and for their suggestions.

I would like to thank my husband Muhammad Ashraful Alam for his support and understanding. My father Mr. Sadequr Rahman has guided me throughout my academic years and takes an active interest in my education even today. And my mother Mrs. Fatema Sadeq has gently encouraged and supported me in every walk of my life. I am forever indebted and grateful to them.

Last, but certainly not the least, I would like to thank my in-laws Mr. and Mrs. Shamsul Alam for their help and care - especially during the last few months of working on this thesis.

| Ch | napter Pa                                                             | ige |

|----|-----------------------------------------------------------------------|-----|

| 1  | INTRODUCTION                                                          | 1   |

| 2  | BACKGROUND INFORMATION                                                | 3   |

|    | 2.1 Summary of Current Wafer Probe Systems                            | 3   |

|    | 2.2 Summary of Marcus-Carr Patent                                     | 4   |

| 3  | DESCRIPTION OF THE NEW SYSTEM                                         | 8   |

|    | 3.1 The System Architecture                                           | 8   |

|    | 3.2 Block Diagram of the System Architecture                          | 9   |

|    | 3.3 Overall Design Strategy and Consideration                         | 10  |

| 4  | DESIGN AND SIMULATION OF MEMS LATCHING PROBE<br>MICROSTRUCTURES       | 11  |

|    | 4.1 Brief Description of Latching Probe Microstructure                | 11  |

|    | 4.1.1 Description of Components                                       | 12  |

|    | 4.1.2 Operation of the Microstructure                                 | 13  |

|    | 4.2 Theory and Numerical Analysis of Microprobe Structure             | 17  |

|    | 4.2.1 Theory of Bending of Bi-metal Strip 1                           | 17  |

|    | 4.2.2 A Brief Description of ANSYS Simulation for Bending Calculation | 22  |

|    | 4.2.3 Results and Discussion of ANSYS                                 | 23  |

|    | 4.2.4 Comparison Between ANSYS Results and Simple Analytical Theory2  | 24  |

|    | 4.3 Physical Layout of the Microstructure                             | 26  |

|    | 4.4 Fabrication Technique                                             | 27  |

### **TABLE OF CONTENTS**

| Cł | Chapter Pa |         |                                                    | Page |

|----|------------|---------|----------------------------------------------------|------|

|    | 4.5        | 5 Nume  | rical Analysis                                     | 32   |

|    |            | 4.5.1   | Calculation of Cooling                             | 32   |

|    |            | 4.5.2   | Calculation of Thermal Time Constant               | 35   |

|    |            | 4.5.3   | Calculation of Current and Resistance of Heater    | 37   |

|    | 4.6        | 5 Sumn  | nary and Conclusion                                | 38   |

| 5  |            |         | GN AND SIMULATION OF CMOS ADDRESSING UITS          | 39   |

|    | 5.1        | The Sl  | nift Register                                      | 39   |

|    |            | 5.1.1   | Circuit Schematic and Analysis                     | 39   |

|    |            | 5.1.2   | Simulation using PSPICE                            | 41   |

|    |            | 5.1.3   | Physical Layout of the Shift Register              | 42   |

|    | 5.2        | 2 The D | igital to Analog Converter                         | 44   |

|    |            | 5.2.1   | Circuit Schematic and Analysis                     | 44   |

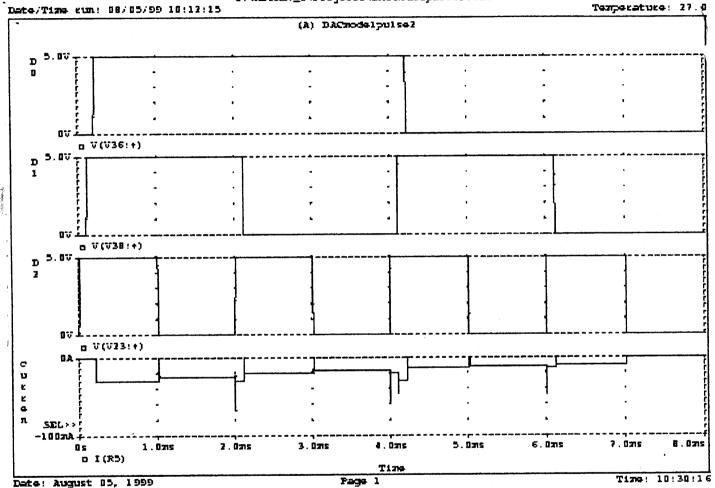

|    |            | 5.2.2   | Simulation using PSPICE                            | 45   |

|    |            | 5.2.3   | Physical Layout of the Digital to Analog Converter | 48   |

|    | 5.3        | Row D   | Driver and Resistor                                | 50   |

|    |            | 5.3.1   | Description of the Circuit                         | 50   |

|    |            | 5.3.2   | Physical Layout of the Row Driver                  | 51   |

#### TABLE OF CONTENTS (Continued)

#### TABLE OF CONTENTS (Continued)

| Cl | hapter Pag                                      | <i>j</i> e |

|----|-------------------------------------------------|------------|

|    | 5.4 Sub-circuit Driving Current in the Pixel    | 53         |

|    | 5.5 Combining Row and Column Address Circuits   | 55         |

|    | 5.5.1 Description of Row Address Circuit        | 56         |

|    | 5.5.2 Description of Column Address Circuit     | 6          |

|    | 5.5.3 Physical Layouts of Combined Cells        | 57         |

|    | 5.6 Summary and Conclusion                      | 60         |

| 6  | THE INTEGRATED CMOS AND MEMS CELL               | 51         |

|    | 6.5 Layout Masks for the CMOS Shift Register    | 51         |

|    | 6.6 Layout Masks for the MEMS Microstructure    | 5          |

|    | 6.7 Integration of CMOS and MEMS Design         | 9          |

|    | 6.8 Summary and Conclusion                      | 85         |

| 7  | SUMMARY AND CONCLUSIONS                         | 6          |

|    | APPENDIX A PSPICE Simulations and Netlist Files | 8          |

|    | APPENDIX B ANSYS Simulation                     | 4          |

|    | APPENDIX C Alternative Theory of Bending        | )5         |

|    | REFERENCES                                      | 9          |

#### LIST OF TABLES

| Table | P                                                                           | age |

|-------|-----------------------------------------------------------------------------|-----|

| 4.1   | Temperature vs deflection of 100µm beam                                     | 23  |

| 4.2   | Temperature vs deflection of 300µm beam                                     | 23  |

| 4.3   | Parameters and their values in theoretical calculation of deflection height | 25  |

| 4.4   | List of masks in the fabrication of the microstructure                      | 29  |

| 5.1   | Simulation results of the sub-circuit                                       | 54  |

#### LIST OF FIGURES

| Figure | Figure Pa                                                                                                  |    |  |

|--------|------------------------------------------------------------------------------------------------------------|----|--|

| 2.1    | Bimorph cantilever proposed by Marcus-Carr patent                                                          | 7  |  |

| 3.1    | Block diagram of 4x4 array of microstructures                                                              | 9  |  |

| 3.2    | Illustration of wafer probing mechanism                                                                    | 9  |  |

| 4.1    | Top view of microstructure                                                                                 | 13 |  |

| 4.2    | Side view of the microstructure                                                                            | 14 |  |

| 4.3    | Steps to latching position                                                                                 | 15 |  |

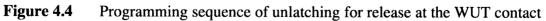

| 4.4    | Steps to unlatching position                                                                               | 16 |  |

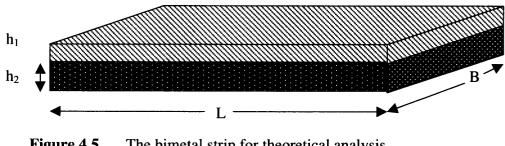

| 4.5    | The bimetal strip for theoretical analysis                                                                 | 17 |  |

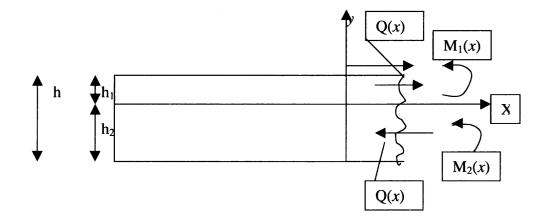

| 4.6    | Forces and moments acting on the bimetal strip                                                             | 19 |  |

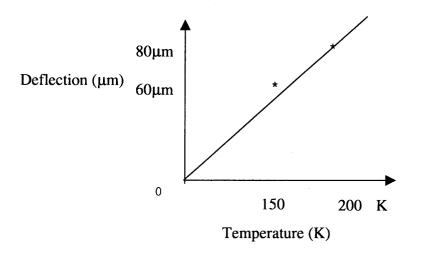

| 4.7    | Illustration of linear relationship between temperature difference and deflection of 300µm long cantilever | 24 |  |

| 4.8    | Layout of the microstructure using L-EDIT                                                                  | 26 |  |

| 4.9    | Graphical illustration of fabrication steps and masks required                                             | 32 |  |

| 4.10   | Block diagram of energy conversion in the system                                                           | 33 |  |

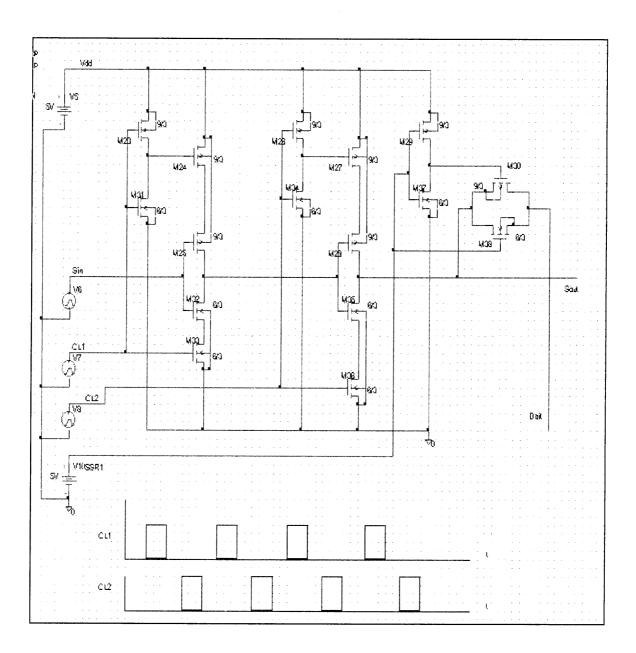

| 5.1    | Schematic of the shift register cell in PSPICE                                                             | 40 |  |

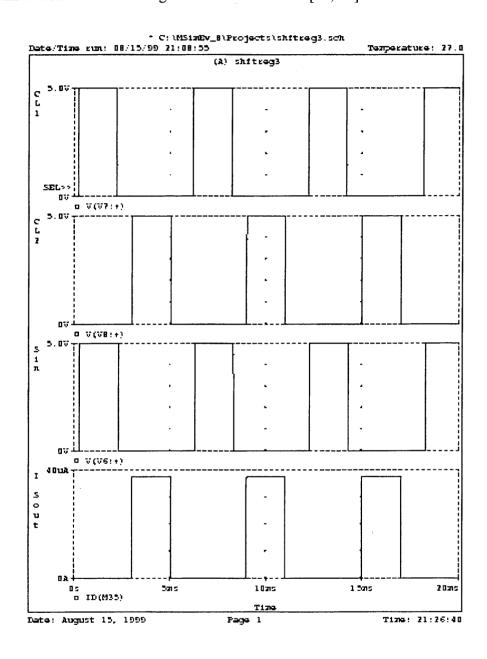

| 5.2    | Simulation of the shift register cell using PSPICE                                                         | 41 |  |

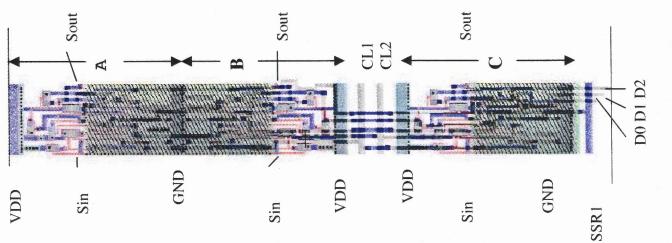

| 5.3    | Physical layout of the 3-bit shift register                                                                | 43 |  |

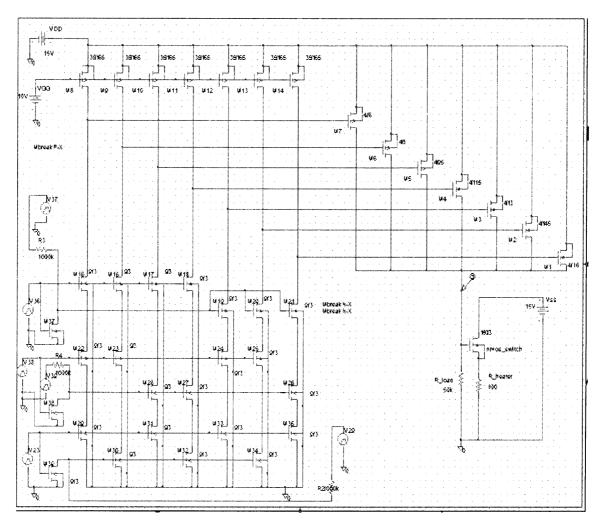

| 5.4    | Schematic of DAC circuit in PSPICE                                                                         | 44 |  |

| 5.5    | Simulation of DAC in PSPICE                                                                                | 46 |  |

| 5.6    | Current in the DAC circuit                                                                                 | 47 |  |

| 5.7    | Layout of the two DAC circuits in L-EDIT. One is the mirror image of other                                 | 49 |  |

| 5.8    | Schematic showing the arrangement of the row address circuit                                               | 50 |  |

#### LIST OF FIGURES (Continued)

| Figure |                                                                          | Page |

|--------|--------------------------------------------------------------------------|------|

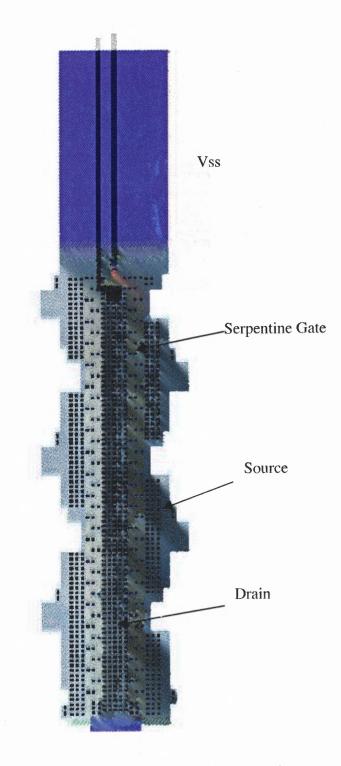

| 5.9    | Layout of PMOS row driver transistor                                     | 52   |

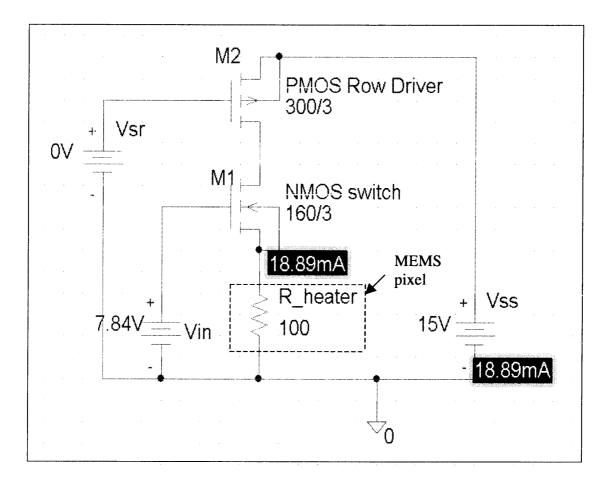

| 5.10   | Schematic of sub-circuit supplying current to pixel heaters              | 53   |

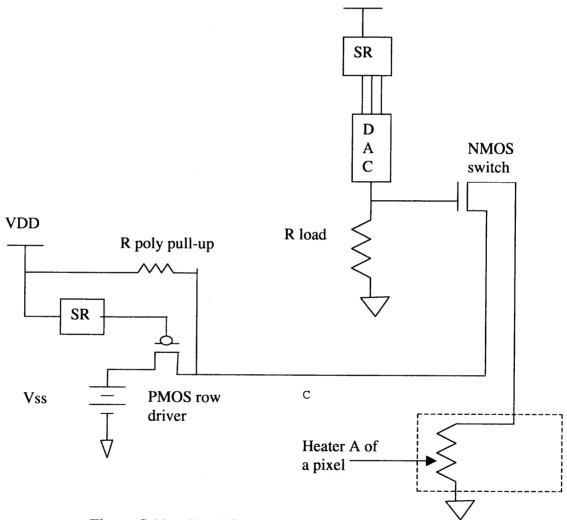

| 5.11   | Simplified circuit schematic of overall design                           | 55   |

| 5.12   | Layout of row address circuit                                            | 58   |

| 5.13   | Layout of two column address circuits, one the mirror image of the other | 59   |

| 6.1    | List of layers in L-EDIT for CMOS circuits                               | 62   |

| 6.2a   | P-well layer for CMOS shift register                                     | 63   |

| 6.2b   | Active layer for CMOS shift register                                     | 64   |

| 6.2c   | N channel field implant layer for CMOS shift register                    | 65   |

| 6.2d   | P channel field implant layer for CMOS shift register                    | 66   |

| 6.2e   | Polysilicon layer for CMOS shift register                                | 67   |

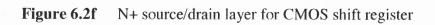

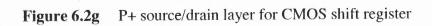

| 6.2f   | N+ source/drain layer for CMOS shift register                            | 68   |

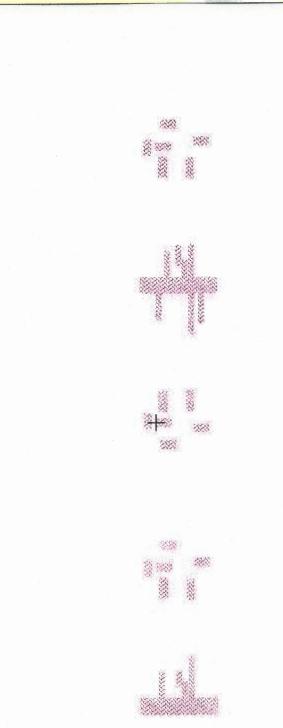

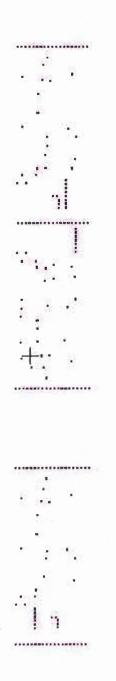

| 6.2g   | P+ source/drain layer for CMOS shift register                            | 69   |

| 6.2h   | Contact layer for CMOS shift register                                    | 70   |

| 6.2i   | Metal1 layer for CMOS shift register                                     | 71   |

| 6.2j   | Via layer for CMOS shift register                                        | 72   |

| 6.2k   | Metal2 layer for CMOS shift register                                     | 73   |

| 6.3    | The composite CMOS shift register                                        | 74   |

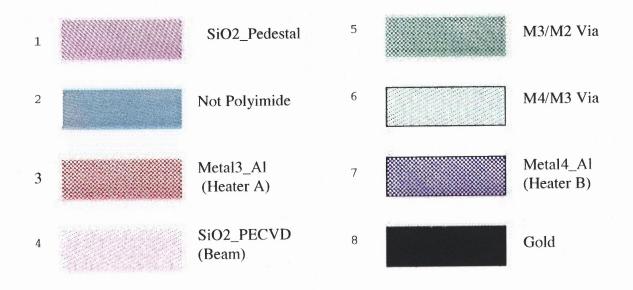

| 6.4    | List of layers in L-EDIT for the layout of the MEMS microstructure       | 75   |

| 6.5a   | SiO2_pedestal layer for the MEMS microstructures                         | 76   |

#### LIST OF FIGURES (Continued)

| Figur       | Figure                                                                          |     |  |

|-------------|---------------------------------------------------------------------------------|-----|--|

| 6.5b        | Polyimide layer for the MEMS microstructures                                    | 76  |  |

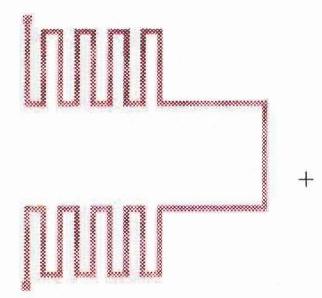

| 6.5c        | Metal3_Al layer for heater A of the MEMS microstructure                         | 77  |  |

| 6.5d        | SiO2_PECVD layer for the beam of the MEMS microstructure                        | 77  |  |

| 6.5e        | Metal4_Al layer for heater B of the MEMS microstructure                         | 78  |  |

| 6.5f        | Gold layer for the probe tip of the MEMS microstructure                         | 78  |  |

| 6.6         | The composite MEMS microstructure                                               | 79  |  |

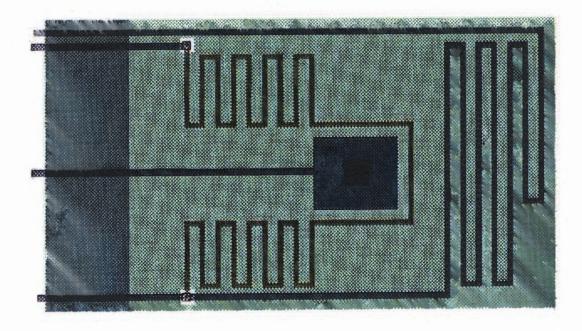

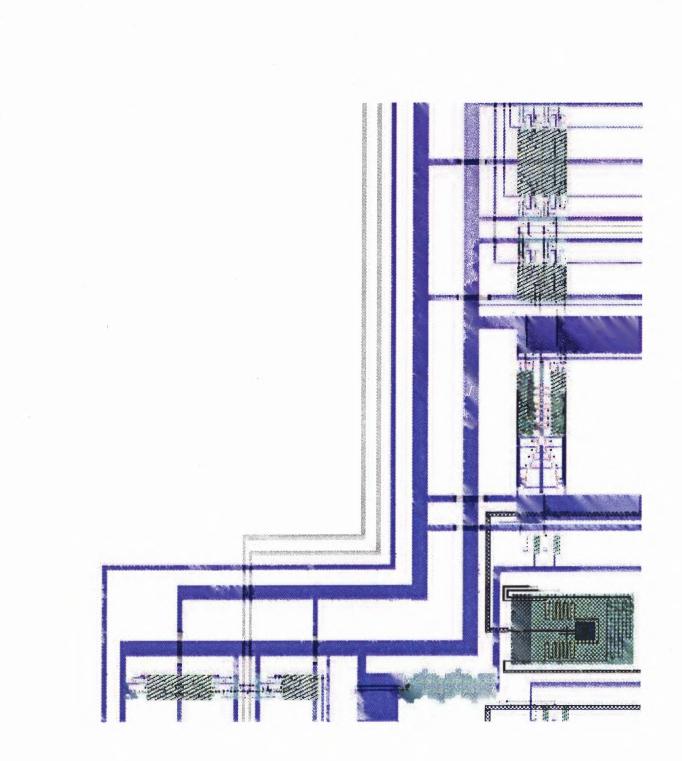

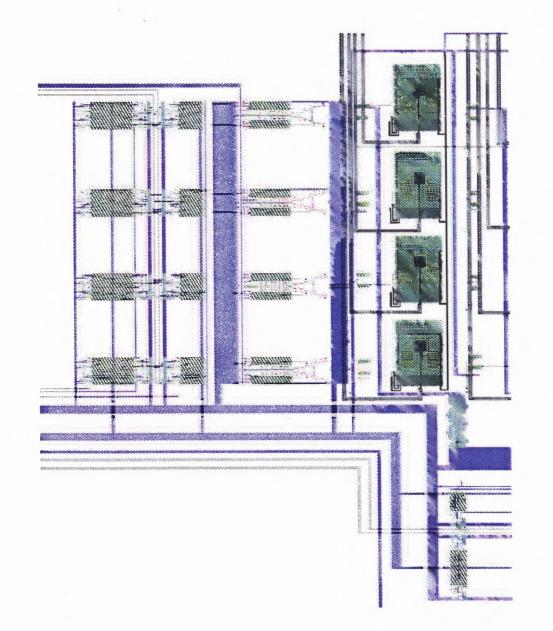

| 6.7a        | Layout of a single MEMS microstructure with its row and column address circuits | 80  |  |

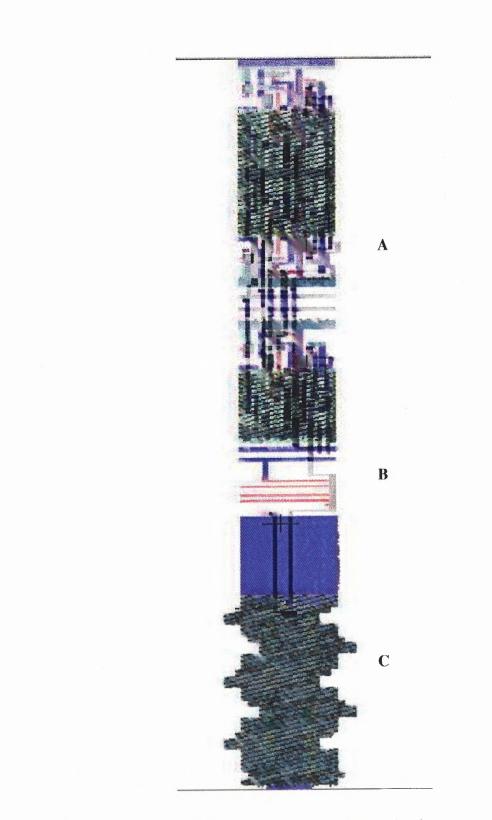

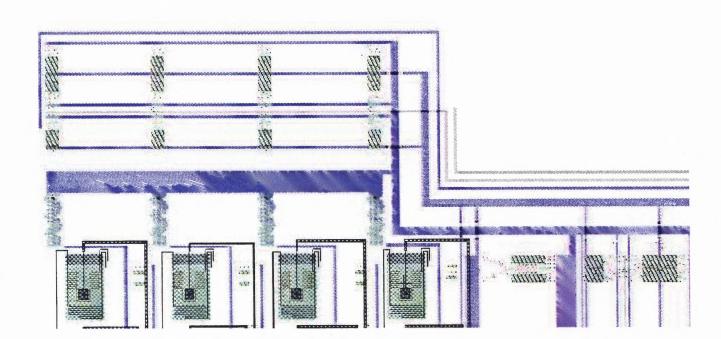

| 6.7b        | Layout showing a row of microstructures                                         | 81  |  |

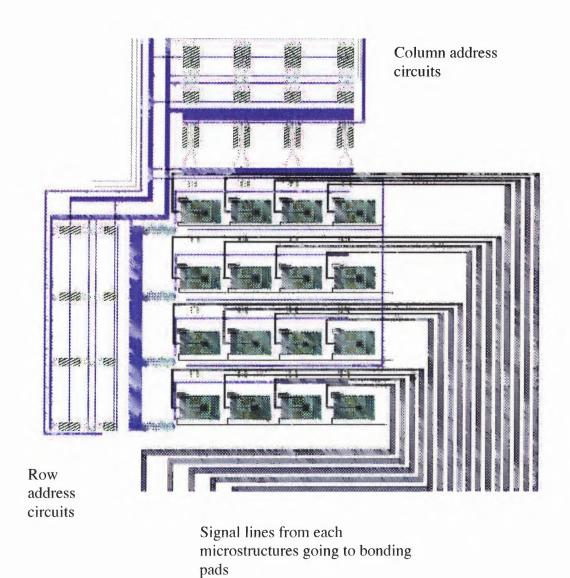

| 6.7c        | Layout showing a column of microstructures                                      | 82  |  |

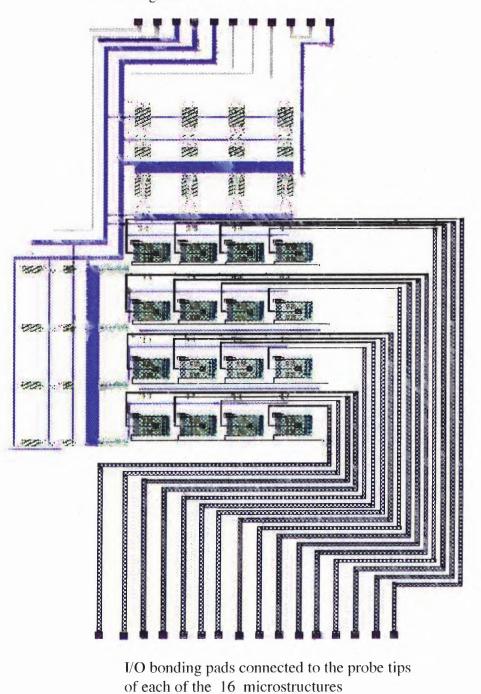

| 6.7d        | Layout of the 4x4 array of MEMS microstructures forming the probe card          | 83  |  |

| 6.7e        | Layout of the whole chip                                                        | 84  |  |

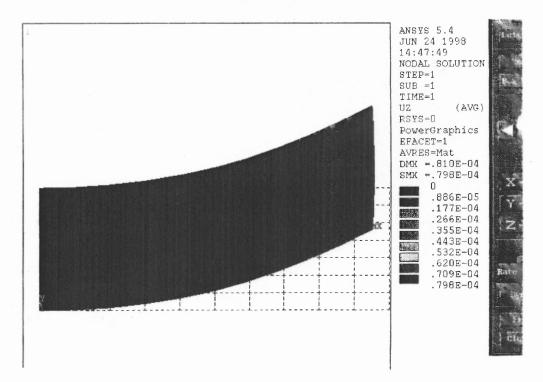

| <b>B</b> .1 | ANSYS simulation of bimorph cantilever                                          | 104 |  |

#### CHAPTER 1

#### INTRODUCTION

Testing of the wafer functionality, during and after the chip has been fabricated, is an important part of silicon device manufacturing and technology. Over the years, many wafer testing systems have been developed that are either controlled manually or by computers. These systems fall into either of two categories. First, some systems include electric wires that act as probes into the wafer being tested [1-3]. Input signals are then applied to the probes, and the output signals from other probes are read out with discrete circuits. Most of the time, these test machines are large, expensive, and are not readily adapted to testing wide variety of chips and input/output pin configurations. Second, in other probe systems the probes are fabricated using micro-machined technology, but the addressing circuits are outside the tester chip [3]. In the later case, the system consumes more power since more power is supplied to the discrete transistor circuits. Also, the fabrication is expensive since the tester and the address circuits are fabricated separately.

The key idea explored in this thesis is whether one wafer can be used to test the functionality of another wafer. The testing wafer has probes that are programmable by addressing circuits fabricated using the same technology as that of the wafer to be tested. In addition, the control or addressing circuit is fabricated in the same chip as the tester probes. This results in a system which is comparatively less expensive to fabricate and consumes less power. In this thesis, a novel design of a wafer test probe head is proposed and demonstrated through an extensive set of numerical simulations. This wafer testing

1

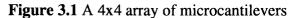

system is based on an integrated circuit that uses CMOS and MEMS technology within a single chip which would be dramatically less expensive than their traditional counterparts [1-3]. This chip will carry both the control circuits as well as the testing probes. The wafer to be tested will be placed over the integrated probe array. The probes are mounted on MEMS structures where each includes a bimorph cantilever. The addressing circuits that control these cantilevers are designed using CMOS logic. The control circuit will heat the bimorph cantilevers to position them such that the probes mounted on the cantilever come in contact with the wafer under test (WUT).

The thesis is arranged in the following manner. Chapter 2 briefly describes the traditional wafer probe systems from a historical perspective, and also summarizes the Marcus-Carr patent which forms the basis of the new probe chip to be designed and analyzed in this thesis. Chapter 3 describes the novel system in detail. Chapter 4 describes the various components of the MEMS structures and includes a detailed description of its operation. In this chapter, not only the physical layout of this structure is discussed, but also a comprehensive calculation pertaining to heat, power dissipation, deflection of probe structure, and stress is included. Also included is a feasible fabrication technique for the MEMS structure, since the fabrication process is not as standardized as the CMOS technology. Chapter 5 describes the CMOS addressing circuit in detail. The simulations of the circuit components using PSPICE are demonstrated and the corresponding physical layout using L-EDIT is illustrated and discussed. Chapter 6 describes the integration of the CMOS and MEMS systems described in Chapters 4 and 5. Finally, in chapter 7, summarization of the thesis and discussion of further extension of this work for practical systems are included.

#### **CHAPTER 2**

#### BACKGROUND

#### 2.1 Summary of Existing Wafer Probe Systems

In chapter 1, it was mentioned that the existing wafer probe equipments are either wiregrid based systems or systems based on VLSI circuits. Currently, the VLSI test systems have essentially replaced the more bulky and expensive wire-grid based test equipments. A number of companies now manufacture such VLSI test systems. One such leading company in this field is 'Advantest' [3].

The VLSI test systems manufactured by Advantest are primarily used in the testing of microprocessors and logic LSI devices. Advantest produces a large array of test structures. For example Advantest T6671B VLSI test system implements functions such as image processing in a system-on-a-chip form. Its test speed is 125MHz (I/O test rate) , 200MHz (data rate, clock rate). It employs 512 I/O pins and the overall timing accuracy is +/-500ps. An improvement over T6671B is T6681. This equipment is a high-performance system for new generation LSI devices such as those designed with a 0.25µm rule. It is used for testing RISC or CISC processors, data communication devices and high speed devices for use in multimedia applications. It has a test speed of 200/400MHz, 1024 I/O pins and a timing accuracy of +/-300ps. The T6682 VLSI test system is the newest member of the family of high performance logic and mixed signal test systems. This technology uses a new multi-pin architecture that provides each tester channel with a choice of three different DUT interface options – standard single wire I/O, Fly-By I/O and a separate (split) input and output per tester channel. The testing speed

3

varies from 250MHz to 1GHz with a high speed clock. The number of I/O pins is up to 1024. This equipment also supports audio and video frequency mixed signal and high speed clock options.

A sampling of these test systems highlight both the importance as well as the sophistication of these test structures. However, these structures also highlight the key limitation of the existing test structures. First, these test systems, with rigid input-output pin structure, and fixed spacing and depth of the probing pins are meant to test certain classes of chips having similar I/O pin structure. Second, the current system can only probe packages chips and are generally inflexible. This lack of versatility, which in turn increases cost, is the key objection to such systems.

The system to be explored in this thesis addresses the key limitations of the test structure and adds remarkable versatility of probing technology by replacing the rigid I/O probe pins with MEMS based microstructures. While there can be many different implementations of this concept, the architecture based on the Marcus-Carr patent [4] was selected as a prototype to explore this concept.

#### 2.2 The Bimorph Structure Proposed by Marcus and Carr [4, 5]

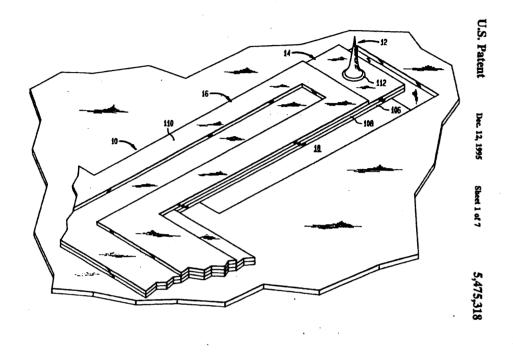

The Marcus-Carr patent outlines a design of a wafer test system that is comprised of a microprobe structure to replace the rigid I/O probe pins in the traditional VLSI test equipment. This microprobe is made up of a base, a microcantilever extending in a plane from the base and a probe tip projecting from the microcantilever out of the plane. It is used for testing silicon wafers by bringing the probe tip in contact with the wafer under test (WUT).

The working principle in this case in quite simple. The microcantilever is a bimorph structure of two layers of materials having different coefficients of thermal expansion. There is also an integrated heating element that supplies heat to the microcantilever. The probe tip is made of silicon. The radius of the tip can be controlled to atomic sharpness (less than 1 nm) if desired. It can also be a planar structure. The two layers of the microcantilever are made of aluminum and silicon dioxide and the heating element is made of a line or ribbon of conductive material such as polysilicon. This heating element is in contact with the aluminum layer and supplies heat thereby causing the probe tip to deflect into an arc and bring it in contact with the material or wafer under investigation. Figure 2.1 shows the cross-sectional view of the microprobe in the present invention.

The microprobe is a monolithic structure (i.e. it is fashioned from a single piece of semiconductor) using the techniques of silicon chip processing. Typically the cantilever is 200 to 600  $\mu$ m long, and about 20 to 30 $\mu$ m wide. The probe tip, which is made of silicon, is about 5 $\mu$ m long. The point of the probe tip is very sharp, typically 0.5nm. This allows it to penetrate the surface oxides for better connections. The air gap is about 10 $\mu$ m wide.

The bimorph structure of the cantilever consists of aluminum which is  $1.5\mu m$  thick and a layer of silicon dioxide which is  $1\mu m$  thick. The ribbon of conductive polysilicon that forms the heating elements is about  $0.5\mu m$  thick.

Due to the difference of coefficients of thermal expansion of aluminum and silicon dioxide the cantilever which is 200µm long and 20µm wide will traverse an arc corresponding to a vertical distance of 10µm when 50mW power is applied to the heating

element. This power raises the temperature of the bimorph to 150 degrees Centigrade. Greater distances can be traversed if the cantilever is made longer. For example, a vertical distance of 50 $\mu$ m can be traversed if the length of the cantilever is increased to 500 $\mu$ m. In all these cases the direction of deflection is upwards. However, it is possible to reverse the direction of deflection with the probe tip pointing downward by reversing the layers of aluminum and silicon dioxide.

There can be many functional extension of the work done in the Marcus-Carr patent. One such extension of the invention is an array of individually addressable microprobes of this kind that are processed out of a silicon wafer and are connected by appropriate leads to the outside world to form a wafer probe card. While the Marcus-Carr patent emphasizes the concept of a flexible MEMS-based probe, one still needs to deal with the complete and specific layout architecture and electrical integrity to see if the basic concept could be converted into true a wafer probe system. This thesis explores in great details the concept presented in this patent. In this work, latching structures are used upon which probes are mounted. It utilizes CMOS row and column addressable circuits to address the programmable segments of the latching structures. The address circuits are also mounted in the same wafer. In short, it extends the basic concept presented into a true wafer probe system to see if the scaled-up version is feasible. The basic design of the patent has been modified to suit the purpose for this work.

Figure 2.1 Bimorph cantilever proposed by Marcus-Carr patent.

In the above figure, the numbers 106 and 108 represent aluminum and silicon dioxide layers respectively. Number 110 is the polysilicon heater and 12 represents the probing pin. The air gap is represented by number 18.

#### **CHAPTER 3**

#### **DESCRIPTION OF THE NEW SYSTEM**

#### 3.1 The System Architecture

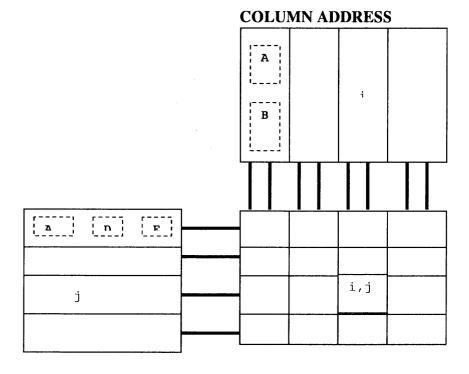

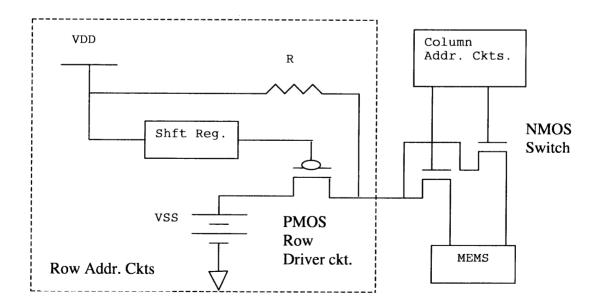

This project utilizes cross row and column address circuits to program the position of a two dimensional array of microcantilever latching structures (see Figure 3.1). The row circuit consists of a shift register, a polysilicon resistor and a row driver. The column circuit consists of a shift register and a D/A converter. This configuration has application for semiconductor manufacturing test systems at the wafer processing level. The row and column circuits select one or more of the MEMS pixels in the array depending on the values shifted through them. A whole string of bits have to be loaded into the column circuits and one bit of data is shifted through the row circuits. Hence, the speeds of clock in the two address circuits are different. The clock rate in the column circuit is faster than the row circuit.

When one or more of the MEMS pixel is selected, current flows through it from the row address circuit. This current heats up the heaters in the pixel and raises the microprobe to touch the wafer being tested. The amount of current flowing depends on the value being loaded into the column address circuits. When all 0's are shifted into the column register, there is no current flow , and all the cantilevers remain in their equilibrium position. When all 1s are shifted, then there is maximum current flow causing maximum deflection of the cantilever beams. The intermediate values will allow current flow into the circuit too and will deflect the bimorph cantilever at varying heights making possible electrical contacts with wafer surface of non-planar topology.

8

#### **3.2** Block Diagram of System Architecture

**ROW ADDRESS**

**MEMS PIXELS**

Figure 3.2 Illustration of wafer probing operation.

The column address circuit consists of a 3-bit shift register represented in Figure 3.1 as block **A** and a DAC, block **B**. The shift register is used to load the digital signal. This signal is sent to the DAC to be converted to analog current. This current will control the

current flowing from the row circuits that will heat the heaters in the microstructures. The DAC is the controller of current to the pixels. The row address circuit consists of a 1-bit shift register **A**, a polysilicon resistor **D** and a large PMOS transistor that acts as a row driver **E**. This row driver is necessary to supply the huge amount of current flowing through the pixels in the selected row. The shift register is the same one used in the column circuit, except only one of its bits is used in the row. The pixel itself includes the latching probe microstructure with the probe integrally mounted on a bimorph cantilever (see Figure 3.2). Current controlled by column address circuit flows from the row address circuit through the selected row of pixels. In Figure 3.1 a pixel represented by the ith column and jth row is selected and its testing operation is illustrated in Figure 3.2. The next chapters describe the microstructure and the address circuits in details.

#### 3.3 Overall Design Strategy and Considerations

The main component in this thesis work is the design of the latching probe microstructure that is the wafer tester itself. First of all, the configuration of this design was chosen, and then the materials used for the design were decided upon depending on the material properties. In Chapter 4, ANSYS simulation was performed to compute the amount of heat required to deflect the probes to the desired height of 60µm. Then the current needed to produce this heat was calculated. In Chapter 5, the addressing circuits that would produce this current were then designed. The D/A converter in the column address circuit is the controller of current in the microstructure. The row driver in the row address circuit is the supplier of the current to heat the cantilever actuation structures.

#### **CHAPTER 4**

#### DESIGN AND SIMULATION OF MEMS LATCHING PROBE MICROSTRUCTURES

In the previous chapter the design strategy for this work was outlined. In this chapter, the design and operation of the latching probe microstructures referred to as 'pixels' in Figure 3.1 will be discussed. Detailed simulation results are presented, and a feasible comprehensive fabrication sequence is discussed.

#### 4.1 Brief Description of Latching Probe Microstructure

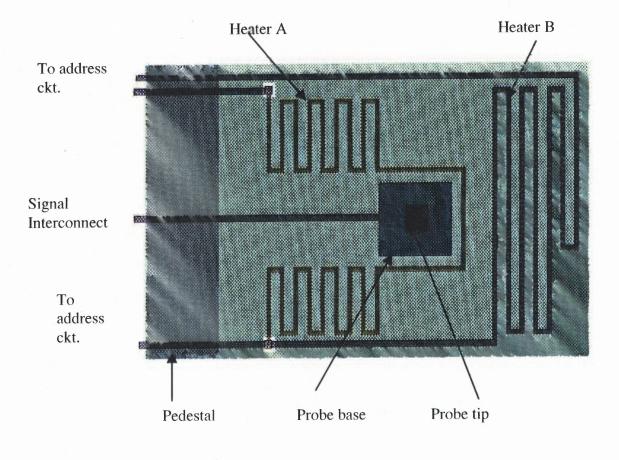

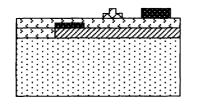

The microstructure consists of a  $SiO_2$  cantilever that is attached to a pedestal on one end. The other end is free to deflect. (See Figure 4.1). The microprobe is situated in the center of the cantilever. There are two aluminum heaters one on top and one on the bottom side of the cantilever. The heater next to the pedestal is located on the bottom side and the other one is on the top side. As a result of this arrangement when both heaters are heated, the cantilever deflects into an arc shape with the probe tip on the peak of the arc. The substrate has grooves cut into it so that with complete deflection, the free end of the cantilever latches into one of the grooves. Hence, the name latching probe microstructure. Once the cantilever is latched into a position, any change in ambient temperature of the heaters or the switching off of the power supply will not change the position of the probe. This helps to reduce power consumption as well as take accurate readings throughout the probe. The probe can only be unlatched with a temperature in excess of 100 degrees Centigrade.

#### 4.1.1 Description of Components

As described in the previous section the components of the microstructure are the following: the pedestal, the SiO<sub>2</sub> cantilever, two aluminum heaters and the probe tip. The dimension of the microstructure is  $300\mu$ m by  $210\mu$ m. The dimension of the SiO<sub>2</sub> cantilever is  $300\mu$ mX210 $\mu$ mX2 $\mu$ m. The two heaters on either side of the probe have serpentine structure. Each is made of approximately 300 squares of aluminum that has a thickness of 100nm. This results in a resistance of  $100\Omega$ . (See Figure 4.1). Heater A is situated below the SiO<sub>2</sub> cantilever and heater B is situated at the top of the cantilever. (See Figure 4.2). As shown in Figure 4.2, the base of the probe tip has a layer of aluminum that is about 1.5 $\mu$ m thick. The tip of the probe is made of gold and is square in shape. The thickness of the gold tip is  $2\mu$ m. The base of the probe has a dimension of 70 $\mu$ m x 70 $\mu$ m and the tip is 25 $\mu$ m x 25 $\mu$ m. Finally the cantilever is attached to a SiO<sub>2</sub> pedestal that is about 80 $\mu$ mX210 $\mu$ mX2 $\mu$ m.

The fabrication technique and masks to fabricate this microstructure is outlined in section 4.4 of this chapter. In the next section, the principle of operation of the microstructure is outlined.

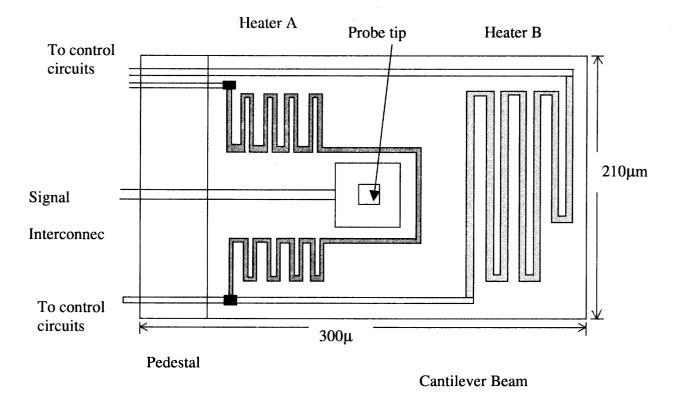

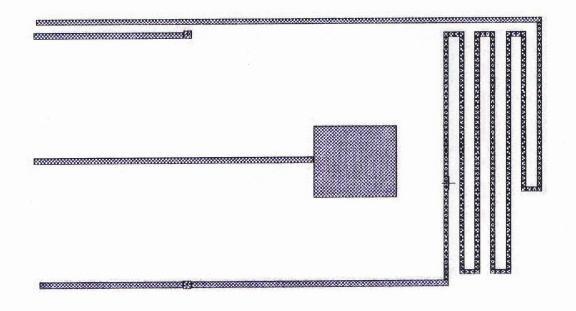

Figure 4.1 Top view of the microstructure

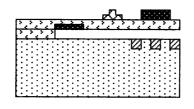

#### 4.1.2 Operation of the Microstructures

Each of the heaters are connected to a row address circuit through an NMOS transistor switch which is controlled by the column address circuit. (See Figure 4.1). Current flows from the row address circuit into the aluminum heaters. The column address circuit controls this amount of current through the NMOS switch and with a load resistance  $50k\Omega$ .

The detailed operation of the addressing circuits will be described in the next chapter. As the current flows into the heater, the heater heats up the cantilever beam.

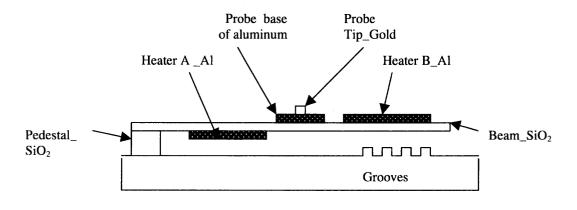

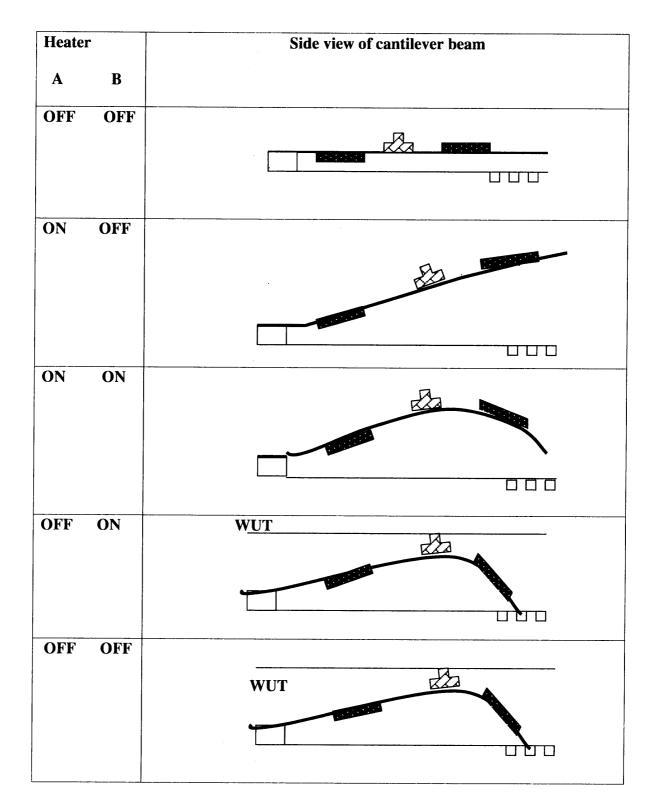

Since it is a bimorph structure as shown in Figure 4.2, heater A will deflect one half of the cantilever upwards and heater B will deflect the other half downwards thus forming an arc. On deflection, the free end of the beam latches itself on one of the grooves cut in the substrate. The wafer under test (WUT) is then brought in contact with the probe tip. Figure 4.3 illustrates graphically the latching process of the cantilever. In order to unlatch the cantilever, both heaters are activated first and then heater B is switched off . Refer to Figure 4.4 for the steps required to unlatch the cantilever from the grooves. This will first bend the cantilever slightly and then straighten the B portion of the cantilever This will release the cantilever from the latched position. Before beginning the unlatching sequence, the WUT is removed from the probe tip contact. Then as both the heaters are off, the cantilever will come to the unstressed level position.

Figure 4.2 Side View of the microstructure

Figure 4.3 Programming sequence of latching position for WUT contact

#### 4.2 Theory and Numerical Analysis of Microprobe Structure

While the previous section gives an overview of the operation, it is important to consider the process more quantitatively. In this section, first an analysis of the theory of bending is provided and then a numerical analysis based on ANSYS [6] simulation is done to quantitatively establish the theory.

#### 4.2.1 Theory of the Bending of the Bi-metal Cantilever [7,8]

The theoretical analysis is based on calculation of longitudinal stress acting over the cross-section as well as the magnitude and distribution of the shearing and normal stresses along the interface. Figure 4.5 shows the components of the bimetal strip.

Figure 4.5 The bimetal strip for theoretical analysis

$h_1$  and  $h_2$  are two thickness of SiO<sub>2</sub> and aluminum, respectively, L is the length and B is the width of strip.

We assume that the bimetal strip is heated by a temperature  $\Delta T$ . The left end is fixed, whereas the right end is free to deflect. The thermal coefficient of expansion of upper component is  $\alpha 1$  and that of lower component is  $\alpha 2$ . The longitudinal displacement of the lower extreme fiber of the component number 1,  $U_1(x)$  and of the upper extreme fiber of component number 2,  $U_2(x)$  are given by:

$$U_{2}(x) = \alpha_{2} \Delta t \, x - \frac{1 - \nu_{21}^{2}}{E_{2} h_{2} b} \int_{0}^{x} Q(\xi) d\xi + \kappa_{21} q(x) + \frac{h_{2}}{2} \int_{0}^{x} d\xi \frac{1}{\rho(\xi)}$$

(4.1)

$$U_{1}(x) = \alpha_{1} \Delta t \, x - \frac{1 - \nu_{1}^{2}}{E_{1} h_{1} b} \int_{0}^{x} Q(\xi) d\xi + \kappa_{1} q(x) + \frac{h_{1}}{2} \int_{0}^{x} d\xi \frac{1}{\rho(\xi)}$$

(4.2)

where  $E_1$ ,  $E_2$  are Young's modulus of elasticity, v1, v2 are Poisson's ratio.

$$\kappa_2 = \frac{2(1+\nu_2)h_2}{3E_2b}$$

(4.3)

$$\kappa_{1} = \frac{2(1+\nu_{1})h_{1}}{3E_{1}b}$$

(4.4)

are the coefficients of interfacial compliance. Here  $\rho(x)$  is the radius of curvature, Q(x) is the shearing force per unit plate length, given by

$$Q(x) = \int_{-l}^{x} q(\xi) d\xi$$

(4.5)

and q(x) Is the force at the X cross-section and L is half the plate's length. The first terms in Equation 4.1 and Equation 4.2 are the unrestricted thermal expansions of the stripes. The second terms are due to the forces Q(x), and the third term account for actual nonuniform distribution of forces Q(x). The last term is due to bending. Since the displacement of the upper and lower stripes, U1(x) and U2(x), must be the same, and therefore Equation 4.1 and Equation 4.2 must be equated:

$$U_1(x) = U_2(x)$$

(4.6)

$$\kappa q(x) - \left(\frac{1 - \nu_1^2}{E_1 h_1} + \frac{1 - \nu_2^2}{E_2 h_2}\right) \int_0^x Q(\xi) d\xi + \frac{bh}{2} \int \frac{d\xi}{\rho(\xi)} = b \Delta \alpha \Lambda t \ x \tag{4.7}$$

where h=h1+h2 and  $\Delta \alpha = \alpha_1 + \alpha_2$ .

$$\kappa = b(\kappa_1 + \kappa_2) = 2 \frac{(1 + \nu_1)}{3E_1} h_1 + 2 \frac{(1 + \nu_2)}{3E_2} h_2$$

(4.8)

Moreover, at equilibrium the net bending moments must be balanced by the shear force.

Figure 4.6 Forces and moments acting on the bimetal strip

The equation of equilibrium for the portion of the plate is as follows.

$$M_{1}(x) + M_{2}(x) - \frac{h}{2}Q(x) = 0$$

(4.9)

where  $M_1(x)$ , M (x) are the bending moments of the strips and D1, D2 are flexural rigidities. It can be shown that

$$M_1(x) = \frac{bD_1}{\rho(x)}$$

,  $M_2(x) = \frac{bD_2}{\rho(x)}$  (4.10)

$$D_{1} = \frac{E_{1}h_{1}^{3}}{12(1-v_{1}^{2})} , \quad D_{2} = \frac{E_{2}h_{2}^{3}}{12(1-v_{2}^{2})}$$

(4.11)

From equations 4.9 and 4.10 we get

$$\frac{1}{\rho(x)} = \frac{h}{2bD}Q(x) \quad , \quad D = D_1 + D_2$$

(4.12)

This is substituted in equation 4.7. After further manipulations it was found that

$$Q(x) = \frac{-b\Delta\alpha\Delta t}{\lambda}\chi(x)$$

(4.13)

where for large value of  $\kappa l$ , we have

$$\chi(x) = 1 - \frac{Cosh(\kappa x)}{Cosh(\kappa l)}$$

$$= 1 - e^{-\kappa(l-x)}$$

(4.14)

and

$$\lambda = \frac{1}{12} \left( \frac{h_1^2}{D_1} + \frac{h_2^2}{D_2} + \frac{3h^2}{D} \right)$$

. . . . .

Hence equation 4.12 can be rewritten as

$$\frac{1}{\rho(x)} = \frac{-h\Delta\alpha\,\Delta t}{2\lambda D}\,\chi(x) \tag{4.15}$$

and the bending moments

$$M_{1}(x) = \frac{-bh\Delta\alpha\Delta t}{2\lambda D} D_{1}\chi(x)$$

(4.16)

$$M_{2}(x) = \frac{-bh\Delta \alpha \Delta t}{2\lambda D} D_{2}\chi(x)$$

(4.17)

The deflection function v(x) can be found using the following equation:

$$\frac{d^2 v}{dx^2} = \frac{-1}{\rho(x)} = \frac{h \Delta \alpha \Delta t}{2\lambda D} \chi(x)$$

(4.18)

After integrating this formula twice, an expression for maximum deflection is got

$$\nu_{\max} = \frac{hl^2 \Delta \alpha \Delta t}{4\lambda D} \tag{4.19}$$

This expression shows that the displacement should vary linearly with temperature, quadratically with half the length of the plate. Later, this expression will be used to verify the detailed numerical simulation based on finite element analysis of the coupled elasto-thermal system by ANSYS software package. An alternative derivation of theoretical bending was performed based on a more recent publication [16]. The resulting expression turned out to support equation 4.19. Refer to Appendix C.

# 4.2.2 A Brief Description of the ANSYS Simulation for Bending Calculation

ANSYS is the software that is used here to simulate the MEMS structures [6]. It is used for thermal, electrical, mechanical, electro-mechanical and many other types of coupledfield analyses. The analysis is done by solving stress, heat, electrical and mechanical equations. The software is interactive and can be used for any combinations of analysis. The method that ANSYS uses for doing the simulation is called finite element method. It breaks down the material under test into finite number of elements of a shape and size chosen by the user and applies stress or heat. Then it meshes the elements together and solves the equations to give the outcome. The finer the size of the mesh, the more accurate the results of the simulation are since more number of algebraic equations has been used to represent the partial differential equations resulting from thermo-mechanical systems. This software is very versatile. It is able to analyze any geometric shape of any material. It can also be used to analyze multi-morph structures made of different materials stacked on top of each other, and therefore ideally suited for our purpose.

For our purpose, ANSYS has been used to simulate the bi-morph cantilever beam to see how much temperature difference is needed to get a deflection of about 60 to  $80\mu$ m, which is the system specification. Shell 91, a 16-layer structural shell was chosen for the simulation. For the thermal-stress analysis the thickness of aluminum and SiO<sub>2</sub> layers was given. The material properties like the Young's modulus of elasticity, the thermal coefficients of expansion and Poisson's ratio for the two materials were also provided as inputs to the preprocessor. The schematic of the cantilever beam was then drawn. It was then broken into finite elements, tethered on one end and meshed. The temperature was then applied uniformly and the post processor was prompted to show the resulting figure. These results were then tabulated and plotted for completeness. The simulation was carried for two cantilever beams of 100µm and 300µm long.

# 4.2.3 Results and Discussion of ANSYS Simulation

The results from the ANSYS simulation are tabulated below. Two cantilever beams of different lengths were simulated to accurately observe the relationship between the temperature and deflection with length.

Table showing deflection vs. temperature for 100µm long beam from ANSYS simulation.

| TEMP. DIFF (ΔT) | DEFLECTION (µm) |  |

|-----------------|-----------------|--|

| 0               | 0               |  |

| 200             | 15              |  |

| 400             | 30              |  |

Table 4.1

Temperature vs deflection of 100µm beam

Table showing deflection vs. temperature for 300µm long beam from ANSYS simulation.

| TEMP. $DIFF(\Delta T)$ | DEFLECTION (µm) |  |

|------------------------|-----------------|--|

| 0                      | 0               |  |

| 150                    | 60              |  |

| 200                    | 80              |  |

Table 4.2

Temperature vs deflection of 300µm beam

Tables 4.1 and 4.2 show that the deflection is linearly proportional to the change in temperature. This fact is illustrated better in the following plot as expected from our theoretical analysis.

**Figure 4.7** Illustration of linear relationship between temperature difference and deflection of 300µm long cantilever

Based on the simulation, it was concluded that for a deflection of 80µm, a cantilever beam of 300µm, and width of 210µm requires a temperature difference of approximately 200 K. Here it should be noted that the deflection calculations are limited to the linear range only.

#### 4.2.4 Comparison between ANSYS and Simple Analytical Theory

In this section, a comparison of the results of deflection obtained by ANSYS and the calculated value of deflection using the analytical expression in equation 4.19 are done. This will validate the ANSYS simulation in a general manner.

| Parameters                            | Symbol                | Value                 | Units                  |

|---------------------------------------|-----------------------|-----------------------|------------------------|

| Length of beam                        | 1                     | 300x10 <sup>-6</sup>  | m                      |

| Thickness of SiO <sub>2</sub>         | <b>h</b> 1            | 2x10 <sup>-6</sup>    | m                      |

| Thickness of Al                       | h <sub>2</sub>        | 100x10 <sup>-9</sup>  | m                      |

| Temperature difference                | ΔΤ                    | 200                   | К                      |

| Difference in thermal exp.            | Δα                    | 22.6x10 <sup>-6</sup> | <b>K</b> <sup>-1</sup> |

| Poisson's ratio of SiO2               | ν <sub>1</sub>        | 0.27                  | -                      |

| Poisson's ratio of Al                 | <b>v</b> <sub>2</sub> | 0.27                  | -                      |

| Young's modulus of SiO <sub>2</sub>   | E <sub>1</sub>        | 0.74x10 <sup>11</sup> | N/m <sup>2</sup>       |

| Young's modulus of Al                 | E <sub>2</sub>        | 0.69x10 <sup>11</sup> | N/m <sup>2</sup>       |

| Constant                              | λ                     | 1.6x10 <sup>-4</sup>  | m <sup>3</sup> /N      |

| Flexural rigidity of SiO <sub>2</sub> | D1                    | 5.32x10 <sup>-8</sup> | N/m                    |

| Flexural rigidity of Al               | D <sub>2</sub>        | 6.2x10 <sup>-12</sup> | N/m                    |

**Table 4.3**Parameters and their values in theoretical calculation of deflection height

Using the above values and Equation 4.19 the maximum deflection found for a  $300\mu m$  beam was approximately  $25\mu m$ . Although the deflection is significantly underestimated by this formula compared to the numerical simulation, however, both the functional dependence expected from the analytical theory (see Equation 4.19) that (a) the deflection is proportional to the temperature difference and (b) that the deflection is proportional to the length are clearly demonstrated in from numbers in

tables 4.1 and 4.2, respectively. It was therefore concluded that although the simple theory is not quantitatively accurate it does capture accurate underlying physics of the problem correctly. An alternative calculation based on a more recent publication [16] is included in Appendix C.

### 4.3 Physical Layout

ANSYS simulation shows that a 300µm long cantilever will bend to give a deflection height of 60 to 80µm when heated by a temperature difference of 200 °K. Hence the layout of the microstructure was then proceeded with.

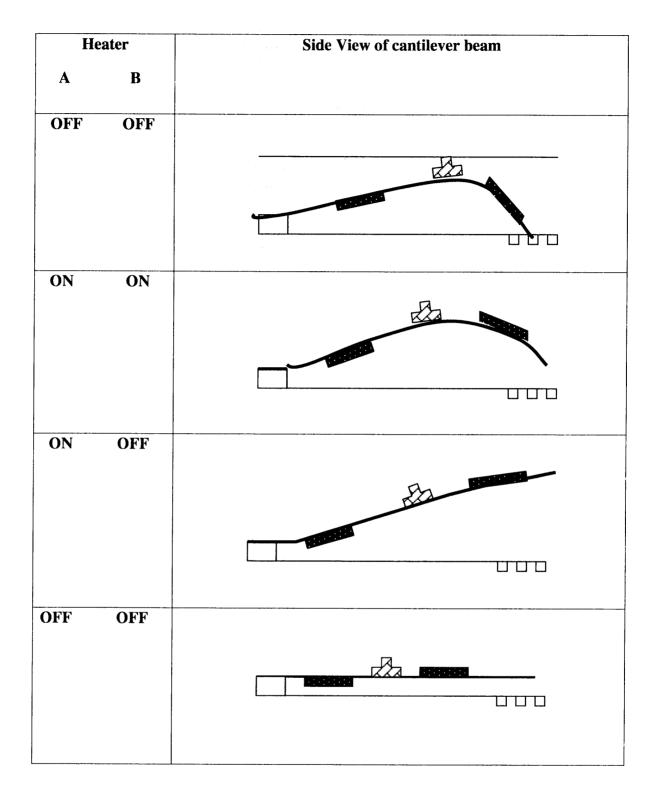

# Figure 4.8 Layout of microstructure from L-EDIT

26

Figure 4.8 clearly shows the layout of the microstructure in LEDIT [9]. The heaters A and B are connected to the row and the column address circuits. The signal from the probe goes out of the pixel and connects to the bonding pad. The dimension of the structure is 300  $\mu$ m x 210  $\mu$ m as mentioned earlier. The different layers used in the layout of the microstructures are shown in Chapter 6.

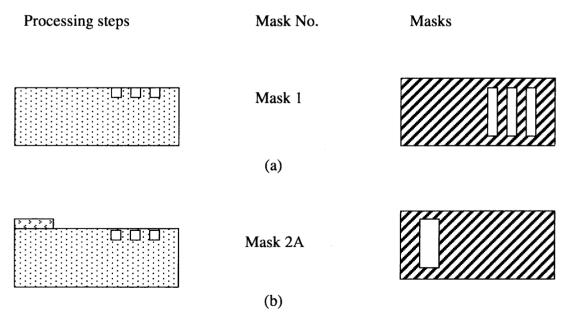

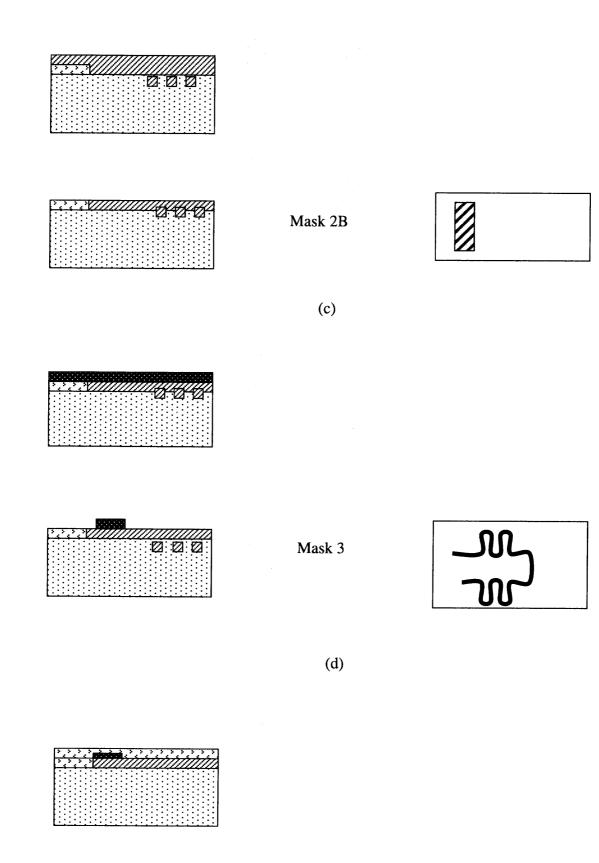

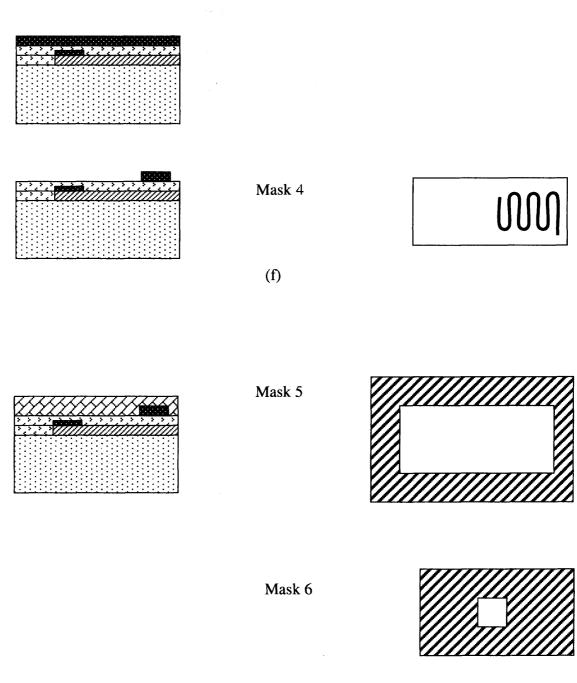

#### 4.4 Fabrication Technique

The previous section shows the desired layout of the microstructure. In this section, a feasible processing technique for the fabrication of MEMS pixels [10] is outlined. The layout of MEMS pixels in L-EDIT shows that there are nine layers of materials used. The number of masks required in this processing is eight. The starting material consists of single crystal Si substrate. This substrate is patterned and etched to form the latching grooves. The grooves are  $2\mu m$  deep and are etched by SF<sub>6</sub> reactive ion etching (RIE). Refer to Figure 4.9a. After patterning the substrate,  $SiO_2$  is formed by dry oxidation in a pure oxygen ambient. Then this layer is patterned with negative photoresist mask and etched with CF<sub>4</sub> RIE to create the pedestal of the cantilever beam (Figure 4.9b). On top of the SiO<sub>2</sub> layer, polyimide is deposited by spin-on technique. This will give, a planar surface for further processing steps and eventually act as sacrificial layer to be etched away at the end of the processing. The polyimide is planarized to the same level as the pedestal. This is done by sputtering (Figure 4.9c). The same mask can be used to pattern the pedestal and the polyimide sacrificial layer with a positive photoresist. This will save the expense of creating a separate mask for this layer. Next the aluminum layer is

deposited by sputtering. In L-EDIT, this is METAL 3. The metal is patterned with heater-A mask, and etched (Figure 4.9d). The etching is done by  $Cl^+$  RIE. The thickness of aluminum layer is 100 nm. On top of the Al layer, another layer of SiO<sub>2</sub> by PECVD technique is deposited (Figure 4.9e). This is done so that the deposition can occur at lower temperature below the melting point of aluminum. This would be 2µm thick, and would eventually form the cantilever beam. On top of this  $SiO_2$  layer, another aluminum layer is deposited to form HEATER B after patterning and etching (Figure 4.9f). The next step is to pattern the  $SiO_2$  cantilever beam. Then photoresist is deposited, and patterned to expose the area where the probe tip will be formed. The probe has four layers of metal stacked on top of each other. It is fabricated using two masks (Figure 4.9g). The first mask is for the base of the probe and the second mask is for the tip. The base is made up of aluminum deposited by sputtering, to a thickness of 1.5µm. The second mask for the tip has a small opening. This mask is used to deposit the gold tip which has a thickness of 2µm and is etched in a wet chemical ambient. The final step of processing is to create the air gap for the free deflection of the cantilever beam (Figure 4.9h). This is done by removing the polyimide sacrificial layer. This removal is done by cutting four access holes in the cantilever and isotropic O<sup>+</sup> plasma etching the polyimide layer. The access holes are created at the beginning of the process and the pattern in the mask for these holes can be used as alligners during the processing steps as well. There is also a mask for the via connecting the heater A to the wires of the address circuits. The following table (Table 4.4) lists the masks in sequence and Figure 4.9 shows the processing steps sequentially.

| Mask Level | Processing Steps                                           |

|------------|------------------------------------------------------------|

| 1          | Create grooves using RIE in silicon substrate              |

| 2A         | Oxidize a SiO2 substrate and pattern for pedestal          |

| 2B         | Spin-on polyimide and planarization                        |

| 3          | Aluminum sputter deposition and patterning into heater A   |

| 4          | Via cut between heater A and heater B                      |

| 5          | Aluminum sputter deposition and patterning into heater B   |

| 6          | Patterning the SiO <sub>2</sub> cantilever beam            |

| 7          | Aluminum sputtered to form the base of probe.              |

| 8          | Gold sputtered or electro deposited to form the probe tip. |

**Table 4.4**List of masks in the fabrication of the microstructure

29

(e)

31

(h)

# Figure 4.9 Graphical illustration of fabrication steps and masks required

#### 4.5 Numerical Analysis

We know how much heat is required for the bending of our bimorph cantilever. The question is how much current is needed? This section explores the various calculations necessary to find the amount of this current.

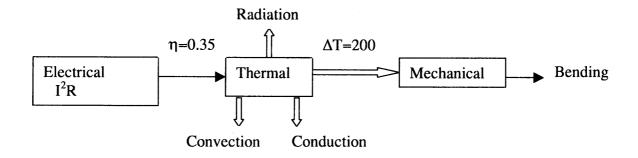

#### **4.5.1** Calculation of Cooling through Power Dissipation

The cooling rate of the cantilever beam is determined by three factors. These three are actually the powers dissipated through the microstructure. This power is equivalent to sum of the convection and radiation power dissipated by the beam [11, 12] and the conduction power dissipated by the aluminum wire over the support pedestal and the  $SiO_2$  pedestal itself. Figure 4.10 shows how the remaining electrical power is converted to heat or thermal power which in turn is converted to mechanical power that will bend the cantilever. By ANSYS simulation in section 4.3 it was found that a temperature change in the heater from 300 °K to 500 °K gave a deflection height of about 60µm.

Figure 4.10 Block diagram of energy conversion in the system

The convection power is given by

$$P_{conv} = \kappa A \Delta T \tag{4.20}$$

where  $\kappa$  is coefficient of convection in SiO<sub>2</sub> and its value is 1.7E-9 J/(s.µm<sup>2</sup>.K)

A is the area of the beam which is  $300\mu mX210\mu m = 63000\mu m^2$

$\Delta T = 200.$

Using equation 4.20 it was found that the convection power  $P_{conv} = 21.42$  mW.

The Radiation power is given by Stefan-Boltzmann law

$$P_{rad} = \sigma A \ e(T^{4} - T_{0}^{4}) \tag{4.21}$$

Where  $\sigma = 5.6696 \text{E-8 W/m}^2 \text{.K}^4$

$e = emissivity of SiO_2$ , assume 0.7

$T=500~^{\circ}K$

$$T_0 = 300 \ ^{\circ}K$$

Using equation 4.21 it was found that the radiation power  $P_{rad} = 0.136$  mW for each surface.

Hence for two surfaces,  $P_{rad}$  is 0.27 mW.

There is also some power being dissipated by conduction through the support portion of the cantilever beam. This is through the aluminum wires on top of the pedestal and also through the  $SiO_2$  pedestal. These are calculated as follows:

$$P_{Al} = A_{Al} \sigma_{Al} \Delta T / L_{Al}$$

(4.22)

Where  $A_{Al}$  is cross-sectional area of wire = 0.1µm x 6µm

$\sigma_{Al}$  is Thermal conductivity of aluminum = 240Wm<sup>-1</sup>K<sup>-1</sup>

$L_{Al}$  is the length of wire over the pedestal = 80 $\mu$ m

$\Delta T$  is the temperature difference = 200 °K

Using equation 4.22 it was found that  $P_{Al} = 0.36$  mW for each wire. There are three wires over the pedestal excluding the signal line (See Figure 4.8). Hence the conduction power through the aluminum wires is 1.08 mW. Similarly, the conduction power through the SiO<sub>2</sub> pedestal is calculated.

$$P_{SiO_2} = A_{SiO_2} \sigma_{SiO_2} \Delta T / L_{SiO_2}$$

Where  $A_{SiO2} = 210 \mu m \times 2 \mu m$  $\sigma_{SiO2} = 1.5 W m^{-1} K^{-1}$

$L_{SiO2} = 80 \mu m$

Using the above values it is found that  $P_{SiO2} = 3.1$  mW. Hence the total conduction power is calculated to be

$P_{cond} = 3 P_{Al} + P_{SiO2} = 1.08 + 3.1 = 4.2 \text{mW}.$

(1 00)

The total power dissipated in the form of heat is also the total power required for actuation of the cantilever to 200 °K in air. This is equivalent to:

$$P_{air} = P_{conv} + P_{cond} + P_{rad} = 25.9 \ mW.$$

(4.23)

It can also be noted that the total power required for actuation of the cantilever to 200 K in vacuum is:

$$P_{vac} = P_{cond} + P_{rad} = 4.47 \, mW \tag{4.24}$$

The amount of input power left after the total dissipation in the form of conduction, convection and radiation is finally converted to mechanical energy that results in the bending of the cantilever. *If it is assumed that the efficiency of the overall system is 35%, then the input power to the system is found to be approximately 40mW.*

#### 4.5.2 Calculation of the Thermal Time Constant of the Cantilever

The thermal time constant in our system is equivalent to the RC time constant in an electrical system [12]. It is basically the time required for the cantilever to completely cool down. It is very crucial to know the thermal time constant  $\tau$  because this will tell us the time after which the microstructure can be reconfigured for a new set of tests. In this section the approximate value of  $\tau$  is calculated. The following parameters and their values will be used in subsequent calculations:

$C_{A1}$  = specific heat capacity of aluminum = 100 JK<sup>-1</sup> Kg<sup>-1</sup>  $C_{SiO2}$  = specific heat capacity of SiO<sub>2</sub> = 750 JK<sup>-1</sup> Kg<sup>-1</sup>  $\rho_{A1}$  = density of aluminum = 2700 Kg m<sup>-1</sup>  $\rho_{SiO2}$  = density of SiO<sub>2</sub> = 2500 Kg m<sup>-1</sup> (101)

$V_{Al\_pedestal}$  = volume of the three aluminum wires on pedestal

= No. of wires x length of wire over pedestal x width of wire x thickness

$= 3 \times 80 \mu m \times 6 \mu m \times 0.1 \mu m = 4.8 \times 10^{-17} m^3$

$V_{SiO2 pedestal} = volume of SiO_2 pedestal$

= length of pedestal x width of pedestal x thickness

$= 80\mu m x 210\mu m x 2\mu m = 3.36 x 10^{-14} m^3$

$V_{Al\_beam}$  = volume of the two aluminum heaters on the cantilever beam

= No. of heaters x length of a heater x width of a heater x thickness

. .

$$= 2 \times 1500 \mu m \times 5 \mu m \times 0.1 \mu m = 1.5 \times 10^{-15} m^3$$

$V_{SiO2\_beam}$  = volume of the SiO<sub>2</sub> cantilever beam

= length of beam x width of beam x thickness

$= 300 \mu m x 210 \mu m x 2 \mu m = 1.26 x 10^{-13} m^3$

The time constant  $\tau$  is given by the following formula :

$$\tau = \frac{\Delta E}{G_{ihermal}\Delta T} \tag{4.24}$$

$$=\frac{\sum C\rho V \Delta T}{P_{thermal}} = \frac{\sum C\rho V \Delta T}{P_{cond} + P_{conv} + P_{rad}}$$

(4.25)

$$= \frac{\Delta T \begin{bmatrix} C_{Al} \rho_{Al} V_{Al_{-}pedestal} + C_{SiO_{2}} \rho_{SiO_{2}} V_{SiO_{2}_{-}pedestal} \\ + C_{Al} \rho_{Al} V_{Al_{-}beam} + C_{SiO_{2}} \rho_{SiO_{2}_{-}} V_{SiO_{2}_{-}beam} \end{bmatrix}}{P_{cond} + P_{conv} + P_{rad}}$$

(4.26)

$$\tau = \frac{200 \left[ 1.3x10^{-11} + 6.3x10^{-8} + 4.05x10^{-10} + 2.36x10^{-7} \right]}{26x10^{-3}}$$

$$= \frac{5.988x10^{-5}}{26x10^{-3}}$$

$$= 2.3m \sec$$

Hence  $\tau = 2.3$  msec in air.

In vacuum,

$$\tau = \frac{5.988 \times 10^{-5}}{P_{cond} + P_{rad}} = \frac{5.988 \times 10^{-5}}{4.47 \times 10^{-3}} = 13.3 \text{ m sec}$$

In the above equations,  $G_{thermal}$  is the total thermal conductivity and  $P_{thermal}$  is the total thermal power in the system. The conduction, convection and radiation power for the above calculation was taken from section 4.5.1. The thermal time constant for actuation to 200 °K in air is found to be 2.3 m sec and that in vacuum is 13.3 m sec.

# 4.5.3 Calculation of Current and Resistance of the Heater

The DAC is indirectly the supplier of current in the circuit since it controls the amount of current that will flow in the circuit from the row driver. According to our design, the maximum length of our heater will be approximately 350 squares of aluminum. Aluminum was chosen as the material of the heater because of its convenience and high coefficient of expansion. The resistivity of aluminum  $\rho(AI) = 27 \times 10^{-2} \Omega/square$ . The resistance of each heater is  $350 \times 27 \times 10^{-2} = 94.5 \Omega$ . A resistance of 100 ohms for design

and simulation purposes is used. From Sec.4.5.1, it is known that the required input power is 40 mW, and the resistance R=100 ohms, the current to be delivered to the microstructure by the DAC should be  $I = \sqrt{(P/R)} = 20$  mA to cause a  $\Delta T = 200$  °K. This is based on using aluminum of thickness 100nm for the heaters.

### 4.6 Summary and Conclusion

In this Chapter, the MEMS cantilever based on ANSYS simulation has been designed. The results were verified by using a simple theoretical analysis. Also a feasible sequence of fabrication, based on standard MEMS processing techniques is discussed. Also, based on simple energy flow, the power requirement of the heater assuming 35% efficiency is found to be 40mW and the corresponding current in each heater is about 20mA. In the next chapter the addressing circuits that will deliver the cantilever the required power and current found in this Chapter, are designed.

#### **CHAPTER 5**

# DESIGN AND SIMULATION OF CMOS ADDRESSING CIRCUITS

In this chapter, the components of the row and column address circuits as shown in the block diagram of Figure 3.1 in details, will be designed. The design and physical layout using LEDIT is illustrated. Finally the combining of the components into the row and column address circuits are shown.

# 5.1 The Shift Register

#### 5.1.1 Circuit Schematic and Analysis

The shift register circuit is used in both the row and column address circuits. The design chosen for this shift register is a two-phase non-overlapping clocked design [13]. The design was done such that 3-bits of data could be shifted simultaneously in the column addressing circuits at every clock cycle. In other words, each column consists of three shift registers. The row, however, shifts only one bit at each clock cycle, and hence only one of the shift registers in the addressing circuits are utilized.

Figure 5.1 shows the schematic of a 1-bit shift register. This circuit is cascaded to form the 3-bit shift register required in this thesis. CMOS logic was used to design this circuit. The Sin bit shown in the figure is the input and Sout is the output, which would be the input for the next bit. The 'D' bit carries the same information as the Sout, but it takes the information into the DAC in the column circuit and to the gate of the row driver in the row circuit. The SSR1 bit acts as an enable. In our case, it is always high.

**Figure 5.1** Schematic of a Shift register cell from PSPICE (Corresponding to block A of Figure 3.1).

# 5.1.2 Simulation Using PSPICE

Figure 5.2 shows the simulation of the one bit shift register illustrated in Figure 5.1. The simulation was done using the software PSPICE [14, 15].

Figure 5.2 Simulation of the shift register cell using PSPICE.

#### 5.1.3 Physical Layout of Shift Register

Since the electrical integrity of the circuits is demonstrated, now the layout of the circuit is considered. All physical layouts of the CMOS circuits are done using p-well 3µm technology [16]. Figure 4.3 shows the layout of the 3-bit shift register. The layout was done using the software LEDIT from Tanner research Inc. [9, 16]. In this design, the first bit was laid out shown in the Figure as A and flipped to form the 2<sub>nd</sub> bit of the shift register, represented by B in the Figure 4.3. This was done to avoid one ground bus. By implementing this technique, a common ground bus can be shared by two bits of the same shift register. After the two bits, the two clock lines were laid out and then the 3<sup>rd</sup> bit represented by C in the figure was laid out. The bits marked as D0, D1 and D2 are the shifted bits that will form the inputs to the DAC in the column circuit. Only D0 is taken in the row circuit. Appendix A describes the design rules used in this and all other subsequent layouts. The different layers used in LEDIT are also outlined. The number of mask levels used for the fabrication of the CMOS circuits is twelve. The layers used in LEDIT to layout all the CMOS circuits are shown in Chapter 6.

# 5.2 Digital to Analog Converter

## 5.2.1 Circuit Schematic and Analysis

The digital to analog converter is used only in the column addressing circuit (See Figure 3.1, block B). It is a 3-bit DAC. The inputs to this DAC are the 3-bits being shifted in the shift register (Figure 5.3). The DAC converts these bits into a specific output current value. Hence the shift register along with the DAC controls the amount of current flowing into the MEMS pixel and in turn controls the amount of bending of the cantilevers. Figure 5.4 shows the schematic of the DAC done in PSPICE.

Figure 5.4 Schematic of DAC circuit in PSPICE

The design of DAC consists of 41 transistors. 17 of them are PMOS and the rest are NMOS. There are three voltage sources in the circuit namely, VDD, VGG, and Vss. (See figure 5.4). The sources A, B, and C are the outputs of the shift register D0, D1 and D2. VDD, VGG, and VSS are 15V, 10V, and 15V respectively. The size of the transistors were chosen according to the required performance of the circuit. The transistor M1 has the largest length and M7 has the shortest length. M7 will be turned on when the input to the circuit is 111. This will allow maximum current to flow into the pixel. In Figure 5.4 there are two resistances. The resistance R5 represents the resistance of one of the heaters in the pixel and its value is  $100\Omega$ . The resistance R1 is the load resistance of 50k that was placed in the circuit to get a full swing of the voltage at the output circuit. The W/L ratio of the NMOS switch transistor is 160/3. When this switch is ON, the current flows from the VSS source in the row address circuit through the switch and into the heater.

## 5.2.2 Simulation Using PSPICE

The following two plots, Figures 5.5 and 5.6 were obtained by simulating the DAC circuit with PSPICE. It can be seen that the maximum current in the circuit is 30mA which clearly fulfills the requirement of this design.

C:\MSinEv\_8\Projects\DACmodelpulse2.sch

Simulation of DAC in PSPICE Figure 5.5

.

46

C:\MSimEv\_B\Projects\D&Cnodelpulse2.sch

Figure 5.6 Current in the DAC circuit

47

#### 5.2.3 Physical Layout of the Digital to Analog Converter

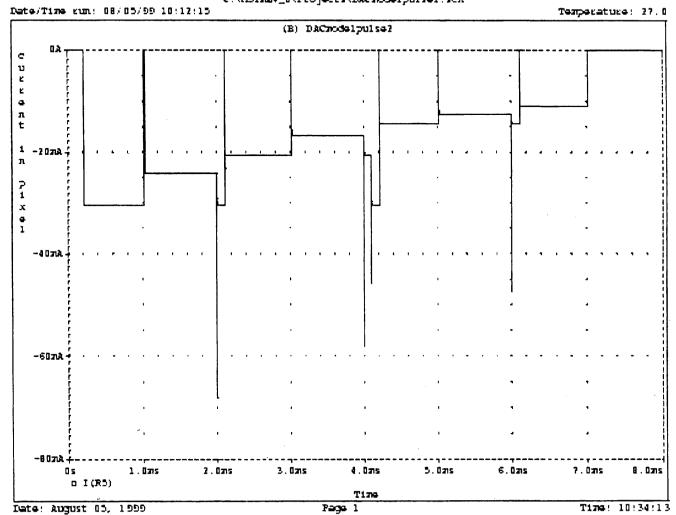

Figure 5.7 shows the physical layout of two digital to analog converter (DAC) circuits in L-Edit. This segment of the circuit marked as A represents one DAC circuit. The other DAC circuit is a flipped version of A. The PMOS transistors M1 through M7 are also shown in Figure 5.7. The line marked as I carries the analog current of the DAC. The current flows from the Vss bus which is the part of the row driver described in the next section.

The reason for designing two DAC is that two column address circuits for each pixel are needed. This is because each of the I outputs are connected to each of the heater in a single pixel through an NMOS switch. Once again, these separate heaters allow for greater flexibility in terms of deflection of the cantilever beam.

The layout of the NMOS switch and the load resistance are not shown in Fig. 5.7. They will be shown in Chapter 6 in the final layer. The switch is just and NMOS transistor with a W/L ratio of 160/3. The resistance was laid out with seventeen squares of p-well. P-well was chosen because of its high resistivity of 3000 ohms/square.

A

**Figure 5.7** Layout of the two DAC circuits in L-EDIT. One is the mirror image of the other.

# 5.3 Row Driver and Poly Resistor

#### 5.3.1 Description of Circuit

The row driver is a large PMOS transistor placed in the row addressing circuit. This is to handle large amount of current that will flow through this transistor and into the heaters of the MEMS pixels. The current is large because it is the collection of all the current flowing through each of the MEMS pixels in that particular row. The switching on and off of the row driver is controlled by the shift register, which is connected to the gate of the row driver. The current from the pixels flow through the source connected to VSS bus which is 15V and out the drain which is connected to the drain of the NMOS switch. When there is a valid input into the column address circuit, the switch is closed and current flows into the heaters. The row resistor **R** is used as a pull-up resistor. It is made up of polysilicon. It is 900 $\mu$ m in length and 3 $\mu$ m wide. Figure 5.8 shows a simplified schematic of the circuit configuration. Detailed operation of the circuit is discussed in Sec. 5.4.

Figure 5.8 Schematic showing the arrangement of row address circuit

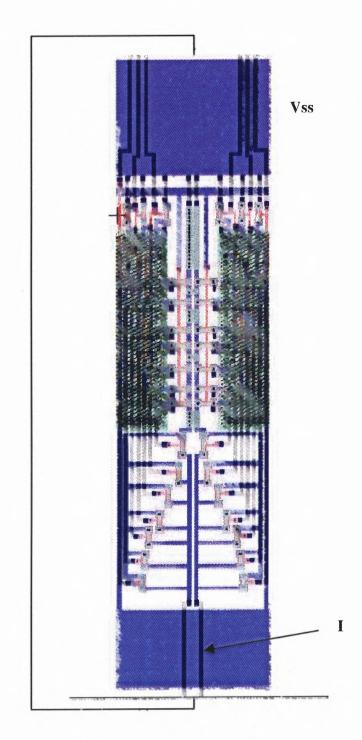

#### **5.3.2 Physical Layout of the Row Driver**

Figure 5.9 shows the layout of the row driver drawn using L-Edit. As shown in the Figure, the gate of the transistor is connected to the shift resister. This gate is a polysilicon serpentine structured gate. The drain is connected to the MEMS pixel at one end and to the polysilicon pull-up resistor on the other end. The source (the portion of the transistor outside the polysilicon gate) is connected to the Vss bus. If the pixel dimension were  $100\mu$ m by  $100\mu$ m, then the row driver circuits could link each other without any difficulty. The cutouts then mesh with each other perfectly. The W/L ratio of this transistor is 3/900. The reason for the large size of this transistor is that this transistor produces the current that will flow through the activated heaters of all the selected pixels in a row. So, if all the heaters in a single row are selected, the row driver will have to supply a total of 160mA of current since the two heaters in each pixel require a total of 40mA of maximum current.

# 5.4 Sub-circuit Driving Current in the Pixel

The sub-circuit described in this section can be viewed as a circuit combining the row and column address circuits. Part of it is connected to the DAC in the column address circuit and part of it to the row driver in the row address circuit. The simulation of this sub-circuit is done in PSPICE to see if the heaters in the pixel are getting enough power for the maximum deflection of the cantilever beam. As mentioned in Chapter 4, the required power is 40mW. The current flowing through the heaters in the pixel is being controlled by the DAC and is supplied by the Vss bus in the row circuit. Figure 5.10 shows the schematic of the sub-circuit simulated in PSPICE.

Figure 5.10 Schematic of sub-circuit supplying current in the pixel heaters

The circuit in Figure 5.10 was simulated with different Vin values and the corresponding current and power in the pixel was tabulated. Table 5.1 shows the results of the simulation. Here  $I_H$  represents the current in one of the heaters in the MEMS pixel and  $P_H$  represents the total input power in the pixel.

| Vin (Volts)           | I <sub>H</sub> (mA)                                                        | P <sub>H</sub> (mW)                                                                                                                         |

|-----------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 5.25x10 <sup>-6</sup> | 15.03x10 <sup>-9</sup>                                                     | $2.25 \times 10^{-14}$                                                                                                                      |

| 4.658                 | 7.956                                                                      | 6.3                                                                                                                                         |

| 4.989                 | 8.942                                                                      | 8.0                                                                                                                                         |

| 5.356                 | 10.08                                                                      | 10.2                                                                                                                                        |

| 5.77                  | 11.42                                                                      | 13.04                                                                                                                                       |

| 6.406                 | 13.59                                                                      | 18.46                                                                                                                                       |

| 6.956                 | 15.56                                                                      | 24.2                                                                                                                                        |

| 7.840                 | 18.89                                                                      | 35.68                                                                                                                                       |

|                       | 5.25x10 <sup>-6</sup><br>4.658<br>4.989<br>5.356<br>5.77<br>6.406<br>6.956 | $5.25 \times 10^{-6}$ $15.03 \times 10^{-9}$ $4.658$ $7.956$ $4.989$ $8.942$ $5.356$ $10.08$ $5.77$ $11.42$ $6.406$ $13.59$ $6.956$ $15.56$ |

**Table 5.1**Simulation Results of the sub-circuit

The Vin values are got by simulating the DAC circuit separately. During that simulation the load resistor of  $50K\Omega$  was included. Hence the values of Vin include the load resistor simulation. From the table it can be seen that the maximum current flowing through the heater is when the DAC input is 111 giving a maximum power of 36mW that meets our requirement of approximately 40mW adequately.

# 5.5 Combining Row and Column Address Circuits

The current components described in the previous section were combined to form the row and column address circuits. Figure 5.11 below shows a simplified schematic of the whole circuit including column and row addressing circuits. In the following sections Figure 5.11 will be referred to, to illustrate the operation of the circuit.

Figure 5.11 Simplified circuit schematic

#### 5.5.1 Description of Row Address Circuit

The row address circuit consists of a one-bit shift register, the polysilicon resistor R and the row driver. The drain of the row driver PMOS transistor is connected to the resistor R and the drain of the NMOS switch, the source of which is connected to one of the heaters (A or B) in a microstructure. The gate of the row driver is connected to the shift register and the source is connected to the Vss bus, which is at 15V. Figure 5.11 shows the schematic of the arrangement.

When the SR in the row circuit has a value of 0, it switches on the PMOS row driver. Current will flow from the Vss bus to point C. The amount of this current is controlled by the input values to the shift register in the column address circuit. If the value is 000, the NMOS switch is open and no current will flow. If it is 111, the NMOS switch is closed and maximum current will flow through the heater. This current is of large amount as it flows through all the heaters in all the pixels in the selected row.

# 5.5.2 Description of Column Address Circuit

The column address circuit consists of a 3-bit shift register and the D/A converter. The data being shifted in the shift-register is the input to the DAC. This value determines the amount of current that will flow from the row address circuit into the MEMS pixel. As mentioned in the previous section, the maximum current that will flow is when the SR register output is 111. When the SR register output is 000, no current will flow. The range of the current change between 000 and 111 will not give maximum deflection to the cantilever in the pixel but will control the height of the probe point. This can be used for testing wafers during fabrication in non-planarized surface. For testing the final chip,