# New Jersey Institute of Technology Digital Commons @ NJIT

#### Theses

Theses and Dissertations

Summer 2002

# On chip implement of deadlock avoidance in wormhole networks

Kiran K. Gururaj New Jersey Institute of Technology

Follow this and additional works at: https://digitalcommons.njit.edu/theses Part of the <u>Electrical and Electronics Commons</u>

#### **Recommended** Citation

Gururaj, Kiran K., "On chip implement of deadlock avoidance in wormhole networks" (2002). *Theses*. 696. https://digitalcommons.njit.edu/theses/696

This Thesis is brought to you for free and open access by the Theses and Dissertations at Digital Commons @ NJIT. It has been accepted for inclusion in Theses by an authorized administrator of Digital Commons @ NJIT. For more information, please contact digitalcommons@njit.edu.

# **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

#### ABSTRACT

#### ON CHIP IMPLEMENTATION OF DEADLOCK AVOIDANCE IN WORMHOLE NETWORKS

## by Kiran K. Gururaj

This thesis gives a detailed description of the Application Specific Integrated Circuit (ASIC) design to avoid deadlocks in Wormhole Networks. Deadlock avoidance is the most critical issue while considering wormhole networks and should be avoided by any routing protocol and algorithm. A novel architecture for the Turn Prohibition Based Routing (TPBR) protocol has been proved to be efficient and was developed as a part of this work. This architecture for implementing the algorithm is divided into three parts. The first part determines the order of selection of the nodes in the network to run the algorithm. The second part deals with the prohibition of the turns through the node. which might possibly create a deadlock. The third part constructs a routing table, which will have the route from a source to a destination, considering the prohibited turns into account. A VHDL model was developed and simulated using IEEE numeric std package for this architecture. This model was synthesized with Cadence tools and the post synthesis simulations verified the functionality of the architecture. The physical design was created using the standard gate cell libraries and implemented in 0.35-micron CMOS technology.

### ON CHIP IMPLEMENTATION OF DEADLOCK AVOIDANCE IN WORMHOLE NETWORKS

by Kiran K. Gururaj

A Thesis Submitted to New Jersey Institute of Technology in Partial Fulfillment of the Requirements for the Degree of Master of Science in Electrical Engineering

Department of Electrical and Computer Engineering

August 2002

#### **APPROVAL PAGE**

#### **ON CHIP IMPLEMENTATION OF DEADLOCK AVOIDANCE IN WORMHOLE NETWORKS**

Kiran K. Gururaj

8/29/02 Date

Dr. Durga Misra, Thesis Advisor Professor of Electrical and Computer Engineering, NJIT

Dr. Lev Zakrevski, Committee Member Assistant Professor of Electrical and Computer Engineering, NJIT

<u>08/29/</u>02 Date

0 8/2 9/02 Date

Dr. Symeon Papavassiliou, Committee Member Assistant Professor of Electrical and Computer Engineering, NJIT

#### **BIOGRAPHICAL SKETCH**

Author: Kiran K. Gururaj

Degree: Master of Science

Date: August 2002

Date of Birth:

Place of Birth:

#### Education

- Master of Science in Electrical Engineering, New Jersey Institute of Technology, Newark, NJ, 2002

- Bachelor of Engineering in Electronics and Communications Engineering, Bangalore University, Bangalore, KA, INDIA

Major: Electrical Engineering

#### **Publications:**

Kiran K. Gururaj, Lev Zakrevski and D. Misra, "VLSI Architecture for Deadlock Avoidance in Wormhole Networks", Proceedings of Fifteenth International Conference on Systems Engineering, ICSE 2002, pp. 322-328, Aug 2002. To My Parents and the Almighty

#### ACKNOWLEDGEMENT

The author wishes to express his sincere gratitude to his Graduate Advisor and Thesis guide Professor D. Misra, for his guidance, moral support and encouragement throughout this work.

Special thanks to Assistant Professors Lev Zakrevski and Symeon Papavassiliou for serving as the members of the committee.

The author also thanks Prof. D. Misra and NJ center for Optoelectronics for the financial assistance during Fall 2001 and Spring 2002.

The author also thanks the Computing Services Division of NJIT for providing the necessary tools and also appreciates the services rendered by them.

Finally, the author would like to thank his beloved parents for giving the encouragement and moral support throughout his course of study at NJIT.

| Chapter H |                                                 |    |

|-----------|-------------------------------------------------|----|

| 1         | INTRODUCTION                                    | 1  |

|           | 1.1 Applications and Importance of NOW          | 3  |

|           | 1.2 Design Flow of the TPBR Chip                | 3  |

|           | 1.3 Outline of the Thesis                       | 4  |

| 2         | OVERVIEW OF THE ROUTING CONCEPTS                | 6  |

|           | 2.1 Wormhole Routing                            | 6  |

|           | 2.2 Deadlock in a Network                       | 8  |

|           | 2.3 Routing Strategies                          | 10 |

|           | 2.4 Up/Down Routing Technique                   | 11 |

| 3         | TPBR ALGORITHM AND ITS MATHEMATICAL MODEL       | 13 |

|           | 3.1 The Algorithm                               | 13 |

|           | 3.2 Mathematical Model                          | 16 |

| 4         | ARCHITECTURAL DESIGN OF THE CHIP                | 20 |

|           | 4.1 Overview of the system                      | 20 |

|           | 4.2 Architecture of the Chip                    | 22 |

|           | 4.3 Token Unit Design                           | 23 |

|           | 4.4 Turn Prohibition Unit                       | 27 |

|           | 4.5 Routing Table Construction                  | 30 |

|           | 4.5.1 Mathematical Model for Table Construction | 30 |

# TABLE OF CONTENTS

# TABLE OF CONTENTS (Continued)

| C | Chapter Pag                                              |    |  |

|---|----------------------------------------------------------|----|--|

| 5 | THE VHDL MODEL FOR TURN PROHIBITION                      | 34 |  |

|   | 5.1 Description of the Model                             | 34 |  |

|   | 5.2 Simulation of the Model                              | 38 |  |

| 6 | SYNTHESIS OF THE MODEL                                   | 44 |  |

|   | 6.1 Synthesis Problems                                   | 44 |  |

|   | 6.2 Synthesis of the model with Cadence Ambit BuildGates | 45 |  |

|   | 6.3 Post Synthesis Simulation                            | 50 |  |

| 7 | LAYOUTS                                                  | 54 |  |

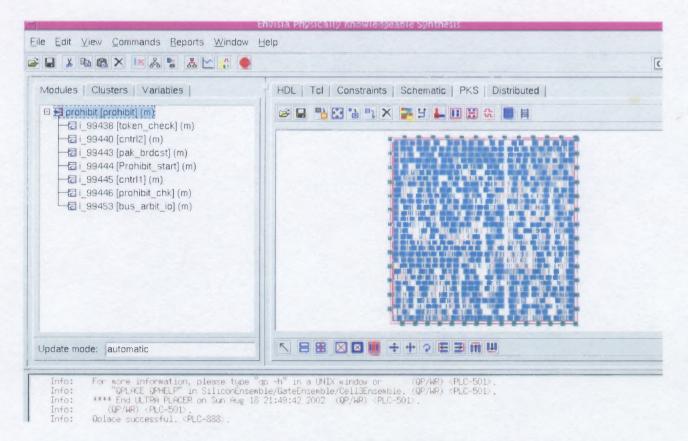

|   | 7.1 Place and Route with Cadence Silicon Ensemble        | 54 |  |

|   | 7.2 DRC and PE with Cadence IC                           | 58 |  |

| 8 | CONCLUSIONS                                              | 60 |  |

| A | PPENDIX A VHDL CODE                                      | 62 |  |

| A | PPENDIX B TOP LEVEL VHDL CODE                            | 84 |  |

| R | EFERENCES                                                | 88 |  |

# LIST OF FIGURES

| Figure |                                                                 |    |

|--------|-----------------------------------------------------------------|----|

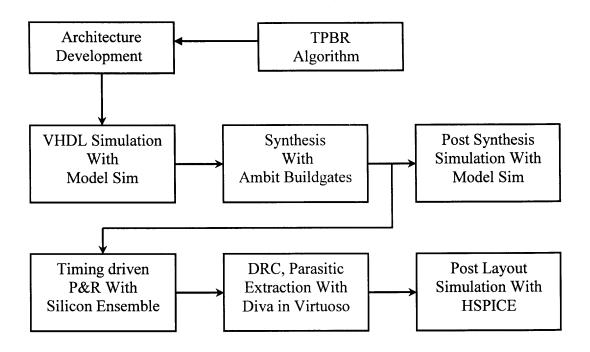

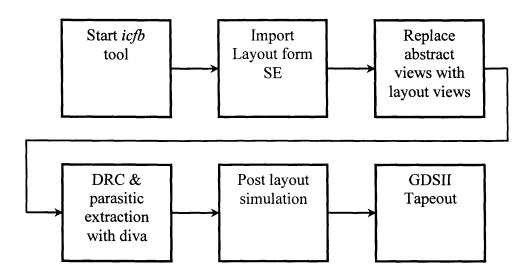

| 1.1    | Design flow for implementing the TPBR algorithm on a chip       | 4  |

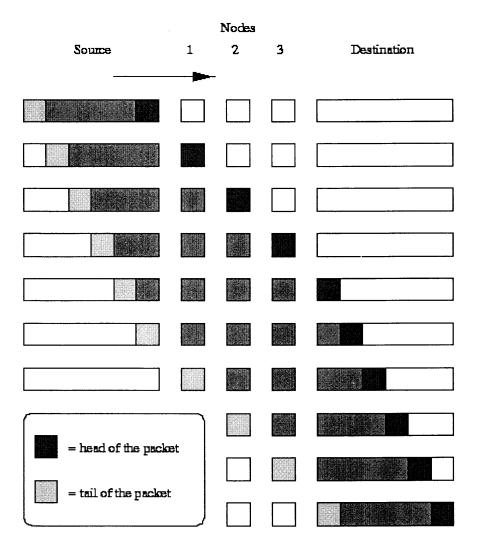

| 2.1    | Wormhole Routing in a Network                                   | 6  |

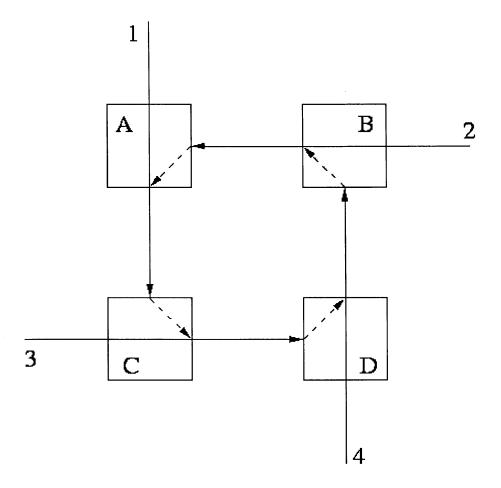

| 2.2    | Deadlock in a Network                                           | 8  |

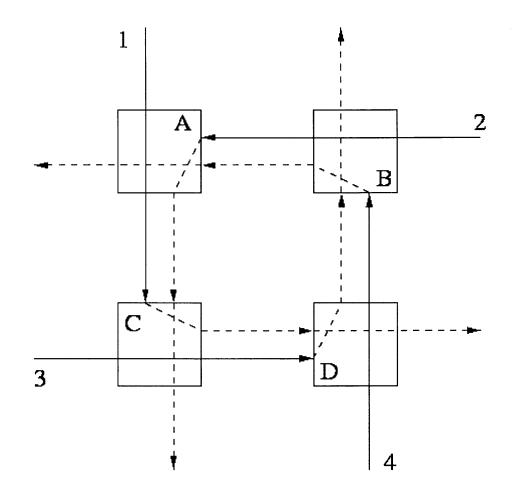

| 2.3    | Possible solutions for avoiding Deadlock                        | 9  |

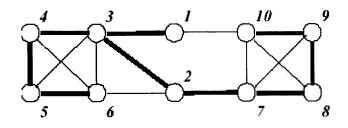

| 3.1    | Network showing the connectivity to show continuity             | 17 |

| 4.1    | Overview of the Workstation in a Network                        | 20 |

| 4.2    | A Network composed of TPBR routers                              | 21 |

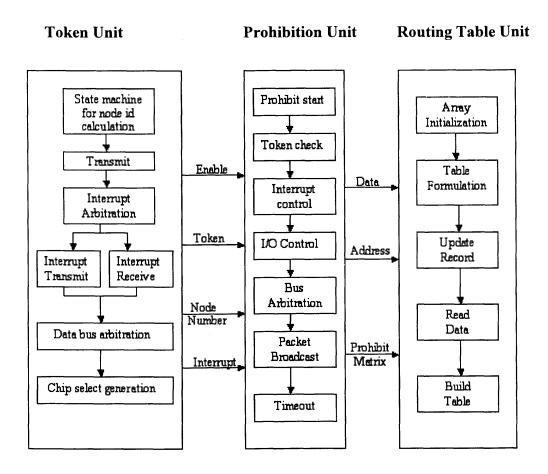

| 4.3    | Architecture of the chip                                        | 22 |

| 4.4    | Architecture of the Token Unit                                  | 24 |

| 4.5    | Structure of the Data field in a type 1 packet                  | 25 |

| 4.6    | Data structure of each slot in a packet                         | 25 |

| 4.7    | State Transition Diagram for Token Unit                         | 26 |

| 4.8    | Entity of the Turn Prohibition Unit                             | 27 |

| 4.9    | Architecture of the Turn Prohibition Unit                       | 28 |

| 5.1    | Block Diagram for the model designed in VHDL                    | 36 |

| 5.2    | High-Level Timing Simulation for the mentioned sequential tasks | 37 |

| 5.3    | Timing Simulation contd after Figure 5.2                        | 41 |

| 5.4    | Timing Simulation contd after Figure 5.3                        | 42 |

| 5.5    | Timing Simulation contd after Figure 5.4                        | 43 |

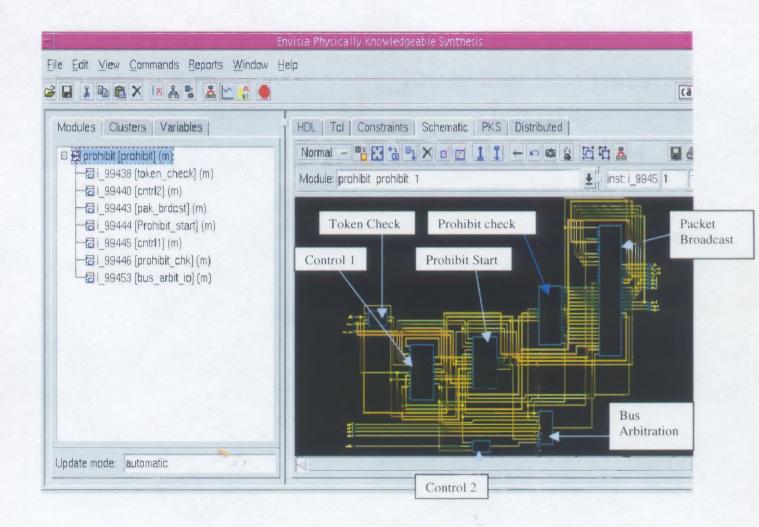

| 6.1    | Optimized synthesis for the Turn Prohibition and Token Unit     | 47 |

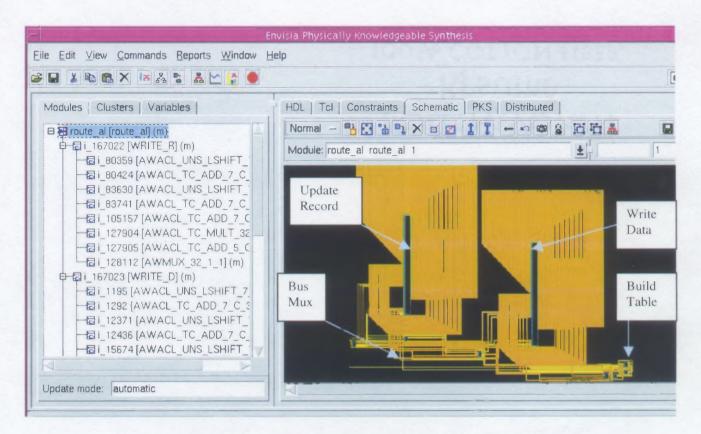

| 6.2    | Optimized synthesis for the Routing Table Unit                  | 48 |

# LIST OF FIGURES (Continued)

| Figure |                                                                       | Page |

|--------|-----------------------------------------------------------------------|------|

| 6.3    | PKS showing the placement of all the cells                            | 49   |

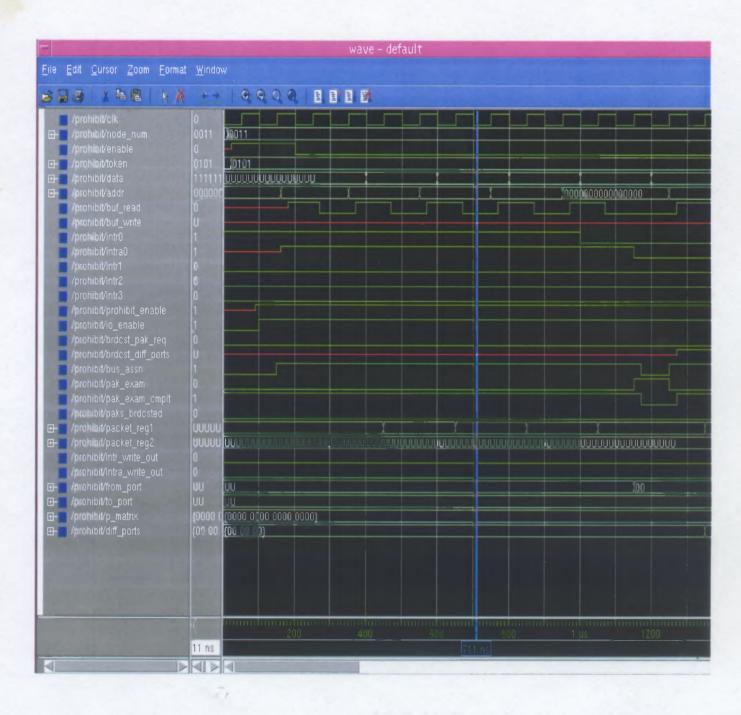

| 6.4    | Post Synthesis Simulation for the model designed                      | 51   |

| 6.5    | Post Synthesis Simulation continued from Figure 6.4                   | 52   |

| 6.6    | Post Synthesis Simulation continued from Figure 6.5                   | 53   |

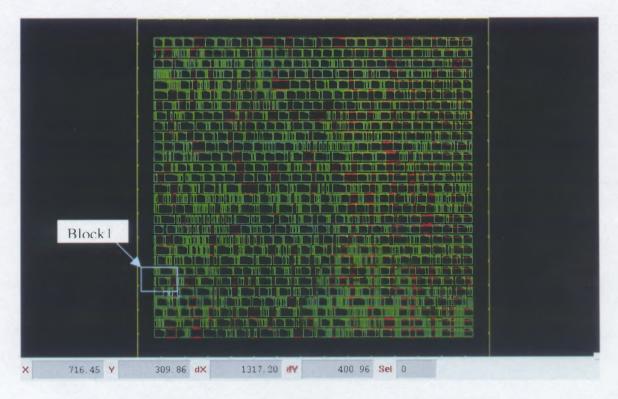

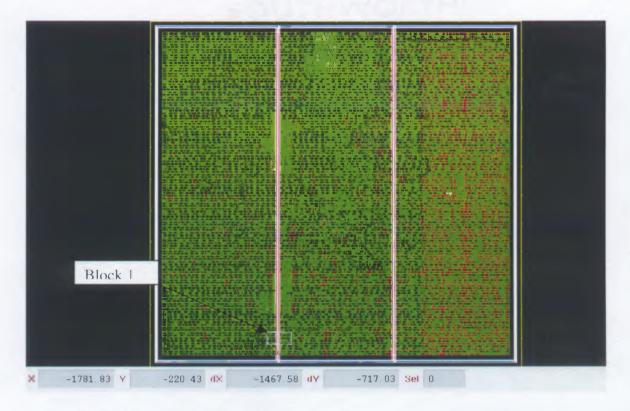

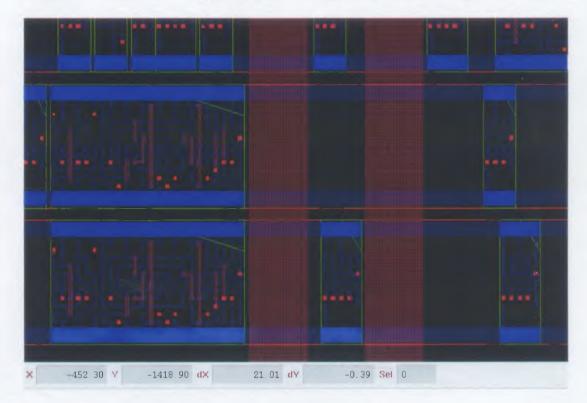

| 7.1    | Layout of a block without power stripes                               | 56   |

| 7.2    | Expansion of 'Block 1'shown in Figure 7.1                             | 56   |

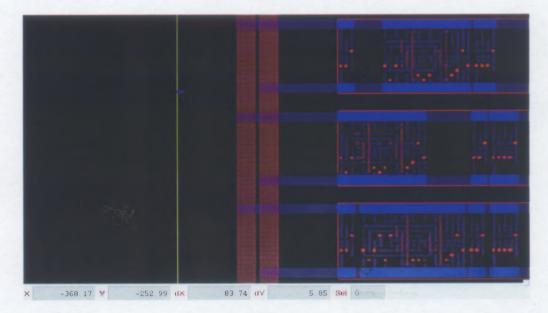

| 7.3    | Layout of the chip with Power and ground rails and striped in between | 57   |

| 7.4    | Expansion of 'Block 1'shown in Figure 7.3                             | 57   |

| 7.5    | Cadence IC Design Flow                                                | 59   |

#### **CHAPTER 1**

#### **INTRODUCTION**

#### **1.1 Applications and Importance of NOW**

Over the past few years, networks with irregular topologies like the Network Of Workstations (NOW) have become an alternative to the parallel multiprocessors. In order to reduce the communication latency, memory requirements and achieve high bandwidth in data communications, the NOW use wormhole routing. However wormhole routing is very much prone to deadlocks as packets are allowed to hold one node while requesting for others. Deadlock avoidance is the most critical issue while considering wormhole networks. Deadlock is an undesired feature that should be avoided by any routing protocol and algorithm because a lot of network resources will be wasted and the performance of the network will be degraded due to the abuse of network resource by deadlock routing. Therefore, design of deadlock-free routing protocols is important to the performance of a NOW. Although NOW do not provide the computing power available in multi-computers and multiprocessors, they meet the needs of a great variety of parallel computing problems at a lower cost. By using the Turn Prohibition Based Routing algorithm (TPBR), deadlocks in the networks can be avoided by eliminating the turns in the networks. In wormhole routing each packet consists of a sequence of elementary flow control units called flits. As long as the transmission route is free, flits are forwarded to their destination in a pipelined manner. The main advantage compared to the store and forward switching is that the latency is reduced since there is no need to wait for the end of the packet before transmitting flits to the next node. However these contiguous flits in

a packet are always contained in the same or adjacent nodes of the network. This can cause difficulties, as possibility of deadlock arises. Deadlock in the interconnection network occurs when no message can advance towards its destination because the queues of the message system are full. As the header flit advances along a specified route, the subsequent flits follow up in a pipelined fashion. This technique provides for low communication latency, almost independent of the distance between the source and the destination. Whenever the header flit is blocked at an intermediate node by another message, the remaining flits stop advancing thus blocking each other. When considering wormhole routing it must either have an effective procedure of recovery after deadlocks or must be deadlocks free which is implemented in the form of a protocol. To prevent deadlocks the necessary and sufficient condition is to eliminate the cycles in a channel dependency graph. This can be achieved by eliminating the turns in the graph, which will form closed loops in the network. Even though there exists other algorithms that implement the wormhole routing, the TPBR algorithm proves to be a better solution for eliminating the deadlocks in the networks.

Networks of Workstations (NOW) are comprised of a collection of routers, communication links and workstations in an irregular topology. They have been applied as an alternative to parallel multiprocessors. In a NOW, the message routed through the network is subject to *deadlock*, which means the path between source and destination forms a loop. Therefore, by applying TPBR algorithm, deadlock can be broken and the flexibility of routing can still be maintained because of the small number of prohibited turns. However, in TPBR algorithm works as a centralized algorithm which needs knowledge of the network topology to determine the prohibited turns. For decentralized

network equipment such as a router, it is difficult for it to get knowledge of the network topology, especially for large-scale networks. In this thesis a protocol for TPBR algorithm to be performed in a decentralized manner is shown, which is implemented on a VLSI chip.

#### 1.2 Design Flow of the TPBR Chip

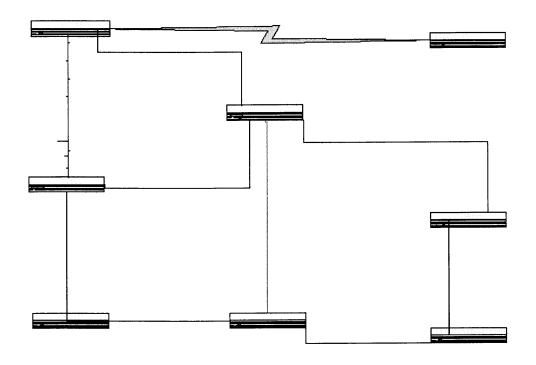

In this thesis, a novel architecture of the TPBR algorithm is proposed, which will make the Network Of Workstations deadlock free. This architecture will be the basis for implementing the Turn Prohibition Based Routing algorithm in VHDL and designing an ASIC. The design flow for implementing the algorithm as an ASIC is as shown in Figure. 1.1. Mostly Cadence tools were used, except Model Sim for VHDL simulations and HSPICE for spice simulations.

The VHDL model for the algorithm is compiled and simulated using Model Sim. The VHDL model is synthesized using Cadence Ambit Bulidgates. The design is synthesized, mapped to the cells in the library for timing calculations. The output from this tool gives us a Verilog file, which has gate level design information, a GCF file, which has timing information and a DEF file which has placement information.

The placement and Routing of the standard cells is done using Cadence Silicon Ensemble. The design, placement and timing information is read from the above produced files and timing driven routing is done. The DRC and parasitic extraction is done in Cadence Virtuoso environment. The extracted spice file is simulated using HSPICE.

Figure 1.1 Design flow for implementing the TPBR algorithm on a chip.

#### **1.3 Outline of the Thesis**

The remainder of the thesis is organized as follows. Chapter 2 provides an overview of Wormhole routing, Deadlocks in a network, various routing strategies present till date and also the Up/Down routing technique. Chapter 3 provides a detailed description of the TPBR algorithm and its advantages over Up/Down routing technique. Chapter 4 describes the proposed architecture of the chip and its various components. Chapter 5 describes the VHDL model and different implementation issues, and it includes the test and the simulation results. Chapter 6 addresses the synthesis issues and problems encountered during the synthesis and modifications of the actual VHDL model to make it synthesizable. Then the simulations of the gate level verilog netlist after synthesis are

listed. Chapter 7 describes the physical layout and device level simulation of the final layout. Chapter 8 concludes this thesis by summarizing the results of the work and discussing alternative implementations for reducing the gate count.

#### CHAPTER 2

# **OVERVIEW OF ROUTING CONCEPTS**

# 2.1 Wormhole Routing

Packets in a network can be transmitted in many ways, including one called wormhole routing. In wormhole routing, packets are divided into smaller parts of equal size called flits (= flow-control digit), which are then transmitted one by one, instead of transmitting the packet as a whole. All the flits of the same packet follow the same path and cannot overtake each other.

Figure 2.1 Wormhole Routing in a Network.

Furthermore, each node on the path of the packet can contain only one flit of that packet and will always try to transmit it to the next node. Because the movement of the packets resembles the movement of a worm, the packets sometimes are called worms themselves. An illustration of how a packet moves through a network is given in Figure. 2.1

In wormhole routing the following is done:

1. The source node starts transmitting the flits one by one to the next node, beginning with the head of the packet.

2. The nodes on the path of the packet receive the flits, but can store only one flit at a time. If a flit is present in a node, other flits cannot enter this node, which means that the previous node cannot send its flit.

3. A node always tries to send the flit which it receives on to the following node, unless the node itself is the destination node.

4. The destination node receives the flits one by one until the last flit of the packet has been received.

It must be noted that, in wormhole routing, it is impossible for flits of another packet to cross the path of the current packet. This means, that even if a node is empty, flits of the other packet cannot use this node, unless the last flit of the current packet has passed it. This characteristic of wormhole routing introduces a problem called deadlock.

#### 2.2 Deadlock in a Network

Deadlock in a network occurs when packets are blocking each other, thus effectively preventing them from moving to their desired destination.

Figure 2.2 Deadlock in a network.

In this Figure. 2.2, packet 4 tries too make a left turn at node B, but is being blocked by packet 2, which tries to make a left turn at node A and is being blocked by packet 1 and so on. It becomes clear, that these four packets are stuck and cannot move, until something radically is being done, like randomly removing one of the four packets. However, this cannot be the solution to the problem.

The packets in Figure. 2.2 block each other, because they all are using the same kind of channel. A possible solution to the problem in Figure. 2.2 is given in Figure. 2.3.

In this Figure, the problem is being solved by introducing two kinds of channels. First, there are the channels (dotted), which will be used by packet, which have made a turn, and second, there are the channels (solid), which will be used by packets, which do not have made a turn yet. Because the packets in the nodes A through D are assigned to different kinds of channels, they will not block each other any longer. In the example above, the solution was to introduce a new kind of channel, namely, the one if a packet has to make a turn. However, the previous solution only works, if other parts of the network can be neglected, and, if the following assumption holds: the packets in the network only have a maximum of ONE turn to make.

Figure 2.3 Possible solutions for avoiding Deadlock [3].

#### **2.3 Routing Strategies**

In an intercommunication network, routing algorithms that are used for determining the path to the destination node can be classified according to their:

• Number of destinations- Unicast: packets may have a single destination, Multicast: packets may hay multiple destinations

• Place where routing decisions are taken- **Centralized**: by centralized controller, Source: by the source node, Distributed: determined in a distributed manner while the packet travels, Multiphase: hybrid, source node computes some destinations, path established in a distributed manner. **De-centralized**: The source and destination is not pre-determined.

• Way of implementation- Table-Lookup: looking at a routing table, Finite-State Machine: executing a routing algorithm in software or hardware according to a finitestate machine

• Adaptivity- Deterministic: always supply the same path between a source/destination pair,Adaptive: use information about network traffic and/or channel status to avoid congested or faulty regions of the network. **Non-deterministic:** can be of any path

• Progressiveness- **Progressive**: move the header forward, reserving a new channel at each routing operation, Backtracking: allow header to backtrack, releasing previously reserved channels (used for fault-tolerant routing)

• Minimality- **Profitable (minimal)**: supply channels that bring the packet closer to its destination, Misrouting(non-minimal): may also supply channels that send the packet away from its destination

• Number of alternative paths- Fully Adaptive, Partially Adaptive, Non -Adaptive.

#### 2.4 UP/DOWN routing technique

In Up/Down routing, one of the nodes is chosen arbitrarily as the root of a tree and all links of the topology are designated as 'up' or 'down' links with respect to this root. The 'up'/'down' state of a link is relative to a spanning tree computed in the background by a distributed algorithm. A link is 'up' if it points from a lower to a higher level node in the tree (i.e, to a node at a lesser distance from the root). Otherwise, it is 'down'. For nodes at the same level, node IDs breaks the tie. The routing from a source to a destination is done in such a fashion that zero or more 'up' links (towards the root) are traversed before zero or more 'down' links are traversed (away from the root) in order to reach the destination. This prevents circular waits and thus the routing is deadlock-free.

Myrinet runs a `mapping' algorithm that computes the current topology in the background. Myrinet uses up/down routing to build these paths [9]. Although the original distributed up/down routing scheme provides partial adaptivity, in Myrinet only one of the routes is selected to be included into the routing table, thus resulting in a deterministic routing algorithm. On the other hand, many paths provided by the up/down routing are non-minimal on certain networks. Myrinet uses up/down routing to build network routes. Up/down routing is based on an assignment of direction to the operational links. To do so, spanning tree is computed and then, the "up" end of each link is defined as:

- The end whose switch is closer to the root in the spanning tree;

- The end whose switch has the lower ID, if both ends are at switches at the same tree level.

The result of this assignment is that each cycle in the network has at least one link in the "up" direction and one link in the "down" direction. To eliminate deadlocks while still allowing all links to be used, this routing uses the following up/down rule:

A legal route must traverse zero or more links in the "up" direction followed by zero or more links in the "down" direction. Thus, cyclic dependencies between channels are avoided because a message cannot traverse a link along the "up" direction after having traversed one in the "down" direction.

Up/down routing can supply several valid routes between two network hosts and, in some cases, there exist more than one shortest up/down route. Therefore, it is stored in the table a set of routes for each source-destination pair, including the best ones, and selecting one of them according to some criteria [5].

The following path selection algorithms:

$\mathcal{A}_{i}$

- OSUD (One Shortest Up/Down path): Always the same shortest up/down path. This is the current routing policy used in Myrinet.

- *RSUD (Random Shortest Up/Down path)*: Randomly selection among all the shortest up/down paths.

- *RRSUD (Round-Robin Shortest Up/Down path)*: Round-robin selection among all the shortest up/down paths.

- *PUD (Probabilistic Up/Down path)*: 80% of selected paths using RSUD, and 20% randomly chosen among up/down paths that are one hop longer than the shortest up/down path. Even though Up/Down routing technique is being used nowadays and is proved advantageous in regular networks, it fails to eliminate deadlocks when used in Wormhole networks.

#### CHAPTER 3

#### **TPBR ALGORITHM AND ITS MATHEMATICAL MODEL**

#### 3.1 The Algorithm

In wormhole routing, a router begins forwarding a packet as soon as the header is received and the required channel buffer in the next router can accept one or more flits of the packet. Flits are transmitted from one router to the next in a pipelined fashion and may occupy several channels along the path from source to destination. Only the header flit of a packet contains information required for routing. If the header flit is blocked because the required buffer in the next router along it's path is full, all of the flits in the packet are blocked. Design of efficient deadlock-free routing algorithms in irregular topologies introduces new challenges.

The steps involved in the algorithm are:

1) Finding out the number of turns in the network.

2) Prohibiting some of the turns in a network over the nodes, this still can make the tree connected.

3) Drawing a spanning tree based on the nodes through which turns are not eliminated.

4) Getting the route from source to the destination.

Now let us consider the prohibition of the some of the turns in a network. Here it is assumed that a network consists of N nodes connected by E edges, constituting a graph G. A node is considered as the router component of the processor-router pair In order to tackle the problem of deadlock, the TPBR algorithm is used to eliminate the number of turns in a network. Every routing algorithm prohibits some of the turns in network graph. A turn (a, b, c) is a three-tuple of nodes such that (a, b) and (b, c) are edges in the

network graph G. In order to correctly model existing switch based networks such as Myrinet, it is assumed that G is symmetric, i.e. if (a, b) is an edge in G, then (b, a) is also an edge in the network.

At the first step, a node with the minimal degree is selected and labeled as node1. If after deletion from G of node1 and all edges neighboring node1, the remaining graph G-1 is still connected, then all d (d -1)/2 turns like (a, 1, b) are prohibited and all turns (1, b, c) are permitted where d is the degree of the node. If after deletion from G of node1 and all edges adjacent to node1 the remaining graph G-1 consists of disconnected sub graphs G<sub>1</sub>...G<sub>s</sub>, (this procedure is used also for s=1) then select nodes a1...as (called *tree* nodes) such that ai is a node of  $G_i$  and (ai, 1) is an edge in G. All edges (ai, 1) are added to the spanning tree. All constructed tree nodes, except one, are added to the set of *basic* nodes B (initially B=0). At the next step the procedure is repeated to the remaining graph G-1, labeling non-basic node with a minimal degree by 2. At each step, basic nodes are selected in such a way, that every component of connectivity has only one basic node. Process is completed, when all nodes are labeled.

Implementing TPBR algorithm in a distributed way which is a requirement of today's' network equipments comes into two aspects. Firstly start the turn prohibition from the node which has minimal  $(d_a^2-2)/\sum (d_i-1)$  where  $d_a$  is the degree of the node that is to be considered d<sub>i</sub> is the degree of the i<sup>th</sup> surrounding node. However, each node does not have any idea on the degree of other nodes in the network. Secondly each node does not have a big picture of the topology of the network, therefore, it is unable to know if a turn is removed from that node, the rest of the network is still connected or not.

To address these problems, a protocol based on the TPBR algorithm is developed, which involves three steps.

# **Step 1:** Calculation of $(d_a^2 - 2)/\sum (d_i - 1)$ .

a. Each node broadcasts its degree to its neighboring nodes.

b. When a node receives the degree value from other nodes, it stores it.

c. When a node gets knowledge of all the nodes neighboring to it, then it will perform a sorting algorithm and determine which turn has to be prohibited.

Step 2: Turn prohibition unit.

a. Each time there is only one node in the entire network, which is trying to determine its prohibited turn.

b. Components of connectivity are constructed in the graph without the selected node. Then it makes an edge special if any, by checking if there is a discontinuity in the graph. The node, which is connected to special edge other than selected node, is marked as special node.

c. TPBR algorithm doesn't select the special node.

d. Likewise the algorithm is carried out recursively until all the nodes are evaluated.

Step 3: Routing table construction.

a. In our TPBR protocol, the Bell-Ford algorithm is extended because it has better decentralized feature than the Dijkstra's algorithm.

b. After each node determines its prohibited turn, then a routing table is constructed. This can be achieved by extending any routing algorithm such as Dijkstra's algorithm or Bell-Ford algorithm. The prohibited turns should be take into account, therefore some paths

cannot be taken even though they have a shorter distance, due to the existence of prohibited turns.

#### **3.2 Mathematical Model**

Assume that the original network consists of N nodes, connected by E edges. Also assume that all nodes are connected (for any two nodes there exists a path between them). In the general case network graph G can be considered as a multigraph with several edges between two nodes. In particular, if V virtual networks are used, any two nodes are connected either by 0, or by V edges.

The total number of turns in  $T=\sum(di \ (di - 1))/2$ , where di is a degree (number of neighbors) of node i. For example, for the up/down routing a spanning tree for G is constructed, nodes are labeled preserving the partial order defined by the tree (the root has label 1) and turn (a,b,c) is prohibited if b>a and b>c.

It is seen that the results on lower and upper bounds on fractions z=z(N,E) of turns which have to be prohibited to prevent deadlocks in a given network graph [2,3,7]. The proposed upper bound is constructive, i.e. its proof generates a simple algorithm (its is called z-algorithm) for construction of a tree and labeling of nodes by 1, 2, ..., N such that turn (a,b,c) is prohibited iff at least one of the edges (a,b) or (b,c) does not belong to the tree and a>b and c>b.

Denote by Z(N,E) a minimal fraction of prohibited turns for prevention of deadlocks in network graph G with N nodes and E edges. Let di be a number of neighbors (degree) of node i and T be the total number of turns 2E = S(i=1 to N)d(i), T=S(i=1 to N)d(i)\*(d(i-1)/2) The following lower bounds for Z(N,E) [10] will be useful to estimate performances of the routing strategies that will be described later. First note, that  $Z(N,E) \ge (E-N+1)/T$  (Bound A). This bound follows from the fact that there are b = E-N+1 linearly independent cycles in G and each one of these cycles has to contain at least one prohibited turn to prevent deadlocks.

Figure 3.1 Network showing the connectivity to show continuity.

For the example shown in Figure. 3.1 it can be seen that N=10, E=17, T=44 and by Z(N,E) >= 8/44. Let C={C1, ...CR} be a system of cycles in G and m is a maximal number of cycles from C containing the same turn[1,2].

Then  $Z(N,E) \ge R/mT$  (Bound B). If m=1, then  $Z(N,E) \ge R/T$ , where R is a maximal number of cycles in the network graph such that every turn belongs to at most one cycle. one can select as C the system of all 9 triangles and one cycle of length 5 (R=10). In this case cycles don't have common turns (m=1), and by  $Z(N,E)\ge 10/44$ . Bound A is useful when a number of cycles in G is small and Bound B can be used for a networks with large numbers of cycles.

Let us now consider graph G=(V,E), with |V|=N nodes (denoted by a,b,...), connected by |E|=M edges (denoted by (a,b) etc.) Considering the non-oriented case, so (a,b)=(b,a). Without losing generality, assume that all nodes are connected (for any two nodes there exist a path between them). If this is not the case, also consider all components of connectivity separately. A path  $P=(v_0,v_1,...,v_L)$  of length L ( $L\geq 1$ ) from node a to node b in G is a sequence of (not necessarily different) nodes  $v_i \in V$ , such that  $v_0=a$ ,  $v_L=b$ , and every two subsequent nodes are connected by an edge, and every ordered pair of subsequent nodes appears exactly once. Length L of the path is the number of edges, included in it. Set W of turns in G is called cycle breaking (11,12,13) if every cycle in G is covered by at least one turn from W. A solution is presented below a for the problem of finding in a given graph a minimal cycle-breaking set of turns. Cyclebreaking set of turns W is called *irreducible*, if there are no cycle-breaking subsets of W, which are not equal to W. (Also note that not every irreducible cycle-breaking set is a minimal one).

For example, for  $2d p \times p$  meshes  $N=p^2$ , M=2(p-1)p,

$$T(G) = 6(p-2)^{2} + 12(p-2) + 4,$$

algorithm.)

$z(G) \ge \frac{p^2 - 2p + 1}{6p^2 - 12p + 4}$ , and the lower bound for z(G) in this case is close to 1/6 for large meshes [1]. (Note that for the North-Last algorithm and 2-d meshes the fraction of prohibited turns is equal to lower bound 1, which proves optimality of the North-Last

For the example as in Figure. 3.1, N=10, M=17, T(G)=44 and by bound 1,  $z(G) \ge 8/44$ .

If r=1, then according to bound 2,  $z(G) \ge R/T(G)$ , where R is a maximal number of cycles in the G with disjoint sets of turns. For the example shown in Figure. 3.1 one can select as C the system of all 9 triangles and one cycle of length 5 (R=10). In this case cycles have no common turns (r=1), and by bound 2,  $z(G) \ge 10/44$ . Bound 1 is useful when a number of cycles in G is small and bound 2 can be used for graphs with large numbers of cycles. To generalize bound 2, Denote for system C of R cycles by  $r_j$ , the number of cycles covered by turn j and assume that  $r_1 \ge r_2 \ge ... \ge r_T$ . Then

Z(G) should satisfy the following condition:  $\sum_{i=1}^{Z(G)} r_i \ge R$  [3]. By this it can be said that the

TPBR algorithm gives us a optimal set of prohibited turns which will be good enough to keep the network deadlock free. This model helps us to determine the set of turns, but the set of turns got is not irreducible but is optimal.

#### **CHAPTER 4**

#### **ARCHITECTURAL DESIGN OF THE CHIP**

#### 4.1 Overview of the System

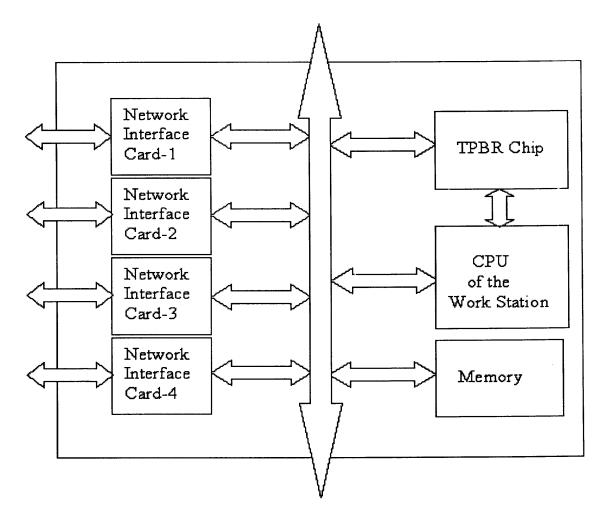

The proposed VLSI architectural design of the whole chip is discussed in this section. Figure. 4.1 gives an overview of the whole system, which can be considered as a single node in an irregular network.

Figure 4.1 Overview of the Workstation in a Network.

As 4-port router is taken into consideration, therefore four network interface cards for each router is taken, which means that four systems can be connected to each of the workstation thus enabling each of the workstation to perform in a parallel fashion thus using the concept of the parallel multiprocessors. The Central Processing Unit (CPU) of the workstation is linked to the Turn Prohibition Based Routing (TPBR) chip, which decides the route the packet should take from the source to the destination keeping the prohibited turns into consideration.

The TPBR chip is responsible for running the proposed TPBR protocol. When the protocol running is finished, the routing table will be stored in the memory. Then CPU can utilize the routing information to receive and transmit message in the networks. A typical network composed of such routers is shown in Figure. 4.2

Figure 4.2 A Network composed of TPBR routers.

#### 4.2 Architecture of the chip

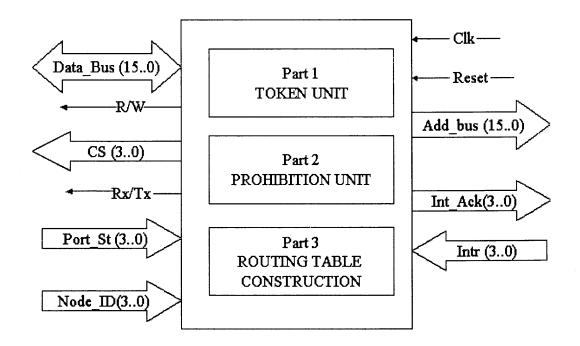

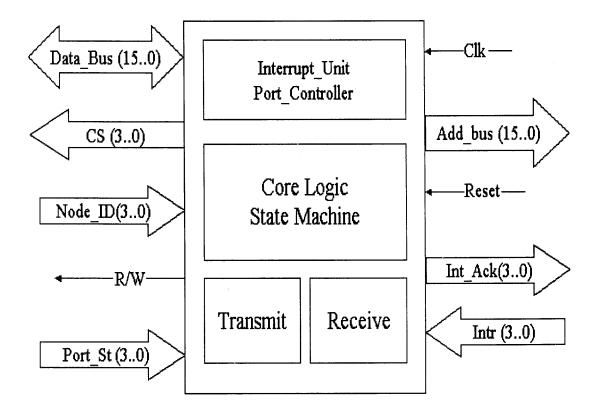

This chip is the controller of the router, so this chip has data bus, address bus, clock signal and some control signals such as reset, chip select (cs), interrupt signals (int\_req) and interrupt acknowledge signals (int\_ack), read and write signals (rw) as shown in Figure. 4.3. In order to get the local information of the decentralized router, the chip has port status input signals, it can be used to detect which port of the router, (also assume each router has four ports) is connected with other neighbor routers. Since each router has its own node id which is used to be identified by itself and located by others. Assign 4 bit input signal for node\_id (3..0). Reset signal is used only during initialization or system failure. Figure. 4.3 demonstrates the architecture of the TPBR chip, which is mainly divided into three sub parts, which individually takes care of a specific function for determining the prohibited turns and thus making the network deadlock free.

Figure 4.3 Architecture of the chip.

These three parts are invoked sequentially one after the other starting from the token unit then the prohibition unit and finally the routing table construction unit. After the process is completed then the routing table will have the route from each particular source to all the other nodes in the network.

#### 4.3 Token Unit Design

The architecture of the token unit is shown in Figure. 4.4. In protocol step 1, each node needs to claim its degree in the network. This information needs to be broadcasted in the entire network. This is the important step in the process of Turn Prohibition, as each node should be aware when and on what all nodes the TPBR has to be run. By giving each node an identity, the nodes will run the algorithm in the way they were assigned the numbers. Only the 'node 0' should be able to claim its degree in a packet type so that is set as 1. Other nodes simply wait for the first packet. The data structure of data field in type 1 packet is shown in Figure. 4.5.

Each node in type 1 packet has a fixed slot for it to claim its own degree information. Whenever it receives a type 1 packet, it checks whether every node has claimed its degree in the packet. This is accomplished by checking the *counter* field, which is incremented by the node when it provides its degree information in its slot as shown in Figure. 4.5. The W bit is used to check whether a node has claimed its degree in this packet. If every node has claimed the degree in the packet, the node that receives the packet will check the R bit in its slot. Based on the functionality of the token unit, it is divided it into several sub-parts, such as interrupt\_unit, port controller, core\_logic unit, transmit unit and receive unit as shown in Figure. 4.4. Core\_logic unit is an essential unit

of this token unit. It is used as the main frame of the design. The transmit and receive process is used to send and receive the packets which will be broadcasted in the network.

Figure 4.4 Architecture of the Token Unit.

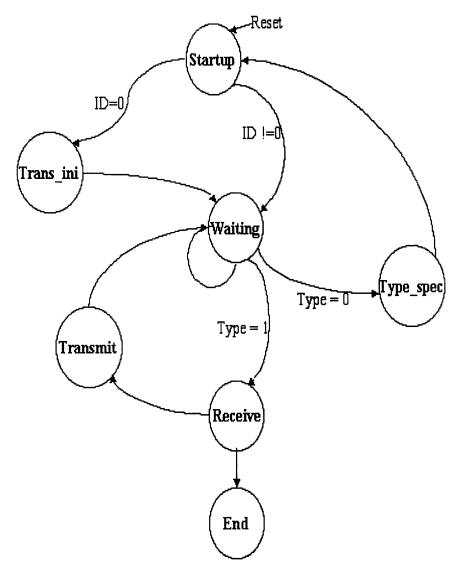

The above protocol design for the Token Unit can be seen in Figure. 4.7 in the form of state transition diagram. In startup state, the chip will be initialized, which includes initializing the registers inside the chip, getting the node\_id and also the port\_status. In trans\_ini state, a packet will be formed according to the format of the packet, which is 16-byte long, and then transmitting it to all the nodes, which are connected with 'node 0'. Only 'node 0' will enter this state. In trans\_spec state, after receiving a packet whose type code is 0, the state machine will enter the trans\_spec state. It will transmit a packet to other nodes. In the transmit state, it is in charge of transmitting

packets to the outside node. In the waiting state, the node will simply wait for an incoming packet and when a packet comes, check its type. If packet is type 0, it will go to trans\_spec state; if type1, it will go to Receive state. In the Receive state, the process will perform the data field check and perform the protocol as described in Figure.4.5 and Figure. 4.6.

| Counter (8 bit) | Degree of Node 0 | Degree of Node 1 | Degree of Node 2 |  |

|-----------------|------------------|------------------|------------------|--|

|                 |                  |                  |                  |  |

Figure 4.5 Structure of a data field in a type 1 packet.

|  | R (Read) (1 bit) | W (Write) (1 bit) | Degree of the Node (2 bits) |

|--|------------------|-------------------|-----------------------------|

|--|------------------|-------------------|-----------------------------|

Figure 4.6 Data structure of each slot in a packet.

In the Token Unit, the Interrupt Unit controls the four interrupts from the outside port and generates the interrupt signal to the receive unit and also generates port number for receive unit. It receives the interrupt\_ack signal from the receive unit. After interrupt unit gets the interupt\_ack signal it begins to wait for a new interrupt from the other port. The Receive Unit gets signal from Interrupt unit and outputs the signal and data to Core Logic unit. After getting the interrupt signal from interrupt unit, receive unit checks which port has data and controls the address bus, data bus , r/w and cs signal to receive data from that port. After receiving data it generates the receive\_data and port number signal for the Core Logic and then waits until Core Logic unit sends the rxd ack signal back to receive unit, and sets the mode to active. Transmit Unit get signal from Core Logic and transmit data to the outside port. After transmitting the data it gives back a txd\_ack signal to the Core Logic. After the process is done then the transmit unit will wait for new data to transmit.

Figure 4.7 State Transition Diagram for the Token Unit.

### **4.4 Turn Prohibition Unit**

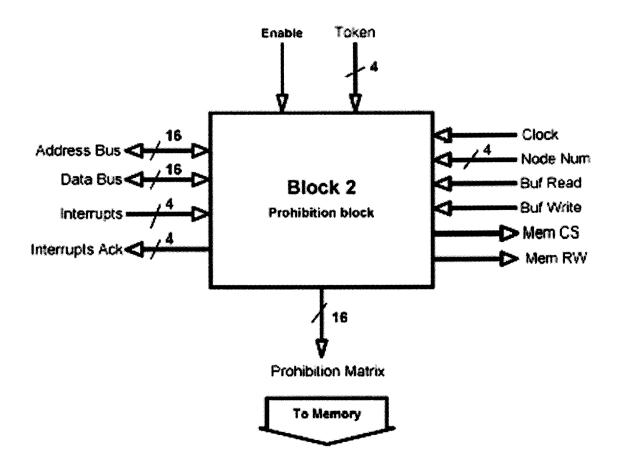

In this block, as in the case of most routing algorithms certain turns in the network graph are prohibited. Consider a turn (a, b, c). The turns (a, b, c) and (c, b, a) are prohibited if some other path exists between nodes 'a' and 'c'. To implement this, a flat packet is broadcasted from all the ports of the node. Components of connectivity are constructed in the graph without the selected node. Then it makes an edge special if any, by checking if there is a discontinuity in the graph. The node, which is connected to special edge other than the selected node, is marked as special node. As seen in the Figure. 4.8, this block gets the 'enable' signal and 'token' from block1, which is the Token Unit. The final output of this block is the P-matrix, which is written to the memory.

Figure 4.8 Entity of the Turn Prohibition Unit.

This block also has interface with the 'address' and 'data' buses for reading and writing data. The 'interrupts' and 'interrupts ack' ports are for synchronizing this block with the IO drivers. This block gets its node number from the 'node num' port. The 'buf read' and 'buf write' will determine the type of IO operation to be performed.

TPBR algorithm doesn't select the special node. After a node recognizes that one of its neighbor is a special node, then it broadcasts a packet to that node indicating the node is special, and then the node will not run the TPBR algorithm. If the received packet is the token release packet from the node with the preceding token then it is checked whether the broadcasting of the flat packets is done previously. If not, it is completed and will wait again for the interrupts.

Figure 4.9 Architecture of the Turn Prohibition Unit.

As seen in Figure. 4.9 the Turn prohibition unit consists of 3 main parts start & control, the turn prohibition unit, I/O memory block. The startup unit receives the 'enable' and the 'token' signal. When 'enable' is 'high', making 'prohibit enable' high turns on the whole block. Making 'prohibit enable' low after the token is released again turns off the whole block. If prohibit enable is '1', broadcast packet is request by making broadcast packet req 'high' and the flat packets are broadcasted by the appropriate process. After the flat packets are broadcasted the timeout process is enabled and waits for a time of 6 I/O operations and after the time is elapsed the 'timeout' signal is made 'high'. If after the IO is enabled, the interrupts are checked and the one with the highest priority is serviced first. The same process is used for memory write after the token release packet is broadcasted that is the token relsd is 'high'. The third block of the Turn Prohibition unit is the core unit of the whole chip, which mainly deals with the Turn Prohibition. This block has three sub-parts, one is the packet broadcast part, which broadcasts the appropriate packets in response to the broadcast packet request, and broadcasts to different ports depending upon the request arrived. The second sub-part is the prohibition part, which runs the TPBR algorithm so as to find the turns to be prohibited. In the process of eliminating the turns, at some time the algorithm recognizes some of the nodes to be special which means that the node which is special, should not run the TPBR algorithm. In order to keep track of the special nodes identified by a particular node (system), a memory module is used which stores the identity of the special node. After the whole process of Turn Prohibition is completed, the special node identity stored in the memory is recalled and is intimated to that corresponding node, so that the special node does not run the TPBR algorithm.

#### 4.5 Routing Table Construction

In this section, a decentralized algorithm is described for the construction of local routing tables (for a given set of prohibited turns Z (G)) minimizing average path length and average delivery time. Assume that Z (G) is already constructed. For a given source *s* and destination *d* our goal is to select the shortest routing path a1...*am* (a1=s, *a*m=d) among all paths, satisfying the routing restrictions (not including turns from Z (G)). For any intermediate node *i* the algorithm estimates the length of the shortest permitted path between neighbors of *i* and the destination, and routes the message to neighbor *j* with the lowest estimated path's length (providing that the corresponding turns in *i* and *j* are permitted). Assume that every node has up to *d* neighbors ("node" here is the router component of the processor-router pair). Hence, it would have up to d+1 input/output buffer, including the buffers for the consumption channel to the processor.

Initially, every router knows the set of turns, which are permitted, and which are prohibited in this router. After the implementation of the TPBR algorithm, all the nodes in the network broadcasts their turns which are either permitted or prohibited through them to all the other nodes in the network by flooding a packet.

# 4.5.1 Mathematical model for Table Construction

This can be represented by  $(d+1) \times (d+1)$  matrix P, such that P (i, j)=1 if the turn from input buffer *i* to the output buffer *j* is permitted and  $i\{0,...,d\}$  (case *i* (or j) =0 corresponds to the consumption channel). It follows from the *TPB*R-algorithm that matrix P has the following properties:

1) It is symmetrical, i.e. P(i,j)=P(j,i);

2)

$$P(0,i)=1, P(i, 0)=1$$

For every node routing matrices R(i,k) and D(i,k) are constructed, where i{ 0,...,d}, k{1,...,N}, N is the number of nodes. R (i, k) = j, if a message, coming from input port i to destination node k, should be routed to output port j. Elements of R take values from 0 to d. D (i,k) is the length (number of hops) on the path from input buffer i to destination node k. Matrix D is used at the pre-routing stage only, while matrix R is used for on-line routing. The total memory required to store these matrices is of the order of 2(d+1) N.For d=4, N=1,000 it is around 10K; hence a hardware implementation for this algorithm is feasible.  $R_a$  and  $D_a$  for node a are initialized as:  $R_a(i,j)=X$ ,  $R_a(i,a)=0$ ,  $D_a$  (i,j)=X,  $D_a$  (i,a)=0. (Assign X as a special value, corresponding to the undetermined case) At each step, elements of  $R_a$  and  $D_a$  are recalculated, using matrices  $R_1...Rd$ ,  $D_1... D_d$  of neighbors I...d of node a. After t steps all paths of length up to t hops will be determined. The rule for step t (initially, t=1) is the following:

If  $R_a(i, j) = X$  then for all m, such that P (i, m) = 1 (the turn from i to m is permitted, node m is a neighbor of node a)

If  $D_m(y,i)=t-1$ , then {  $R_a(i,j):=m$ ;  $D_a(i,j):=t$  } (Here y is the input port for node m, which corresponds to the neighboring node a).

For the hardware realization, at each step t every node should transmit to its neighbors, messages with numbers i, such that  $D_m$  (y, i) =t-1. During the whole prerouting procedure, up to N such numbers can be sent by every link. The algorithm is terminated after L steps, where L is the maximal possible length of a minimal permitted

path between two nodes, or if at some step t no changes have been made in any of the matrices.

It is noted that the proposed algorithm can be used to construct a set of shortest paths for any given set of prohibited turns, which will increase the efficiency of the network. The objective is to find the shortest path from any node to any node in the network. To calculate this the following assumptions are made.

1) It is assumed that the links between nodes are full duplex, which means that there exists a two-way communication between the two nodes.

2) Data can be back routed; i.e., if data is received on port, it can be transmitted back on the same port.

3) A P(i,j) vector will be formed after the execution of the second block, if  $P(i,j)= 0^{\circ}$  then the turn is prohibited.

4) Each node will be labeled and each node as an entity knows its' own label which is unique in the network.

For examples, each port will be labeled with a number and each Node with a letter. Port 0 is reserved for the local machine. Now let us consider the steps for finding the shortest path taking the above assumptions into consideration.

1) Initialize arrays 'D (5x16)' and 'R (5x16)' and zero counter. Through reset signal

- a) A counter is initialized to a count of "0".

- b) Values in 'D (i, a)' 'R (i, a) are set to '0', where 'a' is the node ID. This is the local machine. All other elements for Array 'D' and 'R' are initialized to 255. This assumes 8-bit value, for implementations sake.

*Notes:* For example, node B will set 'D (i, B)' and 'R (i, a) = '0'. Array 'D' is the distance vector. Array 'R' is the routing table vector. The wait period is determined by network latency.

2) Advance time counter by 1, i.e., 't = t+1'

3) Update 'R (i, k)' using information from 'D (i, k)'. If 'D (i, k)' = t-1, 'P (i, j)' = '1' and 'R (i, k)' = '255' then write 'i' into 'R (i, k)'.

4) Make only ONE write to any location in array 'R'. This is accomplished by checking for the default state. The first write made to 'R' is the shortest possible route to destination node k though port i.

a) Read T (k) from port Pr and update D (i, k). Receive message from neighbor and Place in local 'T (k)' array. Update Array 'D (Pr, k)' with 't' if 'T (k)' = 't-1'; Where, Pr is the local receive port ID.

*Notes*: Each message received on a port may or may not update element(s) in Array 'D'. Suppose, Node 'A' received Array 'T (k)' from Node 'B' on Port '4'. Port 4 will cause an update elements 'D (4, k)' if 'T (k)' = t-1.

b) Build message from 'D (i, k)' array and transmit to neighbor.

*Notes*: To build the message for transmit check down the columns of the 'D' array. The 'D' array specifies the "hops" to a destination node. For example, if a column 'k' has the value of 't-1' then it can be said that destination node k is 't-1' hops away, which also means that all ports of this node see node k as 't-1' hops away, if the turn is allowed. If the turn is not allowed, write '255'. All this information must be put in the Tx message. The Tx message will be an array T (1X16).

#### CHAPTER 5

## THE VHDL MODEL FOR TURN PROHIBITION

# 5.1 Description of the Model

The high level simulation module for the architecture discussed in the previous chapter is simulated and tested in VHDL. The basic architectural module underlying the behavioral process consists of 3 sequential units namely token unit, prohibition check and routing table construction. Each of the unit's output is fed as an input to the following unit, which determines its function based the input fed from the previous unit. The system level module consists of various tasks performed at different points of time. They are mentioned below along with the inputs and the outputs. The chip is checked for its sequential execution, which assumes that the Enable signal to be 'high', and also the token is assigned a certain value which can be the identity of the node. Also all the possible interrupts are made 'low', so as to confirm whether the prohibition unit takes the control of the chip after the token unit has completed its computation of the assigning the nodes with an identity. Here the architecture is verified keeping in mind that the nodes already have an identity assigned to them, which means to say that the prohibition unit is mainly targeted for the efficient performance to verify the architecture.

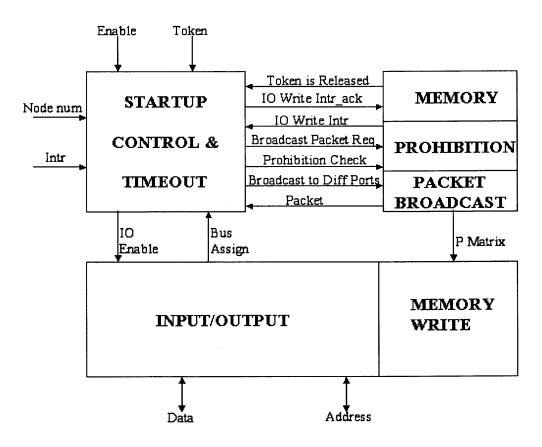

The block diagram for the model designed in VHDL is as shown in Figure. 5.1. This has three blocks basically which are the three main blocks discussed in the architecture namely the Token Unit, Prohibition Unit and the Routing Table Unit. As can be seen each block within the three main blocks has been divided into many sequential sub-blocks. Each sub-block does a unique function, which is described in the architecture.

The Token Unit block has7 sub-blocks. The whole process starts when the Node id and the port status are known. The first sub-block namely the state machine calculates the minimum value of the  $(d_a^2-2)/\Sigma$  (d  $_i-1$ ) based on the information from all the neighboring nodes. After this is done then the transmit process is invoked where in the result to be sent out to the neighboring nodes is ready. Then the block waits and checks if there are any interrupts from the nodes nearing it. This is taken care of by the interrupt arbitration block. Based on the interrupt then either a transmit or a receive process is invoked. After the interrupts are checked, data bus arbitration takes place so as to make to the bus available for the data. Finally the chip select is generated which will basically set the enable signal high and also restores the token, which will enable the Turn Prohibition Unit.

In the Turn Prohibition Unit, the enable and the token is checked by the prohibit and the token processes. Then interrupt control checks for any of the external interrupts and the I/O control checks for the interrupts due to data or the address coming from the other nodes in the network. The next sub-block, which is the bus arbitrator, does the similar function as the one in the Token Unit. In fact the same block is invoked at different points of time depending on the necessity. The packet broadcast block takes care of formulating the packet and also has the information as to which turn is prohibited and which turn is permitted so that the neighboring nodes will have an idea on the turns in the network. The time out process is used as a counter within which the process has to be completed. The Routing Table block gets the input from the Turn Prohibition block, which has mainly the information regarding the ports, which are permitted and the ports, which are not permitted. This information will be in the form of a 16 bit data. Then the table is formulated; this formulation is done initially for the first time. Only updating and reading from the records are done all the time. The build table block is done after updating each record, so that only final table will be stored and that will be used as a reference.

Figure 5.1 Block Diagram for the model designed in VHDL.

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                  |                      | wave - | default             |                       |     |     |                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------|---------------------|-----------------------|-----|-----|----------------------------------------|

| lle <u>E</u> dit <u>C</u> ursor <u>Z</u> oom <u>F</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ormat <u>W</u> indow                                                                                                                                                                                                             |                      |        | A CONTRACTOR        | and the second second |     |     |                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | X 7++F                                                                                                                                                                                                                           | 0000                 |        |                     |                       |     |     |                                        |

| CLOCK<br>ENABLE<br>NODE NUMBER<br>NODE | 0101<br>01010101111<br>00000000000<br>0<br>0<br>1<br>0<br>0<br>1<br>1<br>0<br>1<br>1<br>0<br>1<br>1<br>0<br>1<br>1<br>0<br>1<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 0011<br>0101<br>0101 |        |                     |                       |     |     |                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                  |                      |        |                     |                       |     |     |                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                  |                      |        |                     |                       |     |     |                                        |