# New Jersey Institute of Technology Digital Commons @ NJIT

### Theses

Theses and Dissertations

Summer 2002

# Electrical properties of ultra thin Al2O3 and HfO2 films as gate dielectrics in MOS technology

Vishal R. Mehta New Jersey Institute of Technology

Follow this and additional works at: https://digitalcommons.njit.edu/theses Part of the <u>Materials Science and Engineering Commons</u>

**Recommended** Citation

Mehta, Vishal R., "Electrical properties of ultra thin Al2O3 and HfO2 films as gate dielectrics in MOS technology" (2002). *Theses*. 693. https://digitalcommons.njit.edu/theses/693

This Thesis is brought to you for free and open access by the Theses and Dissertations at Digital Commons @ NJIT. It has been accepted for inclusion in Theses by an authorized administrator of Digital Commons @ NJIT. For more information, please contact digitalcommons@njit.edu.

# **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

### ABSTRACT

# ELECTRICAL PROPERTIES OF ULTRA THIN Al<sub>2</sub>O<sub>3</sub> AND HfO<sub>2</sub> FILMS AS GATE DIELECTRICS IN MOS TECHNOLOGY

# by Vishal R. Mehta

The rapidly evolving silicon industry demands devices with high-speed and low power consumption. This has led to aggressive scaling of the dimensions in metal oxide semiconductor field effect transistors (MOSFETs). The channel length has been reduced as a result of this scaling. The industry favorite, SiO<sub>2</sub>, has reached limitations in the thickness regime of 1-1.5 nm as a gate dielectric. High- $\kappa$  gate dielectrics such as Al<sub>2</sub>O<sub>3</sub> and  $HfO_2$  and their silicates are some of the materials that may, probably, replace  $SiO_2$  as gate dielectric in the next four to five years. The present study is an attempt to understand the electrical characteristics of these exciting materials grown by atomic layer deposition (ALD) technique. The flat band voltages (V<sub>FB</sub>) were determined from C-V measurements on circularly patterned MOS capacitors. For phosphorous doped polysilicon electrodes and Al-oxide based dielectrics, positive shifts in V<sub>FB</sub> were observed, relative to a pure  $SiO_2$  control, ranging from 0.2 to 0.8V. It is believed that this is caused by fixed charges. Rapid thermal annealing at 1000°C tends to decrease V<sub>FB</sub> relative to a 800°C anneal. Changes in V<sub>FB</sub> up to 0.35 V are observed for films deposited over SiO<sub>2</sub> underlayers, while smaller changes, up to 0.05 V, are observed for films deposited directly on Si. Spike annealing is also observed to reduce oxide leakage.  $HfO_2$  showed large amount of leakage resulting in difficulty in performing capacitance measurements. ZrO2 was found to be reacting with polycrystalline silicon and thus high leakage current was observed.

# ELECTRICAL PROPERTIES OF ULTRA THIN Al<sub>2</sub>O<sub>3</sub> AND HfO<sub>2</sub> FILMS AS GATE DIELECTRICS IN MOS TECHNOLOGY

by Vishal R. Mehta

A Thesis Submitted to the Faculty of New Jersey Institute of Technology In Partial Fulfillment of the Requirements for Degree of Master of Science in Materials Science and Engineering

Interdisciplinary Program in Materials Science and Engineering

August 2002

$\langle$

# **APPROVAL PAGE**

# ELECTRICAL PROPERTIES OF ULTRA THIN ALO<sub>3</sub> AND HfO<sub>2</sub> FILMS AS GATE DIELECTRICS IN MOS TECHNOLOGY

Vishal R Mehta

Dr. N. M. Ravindra, Thesis Co-advisor Professor of Physics, NJIT

Dr. Anthony Fiory, Thesis Co-advisor Research Professor of Physics, NJIT

Dr. Dentcho Ivanov, Committee Member Director, Microelectronics Research Center and Research Professor of Biomedical Engineering, NJIT

21

Dr. Sufian Abedrabbo, Committee Member Assistant Professor of Physics, University of Jordan

Date

Date

8 30 02

8/30/02

8/29/02

Date

Date

# **BIOGRAPHICAL SKETCH**

| Author:         | Vishal R. Mehta   |

|-----------------|-------------------|

| Degree:         | Master of Science |

| Date:           | August 2002       |

| Date of birth:  |                   |

| Place of birth: |                   |

# Undergraduate and Graduate education:

- Master of Science in Materials Science and Engineering, New Jersey Institute of Technology, Newark, NJ, 2002.

- Bachelor of Engineering Maharaja Sayajirao University of Baroda, India, 1995.

Major:

Materials Science

# **Journal Publications:**

- N. M. Ravindra et.al., X-ray diffraction studies and electrical properties of sputter deposited tantalum silicide films, Journal of Electronic Materials, October 2002 (in press).

- A. T. Fiory, S. G. Chawda, S. Madishetty, V. R. Mehta, N. M. Ravindra S. P. McCoy, M. E. Lefrançois, K. K. Bourdelle, J.M. McKinley, H.-J. L. Gossmann, and A. Agarwal, "Transient-Enhanced Diffusion in Shallow Junction Formation," J. Electron. Materials. October 2002 (in press).

Dedicated to my beloved family

# ACKNOWLEDGEMENT

The author wishes to express his sincere gratitude to his co-advisors Dr. N. M. Ravindra and Dr. Anthony Fiory for their guidance and encouragement given throughout this research. The author would like to give special thanks to Dr. Dentcho Ivanov and Dr. Sufian Abedrabbo for serving as members of the thesis committee. The author is grateful to Professor N. M. Ravindra for helping with grants, to identify the research topic and also, for helping throughout the research.

The author appreciates the support of Dr. Glen Wilk (Agere Systems) and also of Ms. Mun Yee Ho (Agere System intern from Singapore State University) for helping with the materials and sharing their knowledge. The MOS devices were processed in the nanofabrication cleanroom of Bell Labs. The author is grateful to Tom Sorsch for giving helpful suggestions in his research activities.

The author is thankful to Mr. Henry McCloud and Mrs. Lorna Derilhomme Joasil for their continued support during his course of studies.

Finally, the author expresses words of gratitude to colleagues Aravind Balakrishnan, Sridhar Madishetty, Samrat Chawda and Anand Shenoy for their help and support throughout the course of this research.

vi

# TABLE OF CONTENTS

| С | hapter P                                                                                               | age |

|---|--------------------------------------------------------------------------------------------------------|-----|

| 1 | INTRODUCTION                                                                                           | 1   |

| 2 | METAL OXIDE SEMICONDUCTOR (MOS) FUNDAMENTALS                                                           | 4   |

|   | 2.1 The p-n Junction                                                                                   | 4   |

|   | 2.2 Forward-Bias Junction                                                                              | 7   |

|   | 2.3 Metal Oxide Semiconductor Field Effect Transistor (MOSFET)                                         | 8   |

| 3 | REPLACEMENT OF GATE DIELECTRIC                                                                         | 12  |

|   | 3.1 Limitations of Silicon Dioxide (SiO <sub>2</sub> )                                                 | 12  |

|   | 3.2 Silicon Nitride (Si <sub>3</sub> N <sub>4</sub> )                                                  | 17  |

|   | 3.3 Oxynitrides                                                                                        | 17  |

| 4 | ALTERNATE GATE DIELECTRICS                                                                             | 19  |

|   | 4.1 Fundamentals of High Dielectric Constant Materials                                                 | 19  |

|   | 4.2 Alternative High-κ Gate Dielectrics                                                                | 23  |

|   | 4.2.1 Introduction                                                                                     | 23  |

|   | 4.2.2 Deposition Techniques                                                                            | 23  |

|   | 4.2.3 Zirconium Oxide (ZrO <sub>2</sub> )                                                              | 26  |

|   | 4.2.4 Yttrium (Y <sub>2</sub> O <sub>3</sub> ) and Gadolinium (Gd <sub>2</sub> O <sub>3</sub> ) Oxides | 28  |

|   | 4.2.5 Titanium Oxide (TiO <sub>2</sub> ) and Tantalum Oxide (Ta <sub>2</sub> O <sub>5</sub> )          | 29  |

|   | 4.3 Aluminium Oxide (Al <sub>2</sub> O <sub>3</sub> )                                                  | 32  |

|   | 4.4 Hafnium Oxide (HfO <sub>2</sub> )                                                                  | 33  |

|   | 4.5 Rapid Thermal Annealing (RTA)                                                                      | 35  |

# TABLE OF CONTENTS (Continued)

| С | hap | ter P.                                           | age |

|---|-----|--------------------------------------------------|-----|

| 5 | ELI | ECTRICAL CHARACTERIZATION                        | 38  |

|   | 5.1 | Capacitance Voltage (C-V) Measurements           | 38  |

|   |     | 5.1.1 Low Frequency C-V Measurements             | 39  |

|   |     | 5.1.2 High Frequency C-V Measurements            | 41  |

|   |     | 5.1.3 Analysis of Capacitor Measurements         | 44  |

|   | 5.2 | Current Transport in Thin Oxides                 | 48  |

|   | 5.3 | Time Dependent Dielectric Breakdown (TDDB)       | 52  |

| 6 | EX  | PERIMENTAL DETAILS                               | 55  |

|   | 6.1 | Sample Preparation                               | 55  |

|   | 6.2 | Measurement Procedure                            | 59  |

| 7 | RE  | SULTS AND DISCUSSION                             | 65  |

| 8 | CO  | NCLUSION                                         | 82  |

| A | PPE | NDIX PROGRAM FOR CALCULATION OF -V <sub>FB</sub> | 83  |

| R | EFE | RENCES                                           | 85  |

# LIST OF TABLES

| Tab | ble                                                                                | Page |

|-----|------------------------------------------------------------------------------------|------|

| 3.1 | Comparision Of Relevant Properties Of Various High-ĸ Materials                     | 14   |

| 3.2 | International Technology Roadmap for the Semicondutor Gate Stack                   | 16   |

| 5.1 | Quantities Determined by High Frequency MOS C-V Data Analysis                      | 43   |

| 5.2 | Tunneling Energies in Ultrathin Oxides                                             | 51   |

| 7.1 | Experimental Values of Al <sub>2</sub> O <sub>3</sub> High Gate Dielectric Samples | 73   |

| 7.2 | Experimental Values of Al <sub>2</sub> O <sub>3</sub> High Gate Dielectric Samples | 74   |

| 7.3 | Sample Preparation Chart for HfO <sub>2</sub> Gate Dielectric samples              | 78   |

# **LIST OF FIGURES**

| Fig  | ure P                                                                                                                           | age |

|------|---------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.1  | Energy bands of p and n semiconductor; the current flow                                                                         | 5   |

| 2.2  | The transition region with x=0 defined as metallurgical junction (b) Space charge density (c) electric field distribution       | 6   |

| 2.3  | Reverse breakdown in a p-n junction                                                                                             | 8   |

| 2.4  | Schematic diagram of n-type MOSFET                                                                                              | 9   |

| 2.5  | n channel MOSFET cross section under various operating conditions                                                               | 10  |

| 3.1  | Percolation model. When trap clusters join together, breakdown occurs                                                           | 15  |

| 4.1  | The effect of SiON underlayer on Poly-Si/Al <sub>2</sub> O <sub>3</sub> /SiON (~5Å) MOS capacitor                               | 20  |

| 4.2  | Conduction band offset of SiO <sub>2</sub> , Si <sub>3</sub> N <sub>4</sub> and various high- $\kappa$ materials with Silicon   | 21  |

| 4.3  | Current-voltage of annealed $ZrO_2/SiO_2$ gate stacks on n- type and p-type wafers                                              | 26  |

| 4.4  | HRTEM image of $ZrO_2$ deposited on oxidized silicon by ALCVD                                                                   | 27  |

| 4.5  | Zr-Si-O ternary system phase diagram                                                                                            | 28  |

| 4.6  | Electrical leakage current densities of Y <sub>2</sub> O <sub>3</sub> films                                                     | 29  |

| 4.7  | Gibbs free energy diagrams for Ta-Si-O and Ti-Si-O ternary systems                                                              | 30  |

| 4.8  | HRTEM micrographs of tantalum oxide and interface with Si. (a) After low temperature plasma anneal, and (b) RTA at 800°C        | 30  |

| 4.9  | (a) Leakage current density comparison of different layers, and (b) $J_g$ - $V_g$ characteristics of different dielectric films | 31  |

| 4.10 | ) $I_d$ - $V_d$ characteristics of Ta <sub>2</sub> O <sub>5</sub> /SiO <sub>2</sub> nMOSFET                                     | 32  |

| 4.11 | HRTEM image of deposited and processed ALCVD layers of poly-Si/ $Al_2O_3/Si$                                                    | 33  |

| 4.12 | 2 HRTEM image of Poly-Si/HfO <sub>2</sub> /SiO <sub>2</sub> /Si                                                                 | 34  |

| 4.13 | Metron AG HEATPULSE RTA 8800 machine                                                                                            | 37  |

| 5.1  | Cross-section of an MOS capacitor showing a simple equivalent circuit                                                           | 39  |

# LIST OF FIGURES (Continued)

| Figu | Ire                                                                                                                                                                                        | age |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.2  | Capacitance as a function of bias and corresponding band diagrams                                                                                                                          | 40  |

| 5.3  | C-V measurements at various frequencies                                                                                                                                                    | 41  |

| 5.4  | High frequency curves for two types of substrate dopings                                                                                                                                   | 42  |

| 5.5  | Frenkel-Poole emission                                                                                                                                                                     | 49  |

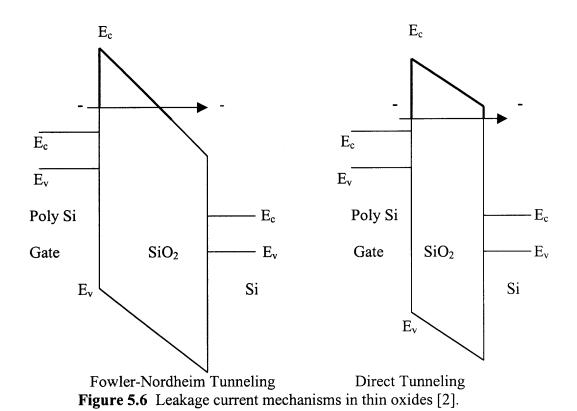

| 5.6  | Leakage current mechanisms in thin oxides                                                                                                                                                  | 52  |

| 5.7  | Time dependent dielectric breakdown of thin oxide layer                                                                                                                                    | 54  |

| 6.1  | ASM PULSAR ALCVD system                                                                                                                                                                    | 55  |

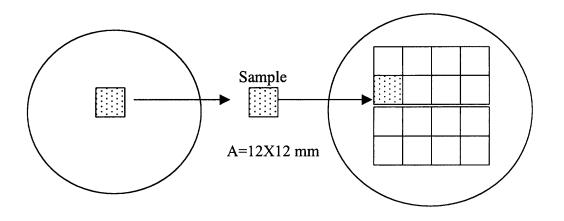

| 6.2  | Sample preparation for RTA activation                                                                                                                                                      | 57  |

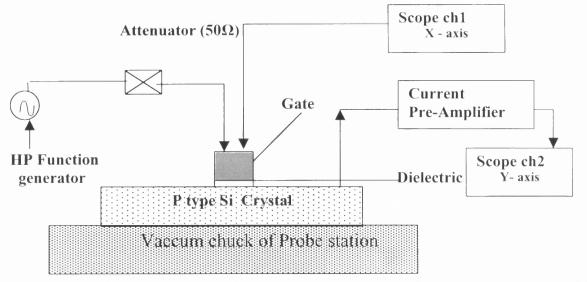

| 6.3  | Schematic circuit of the experimental set-up for Capacitance-Voltage measurements of MOS capacitors                                                                                        | 61  |

| 6.4  | Equivalent electrical circuit of the experimental set-up where R <sub>1</sub> , R <sub>2</sub> and R <sub>3</sub> are contact resistances                                                  | 61  |

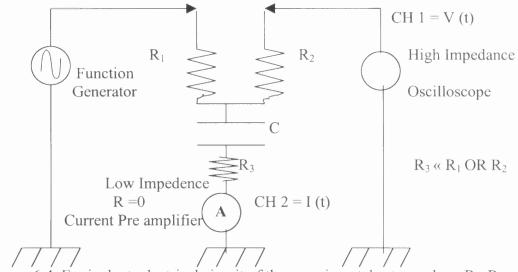

| 6.5  | Voltage output of current pre-amplifier. It shows time dependence of voltage and current (i.e., ch1 and ch2 respectively)                                                                  | 62  |

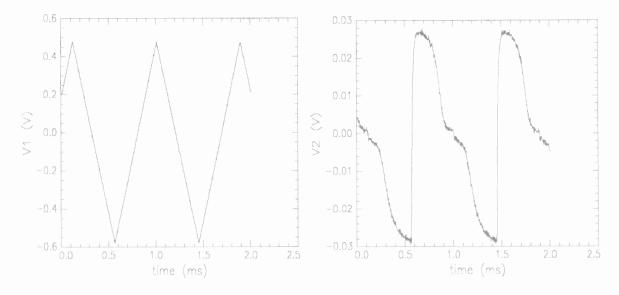

| 6.6  | <ul> <li>(a) The curve fit program plot of 1/C<sup>2</sup><sub>s</sub> (y-axis) v/s V<sub>surface potential</sub> (x-axis). (b) The equivalent circuit of the program</li> </ul>           | 63  |

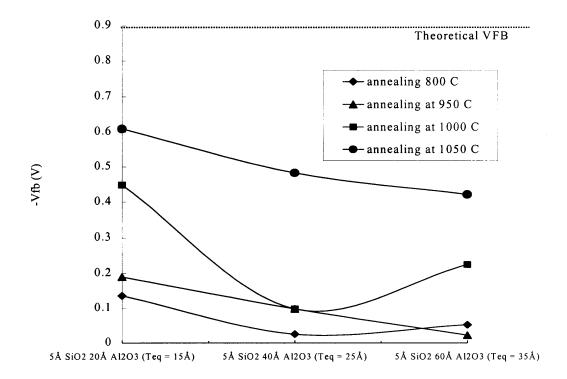

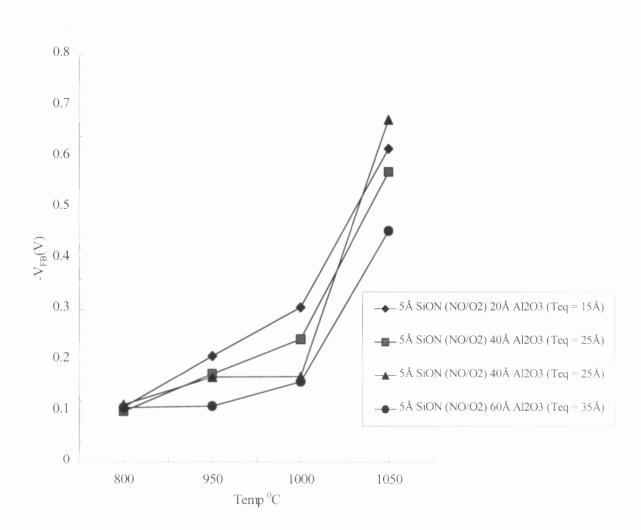

| 7.1  | Plot of $-V_{FB}$ vs Al <sub>2</sub> O <sub>3</sub> thickness and T <sub>eq</sub> for the various annealing temperatures<br>for p type substrates having underlayer of 5Å SiO <sub>2</sub> | 65  |

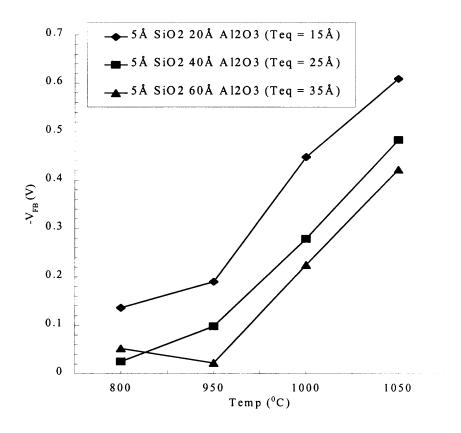

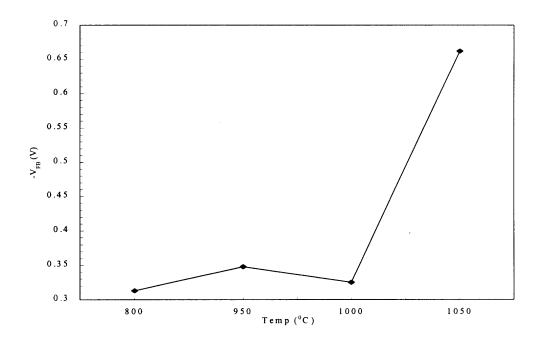

| 7.2  | Plot of -V <sub>FB</sub> vs Temperature for various thickness of Al <sub>2</sub> O <sub>3</sub> with an underlayer of 5Å SiO <sub>2</sub>                                                  | 67  |

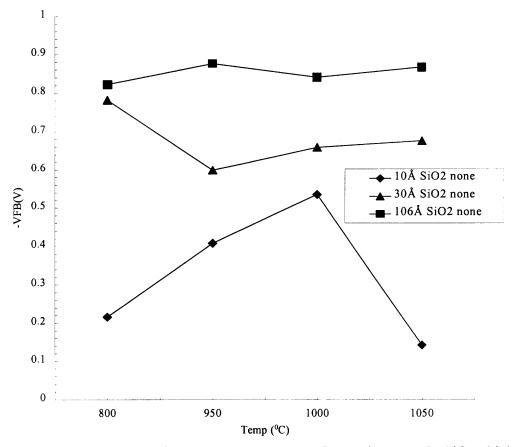

| 7.3  | Plot of $-V_{FB}$ vs Temperature for the various RTO SiO <sub>2</sub> thickness with no underlayer or high- $\kappa$ film                                                                  | 68  |

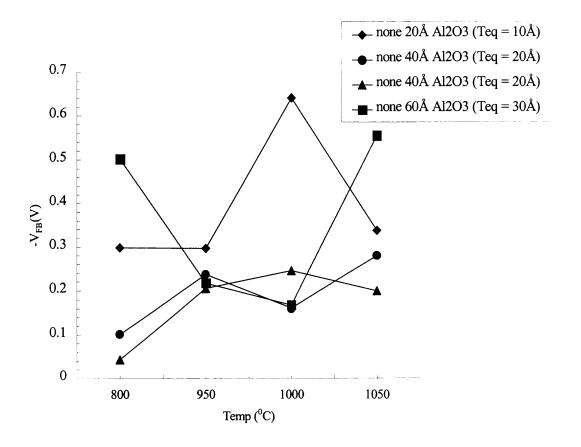

| 7.4  | Plot of $-V_{FB}$ vs Temperature for the ALCVD high- $\kappa$ layer of various thickness.<br>"none" denotes deposition of Al <sub>2</sub> O <sub>3</sub> directly on cleaned Si surface    | 69  |

# LIST OF FIGURES (Continued)

| Figu | lare                                                                                                                                                                                            | Page |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 7.5  | Plot of -V <sub>FB</sub> vs Temperature for various thickness of high-κ layer of Al <sub>2</sub> O <sub>3</sub> having underlayer of 5Å SiON (NO/O <sub>2</sub> )                               | 70   |

| 7.6  | Plot of -V <sub>FB</sub> vs Temperature for 20 Å Al <sub>2</sub> O <sub>3</sub> sample having underlayer of SiON made by NO only                                                                | 71   |

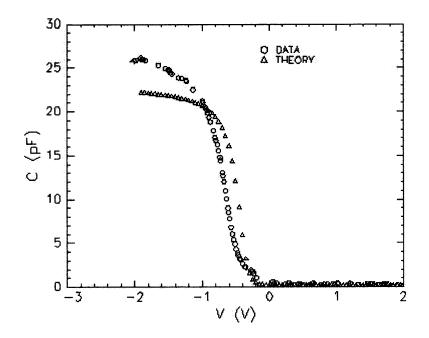

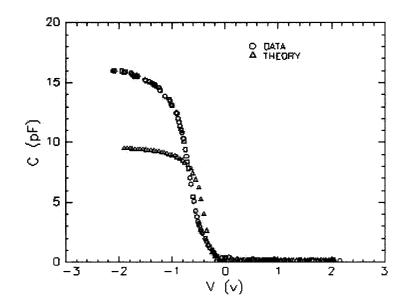

| 7.7  | Comparison of measured C-V data with the theoretical C-V curve of NCSU program for Al <sub>2</sub> O <sub>3</sub> sample having 5Å SiON (NO/O <sub>2</sub> ) underlayer and high-κ layer of 40Å | 75   |

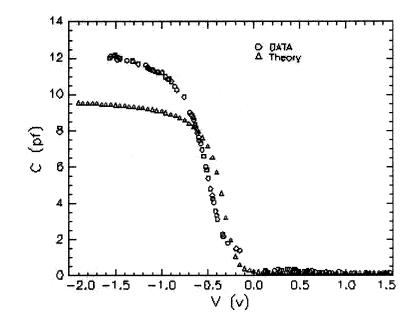

| 7.8  | Comparison of measured C-V with the theoretical C-V curve of NCSU program for Al <sub>2</sub> O <sub>3</sub> 5Å SiON (NO/O <sub>2</sub> ) underlayer and high-κ layer of 60 Å                   | 76   |

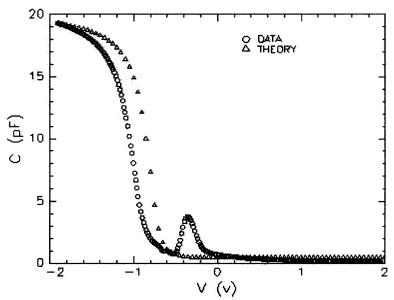

| 7.9  | Comparison of measured C-V data with the theoretical C-V curve of NCSU program for Al <sub>2</sub> O <sub>3</sub> 5Å SiO <sub>2</sub> underlayer and high-κ layer of 60 Å                       | 77   |

| 7.10 | Comparison of measured C-V data with the theoretical C-V curve of NCSU program for 30Å SiO <sub>2</sub>                                                                                         | 77   |

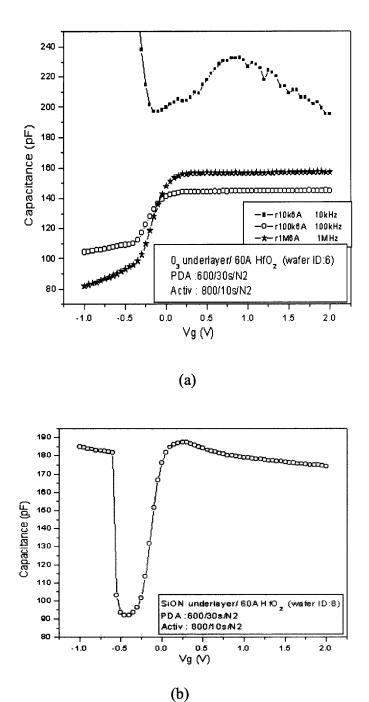

| 7.11 | (a) The C-V measurements at low and high frequency for samples having SiO <sub>2</sub> as underlayer (b) Low frequency measurements of the sample having SiON as underlayer.                    | 80   |

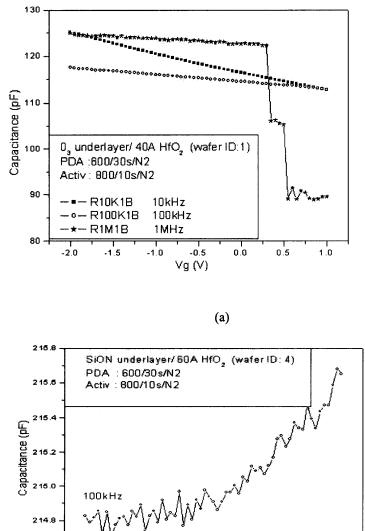

| 7.12 | 2 C-V measurements of n type HFO <sub>2</sub> samples. (a) With chemical oxide (O <sub>3</sub> ) underlayer and (b) With SiON underlayer                                                        | 81   |

# **CHAPTER 1**

# **INTRODUCTION**

Since 1947, when the first bipolar transistor was constructed at Bell Labs [1], the semiconductor industry has come a long way. As scientists gain knowledge of the silicon material behavior at various voltages and temperature, progressively more useful devices are being introduced into the market. With rapid strides in the manufacturing technology, device sizes have also shrunk, thus demanding better material properties and characteristics. Millions of complimentary metal oxide semiconductor (CMOS) devices are fabricated on 300mm wafers. In CMOS, the Metal Oxide Field Effect Transistor (MOSFET) is the building block. The MOSFET is one of the many types of FETs, which is widely used in integrated circuits (ICs). FETs came into general use only in the late 1960s. In FETs, the current from source to drain is controlled by the application of potential (i.e., electric field) on the gate. Thus, the device is called field effect transistor. FET has a negative temperature coefficient at high current levels [2]. This behavior results in uniform distribution over the device area and prevents the FET from thermal runaway. FETs also offer high switching speeds and cutoff frequencies [1].

Field effect transistor is a unipolar device; that is, current is controlled by majority carriers only. It has three terminals which function as follows:

- (1) Source: As the name suggests, it is one of the heavily doped regions of the FET from which carriers are transferred to the channel.

- (2) Drain: This is also a heavily doped region of FET from where the carriers leave the transistor.

(3) Gate: This is the structure used to control the outgoing current. It is mainly made up of polysilicon. Historically, it used to be made up of metal (i.e. aluminum, platinum, etc).

The normally heavily doped source and drain regions are either diffused or implanted into a relatively lightly doped substrate. Ion implantation is a widely used commercial method for this purpose. A thin oxide layer either thermally grown or deposited separates the conducting gate from the Si surface.

Presently, several different types of FETs are available. When the junction is replaced by Schottky barrier, it is called Metal Semiconductor Field Effect Transistor (MESFET). The metal gate electrode can be separated from the semiconductor by an insulator; the device thus created is called a Metal Insulator Semiconductor Field Effect Transistor (MISFET). A more commonly used silicon device is Metal Oxide Semiconductor Field Effect Transistor (MOSFET), which uses SiO<sub>2</sub> or nitrided (N doped oxide) SiO<sub>2</sub> as the gate dielectric. The MOSFET is described in greater detail in Chapter 2.

In order to decrease the time constant of MOSFETs, the channel length is being continuously reduced. The state of the art in commercial production device has 130 nm-channel length and gate oxide of 1.5 nm thickness. However, the applied voltage has not been scaled at the same rate as the dimensions of the device. This situation creates problems. There are fringing field side effects. The reduction in thickness increases the capacitance. However, electrons can easily tunnel through the thin gate oxide. This causes decrease in input impedance and increase in leakage current. There is a concentrated effort to replace the gate oxide (i.e. SiO<sub>2</sub>). If a high dielectric constant material is used, the same capacitance value can be obtained with increased thickness.

Thick films are known to reduce quantum mechanical tunneling of the oxide. Hafnium oxides, aluminum oxides and their silicates are the front-runners in this race to find a suitable gate dielectric in the next three to four years.

The second chapter in this study focuses on the fundamentals of p-n junction diodes and the effects of forward and reverse bias. It ends with brief description of the properties of MOSFETs. The third chapter explains the advantages and limitations of  $SiO_2$  and the need to replace  $SiO_2$ . It ends with description of silicon nitride ( $Si_3N_4$ ) and the importance of oxynitrides.

The fourth chapter describes the different physical as well as electrical properties of high- $\kappa$  dielectrics and their benefits. Fifth chapter explains carrier behavior at low and high frequencies by utilizing Capacitance-Voltage (C-V) measurements. The C-V technique is used to find oxide thickness, fixed charges, interface traps and doping density. A short note about the current conduction mechanism in gate oxides is presented. The chapter concludes with discussion of several theories of time dependent dielectric breakdown (TDDB).

The sixth chapter presents results and discussion of electrical test experiments on capacitors prepared with various high- $\kappa$  dielectrics. Various experimental observations are presented regarding shift in the flat band voltage (V<sub>FB</sub>) and its possible interpretations.

#### **CHAPTER 2**

# METAL OXIDE SEMICONDUCTOR DEVICE FUNDAMENTALS

#### 2.1 The p-n Junction

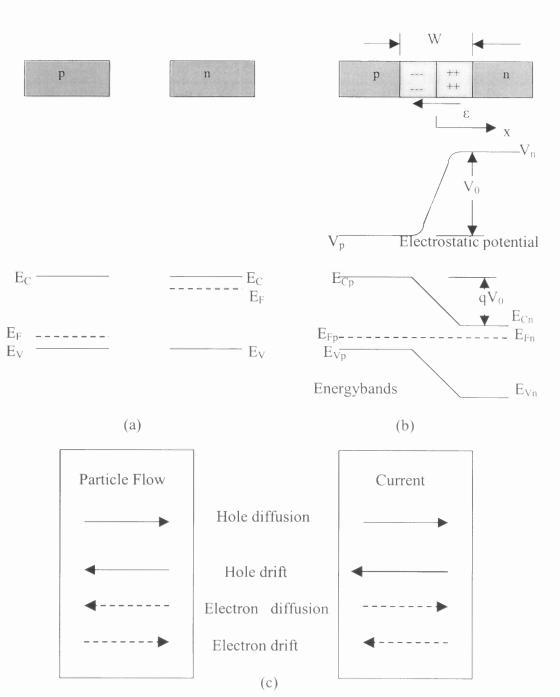

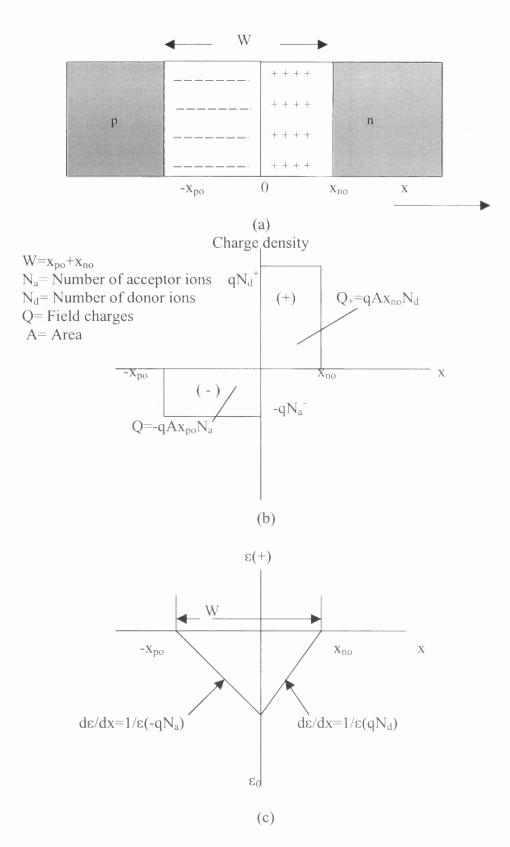

When a p-type or an n-type semiconductor is diffused with n- or p-type impurities, a p-n junction is created. For simplicity, the formation of an abrupt p-n junction is shown in Figures 2.1 (a) and (b). There is a flow of electrons from the n-type to the p-type material and flow of holes from the p-type material to the n-type semiconductor. Thus, there is depletion of electrons near the junction in the n-type material and holes in the p- type region. This is called the depletion region of width W.

The resulting electric field  $\varepsilon$  is directed from the positive charge towards the negative charge. It is in the direction opposite to that of diffusion current for each type of carrier. Thus, the field creates a drift component of current from n to p opposing the diffusion current. At equilibrium, the drift and diffusion currents cancel each other (Figure 2.1(c)). Therefore, electric fields are built up to a point where the net current is zero at equilibrium, assuming the electric field is zero in the neutral region. Hence, a potential difference is generated at the p-n junction [2].

This potential difference is called contact potential  $V_0$ , which is also the built in potential barrier, in the transition region. It is necessary to maintain equilibrium at the junction. The contact potential separates the bands ( $E_c = C$ onduction band and  $E_v =$ Valence band, refer Figure 2.1 (b)). The energy bands on either side of the junction are separated by the contact potential  $V_o$  times the electronic charge q. Also, the Fermi level must be constant throughout the device in equilibrium.

**Figure 2.1** Energy Bands of p and n semiconductor (a) before contact, where  $E_C$  is the conduction band edge,  $E_V$  is the valence band edge and  $E_F$  is the Fermi level of the respective regions. (b) The electrostatic potential  $V_o$  after the regions are brought in contact,  $V_p$  is the voltage at the p region and  $V_n$  is the voltage at the n type region,  $E_{Cn}$  is the conduction band in the n region after contact,  $E_{Vn}$  is the valance band in the n region after joining,  $E_{Cp}$  is the conduction band in the p region,  $E_{Vp}$  is the valance band in the p region after contact,  $E_{Fp}$  and  $E_{Fn}$  are the Fermi levels in the respective regions after contact. (c) The direction of the particle flow and the current flow [2].

**Figure 2.2** (a) The transition region with x=0 defined as metallurgical junction (b) Space charge density (c) electric field distribution [2].

The Fermi level [2] is given by the equation,

$$F(E_i) = \frac{1}{1 + e^{(E_c - E_F)/kT}}$$

(2.1)

where,  $E_i$  is the intrinsic Fermi level. The Fermi level is near the valence band in p-type material, while it is near the conduction band, in n type material. Figure 2.2 illustrates the electric field and charge distributions in the p-n junction area (i.e., depletion region).

#### 2.2 Forward and Reverse Bias

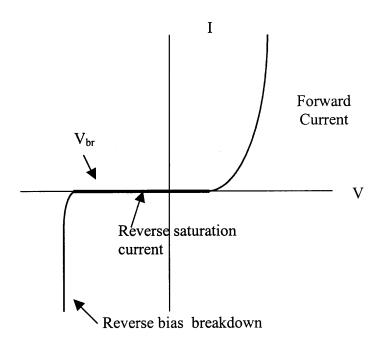

An applied voltage changes the potential barrier and the electric field within the transition region. Thus, changes in the various current components are expected. The potential barrier is lowered when the junction is forward biased. The electrons have more energy and they can diffuse from n to p region. Similarly, holes can diffuse from p to n. Thus, electron diffusion current is greater in forward bias. In reverse bias, the barrier becomes so large that the diffusion current is negligible [2]. This is shown in Figure 2.3.

Two types of currents are mainly involved in the conduction process. These are diffusion current and drift current. The drift current is insensitive to the height of the potential barrier. The drift current arises because of the minority carrier in each region being swept down the potential barrier under the applied field. The number of minority carriers in turn depends on the generation of electron hole pairs. The total current is composed of the sum of both diffusion and drift currents.

Figure 2.3 Current-voltage characteristics a p-n junction [2].

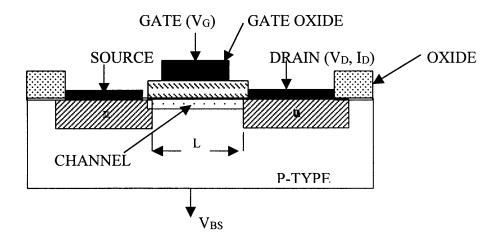

# 2.3 Metal Oxide Semiconductor Field Effect Transistor (MOSFET)

The MOSFET is widely used in CMOS circuits where it is switched from the "off" state to "on" state. As the name suggests, the MOSFET has an oxide layer separating the gate electrode and the substrate. It is known as the gate oxide. Figure 2.4 is a schematic representation of an n-type MOSFET. The basic operation of the MOSFET is as follows.

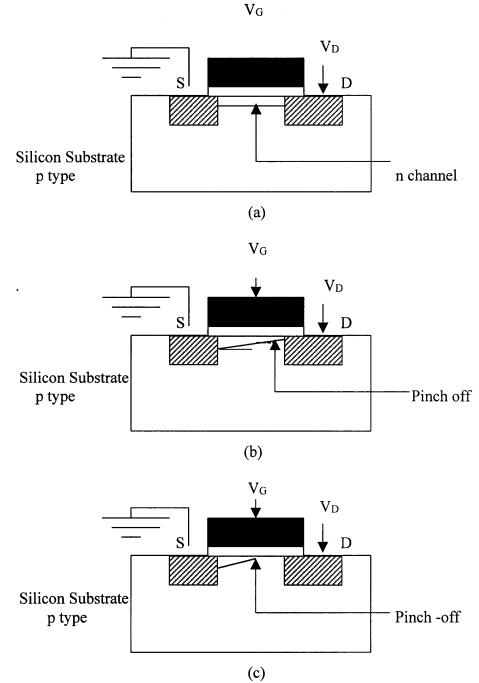

The gate dielectric in between the gate and the substrate has a large band gap and a high dielectric constant. The gate electrode can either be of metal or highly doped polycrystalline silicon (polysilicon). Source and drain are doped in the substrate by ion implantation and then diffused by thermal diffusion. The morphology of the interface between the oxide and the substrate is very critical for the desired operation of the device. It should be smooth, as any roughness might scatter the electrons and reduce the carrier mobility. Since the Fermi level is near the different bands in the adjacent regions, there is a barrier for the carriers due to the built in potential of the back-to-back p-n junctions between the source and drain. No current flows from drain to source without a conducting channel between them. Figure 2.5 explains the change in the number of carriers with the applied bias of an n-type MOSFET.

Figure 2.4 Schematic diagram of an n-type MOSFET.

With the application of the voltage at the gate (V<sub>G</sub>), the outgoing current from the drain (I<sub>D</sub>) can be controlled. This occurs because of the inversion of the semiconductor layer below the gate due to the dielectric effect of the high permittivity material (i.e., SiO<sub>2</sub>). For a p type substrate, n channel will be created below the gate. Since electrons are electrostatically induced in the p-type channel region, the channel becomes less p-type. Therefore, the valence band moves down further away from the Fermi level [2]. This reduces the barrier for the electrons to move from source to drain. If this barrier is reduced sufficiently, by applying voltage in excess of threshold Voltage, V<sub>T</sub>, there is significant current flow form source to drain. It is very important to have high quality, low leakage p-n junctions in order to ensure a low off-state leakage current in the

MOSFET. The threshold voltage  $(V_T)$  is the minimum gate voltage required to induce a conducting channel. This type of transistor is normally off with zero gate voltage and operates in the enhancement mode, by applying gate voltage large enough to induce a conducting channel.

Figure 2.5 n channel MOSFET cross section under various operating conditions.

An increased positive voltage creates a more conducting n-channel. This increases the drain current flow in the channel (Figure 2.5a.). However, there is more Ohmic voltage drop along the channel such that the channel potential varies from zero near the grounded source to whatever the applied drain potential ( $V_D$ ) is near the drain end of the channel [2].

Hence, the voltage difference between the gate and the channel reduces from  $V_G$  near the source to  $(V_G-V_D)$  near the drain end. Once the drain bias is increased to the point that  $(V_G-V_D) = V_T$ , threshold is barely maintained near the drain end, and the channel is said to be pinched off (Figure 2.5 b) [2].

Increasing the drain bias beyond this point ( $V_D$  (sat.)) causes the point at which the channel gets pinched off, to move more and more into the channel, closer to the source end (Figure 2.5 c). Electrons in the channel are pulled into the pinch-off region and travel at the saturation drift velocity because of the very high longitudinal electric field along the channel. Now, the drain current is said to be in the saturation region because it does not increase with drain bias significantly [2].

A MOS capacitor is used to study the properties of the gate dielectric that is used in the fabrication of the MOSFET. An MOS capacitor can be used to measure a large number of properties. Surface band bending and depletion layer width in the silicon as a function of gate bias can be measured. Doping profile in the silicon can be obtained from the MOS capacitor. Voltage and field at avalanche breakdown in the silicon can be determined. For many measurements, the n channel MOSFET is preferred because the mobility of electrons in silicon is higher than for holes. Electrical characterization of the MOS capacitor is described in Chapter 5.

#### CHAPTER 3

### **REPLACEMENT OF GATE DIELECTRIC**

# 3.1 Limitation of Silicon Dioxide

Silicon dioxide has good interface properties with the underlying silicon substrate. In order to be used as an effective gate oxide, an alternative high- $\kappa$  material should have a large band gap and an amorphous structure. If the dielectric has a polycrystalline structure, then the electrons can travel through the grain boundaries and cause leakage of the current, thus discharging the capacitor [3]. In Table 3.1 the various properties of gate dielectric materials are summarized. A good interface quality between the substrate and the dielectric is also desired so as to not to affect the mobility of the electrons by deflection of the surface atoms.

The gate oxide should also have low fixed charge so as not to affect the threshold voltage, which is required to switch on or off the device. In the present study, it has been shown that presence of the fixed oxide charge causes shift in the flatband voltage.  $SiO_2$  has been ideal in all the above-mentioned properties. This explains why  $SiO_2$  has enjoyed a limelight as a useful gate dielectric for many years.

The drive current  $I_d$  for the MOS device increases with respect to applied drain voltage  $V_d$  and then it saturates to a maximum at  $V_{dsat}$  [3]. It is given by,

$$I_{d},sat = (W/L)\mu C_{inv} \{ (V_{d,sat})^2/2 \}$$

(3.1)

Where, W is the width of the transistor channel, L is the channel length,  $\mu$  is the channel carrier mobility, and C<sub>inv</sub> is the capacitance density associated with the gate dielectric. When the underlying channel is in the inverted state,  $V_D = V_G - V_T$ .

To increase drain current, either capacitance has to be increased or the channel length has to be decreased.  $V_d$  suffers from constraints on electric field, reliability and room temperature. SiO<sub>2</sub> has been widely used as a gate dielectric because of its physical and electrical properties. SiO<sub>2</sub> is resistant to dopant diffusion. The shrinkage of the MOSFET dimensions has led to the thinning of the gate dielectric. This causes leakage current in the device to increase.

If a high dielectric constant material is used, then thicker films can be utilized as the dielectric. The equivalent oxide thickness  $t_{eq}$ , is the thickness of any dielectric scaled by the ratio of its dielectric constant to that of silicon dioxide (where  $\varepsilon_{oxide}=3.9$ ) such that

$$\mathbf{t}_{\mathbf{x}} = \mathbf{t}_{eq} \left( \mathbf{\varepsilon}_{\mathbf{x}} / \mathbf{\varepsilon}_{oxide} \right) \tag{3.2}$$

where  $t_{eq}$  and  $t_x$  are the equivalent oxide and physical thickness respectively and  $\varepsilon_{oxide}$  and  $\varepsilon_x$  are respectively the dielectric constant of silicon dioxide and that of the other dielectric. This equation implies that we can have a high dielectric constant material which is physically thicker then SiO<sub>2</sub>. This prevents quantum mechanical tunneling of the carriers through the dielectric layer.

With the decrease in the thickness of  $SiO_2$ , there are problems like change in the dielectric thickness, penetration of the impurities from the gate into the gate dielectric, and the reliability and lifetime of devices made with ultra thin films.

In the study by Muller et al. [4] it was found that the density of states makes a transition from the substrate into the SiO<sub>2</sub> layer, indicating that the full band gap of SiO<sub>2</sub> is obtained after only about two monolayers of SiO<sub>2</sub>. This implies that within two monolayers of the Si channel interface, silicon atoms do not have the full arrangement of oxygen neighbors and therefore cannot form the full band gap that exists within the bulk of the SiO<sub>2</sub> film. These results set an absolute physical thickness limit of SiO<sub>2</sub> of 7 Å.

Below this thickness, the silicon rich interfacial regions from the channel and polycrystalline Si gate interfaces used in MOSFETs overlap, causing an effective "short" through the dielectric, rendering it useless as an insulator [3]. When a thin oxide layer is biased electrically, electrons tunnel through the Si/SiO<sub>2</sub> barrier. As oxide thickness is decreased from 8 to 2 nm, the transition from Fowler-Nordheim tunneling to direct tunneling occurs as electron conduction mechanism through the oxide [1,2,5,6]. This is described in greater detail in chapter 5.

| Material                       | Dielectric           | Band gap  | $\Delta E_{\rm C}({\rm eV})$ | Crystal      | Preparation   |

|--------------------------------|----------------------|-----------|------------------------------|--------------|---------------|

|                                | Constant( $\kappa$ ) | $E_G(eV)$ | to Si                        | Structure    | Methods       |

| SiO <sub>2</sub>               | 3.9                  | 8.9       | 3.2                          | Amorphous    | Thermal       |

| Si <sub>3</sub> N <sub>4</sub> | 7.0                  | 5.1       | 2.0                          | Amorphous    | LPCVD,        |

|                                |                      |           |                              |              | Thermal       |

|                                |                      |           |                              |              | Nitride, JVD, |

|                                |                      |           |                              |              | MOCVD         |

| Al <sub>2</sub> O <sub>3</sub> | 9.0                  | 8.7       | 2.8                          | Amorphous    | Sputtering,   |

|                                |                      |           |                              |              | ALCVD         |

| Y <sub>2</sub> O <sub>3</sub>  | 15.0                 | 5.6       | 2.3                          | Cubic        |               |

| La <sub>2</sub> O <sub>3</sub> | 30.0                 | 4.3       | 2.3                          | Hexagonal,   |               |

|                                |                      |           |                              | cubic        |               |

| Ta <sub>2</sub> O <sub>5</sub> | 26                   | 4.5       | 1-1.5                        | Orthorhombic | MOCVD         |

| TiO <sub>2</sub>               | 80.0                 | 3.5       | 1.2                          | Tetragonal   | MOCVD         |

| HfO <sub>2</sub>               | 25                   | 5.7       | 1.5                          | Mono, Tetra, | Sputtering,   |

| _                              |                      |           |                              | cubic        | ALCVD         |

| BaSrTiO <sub>3</sub>           | 190                  |           |                              |              | MOCVD, PVD    |

| ZrO <sub>2</sub>               | 25                   | 7.8       | 1.4                          | Mono, Tetra, | ALCVD         |

|                                |                      |           |                              | cubic        |               |

Table 3.1 Comparison of Relevant Properties of Various High-K Materials [11]

Silicon dioxide is an amorphous material, and as such its atomic dimensions are not well defined. Average Si-O bond lengths [7] in SiO<sub>2</sub> are dependent upon the local structures assumed ( $\alpha$ - or  $\beta$ -quartz, tridymite, cristobalite). In SiO<sub>2</sub>, Si forms four directional covalent bonds to oxygen atoms. The oxygen atoms are two fold coordinated with a large bond angle and a weak bond-bending force constant. The low average coordination and the floppiness of the oxygen site gives amorphous structure to SiO<sub>2</sub>.

As the SiO<sub>2</sub> thickness is reduced, the gate leakage current through the film increases. Leakage specifications are device design and application dependent. For silicon dioxide, at a gate bias of ~1 V, the leakage current changes from  $1 \times 10^{-12}$  A/cm<sup>2</sup> at ~35Å to  $1 \times 10$  A/cm<sup>2</sup> at ~15 Å [17]. When a gate stack is used, i.e., an under-layer of thin SiO<sub>2</sub> and a high- $\kappa$  dielectric as a gate oxide, then the conduction mechanism will differ in both the oxides and the exact mechanisms are not yet known [8].

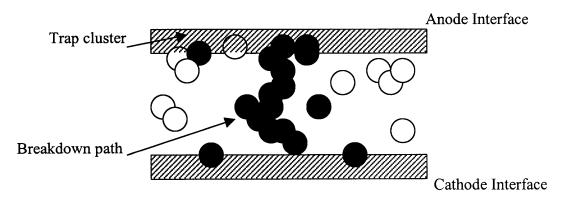

The percolation model suggested by DeGraeve et al. [5] describes breakdown in ultra thin oxides ( $\geq 2.5$  nm) as the buildup of many "defects" within the SiO<sub>2</sub> layer, where in after a certain amount of stress a complete path of defects form across the oxide thickness. This point defines breakdown or failure of the oxide.

Figure 3.1 Percolation model. When trap clusters join together, breakdown occurs [6].

At this moment, the capacitor discharges through the breakdown path and thermal effects can cause further damage to the oxide locally, creating a highly conductive breakdown path. The mechanism, which leads to the creation of these defects, is however, under debate. Figure 3.1 shows the percolation model.

The speed of MOSFETs is defined by how fast conduction electrons/holes can travel in the (inverted) channel between the source and drain regions of the transistor [6]. In ultra small devices, the electrons in the channel are located very close to the very heavily doped gate, source and drain regions and as a result, the electrostatic potential in the gate and source/drain regions can extend into the channel. The long-range electrostatic interactions between these charges may have a negative impact on the performance of devices with thinner gate oxide [6]. It is likely that these electrostatic interactions will require devices with thicker high- $\kappa$  dielectrics.

**Table 3.2** 2001 International Technology Roadmap for the Semicondutor Gate Stack. EOT is equivalent oxide thickness,  $I_g$  is gate leakage current density,  $T_{OX}$  is the oxide thickness [9]

| Year of First Product Shipment<br>Technology Node     | 2001<br>130nm     | 2004<br>90 nm     | 2007<br>65niii    | 2010<br>45nm      | 2013<br>32nm | 2016<br>22nm      |

|-------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|--------------|-------------------|

| EOT for high performance<br>T <sub>ox</sub> (nm)      | 1.3-1.6           | 0.9-1.4           | 0.6-1.1           | 0.5-0.8           | 0.4-0.6      | 0.4-0.5           |

| EOT for low operating power<br>T <sub>ox</sub> (nm)   | 2                 | 1.4               | 1                 | 0.9               | 0.8          | 0.7               |

| EOT for low standby power<br>T <sub>ox</sub> (nm)     | 2.6               | 2                 | 1.4               | 1                 | 0.9          | 0.8               |

| l <sub>g</sub> at 100C (A/cm²)<br>High Performance    | 2X10 <sup>1</sup> | 2X10 <sup>2</sup> | 1X10 <sup>3</sup> | 7X10 <sup>3</sup> | 5N104        | 3X10 <sup>5</sup> |

| l <sub>g</sub> at 100C (A/cm²)<br>Low operating power | 0.11              | 0.19              | 0.31              | 0.33              | 0.4          | 0.56              |

| Thickness control EOT (%)                             | <4                | <4                | <4                | <4                | <4           | <4                |

#### 3.2 Silicon Nitride (Si<sub>3</sub>N<sub>4</sub>)

Silicon Nitride has been researched for many years for its use in non-volatile memory devices. It has been known to be resistant to dopant diffusion. However, it causes threshold voltage shift. Also, its dielectric constant is not very high (Si<sub>3</sub>N<sub>4</sub>, $\kappa$ ~7.0, SiO<sub>2</sub>,  $\kappa$ ~3.9). It shows large amount of fixed charge as well as interface trap charges. Its interface properties are poor. Silicon has more affinity for O than for N. Incorporation of O is a method to improve the electrical properties of nitride layers [10].

The study of Si/Si<sub>3</sub>N<sub>4</sub> interface by Lazar et al [11] showed that the presence of oxygen benefits the properties of the dielectric layer. Hydrogen, however, was found to be a defect precursor. This is due to N-H and Si-H bonds. The Si/Si<sub>3</sub>N<sub>4</sub> interface is constrained. Bonding constraints arise due to differences between the average numbers of bonds per atom on each side of the interface. Studies show [12] that, when the average coordination is about 3.0, good quality interfaces are obtained. If it is more, then there is over coordination results, which increases the number of interface traps. If an oxide layer is grown prior to the nitridation, the properties of the interface improve as the coordination number reaches 3.0.

### 3.3 Oxynitrides

Dopant penetration through the gate dielectric causes change in threshold voltage [13]. The Si-O-N layer acts as a diffusion barrier to impurities [10]. One possible explanation is that the films are denser than SiO<sub>2</sub>. Additionally, diffusivity of N<sub>2</sub>O, NO, O<sub>2</sub> and N<sub>2</sub> is lower. However, the strong bond of N with the lattice may also be one of the reasons. The bonds are more constrained than that of SiO<sub>2</sub>. Consequently, nitrided lattice resists the

diffusion of atoms and small molecules. A number of models have been proposed to explain diffusion resistance of oxynitrides. One particular model suggests that the N competes with boron for occupation of the defect sites [14]. Another model [15] explains that Si-N bond stops the substitution of Si atom with dopant atom. The silicon interstitial generated at the interface during oxynitridation are blocked from diffusing into the oxide [10]. This results in an enhanced flux of the interstitial into the silicon substrates. Chemical Vapor Deposition (CVD), Atomic Layer Deposition (ALD) and Metal Organic Chemical Vapor Deposition (MOCVD) are among the methods utilized for depositing oxynitrides.

#### CHAPTER 4

# ALTERNATE GATE DIELECTRICS

# 4.1 Fundamentals of High Dielectric Constant Materials

As the feature sizes of complementary metal–oxide–semiconductor MOSFETs are scaled downward, the gate dielectric thickness must also decrease to maintain a value of capacitance, to reduce short channel effects and to keep device drive current at an acceptable level. The use of high- $\kappa$  dielectric materials as gate oxides has been proposed since 70's [16]. They are extensively in use in Dynamic Random Access Memory (DRAM) circuits [3]. Thicker films can be employed, when high- $\kappa$  materials are used as gate dielectrics. The high- $\kappa$  dielectrics under consideration for CMOS applications are Ta<sub>2</sub>O<sub>5</sub>, BaSrTiO<sub>3</sub>, TiO<sub>2</sub>, La<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub>, ZrO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub> and Y<sub>2</sub>O<sub>3</sub>. The aluminates and silicates are also of interest because they have higher crystallization temperatures than the pure oxides and show good interface properties.

Some gate dielectrics may form an interfacial layer during deposition even though they appear to be stable when in contact with silicon. Dielectrics such as  $HfO_2$  and  $ZrO_2$ are susceptible to oxygen diffusion, which can create interfacial layers during postdeposition annealing in oxygen atmosphere [3]. Such an interfacial layer may be a silicon oxide or silicate.

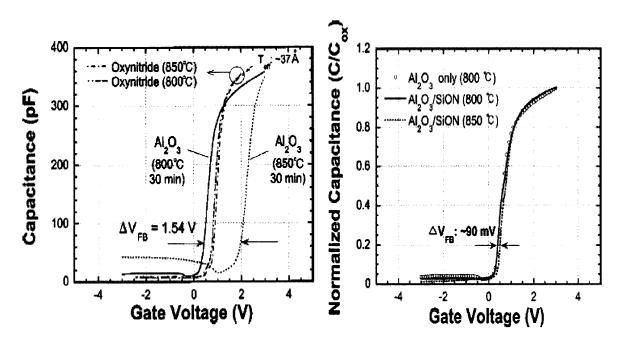

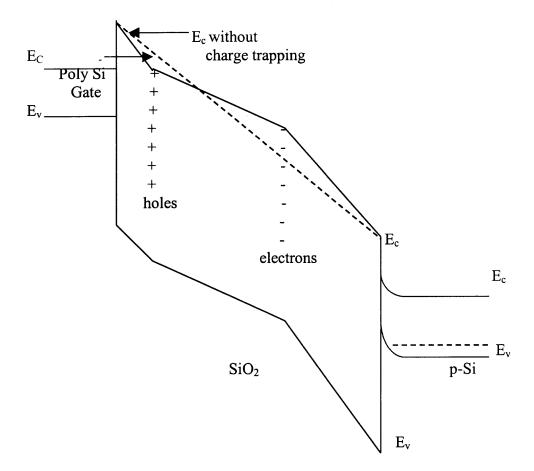

The incorporation of nitrogen into the silicon dioxide film reduces the defect generation rate. Defect generation rate is the density of defects produced per electron of a given energy that traverses the film, where the electron energy is determined by the applied potential or electric field [17]. Incorporation of a nitrogen-based interfacial layer is found to be effective in suppressing the diffusion of oxygen and subsequent growth of silicon oxide. In some studies, it has been shown that a silicate interfacial layer can be beneficial in reducing interface trap density and improving reliability [18]. Figure 4.1 illustrates the importance of interfacial layer in controlling the shift of  $V_{FB}$  denoted as  $\Delta V_{FB}$ .

Figure 4.1 The effect of SiON underlayer in Poly-Si/Al<sub>2</sub>O<sub>3</sub>/SiON ( $\sim$ 5Å)/In-Si MOS capacitor. The shift of the V<sub>FB</sub> is reduced from 1.54 V to -90mV [13].

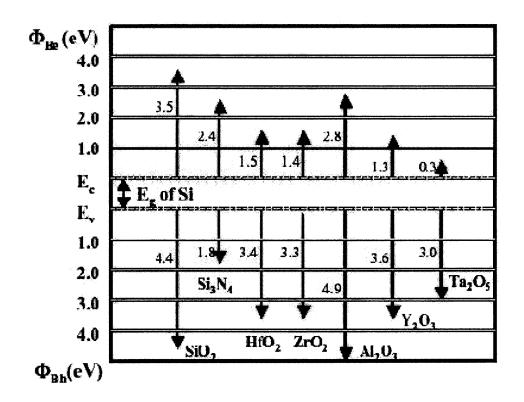

The rare earth oxides such as Lanthanides (i.e.,  $La_2O_3$ ,  $Y_2O_3$ ,  $Gd_2O_3$ , etc.) are found to be hydroscopic which means that they react with water and create a low permittivity interface (hydroxide layer) with the underlying silicon [19]. The new high-k dielectric material must demonstrate thermodynamic stability on silicon with respect to formation of SiO<sub>2</sub> and silicides or silicates. The interface between Si and a high- $\kappa$ dielectric is intrinsically heterovalent due to the large difference in average bond ionicity between the two interfaces. There is a mismatch between the number of electrons available and the number required for covalent bonding leading to intrinsic charged atoms i.e., defects at the interface. Some high- $\kappa$  dielectric films have a high amount of fixed charges. These charges modify the value of V<sub>T</sub> [20]. The interface should show high breakdown strength and acceptable reliability. For metal oxides, breakdown strength is inversely related to permittivity. They should demonstrate low conduction for low power. Low leakage current implies large band-offsets for electrons and holes. The carrier mobility at the dielectric/Si interface should be high. Therefore, low D<sub>it</sub> (e.g., 2E11/cm<sup>2</sup>eV<sup>-1</sup>), low bulk charge or low effective fixed charge at the dielectric/Si interfaces are required. Figure 4.2 illustrates the conduction band offsets of the various high permittivity layers[21].

**Figure 4.2** Conduction Band offset of SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub> and various high- $\kappa$  materials with Silicon.  $\Phi_{bh}$  and  $\Phi_{be}$  are the hole and electron barrier heights respectively [21].

Researchers are now finding ways to replace the polysilicon as gate electrode [3]. This is because of its reactivity with high- $\kappa$  materials e.g. ZrO<sub>2</sub>. Polysilicon depletion effect is the other reason. The reduction of polysilicon activation temperature may cause incomplete activation of the dopants leading to voltage drops across the gate. This is called the polysilicon depletion effect. This occurs because more concentrated activated dopants will have high capacitance while a less dense diffused and inactivated dopant will result in low capacitance. A tunable work function of a Si-based electrode is also required. Therefore, by changing nitrogen concentration, it can be used in both pMOS and nMOS devices [3]. This changes the Fermi level. However, high- $\kappa$  materials demand metal gate electrode. TiN and Pt are choice of metals that are currently being pursued. Metal electrode removes sheet resistance as well as dopant depletion effects.

Use of dual metal gate electrode requires extensive research, i.e., Al reacts with the gate dielectric. Platinum suffers from integration issues, i.e., it does not adhere and create good quality interface and it is costly, too [3]. Other disadvantage is that midgap materials require a threshold voltage of 0.5 V. However, due to scaling the applied voltage will be  $\sim$ 1.0 V. Thus, operation of the MOSFET might not be impossible at such a low voltage. Incorporating metal as gate electrode will require gate stack formation to be moved to the end of the process for reasons of thermal budget.

## 4.2 Alternative High-κ Gate Dielectrics

#### **4.2.1 Introduction**

High-k dielectric films are anticipated to be required by as early as 2005 for certain applications with low power and leakage current specifications [22]. Atomic coordination and bonding determine not just whether a solid can be amorphous or not, but also its electronic structure, because the electronic structure depends fundamentally on coordination, not on the presence of crystalline order.

Unlike SiO<sub>2</sub>, most of the metal oxides have ionic bonding. Moreover, these high- $\kappa$  metal oxides have localized metal-atom d states, which give rise to interface traps. The lowest conduction band offset energies of the high- $\kappa$  oxides and alloys are determined by the d-state energies of the respective transition metal or rare earth atom. The d states generally give rise to states in the gap or near the conduction band, whereas oxygen 2p comprises the top of the valence band [23]. Following is the brief description of the some of the promising high- $\kappa$  materials.

## 4.2.2 Deposition Techniques

Sputtering and electron beam evaporation are not advisable for depositing films of high permittivity materials because of potential radiation or ion-induced damage to the dielectrics. To deposit the thin high k layer, chemical vapor deposition (CVD) in one of its variations, such as metal-organic CVD (MOCVD), atomic layer deposition (ALD) or atomic layer CVD deposition (ALCVD), rapid-thermal CVD (RTCVD), plasma-enhanced CVD (PECVD), Jet Vapor Deposition (JVD) or remote plasma CVD (RPCVD) can be used. The CVD is a process by which a solid film can be formed on a substrate by

the reaction of vapor-phase chemicals that contain the required constituents [24]. Here, there is no consumption of substrate material. CVD thin films can be of high purity. However, a small contamination of carbon and hydrogen may be expected. They can be made of different compositions. Effective process control and good economy in operation can easily be achieved in CVD processes.

The energy for decomposition of the gases can be provided chemically, thermally or by plasma formation. The quality of the film is affected by substrate temperature, type of reactive species, their energy and rate of chemical supply [24]. CVD can be classified differently based upon the use of atmosphere, pressure and temperature.

In CVD systems, reactants are introduced into the reactor. The gas species are activated by mixing heat, plasma or by other means. This reactive species get adsorbed on the substrate surface. The adsorbed species undergo chemical reaction or react with other incoming species to form a solid film. The by-products of these reactions are desorbed from the substrate surface, which are then finally removed from the system [24]. CVD based techniques may find difficulty in yielding films with nucleation on a bare H-terminated silicon surface. Therefore, presence of interlayer of SiO<sub>2</sub> or nitrided SiO<sub>2</sub> is necessary, although, it means decreased permittivity.

Ultrahigh vacuum-physical vapor deposition (UHV-PVD) is attractive because it can be programmed easily for materials screening and studies, and provides very good chemical purity. However, it is still not commonly used for silicon device processing.

Plasma Enhanced Chemical Vapor Deposition (PECVD) uses energy in a plasma state to create more reactive radicals, allowing reactions to occur at lower temperatures. The film is dense. Lower amount of residue is found in the film because reactions occur in the plasma region. However, if process control is not optimized, high impurity levels may occur. Plasma processing may damage devices under conditions of excessive ion bombardment. The film has high residual stress.

Low Pressure Chemical Vapor Deposition (LPCVD) is a high temperature process. It gives good step coverage and high quality films. However, deposition rates are low and can only be used before Al deposition due to high temperature of process ( $\sim$ 900°C).

Molecular Beam Epitaxy (MBE) uses a substrate in high vacuum, while molecular or atomic beams of the constituents impinge upon its surface [2]. The components along with dopants are heated in separate chambers. Collimated beams of these components are directed on the surface of substrate. Good quality crystals can be grown by controlling the rate at which these beams impinge the substrate. Temperature of the substrate is lower than the components. By controlling the shutters, the doping level can be changed on lattice scale. MBE is comparatively costly because of the need for ultra-high vacuum and precise process control parameters.

Metal Organic Chemical Vapor Deposition (MOCVD) is also known as organometallic vapor phase epitaxy (OMVPE). It is widely used for deposition of epitaxial compound semiconductor films. MOCVD is distinguished by the chemical nature of the precursor gases. As the name implies, metal organic compound like Trimethylgallium (TMGa), Trimethyl-Indium (TMIn), etc. are employed. They are reacted with group V hydrides, and during pyrolysis the semiconductor compound is formed. This process can be used at moderately low temperatures. Deposition is efficient and reproducible. Carbon contamination may be one of its drawbacks [25].

## 4.2.3 Zirconium Oxide (ZrO<sub>2</sub>)

$ZrO_2$  is considered to be one of the front-runners in the race for replacing SiO<sub>2</sub>. It has dielectric constant of ~25. Its thermal stability is also considered to be very good up to 900°C. Barrier height and band offset with respect to silicon are also favorable. It has good interface quality with silicon. The electronic configuration of Zr is  $5s^24d^2$  [21]. It donates its four valence electrons to two oxygens, to make  $Zr^{4+}$  and two O<sup>2-</sup>, so that both ions have closed shells. The upper valence band consists of filled oxygen 2p sates and, higher up, empty 5s states [26]. The band gap of 5.8 eV is between the O 2p states and the Zr 4d states. It is given roughly by the difference of orbital energies in the free atom [27]. Figure 4.3 shows I-V measurements of the annealed  $ZrO_2/SiO_2$  gate stacks on n-type and p-type wafers [6].

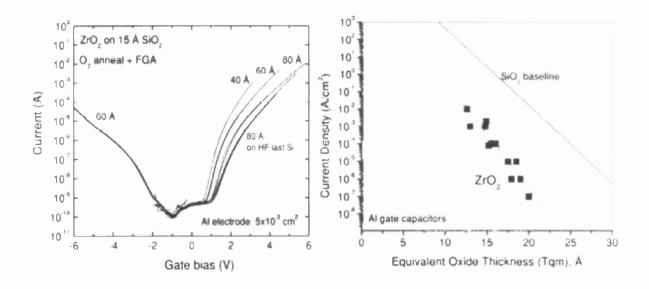

(a) (b) **Figure 4.3** (a) Current-Voltage measurements of annealed  $ZrO_2/SiO_2$  gate stacks on ntype and p-type wafers, (b) Gate leakage current density of  $ZrO_2$  gate stacks as a function of equivalent electrical thickness [6].

However, ZrO<sub>2</sub> suffers from some drawbacks also. When subjected to high temperature post deposition annealing, it crystallizes. This is a cause for concern, as it is believed that a crystallized phase may lead to heavy current leakage, although it has not yet been proved. This may occur because grain boundaries may serve as possible leakage paths [3,19]. It also causes problems of non-uniform dielectric properties.

Other studies [19] have shown that  $ZrO_2$  is susceptible to diffusion of oxygen, which results in the formation of low dielectric interfacial film of SiO<sub>2</sub> or silicate layer. In other words, it decreases the dielectric constant. Also, it is observed that when deposited by Atomic Layer Chemical Vapor Deposition Technique (ALCVD), without an under layer of SiO<sub>2</sub>, poor nucleation occurs. It is suggested [19] that during annealing, excess trapped oxygen in the ZrO<sub>2</sub> may be reacting with the silicon in the gate contact. This oxygen transport leads to interfacial SiO<sub>2</sub>, which results in low overall dielectric constant of the gate dielectric.

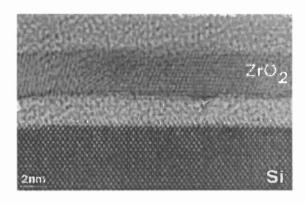

Figure 4.4 shows High Resolution Transmission Electron Microscope (HRTEM) image of 20Å  $ZrO_2$  on top of 15 Å SiO<sub>2</sub>. Studies in the literature [3] have shown that using Zirconium silicate helps remove some of the above-mentioned problems. It has less interface charge, as it is believed to be closer to SiO<sub>2</sub>.

Figure 4.4 HRTEM image of ZrO<sub>2</sub> deposited on oxidized Silicon by ALCVD [3].

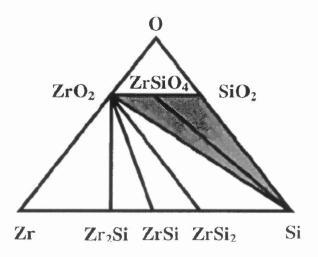

Figure 4.5 Zr-Si-O ternary system phase diagram [3].

In the present studies, it is speculated that  $ZrO_2$  reacts with the polysilicon and forms Zirconium silicide, which causes current leakage in the device . Zirconium silicide is an electrical conductor which reduces overall dielectric thickness of the material. Figure 4.5 shows the Zr-Si-O ternary phase diagram [3]. It indicates that metal oxide ZrO<sub>2</sub> and the compound silicate will both be stable in direct contact with Si even at high temperatures [3].

# 4.2.4 Yttrium (Y<sub>2</sub>O<sub>3</sub>) and Gadolinium Oxides (Gd<sub>2</sub>O<sub>3</sub>)

The rare earth oxides of Yttrium and Gadolinium are thermodynamically stable and have moderate dielectric constants of ~18 and ~14 respectively [19]. Encouraging results [3] have been shown in cases, where Molecular Beam Epitaxy (MBE) deposited  $Gd_2O_3$  films have been used. They are however; highly hygroscopic in nature meaning they react readily with water creating hydroxide layers. Moreover both are under constrained and may form very high defect densities. Trivalent compounds like Yttrium and Gadolinium generally form complex interfaces (i.e., hydroxides) [19].

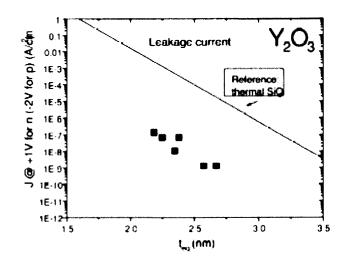

**Figure 4.6** Electrical leakage current densities of  $Y_2O_3$  films (thickness given in terms of equivalent SiO<sub>2</sub> thickness) and SiO<sub>2</sub> films [6].

$Y_2O_3$  has the cubic bixbyite (Mn<sub>2</sub>O<sub>3</sub> defect spinel) structure, in which Y is sevenfold coordinated [21].  $Y_2O_3$  has a large conduction band offset, but it is a fast ionic conductor. Thus, the oxygen ion diffusivity is high. Figure 4.6 shows low leakage of ALD deposited  $Y_2O_3$  compared to thermal SiO<sub>2</sub>.

# 4.2.5 Titanium Oxide (TiO<sub>2</sub>) and Tantalum Oxide (Ta<sub>2</sub>O<sub>5</sub>)

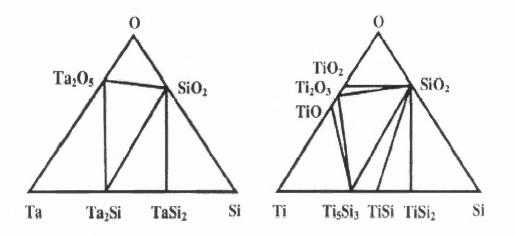

Titanium Oxide (TiO<sub>2</sub>) and Tantalum Oxide (Ta<sub>2</sub>O<sub>5</sub>) have high dielectric constants but they are not thermally stable with silicon. They crystallize above 400-650°C [3,28]. They will react with silicon and create SiO<sub>2</sub>. This layer will decrease the overall capacitance of the stack. Figure 4.7 shows ternary diagrams of Ta-Si-O and Ti-Si-O ternary systems at temperatures in the range of 700-900°C. It shows that Ta<sub>2</sub>O<sub>5</sub> and TiO<sub>2</sub> are not stable when deposited on Si. Figure 4.7 shows that they will tend to separate into phases of SiO<sub>2</sub> and metal oxide (M<sub>x</sub>O<sub>y</sub>, M= metal) [3].

Figure 4.7 Gibbs free energy diagrams for Ta-Si-O and Ti-Si-O ternary systems [3].

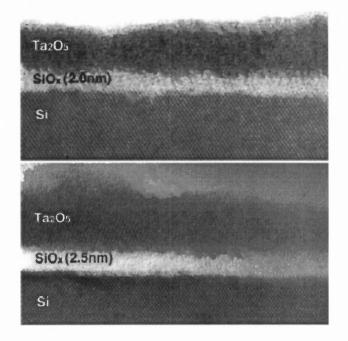

**Figure 4.8** HRTEM micrographs of tantalum oxide and interface with Si. (a) After low-temperature plasma anneal, and (b) RTA at 800°C [29].

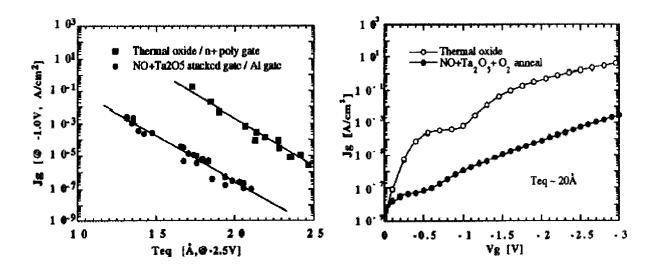

Figure 4.8 shows crystalline regions and growth of the interfacial region (2 nm.) after thermal annealing of  $Ta_2O_5$  gate stack [29]. Figure 4.9 (a) shows the comparison between  $Ta_2O_5$  and thermal oxide samples. The current leakage of  $Ta_2O_5$  devices is  $10^3x$  lower than that of thermal oxide at  $V_g$ = -1.0 V. Figure 4.9 (b) shows improved leakage

with the use of NO passivation layer [30]. If underlayer is not used, interfacial  $SiO_x$  is formed during deposition and post-deposition thermal treatments. At high temperature RTA, the interfacial oxide resembles  $SiO_2$ . Thus, a low temperature annealing is preferred.

Figure 4.9 (a) leakage current density comparison of different layers, and (b)  $J_g$ - $V_g$  characteristics of different dielectric films [30].

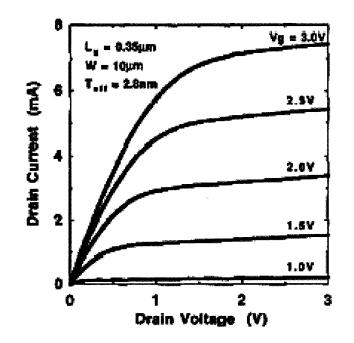

Ta<sub>2</sub>O<sub>5</sub> can be deposited by thermal oxidation, rf magnetron sputtering, UV-photo CVD, LPCVD, PECVD techniques. The conduction mechanism is Schottky emission at low electric field and Frenkel-Poole emission at high electrical field [28]. The underlayer can be oxide or nitrided oxide (NO) layer. This not only improves the interface between the Ta<sub>2</sub>O<sub>5</sub> and Si but also prevents further oxidation of Si due to the deposition process of Ta<sub>2</sub>O<sub>5</sub>. NO layer is stable compared to SiO<sub>2</sub> layer. Figure 4.10 shows the I-V characteristics of Ta<sub>2</sub>O<sub>5</sub>/SiO<sub>2</sub> gate insulator in nMOSFET with T<sub>eq</sub> of 2.8 nm and L<sub>g</sub> of 0.35µm [31].

Deposition of TiO<sub>2</sub> without an underlayer by CVD is extremely difficult but it can be deposited by Jet Vapor Deposition (JVD) process. Its high permittivity (~80-100) is due to a major contribution from soft phonons involving Ti ions. Ti has several stable oxidation states of Ti<sup>3+</sup> and Ti<sup>4+</sup>. This gives rise to reduced oxide. Reduced oxide has large number of oxygen vacancies, which act as carrier traps and high leakage paths [3].

**Figure 4.10** I<sub>d</sub>-V<sub>d</sub> characteristics of Ta<sub>2</sub>O<sub>5</sub>/SiO<sub>2</sub> nMOSFET [31].

### 4.3 Aluminum Oxide (Al<sub>2</sub>O<sub>3</sub>)

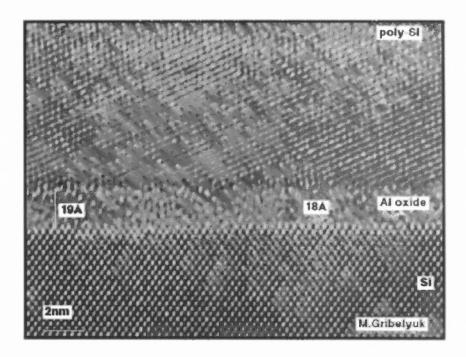

Alumina (Al<sub>2</sub>O<sub>3</sub>) is a group III-VI substance with useful properties for a gate dielectric. It has a large band gap, it is amorphous under conditions of interest and is thermodynamically stable with SiO<sub>2</sub>. In Al<sub>2</sub>O<sub>3</sub>, the electronic structure of the metal atom is Al  $3s^23p^1$  [21]. It donates its electrons to the oxygen to form Al<sup>3+</sup> and O<sup>2-</sup>. The upper valence states are filled O 2*p* states, while the conduction-minimum is the Al 3*s* state. The band gap is between the O 2*p* and the Al *s* states. Al forms more polar bonds to six oxygen atoms in crystalline  $\alpha$ -Al<sub>2</sub>O<sub>3</sub> (sapphire) and four to six oxygen atoms in its amorphous phase. The Al-O bond is 60-70% ionic. It is not a good glass former like SiO<sub>2</sub>. Al<sub>2</sub>O<sub>3</sub> is believed to have a large amount of fixed charge. This may result in a substantial shift in the threshold voltage. ALCVD, MBE or MOCVD can be used to deposit Al<sub>2</sub>O<sub>3</sub>. Figure 4.11 is a HRTEM image of an Al<sub>2</sub>O<sub>3</sub> gate stack [6].

Figure 4.11 HRTEM image of deposited and processed ALCVD layers of poly-Si/  $Al_2O_3/Si$  [6].

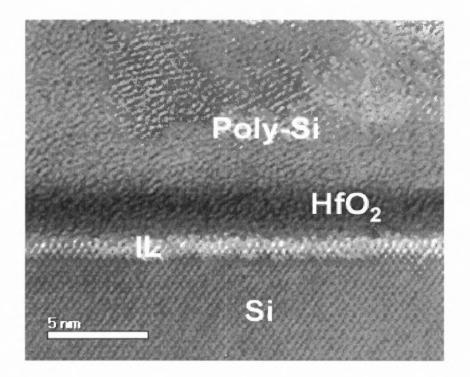

#### 4.4 Hafnium Oxide (HfO<sub>2</sub>)

HfO<sub>2</sub> appears promising due to its high dielectric constant (~25) as compared to SiO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub>. It has relatively high free energy of reaction with Si (47.6kcal/mole at 727°C) as compared to TiO<sub>2</sub> and Ta<sub>2</sub>O<sub>5</sub>. HfO<sub>2</sub> becomes crystallized above 950°C. It mainly

crystallizes in monoclinic phase and some tetragonal phases. At about 1000°C, HfO<sub>2</sub> has been found to interact with polysilicon [22].

The degradation of the mobility of the electrons up to 15% has been observed vis a vis SiO<sub>2</sub>. Poor nucleation of HfO<sub>2</sub> is observed on H-terminated surface [6]. This may be due to the absence of dangling bonds. HfO<sub>2</sub> is extremely susceptible to O diffusion and reaction at the channel interface. Therefore, high interface trap levels may be the other reason for the decrease in mobility. Many researchers [32] have reported promising results when the HfO<sub>2</sub> is sputter deposited. However, as the channel length decreases and device dimensions shrink, sputtering is not advantageous. So the Chemical Vapor Deposition techniques are the preferred methods for depositing the oxide. ALCVD<sup>TM</sup> is foremost amongst them. Figure 4.12 is the HRTEM image of Poly-Si/HfO<sub>2</sub>/SiO<sub>2</sub>/Si [33].

Figure 4.12 HRTEM image of Poly-Si/HfO<sub>2</sub>/SiO<sub>2</sub>/Si, where "IL" denotes the SiO<sub>2</sub> interfacial layer[33].

## 4.6 Rapid Thermal Annealing (RTA)

RTA has been used in the present study for post deposition annealing. RTA is used for spike activating implanted dopant particles in source and drain. It is also used to activate in-situ doped polysilicon. This is required since as-doped polysilicon is usually not activated and has high sheet resistance. Effect of spike annealing on high- $\kappa$  materials has also been studied. Spike annealing is rapid thermal annealing at a short cycle time [36].

RTA is also used for single wafer forming gas annealing in this study. The Rapid thermal annealing is intended to diffuse dopant from the implanted region near the surface to the gate oxide interface, creating in the ideal case a high active carrier concentration in the polysilicon at the interface with negligible diffusion of dopant through the oxide to silicon channel [36].

In other words, RTA is a widely used technique: (a) to create high carrier concentration at the polysilicon /gate dielectric interface, (b) to minimize the depletion depth in the polysilicon, (c) to have negligible penetration of the dopant to the crystalline silicon channel and to maintain gate dielectric reliability with minimal threshold voltage variation [35].

In-situ doped polysilicon was selected over ion-implantation because of the uniformity of the dopant density throughout the layer. In-situ doped polysilicon is heavily doped (5E21). This is to ensure reasonable conductance of the polysilicon gate. In-situ doped polysilicon is electrically inactive as deposited. Consequently, spike annealing has been used to activate the layer.

Electrical activation of the source and drain regions at high temperature proceeds by dissociation of the clusters and diffusion of the dopant that increases junction depth. Heavy dose of the dopant by ion implantation causes damage and strain in the silicon lattice. RTA reduces this strain and anneals out defects. Rapid thermal annealing creates electrically active dopants and reduces the sheet resistance. It reduces defect densities formed by impurities in junctions. Deposition of high- $\kappa$  layer results in a highly stressed film. RTA has some disadvantages. Ion implantation dose and screen oxide thickness variation can occur. It can create metrology problems as well as ambient gas combination variations [24].

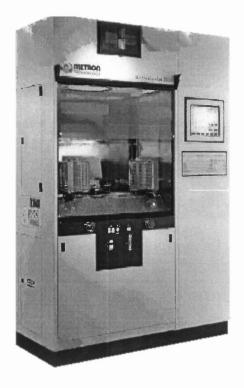

Various methods are used to perform RTA. The furnace bell jar method is largely heated on one side, although there is underside heating as the wafer is raised. Other techniques with single side wafer heating may use an array of incandescent lamps (Applied Materials), an arc lamp or a hot plate (Mattson). Incandescent lamp systems with dual sided heating surround the wafer with maximum lamp exposure to achieve high heating rates. There are tradeoffs in heating and cooling rates, time at maximum temperature, and process uniformity among the methods [34]. Figure 4.8 shows a Metron RTA machine. A similar type of machine has been used in the present study. Generally, multiple lamp methods require more complex multiple-zone power control and wafer rotation to achieve reasonable heating uniformity, compared to systems with a high power lamp or stationary heat source [34].

Figure 4.13 Metron AG HEATPULSE 8800 RTA machine [37].

## **CHAPTER 5**

# **ELECTRICAL CHARACTERIZATION**

# 5.1 Capacitance Voltage (C-V) Measurements

Two types of capacitances can be defined for the MOS capacitor. The static capacitance is defined as  $C_{\text{stat}} = (Q_T/V_G)$ , where  $Q_T$  is the total charge density on the capacitor and  $V_G$ is the bias applied to it. The differential capacitance is defined as  $C = (dQ_T/dV_G)$ . The differential capacitance is most important, because small signal measurements determine the rate of charge of charge with voltage [3].

The C-V measurements can be used to measure a) barrier height, b) deep impurity levels, c) interface traps, d) oxide thickness, e) silicon bend bending, and f) fixed charges. Carrier concentrations in polysilicon and crystalline Si are determined from band bending. The method is convenient, unambiguous, can be nondestructive and effective even for intrinsic samples. The shape of the C-V curve depends upon the type of substrate doping.

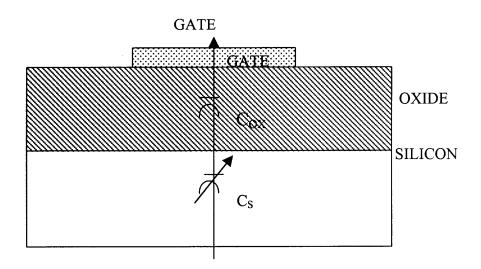

To measure capacitance as a function of gate bias in the steady state, a small alternating component of voltage is superimposed on the gate bias. The small signal range is the range of applied signal amplitude producing a linear response of ac current to ac voltage. Interface traps and interfacial charge non-uniformities influence the small signal range because they alter the variation of admittance of the MOS capacitor varies with gate bias [38]. Figure 5.1 shows the cross section of a MOS capacitor with a simple equivalent circuit.

Figure 5.1 Cross-section of an MOS capacitor showing a simple equivalent circuit [38].

#### 5.1.1 Low Frequency C-V Measurements

Minority carriers in silicon respond to low frequencies [38]. This behavior is observed because their response time is too slow at high frequency, where the cycle is very fast. Following is a discussion of the measurement of low frequency capacitance in a p-type MOS capacitor.

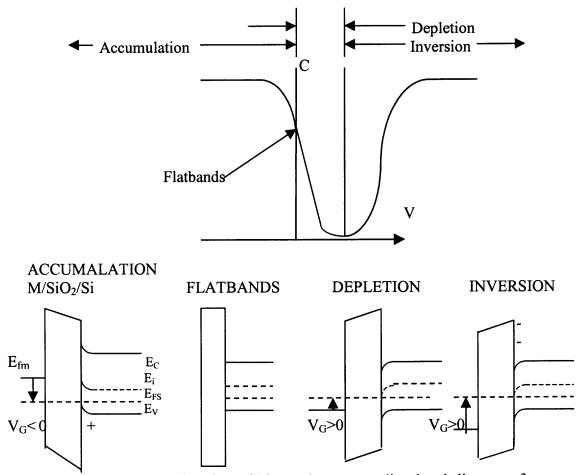

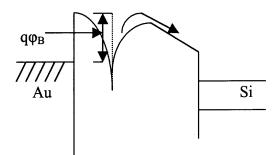

An application of bias across the MOS capacitor establishes the electric field in the oxide layer. For all values of gate bias below the oxide breakdown, no dc current flows when gate bias is applied. Consequently, the Fermi level is always flat as shown in Figure 5.2. When the voltage is increased more towards the negative side, the number of holes increases. At some point the number of holes is more than they are in the bulk. This increase in the number of holes contributes to a large differential capacitance. Thus, the capacitance of semiconductor exceeds that of oxide. When the gate bias is made less negative, there is a net decrease in the number of holes near the surface. Thus, the semiconductor capacitance decreases and the oxide capacitance dominates. As the gate bias is completely removed, the flatband point is reached as shown in Figure 5.2. When the positive bias is applied to the gate, the holes move away from the silicon surface, thereby, creating a depletion region as seen in Figure 5.2. Bands move downwards. These causes a decrease in  $c_s$ , therefore, overall capacitance decreases. Low frequency capacitance can be measured by the following equation [38]:

$$C_{s} = -Sin(u_{B} - u_{s})\left(\frac{\varepsilon_{s}}{\lambda_{i}}\right)\frac{Sinhu_{s} - Sinhu_{B}}{F(u_{s}, u_{B})} , \qquad (5.1)$$

where  $_{i}$  = intrinsic Debye length,  $_{s}$  = semiconductor dielectric constant,  $C_{s}$ = semiconductor capacitance,  $u_{s}$  and  $u_{b}$  are surface and bulk potential.

Figure 5.2 Capacitance as a function of bias and corresponding band diagrams for p-type MOS capacitor [3].

The intrinsic Debye length [38] is defined as  $\lambda_i = (\epsilon_s kT/2q^2n_l)^2$  cm. The value of  $\lambda_i$ , at T= 290°K, is 2.84x10<sup>-3</sup> cm using  $n_i = 10^{10}$  cm<sup>-3</sup>. As the positive gate bias is increased, the Fermi level crosses midgap and the electron and hole densities become equal. When more positive gate voltage is applied, the surface electron density increases compared to holes. This layer is called inversion layer. This inversion layer is also known as the channel.

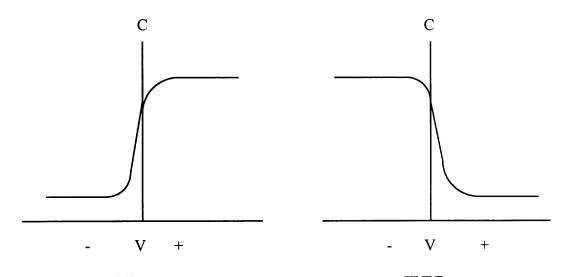

# 5.1.2 High frequency C-V measurements

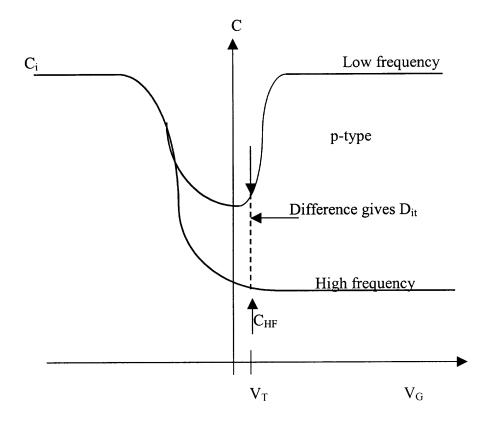

Figure 5.3 C-V measurements at various frequencies [2].

Figure 5.3 shows C-V curves at high and low frequencies. Here,  $C_{HF}$  is the high frequency capacitance,  $C_i$  is insulator capacitance and  $D_{it}$  is interface trap density. The capacitance  $C_i$  is inversely proportional to the thickness of the dielectric layer.

On comparing Figures 5.2 and 5.3 in the accumulation and depletion regions for  $D_{it}=0$ , the high and low frequency capacitance are the same. However, they differ in the inversion region.