#### **New Jersey Institute of Technology Digital Commons @ NJIT**

Theses and Dissertations Theses

Spring 2004

# Study of design tradeoffs of DRAM and SRAM memories, using HSPICE computer simulation

Bageshri Kale New Jersey Institute of Technology

Follow this and additional works at: https://digitalcommons.njit.edu/theses

Part of the Electrical and Electronics Commons

#### Recommended Citation

Kale, Bageshri, "Study of design tradeoffs of DRAM and SRAM memories, using HSPICE computer simulation" (2004). Theses. 551. https://digitalcommons.njit.edu/theses/551

This Thesis is brought to you for free and open access by the Theses and Dissertations at Digital Commons @ NJIT. It has been accepted for inclusion in Theses by an authorized administrator of Digital Commons @ NJIT. For more information, please contact digitalcommons@njit.edu.

### **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

#### **ABSTRACT**

#### STUDY OF DESIGN TRADEOFFS OF DRAM AND SRAM MEMORIES, USING HSPICE COMPUTER SIMULATION

#### by Bageshri Kale

Semiconductor random access memories are complex systems that can be described by performance parameters such as memory cycle time, access delays, storage capacity, bit packing density, chip area and retention time. In this thesis, tradeoffs between cycle time, chip area, and storage size as reflected by bit line capacitance (Cbl) were studied as a function of particular design variables: memory cell capacitance (Cc); CMOS flip-flop sense amplifier (SA) transistor sizes; and size of precharge (PC), and word line (WL) switches. Performance was optimized using circuit simulation software, HSPICE, to observe DRAM and SRAM waveforms. With TSMC 0.18 micron technology, minimum cycle times of 2.11ns (DRAM) and 1.18ns (SRAM) were achieved (Cbl = 100FF), by optimizing the  $k_r$  values of the SA transistors, for a fixed SA area of 1  $\mu$ m<sup>2</sup>, and finding the optimum PC switch width (1.6µm). To maintain the same cycle time when the Cbl of both SRAM and DRAM increased by N, the required total chip area was found to be increased by N<sup>2</sup>. For a constant memory capacity, the ratio of the change in the sense amplifier area to the change in memory cycle time for DRAM was found to be between 1.25 to three times that of SRAM, varying somewhat with cycle time. To optimize SRAM cycle time, the criteria of a bit line difference of 10% of 3V determined the time to terminate the connection of the bit line to the SRAM cell so as to avoid the loading of the parasitic Cc cell by the larger Cbl.

### STUDY OF DESIGN TRADEOFFS OF DRAM AND SRAM MEMORIES, USING HSPICE COMPUTER SIMULATION

by

Bageshri Kale

A thesis

Submitted to the Faculty of

New Jersey Institute of Technology

in Partial Fulfillment of the Requirements for the Degree of

Master of Science in Electrical Engineering

**Department of Electrical and Computer Engineering**

May 2004

#### APPROVAL PAGE

### STUDY OF DESIGN TRADEOFFS OF DRAM AND SRAM MEMORIES, USING HSPICE COMPUTER SIMULATION

#### Bageshri Kale

| Dr. Roy Cornely, Thesis Advisor                                                                   | Date |

|---------------------------------------------------------------------------------------------------|------|

| Professor of Electrical and Computer Engineering, NJIT                                            |      |

|                                                                                                   |      |

| Dr. Durgamadhab Misra, Committee Member<br>Professor of Electrical and Computer Engineering, NJIT | Date |

|                                                                                                   |      |

|                                                                                                   |      |

| Dr. Marek Sosnowski, Committee Member<br>Professor of Electrical and Computer Engineering, NJIT   | Date |

|                                                                                                   |      |

|                                                                                                   |      |

| Dr. Leonid Tsybeskov, Committee Member                                                            | Date |

#### **BIOGRAPHICAL SKETCH**

Author: Bageshri Kale

Degree: Master of Science

**Date**: May 2004

#### **Undergraduate and Graduate Education:**

Master of Science in Electrical Engineering,

New Jersey Institute of Technology, Newark, NJ, 2004

• Bachelor of Science in Electronics and Telecommunication Engineering, Cummins College of Engineering for Women, Pune, India, 2000

Major: Electrical Engineering

This thesis is dedicated to my family and my fiancée whose constant love and support helped me throughout my graduate studies.

#### ACKNOWLEDGMENT

From the formative stages of this thesis to the final draft, I owe an immense debt of gratitude to my advisor, Dr. Roy Cornely. His sound advice and careful guidance were invaluable during the course of my research for this thesis. I would also like to thank Dr. Durgamadhab Misra, Dr. Leonid Tsybeskov, and Dr. Marek Sosnowski for being part of the thesis evaluation committee and for their suggestions and comments. I want to thank Mr. James Dawson and John Davis from IBM, and Mr. Philip Diodato from Lucent, for their valuable guidance.

Finally, sincere thanks and appreciation to my parents, friends and family members for their constant moral support and help throughout my course of study.

Last, but not the least, my heartfelt thanks to my beloved Amit, without whose love and help, I would have never made it this far.

#### TABLE OF CONTENTS

| C | hapter                                                                                             | Page |

|---|----------------------------------------------------------------------------------------------------|------|

| 1 | INTRODUCTION                                                                                       | 1    |

|   | 1.1 Motivation                                                                                     | 1    |

|   | 1.2 Objectives                                                                                     | 1    |

|   | 1.3 Background                                                                                     | 2    |

|   | 1.4 Organization of thesis                                                                         | 3    |

| 2 | EXPERIMENTAL APPROACH                                                                              | 4    |

|   | 2.1 DRAM                                                                                           | 4    |

|   | 2.2 SRAM                                                                                           | 8    |

|   | 2.3 Basic Experiments                                                                              | 10   |

|   | 2.3.1 W/L Ratio of the Pre Charge Transistor                                                       | 10   |

|   | 2.3.2 Bit line length (Cbl value)                                                                  | 11   |

|   | 2.3.3 W/L Ratio of Sense Amplifier Transistors Keeping k <sub>r</sub> Constant                     | 12   |

|   | 2.3.4 Variation of the k <sub>r</sub> Ratio of the Sense Amplifier Transistors Keeping Wn Constant | 13   |

|   | 2.3.5 Variation of the k <sub>r</sub> Ratio of the Sense Amplifier Transistors Keeping Wp Constant | 14   |

|   | 2.3.6 Memory Cell Parameters                                                                       | 14   |

|   | 2.3.7 Word Line Switch                                                                             | 16   |

|   | 2.4 Three Dimensional Plots                                                                        | 17   |

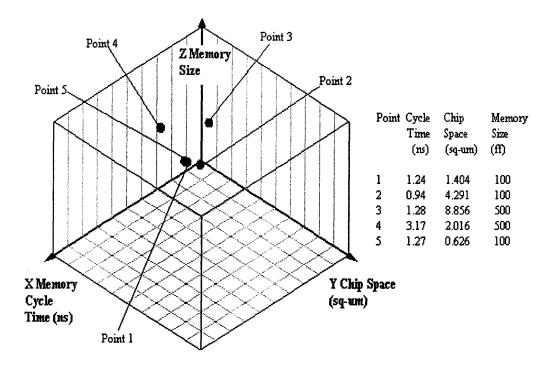

|   | 2.4.1 Experiment I – 3D Point Plots                                                                | 18   |

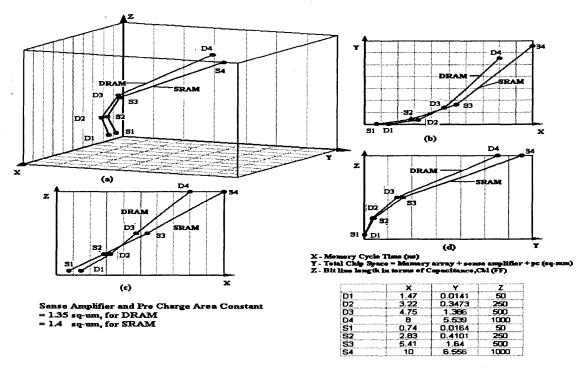

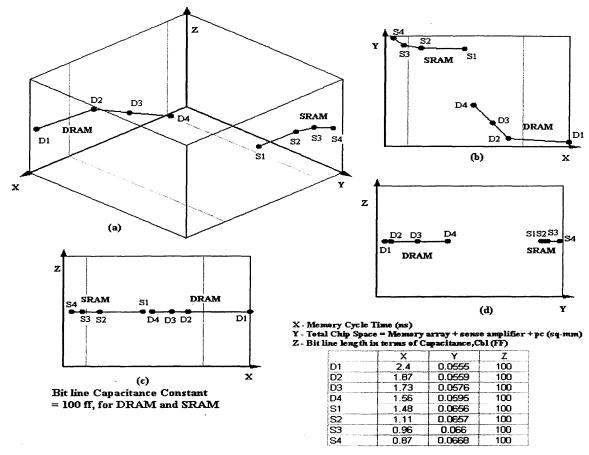

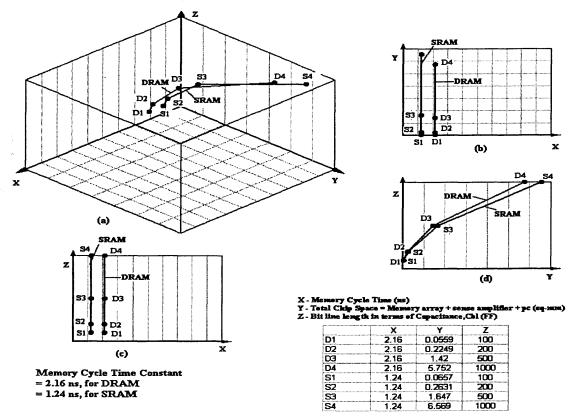

|   | 2.4.2 Experiment II – 3D Line Plots                                                                | 19   |

| 3 | EXPERIMENTAL RESULTS                                                                               | 21   |

## TABLE OF CONTENTS (Continued)

| Chapter                                                                                | Page |

|----------------------------------------------------------------------------------------|------|

| 3.1 DRAM                                                                               | 21   |

| 3.2 SRAM                                                                               | 23   |

| 3.3 Basic Experiments                                                                  | 25   |

| 3.3.1 W/L Ratio of the Pre Charge Transistor                                           | 25   |

| 3.3.2 Bit line length (Cbl Value)                                                      | 30   |

| 3.3.3 Effect of Varying the W/L of Sense Amplifier Keeping k <sub>r</sub> Constant     | 37   |

| 3.3.4 Variation of the k <sub>r</sub> Ratio of the Sense Amplifier Keeping Wn Constant | 43   |

| 3.3.5 Variation of the k <sub>r</sub> Ratio of the Sense Amplifier Keeping Wp Constant | 51   |

| 3.3.6 Memory Cell Parameters                                                           | 57   |

| 3.3.7 Word Line Switch                                                                 | 65   |

| 3.4 Three Dimensional Plots                                                            | 70   |

| 3.4.1 Experiment I – Three Dimensional Point Plots                                     | 70   |

| 3.4.2 Experiment II – Three Dimensional Line Plots                                     | 73   |

| 4 DISCUSSION                                                                           | 82   |

| 5 CONCLUSIONS AND SUGGESTIONS FOR FUTURE WORK                                          | 87   |

| REFERENCES                                                                             | 90   |

#### LIST OF FIGURES

| Figures |                                                                                                                                                                                              | Page |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.1     | DRAM Memory Cell with a flip-flop Sense Amplifier                                                                                                                                            | 4    |

| 2.2     | HSPICE file template for DRAM                                                                                                                                                                | 5    |

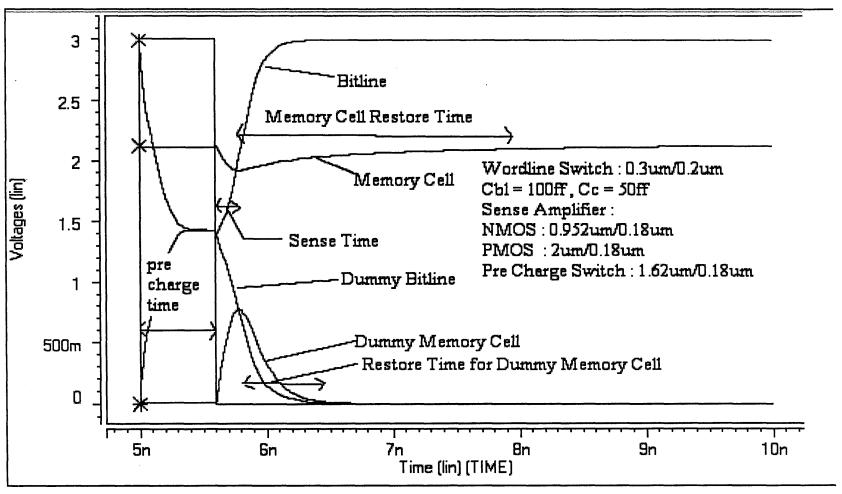

| 2.3     | Figure showing various times such as memory cycle time and bit line recovery time. Components of the memory cycle time – pre charge time, read and restore time.                             | 7    |

| 2.4     | SRAM Memory Cell with a flip-flop Sense Amplifier                                                                                                                                            | 8    |

| 2.5     | HSPICE file template for SRAM                                                                                                                                                                | 9    |

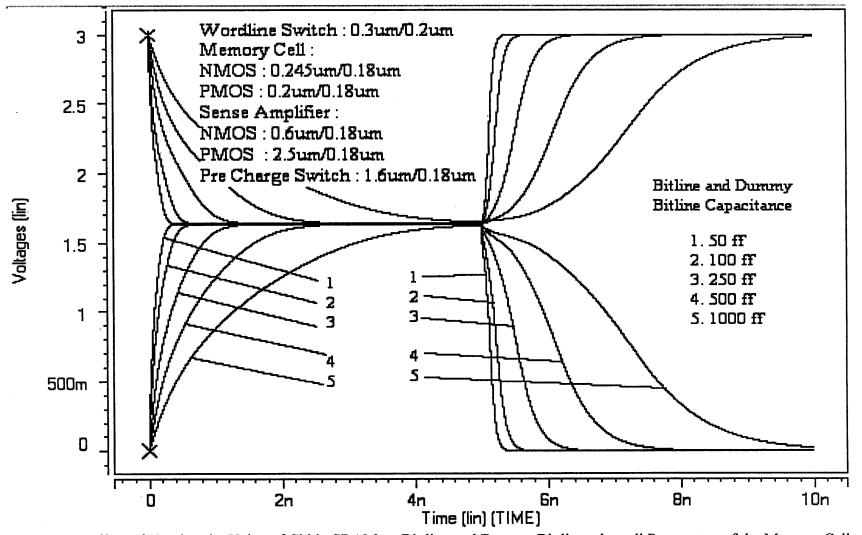

| 3.1     | HSPICE Waveforms for a DRAM Memory Cell and Dummy<br>Memory Cell and Sense Amplifier Showing the Pre Charge Time,<br>Bit Line, Dummy Bit Line, Memory Cell and Dummy Memory Cell<br>Response | 22   |

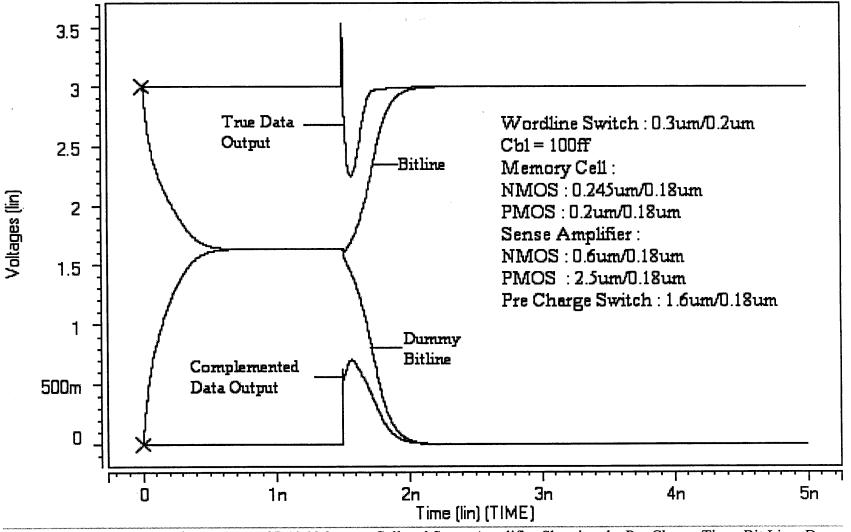

| 3.2     | HSPICE Waveforms for an SRAM Memory Cell and Sense<br>Amplifier Showing the Pre Charge Time, Bit Line, Dummy Bit Line<br>and True and Complemented Data Response                             | 24   |

| 3.3     | Effect of Varying Width of Pre Charge Transistor in the DRAM on Bit lines and Memory Cell                                                                                                    | 27   |

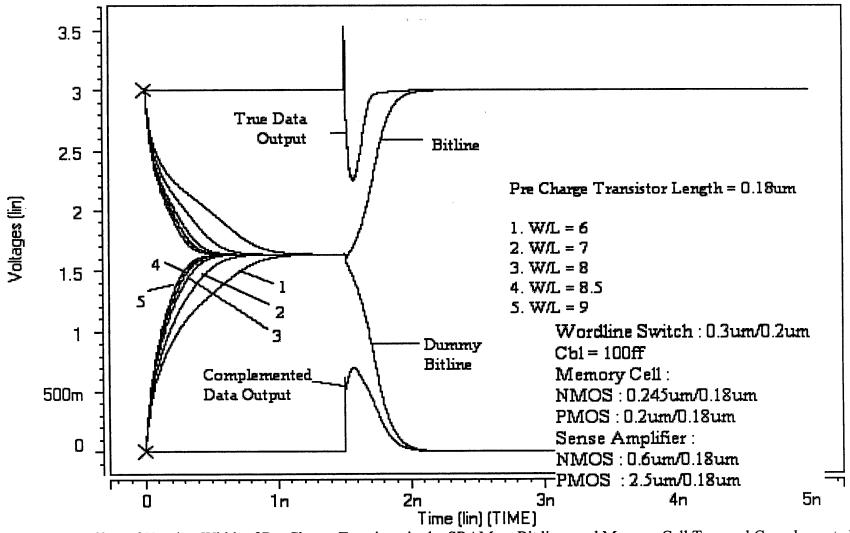

| 3.4     | Effect of Varying Width of Pre Charge Transistor in the SRAM on Bit lines and Memory Cell True and Complemented Data Outputs                                                                 | 28   |

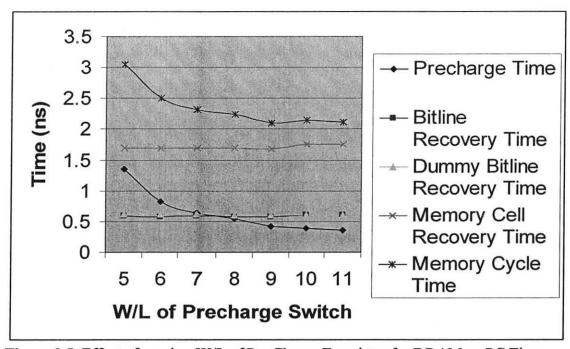

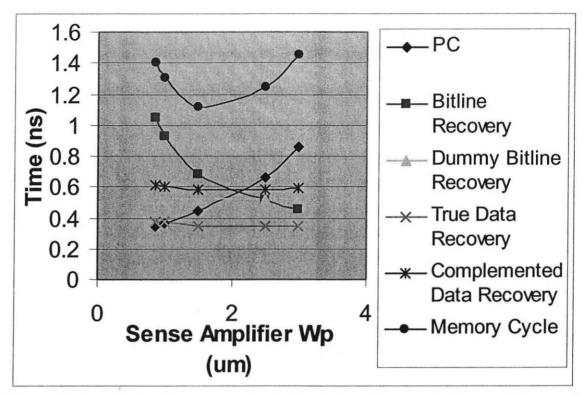

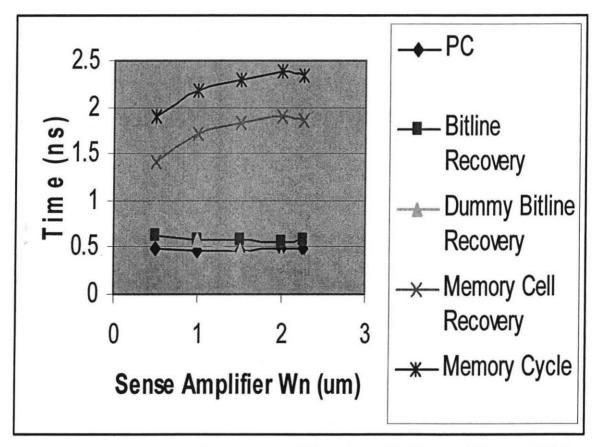

| 3.5     | Effect of Varying W/L of Pre Charge Transistor for DRAM on PC Time, Bit Line Recovery Time, Dummy Bit Line Recovery Time, Memory Cell Recovery Time and Memory Cycle Time                    | 29   |

| 3.6     | Effect of Varying W/L of Pre Charge Transistor for DRAM on PC Time, Bit Line Recovery Time, Dummy Bit Line Recovery Time, Memory Cell Recovery Time and Memory Cycle Time                    | 29   |

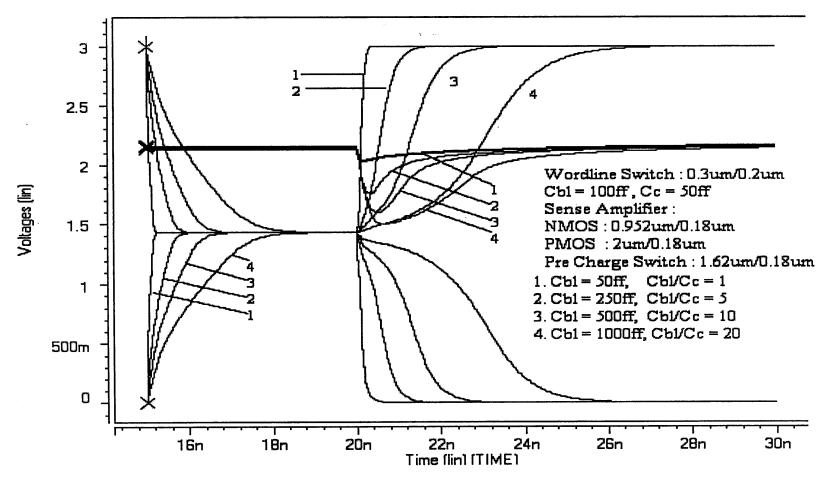

| 3.7     | Effect of Varying Cbl/Cc Ratio in DRAM on Bit lines and Memory Cell, When Cc=50ff                                                                                                            | 32   |

| 3.8     | Effect of Varying the Value of Cbl in SRAM on True and Complemented Data Outputs when all Parameters of the Memory Cell are Kept Constant                                                    | 33   |

| Figures |                                                                                                                                                                                                                                                         | Page |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 3.9     | Effect of Varying the Value of Cbl in SRAM on Bit line and Dummy Bit line when all Parameters of the Memory Cell are kept Constant.                                                                                                                     | 34   |

| 3.10    | Effect of Varying Cbl/Cc by Varying Cbl, for DRAM on PC Time, Bit Line Recovery Time, Dummy Bit Line Recovery Time, Memory Cell Read, Restore and Recovery Time and Memory Cycle Time                                                                   | 35   |

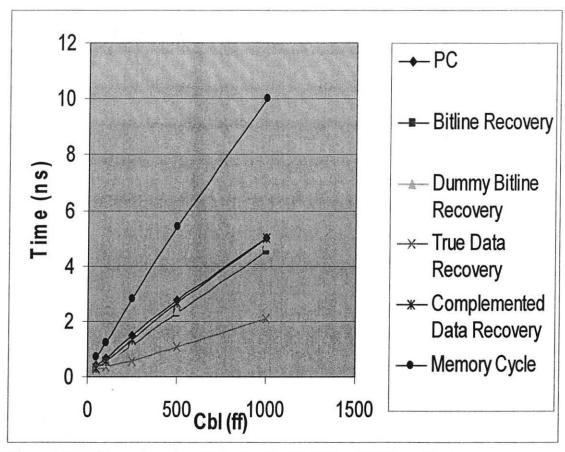

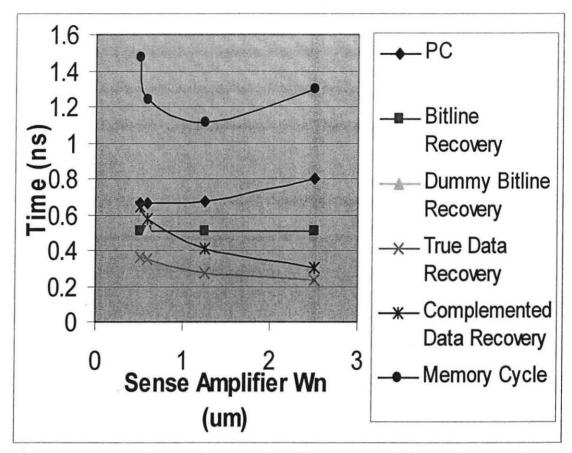

| 3.11    | Effect of Varying Cbl value for SRAM on PC Time, Bit Line Recovery Time, Dummy Bit Line Recovery Time, True and Complemented Data Recovery Time and Memory Cycle Time                                                                                   | 36   |

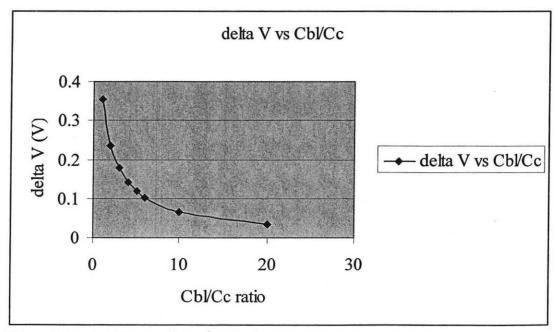

| 3.12    | ΔV Versus Cbl/Cc Ratio for DRAM                                                                                                                                                                                                                         | 36   |

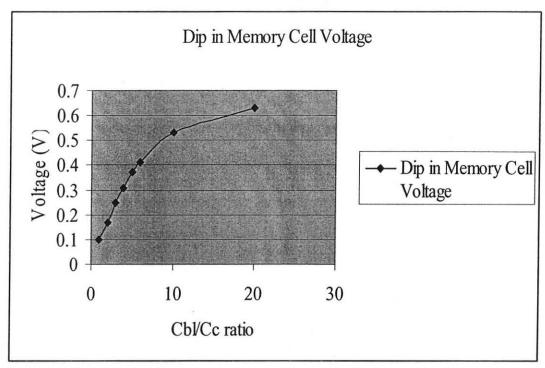

| 3.13    | Initial Dip in Memory Cell Voltage (During Read Operation) Versus Cbl/Cc Ratio for DRAM                                                                                                                                                                 | 37   |

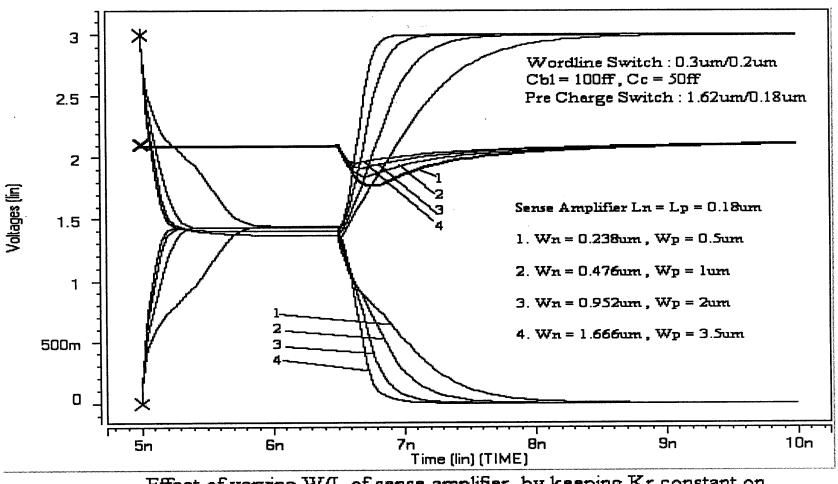

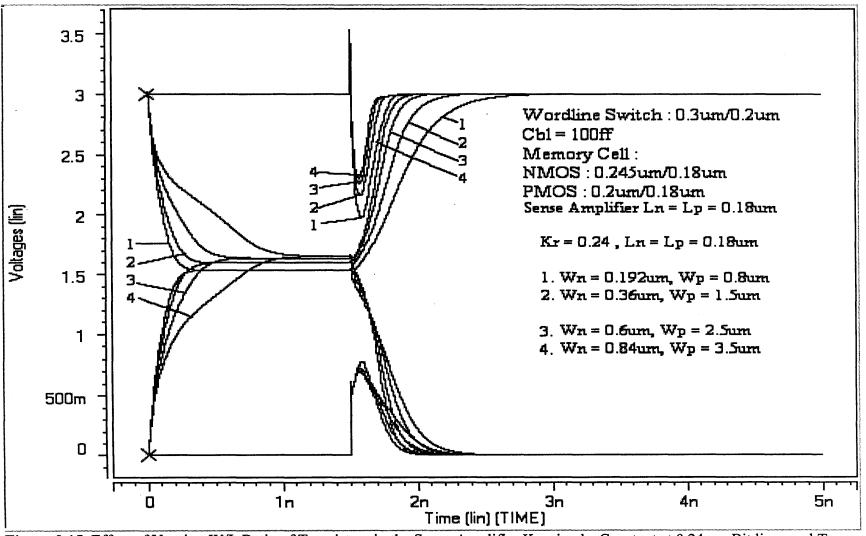

| 3.14    | Effect of Varying W/L Ratio of Transistors in the Sense Amplifier Keeping $k_r$ Constant, on Bit lines and Memory Cell for DRAM                                                                                                                         | 39   |

| 3.15    | Effect of Varying W/L Ratio of Transistors in the Sense Amplifier Keeping $k_{\rm r}$ Constant at 0.24, on Bit lines and True Data and Complemented Data Output for SRAM                                                                                | 40   |

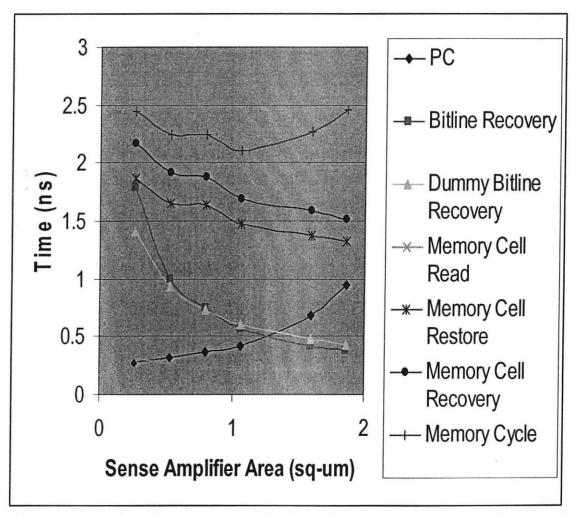

| 3.16    | Effect of Increasing the W/L Ratio and the Sense Amplifier Area for DRAM, keeping k <sub>r</sub> Constant at 0.476, on PC Time, Bit Line Recovery Time, Dummy Bit Line Recovery Time, Memory Cell Read, Restore and Recovery Time and Memory Cycle Time | 41   |

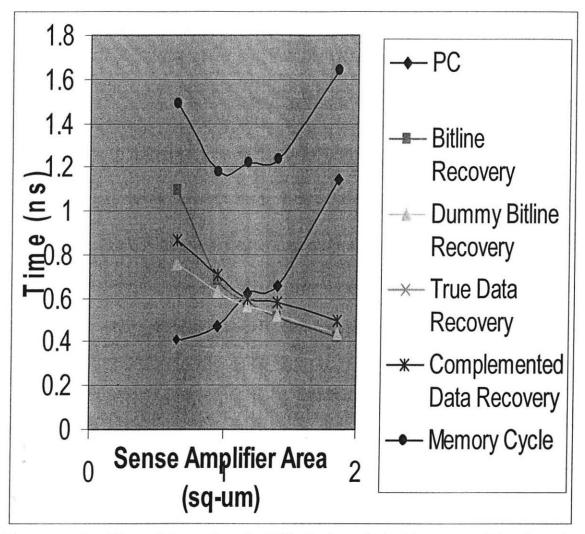

| 3.17    | Effect of Increasing the W/L Ratio and the Sense Amplifier Area for SRAM, keeping $k_r$ Constant at 0.24, on PC Time, Bit Line Recovery Time, Dummy Bit Line Recovery Time, True and Complemented Data Recovery Time and Memory Cycle Time              | 42   |

| 3.18    | Effect of Varying k <sub>r</sub> Ratio of Transistors in the Sense Amplifier by Varying Wp, on Bit lines and Memory Cell for DRAM                                                                                                                       | 45   |

| 3.19    | Effect of Varying k <sub>r</sub> Ratio of Transistors in the Sense Amplifier by Varying Wp, on Bit lines for SRAM                                                                                                                                       | 46   |

| Figures |                                                                                                                                                       | Page |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 3.20    | Effect of Varying $k_r$ Ratio of Transistors in the Sense Amplifier by Varying Wp, on the True and Complemented Data Outputs for the SRAM.            | 47   |

| 3.21    | Effect of Increasing Sense Amplifier Wp on Bit lines and Memory Cell for DRAM                                                                         | 48   |

| 3.22    | Effect of Increasing Sense Amplifier Wp, on Bit lines and True and Complemented Data Output for SRAM                                                  | 49   |

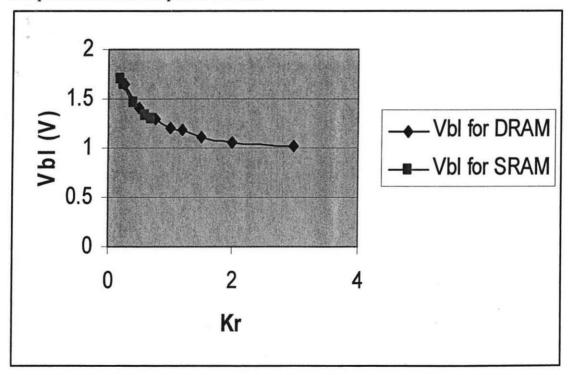

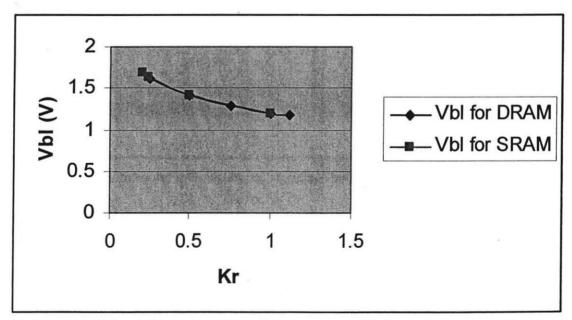

| 3.23    | Effect of Increasing $k_r$ Ratio of Transistors in the Sense Amplifier on the Bit line Common Voltage for DRAM and SRAM                               | 49   |

| 3.24    | Effect of Varying k <sub>r</sub> Ratio of Transistors in the Sense Amplifier, by Varying Wn, on Bit lines and Memory Cell for DRAM                    | 52   |

| 3.25    | Effect of Varying k <sub>r</sub> Ratio of Transistors in the Sense Amplifier by Varying Wn, on Bit lines for SRAM                                     | 53   |

| 3.26    | Effect of Varying k <sub>r</sub> Ratio of Transistors in the Sense Amplifier, by Varying Wn, on True and Complemented Data Outputs for the SRAM       | 54   |

| 3.27    | Effect of Increasing Sense Amplifier Wn, on Bit lines and Memory Cell for DRAM                                                                        | 55   |

| 3.28    | Effect of Increasing Sense Amplifier Wn, on Bit lines and True and Complemented Data Outputs for SRAM                                                 | 56   |

| 3.29    | Effect of Increasing $k_r$ Ratio of Transistors in the Sense Amplifier, on the Bit line Common Voltage for DRAM and SRAM                              | 56   |

| 3.30    | Effect of Varying Memory Cell Capacitance, on Bit lines and Memory Cell for DRAM                                                                      | 57   |

| 3.31    | Effect of Varying Memory Cell Capacitance, on Memory Cell for DRAM                                                                                    | 58   |

| 3.32    | Effect of Varying Widths of the Transistors in the Memory Cell, Keeping k <sub>r</sub> Constant, on Bit lines and True and Complemented Data for SRAM | 59   |

| Figures |                                                                                                                                                                              | Page |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 3.33    | Effect of Varying k <sub>r</sub> of Memory Cell by Varying Wp and Keeping Wn Constant, on Bit lines and True and Complemented Data for SRAM.                                 | 60   |

| 3.34    | Effect of Varying k <sub>r</sub> of Memory Cell by Varying Wn and Keeping Wp Constant, on Bit lines and True and Complemented Data for SRAM.                                 | 61   |

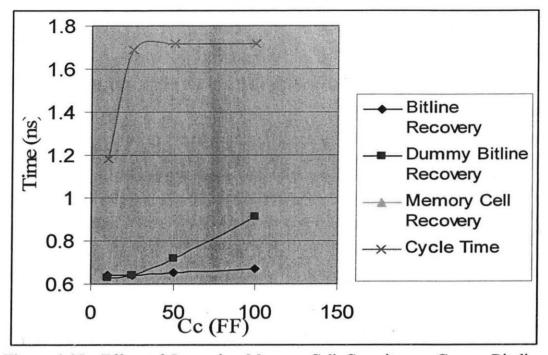

| 3.35    | Effect of Increasing Memory Cell Capacitance, Cc, on Bit lines and Memory Cell for DRAM                                                                                      | 62   |

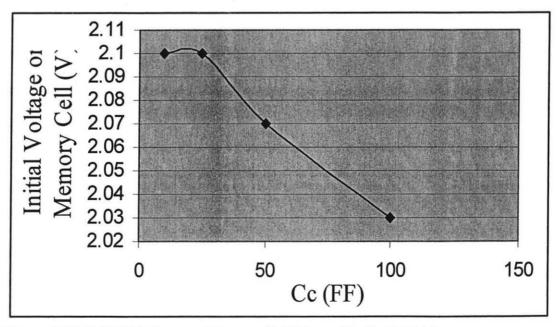

| 3.36    | Initial Voltage on Memory Cell Versus Cc for DRAM                                                                                                                            | 62   |

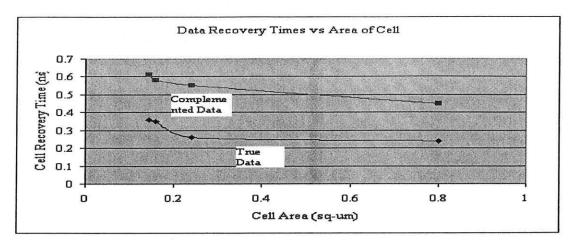

| 3.37    | Effect of Increasing Area of Memory Cell by Increasing Wn and Wp of the Transistors in the Memory Cell, on the Memory Cell True and Complemented Data Recovery Time for SRAM | 63   |

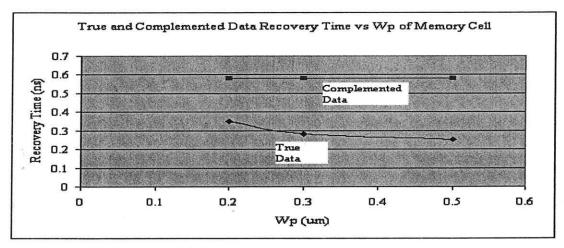

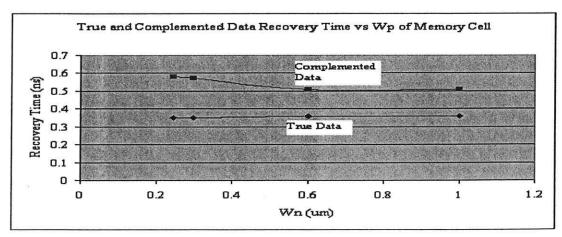

| 3.38    | SRAM Memory Cell True and Complemented Data Recovery Time Versus Wp of Memory Cell, Keeping Wn Constant                                                                      | 63   |

| 3.39    | SRAM Memory Cell True and Complemented Data Recovery Time Versus Wn of Memory Cell, Keeping Wp Constant                                                                      | 63   |

| 3.40    | Effect of Varying Word Line Switch Width on Bit lines for DRAM                                                                                                               | 66   |

| 3.41    | Effect of Varying Word Line Switch Width on Memory Cell for DRAM                                                                                                             | 66   |

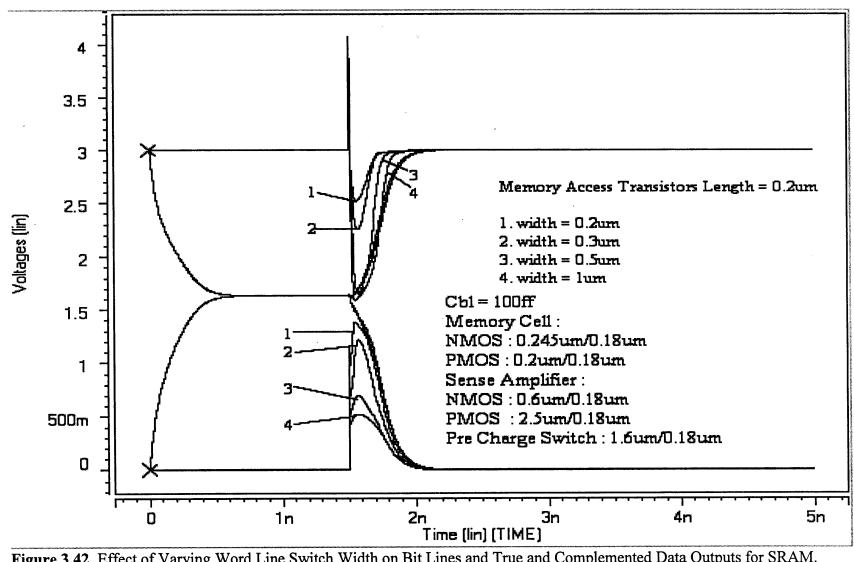

| 3.42    | Effect of Varying Word Line Switch Width on Bit Lines and True and Complemented Data Outputs for SRAM                                                                        | 67   |

| 3.43    | Memory Cell Recovery Time Versus Word Line Switch Width for DRAM and SRAM.                                                                                                   | 68   |

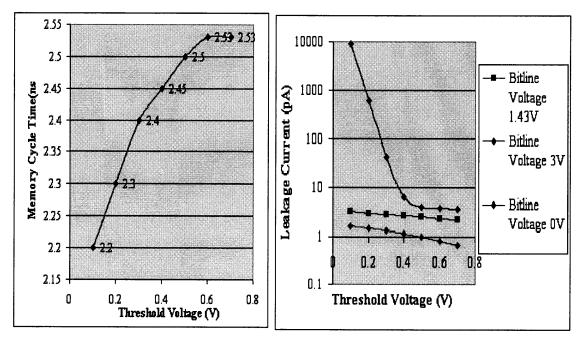

| 3.44    | Effect of Variation of Threshold Voltage of the Word Line Switch, on the Memory Cycle Time.                                                                                  | 69   |

| 3.45    | Comparison of Leakage Currents Through the Word Line Switch, With Bit Line Voltages of 3V and 1.43V                                                                          | 69   |

| 3.46    | Three Dimensional Plot Showing Various Operating Points for DRAM                                                                                                             | 71   |

| Figures |                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Page |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 3.47    | Three Dimensional Plot Showing Various Operating Points for SRAM.                                                                                                                                                                                                                                                                                                                                                                                         | 72   |

| 3.48    | (a) Three Dimensional Line Plot Showing Tradeoffs Between Memory Cycle Time(ns), Total Chip Space(mm2) and Bit Line Capacitance(ff). the Sense Amplifier and Pre Charge Area was Constant at 1.35um2 for DRAM and 1.4um2 for SRAM. (b) Tradeoff Between Total Chip Space(mm2) and Memory Cycle Time(ns). (c) Tradeoff Between Bit Line Capacitance(ff) and Memory Cycle Time(ns). (d) Tradeoff Between Bit Line Capacitance(ff) and Total Chip Space(mm2) | 74   |

| 3.49    | (a) Three Dimensional Line Plot Showing Tradeoffs between Memory Cycle Time(ns), Total Chip Space(mm2) and Bit Line Capacitance(ff). the Bit Line Capacitance was Constant at 100ff for Both DRAM and SRAM. (b) Tradeoff Between Total Chip Space(mm2) and Memory Cycle Time(ns). (c) Tradeoff Between Bit Line Capacitance(ff) and Memory Cycle Time(ns). (d) Tradeoff Between Bit Line Capacitance(ff) and Total Chip Space(mm2)                        | 77   |

| 3.50    | (a) Three Dimensional Line Plot Showing Tradeoffs between Memory Cycle Time(ns), Total Chip Space(mm2) and Bit Line Capacitance(ff). Memory Cycle Time was Constant at 2.16ns for DRAM and 1.24ns for SRAM. (b) Tradeoff Between Total Chip Space(mm2) and Memory Cycle Time(ns). (c) Tradeoff Between Bit Line Capacitance(ff) and Memory Cycle Time(ns). (d) Tradeoff Between Bit Line Capacitance(ff) and Total Chip Space(mm2)                        | 80   |

| 4.1     | Relation Between Memory Size and Bit Line Capacitance                                                                                                                                                                                                                                                                                                                                                                                                     | 82   |

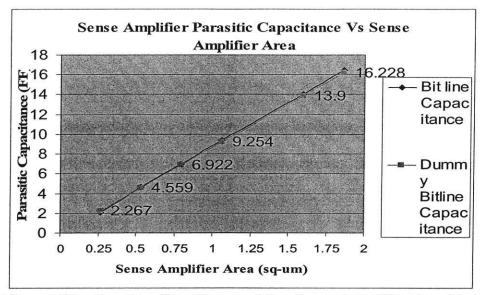

| 4.2     | Parasitic Capacitance of the Sense Amplifier Transistors Versus<br>Sense Amplifier Area.                                                                                                                                                                                                                                                                                                                                                                  | 83   |

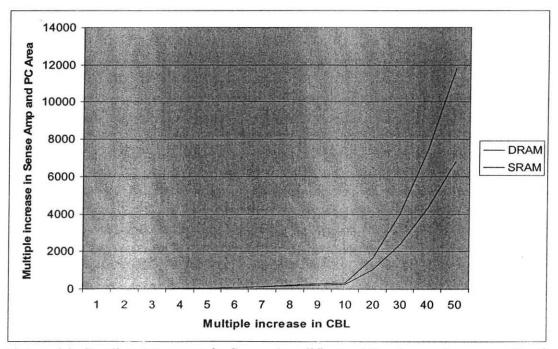

| 4.3     | Predicted Increase in Sense Amplifier and Pre Charge Area, as a Function of Increase in Cbl.                                                                                                                                                                                                                                                                                                                                                              | 84   |

| 4.4     | Tradeoff Between Threshold Voltage of the Word Line Switch, Memory Cycle Time and Leakage Current for DRAM                                                                                                                                                                                                                                                                                                                                                | 85   |

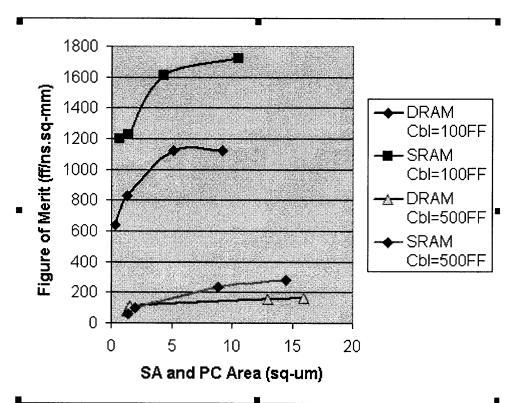

| 4.5     | Figure of Merit as a Function of Sense Amplifier and Pre Charge Area                                                                                                                                                                                                                                                                                                                                                                                      | 86   |

#### LIST OF TABLES

| Tabl | e                                                                                                                 | Pa |

|------|-------------------------------------------------------------------------------------------------------------------|----|

| 3.1  | Bit line and Memory Cell Times as a Function of Pre Charge Transistor W/L Ratio for the DRAM                      |    |

| 3.2  | Bit line and Memory Cell Times as a Function of Pre Charge Transistor W/L Ratio for the SRAM                      |    |

| 3.3  | Bit line and Memory Cell Behavior as a Function of Cbl/Cc Ratio for DRAM                                          |    |

| 3.4  | Bit line and Memory Cell Behavior as a Function of Cbl for SRAM                                                   |    |

| 3.5  | Bit Line and Memory Cell Behavior as a Function of W/L Ratio of Sense Amplifier for DRAM                          |    |

| 3.6  | Bit line and Memory Cell Behavior as a Function of W/L Ratio of Sense Amplifier for SRAM                          |    |

| 3.7  | Bit line and Memory Cell Behavior as a Function of k <sub>r</sub> Ratio of Sense Amplifier by Varying Wp for DRAM |    |

| 3.8  | Bit line and Memory Cell Behavior as a Function of k <sub>r</sub> Ratio of Sense Amplifier by Varying Wp for SRAM |    |

| 3.9  | Bit Line and Memory Cell Behavior as a Function of k <sub>r</sub> Ratio of Sense Amplifier by Varying Wn for DRAM |    |

| 3.10 | Bit Line and Memory Cell Behavior as a Function of k <sub>r</sub> Ratio of Sense Amplifier by Varying Wn for SRAM |    |

| 3.11 | Bit Line and Memory Cell Behavior as a Function of Memory Cell Capacitance for DRAM.                              |    |

| 3.12 | Bit line and Memory Cell Behavior as a Function of Varying Widths of the Transistors in the Memory Cell for SRAM  |    |

| 3.13 | Bit line and Memory Cell Behavior as a Function of k <sub>r</sub> of Memory Cell by Varying Wp for SRAM           |    |

| 3.14 | Bit line and Memory Cell Behavior as a Function of k <sub>r</sub> of Memory Cell by Varying Wn for SRAM           |    |

# LIST OF TABLES (Continued)

| Table |                                                                                                                                                                         | Page       |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 3.15  | Bit line and Memory Cell Behavior as a Function of Word Line Switch Width for DRAM                                                                                      | 65         |

| 3.16  | Bit line and Memory Cell Behavior as a Function of Word Line Switch Width for SRAM                                                                                      | 65         |

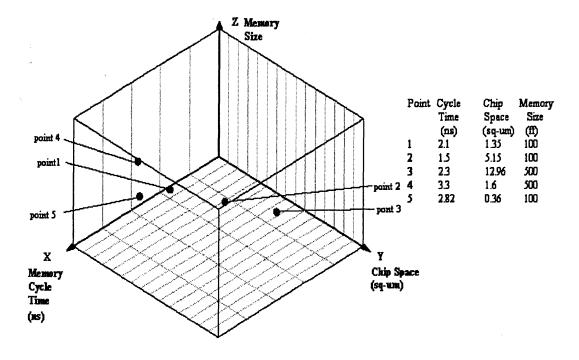

| 3.17  | DRAM Three Dimensional Plot Points and Variables Used to Plot these Points                                                                                              | 70         |

| 3.18  | SRAM Three Dimensional Plot Points and Variables Used to Plot these Points                                                                                              | 71         |

| 3.19  | Operating Points Showing Performance Parameters and Variable Values for Line Graph Keeping Sense Amplifier and Pre Charge Area Constant at 1.35um <sup>2</sup> for DRAM | 73         |

| 3.20  | Operating Points Showing Performance Parameters and Variable Values for Line Graph Keeping Sense Amplifier and Pre Charge Area Constant at 1.4um <sup>2</sup> for SRAM  | 74         |

| 3.21  | Operating Points Showing Performance Parameters and Variable Values for Line Graph for DRAM Keeping Cbl Constant at 100ff                                               | 76         |

| 3.22  | Operating Points Showing Performance Parameters and Variable Values for Line Graph for SRAM Keeping Cbl Constant at 100ff                                               | 76         |

| 3.23  | Operating Points Showing Performance Parameters and Variable Values for Line Graph for DRAM Keeping Memory Cycle Time Constant at 2.16ns.                               | <b>7</b> 9 |

| 3.24  | Operating Points Showing Performance Parameters and Variable Values for Line Graph for SRAM Keeping Memory Cycle Time Constant at 1.24ns                                | 80         |

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 Motivation

The study of semiconductor memories has been an important aspect of semiconductor technology. In the past three decades, engineers have strived to invent different types of memories and to improve their performance. Various performance criteria for memories are low cost, high performance, high density (less chip area), latency, low power dissipation, non-volatility, memory capacity and memory size. To improve the memory performance, it is very important to understand the tradeoffs between these performance criteria.

Of the different types of memories, MOS memories are dominating the memory market today. These fall into two categories – Read/Write Memories [Dynamic Random Access Memories (DRAM) and Static Random Access Memories (SRAM)] and Read Only Memories (ROMs). This thesis was initiated to obtain a better understanding of why some memory manufacturers in Japan have emphasized DRAM while those in USA have emphasized SRAM. The author was curious about the advantages and disadvantages of the two memory approaches.

#### 1.2 Objectives

This work presents the design tradeoffs between the three most important performance parameters for both DRAM and SRAM Memories. These parameters are the memory cycle time which is the time between subsequent memory operations, packing density

described in terms of the space consumed on the chip by the memory and the memory size in terms of number of bits. Each of these parameters can be effectively controlled by the memory designer by controlling various device and circuit variables.

#### 1.3 Background

The DRAM and SRAM allow the user both to read information from memory and to write new information into the memory while it is still in the system. The various components of the memory system include an array of memory cells, decoders and drivers to access a particular cell from the entire memory array and sense amplifiers to read the information stored in the cell (and to restore its information in case of DRAM). The memory array contains columns (bit lines) and rows (word lines). The intersection of a bit line and a word line constitutes a memory cell address. To select a particular memory cell from the array, initially a row is selected by activating a word line corresponding to the address and then a column is selected by activating the bit line. Data can then be written into or read from that memory cell.

Information is stored in DRAM by the presence or absence of charge on a memory capacitor, whereas in SRAM it is stored as a four transistor flip-flop state. The main difference amongst the two is that the DRAM memory capacitor loses its charge over a period of time and hence, DRAM memory has to be refreshed periodically. This increases the memory cell recovery time of DRAM. The SRAM does not lose its information as long as the power supply is kept on, but gains its speed at the cost of its chip area consumed per bit. The DRAM is more cost effective as compared to SRAM,

since due to its small size, its packing density is more and hence the number of bits stored in a chip area is more.

In order to read a memory cell, the word line switch transistor is turned on. The charge on the memory cell is shared with the bit line. This causes a reduction in the signal level and hence, a sensitive sense amplifier is required to detect this charge. A flip-flop is used as a sense amplifier throughout the thesis.

This thesis focuses on optimization of the memory cell and sense amplifier design. The variables used to optimize the design are widths and lengths of the transistors in the sense amplifier, precharge switch, memory cell access switch, memory capacitance, bit line capacitance and the  $k_r$  ratio of the invertors in the sense amplifier.

A circuit simulation software, HSPICE, has been used to simulate the memory behavior. Various design variables such as the width and length values for various transistors, memory cell and bit line capacitances are varied using HSPICE. CMOS 0.18µm technology has been used for describing the transistors, as this is now the industry standard. The input file for HSPICE describes the memory system, and on simulating this input file, an output file is generated. This output can be viewed graphically by using a post processor, AWAVES. Thus, performance goals as the cycle time can be measured and compared for variable design parameter values.

#### 1.4 Organization of Thesis

Chapter 2 describes the experimental setup. Chapter 3 presents the experimental results and Chapter 4, the experimental data obtained have been analyzed and tradeoffs have been discussed. In Chapter 5, conclusions are drawn based on the experiments.

#### CHAPTER 2

#### **EXPERIMENTAL APPROACH**

#### **2.1 DRAM**

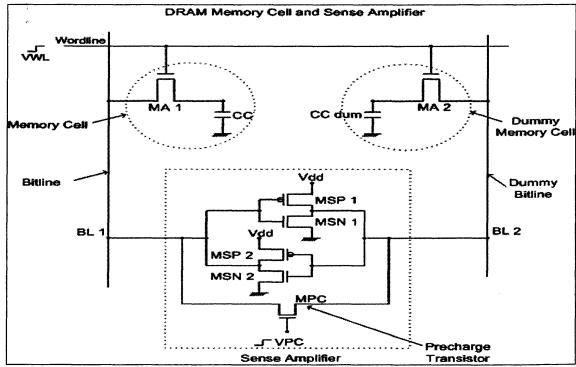

During the design of the memory system, emphasis was placed on optimizing the design of the DRAM memory cell and the sense amplifier. The one transistor and capacitor memory cell was selected for the DRAM memory cell as it is the industry standard. A circuit that either detects a change in voltage or a change in current could be chosen as a sense amplifier. Here a simple flip-flop sense amplifier that detects a change in voltage,  $\Delta V$ , has been selected. This sense amplifier has very low power dissipation. The figure below shows the circuit configuration for the DRAM Memory Cell, along with the bit lines, word lines, the sense amplifier, the dummy memory cell and the pre-charge signal.

Figure 2.1 DRAM Memory Cell with a flip-flop Sense Amplifier.

The circuit above was simulated using HSPICE. The HSPICE template used to describe it is shown below

DRAM options list node post VPC 2 0 DC 0 PULSE(0 3 0NS 0.001NS 0.001NS 0.6NS 5NS) VWL 6 0 DC 0 PULSE(0 3 0.6NS 0.001NS 0.001NS 4.4NS 5NS) VDD 3 0 DC 3 CBL1 5 0 100FF CBL2 4 0 100FF \*STORAGE CELL MA1 5 6 1 0 NCH W=0.3U L=0.2U CC 1 0 50FF MA2 4 6 7 0 NCH W=0.3U L=0.2U CCdum 7 0 50FF \*SENSE AMPLIFIER MSN1 4 5 0 0 NCH W=0.952U L=0.18U MSP1 4 5 3 3 PCH W=2U L=0.18U MSN2 5 4 0 0 NCH W=0.952U L=0.18U MSP2 5 4 3 3 PCH W=2U L=0.18U MPC 5 2 4 0 NCH W=1.62U L=0.18U OP. .TRAN 0.01NS 10ns start=5NS .INCLUDE PCH.M .INCLUDE NCH.M .PROBE V(1) V(2) V(3) V(4) V(5) V(6) V(7) END

Figure 2.2 HSPICE file template for DRAM.

The memory cell capacitance, "CC", is connected to bit line "CBL1" using the word line switch transistor "MA1". The sense amplifier consists of two invertors connected back to back. Transistors "MSN1" and "MSP1" form one inverter, "MSN2" and "MSP2" form the other inverter. A dummy memory cell "CCdum", word line switch "MA2" and dummy bit line "CBL2" are used to balance the sense amplifier. To get both

bit lines to have the same voltage, a pulse "VPC" is applied to the pre charge transistor "MPC". After the bit lines voltages are merged, "VPC" goes low and a pulse, "VWL", is applied at the gate of the word line switches, thus switching on the access transistors. The charge stored in the memory cell capacitor is shared with the bit line, causing the voltage on the bit line to change. The same operation is performed on the dummy memory cell. This generates a differential voltage,  $\Delta V$ , on the bit line pair which is applied to the sense amplifier for amplification. An analysis of the charge sharing between Cc and Cbl that occurs when the word line switch goes high, under the assumption of an ideal word line switch results in equation 2.1.

$$\Delta V = \underline{Vc - Vb1}$$

1+Cb1/Cc (2.1)

Referring to Equation 2.1, Vc is the initial voltage on the memory cell, Vbl is the common voltage to which the bit lines are pre charged, Cbl is the bit line capacitance and Cc is the memory cell capacitance.

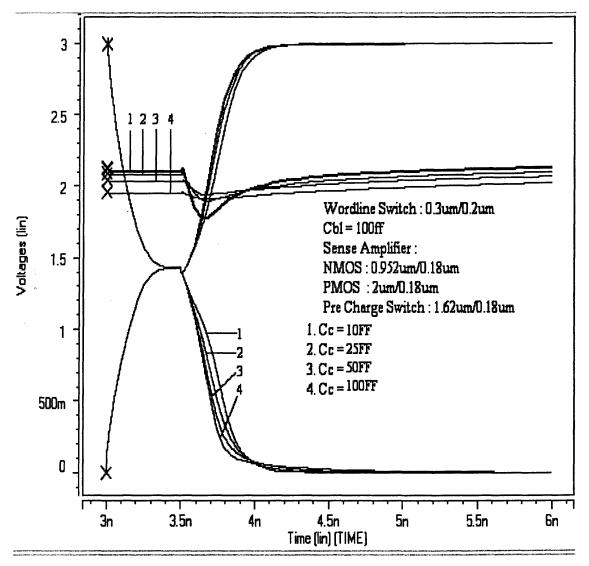

The CMOS 0.18μm technology was used to describe all the transistors in use. All N Channel transistors have been described using the model file "NCH.M" and P Channel transistors using the model file "PCH.M" The lengths of all transistors were restricted to 0.18μm and 3V power supply was used in all the experiments. Initially, memory cell capacitance value (Cc) was chosen as 50ff and bit line capacitance value (Cbl1 and Cbl2) as 100ff so that enough ΔV was generated for the sense amplifier.

The width (W)/length (L) ratio of the access switches was kept at 0.3μm/0.2μm. The W values of the sense amplifier and pre charge (PC) transistors were varied such that

minimum memory cycle time was achieved. The chosen Wn =  $0.952\mu m$ , Wp =  $2 \mu m$  giving  $k_r = 0.476$ . PC width =  $1.62 \mu m$ , giving a total sense amplifier area of  $1.35\mu m^2$ .

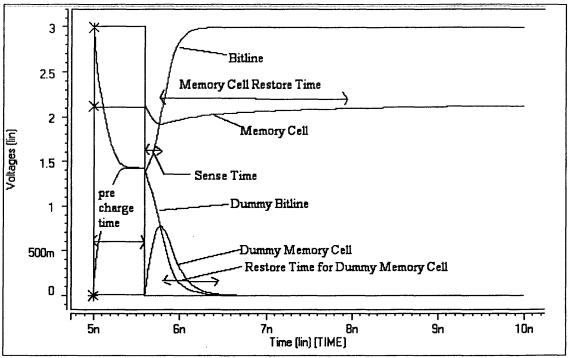

Figure 2.3 Figure showing various times such as memory cycle time and bit line recovery time. Components of the memory cycle time – pre charge time, read and restore time.

As can be seen in Figure 2.3, the memory cycle time consists of the pre charge time and the memory cell recovery time (for DRAM). For SRAM, it is equal to the PC time plus the worst case recovery time. The worst case recovery time is the maximum recovery time of the "1" cell, the "0" cell, the bit line and the dummy bit line. The pre charge time is the time required to merge the two bit lines to the same voltage value. Memory cell recovery time consists of the time required by the sense amplifier to read the charge on the memory cell and the time required to restore the memory cell to its initial value. All times have been measured by considering 0% to 99% swing of the voltage waveform.

#### **2.2 SRAM**

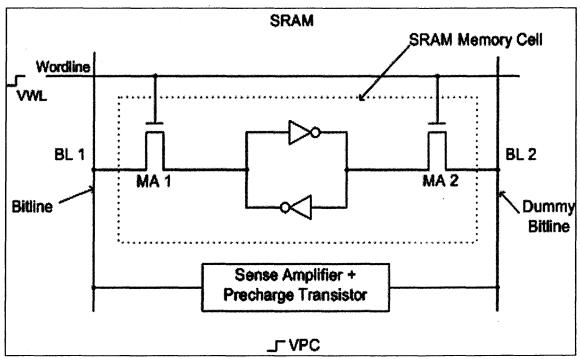

The difference between SRAM and DRAM lies in their memory cell structure. The SRAM memory cell gets its static nature because of the cross coupled four transistor flip-flop it uses. The circuit configuration for SRAM is shown in Figure 2.4 below. An SRAM memory cell uses two invertors connected back to back. Data are stored in this flip flop latch as a "1" state or a "0" state. When a high voltage (3V) is present on the left node (connected to access transistor MA1) of the flip-flop and a low voltage (0V) on the right node (connected to access transistor MA2), a "1" is present and when a high voltage (3V) is present on the right node and low voltage (0V) on the left node, a "0" is present. Memory access transistors MA1 and MA2 are used to connect the memory cell to the bit line BL1 and dummy bit line BL2. Other than the memory cell structure, all other components remain the same as DRAM.

Figure 2.4 SRAM Memory Cell with a flip-flop Sense Amplifier.

The HSPICE file used to describe the circuit in Figure 2.4 is given below

```

SRAM -

options list node post

vpc 7 0 dc 0 pulse(0 3 0ns 0.01ns 0.01ns 1.5ns 5ns)

vwl 6 0 dc 0 pulse(0 3 1.5ns 0.01ns 0.01ns 3.5ns 5ns)

vdd 3 0 dc 3

cbl1 4 0 100FF

cb12 5 0 100FF

*storage cell

MCN1 2 1 0 0 NCH W=0.245U L=0.18U

MCP1 2 1 3 3 PCH W=0.2U L=0.18U

MCN2 1 2 0 0 NCH W=0.245U L=0.18U

MCP2 1 2 3 3 PCH W=0.2U L=0.18U

MA1 4 6 2 0 NCH W=0.3U L=0.2U

MA2 5 6 1 0 NCH W=0.3U L=0.2U

*SENSE AMPLIFIER

MSN1 4 5 0 0 NCH W=0.6U L=0.18U

MSP1 4 5 3 3 PCH W=2.5U L=0.18U

MSN2 5 4 0 0 NCH W=0.6U L=0.18U

MSP2 5 4 3 3 PCH W=2.5U L=0.18U

MRS 5 7 4 0 NCH W=1.6U L=0.18U

OP.

TRAN 0.001NS 5NS

NODESET V(1)=3 V(2)=0

.INCLUDE PCH.M

.INCLUDE NCH.M

PROBE V(1) V(2) V(3) V(4) V(5) V(6) V(7)

END

```

Figure 2.5 HSPICE file template for SRAM.

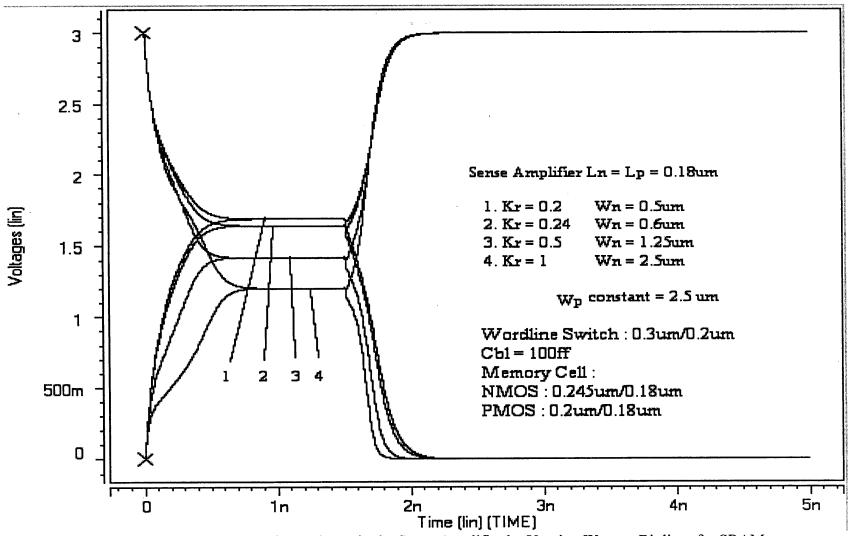

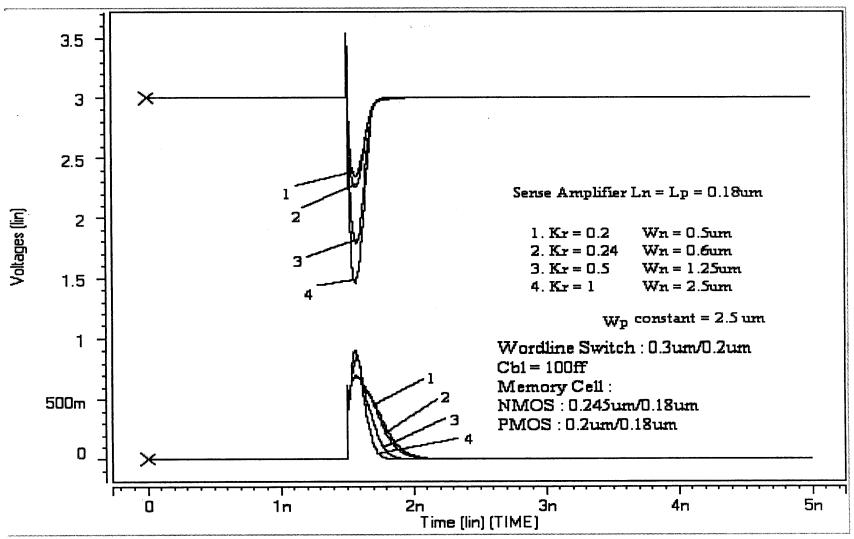

Transistor MCN1 and MCP1 form one invertor and MCN2 and MCP2 form the other invertor of the memory cell. The dimensions chosen for the memory cell transistors are – N Channel = 0.245um/0.18um, P Channel = 0.2um/0.18um. At these values, the charge sharing voltage dip in the "1" and "0" memory cell waveforms are observed to be

equal. The dimensions chosen for the sense amplifier transistors are -N Channel = 0.6um/0.18um, P Channel = 2.5um/0.18um. Using these values,  $k_r = 0.24$  and bit line and dummy bit line show perfect symmetry in recovery time.

#### 2.3 Basic Experiments

Performance goals for DRAM and SRAM memories are controlled by design variables. These design variables include the W/L ratio of the pre charge transistor, the value of Cbl, the W/L ratio of the transistors in the sense amplifier, the k<sub>r</sub> ratio of the invertors in the sense amplifier, the value for Cc in case of DRAM, the W/L ratio of the transistors in the memory cell (for SRAM), the k<sub>r</sub> ratio of the invertors in the memory cell (for SRAM) and the W/L ratio of the word line switch transistors. The effect of these parameters on the performance goals can be observed by designing a set of experiments in which each of these variables are varied and their influence on one or more performance goals is observed.

#### 2.3.1 W/L Ratio of the Pre Charge Transistor

Objectives – The objective of this experiment was to observe in which way the precharge transistor W/L effects the pre-charge time, the bit-line recovery and memory cycle times. It is expected that as width of PC increases, the current flowing through PC transistor increases and hence the time required to merge the bit lines should reduce resulting in a reduction in the recovery time.

#### Experimental Setup and Parameters varied -

The DRAM – PC transistor L was kept at  $0.18\mu m$  and W was varied from  $0.9\mu m$  to  $1.98\mu m$ . All other parameter values were as follows – Cbl = 100ff, Cc = 50ff, Pass

Switch =  $0.3/0.2\mu m$ , Sense amplifier – Wn =  $0.952\mu m$ , Ln =  $0.18\mu m$ , Wp =  $2\mu m$ , Lp =  $0.18\mu m$ ,  $k_r = 0.476$ .

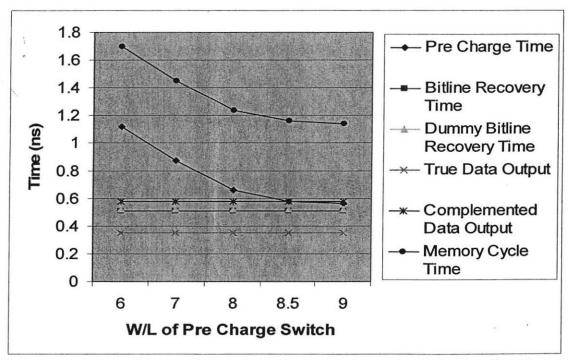

The SRAM – PC transistor L was kept at  $0.18\mu m$  and W was varied from  $1.2\mu m$  to  $1.8\mu m$ . All other parameters values were as follows – Cbl = 100ff, Pass Switch =  $0.3/0.2\mu m$ , Memory Cell – Ln = Lp =  $0.18\mu m$ , Wn =  $0.245\mu m$ , Wp =  $0.2\mu m$ , Sense amplifier – Wn =  $0.6\mu m$ , Ln =  $0.18\mu m$ , Wp =  $2.5\mu m$ , Lp =  $0.18\mu m$ ,  $k_r = 0.24$ .

#### 2.3.2 Bit line length (Cbl value)

Objectives – To observe the effect of varying the length of the bit line and thus the bit line capacitance (Cbl), on the bit lines and the memory cell recovery time. As the total memory size increases, the total length of the bit line increases, which leads to an increase in the bit line capacitance value. This experiment is performed to observe the effect that Cbl (and hence memory size) has on the system.

Referring to Equation 2.1, Vc depends upon the supply voltage and threshold voltage of the word line switch. Vbl depends on the  $k_r$  value of the invertors in the sense amplifier. Since these are held constant, Vc-Vbl is constant. Hence, as Cbl is increased, Vc and Vbl being constant,  $\Delta V$  should reduce. With the reduction in  $\Delta V$ , it should take more time for the sense amplifier to restore the memory cell and bit lines to their initial value. Thus, recovery time and cycle time should increase. Also, as Cbl is increased, it should take more time for the bit lines voltages to merge together.

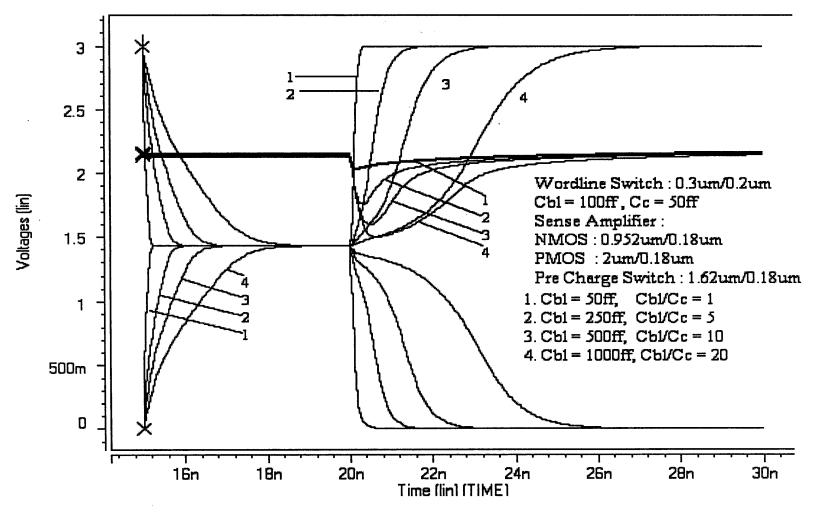

#### Experimental setup and parameters varied -

The DRAM – The Cbl value was varied from 50 ff to 1000 ff. All other parameter values were as follows – Cc = 50ff, Pass Switch =  $0.3/0.2\mu m$ , Sense amplifier – Wn =  $0.952\mu m$ , Ln =  $0.18\mu m$ , Wp =  $2\mu m$ , Lp =  $0.18\mu m$ ,  $k_r = 0.476$ , PC Switch =  $1.62\mu m$  / $0.18\mu m$ .

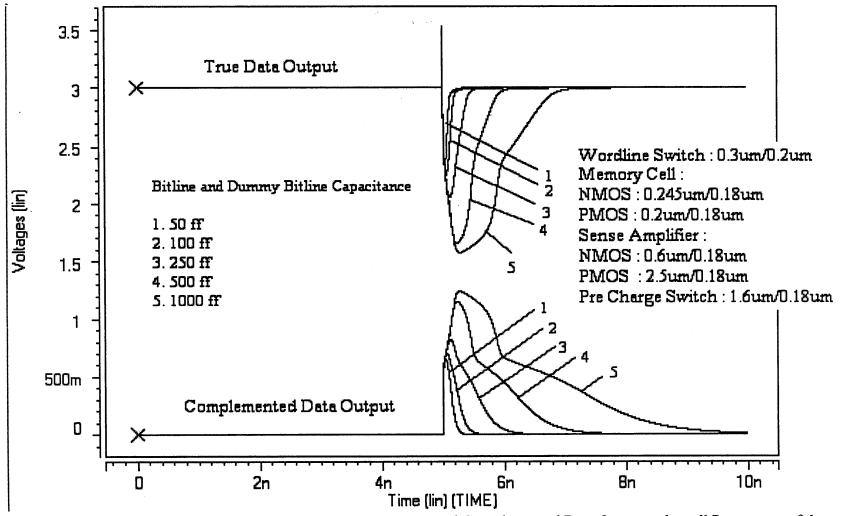

The SRAM – The Cbl value was varied from 50 ff to 1000 ff. All other parameter values were as follows – Pass Switch =  $0.3/0.2\mu m$ , Memory Cell – Ln = Lp =  $0.18\mu m$ , Wn =  $0.245\mu m$ , Wp =  $0.245\mu m$ , Sense amplifier – Wn =  $0.6\mu m$ , Ln =  $0.18\mu m$ , Wp =  $2.5\mu m$ , Lp =  $0.18\mu m$ ,  $k_r = 0.24$ , PC Switch =  $1.62\mu m$  / $0.18\mu m$ .

#### 2.3.3 W/L Ratio of Sense Amplifier Transistors Keeping k<sub>r</sub> Constant

Objectives – To observe the effect of increasing the sensitivity of the sense amplifier on the memory cycle time and the bit line recovery time. The sensitivity of the sense amplifier can be increased by increasing the W/L ratio of the transistors in the sense amplifier. The area of the sense amplifier is given by

Area =  $WL_{N1} + WL_{N2} + WL_{P1} + WL_{P2} + non transistor area$

Due to an increase in the W/L ratio of the transistors in the sense amplifier, the area of the sense amplifier unfortunately increases. The objective of this experiment is to study the tradeoff between the sense amplifier area and the memory cycle time.

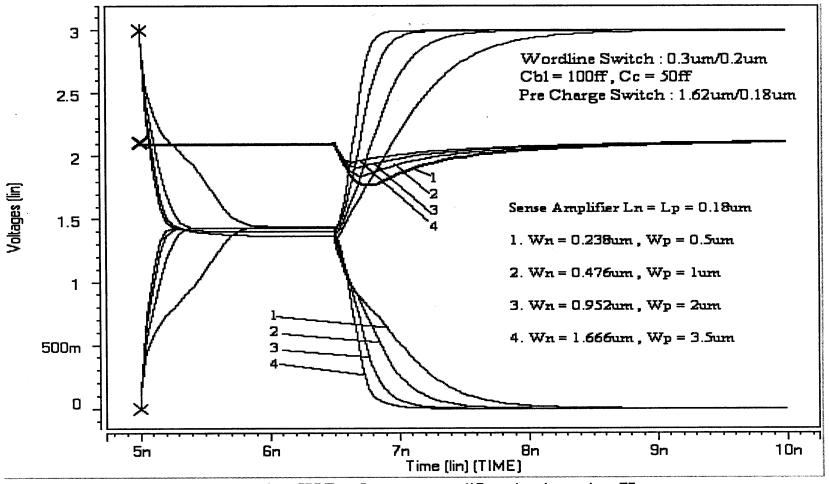

Experimental setup and parameters varied – W/L ratio of transistors in the sense amplifier was varied, keeping all other parameters constant as follows –

The DRAM – Sense amplifier: Ln = Lp =  $0.18\mu m$ . Wn was varied from  $0.238\mu m$  to  $1.666\mu m$  and Wp was varied from  $0.5\mu m$  to  $3.5\mu m$ , such that  $k_r$  was constant at 0.476.

All other variable values were kept constant as follows – Cbl = 100ff, Cc = 50ff, Pass Switch =  $0.3/0.2\mu m$ , PC Switch =  $1.62\mu m$  /0.18 $\mu m$ .

The SRAM – Sense amplifier: Ln = Lp =  $0.18\mu m$ . Wn was varied from  $0.192\mu m$  to  $0.84\mu m$  and Wp was varied from  $0.8\mu m$  to  $3.5\mu m$ , such that  $k_r$  was constant at 0.24. All other variable values were kept constant as follows – Cbl = 100ff, Pass Switch =  $0.3/0.2\mu m$ , PC Switch =  $1.62\mu m$  / $0.18\mu m$ , Memory Cell – Ln = Lp =  $0.18\mu m$ , Wn =  $0.245\mu m$ , Wp =  $0.245\mu m$ .

### 2.3.4 Variation of the $k_r$ Ratio of the Sense Amplifier Transistors Keeping Wn Constant

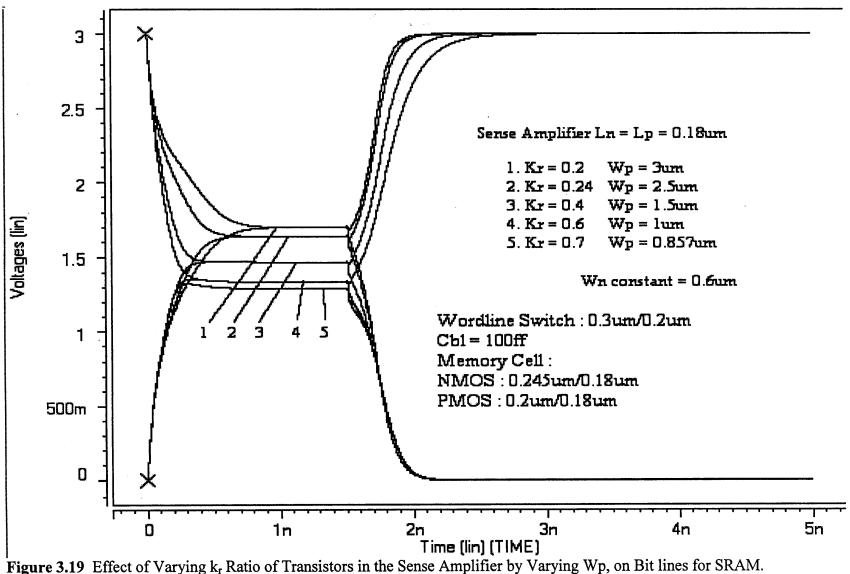

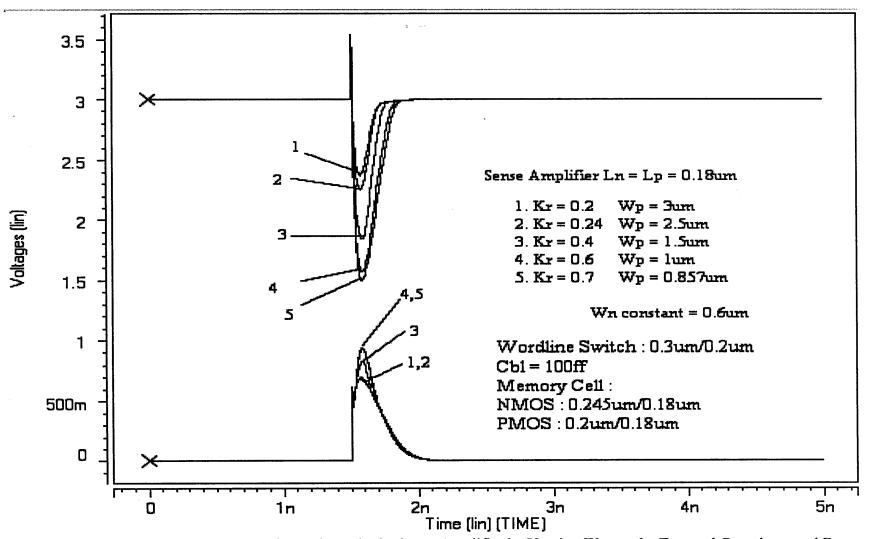

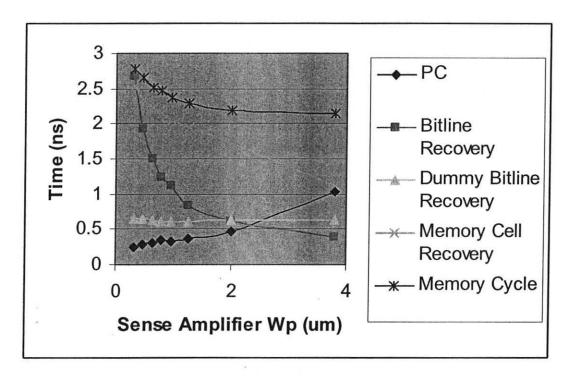

**Objectives** – To observe the effect of varying  $k_r$  on performance goals. As  $k_r$  is varied, the unstable operating point voltage for the bit lines varies. This results in variance in the bit line and memory cell recovery time and also the PC time. In this experiment Wn was kept constant, and Wp was varied to vary  $k_r$ . The PMOS affects the bit line. As Wp is increased, the bit line recovery time should be reduced.

#### Experimental setup and parameters varied -

The DRAM – Value of Wp was varied, such that  $k_r$  was varied from 0.25 to 3 and all other parameters were kept constant as follows – Cbl = 100ff, Cc = 50ff, Pass Switch = 0.3 $\mu$ m /0.2 $\mu$ m, Sense amplifier – Wn = 0.952 $\mu$ m, Ln = 0.18 $\mu$ m, Lp = 0.18 $\mu$ m, PC Switch = 1.62 $\mu$ m /0.18 $\mu$ m.

The SRAM – Value of Wp was varied, such that  $k_r$  was varied from 0.2 to 0.7 and all other parameters were kept constant as follows – Cbl = 100ff, Pass Switch = 0.3/0.2 $\mu$ m, Memory Cell – Ln = Lp = 0.18 $\mu$ m, Wn = 0.245 $\mu$ m, Wp = 0.2 $\mu$ m, Sense amplifier – Ln = Lp = 0.18 $\mu$ m, Wn = 0.6 $\mu$ m, PC Switch = 1.6 $\mu$ m /0.18 $\mu$ m.

### 2.3.5 Variation of the $k_r$ Ratio of the Sense Amplifier Transistors Keeping Wp Constant

**Objectives** – The  $k_r$  ratio of the transistors in the sense amplifier can be varied by varying the width of the NMOS transistors and keeping the width of the PMOS transistors constant. The NMOS transistor affects the dummy bit line. Therefore, when the width of the NMOS transistor (Wn) is increased, the dummy bit line recovery time should be reduced.

#### Experimental setup and parameters varied -

The DRAM – Value of Wn was varied, such that  $k_r$  was varied from 0.25 to 2.25 and all other parameters were kept constant as follows – Cbl = 100ff, Cc = 50ff, Pass Switch =  $0.3\mu m$  /0.2 $\mu m$ , Sense amplifier – Wp =  $2.5\mu m$ , Ln =  $0.18\mu m$ , Lp =  $0.18\mu m$ , PC Switch =  $1.62\mu m$  /0.18 $\mu m$ .

The SRAM – Value of Wn was varied, such that  $k_r$  was varied from 0.2 to 1 and all other parameters were kept constant as follows – Cbl = 100ff, Pass Switch = 0.3/0.2 $\mu$ m, Memory Cell – Ln = Lp = 0.18 $\mu$ m, Wn = 0.245 $\mu$ m, Wp = 0.2 $\mu$ m, Sense amplifier – Ln = Lp = 0.18 $\mu$ m, Wp = 2.5 $\mu$ m, PC Switch = 1.6 $\mu$ m /0.18 $\mu$ m.

#### 2.3.6 Memory Cell Parameters

One of the factors influencing the memory cycle time is the value of the memory cell capacitance. A small memory cell capacitance can be charged and discharged faster as compared to a large value of Cc. But, to detect the charge stored on a very small capacitance, a very sensitive sense amplifier is required. There seems to be a tradeoff between the memory cell capacitance and the sense amplifier size.

In case of DRAM, the memory cell capacitance is equal to value of Cc and in SRAM it is the parasitic capacitance of the left and right nodes of the flip-flop memory cell. This value of capacitance depends on the W/L ratio of the transistors and the  $k_{\rm r}$  value of the invertors in the memory cell.

**Objectives** – To observe the effect of varying memory cell capacitance on the performance goals. Referring to equation 2.1, it can be seen that Cc affects  $\Delta V$  and the recovery time.

#### Experimental setup and parameters varied -

The DRAM – Cc was varied from 10ff to 100ff and all other parameter values were kept constant as follows – Cbl = 100ff, Pass Switch = 0.3/0.2 $\mu$ m, Sense amplifier – Wn = 0.952 $\mu$ m, Ln = 0.18 $\mu$ m, Wp = 2 $\mu$ m, Lp = 0.18 $\mu$ m, k<sub>r</sub> = 0.476,

PC Switch =  $1.62\mu m/0.18\mu m$

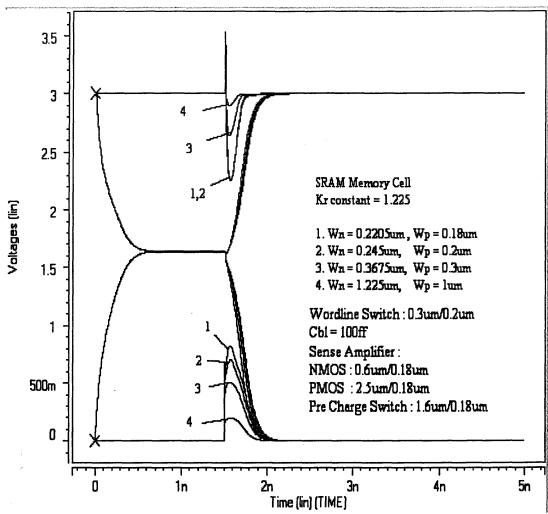

#### The SRAM -

- a)  $k_r$  of the memory cell was kept constant at 1.225 and W/L ratios of the transistors in the memory cell were varied. All other parameter values were kept constant as follows Cbl = 100ff, Pass Switch = 0.3/0.2 $\mu$ m, Sense amplifier Wn = 0.6 $\mu$ m, Ln = 0.18 $\mu$ m, Wp = 2.5 $\mu$ m, Lp = 0.18 $\mu$ m,  $k_r$  of Sense Amplifier = 0.476, PC Switch = 1.6 $\mu$ m /0.18 $\mu$ m.

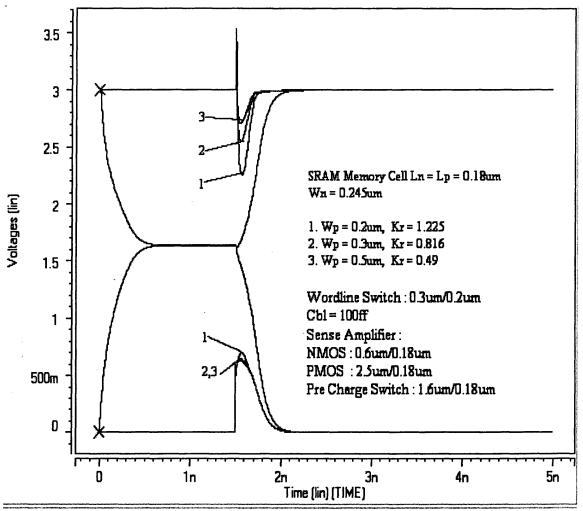

- b) The  $k_r$  of the memory cell was varied by varying the value of Wp and keeping Wn constant at 0.245 $\mu$ m. All other parameter values were kept constant as follows Cbl = 100ff, Pass Switch = 0.3/0.2 $\mu$ m, Sense amplifier Wn = 0.6 $\mu$ m, Ln = 0.18 $\mu$ m, Wp = 2.5 $\mu$ m, Lp = 0.18 $\mu$ m,  $k_r$  of Sense Amplifier = 0.476, PC Switch = 1.6 $\mu$ m /0.18 $\mu$ m.

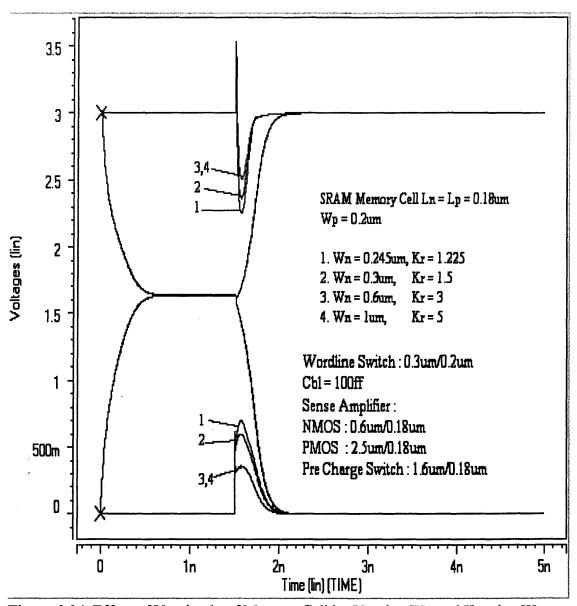

- c) The  $k_r$  of the memory cell was varied by varying the value of Wn and keeping Wp constant at  $0.2\mu m$ .

All other parameter values were kept constant as follows – Cbl = 100ff, Pass Switch =  $0.3/0.2\mu m$ , Sense amplifier – Wn =  $0.6\mu m$ , Ln =  $0.18\mu m$ , Wp =  $2.5\mu m$ , Lp =  $0.18\mu m$ ,  $k_r$  of Sense Amplifier = 0.476, PC Switch =  $1.6\mu m/0.18\mu m$ .

#### 2.3.7 Word Line Switch

The memory access transistor, being a non ideal switch, presents some resistance while turning on and off. It also possesses sub threshold leakage. This resistance, leakage current and the memory capacitance constitute towards the time required to charge and discharge the memory capacitor. To reduce the charging time, it is necessary to reduce the resistance by making the switch wider. At the same time, widening of the switch leads to an increase in memory cell area. There is again a tradeoff between the two. To reduce the sub threshold leakage, it is necessary to increase the threshold voltage of the switch.

Objectives – The width of the word line switch affects the current flowing through it. As width is increased, it should charge up the memory capacitance faster and the memory cycle time should reduce.

#### Experimental setup and parameters varied -

The DRAM – Width of the word line switch is varied from 0.2 $\mu$ m to 2 $\mu$ m and all other parameter values were kept constant as follows – Cbl = 100ff, Cc = 50ff, Pass Switch Length = 0.2 $\mu$ m, Sense amplifier – Wn = 0.952 $\mu$ m, Ln = 0.18 $\mu$ m, Wp = 2 $\mu$ m, Lp = 0.18 $\mu$ m,  $k_r$  = 0.476, PC Switch = 1.62 $\mu$ m /0.18 $\mu$ m.

The threshold voltage of the word line switch was varied from 0.1V to 0.7V and the leakage current and memory cycle time were noted.

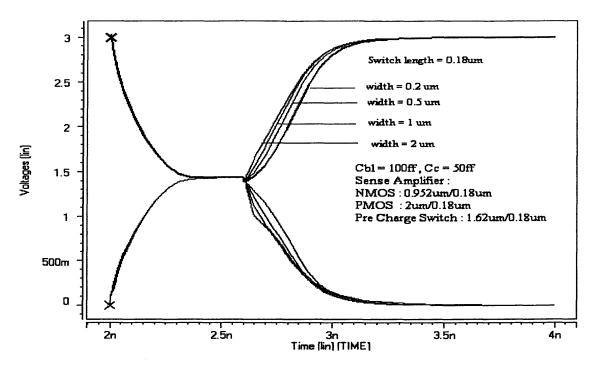

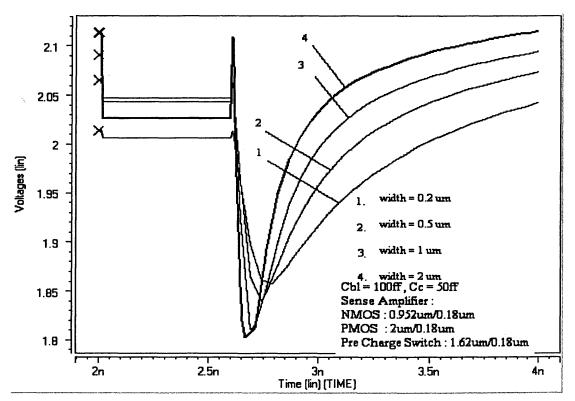

The SRAM – Width of the word line switch is varied from  $0.2\mu m$  to  $1\mu m$  and all other parameter values were kept constant as follows – Cbl = 100ff, Memory Cell – Ln = Lp =  $0.18\mu m$ , Wn =  $0.245\mu m$ , Wp =  $0.2\mu m$ , Pass Switch Length =  $0.2\mu m$ , Sense amplifier – Wn =  $0.6\mu m$ , Ln =  $0.18\mu m$ , Wp =  $2.5\mu m$ , Lp =  $0.18\mu m$ ,  $k_r$  = 0.24, PC Switch =  $1.6\mu m$  / $0.18\mu m$ .

#### 2.4 Three Dimensional Plots

The set of experiments in Section 2.3 described how each design variable affects the performance parameters. Once this relationship is known, desired performance goals can be obtained by adjusting the values of the design variables. Desired performance goals are minimum memory cycle time, minimum space occupied on chip and maximum size. The three performance goals are interrelated. For example to reduce memory cycle time, the area of the sense amplifier has to be increased, resulting in increase in chip area. The sets of experiments in this section have been designed to study this dependency, or in other words, the tradeoffs between the performance goals.

The concept of operating point has been used. An operating point has three coordinates. The X coordinate corresponds to a particular value of cycle time, Y coordinate corresponds to a particular value of chip space and Z coordinate corresponds to a particular value of memory size. The memory size has been specified in terms of the value of Cbl, due to the direct relation between memory size and Cbl. Experiment I deals with studying the tradeoffs using various operating points. In Experiment II, the value of one performance goal is held constant and the other two values are varied and their relation is studied.

#### 2.4.1 Experiment I – 3D Point Plots

Initially, five points are plotted as follows – Memory Cycle Time has been plotted on X axis, Chip Space (in terms of sense amplifier area and PC transistor area) is plotted on Y axis and Memory Size (in terms of Cbl) on Z axis.

- 2.4.1.1 Point 1. Point D1 (DX1, DY1, DZ1) was the operating point that was fundamental for all the DRAM experiments and Point S1 (SX1, SY1, SZ1) was the operating point that was fundamental for all the SRAM experiments

- 2.4.1.2 Point 2. Next, another Operating Point D2 (DX2, DY2, DZ2) was arrived at, such that this point had cycle time value lesser than that of Point D1. Similarly Point S2 (SX2, SY2, SZ2) was also designed.

- 2.4.1.3 Point 3. After this, Points D3 (DX3, DY3, DZ3) and S3 (SX3, SY3, SZ3) were plotted, which demonstrated the effect of increasing memory size. Cbl has been increased from an initial value of 100ff to 500ff. While arriving at these points, keeping cycle time minimum was the priority. Hence the tradeoff between cycle time and chip space was seen from this point

- 2.4.1.4 Point 4. Next, Points D4 (DX4, DY4, DZ4) and S4 (SX4, SY4, SZ4) were plotted by increasing memory size to 500ff. This experiment was similar to the one described in Section 2.3.1.3 except for the fact that priority was keeping chip space minimum by letting the increase in cycle time.

- 2.4.1.5 Point 5. Next, Points D5 (DX5, DY5, DZ5) and S5 (SX5, SY5, SZ5) were plotted by reducing chip space in comparison with Points D1 and S1 and observing the effect on other performance parameters.

#### 2.4.2 Experiment II – 3D Line Plots

In this experiment, 3D line graphs have been plotted. To plot a line graph, initially a performance parameter was held constant and various operating points were obtained. All the operating points were then connected by a line. This experiment is again divided into sub experiments described by the following sections.

While plotting the three dimensional line graphs, chip space refers to the area consumed on the chip by the entire memory array and all the sense amplifiers and pre charge switches.

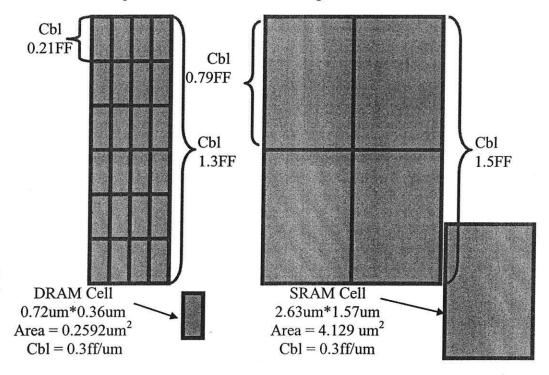

Procedure to calculate the total memory array area is as follows – The dimensions for the DRAM cell are given in literature as 4F \* 2F, for a folded bit line architecture, where "F" is the lithography feature size, which is 0.18um. This gives an area of  $8F^2$  = 0.2592 um<sup>2</sup>, for one memory cell. Considering the capacitance of the bit line to be 0.3ff/um, the total length of the bit line is known once the Cbl value is known. For example for Cbl = 100ff, Bit line length = 333um. The number of cells per bit line = 333 um/4F = 462. Considering an array of 462 \* 462 cells, the total memory array area would then be 55324.68 um<sup>2</sup> or 0.0553mm<sup>2</sup>. Similarly, the dimensions of an SRAM Cell are 2.63um \* 1.57um, giving a memory cell area of 4.129um<sup>2</sup>. Following similar calculations, number of cells for a 100ff bit line capacitance are 126 and total memory array area would then be 126 \* 126 \* 4.129um<sup>2</sup> = 0.0655 mm<sup>2</sup>. Also there exist as much number of sense amplifiers and pre charge switches as the number of cells placed along the word line (462 for DRAM and 129 for SRAM). Total sense amplifier and PC area can be calculated by multiplying the area of a single cell by the number of cells along the word line. In this way, total area or chip space can be calculated.

- 2.4.2.1 Sense Amplifier and Pre Charge Area Constant. In this experiment, the area of a single sense amplifier and the pre charge switch was kept constant at 1.35 um<sup>2</sup> (for DRAM) and 1.4 um<sup>2</sup> (for SRAM), and the memory size was increased from Cbl = 50FF to 1000FF. The tradeoff between cycle time and memory size was studied.

- 2.4.2.2 Memory Size (Cbl) Constant. In this experiment, memory size (Cbl) was held constant. Sense amplifier and pre charge switch area were varied and its effect on cycle time was observed. The tradeoff between chip space and cycle time can thus be studied.  $K_r$  of the invertors in the sense amplifier was kept constant at 0.476(DRAM) and 0.24(SRAM) for symmetry in bit lines recovery. Also PC width was varied in such a manner that the PC time was kept almost constant, in order to compare memory cycle recovery time. Word line switch = 0.3u/0.2u.

- 2.4.2.3 Memory Cycle Time Constant. In this experiment, the memory cycle time was kept constant at 2.1ns (DRAM) and 1.24ns (SRAM) and Cbl was increased. As Cbl was increased, the sense amplifier and pre charge area had to be increased to obtain the same memory cycle time.

# CHAPTER 3

## **EXPERIMENTAL RESULTS**

This chapter presents the variable values in terms of experimental data tables. Waveforms observed using AWAVES have been produced, and graphs have been plotted so that design issues can be studied.

## **3.1 DRAM**

The net list file shown in Figure 2.2, describing the DRAM Memory cell with the Sense amplifier and pre charge circuit was run using HSPICE. The waveforms observed are shown in Figure 3.1.

**Figure 3.1** HSPICE Waveforms for a DRAM Memory Cell and Dummy Memory Cell and Sense Amplifier Showing the Pre Charge Time, Bit Line, Dummy Bit Line, Memory Cell and Dummy Memory Cell Response.

From the waveforms in Figure 3.1, it can be seen that the memory system and sense amplifier are working as expected. The time to merge the bit lines was observed to be 0.42 ns. During calculating the recovery times for the bit lines and the memory cell, 0% to 99% of the swing of the waveform was considered. The recovery time observed for the memory cell to recover to its initial value was 1.68ns, dummy memory cell was 0.6ns, bit line was 0.58ns and dummy bit line was 0.61ns. Thus, the bit lines were observed to be symmetrically recovering. This is due to the adjustment in  $k_r$  value of the inverters in the sense amplifier to 0.476. At this  $k_r$  value speed of the NMOS comes out to be 2.1 times that of PMOS.

Total Memory Cycle Time = Time to merge Bit lines + Memory Cell Recovery Time

= 0.42 ns + 1.68 ns = 2.1 ns

#### **3.2 SRAM**

The net list used to describe the SRAM Cell, shown in Figure 2.5 of Chapter 2 was run using HSPICE. The waveforms observed are shown in Figure 3.2.

Figure 3.2 HSPICE Waveforms For an SRAM Memory Cell and Sense Amplifier Showing the Pre Charge Time, Bit Line, Dummy Bit Line and True and Complemented Data Response.

The time to merge the bit line and dummy bit line to the same voltage level of 1.64V was 0.66ns. The bit line recovery time was 0.51ns and dummy bit line recovery time was 0.52ns. Both recovery times were made almost the same by adjusting  $k_r$  value of the inverters in the sense amplifier to 0.24. Referring to Figure 3.2, it can be seen that the true data output recovers faster than the complemented data output. Recovery time of the true data output was 0.26ns and that of the complemented data output was 0.49ns. On conducting experiments, to reduce the complemented data output recovery time, it was found that Wn of the memory cell had to be increased a lot, which would result in an increase in chip space. Also, during considering the worst case recovery time, the dummy bit line recovery was slower than "0" memory cell. Hence, value of Wn was kept the same value.

Total Memory Cycle Time = Time to merge Bit lines + Worst Case Recovery Time

= 0.66 ns + 0.52 ns = 1.18ns

## 3.3 Basic Experiments

## 3.3.1 W/L Ratio of the Precharge Transistor

The experimental results when the width of the precharge switch was varied are shown below. The experimental data used such as the widths of the precharge transistor and the observations regarding timing have been recorded in Tables 3.1 and 3.2 below.

Table 3.1 Bit line and Memory Cell Times as a Function of Precharge transistor W/L Ratio for the DRAM

| Width of PC (µm) | W/L | Time to   | Bit line   | Dummy Bit  | memory cell | total      |

|------------------|-----|-----------|------------|------------|-------------|------------|

|                  | of  | merge     | recovery   | line       | recovery    | memory     |

|                  | PC  | bit lines | time (0 to | recovery   | time ( 0 to | cycle time |

|                  |     | (ns)      | 99 %) (ns) | time (0 to | 99 %)       | (ns)       |

|                  |     |           |            | 99 %)      | (ns)        |            |

| 0.9              | 5   | 1.35      | 0.59       | 0.62       | 1.7         | 3.05       |

| 1.08             | 6   | 0.82      | 0.57       | 0.62       | 1.69        | 2.51       |

| 1.26             | 7   | 0.63      | 0.59       | 0.62       | 1.69        | 2.32       |

| 1.44             | 8   | 0.55      | 0.58       | 0.61       | 1.69        | 2.24       |

| 1.62             | 9   | 0.42      | 0.58       | 0.61       | 1.68        | 2.1        |

| 1.8              | 10  | 0.39      | 0.6        | 0.61       | 1.75        | 2.14       |

| 1.98             | 11  | 0.36      | 0.6        | 0.61       | 1.75        | 2.11       |

Table 3.2 Bit line and Memory Cell Times as a Function of Precharge transistor W/L Ratio for the SRAM

| Wn (um) | W/L | Time to<br>merge<br>bit lines | Bit line<br>recovery<br>time (ns) | Dummy Bit line recovery | True Data Recovery | Complemented<br>Data Recovery<br>Time (ns) | total<br>memory<br>cycle<br>time |

|---------|-----|-------------------------------|-----------------------------------|-------------------------|--------------------|--------------------------------------------|----------------------------------|

|         |     | (ns)                          |                                   | time (ns)               | Time (ns)          |                                            | (ns)                             |

| 1.2     | 6   | 1.12                          | 0.51                              | 0.52                    | 0.35               | 0.58                                       | 1.7                              |

| 1.4     | 7   | 0.87                          | 0.51                              | 0.52                    | 0.35               | 0.58                                       | 1.45                             |

| 1.6     | 8   | 0.66                          | 0.51                              | 0.52                    | 0.35               | 0.58                                       | 1.24                             |

| 1.7     | 8.5 | 0.58                          | 0.51                              | 0.52                    | 0.35               | 0.58                                       | 1.16                             |

| 1.8     | 9   | 0.56                          | 0.51                              | 0.52                    | 0.35               | 0.58                                       | 1.14                             |

A number of iterations were done by varying the width of the precharge transistor and the results of all these are shown below for comparison purpose. The waveforms obtained for DRAM are shown in Figure 3.3, and those for SRAM are shown in Figure 3.4. Graphs using the experimental results, are shown in Figures 3.5 and 3.6.

Effect of varying Cbl/Cc ratio on bitlines and memory cell

Figure 3.3 Effect of Varying Width of Pre Charge Transistor in the DRAM on Bit lines and Memory Cell.

Figure 3.4 Effect of Varying Width of Pre Charge Transistor in the SRAM on Bit lines and Memory Cell True and Complemented Data Outputs

**Figure 3.5** Effect of varying W/L of Pre Charge Transistor for DRAM on PC Time, Bit Line Recovery Time, Dummy Bit Line Recovery Time, Memory Cell Recovery Time and Memory Cycle Time.

**Figure 3.6** Effect of varying W/L of Pre Charge Transistor for DRAM on PC Time, Bit Line Recovery Time, Dummy Bit Line Recovery Time, Memory Cell Recovery Time and Memory Cycle Time.

Referring to Figures 3.5 and 3.6, it can be seen that as the W/L ratio of the PC transistor was increased, the time required to merge the bit lines to their unstable operating point reduced, as expected. The bit line recovery time, bit line voltage level and memory cell recovery time remain unaffected. However, due to decrease in PC time, the overall memory cycle time is reduced. These observations are common for DRAM and SRAM. Also as PC transistor W/L ratio was increased, the precharge time and the memory cycle times were reduced exponentially to a value where they could not be reduced further. This is the optimum value for W/L of PC = 9 for DRAM, which corresponds to Wn=1.62μm. Similarly Wn=0.6μm was the value chosen for the SRAM PC width.

Thus, the PC switch directly affects the PC time and hence indirectly the memory cycle time. However increase in W/L leads to an increase in chip space. Hence, PC width affects two of the three performance goals – Memory Cycle time and Space consumed on Chip in a give and take manner.

## 3.3.2 Bit line length (Cbl Value)

The experimental results when the bit line length value (Cbl) was varied from 50ff to 1000ff are shown below. The data used and observations made are shown in Table 3.3.for DRAM and Table 3.4 for SRAM.

Table 3.3 Bit line and Memory Cell Behavior as a Function of Cbl/Cc Ratio for DRAM

| Cbl/Cc | Time  | Bit line | Dummy    | Memory | Memory  | memory   | total  | initial | ΔV  |

|--------|-------|----------|----------|--------|---------|----------|--------|---------|-----|

| 1      | to    | recovery | Bit line | Cell   | Cell    | cell     | memory | dip in  | (V) |

|        | merge | time     | recovery | Read   | Restore | recovery | cycle  | memor   |     |

|        | bit   | (ns)     | time     | time   | time    | time     | time   | y cell  |     |

|        | lines |          | (ns)     | (ns)   | (ns)    | (ns)     | (ns)   | voltag  |     |

|        | (ns)  |          |          |        |         |          |        | e (V)   |     |

| 1      | 0.25  | 0.32     | 0.41     | 0.3    | 0.92    | 1.22     | 1.47   | 0.1     | 0.3 |

|        |       |          |          |        |         |          |        |         | 55  |

| 2      | 0.42  | 0.59     | 0.61     | 0.3    | 1.4     | 1.7      | 2.12   | 0.17    | 0.2 |

|        |       |          |          |        |         |          |        |         | 36  |

| 3      | 0.58  | 0.86     | 0.82     | 0.4    | 1.52    | 1.92     | 2.5    | 0.25    | 0.1 |

|        |       |          |          |        |         |          |        |         | 78  |

| 4      | 0.78  | 1.14     | 1.04     | 0.4    | 1.72    | 2.12     | 2.9    | 0.31    | 0.1 |

|        |       |          |          |        |         |          |        |         | 42  |

| 5      | 0.9   | 1.39     | 1.26     | 0.4    | 1.92    | 2.32     | 3.22   | 0.37    | 0.1 |

|        |       |          |          |        |         |          |        |         | 18  |

| 6      | 1.1   | 1.66     | 1.5      | 0.5    | 1.91    | 2.41     | 3.51   | 0.41    | 0.1 |

|        |       |          |          |        |         |          |        |         | 01  |

| 10     | 1.76  | 2.81     | 2.49     | 0.6    | 2.39    | 2.99     | 4.75   | 0.53    | 0.0 |

|        |       |          |          |        |         |          |        |         | 64  |

| 20     | 3.3   | 5.9      | 5.2      | 8.0    | 3.9     | 4.7      | 8      | 0.63    | 0.0 |

|        |       |          |          |        |         |          |        |         | 35  |

Table 3.4 Bit line and Memory Cell Behavior as a Function of Cbl for SRAM

| Cbl (ff) | Time to<br>merge bit<br>lines (ns) | Bit line<br>recovery<br>time (ns) | Dummy Bit<br>line<br>recovery<br>time (ns) | True Data<br>Recovery<br>Time (ns) | Complemented<br>Data Recovery<br>Time (ns) | total<br>memory<br>cycle<br>time<br>(ns) |

|----------|------------------------------------|-----------------------------------|--------------------------------------------|------------------------------------|--------------------------------------------|------------------------------------------|

| F0       | 0.44                               | 0.00                              | 0.0                                        | 0.05                               | 0.22                                       | 0.74                                     |

| 50       | 0.41                               | 0.29                              | 0.3                                        | 0.25                               | 0.33                                       | 0.74                                     |

| 100      | 0.66                               | 0.51                              | 0.52                                       | 0.35                               | 0.58                                       | 1.24                                     |

| 250      | 1.5                                | 1.12                              | 1.19                                       | 0.54                               | 1.33                                       | 2.83                                     |

| 500      | 2.76                               | 2.29                              | 2.39                                       | 1.08                               | 2.65                                       | 5.41                                     |

| 1000     | 5                                  | 4.52                              | 4.75                                       | 2.07                               | 5                                          | 10                                       |

A number of iterations were done by varying the Cbl value and the results of all these are shown below for comparison purpose. The waveforms for DRAM are shown in Figure 3.7 and for SRAM are shown in Figures 3.8 and 3.9. Using the experimental results, graphs have been plotted in Figures 3.10, 3.11 and 3.12 for DRAM and Figure 3.13 for SRAM.

Effect of varying Cbl/Cc ratio on bitlines and memory cell

Figure 3.7 Effect of Varying Cbl/Cc Ratio in DRAM on Bit lines and Memory Cell, When Cc=50ff.

**Figure 3.8** Effect of Varying the Value of Cbl in SRAM on True and Complemented Data Outputs when all Parameters of the Memory Cell are Kept Constant.

Figure 3.9 Effect of Varying the Value of Cbl in SRAM on Bit line and Dummy Bit line when all Parameters of the Memory Cell are kept Constant.

When memory size in increased, the length of the bit line increases. This leads to an increase in the total bit line capacitance value (Cbl). The increased capacitance on the bit lines slows down their recovery. However, they still maintain the symmetry in recovery (as  $k_r$  value is kept constant). Also, it takes more time to precharge the bit lines to the same voltage level. This slowing down effect is due to the large capacitance that the precharge transistor has to face while merging the two bit lines to the same voltage level.

**Figure 3.10** Effect of varying Cbl/Cc by varying Cbl, for DRAM on PC Time, Bit Line Recovery Time, Dummy Bit Line Recovery Time, Memory Cell Read, Restore and Recovery Time and Memory Cycle Time.

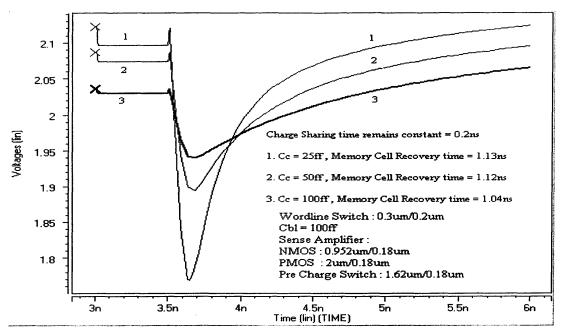

**Figure 3.11** Effect of varying Cbl value for SRAM on PC Time, Bit Line Recovery Time, Dummy Bit Line Recovery Time, True and Complemented Data Recovery Time and Memory Cycle Time.