# New Jersey Institute of Technology Digital Commons @ NJIT

# Dissertations

Theses and Dissertations

Fall 2007

# Architecture design and performance analysis of practical buffered-crossbar packet switches

Ziqian Dong New Jersey Institute of Technology

Follow this and additional works at: https://digitalcommons.njit.edu/dissertations Part of the <u>Electrical and Electronics Commons</u>

# **Recommended** Citation

Dong, Ziqian, "Architecture design and performance analysis of practical buffered-crossbar packet switches" (2007). *Dissertations*. 844. https://digitalcommons.njit.edu/dissertations/844

This Dissertation is brought to you for free and open access by the Theses and Dissertations at Digital Commons @ NJIT. It has been accepted for inclusion in Dissertations by an authorized administrator of Digital Commons @ NJIT. For more information, please contact digitalcommons@njit.edu.

# **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

#### ABSTRACT

# ARCHITECTURE DESIGN AND PERFORMANCE ANALYSIS OF PRACTICAL BUFFERED-CROSSBAR PACKET SWITCHES

# by Ziqian Dong

Combined input crosspoint buffered (CICB) packet switches were introduced to relax inputoutput arbitration timing and provide high throughput under admissible traffic. However, the amount of memory required in the crossbar of an  $N \times N$  switch is  $N^2 \times k \times L$ , where kis the crosspoint buffer size and needs to be of size RTT in cells, L is the packet size. RTTis the round-trip time which is defined by the distance between line cards and switch fabric. When the switch size is large or RTT is not negligible, the memory amount required makes the implementation costly or infeasible for buffered crossbar switches. To reduce the required memory amount, a family of shared memory combined-input crosspoint-buffered (SMCB) packet switches, where the crosspoint buffers are shared among inputs, are introduced in this thesis. One of the proposed switches uses a memory speedup of m and dynamic memory allocation, and the other switch avoids speedup by arbitrating the access of inputs to the crosspoint buffers. These two switches reduce the required memory of the buffered crossbar by 50% or more and achieve equivalent throughput under independent and identical traffic with uniform distributions when using random selections.

The proposed mSMCB switch is extended to support differentiated services and long RTT. To support P traffic classes with different priorities, CICB switches have been reported to use  $N^2 \times k \times L \times P$  amount of memory to avoid blocking of high priority cells. The proposed SMCB switch with support for differentiated services requires  $\frac{1}{mP}$  of the memory amount in the buffered crossbar and achieves similar throughput performance to that of a CICB switch with similar priority management, while using no speedup in the shared memory.

The throughput performance of SMCB switch with crosspoint buffers shared by inputs (I-SMCB) is studied under multicast traffic. An output-based shared-memory crosspointbuffered (O-SMCB) packet switch is proposed where the crosspoint buffers are shared by two outputs and use no speedup. The proposed O-SMCB switch provides high performance under admissible uniform and nonuniform multicast traffic models while using 50% of the memory used in CICB switches. Furthermore, the O-SMCB switch provides higher throughput than the I-SMCB switch.

As SMCB switches can efficiently support an RTT twice as long as that supported by CICB switches and as the performance of SMCB switches is bounded by a matching between inputs and crosspoint buffers, a new family of CICB switches with flexible access to crosspoint buffers are proposed to support longer RTTs than SMCB switches and to provide higher throughput under a wide variety of admissible traffic models. The CICB switches with flexible access allow an input to use any available crosspoint buffer at a given output. The proposed switches reduce the required crosspoint buffer size by a factor of N, keep the service of cells in sequence, and use no speedup. This new class of switches achieve higher throughput performance than CICB switches under a large variety of traffic models, while supporting long RTTs.

Crosspoint buffered switches that are implemented in single chips have limited scalability. To support a large number of ports in crosspoint buffered switches, memorymemory-memory (MMM) Clos-network switches are an alternative. The MMM switches that use minimum memory amount at the central module is studied. Although, this switch can provide a moderate throughput, MMM switch may serve cells out of sequence. As keeping cells in sequence in an MMM switch may require buffers be distributed per flow, an MMM with extended memory in the switch modules is studied. To solve the out of sequence problem in MMM switches, a queuing architecture is proposed for an MMM switch. The service of cells in sequence is analyzed.

# ARCHITECTURE DESIGN AND PERFORMANCE ANALYSIS OF PRACTICAL BUFFERED-CROSSBAR PACKET SWITCHES

by Ziqian Dong

A Dissertation Submitted to the Faculty of New Jersey Institute of Technology in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy in Electrical Engineering

**Department of Electrical and Computer Engineering**

January 2008

Copyright © 2008 by Ziqian Dong ALL RIGHTS RESERVED

# APPROVAL PAGE

# ARCHITECTURE DESIGN AND PERFORMANCE ANALYSIS OF PRACTICAL BUFFERED-CROSSBAR PACKET SWITCHES

# **Ziqian Dong**

| Dr. Roberto Rojas-Cessa, Dissertation Advisor                                     | Date |

|-----------------------------------------------------------------------------------|------|

| Associate Professor, Department of Electrical and Computer Engineering, New Jerse | У    |

| Institute of Technology                                                           |      |

Dr. Nirwan Ansari, Committee Member Date Professor, Department of Electrical and Computer Engineering, New Jersey Institute of Technology

Dr. Sotirios G. Ziavras, Committee Member Date Professor, Department of Electrical and Computer Engineering. New Jersey Institute of Technology

Dr. Jie Hu, Committee Member Date Assistant Professor. Department of Electrical and Computer Engineering, New Jersey Institute of Technology

Dr. Aleksandar Kolarov, Committee Member Senior Scientist, Applied Research, Telcordia Technologies

# **BIOGRAPHICAL SKETCH**

Author:Ziqian DongDegree:Doctor of PhilosophyDate:January 2008

# **Undergraduate and Graduate Education:**

- Doctor of Philosophy in Electrical Engineering, New Jersey Institute of Technology, Newark, NJ, 2008

- Master of Science in Electrical Engineering, New Jersey Institute of Technology, Newark, NJ 2002

- Bachelor of Science in Electrical Engineering, Beijing University of Aeronautics and Astronautics, Beijing, China, 1999

Major:Electrical Engineering

# **Publications:**

- Z. Dong and R. Rojas-Cessa, "Output-Based Shared-Memory Crosspoint-Buffered Packet Switch for Multicast Services," *to appear in IEEE Communications Letters, December* 2007.

- R. Rojas-Cessa, Z. Dong, and Z. Guo, "Load-Balanced Combined Input-Crosspoint Buffered Packet Switch and Long Round-Trip Times," *IEEE Communications Letters*, Vol. 4, issue 7, pp. 661 - 663, July 2005.

- Z. Dong and R. Rojas-Cessa, "Efficient Packet Replication and Switching of Multicast Traffic by Shared-Crosspoint Packet Switches," Proc. IASTED International Conference on Communication Systems, Networks, and Applications, CSNA 2007, October 8-10, 2007.

- R. Rojas-Cessa, L. Ramesh, Z. Dong, B. D'Alessandro and N. Ansari, "Implementation of A Parallel-Search Trie-Based Scheme for Fast IP Lookup," *Proc. IASTED International Conference on Communication Systems, Networks, and Applications, CSNA* 2007, October 8-10, 2007.

- R. Rojas-Cessa, L. Ramesh, Z. Dong, L. Cai and N. Ansari, "Parallel-Search Trie-based Scheme for Fast IP Lookup," *Proc. IEEE IEEE Global Telecommunications Conference,* Washington D.C., 6 pages, November 26 - 30, 2007.

- Z. Dong and R. Rojas-Cessa, "Packet Switching and Replication of Multicast Traffic by Crosspoint Buffered Packet Switches," *Proc. IEEE Workshop on High Performance Switching and Routing*, Brooklyn, NY, 6 pages, May 30 - Jun 1, 2007.

- Z. Dong and R. Rojas-Cessa, "Shared-Memory Combined Input-Crosspoint Buffered Packet Switch for Differentiated Services," *Proc. IEEE Global Telecommunications Conference*, San Francisco, CA, 5 pages, November 27 - December 1, 2006.

- R. Rojas-Cessa and Z. Dong, "Combined Input-Crossspoint Buffered Packet Switch with Flexible Access to Crosspoints Buffers: One-Cell Size Case," *Proc. 6th IEEE International Caribbean Conference on Devices, Circuits and Systems*, Playa del Carmen, Mexico, 5 pages, April 26 - 28, 2006.

- R. Rojas-Cessa, Z. Dong, and S. Ziavras, "Load-Balanced-CICB Packet Switch and Long Round-Trip Time Support," *Proc. of IEEE IEEE Global Telecommunications Conference*, St. Luis, MO, pp. 1002-1006, November 28 - December 2, 2005.

- Z. Dong and R. Rojas-Cessa, "Long Round-Trip Time Support with Shared-Memory Crosspoint Buffered Packet Switch," Proc. IEEE 13th Symposium on High Performance Interconnects, Palo Alto, CA, pp. 138-143, August 17 - 19, 2005.

- R. Rojas-Cessa and Z. Dong, "Combined Input-Crosspoint Buffered Packet Switch with Shared Crosspoint Buffers," Proc. the 39th Conference on Information Sciences and Systems, Baltimore, MD, March 16 - 18, 2005.

To my parents and my husband

#### ACKNOWLEDGMENT

I wish to express my sincere gratitude to my advisor, Dr. Roberto Rojas-Cessa, for giving me the opportunity to work with him and guiding me through this learning process. I am greatly indebted to my advisor for his inspiration and encouragement over the last five years. He is always open to new ideas and I really appreciate the support he gave me while working on my research. This research could not have been possible without his brilliant ideas. Not only was he readily available for me when I have questions, as he generously is for all his students, but also he carefully goes through the drafts of my work. Moreover, Dr. Rojas-Cessa also provided valuable facilities and brilliant guidelines for testing and evaluation of my dissertation. I owe much for his unending help to do the research and for his financial support during my graduate study.

I would also like to thank Dr. Nirwan Ansari, Dr. Sotirios Ziavras, Dr. Jie Hu, and Dr. Aleksandar Kolarov for serving on my committee, reviewing this dissertation and making constructive comments.

My thanks go out to my lab mates Chuan-bi Lin, Zhen Guo, Zhen Qin and Lin Cai who provided help and suggestions for my research. All my friends in and out of NJIT have been great source of support and fun. I thank them for making this journey productive and enjoyable.

I am grateful to the donors of the Hashimoto Fellowship and the National Science Foundation which provide financial support for my study.

I am forever indebted to the unconditional love and trust of my family. My parents and my brother have always been a source of inspiration, support, advice and happiness without which I would not have gone this far. Most importantly, I would like to thank my husband for his patience, love and support throughout the years.

| $\mathbf{C}$ | Chapter Pag |        |                                                                                   |   | ıge |

|--------------|-------------|--------|-----------------------------------------------------------------------------------|---|-----|

| 1            | INT         | RODU   | CTION                                                                             |   | 1   |

|              | 1.1         | Packe  | t Switches                                                                        |   | 1   |

|              |             | 1.1.1  | Output Buffered vs. Input Buffered Switches                                       |   | 3   |

|              |             | 1.1.2  | Combined-Input Crosspoint Buffered Packet Switches                                | • | 4   |

|              | 1.2         | Proble | em Statement                                                                      |   | 5   |

|              |             | 1.2.1  | Effect of Long Round Trip Times                                                   |   | 5   |

|              |             | 1.2.2  | Fast Memory in Switch Fabric                                                      | • | 7   |

| 2            | SH          | ARED I | MEMORY CROSSPOINT BUFFERED SWITCHES                                               | • | 8   |

|              | 2.1         | Introd | luction                                                                           | • | 8   |

|              | 2.2         | Share  | d Memory Combined Input Crosspoint Buffered Switches (SMCB)                       | • | 11  |

|              |             | 2.2.1  | Shared-Memory Crosspoint Buffered Switch with Speedup $m$ (SMCB $\times m$ )      |   | 12  |

|              |             | 2.2.2  | Shared-Memory Crosspoint Buffered Switch with Input-Crosspoin<br>Matching (mSMCB) |   | 13  |

|              | 2.3         | Perfor | rmance Analysis of the SMCB Switch with Random Selection                          |   | 16  |

|              |             | 2.3.1  | mSMCB Switch with $k_s = 1$                                                       |   | 17  |

|              |             | 2.3.2  | mSMCB Switch with $k_s = 2$                                                       | • | 19  |

|              |             | 2.3.3  | SMCB $\times m$ Switch with $k_s = 2$                                             | • | 20  |

|              |             | 2.3.4  | Maximum Throughput of the 2SMCB and SMCBx2 switches with<br>Random Selection      |   | 21  |

|              |             | 2.3.5  | Non Blocking Probability for Small Switch Sizes                                   | • | 23  |

|              | 2.4         | Simul  | ation of the SMCB Switch under Different Traffic Models                           | • | 24  |

|              |             | 2.4.1  | Performance of SMCB Switches with Round-Robin Selection                           | • | 25  |

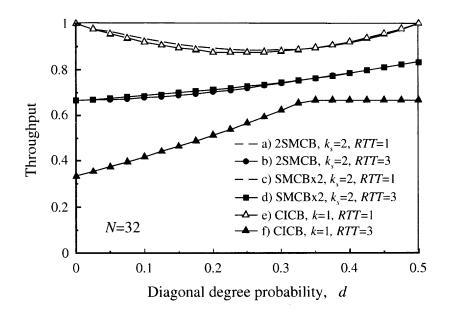

|              |             | 2.4.2  | Nonuniform traffic: Diagonal and PO2 Distributions                                | • | 29  |

|              |             | 2.4.3  | Performance of SMCB Switches with Longest-Queue-Occupanc<br>First (LQF) Selection | • | 31  |

| TABLE | OF   | CONTENTS |  |

|-------|------|----------|--|

| ((    | Cont | tinued)  |  |

| Chapter Page |     |                                                                                              |    |  |

|--------------|-----|----------------------------------------------------------------------------------------------|----|--|

|              |     | 2.4.4 Throughput under Long Round-Trip Times and Nonuniform Traffic                          | 35 |  |

|              | 2.5 | Implementation of an <i>m</i> SMCB Switch                                                    | 35 |  |

|              | 2.6 | Conclusions                                                                                  | 39 |  |

| 3            | DIF | FERENTIATED SERVICE SUPPORT BY SMCB SWITCHES                                                 | 42 |  |

|              | 3.1 | Introduction                                                                                 | 42 |  |

|              | 3.2 | CICB Switch with Dedicated Crosspoint Buffers for Differentiated Services                    | 44 |  |

|              | 3.3 | Shared-Memory Crosspoint Buffered Switch (SMCB)                                              | 45 |  |

|              |     | 3.3.1 Model Description                                                                      | 45 |  |

|              |     | 3.3.2 Crosspoint-Buffer Blocking Probability with Differentiated Traffic                     | 48 |  |

|              | 3.4 | Performance Evaluation of the SMCB Switch under Differentiated Traffic                       | 49 |  |

|              |     | 3.4.1 Uniform traffic                                                                        | 49 |  |

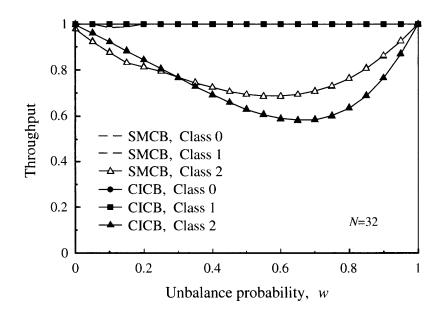

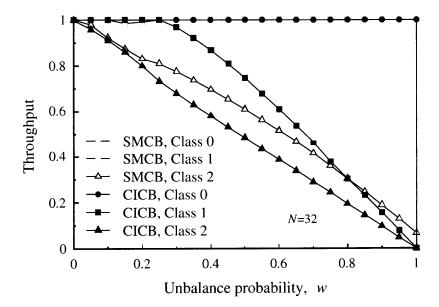

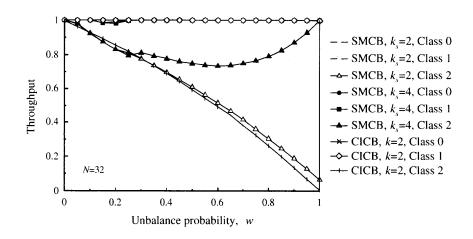

|              |     | 3.4.2 Unbalanced traffic                                                                     | 50 |  |

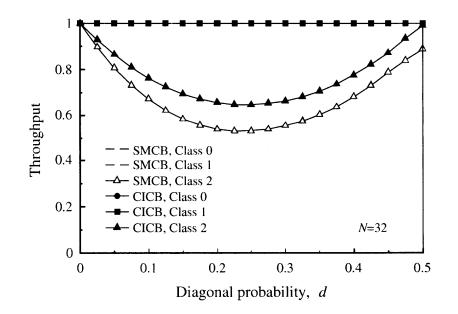

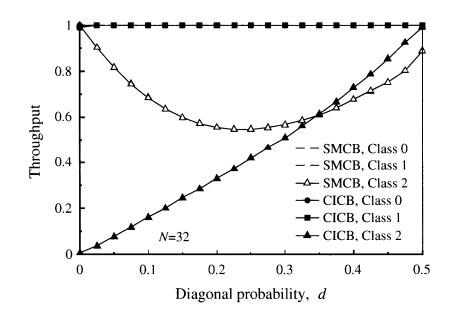

|              |     | 3.4.3 Diagonal traffic                                                                       | 53 |  |

|              | 3.5 | Conclusions                                                                                  | 54 |  |

| 4            |     | CKET SWITCHING AND REPLICATION OF MULTICAST TRAFFIC BY<br>ROSSPOINT BUFFERED PACKET SWITCHES | 57 |  |

|              | 4.1 | Introduction                                                                                 | 57 |  |

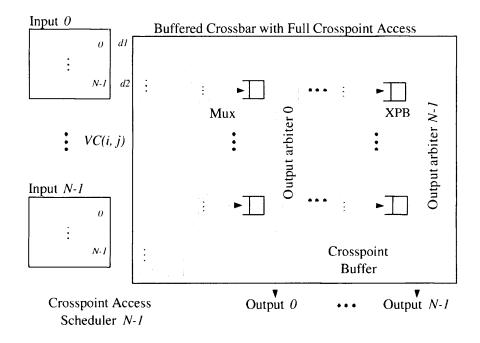

|              | 4.2 | Combined Input-Crosspoint Buffer Switch                                                      | 60 |  |

|              | 4.3 | Shared-Memory Crosspoint Buffered (SMCB) Switch                                              | 62 |  |

|              | 4.4 | Arbitration Schemes for the CICB Switch                                                      | 62 |  |

|              | 4.5 | Arbitration Schemes for the SMCB Switch                                                      | 64 |  |

|              |     | 4.5.1 Input Arbitration Scheme                                                               | 64 |  |

|              |     | 4.5.2 Output Arbitration Schemes                                                             | 65 |  |

|              | 4.6 | Performance Evaluation                                                                       | 65 |  |

|              | 4.7 | Output-based Shared-Memory Crosspoint Buffered (O-SMCB) Switch                               | 68 |  |

|              | 4.8 | O-SMCB Performance Evaluation                                                                | 69 |  |

| $\mathbf{C}$ | hapt | er     |                                                                                                    | Page     |

|--------------|------|--------|----------------------------------------------------------------------------------------------------|----------|

|              | 4.9  | Concl  | usions                                                                                             | 73       |

| 5            | LO   | AD-BA  | LANCED CICB SWITCH                                                                                 | 78       |

|              | 5.1  | Introd | luction                                                                                            | 78       |

|              | 5.2  | Throu  | ghput Degradation in CICB Switches with Rigid Access                                               | 78       |

|              | 5.3  | Load-  | Balanced Combined-Input Crosspoint Buffered Switches                                               | 79       |

|              |      | 5.3.1  | Load-Balanced CICB Full Access (CICB-FA) to Crosspoint Buffers                                     | 5 79     |

|              |      | 5.3.2  | Load-Balanced CICB Switch with Single Access (CICB-SA) to Cros<br>point Buffers                    | s-<br>81 |

|              | 5.4  | In-Sec | quence Cell Service with FCFS Output Arbitration                                                   | 82       |

|              | 5.5  |        | ghput Analysis under Admissible Independent Identical Distributed ffic and Random Selection Scheme | 85       |

|              |      | 5.5.1  | CICB Switch                                                                                        | 86       |

|              |      | 5.5.2  | Load Balanced CICB Switch                                                                          | 87       |

|              | 5.6  | Perfor | mance Analysis                                                                                     | 90       |

|              |      | 5.6.1  | Uniform Traffic                                                                                    | 90       |

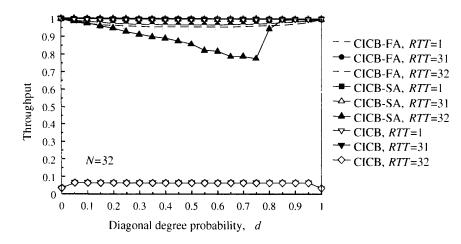

|              |      | 5.6.2  | Nonuniform Traffic: Unbalanced                                                                     | 91       |

|              |      | 5.6.3  | Nonuniform Traffic: Power of Two                                                                   | 93       |

|              |      | 5.6.4  | Nonuniform Traffic: Diagonal                                                                       | 94       |

|              | 5.7  | Concl  | usions                                                                                             | 95       |

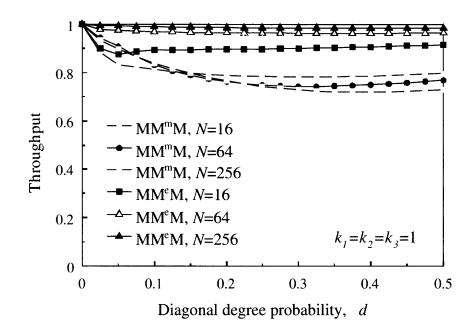

| 6            | ME   | MORY   | -MEMORY-MEMORY CLOS-NETWORK SWITCH                                                                 | 96       |

|              | 6.1  | Introd | uction                                                                                             | 96       |

|              | 6.2  |        | bry-Memory-Memory Clos-Network Switch with Minimum Memory hount at CM ( $MM^mM$ )                  | 97       |

|              | 6.3  |        | bry-Memory-Memory Clos-Network Switch with Extended Memory CMs (MM <sup>e</sup> M)                 | 100      |

|              | 6.4  | Perfor | mance Analysis                                                                                     | 102      |

|              |      | 6.4.1  | Uniform Traffic                                                                                    | 102      |

# TABLE OF CONTENTS (Continued)

# TABLE OF CONTENTS (Continued)

| Chapter P                                                     | age |

|---------------------------------------------------------------|-----|

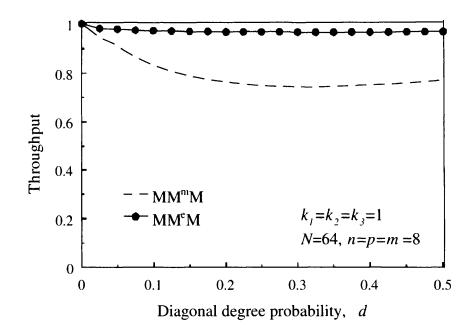

| 6.4.2 Nonuniform Traffic                                      | 104 |

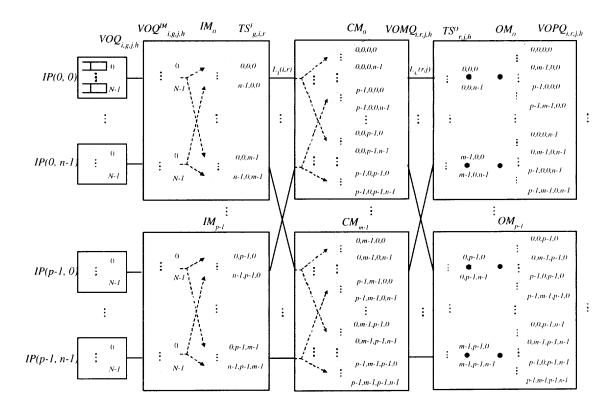

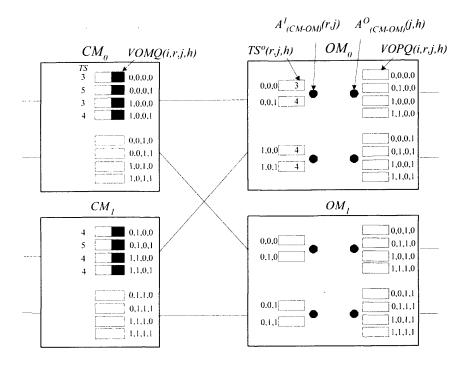

| 6.5 MMM Clos-network Switch with Service of Cells in Sequence | 106 |

| 6.5.1 Providing Service of Cells in Sequence with MCS         | 113 |

| 6.6 Conclusions                                               | 117 |

| 7 CONCLUSIONS                                                 | 118 |

| REFERENCES                                                    | 121 |

# LIST OF TABLES

| Table |                                                                                                          | Page |  |

|-------|----------------------------------------------------------------------------------------------------------|------|--|

| 2.1   | Threshold Setup of SMCB $\times m$ Switch $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 14   |  |

| 4.1   | Throughput under Multicast Traffic                                                                       | 73   |  |

# LIST OF FIGURES

| Figu | Figure                                                                                                                             |    |  |

|------|------------------------------------------------------------------------------------------------------------------------------------|----|--|

| 1.1  | An $N \times N$ crossbar switch                                                                                                    | 2  |  |

| 1.2  | An $N \times N$ buffered crossbar switch.                                                                                          | 3  |  |

| 1.3  | Output buffered (a) and Input buffered (b) switch.                                                                                 | 4  |  |

| 1.4  | Combined input crosspoint buffered switch architecture.                                                                            | 5  |  |

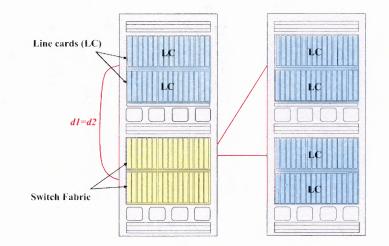

| 1.5  | Multi-Rack Packet Switch.                                                                                                          | 6  |  |

| 2.1  | Throughput performance of a CICB switch [1] with $RTT > 0$                                                                         | 10 |  |

| 2.2  | $N \times N$ shared-memory buffered crossbar switch with speedup $m$                                                               | 13 |  |

| 2.3  | $N \times N$ Shared-memory buffered crossbar switch                                                                                | 15 |  |

| 2.4  | Bipartite matching in an input-access scheduler between inputs and SMBs.                                                           | 15 |  |

| 2.5  | Example of the matching process in a $4 \times 4$ switch                                                                           | 16 |  |

| 2.6  | Diagram of the Markov chain of a buffer of size $k_s$                                                                              | 18 |  |

| 2.7  | Diagram of the Markov chain of a buffer of size $k_s = 1$                                                                          | 19 |  |

| 2.8  | Diagram of the Markov chain of a buffer of size $k_s = 2$                                                                          | 20 |  |

| 2.9  | Calculated throughput of a VOQ under uniform traffic, $\rho = 1$ , $k_s = 1$ for mSMCB switch, $k_s = 2$ for SMCB×2 switch         | 24 |  |

| 2.10 | Calculated throughput of a VOQ under uniform traffic, $\rho = 1$ , $k_s = 2$ for mSMCB and SMCB×2 switch.                          | 25 |  |

| 2.11 | Average cell delay of $32 \times 32$ CICB, SMCB $\times 2$ , and 2SMCB switches with round-robin selection, under uniform traffic. | 26 |  |

| 2.12 | Throughput of SMCB×2 and 2SMCB switches with round-robin selection and the same amount of memory.                                  | 27 |  |

| 2.13 | Throughput of a 2SMCB switch with half $(k_s = 1)$ and equal $(k_s = 2)$ amount of memory to the CICB switch.                      | 28 |  |

| 2.14 | Throughput of the $32 \times 32$ mSMCB with m inputs sharing the buffered cross-<br>point.                                         | 29 |  |

| 2.15 | Throughput of $32 \times 32$ 2SMCB, SMCB×2, and CICB switches with round-robin selection, under diagonal traffic.                  | 30 |  |

# LIST OF FIGURES (Continued)

| Figu | re Pa                                                                                                                                                                                        | ıge |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.16 | Average cell delay of $32 \times 32$ 2SMCB, 2SMCB and CICB switches with LQF selection, under uniform traffic.                                                                               | 32  |

| 2.17 | Throughput of $32 \times 32$ 2SMCB, SMCB×2, and CICB switches with LQF selection, under unbalanced traffic.                                                                                  | 34  |

| 2.18 | Throughput of $32 \times 32$ 2SMCB, SMCB $\times 2$ , and CICB switches with LQF selection, under diagonal traffic.                                                                          | 34  |

| 2.19 | Throughput of $32 \times 32$ 2SMCB, SMCB×2, and CICB switches with LQF selection, under diagonal traffic when $d = 0.25$ and $RTT = 7$                                                       | 36  |

| 2.20 | Throughput of $30 \times 30$ 2SMCB, SMCB×2, and CICB switches with LQF selection, under PO2 traffic and $RTT = 7$ .                                                                          | 36  |

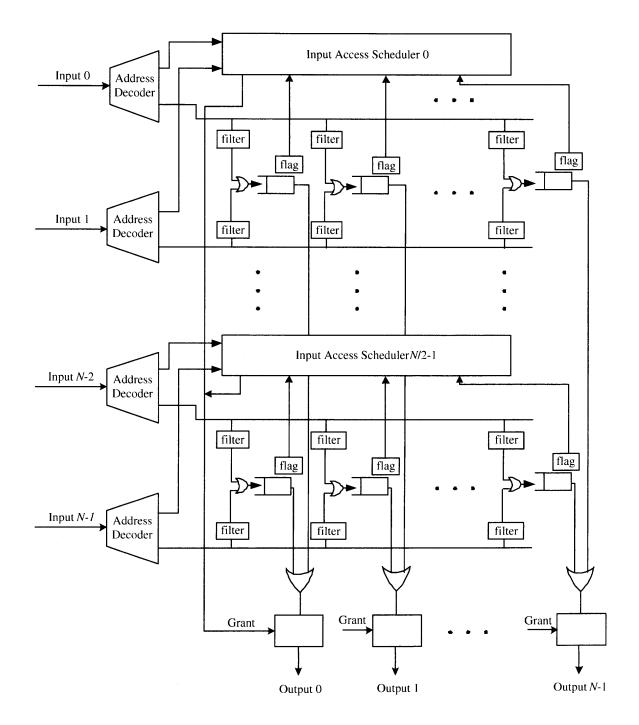

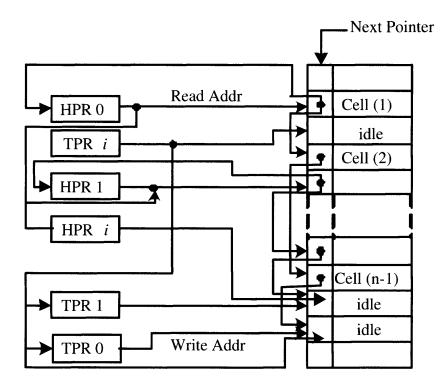

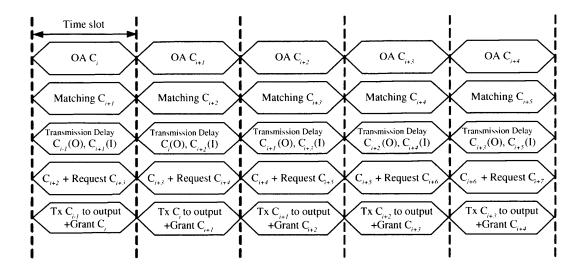

| 2.21 | Implementation of the <i>m</i> SMCB Switch.                                                                                                                                                  | 38  |

| 2.22 | Logical-queue implementation of shared memory buffers of the $m$ SMCB switch.                                                                                                                | 39  |

| 2.23 | Timing diagram of the <i>m</i> SMCB switch's operation.                                                                                                                                      | 40  |

| 3.1  | CICB switch with dedicated crosspoint buffers and round-robin input and out-<br>put arbitrations.                                                                                            | 45  |

| 3.2  | $N \times N$ buffered crossbar with shared crosspoints                                                                                                                                       | 47  |

| 3.3  | State Diagram of a shared memory crosspoint buffer of an $N \times N$ SMCB switch that supports two classes of traffic and $k_s = 2$ .                                                       | 48  |

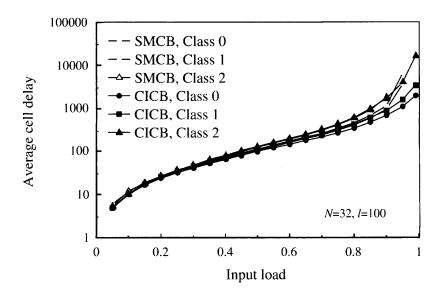

| 3.4  | Average queuing delay of $32 \times 32$ SMCB and CICB switches when $l = 1$ , $k_s = k = 1$ , and $RTT = 1$ .                                                                                | 50  |

| 3.5  | Average queuing delay of $32 \times 32$ SMCB and CICB switches when $l = 100$ , $k_s = k = 1$ , and $RTT = 1$ .                                                                              | 51  |

| 3.6  | Throughput of $32 \times 32$ SMCB and CICB switches when $k_s = k = RTT = 1$                                                                                                                 | 52  |

| 3.7  | Throughput of $32 \times 32$ SMCB and CICB switches when $k_s = k = 1$ , and $RTT=3$ .                                                                                                       | 52  |

| 3.8  | Throughput of $32 \times 32$ SMCB and CICB switches when SMCB switch has half $(k_s = k = 2)$ , the same amount of memory as CICB switch $(k_s = \frac{1}{2}$ and $k = 4$ ), and $RTT = 3$ . | 53  |

| 3.9  | Throughput of $32 \times 32$ switches when the SMCB switch has half the amount of memory of that in the CICB switch ( $k_s = k = 1$ ), and $RTT = 1$                                         | 54  |

# LIST OF FIGURES (Continued)

| Figu | re P                                                                                                                                   | age |

|------|----------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.10 | Throughput of $32 \times 32$ SMCB and CICB switches when they have the same amount of memory ( $k_s = 4$ and $k = 2$ ) and $RTT = 3$ . | 55  |

| 4.1  | Multicast CICB switch with dedicated CPBs.                                                                                             | 61  |

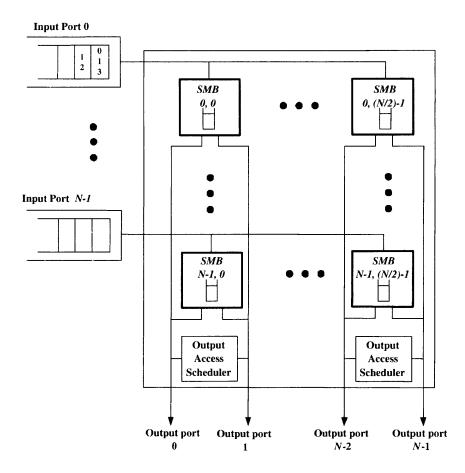

| 4.2  | $N \times N m$ SMCB switch, $m = 2$                                                                                                    | 63  |

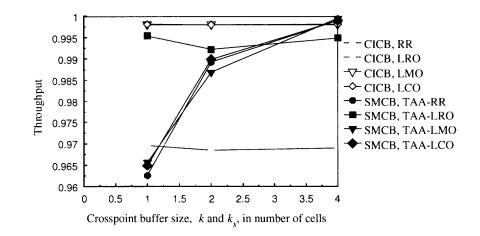

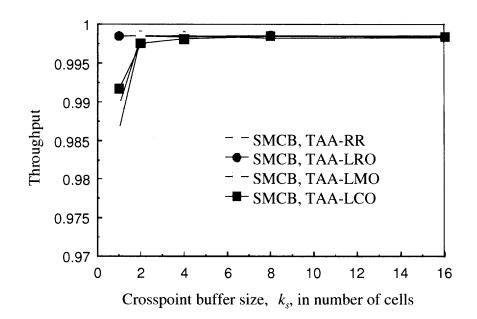

| 4.3  | Throughput of $8 \times 8$ switches using different crospoint-buffer sizes                                                             | 66  |

| 4.4  | Throughput of $16 \times 16$ switches using different crospoint-buffer sizes                                                           | 67  |

| 4.5  | Throughput of $32 \times 32$ switches using different crospoint-buffer sizes                                                           | 68  |

| 4.6  | $N \times N$ O-SMCB switch with shared-memory crosspoints by outputs                                                                   | 70  |

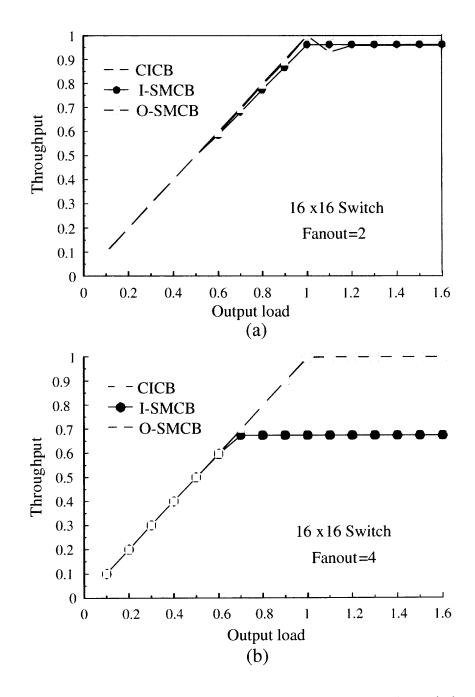

| 4.7  | Throughput performance of $16 \times 16$ I-SMCB and O-SMCB switches under a) diagonal2 traffic and b) diagonal4 traffic.               | 74  |

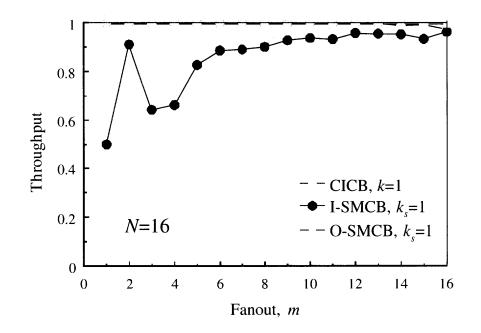

| 4.8  | Throughput performance of $16 \times 16$ I-SMCB and O-SMCB switches under diagonal traffic with different Fanout values.               | 75  |

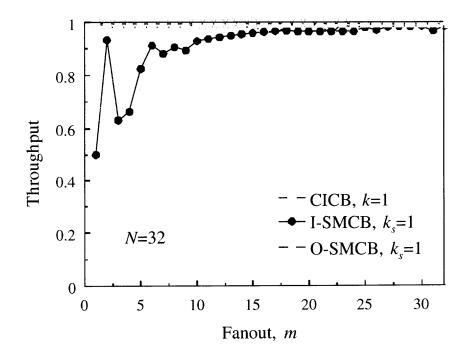

| 4.9  | Throughput performance of $32 \times 32$ I-SMCB and O-SMCB switches under diagonal traffic with different Fanout values.               | 75  |

| 5.1  | $N \times N$ CICB switch with full access (CICB-FA).                                                                                   | 80  |

| 5.2  | $N \times N$ CICB switch with single access (CICB-SA)                                                                                  | 81  |

| 5.3  | Example of cell placement described in Lemma 2                                                                                         | 85  |

| 5.4  | M/M/N queuing model of load balanced CICB switch                                                                                       | 88  |

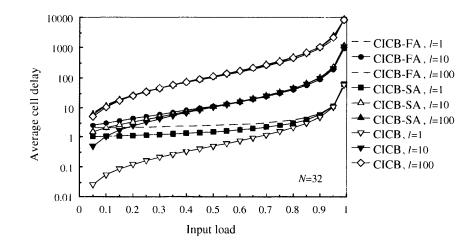

| 5.5  | Average queuing delay of a $32 \times 32$ CICB switches under uniform traffic.                                                         | 91  |

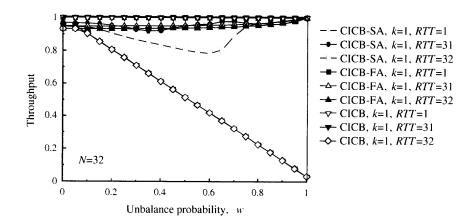

| 5.6  | Throughput of CICB switches with $k=1$ and $RTT = \{1, 31, 32\}$ under unbalanced traffic.                                             | 92  |

| 5.7  | Throughput of the $32 \times 32$ CICB-FA switch with $k=1$ under unbalanced traffic.                                                   | 92  |

| 5.8  | Throughput of the $32 \times 32$ CICB-SA switch with $k=1$ under unbalanced traffic.                                                   | 93  |

| 5.9  | Performance of $30 \times 30$ switches with $k = 1$ under PO2 traffic.                                                                 | 94  |

| 5.10 | Throughput of the $32 \times 32$ switches with $k = 1$ under diagonal traffic                                                          | 94  |

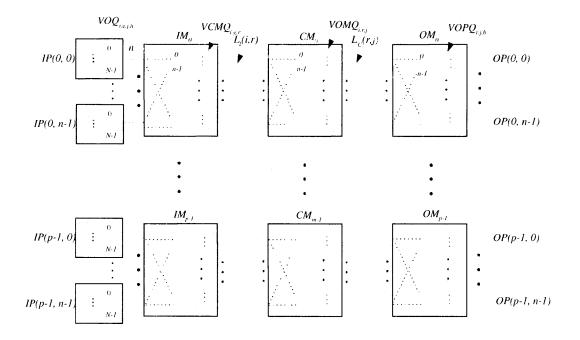

| 6.1  | $N \times N$ MM <sup>m</sup> M Clos-network packet switch                                                                              | 98  |

| 6.2  | $N \times N$ MM <sup>e</sup> M Clos-network packet switch                                                                              | 101 |

# LIST OF FIGURES (Continued)

| Figu | re P                                                                                                                             | age |

|------|----------------------------------------------------------------------------------------------------------------------------------|-----|

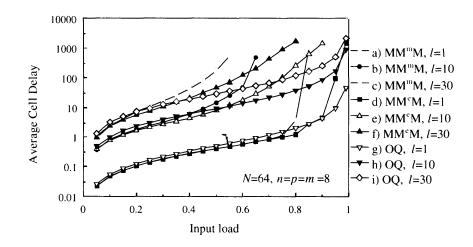

| 6.3  | Average cell delay of $64 \times 64$ MM <sup>m</sup> M, MM <sup>e</sup> M, and OQ switches                                       | 102 |

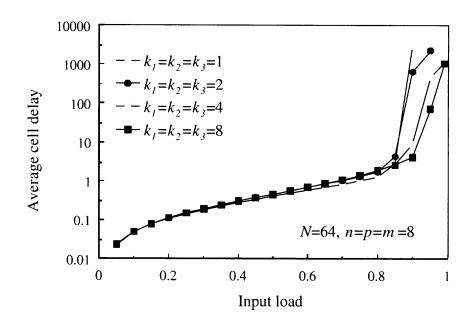

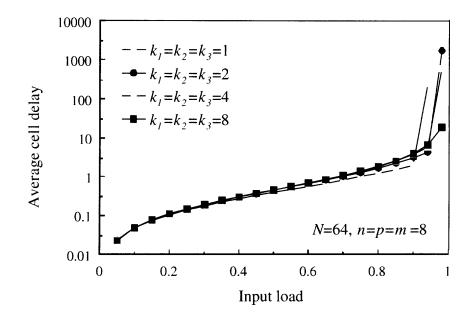

| 6.4  | Average cell delay of $64 \times 64$ MM <sup>m</sup> M switch under uniform traffic with dif-<br>ferent crosspoint buffer sizes. | 103 |

| 6.5  | Average cell delay of $64 \times 64$ MM <sup>e</sup> M switch under uniform traffic with different crosspoint buffer sizes.      | 103 |

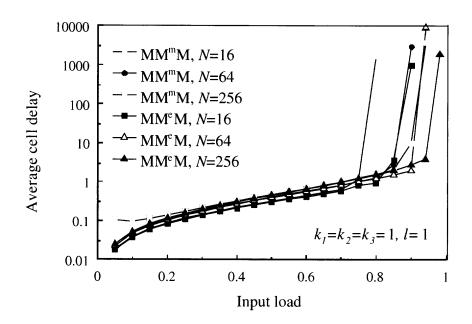

| 6.6  | Average cell delay of $MM^mM$ and $MM^eM$ switches under uniform traffic with different switch sizes.                            | 104 |

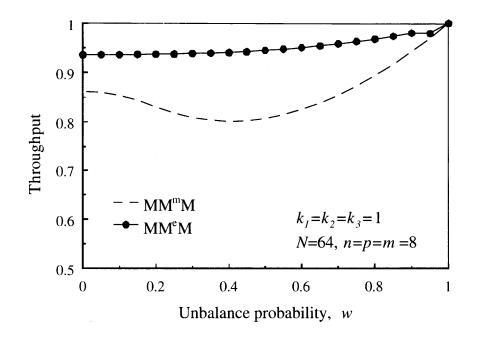

| 6.7  | Throughput of $64 \times 64 \text{ MM}^m \text{M}$ and $\text{MM}^e \text{M}$ switches under unbalanced traffic.                 | 105 |

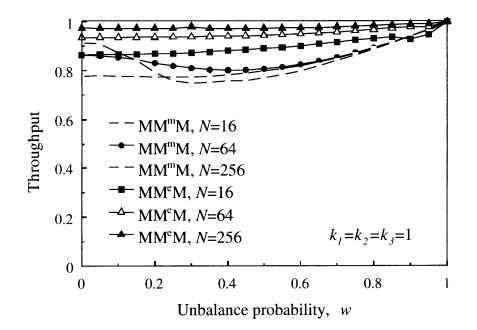

| 6.8  | Throughput of $MM^mM$ and $MM^eM$ switches under unbalanced traffic with different switch sizes.                                 | 105 |

| 6.9  | Throughput of $64 \times 64 \text{ MM}^m \text{M}$ and $\text{MM}^e \text{M}$ switches under diagonal traffic.                   | 106 |

| 6.10 | Throughput of $MM^mM$ and $MM^eM$ switches under diagonal traffic with different switch sizes.                                   | 107 |

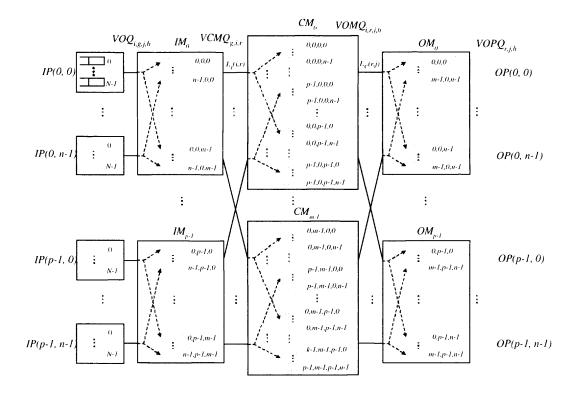

| 6.11 | An $N \times N$ packet switch that serves cell in sequence, or MCS                                                               | 107 |

| 6.12 | Example of matching between CM and OM of a $4 \times 4$ MCS                                                                      | 111 |

| 6.13 | Example of matching process at OM.                                                                                               | 112 |

## **CHAPTER 1**

# **INTRODUCTION**

#### **1.1 Packet Switches**

The exponential growth of Internet traffic requires high speed packet switches and routers to perform switching at higher speed, low latency and to support traffic with multiple priorities. Packet switches are found at the backbone and gateway levels of a network where one network connects with another as well as at the subnetwork level, where data is forwarded in a direction close to its destination. Packet switches operate at layer two of the Open System Interconnection (OSI) model. Those switches that operate at both layer two and three are referred to as routers [2]. Packet switches determine the output port a packet is to be forwarded based on the information from the destination IP address in the packet header and its own routing table. In this dissertation, packets conform with the Internet Protocol (IP).

A packet switch consists of input/output line interface cards (LICs), which perform processes on incoming IP packets, such as segmentation, IP lookup, scheduling, and of a switch fabric which is responsible for transferring fixed-length cells from inputs to outputs [3]. An IP packet is processed in the input line cards and then forwarded to its destination port as retrieved by IP lookup in the LIC through the switch fabric. To synchronize the internal operation within the switch core, incoming variable-size IP packets are segmented into fixed-length packets, called cells, at the ingress side of a switch and re-assembled at the egress side, before the packets depart from the switch. In this dissertation, the use of cells is considered. Time slot is defined as the time it takes for a switch to transfer a cell from an input to an output.

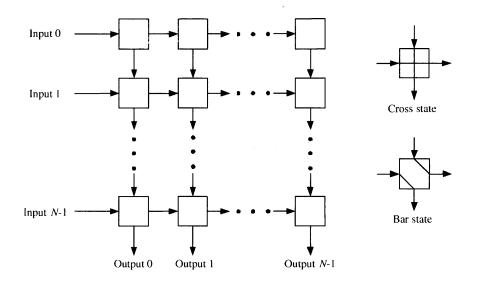

Figure 1.1 An  $N \times N$  crossbar switch.

Different designs of switch fabrics were introduced in [4] [5]. In general, the design of a switch fabric can be summarized into two categories: single-stage switch fabric and multiple-stage switch fabric.

For single-stage switch fabrics as in [6]-[7], there is one path available for a cell to go through from an input to an output. A typical implementation of single-stage switch is the bufferless and buffered crossbar switch. In an  $N \times N$  bufferless crossbar switch, as shown in Figure 1.1, there are  $N^2$  crosspoints, each of which represents an input-output pair. Each crosspoint has two states, cross state and bar state. The connection of input *i* to output *j* is established when crosspoint from *i* to *j* is at bar state. There is no connection between input *i* and output *j* when crosspoint from *i* to *j* is set at cross state. A bufferless crossbar switch has the advantage of implementation simplicity and of being internally nonblocking. However, the scheduling process at the inputs of selecting which output to send a cell has to be done in a very limited time otherwise it becomes a bottleneck of the system when the switch size, N, is large. Buffered crossbar switches, as shown in Figure 1.2, employ buffers at the crosspoints to store internally blocked cells to reduce loss rate [8].

For multiple-stage switch fabrics, there are multiple paths available for a cell to traverse to its destination. Banyan switches [9], multiplane switches [10], and Clos switches

Figure 1.2 An  $N \times N$  buffered crossbar switch.

[11] are examples of multiple-stage switch fabrics. These switches have the advantage of being scalable, but have the problem of blocking by internal contentions. To avoid this blocking condition, the switches need centralized scheduling process to resolve contention, which can result in a complicated implementation since different modules can be located on different chips and boards.

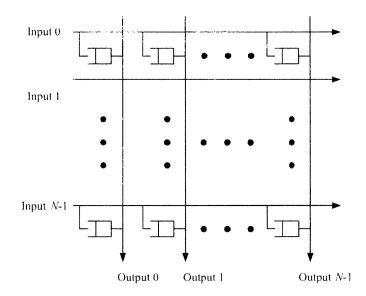

#### 1.1.1 Output Buffered vs. Input Buffered Switches

Single staged packet switches can be categorized as output buffered (OB) switches, iutput buffered (IB) switches and crosspoint buffered switches based on the buffering strategies [12].

Output buffered (OB) switches, as shown in Figure 1.3 (a), employ buffers at the output ports. OB switches can achieve 100% throughput since cells from the inputs will not be blocked by the head-of-line (HOL) cells. However, output buffers need to store N cells in each time slot for an  $N \times N$  switch. The memory needs to run N times faster than the line rate (speedup of N) for dual access memory. In practical backbone packet switches, port speed can be tens Gbits/s. Memory speedup in OB switches makes implementation infeasible when switch size is large because the speed of memory limits the switch size.

Figure 1.3 Output buffered (a) and Input buffered (b) switch.

IB switches, as shown in Figure 1.3 (b), employ first-in first-out (FIFO) buffers at the inputs. To resolve output contention, IB switches need a scheduler to arbitrate cells from different inputs to each output [13] [14] [15]. Scheduling schemes used by the scheduler can be categorized as weighted and weightless scheduling schemes [16][17]. Random selection and round-robin selection are examples of weightless scheduling schemes. Longest queue first (LQF), oldest cell first (OCF) are examples of weighted scheduling schemes. IB switches are easy to implement and scalable. However, IB switches suffer from HOL blocking where cells are prevented from reaching a free output port because of other cells are ahead of it in the buffer and those cannot be transmitted over the switch fabric due to contention. HOL blocking limits the throughput of the IB switch to 58.6% under uniform traffic [18]. The throughput of an IB switch also depends on the scheduling schemes used. Virtual output queues (VOQs) are implemented to resolve the problem of HOL blocking, where *N* virtual output queues are used to store cells destined to different outputs at each input. For a crossbar switch with VOQs at the inputs, the throughput can reach 100% using maximum matching algorithms [19] [20].

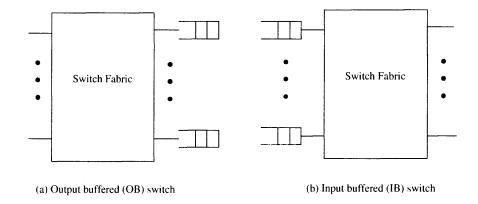

#### 1.1.2 Combined-Input Crosspoint Buffered Packet Switches

Combined input-crosspoint buffered (CICB) switches are an alternative to input-buffered switches to relax arbitration timing and to provide high-performance switching for packet

Figure 1.4 Combined input crosspoint buffered switch architecture.

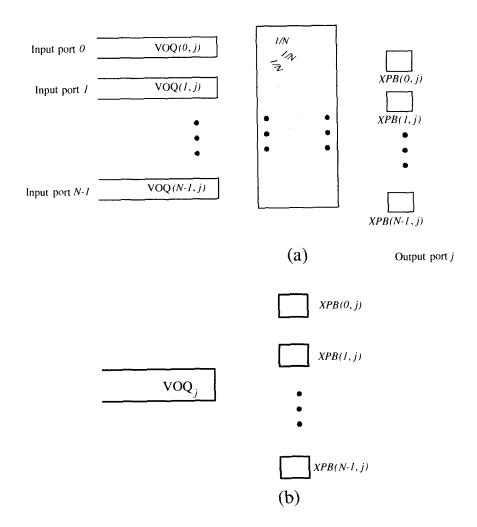

switches with high-speed ports [1] [21] [22] [23]. These packet switches use time efficiently as input and output port arbitrations are performed independently [8]-[14]. Figure 1.4 shows the architecture of a CICB switch. For an  $N \times N$  CICB switch, there are N VOQs at each input. Each VOQ stores cells for one of the N outputs. There are  $N^2$  buffered crosspoints, each of which stores cells from input *i* to output *j*, where  $0 \le i, j \le N - 1$ . A credit-based flow control mechanism is used to indicate the inputs of the crosspoint buffer availability. Different scheduling schemes were proposed in [6] [24] [25] to improve the performance under non-uniform traffic.

#### **1.2** Problem Statement

#### **1.2.1** Effect of Long Round Trip Times

In practical high-speed core packet switches, line cards and the switch fabric can be located on different racks as seen in Figure 1.5 [26]. The distance between line cards and switch

Figure 1.5 Multi-Rack Packet Switch.

fabric can be tens to hundreds of meters. When the port speed is several Gbits/s, the cell transmission delay through the cable connecting the line cards and the switch fabric becomes non-negligible [27]. In this dissertation, round trip time (RTT) is defined as as the sum of the delays of 1) the input arbitration IA, 2) the transmission of a cell from an input to the crossbar d1, 3) the output arbitration OA, and 4) the transmission of the flow-control information back from the crossbar to the input, d2. Cell and bit alignments are included in the transmission times [28] [29]. This dissertation considers equal distance between line cards and switch fabric.

To keep up with high data rates, switch ports must be able to handle flows of up to  $R_c$  b/s,<sup>1</sup> where  $R_c$  is the data-rate capacity of a port in a switch or router. In a CICB switch (e.g., the CIXB switch presented in [1]), the maximum flow rate that the switch can handle is  $R_c \frac{k}{RTT}$ . Note that when  $r_{f(i,j)} = R_c$ , where  $r_{f(i,j)}$  is the rate of f(i, j), the maximum flow rate that the CIXB switch can transfer from inputs to outputs is equivalent to its achievable throughput. A method is proposed in [30] to reduce memory size in the buffered crossbar.

The amount of memory in a buffered crossbar is

$$N^2 \times k \times L,\tag{1.1}$$

<sup>&</sup>lt;sup>1</sup>In contrast, switches unable to support such flows can only handle aggregated data rates of  $R_c$  b/s, where each flow might have a data rate  $r_{single}$ , such that  $r_{single} < R_c$ .

where N is the number of input/output ports, k is the crosspoint buffer size in number of cells, and L is the cell size in bytes. The value of k is defined by the length of the round-trip time (RTT). For example, the switch proposed in [1] requires the size of k to be equal to or larger than the RTT to avoid throughput degradation or crosspoint-buffer underflow for flows (here defined as the data arriving at input i and destined to output j, where  $0 \le i, j \le N - 1$ ) with high data rates.

## 1.2.2 Fast Memory in Switch Fabric

As stated in Subsection 1.1.2, CICB switches use memory in the buffered crosspoints. For practical high-speed core packet switches, the line speed is in the scale of Gbit/s. The memory access speed needs to be at least the same as the line speed. As the switch fabric is implemented on a single chip, the amount of memory that can be allocated is limited by the real estate of the chip. Therefore, fast memory is needed with the speed of static random access memory (SRAM) and the density of dynamic random access memory (DRAM) in the switch fabric for the CICB switches [31]. SRAM is suitable for implementation in the buffered switch fabrics for its access speed. However, SRAM is more expensive and less dense than DRAM. New switch architectures that use less memory are needed to reduce implementation cost and support long RTT.

### **CHAPTER 2**

# SHARED MEMORY CROSSPOINT BUFFERED SWITCHES

#### 2.1 Introduction

This chapter addresses the need of saving memory amount in the buffered crossbar while supporting long RTTs by two shared memory switch architectures. It is first shown that CICB switches suffer from throughput degradation under long RTTs. To support long RTTs, CICB switches need the amount of memory proportional to the switch size and RTT. The implementation of CICB switches becomes infeasible when switch size is large and RTT is long.

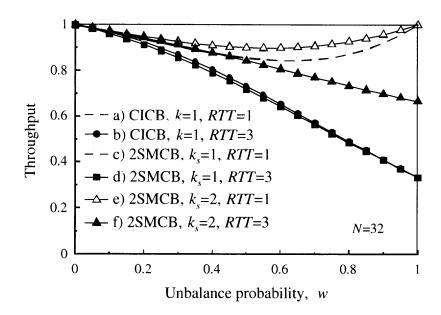

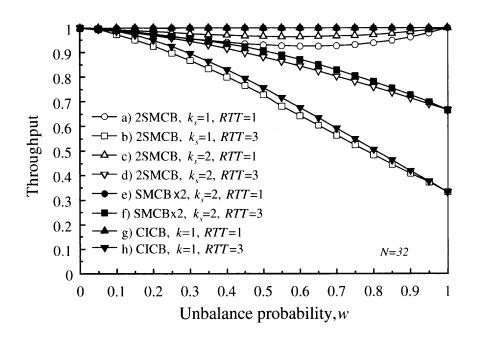

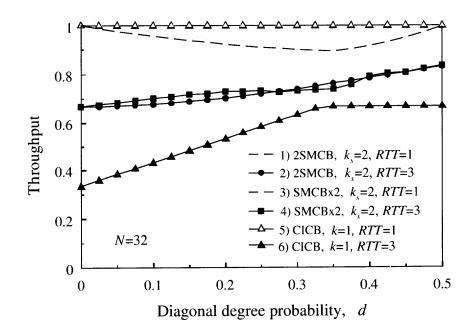

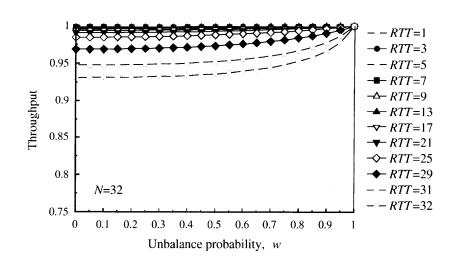

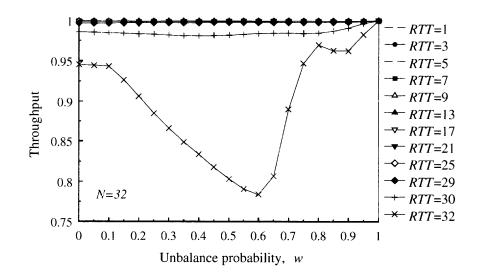

The throughput of the CICB switch is observed under different k and RTT values in a  $32 \times 32$  switch to validate the traffic model. Different from [1], RTT > 0 is considered in this dissertation. Here, it is assumed that the distances between input ports and the buffered crossbar are identical.<sup>2</sup> To model flows with different rates, unbalanced traffic model is used [1]. The unbalanced traffic model uses a probability, w, as the fraction of input load directed to a single predetermined output, while the rest of the input load is directed to all outputs with uniform distribution. For an  $N \times N$  CICB switch with input port s, output port d, and the offered input load for each input port  $\rho$ , the traffic load from input port s to output port d,  $\rho(s, d)$  is given by,

$$\rho(s,d) = \begin{cases} \rho\left(w + \frac{1-w}{N}\right) & \text{if } s = d\\ \rho\frac{1-w}{N} & \text{otherwise.} \end{cases}$$

When w = 0, the offered traffic is uniform and can be represented as the matrix below,

<sup>&</sup>lt;sup>2</sup>The results in this dissertation also apply for non-identical distances.

$$\bar{\rho} = \rho \left( \begin{array}{ccc} \frac{1}{N} & \cdots & \frac{1}{N} \\ \vdots & \ddots & \vdots \\ \frac{1}{N} & \cdots & \frac{1}{N} \end{array} \right)$$

On the other hand, when w = 1, it is completely directional, from input *i* to output *j*, where i = j. This means that all traffic of input port *s* is destined for only output port *d*, where s = d.

The unbalanced traffic can be represented as

$$\bar{\rho} = \rho \begin{pmatrix} w + \frac{1-w}{N} & \dots & \frac{1-w}{N} \\ \vdots & \ddots & \vdots \\ \frac{1-w}{N} & \dots & w + \frac{1-w}{N} \end{pmatrix}$$

As explained in 1.2.1,  $R_c$  is the data-rate capacity of a port in a switch or router and  $r_{f(i,j)}$  is the rate of f(i,j). Under unbalanced traffic, the fraction of  $R_c$  that f(i,j) uses is  $r_{f(i,j)} = w + \frac{1-w}{N}$ . The maximum data rate of f(i,j) is represented by setting w = 1 or  $r_{f(i,j)}^{max} = R_c$ , and the minimum data rate is represented when w = 0 or  $r_{f(i,j)}^{min} = \frac{1}{N}$ . These two w values of the unbalanced traffic model are the critical points in analyzing the throughput performance.

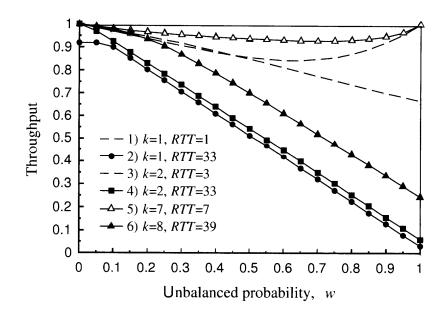

Figure 2.1 shows that when flows have a rate  $r_{f(i,j)} = r_{f(i,j)}^{min}$  (i.e., w=0) for different k values, such that RTT - k < N, the throughput is 100%, as shown by curves 1) and 5), where RTT - k = 0, and as shown by curves 4) and 6), where RTT - k = 31. The uniform distribution of traffic relaxes the demand for buffer space, resulting in high throughput. The figure also shows that when  $RTT - k \ge N$ , the throughput is less than 100%, as shown by curve 2), where RTT - k = 32.

Furthermore, as the data rate of the flow increases (i.e., w), throughput degradation occurs. The worst-case scenario is observed when  $r_{f(i,j)} = R_c$  b/s (i.e., w=1) where the

Figure 2.1 Throughput performance of a CICB switch [1] with RTT > 0.

achieved throughput is  $\frac{k}{RTT}$  for RTT - k > 0, as curves 2)-6) show. In this case, up to k cells can be sent back-to-back in RTT time slots.

The amount of memory in a buffered crossbar is

$$N^2 \times k \times L,\tag{2.1}$$

where N is the number of input/output ports, k is the crosspoint buffer size in number of cells, and L is the cell size in bytes. The value of k is defined by the length of the round-trip time (RTT). For example, the switch proposed in [1] requires the size of k be equal to or larger than the round-trip time to avoid throughput degradation or crosspoint-buffer underflow for flows (here defined as the data arriving at input i and destined to output j, where  $0 \le i, j \le N - 1$ ) with high data rates.

In a CICB switch, the crosspoint-buffer size to avoid underflow by flows of data rate  $R_c$  b/s, where  $R_c$  is the port speed, is

$$RTT = d1 + OA + d2 + IA \le k, \tag{2.2}$$

such that cells are transmitted continuously every time slot [1].

Furthermore, as the buffered crossbar can be physically located far from the input ports in a multi-rack router implementation, actual RTTs can be long. To support long RTTs in a buffered-crossbar switch, the crosspoint-buffer size needs to be increased [32], such that up to RTT cells can be buffered. However, the memory amount that can be allocated in a chip is limited, and therefore, it can make the implementation costly or infeasible when the distance between line cards and the buffered crossbar is long, or else to provide k such that k < RTT without supporting high data rates. An interesting scheme using limited memory is presented in [30] for a switch with p traffic classes, where the crosspoint buffer size is larger than RTT for a single class, and smaller than  $p \times RTT$ .

A solution to keep the crosspoint buffer small while supporting long RTTs and high data rates is needed.

In this chapter, two shared memory combined input crosspoint buffered switches (SMCB) are proposed to reduce the required memory amount in the buffered crossbar as in CICB switches and support long *RTT*. These switches use shared memory in the crosspoint buffers to reduce the total crosspoint buffer size such that flows with high data rates can be handled with smaller memory than a switch with dedicated buffers. This chapter shows that a SMCB switch supports a given round-trip time with half or less memory than a buffered crossbar with dedicated crosspoint buffers and deliver equivalent switching performance. Furthermore, it is shown that no speedup is needed when using the shared-memory approach.

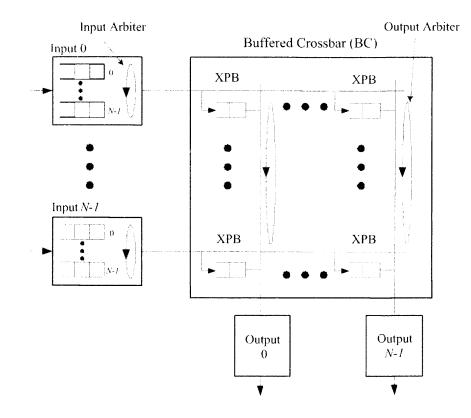

#### 2.2 Shared Memory Combined Input Crosspoint Buffered Switches (SMCB)

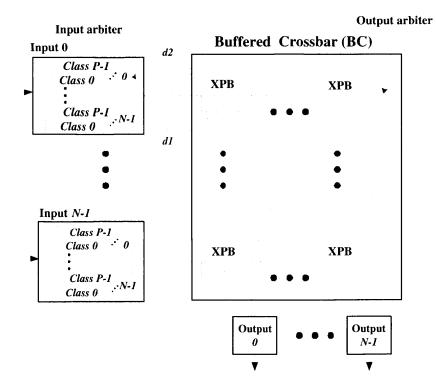

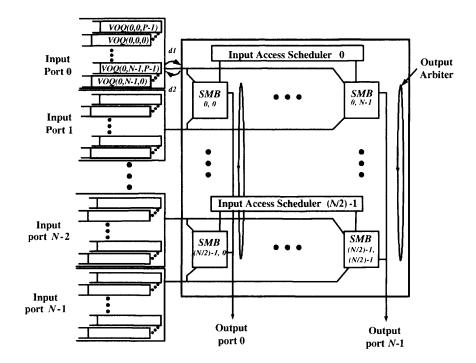

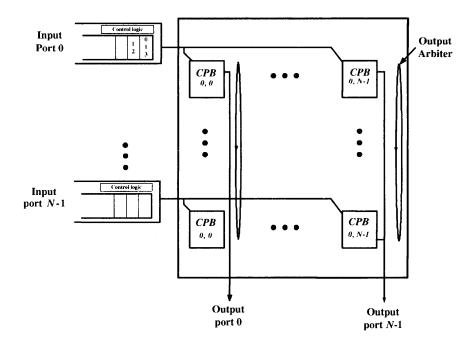

As discussed in Section 2.1, the largest throughput degradation occurs when the  $r_{f(i,j)} = R_c$ b/s, or w = 1 in the unbalanced traffic model. Under these conditions, all traffic at input *i* goes to the crosspoint that connects to output *j* and the other crosspoints receive no traffic. This motivates the sharing of the crosspoint memory by two or more inputs. In an SMCB switch, the crosspoint buffer is shared by m inputs, where  $1 \le m \le N$ . Two SMCB switch architectures are proposed, SMCB with dynamic memory allocation, or the SMCB×m switch, and speedup =m and an SMCB switch with no speedup and input access schedulers, or the mSMCB switch. The SMCB×m switch requires memory speedup and a dynamic partitioning of the amount of memory for each input of the shared memory based on the VOQ occupancy. The mSMCB switch implements input-to-crosspoint matching to eliminate speedup in the shared crosspoint memory.

#### 2.2.1 Shared-Memory Crosspoint Buffered Switch with Speedup m

#### $(SMCB \times m)$

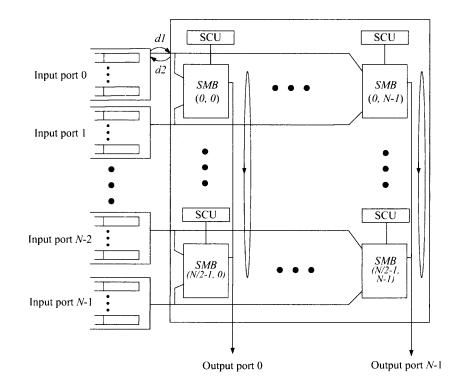

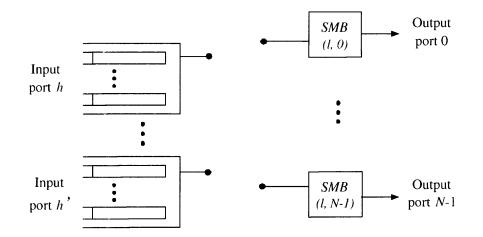

The SMCB×m switch has N VOQs at each input. A crosspoint in the shared-memory buffered crossbar that connects input port i to output j is also denoted as XP(i, j). To minimize the speedup of the shared memory, the crosspoint buffer is only shared by two inputs. The buffer for XP(i, j) and XP(i', j), where  $0 \le i, i' \le N - 1$  and  $i \ne i'$ , that stores cells for output port j and is shared by these two crosspoints (or inputs i and i') is denoted as SMB(q, j), where  $0 \le q \le \frac{N}{2} - 1$ . An even N is assumed for the sake of clarity. However an odd N can be used.<sup>3</sup> For a switch where each crosspoint buffer is shared by m inputs, there are  $\frac{N^2}{m}$  shared-memory crosspoint buffers in the buffered crossbar. The speedup of the shared crosspoint memory is m.

Figure 2.2 shows the architecture of the switch with two inputs sharing the buffered crosspoint. The arbitration scheme for both inputs and outputs is round-robin. The switch works as following. Each input sends its VOQ occupancy  $Z_{i,j}$  to the crossbar. The sharing control unit (SCU) at every SMB sets up a threshold for partition of the shared memory, one for each input, based on the occupancy a VOQ has. This dynamically allocates the memory between the two inputs sharing the buffered crosspoint. The threshold sets the maximum value  $C_{i,j}^{max}$  of credit-based flow control counter at the input. In this architecture,

<sup>&</sup>lt;sup>3</sup>For switches with odd number of ports, one port is left with dedicated buffers of size 0.5 the capacity of a SMB.

**Figure 2.2**  $N \times N$  shared-memory buffered crossbar switch with speedup m.

each shared crosspoint buffer size is  $k_s$ , where  $k_s \ge RTT$ . The threshold value based on the input occupancy of two input sharing the buffered crosspoint is presented in Table 2.1.

The occupancy of the two VOQs that share a crosspoint buffer is represented as  $Z_{i,j}$ and  $Z_{i',j}$ . There are four occupancy states - when  $Z_{i,j} = 0$ ,  $Z_{i,j} \leq \frac{RTT}{2}$ ,  $\frac{RTT}{2} < Z_{i,j} \leq RTT$  and  $Z_{i,j} > RTT$ . Since *m* inputs may need to access the shared memory at the same time, this architecture requires the shared memory have a speedup of *m*. To minimize the speedup, *m* is set to two in this dissertation.

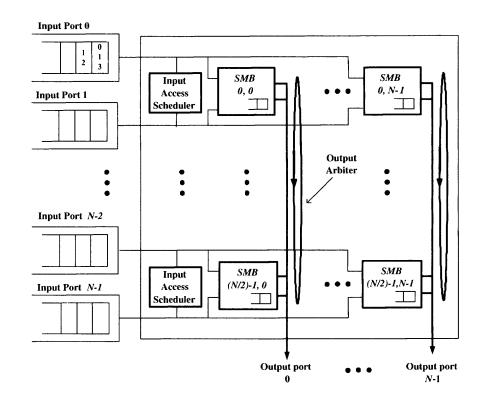

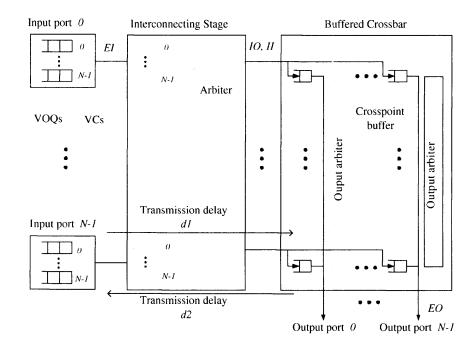

# 2.2.2 Shared-Memory Crosspoint Buffered Switch with Input-Crosspoint Matching (*m*SMCB)

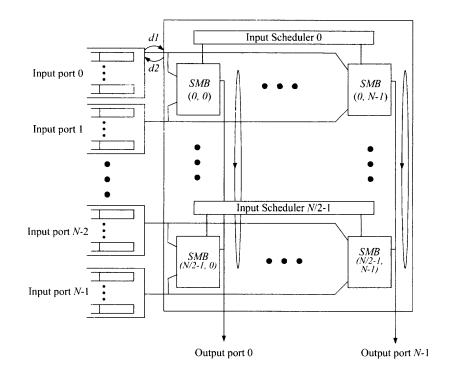

To eliminate the speedup at SMBs, only one input is allowed to access an SMB at a time. An input-access scheduler is used among the m inputs that share the same SMB(q, j) to schedule the SMB access between two inputs that are physically separated. The size of an

| $Z_{i,j}$        | $Z_{i',j}$       | $C_{i,j}^{max}$  | $C_{i',j}^{max}$ |

|------------------|------------------|------------------|------------------|

| 0                | 0                | 0                | 0                |

| [0, RTT]         | 0                | $Z_{i,j}$        | 0                |

| $[RTT,\infty]$   | 0                | RTT              | 0                |

| [0, RTT/2]       | [0, RTT/2]       | RTT/2            | RTT/2            |

| $[RTT/2,\infty)$ | [0, RTT/2]       | $RTT - Z_{i',j}$ | $Z_{i',j}$       |

| $[RTT/2,\infty)$ | $[RTT/2,\infty)$ | RTT/2            | RTT/2            |

**Table 2.1** Threshold Setup of SMCB $\times m$  Switch

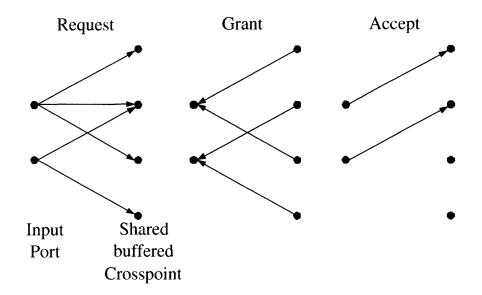

SMB, in number of cells that can be stored, is  $k_s$ . There are  $\frac{N}{m}$  input-access schedulers in the buffered crossbar. An input-access scheduler matches non-empty inputs to the SMBs that have room for storing a new cell. As shown in figure 2.3, there are N/2 input-access schedulers with m = 2.

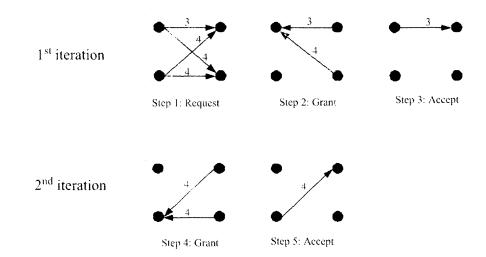

The input-access scheduler performs a matching process among the shared-crosspoint buffers and the inputs that share them. Figure 2.4 shows the inputs and the shared crosspoint buffers that take place in the matching. The matching follows a three-phase process, as performed for IB switches. The matching scheme used in this switch is round-robin based [33] to have a valid comparison with the CIXB switch. However, any matching scheme can be used.

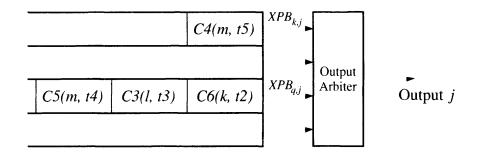

At each output j in the buffered crossbar, there is an output arbiter to select the outgoing cell from non-empty crosspoint buffers as shown in figure 2.3. The transmission delays between ports and the crosspoint are denoted by d1 and d2. An output arbiter can consider up to two cells from an SMB, where each cell belongs to one different input.

The way the *m*SMCB switch works is as follows. Cells destined to output j arrive at VOQ(i, j) and wait for dispatching. Input i notifies the input-access scheduler about the new cell arrival. The input access scheduler selects the next cells to be forwarded to the

Figure 2.3  $N \times N$  Shared-memory buffered crossbar switch.

Figure 2.4 Bipartite matching in an input-access scheduler between inputs and SMBs.

**Figure 2.5** Example of the matching process in a  $4 \times 4$  switch.

crossbar by matching the *m* inputs to the SMBs. Figure 2.5 shows an example of a  $2 \times 4$  bipartite match as used in this input-SMB matching.

A cell going from input *i* to output *j* enters the buffered crossbar and is stored in SMB(q, j). Cells leave output *j* after being selected by the output arbiter. The output arbiter uses round-robin selection.

A flow control mechanism that behaves like the credit-based flow control [1] is applied by input-access schedulers to avoid crosspoint-buffer overflow. Input access scheduler considers VOQs for which the SMBs that are not full as eligible. The input-access scheduler information is sent from the SMB to the corresponding VOQ (i.e., *d*2). Cells and flow-control data experience transmission delays between input ports and the buffered crossbar.

#### 2.3 Performance Analysis of the SMCB Switch with Random Selection

In this section, the throughput of the mSMCB and SMCBxm switches with random-based selection schemes, under independent and identically distributed (i.i.d.) Bernoulli traffic at each input is analyzed. It is demonstrated that under these conditions, speedup is not

necessary. The emphasis is made on switches with m = 2, and it is shown that the 2SMCB switch provides equivalent performance to that of the SMCB×2 switch. At the end, the case of m = N for the mSMCB switch is analyzed to discuss the trade-off between switching performance and memory efficiency. The throughput of data switches with and without speedup is presented in [34] using fluid model approach.

The analysis focuses on the probability that a VOQ receives service. The service is defined in function of the flow of cells through the crosspoint buffer, which is defined by the service rate given by an output arbiter. Therefore, the analysis shows the effect that the matching process has over the switch performance.

In an SMCBx2 switch, SMBs are partitioned before the cells are forwarded from the input to the crosspoints, and therefore, a partition can be considered as a dedicated buffer for input *i*. A VOQ must be selected by the input arbiter to forward a cell to the buffer partition. It is considered that an SMB of size  $k_s$  stores one or more cells for the *m*SMCB switch and two or more cells for the SMCB×*m* switch. The probability that a buffer is full is denoted as  $P_f$  and the probability that a VOQ is blocked (from sending a cell to the corresponding crosspoint buffer) is denoted as  $P_b$ . The probability that a VOQ sends the HOL cell to the buffer is defined by the nonblocking probability of a VOQ,  $1 - P_b$ . For the sake of clarity, the variables for the *m*SMCB switch are represented with the superscript M and those for the SMCB×*m* switch with the superscript X.

#### **2.3.1** *m***SMCB** Switch with $k_s = 1$

The blocking probability of a VOQ in the *m*SMCB switch with  $k_s = 1$ , denoted as  $P_{b1}^M$ , is defined by two cases: a) when the SMB is full with probability  $P_{fk_s}^M$ , the blocking probability is the probability that there is cell to be forwarded to the corresponding VOQ. The probability that there is a cell destined to this specific output is  $\frac{1}{N}$ . b) When the SMB is available, there may be t inputs contending with a specific input, where  $0 \le t \le m - 1$ , requesting access to the SMB, and only one input is granted. Therefore, the probability that

**Figure 2.6** Diagram of the Markov chain of a buffer of size  $k_s$ .

an input receives no grant is  $\frac{t}{t+1}$ . Considering these two cases, the blocking probability for *m*SMCB switch is stated as

$$P_{b1}^{M} = \frac{1}{N} P_{f1}^{M} + \sum_{t=0}^{m-1} {m-1 \choose t} (\frac{1}{N})^{t} (1-\frac{1}{N})^{m-1-t} \frac{t}{t+1} (1-P_{f1}^{M}).$$

(2.3)

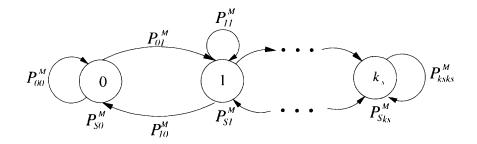

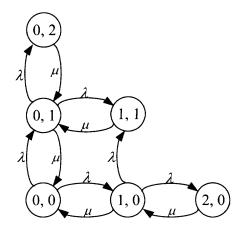

A Markov chain is used to model SMB(i, j) of the *m*SMCB switch [35] [36]. Figure 2.6 shows the Markov chain of an SMB of size  $k_s$ .  $P_{Sr}^M$  is the state probability where  $0 \le r \le k_s$ .  $P_{r,u}^M$  is the transition probability from state *r* to state *u*.  $P_{fk_s}^M$  is the probability that the SMB is full, and it is equivalent to the state probability  $P_{Sk_s}$ .

For any  $k_s$ ,  $P_{01}^M$  is then defined by the product of input arrival rate  $\rho_{i,j}$  and the matching probability between the input and the SMBs,

$$P_{01}^{M} = \rho_{i,j} \sum_{t=0}^{m-1} {\binom{m-1}{t}} (\frac{1}{N})^{t} (1 - \frac{1}{N})^{m-1-t} \frac{1}{t+1}$$

(2.4)

The service rate  $P_{service}^{M}$  is the probability the output arbiter selects a non-empty SMB(i, j) for forwarding a cell to the output. It is easy to see that for m = 2,  $P_{service}^{M} = \frac{2}{N}$  for any state.  $P_{10}^{M}$ , which occurs when input *i* has no requests and SMB(i, q) is selected by the output arbiter, is defined by

$$P_{10}^{M} = (1 - \rho_{i,j}) P_{service}^{M}.$$

(2.5)

**Figure 2.7** Diagram of the Markov chain of a buffer of size  $k_s = 1$ .

Figure 2.7 shows the state diagram when  $k_s = 1$  for mSMCB switch. From this state diagram, the following two balance equations can be obtained,

$$\begin{cases}

P_{01}^{M} P_{S0}^{M} = P_{10}^{M} P_{S1}^{M}; \\

P_{S0}^{M} + P_{S1}^{M} = 1;

\end{cases}$$

(2.6)

and from these, it is defined that

$$P_{f_1}^M = P_{S_1}^M = \frac{P_{01}^M}{P_{01}^M + P_{10}^M}.$$

(2.7)

$P_{00}^{M}$  is the probability that input *i* has no request.  $P_{11}^{M}$  is the probability that input *i* has no request and SMB(i, j) is not selected by output arbiter or input *i* has request and SMB(i, j) is selected by output arbiter to forward a cell. These two transition probabilities have no effect in our balance equations.

## **2.3.2** *m*SMCB Switch with $k_s = 2$

To analyze the performance of the two SMCB switches when they have the same amount of memory in the SMBs,  $k_s$  is set to two.

The probability that an SMB is full follows (2.3),

$$P_{b1}^{M} = \frac{1}{N} P_{f1}^{M} + \sum_{t=0}^{m-1} \binom{m-1}{t} (\frac{1}{N})^{t} (1-\frac{1}{N})^{m-1-t} \frac{t}{t+1} (1-P_{f1}^{M}).$$

(2.8)

Figure 2.8 shows the Markov chain diagram of the *m*SMCB switch when  $k_s = 2$ . From this figure, the following balance equations are obtained:

**Figure 2.8** Diagram of the Markov chain of a buffer of size  $k_s = 2$ .

$$\begin{cases}

P_{01}^{M} P_{S0}^{M} = P_{10}^{M} P_{S1}^{M}; \\

P_{12}^{M} P_{S1}^{M} = P_{21}^{M} P_{S2}^{M}; \\

P_{S0}^{M} + P_{S1}^{M} + P_{S2}^{M} = 1;

\end{cases}$$

(2.9)

and from these equations,

$$P_{f_2}^M = P_{S2}^M = \frac{P_{01}^M P_{12}^M}{P_{01}^M P_{12}^M + P_{01}^M P_{21}^M + P_{10}^M P_{21}^M}.$$

(2.10)

Here, the transition probabilities are defined as:

$$\begin{cases}

P_{01}^{M} = P_{12}^{M} = \rho_{i,j} \sum_{t=0}^{m-1} {\binom{m-1}{t}} (\frac{1}{N})^{t} (1-\frac{1}{N})^{m-1-t} \frac{1}{t+1}; \\

P_{10}^{M} = (1-\rho_{i,j}) \frac{1}{N-1}; \\

P_{21}^{M} = (1-\rho_{i,j}) \frac{2}{N};

\end{cases}$$

(2.11)

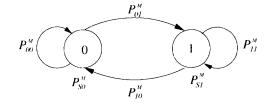

# **2.3.3** SMCB $\times m$ Switch with $k_s = 2$

Without losing generality, let us assume that all VOQs have a backlog longer than RTT, such that in the SMCBxm switch, where an SMB is shared by m inputs (i.e., VOQs), an SMB is partitioned into m equally sized parts, one part for each VOQ. In this case, the blocking probability of a VOQ is in function of the occupancy of the allocated portion for an SMB, such that the portion is either full or available.

For the SMCB×2 switch, the SMB is partitioned into two equally divided parts of size  $\frac{k_s}{2}$ . One part for each VOQ sharing this SMB. This is equivalent to having each VOQ with a designated crosspoint buffer with a variable buffer size. The blocking probability of a VOQ is determined by considering whether the allocated portion of the SMB is full or

available. Under uniform traffic, the average size of allocated portion of the SMB for each VOQ is equal to each other.  $P_b^X$  is represented as

$$P_b^X = \rho_{i,j} P_f^X. \tag{2.12}$$

The allocated portion with size of one cell in an SMB for the SMCB×2 is also modeled as a Markov chain, as the model in Figure 2.6 shows for the *m*SMCB switch (where the superscripts *M*s can be substituted by *X*s). The state transition probability  $P_{01}^X$  for the SMCBx2 switch is the product of input arrival rate  $\rho_{i,j}$  and the probability that the input arbiter selects VOQ(i, j),  $\frac{1}{N}$ . Then,

$$P_{01}^X = \rho_{i,j} \frac{1}{N}.$$

(2.13)

The service rate  $P_{service}^X$  is the probability that the output arbiter selects SMB(i, j) to forward a cell to the output, and this is  $\frac{1}{N}$ . The transition probability  $P_{10}^X$  is the probability of an SMB being selected by the output arbiter while having no request from the input, or

$$P_{10}^X = (1 - \rho_{i,j}) \frac{1}{N}.$$

(2.14)

$P_f^X$  is calculated as in (2.7):

$$P_f^X = P_{S1}^X = \frac{P_{01}^X}{P_{01}^X + P_{10}^X}.$$

(2.15)

# 2.3.4 Maximum Throughput of the 2SMCB and SMCBx2 switches with Random Selection

Considering the blocking probabilities of the VOQs in both switches, the throughput of each switch can be determined as i.i.d. traffic is assumed. Next, it is demonstrated that these two switches have similar performance for large N by looking at the blocking probability of VOQs.

The following equations show the limits of the  $P_b$  functions for the 2SMCB switch when  $k_s$  is 1 and 2 cells, respectively, and for SMCBx2 switch when  $k_s$  is 2 cells.

In the case for the 2SMCB switch with  $k_s = 1$ ,

$$\lim_{N \to \infty} P_{f_1}^M = \lim_{N \to \infty} \frac{1 - \frac{1}{2N}}{3 - \frac{5}{2N}} = \frac{1}{3}$$

(2.16)

therefore,

$$\lim_{N \to \infty} P_{b1}^{M} = \lim_{N \to \infty} \left\{ \frac{1}{N} P_{f1}^{M} + \frac{1}{2N} (1 - P_{f1}^{M}) \right\} = 0.$$

(2.17)

For the case where  $k_s = 2$ :

$$\lim_{N \to \infty} P_{f_2}^M = \lim_{N \to \infty} \frac{1 - \frac{1}{N} + \frac{1}{4N^2}}{3 - \frac{4}{N} + \frac{5}{4N^2} + \frac{2N}{N-1} - \frac{4}{N-1} + \frac{2}{N^2 - N}} = \frac{1}{3}$$

(2.18)

then, the limit follows (2.16),

$$\lim_{N \to \infty} P_{b2}^M = \lim_{N \to \infty} \left\{ \frac{1}{N} P_{f2}^M + \frac{1}{2N} (1 - P_{f2}^M) \right\} = 0.$$

(2.19)

For the SMCBx2 switch with  $k_s = 2$ , using (2.13), (2.14), and (2.15),

$$\lim_{N \to \infty} P_b^X = \lim_{N \to \infty} \frac{1}{N^2} = 0.$$

(2.20)

Therefore, because the minimum  $k_s$  values are addressed, it can be concluded that in all cases, the nonblocking probability,  $1 - P_b$ , for these two switches with any  $k_s$  value approaches 1 as N grows. Since the switch throughput is defined by the non-blocking probability, both switches achieve 100% throughput for a large N.

The reason why this high throughput is achieved with random selection is because the matching size in the 2SMCB switch is  $2 \times N$ , which means that there is an expansion gain, and because the speedup is two in the SMCBx2. However, in the case of the mSMCB switch with no expansion, or m = N, and  $k_s = 1$ , the performance of the mSMCB switch follows that of an IB switch using random selection. Considering that the limit of the non-matching probability is,

$$\lim_{N \to \infty} \sum_{t=0}^{N-1} \binom{N-1}{t} (\frac{1}{N})^t (1-\frac{1}{N})^{N-1-t} \frac{t}{t+1}$$

(2.21)

$$= \lim_{N \to \infty} (1 - \frac{1}{N})^N = 0.368, \qquad (2.22)$$

the probability that the SMB is full is:

to

$$\lim_{N \to \infty} P_{f_1}^M = \lim_{N \to \infty} \frac{(1 - \frac{1}{N})^N}{(1 - \frac{1}{N})^N + N - 1} = 0.$$

(2.23)

Therefore, the nonblocking probability when all N inputs share the SMBs converges

$$1 - \lim_{N \to \infty} P_b^M = 1 - \left(\lim_{N \to \infty} \left\{ \frac{1}{N} P_f^M + \left(1 - \frac{1}{N}\right)^N (1 - P_f^M) \right\} \right) = 0.632$$

(2.24)

Therefore, the throughput of this switch is 63.2% (as in [37], [38] for an  $N \times N$  IB switch with random selection. This proves that the performance of the mSMCB switch is dominantly defined by the matching scheme, and therefore when m is smaller than the switch size, the mSMCB switch delivers higher throughput performance. From this, while a larger m saves more crossbar memory, the throughput performance becomes compromised.

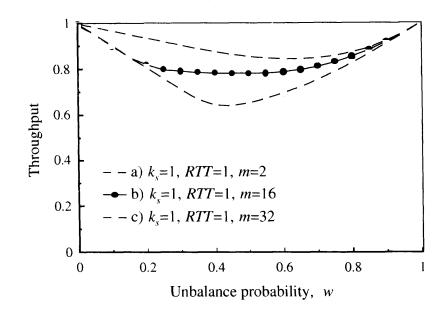

#### 2.3.5 Non Blocking Probability for Small Switch Sizes

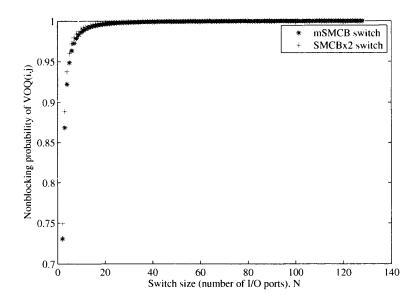

To observe the throughput of smaller switch sizes, the nonblocking probabilities of switches with sizes from 2 to 128 ports are computed as Figure 2.9 shows, using (2.7) and (2.15).

Figure 2.9 shows the nonblocking probability of a VOQ when  $k_s = 1$  for 2SMCB and  $k_s = 2$  for SMCB×2 switch under uniform traffic. The result shows that the SMCB×2 switch achieves higher throughput than the 2SMCB switch when switch size is small (when N < 16). When switch size increases, the throughput of both switches approaches 100%.

**Figure 2.9** Calculated throughput of a VOQ under uniform traffic,  $\rho = 1$ ,  $k_s = 1$  for *m*SMCB switch,  $k_s = 2$  for SMCB×2 switch.

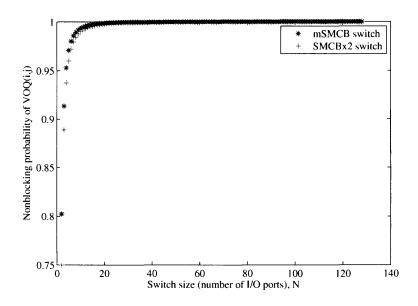

The throughputs of both switches are compared when they have the same amount of memory in the SMBs (i.e., the 2SMCB and SMCB×2 switches with  $k_s = 2$ ). Figure 2.10 shows the nonblocking probability when  $k_s = 2$  for the 2SMCB and SMCB×2 switches. The curves in this figure were generated using (2.7) for the SMCB×2 switch and (2.10) for the 2SMCB switch. The results show that the throughput of the 2SMCB switch is higher than that of the SMCB×2 switch when the switch size N < 16. However, when the switch size increases, the throughputs of both switches become similar, as these approach 100%.

#### 2.4 Simulation of the SMCB Switch under Different Traffic Models

In this section the switching performances of two  $32 \times 32$  switches is compared. It also presents the throughput performances of a CIXB switch and SMCB switches with buffered crosspoint shared by *m* inputs. The throughput and average cell delay under traffic with Bernoulli and bursty arrivals with uniform distribution, and the throughput under Bernoulli traffic with unbalanced distribution are studied.

**Figure 2.10** Calculated throughput of a VOQ under uniform traffic,  $\rho = 1$ ,  $k_s = 2$  for *m*SMCB and SMCB×2 switch.

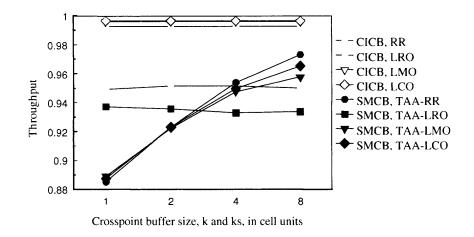

#### 2.4.1 Performance of SMCB Switches with Round-Robin Selection

This section compares the switching performance of  $32 \times 32$  CICB, SMCB×2 and *m*SMCB, all using round-robin selection schemes via computer simulation. It presents the throughput performance and average cell delay of all these switches. The considered traffic models have Bernoulli and bursty arrivals with uniform and nonuniform distributions. Simulation results are obtained with a 95% confidence interval, not greater than 5% standard error for the average cell delay.

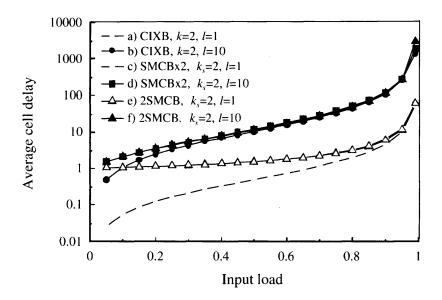

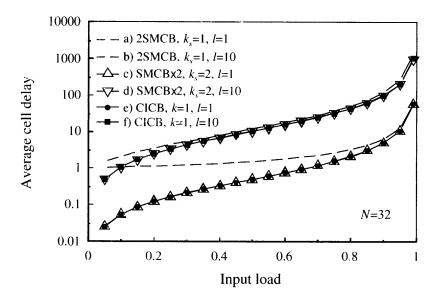

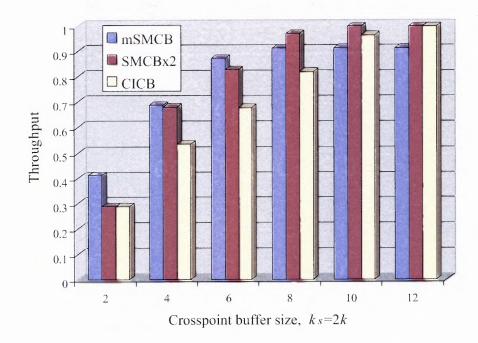

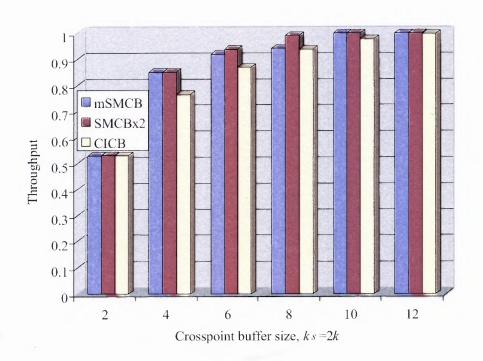

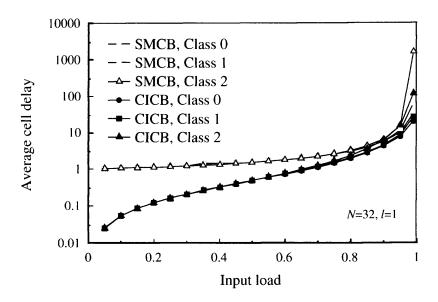

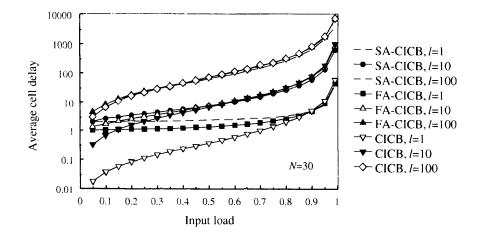

**2.4.1.1 Uniform Traffic.** Figure 2.11 shows the average cell delay of the CICB, SMCB×2, and 2SMCB switches under uniform traffic. Here, the crosspoint buffer size for CICB, k, is 2, and the crosspoint buffer size for the SMCB×2 and 2SMCB switch,  $k_s$ , is also 2. By using these crosspoint buffer sizes, the amount of memory used in the SMCB switches is half the amount of memory of that in the CICB switch. Figure 2.11 shows that the average cell delay of the SMCB×2 and 2SMCB switches are similar. Furthermore, the average cell delay of the SMCB switches shows similar magnitude to that of the CICB switch without

**Figure 2.11** Average cell delay of  $32 \times 32$  CICB, SMCB×2, and 2SMCB switches with round-robin selection, under uniform traffic.

the effects of RTT (i.e,  $RTT \leq 1$ ). The larger average delay shown by SMCB switches at loads from 0.1 to 0.8 are a constant time slot because the VOQs notify the input-access scheduler when a new cell arrives in SMCB×2, and a VOQ is matched before forwarding a cell to the crossbar. These processes always take at least one time slot. For loads over 0.9, the SMCB switches have the average delay similar to that of the CICB switch. The results for bursty traffic, with the average burst length l of 10 cells, is similar for the three switches. It can be observed that these three switches have similar performance under uniform traffic. Therefore, the SMCB switches with m = 2 have equivalent performance under uniform traffic while using half memory amount of the CICB switch.

**2.4.1.2** Nonuniform Traffic: Unbalanced Distribution. As described in Section 2.1, the unbalanced traffic model distributes the load of an input in two different parts: one fraction (i.e. w) to one output port and the rest to all output ports. This traffic model is becoming widely used because switches have been shown to be sensitive to this nonuniform distribution.

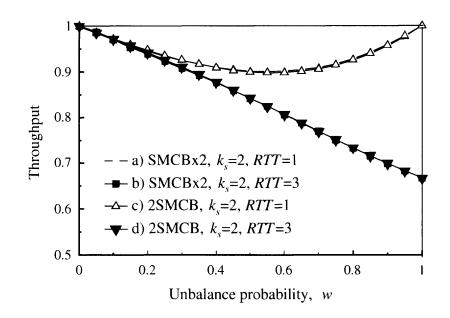

Figure 2.12 Throughput of SMCB $\times$ 2 and 2SMCB switches with round-robin selection and the same amount of memory.

Figure 2.12 shows the throughputs of the SMCB×2 and 2SMCB switches when they have the same amount of memory,  $k_s = 2$ . The amount of memory used is the minimum as SMCB×2 can only work with  $k_s \ge 2$ , according to Table 2.1. This figure shows that these two switches have the same throughput performance for small and long RTTs, RTT = 1and RTT = 3, respectively under unbalanced traffic. Because of this, the following simulations consider only the 2SMCB switch, unless otherwise stated. The effect of long RTTson the proposed switches is observed by measuring the throughputs under the unbalanced traffic model, as in Section 2.1.

Figure 2.13 shows the throughput performance of the 2SMCB switch, with  $k_s \ge 1$ . This switch has a symmetric throughput when w = 0.0 and w = 1.0 or  $r_{f(i,j)} = r_{f(i,j)}^{max} = r_{f(i,j)}^{min}$ , and achieves 100% throughput for  $k_s - RTT \ge 0$  when w = 1.0, as the figure shows in all curves, except for d) and f), which have  $k_s - RTT < 0$  at this value of w. For w = 1.0, the throughput can be 100% using half of the total amount of memory used by the CICB switch.

**Figure 2.13** Throughput of a 2SMCB switch with half  $(k_s = 1)$  and equal  $(k_s = 2)$  amount of memory to the CICB switch.