#### New Jersey Institute of Technology Digital Commons @ NJIT

#### Dissertations

Theses and Dissertations

Summer 2007

## Characterization and modeling of low-frequency noise in Hf-based high -kappa dielectrics for future cmos applications

Purushothaman Srinivasan New Jersey Institute of Technology

Follow this and additional works at: https://digitalcommons.njit.edu/dissertations Part of the <u>Electrical and Electronics Commons</u>

#### **Recommended** Citation

Srinivasan, Purushothaman, "Characterization and modeling of low-frequency noise in Hf-based high -kappa dielectrics for future cmos applications" (2007). *Dissertations*. 824. https://digitalcommons.njit.edu/dissertations/824

This Dissertation is brought to you for free and open access by the Theses and Dissertations at Digital Commons @ NJIT. It has been accepted for inclusion in Dissertations by an authorized administrator of Digital Commons @ NJIT. For more information, please contact digitalcommons@njit.edu.

# **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

#### ABSTRACT

#### CHARACTERIZATION AND MODELING OF LOW-FREQUENCY NOISE IN Hf-BASED HIGH-κ DIELECTRICS FOR FUTURE CMOS APPLICATIONS

#### by Purushothaman Srinivasan

The International Technology Roadmap for Semiconductors outlines the need for high- $\kappa$  dielectric based gate-oxide Metal Oxide Semiconductor Field Effect Transistors for sub-45 nm technology nodes. Gate oxides of hafnium seem to be the nearest and best alternative for silicon dioxide, when material, thermal and structural properties are considered. Usage of poly-Si as a gate electrode material degrades the performance of the device and hence gate stacks based on metal gate electrodes are gaining high interest. Though a substantial improvement in the performance has been achieved with these changes, reliability issues are a cause of concern. For analog and mixed-signal applications, low-frequency (1/f) noise is a major reliability factor. Also in recent years, low frequency noise diagnostics has become a powerful tool for device performance and reliability characterization.

This dissertation work demonstrates the necessity of gate stack engineering for achieving a low 1/f noise performance. Changes in the material and process parameters of the devices, impact the 1/f noise behavior. The impact of 1/f noise on gate technology and processing parameters were identified and investigated. The thickness and the quality of the interfacial oxide, the nitridation effects of the layers, high- $\kappa$  oxide, bulk properties of the high- $\kappa$  layer, percentage of hafnium content in the high- $\kappa$ , post deposition anneal (PDA) treatments, effects of gate electrode material (poly-silicon, fully silicided or metal),

gate electrode processing are investigated in detail. The role of additional interfaces and bulk layers of the gate stack is understood. The dependence of low-frequency noise on high and low temperatures was also investigated. A systematic and a deeper understanding of these parameters on 1/f noise behavior are deduced which also forms the basis for improved physics-based 1/f noise modeling. The model considers the effect of the interfacial layer and also temperature, based on tunneling based thermally activated model. The simulation results of improved drain-current noise model agree well with the experimentally calculated values.

#### CHARACTERIZATION AND MODELING OF LOW-FREQUENCY NOISE IN Hf-BASED HIGH-κ DIELECTRICS FOR FUTURE CMOS APPLICATIONS

by

Purushothaman Srinivasan

A Dissertation Submitted to the Faculty of New Jersey Institute of Technology in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy in Electrical Engineering

**Department of Electrical and Computer Engineering**

August 2007

#### APPROVAL PAGE

#### CHARACTERIZATION AND MODELING OF LOW-FREQUENCY NOISE IN Hf-BASED HIGH-к DIELECTRICS FOR FUTURE CMOS APPLICATIONS

#### Purushothaman Srinivasan

| Dr. Durgamadhab Misra, Dissertation Co-Advisor                                                             | Date |

|------------------------------------------------------------------------------------------------------------|------|

| Professor of Electrical and Computer Engineering, NJIT                                                     |      |

|                                                                                                            |      |

|                                                                                                            |      |

| Dr. Cor Claeys, Dissertation Co-Advisor                                                                    | Date |

| Professor of Electrical Engineering, KUL, Leuven, Belgium                                                  |      |

|                                                                                                            |      |

|                                                                                                            |      |

|                                                                                                            |      |

| Dr. Leonid Tsybeskov, Committee Member<br>Associate Professor of Electrical and Computer Engineering, NJIT | Date |

| Associate Professor of Electrical and Computer Engineering, NJ11                                           |      |

|                                                                                                            |      |

|                                                                                                            |      |

| Dr. Marek Sosnowski, Committee Member                                                                      | Date |

| Professor of Electrical and Computer Engineering, NJIT                                                     |      |

|                                                                                                            |      |

|                                                                                                            |      |

| Dr. Trevor Tyson, Committee Member                                                                         | Date |

| Professor of Physics, NJIT                                                                                 | Dute |

|                                                                                                            |      |

|                                                                                                            |      |

|                                                                                                            |      |

| Dr. Eduard A. Cartier, Committee Member                                                                    | Date |

Member of Technical Staff, IBM TJ Watson Research Center,

Yorktown Heights, NY

Copyright © 2007 by Purushothaman Srinivasan

ALL RIGHTS RESERVED

#### **BIOGRAPHICAL SKETCH**

Author: Purushothaman Srinivasan

Degree: Doctor of Philosophy

Date: August 2007

#### **Undergraduate and Graduate Education:**

- Doctor of Philosophy in Electrical Engineering New Jersey Institute of Technology, Newark, NJ, 2007

- Master of Science in Electrical Engineering New Jersey Institute of Technology, Newark, NJ, 2003

- Bachelor of Technology in Electronics and Communication Pondicherry Engineering College, Pondicherry, India, 1999

Major: Electrical Engineering

#### **Presentations and Publications:**

P. Srinivasan, B. P. Linder, V. Narayanan, D. Misra and E. Cartier, "Impact of high- $\kappa$  and SiO<sub>2</sub> interfacial layer thickness on low-frequency (1/f) noise in aggressively scaled metal gate/HfO<sub>2</sub> n-MOSFETs: Role of high- $\kappa$  phonons", vol. 47, no. 4-5, pp. 501-504, Microelectronic Engineering, Apr-May 2007.

P. Srinivasan, F. Crupi, P. Magnone, E. Simoen, C. Pace, D. Misra, and C. Claeys – "Interfacial layer quality effects on low-frequency noise (1/f) in p-MOSFETs with advanced gate stacks", accepted (in press), Microelectronics Reliability, 2007.

P. Srinivasan, E. Simoen, B. de Jaeger, C. Claeys, and D. Misra, "1/f noise performance of p-MOSFETs with HfO<sub>2</sub> and metal gate on Ge-based substrates", vol. 9, no.4, pp. 721-726, Elsevier, Material Science and Semiconductor Processing, 2006.

P. Srinivasan, E. Simoen, Z. M. Rittersma, W. deWeerd, L. Pantisano, C. Claeys, and D. Misra, "Effect of nitridation on 1/f noise in n-and p-MOSFETs with HfO<sub>2</sub> dielectrics", vol. 153, no. 9, pp. G819-G825, Journal of Electrochemical Society, 2006.

P. Srinivasan, E. Simoen, R. Singanamalla, H. Y. Yu, C. Claeys and D. Misra, "Gateelectrode effects on low-frequency (1/f) noise in p-MOSFETs with high- $\kappa$  dielectrics", vol. 50, pp. 992–998, Solid State Electronics, 2006.

P. Srinivasan, E. Simoen, L. Pantisano, C. Claeys, and D. Misra, "Low Frequency noise performance of n- and p-MOSFETS with poly-Si/Hf-Based Gate Dielectrics", vol. 153, no. 4, pp. G324-329, Journal of Electrochemical Society, 2006.

P. Srinivasan, E. Simoen, L. Pantisano, C. Claeys, and D. Misra, "Impact of high- $\kappa$  gate stack material with metal gates on LF noise in n- and p-MOSFETs", Elsevier, vol. 80, pp. 226-229, Microelectronic Engineering, 2005.

P. Srinivasan, N. A. Chowdhury, and D. Misra, "Charge trapping in Ultra-thin Hafnium silicate/Metal gate stacks", vol. 26, no.12, pp. 913-915, IEEE Electron Device Letters, 2005.

P. Srinivasan, B. Vootukuru and D. Misra, "Screening of Si-H bonds during plasma processing", Elsevier, vol. 48, no. 10-11, pp. 1809-1812, Solid State Electronics, 2004.

F. Crupi, P. Srinivasan, P. Magnone, E. Simoen, C. Pace, D. Misra, and C. Claeys, "Impact of the interfacial layer on the low-frequency noise (1/f) behavior of MOSFETs in advanced gate stacks", vol. 27, no. 8, pp. 688-690, Electron Device Letters, Aug 2006.

N. A. Chowdhury, P. Srinivasan, and D. Misra, "Trapping in Deep Defects under Substrate Hot Electron Stress in TiN/Hf-silicate Based Gate Stacks", vol. 51, no. 1, pp. 80-88, Solid State Electronics, 2007.

F. Crupi, B. Kaczer, R. Degraeve, V. Subramanian, P. Srinivasan, E. Simoen, A. Dixit, M. Jurczak, K. De Meyer, and G. Groeseneken, "Reliability comparison of triple-gate versus planar SOI FETs", vol. 53, no. 9, Sept. 2006, pp. 2351-2357, IEEE Transactions on Electron Devices, 2006.

Z. M. Rittersma, M. Vertregt, W. DeWeered, P. Srinivasan, and E. Simoen, "Mixed-Signal and Noise Properties of nMOSFETs with HfSiON/TaN Gate Stacks", vol. 53, no. 5, pp. 1216-1225, IEEE Transactions on Electron Devices, 2006.

C. Claeys, E. Simoen, P. Srinivasan, and D. Misra, "Impact of gate-dielectric interface on the low-frequency noise of thin gate oxide n-channel metal-oxide-

semiconductor field-effect-transistors",vol. 51,no. 4, pp. 627–632, Solid State Electronics, Apr 2007.

D. Misra, R. Garg, P. Srinivasan, N. Rahim, and N.A. Chowdhury, "Interface Characterization of high- $\kappa$  Dielectrics on Ge substrates", vol. 9, no. 4, pp. 714-718, Elsevier, Material Science and Semiconductor Processing, 2006.

P. Srinivasan, B. P. Linder, V. Narayanan, D.Misra, and E. Cartier, "Role of softoptical phonon scattering in aggressively scaled  $HfO_2$  MOSFETs with metal gates: Thickness and temperature dependent mobility studies", IEEE Electron Device Letters (submitted).

P. Srinivasan, B. P. Linder, V. Narayanan, D. Misra, and E. Cartier, "Impact of high- $\kappa$  layer thickness on low-frequency (1/f) noise in aggressively scaled metal gate/HfO<sub>2</sub> n-MOSFETs: Role of high- $\kappa$  phonons", Extended abstract for Insulating Films on Semiconductors (INFOS), Greece, Jun 2007.

P. Srinivasan, B. P. Linder, V. Narayanan and E. Cartier, "Role of soft-optical phonon scattering in aggressively scaled HfO<sub>2</sub> MOSFETs with metal gates: Thickness and temperature dependent mobility studies", Semiconductor Interface Specialists Conference, San Diego, California, Dec 2006.

F. Crupi, P. Srinivasan, P. Magnone, E. Simoen, C. Pace, D. Misra, and C. Claeys, "Impact of the interfacial layer on the low-frequency noise (1/f) behavior of MOSFETs in advanced gate stacks", Workshop on Dielectrics in Microelectronics (WoDIM), Jun 26-28, 2006.

P. Srinivasan, J.-M. Routoure, E. Simoen, C. Claeys, and D. Misra, "Static characteristics of Hf-based silicates at low temperatures", ESA Seventh International Workshop on Low Temperature Electronics (WOLTE), Noordwijk, Netherlands, Jun 2006.

P. Srinivasan, E. Simoen, B. de Jaeger, C. Claeys, and D. Misra, "1/f noise performance of p-MOSFETs with HfO<sub>2</sub> and metal gate on Ge-based substrates", T - Germanium based Semiconductors ... from materials to devices, European – Material Research Society, Nice, France, May-Jun 2006.

P. Srinivasan, E. Simoen, L. Pantisano, C. Claeys, and D. Misra, "1/f noise as a tool to assess Fermi Level pinning (EF) at the HfO2/poly-Si interface in high-k n-MOSFETs", Tenth Int. Symp on Silicon Materials Science and Technology, 209th meeting of Electrochemical Society, Denver, USA, May 7-12, 2006.

(Invited Paper) C. Claeys, E. Simoen, P. Srinivasan and D. Misra, "High- $\kappa$  Gate Stack Engineering and Low Frequency Noise Performance", 209th meeting of Electrochemical Society, Denver, USA, May 7-12, 2006.

E. Simoen, P. Srinivasan, C. Claeys, and D. Misra, "Impact of gate-dielectric interface on the low-frequency noise of thin gate oxide n-channel metal-oxide-semiconductor field-effect-transistors", 7th European Workshop Ultimate Integration of Silicon (ULIS), Grenoble, France, Apr 2006.

P. Srinivasan, E. Simoen, L. Pantisano, C. Claeys, and D. Misra, "Impact of high-k gate stack material with metal gates on LF noise in n- and p-MOSFETs", Extended abstract for Insulating Films on Semiconductors (INFOS), Leuven, Belgium, 20-22 Jun 2005.

P. Srinivasan, E. Simoen, R. Singanamalla, Y. Hong Yu, C. Claeys, and D. Misra, "Gate-dielectric interface effects on low-frequency noise performance in p-MOSFETs with high-k dielectrics", Proceedings of International Semiconductor Device Research Symposium (ISDRS), Washington DC, USA, Dec 2005.

P. Srinivasan, E. Simoen, and C. Claeys, "Channel length and oxide thickness scaling effects on low-frequency (1/f) noise in metal/high-k sub-micron MOSFETs," Proceedings of 8th Annual Workshop on Semiconductor Advances for Future Electronics and SENSORS (SAFE), Veldhoven, Netherlands, Nov 17-18, 2005.

P. Srinivasan, E. Simoen, L. Pantisano, C. Claeys, and D. Misra, "Effect of nitridation on 1/f noise in n-MOSFETs with high- $\kappa$  dielectric," ECS Transactions based on International Symposium on 208th meeting of Electrochemical Society, G3-Third International Symposium on High Dielectric Constant Gate Stacks, Los Angeles, California, USA, Oct 16-21, 2005.

P. Srinivasan, E. Simoen, L. Pantisano, C. Claeys, and D. Misra, "Impact of gate material on low-frequency noise of nMOSFETs with 1.5 nm SiON gate dielectric: testing the limits of the number fluctuations theory," Proceedings of 18th International Conference on Noise and Fluctuations (ICNF), Editors T. Gonzalez, J. Mateos, and D. Pardo, pp. 231-234, Salamanca, Spain, Sep 19-23 2005.

N. A. Chowdhury, P. Srinivasan, D. Misra, and B. H. Lee, "Observation of deep bulk defects using low temperature techniques in TiN/HfSixOy gate stack and their role in BTI and HCS effects", 2nd International Symposium on Advanced Gate Stack Technology, Austin, Texas, Sep 26-28, 2005.

P. Srinivasan, E. Simoen, L. Pantisano, C. Claeys, and D. Misra, "1/f noise performance of nMOSFETs with Hf-based gate dielectrics," Proceedings of the Symposium on Advanced Gate Stack, Source/Drain, and Channel Engineering for Si-Based CMOS: New Materials, Processes, and Equipment, of International Symposium on 207th meeting of Electrochemical Society Meeting, K1-Section III-pp. 151-160, Quebec City, Canada, May 2005.

P. Srinivasan, N. A. Chowdhury, D. Misra, B. H. Lee and R. Choi, "Charge trapping in metal-gate/high-K nMOSFETs during substrate injection," Proceedings of the Symp. on Advanced Gate Stack, Source/Drain, and Channel Engineering for Si-Based CMOS: New Materials, Processes, and Equipment, International Symposium on 207th meeting of Electrochemical Society Meeting, K1-Section V- pp. 366-75, Quebec City, Canada, 15-20 May 2005.

N. A. Chowdhury, P. Srinivasan, D. Misra, "Trapping in Deep Defects under Substrate Hot Electron Stress in TiN/Hf-silicate Based Gate Stacks", Proceedings of International Semiconductor Device Research Symposium (ISDRS), Washington DC, USA, Dec 2005.

N. A. Chowdhury, P. Srinivasan, and D. Misra, "Evidence of deep energy states from low temperature measurements and its role in charge trapping in metal gate/Hfsilicate gate stack," 208th meeting of Electrochemical Society, G3-Third International Symposium on High Dielectric Constant Gate Stacks, Los Angeles, California, USA, Oct 16-21, 2005.

P. Srinivasan, N. A. Chowdhury, and D. Misra, "Study of electrically active traps in high-k dielectrics," Einstein Expo, A Student Research Conference, City College of New York, Apr 11-15, 2005.

(Invited Paper) D. Misra, N. A. Chowdhury, R. Garg, and P. Srinivasan, "Integration of High-K Dielectrics into Sub-65nm CMOS Technology: Requirements and Challenges," Proceedings of the IEEE TENCON 2004, pp. TA11 (1401), Chiang Mai, Thailand, 21-24 November 2004.

P. Srinivasan and D. Misra, "Screening of Hot Electron Effect during Plasma Processing," Graduate Student Research Poster Session, p. 20, NJIT, Newark, USA, Apr 14, 2004.

P. Srinivasan, B. Vootukuru, and D. Misra, "Screening of hot electron effect during plasma processing," Proceedings of the 17th IEEE International Conference on VLSI Design, vol. 17, 2004, pp. 291-296, Mumbai, India, Jan 5-9, 2004.

P. Srinivasan, B. Vootukuru, and D. Misra, "Impact of High Field and Hot Electron Injection on Si-H Bonds at the Si-SiO<sub>2</sub> interface in n-MOSFETs," Poster Session at International Workshop on Physics of Semiconductor Devices (IWPSD), Chennai, India, Dec 16-20, 2003.

P. Srinivasan, B. Vootukuru, and D. Misra, "Screening of Si-H Bonds during Plasma Processing," Proceedings of the International Semiconductor Device Research Symposium (ISDRS), Washington DC, USA, Dec 8-12, 2003.

P. Srinivasan, B. Vootukuru, and D. Misra, "Si-SiO<sub>2</sub> interface behavior in n-MOSFETs with reverse biased voltage during high field and electron injection," Proceedings of International Symposium on 204th Meeting of Electrochemical Society Meeting, Florida, USA, Oct 12-16,2003.

Z. M. Rittersma, E. Simoen, P. Srinivasan, M. Vertregt, and C. Claeys, "Mixed-Signal and Noise Properties of nMOSFETs with HfSiON/TaN Gate Stacks", Proceedings of 35th European Solid-State Device Research Conference, pp. 105-109, Sep. 12-16, 2005, Grenoble, France.

N. A. Chowdhury, P. Srinivasan, W. Mahmood, D. Misra, R. Choi and Byoung Hun Lee, "Charge Trapping Characteristics of TiN/HfSi<sub>x</sub>O<sub>y</sub>/SiO<sub>2</sub>/p-Si MOS Devices under Stress", International Workshop on Electrical Characterization and Reliability for High-K Devices at SEMATECH, p. 61, Austin, Texas, 4-5 Nov 2004.

G. Sudha, P. Srinivasan, and K. Janardanan, Proceedings on International Conference on Medical Diagnostic Techniques and Procedures, IIT Chennai, India. Dec 15-17, pp 122-126, 1999 (Undergraduate research).

To all those, who with their love and support have encouraged me throughout my doctoral studies.

#### ACKNOWLEDGMENT

From the formative stages of this dissertation to the final draft, I owe my thanks and gratitude to my advisor, Dr. Durgamadhab Misra. His sound advice and careful guidance were invaluable during the course of my research for this dissertation. I would like to express my deepest appreciation to my co-advisor Dr. Cor Claeys of IMEC-KUL, for his guidance, constant support and encouragement during my PhD. I would also like to thank Dr. Leonid Tsybeskov, Dr. Marek Sosnowski and Dr. Trevor Tyson, for being part of the dissertation evaluation committee.

This dissertation owes lots of appreciation from members of various countries and locations. I would like to thank Dr. Eddy Simoen, my daily promoter and advisor at IMEC for assisting me throughout my work. His guidance and constant encouragement has always been my motivating force. Thanks to my colleagues and friends at IMEC especially Vaidy and Vidya Subramanian, Jayaprakash Balachandran, Abdel Karim Mercha, Marc Aoulaiche, Sofie Put, Gino Giusi, Gerardo Bottiglieri, Marco, Pieter Blomme, Thomas Kaureauf, Sharon Shamuilia, Brice De Jaeger and others. Special thanks to high-k team members of IMEC especially Dr. Luigi Pantisano, Dr. Vidya Kaushik, Dr. Wim Deweerd and IMEC-Philips/NXP Dr. Z. M. Rittersma and Dr. Yukiko Furukawa.

A warm appreciation to Associate Professor of University of Calabria, Dr. Felice Crupi and Dr. Jean Marc Routoure at GREYC-ENSICAEN, France for their collaboration. I would also like to take this opportunity to thank my colleagues at NJIT -

xii

Naser, Reenu, Nilufa, Amrita and Tias for helping me throughout my dissertation work.

I would like to take this opportunity to thank the high-k team members at IBM T. J. Watson Research Center, Yorktown Heights, NY – Dr. Eduard Cartier, who has been my mentor and providing timely support whenever I am in need of. Special thanks to Dr. Vijay Narayanan, Dr. Barry Paul Linder, Dr. Martin Frank, Dr. Sufi Zafar, Dr. Vamsi Paruchuri and other colleagues at IBM.

I would also like to acknowledge the partial financial support provided by National Science Foundation (Grant No. ECS 0140584) for my course of research in 2004 and 2005. Thanks also to KUL scholarship, Leuven Belgium; Hashimoto and Phonetel Fellowship that I am able complete my dissertation successfully.

My special thanks to my loving brother Pregas Srinivasan for being always with me interms of need. I also owe my special thanks to Mireia Bargallo Gonzalez, who has been always kind and always sharing my thoughts.

Finally my sincere thanks and appreciation to my parents – Mr. Srinivasan and Mrs. Vijayalakshmi, other family members for their constant moral support and help throughout my course of study. Last but not least, I would like to thank God Almighty who has been benevolent and kind and has been one of the guiding forces throughout my studies and life.

#### TABLE OF CONTENTS

| Chapter                                                        | Page |

|----------------------------------------------------------------|------|

| INTRODUCTION.                                                  | 1    |

| 1.1 Requirements for High-к Gate Dielectric                    | 4    |

| 1.1.1 Electrical Requirements for Alternative Gate Dielectrics | 6    |

| 1.1.2 Hf-Based Dielectrics                                     | 9    |

| 1.1.3 Reliability Considerations for Hf-Based Dielectrics      | 10   |

| 1.2 Motivation and Objective                                   | 25   |

| 1.3 Dissertation Organization                                  | 26   |

| OVERVIEW OF NOISE                                              | 29   |

| 2.1 Noise and Noise Sources                                    | 30   |

| 2.1.1 Thermal Noise                                            | 30   |

| 2.1.2 Shot Noise                                               | 34   |

| 2.1.3 Generation-Recombination Noise                           | 36   |

| 2.1.4 Flicker or 1/f Noise                                     | 36   |

| 2.2 Low-Frequency Noise                                        | 37   |

| 2.2.1 Low-Frequency Noise in Frequency Domain                  | 37   |

| 2.2.2 Low-Frequency Noise in Time Domain                       | 39   |

| 2.3 Low-Frequency Noise Parameters                             | 39   |

| 2.3.1 Drain Current Noise Spectral Density                     | 39   |

#### TABLE OF CONTENTS (Continued)

| С | Chapter H |                                                                                                           | Page |

|---|-----------|-----------------------------------------------------------------------------------------------------------|------|

|   |           | 2.3.2 Input-referred Noise Spectral Density                                                               | 41   |

|   | 2.4       | 1/f Noise Mechanisms in MOSFETs                                                                           | 44   |

|   |           | 2.4.1 Number Fluctuation Theory – ΔN Model                                                                | 44   |

|   |           | 2.4.2 Mobility Fluctuation Theory – $\Delta\mu$ Model                                                     | 51   |

|   |           | 2.5.3 Number-Mobility Correlated Theory – $\Delta N - \Delta \mu$ Model                                   | 53   |

| 3 | NO        | ISE IN HIGH-K BASED MOSFETS                                                                               | 56   |

|   | 3.1       | Noise in High-K Based Dielectrics                                                                         | 56   |

|   |           | 3.1.1 Introduction                                                                                        | 56   |

|   |           | 3.1.2 Literature Study and Review                                                                         | 56   |

|   |           | 3.1.3 Interfacial Layer Effects in NMOSFETs                                                               | 59   |

|   | 3.2       | 1/f Noise in La <sub>2</sub> O <sub>3</sub> Based Systems                                                 | 63   |

|   | 3.3       | 1/f Noise in Al <sub>2</sub> O <sub>3</sub> and HfO <sub>2</sub> / Al <sub>2</sub> O <sub>3</sub> Systems | 64   |

|   | 3.4       | Temperature Dependence of 1/f Noise                                                                       | 66   |

| 4 | TE        | CHNOLOGICAL AND EXPERIMENTAL ASPECTS                                                                      | 68   |

|   | 4.1       | Noise Characterization and Setup                                                                          | 68   |

|   |           | 4.1.1 Noise Characterization Setup at High and Room Temperatures                                          | 68   |

|   |           | 4.1.2 Low-Frequency Noise Measurement Setup at Low Temperatures                                           | 70   |

|   | 4.2       | Gate Dielectric and Gate Electrode Deposition Techniques                                                  | 74   |

|   |           | 4.2.1 Deposition of High-κ Gate Dielectric                                                                | 74   |

|   |           | 4.2.2 Deposition of Gate Electrode Material                                                               | 77   |

## TABLE OF CONTENTS (Continued)

| C | hapter                                                                      | Page |

|---|-----------------------------------------------------------------------------|------|

|   | 4.3 Gate Capacitance and EOT Determination                                  | 78   |

| 5 | 1/F NOISE PERFORMANCE OF ADVANCED HIGH-K GATE STACKS                        | 81   |

|   | 5.1 Interfacial Layer Effect                                                | 82   |

|   | 5.1.1 Interfacial Layer Thickness Effects in HfO <sub>2</sub> /TaN NMOSFETs | 82   |

|   | 5.1.2 Interfacial Layer Thickness Effects in PMOSFETs                       | 85   |

|   | 5.1.3 Interfacial Layer Quality Effects in PMOSFETs                         | 88   |

|   | 5.2 Interfacial Layer Treatment – Nitridation Effects                       | 91   |

|   | 5.2.1 Pre-and Post- Deposition Conditions                                   | 91   |

|   | 5.2.2 Non-Nitrided Interface and Post-Deposition-Anneals in NMOSFETs        | 96   |

|   | 5.2.3 Nitrided Interface and Post-Deposition-Anneals in NMOSFETs            | 98   |

|   | 5.2.4 Non-Nitrided Interface and Post-Deposition-Anneals in PMOSFETs        | 100  |

|   | 5.2.5 Trap Profiles of Nitrided and Non-Nitrided Interface NMOSFETs         | 102  |

|   | 5.2.6 Nitrogen Induced Oxygen Defect Centers                                | 103  |

|   | 5.2.7 Trap Density Estimation                                               | 106  |

|   | 5.3 High-к Layer Effects                                                    | 108  |

|   | 5.3.1 High-к Oxide Thickness                                                | 108  |

|   | 5.3.2 κ-Value Effects                                                       | 110  |

# TABLE OF CONTENTS (Continued)

| Ch | apter                                                             | Page  |

|----|-------------------------------------------------------------------|-------|

|    | 5.4 Gate Electrode Effects                                        | 112   |

|    | 5.4.1 Gate Electrode Material in p-MOSFETs (Poly/Metal/FUSI)      | 112   |

|    | 5.4.2 Comparison in n- and p-MOSFETs Poly-Si Vs TiN-TaN           | 124   |

|    | 5.4.3 Gate Electrode Processing Effects - ALD Vs PVD              | 127   |

| :  | 5.5 Noise Mechanism Study in Hf-Based MOSFETs                     | 129   |

|    | 5.5.1 Poly-Si Gate Electrodes                                     | 129   |

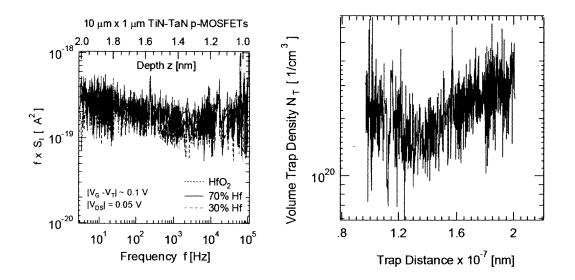

|    | 5.5.2 Metal (TiN-TaN) Gate Electrodes                             | 133   |

| -  | 5.6 Gate/High-κ Interface                                         | 136   |

|    | 5.6.1 Gate/High-к Interface Treatment                             | 136   |

|    | 5.6.2 Fermi-Level Pinning Effects – Poly-Si Vs FUSI               | 137   |

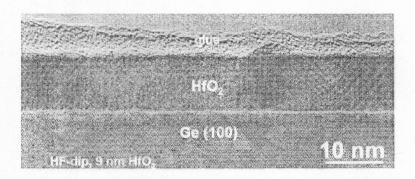

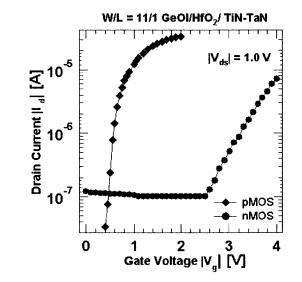

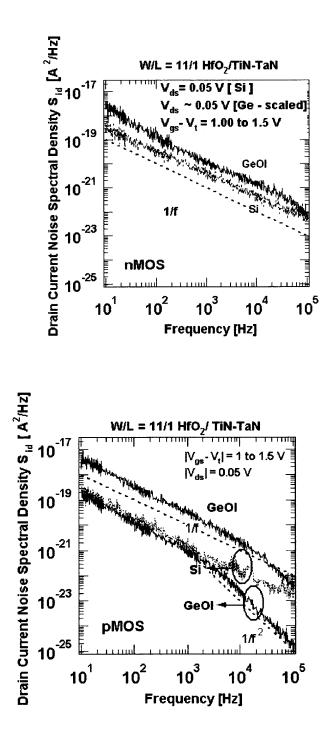

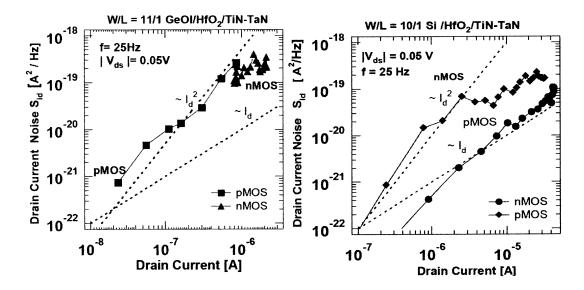

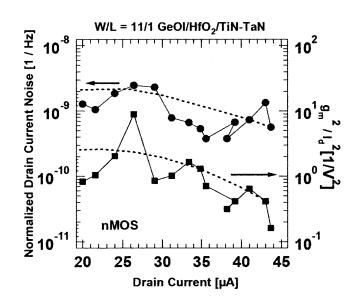

| :  | 5.7 Substrate Effects – Si Vs GeOI                                | 146   |

| :  | 5.8 Temperature Effects                                           | 155   |

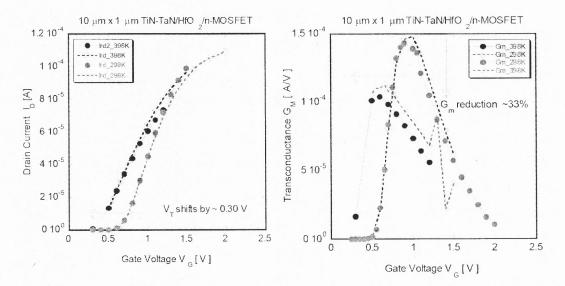

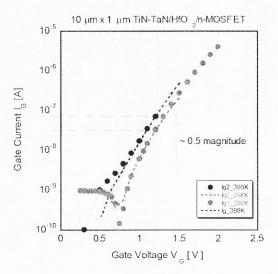

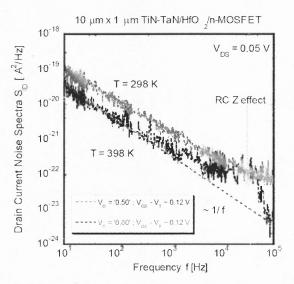

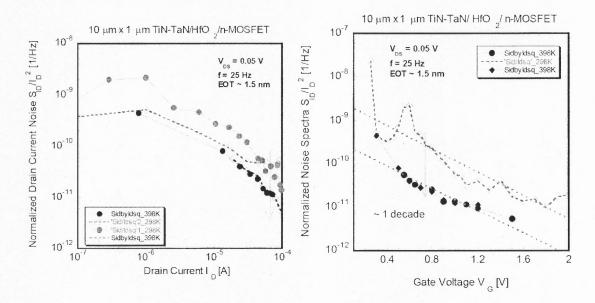

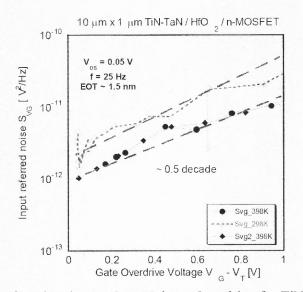

|    | 5.8.1 Effects of High Temperature on 1/f Noise                    | 155   |

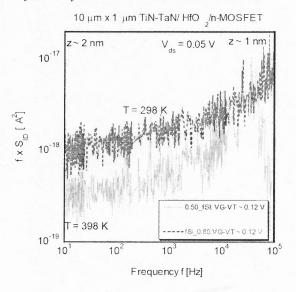

|    | 5.8.2 Effect of High-Temperature on HfO <sub>2</sub> n-MOSFETs    | 156   |

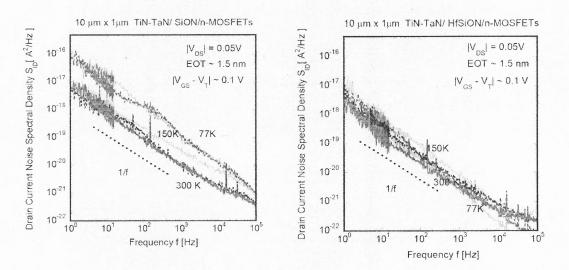

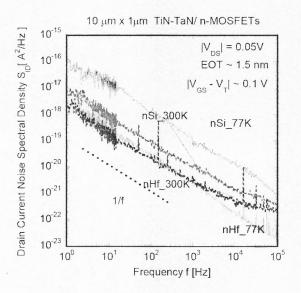

|    | 5.8.3 Effect of Low Temperature 1/f Noise                         | 161   |

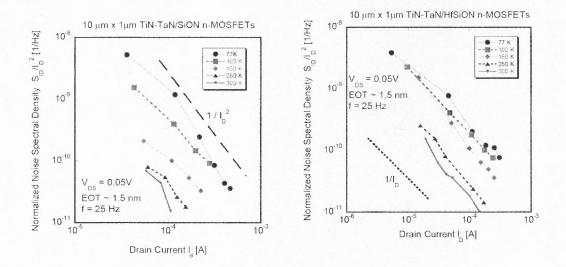

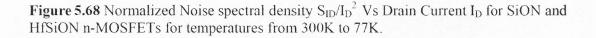

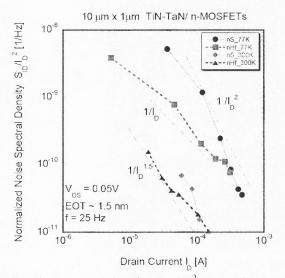

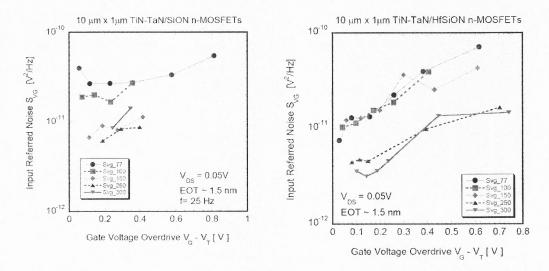

|    | 5.8.4 Low-Temperature 1/f noise in SiON and Hf-Silicate n-MOSFETs | 161   |

|    | 5.8.5 Low-Temperature 1/f noise in SiON and Hf-Silicate p-MOSFETs | 167   |

|    | 5.8.6 Guidelines for reduced 1/f noise in future CMOS devices     | . 172 |

## TABLE OF CONTENTS (Continued)

| С | hapter                                                                              | Page |

|---|-------------------------------------------------------------------------------------|------|

| 6 | NOISE MECHANISMS AND MODELING                                                       | 173  |

|   | 6.1 Limits of Noise Mechanism in Thin Gate SiON MOSFETs                             | 173  |

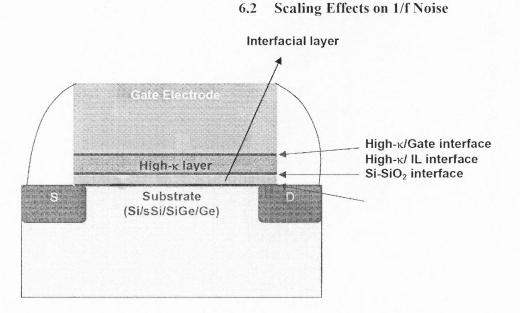

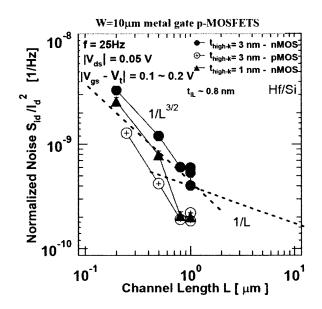

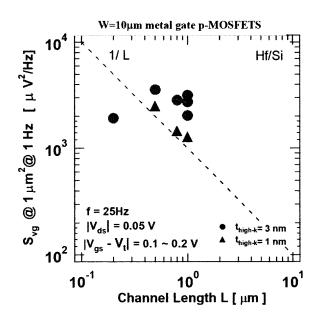

|   | 6.2 Scaling Effects on 1/f Noise                                                    | 176  |

|   | 6.2.1 Oxide Thickness Dependence                                                    | 178  |

|   | 6.2.2 Area Dependence W X L                                                         | 181  |

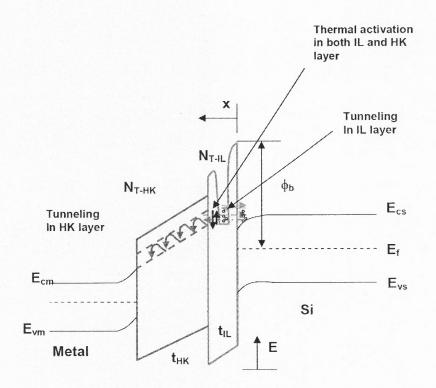

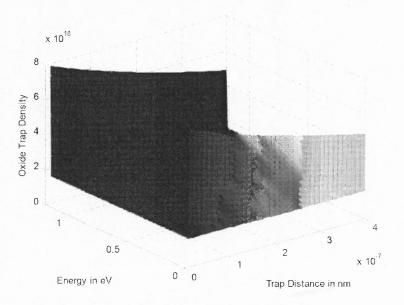

|   | 6.3 Drain Current Noise Model for High-κ Dielectrics in n-MOSFETs                   | 186  |

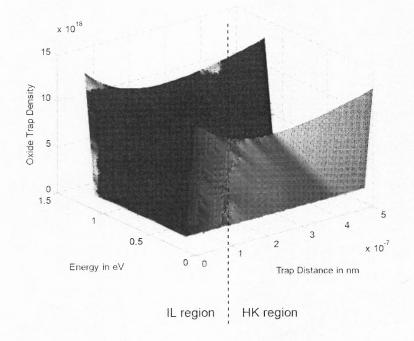

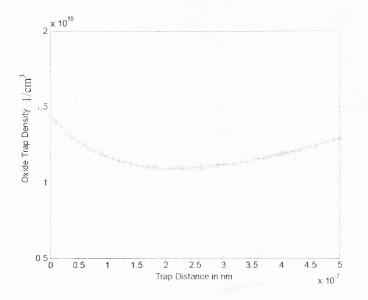

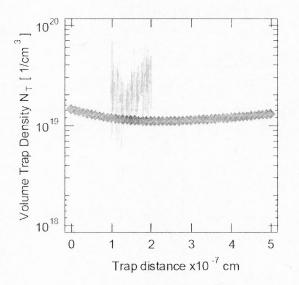

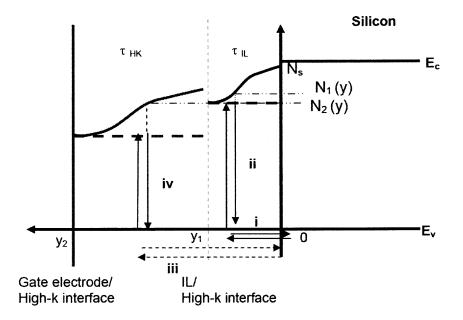

|   | 6.3.1 Trap Density Profiles for Hf-Based Dielectrics                                | 186  |

|   | 6.3.2 Formulation of $1/f$ Drain Current Noise Model for High- $\kappa$ Dielectrics | 192  |

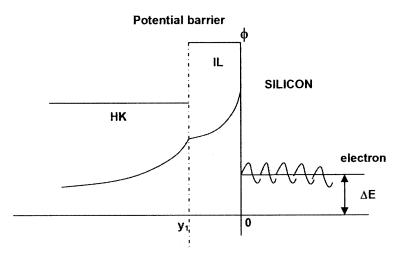

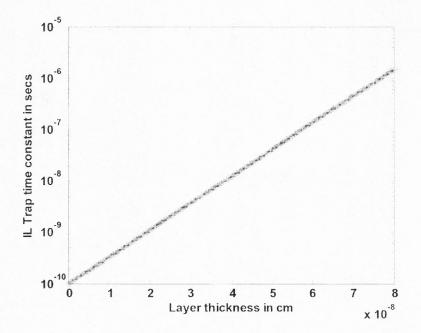

|   | 6.3.3 Approximation for Noise Model for Number Theory                               | 203  |

|   | 6.3.4 Validation of 1/f Drain Current Noise Model for High-κ Dielectrics            | 204  |

| 7 | SUMMARY AND FUTURE OUTLOOK                                                          | 208  |

|   | 7.1 Summary                                                                         | 208  |

|   | 7.2 Recommendation for Future Work                                                  | 209  |

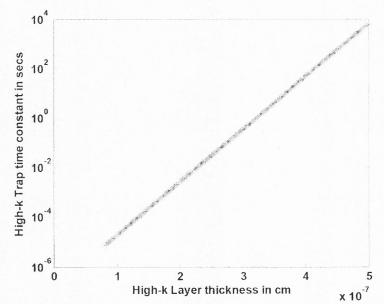

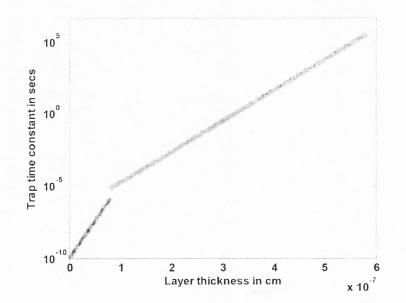

| A | PPENDIX ESTIMATION OF TRAP TIME CONSTANTS                                           | 211  |

| R | EFERENCES                                                                           | 220  |

#### LIST OF TABLES

| Table | P                                                                                                                                                                                                                                                                                                                   | age   |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 1.1   | Material Properties to be Considered as an Alternative to the Present Gate Dielectric SiO <sub>2</sub>                                                                                                                                                                                                              | 6     |

| 1.2   | Mixed-Signal Technology Requirements of a MOSFET Device [7]                                                                                                                                                                                                                                                         | 8     |

| 5.1   | CMOS Fabrication Flow Showing Important Process Steps Required for Nitrided and Non-nitrided Interface n-MOSFETs                                                                                                                                                                                                    | 93    |

| 5.2   | Device and Noise Parameter Values for the Different Nitrided and<br>Non-nitrided Interface n-MOSFET and p-MOSFET Devices Studied                                                                                                                                                                                    | 94    |

| 5.4   | Estimated EOT Values, Physical Thickness and Tunneling Depths of the<br>Devices Studied for Comparison of Gate Electrodes with Dielectrics of<br>Various Composition                                                                                                                                                | 113   |

| 5.5   | Noise Parameters and Estimated Trap Densities for FUSI Gate Devices with Different Hf-percentages of High-κ Dielectric.                                                                                                                                                                                             |       |

| 5.6   | Comparison of Volume $(N_T)$ and Surface Trap Densities $(D_T)$ as Figure of Merit for Various Gate Stack Compositions for n-channel poly-Si and Metal gate (PVD and ALD gate electrode) Devices                                                                                                                    | 129   |

| 5.7   | Comparison of Interfacial Layer Thickness (IL), Input Referred Noise PSD ( $S_{VG}$ ), Volume ( $N_T$ ) and Surface Trap ( $D_T$ ) Densities for n- and pMOS devices on GeOI and Si substrates. Comparison of Results Obtained from Charge Pumping (CP) and Noise Measurements are Also Shown for n- and pMOS GeOI. | . 154 |

| 6.1   | Low-frequency Noise Dependence on Device Parameters                                                                                                                                                                                                                                                                 | 177   |

| 6.2   | Fitting Parameters for Tunneling Constant and Trap Densities Used for High<br>and Interfacial Layer at Various Trap Locations                                                                                                                                                                                       |       |

#### LIST OF FIGURES

| Chapte | er                                                                                                                                                                                                                                                                                                                                                                                                      | Page |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

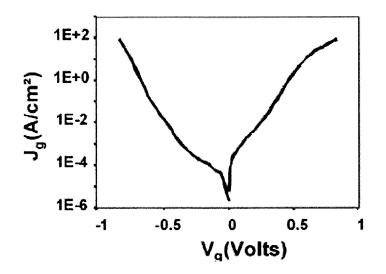

| 1.1    | Gate current leakage for a 0.8nm oxide for the 30nm transistor                                                                                                                                                                                                                                                                                                                                          | 2    |

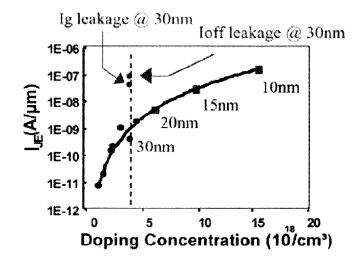

| 1.2    | Junction leakage vs doping concentration of the substrate. Circles represent data points. Squares represent extrapolated points for future technology nodes. source:[6]                                                                                                                                                                                                                                 |      |

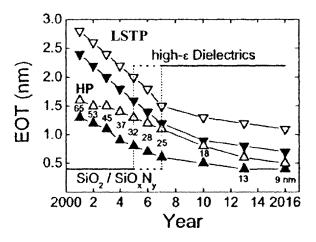

| 1.3    | Equivalent Oxide Thickness (EOT) versus year of introduction for both.<br>High-Performance (HP) and Low Standby-Power (LSTP) technologies. For<br>comparison the minimum (solid symbols) and maximum (open symbols)<br>EOT is shown for each technology generation. The year of introduction for<br>high- $\kappa$ dielectrics indicated between 2005 and 2007<br>source:[7].                           |      |

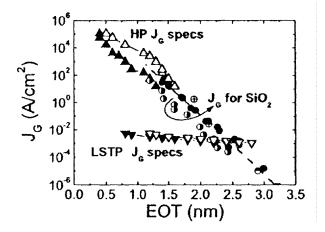

| 1.4    | Gate leakage current specification versus EOT for High-Performance and Low-Standby-Power technologies as per ITRS 2005 specifications. The same symbols for the minimum and maximum EOT are used as in Figure 1.3. Experimental data for SiO <sub>2</sub> from different companies are included to demonstrate the necessity for high-k dielectrics for LSP technologies in the near future. source:[7] |      |

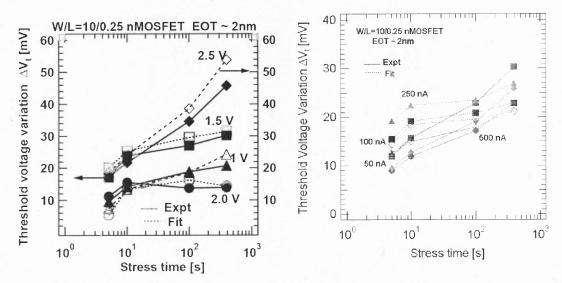

| 1.5    | Change in threshold voltage ( $\Delta Vt$ ) vs. Stress time during CVS. (b) Change<br>in threshold voltage ( $\Delta Vt$ ) Vs. Stress time during CCS. Thick lines are<br>experimental data and dotted lines indicate model fit. Filled symbols<br>indicate the data obtained from the experiment while the open symbols were<br>obtained from the equation                                             |      |

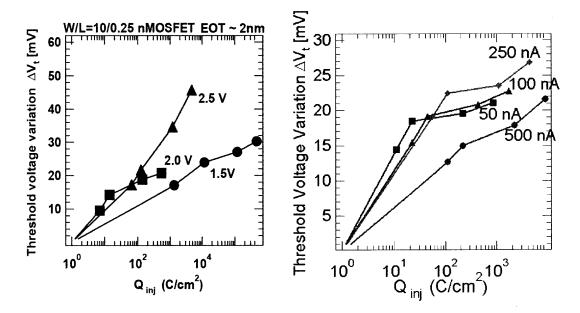

| 1.6    | (a) Injected charge $Q_{inj}$ Vs. Change in threshold voltage $(\Delta V_t)$ for applied CVS. (b)) Injected charge $Q_{inj}$ Vs. Change in threshold voltage $(\Delta V_t)$ for applied CCS.                                                                                                                                                                                                            |      |

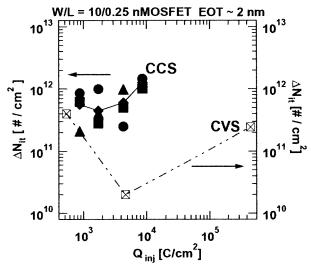

| 1.7    | Change in interface trap density $\Delta N_{it}$ calculated using FACP during CCS (1° Y-axis) and CVS (2°-axis) before and after CVS                                                                                                                                                                                                                                                                    | 15   |

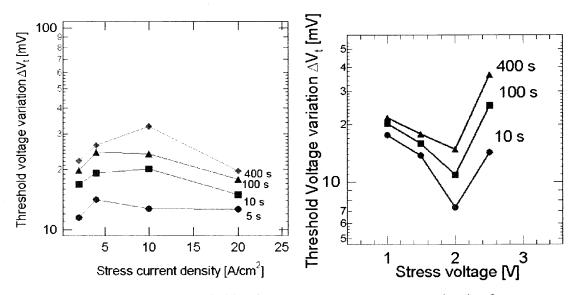

| 1.8    | (a) Change in threshold voltage ( $\Delta Vt$ ) Vs stress current density for constant stress times during CCS. (b) Change in threshold voltage ( $\Delta Vt$ ) versus stress voltage for constant stress times during CVS. A turn-around effect is noticed at higher values in both cases.                                                                                                             | 16   |

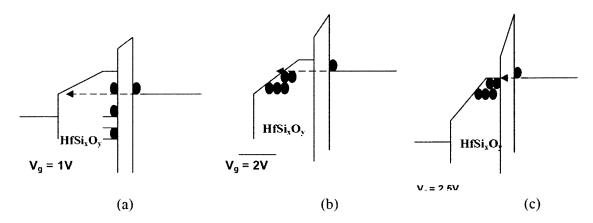

| 1.9    | Band bending induces interface traps at $HfSi_xO_y/SiO_2$ interface to be filled.<br>(b). Shallow traps towards $TiN/HfSi_xO_y$ interface are filled due to band alignment. (c). Shallow traps near $HfSi_xO_y/SiO_2$ interface are filled during stress.                                                                                                                                               | 16   |

#### Chapter

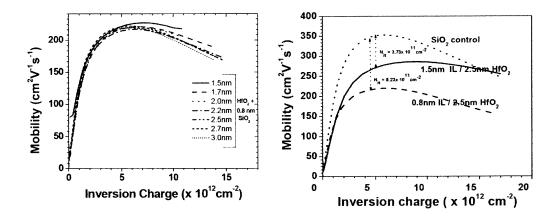

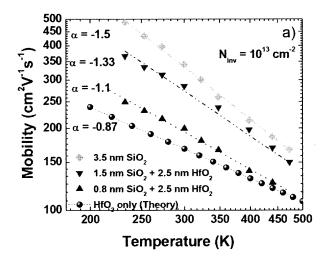

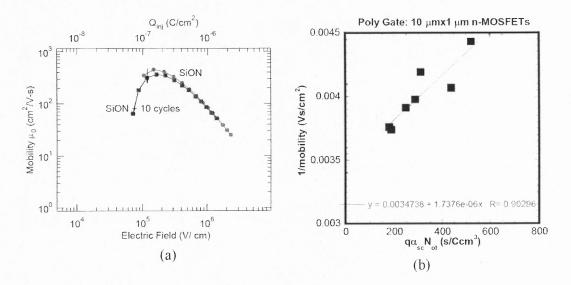

| 1.10 | (a) Mobility Vs Inversion Charge for different HfO <sub>2</sub> thickness thickness studied for 10 x 10 $\mu$ m <sup>2</sup> TiN/HfO <sub>2</sub> /n-MOSFETs. (b) Mobility Vs Inversion Charge for different interfacial thickness studied for 10 x 10 $\mu$ m <sup>2</sup> TiN/HfO <sub>2</sub> /n-MOSFETs | 20 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

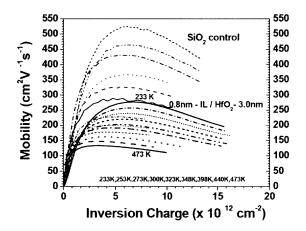

| 1.11 | Mobility Vs Inversion Charge at different temperatures for 0.8nm IL/3.0 nm $HfO_2 10 \times 10 \ \mu m^2 TiN/HfO_2/n-MOSFETs$ . SiON control device is plotted as a reference in all these cases                                                                                                            | 21 |

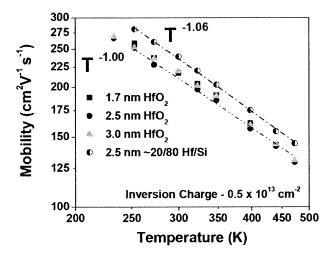

| 1.12 | Temperature acceleration factor – Mobility Vs Temperature for (a) different $HfO_2$ thickness studied for 10 x 10 $\mu$ m <sup>2</sup> TiN/HfO <sub>2</sub> /n-MOSFETs. A 20/80 – $Hf/Si$ is also used for comparison purpose                                                                               | 22 |

| 1.13 | Temperature acceleration factor – Mobility Vs Temperature for different IL thickness studied for 10 x 10 $\mu$ m <sup>2</sup> TiN/HfO <sub>2</sub> /n-MOSFETs. A 20/80 – Hf/Si is also used for comparison purpose.                                                                                         | 22 |

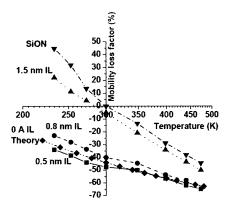

| 1.14 | Mobility loss factor Vs Temperature and factor Vs Inversion charge for different interfacial layer thickness studied for TiN/HfO <sub>2</sub> /n-MOSFETs                                                                                                                                                    | 23 |

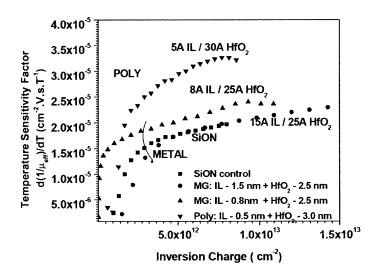

| 1.15 | Temperature sensitivity factor Vs Inversion charge for different interfacial layer thickness studied for TiN/HfO <sub>2</sub> /n-MOSFETs                                                                                                                                                                    | 29 |

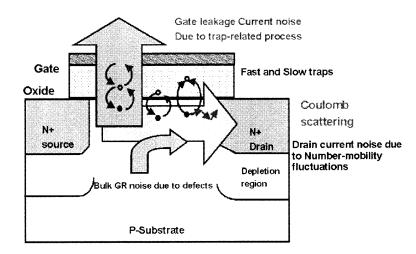

| 2.1  | Noise sources in a MOSFET                                                                                                                                                                                                                                                                                   | 23 |

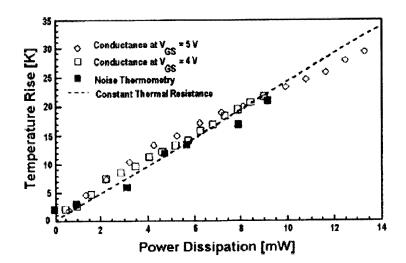

| 2.2  | Extracted parameters from small signal conductance measurements at different bias points, plotted as local device temperature rise vs. power dissipation. source: [36]                                                                                                                                      | 32 |

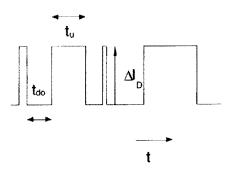

| 2.3  | Definition of the RTS parameters in the time domain                                                                                                                                                                                                                                                         | 34 |

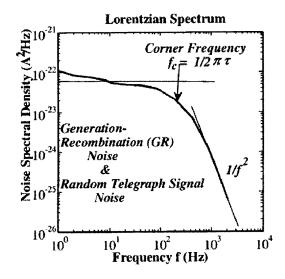

| 2.4  | Illustration of a Lorentzian spectrum corresponding to a G-R noise                                                                                                                                                                                                                                          | 36 |

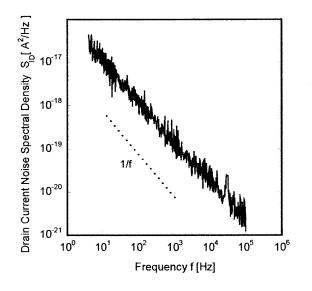

| 2.5  | A typical noise power spectrum                                                                                                                                                                                                                                                                              | 38 |

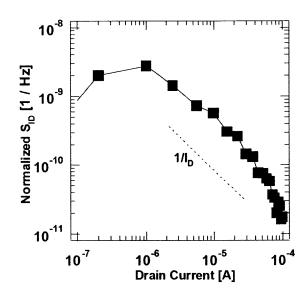

| 2.6  | Normalized drain current spectral density $S_{ID}/I_D^2$ [1/Hz] Vs Drain Current $I_D$ [A] for a typical n-MOSFET                                                                                                                                                                                           | 40 |

| Chapt | ter                                                                                                                                                                                                                                                   | Page |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

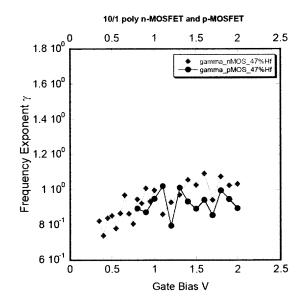

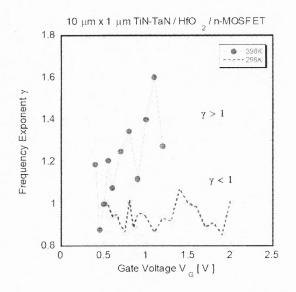

| 2.7   | Frequency Exponent $\gamma$ variation with applied gate bias                                                                                                                                                                                          | 41   |

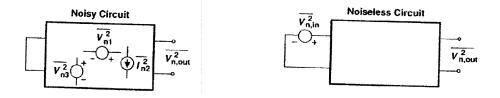

| 2.8   | Determination of input-referred noise voltage at circuit level                                                                                                                                                                                        | 42   |

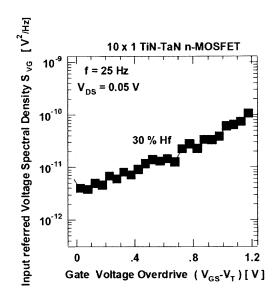

| 2.9   | A typical input referred noise plot for a given noise mechanism                                                                                                                                                                                       | 43   |

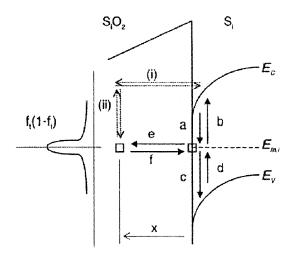

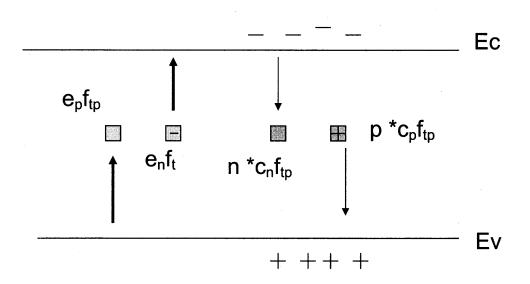

| 2.10  | Capture and tunneling model based on number fluctuation theory. The arrows indicate the possible electron transitions. source: [48]                                                                                                                   | 46   |

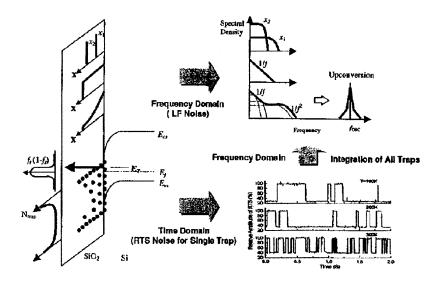

| 2.11  | Noise spectrum and trap distribution in MOS structure in time and frequency domain based on number fluctuation theory                                                                                                                                 | 47   |

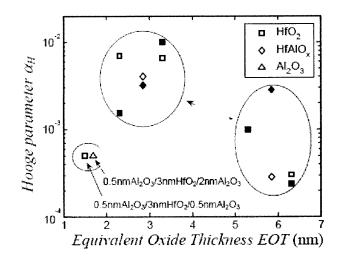

| 3.1   | Reported trap densities in the literature for different high- $\kappa$ materials plotted vs. EOT. Filled symbols denote n-MOSFET, open symbols p-MOSFET.source:[62]                                                                                   | 57   |

| 3.2   | A summary of reported values of $\alpha_H$ plotted versus EOT. Filled symbols denote n-MOSFET and open symbols p-MOSFET, respectively. source:[62]                                                                                                    | 58   |

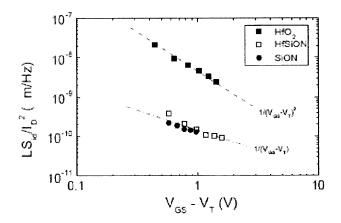

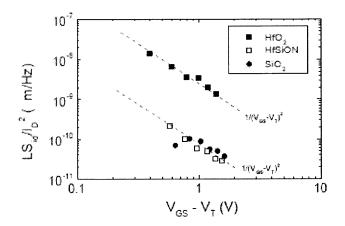

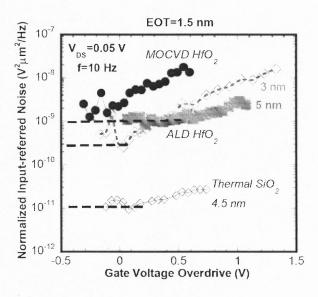

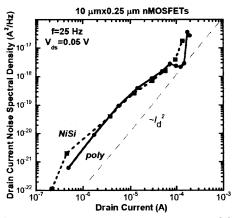

| 3.3   | Normalized noise data with HfO <sub>2</sub> L = 0.25 $\mu$ m, HfSiON L = 0.25 $\mu$ m and SiO <sub>2</sub> , L = 0.20 $\mu$ m. source:[63]                                                                                                            | 58   |

| 3.4   | Normalized noise data with HfO <sub>2</sub> L = 1 $\mu$ m, HfSiON L = 1 $\mu$ m and SiON L = 1 $\mu$ m. source:[63]                                                                                                                                   | 59   |

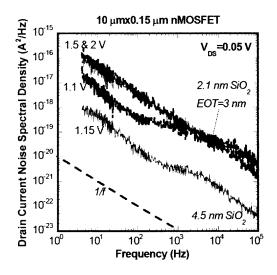

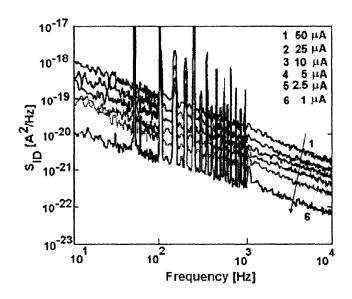

| 3.5   | Low frequency drain current noise spectra at $V_{DS} = 0.05$ V for two different interfacial layer thicknesses studied. source:[61]                                                                                                                   | 60   |

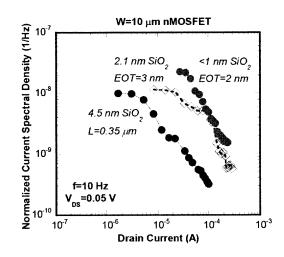

| 3.6   | Normalized current spectral density versus $I_D$ for an n-MOSFET with 5 nm ALD HfO <sub>2</sub> and of three different interface layer thickness, at f=10 Hz and $V_{DS}$ =0.05 V. source:[61]                                                        | 61   |

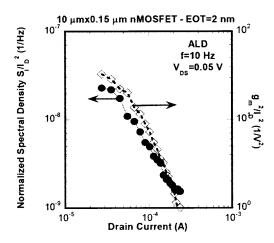

| 3.7   | $S_I/I_D^2$ vs $I_D$ for an L=150 nm n-MOSFET with an EOT=2 nm (HfO <sub>2</sub> by ALD). source:[61]                                                                                                                                                 | 61   |

| 3.8   | Normalized input-referred voltage noise spectral density versus gate voltage overdrive for ALD n-MOSFETs with two different interfacial layer thickness in comparison with 4.5 nm SiO <sub>2</sub> device. f=10 Hz and $V_{DS}$ =0.05 V. source:[61]. | 62   |

#### LIST OF FIGURES

#### (Continued)

| Chapt | Chapter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.9   | Low frequency noise performance of a 27 $\mu$ m/2.5 $\mu$ m n-MOSFET La <sub>2</sub> O <sub>3</sub> device. source:[64]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 63 |

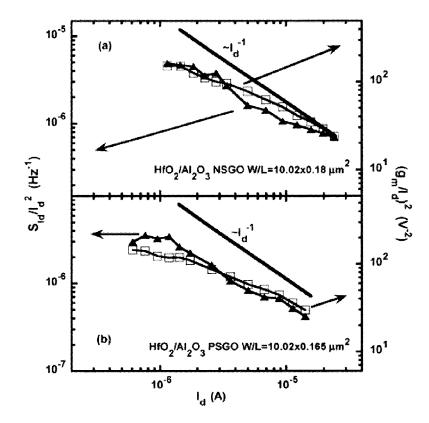

| 3.10  | Comparison of drain-current-normalized drain-current noise spectral density at 1 Hz and transconductance. The solid straight line depicts 1=I dependence for each case. $V_{DS} = 40$ mV. source:[65]                                                                                                                                                                                                                                                                                                                                                                                                                          | 64 |

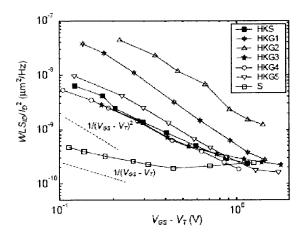

| 3.11  | Normalized drain current noise at 10 Hz vs. gate voltage overdrive. $V_{DS} = 1$ mV. W × L = 10 µm × 0.8 µm. HKS refers to $Al_2O_3/HfAlO_x/Al_2O_3$ (0.5/4/0.5 nm), HKG1 refers to $Al_2O_3$ (5 nm) $Si_{0.8}Ge_{0.2}$ (10 nm) 3.2 nm , HKG2 $Al_2O_3$ (5 nm) $Si_{0.7}Ge_{0.3}$ (10 nm) 3.4 nm, HKG3 refers to $Al_2O_3/HfAlO_x/Al_2O_3$ (0.5/4/0.5 nm) $Si_{0.8}Ge_{0.2}$ (10 nm) 2.4 nm, HKG4 $Al_2O_3/HfAlO_x/Al_2O_3$ (0.5/4/0.5 nm) $Si_{0.7}Ge_{0.3}$ (10 nm) 2.7 nm, HKG5 refers to $Al_2O_3/HfAlO_x/Al_2O_3$ (0.5/4/0.5 nm) $Si_{0.7}Ge_{0.3}$ (10 nm) 2.2 nm, while S refers to $SiO_2$ (3 nm) Si 3 nm. source:[62] | 65 |

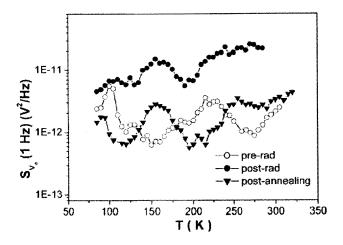

| 3.12  | The noise magnitude at 1 Hz versus temperature for $SiO_2$ before irradiation (open circles), after 10-keV X-ray irradiation to 500 krad ( $SiO_2$ ) (solid circles), and after a 24 h anneal at 477 K at 0 V (solid triangles). source:[66]                                                                                                                                                                                                                                                                                                                                                                                   | 67 |

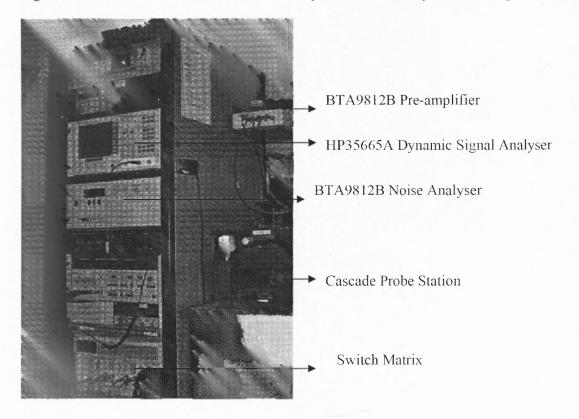

| 4.1   | Wafer-level low-frequency noise characterization system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 68 |

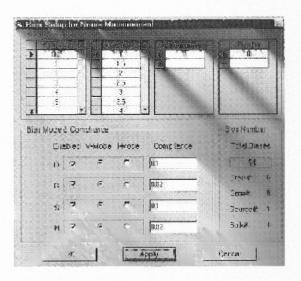

| 4.2   | Voltage bias setup screen using NoisePro software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 70 |

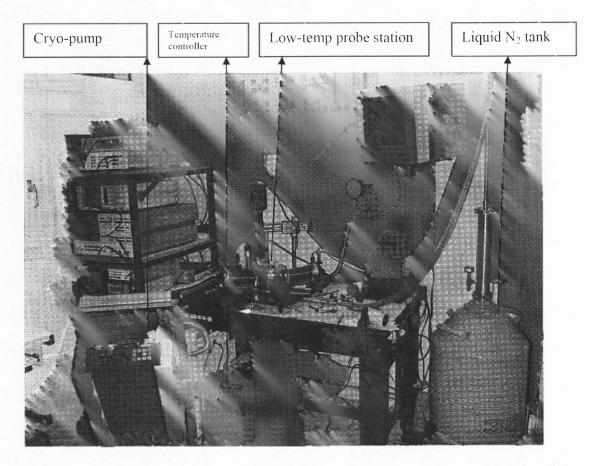

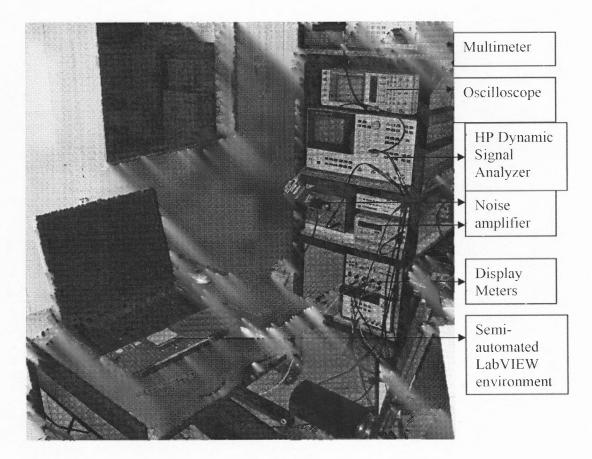

| 4.3   | Low-temperature low-frequency noise characterization system showing the cryo-setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 71 |

| 4.4   | Low-temperature low-frequency noise characterization system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 72 |

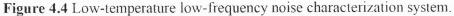

| 4.5   | Low frequency C-V plots to extract gate capacitance and EOT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 79 |

| 5.1   | Drain current and transconductance vs gate voltage for different IL thickness of n-MOSFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 82 |

| 5.2   | Normalized drain current noise spectral density vs. gate voltage overdrive for two different IL thicknesses for n-MOSFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 83 |

Page

| Chapt | ter                                                                                                                                                                                                                                                                    | Page |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 5.3   | Input-referred noise vs. gate voltage overdrive for two different IL thicknesses for n-MOSFET                                                                                                                                                                          | 83   |

| 5.4   | Hooge's parameter vs. gate voltage overdrive for two different IL thicknesses for n-MOSFET.                                                                                                                                                                            | 84   |

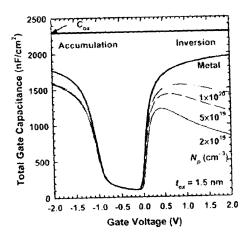

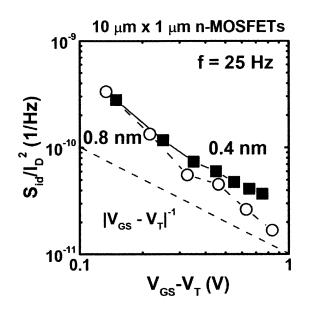

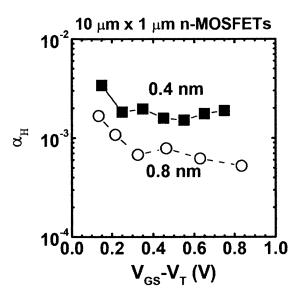

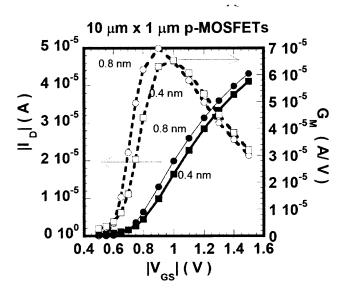

| 5.5   | Device characteristics of 0.4nm and 0.8nm interfacial layer and 2nm of $HfO_2$ dielectric oxides at $ V_{DS}  = 0.05 V$                                                                                                                                                | 85   |

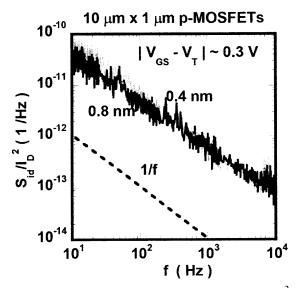

| 5.6   | Drain current noise spectral density $S_{ID}$ Vs Frequency f [Hz] for 0.4nm and 0.8nm IL oxides                                                                                                                                                                        | 86   |

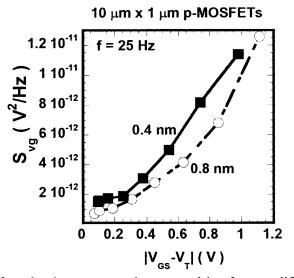

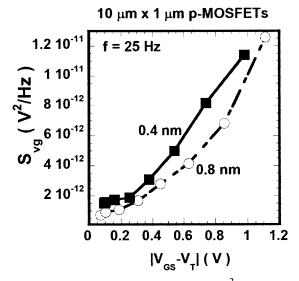

| 5.7   | Input referred noise spectral density $S_{VG}$ [V <sup>2</sup> /Hz] Vs gate voltage overdrive (V <sub>GS</sub> -V <sub>T</sub> ) [V] for two different IL thicknesses for p-MOSFETs                                                                                    | 87   |

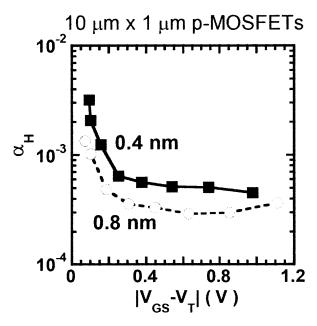

| 5.8   | Hooge's parameter Vs. Gate Voltage Overdrive $(V_{GS}-V_T)$ [V] for two different IL thicknesses for pMOSFETs                                                                                                                                                          | 88   |

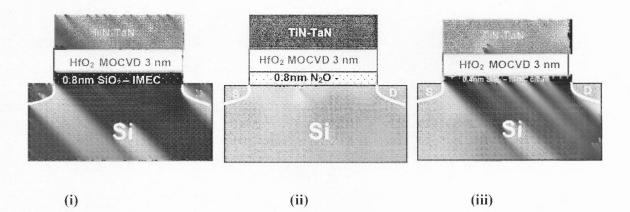

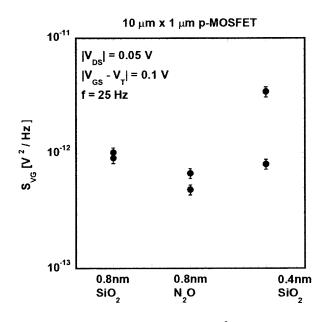

| 5.9   | Three different interfacial layers studied – $0.8$ nm thermal SiO <sub>2</sub> , $0.8$ nm N <sub>2</sub> O and $0.4$ nm SiO <sub>2</sub>                                                                                                                               | 89   |

| 5.10  | Normalized current spectral density versus $I_D$ for a pMOSFET with 5 nm ALD HfO <sub>2</sub> and of three different interface layers, at f=10 Hz and $ V_{DS} =0.05V$                                                                                                 | 89   |

| 5.11  | Input referred noise spectral density $S_{VG}$ [V <sup>2</sup> /Hz] Vs gate voltage overdrive $ V_{GS}-V_T $ [V] for three different IL for p-MOSFETs                                                                                                                  | 90   |

| 5.12  | Input referred noise spectral density $S_{VG}$ [V <sup>2</sup> /Hz] Vs three different IL for p-MOSFETs at $ V_{GS}-V_T  \sim 0.1$ V and $ V_{DS}  \sim 0.05$ V and f =25 Hz                                                                                           | 91   |

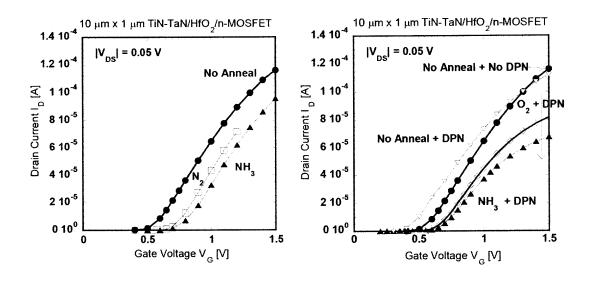

| 5.13  | Device transfer characteristics $I_D$ - $V_G$ for (a) non-nitrided interface and (b) for nitrided interface devices, with different post deposition anneals for n-MOSFETs (c) for non-nitrided interface devices, with different post deposition anneals for p-MOSFETs | 96   |

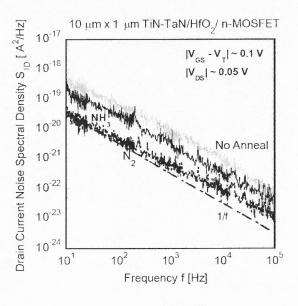

| 5.14  | Drain Current Noise Spectral Density $S_{ID}$ [A <sup>2</sup> /Hz] Vs Frequency f [Hz] for HfO <sub>2</sub> devices with different (PDA) post deposition anneals for n-MOSFETs.                                                                                        | 96   |

## Chapter

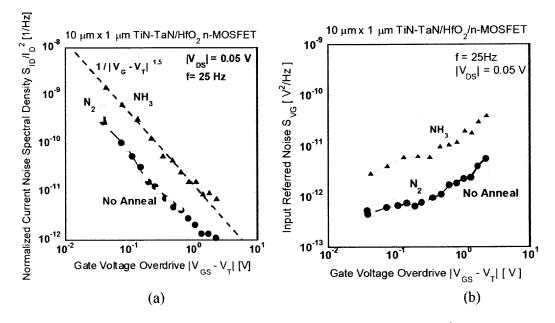

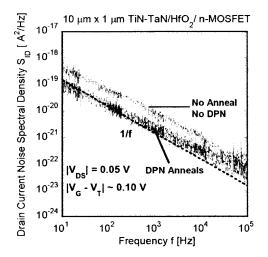

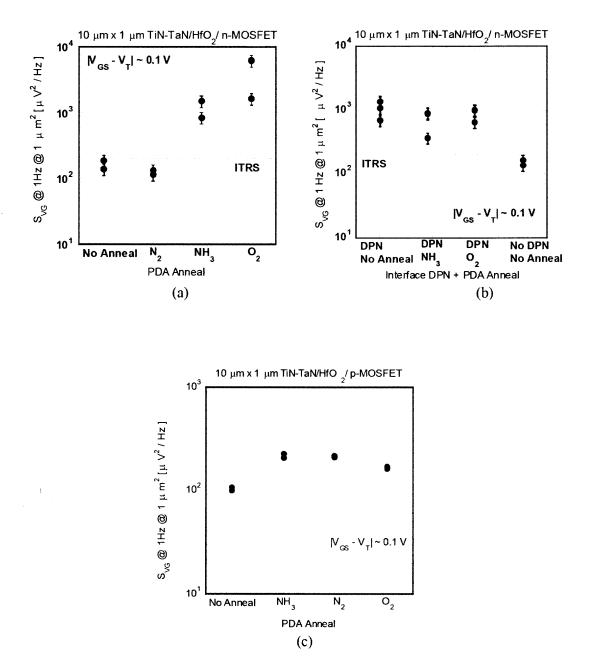

| 5.15 | (a) Normalized Drain Current Noise Spectral Density $S_{ID}/I_D^2$ [1/Hz] Vs Gate Voltage Overdrive $ V_{GS} - V_T $ [V] for non-nitrided interface devices with different post deposition anneals for n-MOSFETs. Figure 5.15(b) Input-referred noise $S_{VG}$ [V <sup>2</sup> /Hz] Vs Gate Voltage Overdrive $V_{GS} - V_T$ [V] for non-nitrided interface devices with different post deposition anneals for n-MOSFETs.  | 97  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

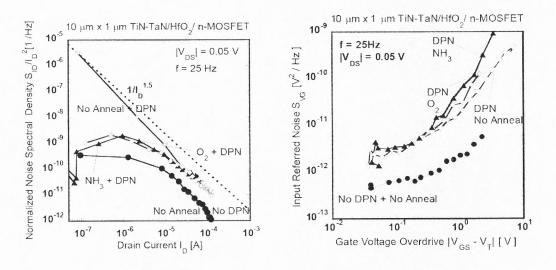

| 5.16 | Drain Current Noise Spectral Density $S_{ID}$ [A <sup>2</sup> /Hz] Vs Frequency f [Hz] for nitrided interface devices with different post deposition anneals for n-MOSFETs                                                                                                                                                                                                                                                 | 98  |

| 5.17 | (a) Normalized Drain Current Noise Spectral Density $S_{ID}/I_D^2$ [1/Hz] Vs Drain Current $I_D$ [A] for nitrided interface devices with different post deposition anneals for n-MOSFETs. Figure 5.17(b) Input-referred noise $S_{VG}$ [V <sup>2</sup> /Hz] Vs Gate Voltage Overdrive  V <sub>GS</sub> - V <sub>T</sub>   [V] for non-nitrided interface devices with different post deposition anneals for n-MOSFETs.     | 99  |

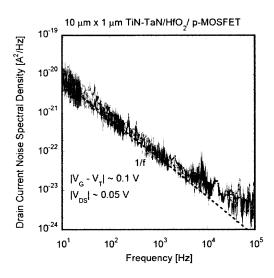

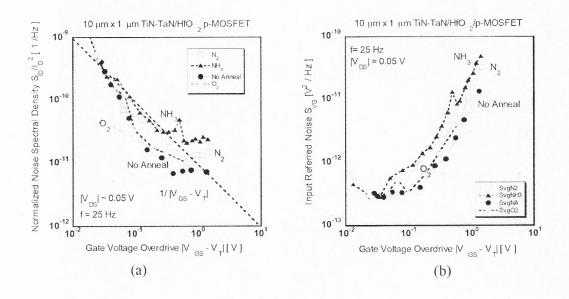

| 5.18 | Drain Current Noise Spectral Density $S_{ID}$ [A <sup>2</sup> /Hz] Vs Frequency f [Hz] for non-nitrided interface devices with different post deposition anneals for p-MOSFETs                                                                                                                                                                                                                                             | 101 |

| 5.19 | (a) Normalized Drain Current Noise Spectral Density $S_{ID}/I_D^2$ [1/Hz] Vs Gate Voltage Overdrive $ V_{GS} - V_T $ [V] for non-nitrided interface devices with different post deposition anneals for p-MOSFETs. Figure 5.19b: Input-referred noise $S_{VG}$ [V <sup>2</sup> /Hz] Vs Gate Voltage Overdrive $ V_{GS} - V_T $ [V] for non-nitrided interface devices with different post deposition anneals for p-MOSFETs. | 102 |

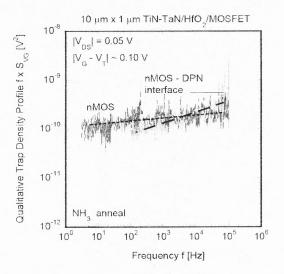

| 5.20 | f x Input-referred noise $S_{VG}$ [A <sup>2</sup> /Hz] Vs Frequency f [Hz] for devices with (a) non-nitrided interface n-MOSFET and (b) nitrided interface n-MOSFET for NH <sub>3</sub> case                                                                                                                                                                                                                               | 102 |

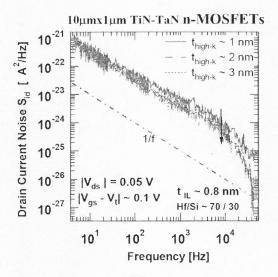

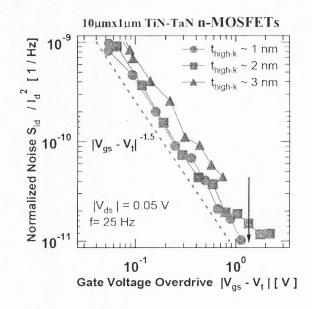

| 5.21 | Drain current spectral density $S_{id}$ versus Frequency f for n-channel devices with various high- $\kappa$ layer thicknesses. The interfacial layer (IL) oxide is SiO <sub>2</sub> and has a thickness of ~0.8 nm                                                                                                                                                                                                        | 106 |

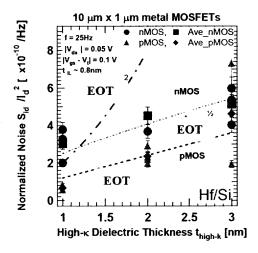

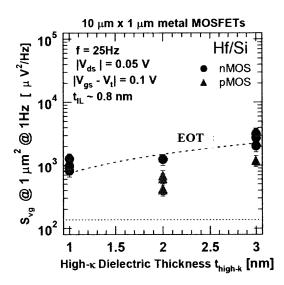

| 5.22 | Drain current spectral density $S_{id}$ versus Frequency f for n-channel devices with various high- $\kappa$ layer thicknesses. The interfacial layer (IL) oxide is SiO <sub>2</sub> and has a thickness of ~0.8 nm                                                                                                                                                                                                        | 109 |

#### Chapter

| 5.23 | Normalized noise spectral density $S_{ID}$ versus gate voltage overdrive ( $V_{GS} - V_T$ ) for n-channel devices with various high- $\kappa$ layer thickness. The interfacial layer (IL) oxide is SiO <sub>2</sub> and has a thickness of ~0.8 nm                                                                                                                    | 109 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

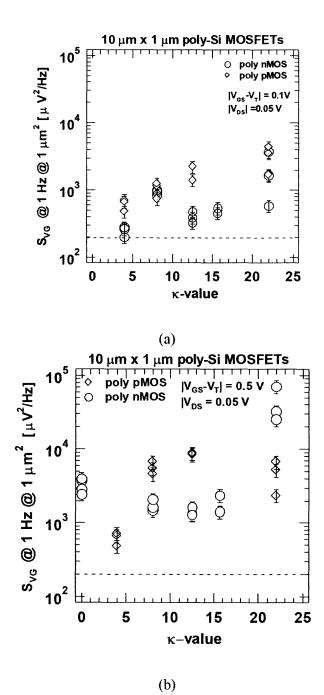

| 5.24 | Normalized input referred gate voltage noise $S_{VG}$ versus % $\kappa$ -value of dielectric for poly-Si n- and p-MOSFET devices at $ V_{DS} $ of 0.05 V and $ V_{GS}-V_T $ of a) 0.1 V and b) 0.5 V.                                                                                                                                                                 | 111 |

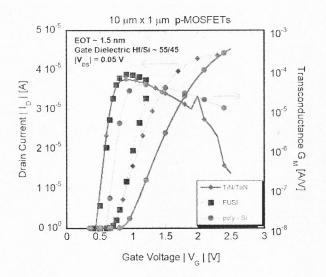

| 5.25 | Drain Current $ I_D $ [A] Vs Gate Voltage $ V_G $ [V] and transconductance $G_M$ Vs gate voltage $ V_G $ [V] characteristics of TiN-TaN, FUSI and poly-Si gate p-MOSFETs for 55% Hf-silicate gate oxides                                                                                                                                                              | 114 |

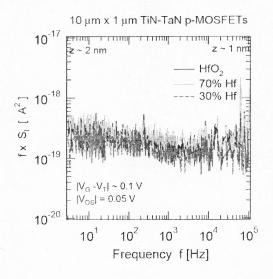

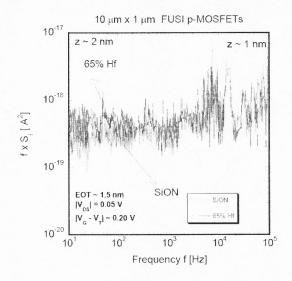

| 5.26 | Qualitative trap profile f x S <sub>I</sub> [ $A^2$ ] Vs frequency f [Hz] at $ V_G - V_T  \sim 0.1$ V of metal gate p-MOSFETs for various Hf-silicate gate oxides                                                                                                                                                                                                     | 114 |

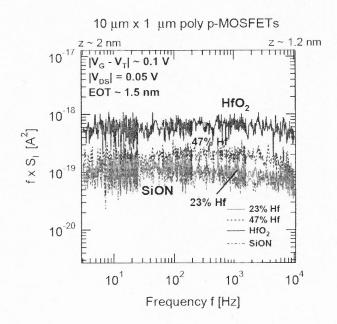

| 5.27 | Qualitative trap profile f x S <sub>I</sub> [ $A^2$ ] Vs frequency f [Hz] at $ V_{GS} - V_T  \sim 0.1$ V of poly gate p-MOSFETs for various Hf-silicate gate oxides                                                                                                                                                                                                   | 115 |

| 5.28 | Qualitative trap profile f x S <sub>I</sub> [ $A^2$ ] Vs frequency f [Hz] Vs f at $ V_G - V_T  \sim 0.2$ V of FUSI gate p-MOSFETs for various Hf-silicate gate oxides.                                                                                                                                                                                                | 116 |

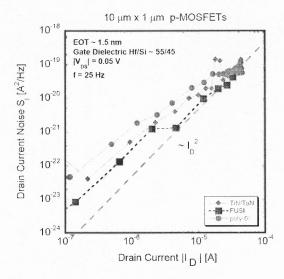

| 5.29 | Drain Current Noise Spectral Density $S_I [A^2/Hz]$ Vs Drain Current $ I_D $ [A] characteristics of TiN-TaN, FUSI and poly-Si gate p-MOSFETs for 55% Hf-silicate gate oxides                                                                                                                                                                                          | 118 |

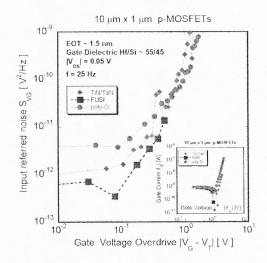

| 5.30 | Input Referred Noise $S_{VG}$ [V <sup>2</sup> /Hz ] Vs Gate Voltage Overdrive $ V_{GS} - V_T $<br>[V] characteristics of TiN-TaN, FUSI and poly-Si gate p-MOSFETs for<br>~55% Hf-silicate gate oxides. (Inset) Gate leakage $ I_G $ [A] – Gate Voltage<br>$ V_G $ [V] characteristics of TiN-TaN, FUSI and poly-Si gate p-MOSFETs for<br>55% Hf-silicate gate oxides. | 120 |

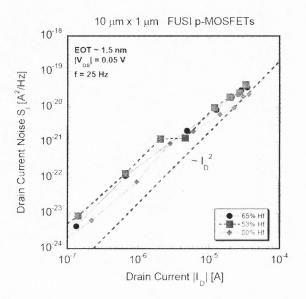

| 5.31 | Drain Current Noise Spectral Density $S_I [A^2/Hz]$ Vs Drain Current $ I_D  [A]$ characteristics of FUSI gate p-MOSFETs for various Hf-silicate gate oxides                                                                                                                                                                                                           | 121 |

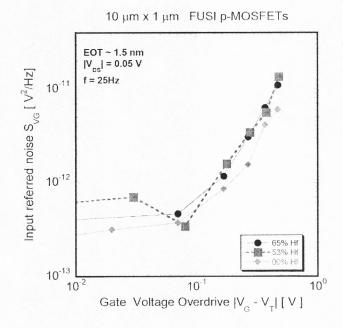

| 5.32 | Input referred noise $S_{VG}$ [V <sup>2</sup> /Hz] Vs Gate Voltage Overdrive  V <sub>G</sub> - V <sub>T</sub>   [V] characteristics of FUSI gate p-MOSFETs for various Hf-silicate gate oxides                                                                                                                                                                        | 122 |

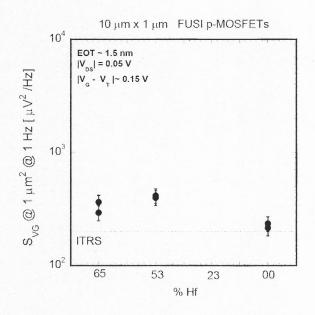

| 5.33 | Input referred noise $S_{VG}$ [V²/Hz] Vs %HfO2 of FUSI gate p-MOSFETs at $ V_G$ - $V_T \sim 0.15$ V.                                                                                                                                                                                                                                                                  | 123 |

## Chapter

Page

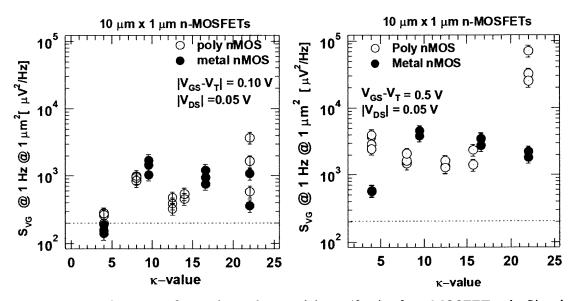

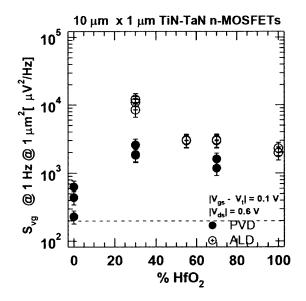

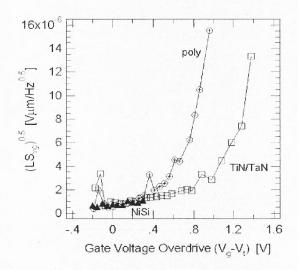

| 5.34 | (a) Impact of gate electrode material on 1/f noise for n-MOSFET poly-Si and metal gate devices. The comparisons are made using the normalized $S_{VG}$ values at $ V_{DS}  = 0.05V$ and $ V_{GS}-V_T  = 0.1V$ and (b) $ V_{DS}  = 0.05V$ and $ V_{GS}-V_T  = 0.5V$ . Dotted line on the figure indicates the ITRS requirement.   | 125 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

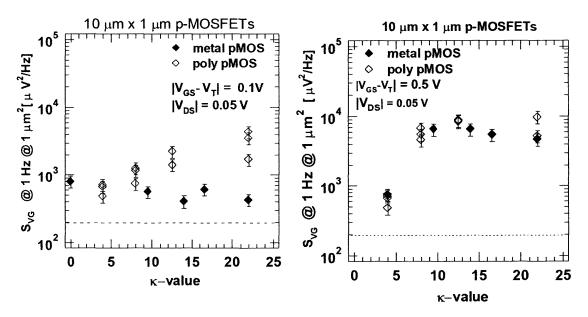

| 5.35 | (a) Impact of gate electrode material on 1/f noise for p-MOSFET poly-Si and metal gate devices. The comparisons are made using the normalized $S_{VG}$ values at (a) $ V_{DS} =0.05V$ and $ V_{GS}-V_T  = 0.1V$ and (b) $ V_{DS}  = 0.05V$ and $ V_{GS}-V_T  = 0.5V$ . Dotted line on the figure indicates the ITRS requirement. | 126 |

| 5.36 | Impact of gate stack processing – ALD Vs PVD on 1/f noise. Comparisons are made using the normalized $S_{VG}$ values at $ V_{DS} =0.6V$ and $ V_{GS}-V_T  = 0.1V$ . Dotted line on the figure indicates the ITRS requirement.                                                                                                    | 127 |

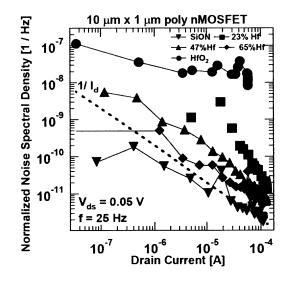

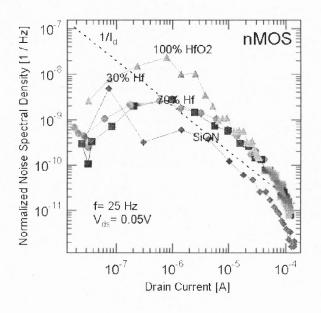

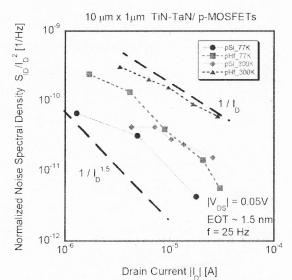

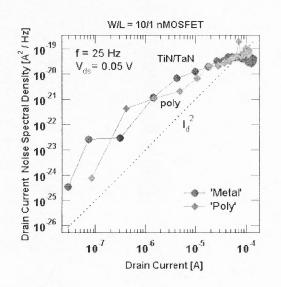

| 5.37 | Normalized drain current spectral density $S_{ID} / I_D^2 Vs$ Drain current $I_D$ for 10 $\mu m \ge 1 \mu m$ poly-Si nMOSFETs for various Hf-silicates at $V_{DS} = 0.05V$ and f = 25Hz                                                                                                                                          | 130 |

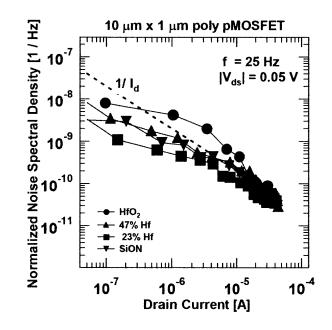

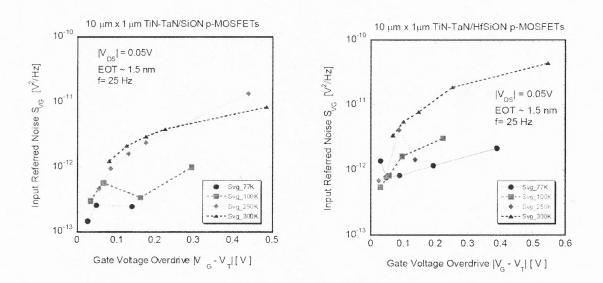

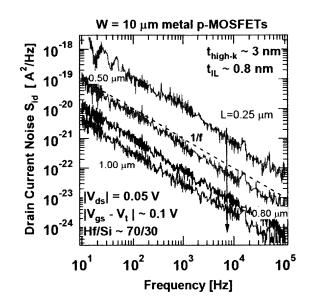

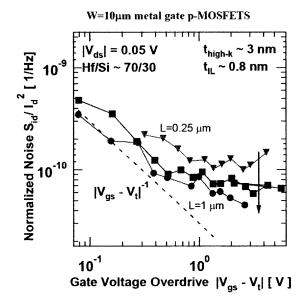

| 5.38 | Normalized drain current spectral density $S_{ID}/I_D^2$ Vs Drain current $I_D$ for 10 $\mu$ m x 1 $\mu$ m poly-Si pMOSFETs for various Hf-silicates at $ V_{DS}  = 0.05$ V and f = 25Hz                                                                                                                                         | 131 |

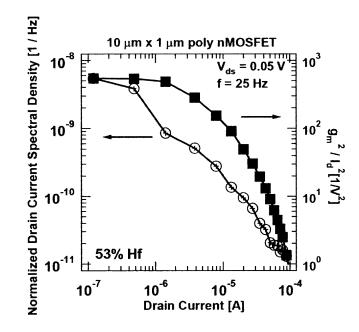

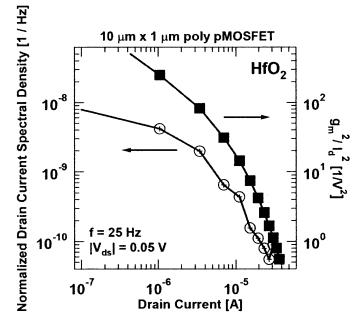

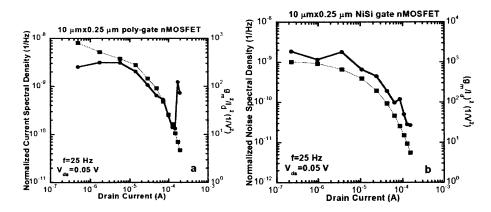

| 5.39 | Normalized drain current spectral density $S_{ID}/I_D^2$ and $g_M^2/I_D^2$ Vs drain current $I_D$ for 10 $\mu$ m x 1 $\mu$ m nMOSFETs for 53% Hf dielectric at $V_{DS} = 0.05V$ and $f = 25Hz$                                                                                                                                   | 132 |

| 5.40 | Normalized drain current spectral density $S_{ID}/I_D^2$ and $g_M^2/I_D^2$ Vs drain current $I_D$ for 10 $\mu$ m x 1 $\mu$ m nMOSFETs for 53% Hf dielectric at $V_{DS} = 0.05V$ and f = 25Hz                                                                                                                                     | 132 |

| 5.41 | Normalized drain current noise spectral density $S_{ID}/I_D^2$ at $ V_{DS}  = 0.05V$ for metal gate nMOSFETs for various gate stack composition with SiON as reference gate oxide                                                                                                                                                | 133 |

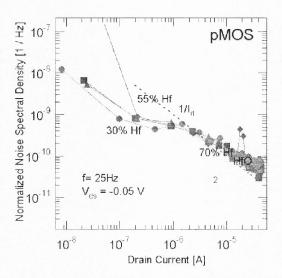

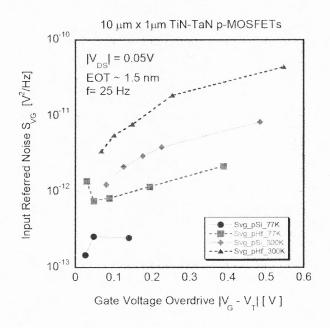

| 5.42 | Normalized drain current noise spectral density $S_{ID}/I_D^2$ at $ V_{DS}  = 0.05V$ for metal gate pMOSFETs for various Hf-based gate stack composition                                                                                                                                                                         | 134 |

#### Chapter

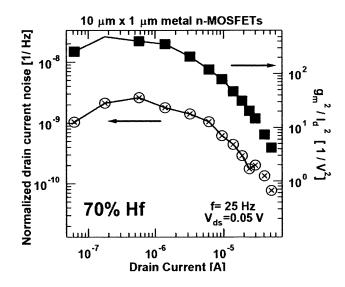

| 5.43 | Normalized drain current spectral density $S_{ID}/I_D^2$ (1° Axis; circles) and $g_M^2/I_D^2$ (2° Axis; squares) versus drain current $I_D$ for 53%Hf n-MOSFETs                                                                                                                                                                                   | 135 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

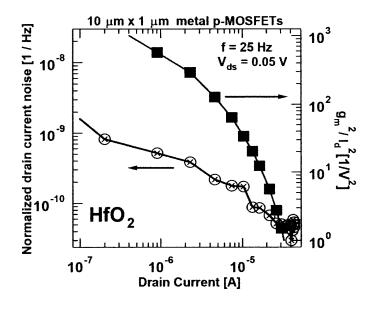

| 5.44 | Normalized drain current spectral density $S_{ID}/I_D^2$ (1° Axis; circles) and $g_M^2/I_D^2$ (2° Axis; squares) versus drain current $I_D$ for HfO <sub>2</sub> p-MOSFETs                                                                                                                                                                        | 135 |

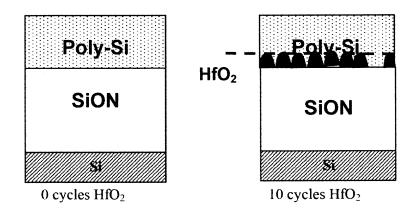

| 5.45 | Schematic of gate stack with and without the growth cycles of HfO <sub>2</sub>                                                                                                                                                                                                                                                                    | 136 |

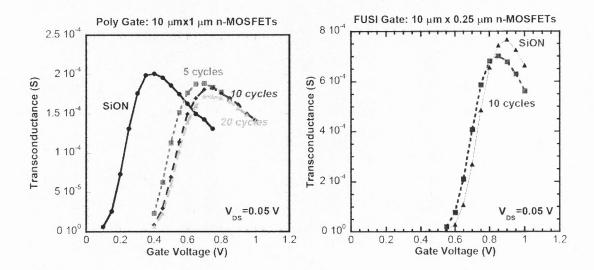

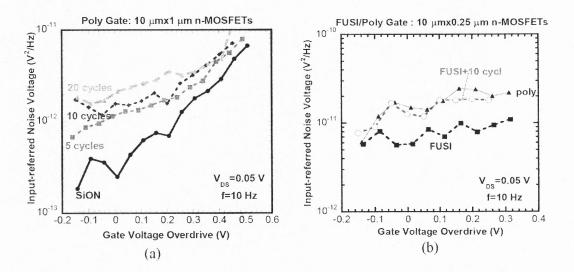

| 5.46 | Input characteristics in linear operation ( $V_{DS}$ =0.05 V) for (a) 10 µmx1.0 µm poly-silicon gate and 10 µmx0.25 µm FUSI gate (b) n-MOSFETs with and without a few cycles of HfO <sub>2</sub> on top of a 1.5 nm SiON gate dielectric                                                                                                          | 137 |

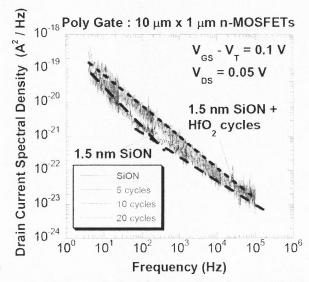

| 5.47 | Drain current spectra $S_I$ Vs frequency f of devices with SiON and 5, 10 and 20 cycles of HfO <sub>2</sub> . Two different slopes are observed for pure SiON devices.                                                                                                                                                                            | 138 |

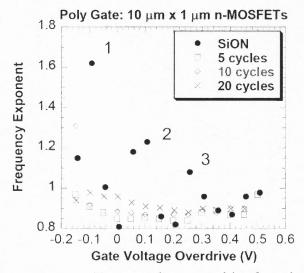

| 5.48 | Frequency exponent $\gamma$ Vs gate voltage overdrive for poly-Si devices with pure SiON and with a few cycles of HfO <sub>2</sub> on top of SiON. Numbers indicate excess noise peaks in SiON                                                                                                                                                    | 139 |

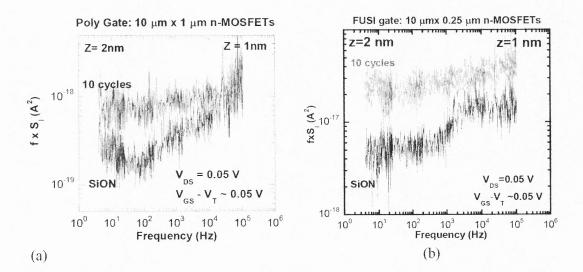

| 5.49 | Normalized low-frequency noise spectrum f x S <sub>I</sub> versus frequency f in linear operation ( $V_{DS}$ =0.05 V) and at $V_{GS}$ - $V_T \sim 0.05$ V, for (a) 10 µmx1 µm poly-Si n-MOSFETs and (b) 10 µmx0.25 µm n-MOSFETs,with SiON and SiON plus 10 cycles HfO <sub>2</sub> , respectively                                                 | 140 |

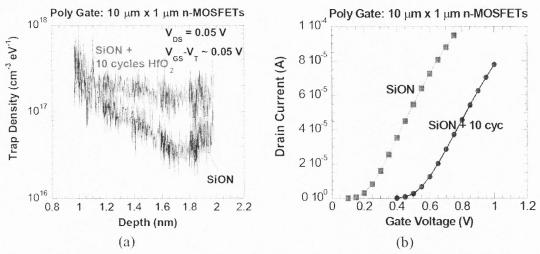

| 5.50 | (a) Trap density versus depth in linear operation ( $V_{DS}$ =0.05 V) and at $V_{GS}$ - $V_T \sim 0.05$ V, for a 10 $\mu$ m x1 $\mu$ m poly-Si n-MOSFET with and without 10 cycles HfO <sub>2</sub> on top of a 1.5 nm SiON gate dielectric. (b) Threshold Voltage $V_T$ shifts observed between SiON and SiON with 10 cycles of HfO <sub>2</sub> | 142 |

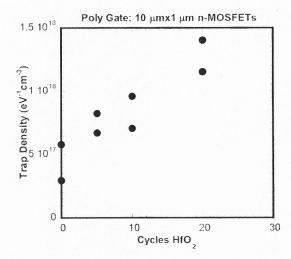

| 5.51 | Trap Density Vs cycles $HfO_2$ for poly-gate 10 $\mu m$ x 1 $\mu m$ n-MOSFETs                                                                                                                                                                                                                                                                     | 144 |

## Chapter

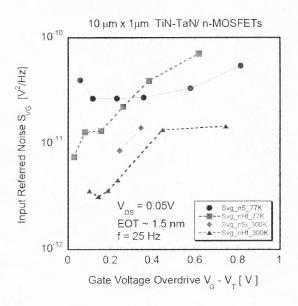

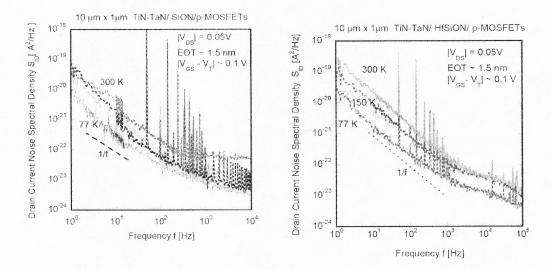

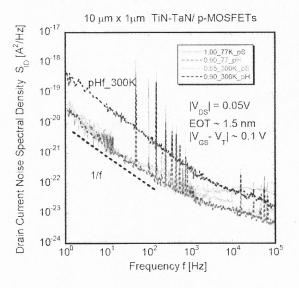

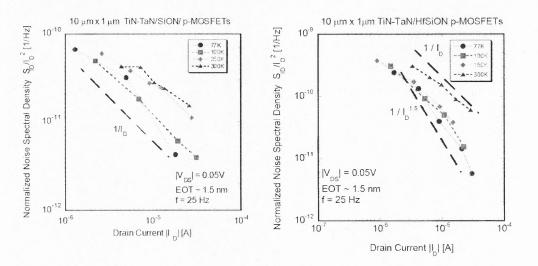

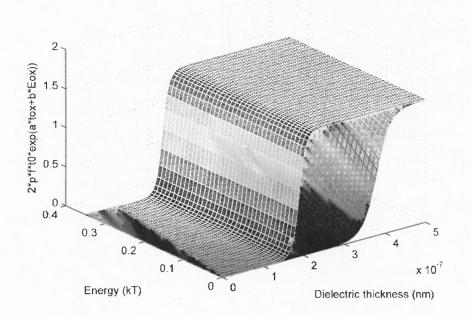

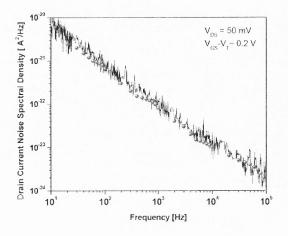

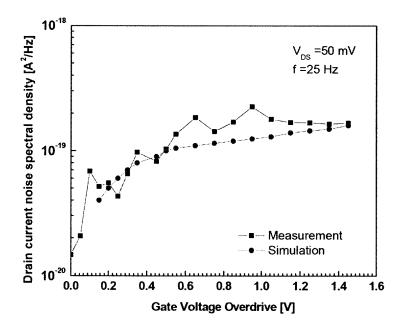

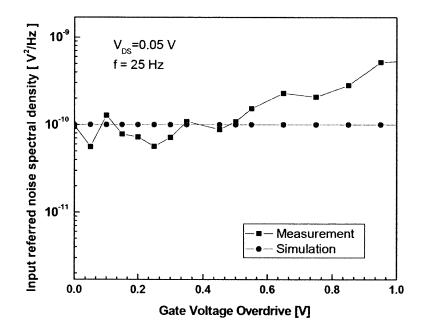

| 5.52 | Input-referred noise spectral density $S_{VG}$ at 10 Hz versus gate voltage overdrive $V_{GS} - V_T$ in linear operation ( $V_{DS}$ =0.05 V) for n-MOSFETs corresponding with (a) a poly silicon gate and SiON or SiON plus a few cycles HfO <sub>2</sub> , and (b) a poly-Si gate with SiON and a poly-Si or FUSI gate with SiON plus a few cycles of HfO <sub>2</sub> . | 144 |