## **New Jersey Institute of Technology** Digital Commons @ NJIT

Theses and Dissertations Dissertations

Fall 2005

## HfO2 as gate dielectric on Si and Ge substrate

Reenu Garg New Jersey Institute of Technology

Follow this and additional works at: https://digitalcommons.njit.edu/dissertations

Part of the Computer Engineering Commons

### Recommended Citation

Garg, Reenu, "HfO2 as gate dielectric on Si and Ge substrate" (2005). Dissertations. 768. https://digitalcommons.njit.edu/dissertations/768

This Dissertation is brought to you for free and open access by the Theses and Dissertations at Digital Commons @ NJIT. It has been accepted for inclusion in Dissertations by an authorized administrator of Digital Commons @ NJIT. For more information, please contact digitalcommons@njit.edu.

## **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

### **ABSTRACT**

### HfO<sub>2</sub> AS GATE DIELETRIC ON Si AND Ge SUBSTRATE

### by Reenu Garg

Hafnium oxide (HfO<sub>2</sub>) has been considered as an alternative to silicon dioxide (SiO<sub>2</sub>) in future nano-scale complementary metal-oxide-semiconductor (CMOS) devices since it provides the required capacitance at the reduced device size because of its high dielectric constant. HfO<sub>2</sub> films are currently deposited by various techniques. Many of them require high temperature annealing that can impact device performance and reliability.

In this research, electrical characteristics of capacitors with HfO<sub>2</sub> as gate dielectric deposited by standard thermal evaporation and e-beam evaporation on Si and Ge substrates were investigated. The dielectric constant of HfO<sub>2</sub> deposited by thermal evaporation on Si is in the range of 18-25. Al/HfO<sub>2</sub>/Si MOS capacitors annealed at 450°C show low hysteresis, leakage current density and bulk oxide charges. Interface state density and low temperature charge trapping behavior of these structures were also investigated.

Degradation in surface carrier mobility has been reported in Si field-effect-transistors with HfO<sub>2</sub> as gate dielectric. To explore the possibility of alleviating this problem we have used germanium (Ge) substrate as this semiconductor has higher carrier mobility than Si. Devices fabricated by depositing HfO<sub>2</sub> directly on Ge by standard thermal evaporation were found to be too leaky and show significant hysteresis and large shift in flatband voltage. This deterioration in electrical performance is mainly due to the formation of unstable interfacial layer of GeO<sub>2</sub> during the HfO<sub>2</sub> deposition. To minimize this effect, Ge surface was treated with the beam of atomic nitrogen prior to the dielectric

deposition. The effect of surface nitridation, on interface as well as on bulk oxide, trap energy levels were investigated using low temperature C-V measurements. They revealed additional defect levels in the nitrided devices indicating diffusion of nitrogen from interface into the bulk oxide. Impact of surface nitridation on the reliability of Ge/HfO<sub>2</sub>/Al MOS capacitors has been investigated by application of constant voltage stress at different voltage levels for various time periods. It was observed that deeper trap levels in nitrided devices, found from low frequency and low temperature measurements, trap the charge carrier immediately after stress but with time these carriers detrap and create more traps inside the bulk oxide resulting in further devices deterioration. It is inferred that though nitrogen is effective in reducing interfacial layer growth it incorporates more defects at interface as well as in bulk oxide. Therefore, it is important to look into alternative methods of surface passivation to limit the growth of GeO<sub>2</sub> at the interface.

## HfO<sub>2</sub> AS GATE DIELETRIC ON Si AND Ge SUBSTRATE

by Reenu Garg

A Dissertation

Submitted to the Faculty of

New Jersey Institute of Technology

in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy in Computer Engineering

**Department of Electrical and Computer Engineering**

January 2006

Copyright © 2006 by Reenu Garg

ALL RIGHTS RESERVED

## APPROVAL PAGE

## HfO<sub>2</sub> AS GATE DIELETRIC ON Si AND Ge SUBSTRATE

## Reenu Garg

| Dr. Durga Misra, Dissertation Advisor                             | Date                                  |

|-------------------------------------------------------------------|---------------------------------------|

| Professor of Electrical and Computer Engineering, NJIT            |                                       |

|                                                                   |                                       |

|                                                                   |                                       |

|                                                                   |                                       |

| Dr. Leonid Tsybeskov, Committee Member                            | Date                                  |

| Associate Professor of Electrical and Computer Engineering, NJIT  | Date                                  |

| Tibboolate I Totobbot of Execution and Compater Engineering, 1311 |                                       |

|                                                                   |                                       |

|                                                                   |                                       |

|                                                                   | · · · · · · · · · · · · · · · · · · · |

| Dr. Marek Sosnowski, Committee Member                             | Date                                  |

| Professor of Electrical and Computer Engineering, NJIT            |                                       |

|                                                                   |                                       |

|                                                                   |                                       |

|                                                                   |                                       |

| Dr. Haim Grebel, Committee Member                                 | Date                                  |

| Professor of Electrical and Computer Engineering, NJIT            |                                       |

|                                                                   |                                       |

|                                                                   |                                       |

|                                                                   |                                       |

| Dr. Pradyumna Swain, Committee Member                             | Date                                  |

| Head of Imaging Systems, Sarnoff Corporation, Princeton, NJ       | Date                                  |

|                                                                   |                                       |

### **BIOGRAPHICAL SKETCH**

Author: Reenu Garg

**Degree:** Doctor of Philosophy

Date: January 2006

### **Undergraduate and Graduate Education:**

- Doctor of Philosophy in Computer Engineering,

New Jersey Institute of Technology, Newark, NJ, 2006

- Master of Science in Computer Engineering,

New Jersey Institute of Technology, Newark, NJ, 2002

- Bachelor of Technology in Computer Engineering,

Govind Bhallabh Pant University of Agriculture and Technology, India, 1998

Major: Computer Engineering

#### **Publications:**

- R. Garg, N. A. Chowdhury, M. Bhaskaran, P. K. Swain and D. Misra, "Electrical characteristics of thermally evaporated HfO<sub>2</sub>", Journal of Electrochemical Society, 151, pp. F215-219 (2004).

- N. A. Chowdhury, R. Garg and D. Misra, "Charge trapping and interface characteristics of thermally evaporated HfO<sub>2</sub>", Applied Physics Letters, vol.85, 15, p. 3289 (2004).

- R. Garg, P. K. Swain and D. Misra, "Ge MOS capacitors using thermally evaporated HfO<sub>2</sub> as gate dielectric", Journal of Electrochemical Society (Accepted: In Press).

- T. Kundu, R. Garg, N. A. Chowdhury, and D. Misra, "Electrical techniques for characterization of dielectric films", ECS Interface, p. 17 (Fall 2005).

- R. Garg, D. Misra, and S. Guha, "Effect of Ge surface nitridation on the Ge/HfO<sub>2</sub>/Al MOS devices", IEEE Trans. Of Dev. & Mat. Rel. (Submitted).

### **Presentations:**

- R. Garg, R. K. Jarwal, M. Bhaskaran, P. K. Swain and D. Misra, "Properties of thermally evaporated HfO<sub>2</sub>", Student Poster Session in 203<sup>th</sup> meeting of Electrochemical Society Meeting, Paris, France, Apr 28 May 2, 2003.

- R. Garg, N. A. Chowdhury, M. Bhaskaran, P. K. Swain and D. Misra, "Electrical characteristics of thermally evaporated HfO<sub>2</sub>", in 204th meeting of Electrochemical Society Meeting, Florida, USA, Oct 12-16,2003.

- N. A. Chowdhury, R. Garg and D. Misra,

"Charge trapping and interface characteristics of thermally evaporated HfO<sub>2</sub>",

Student Poster Session in 205<sup>th</sup> meeting of Electrochemical Society Meeting, San

Antonio, USA, May 9-13, 2004.

- N. A. Chowdhury, R. Garg and D. Misra, "Time dependent dielectric breakdown of thermally evaporated HfO<sub>2</sub> for nanoscale devices", 206th meeting of Electrochemical Society Meeting, Honolulu, Hawaii, Oct 12- 16, 2004.

- R. Garg, P. K. Swain and D. Misra, "Ge MOS devices using thermally evaporated HfO<sub>2</sub> as gate dielectric", 207th meeting of Electrochemical Society Meeting, Quebec, Canada, May 16-19, 2005.

- R. Garg, D. Misra, and S. Guha, "Effect of surface nitridation on Ge/HfO<sub>2</sub> interface", Oct 16-19, 2005, 208th meeting of Electrochemical Society Meeting, Los Angeles, USA, Oct 16-21, 2005.

To my family

#### ACKNOWLEDGMENT

First of all, I would like to convey my deepest regard for Dr. Durga Misra, who not only served as my research supervisor, providing valuable and countless resources, insight, and intuition, but also constantly gave me support, encouragement, and reassurance through out my graduate studies in NJIT. I would also like to thank Dr. Leonid Tsybeskov, Dr. Marek Sosnowski, Dr. Haim Grebel and Dr. Pradyumna Swain for actively participating in my committee.

I would like to acknowledge National Science Foundation for partial fulfillment of research carried out during my Ph. D. I would also like to acknowledge Sarnoff Corporation and IBM Corporation for providing samples used in the research of my degree program.

During my studies at NJIT, many people helped me. Among them, I would like to specially thank Dr. R. Jarwal, who conscientiously taught me the usage of equipment and offered great help in the clean room. I am grateful to my colleagues here in my research group, with whom I spent many hours in the Device Characterization Laboratory, specially Tias Kundu, Amrita Banerjee, N. Chowdhury, and P. Srinivasan for their time spent in discussing the experimental results.

I am blessed to have a lot of close friends in NJIT with whom I have shared my life – the ups and downs, the stressful times, and the fun times. I am very fortunate to have understanding and supporting parents. I am thankful to my mom for her love, advice and wise counsel and my dad for his constant support. And special thanks to my brother and sister for their stimulation and stress -relieving talks.

### **TABLE OF CONTENTS**

| C | hapter                                  | Page |

|---|-----------------------------------------|------|

| 1 | INTRODUCTION                            | 1    |

| 2 | HIGH-κ DIELECTRICS                      | 6    |

|   | 2.1 Background.                         | 6    |

|   | 2.2 Selection Criteria.                 | 7    |

|   | 2.3 Different Deposition Techniques     | 10   |

|   | 2.4 Integration Issues                  | 11   |

|   | 2.5 Ge as a Substrate                   | 13   |

|   | 2.6 High-κ Dielectrics on Ge            | 14   |

| 3 | DEVICE FABRICATION AND CHARACTERIZATION | 16   |

|   | 3.1 Device Fabrication.                 | 16   |

|   | 3.1.1 Starting Materials                | 16   |

|   | 3.1.2 Cleaning.                         | 16   |

|   | 3.1.3 Surface Nitridation.              | 17   |

|   | 3.1.4 HfO <sub>2</sub> Deposition       | 17   |

|   | 3.1.5 Annealing                         | 18   |

|   | 3.1.6 Metal Deposition.                 | 18   |

|   | 3.1.7 Photolithography                  | 18   |

|   | 3.1.8 Etching                           | 18   |

|   | 3.2 Physical Characterization.          | 20   |

|   | 3.2.1 Scanning Electron Microscopy      | 21   |

|   | 3.2.2 X-ray Photoelectron Spectroscopy  | 21   |

## TABLE OF CONTENTS (Continued)

| C | hapter                                                                               | Page |

|---|--------------------------------------------------------------------------------------|------|

|   | 3.3 Electrical Characterization                                                      | 23   |

|   | 3.3.1 High Frequency and Low Frequency C-V Measurements                              | 23   |

|   | 3.3.2 Conductance Measurements                                                       | 24   |

|   | 3.3.3 Estimation of Interface State Density by Terman Method                         | 24   |

|   | 3.3.3.1 Plotting the Ideal C-V Curve                                                 | 24   |

|   | 3.3.3.2 Extraction of Interface State Density                                        | 26   |

|   | 3.3.4 Stress Measurements                                                            | 26   |

|   | 3.3.5 Low Temperature Measurements                                                   | 27   |

| 4 | ELECTRICAL CHARACTERISTICS OF THERMALLY EVAPORATED HfO <sub>2</sub> ON SI SUBSTRATE. | 28   |

|   | 4.1 C-V Characteristics                                                              | 28   |

|   | 4.2 Dielectric Constant                                                              | 32   |

|   | 4.3 Trapped Charges                                                                  | 33   |

|   | 4.4 Leakage Current                                                                  | 35   |

|   | 4.5 Traps Behavior at Low Temperatures                                               | 36   |

|   | 4.6 Effect of Aging.                                                                 | 41   |

|   | 4.7 Comparison with E-Beam Evaporation                                               | 42   |

|   | 4.8 Summary                                                                          | 43   |

| 5 | CHARACTERISTICS OF THERMALLY EVAPORATED HfO <sub>2</sub> ON Ge SUBSTRATE.            | 45   |

|   | 5.1 Physical Characterization.                                                       | 45   |

|   | 5.2 Electrical Characterization                                                      | 48   |

# TABLE OF CONTENTS (Continued)

| C | hapter                                                                   | Page |

|---|--------------------------------------------------------------------------|------|

|   | 5.3 Interface Characteristics                                            | 54   |

|   | 5.4 Summary                                                              | 58   |

| 6 | CHARACTERISTICS OF E-BEAM EVAPORATED HfO <sub>2</sub> ON Ge<br>SUBSTRATE | 60   |

|   | 6.1 C-V Characteristic                                                   | 60   |

|   | 6.2 Effect of Ge Surface Nitridation.                                    | 62   |

|   | 6.3 Low Temperature Characterization.                                    | 66   |

|   | 6.4 Charge Trapping Under Constant Voltage Stress                        | 70   |

|   | 6.5 De-trapping Phenomena                                                | 76   |

|   | 6.6 Summary                                                              | 77   |

| 7 | CONCLUSIONS AND FUTURE WORK                                              | 79   |

|   | 7.1 Conclusions                                                          | 79   |

|   | 7.2 Recommendations for Future Work                                      | 81   |

|   | REFERENCES                                                               | 83   |

## LIST OF TABLES

| Table |                                                                                                                                          | Page |

|-------|------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.1   | Various dielectric materials and their properties with respect to Silicon.                                                               | 9    |

| 3.1   | Various annealing temperature with annealing environments                                                                                | 18   |

| 3.2   | Process flow of Si and Ge MOS capacitors with thermally evaporated HfO <sub>2</sub> as gate dielectric                                   | 19   |

| 3.3   | Process flow of Ge MOS capacitors with HfO <sub>2</sub> , deposited by e-beam evaporation with reactive atomic O beam as gate dielectric | 20   |

| 4.1   | Dielectric constant comparison with other current techniques                                                                             | 33   |

| 6.1   | Conduction and valence band offset of GeO <sub>2</sub> and HfO <sub>2</sub> with respect to Ge and work function values for Ge and Al    | 71   |

## LIST OF FIGURES

| Figure |                                                                                                                                                                                                                                                                                                                                                                                                                                             | Page |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

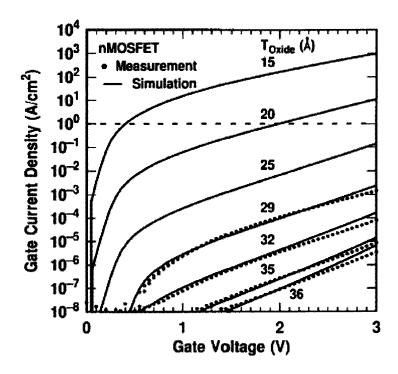

| 1.1    | Measured and simulated Ig-Vg characteristics under inversion conditions of SiO <sub>2</sub> N- MOSFET devices                                                                                                                                                                                                                                                                                                                               | 2    |

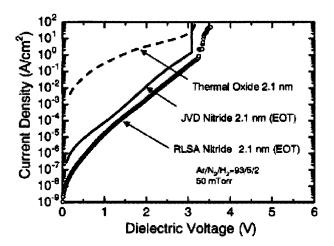

| 2.1    | Current density of various silicon nitride films with EOT of 2.1 nm                                                                                                                                                                                                                                                                                                                                                                         | 7    |

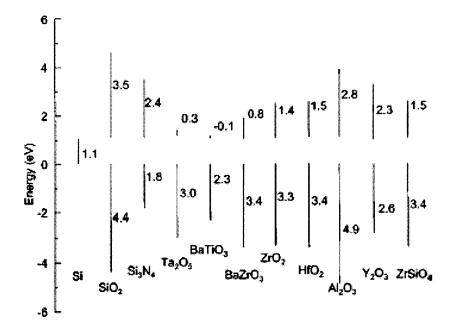

| 2.2    | Band offsets of various high- $\kappa$ dielectrics with respect to silicon                                                                                                                                                                                                                                                                                                                                                                  | 9    |

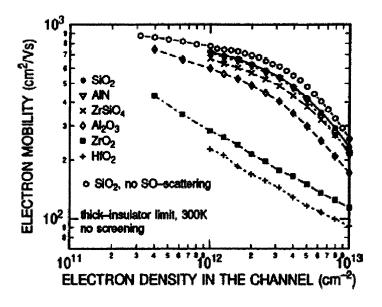

| 2.3    | Electron mobility of various high- $\kappa$ materials with respect to silicon                                                                                                                                                                                                                                                                                                                                                               | 12   |

| 3.1    | Electronic processes in X-ray photoelectron Spectroscopy                                                                                                                                                                                                                                                                                                                                                                                    | 22   |

| 3.2    | XPS measurement schematic                                                                                                                                                                                                                                                                                                                                                                                                                   | 22   |

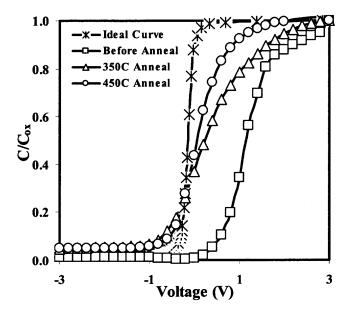

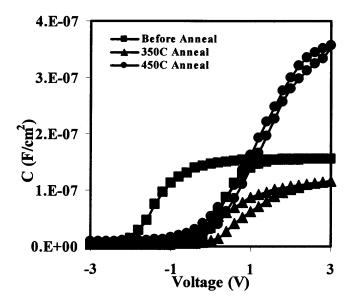

| 4.1    | Normalized C-V curves of MOS capacitors with 50nm $HfO_2$ film compared with ideal C-V curve. Bulk oxide charges were reduced to $1.61 \times 10^{11}/cm^2$ and interface state density was found to be $1.75 \times 10^{12}/cm^2$ eV after samples were annealed at $450^{\circ}C$ .                                                                                                                                                       | 30   |

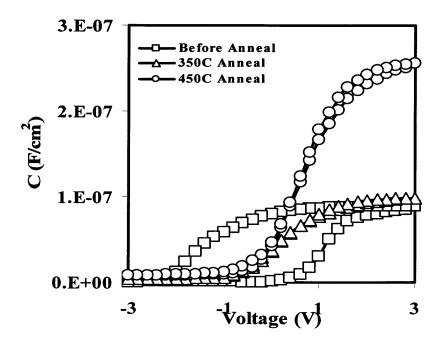

| 4.2    | Normalized C-V curves of MOS capacitors with 50nm HfO <sub>2</sub> film at different annealing temperatures. Hysteresis reduced to 30mV after 450°C FGA                                                                                                                                                                                                                                                                                     | 31   |

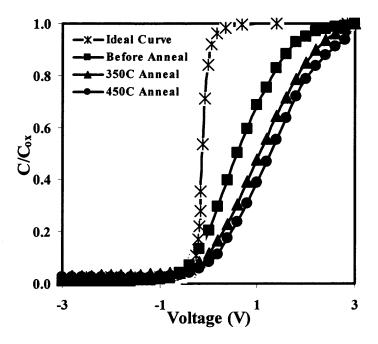

| 4.3    | Normalized C-V curves of MOS capacitors with 60nm $HfO_2$ film compared with ideal C-V curve. Bulk oxide charges were increased up to $1.15 \times 10^{12}/cm^2$ and interface state density was increased to $6.47\times10^{12}/cm^2$ eV after a $450^{\circ}$ C anneal.                                                                                                                                                                   |      |

| 4.4    | Normalized C-V curves of MOS capacitors with 60nm HfO <sub>2</sub> film at different annealing temperatures. Hysteresis reduced to 175mV after 450°C FGA                                                                                                                                                                                                                                                                                    | 32   |

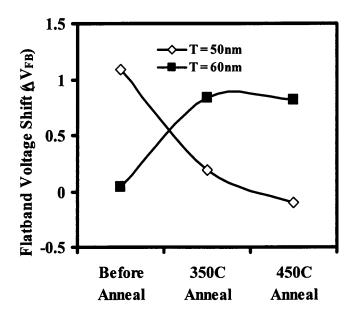

|        | Effect of annealing on flatband voltage shift ( $\Delta V_{FB}$ ). In 50nm HfO <sub>2</sub> films, $\Delta V_{FB}$ has reduced from 1.1V to 0.01V, while in 60nm HfO <sub>2</sub> films it has increased from 0.04V to 0.8V                                                                                                                                                                                                                 | 34   |

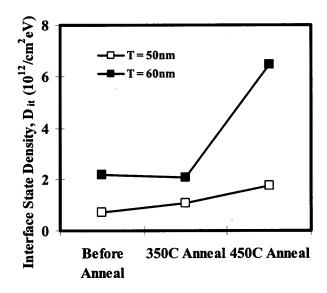

| 4.6    | In 50nm HfO <sub>2</sub> films, interface state density ( $D_{it}$ ) has increased from $0.706\times10^{12}/\text{cm}^2\text{eV}$ before annealing to $1.75\times10^{12}/\text{cm}^2\text{eV}$ after $450^{\circ}\text{C}$ annealing, while in 60nm HfO <sub>2</sub> films it has increased from $2.2\times10^{12}/\text{cm}^2\text{eV}$ before annealing to $6.47\times10^{12}/\text{cm}^2\text{eV}$ after $450^{\circ}\text{C}$ annealing | 35   |

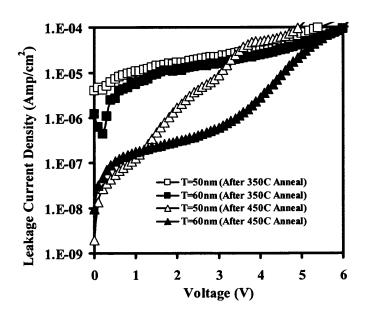

|        | Leakage current density in 50nm and 60nm HfO <sub>2</sub> film MOS capacitor after 350°C and 450°C annealing                                                                                                                                                                                                                                                                                                                                | 36   |

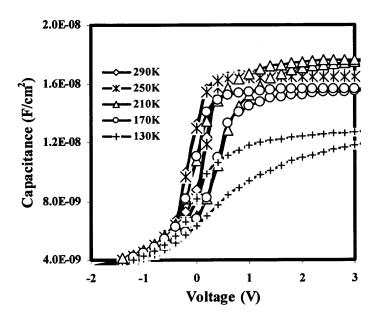

| 4.8    | Low temperature C-V curves for 50nm HfO <sub>2</sub> MOS capacitor                                                                                                                                                                                                                                                                                                                                                                          | 37   |

## LIST OF FIGURES (Continued)

| <b>Figure</b> |                                                                                                                                                                                                                                                                                         | Page |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

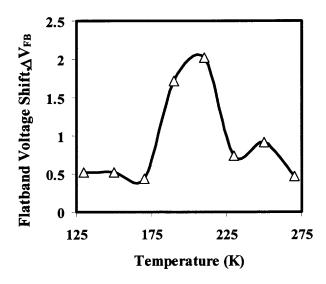

| 4.9           | Flatband voltage shift as a function of temperature for 50nm HfO <sub>2</sub> MOS capacitor                                                                                                                                                                                             | 38   |

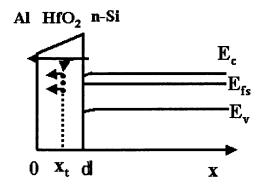

| 4.10          | Energy diagram for Al–HfO <sub>2</sub> –n-Si showing centroid shifting towards the gate electrode                                                                                                                                                                                       | 39   |

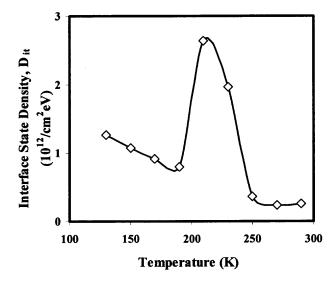

| 4.11          | Interface States, Dit, as a function of temperature for various Al/HfO <sub>2</sub> /n-Si MOS samples                                                                                                                                                                                   | 40   |

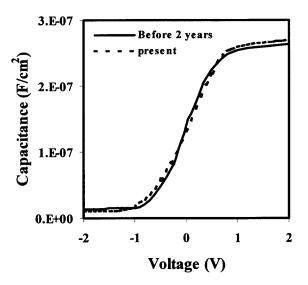

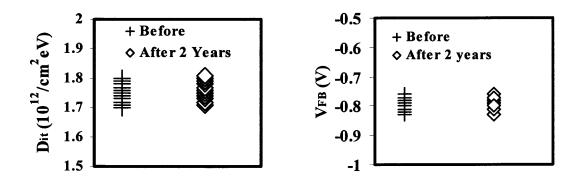

| 4.12          | Comparison of C-V characteristics of 50nm HfO <sub>2</sub> films before and after 2 years                                                                                                                                                                                               | 41   |

| 4.13          | Flatband voltage and Interface state density distribution of 50nm HfO <sub>2</sub> films before and after 2 years                                                                                                                                                                       | 42   |

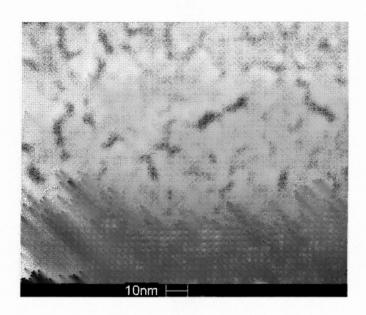

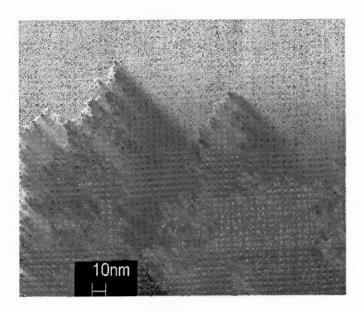

| 5.1(a)        | Top Down scanning electron microscopy image of as deposited thermally evaporated HfO <sub>2</sub> on top of Ge substrate                                                                                                                                                                | 45   |

| 5.1(b)        | Top Down scanning electron microscopy image of 500°C annealed HfO <sub>2</sub> films on top of Ge substrate                                                                                                                                                                             | 46   |

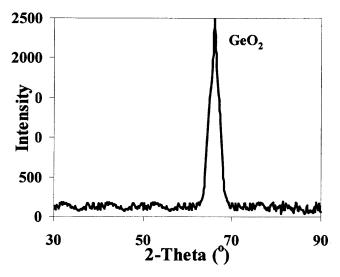

| 5.2           | X-Ray Diffraction spectra of the as deposited films. Peak indicates the presence of crystalline GeO <sub>2</sub>                                                                                                                                                                        | 47   |

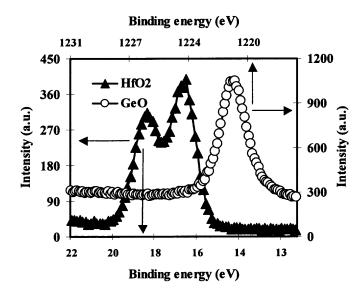

| 5.3           | X-Ray Photoelectron Spectroscopy spectra of Hf4f and Ge2p3 for HfO <sub>2</sub> films after 500°C annealing                                                                                                                                                                             | 48   |

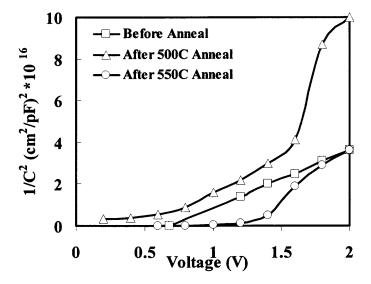

| 5.4           | 1/C <sup>2</sup> vs. applied gate voltage for MOS capacitors with 5nm HfO <sub>2</sub> films before anneal and after anneal. Barrier height, calculated from the intercept on voltage axis is in the range of 0.38V to 0.68V                                                            |      |

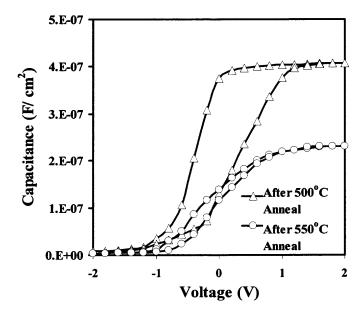

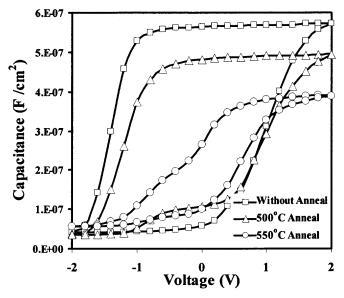

| 5.5           | Capacitance–Voltage characteristics of devices with 5nm $HfO_2$ films after annealing at $500^{\circ}C$ and $550^{\circ}C$ in $N_2$ environment. Hysteresis reduced to $0.2V$ while EOT and $V_{FB}$ increased to $10.5$ nm and $1.23V$ , respectively, after $550^{\circ}C$ annealing. |      |

| 5.6           | Capacitance-Voltage characteristics of devices with 10nm HfO <sub>2</sub> films. Hysteresis reduced to 0.9V, while EOT and V <sub>FB</sub> increased to 9.3nm and 0.73V, respectively, after 550°C annealing                                                                            | 51   |

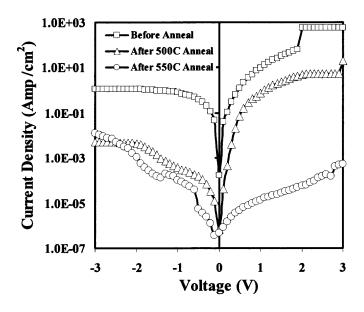

| 5.7           | Leakage current density of the MOS capacitors with 5nm HfO <sub>2</sub> films. After 550°C annealing leakage current reduced to ~10 <sup>-5</sup> A/cm <sup>2</sup>                                                                                                                     | 52   |

## LIST OF FIGURES (Continued)

| Figure |                                                                                                                                                                                                                                                                                                                                                       | rage |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 5.8    | Leakage current density of the MOS capacitors with 5nm HfO <sub>2</sub> films. After 550°C annealing leakage current reduced to ~10 <sup>-5</sup> A/cm <sup>2</sup>                                                                                                                                                                                   | 53   |

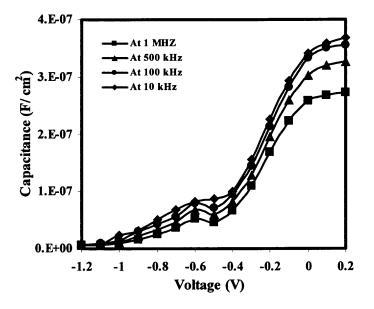

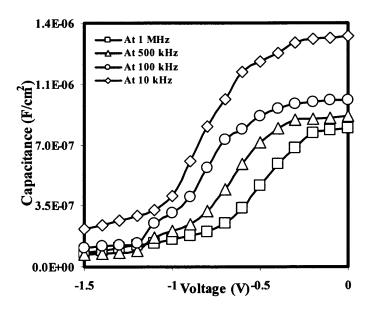

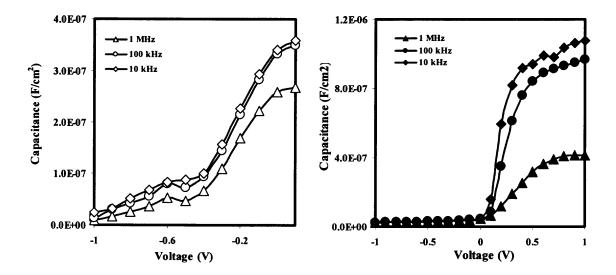

| 5.9    | C-V characteristics of Ge/HfO <sub>2</sub> (5nm)/Al MOSCAPs at different frequencies after 550°C annealing                                                                                                                                                                                                                                            | 55   |

| 5.10   | C-V characteristics of Ge/HfO <sub>2</sub> (10nm)/Al MOSCAPs at different frequencies after 550°C annealing                                                                                                                                                                                                                                           | 55   |

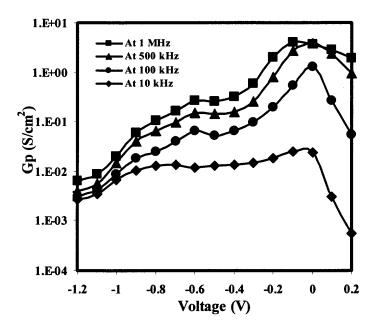

| 5.11   | G-V characteristics of Ge/HfO <sub>2</sub> (5nm)/Al MOSCAPs at different frequencies after 550°C annealing                                                                                                                                                                                                                                            | 56   |

| 5.12   | G-V characteristics of Ge/HfO <sub>2</sub> (10nm)/Al MOSCAPs at different frequencies after 550°C annealing                                                                                                                                                                                                                                           | 57   |

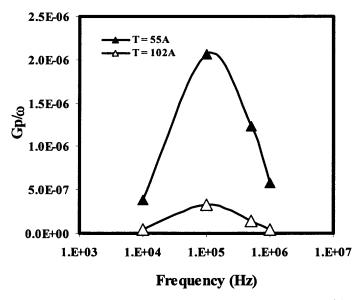

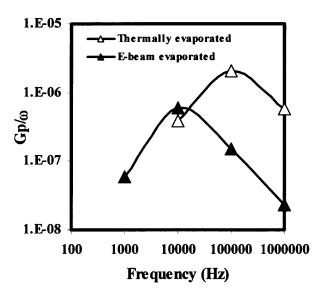

|        | Gp/ $\omega$ vs. $\omega$ for both 5nm and 10nm HfO <sub>2</sub> films after 550°C annealing. Interface state densities (D <sub>it</sub> ) calculated from the peak of Gp/ $\omega$ are, $3.1\times10^{13} \text{cm}^{-2} \text{eV}^{-1}$ and $5.1\times10^{12} \text{cm}^{-2} \text{eV}^{-1}$ for 5nm and 10nm HfO <sub>2</sub> films, respectively. | 57   |

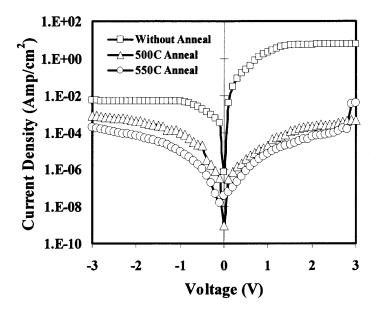

| 6.1    | C-V characteristics of HfO <sub>2</sub> deposited by thermally evaporation and e-beam evaporation with reactive atomic O beam                                                                                                                                                                                                                         | 60   |

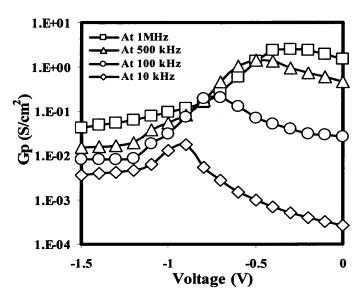

| 6.2    | C-V characteristics at different frequencies ranging from 1 MHz to 10 kHz for <b>a)</b> thermally evaporated HfO <sub>2</sub> , and <b>b)</b> e-beam evaporated HfO <sub>2</sub> with reactive atomic O beam.                                                                                                                                         | 61   |

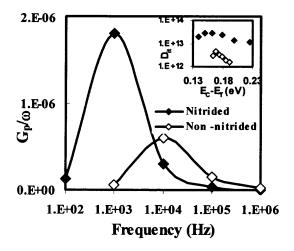

| 6.3    | $Gp/\omega$ vs. frequency for thermally evaporated and e-beam evaporated $HfO_2$ . $D_{it}$ is $4.55\times10^{12} cm^{-2} eV^{-1}$ for e-beam evaporated films while for thermally evaporated films it is $3.1\times10^{13} cm^{-2} eV^{-1}$                                                                                                          |      |

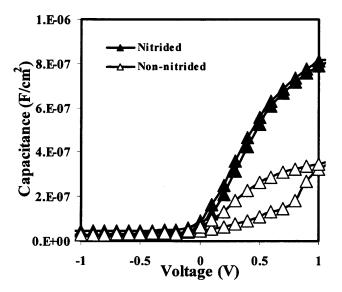

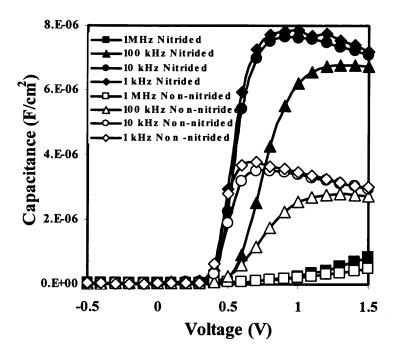

|        | C-V characteristics of nitrided and non-nitrided Ge/HfO <sub>2</sub> /Al MOS capacitors. Nitrided and non-nitrided devices show hysteresis of 0.03V and 0.5V, respectively.                                                                                                                                                                           | 63   |

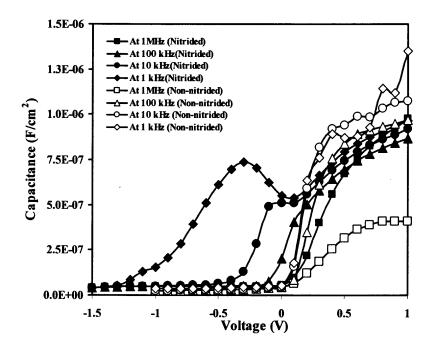

| 6.5    | C-V characteristics of nitrided and non-nitrided Ge/HfO <sub>2</sub> /Al MOS capacitors at different frequencies ranging from 1kHz to 1MHz                                                                                                                                                                                                            | 64   |

|        | Gp/w vs. frequency for nitrided and non-nitrided devices. Interface state density ( $D_{it}$ ) is $2.9\times10^{13}$ cm <sup>-2</sup> eV <sup>-1</sup> and $4.55\times10^{12}$ cm <sup>-2</sup> eV <sup>-1</sup> for nitrided and non-nitrided Ge MOS capacitors, respectively                                                                        | 65   |

# LIST OF FIGURES (Continued)

| <b>Figure</b> |                                                                                                                                                                                                                        | Page |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 6.7           | C-V characteristics of nitrided and non-nitrided Ge/HfO <sub>2</sub> /Al MOS capacitors at different frequencies ranging from 1kHz to 1MHz at 140K                                                                     | 66   |

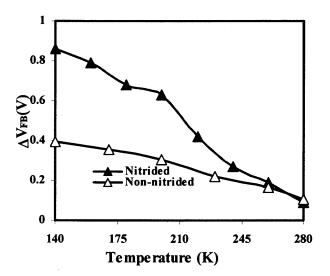

| 6.8           | Shift in flatband voltage, V <sub>FB</sub> , as a function of temperature for nitrided and non-nitrided Ge MOS capacitors                                                                                              | 67   |

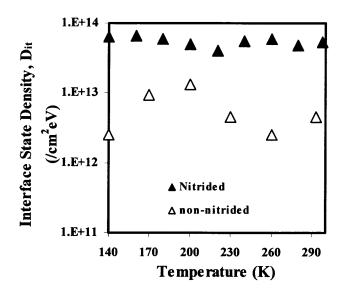

| 6.9           | Interface state density (D <sub>it</sub> ) as a function of temperature for both nitrided and non-nitrided samples                                                                                                     | 68   |

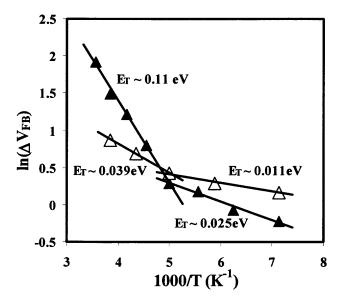

| 6.10          | Ionization energy levels ( $E_T$ ) calculated from $\Delta V_{FB}$ with respect to 1000/K. $E_T$ for nitrided devices is 110meV and 25meV (solid triangles) while non-nitrided it's 39meV and 11 meV (empty triangles) | 69   |

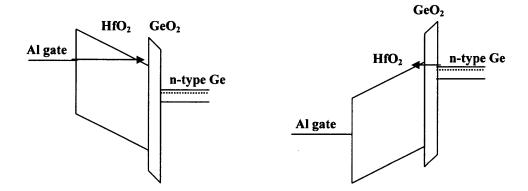

| 6.11          | Schematic band diagrams of a) gate injection, b) substrate injection using numbers given in Table 6.2                                                                                                                  | 70   |

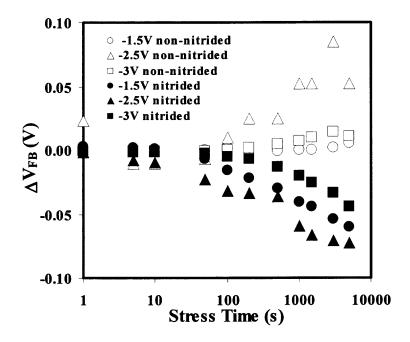

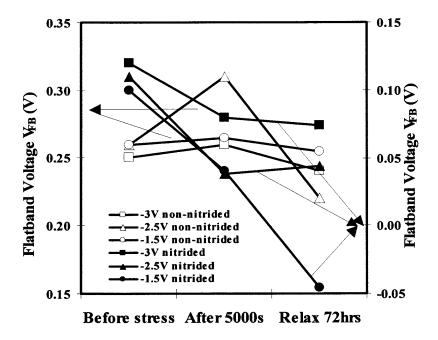

| 6.12          | Shift in flatband voltage, $\Delta V_{FB}$ , after constant voltage stress, under gate injection, of various time periods, for nitrided and non-nitrided Ge MOS capacitors.                                            | 71   |

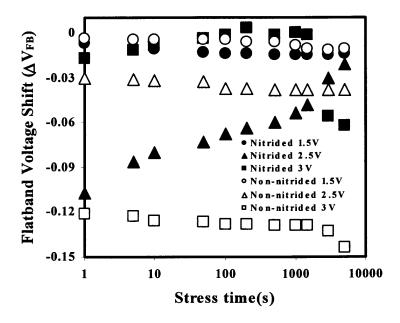

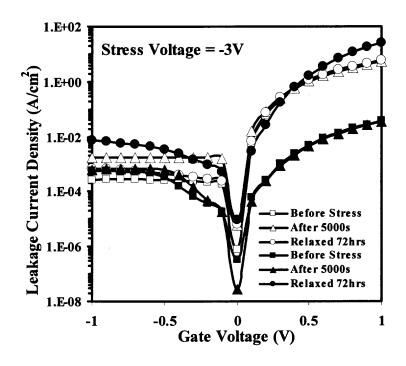

| 6.13          | Shift in flatband voltage, $\Delta V_{FB}$ , after constant voltage stress, under substrate injection, of various time periods, for nitrided and non-nitrided Ge MOS capacitors.                                       | 72   |

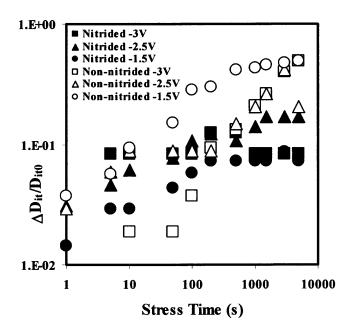

| 6.14          | Increase in interface state density $(D_{it})$ , after stress under gate injection for various time periods, for both nitrided and non-nitrided Ge MOS capacitors                                                      | 73   |

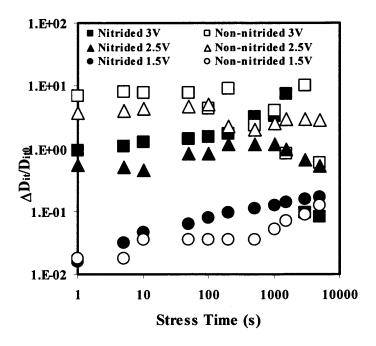

| 6.15          | Increase in interface state density (D <sub>it</sub> ), after stress under substrate injection for various time periods, for both nitrided and non-nitrided Ge MOS capacitors                                          | 74   |

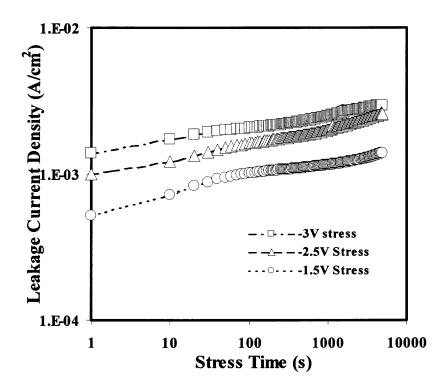

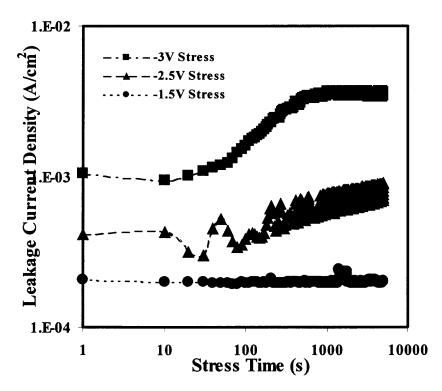

| 6.16          | Gate current as a function of time for a) non-nitrided and b) Ge MOS capacitors for three stress voltage of -1.5V, -2.5V and -3V                                                                                       | 75   |

| 6.17          | Flatband voltage before stress, after 5000s stress and after 72 hours relaxation, for nitrided and non-nitrided Ge MOS capacitors                                                                                      | 76   |

| 6.18          | Leakage current density before stress, after 5000s stress at -3V and after 72 hours relaxation, for nitrided and non-nitrided Ge MOS capacitors                                                                        | 77   |

### **CHAPTER 1**

### **INTRODUCTION**

To fulfill the need of modern information technology i.e. to increase the circuit functionality and performance at lower cost, semiconductor industry has been dramatically decreasing the minimum feature size used to fabricate integrated circuits to the nanometer range. This downscaling of metal-oxide-semiconductor field effect transistors (MOSFETs) implies, among others, the continuous decrease in the thickness of silicon dioxide (SiO<sub>2</sub>) used as the gate oxide film. With this scaling in device dimensions to minimum of 40nm, SiO<sub>2</sub> thickness has to be reduced to keep sufficient current driving capability, as thinner dielectrics improve short channel characteristics.

According to International Technology Roadmap for Semiconductors (ITRS), by the year 2006 electrical equivalent oxide thickness,  $t_{eq}$ , will reach to 1.8nm and gate leakage currents less than  $2\text{mA/cm}^2$  will be required for MOSFET devices for low standby power applications [1]. The microprocessor unit (MPU) applications will further require aggressive scaling of  $t_{eq}$  to 1nm. Amorphous SiO<sub>2</sub>, the natural oxide of Si technology, is only 3-4 monolayers when it reaches the physical thickness of 1.5 - 2 nm. But when the thickness of SiO<sub>2</sub> goes down to 2nm or below, direct tunneling current increases 100 times for every 0.4 - 0.5 nm decrease of thickness [2].

Fig 1.1 shows measured and simulated  $I_G - V_G$  characteristics under inversion conditions of SiO<sub>2</sub> nMOSFETs [3]. As it can be observed at a gate bias of 1V leakage current density increases from  $\sim 10^{-7} \text{A/cm}^2$  to  $\sim 10 \text{A/cm}^2$ , when SiO<sub>2</sub> thickness is decreased from 3.2nm to 1.5nm. Although this leakage current at 1.5nm SiO<sub>2</sub> is still

tolerable for MPU applications with increased failure probabilities, it is simply unacceptable for low standby power applications.

Fig. 1.1 Measured and simulated Ig-Vg characteristics under inversion conditions of SiO2 N- MOSFET devices [3].

Therefore, it has become quite evident that for continuous downscaling of Si CMOS devices, 40 years old SiO<sub>2</sub> technology is leading towards a physical roadblock due to high gate oxide leakage. This increased leakage current in SiO<sub>2</sub> has raised considerable attention on high-κ dielectrics as a suitable replacement of SiO<sub>2</sub>, since they provide the required capacitance at a larger physical thickness than SiO<sub>2</sub> and allow reduction of gate leakage current by suppression of direct tunneling. The ITRS indicates that for CMOS applications, high-κ dielectrics will be needed by the end of year 2005.

Various high-κ dielectrics such as Tantalum Oxide (Ta<sub>2</sub>O<sub>5</sub>), Titanium Oxide (TiO<sub>2</sub>), Aluminum Oxide (Al<sub>2</sub>O<sub>3</sub>), Yttrium Oxide (Y<sub>2</sub>O<sub>3</sub>), Zirconium Oxide (ZrO<sub>2</sub>),

Hafnium Oxide (HfO<sub>2</sub>) [4-6] etc. have been proposed to replace SiO<sub>2</sub>. Among these high- $\kappa$  dielectrics, HfO<sub>2</sub> has emerged as a strong contender because 1) high dielectric constant of ~25-30 (~6-7 times that of SiO<sub>2</sub>), 2) energy band gap of 5.68eV, though much lower than SiO<sub>2</sub> but with band offsets greater than 1eV (1.5eV for electron and 3.4eV for holes), 3) free energy of reaction with Si is about 47.6Kcal/mol at 727°C making it more stable material on Si substrate in comparison to other high-  $\kappa$  dielectrics, 4) unlike other silicides, silicide of Hf can be easily oxidized [7] to form HfO<sub>2</sub>. All these properties of HfO<sub>2</sub> make it an attractive alternative for SiO<sub>2</sub>.

The properties of grown film and interface show a pronounced dependence upon the deposition process and the precise deposition parameters chosen. Each technique has their own set of advantages and disadvantages. However, most of the techniques show some or other kind of interface damage. Sputtering and e-beam assisted depositions create radiation induced surface damage during film growth. All these techniques, therefore, require high temperature annealing which further results in the deterioration of device performance and reliability. Since HfO<sub>2</sub>-Si interface is critical for excellent device characteristics it is important to investigate other reliable deposition techniques for high quality interface.

Another critical drawback is the degradation of carrier mobility in FET channel. In fact, this mobility degradation is so severe that it can be reduced by a factor of 2 [8] in Si MOS devices with HfO<sub>2</sub> as gate dielectric. Many research groups are exploring different ways to enhance carrier mobility, such as the use of strained silicon germanium, SiGe on Si [9] or strained Si on relaxed buffer SiGe layers [10]. Changing the substrate from silicon to germanium could be a possible solution to surface carrier mobility

degradation as Ge has higher carrier mobility (2X for electrons and 4X for holes) in comparison to Si. Originally transistors were fabricated on Ge substrate but lack of stable Ge native oxide has been an obstacle in CMOS device realization in Ge. But recently devices using high-κ gate dielectrics deposited directly on Ge substrate have shown some promise.

The main objective of this research is to evaluate and characterize the MOS devices with HfO<sub>2</sub> as gate dielectrics, deposited by standard thermal evaporation (at Sarnoff Corporation) on Si and Ge substrate as thermal evaporation doesn't produce much damage to the interface and it doesn't require high temperature processing in comparison to other techniques. Second major objective of this research is to study the effect of Ge surface treatment prior to HfO<sub>2</sub> deposition on the reliability of Al/HfO<sub>2</sub>/Ge MOS capacitors using low temperature and stress measurements.

In this dissertation, the second chapter describes the basic properties of high- $\kappa$  dielectrics and what makes them an attractive alternative of SiO<sub>2</sub>. After a short review of the advantages of high- $\kappa$  dielectrics, this chapter reviews the work done by different scientific groups on both silicon and germanium substrate. This chapter analyzes the technical challenges put forth for integration of high- $\kappa$  materials in CMOS technology.

The third chapter gives an overview of the device fabrication and characterization used in this work. It describes each processing step used in fabricating the MOS capacitors. Then, the physical and electrical characterization techniques used in this research have been discussed

Fourth chapter presents the electrical characterization of HfO<sub>2</sub> films deposited by thermal evaporation on Si substrate. Measurements were taken before annealing and after

annealing to see the effect of annealing in these films. It also presents the analysis of experimental data and summarize the performance of MOS capacitors at room temperature as well as at low temperature.

Fifth chapter describes the physical and electrical properties of thermally evaporated HfO<sub>2</sub> films on Ge substrate. Physical characterization of these films has been done using scanning electron microscopy and X-ray photoelectron spectroscopy, while electrical characterization was performed similar to MOS capacitors on Si substrate.

Chapter six compares the HfO<sub>2</sub> films deposited by thermal evaporation and e-beam evaporation with reactive atomic O beam on Ge substrate. Effect of surface treatment prior to gate dielectric deposition has been described. It analyzes the trap energy levels using low temperature measurements and tests the reliability of Al/HfO<sub>2</sub>/Ge MOS capacitors using constant voltage stress measurements.

Finally, chapter seven presents the conclusions of this dissertation and suggestions for further research.

### **CHAPTER 2**

### HIGH-k DIELECTRICS

### 2.1 Background

The continuous scaling of Si CMOS devices has led to the need of increased capacitances per unit area in CMOS conducting channel, which resulted in high gate leakage current. Capacitance can be increased by increasing  $\kappa$  (dielectric constant) or by decreasing the thickness of oxide, shown in eq. (2.1)

$$C_{ox} = \frac{k_{SiO_2} \varepsilon_0}{t_{SiO_2}} = \frac{k_{high-\kappa} \varepsilon_0}{t_{high-\kappa}}$$

(2.1)

Where  $C_{ox}$  is capacitance per unit area,  $k_{SiO2}$  and  $k_{high-\kappa}$  are the dielectric constant of  $SiO_2$  and high- $\kappa$  dielectrics respectively,  $\varepsilon_0$  is the vacuum permittivity, and  $t_{SiO2}$  and  $t_{high-\kappa}$  are the physical thickness of gate dielectric. As  $t_{SiO2}$  can't be reduced below certain limit, the only alternative left is to increase the  $\kappa$  so that a thicker film can be employed compared to  $SiO_2$  while maintaining equivalent  $C_{ox}$ .

Different gate stacks of silicon oxynitride and nitride/oxide films have been studied, showing improved characteristics in terms of leakage current and reliability [11-14]. Fig. 2.1 shows a reduction of  $\sim 10^3 \text{A/cm}^2$  in leakage current density of silicon nitride films grown by different techniques with respect to SiO<sub>2</sub> at  $t_{eq} = 2.1 \text{nm}$ . However, due to relatively low dielectric constants, they can't be scaled down lower than 1 nm. This understanding has raised lot of attention to high- $\kappa$  materials to replace SiO<sub>2</sub>.

Fig. 2.1 Current density of various silicon nitride films with EOT of 2.1 nm. [15]

#### 2.2 Selection Criteria

There are various aspects that need to be taken into consideration before selecting any dielectric material. Obviously the first consideration is the dielectric constant; it should be significantly higher than that of SiO<sub>2</sub>. The replacement dielectric should be thermodynamically stable in contact with Si channel, able to withstand annealing temperatures up to 1050°C and is compatible with CMOS processing. As hot carrier emission into the gate insulator and gate direct-tunneling current is dependent on the barrier height [16, 17], it is desirable that silicon-to-gate oxide barrier height should be sufficiently large for both electrons and holes. In addition, interface trap densities should be close to that of SiO<sub>2</sub> in the silicon bandgap because performance of MOSFETs fundamentally relies on the quality of oxide-Si interface as current flows in Si channel

next to interface. Charge trapping in oxide and reliability of the gate dielectrics are also important in selecting the appropriate material.

Various alternatives have been proposed to replace SiO<sub>2</sub> such as TiO<sub>2</sub> [5,19], ZrO<sub>2</sub> [20], HfO<sub>2</sub> [21], Y<sub>2</sub>O<sub>3</sub> [22], Al<sub>2</sub>O<sub>3</sub> [23, 24], Ta<sub>2</sub>O<sub>5</sub> [25, 26], and La<sub>2</sub>O<sub>3</sub> [27] as well as their silicates and aluminates. Many of the materials initially chosen were inspired by memory capacitor application [28] such as Ta<sub>2</sub>O<sub>5</sub> [29], SrTiO<sub>3</sub> [30] and Al<sub>2</sub>O<sub>3</sub> [31], which have dielectric constants ranging from 10 to 80, and have been employed mainly due to their maturity in memory capacitor applications. However, except Al<sub>2</sub>O<sub>3</sub>, these materials are not thermodynamically stable in direct contact with Si (thermodynamic stability is not a requirement for memory capacitors, since the dielectric is in contact with the electrodes, which are typically nitrided poly-Si or metal). Also, as band gap tends to vary inversely with dielectric constant, one or both of their band offsets are under 1eV leaving them unacceptable for transistor application, shown in Fig. 2.2.

Table 2.1 lists some potential dielectric materials along with their properties to replace silicon dioxide. Though  $TiO_2$  has high permittivity of ~80-100 depending upon the method of deposition, but it has been proved to be thermodynamically unstable with Si [34]. Also, it forms a reaction layer both at channel interface and metal electrodes. Among group III candidate dielectrics,  $Al_2O_3$  is robust and stable with Si, has a larger bandgap of 8.8eV but its relatively low dielectric constant ( $\kappa$ ~8-13) renders it to be short-term solution for industry needs. Various integration issues such as high fixed charge density and boron penetration have also been reported [23, 24].

| Dielectric                     | Dielectric<br>Constant | Bandgap<br>(eV) | Leakage current reduction w.r.t. SiO <sub>2</sub> | Thermal stability w.r.t.<br>Si |

|--------------------------------|------------------------|-----------------|---------------------------------------------------|--------------------------------|

| SiO <sub>2</sub>               | 3.9                    | 9               | N/A                                               | >1050°C                        |

| $Si_3N_4$                      | 7                      | 5.3             | $10^3 - 10^4 \text{ X}$                           | >1050°C                        |

| $Ta_2O_5$                      | 25                     | 4.4             |                                                   | Not thermodynamically stable   |

| $TiO_2$                        | ~80                    | 3.5             |                                                   |                                |

| $ZrO_2$                        | ~23                    | 5.8             | $10^4 - 10^5 \text{ X}$                           | ~900°C                         |

| HfO <sub>2</sub>               | ~25                    | 6               | $10^4 - 10^5 \text{ X}$                           | ~950°C                         |

| $Y_2O_3$                       | ~15                    | 6               | $10^4 - 10^5 \text{ X}$                           | Silicate formation             |

| $Al_2O_3$                      | ~10                    | 8.8             | $10^2 - 10^3 \text{ X}$                           | ~1000°C RTA                    |

| La <sub>2</sub> O <sub>3</sub> | ~21                    | 6               |                                                   |                                |

**Table 2.1** Various dielectric materials and their properties with respect to Silicon [32, 33].

Fig. 2.2 Band offsets of various high-k dielectrics with respect to silicon [33].

HfO<sub>2</sub> and ZrO<sub>2</sub> have high dielectric constants (20~25), high stability on Si, sufficient band offsets to act as barrier for electrons and holes (shown in Fig. 2.2) and can withstand high annealing temperature up to 900°C. However, ZrO<sub>2</sub> reacts with poly-Si and Si substrate [35, 36], which leaves HfO<sub>2</sub> as an only but attractive replacement for SiO<sub>2</sub>.

HfO<sub>2</sub> being a leading candidate has many advantageous qualities including high dielectric constant (~25), large heat of formation (-271 kcal/mol), and band offsets of 1.5eV and 3.4eV for electrons and holes, respectively. It's compatibility with poly-Si and CMOS processing add more support to its suitability.

### 2.3 Different Deposition Techniques

Since these high- $\kappa$  materials need to be deposited on substrate, different research groups have been trying different techniques to get the optimum performance. Films are deposited in a unique way in each technique depending upon the deposition process and the deposition parameters chosen. Atomic layer deposition (ALD) is the most popular technique because of the controllable thickness and good step coverage of HfO<sub>2</sub> [37, 38]. However, in ALD, growth of the film is inversely proportional to temperature [39] that mean substrate temperature has to be 300°C [38, 40] to have controlled growth of film. This high temperature growth induces of degree of crystallanity in the oxide film, highly undesirable for CMOS technology. Another problem with chemical vapor deposition techniques is choosing the right precursor to form HfO<sub>2</sub>, as it is directly related to impurities in the film [41]. Another popular technique is metal-organic chemical vapor deposition because of good film conformality and control on deposition rates. However,

choice of precursor, deposition temperature and incorporation of carbon impurities are major concern in this technique [8].

There are other alternative techniques that people have tried such as ultraviolet ozone oxidation [42], sputtering [43, 44], reactive atomic beam deposition [45], evaporation with ion-assisted beam deposition [46], etc. However, most of these techniques show some or other kind of interface damage, for example sputtering and ebeam assisted depositions create radiation induced surface damage during film growth. Also these techniques require high temperature annealing which further results in the deterioration of device performance and reliability. Since HfO<sub>2</sub>-Si interface in important for excellent device characteristics it is important to investigate other reliable deposition techniques for high quality interface.

### 2.4 Integration Issues

In spite of having all the desirable qualities, still it's a challenge to bring HfO<sub>2</sub> in mainstream CMOS processing. Firstly, MOS capacitors fabricated with HfO<sub>2</sub> as gate oxide show large hysteresis and shift in flatband voltage (V<sub>FB</sub>) [47, 48]. This is mainly because of trapped charge in the oxide layer as well as at the interface. Defects at interface are generated due to lattice mismatch of HfO<sub>2</sub> and Si, which can be reduced by growing a thin interfacial layer of SiO<sub>2</sub>. However, it will lower the effective oxide thickness (EOT) of the gate stacks. Another factor that affects the V<sub>T</sub> instability is the electron trapping and de-trapping taking place in HfO<sub>2</sub> bulk defects [49, 50]. Charge trapping also creates threshold voltage (V<sub>T</sub>) instabilities by continuing the shift under device stress.

Another challenge with high- $\kappa$  dielectrics is oxygen diffusivity and boron penetration during high-temperature annealing for source/drain activation. This lack of stopping power against  $O_2$  leads to significant interfacial layer under low partial pressures of oxygen at low ( $400^{\circ}\text{C} - 600^{\circ}\text{C}$ ) temperatures [51], ultimately bringing down the EOT. Boron penetration through HfO<sub>2</sub> films after annealing, at temperatures as low as 950°C, has been observed [52] resulting in interface degradation and  $V_T$  shifts. Nitridation of the Si surface using prior to a deposition of a high- $\kappa$  dielectric has been shown to be effective in achieving low EOT and preventing boron penetration [52, 53]. However, it results in higher positive interface charges [54], which leads to higher hysteresis and reduced channel mobility.

Major concern in high- $\kappa$  dielectrics is the degradation of surface carrier mobility in MOSFET channel. Fig. 2.3 shows the electron mobility of high- $\kappa$  material with respect to SiO<sub>2</sub>.

Fig. 2.3 Electron mobility of various high-k materials with respect to silicon [55].

Fischetti *et al* [55] explained that the reduced channel carrier mobility of high-κ material is actually related to their dielectric constant. The static dielectric constant of an insulator results from the combination of the ionic and the electronic polarization. Due to the larger bandgap of insulators, there is little electronic polarization. Therefore a higher dielectric constant can only originate from a larger ionic polarization of "soft" metal-oxygen bonds. These soft bonds are associated with low-energy phonons, which are optical in nature because of the ionic character of the atomic bonds in most insulators. This suggests that the higher the dielectric constant, lower the surface-optical-phonon-limited mobility. Another reason for lower mobility could be the Coulomb scattering due to fixed and trapped charges in the high-κ films [56].

### 2.5 Ge as a Substrate

Low surface carrier mobility in the inversion channel of high-κ Si MOSFETs has brought back the long forgotten Ge into CMOS technology. Ge has large hole mobility of 1900cm²/Vs (4X of Si) in comparison to any other common semiconductors and electron mobility of 3900cm²/Vs (2X of Si). These high motilities of Ge can provide drive current enhancement for both p- and n-MOSFETs. Furthermore, Ge has direct bandgap of 0.66eV, giving it an added advantage of being suitable for fiber-optical communication device applications.

The very first point contact transistor (by Brattain and Bardeen, 1947) and first integrated circuit (by Jack Kilby, 1958) both were fabricated on Ge. However, photoelectron spectroscopy studies have shown that annealing of GeO<sub>2</sub> transforms it into GeO on the surface, subsequently thermally desorbs from the surface [57]. The unstable

nature of GeO<sub>2</sub> and the fact it's water soluble, were the one of the biggest obstruction in the realization of very large-scale integration of CMOS devices in Ge.

Scientists have tried various procedures of depositing gate dielectrics involving plasma, pyrolytic and sputter deposition of different oxides and nitrides [58-60]. Most successful effort involved covering the  $GeO_2$  with an insulator  $Al_2O_3$  using molecular beam deposition resulted in interface state densities as low as  $1 \times 10^{11}$  eV<sup>-1</sup>cm<sup>-2</sup> [61]. To obtain more stable oxide different gate stacks of Ge oxynitride ( $GeO_xN_y$ ) using either thermal or plasma anodic nitridation [62, 63] or GeON with low temperature gate oxide were used to form Ge MOSFETs [64].  $SiO_2$  has also been explored as a non-native insulator on Ge [65]. However, its use on Ge has been far less effective in comparison to Si because of the poor interface between Ge and  $SiO_2$ . Most of the historical work has been done with the idea of depositing dielectrics on Ge to obtain films with good interface and bulk characteristics, but these gate stacks are very thick ranging from 5nm to 50nm unable to offer a  $t_{eq}$  of less than 1nm for sub-20nm regime.

### 2.6 High-κ Dielectrics on Ge

Advancements in thin films deposition techniques allowed the deposition of high-κ films in nanometer range on Si. Recently, these techniques have been adapted to deposit thin high-κ dielectrics (t<sub>eq</sub> <1 nm) on Ge as well. Promising results have been reported showing increase hole mobility over Si p-MOSFET's with the same thin high-κ dielectrics. Chui et al [66] reported ultra-thin ZrO<sub>2</sub> (0.6–1nm) on Ge p-MOSFETS with twice the low-field hole mobility of Si MOSFETs, while Ritenour et al [67] have reported

HfO<sub>2</sub> on Ge p-MOSFETs showing 40% hole mobility enhancement over a Si control with an identical HfO<sub>2</sub> dielectric.

In spite of Ge p-MOSFETs showing improvement in terms of hole mobility, devices made by depositing HfO<sub>2</sub> directly on Ge are too leaky or show significant hysteresis. This deterioration in electrical performance is mainly due to the formation of interfacial layer during the HfO<sub>2</sub> deposition. Ge surface treatment prior to gate dielectrics deposition found to be an effective way in improving the MOS device quality. Different kind of Ge surface passivation has been done by forming thin Ge oxynitride [68, 69], by NH<sub>3</sub> annealing [70] or by SiH<sub>4</sub> annealing [71]. Recently, it has been demonstrated that initial treatment of Ge surface by atomic N beam seems to improve the physical and electrical characteristics of MOS capacitors [72]. Though incorporation of nitrogen at interface introduce positive traps in the films. Still, role of nitrogen on interfacial and bulk characteristics of the films is not well understood.

In this research, we are depositing HfO<sub>2</sub> films on silicon and germanium substrate by thermal evaporation as thermal evaporation, unlike other physical vapor deposition techniques, doesn't damage the substrate surface and it doesn't require high temperature processing. Films deposited by thermal evaporation on Ge substrate are compared to films deposited by e-beam evaporation with reactive atomic O beam. Also, effect of Ge surface treatment prior to gate oxide deposition was studied using low temperature measurements and stress measurements.

### CHAPTER – 3

### DEVICE FABRICATION AND CHARACTERIZATION

### 3.1 Device Fabrication

Three sets of MOS capacitors were fabricated with: - 1) thermally evaporated HfO<sub>2</sub> on Silicon substrate, 2) thermally evaporated HfO<sub>2</sub> on Germanium substrate, 3) HfO<sub>2</sub> deposited by e-beam evaporation with reactive atomic O beam on Germanium substrate. Thermal evaporation of hafnium was done at Sarnoff Corporation, while e-beam evaporation of hafnium was carried out at IBM. After gate oxide deposition, MOS capacitor fabrication has been performed in the Microelectronics Fabrication Center at NJIT. A detailed description of the individual process steps is presented below in section 3.1.1 through 3.1.8.

### 3.1.1 Starting Materials

For silicon-based devices, the starting material was 3" n-type (boron doped), <100> oriented CMOS grade silicon wafers with a sheet resistivity of 10-20  $\Omega$ -cm. For germanium-based devices, 2" n-type (antimony doped) <100> germanium wafers with sheet resistivity of 0.4 and 0.1  $\Omega$ -cm were used.

### 3.1.2 Cleaning

In thermal evaporation process, both Ge and Si wafers were cleaned by standard RCA clean (RCA-1 and RCA-2) followed by 50:1 HF dip for 15 minutes immediately before the deposition of the HfO<sub>2</sub> films.

In e-beam evaporation of HfO<sub>2</sub>, Ge wafers were first cleaned by standard solvent cleaning and a de-ionized water (DI) water rinse. Then a cyclical rinse of H<sub>2</sub>O<sub>2</sub>, HCl/H<sub>2</sub>O and DI water was done to further clean the wafer surface.

## 3.1.3 Surface Nitridation

For some device, *in-situ* surface-nitridation of the Ge substrates took place at 350°C-600°C by exposure to an atomic N beam from a remote RF source at 350 W for 30 s, prior to HfO<sub>2</sub> deposition.

# 3.1.4 HfO<sub>2</sub> Deposition

HfO<sub>2</sub> films of different thickness (50 & 60nm on Si substrate and 5 & 10nm on Ge substrate) were deposited on Si and Ge wafers by standard thermal evaporation. Oxygen was added at constant partial pressure during evaporation. The base pressure was maintained at 10<sup>-6</sup> Torr before oxygen was added. As oxygen was added during evaporation, the pressure in the chamber increased to 10<sup>-4</sup> Torr. Tungsten boats were used in evaporating hafnium. Films were deposited at room temperatures, but the measured substrate temperature was around 30-35°C due to source-induced substrate heating. No residual gas analysis was performed during evaporation.

In e-beam evaporation of HfO<sub>2</sub> on Ge, first a protective layer of Ge oxide was formed by immersion in a solution of NH<sub>4</sub>OH/H<sub>2</sub>O<sub>2</sub>/H<sub>2</sub>O. The protective oxide was then removed in ultrahigh vacuum by thermal adsorption. Following oxide adsorption, hafnium oxide was grown at 50°C to 300°C using a reactive atomic O beam from RF discharge source and Hf evaporated from an electron-beam source. HfO<sub>2</sub> films were then further subjected to UV-ozone oxidation at 600 Torr for 60 min., without breaking vacuum, to produce good-quality oxide film.

# 3.1.5 Annealing

After oxide deposition wafers were annealed at different temperatures in different ambience shown in table 3.1. In silicon devices annealing was performed after metal gate deposition.

| Substrate | Annealing Temperatures (°C) |     | Annealing Environment                     |  |

|-----------|-----------------------------|-----|-------------------------------------------|--|

| Silicon   | 350                         | 450 | FGA (N <sub>2</sub> /H <sub>2</sub> : 5%) |  |

| Germanium | 500                         | 550 | N <sub>2</sub>                            |  |

|           | 450                         |     | FGA (N <sub>2</sub> /H <sub>2</sub> : 5%) |  |

**Table 3.1** Various annealing temperature with annealing environments.

# 3.1.6 Metal Deposition

After having undergone the various conditions of annealing the wafers were deposited with metal (Al) using sputtering technique.

# 3.1.7 Photolithography

Photolithography was conducted to to produce devices with diameters 50um 100um, 200um, 250um, 300um, 400um, and 500um.

# 3.1.8 Etching

After photolithography was done, metal etching was done using aluminum etchant (phosphoric, nitric acid, acetic acid and de-ionized water) at 45°C. After metal etching,

photoresist was removed using m-pyrol cleaning (methyl pyrolidine - an acidic mixture). The processing temperature is maintained at 95°C.

The two fabrication processes are summarized in table 3.2 and 3.3.

| S. No. | Process                     | Details                                   |  |

|--------|-----------------------------|-------------------------------------------|--|

| 1.     | Cleaning                    | RCA clean → 50:1 HF dip, 15               |  |

|        |                             | minutes                                   |  |

| 2.     | HfO <sub>2</sub> deposition | Thermal evaporation                       |  |

| 3.     | Annealing                   | FGA, 20min, 350°C & 450°C (Si)            |  |

|        |                             | N <sub>2</sub> , 20min, 500°C, 550°C (Ge) |  |

| 4.     | Metal Deposition            | Al, Sputtering                            |  |

| 5.     | Patterning                  | Photolithography                          |  |

| 6.     | Metal Etching               | Phosphoric acid, nitric acid, acetic      |  |

|        |                             | acid and DI water, 45°C                   |  |

| 7.     | Photoresist Removal         | Methyl pyrolidine, 95°C                   |  |

| 8.     | Backside Metal              | Al, Sputtering → 350°C FGA                |  |

|        | Deposition and Anneal       |                                           |  |

**Table 3.2:** Process flow of Si and Ge MOS capacitors with thermally evaporated  $HfO_2$  as gate dielectric.

| S. No. | Process                        | Details                                                                                            |  |

|--------|--------------------------------|----------------------------------------------------------------------------------------------------|--|

| 1.     | Cleaning                       | Standard solvent and DI water rinse,                                                               |  |

|        |                                | Cyclical rinse of H <sub>2</sub> O <sub>2</sub> , DI, HCl,                                         |  |

| 2.     | HfO <sub>2</sub> formation and | Dip in NH <sub>4</sub> OH/H <sub>2</sub> O <sub>2</sub> /H <sub>2</sub> O $\longrightarrow$ 650°C, |  |

|        | desorption                     | 30min.                                                                                             |  |

| 3.     | Surface Nitridation            | N: 500°C, 30s, RF 350W                                                                             |  |

| 4.     | HfO <sub>2</sub> Deposition    | E-beam evaporation → UHV Ozone                                                                     |  |

|        |                                | oxidation                                                                                          |  |

| 5.     | Annealing                      | FGA, 20min, 450°C                                                                                  |  |

| 6.     | Metal Deposition               | Al, Sputtering                                                                                     |  |

| 7.     | Patterning                     | Photolithography                                                                                   |  |

| 8.     | Metal Etching                  | Phosphoric acid, nitric acid, acetic acid                                                          |  |

|        |                                | and DI water, 45°C                                                                                 |  |

| 9.     | Photoresist Removal            | Methyl pyrolidine, 95°C                                                                            |  |

| 10.    | Backside Metal                 | Al, Sputtering → 350°C FGA                                                                         |  |

|        | Deposition and Anneal          | AI, Sputtering - 330 C FGA                                                                         |  |

**Table 3.3** Process flow of Ge MOS capacitors with HfO<sub>2</sub>, deposited by e-beam evaporation with reactive atomic O beam as gate dielectric.

# 3.2 Physical Characterization

It is increasingly difficult to characterize ultra-thin gate dielectric films (typically 0.1 nm to 3.0 nm) used in MOS devices. Input from various physical characterization techniques is needed to improve the knowledge of structure and composition of these thin films. Scanning electron microscopy evaluates the surface structure of film in terms roughness and non-uniformity, while X-ray photoelectron spectroscopy characterize the elemental and molecular nature of thin films. It can determine the nature of bonds present between different elements in the film depending upon their binding energy.

## 3.2.1 Scanning Electron Microscopy

Field emission scanning electron microscopy (FESEM) [72] was used to study the surface of films after and before annealing. The main advantage of FESEM is that high quality images of insulating surfaces can be taken with nanometer resolution and negligible electrical charging of samples, without the need of conductive coating.

# 3.2.2 X-ray Photoelectron Spectroscopy

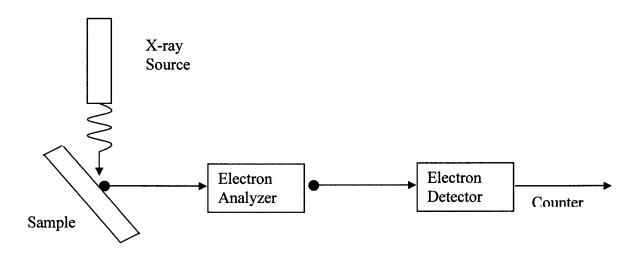

X-ray photoelectron spectroscopy, XPS is primarily used for identifying chemical composition of the films. Electrons can be emitted from any orbital with photoemission occurring for X-ray energies exceeding the binding energy. This is illustrated with the energy band diagram in Fig. 4.2 and the schematic in Fig. 4.3. Primary X-rays of 1-2 keV energy eject photoelectrons from the sample. The measured energy of the ejected electrons at the spectrometer  $E_{sp}$  is related to the binding energy  $E_{b}$ , referenced to the Fermi energy  $E_{F}$  by

$$E_b = h\nu - E_{sp} - q\phi_{sp} \tag{3.1}$$

where hv is the energy of primary X-ray and  $\phi_{sp}$  is the work function of the spectrometer (3 to 4 eV).

Fig. 3.1 Electronic processes in X-ray photoelectron Spectroscopy [72].

## Fig. 3.2 XPS measurement schematic

The electron binding energy is influenced by its chemical surroundings making it suitable for determining chemical states. Though X-rays possess no charge, electron emission from the sample may cause positive sample charging, especially for insulators.

#### 3.3 Electrical Characterization

Measurements of the electrical properties, parameters extracted from these measurements and control over these parameters lead to stable and high performance MOS devices. Bulk oxide and oxide-substrate interface are two major regions of the MOS system. Charges in these two regions are undesirable because they adversely affect the device performance and stability. The MOS capacitor is being used to study the electrical characteristics as it has the advantage of simplicity of fabrication and analysis. Following measurements techniques have been employed in characterizing the charges present in MOS capacitors using HfO<sub>2</sub> as gate dielectric.

# 3.3.1 High Frequency and Low Frequency C-V Measurements

The high frequency (HF) and low frequency (LF) measurements were carried out using Boonton Capacitance meter and HP 4284A. Measurements were carried out from high frequency of 1Mz to low frequency of 1kHz. The devices were probed using cascade microtech probe station. From the low frequency curve and the high frequency curve we can get information of the interface states. Interface states or "fast states" can be detected as a stretch out of the high frequency C-V curve of a MOS capacitor or a distortion in the

LF C-V curve. Oxide charge on the other hand causes a rigid shift along the voltage axis of the high frequency CV curve, and is detected as a change in the flat band voltage of the device [49]. A shift in the HF curve indicates the effect of the annealing effect. A post deposition anneal can reduce the oxide charges.

#### 3.3.2 Conductance Measurement

The conductance measurements were carried out at various frequencies using HP 4284A. The frequencies were 1 KHz, 10kHz, 100 KHz, 1 MHz. This was used to measure the interface state density (D<sub>it</sub>) which was computed using equation (3.4) and (3.5) [73].

$$\frac{G_P}{\omega} = \frac{\omega G_m C_{ox}^2}{G_m^2 + \omega^2 (C_{ox} - C_m)^2}$$

(3.2)

$$D_{ii} = \frac{2.5}{q} \left( \frac{G_P}{\omega} \right)_{\text{max}} \tag{3.3}$$

Where  $G_P$  is interface trap conductance,  $G_m$  is the conductance measured,  $C_{ox}$  is the accumulation capacitance,  $\omega$  is the frequency,  $C_m$  is the measured capacitance at the particular frequency and gate voltage.

## 3.3.3 Estimation of Interface State Density by Terman Method

3.3.3.1 Plotting the Ideal C-V Curve. Ideal C-V curve can be plotted by calculating gate bias voltage  $V_g$  for different surface potential  $\psi_s$  and calculating the corresponding differential capacitance. Gate bias voltage is given by

$$V_g = V_{FB}^0 + \frac{Q_S}{C_m} + \psi_S \tag{3.4}$$

here  $V_{FB}^{o}$  is ideal flatband voltage,  $C_{ox}$  isgate oxide capacitance, and  $Q_{s}$  is the charge in semiconductor given by,

$$Q_{S} = \sqrt{2\left(\frac{kT}{qL_{D}}\right)} \left\{ \left[\frac{q\psi_{s}}{kT} + \exp\left(\frac{-q\psi_{s}}{kT}\right) - 1\right] + \left(\frac{n_{i}}{N_{d}}\right)^{2} \left[\exp\left(\frac{q\psi_{s}}{kT}\right) - 1\right] \right\}^{\frac{1}{2}}$$

(3.5)

here k is Boltzman's constant, T is temperature,  $n_i$  is intrinsic carrier concentration and  $L_D$  is Debye length calculated as,

$$L_D = \sqrt{\frac{\varepsilon_{Si}kT}{q^2N_d}} \tag{3.6}$$

here  $\varepsilon_{Si}$  is dielectric constant of silicon, and  $N_d$  is doping concentration.

Putting all the constant terms in eq. (3.6) at room temperature