## New Jersey Institute of Technology

## Digital Commons @ NJIT

**Dissertations**

**Electronic Theses and Dissertations**

Spring 5-31-2005

# A versatile programming model for dynamic task scheduling on cluster computers

Dejiang Jin New Jersey Institute of Technology

Follow this and additional works at: https://digitalcommons.njit.edu/dissertations

Part of the Computer Engineering Commons

#### **Recommended Citation**

Jin, Dejiang, "A versatile programming model for dynamic task scheduling on cluster computers" (2005). Dissertations. 699.

https://digitalcommons.njit.edu/dissertations/699

This Dissertation is brought to you for free and open access by the Electronic Theses and Dissertations at Digital Commons @ NJIT. It has been accepted for inclusion in Dissertations by an authorized administrator of Digital Commons @ NJIT. For more information, please contact digitalcommons@njit.edu.

# **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

## **ABSTRACT**

# A VERSATILE PROGRAMMING MODEL FOR DYNAMIC TASK SCHEDULING ON CLUSTER COMPUTERS

## by Dejiang Jin

This dissertation studies the development of application programs for parallel and distributed computer systems, especially PC clusters. A methodology is proposed to increase the efficiency of code development, the productivity of programmers and enhance performance of executing the developed programs on PC clusters while facilitating improvement of scalability and code portability of these programs. A new programming model, named the Super-Programming Model (SPM), is created. Programs are developed assuming an instruction set architecture comprised of Super-Instructions (SIs). SPM models the target system as a large Virtual Machine (VM); VM contains functional units which are underlain with sub-computer systems and SIs are implemented with codes. When these functional units execute SIs, their codes will run on member computers to perform the corresponding operations.

This approach resembles the process of designing instruction sets for microprocessors but the VM employs much coarser instructions and data structures. SIs use Super-Data Blocks (SDBs) as their operands. Each SI is assigned to a single member computer and is indivisible (i.e., its implementation is not interrupted for I/O). SIs have predictable execution times because SDB sizes are limited by predefined thresholds. These qualities of SIs help dynamic load balancing. Employing software to implement instructions makes this approach more flexible. The developed programs fit to architectures of cluster systems better. SPM provides mechanisms, such as dynamic load balancing, to assure the efficient execution of programs. The vast majority of current programming models lack such mechanisms

for distributed environments that suffer from long communication latencies. Since SPM employs coarse-grain tasks, the overall management overhead is small. SDB access can often overlap the execution of other SIs; a cache system further decreases average memory latencies. Since all SDBs are virtual entities, with the runtime system support, they can be accessed in parallel and efficiently minimizes additional constraints to parallelism from underlying computer systems.

In this research, a reference implementation of VM has been developed. A performance estimation model is developed that takes these features into account. Finally, the definition of scalability for parallel/distributed processing is refined to represent a multi-dimensional entity. Sample cases are analyzed.

# A VERSATILE PROGRAMMING MODEL FOR DYNAMIC TASK SCHEDULING ON CLUSTER COMPUTERS

by Dejiang Jin

# A Dissertation Submitted to the Faculty of New Jersey Institute of Technology in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy in Computer Engineering

Department of Electrical and Computer Engineering

May 2005

Copyright © 2005 by Dejiang Jin ALL RIGHTS RESERVED

## APPROVAL PAGE

# A VERSATILE PROGRAMMING MODEL FOR DYNAMIC TASK SCHEDULING ON CLUSTER COMPUTERS

## **Dejiang Jin**

| Dr. Sotirios G. Ziavras, Dissertation Advisor<br>Professor of Electrical and Computer Engineering, NJIT       | 'Date' |

|---------------------------------------------------------------------------------------------------------------|--------|

| Dr. Alexandrok Gerbessiotis, Committee Member<br>Associate Professor of Computer Science, NJIT                | Date   |

| Dr. Sui-Hoi (Edwin) Hou, Committee Member<br>Associate Professor of Electrical and Computer Engineering, NJIT | Date   |

| Dr. Roberto Rojas-Cessa, Committee Member<br>Assistant Professor of Electrical and Computer Engineering, NJIT | Date   |

| Dr. Jie Hu, Committee Member Assistant Professor of Electrical and Computer Engineering, NJIT                 | Date   |

#### BIOGRAPHICAL SKETCH

Author: Dejiang Jin

**Degree:** Doctor of Philosophy

**Date:** May 2005

## Undergraduate and Graduate Education:

- Doctor of Philosophy in Computer Engineering,

New Jersey Institute of Technology, Newark, NJ, USA 2005

- Master of Science in Computer Science,

New Jersey Institute of Technology, Newark, NJ, 2000

- Master of Science in Materials Science,

Wuhan University of Technology, Wuhan, P. R. China, 1991

- Bachelor of Science in Chemical Physics,

University of Science & Technology of China, Hefei, P. R. China, 1986

Major: Computer Engineering

#### Presentations and Publications:

- D. Jin and S.G. Ziavras, "Scalability: A Multidimensional Entity," *IEEE Transactions on Parallel and Distributed Systems*, April 2005 (Submitted).

- D. Jin and S.G. Ziavras, "Modeling Distributed Data Representation and its Effect on Parallel Data Accesses," *Journal of Parallel and Distributed Computing, Special Issue on Design and Performance of Networks for Super-, Cluster-, and Grid-Computing*, 2004 (accepted).

- D. Jin and S.G. Ziavras, "A Super-Programming Approach for Mining Association Rules in Parallel on PC Clusters," *IEEE Transactions on Parallel and Distributed Systems*, Vol. 15, 9, p783-794, Sept. 2004.

- D. Jin and S.G. Ziavras, "A Super-Programming Technique for Large Sparse Matrix Multiplication on PC Clusters," *IEICE Transactions on Information and Systems, Special Issue on Hardware/Software Support for High Performance Scientific and Engineering Computing*, Vol. E87-D, 7, p1774-1781, July 2004.

- D. Jin and S.G. Ziavras, "Load Balancing on PC Clusters with the Super-Programming Model," Workshop on Compile/Runtime Techniques for Parallel Computing (in conjunction with the International Conference on Parallel Processing-ICPP03), Kaohsiung, Taiwan, Oct. 6-9, 2003.

- D. Jin and S.G. Ziavras, "A Super-Programming Technique for Large Sparse Matrix Multiplication on PC Clusters," 2nd Workshop on Hardware/Software Support for High performance Scientific and Engineering Computing (SHPSEC-03) [in conjunction with the 12th International Conference on Parallel Architectures and Compilation Techniques (PACT-03)], New Orleans, Louisiana, Sep. 27-Oct. 1, 2003.

献给世界上最伟大的父母. 是他们一如既往的鼓励与支持使我能有勇气和力量不断 探索这无限奇妙的世界.

To the greatest parents in the world. With their support, encourage and guide forever, I could keep on exploring the wonderful world.

#### ACKNOWLEDGMENT

First of all, I would like to express my deepest appreciation to my advisor, Dr. Sotirios G. Ziavras, for his endless encouragement and support through my PhD study at NJIT. His motivation inspires me to move forward in my dissertation research. As my research supervisor, he not only provided countless resources, invaluable insight, and intuition, but also constantly gave me support, encouragement, and reassurance. Greatest thanks give to his enduring patience. I also would like to thank all my committee members, Dr. Alexandros Gerbessiotis, Dr. Sui-Hoi (Edwin) Hou, Dr. Roberto Rojas-Cessa and Dr. Jie Hu for their activel participation.

I also wish to give a special thank to Dr. David Perel for his technical guidance and assistance over the years. I wish to thank Mr. Dan Henderson and the Hashimoto family and fellowship program. Because of their generosity, I was granted a Hashimoto Fellowship for 2004/2005 academic year. Many of my fellow graduate students in the Computer Architecture Research Laboratory are deserving of recognition for their support.

Especially, I wish to thank my father, Limin Jin, and mother Wanzhu Sheng. It is impossible to successfully complete my research without their support in spirit and help in family matters.

| C | hapt | er     |                                                            | Page |

|---|------|--------|------------------------------------------------------------|------|

| 1 | INT  | RODU   | CTION                                                      | . 1  |

|   | 1.1  | Resea  | arch Motivations and Objectives                            | . 1  |

|   |      | 1.1.1  | Problem Statement                                          | . 1  |

|   |      | 1.1.2  | Motivations                                                | . 2  |

|   |      | 1.1.3  | Objectives                                                 | . 3  |

|   | 1.2  | Backg  | ground in Programming Models and Computer Systems          | . 5  |

|   |      | 1.2.1  | Programming Models                                         | . 5  |

|   |      | 1.2.2  | Requirements of Programming Models                         | . 7  |

|   |      | 1.2.3  | Evolution of Systems and Programming Models                | . 8  |

|   | 1.3  | Cluste | ered Computer Systems                                      | 9    |

|   |      | 1.3.1  | Cluster Technology and PC Clusters                         | . 9  |

|   |      | 1.3.2  | More Characteristics of PC Cluster Systems                 | 10   |

|   | 1.4  | Backg  | ground in Programming PC Cluster Systems                   | 10   |

|   |      | 1.4.1  | Programming Model Requirements for PC Cluster Systems      | 10   |

|   |      | 1.4.2  | Existing Programming Models                                | 12   |

|   |      | 1.4.3  | Problems with Current Programming Models for PC Clusters . | 17   |

|   | 1.5  | Resea  | rch Methodology                                            | 20   |

|   | 1.6  | Outlin | ne of This Dissertation                                    | 21   |

| 2 | SUF  | ER-PF  | ROGRAMMING MODEL (SPM)                                     | 23   |

|   | 2.1  | Overv  | riew of the Super-Programming Model                        | 23   |

|   | 2.2  | Super  | -Instruction Set Architecture                              | 25   |

| C. | napt | e <b>r</b>                                             | Page |

|----|------|--------------------------------------------------------|------|

|    |      | 2.2.1 Super-Instructions and Their Features            | . 25 |

|    |      | 2.2.2 Functionality of Super-Instruction Sets          | . 26 |

|    | 2.3  | Programming with SPM                                   | . 27 |

|    |      | 2.3.1 Super-Functions                                  | . 27 |

|    |      | 2.3.2 Functionality of Super-Functions                 | . 27 |

|    | 2.4  | Execution of Super-Programs                            | . 28 |

| 3  | THE  | E RUNTIME SUPPORT SYSTEM AND A REFERENCE MPLEMENTATION |      |

|    | 3.1  | Structure of the Runtime Support System                | . 31 |

|    |      | 3.1.1 Logical Structure of the Runtime Support System  | . 32 |

|    |      | 3.1.2 Physical Structure of the Runtime Support System | . 33 |

|    | 3.2  | Task Distribution System                               | . 35 |

|    |      | 3.2.1 Task Center                                      | . 36 |

|    |      | 3.2.2 Task Pool                                        | . 37 |

|    |      | 3.2.3 Task Agent                                       | . 38 |

|    |      | 3.2.4 Reference Implementation                         | . 38 |

|    | 3.3  | Task Execution System                                  | . 41 |

|    | 3.4  | Data Distribution System                               | . 43 |

|    |      | 3.4.1 Data Center                                      | . 43 |

|    |      | 3.4.2 Data Agent                                       | . 44 |

|    |      | 3.4.3 Reference Implementation                         | . 45 |

|    | 3.5  | Runtime Management System                              | . 47 |

| $\mathbf{C}$ | hapte | er    | P                                                                       | age |

|--------------|-------|-------|-------------------------------------------------------------------------|-----|

| 4            | EXA   | MPLE  | S OF PROGRAM DEVELOPMENT UNDER SPM                                      | 49  |

|              | 4.1   | Exam  | ple 1: Mining Association Rules                                         | 49  |

|              |       | 4.1.1 | Basic Concepts in Mining Association Rules                              | 49  |

|              |       | 4.1.2 | The Super-Data Blocks for Mining Association Rules                      | 50  |

|              |       | 4.1.3 | The Super-Instruction Set for Mining Association Rules                  | 50  |

|              |       | 4.1.4 | The Super-Program for Mining Association Rules                          | 54  |

|              |       | 4.1.5 | The Super-Functions for Mining Association Rules                        | 54  |

|              | 4.2   | Exam  | ple 2: Matrix Multiplication (MM)                                       | 57  |

|              |       | 4.2.1 | The Super-Instruction Set and Super-Data Blocks for $\operatorname{MM}$ | 57  |

|              |       | 4.2.2 | The Super-Function for Matrix Multiplication                            | 57  |

|              |       | 4.2.3 | Scheduling Policies and Parallelization of the SF                       | 58  |

| 5            |       |       | L EXECUTION OF SUPER-PROGRAMS AND RELEVANT EADS                         | 61  |

|              | 5.1   | Overv | riew of Overheads                                                       | 61  |

|              |       | 5.1.1 | Overheads in Program Execution                                          | 61  |

|              |       | 5.1.2 | Quantitative Definition of Overheads in Parallel Executing Programs     | 62  |

|              | 5.2   | Overh | leads of the Runtime System of SPM's VM                                 | 64  |

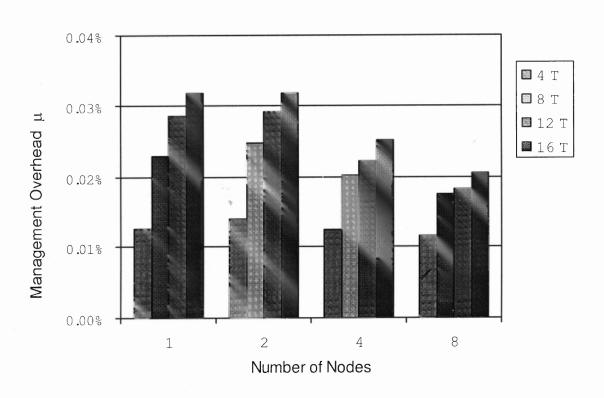

|              | 5.3   | Mana  | gement Overhead                                                         | 65  |

|              |       | 5.3.1 | Source of Management Overhead in SPM Runtime Environment                | 65  |

|              |       | 5.3.2 | Experiment Measure of Management Overhead                               | 66  |

| 6            | LOA   | D BAI | LANCING                                                                 | 69  |

| $\mathbf{C}$ | hapt | er    |                                                                             | Pa | age |

|--------------|------|-------|-----------------------------------------------------------------------------|----|-----|

|              | 6.1  | Overv | view of Load Balancing                                                      |    | 69  |

|              |      | 6.1.1 | Requirement for Load Balancing                                              |    | 69  |

|              |      | 6.1.2 | The Types of Strategies for Load Balancing                                  |    | 71  |

|              | 6.2  | Load  | Balancing for SPM                                                           |    | 73  |

|              |      | 6.2.1 | Mechanism of Automatically Load Balancing in SPM                            |    | 73  |

|              |      | 6.2.2 | A Model of Estimating the Imbalance Overhead for SPM $$                     |    | 75  |

|              | 6.3  | Evalu | ation of the Load Balance Mechanism                                         |    | 78  |

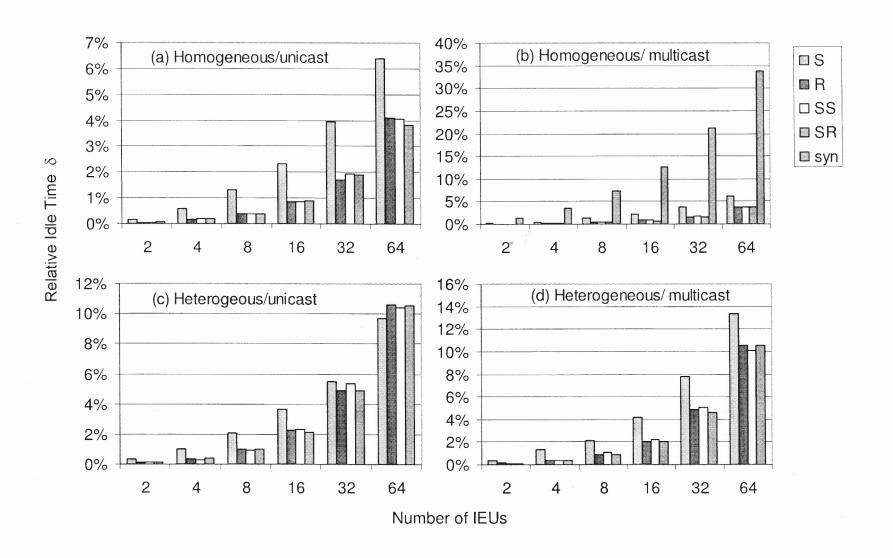

|              |      | 6.3.1 | Simulation of Automatically Load Balancing                                  |    | 78  |

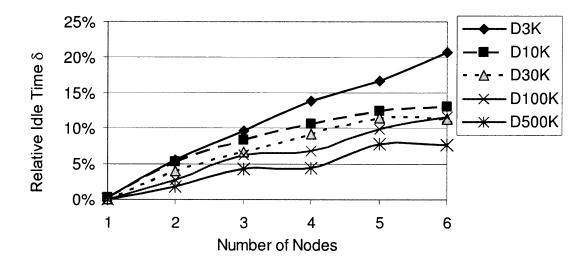

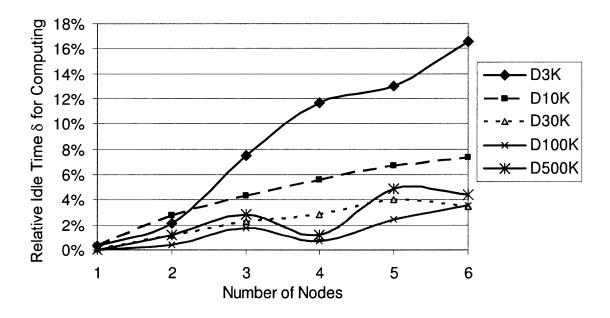

|              |      | 6.3.2 | Experiment of Mining Association Rule                                       |    | 81  |

|              |      | 6.3.3 | Experiment of Sparse Matrix Multiplication                                  | •  | 86  |

| 7            | COI  | MMUN  | ICATION OVERHEAD                                                            | •  | 89  |

|              | 7.1  | Comn  | nunication Overheads for the SPM Runtime System                             |    | 89  |

|              | 7.2  | Techn | nologies to Reduce Communication Overhead                                   |    | 90  |

|              |      | 7.2.1 | Techniques to Reduce Type I Communication Overhead                          |    | 90  |

|              |      | 7.2.2 | Techniques to Reduce Type II Communication Overhead $$                      |    | 91  |

|              | 7.3  |       | l to Estimate the Communication Overhead of the SPM Runtimetem              |    | 91  |

|              |      | 7.3.1 | System Condition and a Statistical Estimation of the Communication Overhead |    | 92  |

|              |      | 7.3.2 | The Effect of Loading Remote Data in the Burst Access Mode                  | Э  | 95  |

|              |      | 7.3.3 | The Effect of the Local Cache                                               |    | 97  |

|              |      | 7.3.4 | The Effect of Multicasting on the Communication Overhead .                  |    | 99  |

| C. | hapt | er     |                                                               | Р    | age  |

|----|------|--------|---------------------------------------------------------------|------|------|

|    | 7.4  | Evalu  | nation of Communication Overheads in SPM                      |      | 103  |

| 8  | PAF  | RALLE  | L DATA VIRTUALIZATION AND DATA ACCESSES                       |      | 111  |

|    | 8.1  | Paral  | lel Data Accesses for the Parallelization of Programs         |      | 111  |

|    | 8.2  | Data   | Virtualization and Parallel Data Accesses                     |      | 112  |

|    | 8.3  | Evalu  | ation of SPM in Accessing Parallel Data                       |      | 112  |

|    | 8.4  | Perfo  | rmance Analysis                                               |      | 121  |

| 9  | SCA  | LABII  | LITY                                                          |      | 125  |

|    | 9.1  | Scalal | bility and its Analysis                                       |      | 125  |

|    |      | 9.1.1  | Demand on Scalability                                         |      | 125  |

|    |      | 9.1.2  | Scalability as a Comprehensive Entity                         |      | 127  |

|    |      | 9.1.3  | Existing Scalability Definitions                              |      | 128  |

|    |      | 9.1.4  | More on Limitations of Current Approaches                     |      | 130  |

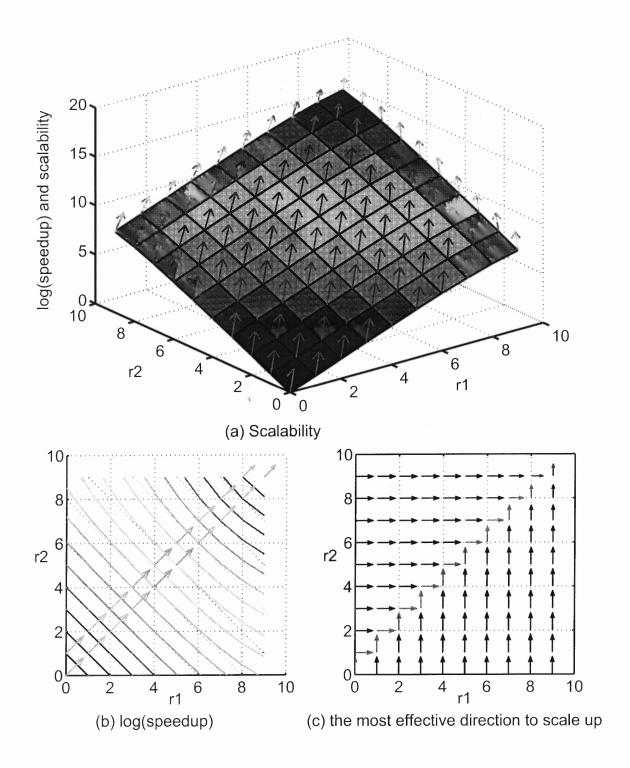

|    | 9.2  | New 0  | Quantitative Analysis of Scalability                          |      | 132  |

|    |      | 9.2.1  | Mathematical Definition of Scalability                        |      | 132  |

|    |      | 9.2.2  | Directionality of Scalability                                 |      | 134  |

|    |      | 9.2.3  | Studying the Cost for Optimal Scale Up                        |      | 135  |

|    | 9.3  | Scalin | ng up PC Clusters and Scalability Study under SPM             |      | 137  |

|    |      | 9.3.1  | Techniques for Scaling up PC Clusters                         | •    | 137  |

|    |      | 9.3.2  | Scaling Up Programs Developed under SPM                       |      | 139  |

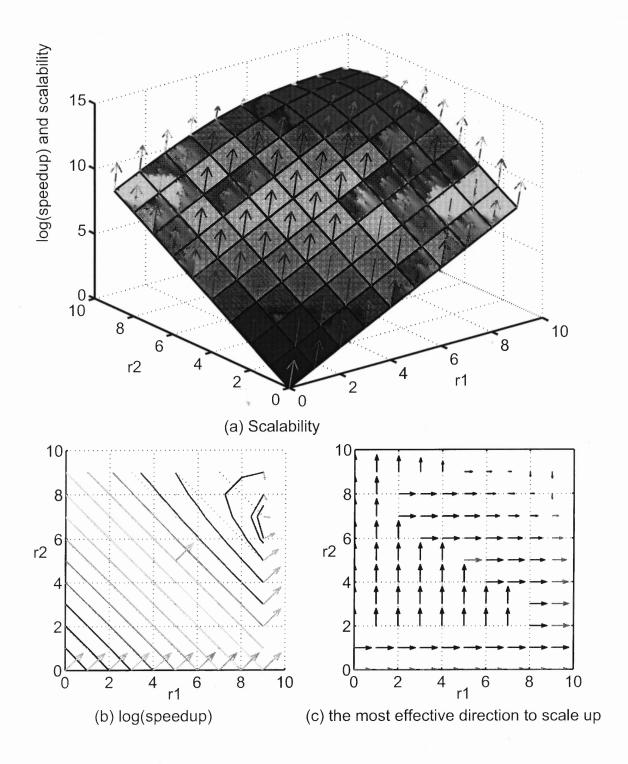

|    |      | 9.3.3  | Scalability of SPs for Hierarchical PC Clusters               |      | 142  |

|    |      | 9.3.4  | Scalability of an Optimally Configured Solution for a PC Clus | ster | :144 |

| Chapter |        |           |       |     | ag€  |     |    |   |    |    |    |     |   |   |   |      |   |  |  |     |

|---------|--------|-----------|-------|-----|------|-----|----|---|----|----|----|-----|---|---|---|------|---|--|--|-----|

| 9.4     | Case S | Studies . |       |     |      |     |    |   |    |    |    |     |   |   |   | <br> |   |  |  | 146 |

|         | 9.4.1  | Case 1    |       |     |      |     |    | • |    |    |    |     |   |   | • | <br> |   |  |  | 147 |

|         | 9.4.2  | Case 2    |       |     |      |     |    |   |    |    |    |     |   |   |   |      | • |  |  | 149 |

|         | 9.4.3  | Cases 3   | and 4 |     |      |     |    |   |    |    |    |     |   |   | • |      |   |  |  | 151 |

|         | 9.4.4  | Case 5    |       |     |      |     |    |   |    |    |    |     |   | • |   |      |   |  |  | 154 |

| 10 COI  | NCLUS  | IONS .    |       |     |      |     |    |   |    |    | •  |     |   |   |   |      |   |  |  | 157 |

| APPEN   | NDIX   | A PROC    | F OF  | THI | E OI | PTI | MA | L | DI | ME | NS | SIC | N |   |   |      |   |  |  | 161 |

| BIBLIC  | OGRAF  | РНΥ       |       |     |      |     |    |   |    |    |    |     |   |   |   |      |   |  |  | 163 |

## LIST OF TABLES

| Table |                                                                                               | P | age |

|-------|-----------------------------------------------------------------------------------------------|---|-----|

| 4.1   | The SDBs for mining association rules                                                         | • | 51  |

| 6.1   | Name and properties of synthetic databases used                                               |   | 81  |

| 6.2   | Design parameters of SDBs and VM for mining association rules                                 |   | 82  |

| 6.3   | Summary of execution times and idle times of VM for executing the SP mining association rule. |   | 83  |

| 7.1   | A static task schedule for a heterogeneous PC cluster with 64 nodes                           |   | 104 |

| 8.1   | Properties of the data matrices                                                               |   | 114 |

| 8.2   | Experimental configurations and data                                                          |   | 114 |

| 8.3   | Intrinsic degree of parallelism in the experimental SP                                        |   | 122 |

## LIST OF FIGURES

| Figu | re                                                                                                  | age |

|------|-----------------------------------------------------------------------------------------------------|-----|

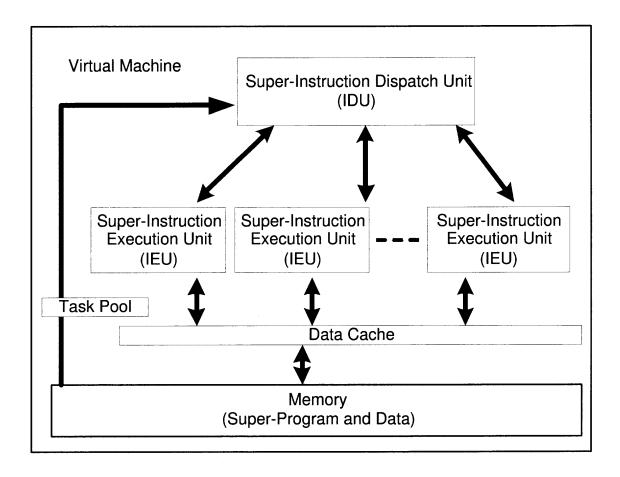

| 3.1  | Logical structure of the virtual machine                                                            | 32  |

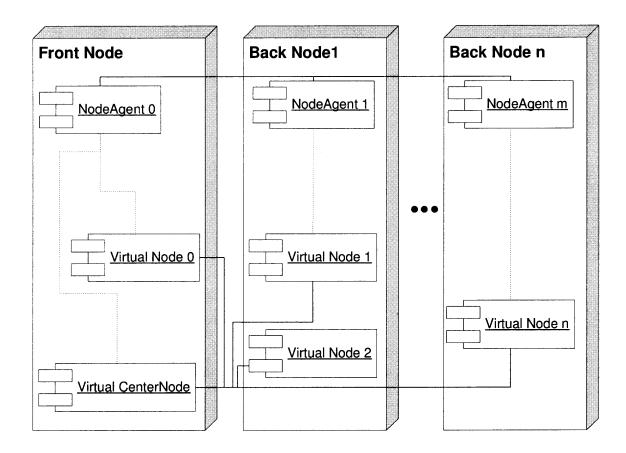

| 3.2  | Physical structure of the reference runtime support system                                          | 33  |

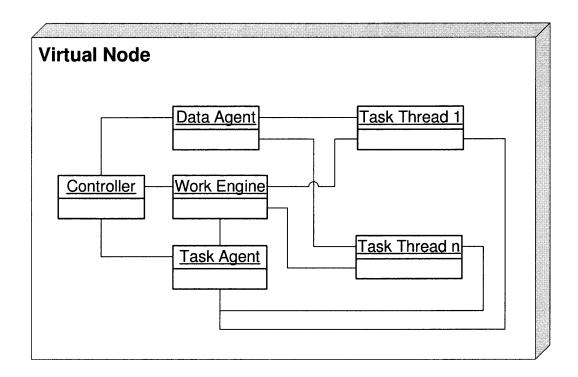

| 3.3  | The components of a virtual node                                                                    | 34  |

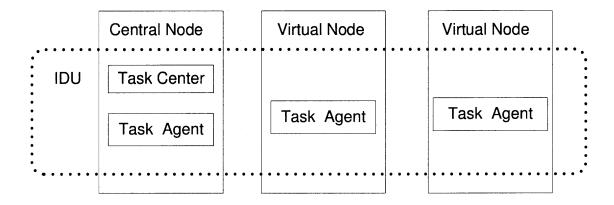

| 3.4  | The distributed structure of the IDU                                                                | 35  |

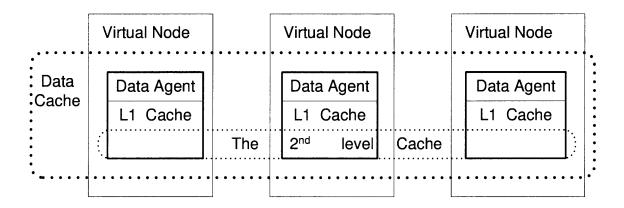

| 3.5  | The distributed structure of the data cache subsystem                                               | 35  |

| 3.6  | The interface of the task agent                                                                     | 39  |

| 3.7  | The interface of the task center                                                                    | 39  |

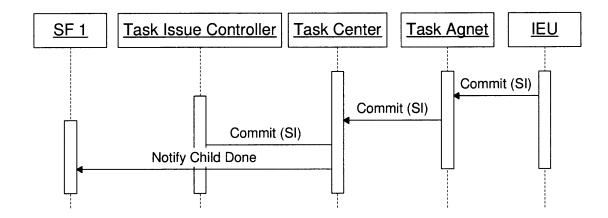

| 3.8  | The sequence diagram for committing an SI                                                           | 40  |

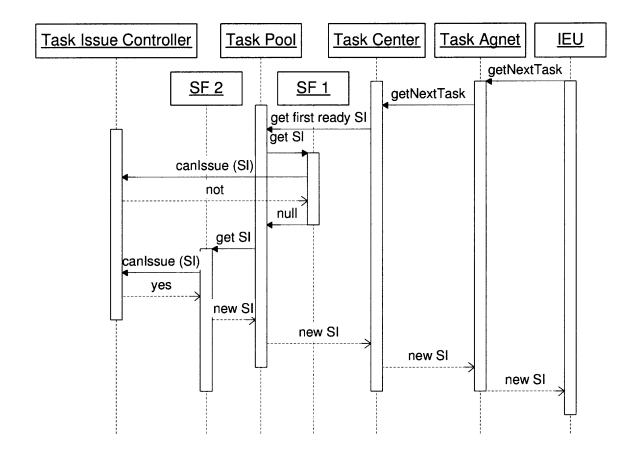

| 3.9  | The sequence diagram for issuing an SI                                                              | 40  |

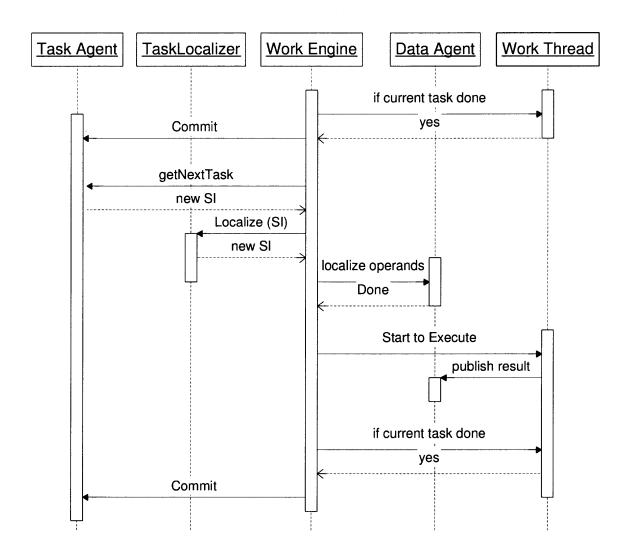

| 3.10 | The sequence diagram for executing an SI on an IEU                                                  | 42  |

| 3.11 | The interface of the data center                                                                    | 45  |

| 3.12 | The interface of the data agent                                                                     | 46  |

| 4.1  | The SP of mining association rules                                                                  | 54  |

| 4.2  | The super-function for matrix multiplication                                                        | 58  |

| 5.1  | Relative management overhead in execution of the MM SP                                              | 68  |

| 6.1  | Simulation results of imbalance overhead of the MM SP                                               | 79  |

| 6.2  | Percentage of average node idle time of the SP of mining association rules                          | 85  |

| 6.3  | Percentage of average node idle time of the SP of mining association rules (in the computing stage) | 86  |

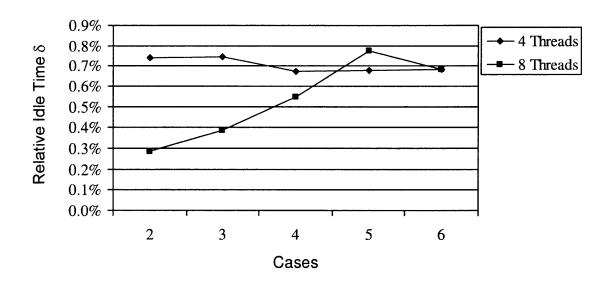

| 6.4  | Comparison of the relative idle time for SPM and HPA                                                | 87  |

| 6.5  | Relative idle time of IEUs in execution of the MM SP (experiment)                                   | 88  |

## LIST OF FIGURES

| Figu | are Page                                                                                                                                                                       |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

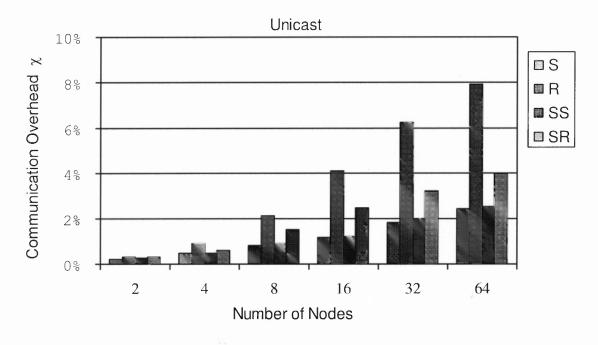

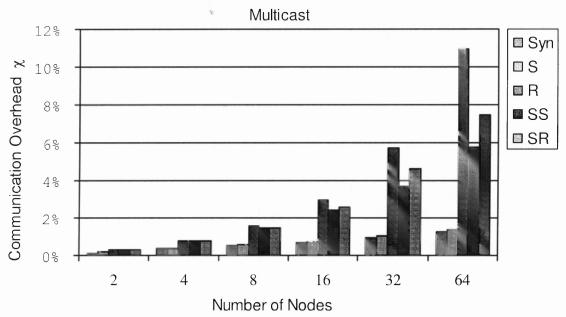

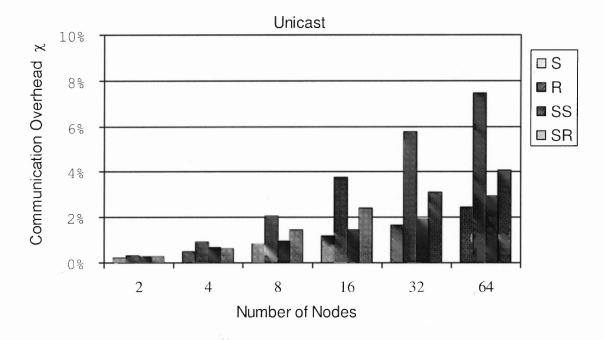

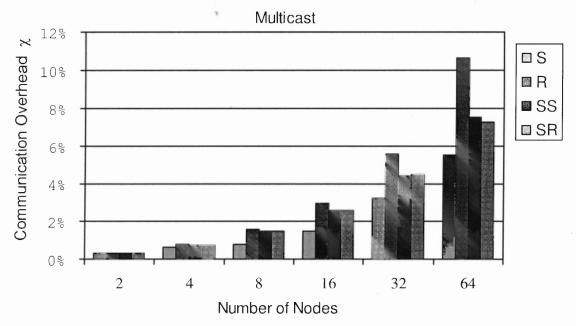

| 7.1  | Simulation results of communication overhead in a homogeneous environment                                                                                                      |

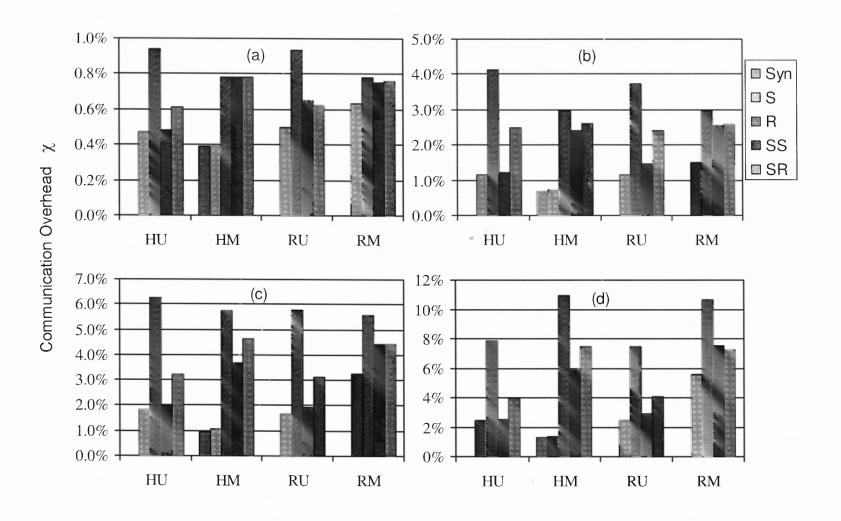

| 7.2  | Simulation results of communication overhead in a heterogeneous environment                                                                                                    |

| 7.3  | Comparison of communication overheads under different strategies 109                                                                                                           |

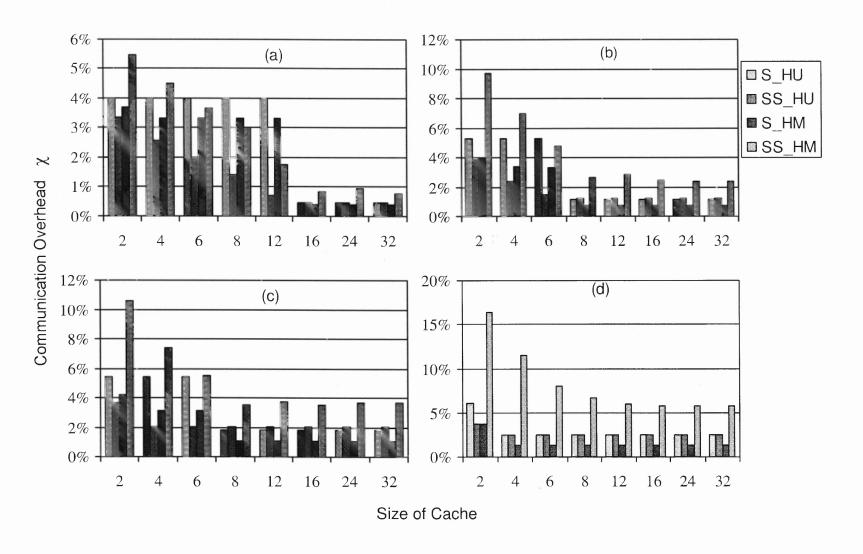

| 7.4  | Communication overheads under different strategies in a homogeneous environment for different cache size                                                                       |

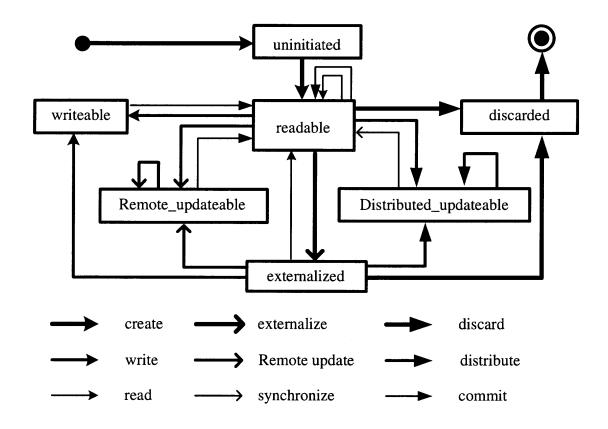

| 8.1  | State diagram for logical data entities                                                                                                                                        |

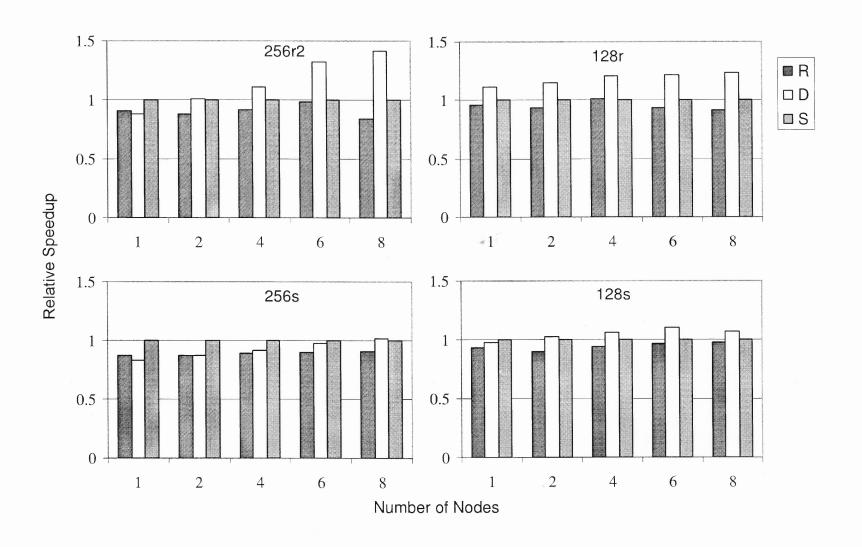

| 8.2  | Relative performances of the three SPs using different data writing methods115                                                                                                 |

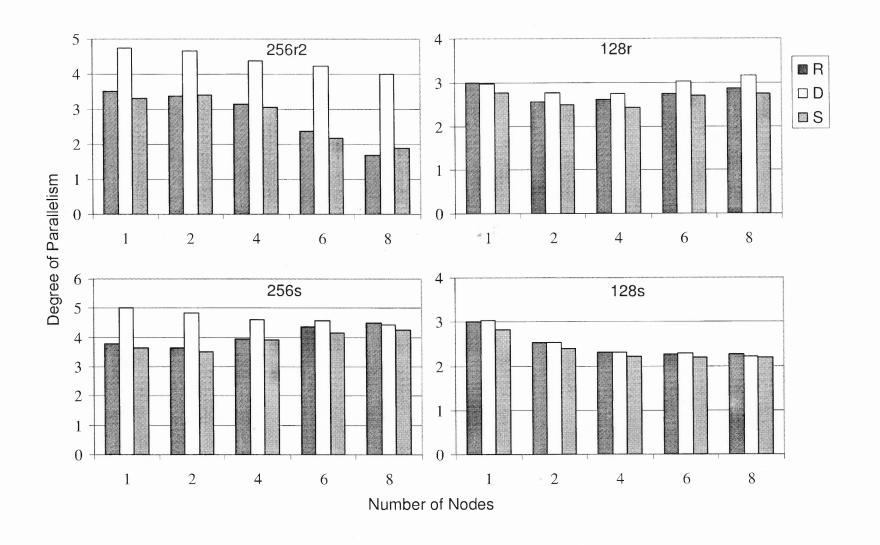

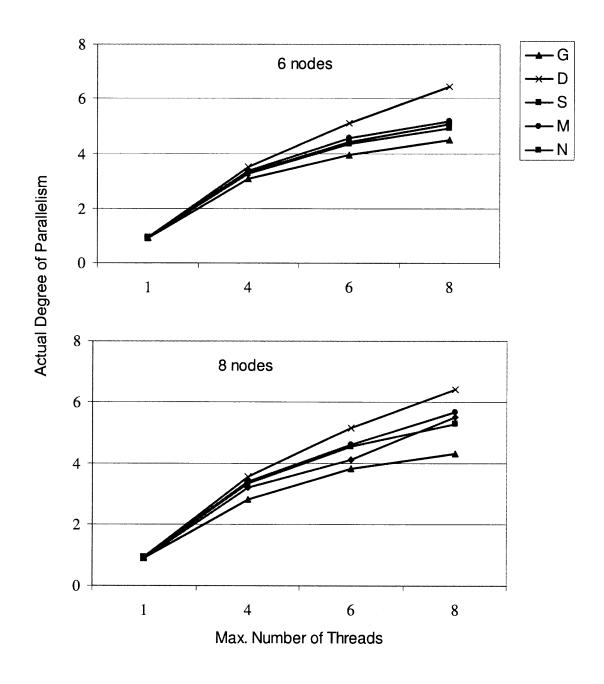

| 8.3  | The effect of the data access methods on the degree of parallelism 116                                                                                                         |

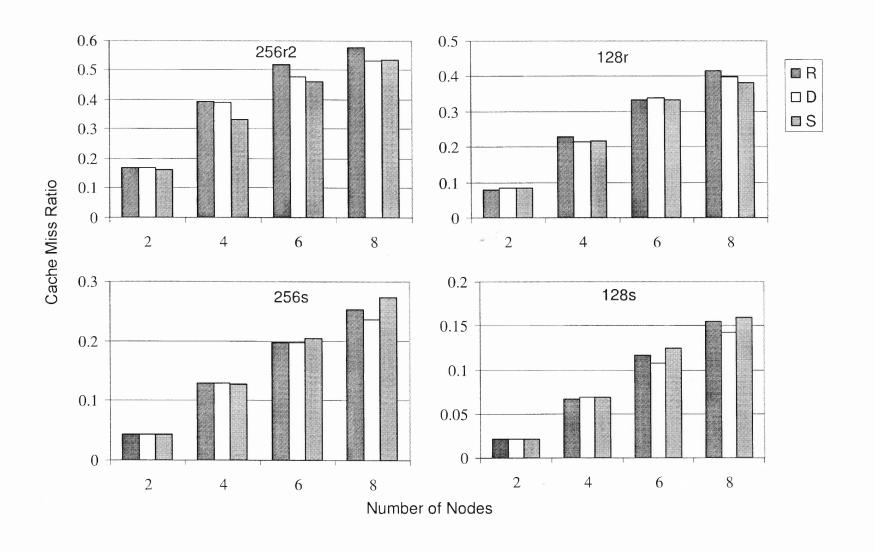

| 8.4  | The local cache-miss ratio of data access                                                                                                                                      |

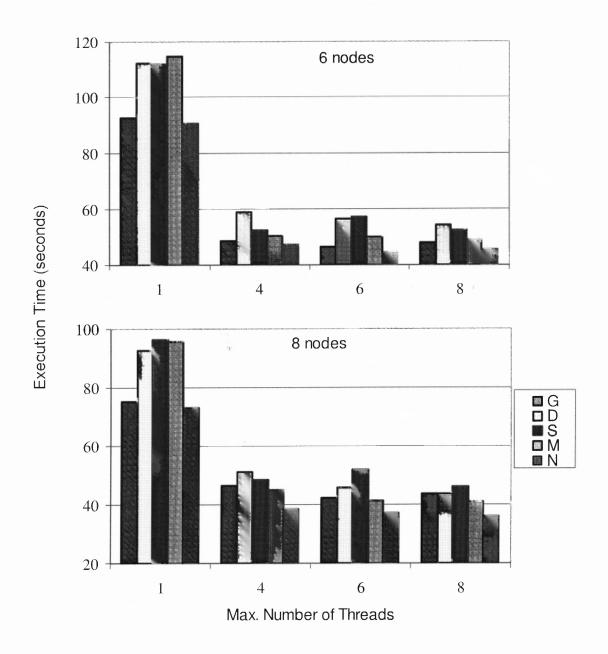

| 8.5  | The effect of multithreading on the execution time of the SPs                                                                                                                  |

| 8.6  | The effect of the limit of threads per node on the actual degree of parallelism119                                                                                             |

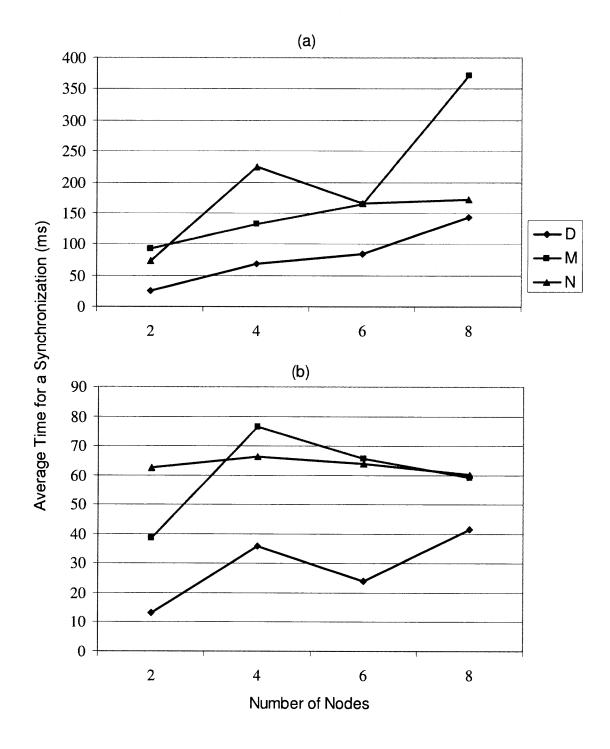

| 8.7  | Average time for synchronization of a sub-matrix block                                                                                                                         |

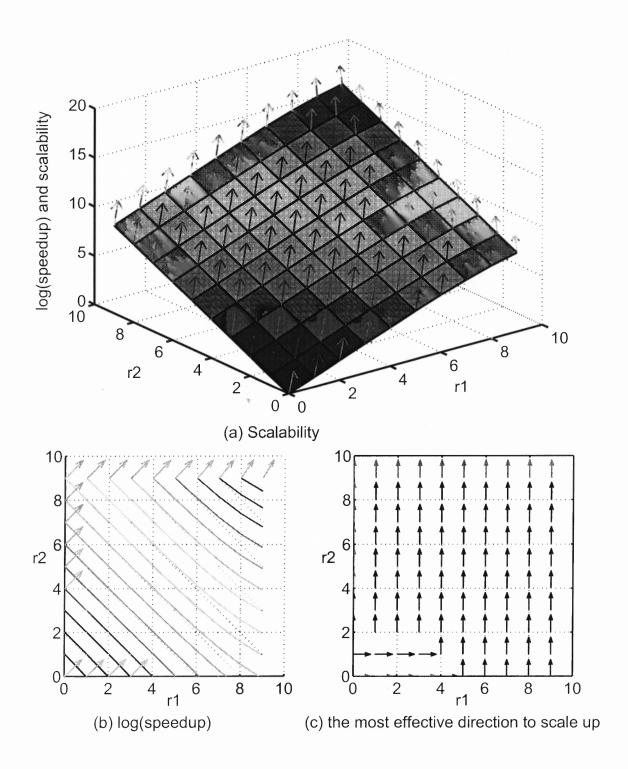

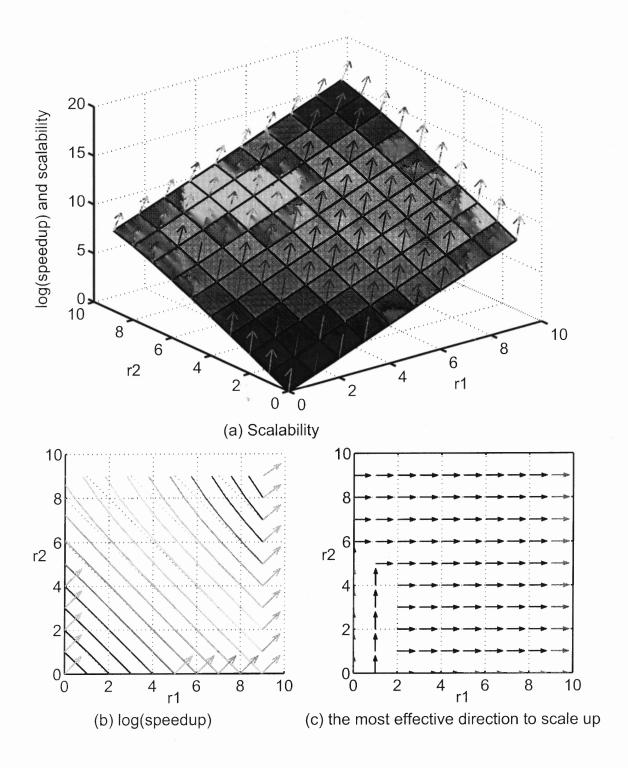

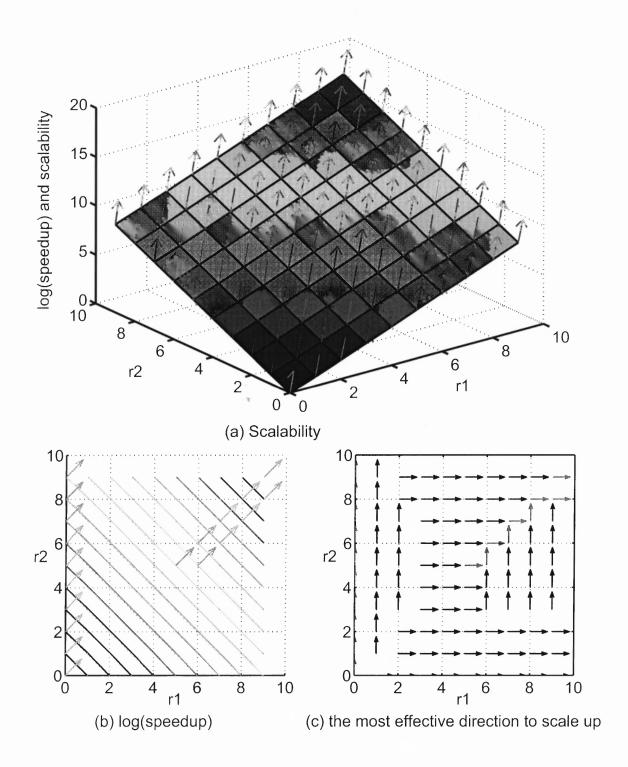

| 9.1  | Scalability of a two-level cluster for matrix multiplication with fixed workload for the program and level-1 SIs                                                               |

| 9.2  | Scalability of a two-level cluster for matrix multiplication with fixed overall workload but the workload of level-1 SIs increases with increases in the size of level-1 nodes |

| 9.3  | Scalability of a two-level cluster for matrix multiplication in which the workload of level-1 SIs increases with the size of level-1 nodes and $w_1$ is constant               |

| 9.4  | Scalability of a two-level cluster for matrix multiplication where the $w_1$ increases with the number of subcluster nodes and $w_2$ is constant 153                           |

| 9.5  | Scalability of a two-level cluster for matrix multiplication where $w_1$ and $w_2$ increase with the number of level-1 nodes and level-2 nodes, respectively                   |

#### CHAPTER 1

#### INTRODUCTION

### 1.1 Research Motivations and Objectives

The main objective of this dissertation is to describe an innovative programming model for developing parallel programs that can efficiently execute in parallel on distributed computer systems, mainly cluster computer systems.

## 1.1.1 Problem Statement

In our world people increasingly rely on computers to achieve their daily activities. Scientists often need powerful, scalable and easily accessible computer systems. Also business people often need powerful computers to as processing engines of their information systems in order to achieve management operations effectively or even use such systems to make strategic decisions. The demands for high performance and faster response drive the evolution of computer systems. Since sequential computer systems can hardly provide the required performance, users and computer system developers often focus on parallel and/or distributed computer systems [1,2]. Their focus drives the evolution of various facets of software development. One of the most important facets is programming models. Developing software comprises multiple levels [3–6]. Each level adopts a programming model to achieve its tasks. Programming models are designed based on system models described with abstract machines; there are some assumptions associated with abstract machines [7,8].

PC clusters are distributed systems used to run parallel programs. They have major advantages in potentially large raw capability, scalability and reasonable cost. However, abstract machines for existing programming models do not match well with PC clusters. As a result performance degradation is common. PC clusters have long communication latencies than SMP servers or supercomputers [9, 10]. Therefore, the users cannot often obtain high performance by simply using existing parallel programming models. A new programming model for such systems is needed [11]. The model should hide the long communication latency of these distributed systems and should address the issue of load balancing very well for high performance. In addition, it should be easy to learn and use, and should be as much compatible in concepts as possible with current widely used programming models [12].

## 1.1.2 Motivations

The motivations of this research stem from the need to develop a new parallel programming model for efficient development of programs that can be executed on a wide class of parallel and distributed computer systems; this need is of paramount importance for emerging PC cluster systems. The satisfaction of the users is, of course, critical. For given hardware it can usually be measured for a piece of software with the total cost of ownership (TCO). This cost can be divided into two parts: the cost of obtaining the software, which ultimately depends on the development cost, and the cost of using the software, which ultimately depends on its performance and maintenance cost [12]. The general goal of any new parallel programming model should be to minimize the TCO of software developed under the programming model.

One of the objectives should be to obtain high performance since it is the most important factor in satisfying end users; it also affects directly users' cost in using the software. Programming models have much larger effect on the performance of programs executing in parallel compared to sequential programs. It stems from balancing the distributed workload, accessing remote data and various other overheads. Other motivations that can be addressed by an innovative programming

model are: 1) support dynamic load balancing for programs executing in parallel; 2) provide cache prefetching for large data sets so that the latency of communications can be hidden; 3) pack data objects and tasks coarsely, as needed, to reduce various overheads; and 4) support the portability of programs and the scalability of program-system pairs to satisfy end users [13]. This way, end users are free to update their cluster systems gradually on-demand without additional cost and constraints for migrating application programs. Also, the number of potential users for each program should often increase.

These research motivations are compatible with existing wide used models. From the view of software engineering, such models are easy to learn and use which are important factors in satisfying end users [14]. How easy it is to use a programming model can affect the speed and efficiency of software development. How easy it is to learn to apply the model can affect the availability of qualified developers. Both ultimately can affect the cost of software development and increase TCO. Therefore, we should be motivated to deploy a parallel programming model that is extremely similar with widely accepted sequential programming models; thus, any programmer with sequential programming experience could quickly learn to use it. As a result, a large number of programmers might shift to parallel program development for distributed systems.

## 1.1.3 Objectives

The main objective of this research is to develop an easy to use parallel programming model that can facilitate the development of high performance programs targeting parallel and/or distributed computer systems; the main focus is PC cluster systems. To achieve this main objective, our new programming model needs to:

• Facilitate task partitioning for parallel computation.

- Provide a runtime support system of the model to transparently distribute and schedule the execution of computing tasks for good workload balancing among the member computers in the cluster.

- Provide a standard interface to programmers to explicitly express, if desired, specific requirements for parallel scheduling and task distribution (mapping). The runtime support system should then be obliged to follow these explicit policies of task scheduling and distribution instead of the default policies.

- Facilitate the partitioning of application data

- Provide a mechanism for data provisioning so that the programmers should not consider data location. This requires that the long latency of remote data accesses should be hidden.

- Minimize all overheads corresponding to communication, data distribution and task management.

From the software engineering point of view, this model should:

- Be used to develop programs for parallel execution on both homogeneous and heterogeneous systems. Re-engineering the underlying cluster systems should not prevent from continuing using the application programs.

- Make the software development scalable. Programs should be able to run on various cluster systems of different sizes.

- Be portable. Software developed with this model could be ported to various cluster systems.

- Be very easy to learn. It should be a direct extension of widely accepted programming models.

## 1.2 Background in Programming Models and Computer Systems

## 1.2.1 Programming Models

Generally programming is the process of developing software to enforce a computer system to implement a required function; that means, it is the process of "customizing" computer systems for specific tasks. This is a complex process. To make this process of programming efficient, correct and easy, developers need appropriate system methodologies. Practice proves that layering the task into multiple layers of development is the most efficient methodology [5,15]. In history, creating a new layer is a milestone in progress. For example, the appearance of high-level programming languages is such a great progress [16]. It makes programming more convenient and productive.

In this multilayered infrastructure, a computer system is viewed as multiple virtual/abstract computer systems or machines. Each machine is built on top of another. The abstract machine provides some abstract operations [5]. The most top layer is our application system.

Generally a programming model is a set of schemes for program organization, data and task decomposition, and execution arrangement. A programming model exists in a layered context and is associated with a set of abstract entities, namely a system model and an execution model. The underlying systems are modelled as sets of abstract entities described with a set of interfaces and programming is solely based on the behavior of the specified logical entities. Well-defined interfaces serve as a contract for the behavior, requirements and responsibilities of each part. That is where the programming model stands [17,18]. It is an instrument with guidelines to build software in a layered context.

The system model is an abstract machine that provides an abstract description of the underlying virtual computer system. A programming model usually employs the abstract machine to encapsulate the underlying support system and setup program semantics [19–21]. So, the architecture of the underlying system is hidden. The structure of software is simplified by expressing operations for the abstract This makes program development easy and the programs are easily machine. manageable. These abstract entities in programming models are used to describe various facets of software, the requirements and constraints of their executions, and the program's execution environment. These abstractions also specify the semantics of the languages that are used to build a higher layer program by specifying the requests for services of an underlying layer. They help developers to analyze the correctness and many other properties of programs or even analyze and estimate the performance of program execution. These abstractions may include data models and various mechanisms for data storage, information exchange and data manipulation. In some sense, any programming language corresponds to a model. To conclude, developing software with a programming model corresponds to just applying these abstractions to build software and to describe the desired logic of data manipulation.

The well-known von Neumann computer model represents computation on those sequential machines. It sets up a contract between the low-level computer hardware and the high level software. Even though technology and architectural ideas evolve rapidly, hardware designers still target efficient von Neumann machines without much concern for the programs that will be executed on them. On the other hand, software developers focus on programs that can be executed efficiently on this model, without explicit consideration of the hardware. The von Neumann model is versatile to enable diverse programs to run efficiently on sequential machines [18].

An execution model is the scheme used to execute software on the corresponding abstract machine. It specifies how operations in a program are executed. Combining an abstract machine and its execution model provides an instrument to describe

the process of state change in the corresponding computer system. Such a state machine can clearly define program semantics. This provides the basis for analyzing the correctness of programs. The execution model also can be used to estimate program performance. Programmers and/or the compiler can use it to optimize coded programs [22].

Since programming models provide an instrument to express operations of application programs in a highly abstract manner, programmers can focus on high-level application logic, but ignore the details of the computer system and its execution steps. The programming with such abstract operations can offload major work to lower layer system developers. So the employment of high-level programming models can reduce the complexity of programming [14]. This, in turn, can increase the efficiency of program development and increase productivity.

## 1.2.2 Requirements of Programming Models

Abstraction in programming models is essential. Programming models must be based on abstract machines, should completely encapsulate the underlying support systems and should be independent of system architectures [18,23]. Programs developed with such models will be easily ported. Developed software will be more stable and could survive the evolution of computer system hardware. To adhere to abstraction, the implementations of abstract entities in these models must be transparent to the users of the programming models.

For programming models to be usable, programmers must be able to express data structures and logical operations with the basic elements and constructors of the model. Only if the programming model provides adequate expressiveness, will it be possible to isolate high-level programming from low-level implementations of the underlying computer system. Otherwise, encapsulation in the programming model

of the underlying system is broken. It is also important for the programming model to get sufficient support from the underlying computer system. To be practically usable, the architecture should provide good support to implement the model.

## 1.2.3 Evolution of Systems and Programming Models

For higher performance and better usability, computer system architectures have been constantly evolving. One of the common trends in system evolution is the so called parallelization [24]. In some sense, almost all contemporary computer systems are parallel in nature. They have multiple functional units in a single processor [25,26], multiple processors on a board, multiple computers in a box [27–29] or even multiple computer hosts in a network [9,30,31]. Another trend is distributed system. This evolution is driven by both improved design techniques and increased social needs. The appearance of the Internet, www services [32,33] and grid computing [34,35] are all results of this trend. During the evolution of computer systems, standardization plays a critical role. It gives developers of programs concise and clear environments. Programs become portable for wider use. PC cluster systems are a good example of using commercial the off-the-shelf (COTS) PCs as building blocks for cost-effective parallel and distributed computer systems [24].

Because of the recent evolution in computer system architectures that has broken away from those previous abstract machines for parallel computers and supercomputers, old programming models cannot encapsulate the new emerging features without loss in performance. In this case, both the system model and programming models also have to evolve. Thus, the development of a unifying model for parallel computation is required for general-purpose parallel and distributed computing [18].

## 1.3 Clustered Computer Systems

## 1.3.1 Cluster Technology and PC Clusters

Clustering of resources is a technique that groups identical or similar functional units together to form a larger system. A clustering technique can be used at various levels of a computer system for different components. The clustered components could be multiple ALUs in a processor [36], multiple processors in a computer [29,37], multiple disks in a storage system [38,39], multiple computers in a large web server or a large computing facility [40–43].

The primary reasons of using a cluster technology are to build a large system with improved capabilities, reliability and availability using COTS components [44]. Clustering also provides a mechanism to improve the scalability of a system [2, 45] because users/administrators can expand the system easily by adding additional COTS components; for at least a certain size range, the capabilities of a clustered system can almost linearly increase by increasing the number of member components. Clustering provides a mechanism to improve system availability [46,47] and reliability [48–50]; member components can back each other up. Since member components are often similar and standardized the cost of development is low.

Computer clusters contain computers as the building blocks. The member computers, called nodes or hosts, could be SMP (Symmetric multiprocessors) servers, minicomputers, workstations or PCs (personal computers) [29, 51]. PC cluster systems (or PC clusters in short) employ common PCs normally running public domain software [31]. They are also connected via standard network devices and techniques.

The main reasons that have made PC clusters very popular are cost affordability and accessibility.

## 1.3.2 More Characteristics of PC Cluster Systems

A feature that differentiates PC clusters from other multi-computer systems is their network. A super-computer has a customized inter-processor communication network [15, 52, 53] and a customized data network that connects the processors to mass memory devices. When increasing the number of processors, the complexity of these networks increase super-linearly. However, a PC cluster has neither specialized inter-processor communication network nor special memory access networks [54,55]. The communication between processors belonging to different member computers must go through network interface cards and the general-purpose network. Current practices have shown that simple and linearly scalable networks can be used to build very large computer systems, thus, improving scalability. Compared to massively parallel processor systems, PC clusters have very fat nodes. Each member node is an individual single- or multi-processor computer containing several memory These PCs may possess locally installed modules and various storage disks. programming libraries, administration software and utility programs; there may also exist many local system services on these member computers. These PCs even have auxiliary processors dedicated to network access. Also, nodes in PC clusters are fat autonomous systems where tasks are ultimately scheduled by the local operating system.

## 1.4 Background in Programming PC Cluster Systems

## 1.4.1 Programming Model Requirements for PC Cluster Systems

Generally, programming models are required to have some basic functionality. They should provide:

1) Instruments to decompose application data (to declare complex data)

- 2) Tools to define and delineate subtasks (statements) so that programmers can develop large application conveniently

- 3) Mechanisms to specify order constraints in executing the subtasks in application programs (for scheduling).

For distributed programming models, additional functionality is required corresponding to:

- 1) Partitioning application data into multiple groups and distributing them among the member computers

- 2) Providing a mechanism for data communication between distributed processes (i.e. a facility to remotely access distributed data).

- 3) Mapping application tasks into multiple groups of member computers so that all of these resources can be utilized.

- 4) Providing a mechanism to distribute tasks to member computers (either by distributing the existing tasks or launching more threads).

For high performance, the runtime support system of a parallel programming model should also provide:

- 1) Mechanisms to exploit the parallelism in programs while execution system can keep the aforementioned order constraints.

- 2) Workload balancing among multiple processors.

## 1.4.2 Existing Programming Models

Since the nature of PC clusters, which are both parallel and distributed, currently programmers employ various existing parallel programming models and/or distributed programming models to develop application programs. Most of these models were initially developed for some other types of systems. Distributed system programming models assume that processors and memories are spatially distributed in multiple autonomous computers [56]. Processors can only access their local memory. Programs consist of multiple pieces running on different computers. These pieces have their own instruction streams and data stored in the local memory. They co-operate with each other by communicating through a network. distributed system programming models stem from the client-server model [57]. In the client-server programming model, applications are split into client and server parts distributed to many computers. Clients invoke methods of server programs when they need to achieve pre-defined tasks; server programs execute predefined procedures when receiving requests and they then send the results to clients. After gotten a response, a client resumes its blocked thread. That is, the execution of threads crosses the boundary between processes and computers. RPC (Remote In distributed Procedure Call) is a typical client-server programming model. programming models, partitioning and delineating tasks is embedded in declaring and defining for remote accesses; remote procedure invocations provide mechanisms for both data and task distribution. Each call of a remote procedure just delivers a task to a server process. The passing of arguments and the return of results for remote procedures achieve the functionality of distributing data. In principle, distributed programming models emphasize the distribution of tasks. The roles of client and server can be dynamically determined within the context of programs progressing [58]. CORBA is a widely used distributed programming model [59,60].

Logical threads in CORBA consist of executing methods on objects distributed to multiple computers. Through invoking remote methods, multiple distributed threads executing these methods are connected and they form these logical threads. DCOM is another example of a distributed programming model in the Windows world [61]. RMI is the Java version of a distributed programming model [62–64].

In a strict sense, client-server programming models are not parallel programming models, since an underlying program is blocked. Several distributed programming models do develop some basic features to support parallel execution, where clients also can invoke methods of servers asynchronously. Clients no longer need to block local execution threads. Servers can send back their responses via callback interfaces of the clients. The message-driven EJB in J2EE is such a good example that use asynchronous communication. However, these models still lack a sophisticated mechanism to schedule global tasks. For this reason, there are a number of efforts to enhance the parallel features of distributed programming models [63].

Parallel programming models have been studied extensively [65–68]. In these models application programs consist of multiple processes [15, 23, 56, 69] executing the same or different program codes simultaneously on multiple processors. Parallel programming models can roughly be classified into two types [56, 70]. The first one follows the SIMD (or SPMD) paradigm that exploits the data parallelism. The second one follows the MIMD paradigm that exploits the task parallelism. Based on the way of exchanging data between processes, parallel programming models are basically classified into two groups [71]. The first group is message-passing models where each process only has a local view of its own independent programming space [23, 72, 73]. It has no idea about the data structure used by peer processes. The other group is shared-memory models where the processes use a shared logical programming space [23, 74–76]. These programming models are independent of

the system architecture [23, 77], which can be encapsulated. The shared-memory programming models can be used for both shared-memory and message-passing architectures. Shared-memory models may need software distributed memory (SDM) systems [74,78] to encapsulate distributed architectures. On the other hand, message-passing programming models can also be used for shared-memory architectures by using the sharing memory mechanisms to emulate with message-passing channels [79]. These encapsulations usually introduce additional overheads [80].

Message-passing models are very common in parallel programming. In practice, programs are written in a sequential programming language, such as C or Fortran, and data exchanges employ calls to message-passing libraries. PVM (Parallel Virtual Machine) is a message-passing programming system that combines a set of computers to form a single, manageable virtual machine [81,82]. PVM exploits both data and task parallelism. It has been ported to many different systems. MPI (Message Passing Interface) is another standard specification for message passing [83]. Following MPI, many libraries such as MPICH [84] and LAM [85] have been developed. The primary advantages that make MPI popular are its generality and portability. Using MPI, programmers can express any conceivable data distribution and be confident that the programs developed with MPI could run on any parallel platform.

Bulk Synchronous Parallel (BSP) is a special kind of a message-passing programming model [86]. In standard message-passing models, messages can be sent at any time and may be received out of order. Messages coming from different senders may interleave each other. Such a scheme makes programs prone to deadlocks and analyzing and predicting the performance of programs may be impossible. Instead of allowing this chaotic approach, BSP organizes the execution of application programs in a sequence of supersteps [18, 87]. Each superstep consists of three segments:

local computation, global communication and barrier synchronization. Only in the global communication stage, the distributed processes are allowed to exchange results generated in the previous computation and prepare the operands for the next computation stage. Thus, no process is stalled to wait for data during execution [86]. In the communication stage, many messages may be merged into large packages that make communications more efficient.

Shared-memory models also are widely used for their simplicity and easiness of programming. Shared-memory models can adopt data or task partitioning to allocate the workload. When applied to distributed systems, they usually employ an abstract data layer to encapsulate the distributed memory in the underlying machines [88]. Global array languages use shared-memory models with the SIMD (SPMD) paradigm to exploit data parallelism. ZPL [89], Co-Array Fortran [90], Unified Parallel C [91,92] and Titanium [93] are all in this style. OpenMP is another shared-memory parallel programming model [94]. It defines a specification for a set of compiler directives, library routines, and environment variables that can be used to specify shared memory parallelism in Fortran and C/C++ programs. Programmers use these directives to declare parallel constructs in sequential-like programs. OpenMP uses the fork-join parallel execution model. When a parallel construct is encountered, the executing thread creates a group of working threads and the creator becomes the master of the group. Each thread in the group executes in parallel the same code specified by the construct. At the end of the construct, all threads in the group execute a barrier. Although this fork-join model can be useful in solving a variety of problems, it is somewhat tailored for large array-based applications.

There are also many shared-memory parallel-programming languages that adopt the MIMD style to exploit both data parallelism and task parallelism. *Cilk* is a typical example in this category [95,96]. Programs consist of multiple computation

tasks executed in individual threads in a shared common context. The programmer concentrates on structuring the program and leaves the responsibility of scheduling the computation to the runtime system [95,97]. Cilk also uses the fork-join model [98,99]. Programmers can split a part of the computation into an independent task that will execute in a separate thread. This achieves the functionality of task mapping.

Object-oriented programming methodologies extend the concept of shared-memory models to shared-object models [100,101] and combine parallel-programming with distributed- programming models. Under this kind of models, objects are programming entities. Programmers implement their programs in a global object space instead of global address space. All application data are encapsulated in objects and all computations are encapsulated in methods that can be applied to the objects; methods are called to manipulate data stored in objects. The primary responsibility of the programmers is to implement these methods and to specify when and which objects are called. During execution, these objects are distributed among multiple processes. They know each other by their name or ID rather than their address. The execution of programs may produce calls that may cross the boundary of processes by sending messages. The execution of programs is driven by events that trigger calls to methods.

Charm++ is a good example of an object-oriented parallel-programming model [102]. Charm++ uses a runtime library to let C++ objects communicate with each other efficiently. A program consists of a number of charm++ objects named chares. Chares send messages to each other by invoking these entry methods asynchronously. One of the important differences of charm++ with other distributed programming models is that objects float between processors; that means objects may be migrated when the runtime system wants to balance the workload among

the processors. Programmers are responsible in decomposing the computation into entry methods of chares and specifying when to create new chares or send messages to existing chares. The intelligent runtime system maps these chares to available processors and schedules the execution of methods to respond to messages [103]. Conceptually, the system maintains a "work-pool" consisting of seeds for new chares and messages for existing chares. The runtime system may pick up multiple items non-deterministically from this pool and execute them. Charm++ uses one-side asynchronous remote method invocation. Charm++ supports efficient dynamical load balancing by using object migration for irregular and dynamic applications; it can also deal with external factors that cause load imbalance.

# 1.4.3 Problems with Current Programming Models for PC Clusters

Most of current parallel programming models were initially developed for some special computer systems and then ported to other types of parallel computing platforms. So far no "native" programming model has been developed for PC clusters. Even though all parallel programming models can be ported to PC clusters, the cost of porting these models is usually a major sacrifice in overall performance because the architecture of PC clusters does not match well initial prototypes for these models. There are two fundamental features that prevent developers from applying very well existing programming models to PC clusters. The first one is the atomicity of nodes. Since local operating systems control the computing resources, estimating the execution time of partitioned tasks becomes more difficult and workload balancing becomes a bigger issue that impacts system performance. Another feature is the long communication latency associated with interconnection networks for PC clusters. Due to the lack of dedicated data networks, the latencies of data communications may be more than 1000 CPU cycles. This is much longer than

the latencies in systems with dedicated data exchange networks. With the improved frequencies of CPUs for member computers, the effect of these latencies will become even more preeminent.

The existing shared-memory programming models are too sensitive to data access time. All of these models depend on sequential programming languages that support ad hoc accesses of fine grain data. Instructions on individual processors are in a sequential stream, so if accessing the memory takes too long time the instruction using the data and all following instructions have to be stalled. Mature sequential programming models address this issue by attempting to hide the latency of accessing memory. But in PC clusters, the latencies are prohibitively high. Thus, it is difficult to hide latencies. Another problem of applying existing shared-memory programming models to PC clusters is related to the appropriate decomposition of tasks for load balancing.

In global array languages, the work of mapping tasks is statically done through code directives that partition the global arrays and map them to processors. The effectiveness of this approach depends on predicting accurately the workloads of processors. For PC clusters, the CPU time for individual tasks varies; many external factors can affect the execution time of a task. Thus, the approach of statically balancing the workload may not work very well. Other shared-memory programming models that exploit task parallelism, such as Cilk, dynamically map tasks to the processors. The runtime system can balance the workload dynamically by launching threads for new tasks on light processors or migrating active ones. This is a very attractive approach that is much better than static approaches. The problem of applying this approach to PC clusters is the cost of migrating active threads.

Message-passing models for PC clusters can partially address the issue of long latencies through multithreading and asynchronous communication techniques for

latency hiding. However the primary disadvantage of these models is that they require the programmers to manage all of the details for data distribution, parallel computation and inter-processor communication for each process. This is tedious and error-prone, and it often obscures logical computations. The tasks are statically associated with the program(s) at the time of coding and are mapped to processors at launching time. If the programmers do not include some adaptive logic in their code, the distribution of the workloads can only be statically balanced; as mentioned above, the statically approaches do not work very well for PC clusters. Adding some adaptive logic in the programs may do much better [104, 105]. The drawback of dynamically balancing the workload is that programmers must code the adaptive logic and embed it into the application logic. The message-passing model and corresponding runtime systems do not provide automatic mechanisms to do so. Incorporating dynamically load balancing techniques at the application level involves significant changes to the design and structure of applications. Actually, the logic of load balancing is incorporated in the data distribution logic. This approach makes communications even more complex and the process of developing large complex software becomes even more tedious, more error-prone and less productive. In the view of software engineering, mixing application logic with logic for load balancing makes it more difficult to reuse the logic for load balancing. Thus, programmers have to recodes the logic for load balancing for each application program.

The problems of applying object-oriented parallel programming models to PC clusters are still load balancing and long latencies for communications. Load balancing is bigger issue. It is a problem related to object distribution since computation code is associated with specific objects; these objects may be pinned to processors, may be duplicated among processors or may float among processors. For many distributed programming models, such as CORBA and J2EE, administrators

deploy these objects into some containers that reside on specific computers. These approaches are equivalent to static load balancing. In some situations, some objects may become hotspots. In the purpose of balancing the workload, floating these objects is more attractive. This necessitates migrating objects from one process context to another one when load is not balanced. But similarly to migrating active threads, the cost of migrating objects will rise. In complex heterogeneous environments, this cost may be prohibitively high. This may be the reason that most distributed programming models currently choose a static model of deployment.

# 1.5 Research Methodology

In this research, the author tries to port the von-Neumann computer model to the context of PC clusters. The proposed approach inherits all the advantages of existing programming models and the most widely accepted concepts. The new model is easy to comprehend and grasp and optimizes the spatial and temporal localities in program execution for high performance. There are two characteristics that support these changes. First, all program components are virtualized through appropriate software implementation. Second, coarse-grain data and complex domain dependent operations are employed. The former virtualization eliminates the limitations imposed by hardware implementations and makes it possible to change the size of these components in a very large scale. One of the most obvious example is instructions. Traditionally, a processor instruction adheres to its hardware implementation and can complete a simple logical or arithmetic operation. Also its operands are limited in size (such as 32bits or 64 bits). In contract, our approach for program development employs instruction that can deal with operands of various sizes.

This modular approach inherits huge volume of valuable assets by exploiting existing achievements. There are a lot of libraries to support various functions

and a lot of tools have been developed. All of them can be used directly for programming PC clusters without much effort to port them. Programming models and methodologies for program development for PCs are very mature. They can be employed directly for programming PC cluster. Also, the major of program developers are familiar with these models and methodologies. Thus, it will be a big advantage to exploit these successful achievements when developing code for PC clusters. To conclude, our proposed program design methodology will be based on sequential programming concepts through the development of appropriate instruction sets for applications. In addition, a runtime support environment will be developed for code porting, data sharing and exchanges and latency hiding

#### 1.6 Outline of This Dissertation

Outline of Dissertation Following this introduction, Chapter 2 will give complete description of the proposed programming model - Super-Programming Model. In Chapter 3, a complete description of the runtime support system for our programming model is given, and a reference implementation and a set of relevant interfaces are presented. In Chapter 4, two examples from two different application domains, namely the business intelligence and scientific/engineering computation domains, are presented to illustrate how to develop programs targeting PC clusters for distributed processing. In Chapter 5, based on the execution model of SPs developed under SPM, the cost of execution is analyzed; various overheads are quantitatively defined and the management overhead is discussed as well. In Chapter 6, a mechanism for load balancing under SPM is discussed. Also, a model to estimate the imbalance overhead is formalized. The real effect of the imbalance overhead is evaluated with experiments. Our results are also compared with another approach for programming PC clusters. In Chapter 7, the communication overheads of SP execution are analyzed; the techniques that can be used to minimize factors

that can reduce the execution performance are discussed. In Chapter 8, a distributed data virtualization scheme that can benefit parallel program execution is presented. In Chapter 9, a new definition of scalability is presented and the scalability properties of various setups are analyzed. The chapter 10, summarize this research.

#### CHAPTER 2

# SUPER-PROGRAMMING MODEL (SPM)

In sequential computation, the von Neumann unifying model sets up a standard for hardware and high-level software designs. Software developers target programs that can be executed efficiently under this model, without explicit consideration of the underlying hardware. Parallel programming also needs such standard bridge models [18, 19]. In this chapter, a parallel programming model is proposed for distributed computer systems.

# 2.1 Overview of the Super-Programming Model

In this dissertation the *super-programming model (SPM)* is proposed for developing parallel programs for distributed systems, such as PC clusters. The proposed model expends existing mature programming models for von-Neumann machines. The system model is basically modeled as a von-Neumann machine with multiple ALUs that can perform complex tasks. It replaces simple processor operations with much coarser tasks.

Developing software under the SPM consists of four layers. The lowest layer is development of the virtual machine (VM). It includes designing and implementing various components of the VM. The second layer is development of a super-instruction (SI) set architecture to customize the virtual machine. The third layer is development of reusable parallel program units called super-functions (SFs) that are implemented with super-instructions. The highest layer is development of application programs with super-functions and super-instructions

In SPM, targeted systems such as PC clusters are modeled as VMs with high-level architecture similar to a PC [106]. The VM contains a super-processor consisting of an instruction fetch/dispatch unit (IDU) and multiple instruction execution units (IEUs) that form the ALUs of the VM. The important difference between the VM and a PC is that the functional units (FUs) in the VM are much coarser and each FU contains a complete "microcomputer system." These FUs are implemented as a set of processes running on member nodes. Communication channels between these processes carry out the functionality of "buses" in the VM. The main memory of nodes can work as data and instruction caches. All these implementation processes of the FUs make up the runtime support system.

The processors in the VM can execute some predefined abstract operations to manipulate a set of "built-in" data types that may be specific to the application. These data types are called as *super-data blocks* (SDBs) and are much coarser than an integer or floating point number. These abstract operations are called *super-instructions* (SIs). Programming in SPM ultimately is just coding application programs using SDBs and SIs.

SDBs work as abstract operands for SIs. They input data and receive result data. An SDB may be expressed in different local formats on different nodes. At runtime these SDBs are incarnated and mapped onto data structures stored in underlying nodes. Implementers are free to incarnate SDBs with any data structure. As long as the SDB formats have been set up along with the SDB exchange protocols, nodes with different architectures can freely exchange SDBs. This feature makes it very easy to work with heterogeneous clusters.

# 2.2 Super-Instruction Set Architecture

The instruction set architecture (ISA) is most important user interface of a computer. It bridges hardware implementations with software systems. It is the basis of programming. SPM also uses the concept of ISA. The super-instruction set (SIS) architecture is the core of SPM that becomes the interface to high-level programming.

# 2.2.1 Super-Instructions and Their Features

SIs are abstract "built-in" operations of the VM. Since the FUs of the VM are implemented with software programs, these SIs are mapped at runtime to ordinary procedures and are executed in the context of IEUs. Since IEUs are supported by complete PC nodes, they may be very powerful. But, SIs have the following features similar to ISAs for ordinary processors:

- SIs support atomic operations. Each SI can only be assigned to and be executed on a single IEU. Also there is no communication logic embedded in the body of an SI.

- 2) SIs are for abstract operations. Programs using SIs only care about the result of the executed SIs. Thus, system developers are free to implement SIs in any way and the runtime support system also is free to choose the most appropriate procedure in executing them.

- 3) The workload of an SI is predictable. Each SI has a set of known operands with a pre-defined size limitation. Thus, the workload of an SI has a quite accurate upper bound.

4) The data dependences are handled only at the beginning and end of an SI's execution. Once all operands are locally available, an SI can be executed without any interruption.

# 2.2.2 Functionality of Super-Instruction Sets

The chosen ISA in SPM is an instrument in customizing the clustered computer system. For each application domain, domain experts can develop an effective SI set architecture. Also, the SI set is expandable for each domain so that it matches the application's requirements. The SI set should provide all required basic operations. This is called completeness of the SI set. This makes it possible to express all applications in the domain with these SIs. The SI set encapsulates the underlying support system. This enhances portability and reusability of software components. Application programs are modelled as *super-programs* (SPs) that can be ultimately coded with SIs of the particular domain. Application programs just use SIs without a need to take care about the implementation of SIs.

SIs also provide a good basis for program porting. Since SIs are implemented with procedures, portability is enforced through standardizing SIs. As long as an efficient implementation exists for each SI on the nodes, SP code portability is guaranteed. The SIs also normalize operation workload. The workloads of SIs can be designed to have a similar upper bound. Thus, SIs can have expectable workloads. This provides a good basis for dynamically balancing the workload by appropriately scheduling these SIs. The multiple IEUs in the VM can be easily balanced through dynamically scheduling SIs to available processing units at run time. When the degree of parallelism in an SP is much larger than the number of nodes in the cluster, any node has little chance to be idle. Good load balancing becomes more feasible by focusing on scheduling at this coarser SI level.

# 2.3 Programming with SPM

Programming with SPM inherently is the process of developing programs with SIs for a specified application domain. For completeness, a high-level programming language and a corresponding compiler may be needed. However, for illustrative purposes in this dissertation, this process is simplified and embedded in the code used to implement the VM.

## 2.3.1 Super-Functions

To facilitate ease of developing applications, SPM adopts a structured programming style. Higher-level reusable programming units called *Super-Functions* (SFs) are developed. SFs are coded with SIs and/or other SFs. They may combine many SIs to form higher level abstract operations. SFs are "binary" executables for the VM. While executing SFs, the IDU fetches SIs in SFs and dispatches them to the IEUs to execute. More than holding a set of SIs, SFs also include order constraints in issuing SIs. By cooperating with the VM, SFs control how to issue the SIs in order and how to exploit parallelism.

# 2.3.2 Functionality of Super-Functions

Super-functions play a critical role in SPM. First, they provide a high-level abstract layer. It makes SPs to be more concise when expressed with SFs. These SFs can also be reused in either the same SP or different SPs as library components. Therefore, these SFs can be developed once and be used in many places. This can increase productivity and reduce the development time. Thus, ultimately they can reduce the cost of program development. Second, SFs play a critical role in the parallelization of SPs. As mentioned above, SPM targets parallel and distributed

systems and the VM provides the mechanism to execute multiple SIs simultaneously. Thus super-instruction level parallelism (sILP) is supported, while SIs are sequential procedures. This means that programmers and/or developing tools must deal with the parallelization when coding SPs. To parallelize the execution of SPs, the VM must extract parallelism among SIs when executing a SP. Since SFs include all SIs and also hold information about dependences among the SIs, these SFs, can cooperatively give the information that the VM need to schedule SIs, i.e., SFs are responsive of helping the VM to make execution of SPs parallel.