#### New Jersey Institute of Technology

## Digital Commons @ NJIT

**Dissertations**

**Electronic Theses and Dissertations**

Spring 5-31-2001

## Design of traffic shaper / scheduler for packet switches and DiffServ networks: algorithms and architectures

Surong Zeng New Jersey Institute of Technology

Follow this and additional works at: https://digitalcommons.njit.edu/dissertations

Part of the Electrical and Electronics Commons

#### **Recommended Citation**

Zeng, Surong, "Design of traffic shaper / scheduler for packet switches and DiffServ networks: algorithms and architectures" (2001). Dissertations. 491.

https://digitalcommons.njit.edu/dissertations/491

This Dissertation is brought to you for free and open access by the Electronic Theses and Dissertations at Digital Commons @ NJIT. It has been accepted for inclusion in Dissertations by an authorized administrator of Digital Commons @ NJIT. For more information, please contact digitalcommons@njit.edu.

## **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

#### ABSTRACT

## DESIGN OF TRAFFIC SHAPER/SCHEDULER FOR PACKET SWITCHES AND DIFFSERV NETWORKS: ALGORITHM AND ARCHITECTURE

### by Surong Zeng

The convergence of communications, information, commerce and computing are creating a significant demand and opportunity for multimedia and multi-class communication services. In such environments, controlling the network behavior and guaranteeing the user's quality of service is required. A flexible hierarchical sorting architecture which can function either as a traffic shaper or a scheduler according to the requirement of the traffic load is presented to meet the requirement. The core structure can be implemented as a hierarchical traffic shaper which can support a large number of connections with a wide variety of rates and burstiness without the loss of the granularity in cells' conforming departure time. The hierarchical traffic shaper can implement the exact sorting scheme with a substantial reduced memory size by using two stages of timing queues, and with substantial reduction in complexity, without introducing any sorting inaccuracy.

By setting a suitable threshold to the length of the departure queue and using a lookahead algorithm, the core structure can be converted to a hierarchical rate-adaptive scheduler. Based on the traffic load, it can work as an exact sorting traffic shaper or a Generic Cell Rate Algorithm (GCRA) scheduler. Such a rate-adaptive scheduler can reduce the Cell Transfer Delay and the Maximum Memory Occupancy greatly while keeping the fairness in the bandwidth assignment which is the inherent characteristic of GCRA. By introducing a best-effort queue to accommodate best-effort traffic, the hierarchical sorting architecture can be changed to a near work-conserving scheduler. It assigns remaining bandwidth to the best-effort traffic so

that it improves the utilization of the outlink while it guarantees the quality of service requirements of those services which require quality of service guarantees. The inherent flexibility of the hierarchical sorting architecture combined with intelligent algorithms determines its multiple functions. Its implementation not only can manage buffer and bandwidth resources effectively, but also does not require no more than off-the-shelf hardware technology.

The correlation of the extra shaping delay and the rate of the connections is revealed, and an improved fair traffic shaping algorithm, Departure Event Driven plus Completing Service Time Resorting algorithm, is presented. The proposed algorithm introduces a resorting process into Departure Event Driven Traffic Shaping Algorithm to resolve the contention of multiple cells which are all eligible for transmission in the traffic shaper. By using the resorting process based on each connection's rate, better fairness and flexibility in the bandwidth assignment for connections with wide range of rates can be given.

A Dual Level Leaky Bucket Traffic Shaper(DLLBTS) architecture is proposed to be implemented at the edge nodes of Differentiated Services Networks in order to facilitate the quality of service management process. The proposed architecture can guarantee not only the class-based Service Level Agreement, but also the fair resource sharing among flows belonging to the same class. A simplified DLLBTS architecture is also given, which can achieve the goals of DLLBTS while maintain a very low implementation complexity so that it can be implemented with the current VLSI technology.

In summary, the shaping and scheduling algorithms in the high speed packet switches and DiffServ networks are studied, and the intelligent implementation schemes are proposed for them.

## DESIGN OF TRAFFIC SHAPER/SCHEDULER FOR PACKET SWITCHES AND DIFFSERV NETWORKS: ALGORITHM AND ARCHITECTURE

by Surong Zeng

A Dissertation

Submitted to the Faculty of

New Jersey Institute of Technology

in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy in Electrical Engineering

Department of Electrical and Computer Engineering

May 2001

Copyright © 2001 by Surong Zeng

ALL RIGHTS RESERVED

### APPROVAL PAGE

# DESIGN OF TRAFFIC SHAPER/SCHEDULER FOR PACKET SWITCHES AND DIFFSERV NETWORKS: ALGORITHM AND ARCHITECTURE

## Surong Zeng

| Dr. Necdet Uzun, Dissertation Co-Advisor                         | Date            |

|------------------------------------------------------------------|-----------------|

| Chief Architect, AuroraNetics, Inc.                              |                 |

|                                                                  |                 |

|                                                                  |                 |

|                                                                  |                 |

|                                                                  |                 |

| Dr. Symeon Papavassiliou, Dissertation Co-Advisor                | Date            |

| Assistant Professor of Electrical and Computer Engineering, NJIT |                 |

|                                                                  |                 |

|                                                                  |                 |

|                                                                  |                 |

|                                                                  |                 |

| Dr. Nirwan Ansari, Committee Member                              | Date            |

| Professor of Electrical and Computer Engineering, NJIT           |                 |

|                                                                  |                 |

|                                                                  |                 |

|                                                                  |                 |

|                                                                  |                 |

| Dr. Sirin Tekinay, Committee Member                              | $\mathbf{Date}$ |

| Assistant Professor of Electrical and Computer Engineering, NJIT |                 |

|                                                                  |                 |

|                                                                  |                 |

|                                                                  |                 |

|                                                                  |                 |

| Dr. Haldun Hadimioglu, Committee Member                          | Date            |

| Associate Professor of Computer and Information Science,         |                 |

| Polytechnic University, Brooklyn, NY                             |                 |

#### BIOGRAPHICAL SKETCH

Author: Surong Zeng

**Degree:** Doctor of Philosophy

**Date:** May 2001

#### Undergraduate and Graduate Education:

• Doctor of Philosophy in Electrical Engineering, New Jersey Institute of Technology, Newark, NJ 2001

- Master of Science in Electrical Engineering,

University of Electronic Science and Technology of China,

Chengdu, Sichuan, P.R.China, 1998

- Bachelor of Science in Electrical Engineering,

University of Electronic Science and Technology of China,

Chengdu, Sichuan, P.R.China, 1995

Major: Electrical Engineering

#### **Publications and Presentations:**

S. Zeng, N. Uzun,

"A Hierarchical Traffic Shaper for Packet Switches", *Proc. of IEEE GLOBECOM'99*, pp. 1655-1659, Rio de Janeiro, Brazil, Dec. 1999.

- S. Zeng, N. Uzun, T. Mehmet, and N. Gogate,

"A Novel Hierarchical Rate-Adaptive Scheduler for High Speed

Packet Switches",

Networld+Interop'2000, Las Vegas, NV, May 2000.

- S. Zeng, N. Uzun,

"A Novel Hierarchical Traffic Shaper/Scheduler for High Speed

Packet Switches", submitted to *IEEE/ACM Transaction on Networking*, March 2000.

S. Zeng, N. Uzun, and S. Papavassiliou,

"An Improved Fair Traffic Shaping Algorithm for High Speed

Packet Switches",

accepted by Proc. of 2001 IEEE Workshop on High Performance

Switching and Routing, Dallas, TX, May 2001.

S. Zeng, N. Uzun, and S. Papavassiliou, "A Dual Level Leaky Bucket Traffic Shaper Architecture for DiffServ Networks", accepted by Proc. of 2001 IEEE Workshop on High Performance Switching and Routing, Dallas, TX, May 2001.

S. Zeng, N. Uzun, and S. Papavassiliou,

"A Dual Level Access Control Architecture for DiffServ Networks"

submitted to Journal of Network and Systems Management, April 2001.

This work is dedicated to my beloved family

#### ACKNOWLEDGMENT

First and foremost, I would like to express my sincere gratitude to my advisors and mentors, Dr. Necdet Uzun and Dr. Symeon Papavassiliou. I would like to thank Dr. Uzun, an excellent advisor and a good friend, for introducing me to this exciting field of research; for his constant support, guidance and encouragement in every step of my way; and for his inspiration and valuable discussions. I appreciate Dr. Papavassiliou for his excellent suggestions; and for the time he has put into help me to make the dissertation complete.

I would like to thank my dissertation committee, Dr. Nirwan Ansari, Dr. Sirin Tekinay, and Dr. Haldun Hadimioglu (Brooklyn Polytechnic), for their being interested in this work and stimulating valuable discussions and suggestions.

I would like to thank all fellow researchers at NJCMR for all the help they have offered during my doctoral research. I would especially like to thank Feihong Chen and Jie Yang for patiently discussing with me, and giving me valuable suggestions. I would also like to thank Qiang Peng, Bin He, Xufei Wei, Minyi Zhao, Xiaodong Cai for their continuous help and advice since the first day I joined NJIT. I would like to thank all my friends at NJCMR for making my stay here enjoyable.

Words cannot express the gratitude I felt toward my parents, whose support provides the foundation upon which this work was built.

## TABLE OF CONTENTS

| $\mathbf{C}$ | hapt | e <b>r</b> P                                                                                 | age |

|--------------|------|----------------------------------------------------------------------------------------------|-----|

| 1            | INT  | RODUCTION                                                                                    | 1   |

|              | 1.1  | Background                                                                                   | 1   |

|              | 1.2  | Outline of the Dissertation                                                                  | 2   |

| 2            | REI  | LATED WORK OVERVIEW                                                                          | 6   |

|              | 2.1  | Traffic Management Framework                                                                 | 7   |

|              | 2.2  | Traffic Parameters and QoS Parameters                                                        | 11  |

|              | 2.3  | ATM Service Classes                                                                          | 15  |

|              | 2.4  | Traffic Shaping                                                                              | 17  |

|              |      | 2.4.1 Generic Cell Rate Algorithm                                                            | 18  |

|              |      | 2.4.2 Event-Driven Traffic Shaping Algorithms                                                | 21  |

|              | 2.5  | QoS in Internet                                                                              | 25  |

|              |      | 2.5.1 Integrated Services and RSVP                                                           | 25  |

|              |      | 2.5.2 Differentiated Services                                                                | 32  |

| 3            | THE  | E HIERARCHICAL TIMING QUEUES TRAFFIC SHAPER                                                  | 36  |

|              | 3.1  | Motivation for the Hierarchical Timing Queues Traffic Shaper                                 | 36  |

|              |      | 3.1.1 Existing Traffic Shaper Architectures                                                  | 36  |

|              |      | 3.1.2 Problems in the Existing Traffic Shaper Architecture                                   | 39  |

|              | 3.2  | The Architecture Description for the Hierarchical Traffic Shaper                             | 41  |

|              | 3.3  | The Algorithm Description for the Hierarchical Traffic Shaper                                | 44  |

|              | 3.4  | Performance Evaluation for the Hierarchical Traffic Shaper                                   | 47  |

| 4            |      | E RATE-ADAPTIVE SCHEDULER IMPLEMENTED BY HIERAR-HICAL SORTING UNITS WITH LOOKAHEAD ALGORITHM | 60  |

|              | 4.1  | Introduction                                                                                 | 60  |

# TABLE OF CONTENTS (Continued)

| $\mathbf{C}$ | hapt | er Pag                                                                                               | ge  |

|--------------|------|------------------------------------------------------------------------------------------------------|-----|

|              | 4.2  | Algorithm Description of the Hierarchical Rate-Adaptive GCRA Scheduler with Lookahead Algorithm      | 61  |

|              | 4.3  | Performance Evaluation of the Hierarchical Rate-Adaptive Scheduler with Lookahead Algorithm          | 67  |

|              | 4.4  | The Hierarchical Near Work-Conserving Scheduler with Best Effort Traffic                             | 70  |

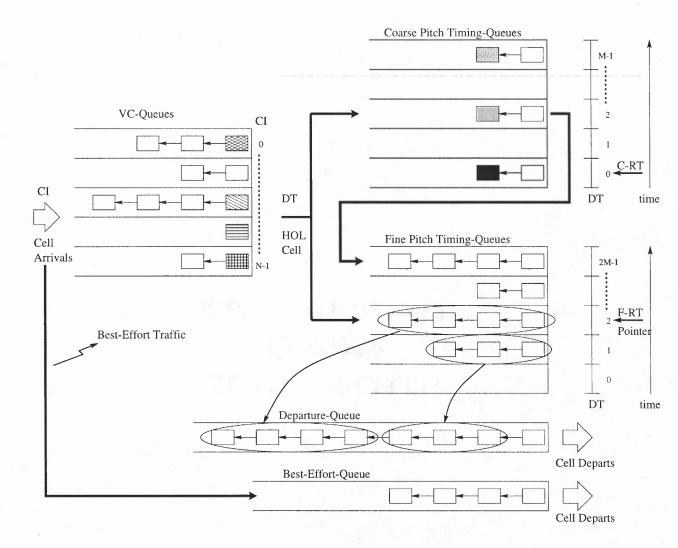

|              |      | 4.4.1 The Architecture of Hierarchical near Work-Conserving Scheduler with Best Effort Traffic       | 70  |

|              |      | 4.4.2 Performance Evaluation for the Hierarchical Work-Conserving Scheduler with Best Effort Traffic | 72  |

| 5            |      | IMPROVED FAIR TRAFFIC SHAPING ALGORITHM AND IMPLE-<br>ENTATION                                       | 74  |

|              | 5.1  | Revisit Existing Shaping Algorithms                                                                  | 75  |

|              | 5.2  | Departure Event Driven plus Completing Service Time ReSorting (DED+CTS) Traffic Shaping Algorithm    | 78  |

|              |      | 5.2.1 Motivation and Description of the Algorithm                                                    | 78  |

|              |      | 5.2.2 Implementation of the Algorithm                                                                | 81  |

|              | 5.3  | Performance Evaluation for DED+CTS Algorithm                                                         | 83  |

| 6            |      | UAL LEVEL ACCESS CONTROL ARCHITECTURE FOR DIFFSERV ETWORKS                                           | 86  |

|              | 6.1  | Motivation for Dual Level Access Control Architecture for DiffServ Networks                          | 86  |

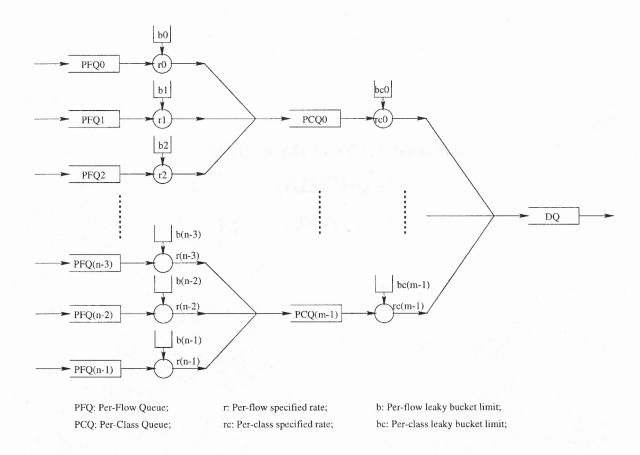

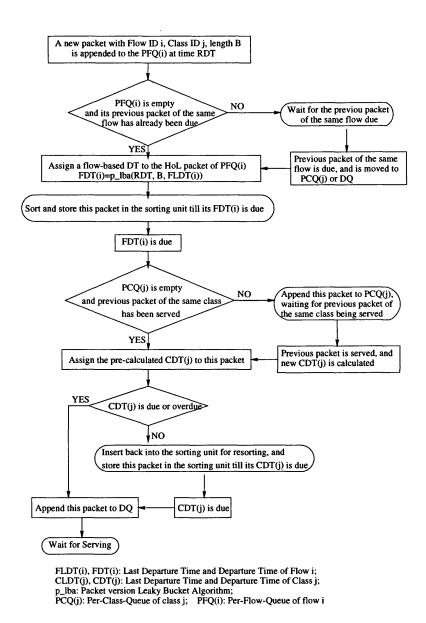

|              | 6.2  | Dual Level Leaky Bucket Traffic Shaper for DS Networks                                               | 88  |

|              |      | 6.2.1 Leaky Bucket Traffic Shaping Algorithm for Variable Length Packet                              | 88  |

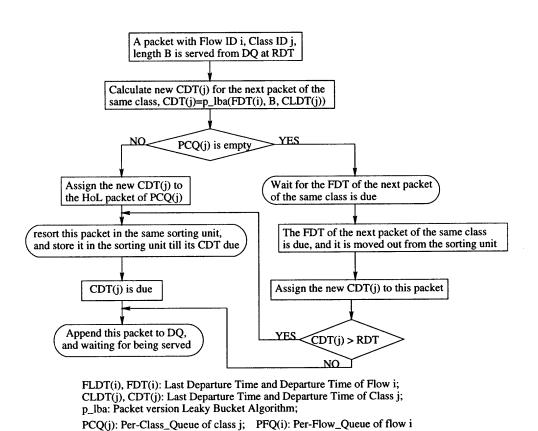

|              |      | 6.2.2 Dual Level Leaky Bucket Traffic Shaper                                                         | 88  |

|              | 6.3  | Practical Implementation DLLBTS Architecture                                                         | 91  |

|              | 6.4  | Performance Evaluation for Dual Level Leaky Bucket Traffic Shaper Architecture                       | 93  |

| 7            | COI  | NCLUSIONS AND FUTURE WORK                                                                            | 101 |

## TABLE OF CONTENTS (Continued)

| Pag                                                                          | ,e |

|------------------------------------------------------------------------------|----|

| PPENDIX A NUMBER OF THE BACKLOGGED CONFORMING CELLS IN A SHAPING MULTIPLEXER | 04 |

| PPENDIX B CONFORMING DEPARTURE TIME BASED PGPS 10                            | 07 |

| EFERENCES                                                                    | 09 |

## LIST OF FIGURES

| Figu | P                                                                                                       | age |

|------|---------------------------------------------------------------------------------------------------------|-----|

| 2.1  | Cell Transfer Delay Probability Density Model [34]                                                      | 14  |

| 2.2  | ATM Service Category Attributes [34, 44]                                                                | 16  |

| 2.3  | Generic Cell Rate Algorithm [34]                                                                        | 19  |

| 2.4  | Depiction of GCRA(I, L) [81]                                                                            | 19  |

| 2.5  | Arrival Event Driven Traffic Shaping Algorithm                                                          | 22  |

| 2.6  | An Example of DT Calculation Diagram for AEDTS (L=2, I=4, GCRA(4, 2))                                   | 23  |

| 2.7  | Clumping Phenomenon in AEDTS (both connections with L=2, I=4) $\ .$ .                                   | 24  |

| 2.8  | Departure Event Driven Traffic Shaping Algorithm                                                        | 26  |

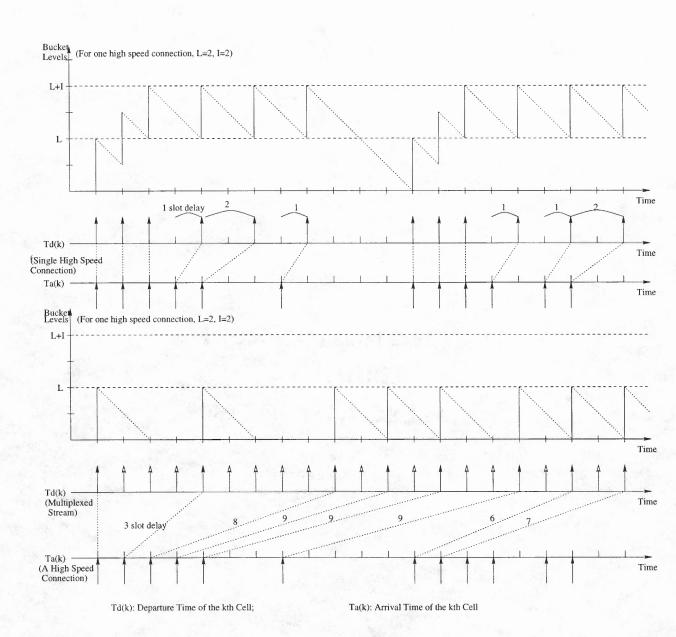

| 2.9  | An Example of DT Calculation Diagram of DEDTS (L=2, I=4) $\dots$                                        | 27  |

| 2.10 | An Example of DT Calculation of DEDTS in Multiplexing Scenario (both connections with L=2, I=4) $\dots$ | 28  |

| 2.11 | RSVP Signaling Process                                                                                  | 30  |

| 2.12 | The Implementation Reference Model of IntServ/RSVP [9]                                                  | 31  |

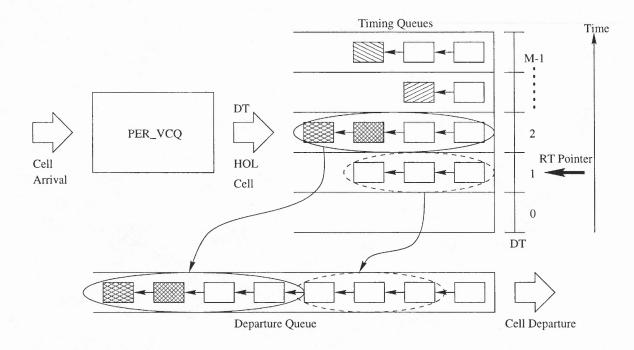

| 3.1  | Direct Exact Sorting Architecture                                                                       | 36  |

| 3.2  | Rate-Based Grouping Traffic Shaper                                                                      | 38  |

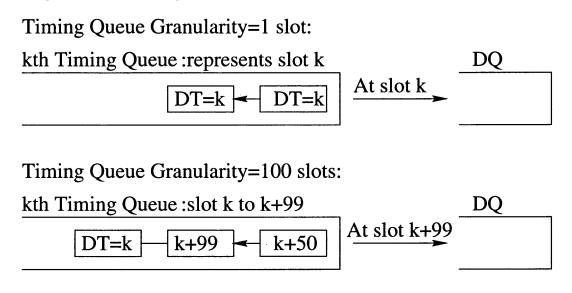

| 3.3  | Timing Queue Granularity Depiction                                                                      | 40  |

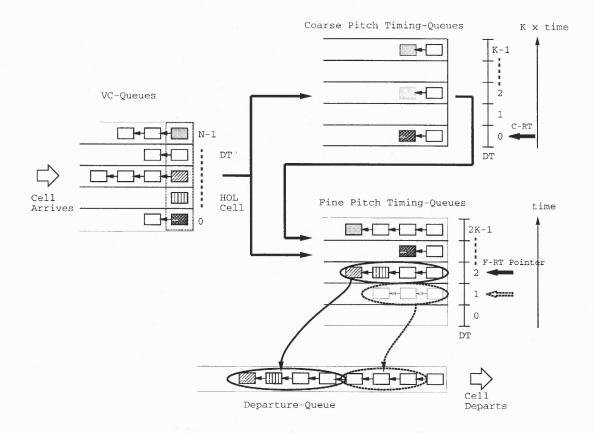

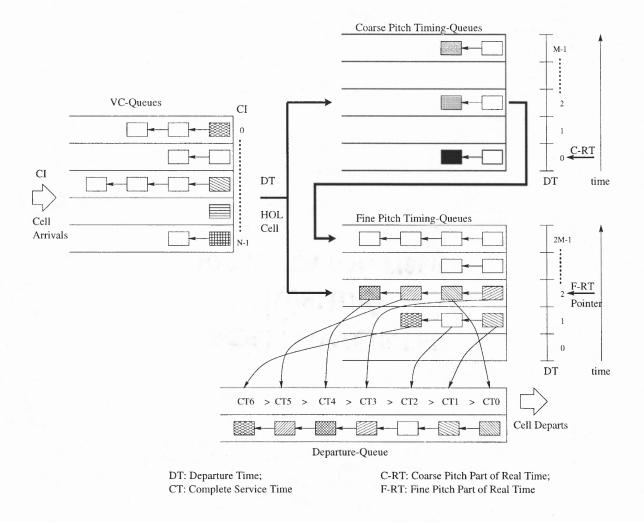

| 3.4  | Traffic Shaper with Hierarchical Timing Queues                                                          | 42  |

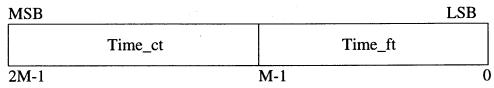

| 3.5  | Data Structure of Time Register                                                                         | 43  |

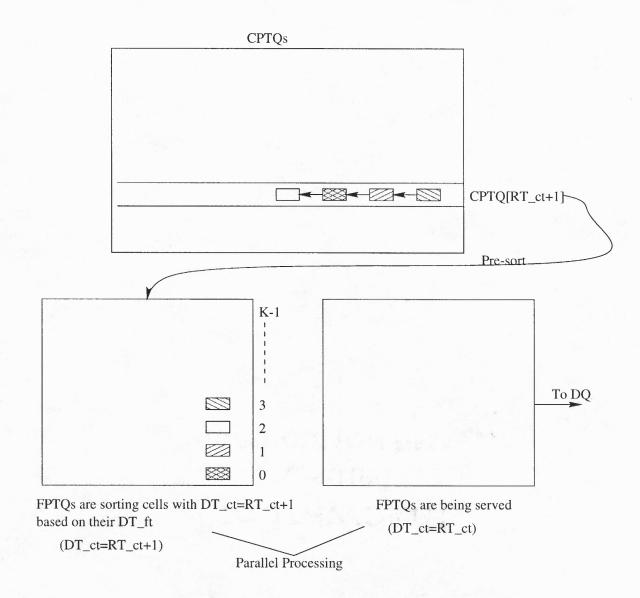

| 3.6  | The Process of the Prefetching Scheme                                                                   | 50  |

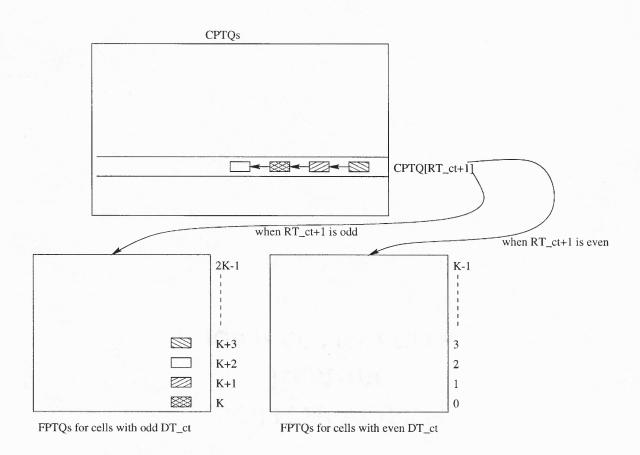

| 3.7  | The Real Implementation of the Prefetching Scheme                                                       | 51  |

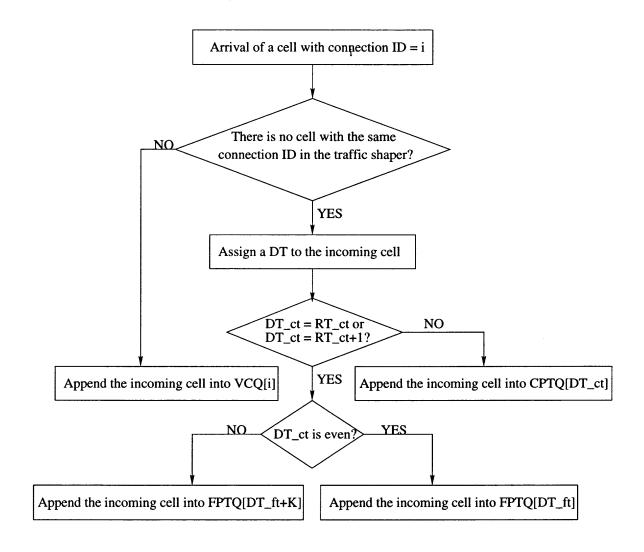

| 3.8  | The Process Triggered by the Arrival of A Cell with the Connection ID i                                 | 52  |

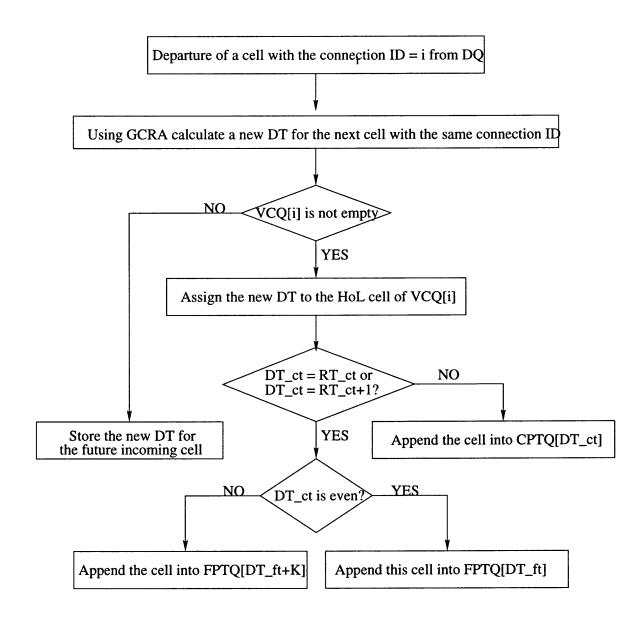

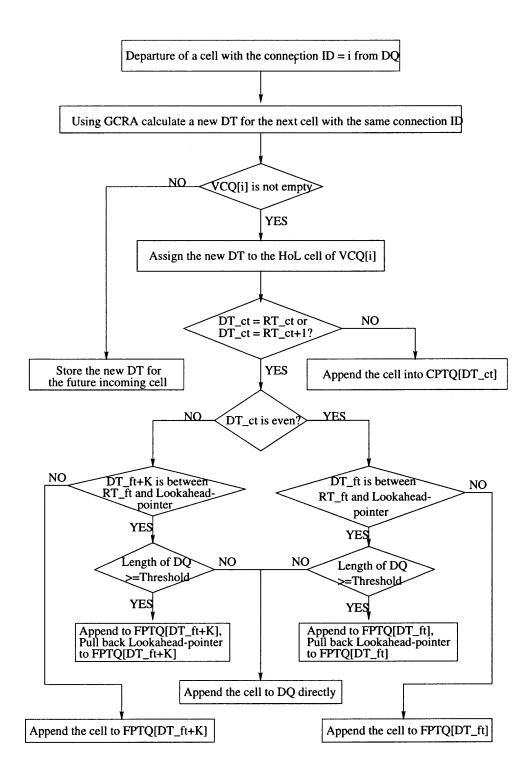

| 3.9  | The Process Triggered by the Departure of A Cell with the Connection ID i from DQ                       | 53  |

## LIST OF FIGURES (Continued)

| Figu | ire Pa                                                                       | age |

|------|------------------------------------------------------------------------------|-----|

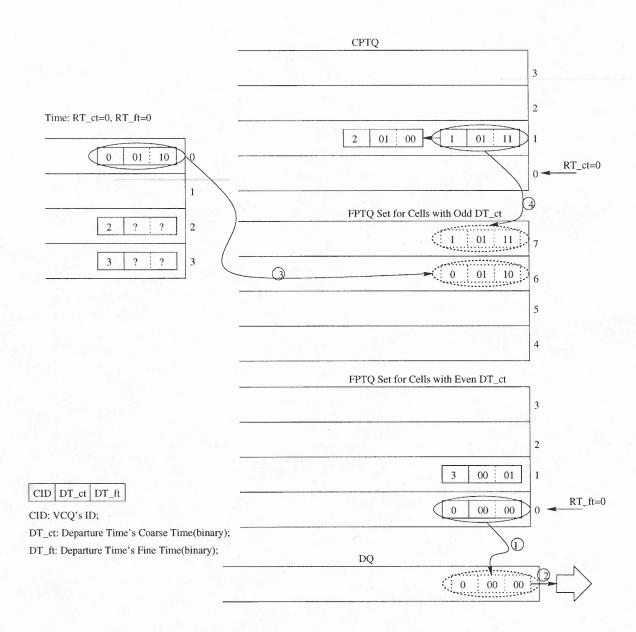

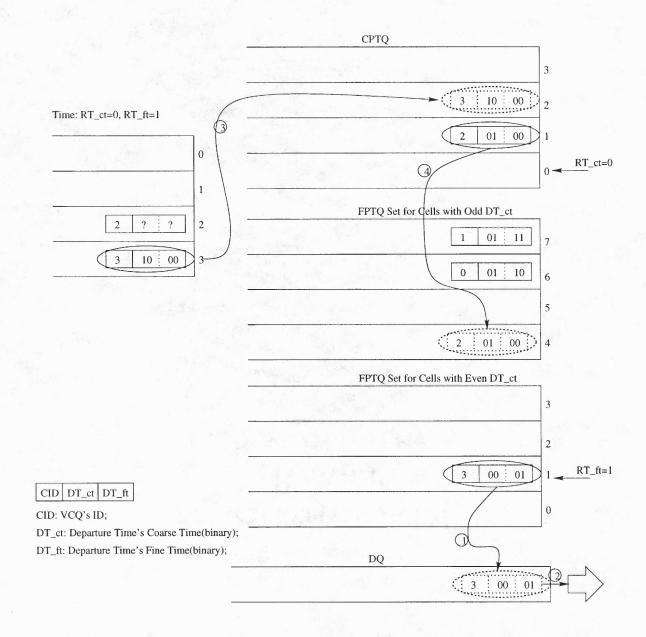

| 3.10 | The Process of Moving Cells between VCQ, CPTQ, FPTQ (Slot 0)                 | 54  |

| 3.11 | The Process of Moving Cells between VCQ, CPTQ, FPTQ (Slot 1)                 | 55  |

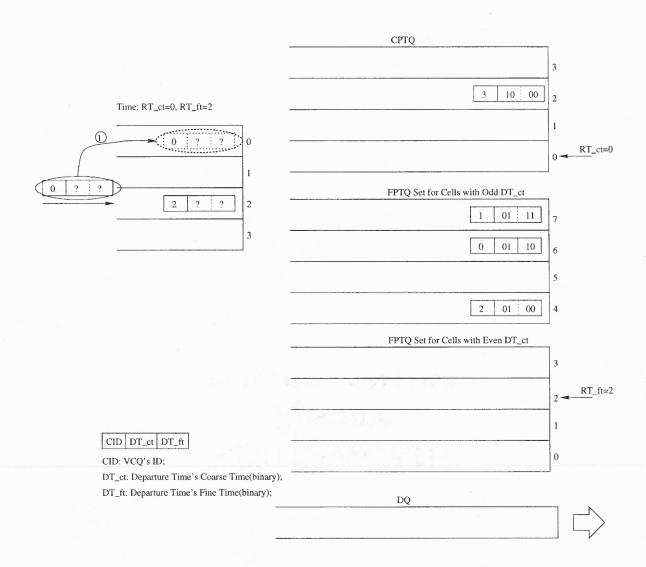

| 3.12 | The Process of Moving Cells between VCQ, CPTQ, FPTQ (Slot 2)                 | 56  |

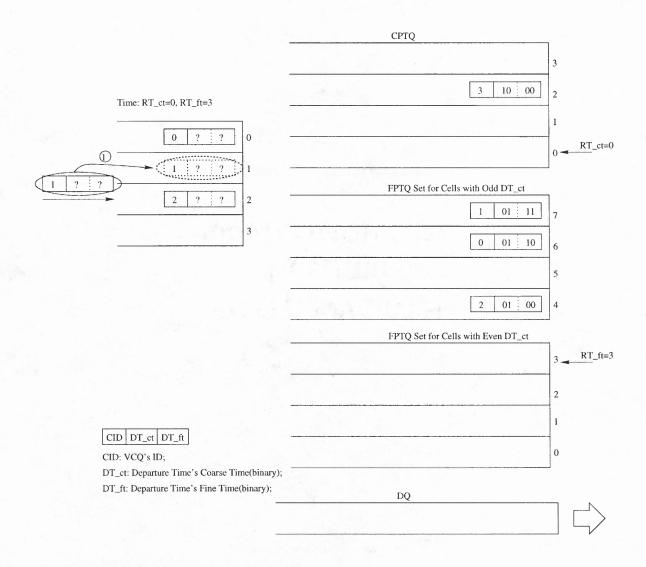

| 3.13 | The Process of Moving Cells between VCQ, CPTQ, FPTQ (Slot 3)                 | 57  |

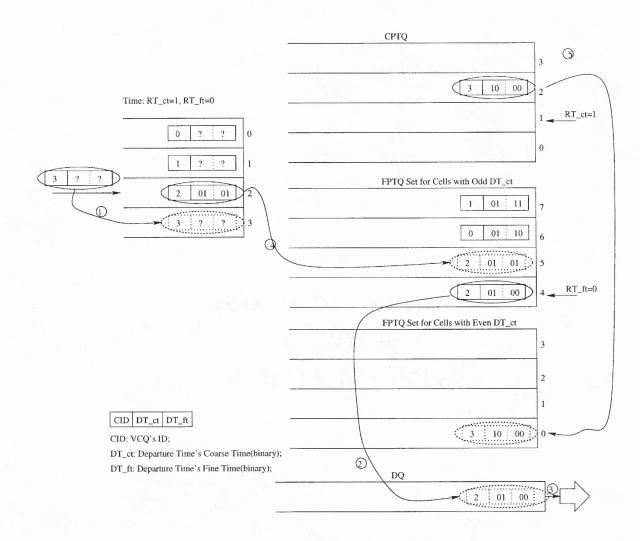

| 3.14 | The Process of Moving Cells between VCQ, CPTQ, FPTQ (Slot 4)                 | 58  |

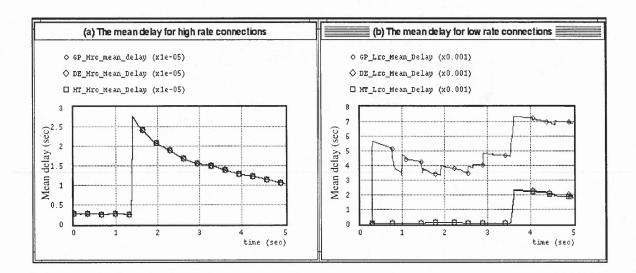

| 3.15 | Mean Cell Delay for these three schemes                                      | 59  |

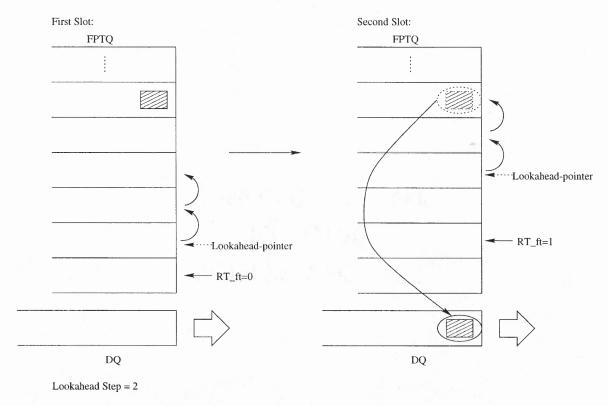

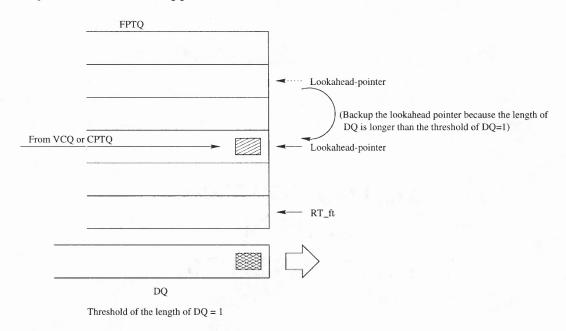

| 4.1  | An Example of Moving the Lookahead Pointer                                   | 62  |

| 4.2  | The Scenario of Backing Up the Lookahead Pointer                             | 63  |

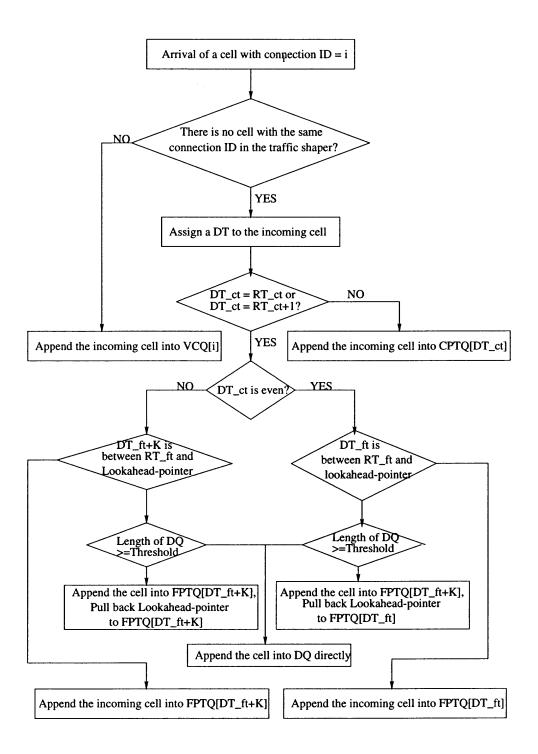

| 4.3  | Process Triggered by the Arrival of A Cell in HRAS                           | 65  |

| 4.4  | Process Triggered by the Departure of A Cell in HRAS                         | 66  |

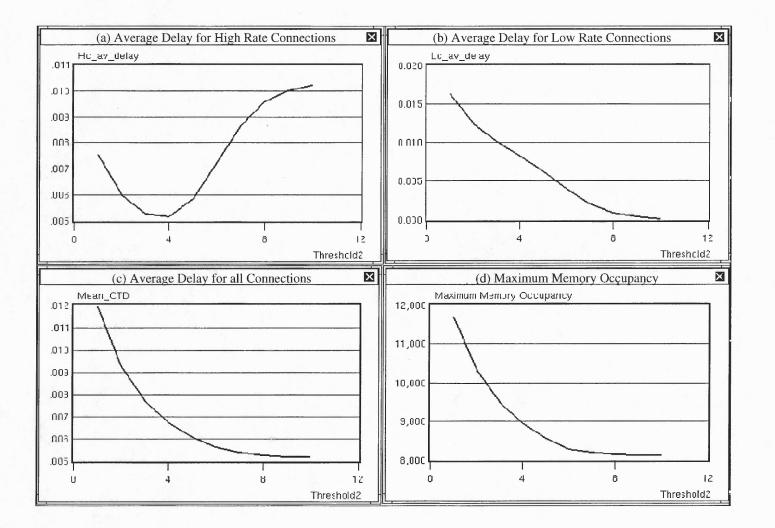

| 4.5  | The effect of different threshold of DQ length (delay: second)               | 69  |

| 4.6  | The Performance Comparison under Heavy Traffic Load $ ho=0.9$                | 70  |

| 4.7  | The Performance Comparison under Light Traffic Load $ ho=0.6\ldots$          | 71  |

| 4.8  | Hierarchical Work-Conserving Scheduler with BEQ                              | 72  |

| 4.9  | Performance Comparison between the Scheduler with BEQ and the Traffic Shaper | 73  |

| 5.1  | Functional Model of Conventional DEDTS algorithm                             | 78  |

| 5.2  | Extra Shaping Delay in DEDTS (L=2, I=2, GCRA(2,2))                           | 80  |

| 5.3  | The Implementation Architecture of DED+CTS Algorithm                         | 82  |

| 5.4  | The Performance Comparison for DED+CTS and DEDTS                             | 84  |

| 6.1  | Logic Architecture of a Packet Classifier and Traffic Conditioner [5]        | 87  |

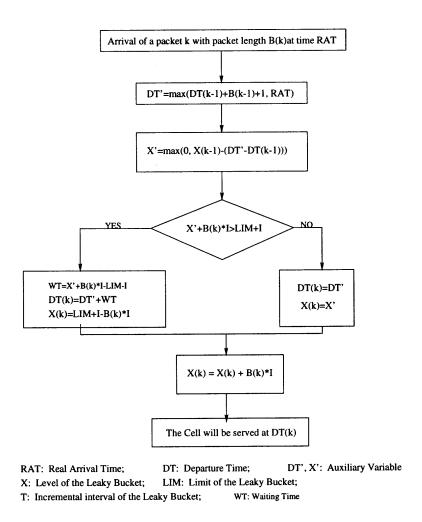

| 6.2  | Packet-Version Leaky Bucket Algorithm                                        | 89  |

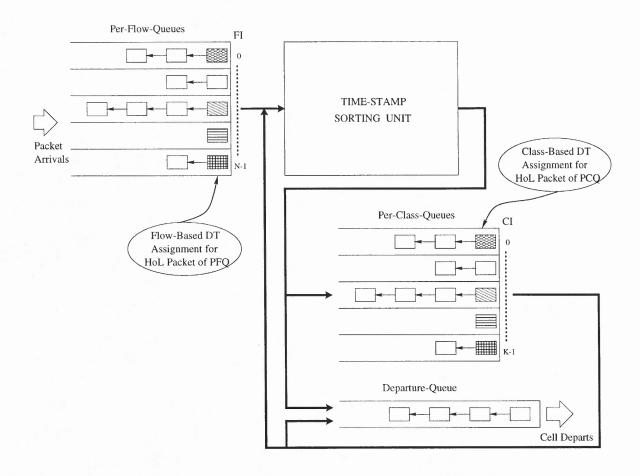

| 6.3  | Dual Level Traffic Shaper Architecture in the Edge Node of DiffServ Network  | 90  |

| 6.4  | Simplified DLLBTS Architecture in the Edge Node of DiffServ Network .        | 92  |

| 6.5  | The Operation Process Triggered by The Arrival of A Packet                   | 97  |

| 6.6  | The Operation Process Triggered by The Departure of A Packet                 | 98  |

## LIST OF FIGURES (Continued)

| Figu | ıre                                                                      | age |

|------|--------------------------------------------------------------------------|-----|

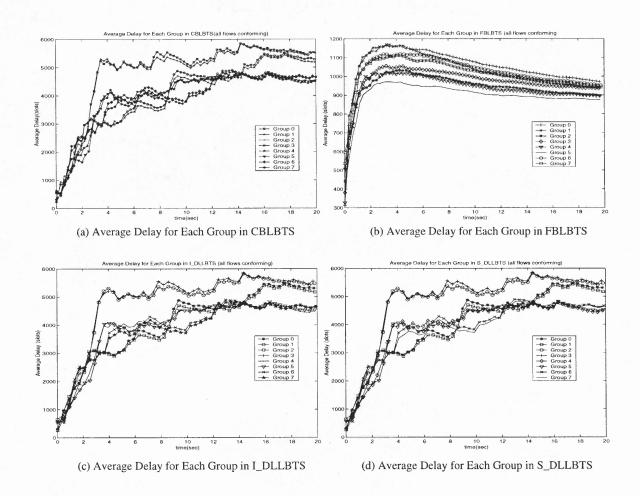

| 6.7  | The Average Packet Delay of Each Group (all flows conforming)            | 99  |

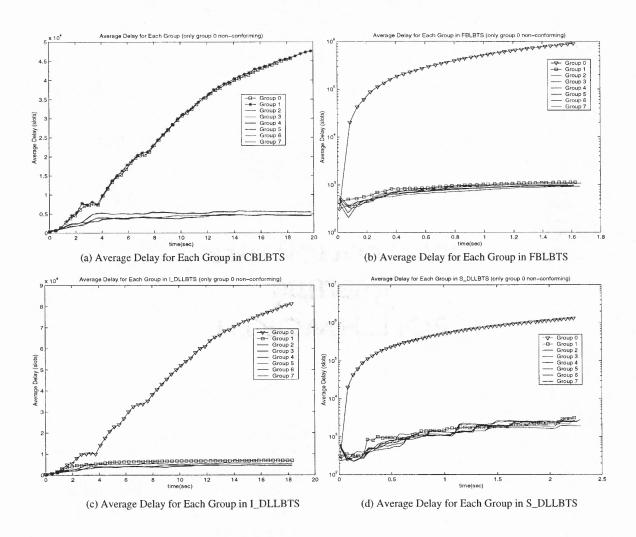

| 6.8  | The Average Packet Delay of Each Group (flows of group 0 non-conforming) | 100 |

| 6.9  | Class-Based Violation Comparison in All Schemes                          | 100 |

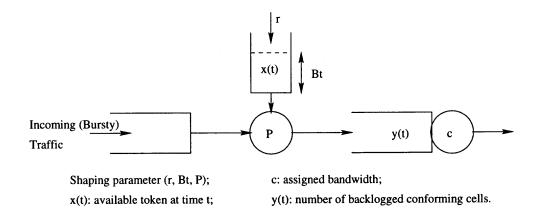

| A.1  | Single Source Shaping System Model                                       | 105 |

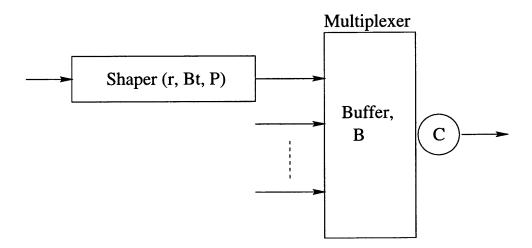

| A.2  | Multiple Source Shaping Multiplexer                                      | 105 |

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 Background

Broadband networks must accommodate integrated services with a very wide range of Quality of Service (QoS) requirements, such as voice, video, and data. In order to utilize network resources effectively while providing a broad range of satisfactory QoS guarantees to all users on the network, traffic regulation at the network edge is necessary. Connections are monitored by network operators based on the traffic contract established during admission control [15]. If a connection does not conform to the traffic contract, a Usage Parameter Control (UPC) device at the network edge can discard the violating cells or tag them to a lower priority. It also can employ traffic shaping to delay non-conforming cells until they are compliant with conditions described by the traffic contract [45, 61, 88].

The widely used traffic shaping and scheduling algorithm is the Generic Cell Rate Algorithm (GCRA), which is also known as leaky bucket algorithm [7, 12, 39, 71, 79]. The GCRA is used to judge whether an incoming cell conforms to the negotiated QoS parameters, and calculate its earliest conformance time. The QoS parameters for each service are a set of values that pertain to delay and loss of the transferred cells. These values are negotiated between the user and the network, and the network promises to guarantee the QoS requirements of the user's service only when the user conforms to these values. The user has to specify the traffic parameters of the source so that the network can estimate the bandwidth correctly. These traffic parameters may include Peak Cell Rate (PCR), Cell Delay Variation Tolerance (CDVT), Sustained Cell Rate (SCR), and Burst Tolerance (BT) [34]. A different set of traffic parameters is specified for each service category that the network provides.

In the design of a traffic shaper, three essential attributes should be taken into consideration: (1) low system delay for incoming cells; (2) simplicity and low cost in the implementation of sorting time stamps in order to select the cell with the minimum conformance time; and (3) fairness of bandwidth assignment. Generally, the delay, and the implementation complexity are the most important criteria for a system design [82]. The implementation complexity and cost are dominated by the complexity of sorting and storing time stamps [23]. Based on the GCRA, many implementations of traffic shapers are proposed, such as direct exact sorting scheme, rate-based grouping scheme, etc.

#### 1.2 Outline of the Dissertation

A new traffic shaper architecture with hierarchical timing queues is proposed in this dissertation. In this new architecture, two stages of timing queues are used to implement the exact sorting algorithm so that this shaper architecture can substantially reduce the number of subqueues needed to store time stamps. Meanwhile, the exact sorting algorithm is combined with the UPC compliant departure event driven traffic shaping (DEDTS) algorithm [15], so that there is at most one cell for every connection in the sorting unit at any given time. Consequently, sorting unit complexity can be reduced. In contrast to various existing architectures for implementing a traffic shaper, the proposed implementation can reduce the cost and complexity greatly by reducing memory size substantially and eliminating complex arbitration logic of a scheduler.

This hierarchical traffic shaper can be implemented as a hierarchical rateadaptive scheduler by using a rate-based lookahead algorithm. When the traffic load is light, this hierarchical rate-adaptive scheduler can work as a GCRA scheduler to reduce the Cell Transfer Delay (CTD) and Maximum Memory Occupancy (MMO) in comparison with those of the traffic shaper. When the traffic load is heavy, it performs the shaping function in order to avoid the congestion of the outlink.

This hierarchical sorting architecture can also be implemented as a near work-conserving scheduler. Generally, in a high speed packet switch hardware design, a memory limit and a cell loss ratio limit should be given. Under these two conditions, the maximum accepted traffic which requires QoS guarantees and the maximum outlink utilization are set. Under the same conditions, a best-effort queue is introduced to accommodate the best-effort traffic, and the remaining bandwidth is assigned to it. Such a scheduler not only improves the outlink utilization, but also relaxes the Connection Admission Control(CAC) constraints.

An improved fair traffic shaping algorithm is also proposed in this dissertation. It modifies the DEDTS algorithm by adding a process to resort the Completing Service Time stamps (CT) of all conforming cells. The CT is the sum of the conforming Departure Time (DT) and the service time of its associated connection. The service time of a connections is the reciprocal of the rate of the connection. By resorting the CT stamps, conforming cells can be prioritized based on the rates of the connections, and the available bandwidth can assigned more fairly so that this algorithm reduces the shaping delay of high rate connections greatly. This algorithm can be implemented by modifying the Hierarchical Timing Queues Traffic Shaper architecture easily.

Currently, the Internet can not support Quality of Service (QoS) requirements. With the growth of the Internet, more and more applications demand QoS support from the networks. To meet these demands, the Integrated Services architecture was proposed first by Internet Engineering Task Force (IETF). In the Integrated Services (IntServ) networks, all QoS mechanisms are flow-based. However, there are generally thousands, even ten or hundred thousands of flows in the network at the same time. The state information and processing capability are proportional

to the number of flows, therefore, IntServ is definitely unscalable to the Internet. In order to resolve the scalability problem while keeping the QoS support function, Differentiated Services (DiffServ) architecture is proposed [4, 91].

In the DiffServ networks, the traffic conditioner is one of the most important part, and the shaper is one of its components. In the IETF draft, a rate adaptive shaper for DiffServ networks was proposed [6]. However, it doesn't resolve the fair resource sharing problem for flows in the same class. In this dissertation, a Dual Level Leaky Bucket Traffic Shaper (DLLBTS) architecture is proposed for the edge nodes of DiffServ networks. In DLLBTS architecture, there are two levels of leaky buckets. The first level is a set of flow-based leaky buckets. It can shape flows based on the traffic profile of each flow so that it can guarantee that all flows can fairly share the network resources in the same class when they merge into one class. The second one is a set of class-based leaky buckets same as all other traffic shapers for interior nodes of the DiffServ networks. They can guarantee the aggregate behavior of a class conforming to the Service Level Agreement (SLA). However, two sets of leaky bucket traffic shaper need two sets of sorting units, and generally, the sorting unit dominates the complexity of the implementation of a traffic shaper. It is an expensive solution to implement two sets of complex sorting units in a traffic shaper. A simplified DLLBTS is proposed, which combines the two levels of leaky buckets to one stage so that only one set of sorting unit is needed. The simulation results show that the simplified DLLBTS can reach the goal of DLLBTS while keeping the low implementation complexity.

The dissertation is organized as follows. The second chapter reviews the related work, including traffic management, traffic parameters, event-driven traffic shaping algorithms, and QoS in Internet. The third chapter describes the details of the proposed hierarchical traffic shaper architecture, and compares it with two other architectures. It shows that the new architecture has lower implementation

complexity and cost. In this chapter, the performance evaluation for the hierarchical traffic shaper is given, and it shows that the simplified implementation performs as well as the exact sorting scheme. The fourth chapter presents the rate-adaptive scheduler implemented by hierarchical sorting units with a lookahead algorithm, and gives the performance evaluation. In the same chapter, the hierarchical near work-conserving scheduler with best effort traffic is also given. It is implemented by adding a best-effort queue to accommodate the best effort traffic, and it shows that the proposed technique improves the outlink utilization without increasing memory occupancy and cell loss ratio for service with QoS requirements. The fifth chapter depicts the improved fair traffic shaping algorithm and its implementation. The performance evaluation shows that this proposed traffic shaping algorithm can give better fairness performance in the bandwidth allocation. The sixth chapter proposes DLLBTS for the edge node of DiffServ networks, and a simplified DLLBTS architecture is proposed for implementation purposes. The last chapter draws conclusions.

## CHAPTER 2 RELATED WORK OVERVIEW

The network is becoming ubiquitous, and more and more applications require the network to support high quality of service which generally has to consume much more network resources. Although the network capacity is increasing at an astounding rate, users still suffer from the congested network, and with the development of the high-bandwidth requirement applications, this situation will not be alleviated in the near future [4]. In order to enhance the ability of a network to offer high-quality service guarantees while simultaneously making efficient use of raw network resources, sophisticated QoS mechanisms have to be adopted. QoS mechanisms are a set of technologies that enable network administrators to reduce, even avoid the effects of congestion on application traffic by using network resources optimally, rather than by continually adding capacity [4]. The most common QoS mechanisms include scheduling, shaping, policing, admission control, intelligent routing etc. [91]. To meet appropriate differentiated QoS requirements, the ATM Forum proposed a framework for managing traffic and controlling congestion in ATM networks [34]. The framework consists of many QoS mechanisms, which will be discussed later.

In this chapter, the framework of the traffic management in ATM networks is described. Traffic regulations, including traffic descriptor, QoS parameters, and regulation algorithm based on these parameters are also discussed. Users specify the traffic parameters to describe their traffic in a quantitative means. According to the characteristics and QoS requirements of the traffic, service classes are defined in the ATM networks, which are discussed in the third section. Based on the traffic information and the current network state, administrators of the network can deploy CAC to make a connection decision. Once the connection is accepted, there is a traffic contract constructed. A traffic contract is a legal binding agreement between users and networks [44]. It is defined by the users' traffic descriptor, QoS requirement, and

connection descriptor. In the whole duration of the communication, administrators employ Usage/Network Parameter Control (UPC/NPC) to monitor whether the behavior of the traffic conforms to the traffic contract or not. For the non-conforming traffic, there are many algorithms and regulations which can be deployed to regulate it. The widely used policing and shaping algorithm Generic Cell Rate Algorithm (GCRA) is explained, and the existing event-driven traffic shaping algorithms are discussed in the fourth section. Finally, the QoS in the Internet is discussed, and IntServ and DiffServ are described and compared in this chapter.

#### 2.1 Traffic Management Framework

Traffic management is to protect the network and the end-system from congestion in order to achieve high network performance, provide high QoS guarantees, as well as promote the efficient use of the network resources [34, 81, 90].

In order to meet such objectives, a framework for managing and controlling traffic and congestion in ATM networks is proposed by ATM Forum [34]. It consists of the following QoS mechanisms:

- Connection Admission Control (CAC)

- Usage/Network Parameter Control (UPC/NPC) (traffic policing)

- Cell Loss Priority Control

- Traffic Shaping

- Network Resource Management (NRM)

- Feedback Controls

- Frame Discard (Memory Management)

- ABR Flow Control

#### • Other control functions

In this section, the functions in the QoS framework of ATM networks are discussed as the following, except the traffic shaping which will be studied in details in the later sections.

#### • Connection Admission Control (CAC):

Connection admission control is the first line of defense for the network in protecting itself from excessive loads [81]. It is defined as the set of actions taken by the network at the call setup phase (or during a call renegotiation phase) to determine whether the connection can be accepted or not. Only when there are sufficient network resources to accommodate the new connection without impacting the performance of other existing connections, the new connection can be accepted. At the instance of the connection establishment, the traffic contract is formed by being negotiated with the user. During the whole period of the connection lifetime, the network resources will be deployed to satisfy the QoS requirements of the connection if its traffic complies with the traffic contract [34, 58, 81, 90].

In ATM networks, the CAC is to determine whether a Virtual Channel Connection (VCC) or a Virtual Path Connection (VPC) can be accepted. In the multimedia application scenario, one call can require more than one connection, then the CAC procedures are performed for each VCC or VPC [90]. Some CAC algorithms and schemes are proposed in [31, 29, 37, 53, 75].

## • Usage/Network Parameter Control (UPC/NPC)(traffic policing):

The UPC and the NPC are defined as a set of actions taken by the network to monitor and control traffic conforming to the traffic contract at the User-Network Interface (UNI) and the Network-Network Interface (NNI), respectively. They are also known as traffic policing, which is one of the most important QoS mechanisms. The main role of the UPC/NPC is to protect network resources from malicious as well as unintentional misbehavior by detecting violations of negotiated parameters, and taking appropriate action, such as marking, dropping, or shaping [90]. Networks may use different UPC/NPC algorithm to police different service classes. Algorithms for the UPC/NPC are primarily based on the GCRA which will be discussed later in this chapter. Many traffic policing algorithms are proposed and studied in [8, 60, 28, 92].

#### • Cell Loss Priority Control:

Cell loss priority control is a set of priority policy for accepted connections. The end system may base the policy to mark the traffic from different service categories different Cell Loss Priority (CLP). If the traffic is treated as significant, the network may selectively drop cells with low CLPs to protect the QoS objectives of cells with high CLPs [16, 19, 27, 34, 64].

When a traffic is not conforming to its traffic contract, even its contract specifies a high CLP for it, it can be marked as low priority to protect other conforming traffic from performance degradation due to the misbehavior of some connection.

### • Traffic Shaping:

Traffic shaping mechanisms are used to modify the traffic characteristics in a desired manner [34]. They will be discussed in the later sections.

## • Network Resource Management (NRM)

The service classification mode makes the logical separation of connections according to service characteristics possible, while the Virtual Paths makes the cell scheduling and resource provisioning to be able to provide appropriate

isolation and access to resources. VPCs play a key role in network resource management [34].

VP bandwidth control reduces the required VP bandwidth due to the statistical multiplexing characteristics, and provides fine bandwidth assignment granularity so that the bandwidth of a VP can be precisely tailored to meet the demand [90]. The details of the resource management can be found in [17, 52, 56, 77, 80, 85, 86].

#### • Frame Discard (Memory Management):

In ATM networks, if a cell is discarded, it may lead to upper layer to discard the whole frame or packet. It is more effective to discard at the frame level rather than at the cell level. Frame discard may help avoid congestion collapse and can increase goodput [34].

Partial Packet Discard (PPD) and Early Packet Discard (EPD) are two widely used frame discard schemes.

- Partial Packet Discard (PPD): If a cell from a packet is dropped from a switch buffer, the subsequent cells in that packet are also discarded [81].

- Early Packet Discard (EPD): When a switch buffer reaches a threshold level, but before it is actually required to discard any cells due to buffer overflow, and entire packet is dropped. Then, when the switch senses that congestion is beginning and that cell discard may soon be necessary, it begins to drop some packets with low priority so that it can guarantee the goodput of packets with higher priority to some extent [81].

Many modified versions of these schemes are proposed and studied in [11, 22, 24, 33, 36, 51, 62].

#### • Feedback Controls:

Feedback control is defined as the set of actions taken by both the network and users to regulate the traffic submitted to the connections according to the feedback of the state of network elements. Details of feedback control can be found in [34, 46, 54, 55, 68].

#### 2.2 Traffic Parameters and QoS Parameters

Traffic parameters describe the characteristics of a connection. They can be grouped into the source traffic descriptor and the connection traffic descriptor. The source traffic descriptor describes the intrinsic characteristics of a source. The connection traffic descriptor describes the traffic characteristics at standardized network interfaces [10, 34, 44].

### • Source Traffic Descriptor

The source traffic descriptor is a set of parameters which captures the intrinsic characteristics of a source. It is used to request a connection establishment by the source. The main parameters are Peak Cell Rate (PCR), Sustainable Cell Rate (SCR), Maximum Burst Size (MBS), and Minimum Cell Rate (MCR). Types of source traffic descriptors are dependent on the ATM service categories, which are listed in Fig. 2.2. For the VBR services, PCR, SCR and MBS are all defined, but for CBR, only the PCR is defined. These parameters are explained as follows.

1. Peak Cell Rate (PCR): The PCR specifies the upper bound on the source rate. Enforcement of this bound by the UPC allows the network operator to allocate sufficient resources to ensure that the network performance objectives (e.g., for Cell Loss Ratio) can be achieved. The inverse of PCR is the peak emission interval of the connection:  $T_p$ , which is enforced by UPC in the real operation [34, 44].

- 2. Sustainable Cell Rate (SCR): The SCR indicates the upper bound on the conforming average rate of an ATM connection, over time scales which are long relative to those for which the PCR is defined. Enforcement of this bound by the UPC could allow the network to allocate sufficient resources, less than those based on the PCR, and still ensure that the performance objectives can be achieved. Similarly, the inverse of SCR  $T_s$  is enforced by UPC in the real operation [34, 44].

- 3. Maximum Burst Size (MBS): The MBS is the maximum number of cells transmitted in PCR. MBS together with PCR and SCR may determine the Burst Tolerance (BT).

- 4. Minimum Cell Rate (MCR): The MCR is the rate at which the source is always allowed to send. This is the minimum allocated bandwidth of a connection.

### • Connection Traffic Descriptor

The connection traffic descriptor specifies the traffic characteristics of an ATM connection. The connection traffic descriptor includes the source traffic descriptor, the Cell Delay Variation Tolerance (CDVT), Burst Tolerance (BT), and the conformance definition that is used to specify the conforming cells of the connection.

1. Cell Delay Variation Tolerance (CDVT): ATM layer functions (e.g., cell multiplexing), OAM cells, and other physical layer overhead may alter the traffic characteristics of connections by introducing Cell Delay Variation. Consequently, the peak emission interval T<sub>p</sub> may be affected, which may lead to cell clumping phenomenon. The upper bound on the "clumping" measure is the CDVT. CDVT is defined in relation to the PCR according to the GCRA denoted by GCRA(T<sub>p</sub>, CDVT).

- 2. Burst Tolerance (BT): BT also specifies the upper bound of cell clumping phenomenon with respect to the sustainable emission interval  $T_s$ . Consequently, BT is defined in relation to the SCR according to GCRA( $T_s$ , BT).

- 3. Conformance Definition: The conformance of cells of a connection is defined in relation to the conformance algorithm and corresponding parameters specified in the connection traffic descriptor. In traffic contract, a conformance definition based on the conformance algorithm GCRA is defined. We will explain the details of the GCRA later.

#### • QoS Parameters

In this subsection, the negotiable QoS parameters are described. They are Maximum Cell Transfer Delay (MaxCTD), Peak-to-Peak Cell Delay Variation (p-to-p CDV), and Cell Loss Ratio (CLR).

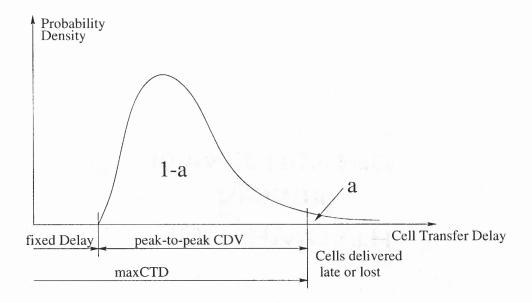

1. MaxCTD: The measured Cell Transfer Delay (CTD) is defined as the elapsed time between a cell exit event at the source point and the corresponding cell entry event at the destination point for a particular connection. It is the sum of the total inter-node transmission delay and the total node processing delay between these two points. Fig. 2.1 shows the probability density function of the CTD, and relates it to maxCTD and p-to-p CDV parameters.

The maxCTD specified for a connection is the  $(1 - \alpha)$  quantile of CTD.

2. Peak-to-Peak CDV: The peak-to-peak CDV is the difference between the maxCTD and the fixed CTD as shown in Fig. 2.1. The fixed CTD is experienced by any delivered cell on a connection during the entire connection holding time.

Two methods are defined to measure the CDV:

Figure 2.1 Cell Transfer Delay Probability Density Model [34]

- One-point CDV: The one-point CDV for k  $(y_k)$  at a measurement point is defined as the difference between the cell's reference time  $(c_k)$ and actual arrival time  $(a_k)$ at the same measurement point:

$$y_k = c_k - a_k \tag{2.1}$$

. The reference time is defined as:

$$c_0 = a_0 \tag{2.2}$$

$$c_k + 1 = \begin{cases} a_k + T & \text{if } a_k > c_k \\ c_k + T & \text{otherwise} \end{cases}$$

(2.3)

Positive one-point CDV means cell clumping phenomenon observed; and the negative one corresponds to gaps in the cell stream. The reference arrival time defined above eliminates the effect of gaps and provides a measurement of cell clumping.

Two-point CDV: The two-point CDV is the variability in the pattern

of cell arrival events observed at the output of a measurement point

with reference to the pattern of the corresponding events observed at

the input to another measurement point. The two-point CDV for cell  $k(v_k)$  between two measurement points is the difference between the absolute CTD of cell  $k(x_k)$  between these two points and a defined reference CTD  $(d_{1,2})$  between the same points:  $v_k = x_k - d_{1,2}$ . The absolute CTD  $(x_k)$  of cell k between two measurement points is the same as CTD. The reference CTD  $(d_{1,2})$  between these two points is the absolute CTD experienced by a reference cell between the two measurement points.

3. Cell Loss Ratio: The Cell Loss Ratio is defined for a connection as:

$$CLR = \frac{Lost \ Cells}{Total \ Transmitted \ Cells}$$

(2.4)

The Cell Loss Ratio parameter is the value of CLR that the network agrees to offer as an objective over the lifetime of the connection.

#### 2.3 ATM Service Classes

ATM Forum's Traffic Management Version 4.0 specifies four main service classes based on the traffic characteristics and QoS requirements. They are Constant Bit Rate (CBR) service, Variable Bit Rate (VBR) service which also includes Real-Time (RT) and Non-Real-Time (NRT) traffic, Unspecified Bit Rate (UBR) service, and Available Bit Rate (ABR) service [34].

Fig. 2.2 shows the list of ATM traffic parameters for each service category.

CBR is a service category for connections that request a static amount of bandwidth that is continuously available during the connection lifetime [34]. The cell intervals in the CBR are almost constant. CBR offers consistent delay predictability of circuit-switched services or leased line services with guaranteed bandwidth allocation. CBR traffic (e.g., voice traffic supported by the conventional telephone network) requires the Peak Cell Rate bandwidth allocation to an ATM

| A 44-71                   | ATM Layer Service Category |                                      |                                      |                   |                    |

|---------------------------|----------------------------|--------------------------------------|--------------------------------------|-------------------|--------------------|

| Attribute                 | CBR                        | rt-VBR                               | nrt-VBR                              | UBR               | ABR                |

| Traffic<br>Parameter      | PCR<br>CDVT                | PCR, CDVT<br>SCR, BT<br>MBS          | PCR, CDVT<br>SCR, BT<br>MBS          | PCR<br>CDVT       | PCR<br>MCR<br>CDVT |

| QoS<br>Parameter          | p-p CDV<br>maxCTD<br>CLR   | p-p CDV<br>maxCTD<br>CLR             | CLR                                  |                   | CLR                |

| Conformance<br>Definition | GCRA(1/PCR, CDVT)          | GCRA(1/PCR, CDVT)<br>GCRA(1/SCR, BT) | GCRA(1/PCR, CDVT)<br>GCRA(1/SCR, BT) | GCRA(1/PCR, CDVT) | Dynamic_<br>GCRA   |

Figure 2.2 ATM Service Category Attributes [34, 44]

connection [90]. CBR service is intended to support real-time applications which are sensitive to the delay and delay variation [47, 48]. In the CBR capability, the source may emit idle cells at, or below the PCR. It also may delete those cells which are delayed beyond the specified maxCTD [34].

VBR is a service category for the variable-bit-rate-type traffic in which the cell interval is not constant. VBR traffic is described by PCR, SCR, MBS. It does not always require the allocation of the PCR bandwidth. The bandwidth allocation of VBR traffic is based on its PCR and SCR, generally between these two value [90]. Therefore, VBR service is good for the bandwidth utilization than CBR service, in which it is always allocated the PCR bandwidth. VBR includes two types of traffic. They are:

• Real-Time VBR(rt-VBR) service: it is intended for real-time applications which require constrained delay and delay variation. Sources are expected to transmit at a rate which varies with time. It means that the source can be described as "bursty" [34]. Its QoS requirements include the maxCTD. It can support statistical multiplexing of real-time sources, and get a relatively high bandwidth utilization. It was studied in [3, 57, 59, 88].

• Non-Real-Time VBR(nrt-VBR) service: it is intended for non-real-time applications which have bursty traffic characteristics. Cells experience a low cell loss ratio when they are conforming to the traffic contract. No delay bounds are specified in this service category [34].

UBR is a service category for non-real-time application. In UBR, the CLR and CTD of each connection are not guaranteed. Although it is also described by PCR, the value of PCR is just informational. The network may not allocate bandwidth based on its PCR. The UBR service is served whenever the network resources are available. It is like a best-effort traffic [1, 49, 50, 65]. The UBR traffic will be dropped first when the network is congested [34, 90].

ABR is a service that its ATM layer transfer characteristics may change based on the available network resources during the connection lifetime. A flow control mechanism must be used to control the source rate in response to changing ATM layer transfer characteristics [21, 50, 93, 100]. In order to get the information of available network resources, several types of feedback are supported in ABR capability. The ABR services doesn't guarantee the delay and delay variation, so it can not be for real-time applications. The ABR is described by PCR and MCR, which designate the maximum required bandwidth and a minimum usable bandwidth, respectively. The available bandwidth of the network may vary, but shall not become less than MCR [34, 90].

## 2.4 Traffic Shaping

In ATM networks, if there is any cell non-conforming to the traffic contract established at the instance of acceptance of the connection, network operators can drop or tag the non-conforming cells. They also can use traffic shaper to shape the stream, that is, delay the non-conforming cell till its conforming Departure Time(DT). There are many algorithms that can be used to calculate the conforming DT,

such as, jumping window [60, 72, 92], moving window [44], exponentially weighted moving average [28, 72] etc.. However, the most widely accepted traffic shaping and scheduling algorithm is Generic Cell Rate Algorithm (GCRA), also known as Leaky Bucket Algorithm.

#### 2.4.1 Generic Cell Rate Algorithm

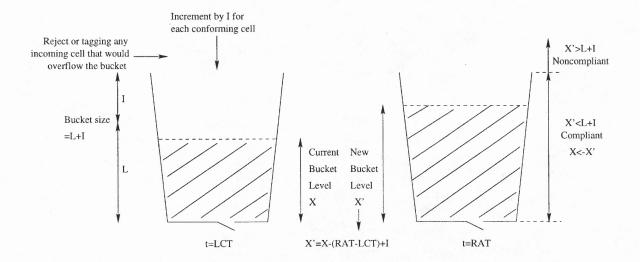

The GCRA is used to define conformance with respect to the traffic contract. It is well known as Leaky Bucket Algorithm [13, 15]. The GCRA is a virtual scheduling algorithm or a continuous-state leaky-bucket algorithm. The GCRA is defined with two parameters: the Increment (I), and the Limit (L), and denoted as GCRA(I, L). The basic process of this algorithm is described by ATM Forum [34] as in Fig. 2.3.

The explanation for the flowchart follows. The virtual scheduling algorithm updates the Theoretical Arrival Time (TAT), which is the nominal arrival time of the cell assuming equally spaced cells when the source is active. If the actual arrival time of a cell is not too early compared to the TAT, in particular the actual arrival time is not earlier than TAT - L, then the cell is conforming. Otherwise, the cell is not conforming. The continuous-state leaky-bucket algorithm can be viewed as finite-capacity bucket whose real-valued content drains out at a continuous rate of 1 unit of content per time unit and whose content is increased by the increment I for each conforming cell. If at a cell arrival the content of the bucket is less than or equal to the limit value, L, then the cell is conforming. Otherwise, the cell is non-conforming. The capacity of the bucket is L + I [34, 44]. The depiction of the GCRA(I,L) is shown in the Fig. 2.4.

According to the individual connection's traffic contract, traffic shaper assigns a conformance time to each incoming cell using the GCRA. When a cell arrives, the GCRA updates the leaky bucket level X' according to the new arrival time RAT(k)

ALGORITHM

TAT(k): Theoretical Arrival Time of cell k RAT(k): Real Arrival Time of cell k

INC: Increment of Leaky Bucket counter

LCT: Last Conforming Time

# LEAKY BUCKET ALGORITHM

X: Value of the Leaky Bucket counter

X': Auxilary variable

LIM: Limit of the Leaky Bucket counter

Figure 2.3 Generic Cell Rate Algorithm [34]

Figure 2.4 Depiction of GCRA(I, L) [81]

and the Last calculated Compliance Time LCT,

$$X' = X - (RAT(k) - LCT). \tag{2.5}$$

If the updated leaky bucket level X' exceeds the limit of bucket (L), then this is a non-conforming cell, and should be delayed at least X' - L. Otherwise, this is a conforming cell, and should be assigned a conformance time equal to RAT(k) [69].

Generally, the dual leaky bucket algorithm is employed to control the bursty data service [43]. There are four traffic parameters associated with dual leaky bucket algorithm, PCR, CDVT, SCR, BT. The dual leaky bucket algorithm is denoted by  $GCRA(T_p, \tau_p, T_s, \tau_s)$ , in which,  $T_p$  is the Peak Emission Interval,  $T_s$  is the Sustained Emission Interval,  $T_p = \frac{1}{PCR}, \tau_p = CDVT, T_s = \frac{1}{SCR}, \tau_s = BT$ . One of the leaky buckets is defined by  $T_p$  and  $\tau_p$ , which is used to eliminate the sustained high rate but small burst size phenomenon, another is defined by  $T_s$  and  $\tau_s$ , which is used to control the sustained medium rate but with very large burst size phenomenon. When there is a cluster of cells coming at a high speed, even the length of the cluster is small, it may make the bucket associated with the PCR full. Then, the cells are delayed so that the rate is reduced, and congestion may be avoided. In another case, although the rate of the cells are moderate, just little higher than the SCR, however, if the length of burst is very large, it also may lead to the leaky bucket associated with the SCR full. Then, this SCR bucket can control such a kind of bursts. Therefore, the dual leaky bucket algorithm can control the bursty data much more efficient than single leaky bucket algorithm. The algorithm of each leaky bucket is as same as Fig. 2.3 describes. The leaky bucket levels are denoted by  $X_s, X_p$ , and updated leaky bucket levels are denoted by  $X'_s, X'_p$  respectively.

For an incoming cell, if it does not conform to anyone of the leaky buckets, it is judged as non-conforming cell, and should be assigned a conforming departure time

$$DT = RT + \max(X_s' - \tau_s, X_n' - \tau_p), \tag{2.6}$$

in which, RT is the Real Time or current time.

# 2.4.2 Event-Driven Traffic Shaping Algorithms

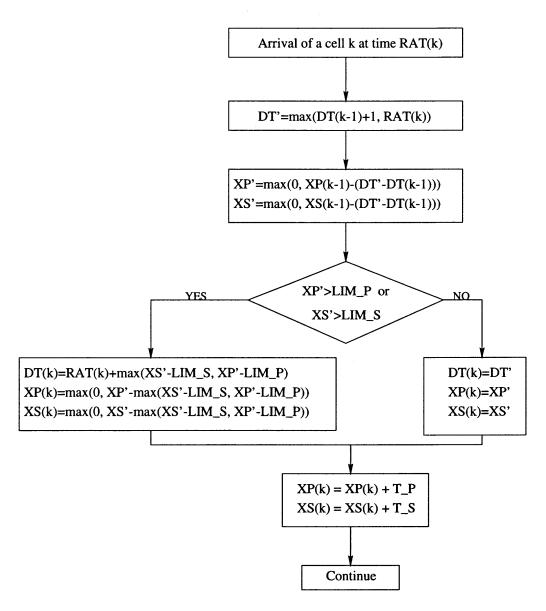

Based on the GCRA, the traffic shaper assigns conforming DT to each incoming cell so that it can schedule their transmission. For the assignment of departure time, two event-driven traffic shaping algorithms are proposed: Arrival Event Driven Traffic Shaping algorithm and Departure Event Driven Traffic Shaping algorithm [15, 18, 44].

2.4.2.1 Arrival Event Driven Traffic Shaping Algorithm (AEDTS) Arrival Event Driven Traffic Shaping Algorithm (AEDTS) is the conventional leaky bucket algorithm which is recommended by ATM Forum [34]. In AEDTS, while a new cell is received and appended to its associated Virtual Connection Queue (VCQ), its departure time will be calculated based on the calculated DT of the previous cell in the same VCQ using GCRA. The leaky bucket level will be updated at the same time [18, 44]. The algorithm is shown in Fig. 2.5.

An example of AEDTS is shown in Fig. 2.6.

In this example, there is only one connection. This connection's increment I=4, and the limit L=2, that is T=4, and  $\tau=2$ , the capacity of the bucket is  $T+\tau=4+2=6$ . The output of the traffic shaper is a strict conforming traffic flow. No departure cell makes the leaky bucket overflow.

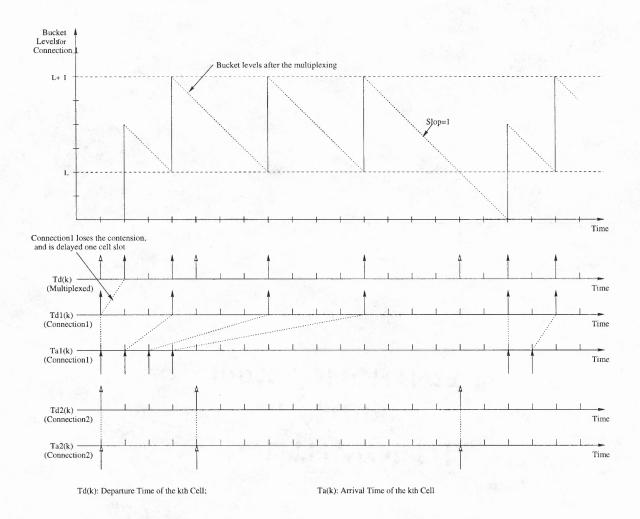

However, for AEDTS, although the output of each connection complies with its own leaky bucket parameters, as multiplexed on the outlink, each shaped cell may violate the shaping parameter because of the contention among eligible cells for transmission [15]. If the previous cell of one VCQ is delayed due to loss of contention, the successive cell of the same VCQ may be assigned an improper DT based on the calculated DT of the previous cell which is earlier than its real departure time. Such

RAT: Real Arrival Time;

DT: Departure Time;

DT', XP', XS': Auxiliary Variable

XP: Level of the Leaky Bucket associated with Peak\_cell\_rate;

LIM\_P: Limit of the Leaky Bucket associated with Peak\_cell\_rate;

XS: Level ofthe Leaky Bucket associated with Sustainable\_cell\_rate;

LIM\_S: Limit of the Leaky Bucket associated with Sustainable\_cell\_rate;

T\_S: Increasement interval of the Leaky Bucket associated with PCR

T\_P: Increasement interval of the Leaky Bucket associated with SCR;

Figure 2.5 Arrival Event Driven Traffic Shaping Algorithm

Figure 2.6 An Example of DT Calculation Diagram for AEDTS (L=2, I=4, GCRA(4, 2))

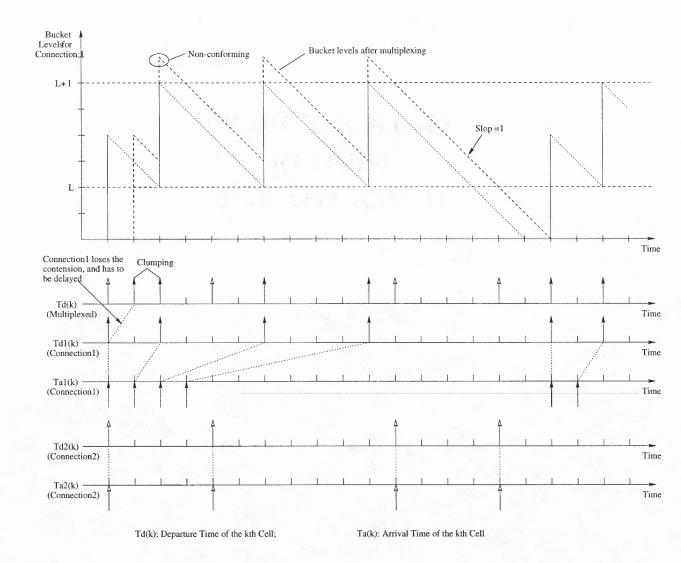

Figure 2.7 Clumping Phenomenon in AEDTS (both connections with L=2, I=4)

improper assignment of DT may clump the successive cell sequence so that it leads to a larger Cell Delay Variation which may violate the traffic contract CDVT and BT. This problem is shown in Fig. 2.7.

In this scenario, after the multiplexing, due to the first cell of connection 1 loses its contention, and has to be delayed one cell slot, the first two cells of connection 1 are clumped together, and violate the traffic contract, overflow the bucket. It shows that the AEDTS may not guarantee the multiplexed connections strict compliant to their individual traffic contract any more.

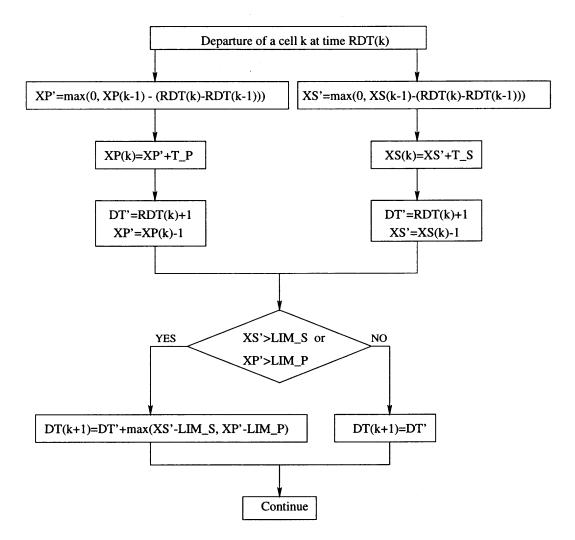

# 2.4.2.2 Departure Event Driven Traffic Shaping Algorithm (DEDTS)

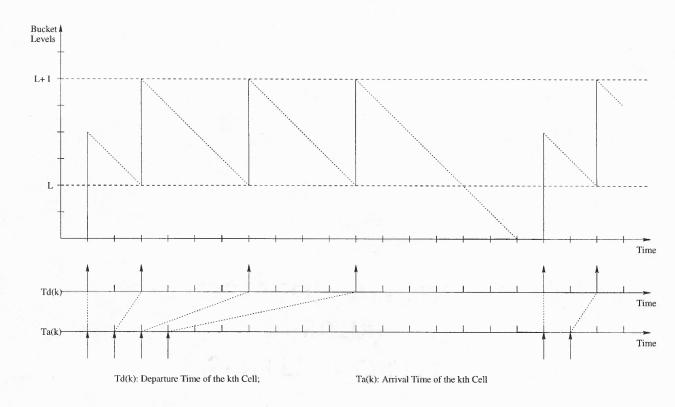

In order to strictly limit the CDVT and BT at the output of the shaping multiplexer [15, 44], Departure Event Driven Traffic Shaping Algorithm (DEDTS) is proposed. Compared to the traditional GCRA which is AEDTS, in DEDTS, bucket level update and DT calculation are performed only when the previous cell of the same connection departs from the multiplexer. The algorithm is shown in Fig. 2.8. An example of DT calculation of DEDTS is shown in Fig. 2.9.

In this example, there is only one connection. It is same as in AEDTS in this scenario. However, when multiple connections are multiplexed together, the DEDTS resolves the clumping problem which is shown in Fig. 2.10.

Because the DT is calculated based on the real DT of the previous cell of the same connection, DEDTS can guarantee strict conforming to CDVT value of each connection. Meanwhile, in each time slot, only one cell is transmitted, so only one new conformance time DT is calculated, which also eliminates the bottleneck due to multiple DT calculation for more than one cell arriving at the same cell slot in AEDTS.

# 2.5 QoS in Internet

With the Internet evolves from a best effort network to a network supporting QoS, the IETF has proposed many service models and mechanisms to meet the demand for QoS. Integrated Services (IntServ) framework and Differentiated Services (DiffServ) framework are two of the most important proposals.

# 2.5.1 Integrated Services and RSVP

RSVP is a signaling protocol that can be used by hosts to request resource reservations through a network, and set up paths [4, 91, 101]. The IntServ model is a framework for providing end-to-end services in the context of RSVP signaling. It is

RDT: Real Departure Time;

DT: Assigned Departure Time;

T\_P, T\_S: Increasement of Leaky Buckets;

DT', XP', XS': Auxiliary Variable

XP: Level of the Leaky Bucket associated with PCR;

LIM\_P: Limit of the Leaky Bucket associated with PCR;

XS: Level of the Leaky Bucket associated with SCR;

LIM\_S: Limit of the Leaky Bucket associated with SCR;

Figure 2.8 Departure Event Driven Traffic Shaping Algorithm

Figure 2.9 An Example of DT Calculation Diagram of DEDTS (L=2, I=4)

Figure 2.10 An Example of DT Calculation of DEDTS in Multiplexing Scenario (both connections with L=2, I=4)

characterized by resource reservation. IntServ assumes that network devices support traffic handling mechanisms, which guarantee service to each traffic flow in strict isolation from other traffic flows. In the integrated services model [9], there are three service classes. They are:

- Guaranteed Service: it is for applications requiring fixed delay bound [76, 91];

- Controlled-load Service: it is for applications requiring reliable and enhanced best-effort service [89, 91];

- Best-effort Service: it is for the traditional Internet applications.

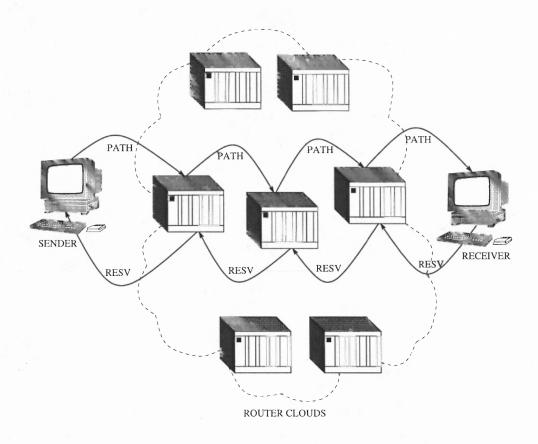

The philosophy of this model is that "There is an inescapable requirement for routers to be able to reserve resources in order to provide special QoS for specific user packet streams, or flows. This in turn requires flow-specific state in the routers" [9, 91]. RSVP was invented to reserve resources for applications. The RSVP signaling process is illustrated in Fig. 2.11.

The whole process is described as the following:

- 1. the sender generates RSVP message known as the PATH message. The PATH message carries the information for the traffic description. It includes the identity of the sender, the sending application, the traffic profile, and the classification criteria by which the traffic can be recognized [4].

- 2. The sender sends this PATH message to the receiver specifying the characteristics of the traffic. Every intermediate network device, such as a router, along the path installs the PATH state, and forwards the PATH message to the next hop determined by the routing protocol.

- 3. When the receiver gets this PATH message, it responds with a RESV message to request resources for the flow. Every intermediate router along the path can

Figure 2.11 RSVP Signaling Process

apply admission control to determine whether the request of the RESV message is accepted or not. If the request is accepted, link bandwidth and buffer space are allocated for the flow, and related flow state information will be installed in the network device. When a device rejects a request, error messages are sent along the data path, notifying other RSVP-aware devices of the admission control failure [4, 91].

Recently, the RSVP has been modified and extended in several ways to reserve resources for aggregation of flows, to set up explicit routes (ERs) with QoS requirements, and to do some other signaling tasks [32, 38, 63].

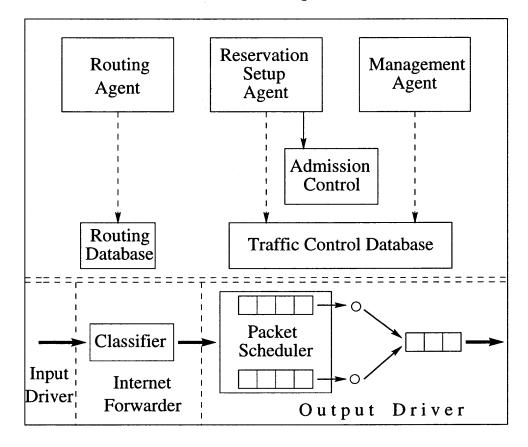

IETF proposed a reference implementation framework to realize the IntServ/RSVP model. This framework consists of four components: the packet scheduler, the

admission control routine, the classifier, and the reservation setup protocol [9]. The implementation reference model is shown in Fig. 2.12.

Figure 2.12 The Implementation Reference Model of IntServ/RSVP [9]

The packet scheduler manages the forwarding of different packet streams using a set of queues and queue management policy, and runs some scheduling algorithm. The classifier classifies or maps each incoming packet into different classes, and all packets in the same class get the same treatment from the packet scheduler. The classifying or mapping may be based upon the contents of the existing packet header(s) and/or some additional classification number added to each packet. The admission control determines whether there are enough resources for the new flow without impacting the existing connections in the network. Based on this decision, the network device chooses to accept or reject the new flow. The fourth component is the RSVP. It sets up a path for the new flow, as well as creates and maintains

flow-specific state in the endpoint hosts and in network devices along the path of the flow [9].

The IntServ network model makes a fundamental change to the concept of the Internet architecture. It requires that all flow-related information should be in the end systems. This scheme can guarantee the QoS for each flow [25, 91]. However, it also leads to some problems:

- The amount of state information increases proportionally to the number of flows. In the current Internet, there can be thousands, ten thousands, even hundred thousands of flows simultaneously. This architecture is definitely unscalable [91].

- The implementation complexity of the network device is very high. Each device must have the packet scheduler, classifier, admission control, and RSVP. It also leads to the scalability problem [4, 91].

#### 2.5.2 Differentiated Services

2.5.2.1 Motivation for DiffServ Because of the difficulty in implementing and deploying the IntServ/RSVP architecture, differentiated services (DiffServ) architecture is proposed by the IETF to resolve the scalability problem in the IntServ/RSVP model.

DiffServ is a traffic handling mechanism [4]. It defines a field in packets' IP headers, called the diffserv codepoint (DSCP). It is six-bit wide in IPv6, and three-bit wide in IPv4 which is also called type of service (TOS) in IPv4 header. In addition, it defines a base set of packet forwarding treatments, called the per-hop behavior, or PHBs [66]. By marking the DSCP of packets differently, the network devices can classify packets and apply specific queueing behavior based on the results of the classification. Traffic from multiple flows having similar QoS requirements is marked with the same DSCP, thus aggregating the flows to a common queue or scheduling

behavior. The distinguishing feature of DiffServ is its scalability [4]. It is because that the aggregate traffic handling mechanisms require significantly less state information and processing capability in network nodes than their per-flow counterparts.

2.5.2.2 Configuration of a DiffServ Network In the DiffServ model proposed by the IETF, the DiffServ network is configured to provide many services to its customers. These services are specified by the service level agreement (SLA). The SLA is defined at the instance that the customers submit traffic to the DiffServ network's ingress router. An SLA may specify the traffic profile, service class that the submitted traffic belongs to, QoS requirements, etc. The administrator of the DiffServ network will use whatever provisioning and configuration tools are available to meet the SLA for those conforming traffic [4]. An SLA can be static or dynamic. Static SLAs are negotiated on a regular time interval, which is a generally relative long term. Customers with dynamic SLAs must use a signaling protocol (e.g. RSVP) to request services on demand [91].

In a DiffServ network, routers at the ingress point would be configured to classify traffic based on the IP addresses, ports in packet headers and its SLA. The routers would be configured to mark the DS field of packets with one of DSCPs based on the classification results. The internal routers of the DiffServ networks would be configured to classify packets based on DSCP and direct them to a corresponding queue. Queues would be configure to satisfy certain service characteristics specified by the SLAs [4].

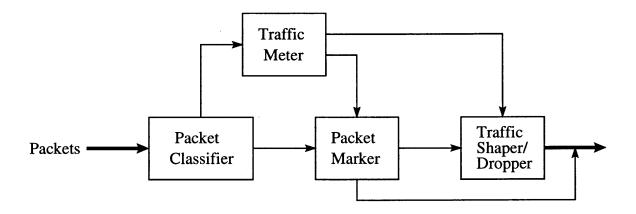

In order to provide the QoS guarantee to the conforming traffic, the traffic conditioning must be executed. The traffic conditioning is a set of control functions that can be applied to a behavior aggregate, application flow, or other subset of traffic. They may include metering, policing, shaping, and packet marking as shown in Fig. 6.1 [5, 66]. The classification, policing, scheduling, and shaping rules used

at the ingress routers are derived from the SLAs [91]. The traffic conditioning is typically deployed in the ingress routers. Generally, the packets are classified, policed, and possibly shaped and scheduled in DiffServ boundary nodes.

# 2.5.2.3 Service Classes in DiffServ Networks In a DiffServ network, many services can be provided. They are include:

- Premium Service: It provides low-delay and low-jitter service for customers that generate fixed peak bit rate traffic. Premium service is suitable for those real-time applications, such as Internet telephony, videoconferencing, etc. The SLA for the premium services should specify a desired peak bit-rate for a specific flow or an aggregation of flows. The Internet service provider (ISP) guarantees that the contracted bandwidth will be available when the conforming traffic is sent.

- Assured Service: It is for applications requiring better reliability than besteffort service even in times of network congestion. The SLAs of assured services will specify the amount of bandwidth allocated for the customers, and customers themselves determine how they share that amount of bandwidth.

- Olympic Service: It provides three tiers of services: gold, silver, and bronze, with decreasing quality [40, 67, 91].

# 2.5.2.4 Characteristics of the DiffServ Model DiffServ model has two most distinguishing features different from the IntServ model. They are:

• One is that there are only a small limited number of service classes indicated by the DS field, and the amount of state information is proportional to the number of classes rather than the number flows, so the management complexity for the state information and the device processing power are reduced greatly.

• Another one is that sophisticated classification, marking, policing, and shaping operation are only needed at the boundary of the networks. Those core network devices only have to deal with behavior aggregate (BA) classification. Consequently, it is easier and more cost efficient to implement and deploy DiffServ networks, and resolve the scalability problem in the IntServ model [4, 91].

2.5.2.5 Access Control at the Edge of the DiffServ Networks In DiffServ networks, all traffic control mechanisms are class-based. However, access networks, such as local area networks, may deal with traffic as individual flows, so the convergence at the edge of the DiffServ network is an important issue. In this dissertation, the traffic shaping mechanism is extended to the DiffServ network environment to implement the fair convergence at the edge of the DiffServ networks, and an implementation scheme for the access control is proposed.

#### CHAPTER 3

# THE HIERARCHICAL TIMING QUEUES TRAFFIC SHAPER

# 3.1 Motivation for the Hierarchical Timing Queues Traffic Shaper

There are many architectures proposed to implement shaping function. These architectures are classified as either Direct Exact Sorting [15, 18, 44], or Rate Based Grouping architectures in this thesis [73]. In this section, the existing traffic shaper architectures are described, and their problems are pointed out.

# 3.1.1 Existing Traffic Shaper Architectures

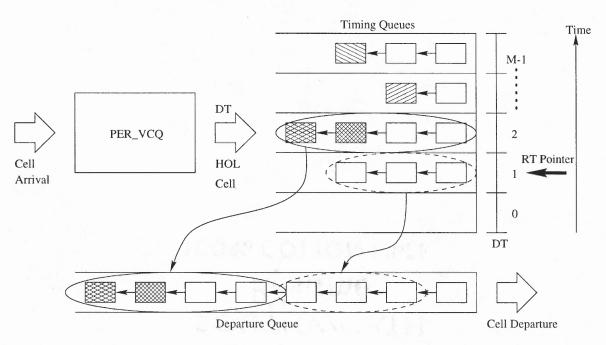

3.1.1.1 Direct Exact Sorting Architecture Direct Exact Sorting architecture is shown in Fig. 3.1. This architecture employs Per-Virtual-Connection-Queue

Figure 3.1 Direct Exact Sorting Architecture

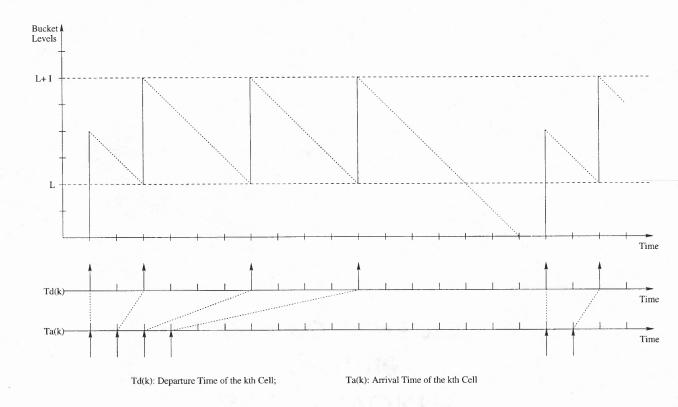

(Per-VCQ) structure at the input port. Following the Per-VCQ, there is a sorting unit. It is a set of timing queues which is formed based on the incoming cell's conforming Departure Time(DT). At the output port, a Departure Queue (DQ) is used to store cells with the conformance time due or overdue.

In each cell slot, if the DQ is not empty, its Head of Line (HoL) cell with connection ID i will be served. Then, according to the traffic contract of connection i, a new DT of this connection will be calculated by its associated dual leaky buckets. Based on the new DT, the next HoL cell of connection i will be appended to one of timing queues. Once the real time pointer RT points to a timing queue, all cells in the queue become due. Hence, they are appended to the DQ. In the Direct Exact Sorting architecture, all cells with the same DT are appended to the same timing queue, so the DT of a cell becomes the sequence number indicating which timing queue the cell should be appended to. This is the key point of this architecture.

The timing queue scheme can reduce the implementation complexity of the exact sorting of time stamps. Especially, it avoids comparison and insertion operations which are time-consuming. Due to DEDTS, it only needs to calculate one time stamp value per cell slot. However, for hardware implementation, the number of the timing queues can not be infinite. The timing queue sequence numbers should be reused to represent the time stamps. If the maximum sequence number is M-1, there can only be M timing queues. In order to avoid confusion between RT and RT+M, it should guarantee that the farthest DT of a cell being appended into the timing queues is not larger than RT+(M-1). If the rate of a connection is denoted by  $\rho$ , then, the head of line (HOL) cell of the slowest connection can be assigned a DT at most  $\frac{1}{\rho_{min}}$  into the future. If only one cell from each connection is kept to stay in the sorting unit, only cells which are at most  $\frac{1}{\rho_{min}}$  ahead of the RT should be accommodated in the sorting unit. In order to satisfy the high speed connection performance accuracy,  $1/\rho_{max}$  should be chosen as the timing queue granularity. Therefore, in the design of this system, the number of timing queues M should satisfy the inequality below,

$$M \ge \rho_{max}/\rho_{min}. \tag{3.1}$$

There is a shortcoming in the scalability of this architecture. When a broadband network should accept a great number of connections with very wide range of rates, the value M will be very large. With the range of rates increasing, the value of M will increase linearly, which means that the complexity of the implementation of this architecture is

$$O(\rho_{max}/\rho_{min}).$$

(3.2)

So this architecture is not suitable for accommodating connections with a very wide range of rates.

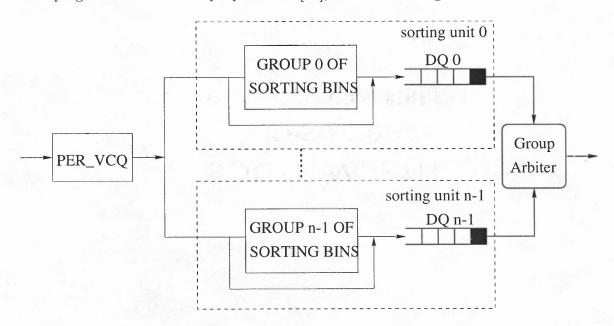

3.1.1.2 Rate-Based Grouping Architecture In order to improve the scalability and reduce the complexity of implementation of the Direct Exact Sorting, Rate-Based Grouping Architecture was proposed in [73], as shown in Fig.3.2.