New Jersey Institute of Technology Digital Commons @ NJIT

Theses

**Electronic Theses and Dissertations**

Fall 1-31-2010

# A FPGA/DSP design for real-time fracture detection using low transient pulse

Akash Mathur New Jersey Institute of Technology

Follow this and additional works at: https://digitalcommons.njit.edu/theses

Part of the Electrical and Electronics Commons

#### **Recommended Citation**

Mathur, Akash, "A FPGA/DSP design for real-time fracture detection using low transient pulse" (2010). *Theses.* 49. https://digitalcommons.njit.edu/theses/49

This Thesis is brought to you for free and open access by the Electronic Theses and Dissertations at Digital Commons @ NJIT. It has been accepted for inclusion in Theses by an authorized administrator of Digital Commons @ NJIT. For more information, please contact digitalcommons@njit.edu.

# **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

#### ABSTRACT

#### A FPGA/DSP DESIGN FOR REAL-TIME FRACTURE DETECTION USING LOW TRANSIENT PULSE by Akash Mathur

This work presents the hardware and software architecture for the detection of fractures and edges in materials. While the detection method is based on the novel concept of Low Transient Pulse (LTP), the overall system implementation is based on two digital microelectronics technologies widely used for signal processing: Digital Signal Processor (DSP) and Field Programmable Gate Array (FPGA). Under the proposed architecture, the DSP carries out the analysis of the received baseband signal at a lower rate and hence can be used for large number of signal channels. The FPGA's master clock runs at a higher frequency (62.5MHz) for the generation of LTP signal and to demodulate the passband ultrasonic signals sampled at 1MHz which interrupts the DSP at every 1µs. This research elaborates on designing a Quadrature Amplitude Modulator demodulator (QAM) on the FPGA for the received signal from the ultrasound and edge detection on the DSP processor to detect the presence of edges/fractures on a test Sawbone plate. In this work, the LTP technology is applied to determine the location of the Sawbone plate edges based on the reflected signals to the receivers. This signal is then passed through a QAM to get the maxima (peaks) at the received signal to study the parameters in the DSP. This work successfully demonstrates the feasibility of modular programming approach across the two platforms. The dual time scale platform readily accommodates higher temporal resolution needed for the generation of Low Transient Pulses and the processing of real time baseband signals on the DSP for various test conditions.

### A FPGA/DSP DESIGN FOR REAL-TIME FRACTURE DETECTION USING LOW TRANSIENT PULSE

by Akash Mathur

A Thesis

Submitted to the Faculty of New Jersey Institute of Technology in Partial Fulfillment of the Requirements for the Degree of Master of Science in Electrical Engineering

**Department of Electrical and Computer Engineering**

January 2010

$\langle$

# APPROVAL PAGE A FPGA/DSP DESIGN FOR REAL-TIME FRACTURE DETECTION USING LOW TRANSIENT PULSE

#### **Akash Mathur**

1/11/2010 Dr. Timothy Chang, Thesis Advisor Interim Chairperson, Professor of Electrical and Computer Engineering, NJIT

Dr. Durgamadhab Misra, Committee Member Date Graduate Advisor, Professor of Electrical and Computer Engineering, NJIT

$\frac{1}{100}$

Dr. Edwin Hou, Committee Member Associate Chair for Undergraduate Studies, Associate Professor of Electrical and Computer Engineering, NJIT

#### **BIOGRAPHICAL SKETCH**

Author: Akash Mathur

**Degree:** Master of Science

Date: January 2010

#### Undergraduate and Graduate Education:

- Master of Science in Electrical Engineering, New Jersey Institute of Technology, Newark, NJ, 2010

- Bachelor of Technology in Electronics and Communications Engineering, Kurukshetra University, Haryana, India, 2006

"100 yrs from now no one will ever remember what clothes you wore, which car you drove, which perfume you put, which country you lived..... But what will be remembered from this thesis is that blessed are

those whose parents are like mine and the love I have for them is not something so easy to define.....

I dedicate my thesis to my parents

-- Akash

#### ACKNOWLEDGMENT

I am heartily thankful to my thesis advisor, Dr. Timothy Chang, whose encouragement, guidance, lot of novel ideas and support throughout my research and in writing my thesis is unquestionable. His extreme patience, forgiveness, inspiration, enthusiasm, and immense knowledge are the primary reasons for the success of my research.

Alongside my adviser I would like to thank my thesis committee, Dr. Durgamadhab (Durga) Misra and Dr. Edwin Hou, for their support and encouragement. I am really honored and thankful to them for being in the committee for my defense.

I am indebted to many of my colleagues to support me. Dr. Biao Cheng has helped me selflessly throughout the thesis and his contribution for my completion is undeniable. Ashish Ratnakar and Lan Yu have supported and helped me in more than one ways.

Lastly but most importantly, I will like to thank my parents and my sister for supporting me in which ever way they could and because of whom I am able to complete my thesis and hence achieve the degree of Master of Science.

# **TABLE OF CONTENTS**

| С | hapter                             | Page |

|---|------------------------------------|------|

| 1 | INTRODUCTION                       | 1    |

|   | 1.1 Overview                       | 1    |

|   | 1.2 Hardware Architecture          | 4    |

|   | 1.3 DSP Starter Kit                | 5    |

|   | 1.4 Daughter Board                 | 5    |

|   | 1.5 Low Transient Pulse            | _ 7  |

|   | 1.6 Benefits                       | 8    |

|   | 1.6.1 TMS320C6416T                 | 8    |

|   | 1.6.2 SPARTAN IIE (XC2S300E)       | 11   |

|   | 1.7 RTDX (Real Time Data Exchange) | 11   |

| 2 | TMS32C6416: TI's DSP PROCESSOR     | 13   |

|   | 2.1 Digital Signal Processor       | 13   |

|   | 2.2 Memory Map                     | 14   |

|   | 2.3 Interrupts                     | 15   |

|   | 2.4 Timers                         | 17   |

|   | 2.5 Software Programming           | 19   |

|   | 2.5.1 Project File (.pjt)          | 20   |

|   | 2.5.2 Linker File                  | 20   |

|   | 2.5.2.1 Memory                     | 21   |

|   | 2.5.2.2 Section                    | 21   |

..

| TABLE | OF   | CO   | NTE | NTS |

|-------|------|------|-----|-----|

| (0    | Cont | inue | ed) |     |

.

| Chapter                                               | Page |

|-------------------------------------------------------|------|

| 2.5.3 FPGA (.out) File                                | 22   |

| 2.5.4 main.c Program                                  | 22   |

| 2.5.4.1 Initialization                                | 22   |

| 2.5.4.1.1 ADC(THS1206)                                | 22   |

| 2.5.4.1.2 Flag Setup                                  | 24   |

| 2.5.4.1.3 Miscellaneous                               | 25   |

| 2.5.4.2 Loading the FPGA                              | 26   |

| 2.5.4.3 Free Run                                      | 27   |

| 2.5.4.3.1 Moving Average Filter                       | 28   |

| 2.5.4.3.2 Edge Detection                              | 29   |

| 3 SPARTAN 2E:FPGA                                     | 31   |

| 3.1 Hardware                                          | 31   |

| 3.2 System Design                                     | 32   |

| 3.2.1 Programming                                     | 32   |

| 3.2.3 Simulation Analysis                             | 33   |

| 3.3 Programming FPGA                                  | 34   |

| 3.3.1 Quadrature Amplitude Modulator-demodulator(QAM) | 36   |

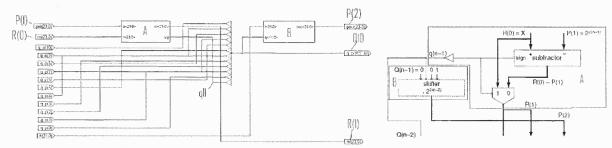

| 3.3.1.1 Since and Cosine Generator                    | 36   |

| 3.3.1.1.1 Simulation Results                          | 37   |

| 3.3.1.1.2 Register Transistor Logic                   | 39   |

. \_

# TABLE OF CONTENTS (Continued)

| Chapter                                                       | Page |

|---------------------------------------------------------------|------|

| 3.3.1.1.3 Synthesized Output                                  | 40   |

| 3.3.1.2 Infinite Impulse Response (IIR) Filter                | 40   |

| 3.3.1.2.1 Simulation Results and Design                       | 41   |

| 3.3.1.2.2 Register Transistor Logic                           | 44   |

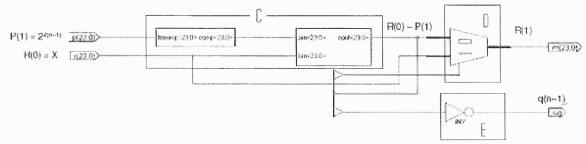

| 3.3.1.3 Square Root                                           | 45   |

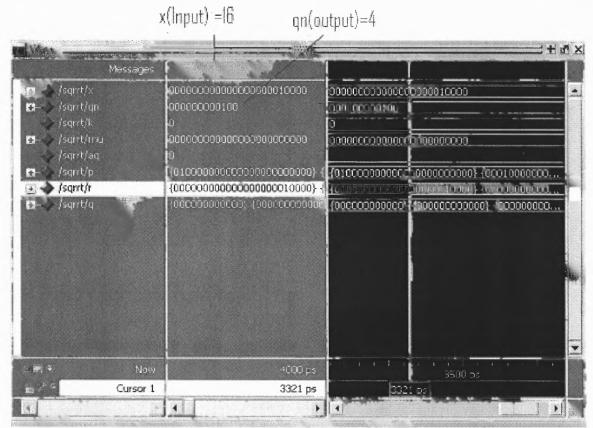

| 3.3.1.3.1 Simulation Results                                  | 47   |

| 3.3.1.3.2 Register Transistor Logic                           | 47   |

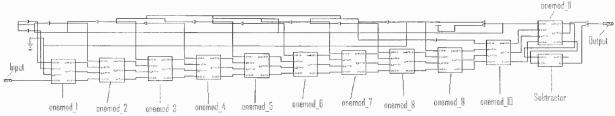

| 3.3.1.4 Full QAM                                              | 49   |

| 3.3.1.5 Frequency Spectrum                                    | 49   |

| 3.3.2 Low Transient Pulse                                     | 51   |

| 3.3.2.1 Register Transistor Logic                             | 51   |

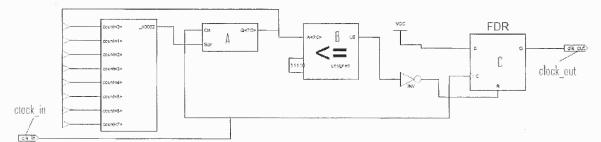

| 3.3.3 Clock Divider                                           | 52   |

| 3.3.3.1 Register Transistor Logic                             | 52   |

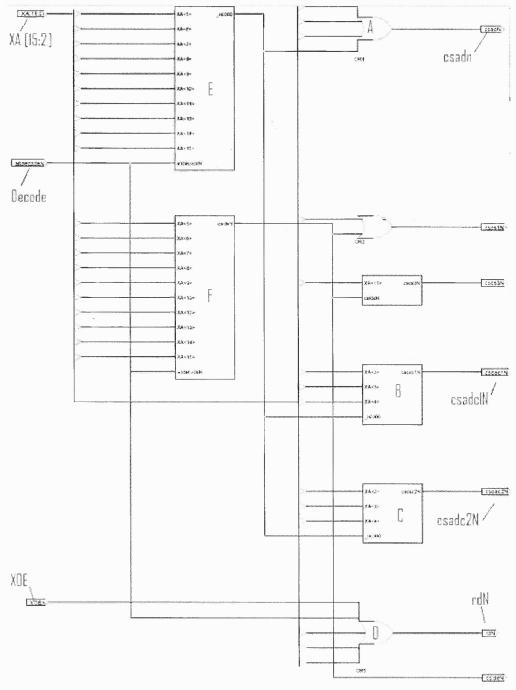

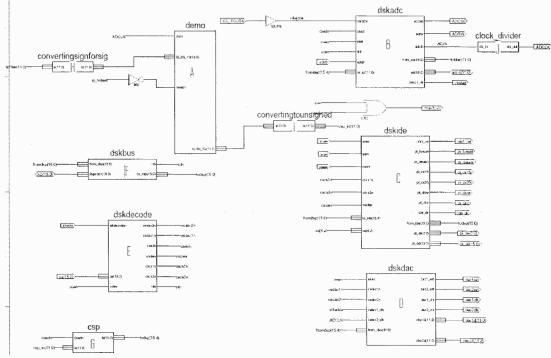

| 3.3.4 Interface (FPGA- DSP)                                   | 53   |

| 3.3.4.1 Register Transistor Logic: Decoder                    | 54   |

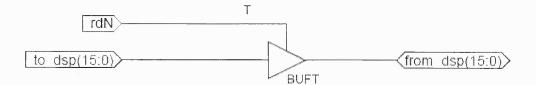

| 3.3.5 ADC Module                                              | 57   |

| 3.3.5.1 Register Transistor Logic                             | 57   |

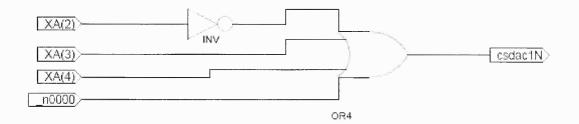

| 3.3.6 UnsignedtoSigned and SignedtoUnsigned Converters Module | 58   |

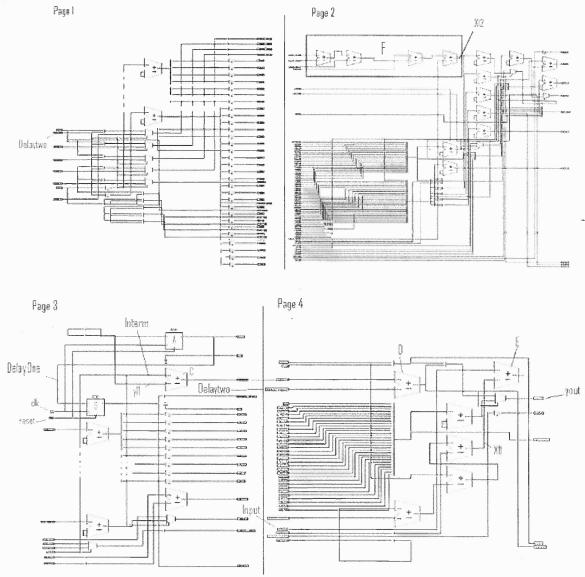

| 3.3.7 Complete FPGA System Design                             | 58   |

| 4 ALGORITHM AND RESULTS                                       | 60   |

# TABLE OF CONTENTS (Continued)

| Chapter                        | Page |

|--------------------------------|------|

| 4.1 Algorithm                  | 60   |

| 4.2 Experimental Verifications | 61   |

| 4.2.1 Symmetric Placement      | 62   |

| 4.2.2 Asymmetric Placement     | 63   |

| 5 CONCLUSION                   | 65   |

| 5.1 Conclusion                 | 65   |

| 5.2 Future Work                | 66   |

| APPENDEX A RESOLUTION          | 67   |

| APPENDEX B DSP MEMORY          | 69   |

| APPENDEX C SAMPLING TIME       | 71   |

| REFERENCES                     | 74   |

.

# LIST OF TABLES

| Table  |                                                                           | Page |

|--------|---------------------------------------------------------------------------|------|

| 1.1    | Comparison of various DSP processors in the market                        | 9    |

| 2.1    | Variables used in the FPGA program                                        | 26   |

| 3.1    | System Information                                                        | 31   |

| 3.2    | Available IOs with various Spartan 2E packages                            | 31   |

| 3.3    | Filter Parameters defined in Matlab and the corresponding poles and zeros | 41   |

| 3.4    | Memory map of the EMIF for the interface between DSP and FPGA             | 54   |

| 4.1(a) | Estimation of longitudinal parameter of the plate, symmetric placement    | 63   |

| 4.1(b) | Passband maxima detection: summary of plate position errors               | 63   |

| 4.1(c) | Envelope maxima detection: summary of plate position errors               | 63   |

| 4.2(a) | Estimation of longitudinal parameter of the plate, asymmetric placement   | 64   |

| 4.2(b) | Passband maxima detection: summary of plate position errors               | 64   |

| 4.2(c) | Envelope maxima detection: summary of plate position errors               | 64   |

..

## LIST OF FIGURES

| Figure |                                                                             | Page |

|--------|-----------------------------------------------------------------------------|------|

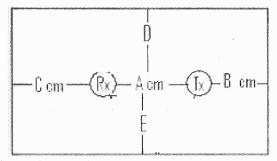

| 1.1    | Experimental ultrasonic crack detection system                              | 3    |

| 1.2    | Block diagram to show the interface between the DSP and FPGA                | 4    |

| 1.3    | Block diagram for the on board components and their interfaces on the DSK   | 5    |

| 1.4    | Low Transient Pulse                                                         | 7    |

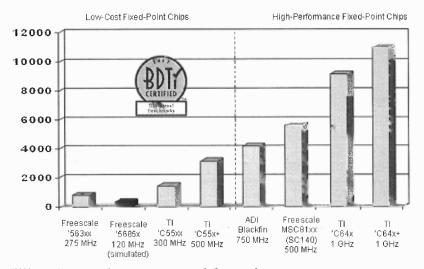

| 1.5    | Millions instruction per second for various processors                      | 10   |

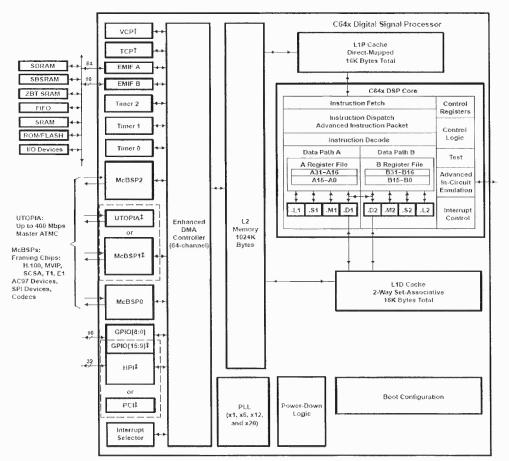

| 2.1    | Architectural overview of TMS320C6416 CPU                                   | 13   |

| 2.2    | Memory map of C6416T DSP Starter Kit (DSK)                                  | 15   |

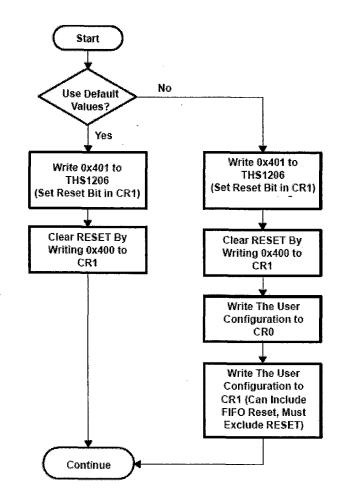

| 2.3    | THS1206 configuration flow                                                  | 23   |

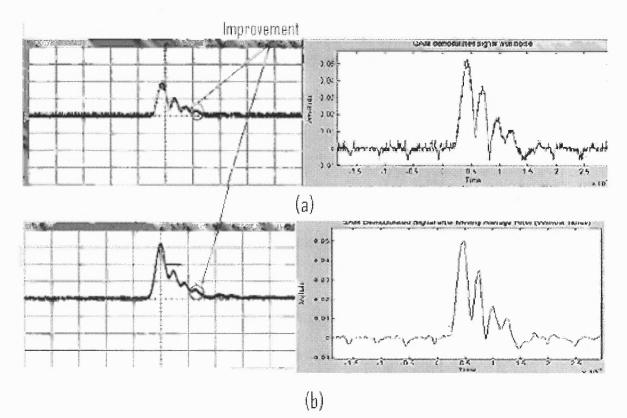

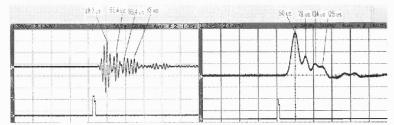

| 2.4(a) | Envelope signal before filtering                                            | 29   |

| 2.4(b) | Envelope signal after filtering                                             | 29   |

| 2.5    | Snapshot of the value displayed in the Watch window of the CCS              | 30   |

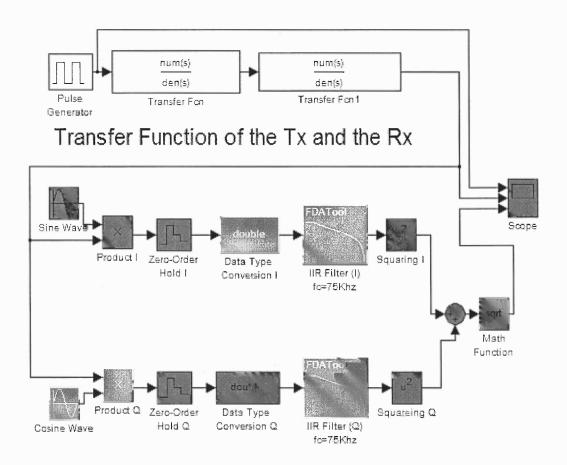

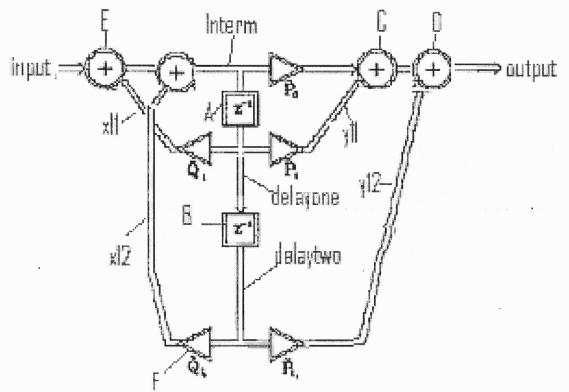

| 3.1(a) | Matlab/Simulink model for the QAM system which is implemented on the FPGA   | 33   |

| 3.1(b) | Matlab/Simulink simulation results for the QAM system                       | 34   |

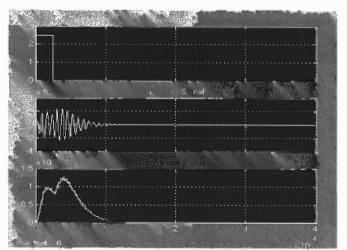

| 3.2    | Design flow of FPGA                                                         | 35   |

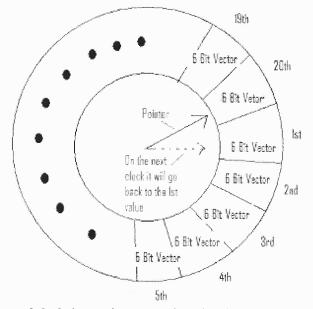

| 3.3    | Schematic displaying the design of the sine and cosine generator            | 36   |

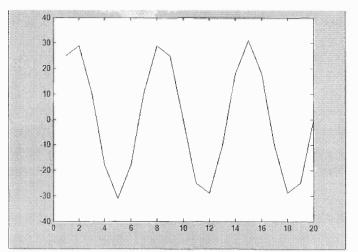

| 3.4    | Matlab simulation result for the generated data for the sine wave generator | 37   |

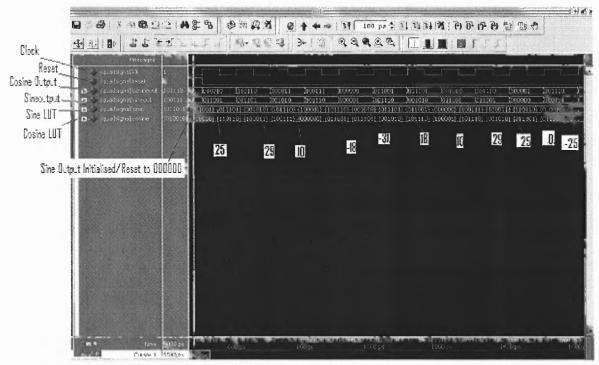

| 3.5(a) | Simulation results for the sine and cosine generator for i= 1 to i=11       | 38   |

| 3.5(b) | Simulation results for the sine and cosine generator for $i=11$ to $i=21$   | 38   |

| 3.6    | RTL logic for the sine and cosine generator                                 | 39   |

# LIST OF FIGURES (Continued)

| Figur  | e                                                                                                            | Page |

|--------|--------------------------------------------------------------------------------------------------------------|------|

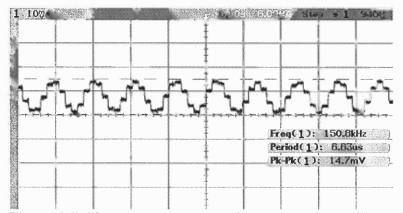

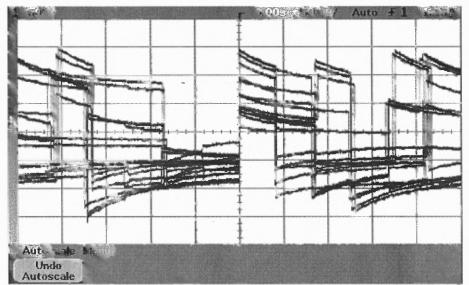

| 3.7    | Sine generator output observed on the oscilloscope                                                           | 40   |

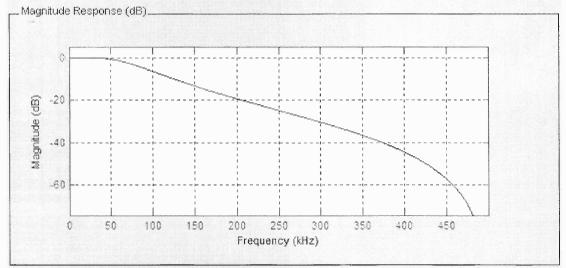

| 3.8    | Magnitude response of the filter with parameters from Table 3.3                                              | 41   |

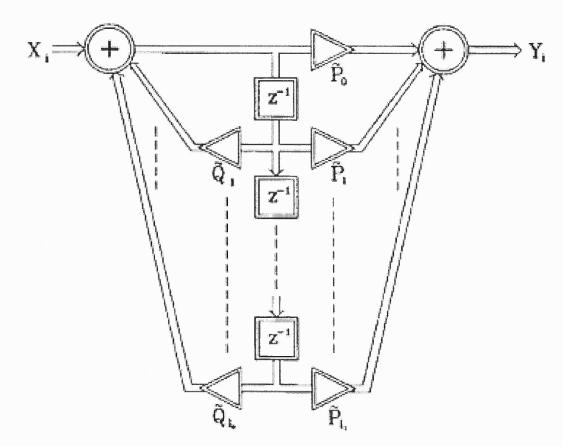

| 3.9a   | Direct- II form for the implementation of an IIR filter                                                      | 42   |

| 3.9b   | Direct-II form re-arranged for its implemented over the FPGA                                                 | 43   |

| 3.10   | RTL for the IIR Filter                                                                                       | 45   |

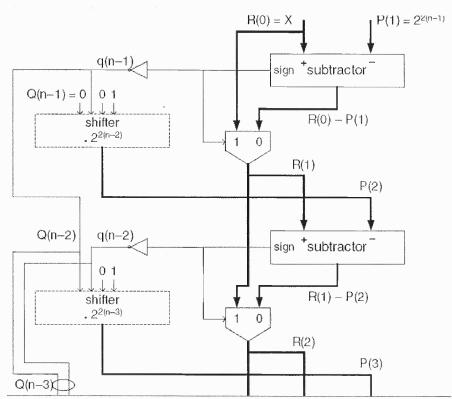

| 3.11   | Restoring 2n-bit square rooter, combinational implementation                                                 | 46   |

| 3.12   | Simulation result for the square rooter                                                                      | 47   |

| 3.13(a | )RTL for the Square Root consisting on onemod and subtractor modules                                         | 48   |

| 3.13(b | )RTL for the sub block onemod consisting modules                                                             | 48   |

| 3.13(c | ) RTL for the sub-sub-block (A) consisting a 2's complement, full adder, multiplexer and an inverter modules | 48   |

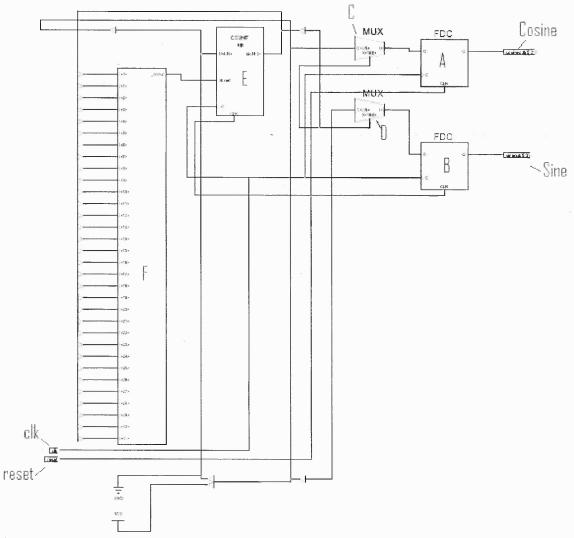

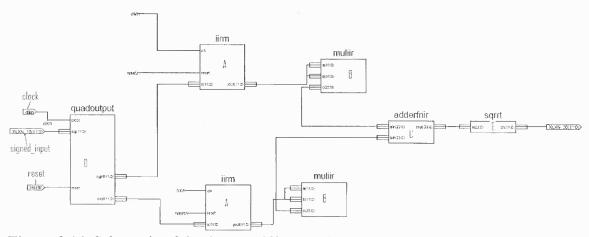

| 3.14   | Schematic of the QAM. Different sub-blocks port mapped to form one whole system                              | 49   |

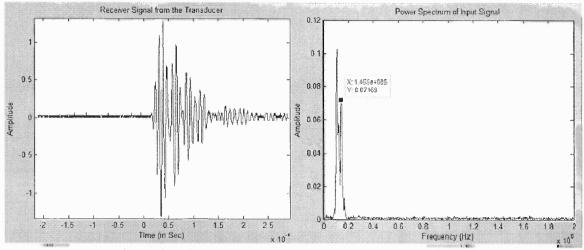

| 3.15   | Received signal and its FFT                                                                                  | 50   |

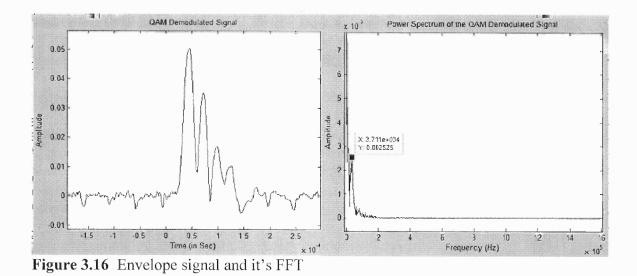

| 3.16   | Envelope signal and its FFT                                                                                  | 51   |

| 3.17   | RTL for the LTP                                                                                              | 52   |

| 3.18   | RTL for the Clock Divider                                                                                    | 53   |

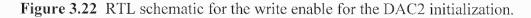

| 3.19   | RTL decoder schematic for the interface between the FPGA and the DSP                                         | 55   |

| 3.20   | RTL schematic for the read enable for the ADC initialization                                                 | 56   |

| 3.21   | RTL logic for the write enable for the DAC1 initialization                                                   | 57   |

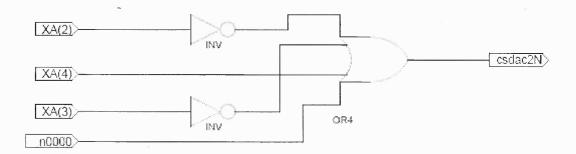

| 3.22   | RTL logic for the write enable for the DAC2 initialization                                                   | 57   |

-

# LIST OF FIGURES (Continued)

.

| Figure |                                                                                                                   | Page |

|--------|-------------------------------------------------------------------------------------------------------------------|------|

| 3.23   | RTL schematic for the retrieval of sampled data from the ADC                                                      | 58   |

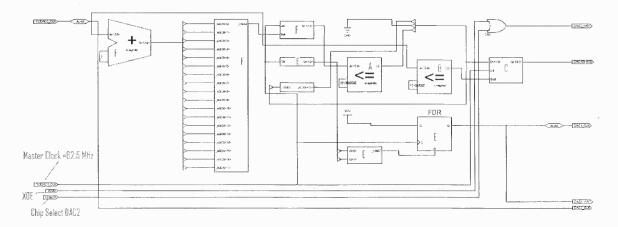

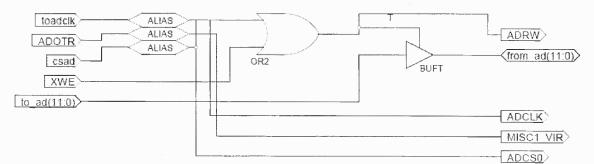

| 3.24   | Top level schematic of the system on the FPGA                                                                     | 59   |

| 4.1    | Sawbone plate with its dimensions with the edges                                                                  | 62   |

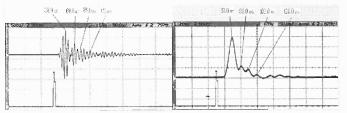

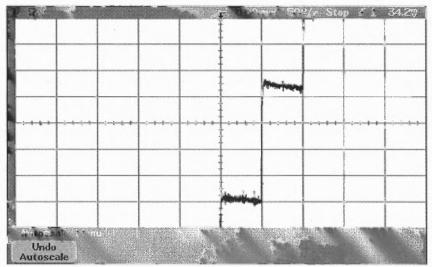

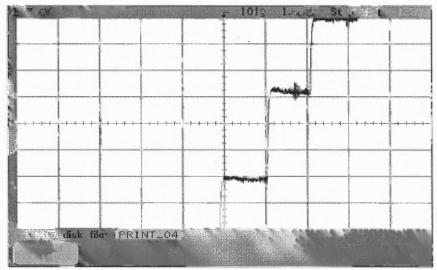

| 4.2    | Received signal and its envelope signal observed on the oscilloscope with symmetric placement of the transducers  | 63   |

| 4.3    | Received signal and its envelope signal observed on the oscilloscope with the asymmetric placement of transducers | 64   |

| C.1    | Output on the oscilloscope showing the step size of 3.10 $\mu$ s                                                  | 71   |

| C.2    | Output on the oscilloscope showing the step size of 2.50 $\mu$ s                                                  | 72   |

| C.3    | Output on the oscilloscope showing the step size of 1.66 $\mu$ s                                                  | 72   |

| C.4    | Output on the oscilloscope showing error for any sampling period above 0.5µs (2MHz)                               | 73   |

,

#### **CHAPTER 1**

#### **INTRODUCTION**

#### 1.1 Overview

Ultrasound has been used widely used in applications for the detection and location of the cracks and fracture on various materials i.e. bone, composite structures, and metals etc.[2-4]. Other detection methods are based on the monitoring of the nonlinear elastic material behavior of damaged material [1], guided waveguides [2], magnetic leakage flux [2] and laser based techniques [3]. This thesis applies the low transient pulse method [4] for the determination of the crack in the Sawbone which is a synthetic composite material designed to emulate the acoustic properties of the cortical bone.

The recent generation of 3-D X-ray bone densitometry and peripheral quantitative CT (pQCT) has made major advances. However, they are expensive and emit ionizing radiation. Therefore it is of significant interest to explore quantitative ultrasound (QUS) because ultrasound is also highly sensitive to elastic properties and defects of bone materials. In addition, ultrasound is safe and easy to deploy so that ultrasonic equipment can be made portable and relatively inexpensive [2]. Ultrasonic methods have also been used for monitoring bone fracture healing and creep in structural materials [5-8]. Although some researchers have employed ultrasonography and power Doppler ultrasonography to assess the appearance and neo-vascularization of the callus tissue during healing, the majority of the studies have utilized quantitative ultrasound techniques [5]. Ultrasonic monitoring of bone healing is discussed in detail in [5]. Many

methods have been employed for the detection of edge cracks like the Frobenius method to enable possible detection of location of the crack based on the measurement of natural frequencies [9], the wavelet theory, eddy current and many more for various surfaces [10-12].

There are various benefits of using ultrasound for Non Destruction Testing (NDT). This work addresses the use of the low transient acoustic pulses to enhance system resolution and to simplify hardware requirements. The Low Transient Pulse (LTP), as opposed to the conventional acoustic pulse, has shorter pulse duration and thus results in less phase interference and higher performance. To produce low transient acoustic pulses, it is often necessary to have a prescribed signal to drive the transmitter [4]. Nondestructive evaluation (NDE) is a term that is often used interchangeably with NDT [13]. However, technically, NDE is used to describe measurements that are more quantitative in nature. For example, an NDE method would not only locate a defect, but it would also be used to measure something about that defect such as its size, shape, and orientation. NDE may be used to determine material properties, such as fracture toughness, formability, and other physical characteristics. In ultrasonic testing, high-frequency sound waves are transmitted into a material to detect imperfections or to locate changes in material properties [13].

Field-Programmable Gate Arrays/Digital Signal Processor (FPGA/DSP) environment has been used so far for various designs like Predictive Current Control of Voltage-Source Inverters, AC-voltage regulation, neural network controller so on and so forth [14-16]. The purpose of using this setup varies, from unloading the DSP processor by performing certain part in the hardware FPGA [14] to that design which cannot be reached using a digital signal processor (DSP) [16].Also while some are used for cost effective implementation [15] others are mainly used for performing high frequency computation on FPGA and data processing on DSP [17]. In other words resources (FPGA/DSP) partitioning of the architecture is based upon the functionality and speed requirements [18].

FPGAs have become an extremely popular implementation technology for custom hardware because they offer a combination of low cost and very fast turnaround, but the use of FPGAs is hampered by the very large overhead of FPGA-based architectures [19]. This is the reason we are using the two technologies for their best use in our work. While we will perform the high frequency (62.5 MHz) computing with FPGA all lower frequency (>1MHz) data extensive processing will be done within the DSP. The flexibility of FPGAs provides multiprocessor and open architecture interface [20]. This flexibility helps us to interface the DSP in our system with the eternal components like the ADC (Analog to Digital Converter) and the DAC (Digital to Analog Converter) through its EMIF bus for high speed data communication between them.

Figure 1.1 Experimental ultrasonic crack detection system

#### **1.2 Hardware Architecture**

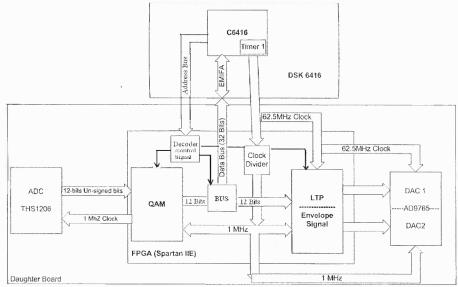

The experimental test system shown in Figure 1.1 is implemented with DSP and FPGA where, the DSP carries out the analysis of the received signal at 1MHz while the FPGA operates at 62.5MHz for the generation of LTP signal and to retrieve the envelope of the received signal. The software for DSP is written in C while that for FPGA is written in VHDL. The FPGA executes front end processing tasks at a higher rate while the DSP analyzes data of the received baseband signal from the FPGA at a much lower rate.

As shown in Figure 1.1, the experimental hardware consists of Spectrum DSP's (TMS320C6416) DSP Starter Kit (DSK), Dalanco Spry's daughter board (FPGA, Spartan-IIE), Physical Acoustic Corporation's wide bandwidth AE amplifier and a set of ultrasonic transducer. Figure 1.2 shows the interface structure of the DSK and the FPGA and the task allocation among the two processors. The test plate is shown in lower right hand side of Figure.1.1 where a set of two Physical Acoustic 150 KHz ultrasonic transducers are mounted on the test material.

Figure 1.2 Block diagram to show the interface between the DSP and FPGA

#### 1.3 DSP Starter Kit

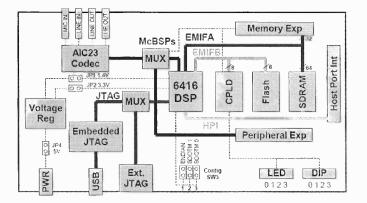

The C6416 DSK is a low-cost standalone development platform that serves as a hardware reference design for the TMS320C6416 DSP. Figure 1.3 shows the schematic diagram of the DSK board with the on board components and interfaces. The C6416 DSP device operates at 1GHz clock rate, with information processing rate of about 8800 MIPS (nearly 9 billion instructions per second), three flexible multi-channel buffered serial ports and the internal DMA engine which can provide over 2Gbps of I/O bandwidth with 64 independent channels, a high performance fixed point processor [21]. The sampling rates of the ADC and DAC codec converters and the hardware interrupt are functions of the timer frequency which is software controlled. The AIC23 is designed for conventional audio processing and is not used in this experiment.

Figure 1.3 Block diagram for the on board components and their interfaces on the DSK Source: TMS320C6416 DSK Technical Reference, 505945-0001 Rev. A April 2003

#### **1.4 Daughter Board**

Drive signal synthesis, receiver signal demodulation and interfaces between the DSK, ADC, DAC, etc. are carried out on the Dalanco Spry daughter board. The main components on the daughter board include: Spartan-IIE FPGA, THS1206 ADC and ADC9765 DAC. The THS1206 is a 12-bit ADC which runs at 1MHz (clock from the

FPGA), has four channels with signal-to-noise ratio of 68 db [22]. The AD9765 is a dualport, high speed, 2-channel, 12-bit CMOS DAC [23]. It integrates two high quality, 12bit TxDAC+ cores, a voltage reference, digital interface circuitry into a small 48-lead LQFP and supports update rates up to 125 MSPS [23]. For the current system, AD9765 is running on two clocks viz. 62.5 MHz and 1MHz for two different channels. A VHDL and schematic mixed design entry is used to generated the configuration file for the FPGA. VHDL is a hardware description language for very high speed integrated circuits; it is used to describe electronic systems without any dependency on implementation [24].

The Spartan-IIE FPGA itself has 6,912 logical cells and 16 bits/LUT distributed RAM with a speed grade of -6. They are customized by loading configuration data into internal static memory cells [25, 26]. Unlimited reprogramming cycles are possible with this approach [25, 26]. Stored values in these cells determine logic functions and interconnections implemented in the FPGA [25, 26]. Configuration data can be read from an external serial PROM (master serial mode), or written into the FPGA in slave serial, slave parallel, or boundary scan modes [25, 26]. The configuration of the Spartan IIE FPGA determines the interaction of the ADC, DAC, and digital I/O with the local bus. The current experimental system utilizes 1,581 slices out of 3072 with a total gate count of 30,892 [25, 26]. Other benefits of the Daughter Board include:

1) Higher sampling rate: The C6416 DSK has an onboard CODEC (TLV320AIC23) that has predefined sampling rates. This CODEC has the maximum sampling frequency of 96KHz [22], which is significantly less than the required sampling frequency of 1MHz for the ADC and 62.5MHz required for the DAC (Low Transient Pulse Generation). The

Daughter Board's ADC and DAC operate in the MHz range and are adequate for this application.

2) No DC blocking: The C6416 DSK CODEC blocks DC and hence cannot be used for motion control. The Daughter Board's analog interface, on the other hand, operates from DC to 125MHz.

#### **1.5** Low Transient Pulse

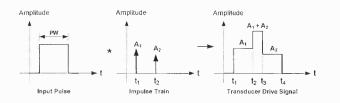

The Low transient pulse (LTP) technology is an innovative technique [4] to produce a short duration and compact acoustic pulse by means of pre-shaping the excitation signal. It has been experimentally verified that the LTP method produces a better measurement resolution and simpler hardware implementation due to less phase interference and a less complex algorithm. No modulation circuits or regenerative loops are necessary to synthesize the drive signal. Within the quantitative ultrasonography context, the LTP method improves detection resolution by minimizing aliasing of signals transmitted from soft and hard tissues. This improvement is achieved by convolving the input pulse with the impulse sequence to generate a necessary drive signal. Figure 1.4 below shows the pulse-impulse convolution scheme.

Source: B. Cheng and T. Chang, "Enhancing ultrasonic imaging with low transient pulse shaping," Ultrasonics, Ferroelectrics and Frequency Control, IEEE Transactions on, vol. 54, pp. 627-635, 2007.

A typical ultrasonic transducer can be approximated by a second order underdamped transfer function as:

$$G(s) = \frac{\alpha s}{s^2 + 2\zeta \omega_n s + \omega_n^2}$$

The design parameters for a two-impulse low transient pulse shaper can be summarized as follows [4]:

$$A_{1} = \frac{1}{1 + M_{p}^{n}}, \ t_{1} = 0$$

$$A_{2} = \frac{M_{p}^{n}}{1 + M_{p}^{n}},$$

$$t_{2} = \frac{n\pi}{\omega_{n}\sqrt{1 - \zeta^{2}}} = \frac{n\pi}{\omega_{d}}, \quad M_{p}^{n} = \left(e^{-\frac{\zeta\pi}{\sqrt{1 - \zeta^{2}}}}\right)^{n}, n = 1, 3, 5, ...$$

where  $A_1$  and  $A_2$  are the impulse amplitudes that occur at time  $t_1$  and  $t_2$ , respectively

while  $M_p^n = \left(e^{-\frac{\zeta \pi}{\sqrt{1-\zeta^2}}}\right)^n$  the variable n determines the oscillation cycles of the LTP acoustic

signal.

#### **1.6** Benefits

#### 1.6.1 TMS320C6416T

• C6416 is the world's first 90nm DSP running at 1GHz. Moving transistors closer together has increased the speed of the operation, as well as it allows a higher density of on-chip memory to increase application efficiency [27]. This 90 nm process technology has eased integration of system-on-a-chip architectures by streamlining communication between the DSP, memory, peripherals, RISC processors and analog components [27].

• There are three main vendors of single DSP core processor chips: Analog Devices, Freescale, and Texas Instruments. Table 1.1 [28]compares these DSPs.

| Table 1.1 Comparison of various DST processors in market | Table 1.1 | Comparison of various DSP processors in mark | et |

|----------------------------------------------------------|-----------|----------------------------------------------|----|

|----------------------------------------------------------|-----------|----------------------------------------------|----|

| Chip Family                                                              | Price            | Data           | Clock      | Primary               | Primary                                   |

|--------------------------------------------------------------------------|------------------|----------------|------------|-----------------------|-------------------------------------------|

| (Development Boards)                                                     | Range            | Format         | speed/core | Competitors           | Application<br>Telecom,<br>Infrastructure |

| ADI Black Fin (ADSP-                                                     |                  | 32bit          |            | C '55x and            | ,automotive                               |

| BF518F EZ-BOARD)                                                         | \$325            | fixed          | 400 MHz    | C'64x                 | and video                                 |

| ADI Tiger Shark (                                                        |                  | 201.4          |            |                       | Military                                  |

| ADZS-TS201S-<br>EZLITE)                                                  | \$1,000          | 32bit<br>float | 500 MHz    | C'67x and<br>ADISharc | Imaging and<br>Infrastructure             |

| $\mathbf{E}\mathbf{E}\mathbf{E}\mathbf{I}\mathbf{E}\mathbf{E}\mathbf{I}$ | \$1,000          | moat           | JUU MINZ   | C'67x and             | mnastructure                              |

| ADI Sharc ( ADSP-                                                        |                  | 32bit          |            | ADITiger              | Audio                                     |

| 21371 EZ-KIT Lite)                                                       | \$495            | float          | 266 MHz    | Shark                 | Applications                              |

|                                                                          |                  |                |            |                       | Motor                                     |

|                                                                          |                  |                |            |                       | Control,                                  |

| Free Scale '5685x                                                        |                  | 24Bit          |            | C '64 and<br>TI       | Digital<br>Power                          |

| (EVM100)                                                                 | \$149            | fixed          | 120 MHz    | C28x/24x              | supply                                    |

| ()                                                                       | <b>+ -</b> · · · |                |            |                       | Control                                   |

|                                                                          |                  |                |            |                       | (Automobile,                              |

|                                                                          |                  |                | ~~~        |                       | Industrial)                               |

| TI C28x/24x (eZdsp <sup>TM</sup> $E2812$ )                               | \$205            | 32/16bit       | 60/40      | Freescale             | and digital                               |

| F2812)                                                                   | \$325            | Fixed          | MHz        | '5685                 | power                                     |

|                                                                          |                  |                |            |                       | Portable                                  |

|                                                                          |                  |                |            |                       | Audio,<br>Consumer                        |

|                                                                          |                  | 16bit          |            | ADI Black             | Electronics                               |

| TI 'C55x (C55x DSK)                                                      | \$515            | Fixed          | 200 MHz    | Fin                   | like Mobiles                              |

|                                                                          |                  |                |            |                       | Telecom,                                  |

| TI 'C6416T (C64x                                                         |                  | 32bit          |            | ADI Black             | Infrastructure                            |

| DSK)                                                                     | \$515            | Fixed          | 1GHz       | Fin                   | and video                                 |

|                                                                          |                  |                |            |                       | Automobile                                |

|                                                                          |                  | 1 (1 )         |            |                       | and                                       |

| ADSP-BF5xx(ADZS-                                                         | <u> </u>         | 16bit<br>Fixed |            |                       | consumer                                  |

| BF561-EZLITE)                                                            | \$500            | Fixed          | 600 MHz    | TI' C55x              | Electronics                               |

| TI '67 (C67x DSK)                                                        | \$414            | 32bit<br>Float | 720 MHz    | SHARC,<br>CPUs        | Audio                                     |

|                                                                          |                  | 1'IUat         |            |                       | systems                                   |

Source: BDTI 2009; Datasheet of TMS320C6414T, TMS320C6415T, TMS320C6416T Fixed-Point Digital Signal Processors, SPRS226M, 2009; Datasheet of ADSP-BF512/BF512F ; Datasheet of ADSP-TS201S; Datasheet of ADSP-21371; 56F826 Evaluation Module Hardware User's, Freescale Manual; Technical reference eZdsp<sup>™</sup> F2812, Spectrum Digital ; Datasheet of TMS320LC549-80; Datasheet of ADSP-BF561; Datasheet of TMS320C6713

..

.

**Figure1.5** Millions Instructions per second for various processors. Source: BDTI 2009; Datasheet of TMS320C6414T, TMS320C6415T, TMS320C6416T Fixed-Point Digital Signal Processors, SPRS226M, 2009; Datasheet of ADSP-BF512/BF512F ; Datasheet of ADSP-TS201S; Datasheet of ADSP-21371; 56F826 Evaluation Module Hardware User's, Freescale Manual; Technical reference eZdsp<sup>TM</sup> F2812, Spectrum Digital ; Datasheet of TMS320LC549-80; Datasheet of ADSP-BF561; Datasheet of TMS320C6713

Based on the above data we use TMS320C6416T chiefly for the following reasons

• C6416T running at 1GHz can execute close to approximately 10 billion instructions per second. This can facilitate in performing exhaustive data crunching of the demodulated data. RTDX which uses lot of instruction cycles for its execution for the communication between the host and the DSP can be used to display the data on the host PC in real time

• Since C6416T is a fixed point DSP, its power consumption is low hence this feature can be exploited for the future design of a hand held ultrasound device.

• Most prominently, as per our design requirement, C6416T can generate a maximum clock frequency (timer) of 62.5 MHz (16 ns) which helps in the enhanced resolution of the Low Transient Pulse (LTP) generation. For the present application, LTP width is about  $3.75\mu$ s. Although we do get a quantization error of ( $16*235=3750\mu$ s, 3760-3750=10ns), this error is within experimental tolerances.

#### 1.6.2 Spartan-IIE, (XC2S300E)

• Spartan-IIE FPGAs are typically used in high-volume applications where the flexibility of a fast programmable solution adds benefits and are ideal for shortening product development cycles while offering a cost-effective solution for high volume production [26].

• It offers on-chip synchronous single-port and dual-port RAM (block and distributed form), DLL clock drivers, programmable set and reset on all flip-flops, fast carry logic, and many other features [26].

• It contains an optimal number of gates for the design, hence extremely efficient implementation for cost/transistor. It also readily interfaces, without any glitches, with the DSP, ADC and DAC with multiple clocks.

• The design of the daughter board permits programming of the FPGA through the DSP's Code Composer Studio® (CCS) and hence saves time from JTAG emulation separately for the FPGA. The process of programming through the DSP is explained in Chapter 2.

#### 1.7 RTDX (Real Time Data Exchange)

Real-Time Data Exchange (RTDX) is a technology developed by Texas Instruments that enables real-time bi-directional communication between a digital signal processor (DSP) or microcontroller and a host application that provides real-time, continuous visibility into the way DSP applications operate in the real world [29, 30]. This property of C6416T allows us to take our design to another level. By the use of RTDX we can transfer the envelope signal received in the DSP to the host computer in real time. Since RTDX is bi-directional, we are not restricted to receive the transducer signals but can send data back into the DSP. This allows us to perform real time analysis using tools like Matlab. Matlab's Embedded IDE Link<sup>TM</sup> CC is the tool which helps to interface the host PC with the DSP and communicate in real time. It automates debugging, project generation, and verification of object code executing on an embedded processor or on the instruction set simulator provided by the integrated development environment (IDE) [31].

#### **CHAPTER 2**

#### TMS320C6416: TI's DSP PROCESSOR

#### 2.1 Digital Signal Processor

In the design, C6416DSK functions as the central processing (Edge Detection) and control unit (Initialization of ADC and FPGA, Clock Source, Interface between FPGA/DSP) of the system. From executing the analysis of the received signal to controlling all the peripherals components, C6416 acts as the key component of the system. A brief review of the C6416 system is given in the following section based on materials [21, 27-30, 32-37]

**Figure 2.1** Architectural overview of TMS320C6416 DSP Source: Datasheet of TMS320C6414T, TMS320C6415T, TMS320C6416T Fixed-Point Digital Signal Processors, SPRS226M

Figure 2.1 shows the functional unit of the C6416 and its key feature [37] are as shown below:

- Highest-Performance Fixed-Point DSPs , 1 GHz instruction cycles, 8000 MIPS

- VelociTI.2<sup>™</sup> Extensions to VelociTI<sup>™</sup> Advanced Very-Long-Instruction-Word(VLIW) TMS320C64x<sup>™</sup> DSP Core

- Two External Memory Interfaces (EMIFs)

- Enhanced Direct-Memory-Access (EDMA) Controller (64 Independent Channels).

- L1/L2 Memory Architecture: 128K-Bit (16K-Byte) L1P Program Cache (Direct Mapped), 128K-Bit (16K-Byte) L1D Data Cache (2-Way Set-Associative) 8M-Bit (1024K-Byte) L2 Unified Mapped RAM/Cache (Flexible Allocation).

- Three 32-Bit General-Purpose Timers

#### 2.2 Memory Map

The memory map of C6416 is as shown in Figure 2.2, where by default, the internal memory sits at the beginning of the address space and portions of memory can be remapped in software as L2 cache rather than fixed RAM [21].

Each EMIF (External Memory Interface) has 4 separate addressable regions called chip enable spaces (CE0-CE3) where the SDRAM occupies CE0 of EMIFA, CPLD and Flash are mapped to CE0 and CE1 of EMIFB respectively and the Daughtercards use CE2 and CE3 of EMIFA [21]. In the design, EMIFA is used to connect to the Dalanco Spry daughter board. CE2 (0xa0000000) among two chip selects (CE2 and CE3) is used for the interface with the daughter board hence with the FPGA and other components like the ADC and DAC on board.

| Address    | Generic 6416<br>Address Space           | 6416 DSK                     |

|------------|-----------------------------------------|------------------------------|

| 0×00000000 | Internal Memory                         | Internal<br>Memory           |

| 0×00100000 | Reserved Space<br>or<br>Peripheral Regs | Reserved<br>or<br>Peripheral |

| 0×60000000 | EMIFB CE0                               | CPLD                         |

| 0x64800900 | EMIFB CE1                               | Flash                        |

| 0x68000000 | EMIFB CE2                               |                              |

| 0x6C000000 | EMIFB CE3                               |                              |

| 00000008x0 | EMIFA CE0 -                             | SDRAM                        |

| 0x90000000 | EMIFA CE1                               |                              |

| 0xA0000000 | EMIFA CE2                               | Daughter                     |

| 0xB0000000 | EMIFA CE3                               | Card                         |

| Figure     | 1-2, Memory Map, C64                    | 16T DSK                      |

**Figure 2.2** Memory Map of C6416T DSP Starter Kit (DSK) Source: TMS320C6416 DSK Technical Reference, 505945-0001 Rev. A April 2003.

The DSK Board has two External Memory Interfaces (EMIF's)[36]:

- One 64-Bit (EMIFA) and a 16-Bit (EMIFB).

- Glueless interface to Asynchronous Memories (SRAM and EPROM) and

- Synchronous Memories (SDRAM, SBSRAM, ZBT SRAM and FIFO)

- 1280 MB Total addressable external memory space

#### 2.3 Interrupts:

DSPs work in an environment that contains multiple external asynchronous events. These events require tasks to be performed by the DSP when they occur. Real-time data input/output handling by the C6416 includes:

A. Interrupts -An interrupt stops the current CPU process so that it can perform a required task initiated by the interrupt whose source can be an ADC, a timer and so on, by redirecting the program flow to an ISR [38].

B. Polling - A polling-based program (non-interrupt driven) continuously polls or tests whether or not data are ready to be received or transmitted which makes it less efficient than the interrupt scheme [38].

#### • Interrupt service Table

A vectors file is used for the interrupt-driven program for the system. In the system designed interrupt is used to fetch the sampled data from the ADC to the DSP and send it back to the DAC. C6000 DSP Peripheral set has up to 32 interrupt sources however the CPU has 12 interrupts available for the use [32]. The interrupt service table (IST) is used when an interrupt begins, which has Fetch Packets (FP) associated with it [38]. There is an offset associated with each specific interrupt since each FP contains eight 32-bit instructions (256 bits) or 32 bytes, each offset address in the table is incremented by (0x20)h = 32 [38]. Below is the description of the vector.asm used for the system [38].

| .ref  | _adc_ISR  |

|-------|-----------|

| .ref  | _c_int00  |

| .sect | "vectors" |

RESET RST: mvkl .S2 c int00.B0 c int00,B0 mvkh .S2 В .S2 B0 NOP NOP NOP NOP NOP NMI RST: NOP NOP NOP .endloop INT4: mvkl.S2 adc isr, B0

mvkh .S2 adc isr, B0

B .S2 B0 NOP NOP NOP NOP NOP

- .ref command refers to the ISR naming used in the main.c program. \_adc\_ISR is the name of the ISR used for the interrupt from the ADC in C program. The function \_c\_int00 is the name of the ISR which is the entry point in the BOOT program which sets up the stack and calls for main in the C program [38].

- .sect command assigns the name of this sector to be *vector* which is used to allocate it to the memory in the Linker Command (.cmd) file.

- All the NOPs (No operations performed) are for the FP (Fetch Packet) in the interrupt which are not used.

- In INT4 (Interrupt No.4), *mvkl.S2* moves (using the one of the eight functional unit of the CPU .S2) the 16 LSBs of address \_adc\_isr to 16 LSBs of B0 and similarly *mvkh.S2* moves the rest of 16 MSBs of address adc\_isr to B0. Hence B0 contains the full 32 bit address of adc\_isr. *B* .*S2 B0* then branch to the address in B0. For the other FPs still we don't use them we use NOPs [34, 38] . Refer to [38] Chapter 3 (3.8.2) for more information on Types of Instructions.

#### 2.4 Timers

The timers of C6416 have two signaling modes and can be clocked by an internal or an external source with the input and output pins (TINP and TOUT) that can function as timer clock input and clock output, where an internal clock, for example the timer can signal an external ADC to start a conversion, or it can trigger the DMA controller to

begin a data transfer [33]. In the system designed, timer 1 is used to signal an external ADC, DAC and the FPGA. Since the generation of the LTP in the FPGA requires a pulse with of 3.75us, timer 1 is run at its maximum frequency of 62.5 MHz by setting up the Period to be '1' as per equation (2.1), from [33].

Timer Frequency= CPUrate

$$(1 \text{ GHz}) / (2^* \text{ Period } *8)$$

(2.1)

More detail about setting up the timer and its register can be found at [33] and Appendix C. Dividing the timer frequency (62.5MHz) for the clock of ADC (1MHz) and for other modules (like QAM) in FPGA is done in the FPGA itself which using clock diver as shown in later chapters. The system designed has timer 1 set as shown below.

```

void timer1_start()

```

{

}

\*(unsigned volatile int \*)\_TIMER\_CTL1\_ADDR &= 0xff3f; / hold the timer \*(unsigned volatile int \*)\_TIMER\_CTL1\_ADDR |= 0x301; /0x211; \*(unsigned volatile int \*)\_TIMER\_PRD1\_ADDR = 0x01; /set for 32 bit cnt \*(unsigned volatile int \*)\_TIMER\_CTL1\_ADDR |= 0xC0; /start the timer

The first statement disables the counter and holds it at the current state. In the next, while the counter is disabled, we configure the timer by setting the TOUT pin to be output pin and enabling the clock mode and internal clock source (CPU clock/8). The period of the timer is set to '1'. The last statement initialize the counter register to zero and it starts counting from the next clock.

In the code at various locations we have used statements as shown below

\*(short \*) dacaddr1 = value

\*(unsigned volatile int \*)\_TIMER\_CTL1\_ADDR &= 0xff3f

These statements are chiefly used for writing to peripherals (I/O) and setting external

registers. (short\*)dacaddr1 is the declaration of a pointer daccdr1 to type short. It just type cast dacaddr1 to be a pointer of type short if not declared in the beginning of the program. Hence \*(short\*)dacaddr1 is the value stored at address pointed by dacaddr1. Note that in the program dacaddr1 has been defined with a hex value (address of the DAC1). So \*(short \*) dacaddr1 = value transfers the value to the external DAC1. Similarly for \*(unsigned volatile \*) TIMER CTL1 ADDR int &= 0xff3, TIMER CTL1 ADDR defines the address for the control register of timmer1. \*(unsigned volatile int \*) TIMER CTL1 ADDR is the value stored at the control register and the complete statement mean ANDing it with the current value of the register.

## 2.5 Software Programming

Among the three different languages available for the coding of C6416 i.e. C, Linear Assembly and Assembly [38], we have used C in our design. Although the choice will have an impact on the programming and optimization efforts required but since our use of the DSP is straightforward and doesn't involve tight code integration, we have written our code in C. Also the compiler of CCS tool aids in optimization of the code into assembly very efficiently.

Careful consideration is given to the data type when writing the code. While the data communicated between the FPGA and the DSP and in the buffers for the moving average filter are declared to be short since there are only 12-bits of data, both retrieved from the ADC and sent to the DAC, unsigned int types are used for loop counters and ADC sampled data (unsigned) to avoid any unnecessary signed extension instruction [35].

After running the program in DSP from main, interrupt flags are set, the frontend program is loaded on to the FPGA and the ADC is initialized. The DSP then enters into an infinite while loop and waits for the hardware interrupt INT4 to occur (as defined in vector.asm). At each sampling time, the ADC module in the FPGA acquires the data from the THS1206 and also triggers an interrupt to the DSP to send this over. This interface (EMIF) between the FPGA and DSP has been explained in more detail in later chapters. The data which the DSP gets through the FPGA during the hardware interrupt is a 12-bit unsigned number and has a DC level of 0x800 or +2.7 V (More about resolution is given in Appendix A )

## 2.5.1 Project File (.pjt)

This is the main file and contains sub folders like Source (.c, .cmd and .asm), Library (.lib), Include (.h), DSP/BIOS Configure (.tcf) etc. Executing "Rebuild All" in the project tab of the CCS integrates all these files to .out file [35]. This file is loaded onto to the DSP for its execution.

## 2.5.2 Linker File (.cmd)

This file is used to map different section to the memory and it shows which section resides in which part of the memory [38]. The linker allocates the program in memory using default location algorithm and places the various sections into appropriate memory locations, where code and data reside [38]. By using a linker command file with extension .cmd, one can customize the allocation process, specifying MEMORY and SECTIONS directives within the linker command file [38]. The Linker file (.cmd) [39] used for the system is as shown below:

```

MEMORY

ł

org=0x0

1 = 0 \times 200

vecs :

org = 0x200,

len=0x10000000

ISRAM:

SDRAM:

org=0x80500000,

len=0x4000000

org=0xA00000000000, len=0x400000

CE2:

}

SECTION

"vectors" > vecs

.text

>ISRAM

>ISRAM

.bss

.cinit > ISRAM

.const > ISRAM

.far >ISRAM

.stack >ISRAM

.cio >ISRAM

.sysmem >ISRAM

.mw isrambuff >ISRAM

Linker file consists on two main parts:

```

## 2.5.2.1 Memory

This is used to declare all the memories (internal or external) or the interfaces associated with the DSP. These include the Internal SRAM (ISRAM), SDRAM (FPGA's .out file) and CE2 (EMIF, External Memory Interface). For each memory declared, the base address and size are specified. The memory vecs declared in the memory is used for the vector.asm file used for the interrupts. SDRAM declared in the memory is used to load the .out data for the FPGA. CE2 is used for the communication between the DSP and the FPGA through EMIF.

## 2.5.2.2 Section

This allocates the output sections into defined memory and designates the various code sections to available memory spaces[38].All the mnemonics like *.text .bss, .cint, .const*

used in the SECTION are called the Assembler Directives. An assembler directive is a message for the assembler which gets resolved during the assembling process and does not occupy memory space, since it does not produce executable code [38]. Other sections are assigned to the internal memory of the DSP. The *vectors* directive which is declared in the *vector.asm* file is assigned to *vecs* memory in the *.cmd* file. More information on different assembler directive and their use can be found in [40].

## 2.5.3 FPGA (.out) File

A *.hex* file is generated for the design using the Xilinx ISE. This file is converted to .out file using a converter provided by Dalanco Spry. In the present system, this file is loaded onto the FPGA through the DSP, so prior to running the program it is necessary to load this file onto the SDRAM which is mapped to DSP through the Chip Select 0 (CE0) by the Load option in the Code Composer Studio. This is then transferred to the FPGA as explained in section 2.5.4.2.

## 2.5.4 main.c Program

The basic main.c program provided by [39] is modified to a large extent for the design of the system as per the requirement in the FPGA-DSP environment.

### 2.5.4.1 Initialization

This process involves setting up the interrupt flags and initializing the ADC with values for CR0 and CR1. All the information for ADC and its setup used for the design is taken from here [22].

### 2.5.4.1.1 ADC (THS1206)

Figure 2.3 shows the configuration flow for the THS1206. The system designed doesn't

use the default configuration but configures the ADC as per the requirement instead.

Figure 2.3 THS1206 Configuration Flow

Source: Datasheet of THS1206: 12-Bit, 6 MSPS, Simultaneous Sampling Analog-to-Digital Converter (Rev. H), Texas Instruments.

So as per the flow, 0x401 is first written to the ADC followed by 0x400. Then we set CRO. Since the ADC receives the upper 12-bits of the 16 bits register in the DSP, in the main.c we set the CRO to (0x 01A0)h which the ADC receives as (0x01A)h. This basically sets the ADC for the following from the LSB to the MSB

- Internal reference voltage selected

- Continuous conversion mode selected

- ADC made active

## • Analog input BINP (ADC 4)

Then we set CR1. Same as for CR0 we set CR1 to be 0x4d20 which gets to ADC as 0x4d2. This configures the ADC for the following (LSB  $\rightarrow$ MSB)

- No Reset of the ADC '0'

- In the write only mode to the ADC we reset the FIFO '1'

- Trigger level set to 0 for single channel '00'

- Trigger condition for DATA\_AV set to Active low pulse '01'

- Since we are wiring to the ADC we set the bit to '1'

- Since we want the ADC to given an unsigned output we set this bit to '1'

- Normal conversion mode '00'

- To be set to '1' by default for CR0.

For more information on the ADC and the registers refer to [22].

# 2.5.4.1.2 Flag Setup

Flags in the main.c file are set in the following order:

- CSR (Chip Select Register): This register is first set to a value of 0x100. This disables all the interrupts except the NMI and sets it to little endian.

- IER (Interrupt Enable Register): This register is first set to value 0x1. This resets the interrupt enable.

- ICR (Interrupt Clear Register): This register is first set to value 0xffff. This clears all the corresponding flags in the IFR (Interrupt Flag Register).

After IER, ICR and CSR are set we perform the process stated in section 2.5.4.1.2 and section 2.5.4.2 and just before going to the infinite while loop (section 2.5.4.3) we configure the flags again for the following.

- IER (Interrupt Enable Register): To set this register we OR its current value with 0x12. This enables all the nonreset interrupts and also enables interrupt No. 4 (non-NMI).

- CSR (Chip Select Register): To set this register we OR its current value with 0x1. This is for global interrupt enabler.

More information on interrupt registers can be found in [41].

# 2.5.4.1.3 Miscellaneous

EMIFA CE2 space control register (CECTL2, 0x 01800010) [36] is configured since we use this for our communication with the Daughter Board. This register is set with value 0x3c0cf20 for the following

- Zero number of clock cycles for AOE\_N and ARE\_N '00'

- Reserved ' 00'

- Sets EMIFA to 32 bit Asynchronous interface '010'

- Reserved '0'

- 15 clock cycles for the width of read strobe '001111'

- Reserved '11'

- 1 clock cycle for the read setup '0001'

- 0 clock cycles for write hole width and the hold time of AOE and ARE rising '00'

- 60 clock cycles for write strobe width.

Also, the program system sets the EXTPOL (External Interrupt Polarity Register, 0x19c0008) to value 0x1 which makes a high-to-low transition on an interrupt source recognized as an interrupt [32].

## 2.5.4.2 Loading the FPGA

The various critical variables declared with their hex values in the main.c program with

their use are as shown in Table 2.1

Table 2.1 : Variables used in the FPGA program

| Variable Name | Hex Value  | <b>Remark</b><br>This is the base address of SDRAM where we<br>load the .out file for the FPGA from the Code                          |

|---------------|------------|---------------------------------------------------------------------------------------------------------------------------------------|

| VIRTEX_MEM    | 0x80500000 | Composer Studio<br>This is the size of the memory of the FPGA                                                                         |

| VIRTEX SIZE   | 0x393D8    | (300K). Any data bigger than this wont be transferred to the FPGA                                                                     |

| VICILA_DIZE   | 04373130   | This is the address line for sending the data to                                                                                      |

| VIRTEX_ADDR   | 0xa0000000 | the FPGA                                                                                                                              |

| VIRTEX_WRCS   | 0xa0000004 | Address for sending control bits for to the FPGA. The 2nd and the 1st bit is for Write (WR_N) and Chip Select(CS_N) bits respectively |

| VIRTEX_PROG   | 0xa0000008 | Address for sending the progress control bits to<br>the the FPGA.PROGHI and PROGLO are used<br>to make it either high or low          |

A function AVR32\_LoadVir () is used to load the data into the FPGA during its execution in the main program. The execution of this function is described below:

• First, all the control bits are put to high (disabled all). Then status of the control lines is checked by reading the bits on VIRTEX\_STAT. If both the bits are zero, the execution goes to the next line, else it waits on the statement till both get zero.

• Second, in order to write data onto the FPGA, the active low Chip Select and Write bits are enabled by writing a 0x00 at address for VIRTEX\_WRCS. The program, then checks and verifies to confirm that both the bits are '0'.

• DSP then starts transferring data from the SDRAM to the FPGA. For this to take place, the program goes to the address location VIRTEX\_MEM to retrieve the 8 bits. The

data bus between the DSP and FPGA are mapped in a way that the bits are to be rearranged before they are sent e.g. the 1<sup>st</sup> of the 8 bit data from SDRAM goes to the 31<sup>st</sup> bit of the data bus on to the address location of VIRTEX\_ADDR. This bits restructuring is performed as shown below.

d31 = (1 & inword) ? BIT31 : 0; // Virtex d0/din LSB d23 = (2 & inword) ? BIT23 : 0; // Virtex d1

# output = d31|d23|d22|d17|d11|d6|d5|d0;

The last statement for output concatenates each individual bit to form one byte to be transferred on to the FPGA. This transfer of data takes place for address VIRTEX\_MEM + pointer. This pointer gets incremented after transfer of each 8 bits of data till it reaches the value equal to VIRTEX\_SIZE i.e. memory size in the FPGA. Since VIRTEX\_SIZE defined is little less than 300K we send 0's to the FPGA for approximately 20 times after the data from SDRAM to FPGA has been transferred.

• After the transfer is completed Chip select and Write enable are pulled back to high to stop any further erroneous transfer. These bits are then checked after they are pulled back to '11'. At the end AVR32\_LoadVir function returns the control back to the main.

## 2.5.4.3 Free Run

Subsequent to the system being initialized and the data being loaded onto the FPGA, the program then enters an infinite while loop to wait for the interrupt from the ADC. When the interrupt occurs, the demodulated data for the received signal in the ADC are fetched into the DSP. Inside the DSP we execute two main functions.

## 2.5.4.3.1 Moving Average Filter

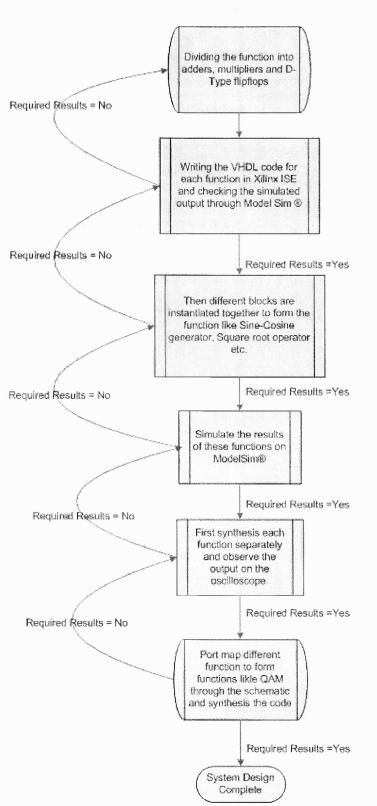

As observed on the oscilloscope, the envelope (demodulated) signal of the receiver has a high frequency noise component as shown in Figure 2.4(a). This is a problem for detecting the 3<sup>rd</sup> and the 4<sup>th</sup> maxima/peak during the estimation of plate parameter. To remove this high frequency noise we use a Moving Average Filter (MAF). For the design of this filter the demodulated data from the QAM is captured in the oscilloscope and is used as the input to the MAF filter first designed in Matlab. Simulated results show improved and desirable envelope with a MAF (window width=16) by removing all high frequency noise and giving observable peaks of the demodulated signal. This is implemented by construing a FIFO in the DSP. In this, on each interrupt, the 12-bit input from the QAM is first converted to signed and then stored at the 1<sup>st</sup> location of , the data stored on the previous clock is shifted to 2<sup>nd</sup>, so on and so forth. The data on the 16<sup>th</sup> location is discarded. Then, all the signed values in the FIFO are added and later divided by 16 to give the desired MAF output. The improvement on the received data from the QAM is as shown in Figure 2.4(b).

Figure 2.4 Envelop signal (a) before filtering and (b) after filtering.

## 2.5.4.3.2 Edge Detection

To detect the maxima or peaks from the QAM demodulated signal, an edge detection algorithm has been implemented to detect the maxima and then based on the time difference between the 1<sup>st</sup> peak and the subsequent peaks, it determines the parameter of the plate since the speed of ultrasounds in Sawbone is known. The captured, demodulated filtered data are first used to design and optimize an algorithm in Matlab which is later implemented on to the DSP.

For the detection of  $1^{st}$  maximum, we store the current value into a buffer from the QAM demodulator if it is greater than the previous value. Also, in the main program, a counter is incremented on each interrupt which starts from time t=0 and on detection of the  $1^{st}$  maximum , stores its value . This stored integer indexes the time for the first maxima in µs.

For the 2<sup>nd</sup> maximum, two conditions are taken into account. Firstly, the current value should be smaller than the 1<sup>st</sup> maximum. Secondly, unlike for finding the 1<sup>st</sup> maximum, the last value stored should be less than the current value. The second condition is important because it prevents any false reporting of 2<sup>nd</sup> maximum from the 1<sup>st</sup> parabola as many points over it will be greater than the maxima from the 2<sup>nd</sup> parabola. Therefore we check for the rising curve. When both of the conditions are satisfied, the counter value during that interrupt is stored and displayed in the watch window of the CCS. For subsequent maxima, we follow the same approach as for 2<sup>nd</sup> maximum.

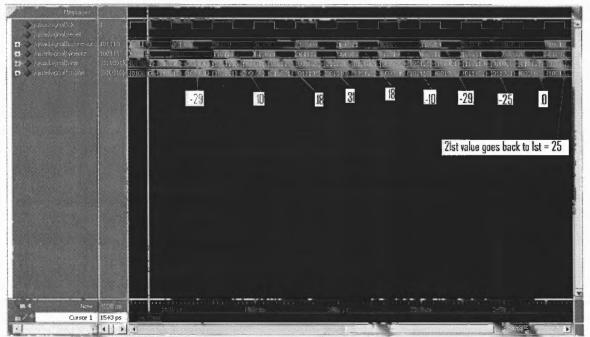

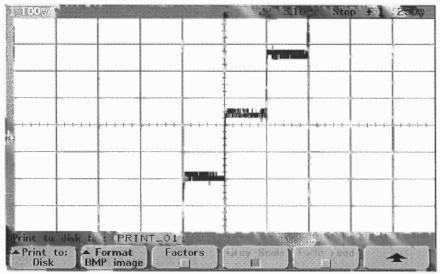

As shown in Figure 2.5, watch window displays the occurrence for the  $1^{st}$ ,  $2^{nd}$ ,  $3^{rd}$  and  $4^{th}$  maxima at time n1 (=51 µs), n2(=80 µs), n3(=102 µs) and n4 (=128 µs) respectively.

| Image: Problem of the image of the |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ♦ n3         102         int         dec           ♦ n4         125         int         dec                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| • n3         102         init         dec           • n4         125         init         dec                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| # 711 ····· ···· ···· ····· ·····                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |