## **New Jersey Institute of Technology** Digital Commons @ NJIT

Theses and Dissertations Dissertations

Fall 2009

## Soft-error resilient on-chip memory structures

Shuai Wang New Jersey Institute of Technology

Follow this and additional works at: https://digitalcommons.njit.edu/dissertations

Part of the Computer Engineering Commons

#### Recommended Citation

Wang, Shuai, "Soft-error resilient on-chip memory structures" (2009). Dissertations. 207. https://digitalcommons.njit.edu/dissertations/207

This Dissertation is brought to you for free and open access by the Theses and Dissertations at Digital Commons @ NJIT. It has been accepted for inclusion in Dissertations by an authorized administrator of Digital Commons @ NJIT. For more information, please contact digitalcommons@njit.edu.

## **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

#### **ABSTRACT**

#### SOFT-ERROR RESILIENT ON-CHIP MEMORY STRUCTURES

## by Shuai Wang

Soft errors induced by energetic particle strikes in on-chip memory structures, such as L1 data/instruction caches and register files, have become an increasing challenge in designing new generation reliable microprocessors. Due to their transient/random nature, soft errors cannot be captured by traditional verification and testing process due to the irrelevancy to the correctness of the logic. This dissertation is thus focusing on the reliability characterization and cost-effective reliable design of on-chip memories against soft errors.

Due to various performance, area/size, and energy constraints in various target systems, many existing unoptimized protection schemes on cache memories may eventually prove significantly inadequate and ineffective. This work develops new lifetime models for data and tag arrays residing in both the data and instruction caches. These models facilitate the characterization of cache vulnerability of the stored items at various lifetime phases. The design methodology is further exemplified by the proposed reliability schemes targeting at specific vulnerable phases. Benchmarking is carried out to showcase the effectiveness of these approaches.

The tag array demands high reliability against soft errors while the data array is fully protected in on-chip caches, because of its crucial importance to the correctness of cache accesses. Exploiting the address locality of memory accesses, this work proposes a Tag Replication Buffer (TRB) to protect information integrity of the tag array in the data cache with low performance, energy and area overheads. To provide a comprehensive evaluation of the tag array reliability, this work also proposes a refined evaluation metric, detected-without-replica-TVF (DOR-TVF), which combines the TVF and access-with-replica (AWR) analysis. Based on the DOR-TVF analysis, a TRB scheme with early write-back (TRB-EWB) is proposed, which achieves a zero DOR-TVF at a negligible per-

formance overhead.

Recent research, as well as the proposed optimization schemes in this cache vulnerability study, have focused on the design of cost-effective reliable data caches in terms of performance, energy, and area overheads based on the assumption of fixed error rates. However, for systems in operating environments that vary with time or location, those schemes will be either insufficient or over-designed for the changing error rates. This work explores the design of a self-adaptive reliable data cache that dynamically adapts its employed reliability schemes to the changing operating environments in order to maintain a target reliability. The experimental evaluation shows that the self-adaptive data cache achieves similar reliability to a cache protected by the most reliable scheme, while simultaneously minimizing the performance and power overheads.

Besides the data/instruction caches, protecting the register file and its data buses is crucial to reliable computing in high-performance microprocessors. Since the register file is in the critical path of the processor pipeline, any reliable design that increases either the pressure on the register file or the register file access latency is not desirable. This work proposes to exploit narrow-width register values, which represent the majority of generated values, for making the duplicates within the same register data item. A detailed architectural vulnerability factor (AVF) analysis shows that this in-register duplication (IRD) scheme significantly reduces the AVF in the register file compared to the conventional design. The experimental evaluation also shows that IRD provides superior read-with-duplicate (RWD) and error detection/recovery rates under heavy error injection as compared to previous reliability schemes, while only incurring a small power overhead.

By integrating the proposed reliable designs in data/instruction caches and register files, the vulnerability of the entire microprocessor is dramatically reduced. The new lifetime model, the self-adaptive design and the narrow-width value duplication scheme proposed in this work can also provide guidance to architects toward highly efficient reliable system design.

## SOFT-ERROR RESILIENT ON-CHIP MEMORY STRUCTURES

by Shuai Wang

A Dissertation

Submitted to the Faculty of

New Jersey Institute of Technology

in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy in Computer Engineering

Department of Electrical and Computer Engineering

January 2010

Copyright © 2010 by Shuai Wang ALL RIGHTS RESERVED

## APPROVAL PAGE

## SOFT-ERROR RESILIENT ON-CHIP MEMORY STRUCTURES

## Shuai Wang

| De Distriction Advisor                                           |      |

|------------------------------------------------------------------|------|

| Dr. Jie Hu, Dissertation Advisor                                 | Date |

| Assistant Professor of Electrical and Computer Engineering, NJIT |      |

|                                                                  |      |

|                                                                  |      |

|                                                                  |      |

|                                                                  |      |

| Dr. Sotirios G. Ziavras, Committee Member                        | Date |

| Professor of Electrical and Computer Engineering, NJIT           |      |

|                                                                  |      |

|                                                                  |      |

|                                                                  |      |

|                                                                  |      |

| Dr. Edwin Hou, Committee Member                                  | Date |

| Associate Professor of Electrical and Computer Engineering, NJIT | Date |

| Associate Professor of Electrical and Computer Engineering, 1911 |      |

|                                                                  |      |

|                                                                  |      |

|                                                                  |      |

|                                                                  |      |

| Dr. Roberto Rojas-Cessa, Committee Member                        | Date |

| Associate Professor of Electrical and Computer Engineering, NJIT |      |

|                                                                  |      |

|                                                                  |      |

|                                                                  |      |

|                                                                  |      |

| Dr. Joseph Y. Leung, Committee Member                            | Date |

| Distinguished Professor of Computer Science, NJIT                |      |

| 1                                                                |      |

#### **BIOGRAPHICAL SKETCH**

Author:

Shuai Wang

Degree:

Doctor of Philosophy

Date:

January 2010

#### **Undergraduate and Graduate Education:**

- Doctor of Philosophy in Computer Engineering,

New Jersey Institute of Technology, Newark, New Jersey, 2010

- Bachelor of Science in Computer Science, Nanjing University, China, 2003

Major:

Computer Engineering

**Publications:**

Shuai Wang, Jie Hu, and Sotirios G. Ziavras. On the Characterization and Optimization of On-Chip Cache Reliability against Soft Errors, IEEE Transactions on Computers (TC), Volume 58, Issue 9, pp. 1171 - 1184, September 2009.

Jie Hu, Shuai Wang, and Sotirios G. Ziavras. On the Exploitation of Narrow-Width Values for Improving Register File Reliability, IEEE Transactions on Very Large Scale Integration Systems (TVLSI), Volume 17, Issue 7, pp. 953 - 963. July 2009.

Shuai Wang, Jie Hu, Sotirios G. Ziavras, and Sung Woo Chung. Exploiting Narrow-Width Values for Thermal-Aware Register File Designs, In Proc. of the Conference on Design, Automation and Test in Europe (DATE 2009), pp. 1422 - 1427, Nice, France, April 20-24, 2009.

Shuai Wang, Jie Hu, and Sotirios G. Ziavras. Self-Adaptive Data Caches for Soft-Error Reliability, IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), Volume 27, Issue 8, pp. 1503 - 1507, August 2008.

Shuai Wang, Hongyan Yang, Jie Hu, and Sotirios G. Ziavras. Asymmetrically Banked Value-Aware Register Files for Low Energy and High Performance, Microprocessors and Microsystems, Volume 32, Issue 3, pp. 171 - 182, May 2008.

- Shuai Wang, Jie Hu, and Sotirios G. Ziavras. BTB Access Filtering: A Low Energy and High Performance Design, In Proc. of the IEEE Computer Society Annual Symposium on VLSI (ISVLSI 2008), pp. 81 86, Montpellier, France, April 7-9, 2008.

- Shuai Wang, Hongyan Yang, Jie Hu, and Sotirios G. Ziavras. Asymmetrically Banked Value-Aware Register Files, In Proc. of the IEEE Computer Society Annual Symposium on VLSI (ISVLSI 2007), pp. 363 368, Porto Alegre, Brazil, May 9-11, 2007.

- Hongyan Yang, Shuai Wang, Sotirios G. Ziavras, and Jie Hu. Vector Processing Support for FPGA-Oriented High Performance Applications, In Proc. of the IEEE Computer Society Annual Symposium on VLSI (ISVLSI 2007), pp. 447 448, Porto Alegre, Brazil, May 9-11, 2007.

- Shuai Wang, Jie Hu, and Sotirios G. Ziavras. On the Characterization of Data Cache Vulnerability in High-Performance Embedded Microprocessors, In Proc. of the International Conference on Embedded Computer Systems: Architectures, Modeling, and Simulation (SAMOS VI), pp. 14 20, Samos, Greece, July 17-20, 2006.

- Jie Hu, Shuai Wang and Sotirios G. Ziavras. In-Register Duplication: Exploiting Narrow-Width Value for Improving Register File Reliability, In Proc. of the International Conference on Dependable Systems and Networks (DSN 2006) Dependable Computing and Communications Symposium (DCCS), pp. 281 290, Philadelphia, PA, June 25-28, 2006.

- Jie Hu, Greg M. Link, Johnsy John, Shuai Wang, Sotirios G. Ziavras. Resource-Driven Optimizations for Transient-Fault Detecting SuperScalar Microarchitectures, In Proc. of the Asia-Pacific Computer Systems Architecture Conference (ACSAC 2005), pp. 200 214, Singapore, October 24-26, 2005.

To My Mom and Dad

#### ACKNOWLEDGMENT

First, I would like to thank my advisor Professor Jie Hu for supporting me throughout this work and for his constant advice and encouragement. He has showed me the whole picture of research on computer architecture, guided me in entering and exploring this exciting area. I treasure my learning experience under his invaluable guidance. I also like to thank Professor Sotirios G. Ziavras for spending incalculable effort and time working with me on my research projects. Over the course of our interaction, his devotion and persistence in his research, intelligent and insightful thoughts, and diligent work have been an inspiration.

Thanks to Professor Roberto Rojas-Cessa. I have gotten a lot out of my collaboration with him. Thanks to Professor Edwin Hou for advising me on my TA work for four years. Thanks to Professor Joseph Y. Leung for reading my dissertation and sitting on my committee.

I would like to thank all the member of our CAPPL research group for their friendly assistance and interesting discussions. Thanks to Xiaofang Wang, Hongyan Yang, Mohammad Z. Hasan, Xizhen Xu, and Johnsy K. John.

Thanks to all my friends who have made my life in NJIT so enjoyable and memorable. Thanks to Mr. and Mrs. Huang for helping a lot in my everyday life. Special thanks to Xianhong Feng for all her support and making my life more colorful.

Last but not lest, I like to thank Mom and Dad for their endless love, patience, support and encouragement. Most of all, thank you for sharing this journey and believing in me.

## TABLE OF CONTENTS

| Cł | apte | r      |                                                                  | Page |

|----|------|--------|------------------------------------------------------------------|------|

| 1  | INT  | RODUC  | CTION                                                            | . 1  |

|    | 1.1  | Soft E | rrors                                                            | . 1  |

|    | 1.2  | On-Ch  | nip Caches                                                       | . 3  |

|    | 1.3  | Regist | er Files                                                         | . 5  |

|    | 1.4  | Relate | d Work                                                           | . 6  |

|    |      | 1.4.1  | Reliable Design of On-Chip Caches                                | . 7  |

|    |      | 1.4.2  | Reliable Design of Register Files                                | . 8  |

|    | 1.5  | Contri | bution                                                           | . 9  |

|    |      | 1.5.1  | Cache Lifetime Models for Reliability                            | . 9  |

|    |      | 1.5.2  | Optimizing Schemes to Improve On-Chip Caches Reliability         | . 10 |

|    |      | 1.5.3  | Tag Replication Buffer for Enhancing Cache Tag Array Reliability | . 10 |

|    |      | 1.5.4  | Self-Adaptive Data Caches for Soft-Error Reliability             | . 11 |

|    |      | 1.5.5  | Reliable Register Files with Narrow-With Duplication             | . 11 |

|    | 1.6  | Organ  | ization of the Dissertation                                      | . 11 |

| 2  | EXF  | PERIME | ENTAL SETUP                                                      | . 13 |

|    | 2.1  | Simula | ated Processor                                                   | . 13 |

|    | 2.2  | Bench  | marks                                                            | . 13 |

| 3  | ON-  | CHIP C | CACHE VULNERABILITY ANALYSIS AND OPTIMIZATION .                  | . 16 |

|    | 3.1  | Introd | uction                                                           | . 16 |

|    | 3.2  | Tempo  | oral Vulnerability Factor of the Data Array in Data Caches       | . 19 |

|    |      | 3.2.1  | A General Lifetime Model of the Data Array                       | 19   |

|    |      | 3.2.2  | Temporal Vulnerability Factor (TVF)                              | 21   |

| Cha | apter | •       |                                                             | Page |

|-----|-------|---------|-------------------------------------------------------------|------|

|     |       | 3.2.3   | Data Array Vulnerability Characterization                   | . 22 |

|     |       | 3.2.4   | The Impact of Different Cache Write Policies                | . 26 |

|     |       | 3.2.5   | Clean Cacheline Invalidation (CCI)                          | . 31 |

|     |       | 3.2.6   | Narrow Width Value Compression (NWVC)                       | . 35 |

|     |       | 3.2.7   | The Combined Scheme                                         | . 36 |

|     | 3.3   | Analyz  | zing the Data Array of the Instruction Cache                | . 38 |

|     |       | 3.3.1   | The Lifetime Model                                          | . 38 |

|     |       | 3.3.2   | CCI Scheme for TVF Optimization                             | . 39 |

|     |       | 3.3.3   | Cacheline Scrubbing (CS)                                    | . 41 |

|     |       | 3.3.4   | The Combined (CS-CCI) Scheme                                | . 43 |

|     | 3.4   | TVF C   | Characterization of Tag Arrays                              | . 43 |

|     |       | 3.4.1   | Tag Array of the Data Cache                                 | . 44 |

|     |       | 3.4.2   | Tag Array of the Instruction Cache                          | . 50 |

|     | 3.5   | Summa   | ary                                                         | . 50 |

| 4 ' | TAG   | REPLI   | ICATION BUFFER FOR ENHANCING THE RELIABILITY OF             |      |

|     | THE   | CACH    | E TAG ARRAY                                                 | . 52 |

|     | 4.1   | Introdu | action                                                      | . 52 |

|     | 4.2   | Tag Re  | eplication Buffer (TRB) for Improving Tag Array Reliability | . 53 |

|     |       | 4.2.1   | Basics of the TRB Design                                    | . 53 |

|     |       | 4.2.2   | TRB Design                                                  | . 54 |

| •   | 4.3   | Explor  | ring the Design Space of the TRB                            | . 56 |

|     |       | 4.3.1   | How to Deal With Soft Errors                                | . 56 |

| Chapter | •      |                                                              | Page |

|---------|--------|--------------------------------------------------------------|------|

|         | 4.3.2  | When to Duplicate                                            | . 56 |

|         | 4.3.3  | How to Do the Replacement                                    | . 57 |

|         | 4.3.4  | Replacement Policies in the TB                               | . 57 |

| 4.4     | Optim  | izing the TRB Design                                         | . 58 |

|         | 4.4.1  | Improving the Replacement Policy in the TB: LRU+ and FIFO+ . | . 58 |

|         | 4.4.2  | Tag Value Compression                                        | . 58 |

|         | 4.4.3  | Selective TRB                                                | . 61 |

|         | 4.4.4  | Performance Impact                                           | . 61 |

| 4.5     | TVF A  | Analysis of Tag Arrays                                       | . 62 |

|         | 4.5.1  | Lifetime of Tag Arrays                                       | . 62 |

|         | 4.5.2  | Detected withOut Replica (DOR) TVF                           | . 62 |

|         | 4.5.3  | AWR v.s. DOR-TVF                                             | . 63 |

|         | 4.5.4  | Early Write-Back Triggered by TB Entry Replacement           | . 63 |

| 4.6     | Evalua | ation                                                        | . 64 |

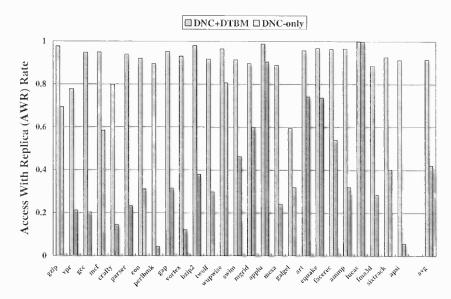

|         | 4.6.1  | TB Duplication Policies: DNC-Only v.s. DNC+DTBM              | . 64 |

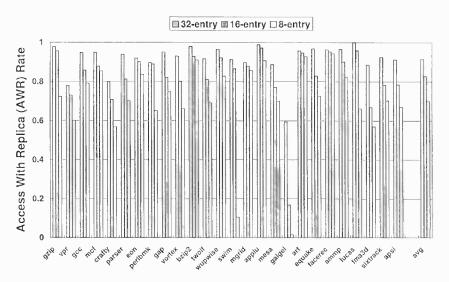

|         | 4.6.2  | TB Sizes                                                     | . 65 |

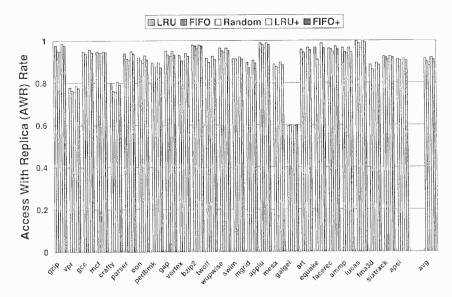

|         | 4.6.3  | TB Replacement Policies                                      | . 65 |

|         | 4.6.4  | Comparison to Related Work                                   | . 65 |

|         | 4.6.5  | TRB Optimization Schemes                                     | . 68 |

|         | 4.6.6  | Tag Array TVF Analysis                                       | . 70 |

|         | 4.6.7  | TRB with Early Write-Back (EWB)                              | . 70 |

| 4.7     | Summ   | nary                                                         | . 73 |

| Cl | apte | r       |                                                          | Page |

|----|------|---------|----------------------------------------------------------|------|

| 5  | SEL  | F-ADA   | PTIVE DATA CACHES                                        | . 74 |

|    | 5.1  | Introd  | uction                                                   | . 74 |

|    | 5.2  | Error I | Model and Soft Error Injection                           | . 75 |

|    | 5.3  | Reliab  | le Data Caches Built upon Byte-Level Parity Coding       | . 76 |

|    |      | 5.3.1   | Limits of Conventional Reliable Data Caches              | . 76 |

|    |      | 5.3.2   | Computing the Architectural Vulnerability Factors (AVFs) | . 81 |

|    | 5.4  | The Se  | elf-Adaptive Reliable Data Cache                         | . 82 |

|    |      | 5.4.1   | Why Self-Adaptive Scheme?                                | . 82 |

|    |      | 5.4.2   | A Soft-Error Monitoring Mechanism                        | . 83 |

|    |      | 5.4.3   | Control of Self Adaptation                               | . 83 |

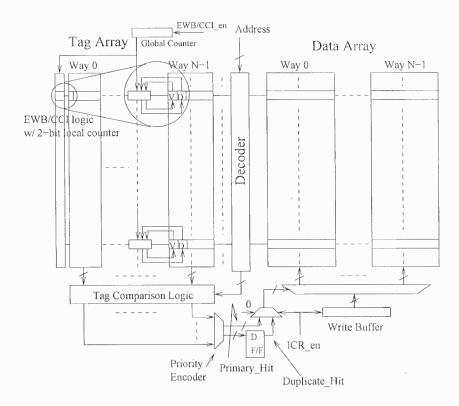

|    |      | 5.4.4   | Microarchitecture of the SA-RDC                          | . 84 |

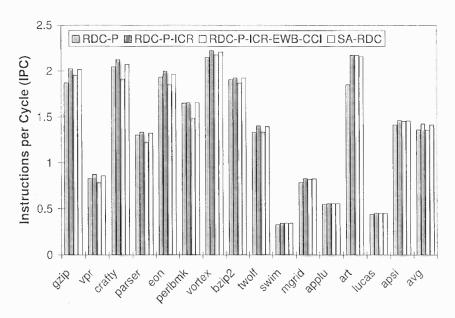

|    |      | 5.4.5   | Evaluation of the SA-RDC Scheme                          | . 85 |

|    | 5.5  | Limita  | ations of this study                                     | . 89 |

|    | 5.6  | Summ    | nary                                                     | . 89 |

| 6  | IN-F | REGIST  | ER DUPLICATION FOR ENHANCING REGISTER FILE RELI-         |      |

|    | ABI  | LITY    |                                                          | . 90 |

|    | 6.1  | Introd  | uction                                                   | . 90 |

|    | 6.2  | Basics  | s of Register Renaming in Superscalar Microprocessors    | . 91 |

|    |      | 6.2.1   | Register Renaming                                        | . 91 |

|    |      | 6.2.2   | Register File Utilization and Performance Sensitivity    | . 92 |

|    | 6.3  | Narro   | w-Width Register Values                                  | . 94 |

|    | 6.4  | Explo   | iting Narrow-Width Register Values                       | . 94 |

|    |      | 6.4.1   | Narrow-Width Value Detection                             | . 95 |

| Ch | apter | •      |                                                        | Page  |

|----|-------|--------|--------------------------------------------------------|-------|

|    |       | 6.4.2  | Exploiting In-Register Duplication for Error Detection | . 97  |

|    |       | 6.4.3  | Integrating In-Register Duplication and Parity Coding  | . 98  |

|    |       | 6.4.4  | Protecting Regular Values                              | . 100 |

|    | 6.5   | New M  | Models for Register File AVF Estimation                | . 101 |

|    | 6.6   | Evalua | tion                                                   | . 104 |

|    |       | 6.6.1  | Duplication Rates and Performance Impact               | . 104 |

|    |       | 6.6.2  | Power Efficiency of the IRD Register File              | . 105 |

|    |       | 6.6.3  | Register File AVF Estimation                           | . 107 |

|    |       | 6.6.4  | Error Model and Soft Error Injection                   | . 108 |

|    |       | 6.6.5  | Error Behavior under Soft Error Injection              | . 110 |

|    |       | 6.6.6  | Error Detection and Recovery from Detected Soft Errors | . 112 |

|    | 6.7   | Summ   | ary                                                    | . 114 |

| 7  | CON   | NCLUS] | IONS AND FUTURE WORK                                   | . 115 |

|    | 7.1   | Conclu | usions                                                 | . 115 |

|    | 7.2   | Future | : Work                                                 | . 117 |

| RI | EFER) | ENCES  |                                                        | . 119 |

## LIST OF TABLES

| Tabl | e                                                                           | Pa |     |  |

|------|-----------------------------------------------------------------------------|----|-----|--|

| 2.1  | Parameters for the simulated microprocessor in Chapter 3 and 5              |    | 14  |  |

| 2.2  | The Modified Processor Core in Chapter 6                                    |    | 14  |  |

| 2.3  | SPEC CPU2000 benchmark suite                                                | •  | 15  |  |

| 3.1  | The comparison of vulnerability characterization at different granularities |    | 26  |  |

| 3.2  | Overhead of the combined scheme                                             |    | 38  |  |

| 3.3  | Summary of targeting vulnerable phases of all proposed schemes              |    | 50  |  |

| 3.4  | Comparison of all proposed schemes                                          |    | 51  |  |

| 4.1  | The Comparison of the ECC, CAT, FD, and TRB schemes                         |    | 67  |  |

| 6.1  | A characterization of erroneous reads for input operands                    |    | 111 |  |

| Figu | re                                                                                                             | Page |

|------|----------------------------------------------------------------------------------------------------------------|------|

| 1.1  | Soft error generation by a cosmic ray                                                                          | 2    |

| 1.2  | Levels of a typical memory hierarchy in the modern computer system                                             | 4    |

| 1.3  | Address format for the cache access                                                                            | 4    |

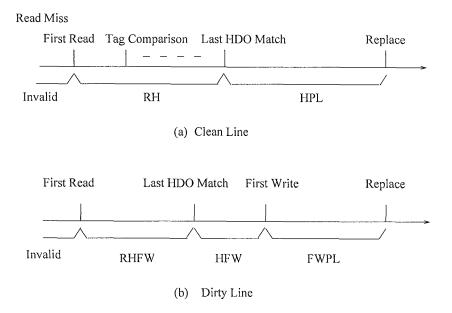

| 3.1  | The lifetime of a cacheline with respect to various access activities                                          | 21   |

| 3.2  | The lifetime distribution of the data array in the data cache with the 64-byte cacheline                       | 23   |

| 3.3  | The lifetime distribution of the data array in the data cache with the 32-byte cacheline                       | 23   |

| 3.4  | The lifetime distribution of the data array in the data cache with the 16-byte cacheline                       | 24   |

| 3.5  | A scenario of cache accesses and error occurrences that contribute RW or WW to vulnerable phases.              | 25   |

| 3.6  | The lifetime distribution of the data array in the data cache for the fine granularity data item (64-bit word) | 27   |

| 3.7  | The lifetime distribution of the data array in the data cache for the fine granularity data item (8-bit byte)  | 27   |

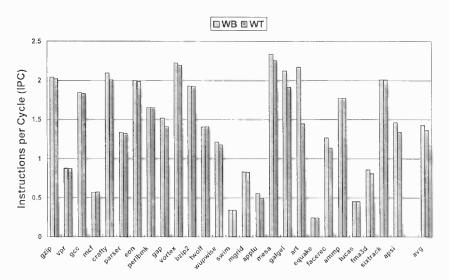

| 3.8  | The comparison of IPCs between writethrough and writeback caches                                               | 29   |

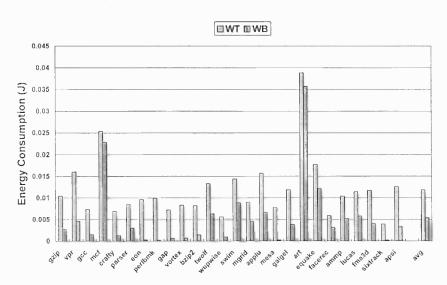

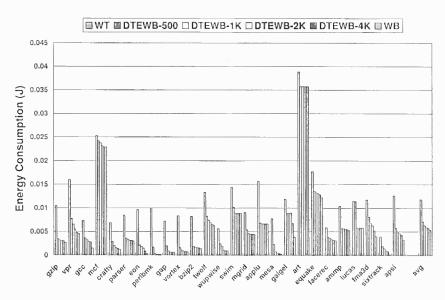

| 3.9  | The comparison of dynamic energy consumption in the L2 cache for writethrough and writeback data caches        |      |

| 3.10 | The energy savings in cache writeback when applying the MDB scheme at various granularities                    | 30   |

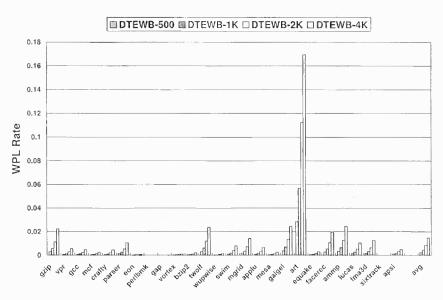

| 3.11 | The comparison of dynamic energy consumption in the L2 cache at different dead times                           | 32   |

| 3.12 | The comparison of WPL rates at different dead times                                                            | 32   |

| Figui | re                                                                                                                                                                                                                                                                 | Pa | age |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|

| 3.13  | Cumulative distribution of the time intervals between two reads (RR) in clean cachelines.                                                                                                                                                                          |    | 33  |

| 3.14  | The IPC comparison of different invalidation intervals                                                                                                                                                                                                             |    | 33  |

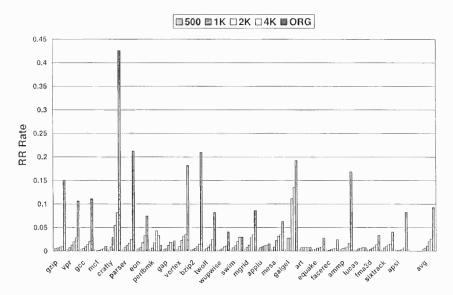

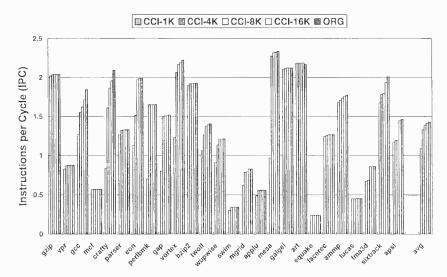

| 3.15  | (The RR phase comparison of different invalidation intervals. (ORG is the conventional data cache without the invalidation scheme.)                                                                                                                                |    | 34  |

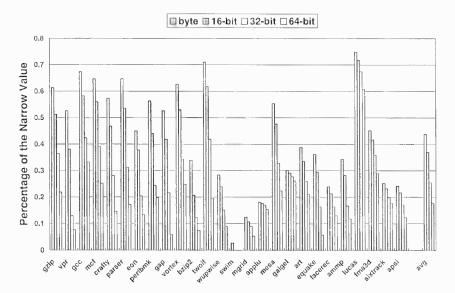

| 3.16  | The percentage of narrow width values in active cachelines at different granularities.                                                                                                                                                                             | •  | 36  |

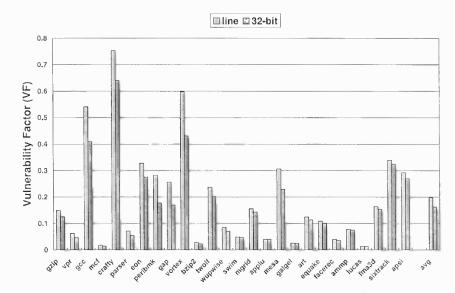

| 3.17  | The comparison between the data cache employing the combined scheme and the conventional data cache for the temporal vulnerability factor (TVF). $\dots$                                                                                                           |    | 37  |

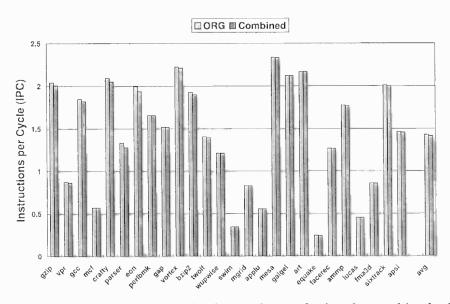

| 3.18  | The comparison between the data cache employing the combined scheme and the conventional data cache for the performance (IPC) impact                                                                                                                               |    | 37  |

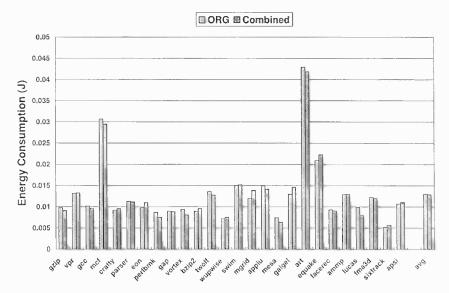

| 3.19  | The comparison between the data cache employing the combined scheme and the conventional data cache for the energy consumption in L1 data cache and the L2 cache.                                                                                                  |    | 38  |

| 3.20  | The temporal vulnerability factor of the data array in the instruction cache at different granularities of a cacheline or 32-bit data                                                                                                                              |    | 39  |

| 3.21  | The IPC comparison at different invalidation intervals while applying the CCI scheme to the instruction cache. (ORG is the conventional instruction cache without CCI.)                                                                                            |    | 40  |

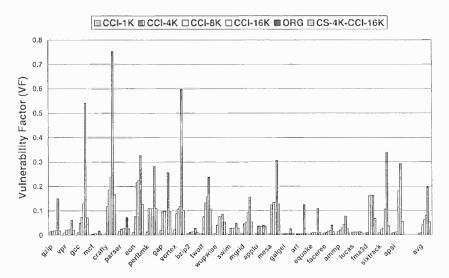

| 3.22  | The TVF comparison at different invalidation intervals while applying the CCI scheme to the instruction cache. (ORG is the conventional instruction cache without CCI. CS-4K-CCI-16K is the combined scheme with 4K-cycle CS interval and 16K-cycle CCI interval.) |    | 40  |

|       |                                                                                                                                                                                                                                                                    |    | -   |

| F | igu  | re Pa                                                                                                                                                                                                                                                                        | age |

|---|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

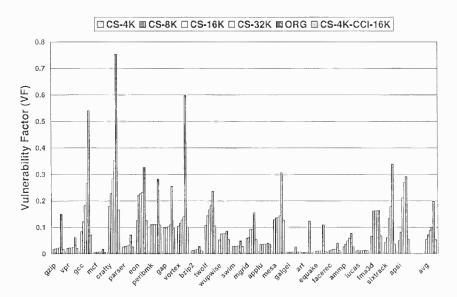

| 3 | 3.23 | The TVF comparison at different scrubbing intervals at different scrubbing intervals. (ORG is the conventional instruction cache without scrubbing. CS4K-CCI-16K is the combined scheme with 4K-cycle CS interval and 16K-cycle CCI interval.)                               | 42  |

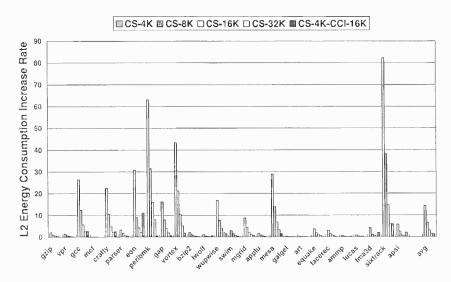

| 3 | 3.24 | The comparison of the energy consumption increase rate (x times) in the L2 cache at different scrubbing intervals. (ORG is the conventional instruction cache without scrubbing. CS-4K-CCI-16K is the combined scheme with 4K-cycle CS interval and 16K-cycle CCI interval.) | 42  |

| 3 | 3.25 | The tag lifetime of a cacheline in the writeback cache                                                                                                                                                                                                                       | 46  |

| 3 | 3.26 | The lifetime distribution for the tag array in the writeback data cache at entry level                                                                                                                                                                                       | 47  |

| 3 | 3.27 | The lifetime distribution for the tag array in the writeback data cache at bit level.                                                                                                                                                                                        | 47  |

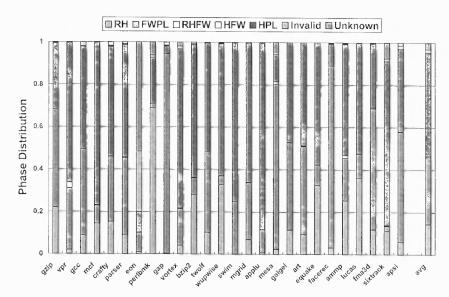

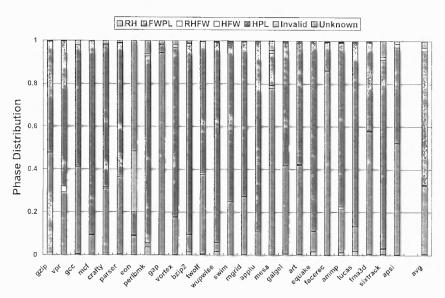

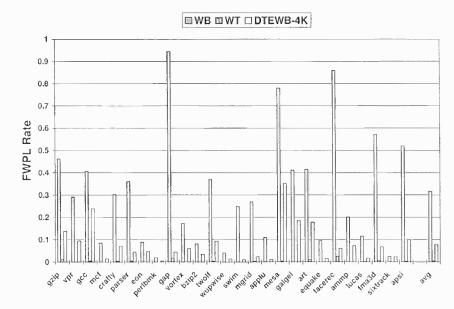

| 3 | 3.28 | The FWPL rate comparison for the tag array in writeback (WB), writethrough (WT), and DTEWB caches.                                                                                                                                                                           | 48  |

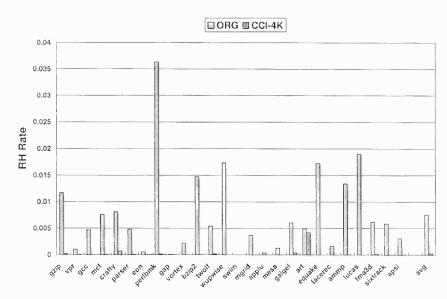

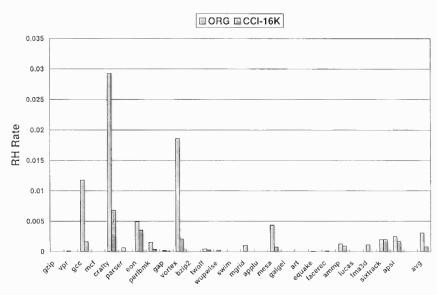

| 3 | 3.29 | The RH rate comparison between the original and CCI schemes in the data cache.                                                                                                                                                                                               | 49  |

| 3 | 3.30 | The RH rate comparison between the original and CCI schemes for the tag array in the instruction cache                                                                                                                                                                       | 49  |

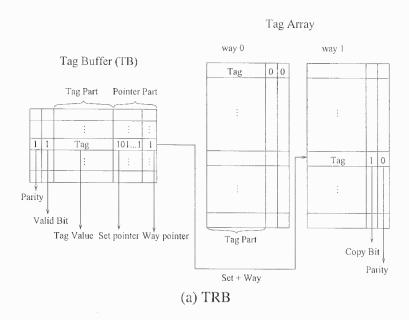

| 2 | 4.1  | The block diagrams of the TRB and modified CAT designs                                                                                                                                                                                                                       | 55  |

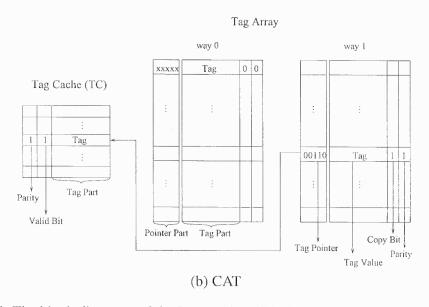

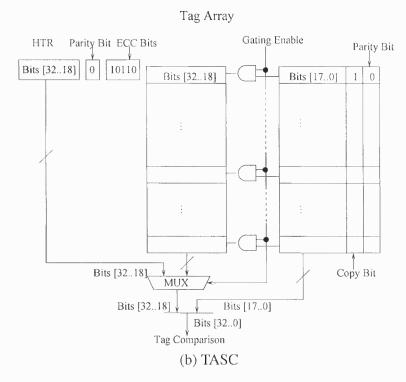

| 4 | 1.2  | The block diagrams of TBSC and TASC designs                                                                                                                                                                                                                                  | 59  |

| 4 | 4.3  | The AWR rate comparison of the TRB with different duplication policies                                                                                                                                                                                                       | 66  |

| 2 | 4.4  | The AWR rate comparison of the TRB with different TB sizes                                                                                                                                                                                                                   | 66  |

| 2 | 4.5  | The AWR rate comparison of the TRB with different TB replacement policies.                                                                                                                                                                                                   | 69  |

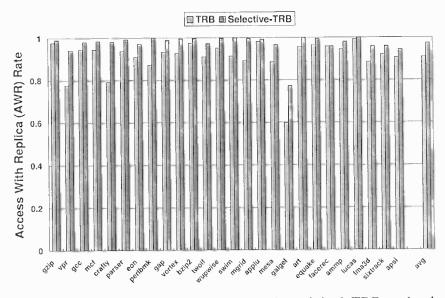

| 2 | 4.6  | The AWR rate comparison between the original TRB and selective-TRB schemes.                                                                                                                                                                                                  | 69  |

| Figu | re                                                                                                                                                                    | Pa | ige |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|

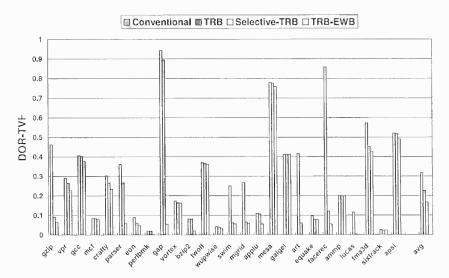

| 4.7  | The DOR-TVF comparison for the parity-protected tags of the cachelines with write operations among conventional, original TRB, selective-TRB, and TRB-EWB data caches |    | 71  |

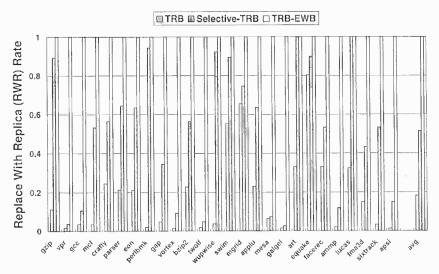

| 4.8  | The replace-with-replica (RWR) rate of the original TRB, selective-TRB, and TRB-EWB schemes.                                                                          |    | 71  |

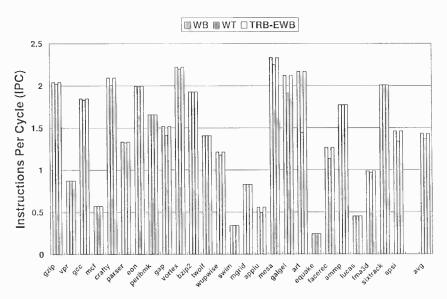

| 4.9  | The comparison of performance among conventional write-back (WB), write-through (WT), and TRB-EWB data caches.                                                        |    | 72  |

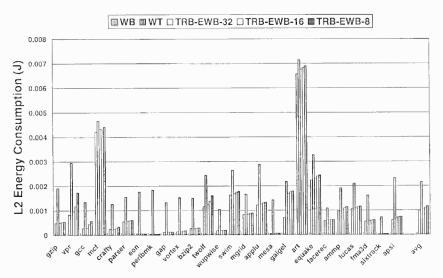

| 4.10 | The comparison of L2 cache energy consumption among conventional write-back (WB), write-through (WT), and TRB-EWB data caches                                         | •  | 72  |

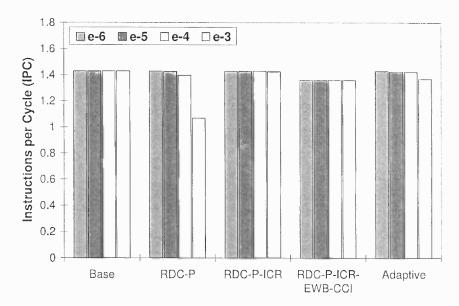

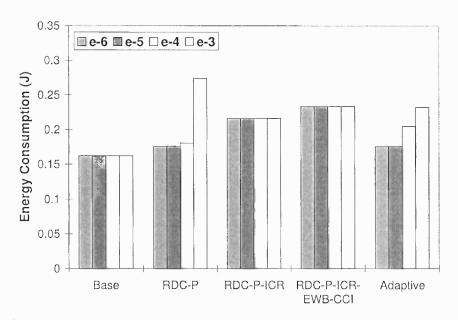

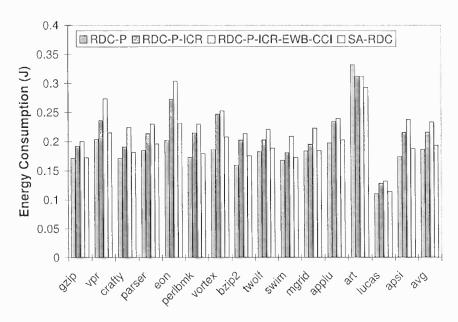

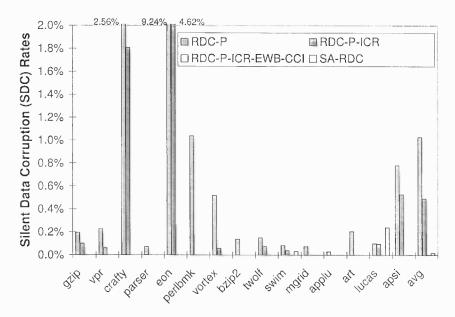

| 5.1  | The performance comparison between the SA-RDC and fixed RDC schemes under error injection                                                                             |    | 77  |

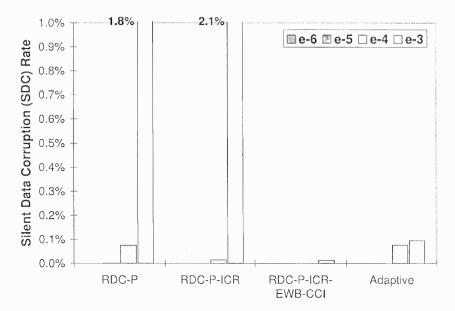

| 5.2  | The Energy consumption comparison between the SA-RDC and fixed RDC schemes under error injection                                                                      | •  | 77  |

| 5.3  | The SDC rate comparison between the SA-RDC and fixed RDC schemes under error injection.                                                                               |    | 78  |

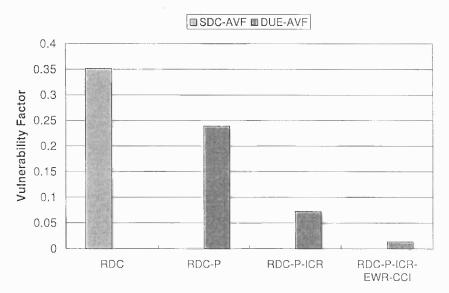

| 5.4  | AVF comparison for different data caches                                                                                                                              |    | 82  |

| 5.5  | The microarchitectural schematic of the proposed SA-RDC                                                                                                               |    | 86  |

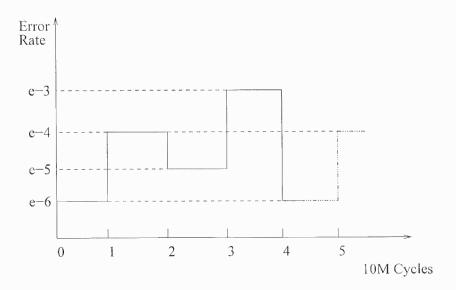

| 5.6  | Soft error rate profile to simulate the changing error rate                                                                                                           |    | 86  |

| 5.7  | The performance comparison between the SA-RDC and fixed RDC schemes.                                                                                                  |    | 87  |

| 5.8  | The energy consumption comparison between the SA-RDC and fixed RDC schemes.                                                                                           |    | 87  |

| 5.9  | The SDC rate comparison between the SA-RDC and fixed RDC schemes                                                                                                      |    | 88  |

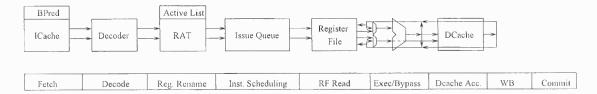

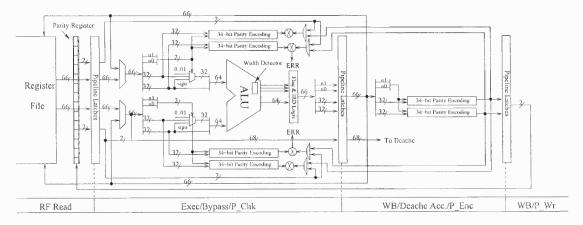

| 6.1  | Datapath and the pipeline stages of the simulated superscalar microprocessor.                                                                                         |    | 91  |

| Figu | re                                                                                                                                                                                          | Page  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

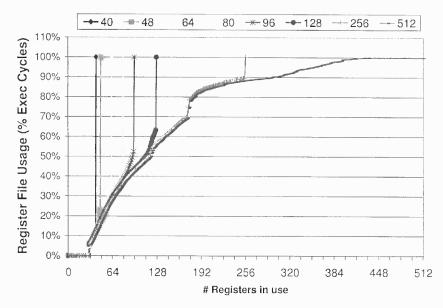

| 6.2  | A cumulative distribution of register file utilization for different sizes of register files                                                                                                | . 93  |

| 6.3  | Performance sensitivity to the register file size                                                                                                                                           | . 93  |

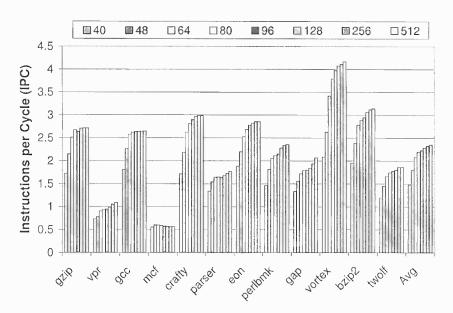

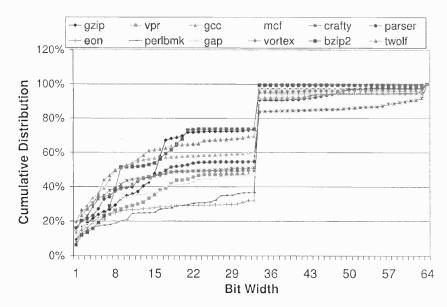

| 6.4  | Cumulative distribution of the Register value width                                                                                                                                         | . 95  |

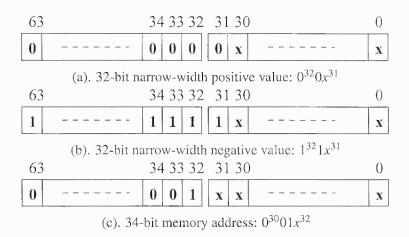

| 6.5  | Bit patterns for three types of narrow-width values considered: (a). 32-bit positive value, (b). 32-bit negative value, and (c). 34-bit memory address. An "x" bit can be either "1" or "0" | . 95  |

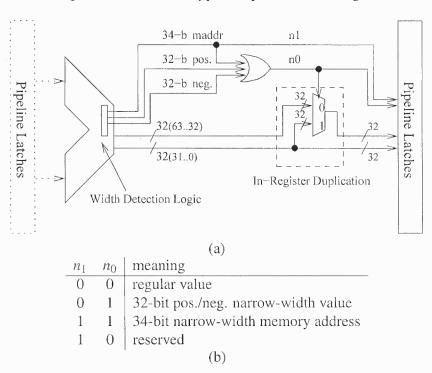

| 6.6  | (a) Augmented functional unit datapath with narrow-width flag generation and in-register duplication logic. (b) The meaning of the value of narrowness flag bits $n_1n_0$                   | . 96  |

| 6.7  | The augmented datapath integrating in-register duplication and parity coding to support both error detection and error recovery                                                             | . 98  |

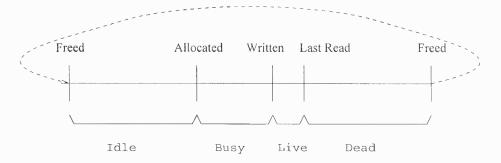

| 6.8  | The lifetime model of a physical register                                                                                                                                                   | . 102 |

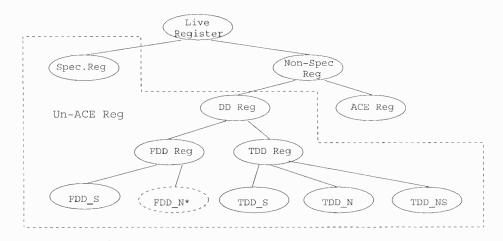

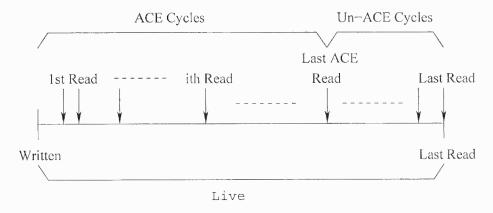

| 6.9  | Register level ACE analysis and register value classification for Live registers. (DD: dynamically dead, FDD: first-level dynamically dead, TDD: transitively dynamically dead)             | . 103 |

| 6.10 | Extracting un-ACE cycles from the Live phase of an ACE register                                                                                                                             | . 103 |

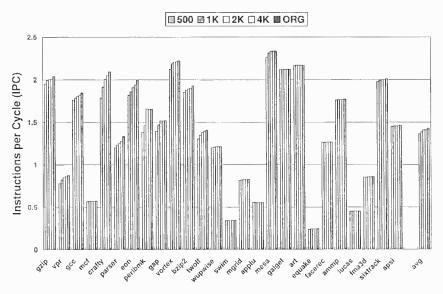

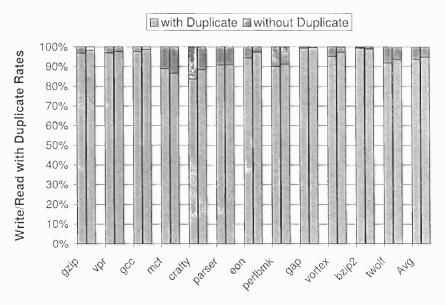

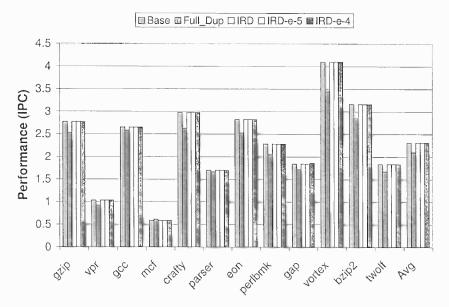

| 6.11 | Write-with-duplicate rate (left bar) and read-with-duplicate rate (right bar) of the in-register duplication scheme.                                                                        |       |

| 6.12 | Performance comparison of various register file schemes                                                                                                                                     | . 106 |

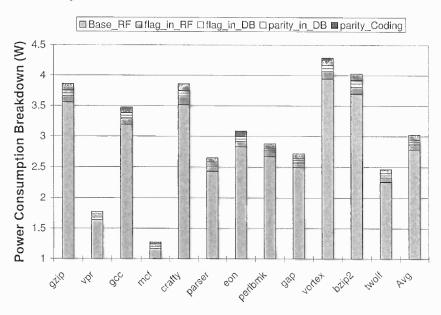

| 6.13 | A breakdown of the power consumption in the IRD register file                                                                                                                               | . 107 |

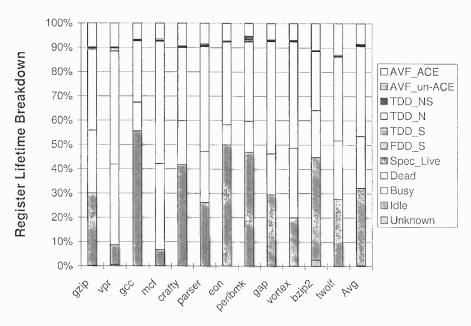

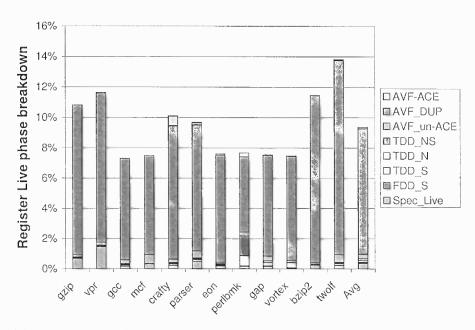

| 6.14 | Register lifetime breakdown for AVF measurement in a base register file, a zoom-in view of its Live phase breakdown                                                                         | . 109 |

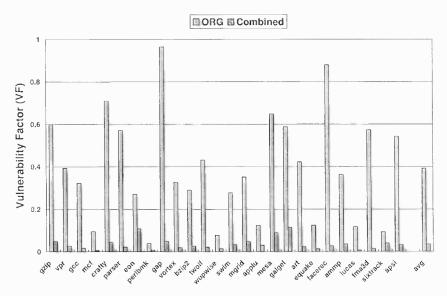

| 6.15 | Register lifetime breakdown for AVF measurement in the IRD register file, a zoom-in view of its Live phase breakdown.                                                                       | . 109 |

| Figu | re                                                                                                                                                             | Page |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

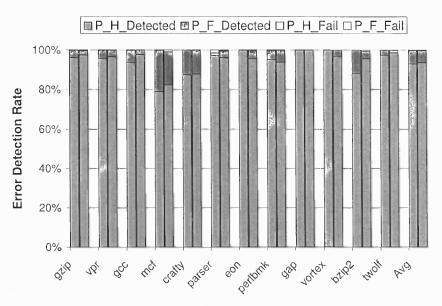

| 6.16 | Soft error detection in the IRD scheme by parity checking. (Left bar for e-5 and right bar for e-4)                                                            |      |

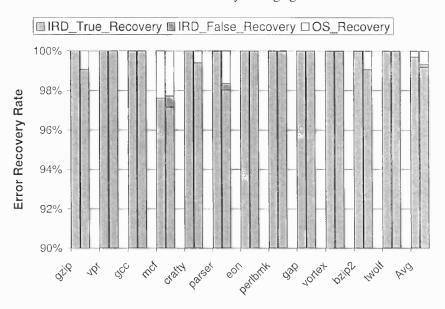

| 6.17 | Error recovery rate of detected errors in IRD scheme, under error injection rates of $10^{-5}$ (left bar) and $10^{-4}$ (right bar) per selected bit per cycle |      |

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 Soft Errors

System failures are caused mainly by two types of faults: hardware faults and software faults. Software faults are design faults that are closely related to human factors and the design process. In contrast, hardware faults are dominated by physical faults. Given the fault occurrence pattern during system operation, hardware faults can be divided into permanent faults and temporary faults. Permanent faults originate from incorrect designs, manufacturing defects, device wearout, etc. Temporary faults can be further classified into two groups with different origins: transient and intermittent. Intermittent faults are mainly due to operation margin problems, weak parts, process variation, random dopant fluctuation, etc. Different from other faults, transient faults (soft errors) in electronic systems are caused by external interferences such as energetic particles from radioactive impurities and cosmic rays, electrical noise, electromagnetic interference, etc. Many permanent faults can be avoided by thorough validation, testing, and early life failure screening. Modular redundancy is also commonly employed for highly reliable systems design. Due to the transient/random nature, transient faults cannot be captured by traditional verification and testing process due to the irrelevancy to the correctness of the logic. On the other hand, the high expense of applying techniques such as hardware triple modular redundancy (TMR) or N-modular redundancy (NMR) for addressing soft errors might not be acceptable to commercial computer systems in most market segments. As the electrical noise and electromagnetic interference can be effectively addressed in a satisfactory manner by shielding and sound designs, energetic particle induced soft errors present tremendous challenges in systems design[1][2][3].

With continuous technology scaling down, on-chip memory structures, such as on-

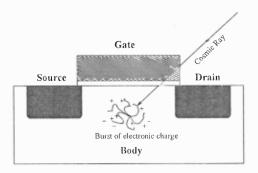

chip *Caches* and *Register Files*, suffer from a significantly higher Soft Error Rate (SER) than on-chip combinational logic at the current and near future technologies, due to their large share of the transistor budget and die area [4]. In SRAM cells, an upset event caused by the soft errors can charge or discharge a particular node to incur a bit flip. Figure 1.1 shows the schematic of soft error generation by a cosmic ray [1]. However, this single upset event (SUE) doses not damage the circuit. A method to estimate the SER in CMOS circuits was developed in [5]. The following equations summarize this model:

$$SER = NF \times CS$$

$$CS \propto A_{Drain} \times exp(-\frac{Q_{Critical}}{Q_S})$$

(1.1)

where NF is the intensity of the Neutron Flux, CS is the atmospheric neutron Cross Section,  $Q_{Critical}$  is the Critical Charge of a particular node,  $Q_S$  is the Collection Slope, and  $A_{Drain}$  is the Drain Area. If a collected charge Q caused by a particle strike exceeds critical charge  $Q_{Critical}$  of a circuit node, it results in a bit flip in that node and a soft error occurs.  $Q_S$  depends on the doping and the supply voltage  $V_{CC}$ .  $Q_{Critical}$  is proportional to the node capacitance and the  $V_{CC}$ . According to this model, at device/circuit level, the soft error rate can be reduced by hardening the CMOS transistors either increasing  $Q_{Critical}$ , reducing  $Q_S$ , or reducing  $A_{Drain}$  [6][7][8][9][10]. However, due to their inability to exploit architectural

Figure 1.1 Soft error generation by a cosmic ray.

or application specific features, circuit level techniques are increasingly recognized as non-cost-effective over-designs. In contrast, this dissertation is targeting at microarchitecture-level designs and analysis of reliable on-chip memory structures against soft errors.

## 1.2 On-Chip Caches

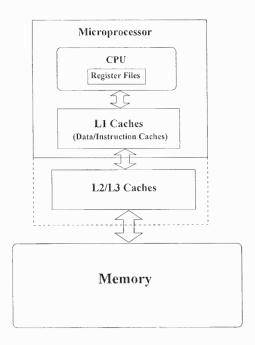

To bridge the speed gap between the fast CPU and the main memory, today's microprocessors adopt the memory hierarchy design by exploiting the principle of locality [11]. Figure 1.2 shows the levels of a typical memory hierarchy in the modern computer system. Basically, there are two types of L1 caches, data cache and instruction cache. The data cache contains the data that programs need and can support the read and write operations. The instruction cache is a read-only memory structure that stores the instructions of programs. The L2/L3 caches can be either on-chip or off-chip caches [11]. This dissertation focuses on the reliability design of the on-chip L1 data/instruction caches.

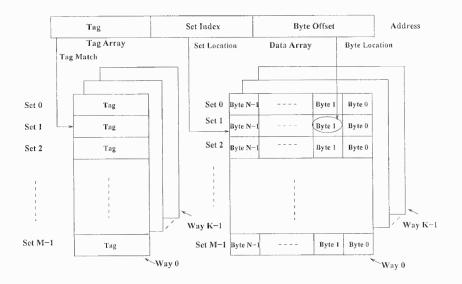

Each cache contains two main components, the data array and tag array. The data information is stored in the data array. The tag array stores the tag information to determine cache hit or miss during cache accesses. Figure 1.3 shows how an address is formatted to locate a certain byte in the cache. In a cache access, Set Index locates the set and Byte Offset selects the corresponding byte from that set. Tag field of the address are compared with the tag of the selected set stored in the tag array. If the result is a match, the cache hits. Otherwise, the cache misses. The number of bits in each address field are summarized in Equation 1.2, where  $Bit_{BO}$  is the number of bits in the Byte Offset field,  $Bit_{SI}$  is the number of bits in the Set Index field,  $Bit_{Tag}$  is the number of bits in the Tag field,  $Bit_{Addr}$  is the number of bits of the entire address, N is the number of bytes in each set, and M is the number of sets in the cache.

Figure 1.2 Levels of a typical memory hierarchy in the modern computer system.

Figure 1.3 Address format for the cache access.

$$Bit_{BO} = \log_2 N$$

$Bit_{SI} = \log_2 M$

$Bit_{Tag} = Bit_{Addr} - Bit_{BO} - Bit_{SI}$  (1.2)

When the L1 data cache is updated by the CPU, the corresponding data in the lower memory hierarchy (L2/L3 caches and main memory) also need to be updated. The *write policy* controls the time of the update. In a *write-through* cache, every write to the cache causes a write to the lower memory hierarchy. In a *write-back cache*, writes are not immediately mirrored to the lower levels. Instead, the cache marks these updated cachelines as dirty. Data in these dirty cachelines are written to the lower levels when these cachelines are evicted from the cache.

## 1.3 Register Files

Superscalar microprocessors dynamically exploit instruction-level parallelism (ILP) to issue multiple instructions per cycle for improved performance. Register renaming is one of the fundamental techniques employed in superscalar microprocessors to increase the ILP by eliminating the two false data dependences, write-after-read (WAR) and write-after-write (WAW) [11]. Microprocessors supporting register renaming present two views of the register files, the architectural/logical register file that is visible to the compiler/programmer, and the physical register file that is managed by the register renaming mechanism. From the implementation point of view, the architectural and physical register files can be either two separately hardware-implemented register files or just one combined register file. In the separate register files implementation, once the instruction is committed, the result value in the physical register needs to be copied to its architectural register. In the combined implementation, no explicit data copy or movement is required when instructions

are committed. The mapping of the architectural registers is dynamically changing in the combined architectural/physical register file implementation.

In the register renaming stage, the logical register ids of the source operands in a decoded instruction are used to access the register alias table (RAT), a.k.a. register mapping table. The table entry indexed by the logical register id contains the physical register id that the source register was renamed to. For the destination register, a free physical register is allocated from the register free list and the RAT is updated as follows: the old physical register id is read out from the RAT and stored in the active list entry allocated to the instruction, and then the new physical register id is written to the same RAT entry indexed by the logical destination register id. The destination register is said to have been remapped to the new physical register and the old physical register is said to have been unmapped. In case the register free list is empty, the renaming stage is stalled till some physical register is freed [12]. Notice that a physical register cannot be freed until an instruction that previously unmapped this physical register is committed. Furthermore, a physical register is susceptible to soft errors only after a value is written into the register and before it is freed.

#### 1.4 Related Work

Fault-tolerant designs based on modular redundancy have been widely used to build highly reliable systems [13]. For example, cycle-by-cycle lockstepping of dual-processors and comparison of their outputs are employed for error detection in Compaq Himalaya [14] and IBM z900 [15] with G5 processors. Other designs use asymmetric redundancy to include a watch-dog processor [16] or a low-performance checker processor in DIVA [17] to verify the correctness of the execution on the main processor.

Targeting the increasing processor vulnerability to soft errors at new technologies, temporal redundancy based reliable schemes exploiting simultaneous multithreading (SMT) architectures have been extensively studied for both single processors and chipmultiprocessors, such as AR-SMT [18], SRT [19][20], SRTR [21], and Slipstream [22].

Lately, many research efforts have been spent on exploiting the redundant resources in superscalar processors for instruction-level redundant execution against transient faults. In [23], each instruction is executed twice and the results from duplicate execution are compared to verify the absence of transient errors in functional units. However, each instruction only occupies a single re-order buffer (ROB) entry. On the other hand, the dual-instruction execution scheme (DIE) in [24] physically duplicates each decoded instruction to provide a *Sphere of Replication* including the instruction issue queue/ROB, functional units, physical register files, and the interconnection among them. Due to the substantially increased pressure on the hardware resources, dual-instruction execution in general suffers from significant performance loss. Follow-up work such as DIE-IRB [25], SHREC [26], and PER-IRTR [27], try to alleviate the resource contention in DIE processors in order to recover the performance loss.

### 1.4.1 Reliable Design of On-Chip Caches

Most of the above techniques protecting the datapath within a single processor are quite independent of the memory hierarchy, where the on-chip caches and external memories are assumed to be error-free by means of some error protection schemes.

Information redundancy is fundamental in building reliable memory structures. Various coding schemes are used to protect information integrity in latches, register files, and on-chip caches, providing different levels of reliability at different performance, energy, and hardware costs. For example, simple parity coding is capable of detecting the odd number of bit errors but is not able to recover from detected errors. On the other hand, error correcting codes (ECCs) typically provide single error correction and double error detection (SEC-DED). However, the performance overhead and additional energy consumption due to ECC encoding/decoding make ECC a reluctant choice for high speed on-chip caches, i.e., L1 data and instruction caches [28]. Another form of information redundancy is to maintain redundant copies of the data in cache memories [29][30]. In these schemes,

cachelines are duplicated when they are brought to L1 caches on read/write misses or on write operations. During a cache write (store), the replicas should be also updated with the latest value. On a cache read (load) operation, multiple copies may need to be read out and compared against each other to verify the absence of soft errors or to perform majority voting. Notice that maintaining redundant copies of cachelines presents great challenges to the bandwidth and power dissipation of the caches [28][30].

For the reliable tag array design, a fault behavior of the CAM (content address-able memory) tags has been studied and single-error tolerant solutions were provided in [31]. A functional level framework was also proposed in [32] for implementing a fault-tolerant/self-checking CAM architecture, with a focus on CAM cell designs. Compared to their hardware circuit solutions, this work focuses on the microarchitecture design of the reliable cache. Biswas et al. [33] presented some initial efforts on vulnerability analysis of the tag array. However, they did not provide any direct reliability optimization schemes on the tag array. In [34], a caching address tag (CAT) scheme was proposed to reduce the area cost of the on-chip caches. Due to the CAM implementation of the pointer part in the tag side, their scheme will incur extremely high energy consumption caused by the CAM search operation if it is adopted for reliability improvement.

#### 1.4.2 Reliable Design of Register Files

Previous work [35] has exploited utilizing free registers or predicted dead registers to maintain a replica of the value in the register file to increase its error resilience. Recent work [36] studied the trade-offs between performance and reliability of the register file when overclocking is applied to increase the operation frequency. In [37], compiler-guided techniques were proposed to improve the register file reliability by changing the instruction scheduling and register assignment. Recent work [38] studied a register replication approach by selectively copying register values to the unused physical registers for enhancing reliability. Work [39] proposed to selectively protect registers by generating, storing, and checking the

ECCs of only the most vulnerable registers with useful data, while parity coding is used for all the registers. Different from their work, the proposed in-register duplication scheme is based on the detection and capture of narrow-width register values such that redundant copies are generated within a single 64-bit data item to improve the reliability of the register file system, eliminating the need for copy registers and related hardware enhancements.

#### 1.5 Contribution

The contributions of this dissertation consist of four parts: (1) cache lifetime models to characterize the vulnerability of the on-chip caches, (2) optimizing schemes to improve the on-chip caches reliability, (3) the tag replication buffer for enhancing cache tag array reliability, (4) self-adaptive data caches for soft-error reliability, and (4) reliable register files with narrow-with duplication.

#### 1.5.1 Cache Lifetime Models for Reliability

In this dissertation, detailed lifetime models are developed for L1 data and instruction caches to capture all possible activities of all data items. A data item under consideration can be at different granularities such as cacheline, sub-block, word, half word, byte, or even bit. The new lifetime models distinguishes among different lifetime phases for each data item according to the previous activity and the current one, and further categorizes them into two groups, *vulnerable* and *non-vulnerable* phases. A vulnerable phase is characterized by the fact that any error occurring during this phase has the potential to propagate either to the CPU (by load operations) or to the L2 cache (via a dirty line writeback). The cache temporal vulnerability factor (TVF) is defined as the percentage of data items present in vulnerable phases over all possible data items that the cache can hold, an average along the time axis. Therefore, the lifetime vulnerability factor indicates how reliable the cache is. A smaller value of TVF implies that the cache is more resilient to soft errors.

### 1.5.2 Optimizing Schemes to Improve On-Chip Caches Reliability

Based on the fact that the WPL (lifetime phase between the last write and the replacement without any read in between) vulnerable phase contributes the most to TVF in the data cache, the multiple-dirty-bits (MDB) scheme is proposed to reduce the WPL vulnerable phase as well as the energy consumption during the writeback. To further reduce the the second largest vulnerable phase, RR (lifetime phase between two consecutive reads of a clean data item), a clean cacheline invalidation (CCI) scheme is proposed. A combined scheme that incorporates the previous DTEWB (Dead Time based Early Write Back) [40][41] and NWVC (Narrow Width Value Compression) [42][43] schemes are proposed to reduce the overall TVF of the data cache. For the instruction cache, a variation of the cacheline scrubbing (CS) with CCI is proposed to achieve a lower TVF with the minimized performance and energy overheads.

### 1.5.3 Tag Replication Buffer for Enhancing Cache Tag Array Reliability

Exploiting the address locality of memory accesses, this dissertation proposes a Tag Replication Buffer (TRB), a small buffer that captures and maintains the replicas of frequently accessed tag entries, to enhance the reliability of the tag array in the on-chip data cache. A detailed design space exploration is performed for the TRB implementation and several optimized schemes are proposed to improve the tag array reliability as well as to reduce the area and energy overheads of the TRB. To further improve the protection effectiveness and the provided reliability of the TRB, a selective TRB scheme that only duplicates tag entries for dirty cachelines is proposed. In order to provide a comprehensive evaluation on the reliability of the cache tag array, the dissertation conducts a cache tag vulnerability factor analysis and propose a refined cache tag reliability evaluation metric DOR (detected without replica) TVF that combines the TVF and access-with-replica (AWR) analysis. Based on the DOR-TVF analysis, a new TRB scheme with early write-back (TRB-EWB) triggered by the TB (tag buffer) replacement is proposed, which can achieve a 100% AWR

rate and a zero DOR-TVF with a minimum performance and energy overhead.

## 1.5.4 Self-Adaptive Data Caches for Soft-Error Reliability

For the systems working in the changing operating environments, a self-adaptive reliable data cache is proposed to dynamically adapt its employed reliability schemes to maintain a target reliability. This self-adaptive data cache is implemented with three levels of error protection schemes, a monitoring mechanism, and a control component that decides whether to upgrade, downgrade, or keep the current protection level based on the feedback from the monitor. The self-adaptive data cache is evaluated by injecting errors with a changing soft error rates to prove that it can achieve similar reliability to a cache protected by the most reliable scheme, while maintaining the minimized performance and energy overheads.

#### 1.5.5 Reliable Register Files with Narrow-With Duplication

To improve the reliability of the register files in the microprocessor, this dissertation proposes to make a duplication of the value within the same data item by exploiting narrow-width register values. This in-register duplication (IRD) does not require additional copy registers. The datapath pipeline is augmented to efficiently incorporate parity encoding and parity checking such that error recovery is seamlessly supported in IRD and the parity checking is overlapped with the execution stage to avoid increasing the critical path. IRD can achieve extremely high read-with-duplicate (RWD) and error detection/recovery rates under heavy error injection with a negligible power overhead.

#### 1.6 Organization of the Dissertation

The rest of the dissertation is organized as follows. The next chapter presents the experimental setup used in this work. Chapter 3 discusses the proposed new lifetime model for

the cache vulnerability analysis and the improving schemes to enhance the reliability of the on-chip caches. Chapter 4 presents the tag replication buffer for reliable cache tag array design. Chapter 5 describes the design of a self-adaptive data cache for soft-error reliability. A reliable register file by exploiting and duplicating the narrow-width value is proposed in Chapter 6. Chapter 7 gives conclusions and describes the directions of future work.

#### **CHAPTER 2**

#### EXPERIMENTAL SETUP

#### 2.1 Simulated Processor

The simulator used in this work is derived from SimpleScalar V3.0 [44]. In Chapter 3 and 5, it is modified to model a contemporary high-performance microprocessor similar to Alpha 21364 [45]. In the new simulator, the original RUU (register update unit) structure is replaced by a separated integer issue queue, a floating-point issue queue, an integer register file, a floating-point register file, and an active list (a.k.a. the re-order buffer). A MIPS R10000 [12] style register renaming scheme is adopted in the implementation. There is no separate architectural/logical register file. Committing the current instruction frees the physical register that is being renamed to the immediately previous instruction with the same destination/result logical register. The new simulator also implements the tournament branch predictor (the local predictor uses 2-bit counters) used in Alpha 21364 microprocessors [45]. Table 2.1 gives the detailed configuration of the simulated microprocessor in Chapter 3, 4, and 5. Cacti 3.2 [46] and Wattch [47] are used for energy profiling during the simulation.

Since Chapter 6 focuses on the reliable register file design, the simulator is further modified to model a modern microprocessor similar to Alpha 21464 [48], in which the integer register file size is set to 128 to simulate the register pressure in SMT (simultaneous multithreading) environments. Table 2.2 shows the modified processor core different from Table 2.1

#### 2.2 Benchmarks

For experimental evaluation, this work uses the SPEC CPU2000 benchmark suite [49] compiled for the Alpha instruction set architecture using the "-arch ev6 -non\_shared" op-

**Table 2.1** Parameters for the simulated microprocessor in Chapter 3 and 5.

| Processor Core        |                                                  |  |  |  |  |

|-----------------------|--------------------------------------------------|--|--|--|--|

| Int/FP issue queue    | 20/15 entries                                    |  |  |  |  |

| Load/Store Queue      | 64 entries                                       |  |  |  |  |

| Active list (ACL)     | 80 entries                                       |  |  |  |  |

| Int/FP Register File  | 80/72 registers                                  |  |  |  |  |

| Datapath width        | 4 instructions per cycle                         |  |  |  |  |

| Function Units        | 4 IALU, 1 IMULT/IDIV                             |  |  |  |  |

|                       | 2 FALU, 1 FMULT/FDIV/FSQRT                       |  |  |  |  |

|                       | 2 MemPorts                                       |  |  |  |  |

|                       | Branch Predictor                                 |  |  |  |  |

| Branch Predictor      | Tournament predictor with a 4K meta-table,       |  |  |  |  |

|                       | a 4K bimodal predictor table, and a 2-level      |  |  |  |  |

|                       | gshare predictor with 12-bit history             |  |  |  |  |

|                       | 2048-entry, 2-way BTB, and 32-entry RAS          |  |  |  |  |

| Memory Hierarchy      |                                                  |  |  |  |  |

| L1 I/DCache           | 64KB, 2 ways, 64B blocks, 2 cycle latency        |  |  |  |  |

| L2 UCache             | 4MB, 8 ways, 128B blocks, 12 cycle latency       |  |  |  |  |

| Memory                | 225 cycles first chunk, 12 cycles rest           |  |  |  |  |

| TLB                   | Fully-assoc., 128 entries, 30-cycle miss penalty |  |  |  |  |

| Technology Parameters |                                                  |  |  |  |  |

| Vdd                   | 0.9V                                             |  |  |  |  |

| Clock frequency       | 3GHz                                             |  |  |  |  |

| Technology            | 70nm                                             |  |  |  |  |

Table 2.2 The Modified Processor Core in Chapter 6.

| Processor Core       |                                |  |  |  |

|----------------------|--------------------------------|--|--|--|

| Int/FP issue queue   | 128 entries                    |  |  |  |

| Load/Store Queue     | 256 entries                    |  |  |  |

| Active list (ACL)    | 512 entries                    |  |  |  |

| Int/FP Register File | 128/512 registers              |  |  |  |

| Datapath width       | 8 instructions per cycle       |  |  |  |

| Function Units       | 8 IALU, 2 IMULT/IDIV, 4 FALU   |  |  |  |

|                      | 2 FMULT/FDIV/FSQRT, 4 MemPorts |  |  |  |

tion with "peak" tuning. The reference input sets is used for this study. Each benchmark is first fast-forwarded to its early single simulation point (*gap* and *ammp* use the standard single simulation point instead of the very large early single simulation point) specified by SimPoint [50]. The last 100 million instructions during the fast-forwarding phase are used to warm-up the caches if the number of skipped instructions is more than 100 million. Then, the next 100 million instructions are simulated in detail. The description of the simulated SPEC CPU2000 benchmarks is shown in Table 2.3.

Table 2.3 SPEC CPU2000 benchmark suite

|                                     |            | benchmark su |                                                    |  |

|-------------------------------------|------------|--------------|----------------------------------------------------|--|

| Benchmark                           | Language   | Fast Forword | Category                                           |  |

| CINT2000 (Integer Benchmarks)       |            |              |                                                    |  |

| 164.gzip                            | С          | 300M         | Compression                                        |  |

| 175.vpr                             | С          | 7100M        | FPGA Circuit Placement and Routing                 |  |

| 176.gcc                             | C          | 10900M       | C Programming Language Compiler                    |  |

| 181.mcf                             | С          | 31600M       | Combinatorial Optimization                         |  |

| 186.crafty                          | С          | 0M           | Game Playing: Chess                                |  |

| 197.parser                          | С          | 1600M        | Word Processing                                    |  |

| 252.eon                             | C++        | 1800M        | Computer Visualization                             |  |

| 253.perlbmk                         | С          | 100M         | PERL Programming Language                          |  |

| 254.gap                             | С          | 67600M       | Group Theory, Interpreter                          |  |

| 255.vortex                          | C          | 5700M        | Object-oriented Database                           |  |

| 256.bzip2                           | С          | 900M         | Compression                                        |  |

| 300.twolf                           | C          | 3100M        | Place and Route Simulator                          |  |

| CFP2000 (Floating Point Benchmarks) |            |              |                                                    |  |

| 168.wupwise                         | Fortran 77 | 58400M       | Physics / Quantum Chromodynamics                   |  |

| 171.swim                            | Fortran 77 | 58400M       | Shallow Water Modeling                             |  |

| 172.mgrid                           | Fortran 77 | 500M         | Multi-grid Solver: 3D Potential Field              |  |

| 173.applu                           | Fortran 77 | 1800M        | Parabolic / Elliptic Partial Differential Equation |  |

| 177.mesa                            | С          | 8900M        | 3-D Graphics Library                               |  |

| 178.galgel                          | Fortran 90 | 67600M       | Computational Fluid Dynamics                       |  |

| 179.art                             | C          | 6700M        | Image Recognition / Neural Networks                |  |

| 183.equake                          | C          | 19400M       | Seismic Wave Propagation Simulation                |  |

| 187.facerec                         | Fortran 90 | 13600M       | Image Processing: Face Recognition                 |  |

| 188.ammp                            | C          | 67600M       | Computational Chemistry                            |  |

| 189.lucas                           | Fortran 90 | 3500M        | Number Theory / Primality Testing                  |  |

| 191.fma3d                           | Fortran 90 | 29800M       | Finite-element Crash Simulation                    |  |

| 200.sixtrack                        | Fortran 77 | 8200M        | High Energy Nuclear Physics Accelerator Design     |  |

| 301.apsi                            | Fortran 77 | 4600M        | Meteorology: Pollutant Distribution                |  |

#### **CHAPTER 3**

# ON-CHIP CACHE VULNERABILITY ANALYSIS AND OPTIMIZATION

#### 3.1 Introduction

Most of the previous works have studied tradeoffs between performance, energy consumption, area overheads and the achieved cache reliability for their proposed schemes [51][52][53][28][40][29][54][55][56][57][41]. Therefore, a more systematic study of cache vulnerability is needed. Such a study could provide enough insight into cache reliability behavior, that the designer could take advantage of to design highly cost-effective reliable caches. Recent papers [41][55][51][58][59][60] present some initial efforts towards such a cache vulnerability analysis. However, their cacheline- or word-based vulnerability characterization used some simple generation model [61] that could not explore the temporal vulnerability of the cache, i.e., how different lifetime phases of the cache data contribute to vulnerability. This temporal information is of critical importance in determining which data in the cache should be protected at what time with which protection schemes, in order to achieve high reliability. This dissertation targets at providing such a bridge from perception to practice in designing reliable caches.

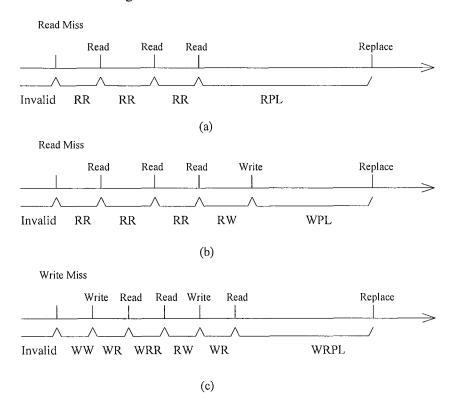

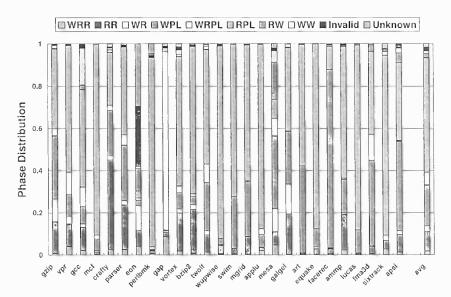

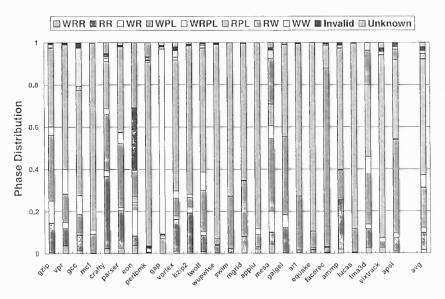

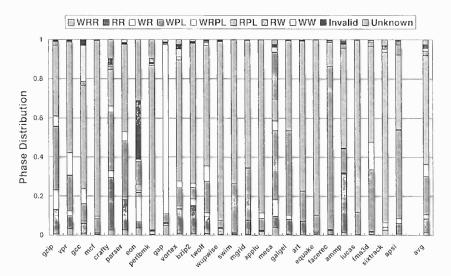

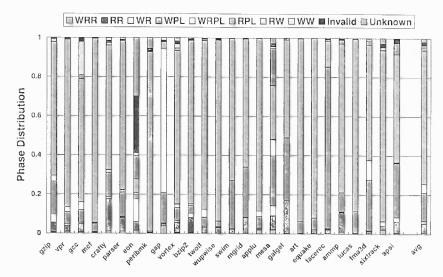

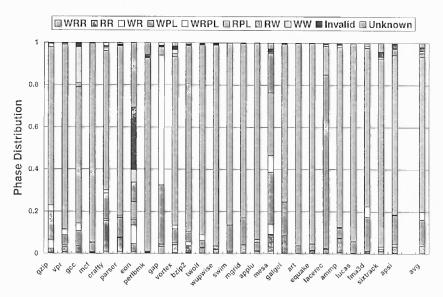

For the aforementioned purpose, a detailed lifetime model is proposed for the data arrays in the L1 data and instruction caches, as the first step, to capture all possible activities that could involve these data items. A data item under consideration can be at various granularities such as cacheline, sub-block, word, half word, byte, or even bit. In the data cache, the new lifetime model distinguishes among nine lifetime phases for each data item according to the previous activity and the current one, and further categorizes them into two groups, *vulnerable* and *non-vulnerable* phases. A cache vulnerable phase is defined as the phase during which any occurring error has the potential to propagate either to the CPU

datapath (by load operations) or to the L2 cache (via a dirty line writeback). The cache temporal vulnerability factor (TVF) is defined as the percentage of data items present in vulnerable phases over all possible data items that the cache can hold, an average along the time axis.

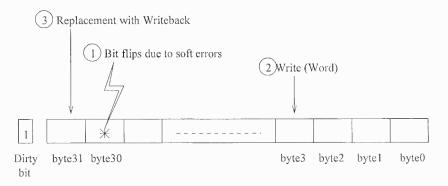

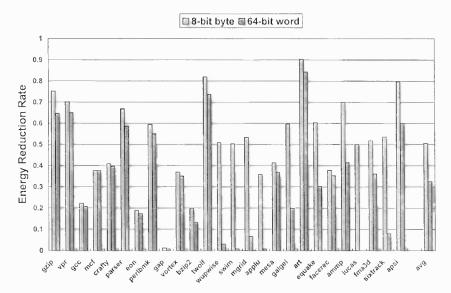

To derive highly cost-effective reliability schemes for on-chip cache memories, new design methodologies driven by TVF characterization and analysis are proposed. First, a cacheline-based TVF analysis is performed on the entire data array. The results show that the vulnerable phase write-replace (WPL, the lifetime phase between the last write and the replacement without any read in between) contributes the most to TVF in the data cache. A writethrough data cache can effectively eliminate this phase by immediately writing back the data to the L2 cache after a store operation. However, the excessive accesses to the L2 cache degrade the performance and increase the energy consumption. An alternative to solve this problem is to early write back dirty lines, such as the deadtime based early writeback (DTEWB) scheme in [40]. Further analysis indicated that this cacheline-based analysis cannot fully capture the nature of CPU accesses to the data cache. Since the unit size for data cache accesses is the byte, different bytes in the same cacheline may be in different lifetime phases at any given time, e.g., some bytes in a dirty cacheline may be in the clean state. Treating all the bytes in a cacheline equally may lead to inaccurate calculation of the cache TVF. It concludes that fine-grain (e.g., byte-based) lifetime models should be considered for more accurate TVF characterization. Based on the byte-level analysis, the work also proposes the multiple-dirty-bits (MDB) scheme to further reduce the WPL vulnerable phase as well as the energy consumption during the writeback.

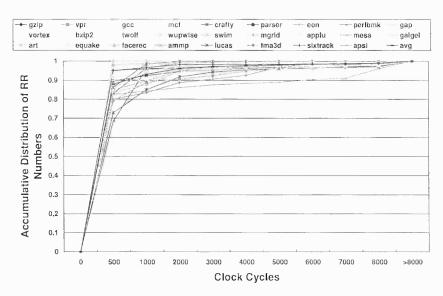

After WPL optimization, the vulnerable phase *read-read* (RR, the lifetime phase between two consecutive reads of a clean data item) with the potential to propagate errors to the CPU raises as another major part in the vulnerability factor of the data cache. Experimental study shows that a 87.8% majority of RRs have a short time interval (<= 0.5K cycles) and account for only 15.5% of the overall RR vulnerable intervals. Based on this