### New Jersey Institute of Technology

## Digital Commons @ NJIT

**Dissertations**

**Electronic Theses and Dissertations**

Fall 1-31-2015

# Reliability study of Zr and Al incorporated hf based high-k dielectric deposited by advanced processing

Md Nasir Uddin Bhuyian New Jersey Institute of Technology

Follow this and additional works at: https://digitalcommons.njit.edu/dissertations

Part of the Electrical and Electronics Commons

#### **Recommended Citation**

Bhuyian, Md Nasir Uddin, "Reliability study of Zr and Al incorporated hf based high-k dielectric deposited by advanced processing" (2015). Dissertations. 96.

https://digitalcommons.njit.edu/dissertations/96

This Dissertation is brought to you for free and open access by the Electronic Theses and Dissertations at Digital Commons @ NJIT. It has been accepted for inclusion in Dissertations by an authorized administrator of Digital Commons @ NJIT. For more information, please contact digitalcommons@njit.edu.

# **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

#### **ABSTRACT**

# RELIABILITY STUDY OF Zr AND AI INCORPORATED Hf BASED HIGH-K DIELECTRIC DEPOSITED BY ADVANCED PROCESSING

#### by Md Nasir Uddin Bhuyian

Hafnium-based high- $\kappa$  dielectric materials have been successfully used in the industry as a key replacement for SiO<sub>2</sub> based gate dielectrics in order to continue CMOS device scaling to the 22-nm technology node. Further scaling according to the device roadmap requires the development of oxides with higher  $\kappa$  values in order to scale the equivalent oxide thickness (EOT) to 0.7 nm or below while achieving low defect densities. In addition, next generation devices need to meet challenges like improved channel mobility, reduced gate leakage current, good control on threshold voltage, lower interface state density, and good reliability. In order to overcome these challenges, improvements of the high- $\kappa$  film properties and deposition methods are highly desirable.

In this dissertation, a detail study of Zr and Al incorporated HfO<sub>2</sub> based high- $\kappa$  dielectrics is conducted to investigate improvement in electrical characteristics and reliability. To meet scaling requirements of the gate dielectric to sub 0.7 nm, Zr is added to HfO<sub>2</sub> to form Hf<sub>1-x</sub>Zr<sub>x</sub>O<sub>2</sub> with x=0, 0.31 and 0.8 where the dielectric film is deposited by using various intermediate processing conditions, like (i) DADA: intermediate thermal annealing in a cyclical deposition process; (ii) DSDS: similar cyclical process with exposure to SPA Ar plasma; and (iii) As-Dep: the dielectric deposited without any intermediate step. MOSCAPs are formed with TiN metal gate and the reliability of these devices is investigated by subjecting them to a constant voltage stress in the gate injection mode. Stress induced flat-band voltage shift ( $\Delta V_{FB}$ ), stress induced leakage current (SILC)

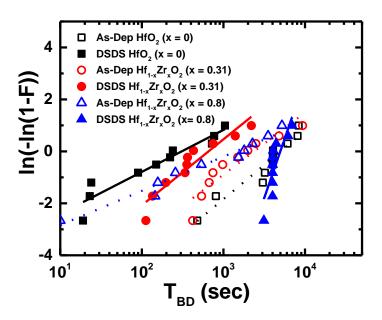

and stress induced interface state degradation are observed. DSDS samples demonstrate the superior characteristics whereas the worst degradation is observed for DADA samples. Time dependent dielectric breakdown (TDDB) shows that DSDS Hf<sub>1-x</sub>Zr<sub>x</sub>O<sub>2</sub> (x=0.8) has the superior characteristics with reduced oxygen vacancy, which is affiliated to electron affinity variation in HfO<sub>2</sub> and ZrO<sub>2</sub>. The trap activation energy levels estimated from the temperature dependent current voltage characteristics also support the observed reliability characteristics for these devices.

In another experiment, HfO<sub>2</sub> is lightly doped with Al with a variation in Al concentration by depositing intermediate HfAlO<sub>x</sub> layers. This work has demonstrated a high quality HfO<sub>2</sub> based gate stack by depositing atomic layer deposited (ALD) HfAlO<sub>x</sub> along with HfO<sub>2</sub> in a layered structure. In order to get multifold enhancement of the gate stack quality, both Al percentage and the distribution of Al are observed by varying the HfAlO<sub>x</sub> layer thickness and it is found that < 2% Al/(Al+Hf)% incorporation can result in up to 18% reduction in the average EOT along with up to 41% reduction in the gate leakage current as compared to the dielectric with no Al content. On the other hand, excess Al presence in the interfacial layer moderately increases the interface state density  $(D_{it})$ . When devices are stressed in the gate injection mode at a constant voltage stress, dielectrics with Al/(Hf+Al)% < 2% show resistance to stress induced flat-band voltage shift ( $\Delta V_{FB}$ ), and stress induced leakage current (SILC). The time dependent dielectric breakdown (TDDB) characteristics show a higher charge to breakdown and an increase in the extracted Weibull slope  $(\beta)$  that further confirms an enhanced dielectric reliability for devices with < 2%Al/(Al+Hf)%.

# RELIABILITY STUDY OF Zr AND AI INCORPORATED Hf BASED HIGH-K DIELECTRIC DEPOSITED BY ADVANCED PROCESSING

by Md Nasir Uddin Bhuyian

A Dissertation

Submitted to the Faculty of

New Jersey Institute of Technology

in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy in Electrical Engineering

Helen and John C. Hartmann Department of Electrical and Computer Engineering

January 2015

Copyright © 2015 by Md Nasir Uddin Bhuyian

ALL RIGHTS RESERVED

#### APPROVAL PAGE

# RELIABILITY STUDY OF Zr AND AI INCORPORATED Hf BASED HIGH-K DIELECTRIC DEPOSITED BY ADVANCED PROCESSING

## Md Nasir Uddin Bhuyian

| Dr. Durgamadhab Misra, Dissertation Advisor<br>Professor of Electrical and Computer Engineering, NJIT | Date |

|-------------------------------------------------------------------------------------------------------|------|

| Dr. Leonid Tsybeskov, Committee Member Professor of Electrical and Computer Engineering, NJIT         | Date |

| Dr. Marek Sosnowski, Committee Member Professor of Electrical and Computer Engineering, NJIT          | Date |

| Dr. George Georgiou, Committee Member<br>Research Professor of Physics, NJIT                          | Date |

| Dr. Kandabara Tapily, Committee Member<br>Senior Technical Staff Member,                              | Date |

Thin Film Process Technology Division, TEL

#### BIOGRAPHICAL SKETCH

**Author:** Md Nasir Uddin Bhuyian

**Degree:** Doctor of Philosophy

**Date:** January 2015

#### **Undergraduate and Graduate Education:**

- Doctor of Philosophy in Electrical Engineering, New Jersey Institute of Technology, Newark, NJ, 2015

- Master of Science in Electrical and Electronic Engineering,

Bangladesh University of Engineering and Technology, Dhaka, Bangladesh, 2011

- Bachelor of Science in Electrical and Electronic Engineering,

Bangladesh University of Engineering and Technology, Dhaka, Bangladesh, 2007

**Major:** Electrical Engineering

#### **Presentations and Publications:**

- M.N. Bhuyian, D. Misra, K. Tapily, R. Clark, S. Consiglio, C. Wajda, G. Nakamura, and G. Leusink, "Cyclic Plasma Treatment during ALD Hf<sub>1-x</sub>Zr<sub>x</sub>O<sub>2</sub> Deposition," *ECS Journal of Solid State Science and Technology*, vol. 3, no. 5, p. N83, 2014.

- M.N. Bhuyian, D. Misra, K. Tapily, R. Clark, S. Consiglio, C. Wajda, G. Nakamura, and G. Leusink, "Reliability of ALD Hf<sub>1-x</sub>Zr<sub>x</sub>O<sub>2</sub> Deposited by Intermediate Annealing or Intermediate Plasma Treatment," *ECS Transactions*, vol. 58, no. 7, p. 17, 2013.

- M.N. Bhuyian, and D. Misra, "Reliability Considerations of High-κ Dielectrics Deposited by Various Intermediate Treatment," *ECS Transactions*, vol. 60, no. 1, p. 103, 2014.

- M.N. Bhuyian, D. Misra, K. Tapily, R. Clark, S. Consiglio, C. Wajda, G. Nakamura, and G. Leusink, "Cyclic Plasma Treatment during ALD Hf<sub>1-x</sub>Zr<sub>x</sub>O<sub>2</sub> Deposition," *ECS Transactions*, vol. 61, no. 2, p. 41, 2014.

- M.N. Bhuyian, D. Misra, K. Tapily, R. Clark, S. Consiglio, C. Wajda, G. Nakamura, and G. Leusink, "Effect of Al Doping on the Reliability of ALD HfO<sub>2</sub>," *ECS Transactions*, vol. 64, no. 8, p. 29, 2014.

- M.N. Bhuyian and D. Misra "Reliability of Hf<sub>0.2</sub>Zr<sub>0.8</sub>O<sub>2</sub> and HfO<sub>2</sub> Films Deposited by Cyclic Annealing or Cyclic Plasma Treatment" (Submitted to Microelectronics Reliability).

- M.N. Bhuyian and D. Misra, "Multilayered ALD HfAlO<sub>x</sub> and HfO<sub>2</sub> for High Quality Gate Stack" (Submitted to IEEE Transactions on Device and Materials Reliability).

- M.N. Bhuyian and D. Misra, "Effect of Cyclic Plasma Treated Hf<sub>1-x</sub>Zr<sub>x</sub>O<sub>2</sub> on Interface State Density" (Submitted to Solid State Electronics Journal).

- M.N. Bhuyian and D. Misra, "ALD HfAlOx in Multi Layered Structure Gate Stack:

Reliability" (Submitted to 2015 IEEE International Reliability Physics Symphosium).

- M. N. Bhuyian, D. Misra, and S. Poddar, "Impact of Cyclic Plasma Treatment on Defects in TiN/HfZrO/SiON/Si Gate Stacks," (In preparation).

- M.N. Bhuyian, D. Misra, K. Tapily, R. Clark, S. Consiglio, C. Wajda, G. Nakamura, and G. Leusink, "Reliability of ALD Hf<sub>1-x</sub>Zr<sub>x</sub>O<sub>2</sub> Deposited by Intermediate Annealing or Intermediate Plasma Treatment," Semiconductors, Dielectrics and Metals for Nanoelectronics 11, 224<sup>th</sup> ECS Meeting, San Francisco, CA, October 27 November 1, 2013.

- M.N. Bhuyian and D. Misra, "Cyclic Plasma Treatment during ALD Hf<sub>1-x</sub>Zr<sub>x</sub>O<sub>2</sub>

Deposition," Dielectrics for Nanosystems 6: Materials Science, Processing,

Reliability, and Manufacturing, 225<sup>th</sup> ECS Meeting, Orlando, FL, May 11-15, 2014.

- M. N. Bhuyian and D. Misra, "Effect of Al Doping On The Reliability of ALD HfO<sub>2</sub>," Semiconductors, Dielectrics, and Metals for Nanoelectronics 12, 226<sup>th</sup> ECS Meeting, Cancun, Mexico, Oct 5-9, 2014.

- M.N. Bhuyian and D. Misra, "Reliability of Al Doped HfO<sub>2</sub> with Multi Layered ALD HfAlO<sub>x</sub>," 2014 GSA Research Day Poster Presentation, New Jersey Institute of Technology, Newark, NJ.

- S. Poddar, M.N. Bhuyian, and D. Misra, "Understanding Defects in TiN/HfZrO/SiON/Si Gate Stacks," 2014 Summer Research Program Poster Presentation, New Jersey Institute of Technology, Newark, NJ.

- S. Bhattacharya, I. Priyadharshini, A. Mohan, M.N. Bhuyian, D. Misra, "Reliability Of ALD Hf<sub>1-x</sub>Zr<sub>x</sub>O<sub>2</sub> Deposited by Intermediate Plasma Treatment (DSDS) with Nitrided Chemically Grown Interface and Plasma Oxynitride Interface," 2013 Summer Research Program Poster Presentation, New Jersey Institute of Technology, Newark, NJ.

- D. Chattopadhyay, H. Chakraborty, J. Krishnasamy, M. N. Bhuyian, D. Misra,

"Characterization Of High-K Gate Dielectrics Using a MOS Capacitor," 2012

Summer Research Program Poster Presentation, New Jersey Institute of Technology, Newark, NJ.

To my parents

#### ACKNOWLEDGMENT

I would like to express my deepest appreciation to my dissertation advisor, Dr. Durgamadhab Misra, for his guidance, constant support, and encouragement throughout my Ph.D. studies. He not only guided me through my research, but also helped me enormously to be independent. I want to express my gratitude to all my committee members, Dr. Leonid Tsybeskov, Dr. Marek Sosnowski, Dr. George Georgiou, and Dr. Kandabara Tapily for their valuable suggestions.

I would like to thank Dr. Kandabara Tapily, Dr. Robert Clark and other researchers of TEL Technology Center, America, Albany, NY, for supplying devices and helpful discussions for this research.

My colleagues and friends at NJIT have always given me technical and moral support during this time of research work. I want to take this opportunity to thank Selina Mala, Peter Paliwoda, Yiming Ding, Tazima Selim Chowdhuru, Hillol Debnath, and Tariq M Arif.

I am grateful to my family members especially my elder brother D. M. Alamgir Chowdhury Plabon for his constant support and encouragement since my childhood. I am indebted to my parents, who taught me first the principles, to dream for best things in the world and to be a good human being.

Finally, I want to thank my lovely wife, Faria Sharmin, for her single handed support, patience, and encouragement that have made this endeavor easy to bear.

## TABLE OF CONTENTS

| Cl | napter                  |                                                                                       | Page |

|----|-------------------------|---------------------------------------------------------------------------------------|------|

| 1  | INTF                    | RODUCTION, MOTIVATION AND OBJECTIVE                                                   | 1    |

|    | 1.1                     | Introduction                                                                          | 1    |

|    | 1.2                     | Motivation and Approach                                                               | 6    |

|    | 1.3                     | Objectives                                                                            | 9    |

|    | 1.4                     | Dissertation Organization.                                                            | 10   |

| 2  | HfO <sub>2</sub><br>PRO | BASED HIGH-K DIELECTRICS WITH ADVANCED CESSING: CURRENT STATUS                        | 12   |

|    | 2.1                     | Introduction                                                                          | 12   |

|    | 2.2                     | Selection Criteria of High-κ Dielectric Materials                                     | 13   |

|    | 2.3                     | Alloying HfO <sub>2</sub> and ZrO <sub>2</sub>                                        | 15   |

|    | 2.4                     | Intermediate Treatment in High-κ Dielectric Deposition                                | 21   |

|    | 2.5                     | Slot Plane Antenna (SPA) Plasma                                                       | 22   |

|    | 2.6                     | Al Incorporation into HfO <sub>2</sub>                                                | 23   |

|    |                         | 2.6.1 HfAlO <sub>x</sub> Alloy Structures                                             | 24   |

|    |                         | 2.6.2 Al <sub>2</sub> O <sub>3</sub> /HfO <sub>2</sub> Bilayer Structures             | 26   |

|    |                         | 2.6.3 Problems with Excess Al Incorporation                                           | 30   |

|    | 2.7                     | Chapter Summary.                                                                      | 32   |

| 3  | DEV<br>REL              | ICE FABRICATION, PHYSICAL CHARACTERIZATION, IABILITY ISSUES, AND EXPERIMENTAL DETAILS | 33   |

|    | 3.1                     | Introduction                                                                          | 33   |

|    | 3.2                     | Zr Incorporation in HfO <sub>2</sub> and Intermediate Treatments                      | 33   |

# TABLE OF CONTENTS (Continued)

| Cha | apter |         |                                                                                                                                                 | Page |

|-----|-------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------|------|

|     |       | 3.2.1   | Device Fabrication.                                                                                                                             | 33   |

|     |       | 3.2.2   | Fundamental Properties of Hf <sub>1-x</sub> Zr <sub>x</sub> O <sub>2</sub> Deposited by Different Processing                                    | 35   |

|     | 3.3   | Extren  | nely Low Al Incorporation in HfO <sub>2</sub>                                                                                                   | 39   |

|     |       | 3.3.1   | Device Fabrication- ALD Multi Layered Structure                                                                                                 | 39   |

|     |       | 3.3.2   | Physical Properties of HfAlO <sub>x</sub> Dielectrics                                                                                           | 41   |

| •   | 3.4   | Defect  | s and Reliability of High-к Dielectrics                                                                                                         | 43   |

|     |       | 3.4.1   | Constant Voltage Stress Induced Degradations                                                                                                    | 45   |

|     |       | 3.4.2   | Time Dependent Dielectric Breakdown (TDDB)                                                                                                      | 49   |

| ,   | 3.5   | Electri | cal characterization and Reliability Study                                                                                                      | 53   |

|     |       | 3.5.1   | Capacitance-Voltage (C-V) Measurement                                                                                                           | 54   |

|     |       | 3.5.2   | Conductance Measurement                                                                                                                         | 54   |

|     |       | 3.5.3   | Current-Voltage (I-V) Measurement                                                                                                               | 55   |

|     |       | 3.5.4   | Constant Voltage Stress (CVS) for Reliability Study                                                                                             | 55   |

|     |       | 3.5.5   | Measurement Automation                                                                                                                          | 57   |

| ,   | 3.6   | Chapte  | er Summary                                                                                                                                      | 58   |

| (   | CYCI  | LIC DE  | AL CHARACTERIZATION OF ALD Hf <sub>1-x</sub> Zr <sub>x</sub> O <sub>2</sub> WITH POSITION AND ANNEALING (DADA), AND CYCLIC SPA TREATMENT (DSDS) | 59   |

| 4   | 4.1   | Introd  | uction                                                                                                                                          | 59   |

| 4   | 4.2   | Capaci  | itance-Voltage Characteristics, EOT, and Flat-band Voltage                                                                                      | 60   |

# TABLE OF CONTENTS (Continued)

| Cl | napter |         |                                                                                                         | Page |

|----|--------|---------|---------------------------------------------------------------------------------------------------------|------|

|    | 4.3    | Gate I  | Leakage Current Density Comparison                                                                      | 64   |

|    | 4.4    | Interfa | ace State Density, $D_{it}$ Extraction by Conductance Method                                            | 66   |

|    |        | 4.4.1   | Impact of Zr Addition and SPA Ar Plasma Exposure on $D_{it}$                                            | 67   |

|    |        | 4.4.2   | Mid gap $D_{it}$ Comparison for DSDS, DADA, and As-Dep Processing.                                      | 69   |

|    | 4.5    | Chapte  | er Summary                                                                                              | 70   |

| 5  | DEPO   |         | TY STUDY OF ALD $Hf_{1-x}Zr_xO_2$ WITH CYCLIC N AND ANNEALING (DADA), AND CYCLIC SPA AR REATMENT (DSDS) | 71   |

|    | 5.1    |         | uction                                                                                                  | 71   |

|    | 5.2    |         | t of Constant Voltage Stress                                                                            | 72   |

|    |        | 5.2.1   | Stress Induced Flat-band Voltage Shift ( $\Delta V_{FB}$ )                                              | 72   |

|    |        | 5.2.2   | Stress Induced Leakage Current (SILC)                                                                   | 76   |

|    |        | 5.2.3   | Stress Induced Interface State Generation                                                               | 80   |

|    |        | 5.2.4   | Time Dependent Dielectric Breakdown                                                                     | 84   |

|    | 5.3    | Effect  | of Quality of Interfacial Layer                                                                         | 88   |

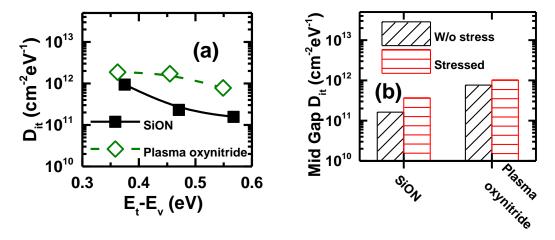

|    |        | 5.3.1   | Interface State Density Comparison for SiON and Plasma Oxynitride Interface                             | 90   |

|    | 5.4    | High 7  | Γemperature I-V Measurement                                                                             | 92   |

|    |        | 5.4.1   | Defect Energy Level Calculation.                                                                        | 93   |

|    |        | 5.4.2   | SILC Activation Energy.                                                                                 | 96   |

|    | 5.5    | Chapte  | er Summary                                                                                              | 98   |

# **TABLE OF CONTENTS** (Continued)

| Cł | apter |         |                                                                                                                    | Page |

|----|-------|---------|--------------------------------------------------------------------------------------------------------------------|------|

| 6  |       |         | ΓΥ STUDY OF DIELECTRICS WITH EXTREMELY LOW AI ATION IN HfO <sub>2</sub>                                            | 99   |

|    | 6.1   | Introd  | uction                                                                                                             | 99   |

|    | 6.2   | Electri | ical Characteristics of Multi Layered ALD HfAlO <sub>x</sub>                                                       | 101  |

|    |       | 6.2.1   | C-V and I-V Characteristics.                                                                                       | 102  |

|    |       | 6.2.2   | Equivalent Oxide Thickness (EOT), Flat-band Voltage ( $V_{FB}$ ), and Leakage Current Density ( $J_g$ ) Comparison | 103  |

|    |       | 6.2.3   | Comparison of Interface State Density                                                                              | 107  |

|    | 6.3   | Reliab  | ility Study by Constant Voltage Stress                                                                             | 108  |

|    |       | 6.3.1   | Impact of Stress on $\Delta V_{FB}$ , SILC and $D_{it}$                                                            | 108  |

|    |       | 6.3.2   | Comparison of TDDB Characteristics.                                                                                | 113  |

|    | 6.4   | Chapte  | er Summary                                                                                                         | 116  |

| 7  | SUM   | MARY    | AND FUTURE WORK                                                                                                    | 117  |

|    | 7.1   | Summ    | ary                                                                                                                | 117  |

|    | 7.2   | Future  | Work                                                                                                               | 120  |

|    |       | 7.2.1   | ALD $Hf_{1-x}Zr_xO_2$ and $HfAlO_x$ on Si Substrate                                                                | 120  |

|    |       | 7.2.2   | Zr and Al Incorporated Hf Based High-κ Dielectrics on High<br>Mobility Substrates                                  | 120  |

| RF | EFERF | ENCES   |                                                                                                                    | 122  |

## LIST OF TABLES

| Table |                                                                                                                                                                                                                           | Page |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 3.1   | Composition of Hf and Al from XPS and Dielectric Thickness Measured by SE                                                                                                                                                 | 42   |

| 4.1   | Comparison of Interface State Density, $D_{it}$ at Mid Gap for Different Dielectrics.                                                                                                                                     | 69   |

| 5.1   | Weibull Slope for As-Dep and DSDS Hf <sub>1-x</sub> Zr <sub>x</sub> O <sub>2</sub> With Different Zr Percentages.                                                                                                         | 86   |

| 5.2   | Failure Time (T <sub>63%</sub> ) for Different Dielectrics. (Five Devices from Each Device Type Were Stressed in The Gate Injection Mode until Hard Breakdown)                                                            | 88   |

| 5.3   | Defect Activation Energy ( $E_a$ ) for DSDS and As-Dep $Hf_{1-x}Zr_xO_2$ ( $x$ =0 and 0.8)                                                                                                                                | 95   |

| 5.4   | Comparison of SILC Activation Energy ( $E_c$ ) for DSDS and As-Dep $Hf_{1-x}Zr_xO_2$ ( $x$ =0 and 0.8)                                                                                                                    | 97   |

| 6.1   | Comparison of Interface State Density, Dit in The Si Mid-gap Level                                                                                                                                                        | 107  |

| 6.2   | Power Exponent (n) for $\Delta V_{FB}$ , and $\Delta J_g/J_{g0}$ , and $\Delta D_{it}/D_{it0}$ Comparison for Different Dielectrics.                                                                                      | 111  |

| 6.3   | Weibull Slope, $\beta$ for Lot A (A <sub>1</sub> , A <sub>2</sub> , and A <sub>3</sub> ), Lot B (B <sub>1</sub> , and B <sub>2</sub> ) With HfAlO <sub>x</sub> Layer and the Control Device, C With HfO <sub>2</sub> Only | 114  |

| Figure |                                                                                                                                                                                                                                                                     | Page |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

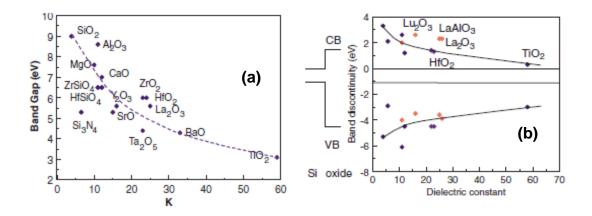

| 2.1    | (a) Optical band gap vs dielectric constant (k) of candidate gate dielectrics, and (b) Band offset with Si valence band (VB) and conduction band (CB) as a function of dielectric constant for candidate gate dielectrics.                                          | 14   |

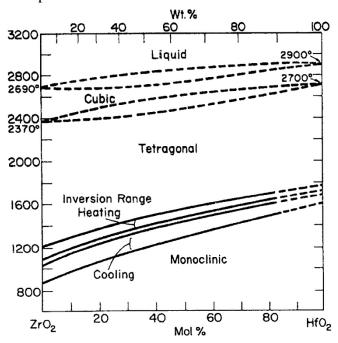

| 2.2    | Temperature-composition phase diagram of HfO <sub>2</sub> - ZrO <sub>2</sub>                                                                                                                                                                                        | 15   |

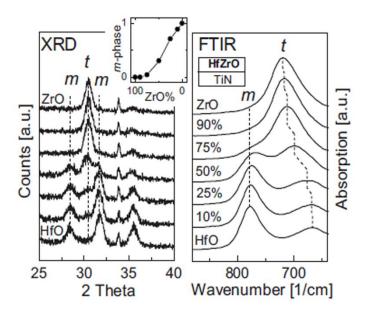

| 2.3    | XRD (left) and ATR-FTIR (right) spectra for HfZrO with various compositions. The inset shows the volume fraction of monoclinic phase decreases with increase in Zr fraction                                                                                         | 16   |

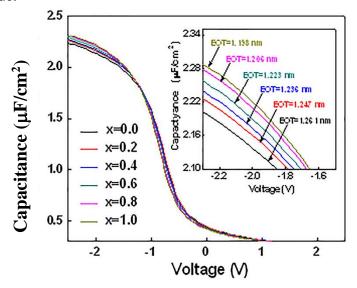

| 2.4    | Typical C-V plot for $Hf_{1-x}Zr_xO_2$ for different $Zr/(Hf+Zr)$ content. Inset shows the magnified C-V plot to demonstrate the relationship between EOT and Zr Content.                                                                                           | 17   |

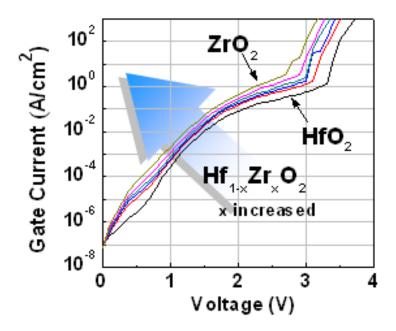

| 2.5    | Comparison of gate leakage current for $Hf_{1-x}Zr_xO_2$ with different $Zr/(Hf+Zr)$ content.                                                                                                                                                                       | 18   |

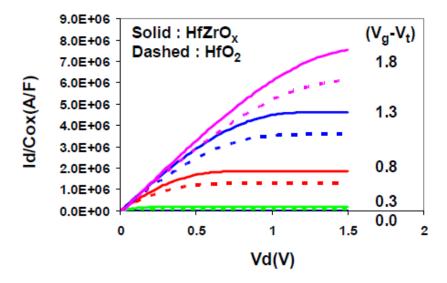

| 2.6    | $I_d$ - $V_d$ characteristics of $HfO_2$ and $HfZrO_x$ NMOSFET (W/L=10umX10um). Devices were fabricated with $Ta_xC_y$ gate dielectrics were annealed in $N_2$ ambient at $1000^0C$                                                                                 | 19   |

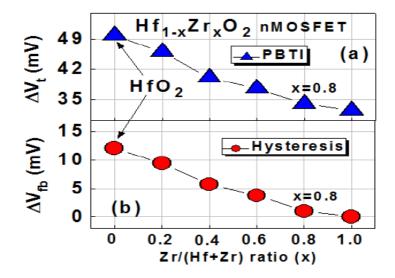

| 2.7    | (a) Normalized PBTI $V_t$ shift and (b) Hysteresis of TiN/ $Hf_{1-x}Zr_xO_2/SiO_2$ nMOSFET with different $ZrO_2$ concentrations. ALD $Hf_{1-x}Zr_xO_2$ deposited by using $HfCl_4$ , $ZrCl_4$ , and $H_2O$ precursors on in situ steam grown $SiO_2/Si$ interface. | 20   |

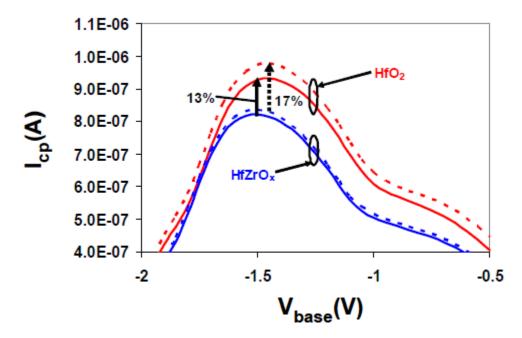

| 2.8    | Charge pumping current, $I_{cp}$ as a function of base voltage for $HfO_2$ and $HfZrO_x$ NMOSFET before (solid line) and after stress at 1.8 V for 1000s (dashed line).                                                                                             | 20   |

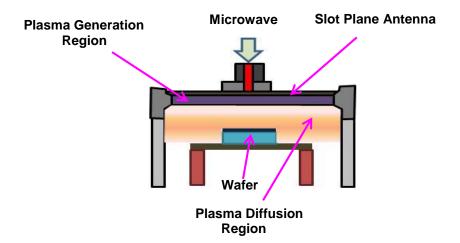

| 2.9    | A typical slot plane antenna plasma system                                                                                                                                                                                                                          | 22   |

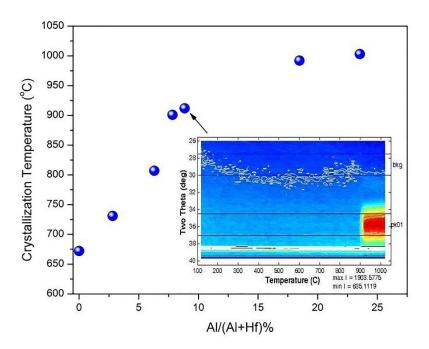

| 2.10   | Crystallization temperature of $Hf_{1-x}Al_xO_y$ as a function of $Al/(Al+Hf)\%$ in the dielectrics. Inset shows XRD plot at the on set of crystallization for $Hf_{1-x}Al_xO_y$ with $x=0.09$ .                                                                    | 24   |

# LIST OF FIGURES (Continued)

| Figure |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Page |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

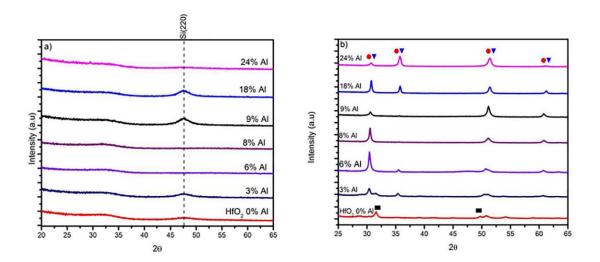

| 2.11   | Synchronous grazing in plane X ray diffraction pattern for (a) as deposited ALD $Hf_{1-x}Al_xO_y$ , (b) annealed ALD $Hf_{1-x}Al_xO_y$ as a function of $Al/(Al+Hf)\%$ .                                                                                                                                                                                                                                                                                                                                           | 25   |

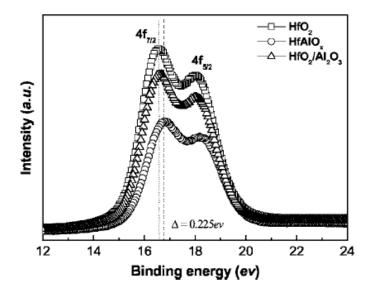

| 2.12   | The XPS Hf 4f spectra of pure HfO <sub>2</sub> , HfAlO <sub>x</sub> alloy, and Al <sub>2</sub> O <sub>3</sub> /HfO <sub>2</sub> stack, respectively, after 500°C RTA PDA for 30 s in N <sub>2</sub> atmosphere. All samples were deposited with total 40 ALD cycles. Both HfAlO <sub>x</sub> and Al <sub>2</sub> O <sub>3</sub> /HfO <sub>2</sub> were deposited with 26 ALD cycles for HfO <sub>2</sub> deposition and 14 ALD cycles for Al <sub>2</sub> O <sub>3</sub> deposition                                | 25   |

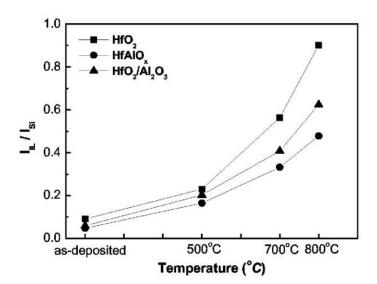

| 2.13   | The intensity ratio of $I_{II}/I_{Si}$ obtained from XPS Si 2p core-level spectra for pure $HfO_2$ , $HfAlO_x$ alloy, and $Al_2O_3/HfO_2$ stack, respectively, after PDA at different temperatures.                                                                                                                                                                                                                                                                                                                | 27   |

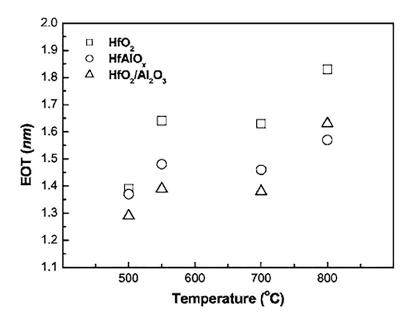

| 2.14   | The variation of EOT value of pure $HfO_2$ , $HfAlO_x$ alloy, and $Al_2O_3/HfO_2$ stack, respectively, as a function of PDA temperatures                                                                                                                                                                                                                                                                                                                                                                           | 28   |

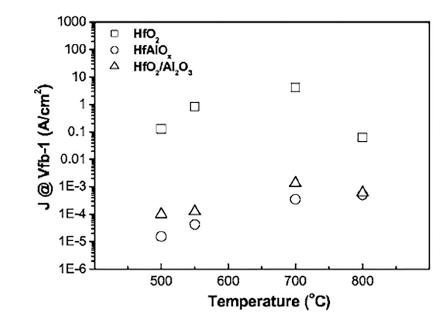

| 2.15   | The variation of current density at $V_{\rm FB}-1$ volts as a function of PDA temperatures for pure $\rm HfO_2$ , $\rm HfAlO_x$ alloy, and $\rm Al_2O_3/HfO_2$ stack on Si, respectively.                                                                                                                                                                                                                                                                                                                          | 29   |

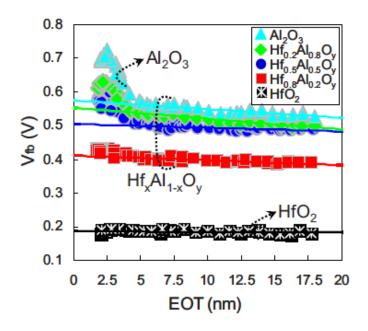

| 2.16   | $V_{FB}$ –EOT plots for NiSi/Hf $_x$ Al $_{1-x}O_y$ /terraced SiO $_2$ /n-Si p-MOSFETs. All samples were subjected to PDA at $800^{0}$ C and post Si deposition annealing at $1000^{0}$ C.                                                                                                                                                                                                                                                                                                                         | 30   |

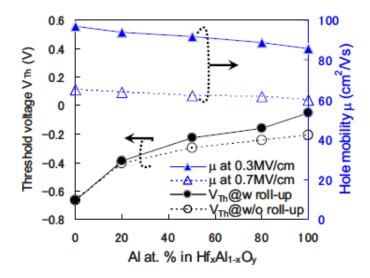

| 2.17   | Dependencies of $V_{th}$ and hole mobility at both 0.3 and 0.7 MV/cm on Al content in $Hf_xAl_{1-x}O_y$ for $NiSi/Hf_xAl_{1-x}O_y$ / $SiO_2(1 \text{ nm})$ / $Si$ $p$ -MOSFETs. The closed circles stand for experimental $V_{th}$ that takes $V_{th}$ roll-up effects into consideration and the open circles stand for estimated $V_{th}$ that excludes $V_{th}$ roll-up effects, which have been calculated qualitatively by comparing measured data with fitted linear $V_{th}$ -EOT relationship in Fig. 2.16 | 31   |

| 2.18   | Defect levels within the bulk high-κ in the context of MOS energy-band diagram                                                                                                                                                                                                                                                                                                                                                                                                                                     | 35   |

# LIST OF FIGURES (Continued)

| Figure |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Page |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

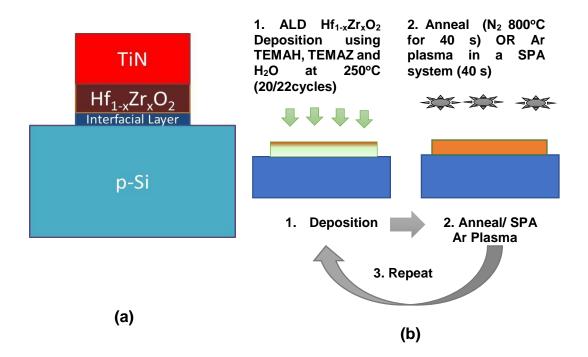

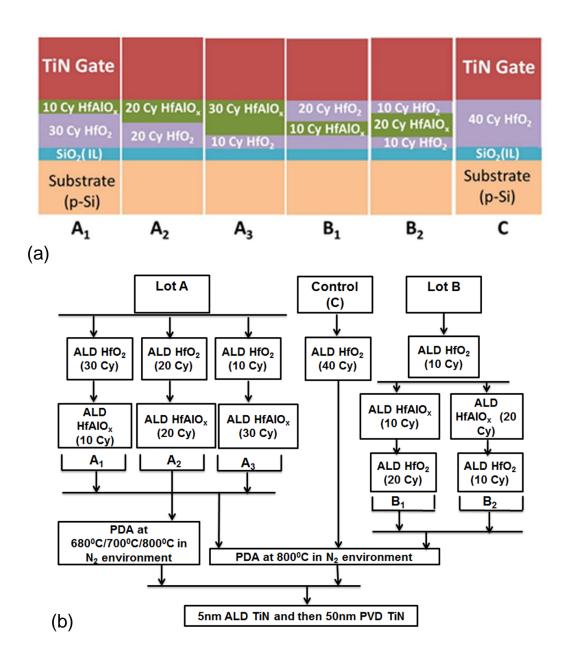

| 3.1    | (a) Device structure of TiN/Hf <sub>1-x</sub> Zr <sub>x</sub> O <sub>2</sub> /SiON/p-Si MOSCAP, (b) dielectric deposition with cyclic deposition and annealing (DADA) cyclic SPA plasma exposure (DSDS).                                                                                                                                                                                                                                                                              | 34   |

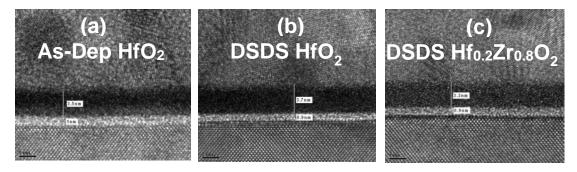

| 3.2    | TEM images for (a) As-Dep HfO <sub>2</sub> , (b) DSDS HfO <sub>2</sub> , and (c) DSDS Hf $_{0.2}$ Zr $_{0.8}$ O <sub>2</sub>                                                                                                                                                                                                                                                                                                                                                          | 36   |

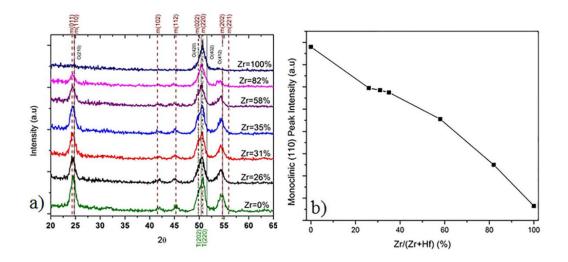

| 3.3    | a) GIIXRD spectra of DADA $Hf_{1-x}Zr_xO_2$ as a function of Zr% in the dielectrics, b) intensity of monoclinic (110) diffraction peak as a function of $Zr/(Zr+Hf)\%$ in the dielectrics                                                                                                                                                                                                                                                                                             | 37   |

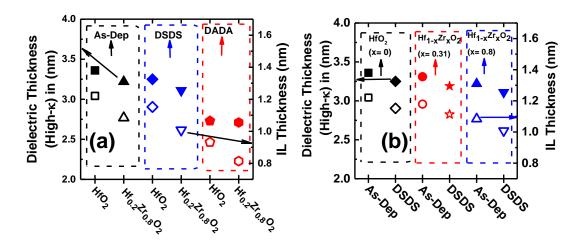

| 3.4    | (a) Dielectric thickness (filled symbols on left scale) and interfacial layer (IL) thickness (open symbols on right scale) for MOSCAPs with DSDS, DADA, and As-Dep HfO <sub>2</sub> and Hf <sub>0.2</sub> Zr <sub>0.8</sub> O <sub>2</sub> , (b) Dielectric thickness (filled symbols on left scale) and interfacial layer (IL) for Hf <sub>1-x</sub> Zr <sub>x</sub> O <sub>2</sub> with x=0, 0.31, and 0.8 for DSDS and As-Dep processing conditions.                               | 37   |

| 3.5    | (a) Device structure for Al incorporation in HfO <sub>2</sub> , (b) Device fabrication process flow                                                                                                                                                                                                                                                                                                                                                                                   | 40   |

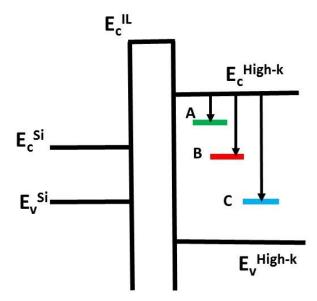

| 3.6    | Defect levels within the bulk high- $\kappa$ in the context of MOS energy-band diagram.                                                                                                                                                                                                                                                                                                                                                                                               | 44   |

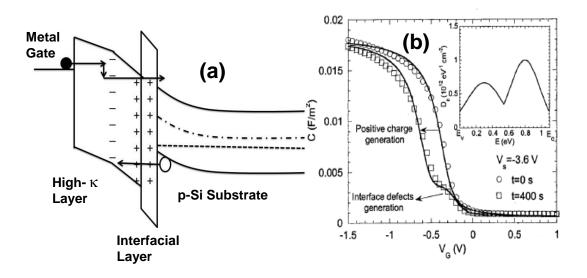

| 3.7    | (a) Band diagram showing positive charge formation in the dielectric under stress in the gate injection mode, (b) Capacitance–voltage characteristics of <i>p</i> -Si/SiO <sub>2</sub> /ZrO <sub>2</sub> /TiN structures measured before and after constant gate voltage stress at -3.6 V for 400 s. Solid lines are fits to the data using a computer simulation. Inset: Energetic distribution of interface defects used for simulation of the <i>C</i> – <i>V</i> characteristics. | 46   |

## (Continued)

| Figure |                                                                                                                                                                                                                                                                                                                                                                                                                        | Page |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

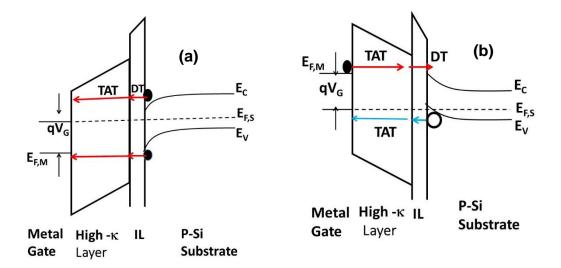

| 3.8    | Band diagram showing trap assisted tunneling (TAT) through high- $\kappa$ layer and direct tunneling (DT) through interfacial layer (IL) during (a) positive gate bias and (b) negative gate bias. Electron tunneling is shown by red line and hole tunneling is shown by blue line                                                                                                                                    | 40   |

|        |                                                                                                                                                                                                                                                                                                                                                                                                                        | 48   |

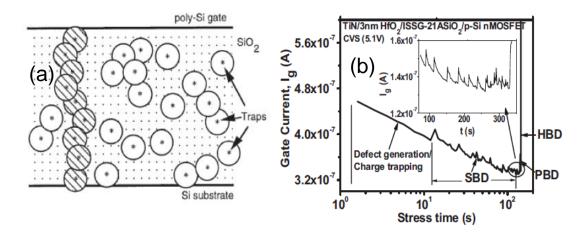

| 3.9    | Formation of percolation path (shaded spheres) due to trap generation (b) Different breakdown regimes during constant voltage stress                                                                                                                                                                                                                                                                                   | 50   |

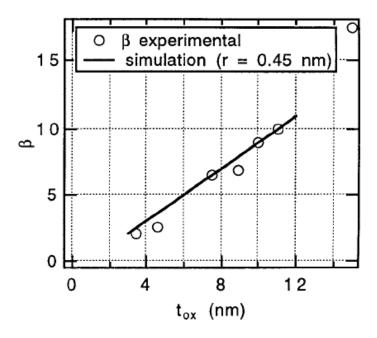

| 3.10   | Dependence of Weibull slope $\beta$ of the charge to breakdown, $Q_{BD}$ on oxide thickness.                                                                                                                                                                                                                                                                                                                           | 52   |

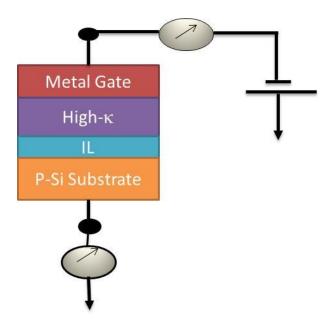

| 3.11   | Stressing MOS capacitor at a constant voltage stress in the gate injection mode                                                                                                                                                                                                                                                                                                                                        | 56   |

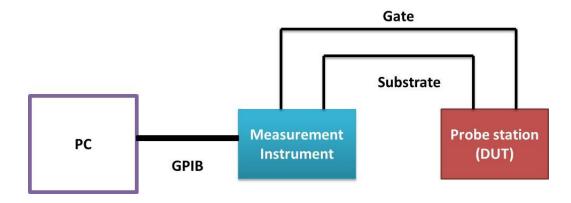

| 3.12   | Basic arrangement for electrical measurement automation of a simple two-terminal device, e.g., MOS-Capacitor                                                                                                                                                                                                                                                                                                           | 57   |

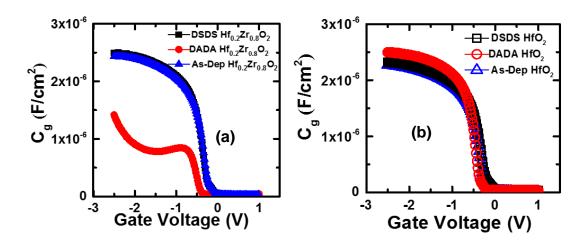

| 4.1    | Comparison of CV characteristics for (a) Hf <sub>0.2</sub> Zr <sub>0.8</sub> O <sub>2</sub> with DSDS, DADA and As-Dep samples and (b) HfO <sub>2</sub> with DSDS, DADA and As-Dep samples                                                                                                                                                                                                                             | 60   |

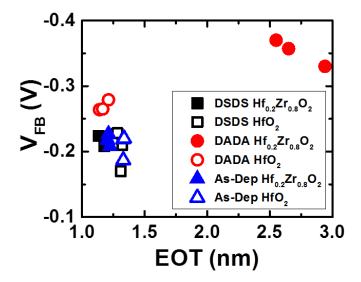

| 4.2    | Flat-band voltage $V_{FB}$ , as a function of EOT for $Hf_{0.2}Zr_{0.8}O_2$ and $HfO_2$ with DSDS, DADA, and As-Dep processing                                                                                                                                                                                                                                                                                         | 61   |

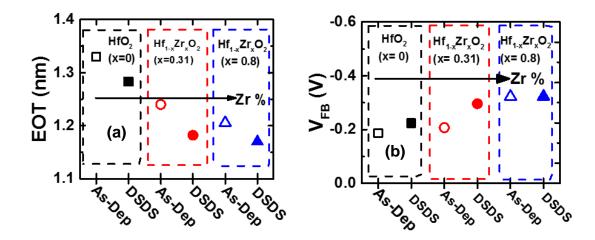

| 4.3    | (a) Comparison of EOT for DSDS and As-Dep MOSCAPs with HfO <sub>2</sub> (x=0), Hf <sub>1-x</sub> Zr <sub>x</sub> O <sub>2</sub> (x=0.31), and Hf <sub>1-x</sub> Zr <sub>x</sub> O <sub>2</sub> (x=0.8), (b) flat-band voltage variation for the devices with intermediate SPA plasma and without plasma as a function of zirconium percentage. Filled symbols represent DSDS and open symbols represent As-Dep samples | 63   |

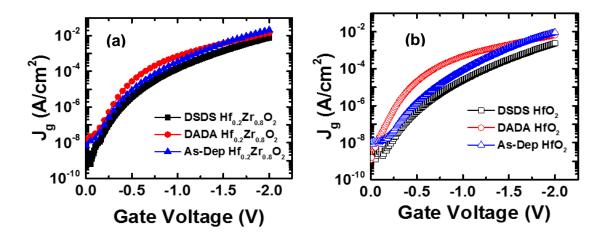

| 4.4    | Comparison of <i>J-V</i> characteristics of (a) DSDS, DADA, and As-Dep Hf <sub>0.2</sub> Zr <sub>0.8</sub> O <sub>2</sub> and, (b) DSDS, DADA, and As-Dep HfO <sub>2</sub>                                                                                                                                                                                                                                             | 64   |

## (Continued)

| Figure |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Page |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

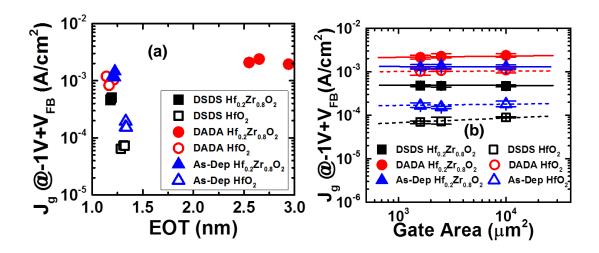

| 4.5    | (a) Gate leakage current density, $Jg$ sensed at -1V+ $V_{FB}$ as a function of EOT for dielectrics with cyclic plasma treatment (DSDS), cyclic annealing (DADA), and As-Dep processing schemes, (b) comparison of gate leakage current density for MOS capacitors with $40\mu m \times 40\mu m$ , $50\mu m \times 50\mu m$ , and $100\mu m \times 100\mu m$ gate area                                                                                                                                                              | 65   |

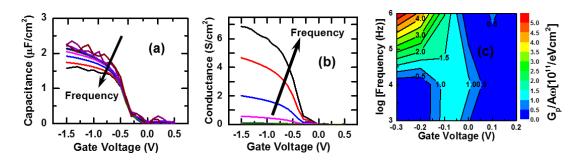

| 4.6    | (a) Frequency dependent C-V characteristics, (b) G-V characteristics measured at different frequencies, and (c) map of the normalized parallel conductance $Gp/A\omega$ , as a function of gate bias and frequency. Measurement frequency was varied from 1 MHz to 100 Hz                                                                                                                                                                                                                                                           | 66   |

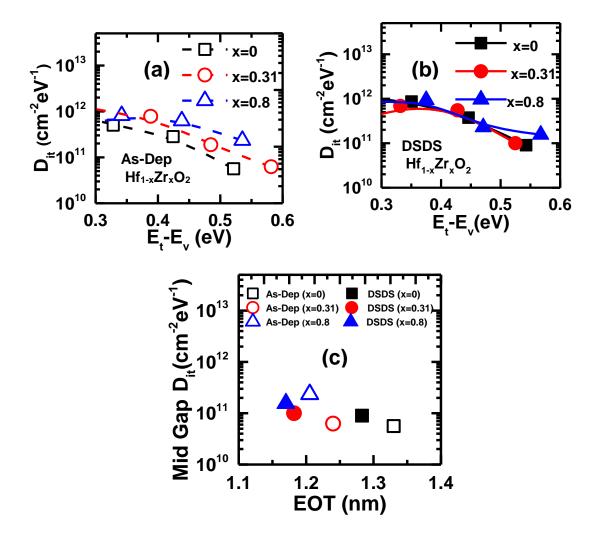

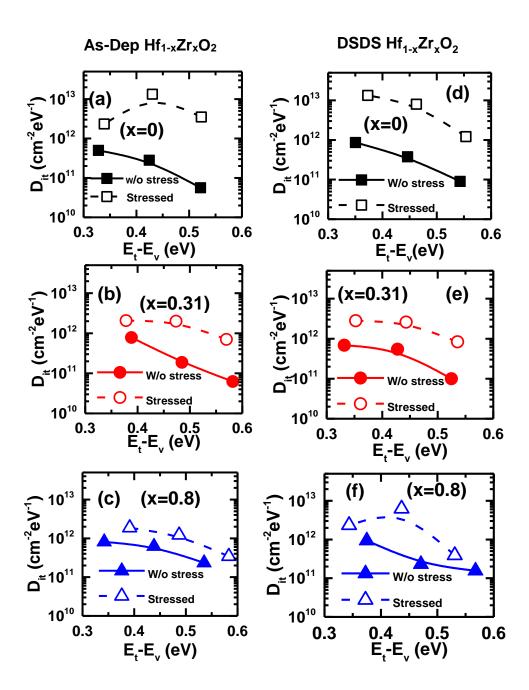

| 4.7    | (a-b) $D_{it}$ as a function of trap level (E <sub>t</sub> -E <sub>v</sub> : energy difference between trap level, E <sub>t</sub> and the majority carrier band edge, E <sub>v</sub> ) in the Si band gap for As-Dep Hf <sub>1-x</sub> Zr <sub>x</sub> O <sub>2</sub> and for DSDS Hf <sub>1-x</sub> Zr <sub>x</sub> O <sub>2</sub> with x=0, 0.31, and 0.8, and (c) comparison of mid-gap level $D_{it}$ as a function of EOT for different dielectrics.                                                                           | 68   |

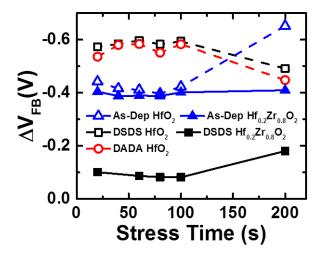

| 5.1    | Flat-band voltage shift ( $\Delta V_{FB}$ ) as a function of stress time for HfO <sub>2</sub> with As-Dep, DSDS, and DADA processing and Hf <sub>0.2</sub> Zr <sub>0.8</sub> O <sub>2</sub> with As-Dep, and DSDS processing conditions                                                                                                                                                                                                                                                                                             | 73   |

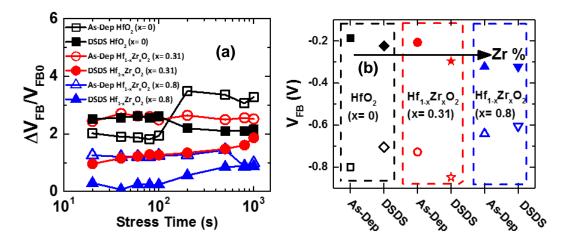

| 5.2    | (a) Stress induced flat-band voltage shifts as a function of stress time, (b) Flat-band voltage before and after stress for MOSCAPs with increasing Zr content, $HfO_2(x=0)\rightarrow (squares)$ , $Hf_{1-x}Zr_xO_2$ with $x=0.31\rightarrow (circles)$ , and $Hf_{1-x}Zr_xO_2$ with $x=0.8\rightarrow (triangles)$ with a constant voltage stress for 1000s in the gate injection mode. The filled symbols represent the flat-band voltage for unstressed devices, whereas open symbols represent after-stress flat-band voltages | 75   |

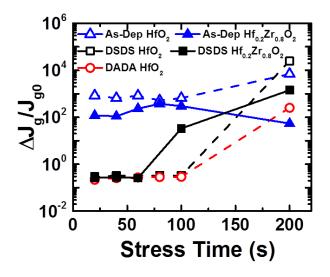

| 5.3    | Comparison of stress induced leakage current ( $\Delta J_g/J_{g0}$ ) sensed at -1V for different dielectrics                                                                                                                                                                                                                                                                                                                                                                                                                        | 77   |

## (Continued)

| Figure |                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Page |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

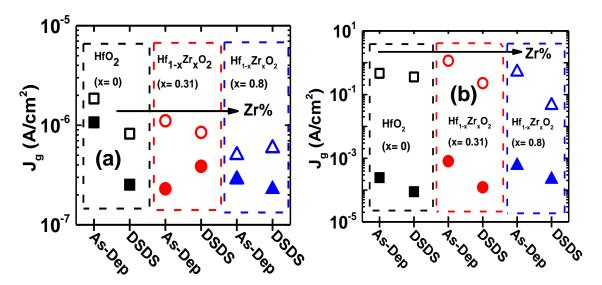

| 5.4    | Gate leakage current density for unstressed devices (closed symbols) and for stressed devices (open symbols) for DSDS and As-Deposited MOSCAPs with HfO <sub>2</sub> (x=0), Hf <sub>1-x</sub> Zr <sub>x</sub> O <sub>2</sub> (x=0.31)), and Hf <sub>1-x</sub> Zr <sub>x</sub> O <sub>2</sub> (x=0.8) at a constant voltage stress for 1000s in the gate injection mode. Post stress measurement (a) at $E_{OX} = 10$ MV/cm and (b) at $E_{OX} = -10$ MV/cm | 78   |

| 5.5    | Interface state density, $D_{it}$ in the Si-band gap for unstressed devices (filled symbols with solid lines) and for stressed devices (open symbols with dashed lines). Constant voltage stress was applied in the gate injection mode for 1000s. Stress voltage was ranged between -3V to -3.4V according to the variation of EOT and flat-band voltage shift for different dielectrics.                                                                 | 81   |

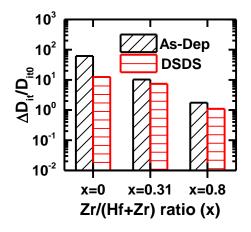

| 5.6    | Change in mid-gap $D_{it}$ for As-Dep and DSDS Hf <sub>1-x</sub> Zr <sub>x</sub> O <sub>2</sub> with x=0, 0.31, and 0.8                                                                                                                                                                                                                                                                                                                                    | 82   |

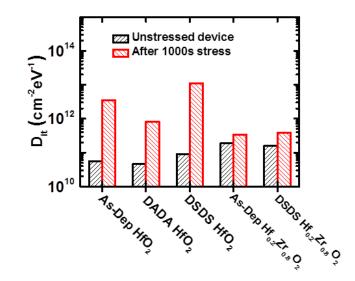

| 5.7    | Interface state density, $D_{it}$ in the mid gap level for unstressed devices and for devices stressed with a constant voltage stress for 1000s                                                                                                                                                                                                                                                                                                            | 83   |

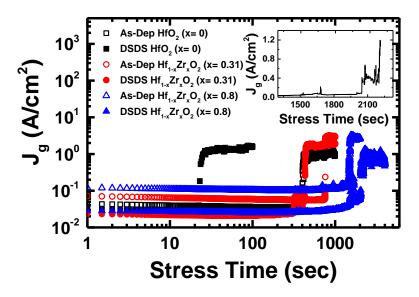

| 5.8    | Breakdown characteristics during gate injection stress showing electron trapping, soft breakdown and hard breakdown. Inset shows progressive breakdown prior to hard breakdown for DSDS $Hf_{1-x}Zr_xO_2$ (x=0.8).                                                                                                                                                                                                                                         | 85   |

| 5.9    | Weibull plot of time to breakdown ( $T_{BD}$ ) for DSDS and As-Dep $Hf_{1-x}Zr_xO_2$ with different $Zr$ percentages.                                                                                                                                                                                                                                                                                                                                      | 86   |

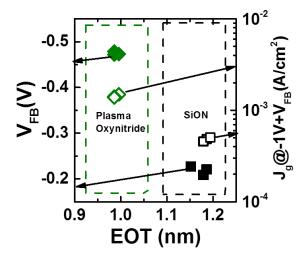

| 5.10   | Comparison of $V_{FB}$ (filled symbols : left scale), and $J_g$ @-1V+ $V_{FB}$ (open symbols: right scale) for DSDS Hf <sub>0.2</sub> Zr <sub>0.8</sub> O <sub>2</sub> with SiON and plasma oxynitride interfacial layers.                                                                                                                                                                                                                                 | 89   |

# LIST OF FIGURES (Continued)

| Figure |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Page |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

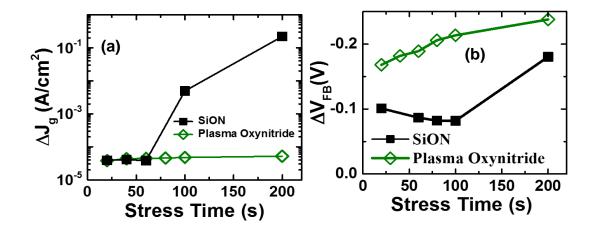

| 5.11   | $\Delta I_g$ as a function of stress time for DSDS Hf <sub>0.2</sub> Zr <sub>0.8</sub> O <sub>2</sub> with SiON and plasma oxynitride interfacial layers, (b) comparison of stress induced flat-band voltage shift ( $\Delta V_{FB}$ ) as a function of stress time                                                                                                                                                                                                                                                                      | 89   |

| 5.12   | (a) $D_{it}$ in the Si band gap for SiON and plasma oxynitride interfacial layer, and (b) change in mid gap $D_{it}$ for two different type of interfacial layer.                                                                                                                                                                                                                                                                                                                                                                        | 90   |

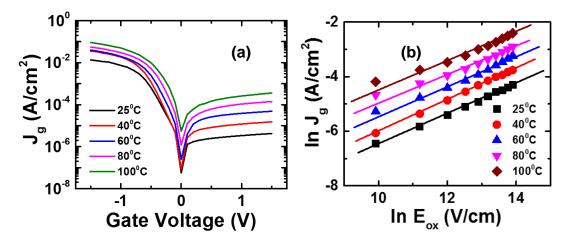

| 5.13   | (a) Current voltage (I-V) characteristics at elevated temperatures, (b) $ln(J_g)$ as a function of $ln(E_{ox})$ in the negative bias region                                                                                                                                                                                                                                                                                                                                                                                              | 92   |

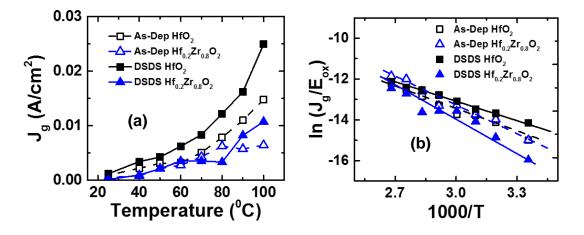

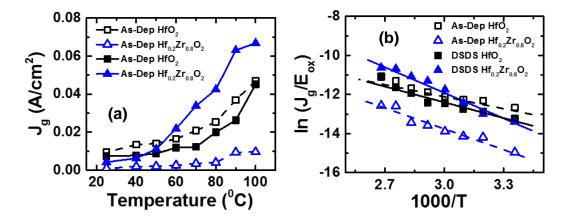

| 5.14   | (a) Gate leakage current sensed at -0.5V for DSDS and As-Dep $Hf_{1-x}Zr_xO_2$ (x=0 and 0.8), (b) $ln(J_g/E_{ox})$ vs 1000/T (Arrhenius plot) for different dielectrics.                                                                                                                                                                                                                                                                                                                                                                 | 93   |

| 5.15   | (a) $J_g$ as a function of temperature for devices stressed at -2V for 500s, (b) Arrhenius plots for different dielectrics                                                                                                                                                                                                                                                                                                                                                                                                               | 94   |

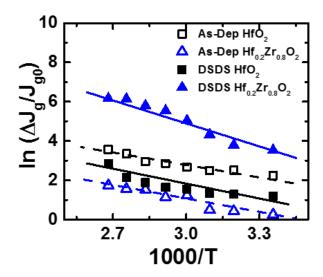

| 5.16   | Arrhenius plot for SILC activation energy for HfO <sub>2</sub> and Hf <sub>0.2</sub> Zr <sub>0.8</sub> O <sub>2</sub> with DSDS and As-Dep processing conditions. Devices were stressed at -2V in the gate injection mode for 500s.                                                                                                                                                                                                                                                                                                      | 97   |

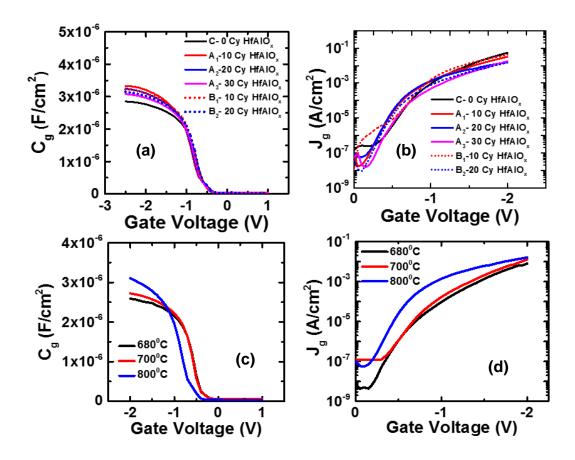

| 6.1    | (a) Capacitance voltage characteristics comparison for Lot $A(A_1, A_2, A_3)$ , Lot $B(B_1 \text{ and } B_2)$ and Lot $C$ (control device) (b) gate voltage (V) vs leakage current density $(J_g)$ for different dielectrics for both Lot $A$ , and Lot $B$ with $HfAlO_x$ in layered structure and for the control sample, $C$ with $HfO_2$ . PDA temperature was $800^0C$ for these dielectrics (a-b). Comparison of $C$ -V and $J$ -V plots for $A_2(20 \text{ Cy } HfAlO_x)$ with PDA temperature variation are shown in (c) and (d) | 102  |

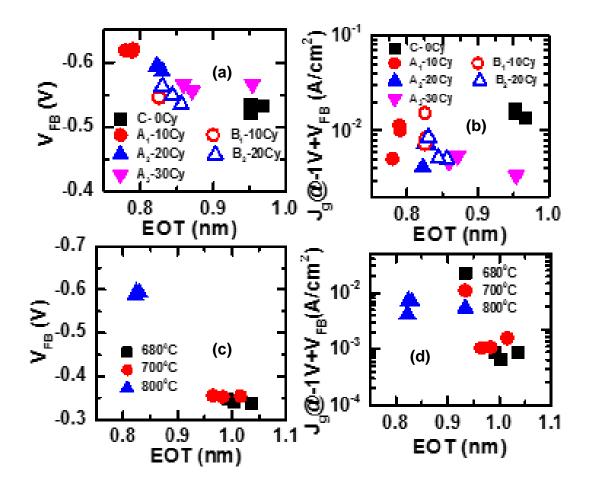

| 6.2    | (a)-(b) Flat-band voltage, $V_{FB}$ and gate leakage current, $J_g$ sensed at -1V+ $V_{FB}$ as a function of EOT for dielectrics annealed at 800°C. Comparison for $A_2$ with 20Cy HfAlO <sub>x</sub> annealed at 680°C, 700°C, and 800°C in (c)-(d). For possible variation analysis, three devices from each device types are presented (a-d)                                                                                                                                                                                          | 104  |

# LIST OF FIGURES (Continued)

| Figure |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Page |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

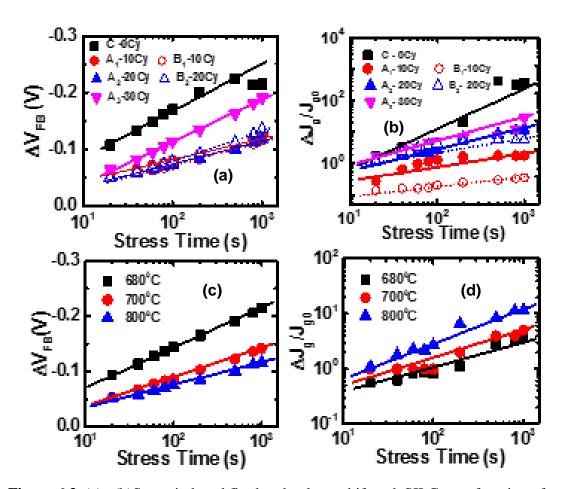

| 6.3    | (a) –(b)Stress induced flat-band voltage shift and SILC as a function of stress time for dielectrics annealed at $800^{\circ}$ C. Applied stress voltage in the gate injection mode was varied in the range -2.18V to -2.57V according to EOT and V <sub>FB</sub> variation to have equal stress field across all dielectrics. Evolution of $\Delta V_{FB}$ and SILC as a function of time for A <sub>2</sub> annealed at $680^{\circ}$ C, $700^{\circ}$ C, and $800^{\circ}$ C in (c)-(d) | 108  |

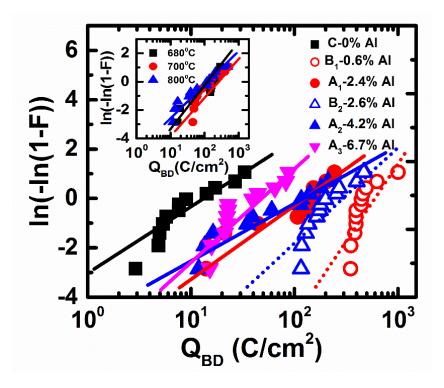

| 6.4    | Weibull plot of charge to breakdown, Q <sub>BD</sub> for devices with Al incorporation in HfO <sub>2</sub> . Inset shows Weibull plot for A <sub>2</sub> with different annealing temperatures.                                                                                                                                                                                                                                                                                            | 113  |

#### **CHAPTER 1**

#### INTRODUCTION, MOTIVATION AND OBJECTIVES

#### 1.1 Introduction

According to the International Technology Roadmap for Semiconductor (ITRS) 2013 updates [1], many physical dimensions of transistors are expected to be crossing the 10 nm threshold in the years 2020-2025. Continuous device scaling leads to a decrease in cost per function of technology and improves the economic productivity and the quality of life through proliferation of computers, communication, and other industrial and consumer electronics. With the scaling of devices below the 45 nm technology node, high-κ gate dielectric materials emerged as a replacement of SiO<sub>2</sub> in the high performance (HP) logic family and low standby power (LSTP) logic family [2]. HfO<sub>2</sub> based dielectric materials have been considered as the most promising alternative of SiO<sub>2</sub> in the CMOS technology because of their quality superior to other high-κ dielectrics considering CMOS compatibility, higher dielectric constant, suitable band offset with Si, and good thermal stability with Si [2-3].

Although research on the high-κ (HK)/metal gate (MG) started in mid 90s, the first successful use of HfO<sub>2</sub> as a dielectric in the high volume manufacturing industry emerged in early 2007 by Intel in the 2007 processor series codenamed Penryn [4]. Research on HK/MG is continuing to scale the equivalent oxide thickness (EOT) to sub 0.7 nm as well to have better quality dielectrics [1-3]. Improvement came in the deposition process and treatment during and after the deposition of gate stacks [5-16]. Further investigations were

carried out with incorporating other materials like Zr or Al into HfO<sub>2</sub> in order to foster device scaling and their performance enhancement [17-34].

Recently, various interleaved treatments in the ALD deposition process of Hf-based high-k dielectrics have attracted tremendous attention in order to enhance the quality of dielectrics for CMOS technology [5-11]. Multiple deposition and annealing was reported to be beneficial for better film properties and enhanced device performance as compared to a single post deposition annealing (PDA) [12-16]. The addition of Zr in HfO<sub>2</sub> was also shown to be beneficial for better EOT downscaling by several reports [17-21]. Recently, Clark et al. [11] observed that the use of a cyclical deposition and annealing technique, DADA, during the ALD HfO<sub>2</sub> deposition could result in a better EOT downscaling with one order of magnitude reduction in the gate leakage current as compared to the PDA HfO<sub>2</sub>. The same DADA process was also extended to Hf<sub>1-x</sub>Zr<sub>x</sub>O<sub>2</sub> [35], which showed that this process can result a tetragonal (111) fiber texture for Hf<sub>1-x</sub>Zr<sub>x</sub>O<sub>2</sub> with more than 50% Zr addition in HfO<sub>2</sub> in contrast to a random orientation in PDA films. It is known that among different crystalline phases of HfO<sub>2</sub> and ZrO<sub>2</sub>, the tetragonal phase offers a higher dielectric constant as compared to the monoclinic phase which is the thermodynamically stable phase for these dielectrics [3, 36]. For PDA Hf<sub>1-x</sub>Zr<sub>x</sub>O<sub>2</sub> films, a partial stabilization of the tetragonal phase was also achieved for around 60% Zr/(Hf+Zr) [36]. It was found that the addition of Zr in HfO<sub>2</sub> decreases the grain size, which in turn decreases the driving force for a tetragonal to monoclinic transition [36].

In addition to thermal annealing, interleaved treatment in the ALD deposition process was found to enhance device performance by using room temperature ultraviolet ozone, D<sub>2</sub>O radical, and remote microwave N<sub>2</sub>O plasma [5-6,8-10]. Recently, it has been

reported that the poor dielectric characteristics of CVD and ALD grown silicon oxide films can be improved by exposing them to a slot-plane-antenna (SPA) plasma with various gases such as O<sub>2</sub>/Ar, Ar, O<sub>2</sub>/He [37-39]. The SPA plasma provides a high-density plasma with low electron temperature, where the radicals diffuse from the plasma generation region to the wafer surface. The SPA plasma is also a very low damage plasma process compared to conventional inductively coupled plasma (ICP) or electron cyclotron resonance (ECR) plasma [39]. It was found that the SPA plasma helps better film densification as well as improved interfacial layer growth [39-40]. This research has utilized cyclic deposition and annealing (DADA), and cyclic deposition and SPA plasma exposure (DSDS) during the ALD Hf<sub>1-x</sub>Zr<sub>x</sub>O<sub>2</sub> deposition process.

Another process of foreign material incorporation in HfO<sub>2</sub> is to add Al in HfO<sub>2</sub>. The incorporation of aluminum into HfO<sub>2</sub> by forming (HfO<sub>2</sub>)<sub>1-x</sub>(Al<sub>2</sub>O<sub>3</sub>)<sub>x</sub> films [22-31] or HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> bi-layers [23, 32-33] was reported to be promising for high- $\kappa$  on silicon and high mobility substrates. For ALD (HfO<sub>2</sub>)<sub>1-x</sub>(Al<sub>2</sub>O<sub>3</sub>)<sub>x</sub> films, Ho *et al.* (x: 0.25 $\leftrightarrow$ 0.8) [26], Yu *et al.* (x: 0.15 $\leftrightarrow$ 0.33) [27], and Wilk *et al.* (x: 0.5 and 0.75) [28] demonstrated a significant increase in the amorphous to polycrystalline transition temperature when aluminum was incorporated into HfO<sub>2</sub>. This characteristic, in turn, helps to eliminate electrical and mass transport along the grain boundaries. Also, Park *et al.* [25] demonstrated an ALD Hf aluminate film with (002) oriented tetragonal phase stabilization with increased dielectric constant by the addition of Al<sub>2</sub>O<sub>3</sub> into HfO<sub>2</sub>. Recently, Tapily *et al.* [34] reported a mixed structure of tetragonal and monoclinic phase formation for ALD Hf<sub>1-x</sub>Al<sub>x</sub>O<sub>y</sub> (x=0 to 0.25) with 2Å lower EOT and one order of magnitude reduced gate leakage current. Reductions in oxygen vacancy and in carbon in the film were also

observed for HfAlO<sub>x</sub> films [30, 41]. For HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> bilayer structures, Cho *et al.* [32], and Nishimura *et al.* [33] showed an improved thermal stability for dielectrics annealed up to 900°C. A comparative study showed that incorporation of Al in the alloy form provides a better EOT downscaling potential with a reduced gate leakage current as compared to the bilayer form [23]. However, Al diffusion after annealing can introduce fixed charges near the Si/SiO interface [42]. Also, an increased Al incorporation can shift flat-band voltage by forming a dipole layer at high-κ/SiO<sub>x</sub> interface [43-45]. Therefore, in order to get good control on the device threshold voltage for highly scaled transistors, an extremely low Al incorporation is desirable.

Reliability is a critical concern for high-κ dielectrics in order to integrate them into mainstream commercial integrated circuits. Gate stack reliability can be evaluated by understanding the charge trapping behavior of the dielectric and its response to the electrical stress [46-51]. Stress induced flat-band voltage shifts [49, 52] and stress-induced leakage currents (SILC) [53-54] demonstrate the robustness of these films. HfO<sub>2</sub> has been widely studied for its reliability under different stress conditions [46-55]. HfO<sub>2</sub> emerged as an early favorite because of its slightly higher band gap and comparatively better thermal stability as compared to ZrO<sub>2</sub> [3]. As devices are now fabricated with an intentionally grown interfacial layer [1-3], ALD Hf<sub>1-x</sub>Zr<sub>x</sub>O<sub>2</sub> can be considered as an alternative of HfO<sub>2</sub> for next generation CMOS devices. Also, PDA Hf<sub>1-x</sub>Zr<sub>x</sub>O<sub>2</sub> showed reduced V<sub>T</sub> shift, lower C-V hysteresis, and higher time to failure as compared to HfO<sub>2</sub> [17, 21, 56]. As the cyclic SPA plasma treatment (DSDS), and the cyclic thermal annealing (DADA) are promising, impact of these intermediate treatment on the reliability of ALD HfO<sub>2</sub> and Hf<sub>1-x</sub>Zr<sub>x</sub>O<sub>2</sub> needs to be analyzed in detail. Although HfAlO<sub>x</sub> has been studied with both (HfO<sub>2</sub>)<sub>1-x</sub>(Al<sub>2</sub>O<sub>3</sub>)<sub>x</sub>

alloy structures and HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> bilayer structures, they did not meet reliability challenges because of comparatively higher Al (more than 6% Al) incorporation in HfO<sub>2</sub> [23-24, 57-58]. For Al incorporated HfO<sub>2</sub>, Samanta *et al.* [57] studied electrical stress induced charge carrier generation/trapping related degradation of HfAlO<sub>x</sub>/SiO<sub>2</sub> for 1:1 weight ratio of HfO<sub>2</sub>-Al<sub>2</sub>O<sub>3</sub> incorporated in the high-κ/metal gate structure. Intrinsic time zero dielectric breakdown characteristics of HfAlO<sub>x</sub> alloys (Al% ranged from 8 to 78%) for metal-insulator-metal (MIM) capacitors were also studied [58]. But these studies did not address the impact of Al incorporation on either the dielectric/metal gate interface or on the Si/SiO<sub>x</sub> interface for the high-κ/metal gate devices in CMOS technology. A detailed study of the reliability for the high-κ/metal gate with a variation in Al concentration near the high-κ/metal gate interface and the Si/SiO<sub>x</sub> interface is, therefore, required. Additionally, since the standard thermal process required for source/drain activation in CMOS devices can be as high as 1000°C [59], a post deposition annealing temperature variation can also impact the dielectric.

Since Zr or Al incorporation in HfO<sub>2</sub> and interleaved treatment processes are promising, the reliability of these dielectrics needs to be investigated. The knowledge of stress induced defects, defect activation energy, and charge to breakdown can improve the understanding of their effects on device reliability. Also, it is known that even though the EOT is successfully scaled in some processes, the performance of the MOS device strongly depends on the quality of the interface between the silicon substrate and the interfacial layer [60-64]. In addition, the process-induced interface traps also significantly influence the long term reliability of the devices. Interface traps, the result of a structural imperfection, act as generation/recombination centers with an energy distribution

throughout the silicon band gap. When the device is in operation, electrons or holes occupy interface traps and contribute to the threshold voltage shift. They also contribute to leakage current, low-frequency noise, reduced mobility, drain current, and transconductance [60]. It was found that under the NBTI stress, the density of generated traps is higher in the proximity of the interfacial layer [61]. Minimizing the interface state degradation due to the electrical stress during device operation is considered a critical task for the semiconductor industry [62-64]. Density of interface states,  $D_{ii}$  versus energy, E, at the Si/IL interface provides a comprehensive understanding of the impact of various process conditions on interface defects. Also, an understanding of the impact of electrical stress on interface state generation for these dielectrics will help their integration in future CMOS technology.

#### **1.2 Motivation and Approach**

In order to integrate new materials and processes to the emerging technology generations, they needs to be tested for quality and reliability. The reliability of high- $\kappa$  gate dielectric stack is influenced by both the high- $\kappa$  layer and the SiO<sub>2</sub> like interfacial layer which forms either spontaneously or intentionally in order to maintain a sufficient carrier mobility and to facilitate the growth of the high- $\kappa$  layer. The dielectric deposition process and treatments have significant influence on the dielectric constant and thickness of both layers, as oxygen vacancies and oxygen diffusion to the interface from the high- $\kappa$  layer vary under different conditions [65]. Also, control of the interface state density,  $D_{ii}$  is another reliability challenge for alternative high- $\kappa$  dielectrics, which strongly depends on processing conditions [60-64]. The impact of the SPA plasma treatment during the

deposition of ALD  $Hf_{1-x}Zr_xO_2$  on the interfacial layer or at the interface has not been thoroughly investigated yet. The impact of incorporated Al on Si/SiO<sub>x</sub> interface needs to be addressed in detail. It was found that electron trapping is comparatively higher in HK/MG stacks due to the presence of more oxygen vacancy defects [55]. Stress induced flat-band voltage shift, SILC, and  $\Delta D_{it}$  can provide the important reliability information for high- $\kappa$  dielectrics deposited with advanced processing. Under the electrical stress, the defect activation energy varies with different processing conditions [66-67]. High temperature measurements can help to understand the evolution of the defect level with the processing condition variation [66-68]. With the thinning of dielectric stacks, the time dependent dielectric breakdown (TDDB) becomes a vital reliability issue, as an increased gate leakage current degrades the TDDB reliability [55].

Even though Zr and Al incorporated dielectrics with advanced processing showed potential towards the EOT downscaling, their reliability needs to be investigated. Also, the reliability of dielectrics with intermediate treatments such as the cyclic SPA plasma exposure, or the cyclic thermal annealing needs to be analyzed in detail to evaluate the impact of these intermediate treatments. Therefore, this research attempts to find the effect of Zr and Al incorporation into Hf based high-κ dielectrics and the effects of intermediate treatments during the deposition process on the reliability of these dielectrics which would help its integration in future CMOS technologies.

To understand the impact of Zr addition, ALD  $Hf_{1-x}Zr_xO_2$  with x=0, 0.31, and 0.8 were deposited in nMOS capacitor with SiON interfacial layer and TiN metal gate. One set of dielectrics were subjected to the cyclic deposition and annealing termed as DADA and other set of dielectrics were subjected to the cyclic deposition and SPA Ar plasma exposure

termed as DSDS process. The control samples were deposited by standard as-deposition process. Using two different type of interfacial layers, (i) chemically grown oxide followed by radical flow nitridation (Chemox+RFN) and (ii) plasma oxynitride grown after removing chemically grown oxide (COR+SPAON), the influence of the intermediate plasma treatment on the interfacial layer was further investigated.

To incorporate extremely low percentage of Al in HfO<sub>2</sub>, ALD HfAlO<sub>x</sub> was deposited in a layered structure along with ALD HfO<sub>2</sub>. Two different lots, Lot A with HfAlO<sub>x</sub> as the top layer in a bilayer structure, and Lot B with HfAlO<sub>x</sub> as the intermediate layer sandwiched between two HfO<sub>2</sub> layers were studied along with the control sample C without any HfAlO<sub>x</sub> layer. In this process, Al/(Al+Hf)% in the range <1% to ~7% was obtained. Al concentration variation near the metal gate/high-k interface and near the Si/SiO<sub>2</sub> interface was obtained by changing the location and thickness of ALD HfAlO<sub>x</sub> layer in a multilayered gate stack.

The reliability of these dielectrics were evaluated by subjecting them to a constant voltage stress in the gate injection mode. The applied stress voltage was modified according to the variation in EOT and flat-band voltage to have an equal field across all dielectrics. The impact of stress on the flat-band voltage, the leakage current, and the interface stress density was analyzed for different processing conditions for Zr or Al incorporated HfO<sub>2</sub>. Also dielectrics were subjected to TDDB stress in the gate injection mode.

#### 1.3 Objectives