### New Jersey Institute of Technology

## Digital Commons @ NJIT

**Dissertations**

**Electronic Theses and Dissertations**

Summer 8-31-2016

## Electrical characterization of high-k gate dielectrics for advanced CMOS gate stacks

Yi Ming Ding New Jersey Institute of Technology

Follow this and additional works at: https://digitalcommons.njit.edu/dissertations

Part of the Electrical and Electronics Commons

#### **Recommended Citation**

Ding, Yi Ming, "Electrical characterization of high-k gate dielectrics for advanced CMOS gate stacks" (2016). Dissertations. 83.

https://digitalcommons.njit.edu/dissertations/83

This Dissertation is brought to you for free and open access by the Electronic Theses and Dissertations at Digital Commons @ NJIT. It has been accepted for inclusion in Dissertations by an authorized administrator of Digital Commons @ NJIT. For more information, please contact digitalcommons@njit.edu.

## **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

#### **ABSTRACT**

## ELECTRICAL CHARACTERIZATION OF HIGH-K GATE DIELECTRICS FOR ADVANCED CMOS GATE STACKS

### by Yi Ming Ding

The oxide/substrate interface quality and the dielectric quality of metal oxide semiconductor (MOS) gate stack structures are critical to future CMOS technology. As SiO<sub>2</sub> was replaced by the high-k dielectric to further equivalent oxide thickness (EOT), high mobility substrates like Ge have attracted increasing in replacing Si substrate to further enhance devices performance. Precise control of the interface between high-k and the semiconductor substrate is the key of the high performance of future transistor. In this study, traditional electrical characterization methods are used on these novel MOS devices, prepared by advanced atomic layer deposition (ALD) process and with pre and post treatment by plasma generated by slot plane antenna (SPA).

MOS capacitors with a TiN metal gate/3 nm HfAlO/0.5 nm SiO<sub>2</sub>/Si stacks were fabricated by different Al concentration, and different post deposition treatments. A simple approach is incorporated to correct the error, introduced by the series resistance ( $R_s$ ) associated with the substrate and metal contact. The interface state density ( $D_{it}$ ), calculated by conductance method, suggests that  $D_{it}$  is dependent on the crystalline structure of hafnium aluminum oxide film. The amorphous structure has the lowest  $D_{it}$  whereas crystallized HfO<sub>2</sub> has the highest  $D_{it}$ .

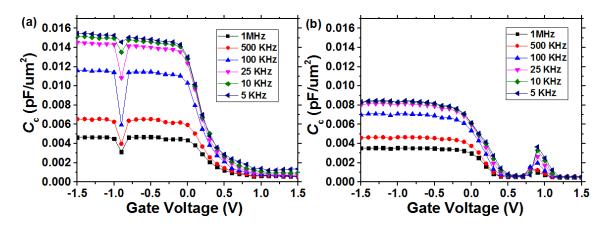

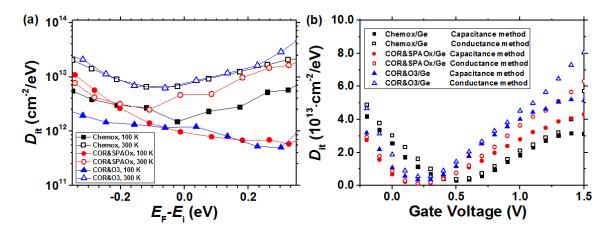

Subsequently, the dry and wet processed interface layers for three different p type Ge/ALD 1nm-Al<sub>2</sub>O<sub>3</sub>/ALD 3.5nm-ZrO<sub>2</sub>/ALD TiN gate stacks are studied at low temperatures by capacitance-voltage (CV), conductance-voltage (GV) measurement and

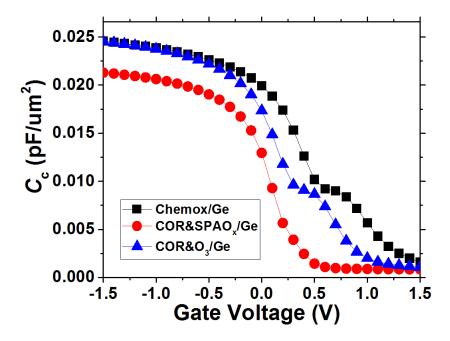

deep level transient spectroscopy (DLTS). Prior to high-k deposition, the interface is treated by three different approaches (i) simple chemical oxidation (Chemox); (ii) chemical oxide removal (COR) followed by 1 nm oxide by slot-plane-antenna (SPA) plasma (COR&SPAO<sub>x</sub>); and (iii) COR followed by vapor O<sub>3</sub> treatment (COR&O<sub>3</sub>). Room temperature measurement indicates that superior results are observed for slot-plane-plasma-oxidation processed samples.

The reliability of TiN/ZrO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/p-Ge gate stacks is studied by time dependent dielectric breakdown (TDDB). High-k dielectric is subjected to the different slot plane antenna oxidation (SPAO) processes, namely, (i) before high-k ALD (Atomic Layer Deposition), (ii) between high-k ALD, and (iii) after high-k ALD. High-k layer and interface states are improved due to the formation of GeO<sub>2</sub> by SPAO when SPAO is processed after high-k. GeO<sub>2</sub> at the interface can be degraded easily by substrate electron injection. When SPAO is processed between high-k layers, a better immunity of interface to degradation was observed under stress.

To further evaluate the high-k dielectrics and how EOT impacts on noise mechanism time zero 1/f noise is characterized on thick and thin oxide FinFET transistors, respectively. The extracted noise models suggest that as a function of temperatures and bias conditions the flicker noise mechanism tends to be carrier number fluctuation model (McWhorter model). Furthermore, the noise mechanism tends to be mobility fluctuation model (Hooge model) when EOT reduces.

## ELECTRICAL CHARACTERIZATION OF HIGH-K GATE DIELECTRICS FOR ADVANCED CMOS GATE STACKS

by Yi Ming Ding

A Dissertation

Submitted to the Faculty of

New Jersey Institute of Technology

in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy in Electrical Engineering

**Department of Electrical and Computer Engineering**

August 2016

Copyright © 2016 by Yi Ming Ding

ALL RIGHTS RESERVED

.

### APPROVAL PAGE

## ELECTRICAL CHARACTERIZATION OF HIGH-K GATE DIELECTRICS FOR ADVANCED CMOS GATE STACKS

### **Yi Ming Ding**

| Dr. Durgamadhab Misra, Dissertation Advisor<br>Professor of Electrical and Computer Engineering, NJIT | Date |

|-------------------------------------------------------------------------------------------------------|------|

| Dr. Leonid Tsybeskov, Committee Member<br>Professor of Electrical and Computer Engineering, NJIT      | Date |

| Dr. Marek Sosnowski, Committee Member Professor of Electrical and Computer Engineering, NJIT          | Date |

| Dr. Alan E. Delahoy, Committee Member<br>Research Professor of Physics, NJIT                          | Date |

| Dr. Purushothaman Srinivasan, Committee Member<br>Member of Technical Staff, Globalfoundries          | Date |

| Dr. Kandabara Tapily, Committee Member<br>Senior Engineering, Tokyo Electron Limited                  | Date |

### **BIOGRAPHICAL SKETCH**

**Author:** Yi Ming Ding

**Degree:** Doctor of Philosophy

**Date:** August 2016

### **Undergraduate and Graduate Education:**

- Doctor of Philosophy in Electrical Engineering,

New Jersey Institute of Technology, Newark, NJ, 2016

- Master of Science in Electrical Engineering,

New Jersey Institute of Technology, Newark, NJ, 2014

- Bachelor of Engineering in Measurement Technology and Instrument,

Nanjing University of Science and Technology, Nanjing, P. R. China, 2011

Major: Electrical Engineering

#### **Presentations and Publications:**

- Y. M. Ding, D. Misra, M. N. Bhuyian, K. Tapily, R. D. Clark, S. Consiglio, *et al.*, "Electrical Characterization of Dry and Wet Processed Interface Layer in Ge/high-k Devices," *J. Vac. Sci. Technol. B*, vol. 34, p. 021203 2016.

- Y. M. Ding, and D. Misra, "Oxide Structure-Dependent Interfacial Layer Defects of HfAlO/SiO<sub>2</sub>/Si Stack Analyzed by Conductance Method," *J. Vac. Sci. Technol. B*, vol. 33, p. 021203, 2014.

- Y. Ding, D. Misra, M. N. Bhuyiana, K. Tapily, R. D. Clarkb, S. Consigliob, *et al.*, "Electrical Characterization of Dry and Wet Processed Interface Layer in Ge/high-k Devices," in *ECS Trans.*, Pheonix, AZ, 2015, p. 313.

- Y. M. Ding and D. Misra, "Oxide Structure-Dependent Interfacial Layer Defects of HfAlO/SiO<sub>2</sub>/Si Stack Analyzed by Conductance Method," in *ECS Trans.*, Chicago, US, 2015, p. 245.

- S. Mukhopadhyay, S. Mitra, Y. M. Ding, K. L. Ganapathi, D. Misra, N. Bhat, *et al.*, "Effect of Post Plasma Oxidation on Ge Gate Stacks Interface Formation," in *ECS Trans.*, Sandiego, US, 2016, p. 303.

- D. Misra, M. N. Bhuyian, and Y. M. Ding, "Dielectric-Semiconductor Interface for high-k Gate Dielectrics for Sub-16 nm CMOS Technology," in *IEEE EDSSC*, Singapore, 2015, p. 95.

- Y. M. Ding, Z. Chen, D. Misra, A. E. Delahoy, G. E. Georghiou, X. Cao, *et al.*, "Spatial-Sensitive Feature of DLTS and Application in CdS/CdTe Solar Cells," in *EUPVSEC*, Hamburg, 2015, p. 3.49.

- Y. M. Ding, Z. Chen, X. Tan, D. Misra, A. E. Delahoy, and K. K. Chin, "Detection of Electron Emission as DLTS Signal in CdTe Solar Cells," submitted to *J. Appl. Phys.*

- Y. M. Ding, D. Misra, K. Tapily, R. D. Clark, S. Consiglio, C. S. Wajda, and G. J. Leusink, "Impact of Slot Plane Antenna Annealing on Carrier Transport Mechanism and Reliability on ZrO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/Ge Gate Stack" in preparation.

- Y. M. Ding, D. Misra, and P. Srinivasan, "Flicker Noise Mechanism on Thick and Thin Oxide FinFET" in preparation.

感谢我的父母和激励过我的人 To my parents and those encouraged me

#### **ACKNOWLEDGMENT**

I would like to express my sincere appreciation to my dissertation and academic advisor, Dr. Durgamadhab Misra. It's his effort, which brings me to the door of semiconductor characterization. Under his guidance, I have not only gained the knowledge but also professional communication skills. Besides, I would like to thank my committee members who gave me valuable suggestion during the research, Dr. Leonid Tsybeskov, Dr. Marek Sosnowski, Dr. Alan E. Delahoy, Dr. Purushothaman Srinivasan and Dr. Kandabara Tapily.

I would like to also thank Dr. Kandabara Tapily, Dr. Robert Clark, Dr. Steve Consiglio, Cory Wajda, Dr. Gert Leusink and other researchers of TEL Technology Center, America, LLC, Albany, NY, for supplying devices used in this research and sponsorship for this research.

During my research study, I spent a great deal of time with my colleagues, and they also assisted me with my work when it was necessary. They are, but no limited to: Dr. Md Nasir Uddin Bhuyian, Dr. Zi Meng Cheng, Dr. Xue Hai Tan, Peter Paliwoda, Sromana Mukhopadhyay and Shilpa, Mitra.

Finally, I have to express my love to my parents, who encouraged me to achieve a Ph. D degree. Without their encouragement and support, I could not have achieved this.

## TABLE OF CONTENTS

| Cl | hapte    | er                                                                  | Page |

|----|----------|---------------------------------------------------------------------|------|

| 1  | INT      | RODUCTION                                                           | 1    |

|    | 1.1      | Motivation and Objectives                                           | 5    |

|    | 1.2      | Proposal Organization.                                              | 6    |

| 2  |          | ERATURE REVIEW: HIGH-K MATERIAL AND ITS APPLICATION Si/Ge SUBSTRATE | 8    |

|    | 2.1      | Requirement of High-k and the Necessary Property of Implementation  | 8    |

|    |          | 2.1.1 Permittivity, Bandgap, and Band Alignment to Silicon          | 10   |

|    |          | 2.1.2 Thermodynamic Stability                                       | 11   |

|    |          | 2.1.3 Film Morphology and Deposition Method                         | 12   |

|    |          | 2.1.4 Interface Quality and Bulk Defects.                           | 13   |

|    |          | 2.1.5 Gate Compatibility and Process Compatibility                  | 15   |

|    | 2.2      | Interfacial Layer Scavenging.                                       | 17   |

|    | 2.3      | High-k Application on Ge Channel.                                   | 22   |

| 3  | MO<br>CH | S CAPACITOR DEVICE MODELLING AND ELECTRICAL ARACTERIZATION METHOD.  | 28   |

|    | 3.1      | MOS Capacitor Device Modeling.                                      | 28   |

|    | 3.2      | Electrical Characterization Method.                                 | 36   |

|    |          | 3.2.1 Low Frequency CV.                                             | 36   |

|    |          | 3.2.2 CV Hysteresis                                                 | 38   |

|    |          | 3.2.3 Conductance Method.                                           | 40   |

|    |          | 3.2.4 Deep Level Transient Spectroscopy (DLTS)                      | 44   |

# **TABLE OF CONTENTS** (Continued)

| Cl | hapte | er    |                                                                                                          | Page |

|----|-------|-------|----------------------------------------------------------------------------------------------------------|------|

|    |       | 3.2.5 | Flicker Noise.                                                                                           | 48   |

|    |       | 3.2.6 | IV Temperature Dependence                                                                                | 51   |

|    |       | 3.2.7 | Time Dependent Dielectric Breakdown (TDDB)                                                               | 52   |

| 4  |       |       | TRUCTURE-DEPENDENT INTERFACIAL LAYER DEFECTS SiO <sub>2</sub> /Si STACK ANALYZED BY CONDUCTANCE METHOD   | 55   |

|    | 4.1   | Resea | rch Motivation for Al Doped HfO <sub>2</sub> as High-k Dielectrics                                       | 55   |

|    | 4.2   | Devic | e Information and Experimental Procedure                                                                 | 58   |

|    | 4.3   | CV, G | V, EOT, Dielectric Constant, Leakage Current Density, $D_{\rm it}$ and $V_{\rm FB}$                      | 62   |

|    | 4.4   | Discu | ssion on the Role of Aluminum in HfO <sub>2</sub>                                                        | 69   |

| 5  |       | -     | CAL CHARACTERIZATION OF DRY AND WET PROCESSED CE LAYER IN Ge/HIGH-K DEVICES                              | 78   |

|    | 5.1   | Resea | rch Motivation for Interface Treatment of High-k/Ge                                                      | 78   |

|    | 5.2   | Devic | e Information and Experimental Procedure                                                                 | 80   |

|    | 5.3   |       | $V_{\mathrm{FB}}$ , $N_{\mathrm{A}}$ , Low Temperature CV, Surface Potential and $D_{\mathrm{it}}$ ation | 82   |

|    | 5.4   | Resul | ts and Discussion                                                                                        | 89   |

|    |       | 5.4.1 | Impact of Interface Treatment.                                                                           | 89   |

|    |       | 5.4.2 | Deep Level Transient Spectroscopy (DLTS)                                                                 | 92   |

|    |       | 5.4.3 | I-V Characteristics.                                                                                     | 95   |

|    |       | 5.4.4 | Evidence of Edge Capacitance in Pseudo-Accumulation Region                                               | 96   |

|    | 5.5   | Concl | usion                                                                                                    | 97   |

# **TABLE OF CONTENTS** (Continued)

| Cl | napte | r                                                                                                                                        | Page |

|----|-------|------------------------------------------------------------------------------------------------------------------------------------------|------|

| 6  | TRA   | ACT OF SLOT PLANE ANTENNA ANNEALING ON CARRIER ANSPORT MECHANISM AND RELIABILITY ON ZrO <sub>2</sub> /Al <sub>2</sub> O <sub>3</sub> /Ge | 98   |

|    | 6.1   | Research Motivation of SPAO on High-k Layer                                                                                              | 98   |

|    | 6.2   | Device Information and Experimental Procedure                                                                                            | 99   |

|    | 6.3   | Carrier Transport Mechanism.                                                                                                             | 101  |

|    | 6.4   | Time Dependent Dielectric Breakdown Performance                                                                                          | 108  |

|    | 6.5   | Conclusion.                                                                                                                              | 113  |

| 7  | FLIC  | CKER NOISE MECHANISM ON THICK AND THIN OXIDE FINFET                                                                                      | 114  |

|    | 7.1   | Motivation of Noise Model Study on FinFET                                                                                                | 114  |

|    | 7.2   | Device Information and Measurement Method.                                                                                               | 116  |

|    | 7.3   | Results and Discussion.                                                                                                                  | 117  |

|    |       | 7.3.1 Bias Dependence of Flicker Noise                                                                                                   | 117  |

|    |       | 7.3.2 Short and Long Channel Effect on Flicker Noise                                                                                     | 118  |

|    |       | 7.3.3 Noise Model Extraction at Room Temperature                                                                                         | 119  |

|    |       | 7.3.4 Temperature Effect on Flicker Noise Model                                                                                          | 121  |

|    |       | 7.3.5 Planar Structure VS FinFET.                                                                                                        | 126  |

|    | 7.4   | Conclusion.                                                                                                                              | 128  |

| 8  | SUN   | MMARY AND FUTURE WORK                                                                                                                    | 129  |

|    | 8.1   | Summary                                                                                                                                  | 129  |

|    | 8.2   | Future Work                                                                                                                              | 132  |

# **TABLE OF CONTENTS** (Continued)

| Chapter    | Page |

|------------|------|

| REFERENCES | 133  |

## LIST OF TABLES

| Tab | le                                                                                         | Page |

|-----|--------------------------------------------------------------------------------------------|------|

| 2.1 | Comparison of Relevant Properties for High-k Candidates                                    | 10   |

| 2.2 | Material Characteristics of Alternative Channel Materials for Ge and Si                    | 24   |

| 4.1 | List of Process Information of 13 HfAlO Samples                                            | 62   |

| 4.2 | List of Results of 13 HfAlO Samples                                                        | 68   |

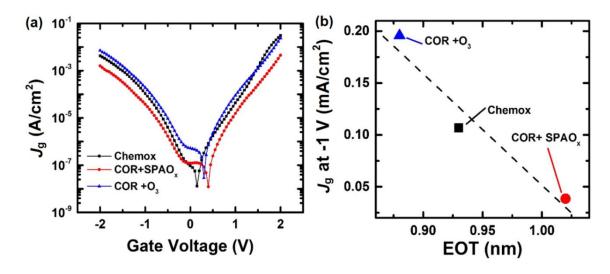

| 5.1 | Estimated EOT, $V_{\rm FB}$ , $D_{\rm it}$ , and $J_{\rm g}$ Information for Three Samples | 83   |

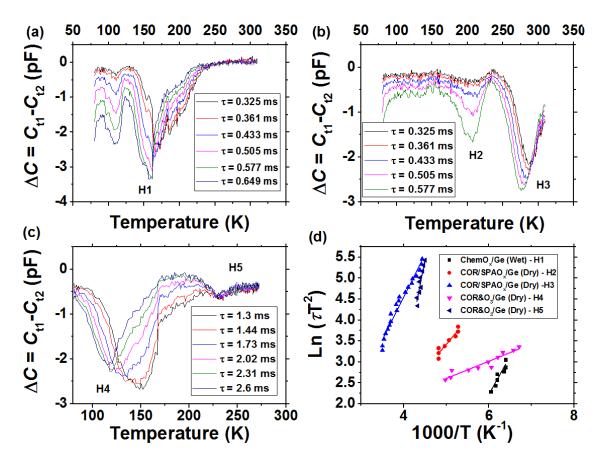

| 5.2 | Arrhenius Plot Fitting Results.                                                            | 94   |

| 6.1 | EOT, $V_{\text{FB}}$ , $D_{\text{it}}$ , and Interfacial Layer Type for Three Samples      | 99   |

| 6.2 | Transport Mechanisms are Summarized for Both GEI and SEI Mode                              | 107  |

| 7.1 | Information of Devices Under Test.                                                         | 116  |

| 8.1 | Comparison of Characterization Method for $D_{it}$                                         | 130  |

## LIST OF FIGURES

| Figu | re                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

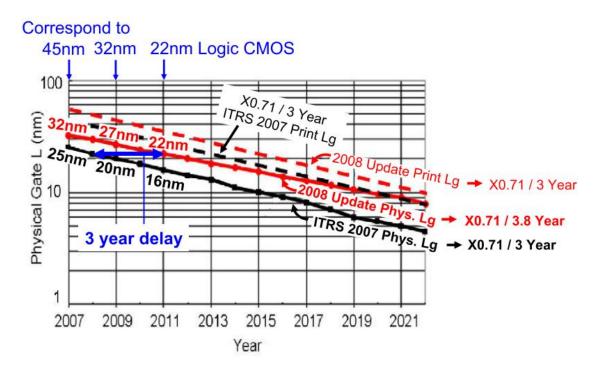

| 1.1  | Comparison of ITRS 2007 and 2008 Update for the trends of printed (resist) and physical gate lengths                                                                                                                                                                                                                                                                                                                                                                          |

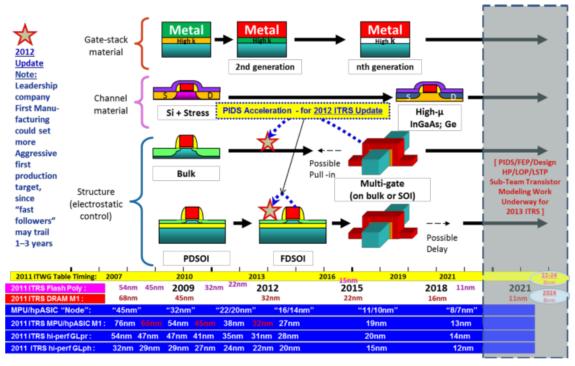

| 1.2  | 2011 ITRS "Equivalent Scaling" process technologies timing, overall roadmap technology characteristics (ORTC) MPU/High-performance ASIC half pitch and gate length trends and timing, and industry "Nodes".                                                                                                                                                                                                                                                                   |

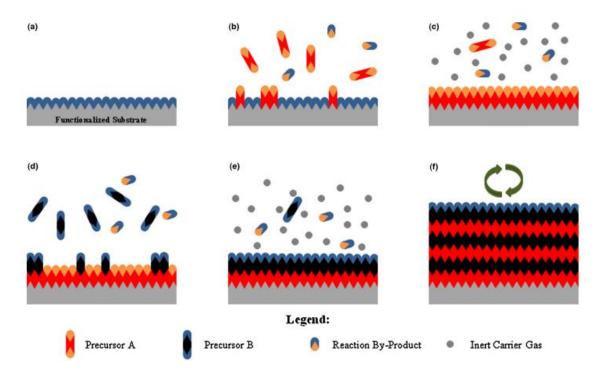

| 1.3  | Schematic of ALD process. (a) Substrate surface has natural functionalization or is treated to functionalize the surface. (b) Precursor A is pulsed and reacts with surface. (c) Excess precursor and reaction byproducts are purged with inert carrier gas. (d) Precursor B is pulsed and reacts with surface. (e) Excess precursor and reaction by-products are purged with inert carrier gas. (f) Steps 2–5 are repeated until the desired material thickness is achieved. |

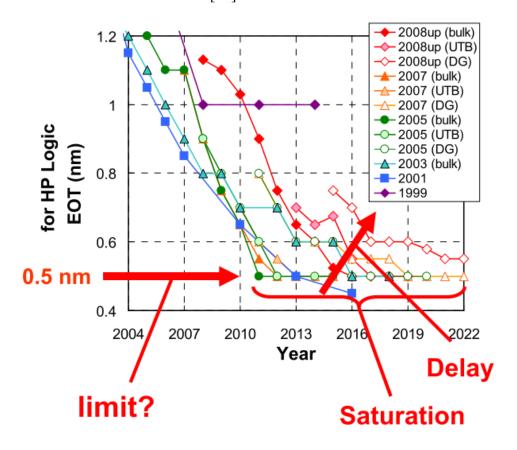

| 2.1  | Trend of EOT of the gate insulator for various versions of ITRS                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.2  | Static dielectric constant versus band gap for candidate gate oxides                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.3  | TEM image of crystallization in HfO <sub>2</sub> /SiO <sub>2</sub> dielectrics with (a) 40% HfO <sub>2</sub> and (b) 80%                                                                                                                                                                                                                                                                                                                                                      |

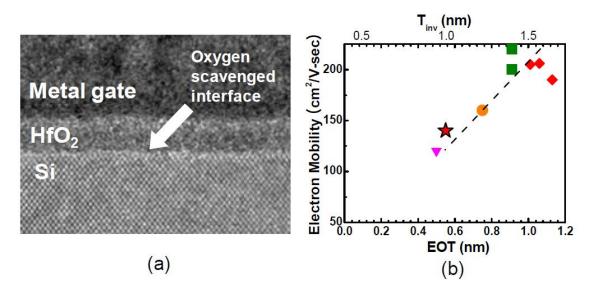

| 2.4  | (a) TEM cross section of a high-k/metal gate stack where the BIL (bottom interfacial layer) was removed by post anneal technique (b) High field electron mobility degradation as a function of EOT from literature data. The mobility values are taken at at $E_{\rm eff} = 1~{\rm MV/cm}$ .                                                                                                                                                                                  |

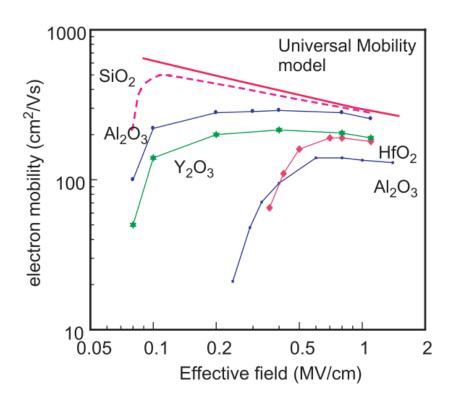

| 2.5  | Electron mobility in devices with high-k gate oxides.                                                                                                                                                                                                                                                                                                                                                                                                                         |

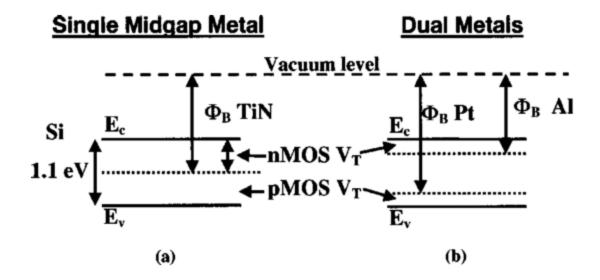

| 2.6  | Energy diagrams of threshold voltages for nMOS and pMOS devices using (a) midgap metal gates and (b) dual metal gates                                                                                                                                                                                                                                                                                                                                                         |

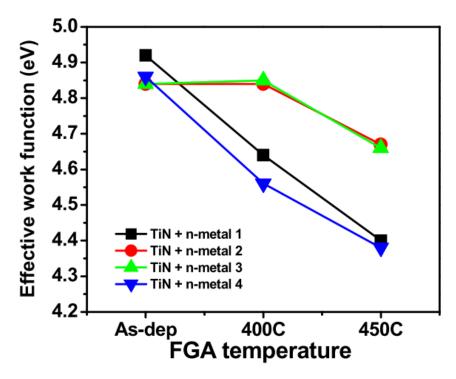

| 2.7  | EWF change with anneal temperature. Four different compositions of Al based n-metals deposited on thin TiN layer followed by barrier layer and Al-fill.                                                                                                                                                                                                                                                                                                                       |

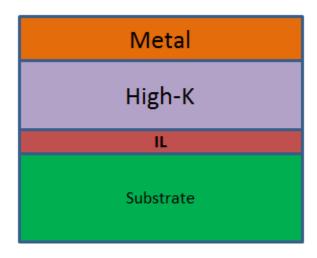

| 2.8  | Schematic of metal high-k gate stack                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Figur | <b>∙e</b>                                                                                                                                                                                                                                                                                                                                                                  | Page |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

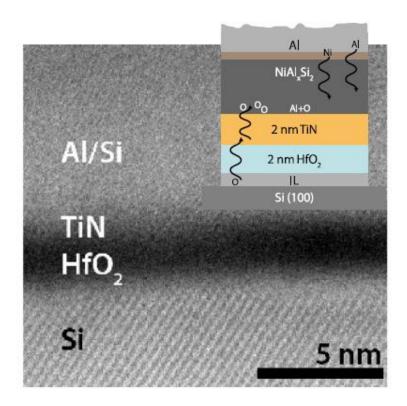

| 2.9   | Bright field micrograph of the gate stack from STEM. The interface to Si/HfO <sub>2</sub> shows a weak contrast. Al and Si were found by EELS above TiN. Inset: Schematic gate stack structure and Al scavenging process. During silicidation Al distributes uniformly into poly-Si. In between NiSi and TiN, SiO <sub>x</sub> and AlO <sub>x</sub> accumulation is found. | 19   |

| 2.10  | Schematics of direct and remote scavenging techniques in the literature                                                                                                                                                                                                                                                                                                    | 21   |

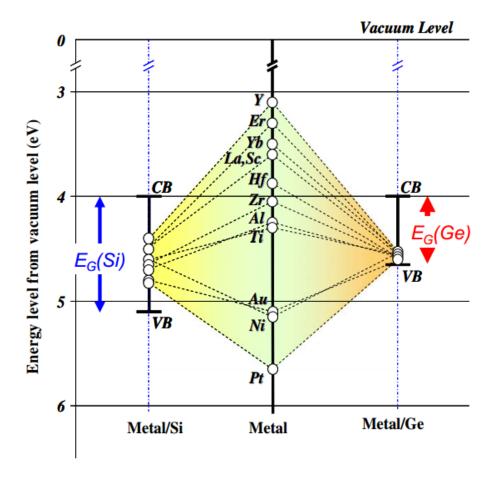

| 2.11  | Schottky barrier heights obtained experimentally for various metals with different vacuum work-functions. In case of Ge, the Fermi-level is strongly pinned near the valence band edge.                                                                                                                                                                                    | 25   |

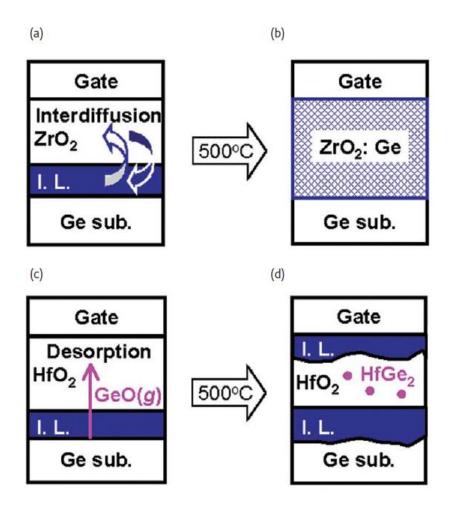

| 2.12  | Schematic showing the effect of annealing on ZrO <sub>2</sub> /Ge gate stack (a, b) and HfO <sub>2</sub> /Ge gate stack (c, d), before (a, c) and after (b, d) annealing at 500°C. HfGe <sub>2</sub> in (d) is speculation and has not been observed                                                                                                                       | 26   |

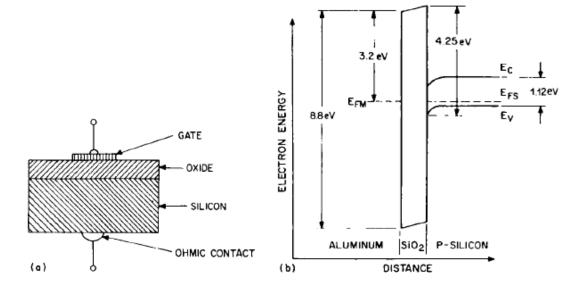

| 3.1   | (a) Cross section of a MOS capacitor. (b) Energy-band diagram of the MOS capacitor showing the energy barrier between metal and $SiO_2$ and between silicon and $SiO_2$ . The metal is aluminum and the silicon is p-type.                                                                                                                                                 | 29   |

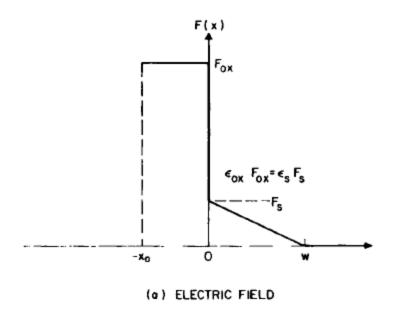

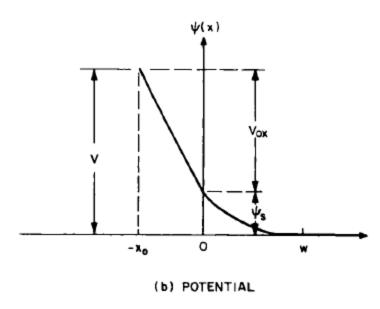

| 3.2   | (a) Electrical field configuration in the $SiO_2$ and silicon surface calculated from Equations (3.1-3.5) as function of x. (b) Potential distribution in the $SiO_2$ and the silicon surface calculated from Equations (3.1-3.5) corresponding to the electric field configuration in (a)                                                                                 | 32   |

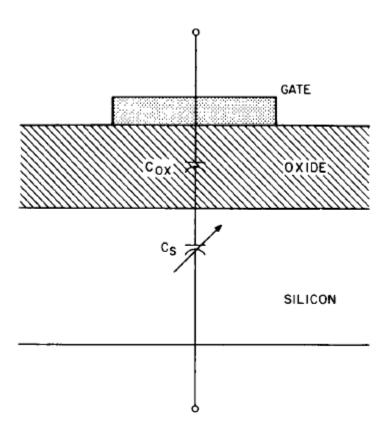

| 3.3   | Cross section of a MOS capacitor showing a simple equivalent circuit. The capacitor labeled $C_s$ is shown variable to denote its bias dependence                                                                                                                                                                                                                          | 33   |

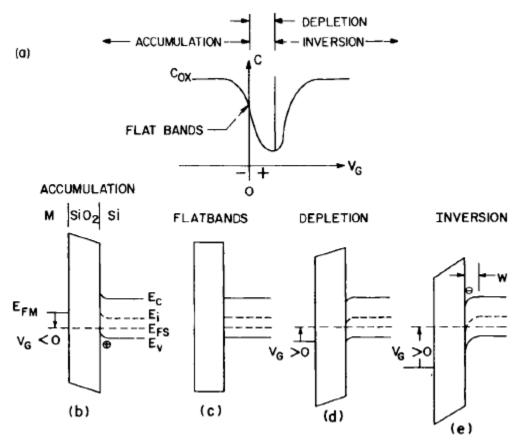

| 3.4   | To illustrate the operation of a MOS capacitor, capacitance as a function of bias, and the corresponding energy-band diagrams are shown in accumulation, depletion, inversion, and at flatbands. Energy values $E_{\rm c}$ and $E_{\rm v}$ are the conduction and valence band edges, respectively                                                                         | 35   |

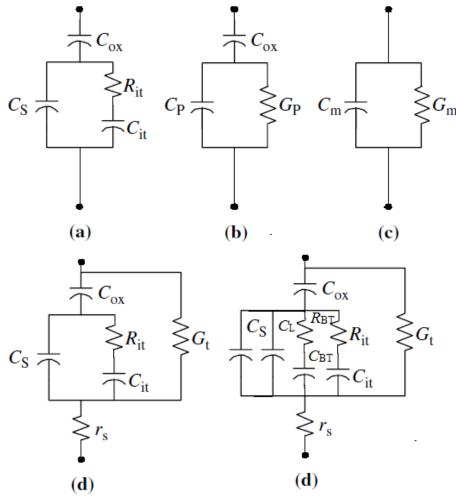

| 3.5   | Equivalent circuits for conductance measurements; (a) MOS-C with interface trap time constant $\tau_{it} = R_{it}C_{it}$ , (b) simplified circuit of (a), (c) measured circuit, (d) including series $r_s$ resistance and tunnel conductance $G_t$ , capacitance and reistance from border trap $C_{BT}$ , $R_{it}$ , capacitance from side of measured area $C_L$         | 36   |

| Figui | e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Page |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

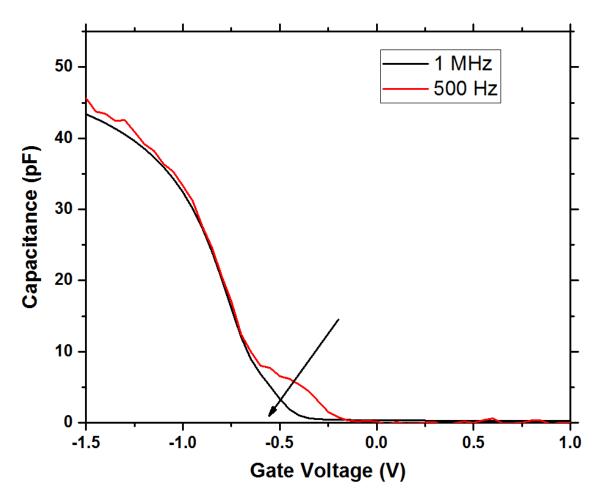

| 3.6   | Low frequency method applied on HfAlO/Si devices. $D_{it}$ is calculated in the range where the pointer indicates (depletion region). The dispersion in the negative range (accumulation region) is due to border traps                                                                                                                                                                                                                                                                                                | 38   |

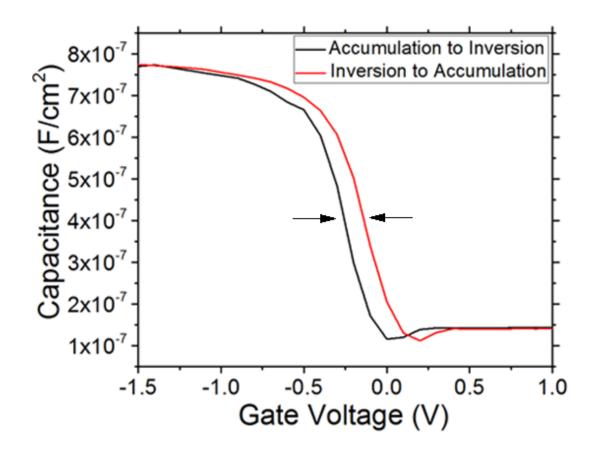

| 3.7   | CV hysteresis are taken by sweep voltage from accumulation to inversion, and sweep back immediately                                                                                                                                                                                                                                                                                                                                                                                                                    | 39   |

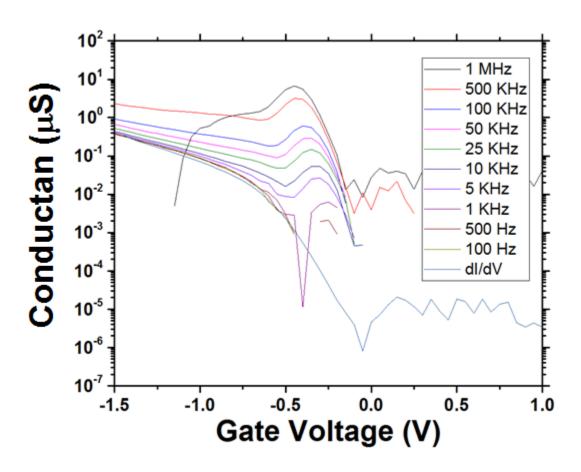

| 3.8   | dI/dV is the derivative from DC measurement of IV characteristics. This conductance is due to tunneling current. Small conductance signal is due to both tunneling current and interface states. When frequency is low enough, it converges to $dI/dV$                                                                                                                                                                                                                                                                 | 42   |

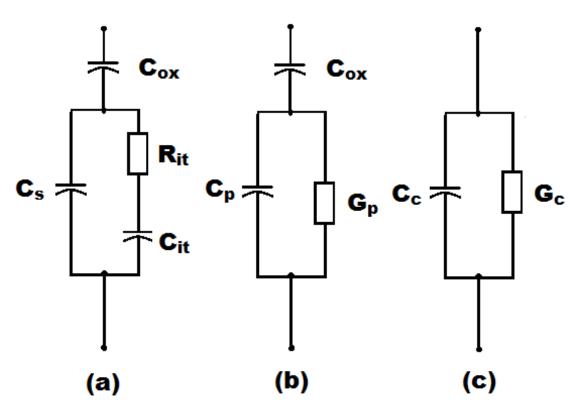

| 3.9   | (a) MOS-C model with the interface trap time constant ( $\tau_{it} = R_{it}C_{it}$ ), where $C_{ox}$ is the oxide capacitance, $C_s$ is the substrate capacitance, $R_{it}$ and $C_{it}$ are the interface defects induced resistance and capacitance, respectively. (b) Simplified circuit of (a), $C_p$ and $G_p$ are the equivalent capacitance and conductance in the substrate. (c) Circuit used for measurement after the correction, $G_c$ is the corrected conductance and $C_c$ is the corrected capacitance. | 43   |

| 3.10  | Screen shot of Labview program for $D_{\rm it}$ measurement                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 44   |

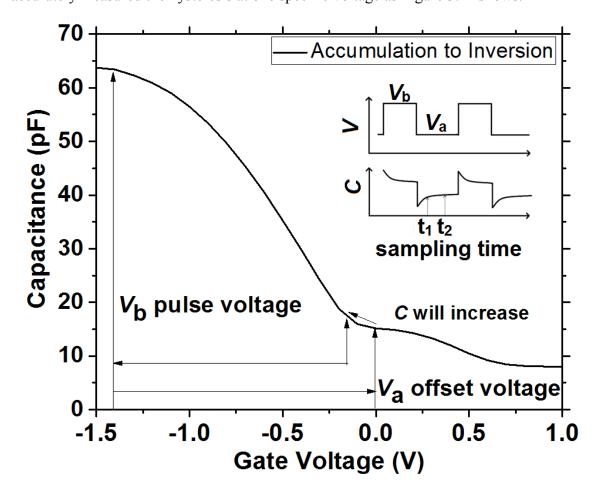

| 3.11  | Two voltages, namely $V_a$ and $V_b$ , are alternatively applied on the gate stack. Capacitance was sampled at two different time $t_1$ and $t_2$ after voltage was returned to $V_a$ . Normally, an observation of increased capacitance will happen if there is majority carrier emission from the traps at the interface.                                                                                                                                                                                           | 45   |

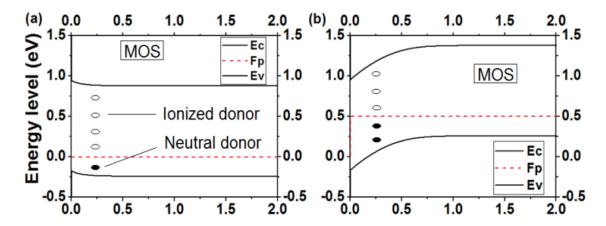

| 3.12  | Band diagram at two different bias conditions for p type substrate are plotted for both MOS structure ( $SiO_2/p$ type Si) and PN junction (n type CdS/p type CdTe): (a) MOS structure, bias voltage = 0 V, (b) MOS structure, bias voltage = -0.5 V (voltage difference between Si and SiO <sub>2</sub> );                                                                                                                                                                                                            | 46   |

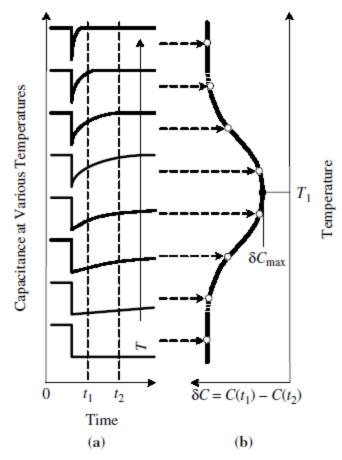

| 3.13  | Implementation of the rate window concept with a double boxcar integrator. The output is the average difference of the capacitance amplitudes at sampling times $t_1$ and $t_2$                                                                                                                                                                                                                                                                                                                                        | 48   |

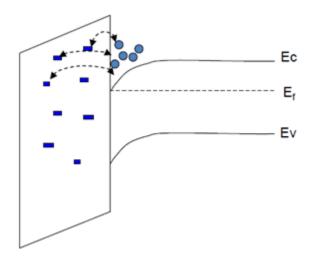

| 3.14  | Carriers in channel are trapped and detraped from dielectric                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 49   |

| Figu | re                                                                                                                                                                                                                                                                                                                                                                                                                                           | Page |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

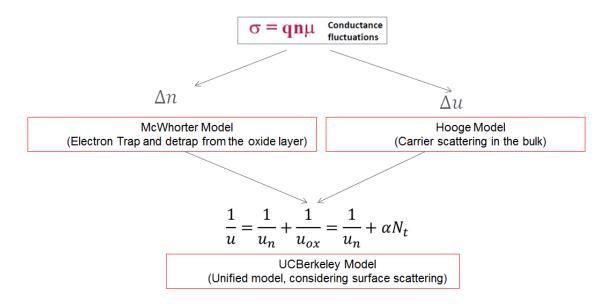

| 3.15 | To illustrate source of noise, McWhorter model is based carrier number fluctuation, and Hooge model is based on mobility fluctuation. Unified model correlated them by surface scattering process                                                                                                                                                                                                                                            | 50   |

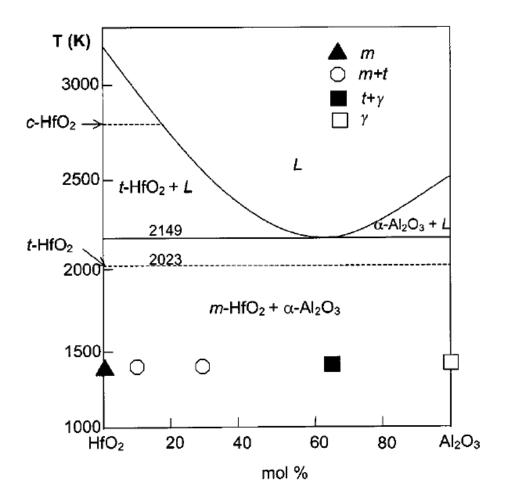

| 4.1  | Schematic of the $HfO_2$ – $Al_2O_3$ phase diagram, the symbols represent the crystalline phases identified by electron diffraction in the films with different amounts of $Al_2O_3$ after annealing at 1400 °C                                                                                                                                                                                                                              | 57   |

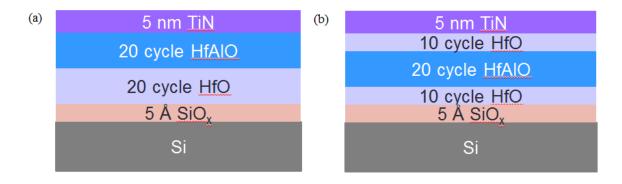

| 4.2  | Typical MOS structure in this study. (a) cap structure, (b) sandwich structure                                                                                                                                                                                                                                                                                                                                                               | 59   |

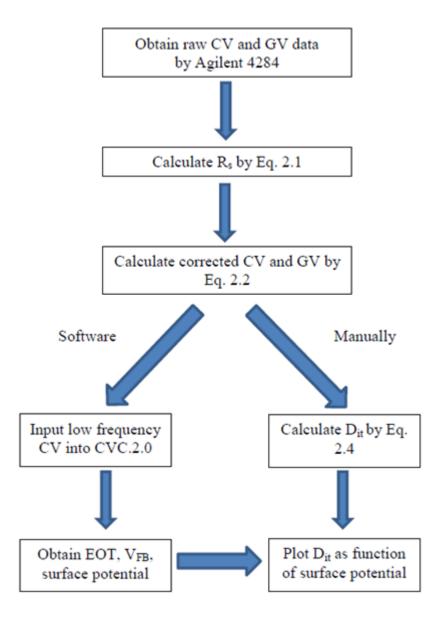

| 4.3  | Steps calculating $C_c$ , $G_c$ and $D_{it}$                                                                                                                                                                                                                                                                                                                                                                                                 | 61   |

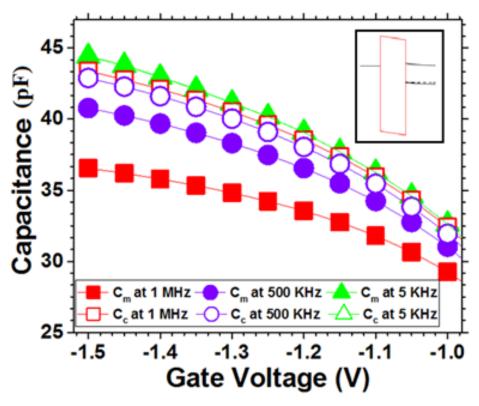

| 4.4  | Capacitance data of the sample fabricated by depositing 10 cycles of HfAlO as a cap layer on the 30 cycles of HfO (T3-A2.4%), where the corrected capacitance. $C_{\rm c}$ , show less frequency dispersion as compared to the measured capacitance, $C_{\rm m.}$ Inset figure is the corresponding band diagram when gate voltage equals to -1 V                                                                                            | 63   |

| 4.5  | Conductance data of the sample fabricated by depositing 10 cycles of HfAlO as a cap layer on the 30 cycles of HfO (T3-A2.4%), where the corrected conductance, $G_{\rm c}$ in the accumulation region is much smaller than in the depletion region. However, the measured conductance, $G_{\rm m}$ , show frequency dispersion in the accumulation region. Inset figure is the corresponding band diagram when gate voltage equals to -0.5 V | 64   |

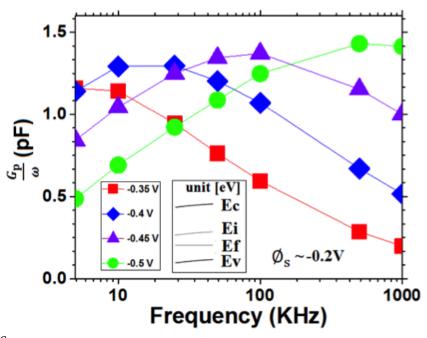

| 4.6  | $\frac{G_{\rm p}}{\omega}$ is plotted by sweeping both frequency and gate voltage. The inset shows band diagram. $E_{\rm c}$ , $E_{\rm i}$ , $E_{\rm F}$ and $E_{\rm v}$ are the conduction band, intrinsic level, Fermi-level and valence band, respectively.                                                                                                                                                                               | 66   |

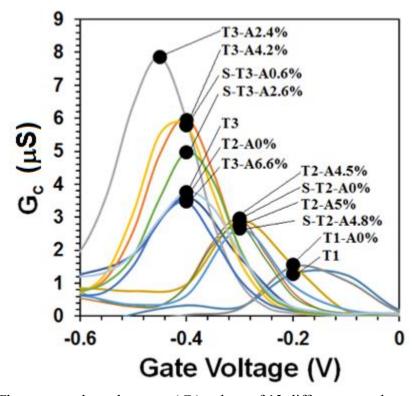

| 4.7  | The corrected conductance $(G_c)$ values of 13 different samples are plotted as a function of gate voltage                                                                                                                                                                                                                                                                                                                                   | 66   |

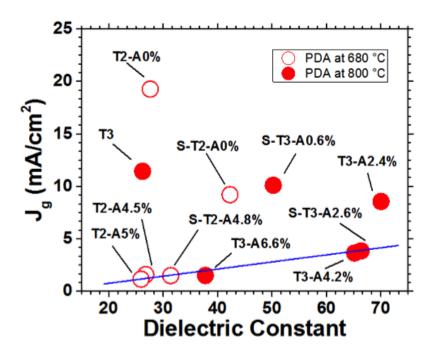

| 4.8  | Leakage current density measured at gate voltage ( $V_{\rm FB}$ -1 V). The results of 13 samples which were annealed at the temperatures 680 °C and 800 °C, are plotted as a function of dielectric constant.                                                                                                                                                                                                                                | 70   |

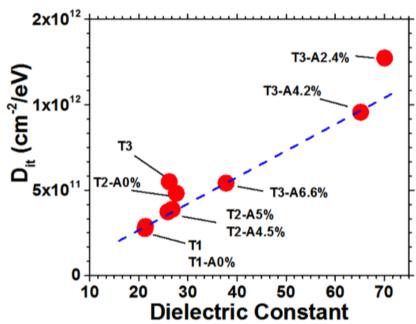

| 4.9  | The interface state density $(D_{it})$ values are plotted as a function of the dielectric constant of 13 samples.                                                                                                                                                                                                                                                                                                                            | 73   |

| Figur | re                                                                                                                                                                                                                                                                                                                                                             | Page |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

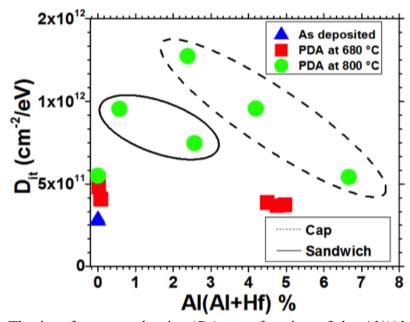

| 4.10  | The interface state density ( $D_{it}$ ) as a function of the Al/(Al+Hf) % of 13 samples are plotted. Data points within the dashed line are the 3 samples where Al was introduced by HfAlO as the cap layer on HfO <sub>2</sub> . Data points in solid line are the 2 samples where Al was introduced by sandwiching HfAlO inside the HfO <sub>2</sub> stack. | 74   |

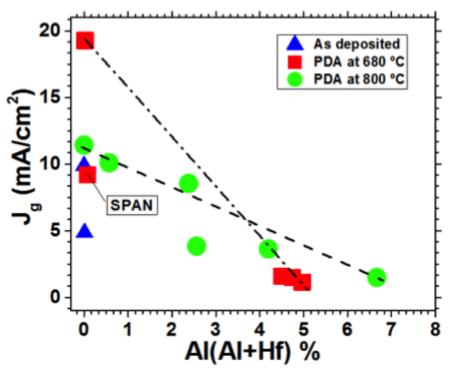

| 4.11  | The leakage current density $(J_{\rm g})$ measured at the gate voltage $(V_{\rm FB}\text{-}1~{\rm V})$ as a function of the Al/(Al+Hf) % of 13 samples is shown as a function of Al concentration. Dashed dot line and dashed line follow the trend of $J_{\rm g}$ varies with different Al doping level at 680 °C PDA and 800 °C PDA, respectively.           | 76   |

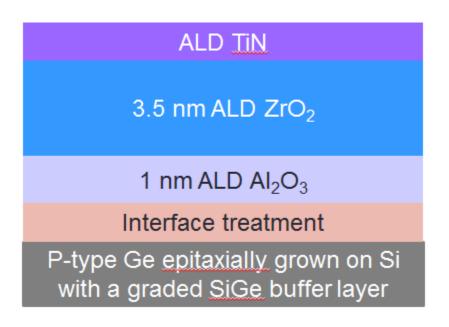

| 5.1   | Structure of MOS capacitor of high-k/Ge.                                                                                                                                                                                                                                                                                                                       | 81   |

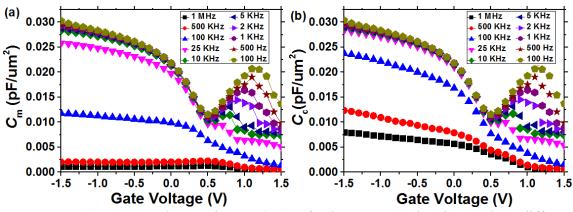

| 5.2   | (a) Measured capacitance $(C_{\rm m})$ of Chemox sample observed at different frequencies is plotted as a function of gate bias. (b) Corrected capacitance $(C_{\rm c})$ of Chemox sample measured at different frequencies is plotted as a function of gate bias.                                                                                             | 84   |

| 5.3   | Corrected capacitance $(C_c)$ at different frequencies and different temperatures is plotted as a function of gate bias for sample Chemox. (a) at five different temperature, (b) at 100 K and 300 K. Both frequency dispersion and temperature dispersion can be observed                                                                                     | 86   |

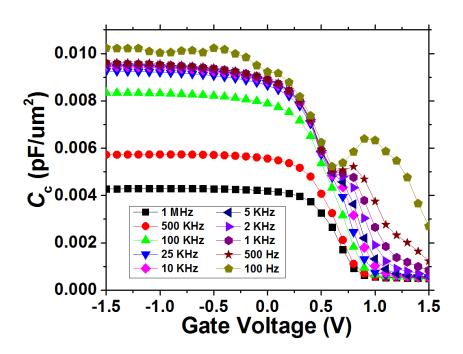

| 5.4   | Corrected capacitance $(C_c)$ of Chemox sample measured by different frequencies at 100 K is plotted as a function of gate bias. Frequency dispersion can be observed.                                                                                                                                                                                         | 87   |

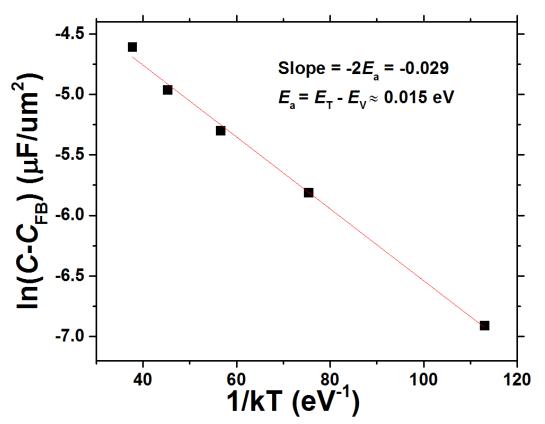

| 5.5   | $C_{\rm it}$ ( $C_{\rm it}$ = $C_{\rm acc}$ - $C_{\rm FB}$ ) as function of temperature (1/kT) at fixed frequency (100 KHz).                                                                                                                                                                                                                                   | 89   |

| 5.6   | Corrected 1 MHz capacitances ( $C_c$ ) of three samples are plotted as a function of gate voltage at room temperature. Device area is $40~\mu m \times 40~\mu m$ .                                                                                                                                                                                             | 90   |

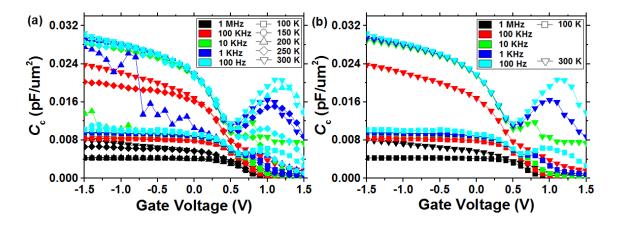

| 5.7   | Corrected capacitance ( $C_c$ ) is plotted as function of gate voltage at 100 K, (a) COR&SPAO <sub>x</sub> , (b) COR&O <sub>3</sub>                                                                                                                                                                                                                            | 91   |

| Figur | <b>e</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Page |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 5.8   | (a) Interface state density $(D_{\rm it})$ is plotted as function of bandgap for three samples at two temperatures (100 K and 300 K), other $D_{\rm it}$ as a function of temperature are within this range; (b) Calculated $D_{\rm it}$ of three samples as a function of gate voltage by capacitance spectroscopy method and conductance method.                                                                                                                                                                                     | 92   |

| 5.9   | Deep level transient spectrum for three samples, $C_{t1}$ and $C_{t2}$ are two capacitance values sampled at two different time $(t_1 < t_2)$ , T is temperature, Ln is nature logarithm, $\tau$ is time constant calculated as $\frac{t2-t1}{Ln(t2/t1)}$ . (a) simple chemical oxidation (Chemox), (b) chemical oxide removal (COR) followed by 1 nm oxide by slot-plane-antenna (SPA) plasma (COR&SPAO <sub>x</sub> ), (c) COR followed by vapor $O_3$ treatment (COR&O <sub>3</sub> ). (d) is Arrhenius plot for all three samples. | 95   |

| 5.10  | Comparison of gate leakage current density $(J_g)$ , (a) $J_g$ as a function of gate voltage, (b) $J_g$ as a function of EOT for different splits                                                                                                                                                                                                                                                                                                                                                                                      | 96   |

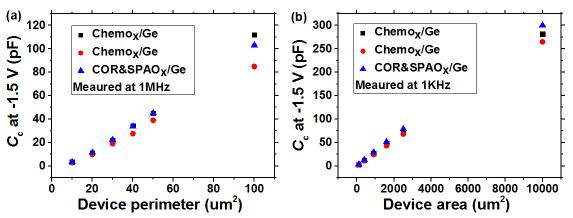

| 5.11  | Corrected capacitance ( $C_c$ ) measured at -1.5 V (pseudo-accumulation) were measured at two different frequencies, 1 MHz and 1 KHz, respectively. (a) At 1 MHz, the capacitance is contributed from edge and it has linear dependence of device perimeter (b) At 1 MHz, the capacitance is contributed from interface states in area and it has linear dependence of device area.                                                                                                                                                    | 97   |

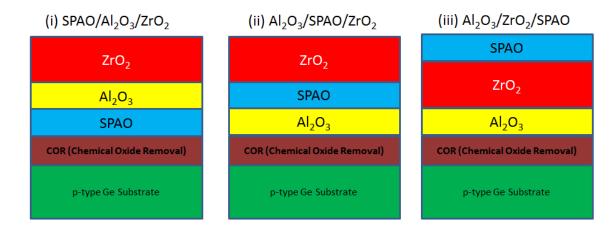

| 6.1   | Application of SPAO at different stages of gate stack deposition                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 100  |

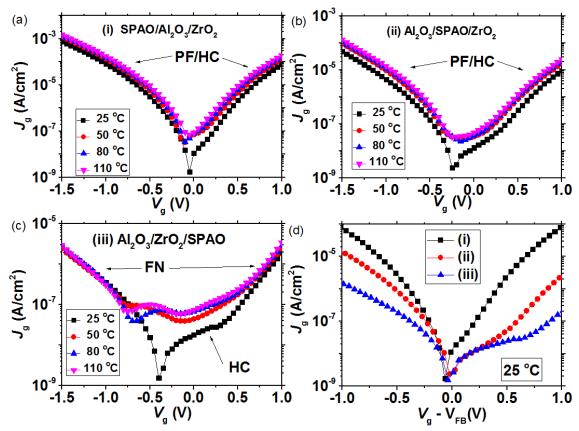

| 6.2   | Current density ( $J_g$ ) is plotted as a function of gate voltage ( $V_g$ ) at four different temperatures (25 °C, 50 °C, 80 °C, 110 °C) for three different samples, (a) Ge/SPAO/Al <sub>2</sub> O <sub>3</sub> /ZrO <sub>2</sub> , (b) Ge/Al <sub>2</sub> O <sub>3</sub> /SPAO/ZrO <sub>2</sub> , (c) Ge/Al <sub>2</sub> O <sub>3</sub> /ZrO <sub>2</sub> /SPAO. (d) $J_g$ as a function of $V_g$ - $V_{FB}$ is plotted for the above three samples at 25 °C where $V_{FB}$ is the flat band voltage.                               | 103  |

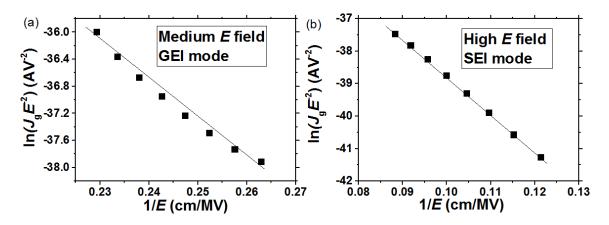

| 6.3   | $ln(J_gE^{-2})$ is plotted as function of $1/E$ as FN tunneling for sample $Ge/Al_2O_3/ZrO_2/SPAO$ , $J_g$ is current density and $E$ is electric field. (a) gate electron injection mode (GEI), (b) substrate electron injection mode (SEI).                                                                                                                                                                                                                                                                                          | 103  |

| Figur | ·e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Page |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

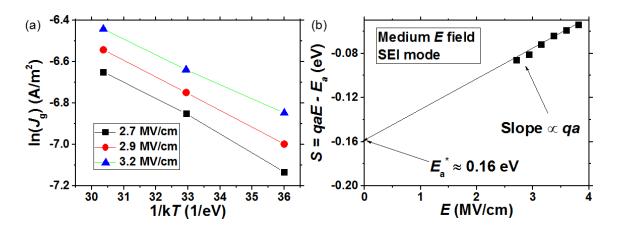

| 6.4   | (a) Current density $\ln(J_g)$ is plotted as function of $1/kT$ for sample Ge/Al <sub>2</sub> O <sub>3</sub> /ZrO <sub>2</sub> /SPAO, in SEI mode. (b) Slope value ( $S = qaE - E_a$ ), which is obtained from (a) is then plotted as function electric field $E$ (SEI mode)                                                                                                                                                                                                                                                                                                                                                                                                           | 105  |

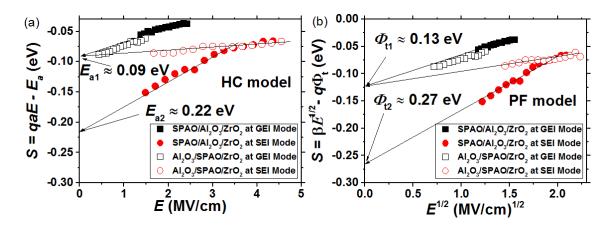

| 6.5   | Hopping Conduction and Poole-Frenkel emission (PF) were used to fit the I-V characteristics for sample Ge/SPAO/Al <sub>2</sub> O <sub>3</sub> /ZrO <sub>2</sub> (solid symbol) and sample Ge/Al <sub>2</sub> O <sub>3</sub> /SPAO/ZrO <sub>2</sub> (open symbol) at both GEI mode (black symbol, squares) and SEI mode (red symbol, circles). (a) Slope value ( $S = qaE - E_a$ ) is plotted as function electric field $E$ . (b) Slope value ( $S = \beta E^{1/2} - q\phi_1$ ) is plotted as function $E^{1/2}$ , where $E_a = q^3 / \pi \epsilon_r \epsilon_o$ . The slope value $E_a = q^3 / \pi \epsilon_r \epsilon_o$ . The slope value $E_a = q^3 / \pi \epsilon_r \epsilon_o$ . | 106  |

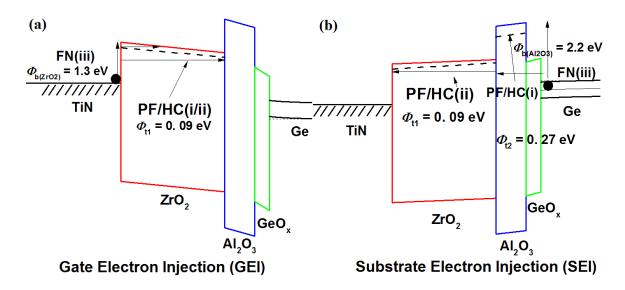

| 6.6   | Carrier transport mechanisms are explained in band diagram for both GEI mode and SEI mode. (a) GEI mode, band diagram is simulated under $V_{\rm g} = -1.5$ V. (b) SEI mode, band diagram is simulated under $V_{\rm g} = 1$ V                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 108  |

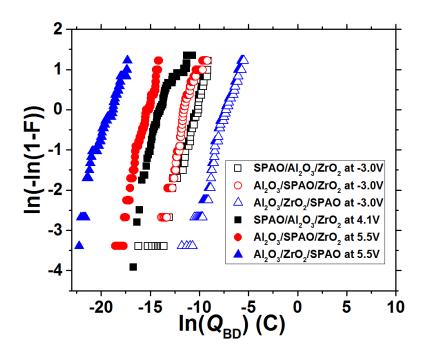

| 6.7   | $\beta$ values are around 0.7 and similar for all samples and stress conditions, which were obtained by Weibull plot                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 110  |

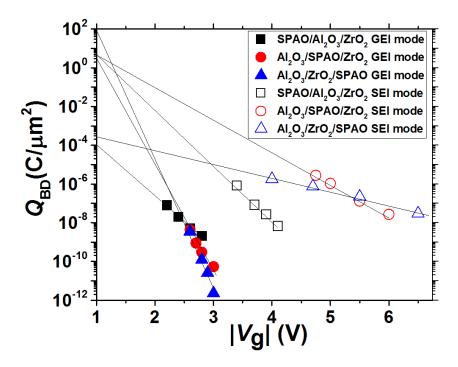

| 6.8   | Charge to breakdown value ( $Q_{\rm BD}$ ) is plotted as function of gate voltage ( $V_{\rm g}$ ) for both GEI mode (solid symbol) and SEI mode (open symbol)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 111  |

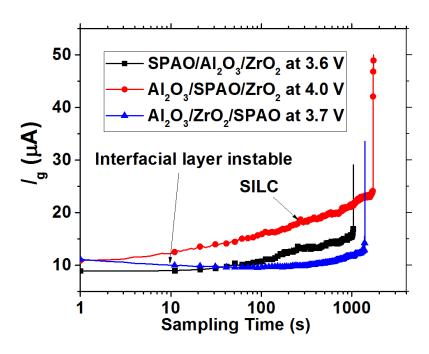

| 6.9   | Gate leakage current $(I_g)$ is plotted as function sampling time for all samples.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 112  |

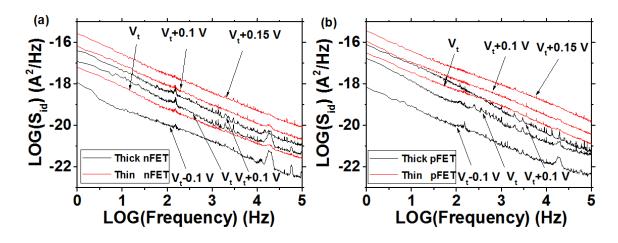

| 7.1   | Noise spectra (average value of eight dies) are plotted for both (a) nFinFET and (b) pFinFET. Bias conditions are at low overdrive voltage in linear region.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 118  |

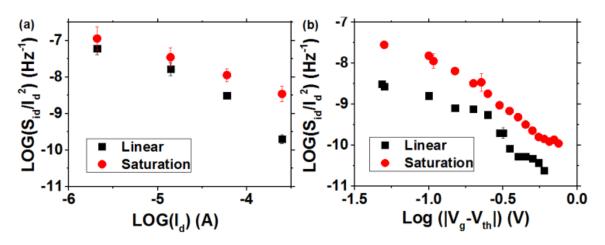

| 7.2   | Normalized $S_{id}$ ( $S_{id}$ / $I_d$ <sup>2</sup> ) sampled at 25 Hz is plotted against (a) drain current ( $I_d$ ), and (b) overdrive voltage ( $V_g$ - $V_{th}$ ). Device under test is thin nFinFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 118  |

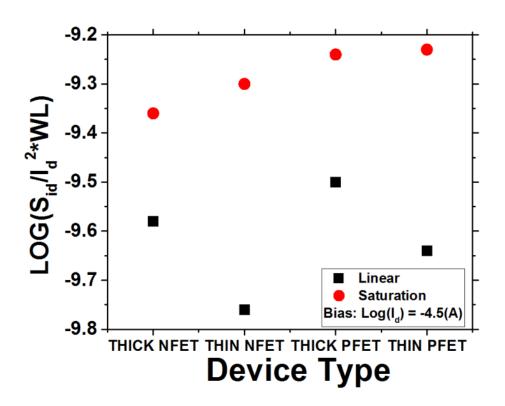

| 7.3   | The normalized $S_{\rm id}$ ( $S_{\rm id}/I_{\rm d}^{2}*WL$ ), is plotted for all four type FinFET at both linear and saturation regions. At relative large gate bias, $\sim V_{\rm t} + 0.2$ V, thin oxide FinFET shows larger discrepancy than thick oxide due to both short channel and LDD effect.                                                                                                                                                                                                                                                                                                                                                                                 | 119  |

| Figur | re                                                                                                                                                                                                                                                                                                                                                               | Page |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

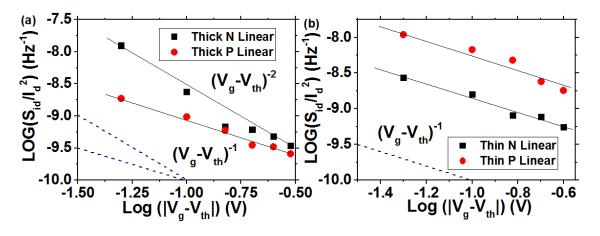

| 7.4   | Noise mechanisms were extracted at low gate bias in linear region by fitting normalized $S_{\rm id}$ versus $V_{\rm g}$ - $V_{\rm th}$ . (a) n/p thick FinFET, (b) n/p thin FinFET.                                                                                                                                                                              | 120  |

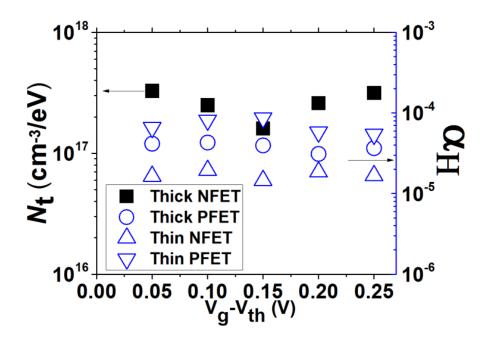

| 7.5   | Left axis shows oxide trap density $(N_{\rm t})$ against overdrive voltage in linear region for thick nFinFET, right axis shows Hooge empirical parameter $(\alpha_{\rm H})$ against overdrive voltage $(V_{\rm g}\text{-}V_{\rm th})$ in linear region for thick pFinFET and thin n/p FinFET.                                                                   | 121  |

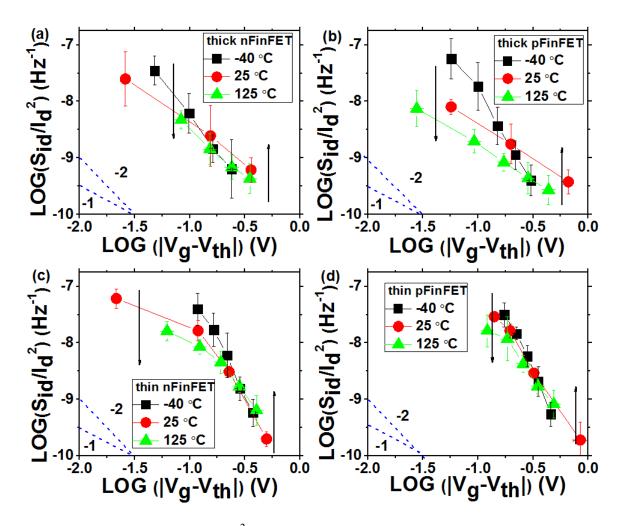

| 7.6   | Normalized $S_{\rm id}$ ( $S_{\rm id}/I_{\rm d}^2$ ) is plotted as function of overdrive voltage ( $V_{\rm g}$ - $V_{\rm th}$ ) at linear bias condition under three different temperatures (-40 °C, 25 °C, 125 °C) for four types of devices (a) thick nFinFET, (b) thick pFinFET, (c) thin nFinFET, (d) thin pFinFET. The data is an average of eight devices. | 123  |

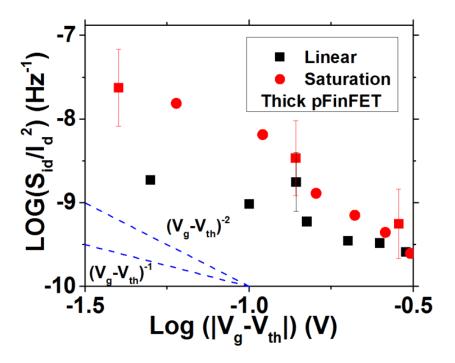

| 7.7   | Normalized $S_{id}$ ( $S_{id}/I_d^2$ ) is plotted as function of overdrive voltage ( $V_g$ - $V_{th}$ ) at both linear and saturation bias conditions for thick pFinFET                                                                                                                                                                                          | 125  |

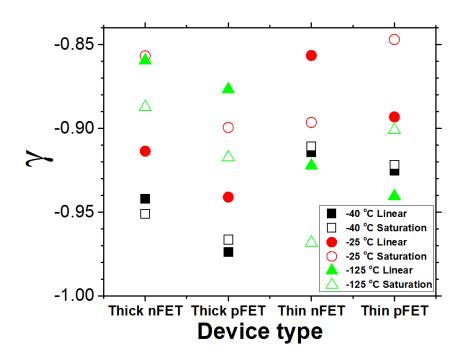

| 7.8   | Slope of flicker noise spectra, $\gamma$ ( $S_{id} = \frac{1}{f^{\gamma}}$ ) plotted for four devices at different temperatures (-40 °C, 25 °C, 125 °C) and bias conditions (linear and saturation). Slope values are average value obtained from eight devices at both the bias conditions.                                                                     | 126  |

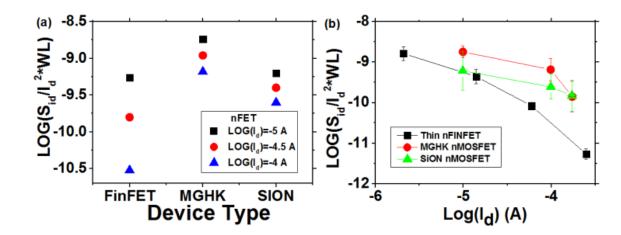

| 7.9   | (a) Normalized $S_{id}$ ( $S_{id}/I_d^{2*}WL$ ) is plotted against different structure at different current bias condition (linear region) for nFET; (b) Normalized $S_{id}$ ( $S_{id}/I_d^{2*}WL$ ) is plotted against drain current ( $I_d$ ) at linear region for nFET.                                                                                       | 127  |

#### **CHAPTER 1**

#### INTRODUCTION

The gate length of Complementary Metal Oxide Semiconductor (CMOS) technology has been scaled to 14 nm (channel length) and is commercially available in 2014 from Intel, which is a three years delay from the predicted year from ITRS 2007 report (Figure 1.1) [1]. Since then, the aggressive scaling has slowed down due to transistor reaching its physical limits, one such issue is high leakage current between source and drain. To address the S/D off-leakage current, industries have been finding solutions. As Figure 1.2 shows, three approaches are being followed to continue scaling of chips [2]: (i) gate stack material, (ii) channel material, and (iii) device architecture. The oxide layer of gate stack is the leading candidate as devices below 10 nm [3]. Metal gate high-k (MGHK) has been implemented to boost chip performance while physical thickness is kept thick enough (~5 nm) to prevent large direct tunneling current. Different materials other than Si, have been considered as a substrate over decades at research level, which have higher carrier mobility [4]. Nevertheless, only strained silicon has been implemented so far, since Ge or GaAs are still in their research stage. 3D structures like FinFET have been successfully implemented in the industry to improve drain-induced barrier lowering (DIBL) (short channel effect) [5]. This dissertation is focused on electrical characterization methods on these new novel nano devices and their electrical property under different process conditions. Critical issues need to be addressed before the implementation of these devices in the semiconductor industry. Additionally, compared to traditional CMOS devices, other physical phenomena are occurring since the

device is in nano range.

**Figure 1.1** Comparison of ITRS 2007 and 2008 Update for the trends of printed (resist) and physical gate lengths.

Source: [1].

While CMOS technology is scaling down, the process for high-k deposition and annealing have also improved. Atomic layer deposition (ALD) method has significant advantage over alternative deposition methods, such as chemical vapor deposition (CVD) and various physical vapor deposition (PVD) techniques, due to its conformity and control over materials thickness and composition. These desirable characteristics originate from self-saturating nature of ALD processes [6]. For deposition of dielectric (high-k material), ALD has been used in this research. Figure 1.3 shows the schematic of ALD process.

**Figure 1.2** 2011 ITRS "Equivalent Scaling" process technologies timing, overall roadmap technology characteristics (ORTC) MPU/High-performance ASIC half pitch and gate length trends and timing, and industry "Nodes". Source: [2].

During or after the ALD deposition, the quality of dielectric in terms of EOT and interface state density can be improved by exposing them to a slot-plane-antenna (SPA) plasma with various gases such as O<sub>2</sub> or inert gases [7]. The SPA plasma provides a high density plasma at low electron temperature, where the radicals diffuse from the plasma generation region to the wafer surface. SPA plasma is also a very low damage plasma process compared to conventional inductively coupled plasma (ICP) or electron cyclotron resonance (ECR) plasma [7]. It was found that the SPA plasma helps better film densification as well as improved interfacial layer growth. The dielectric is prevented from crystallization at low annealing temperatures. Consequently, oxygen cannot diffuse through boundary of crystalline and interfacial layer thickness is kept thin.

**Figure 1.3** Schematic of ALD process. (a) Substrate surface has natural functionalization or is treated to functionalize the surface. (b) Precursor A is pulsed and reacts with surface. (c) Excess precursor and reaction by-products are purged with inert carrier gas. (d) Precursor B is pulsed and reacts with surface. (e) Excess precursor and reaction by-products are purged with inert carrier gas. (f) Steps 2–5 are repeated until the desired material thickness is achieved.

Source: [6].

Several electrical characterization methods were used to evaluate the interface quality or oxide quality in terms of defects. These methods can be categorized into two major groups, i.e., evaluation of capacitance of the gate stack and leakage current through the dielectric. Because of existing defects, experimental results can deviate from theoretical calculations. On the other hand, these deviations can be utilized to evaluate defects in the device. Characterization methods such as conductance method [8], capacitance-voltage (CV) at various low temperatures, flicker noise, capacitance transient spectroscopy, deep level transient spectroscopy (DLTS) [9], CV hysteresis, and time dependent dielectric breakdown (TDDB) [10] are used in this work.

### 1.1 Motivation and Objectives

The devices under test in this research involve high-k/Si (next generation), high-k/Ge, and MGHK-FinFETs. One of the critical issues in MGHK, is the high interface state density ( $D_{\rm it} \sim 10^{12} \, {\rm cm}^{-2} {\rm eV}^{-1}$ ) [11] compared to traditional SiO<sub>2</sub>/Si system ( $\sim 10^{10} \, {\rm cm}^{-2} {\rm eV}^{-1}$ ) [12]. Conventional SiO<sub>2</sub>/Si system prevailed over decades due to its perfect interface quality due to thermally grown SiO<sub>2</sub> on Si substrate [12]. Introducing high-k with metal gate (HKMG) brings additional reliability issue like threshold voltage degradation ( $\Delta V_{\rm th}$ ) after bias temperature instability (BTI) stress in both nMOS and pMOS transistors [13]. This is due to the degradation of both interface and high-k gate dielectrics. If silicon substrate is replaced by other materials, it is necessary to address the interface defects density before expected mobility can be achieved [14]. Therefore, it is imperative to characterize the high-k dielectric layer and the interface quality.

The objective of this research is to use various electrical characterization techniques to study interface quality and high-k dielectrics deposited by various process condition. This provides the comprehensive information on defects, such as density, energy level, time constant and how they interact with other parameters (like flat band voltage  $V_{\rm FB}$ , flicker noise, and dielectric life time). Both theoretical model and experimental work are involved in the research work. Different evaluation methods can provide a good analytical approach to study the dielectrics in the gate stacks. The correlation of experimental data from different methods can enhance the understanding the defects behavior. Furthermore, this study will discuss the advantages and disadvantages of various techniques, since each method has its own limitation like sensitivity, range, different extracted parameters and difficulty of implementation.

### 1.2 Dissertation Organization

Chapter 2 reviews state of art MOS-capacitor. Introduce why high-k layer is a requirement for future transistor scaling, and explain the basic requirement to scale EOT below sub-nm range. New interface control technique was introduced. high-k/Ge was discussed as well as for its high mobility and its subsequent interface challenge before it can be fully considered for commercial use.

Chapter 3 reviews different electrical characterization methods that used in this research work

Chapter 4 discusses the interface properties in a metal oxide semiconductor capacitor (MOS-C) device with a 3 nm HfAlO/0.5 nm SiO<sub>2</sub>/Si stack prepared by various processing conditions. Different Al doping, different post deposition annealing temperatures and different deposition steps were discussed in this chapter. EOT and  $V_{\rm FB}$  were obtained from capacitance-voltage measurements. The correcting of the error introduced by the series resistance ( $R_{\rm s}$ ) associated with the substrate and contact is also discussed here.

Chapter 5 discusses the dry and wet processed interface layer properties for three different p type Ge/ALD 1nm-Al<sub>2</sub>O<sub>3</sub>/ALD 3.5nm-ZrO<sub>2</sub>/ALD TiN gate. Several parameters like EOT, flat band voltage, bulk doping, and surface potential as a function of gate voltage are reported. It is also discussed that the high frequency capacitance of TiN/ZrO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/p-Ge gate stacks measured in the accumulation region depends on the device area after substrate resistance correction.

Chapter 6 deals with the TiN/ZrO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/p-Ge gate stacks subjected to the different SPAO (Slot Plane Antenna Oxidation) annealing conditions, namely, (i) before

high-k ALD (Atomic Layer Deposition), (ii) between high-k ALD, and (iii) after high-k ALD. After XPS (X-ray Photoelectron Spectroscopy) and EOT (estimated by capacitance voltage) measurement. The carrier transport mechanisms on these samples were extracted at high field range to reveal how SPAO can effective remove traps in high-k layer. The reliability of interfacial layer (GeO<sub>x</sub>/GeO<sub>2</sub>) is evaluated by TDDB performance under substrate electron injection condition.

Chapter 7 characterizes time zero 1/f noise on different oxide thickness of thick and thin oxide FinFET transistors to study how EOT impacts the noise mechanism. At room temperature, the flicker noise mechanisms were determined at linear region to study the bias dependence of FinFET. The noise models were subsequently extracted. The impact of temperature on the noise level and noise mechanism was discussed as well.

Chapter 8 summarized the overall work of this research and discusses future work.

#### **CHAPTER 2**

## LITERATURE REVIEW: HIGH-K MATERIAL AND ITS APPLICATION ON Si/Ge SUBSTRATE

In this chapter, historical requirement of implementation of high-k dielectric will be reviewed. The basic requirement is to improve the high-k and interface property if high-k can be successful implemented on silicon substrate. The current status of high-k dielectrics will be discussed in relation to different methods to further scale EOT below 0.7 nm. Finally, the challenge of enhancing the properties of high-k dielectrics and its application on germanium channel is discussed.

### 2.1 Requirement of High-k and the Necessary Property of Implementation

The first point-contact transistor was invented by Bardeen, Brattain, and Shockley invented in 1947. In acknowledgement of this accomplishment, Shockley, Bardeen, and Brattain were jointly awarded the 1956 Nobel Prize in Physics "for their researches on semiconductors and their discovery of the transistor effect." [15]. Interestingly, the first transistor was germanium. However, researchers discovered that material property of Si, which is same as in group IV as Ge, is better than Ge, when considering the formation of gate oxide: SiO<sub>2</sub> can be grown on its surface, which is a very good insulator. On the other hand, Ge does not form this oxide layer on its surface so easily and GeO<sub>2</sub> is hydroscopic and not thermally stable [16]. Additionally, Si is abundant, for example, sand is a source of Si.

In 2004, EOT (oxide thickness calculated by using dielectric constant of  $SiO_2$ ) was scaled to ~1.2 nm [1] as Figure 2.1 indicates, as oxide layer was the first layer went

to sub 1 nm range. However, ultrathin SiO<sub>2</sub> suffers from direct-tunneling current which increases exponentially as thickness decreases [17]. The large gate leakage current exhausts battery rapidly. To overcome gate leakage problems, addition of N into SiO<sub>2</sub> has been used either by post deposition annealing in nitrogen ambient or forming a nitride/oxide stack structure. As incorporating nitrogen into SiO<sub>2</sub>, it not only increases the dielectric constant but also acts as a better barrier preventing boron penetration from poly silicon gate. SiON served as a transition stage between high-k and SiO<sub>2</sub>, which has maxim dielectric constant less than 8 [18].

**Figure 2.1** Trend of EOT of the gate insulator for various versions of ITRS.

Source: [1].

High-k materials were first studied on memory device. Table 2.1 listed high-k

candidates and their relevant properties. Before it can be implemented in industry, the following issues has to be considered first: (a) permittivity, bandgap, and band alignment to silicon, (b) thermodynamical stability, (c) film morphology and deposition method, (d) interface quality and bulk defects, (e) gate compatibility and process compatibility [3].

**Table 2.1** Comparison of Relevant Properties for High-k Candidates

| Material         | Dielectric constant | Band gap $E_{G}$ (eV) | $\Delta E_{\rm c}$ (eV) to Si | Crystal Structure(s)                              |

|------------------|---------------------|-----------------------|-------------------------------|---------------------------------------------------|

| SiO <sub>2</sub> | 3.9                 | 8.9                   | 3.2                           | Amorphous                                         |

| $Si_3N_4$        | 7                   | 5.1                   | 2                             | Amorphous                                         |

| $Al_2O_3$        | 9                   | 8.7                   | $2.8^{a}$                     | Amorphous                                         |

| $Y_2O_3$         | 15                  | 5.6                   | $2.3^{a}$                     | Cubic                                             |

| $La_2O_3$        | 30                  | 4.3                   | $2.3^{a}$                     | Hexgaonal, cubic                                  |

| $Ta_2O_5$        | 26                  | 4.5                   | 1-1.5                         | Orthorhombic                                      |

| $TiO_2$          | 80                  | 3.5                   | 1.2                           | Tetrag. <sup>c</sup> (rutile, anatase)            |

| $HfO_2$          | 25                  | 5.7                   | 1.5 <sup>a</sup>              | Mono. <sup>b</sup> , tetrag. <sup>c</sup> , cubic |

| $ZrO_2$          | 25                  | 7.8                   | 1.4 <sup>a</sup>              | Mono. <sup>b</sup> , tetrag. <sup>c</sup> , cubic |

<sup>&</sup>lt;sup>a</sup>Calculated by Robertson. [19]

Source: [3].

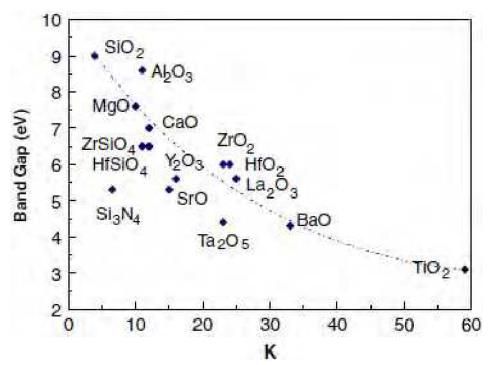

### 2.1.1 Permittivity, Bandgap, and Band Alignment to Silicon

In order to have a good insulating property, it is suggested that conduction band offset (CBO) between high-k and substrate should be larger than 1 eV to inhibit Schottky emission, and it is same for valence band offset as well. Considering different work function between substrate and the high-k dielectric, specifically a bandgap of 4 eV is necessary to avoid serious leakage current and breakdown. Figure 2.2 shows a relationship between dielectric constant and bandgap. Unfortunately, large K material like TiO<sub>2</sub> suffers from a low bandgap problem, and its large dielectric constant will give extra

bMono.=monoclinic.

<sup>&</sup>lt;sup>c</sup>Tetrag.=tetragonal.

fringe capacitance between gate and source/drain, which is not desirable. In Figure 2.2, it suggests that ZrO<sub>2</sub> and HfO<sub>2</sub> are good candidates since they have bandgap larger than 4 eV and its dielectric constant is still large enough for further EOT scaling.

**Figure 2.2** Static dielectric constant versus band gap for candidate gate oxides. Source: [19].

### 2.1.2 Thermodynamic Stability

In gate first CMOS processes, the gate stacks must undergo rapid thermal annealing (RTA) at 1000 °C for 5s. This requires that the gate oxides must be thermally and chemically stable with the contacting materials [20]. From this point of view, HfO<sub>2</sub> has better thermal stability than ZrO<sub>2</sub> [21]. Additionally, as ZrO<sub>2</sub> and HfO<sub>2</sub> thin films were grown by atomic layer deposition, the structural and electrical behavior of the films were somewhat precursor-dependent, revealing better insulating properties in the films grown from oxygen-containing precursors, therefore the HfO<sub>2</sub> films showed lower leakage

compared to ZrO<sub>2</sub> [22].

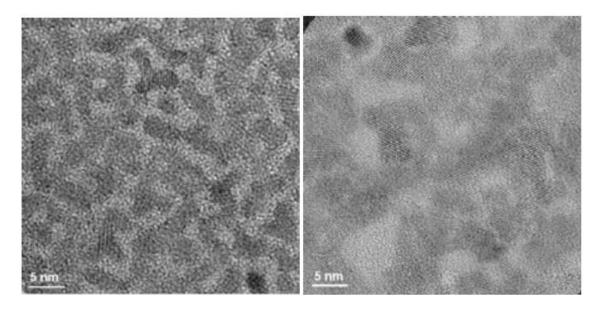

# 2.1.3 Film Morphology and Deposition Method

It is desirable to have an amorphous high-k layer after necessary processing treatments due to serval benefits of amorphous structure. Polycrystalline gate dielectrics are not favored as gate oxide layer since grain boundaries serve as high-leakage paths. In addition, grain size and orientation can cause significant variation in K value. However, most

high-k material except  $Al_2O_3$  will form polycrystalline film either during deposition or after thermal treatment if temperature is high enough. HfO<sub>2</sub> or ZrO<sub>2</sub>, crystallize at much lower temperatures at ~400 °C and ~300 °C, shown in Figure 2.3 [23].