# Hardware Implementation of Barrett Reduction Exploiting Constant Multiplication

by

Crystal Andrea Roma

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Master of Applied Science in Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2019

© Crystal Andrea Roma 2019

#### Author's Declaration

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### Abstract

The efficient realization of an Elliptic Curve Cryptosystem is contingent on the efficiency of scalar multiplication. These systems can be improved by optimizing the underlying finite field arithmetic operations which are the most costly such as modular reduction. There are elliptic curves over prime fields for which very efficient reduction formulas are possible due to the special structure of the moduli. For prime moduli of arbitrary form, however, use of general reduction formulas, such as Barrett's reduction algorithm, are necessary. Barrett's algorithm performs modular reduction efficiently by using multiplication as opposed to division, an operation which is generally expensive to realize in hardware. We note, however, that when an Elliptic Curve Cryptosystem is defined over a fixed prime field, all multiplication steps in Barrett's scheme can be realized through constant multiplications; this allows for further optimization.

In this thesis, we study the influence using constant multipliers has on four different Barrett reduction variants targeting the Virtex-7 (xc7vx485tffg1157-1). We use the FloPoCo core generator to construct constant multiplier implementations for the different multiplication steps required in each scheme. Then, we create a hybrid constant multiplier circuit based on Karatsuba multiplication which uses smaller FloPoCo-generated base multipliers. It is shown that for certain multiplication steps, the hybrid design provides an improvement in the resource utilization of the constant multiplier circuit at the cost of an increase in the critical path delay. A performance comparison of different Barrett reduction circuits using different combinations of constant multiplier architectures is presented. Additionally, a fully pipelined implementation of each Barrett reduction variant is also designed capable of achieving operational frequencies in the range of 496-504MHz depending on the Barrett scheme considered. With the addition of a 256-bit pipelined Karatsuba multiplier circuit, we also present a compact and fully pipelined modular multiplier based on these Barrett architectures capable of achieving very high throughput compared to others in the literature without the use of embedded multipliers.

#### Acknowledgements

I would like to thank my supervisor, Dr. Anwar Hasan, for his guidance throughout the completion of my degree; your unending support and guidance were truly invaluable. I would also like to express my gratitude to all of the professors which I had the pleasure to take courses with throughout my Masters, particularly Dr. Alfred Menezes, Dr. Andrew Morton, Dr. Nachiket Kapre, and Dr. Mahesh Tripunitara.

A very special thanks to the Natural Sciences and Engineering Research Council of Canada and the Electrical and Computer Engineering Department at the University of Waterloo for their generous financial support.

Last but certainly not least, I would like to thank my family and friends. Thank you to my parents, Maria and Andrea, despite the distance between us, your love and support was always felt. Giovanna and Alessia, I could say thank you for many things but most of all, thank you for always showing me what one can achieve with a little hard work. You two inspire me every day to strive for more and push my limits; I am blessed and incredibly lucky to call you my sisters. Finally to Hejir, I would like to say thank you for seeing me through every struggle and every triumph. This experience would not have been the same had it not been shared with you.

#### Dedication

This thesis is dedicated to my parents, Maria and Andrea Roma.

## **Table of Contents**

| Li | st of | Table   | S                                                | ix   |

|----|-------|---------|--------------------------------------------------|------|

| Li | st of | Figur   | es                                               | xi   |

| A  | bbre  | viation | IS                                               | xiii |

| 1  | Intr  | roduct  | ion                                              | 1    |

|    | 1.1   | Motiv   | $\operatorname{ation}$                           | 1    |

|    | 1.2   | Contr   | ibutions                                         | 2    |

|    | 1.3   | Thesis  | s Organization                                   | 3    |

| 2  | Bac   | kgrou   | nd                                               | 4    |

|    | 2.1   | Ellipti | ic Curve Cryptography                            | 4    |

|    |       | 2.1.1   | Finite Fields                                    | 5    |

|    |       | 2.1.2   | Finite Field Arithmetic                          | 6    |

|    |       | 2.1.3   | Point Arithmetic in ECC over Prime Finite Fields | 7    |

|    |       | 2.1.4   | Select Elliptic Curves Over $\mathbb{F}_P$       | 9    |

|    | 2.2   | Karat   | suba Multiplication                              | 11   |

|    | 2.3   | Const   | ant Multiplication                               | 13   |

|    | 2.4   | Summ    | nary                                             | 16   |

| 3 | Bar | rett R | eduction Variants                             | 17 |

|---|-----|--------|-----------------------------------------------|----|

|   | 3.1 | Modu   | lar Reduction                                 | 17 |

|   | 3.2 | Gener  | al Barrett Reduction                          | 18 |

|   | 3.3 | Impro  | ved Barrett Reduction                         | 21 |

|   | 3.4 | Foldin | g Barrett Reduction                           | 23 |

|   | 3.5 | Modu   | lar Multiplier with Folding Barrett Reduction | 26 |

|   | 3.6 | Comp   | arison of Reduction Techniques                | 29 |

|   | 3.7 | Summ   | ary                                           | 33 |

| 4 | Cor | nstant | Multiplier Hardware Implementation            | 36 |

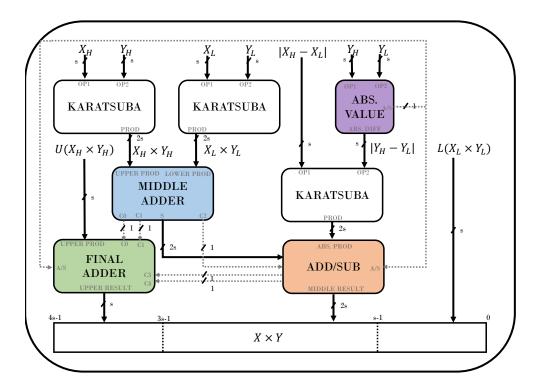

|   | 4.1 | Descri | ption of Multiplier Module                    | 36 |

|   |     | 4.1.1  | Absolute Value                                | 38 |

|   |     | 4.1.2  | Middle Adder                                  | 40 |

|   |     | 4.1.3  | Adder/Subtractor                              | 40 |

|   |     | 4.1.4  | Final Adder                                   | 41 |

|   |     | 4.1.5  | Modifications for Fully Pipelined Design      | 41 |

|   | 4.2 | Study  | of Constant Multipliers                       | 42 |

|   | 4.3 | Result | s of Constant Multiplier (Not Pipelined)      | 46 |

|   |     | 4.3.1  | General Barrett                               | 46 |

|   |     | 4.3.2  | Folding Barrett                               | 49 |

|   | 4.4 | Result | s of Constant Multiplier (Pipelined)          | 53 |

|   |     | 4.4.1  | General Barrett                               | 53 |

|   |     | 4.4.2  | Folding Barrett                               | 57 |

|   | 4.5 | Summ   | ary                                           | 62 |

| 5 | Bar           | rett Reduction Hardware Implementations          | 63 |

|---|---------------|--------------------------------------------------|----|

|   | 5.1           | Barrett Reduction Implementation (Not Pipelined) | 63 |

|   | 5.2           | Barrett Reduction Implementation (Pipelined)     | 66 |

|   | 5.3           | Modular Multiplier                               | 68 |

|   | 5.4           | Summary                                          | 70 |

| 6 | Cor           | clusion and Future Work                          | 72 |

|   | 6.1           | Concluding Remarks                               | 72 |

|   | 6.2           | Future Work                                      | 73 |

| R | e <b>fere</b> | nces                                             | 74 |

## List of Tables

| 2.1 | The prime field used by each of the four curves studied in this thesis. Each prime field in question is 256 bits in length.                                                                 | 12 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | Precomputations pertinent to each variation of the Barrett reduction scheme where $k$ is the length of the modulus.                                                                         | 30 |

| 3.2 | Operations required for each reduction scheme where k is the length of the modulus                                                                                                          | 30 |

| 3.3 | The precomputed constants for each curve in question when using the General Barrett reduction scheme. Each $\mu$ constant is 257 bits in length                                             | 34 |

| 3.4 | The precomputed constants for each curve in question when using the Improved Barrett reduction scheme. Each $\mu$ constant is 260 bits in length                                            | 34 |

| 3.5 | The precomputed constants for each curve in question when using the Fold-<br>ing Barrett reduction scheme. Each $\mu$ constant is 129 bits in length and<br>each $P'$ constant is 256 bits. | 35 |

| 3.6 | The precomputed constants for each curve in question when using the Improved Folding Barrett reduction scheme. Each $\mu$ constant is 132 bits in length and each $P'$ constant is 256 bits | 35 |

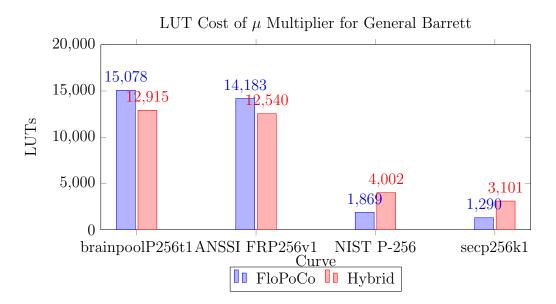

| 4.1 | LUTs, delay, and area×time metrics for the $\mu$ multiplier in General Barrett.                                                                                                             | 47 |

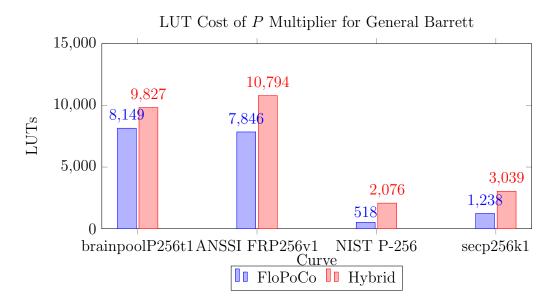

| 4.2 | LUT, delay, and area×time metrics for the $P$ multiplier in General Barrett.                                                                                                                | 48 |

| 4.3 | LUTs, delay, and area×time metrics for the $P'$ multiplier in Folding Barrett.                                                                                                              | 50 |

| 4.4  | LUTs, delay, and area×time metrics for the $\mu$ multiplier in Folding Barrett.                                                                                                                           | 51 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.5  | LUT, delay, and area×time metrics for the $P$ multiplier in Folding Barrett.                                                                                                                              | 52 |

| 4.6  | Resource utilization, frequency, and pipeline depth metrics for the $\mu$ multiplier in pipelined General Barrett.                                                                                        | 56 |

| 4.7  | Resource utilization, frequency, and pipeline depth metrics for the <i>P</i> multiplier in pipelined General Barrett.                                                                                     | 56 |

| 4.8  | Resource utilization, frequency, and pipeline depth metrics for the $P'$ multiplier in pipelined Folding Barrett.                                                                                         | 61 |

| 4.9  | Resource utilization, frequency, and pipeline depth metrics for the $\mu$ multiplier in pipelined Folding Barrett.                                                                                        | 61 |

| 4.10 | Resource utilization, frequency, and pipeline depth metrics for the $P$ multiplier in pipelined Folding Barrett.                                                                                          | 62 |

| 5.1  | LUT, delay, and area×time metrics for the Barrett reduction under different multiplication methods for the modulus characteristic to the Brainpool curve.                                                 | 65 |

| 5.2  | LUT, delay, and area×time metrics for the Barrett reduction under different multiplication methods for the modulus characteristic to the ANSSI curve.                                                     | 66 |

| 5.3  | Resource utilization, frequency, and pipeline depth metrics for various Bar-<br>rett reduction schemes under different multiplication methods for the mod-<br>ulus characteristic to the Brainpool curve. | 67 |

| 5.4  | Resource utilization, frequency, and pipeline depth, metrics for various Bar-<br>rett reduction schemes under different multiplication methods for the mod-<br>ulus characteristic to the ANSSI curve.    | 68 |

| 5.5  | Resource utilization, frequency, and pipeline depth, metrics for a 256-bit<br>modular multiplier based on the different Barrett reduction schemes pre-<br>sented compared against those in the literature | 71 |

|      | semen compared against mose in the interature                                                                                                                                                             | 11 |

# List of Figures

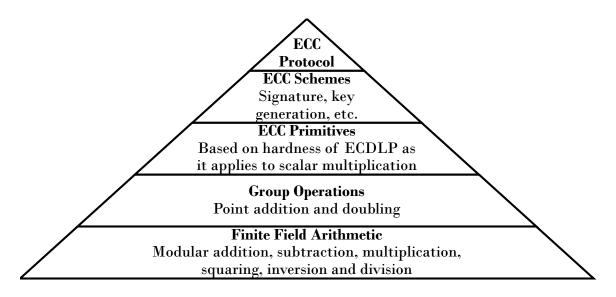

| 2.1 | The hierarchy of Elliptic Curve Cryptosystems.                                                                                                                                                                                                            | 8  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

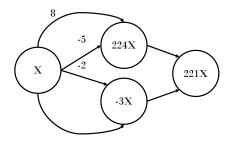

| 2.2 | Example of a possible DAG for the multiplication $221X$                                                                                                                                                                                                   | 15 |

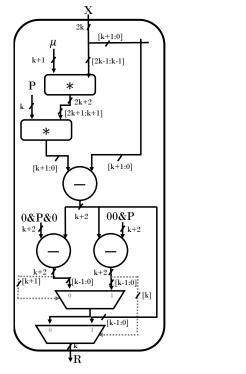

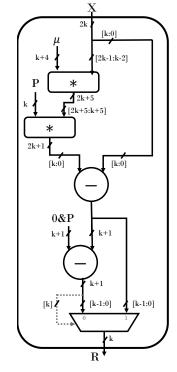

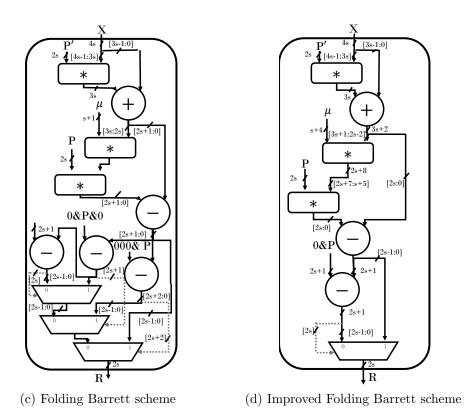

| 3.1 | Architectures of Barrett reduction schemes                                                                                                                                                                                                                | 33 |

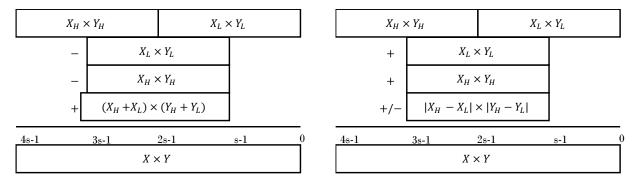

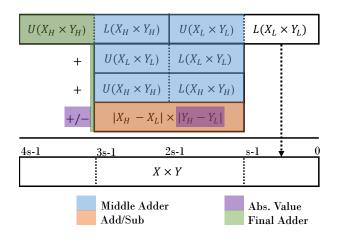

| 4.1 | a) Graphical representation of the original Karatsuba algorithm compared<br>to b) a modified version of Karatsuba using absolute value and conditional<br>adder/subtractor unit where $2s = k$ and $k$ is the length of the operands<br>being multiplied. | 38 |

| 4.2 | Top level of the Karatsuba arithmetic based on [10]                                                                                                                                                                                                       | 39 |

| 4.3 | Top level of the Karatsuba module based on [10].                                                                                                                                                                                                          | 39 |

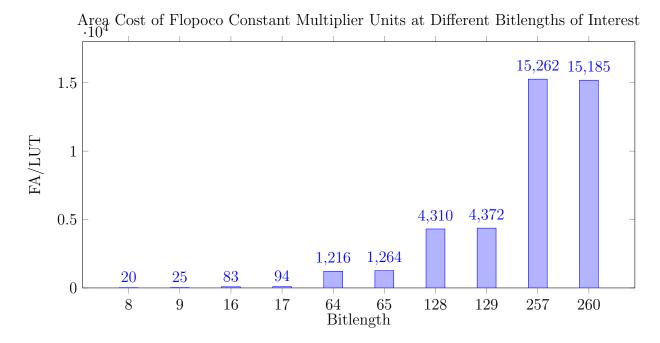

| 4.4 | Exploring the LUT cost of FloPoCo constant multipliers at varying bitlengths.                                                                                                                                                                             | 43 |

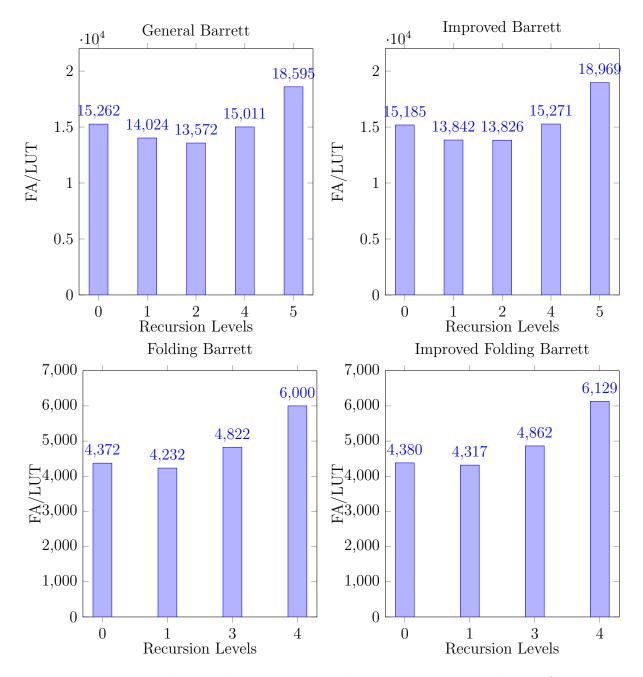

| 4.5 | Estimated cost when using Karatsuba multiplication and FloPoCo constant multipliers as it pertains to each $\mu$ constant for the different Barrett variants studied.                                                                                     | 45 |

| 4.6 | Comparison of synthesized multiplier designs when considering the $\mu$ multiplier in the General Barrett reduction scheme.                                                                                                                               | 47 |

| 4.7 | Comparison of synthesized multiplier designs when considering the $P$ multiplier in the General Barrett reduction scheme.                                                                                                                                 | 48 |

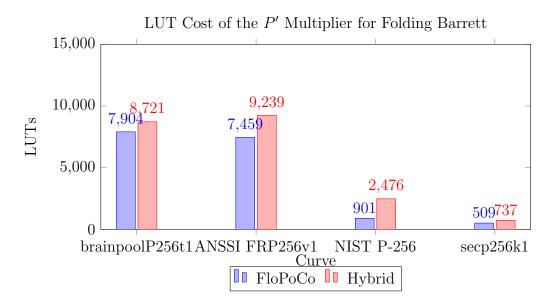

| 4.8 | Comparison of synthesized multiplier designs when considering the $P'$ multiplier in the Folding Barrett reduction scheme.                                                                                                                                | 50 |

| 4.9  | Comparison of synthesized multiplier designs when considering the $\mu$ multiplier in the Folding Barrett reduction scheme. | 51 |

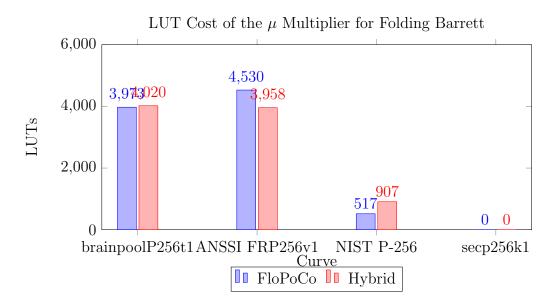

|------|-----------------------------------------------------------------------------------------------------------------------------|----|

| 4.10 | Comparison of synthesized multiplier designs when considering the $P$ multiplier in the Folding Barrett reduction scheme.   | 52 |

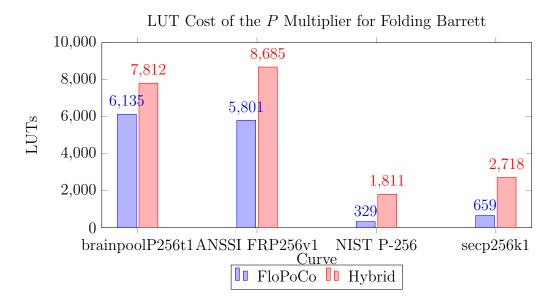

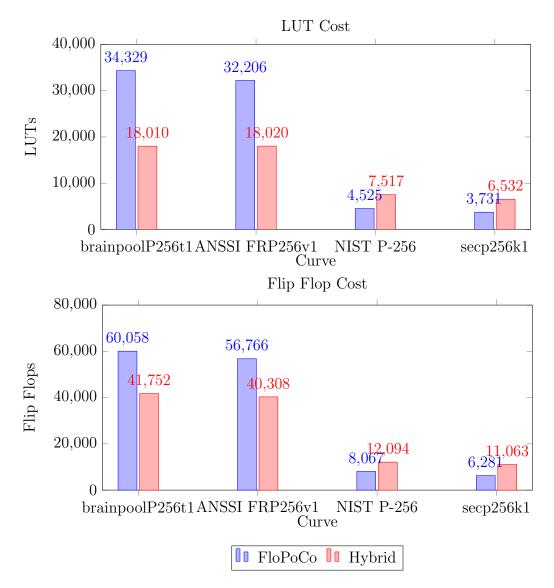

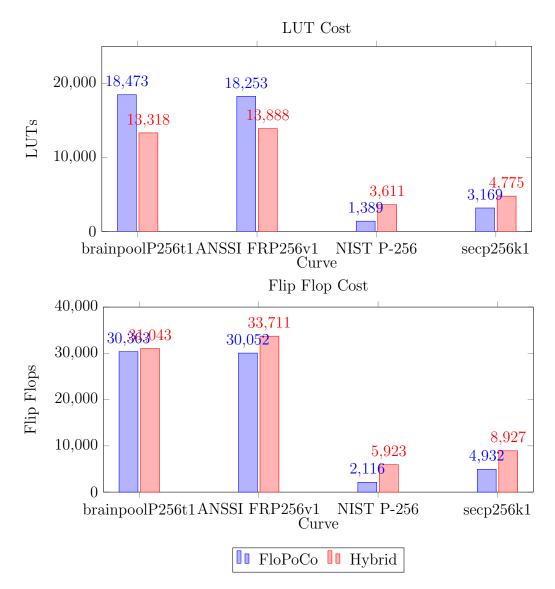

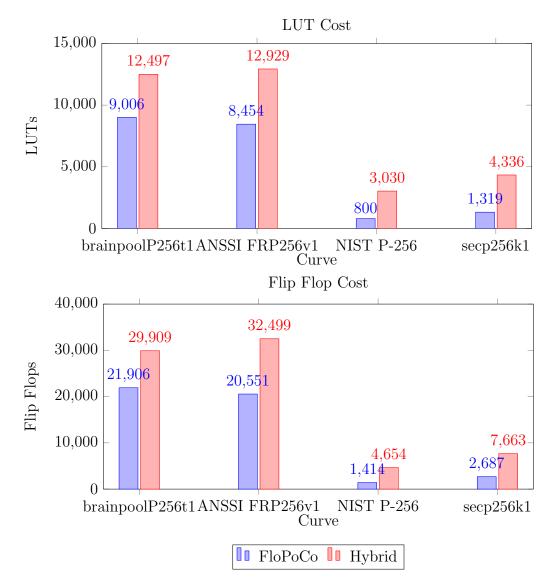

| 4.11 | LUT and Flip Flop cost for pipelined $\mu$ multiplier for the General Barrett reduction scheme.                             | 54 |

| 4.12 | LUT and Flip Flop cost for pipelined <i>P</i> multiplier for the General Barrett reduction scheme.                          | 55 |

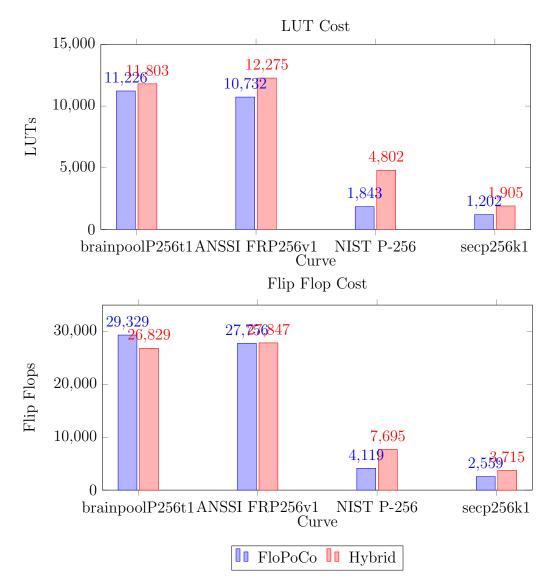

| 4.13 | LUT and Flip Flop cost for pipelined $P'$ multiplier for the Folding Barrett reduction scheme.                              | 58 |

| 4.14 | LUT and Flip Flop cost for pipelined $\mu$ multiplier for the Folding Barrett reduction scheme.                             | 59 |

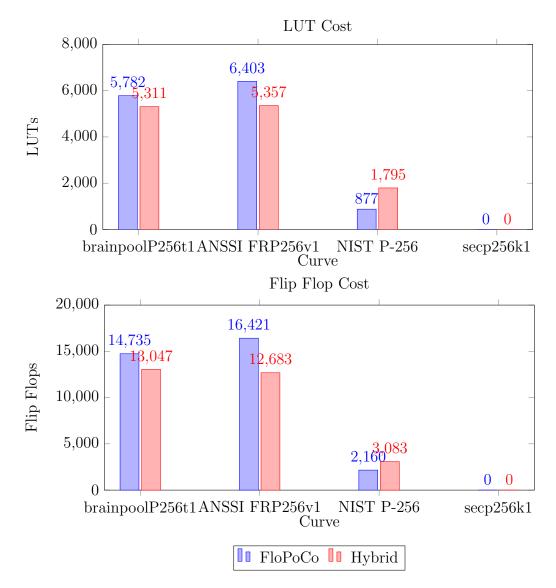

| 4.15 | LUT and Flip Flop cost for pipelined $P$ multiplier for the Folding Barrett reduction scheme.                               | 60 |

## Abbreviations

- **ANSSI** Agence nationale de la sécurité des systèmes d'information 3, 10

- BHM Bull-Horrocks Modified 16

- CSD Canonical Signed-Digit 14

- **CSE** Common Sub-Expression Elimination 15

- DAG Directed Acyclic Graph 2, 16

- **ECC** Elliptic Curve Cryptography 1

- **ECDLP** Elliptic Curve Discrete Logarithm Problem 4

- **ETSI** European Telecommunications Standards Institute 11

- FPGAs Field Programmable Gate Arrays 13

- GLV Gallant-Lambert-Vanstone 10

- NAF Non-Adjacent Form 8

- **NIST** National Institute of Standards and Technology 1

- **RAG-n** n-Dimensional Reduced Adder Graph 16

- **SCM** Single Constant Multiplication 14

### Chapter 1

## Introduction

### 1.1 Motivation

The algorithms which comprise public-key cryptographic schemes rely on the hardness of the underlying mathematics on which they are based. Security is guaranteed by the fact that the computational work required to break the core mechanisms of these schemes on a conventional computer is infeasible. Elliptic Curve Cryptography (ECC) was developed independently by Koblitz and Miller in 1985 [31, 39]. ECC is generally preferred over its RSA counterparts as it achieves the same security guarantees while using smaller key sizes. As a result, more efficient realizations of these cryptosystems are possible. Vital to the efficiency of these elliptic curve operations is the underlying finite field primitives by which they are implemented.

The computational complexity of division in hardware has given rise to the need for efficient reduction algorithms. Many elliptic curve cryptosystems today are defined over primes of special form which lead to efficient finite field operations. For instance, the National Institute of Standards and Technology (NIST) recommends primes of the General Mersenne Prime form for which efficient reduction algorithms have been devised which are comprised of a handful of shifts, additions and subtractions. Despite this, there has been growing interest in designing ECC cryptosystems over pseudo-random primes due to increased skepticism in the NIST primes and due to a number of attacks which exploit this special form. Unfortunately, due to the pseudo-random nature of these prime moduli, reduction must be performed using a generic reduction algorithm, such as that due to Barrett or Montgomery [3, 40]. By consequence, the achievable performance of these primes pales in comparison to those of special form. Modular multipliers in the literature typically either focus on high-performance elliptic curve processors over specialized primes or rather, provide a general implementation suitable for any finite field of a certain length.

The focus of this thesis is instead on designing a modular reduction circuit based on Barrett's algorithm targeting specifically pseudo-random or generalized moduli. The Barrett reduction module is optimized by focusing on the multiplication steps within the algorithm, all of which are multiplications by a constant provided that the finite field over which the cryptosystem is designed is fixed. The goal of designing an efficient Barrett reduction implementation then reduces to the problem of designing efficient constant multipliers. Consequently, additional efforts can be made to optimize the circuit to achieve better area and performance metrics.

### **1.2** Contributions

As modular reduction is such a critical step in designing efficient ECC implementations, there are many proposed works in the literature. There have been works which propose special moduli sets with which the multiplication steps in Montgomery and Barrett reduction algorithms can be replaced by simple shift operations, offering further speed ups [30, 50]; however, this again reduces to using only specific sets of prime moduli and cannot be expanded to pseudo-random primes of arbitrary form.

First, a study of the hardware complexity of FloPoCo's core generator Shift-and-Add Directed Acyclic Graph (DAG) constant multiplier [12] is provided as it pertains to the multiplication steps of four different Barrett variants. This constant multiplier is then used as a base atop which Karatsuba's algorithm is applied recursively at varying depths to study whether this divide-and-conquer algorithm can improve constant multiplication modules. To our knowledge, there has yet to be a work which marries these two ideas. It is shown that under certain conditions, the hybrid Karatsuba-FloPoCo constant multiplier requires less resources to implement than a pure FloPoCo-generated constant multiplier. Next, we apply the results of our constant multiplication study to four different Barrett reduction variants that have been presented in the literature. We target specifically two elliptic curve standards which are defined over pseudo-random prime finite fields: BrainpoolP256t1 and Agence nationale de la sécurité des systèmes d'information (ANSSI) FRP256v1. The performance and resource utilization of the four different Barrett variants are contrasted. Lastly, a fully pipelined architecture is also provided which is then used in conjunction with a generic pipelined 256-bit Karatsuba multiplier to realize a 256-bit modular multiplier. Our design is capable of operating around 500MHz on the Virtex-7 (xc7vx485tffg1157-1) and is able to accept new data on every clock cycle. Compared to general 256-bit modular multipliers in the literature, our design presents a compact and portable alternative which achieves much better throughput.

### **1.3** Thesis Organization

This thesis is organized as follows. Chapter 2 provides background information centered around elliptic curves and finite field arithmetic, Karatsuba's multiplication, and an introduction to the different algorithms available to perform constant multiplication. Chapter 3 gives an overview of modular reduction with a focus on four different Barrett reduction variants. Chapter 4 provides a description of the Karatsuba-based constant multiplier used in the hybrid circuit. We also present synthesis results for the various constant multipliers as required by the four Barrett variants, concentrating on four different prime finite fields. Here, the FloPoCo-generated constant multiplier is compared against the hybrid multiplier for each of the constant multiplication steps required by the different Barrett forms studied. Chapter 5 presents full Barrett reduction circuits as based on the results obtained in Chapter 4, as well as fully pipelined 256-bit modular multiplier architectures. Lastly, concluding remarks and opportunities for future work are provided in Chapter 6.

## Chapter 2

## Background

Presented here is general background information which will lay the ground work for the remainder of this thesis. This consists of a mathematical background relevant to ECC as well as multiplication methods of importance to this work. A short introduction to finite field arithmetic is provided as a motivation for the work. An introduction to Karatsuba's algorithm is given which will later be adapted to suit the implemented multiplier. Further, an exploration into the importance of constant multiplication is provided as well as a study of the various existing methods in the literature.

### 2.1 Elliptic Curve Cryptography

Public-key cryptosystems are designed in a hierarchical manner. They can broadly be categorized into three levels: primitives, schemes, and protocols [27]. A primitive is a basic mathematical operation which is based in a complex number-theoretic problem. The three main problems on which the majority of public-key systems today are based are integer factorization, discrete logarithms over finite fields, and the Elliptic Curve Discrete Logarithm Problem (ECDLP). Atop these primitives, a scheme can be designed which provides complexity-theoretic security due to the underlying hard problem characteristic to said primitives. From these schemes, application-specific protocols can be designed to provide the desired security goal [27].

ECC was first proposed as an alternative approach to carrying out the Diffie-Hellman key exchange protocol. Since then, ECC has expanded tremendously and been applied to a wider range of cryptographic applications. Its security lies in the hardness of the ECDLP. This problem has been proven to be harder to solve than other public-key protocols which rely on the hardness of factoring. As a result, practical implementations of these protocols are more efficient in terms of time and space [24]. It is for this reason that many applications have been upgrading to ECC.

#### 2.1.1 Finite Fields

In ECC, elliptic curves are defined over finite fields. In general, a field is a set  $\mathbb{F}$  of a finite number of elements together with the addition (+) and multiplication (·) operations. A prime finite field is a field which contains a prime number of members. The prime finite field  $\mathbb{F}_P$ , where P is an odd prime, consists of the finite set of integers [0, P - 1] where addition and multiplication operations are defined modulo the prime P. Given positive integers  $a, b, c \in \mathbb{F}_P$ , prime finite fields satisfy the following properties:

- 1. Addition: the set of elements in  $\mathbb{F}_P$  together with the addition operation form an abelian group with additive identity 0.

- 2. Multiplication: the set of elements in  $\mathbb{F}_P$  together with the multiplication operation form an abelian group with identity 1.

- 3. Negatives: the element (-b) is the unique negative of b with the property that  $(b + (-b)) \mod P \equiv 0 \mod P$ .

- 4. Inverses: the element  $(b^{-1})$  is the unique inverse of b with the property that  $(b \cdot (b^{-1})) \mod P \equiv 1 \mod P$ .

- 5. Distributive: The distributive law holds so that  $(a+b) \cdot c = a \cdot c + b \cdot c$  for all  $a, b, c \in \mathbb{F}_{\mathbb{P}}$ .

#### 2.1.2 Finite Field Arithmetic

Suppose positive integers  $a, b \in \mathbb{F}_P$  are to be added. To compute  $(a + b) \mod P$ , the sum is first obtained. Since  $a, b \in \mathbb{F}_P$  then it must be that a, b < P. As a result, (a + b) < 2P. Reduction would then involve at most one subtraction by P. Now, suppose these numbers are to be multiplied. To compute  $a \cdot b \mod P$  in the classical way, the product is first obtained and the result is then reduced to obtain a product in the range of [0, P-1]. Since a, b < P, the size of the number to be reduced in the case of multiplication is  $(a \cdot b) < P^2$ [24].

Subtraction and division are also possible field operations. Both of these operations are defined with regards to field addition and field multiplication. A modular subtraction is defined as  $(a - b) \mod P \equiv (a + (-b)) \mod P$ . To compute  $(a - b) \mod P$ , a regular subtraction a - b is first performed. In the case that  $a \ge b$  then 0 < a - b < P and no correction step is needed. When a < b, however, the lower bound on the value of the difference is (a - b) > -P. Correction would then involve at most one addition by Pin order for the integer result to be in the range [0, P - 1]. Next, suppose with positive integers  $a, b \in \mathbb{F}_P$  we wish to perform the division of a by b. If  $b \ne 0$ , then modular division is defined as  $(a/b) \mod P \equiv (a \cdot (b^{-1})) \mod P$ . To compute  $(a/b) \mod P$  in the classical way, the inverse of b must be obtained; the product is then computed. To obtain a result in the range of [0, P - 1], the result must be reduced. Since  $a, b^{-1} < P$ , the size of the number to be reduced in the case of division is  $(a/b) < P^2$  [24].

**Example** By the above definitions, we demonstrate field operations over the prime field  $\mathbb{F}_{31}$ . This prime finite field consists of the numbers [0, 30]. All field operations are performed mod 31.

- 1. Addition:  $(24 + 27) \mod 31 \equiv 51 \mod 31 \equiv 20$

- 2. Subtraction:  $(24 + (-27)) \mod 31 \equiv -3 \mod 31 \equiv 28$

- 3. Multiplication:  $(24 \cdot 27) \mod 31 \equiv 648 \mod 31 \equiv 28$

- 4. *Inversion*:  $(27^{-1}) \mod 31 \equiv 23$

- 5. Division:  $(24/27) \mod 31 \equiv (24 \cdot 27^{-1}) \mod 31 \equiv 552 \mod 31 \equiv 25$

#### 2.1.3 Point Arithmetic in ECC over Prime Finite Fields

These ideas are now expanded with respect to elliptic curves. Elliptic curves over odd prime finite fields can be described by the short Weirerstrass equation:

$$E/\mathbb{F}_P: y^2 = x^3 + ax + b \tag{2.1}$$

where a and b are integers modulo P such that  $4a^3 + 26b^2 \neq 0 \mod P$ . An elliptic curve defined over a finite field  $\mathbb{F}_P$  has a finite number of points Q = (x, y). The x and y coordinates lie within the underlying field  $(x, y \in \mathbb{F}_P)$ . These points satisfy the given Weierstrass equation. The number of points on the curve, including an additional point known as the point at infinity (denoted as  $\infty$ ) is called the order of the curve [24].

Points on an elliptic curve can be added to yield a third point on the curve.  $E/\mathbb{F}_P$  forms an abelian group under addition with the point at infinity being the identity element. The group law of elliptic curves which is used in elliptic curve cryptosystems defined over a prime field is given below, where the use of affine coordinates is assumed. It should be noted that the formulas for addition and doubling are defined over the prime finite field; the resulting point coordinates must be obtained by applying the finite field arithmetic operations described in the previous section.

- 1. Identity:  $Q + \infty = \infty + Q = Q$  for all  $Q \in E/\mathbb{F}_P$ .

- 2. Negatives:  $(x, y) + (x, -y) = \infty$ . The point (x, -y) is called the *negative* of Q and is denoted by -Q.

- 3. Point Addition: For points  $Q = (x_1, y_1)$  and  $Z = (x_2, y_2) \in E/\mathbb{F}_P$  where  $Q \neq \pm Z$  the addition  $Q + Z = (x_3, y_3)$  is obtained by computing

$$x_3 = \left(\frac{y_2 - y_1}{x_2 - x_1}\right)^2 - x_1 - x_2$$

and  $y_3 = \left(\frac{y_2 - y_1}{x_2 - x_1}\right)(x_1 - x_3) - y_1$

4. Point Doubling: For point  $Q = (x_1, y_1) \in E/\mathbb{F}_P$  where  $Q \neq -Q$  then  $2Q = (x_3, y_3)$  is obtained by computing

$$x_3 = \left(\frac{3x_1^2 + a}{2y_1}\right)^2 - 2x_1 \text{ and } y_3 = \left(\frac{3x_1^2 + a}{2y_1}\right)(x_1 - x_3) - y_1$$

Figure 2.1: The hierarchy of Elliptic Curve Cryptosystems.

The hierarchy of ECC follows the same organization as previously described. ECC protocols are designed using ECC schemes built on top of the operation of elliptic curve scalar multiplication. This operation is a mathematical primitive based on the hardness of the ECDLP. Scalar multiplication of a point on an elliptic curve essentially reduces to repeated addition of the same point. The hierarchy of ECC can be seen in Figure 2.1.

Performing scalar multiplications efficiently is critical to the overall efficiency of an ECC cryptosystem. As depicted by Figure 2.1, optimization at any of the lower levels translates upwards to achieve a more efficient scalar multiplication operation. At the primitive level, the main approach towards achieving better performance is through the use of scalar *recoding* schemes such as the Non-Adjacent Form (NAF) which reduces the overall density of non-zero digits in the representation of the scalar [49]. Such an approach will reduce the number of additions needed when using the *double-and-add* approach to scalar multiplication. At the group level, the use of different coordinate systems can also improve the efficiency of elliptic scalar multiplication by adjusting the number of field operations needed to perform a point addition and point doubling. This can be advantageous as certain field operations (namely modular inversion) are quite costly to perform. The reader is referred to [24] or [47] for further details on the point addition and

doubling formulas which pertain to each coordinate system variant. Lastly, optimization efforts can also target the finite field arithmetic by optimizing the modular operations which are the most costly, such as modular multiplication. It is this level that is targeted in this thesis.

#### 2.1.4 Select Elliptic Curves Over $\mathbb{F}_P$

As the focus of this thesis is on the exploitation of constant multiplications, implementations are designed with four different fields in mind. The fields in this study are chosen such as to show the impact a custom Barrett reduction deployment can have on the overall area and performance of the scheme. Particularly, such an approach may be of use in cryptosystems using a general prime field for which no efficient reduction scheme exists. To demonstrate this contrast, we select two elliptic curves whose underlying prime field has a special form and two curves which have been randomly constructed. Despite the different forms the primes may take, all are 256 bits in length. The prime finite field parameter of these four curves can be seen in Table 2.1.

In FIPS 186-4 Digital Signature Standard [53], NIST recommends the use of five prime fields targeting different security strengths. Each of these primes are Generalized Mersenne primes which are of the form:

$$P = b^n + c_{n-1}b^{n-1} + \dots + c_0 (2.2)$$

where b is a power of 2 corresponding to a machine's native wordsize and  $c_i$  is an integer. When a number is to be reduced modulo this type of prime, specialized fast reduction algorithms can be used [53]. In a method designed by Solinas, the number to be reduced can be expressed as a sum or difference of a small number of terms, all of which are scaled by powers of 2 [48]. Once computed, the final result may need to be subtracted by multiples of P to be in the range [0, P - 1]. These powers are expressed as multiples of 32, leading to a very fast implementation on hardware. NIST curve P-256 (also known as secp256r1) is one of the NIST recommended elliptic curves defined which will be studied in this thesis. Reduction over NIST P-256 reduces to two doublings, four 256-bit subtractions, and four 256-bit additions with the final result in the range (-4P, 5P), requiring up to four additions/subtractions to achieve the final corrected result [22, 48, 53]. NIST's curve P-256 is one of the most widely used elliptic curves; it is supported in applications such as OpenSSL and internet browsers such as Apple Safari, Google Chrome, Microsoft Internet Explorer, and Mozilla Firefox [21].

Secp256k1 is a Koblitz curve of prime order defined in Certicom Research's Standards for Efficient Cryptography [43]. The finite field is specified by a Pseudo-Mersenne prime, which are special primes of the form:

$$P = 2^{\alpha} - \gamma \tag{2.3}$$

where  $\alpha$  is a parameter corresponding to the desired security strength, and  $\gamma$  is a positive integer that is relatively small compared to the modulus. Pseudo-Mersenne primes can achieve even faster modular reduction compared to Generalized Mersenne primes. Reduction using secp256k1's prime modulus can be designed in a compact way using a specialized reduction formula [38]. An integer  $0 \le z < (2^{\alpha} - \gamma)^2$  can be represented in radix- $2^{\alpha}$  as  $U(z)2^{\alpha} + L(z)$  where U(z) and L(z) represent the upper and lower bits of z. Then, using the fact that  $2^{\alpha} \equiv \gamma \mod P$ , we have  $U(z)2^{\alpha} + L(z) \equiv U(z)\gamma + L(z) \mod P$  where  $0 \leq U(z)\gamma + L(z) < (\gamma + 1)2^{\alpha}$ . Another radix- $2^{\alpha}$  split brings the intermediate result into the range  $[0, 2^{\alpha} + \gamma^2)$ ; the final result is obtained after additional subtractions by P [6, 11]. If it is assumed that  $\gamma$  is smaller than the machine wordsize, then this reduction requires only shifts, additions, and single-precision multiplications. In addition to this custom reduction formula, Koblitz curves are especially efficient in practice as they possess efficiently computable endomorphisms through which efficient scalar multiplication operations can be performed by using the Gallant-Lambert-Vanstone (GLV) decomposition [5]. Due to its high-performance, secp256k1 is used by cryptocurrencies such as the Bitcoin and Ripple networks [20].

Although the special structure of the aforementioned curves leads to very efficient implementations, it may also be the cause of security vulnerabilities, such as that presented in [18]. This is among the reasons for which other elliptic curve standards defining elliptic curves over pseudo-random prime fields are used. ANSSI FRP256v1 is one such curve which has no special structure [14]. Unlike the previous curves mentioned, there is no fast reduction formula for the ANSSI curve. Unfortunately, the standard provides no

justification for the choice of its parameters, a cause for much skepticism regarding its deployment.

Since the Snowden documents suggested that there exists a back door in NIST's standardized Dual Elliptic Curve Deterministic Random Number Generator [52], there has been a movement towards using elliptic curves whose parameters have been generated by a verifiably deterministic way. The Brainpool standard curves were created with the goal of providing standard elliptic curve parameters which were created in a pseudo-random, systematic, and reproducible fashion and to avoid the security vulnerabilities to which many elliptic curves of special form fall victim [35]. These features make the Brainpool curves attractive for applications requiring high-assurance such as vehicle-to-vehicle and vehicleto-infrastructure communication, where there has been a push to include the Brainpool curves as part of the European Telecommunications Standards Institute (ETSI) standards [36, 46]. Unfortunately, due to its pseduo-random nature, its deployment is usually much slower in practice compared to other prime curves targeting the same security level [37].

### 2.2 Karatsuba Multiplication

The Karatsuba algorithm for integer multiplication was proposed in 1962 by Karatsuba and Ofman as an alternative approach to conventional multiplication [29]. The algorithm follows a divide-and-conquer approach which can be much faster than the classical method of multiplication when working with very large operands, as is the case in ECC. Let Xand Y be two k-bit unsigned integers and k is even. These two operands can be split in half and written as

$$X = 2^{k/2}X_H + X_L$$

and  $Y = 2^{k/2}Y_H + Y_L$

where the subscript denotes the most significant  $(_{-H})$  and least significant  $(_{-L})$  halves of the operands. In the classical method, multiplying the two operands leads to the expression below. This leads to four half-sized multiplications and three additions.

$$XY = 2^{k}X_{H}Y_{H} + 2^{k/2}(X_{L}Y_{H} + X_{H}Y_{L}) + X_{L}Y_{L}$$

| Curve             | Field                                                                                |

|-------------------|--------------------------------------------------------------------------------------|

|                   | P = 115792089210356248762697446949407573530086143415290314195533631308867097853951   |

| NIST P-256        | =xFFFFFFFF000000010000000000000000000000                                             |

|                   | $=2^{256} - 2^{224} + 2^{192} + 2^{96} - 1$                                          |

|                   | P = 115792089237316195423570985008687907853269984665640564039457584007908834671663   |

| ${ m secp256k1}$  | = xFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF                                              |

|                   | $=2^{256}-2^{32}-977$                                                                |

|                   | $P{=}76884956397045344220809746629001649093037950200943055203735601445031516197751$  |

| DFattipoolf 2004  | = xA9FB57DBA1EEA9BC3E660A909D838D726E3BF623D52620282013481D1F6E5377                  |

| A NECT ED DAE61   | $P{=}109454571331697278617670725030735128145969349647868738157201323556196022393859$ |

| TADEZ JU J TECHTE | = xF1FD178C0B3AD58F10126DE8CE42435B3961ADBCABC8CA6DE8FCF353D86E9C03                  |

Table 2.1: The prime field used by each of the four curves studied in this thesis. Each prime field in question is 256 bits in length. Karatsuba's algorithm arises from rearranging the middle term such that it reuses the  $X_H Y_H$  and  $X_L Y_L$  product terms.

$$(X_L Y_H + X_H Y_L) = (X_H + X_L)(Y_H + Y_L) - X_H Y_H - X_L Y_L$$

The final form of Karatsuba's multiplication method is demonstrated in Equation 2.4. This leads to a multiplication method which requires only *three* half-sized multiplications at the expense of a few extra additions. The cost of these extra additions is generally minimal in comparison to the savings obtained by eliminating a multiplication.

$$XY = 2^{k}X_{H}Y_{H} + 2^{k/2}((X_{H} + X_{L})(Y_{H} + Y_{L}) - X_{H}Y_{H} - X_{L}Y_{L}) + X_{L}Y_{L}$$

(2.4)

Computation of the product terms can be postponed by applying the algorithm recursively so that at each level a product term is replaced by three multiplications of half size. Using this recursive approach allows a multiplication of two *n*-bit integers to be computed with complexity  $\mathcal{O}(n^{1.58})$  as opposed to the  $\mathcal{O}(n^2)$  of schoolbook multiplication.

#### 2.3 Constant Multiplication

The design of compact and efficient constant multiplier cores is critical in many applications ranging from digital signal processing to cryptography. For public-key cryptosystems, it is often the case that very large numbers are to be multiplied by a fixed parameter. Although modern Field Programmable Gate Arrays (FPGAs) are equipped with embedded multiplier blocks capable of performing efficient multiplication, it is not necessarily beneficial to use these devices to perform a constant multiplication as more compact, logic-based techniques are possible. Suppose we wish to multiply two *n*-bit numbers by the naive method. The multiplier is a constant, C, and our multiplicand is a variable X. We may represent the constant in its binary form as

$$C = \sum_{i=0}^{n-1} c_i 2^i$$

where  $c_i \in \{0, 1\}$ . Then, computing the product CX can be written as

$$CX = \sum_{i=0}^{n-1} c_i 2^i X$$

By this expression, constant multiplication reduces to the accumulation of shifted versions of the multiplicand. The number of partial products is equal to the number of set bits in the constant multiplier. Considering this operation in hardware, the shift operations can be accomplished through appropriate wiring and thus, has no associated cost. The complexity of this method can then be quantified by the number additions required. In the worst case, all n bits of the multiplier are set and it is necessary to perform a total of n n-bit additions, leading to an overall complexity of  $\mathcal{O}(n^2)$ . This method is akin to the schoolbook method of multiplication.

It is clear from the above evaluation that the complexity of constant multiplication strongly depends on the weight of the multiplier; that is, it depends on the number of set bits in a constant. This has motivated the use of recoding schemes where the weight of a number is reduced through a redundant representation. Canonical Signed-Digit (CSD) is one such number representation [2]. CSD recoding uses the digits  $\{-1, 0, 1\}$  to represent a number in such a way that no two adjacent digits are non-zero. Unlike in the naive approach, subtraction is also required having similar cost to addition. By using this redundant representation, at most  $\frac{n}{2}$  bits of the constant will be set and on average,  $\frac{n}{3}$  [55].

As an example, suppose we wish to compute 221X. We translate the multiplication into adds and left shifts, which is represented by the  $\ll$  operator. Using the binary encoding of 221, this multiplication reduces to:

$$221X = 11011101_2 X = X \ll 7 + X \ll 6 + X \ll 4 + X \ll 3 + X \ll 2 + X$$

requiring 5 adders. If instead we represent the constant by its CSD representation, the previous approach can be improved to use only 3 adders/subtractors:

$$221X = 100\overline{1}00\overline{1}01_{CSD}X = X \ll 8 - X \ll 5 - X \ll 2 + X.$$

Performing constant multiplication without the use of multipliers can lead to significant savings and has thus garnered a great deal of attention from the research community. The problem of realizing optimal single constant coefficient multiplication is considered to be an NP-Complete optimization problem known as the Single Constant Multiplication (SCM) problem [9]. It has been shown that the number of adders required to perform a constant

Figure 2.2: Example of a possible DAG for the multiplication 221X.

multiplication is sub-linear [17]. An exhaustive search algorithm has led to an optimal solution for any constant up to 12 bits [15] which was then extended to 19 bits in length in [23], and most recently to 32 bits in [51]. For problems involving larger constants, other algorithms can be used.

A constant multiplication decomposed into a series of shifts and additions can be represented by a DAG. Each vertex in the graph represents an adder (or subtractor) and each edge represents a left bit shift by a certain weight. A negative weight indicates whether the term is to be subtracted rather than added. Each vertex has an in-degree of two, representing the two numbers to be added (or subtracted) except for the first vertex which has an in-degree of 0. This vertex represents the variable multiplicand by which we are multiplying. Every vertex has an out-degree of at least 1 except for the last vertex having out-degree 0, representing the result, CX. By this representation, each vertex computes a certain multiple of the input multiplicand.

The main strategies in the literature used to tackle the SCM problem are Common Sub-Expression Elimination (CSE) algorithms and graph-based algorithms. CSE algorithms find common subpatterns within a signed digit representation of a constant as a way of reducing the number of adders required [8, 25, 33, 41]. The algorithm presented by Lefèvre in [33] aims to minimize the number of adders by finding maximum repeating bit patterns in the full CSD representation of the constant in question. The authors show through experimentation that for an *n*-bit constant, the number of additions grows with  $\mathcal{O}(n^{0.85})$ . On the other hand, Brisbarre et al. present a CSE-based constant multiplier algorithm which, by means of parenthesizing the CSD representation and developing a cost model with a hardware target in mind, tries to minimize the number of full adder cells to yield a low-latency and easy to pipeline architecture [8, 13]. Better results may be produced when all possible graph topologies are considered to find the optimal decomposition of a constant. Graph-based algorithms use heuristics to iteratively construct a DAG. Examples of graph-based algorithms are Bernstein's algorithm [4], Bull-Horrocks Modified (BHM) algorithm [15], the *n*-Dimensional Reduced Adder Graph (RAG-n) algorithm [15], and Hcub [54]. Each of these algorithms build the DAG bottom-up by using a heuristic which will determine the next vertex to add to the DAG. The SPIRAL project has published an online generator which produces constant multiplier DAGs based on the BHM, Hcub, and RAG-n algorithms which the public can use [42].

The majority of algorithms in the literature focus on minimizing the number of adders as a means of reducing the total amount of logic resources required. It is shown in [8] that this does not necessarily provide the best implementation in hardware. Their constant multiplier algorithm is included in the FloPoCo core generator. The FloPoCo project is an open-source framework which, through a command-line interface, takes as input an operator specification and user-defined parameters, and outputs synthesizable VHDL code [12]. As this multiplier is geared specifically towards FPGAs, it is used in this thesis.

### 2.4 Summary

Basic concepts pertaining to ECC have been reviewed. Four different 256-bit prime fields used in practice have been discussed. These primes will reappear throughout this work. Different multiplication techniques have been presented. This includes Karatsuba's algorithm which has been shown to be more efficient than the schoolbook method when multiplying large operands. Karatsuba's multiplication is typically used for multiplication by arbitrary numbers. A number of methods by which constant multipliers can be realized have also been studied.

## Chapter 3

## **Barrett Reduction Variants**

In this chapter, the Barrett algorithm for modular reduction is introduced. A brief survey of different variants of the Barrett algorithm is provided. Each respective variant is analyzed in order to compare the number of operations required to complete a single reduction.

### 3.1 Modular Reduction

Modular reduction is the operation of performing  $X \mod P$  where, in our context, both X and P are integers. Let us assume that the bitlength of P is k. When computing modular addition and subtraction involving two k-bit integers, the result can be corrected to be within the range of [0, P-1] by simply adding or subtracting the modulus, P. When computing the product of two k-bit numbers, however, the 2k-bit result is significantly larger than the k-bit modulus, P. In applications such as public-key cryptography where P is very large and prime, correction of the product by simply subtracting or adding multiples of the modulus would be extremely inefficient. As a result, the reduction step would need to be replaced by a computationally less intensive algorithm. This gives rise to the need for efficient modular reduction schemes.

As modular multiplication is a critical step in any public-key cryptosystem, there has been extensive research in improving this operation in the literature. It is for this reason that many ECC systems in practice use prime P of special form for which there exists efficient reduction techniques. When primes of arbitrary form are used, however, a general reduction technique is necessary. The two most used include the Montgomery reduction [40] and the Barrett reduction [3] algorithms. The primary source for the speedup these algorithms provide over the classical reduction scheme is due to the replacement of the costly division step by multiplication by a precomputed value. Montgomery reduction can be considered a right-to-left approach whereas Barrett's scheme reduces from left to right.

Many variants of the aforementioned algorithms have also been presented. Modular multiplication can be separated (multiply and then reduce) [50, 32] or interleaved [1, 30, 45]. There have also been works which propose special moduli sets with which the multiplication steps in Montgomery and Barrett reduction algorithms can be replaced by simple shift operations, offering further speed ups [30, 50]. The advantages of both Barrett and Montgomery's schemes can be combined to parallelize the modular multiplication operation as presented in the bipartite and tripartite modular multiplication alrogithms [28, 44]. In this thesis, focus is directed to four Barrett variants: the General Barrett scheme [3], the Improved Barrett scheme due to Dhem [16], the Folding Barrett reduction algorithm based on Karatsuba's algorithm and the Folding Barrett reduction scheme implemented in [56].

In the sections to follow, the following notations are used. For integers X and P there exists integers q and r such that X = qP + r where  $r \in [0, P - 1]$ . We denote q as the quotient and r as the remainder. The quotient, q, may also be represented as  $q = \left\lfloor \frac{X}{P} \right\rfloor$  and the remainder as  $r \equiv X \mod P$ .

#### **3.2** General Barrett Reduction

Barrett reduction [3] aims to compute  $X \mod P$  given positive integers X and P. In the notation described above, the numerator and denominator can be equivalently expanded as in Equation (3.1). Rather than calculating the quotient directly, which would involve a costly division operation, Barrett's reduction computes a quotient estimate,  $\hat{q}$ . Following the representation of the quotient in Equation (3.1), the quotient estimate can be defined

as in Equation (3.2).

$$q = \left\lfloor \frac{X}{P} \right\rfloor = \left\lfloor \frac{\frac{X}{2^k} \times \frac{2^{2k}}{P}}{2^k} \right\rfloor$$

(3.1)

$$\hat{q} = \left\lfloor \frac{\left\lfloor \frac{X}{2^k} \right\rfloor \times \left\lfloor \frac{2^{2^k}}{P} \right\rfloor}{2^k} \right\rfloor$$

(3.2)

When analyzing the equation for  $\hat{q}$ , we see that the numerator consists of the multiplication of two terms, one of which is the quotient produced by dividing  $2^{2k}$  by P. Although Barrett's reduction algorithm is motivated by the need to avoid costly division operations, the modulus P is usually a fixed parameter in most cryptosystems. As a result, this term can be precomputed and regarded as a constant. If the remainder obtained from a division operation is defined as r = X - qP, then an estimate of the remainder,  $\hat{r}$ , can be calculated using the quotient estimate as  $\hat{r} = X - \hat{q}P$ . In order for this to be a valid estimate, it must be shown that the difference between  $\hat{r}$  and r is small.

By the definition of the floor function, it is true that for any number,  $z, 0 \leq z - \lfloor z \rfloor < 1$ . Using this property, the relationship between q and  $\hat{q}$  can be derived. We first define  $\tau$  and  $\zeta$  where  $0 \leq \tau, \zeta < 1$  such that  $\tau = \frac{X}{2^k} - \lfloor \frac{X}{2^k} \rfloor$  and  $\zeta = \frac{2^{2k}}{P} - \lfloor \frac{2^{2k}}{P} \rfloor$ . This property can be used to rewrite q.

$$0 \le \hat{q} \le q = \left\lfloor \frac{\frac{X}{2^k} \times \frac{2^{2k}}{P}}{2^k} \right\rfloor$$

$$0 \le \hat{q} \le q = \left\lfloor \frac{\left( \left\lfloor \frac{X}{2^k} \right\rfloor + \tau \right) \times \left( \left\lfloor \frac{2^{2k}}{P} \right\rfloor + \zeta \right)}{2^k} \right\rfloor$$

Next, after distribution and with knowledge of the bounds on the values  $\tau$  and  $\zeta$ , q can be represented by the inequality below.

$$0 \le \hat{q} \le q < \left\lfloor \frac{\left\lfloor \frac{X}{2^k} \right\rfloor \times \left\lfloor \frac{2^{2k}}{P} \right\rfloor}{2^k} + \frac{\left\lfloor \frac{X}{2^k} \right\rfloor + \left\lfloor \frac{2^{2k}}{P} \right\rfloor + 1}{2^k} \right\rfloor$$

Noting that the first term in the above expression is exactly our representation of  $\hat{q}$ , the

above inequality becomes:

$$0 \leq \hat{q} \leq q < \left\lfloor \hat{q} + \frac{\left\lfloor \frac{X}{2^k} \right\rfloor + \left\lfloor \frac{2^{2k}}{P} \right\rfloor + 1}{2^k} \right\rfloor$$

As it is assumed that the modulus is k bits long, it must be true that  $2^{k-1} \leq P < 2^k$ ; however, in the case that  $P = 2^{k-1}$ , a simple power of 2, the reduction can be performed by a simple shift operation. Thus, we instead only consider the case where  $2^{k-1} < P < 2^k$ Similarly, the integer being reduced is assumed to be 2k bits in length and can take on the values in the range  $0 \leq X < 2^{2k}$ . We wish to find the upper bound on q. Thus, we evaluate the inequality at  $X = 2^{2k}$  and  $P = 2^{k-1}$ .

$$0 \le \hat{q} \le q < \left\lfloor \hat{q} + \frac{\left\lfloor \frac{2^{2k}}{2^k} \right\rfloor + \left\lfloor \frac{2^{2k}}{2^{k-1}} \right\rfloor + 1}{2^k} \right\rfloor$$

$$0 \le \hat{q} \le q < \left\lfloor \hat{q} + \frac{2^k + 2^{k+1} + 1}{2^k} \right\rfloor$$

$$0 \le \hat{q} \le q < \hat{q} + 3$$

Since it is required that the quotient be an integer, then the quotient estimate can be represented by the bounds below.

$$0 \le \hat{q} \le q \le \hat{q} + 2 \tag{3.3}$$

The estimated quotient,  $\hat{q}$ , will be at most equal to q and at least equal to q-2. Substituting this into our estimate for the remainder, we see that  $\hat{r} = X - \hat{q}P \leq X - (q-2)P = x - qP + 2P = r + 2P$ . Then, extending from the fact that  $r \in [0, P-1]$ ,  $\hat{r} < 3P < 2^{k+2}$ . Clearly, at most two additional subtractions by the modulus P would need to be performed in addition to the aforementioned steps to arrive at the correct remainder. The reduction procedure is described below in Algorithm 1.

Algorithm 1 General Barrett Reduction [3]

Input Integers P, X and  $\mu$  where  $2^{k-1} < P < 2^k, 0 \le X < 2^{2k}, \mu = \left\lfloor \frac{2^{2k}}{P} \right\rfloor$ Output  $r \equiv X \mod P$ 1:  $q_1 \leftarrow \left\lfloor \frac{X}{2^k} \right\rfloor$ 2:  $q_2 \leftarrow q_1 \times \mu$ 3:  $q_3 \leftarrow \left\lfloor \frac{q_2}{2^k} \right\rfloor$ 4:  $r_1 \leftarrow X \mod (2^{k+2}) - (q_3 \times P) \mod (2^{k+2})$ 5:  $r_2 \leftarrow r_1 - P$ 6:  $r_3 \leftarrow r_1 - 2P$ 7: return  $\{r \in \{r_1, r_2, r_3\} | 0 \le r < P\}$

### 3.3 Improved Barrett Reduction

The procedure followed in Algorithm 1 computes a quotient estimate which satisfies  $q-2 \leq \hat{q} \leq q$ . By consequence, up to two additional subtractions are needed for correction of the result. Dhem improved upon the classical Barrett reduction algorithm by reducing the error between the quotient, q, and the quotient estimate,  $\hat{q}$ , to 1; by consequence, one of the extra subtraction steps can be eliminated [16]. In this approach, the quotient, q, is written in terms of two parameters  $\alpha$  and  $\beta$  to formulate a more general approach to the problem, as seen in Equation (3.4). Following the same procedure as before, the corresponding quotient estimate,  $\hat{q}$  can be described as in Equation (3.5).

$$q = \left\lfloor \frac{X}{P} \right\rfloor = \left\lfloor \frac{\frac{X}{2^{k+\beta}} \times \frac{2^{k+\alpha}}{P}}{2^{\alpha-\beta}} \right\rfloor$$

(3.4)

$$\hat{q} = \left\lfloor \frac{\left\lfloor \frac{X}{2^{k+\beta}} \right\rfloor \times \left\lfloor \frac{2^{k+\alpha}}{P} \right\rfloor}{2^{\alpha-\beta}} \right\rfloor$$

(3.5)

In this form, the precomputed term is  $\mu = \left\lfloor \frac{2^{k+\alpha}}{P} \right\rfloor$ . We now show the proper choice of  $\alpha$  and  $\beta$ . If for any natural  $z, z \ge \lfloor z \rfloor > z - 1$ , all of the floor functions may be rewritten as

below. With this, the multiplicative terms can then be expanded.

$$\begin{split} \hat{q} &= \left\lfloor \frac{\left\lfloor \frac{X}{2^{k+\beta}} \right\rfloor \times \left\lfloor \frac{2^{k+\alpha}}{P} \right\rfloor}{2^{\alpha-\beta}} \right\rfloor > \frac{\left\lfloor \frac{X}{2^{k+\beta}} \right\rfloor \times \left\lfloor \frac{2^{k+\alpha}}{P} \right\rfloor}{2^{\alpha-\beta}} - 1 \\ \hat{q} &> \frac{\left(\frac{X}{2^{k+\beta}} - 1\right) \times \left(\frac{2^{k+\alpha}}{P} - 1\right) - 2^{\alpha-\beta}}{2^{\alpha-\beta}} \\ \hat{q} &> \frac{\left(\frac{X}{P}\right) \times 2^{\alpha-\beta} - \frac{2^{k+\alpha}}{P} - \frac{X}{2^{k+\beta}} + 1 - 2^{\alpha-\beta}}{2^{\alpha-\beta}} \end{split}$$

Following the property that  $z \ge \lfloor z \rfloor$ , the inequality still holds when we replace the term  $\left(\frac{X}{P}\right)$  by  $\lfloor \frac{X}{P} \rfloor$ . Noticing that  $\lfloor \frac{X}{P} \rfloor = q$ , the expression can be further simplified.

$$\hat{q} > \frac{\left\lfloor \frac{X}{P} \right\rfloor \times 2^{\alpha-\beta} - \frac{2^{k+\alpha}}{P} - \frac{X}{2^{k+\beta}} + 1 - 2^{\alpha-\beta}}{2^{\alpha-\beta}}$$

It is assumed that the modulus  $2^{k-1} < P < 2^k$  and that the integer being reduced is in the range  $0 \le X < 2^{2k}$ . Evaluating the inequality at these bounds arrives at the expression below:

$$\hat{q} > \frac{q \times 2^{\alpha - \beta} - 2^{\alpha + 1} - 2^{k - \beta} + 1 - 2^{\alpha - \beta}}{2^{\alpha - \beta}}$$

$$\hat{q} > q - 2^{\beta + 1} - 2^{k - \alpha} + 2^{\beta - \alpha} - 1$$

Next, values for  $\beta$  and  $\alpha$  are chosen such that the difference between q and  $\hat{q}$  can be minimized. Suppose  $\alpha \geq k+1$  and  $\beta \leq -2$ . As the term  $2^{\beta-\alpha}$  becomes fractional after substitution, it is replaced by  $\sigma$ .

$$\begin{split} \hat{q} &> q - 2^{(-2)+1} - 2^{k-(k+1)} + \sigma - 1 \\ \hat{q} &> q - \frac{1}{2} - \frac{1}{2} + \sigma - 1 \\ \hat{q} &> q - 2 + \sigma \end{split}$$

Since it is required that  $\hat{q}$  be an integer by definition, then the difference between q and  $\hat{q}$  limited to 1.

$$\hat{q} > q - 2 + \sigma \ge q - 1$$

$$0 \le \hat{q} \le q \le \hat{q} + 1 \tag{3.6}$$

By the above derivation,  $\hat{q}$  will be at most equal to q and at least equal to q-1 provided that  $\alpha \geq k+1$  and  $\beta \leq -2$ . Substituting this into our estimate for the remainder, we see that  $\hat{r} = X - \hat{q}P \leq X - (q-1)P = X - qP + P = r + P$ . Then, extending from the fact that  $r \in [0, P-1]$ ,  $\hat{r} < 2P < 2^{k+1}$ . Clearly, at most one additional subtraction by the modulus P would need to be performed to arrive at the correct remainder. We choose to work with the  $\alpha$  and  $\beta$  values as determined in [32] to be consistent with the parameters as required by the Improved Folding Barrett variant to be described later. In Kong's method,  $\alpha = k + 3$  whereas  $\beta = -2$  so that the  $\mu$  constant can be calculated as  $\mu = \left\lfloor \frac{2^{2k+3}}{P} \right\rfloor$ . The final procedure is given in Algorithm 2.

Algorithm 2 Improved Barrett Reduction [16] [32]

Input Integers P, X and  $\mu$  where  $2^{k-1} \leq P < 2^k, 0 \leq X < 2^{2k}, \mu = \left\lfloor \frac{2^{2k+3}}{P} \right\rfloor$ Output  $r \equiv X \mod P$ 1:  $q_1 \leftarrow \left\lfloor \frac{X}{2^{k-2}} \right\rfloor$ 2:  $q_2 \leftarrow q_1 \times \mu$ 3:  $q_3 \leftarrow \left\lfloor \frac{q_2}{2^{k+5}} \right\rfloor$ 4:  $r_1 \leftarrow X \mod (2^{k+1}) - (q_3 \times P) \mod (2^{k+1})$ 5:  $r_2 \leftarrow r_1 - P$ 6: return  $\{r \in \{r_1, r_2\} | 0 \leq r < P\}$

#### **3.4** Folding Barrett Reduction

The authors in [26] modified the classical Barrett scheme with the aim of reducing the size of the multiplications involved. Rather than just precomputing a single value which is dependent on the modulus, P, the Folding Barrett scheme relies on multiplication by two values, both of which are dependent on the modulus P and thus, can be computed beforehand. Again, it is assumed that the modulus is a k-bit value. Representing  $s = \frac{k}{2}$ , these constants can be denoted  $\mu = \left\lfloor \frac{2^{3s}}{P} \right\rfloor$  and  $P' = 2^{3s} \mod P$ . Using these constants, the integer to be reduced, X, can be partially reduced to a 3s + 1 bit integer, represented

by  $X' = X \mod 2^{3s} + \lfloor \frac{X}{2^{3s}} \rfloor \times P'$ . It can be shown that  $X' \equiv X \mod P$  and so reduction proceeds to compute the value  $X' \mod P$  as opposed to  $X \mod P$  which is a smaller number than the original 4s-bit number that needed to be reduced [26]. As a result, the actual size of the multiplications involved in the reduction is smaller. Assuming Karatsuba multiplication is used for all multiplications involved, the two k-bit multiplications in the classical Barrett method would be equivalent to six s-bit multiplications, whereas the Folding Barrett reduction scheme only requires five, amounting to a 20% savings [26]. The new quotient, q', may be represented as  $q' = \lfloor \frac{X'}{P} \rfloor$ . In this form, the numerator and denominator can be equivalently expanded as in Equation (3.7) and the quotient estimate can be defined as in Equation (3.8).

$$q' = \left\lfloor \frac{X'}{P} \right\rfloor = \left\lfloor \frac{\frac{X'}{2^{2s}} \times \frac{2^{3s}}{P}}{2^s} \right\rfloor$$

(3.7)

$$\hat{q}' = \left\lfloor \frac{\left\lfloor \frac{X'}{2^{2s}} \right\rfloor \times \left\lfloor \frac{2^{3s}}{P} \right\rfloor}{2^s} \right\rfloor$$

(3.8)

We now study the number of final corrections required by this new quotient estimate. If the remainder obtained from a division operation is defined as r' = X' - q'P, then an estimate of the remainder,  $\hat{r}'$ , can be calculated using the quotient estimate as  $\hat{r}' = X' - \hat{q}'P$ . Using the property of the floor function, the relationship between q' and  $\hat{q}'$  can be derived. We first define  $\tau$  and  $\zeta$  where  $0 \leq \tau, \zeta < 1$  such that  $\tau = \frac{X'}{2^{2s}} - \lfloor \frac{X'}{2^{2s}} \rfloor$  and  $\zeta = \frac{2^{3s}}{P} - \lfloor \frac{2^{3s}}{P} \rfloor$ . This property can be used to rewrite q'.

$$0 \le \hat{q}' \le q' = \left\lfloor \frac{\frac{X'}{2^{2s}} \times \frac{2^{3s}}{P}}{2^s} \right\rfloor$$

$$0 \le \hat{q}' \le q' = \left\lfloor \frac{\left( \left\lfloor \frac{X'}{2^{2s}} \right\rfloor + \tau \right) \times \left( \left\lfloor \frac{2^{3s}}{P} \right\rfloor + \zeta \right)}{2^s} \right\rfloor$$

Next, after distribution and with knowledge of the bounds on the values  $\tau$  and  $\zeta$ , q' can be represented by the inequality below.

$$0 \le \hat{q}' \le q' < \left\lfloor \frac{\left\lfloor \frac{X'}{2^{2s}} \right\rfloor \times \left\lfloor \frac{2^{3s}}{P} \right\rfloor}{2^s} + \frac{\left\lfloor \frac{X'}{2^{2s}} \right\rfloor + \left\lfloor \frac{2^{3s}}{P} \right\rfloor + 1}{2^s} \right\rfloor$$

Noting that the first term in the above expression is exactly our representation of  $\hat{q}'$ , the above inequality becomes:

$$0 \le \hat{q}' \le q' < \left\lfloor \hat{q}' + \frac{\left\lfloor \frac{X'}{2^{2s}} \right\rfloor + \left\lfloor \frac{2^{3s}}{P} \right\rfloor + 1}{2^s} \right\rfloor$$

As P is k bits in length (where k = 2s), it must be true that  $2^{2s-1} \leq P < 2^{2s}$ . We assume that  $2^{2s-1} < P < 2^{2s}$  since if  $P = 2^{2s-1}$ , reduction would be trivial. Similarly, X' is a 3s + 1 bit integer and can take on the values in the range  $0 \leq X < 2^{3s+1}$ . To find the upper bound on q', we evaluate the inequality at  $X' = 2^{3s+1}$  and  $P = 2^{2s-1}$ .

$$0 \leq \hat{q}' \leq q' < \left[ \hat{q}' + \frac{\left\lfloor \frac{2^{3s+1}}{2^{2s}} \right\rfloor + \left\lfloor \frac{2^{3s}}{2^{2s-1}} \right\rfloor + 1}{2^s} \right]$$

$$0 \leq \hat{q}' \leq q' < \left\lfloor \hat{q}' + \frac{(2^{s+1}) + 2^{s+1} + 1}{2^s} \right\rfloor$$

$$0 \leq \hat{q}' \leq q' < \hat{q}' + 4$$

$$0 < \hat{q}' < q' < \hat{q}' + 3$$

(3.9)

Thus, the estimated quotient,  $\hat{q}'$ , will be at most equal to q' and at least equal to q' - 3. Substituting this into our estimate for the remainder, we see that  $\hat{r}' = X' - \hat{q}'P \leq X' - (q'-3)P = X' - q'P + 3P = r' + 3P$ . Then, extending from the fact that  $r' \in [0, P - 1]$ ,  $\hat{r}' < 4P < 2^{2s+2}$ . Therefore, at most three additional subtractions by the modulus P would need to be performed. The description of this procedure can be seen in Algorithm 3.

Algorithm 3 Folding Barrett Reduction [26]

Input Integers  $X, P, \mu$ , and P' where  $2^{k-1} \leq P < 2^k, 0 \leq X < 2^{2k}, \mu = \left\lfloor \frac{2^{3s}}{P} \right\rfloor$  and  $P' = 2^{3s}$ mod P. Assume k = 2sOutput  $r \equiv X \mod P$ 1:  $q_1 \leftarrow \left\lfloor \frac{X}{2^{2s}} \right\rfloor$ 2:  $q_2 \leftarrow q_1 \times P'$ 3:  $X' \leftarrow X \mod (2^{3s}) + q_2$ 4:  $q_3 \leftarrow \left\lfloor \frac{X'}{2^{2s}} \right\rfloor$ 5:  $q_4 \leftarrow q_3 \times \mu$ 6:  $q_5 \leftarrow \left\lfloor \frac{q_4}{2^s} \right\rfloor$ 7:  $r_1 \leftarrow X' \mod (2^{2s+2}) - (q_5 \times P) \mod (2^{2s+2})$ 8:  $r_2 \leftarrow r_1 - P$ 9:  $r_3 \leftarrow r_1 - 2P$ 10:  $r_4 \leftarrow r_1 - 3P$ 11: return  $\{r \in \{r_1, r_2, r_3, r_4\} | 0 \leq r < P\}$

## 3.5 Modular Multiplier with Folding Barrett Reduction

All of the previous methods explored have only considered the operation of modular reduction; should a modular multiplation be required, the product would first need to be computed separately. As demonstrated in the previous section, the Folding Barrett reduction algorithm proposed in [26] decreases the size of the multiplications required to compute a reduction step at the cost of three extra subtractions performed at the end. This is the largest number of subtractions required by all Barrett reduction variants studied thus far. Noting how Dhem was able to reduce the number of correction steps required by proposing a more general form of the algorithm in [16], Wu et al. combine the benefits of both the Folding Barrett and Improved Barrett scheme to produce a modular multiplier which uses the folding technique while requiring only one additional subtraction step [56]. By using both methods and integrating Karatsuba's algorithm into the computation of the product, the authors are able to realize a low-area design and decrease the critical delay of the reduction step [56]. It is assumed that the modulus is a k-bit value and that k is even. Representing  $s = \frac{k}{2}$ , the precomputed constants can be denoted  $\mu = \left\lfloor \frac{2^{3s+3}}{P} \right\rfloor$  and  $P' = 2^{3s} \mod P$ . Using these constants, the integer to be reduced, X, can be partially reduced to a 3s + 2 bit integer, X". The new quotient, q", may be represented as  $q'' = \left\lfloor \frac{X''}{P} \right\rfloor$ . In this form, the numerator and denominator can be equivalently expanded as in Equation (3.10) and the quotient estimate can be defined as in Equation (3.11).

$$q'' = \left\lfloor \frac{X''}{P} \right\rfloor = \left\lfloor \frac{\frac{X''}{2^{2s-2}} \times \frac{2^{3s+3}}{P}}{2^{s+5}} \right\rfloor$$

(3.10)

$$\hat{q}'' = \left\lfloor \frac{\left\lfloor \frac{X''}{2^{2s-2}} \right\rfloor \times \left\lfloor \frac{2^{3s+3}}{P} \right\rfloor}{2^{s+5}} \right\rfloor$$

(3.11)

Suppose we wish to compute the modular multiplication of two 2s-bit integers A and B under the 2s-bit modulus P. By Karatsuba's method, the product  $X = A \times B$  can be expressed as:

$$X = (A \times B) = (2^{s}A_{H} + A_{L})(2^{s}B_{H} + B_{L})$$

$$X = 2^{2s}A_{H}B_{H} + 2^{s}((A_{H} + A_{L})(B_{H} + B_{L}) - A_{H}B_{H} - A_{L}B_{L}) + A_{L}B_{L}$$

Splitting the first product term  $A_H B_H$  into its upper and lower *s* bits can be written as  $U(A_H B_H) = 2^s \lfloor \frac{A_H B_H}{2^s} \rfloor$  and  $L(A_H B_H) = A_H B_H \mod (2^s)$ . The X' term from the Folding Barrett reduction scheme is now replaced by X", a 3s+2 bit integer which can be computed as seen below.

$$X = 2^{3s}U(A_HB_H) + 2^{2s}L(A_HB_H) + 2^s((A_H + A_L)(B_H + B_L) - A_HB_H - A_LB_L) + A_LB_L$$

$$X'' = (P'U(A_HB_H) + 2^{2s}L(A_HB_H) + \dots$$

$$\dots 2^s((A_H + A_L)(B_H + B_L) - A_HB_H - A_LB_L) + A_LB_L) \mod P$$

$$X'' \equiv X \mod P$$

It now remains to show how the above definitions yield an implementation requiring only one final reduction step.

$$0 \le \hat{q}'' \le q'' = \left\lfloor \frac{\frac{X''}{2^{2s-2}} \times \frac{2^{3s+3}}{P}}{2^{s+5}} \right\rfloor$$

Again,  $\tau$  and  $\zeta$  are defined, where  $0 \leq \tau, \zeta < 1$  such that  $\tau = \frac{X''}{2^{2s-2}} - \lfloor \frac{X''}{2^{2s-2}} \rfloor$  and  $\zeta = \frac{2^{3s+3}}{P} - \lfloor \frac{2^{3s+3}}{P} \rfloor$ . This property can be used to rewrite q'.

$$0 \le \hat{q}'' \le q'' = \left\lfloor \frac{\left( \left\lfloor \frac{X''}{2^{2s-2}} \right\rfloor + \tau \right) \times \left( \left\lfloor \frac{2^{3s+3}}{P} \right\rfloor + \zeta \right)}{2^{s+5}} \right\rfloor$$

Distributing the terms of the multiplication in the numerator and applying the bounds on the values  $\tau$  and  $\zeta$ , q'' can be represented by the inequality below.

$$0 \le \hat{q}' \le q' < \left\lfloor \frac{\left\lfloor \frac{X''}{2^{2s-2}} \right\rfloor \times \left\lfloor \frac{2^{3s+3}}{P} \right\rfloor}{2^{s+5}} + \frac{\left\lfloor \frac{X''}{2^{2s-2}} \right\rfloor + \left\lfloor \frac{2^{3s+3}}{P} \right\rfloor + 1}{2^{s+5}} \right\rfloor$$

As P is k bits in length (where k = 2s), it must be true that  $2^{2s-1} < P < 2^{2s}$ . As derived in [56], X" is a 3s + 2 bit integer, ranging in value from  $0 \le X < 2^{3s+2}$ . To find the upper bound on q'', we evaluate the inequality at  $X'' = 2^{3s+2}$  and  $P = 2^{2s-1}$ .

$$0 \leq \hat{q}'' \leq q'' < \left[ \hat{q}'' + \frac{\left\lfloor \frac{X''}{2^{2s-2}} \right\rfloor + \left\lfloor \frac{2^{3s+3}}{2^{2s-1}} \right\rfloor + 1}{2^{s+5}} \right]$$

$$0 \leq \hat{q}'' \leq q'' < \left\lfloor \hat{q}'' + \frac{(2^{s+4}) + 2^{s+4} + 1}{2^{s+5}} \right\rfloor$$

$$0 \leq \hat{q}'' \leq q'' < \hat{q}'' + 2$$

$$0 \leq \hat{q}'' \leq q'' \leq \hat{q}'' + 1$$

(3.12)

by the above evaluation, the estimated quotient,  $\hat{q}''$ , will be at most equal to q'' and at least equal to q'' - 1. Substituting this into our estimate for the remainder, we see that  $\hat{r}'' = X'' - \hat{q}''P \leq X'' - (q'' - 1)P = X'' - q''P + P = r'' + P$ . Knowing that the remainder must adhere to  $r'' \in [0, P - 1]$ ,  $\hat{r}'' < 2P < 2^{2s+1}$ . Therefore, at most one additional subtraction by the modulus P would need to be performed. The final algorithm can be seen in Algorithm 4.

Algorithm 4 Modular Multiplier by Folding Barrett Reduction [56]

Input Integers  $\overline{A, B, P, \mu}$ , and P' where  $2^{k-1} \leq A, B, P < 2^k, \mu = \left\lfloor \frac{2^{3s+3}}{p} \right\rfloor$  and  $P' = 2^{3s}$ mod P. Assume k = 2sOutput  $r \equiv X \mod P$  where  $X = A \times B$ 1:  $q_1 \leftarrow \left\lfloor \frac{A_H B_H}{2^s} \right\rfloor$ 2:  $q_2 \leftarrow q_1 \times P'$ 3:  $q_3 \leftarrow 2^{2s}(A_H B_H \mod (2^s)) + 2^s((A_H + A_L)(B_H + B_L) - A_H B_H - A_L B_L) + A_L B_L$ 4:  $X'' \leftarrow q_2 + q_3$ 5:  $q_4 \leftarrow \left\lfloor \frac{X''}{2^{2s+2}} \right\rfloor$ 6:  $q_5 \leftarrow q_4 \times \mu$ 7:  $q_6 \leftarrow \left\lfloor \frac{q_5}{2^{s+5}} \right\rfloor$ 8:  $r_1 \leftarrow X'' \mod (2^{2s+1}) - (q_6 \times P) \mod (2^{2s+1})$ 9:  $r_2 \leftarrow r_1 - P$ 10: return  $\{r \in \{r_1, r_2\} | 0 \leq r < P\}$

As the previous Barrett variants studied only consider reduction and not modular multiplication, we will largely only refer to the reduction aspects of Algorithm 4. Since the aspects of reduction of the above algorithm can be viewed as a union of the ideas presented by the Improved Barrett reduction scheme [16] and the Folding Barrett implementation [26], we will refer to this as the Improved Folding Barrett reduction variant hereafter. The reduction aspects of this scheme assume that  $q_1$  and  $q_3$  are provided and need not be computed.

## 3.6 Comparison of Reduction Techniques

Each of the algorithms differ in terms of the precomputed constants that are used, the number of subtractions necessary for the final reduction, as well as the size of the multiplications involved. Here, we summarize the differences in the variants of the Barrett schemes previously discussed. A comparison of the precomputed constants is provided in Table 3.1.

Table 3.1: Precomputations pertinent to each variation of the Barrett reduction scheme where k is the length of the modulus.

| Scheme                   | Precomputed Constants                                                                          | Size                      |

|--------------------------|------------------------------------------------------------------------------------------------|---------------------------|

| General Barrett          | $\mu = \left\lfloor \frac{2^{2k}}{P} \right\rfloor$                                            | k+1                       |

| Improved Barrett         | $\mu = \left\lfloor \frac{2^{2k+3}}{P} \right\rfloor$                                          | k+4                       |

| Folding Barrett          | $\mu = \left\lfloor \frac{2^{\frac{3k}{2}}}{P} \right\rfloor$ $P' = 2^{\frac{3k}{2}} \mod P$   | $\frac{\frac{k}{2}+1}{k}$ |

| Improved Folding Barrett | $\mu = \left\lfloor \frac{2^{\frac{3k}{2}+3}}{P} \right\rfloor$ $P' = 2^{\frac{3k}{2}} \mod P$ | $\frac{\frac{k}{2}+4}{k}$ |

Table 3.2: Operations required for each reduction scheme where k is the length of the modulus.

| Reduction Scheme         | Multiplications                                                                                                                                    | Additions                              |