**Universidade do Minho** Escola de Engenharia

Ângelo André Oliveira Ribeiro

**Deploying RIOT Operating System on a Reconfigurable Internet of Things End-device**

**Universidade do Minho** Escola de Engenharia

### Ângelo André Oliveira Ribeiro

### **Deploying RIOT Operating System on a Reconfigurable Internet of Things End-device**

Dissertação de Mestrado Mestrado Integrado em Engenharia Eletrónica Industrial e Computadores

Trabalho efetuado sob a orientação do **Professor Doutor Tiago Gomes**

### Acknowledgments

First of all, I express my gratitude to the best advisor Dr. Tiago Gomes, for his friendship, patience, priceless motivation and for the huge transmission of knowledge in such an adventure through IoT. I also wish to express my gratitude to the most challenging, motivational and inspiring professors Dr. Adriano Tavares and Dr. Jorge Cabral that were fundamental in my development of knowledge in the embedded systems field.

To all the companions in this journey Hugo Araujo, Ailton Lopes, Sérgio Pereira, Nuno Silva, José Silva, Pedro Machado, Pedro Ribeiro, Francisco Petrucci and Ricardo Roriz I express my deepest gratitude for all the friendship, craziness and company on those long days and nights of work. I present also my gratitude to Cristiano Rodrigues and Ivo Marques for the collaboration and help in the development of the XIoT.

A special thank you to Guilherme Raimundo, Barbara Rodrigues, João Torre and Tiago Ribeiro.

To my family, specially to my mother, for all the support during these course, for never let me give-up, for making the impossible possible, and for sure, if I wright this words is thanks to you. Last but not least to my grandmother for such an example of perseverance and love.

To my grandfather Chico, and to you Astronauta.

"The present is theirs; the future, for which I really worked, is mine."

—Nikola Tesla

### Abstract

The Internet of Everything (IoE) is enabling the connection of an infinity of physical objects to the Internet, and has the potential to connect every single existing object in the world. This empowers a market with endless opportunities where the big players are forecasting, by 2020, more than 50 billion connected devices, representing an 8 trillion USD market.

The IoE is a broad concept that comprises several technological areas and will certainly, include more in the future. Some of those already existing fields are the Internet of Energy related with the connectivity of electrical power grids, Internet of Medical Things (IoMT), for instance, enables patient monitoring, Internet of Industrial Things (IoIT), which is dedicated to industrial plants, and the Internet of Things (IoT) that focus on the connection of everyday objects (e.g. home appliances, wearables, transports, buildings, etc.) to the Internet.

The diversity of scenarios where IoT can be deployed, and consequently the different constraints associated to each device, leads to a heterogeneous network composed by several communication technologies and protocols co-existing on the same physical space. Therefore, the key requirements of an IoT network are the connectivity and the interoperability between devices. Such requirement is achieved by the adoption of standard protocols and a well-defined lightweight network stack. Due to the adoption of a standard network stack, the data processed and transmitted between devices tends to increase. Because most of the devices connected are resource constrained, i.e., low memory, low processing capabilities, available energy, the communication can severally decrease the device's performance.

Hereupon, to tackle such issues without sacrificing other important requirements, this dissertation aims to deploy an operating system (OS) for IoT, the RIOT-OS, while providing a study on how network-related tasks can benefit from hardware accelerators (deployed on reconfigurable technology), specially designed to process and filter packets received by an IoT device.

### Resumo

O conceito Internet of Everything (IoE) permite a conexão de uma infinidade de objetos à Internet e tem o potencial de conectar todos os objetos existentes no mundo. Favorecendo assim o aparecimento de novos mercados e infinitas possibilidades, em que os grandes intervenientes destes mercados preveem até 2020 a conexão de mais de 50 mil milhões de dispositivos, representando um mercado de 8 mil milhões de dólares.

IoE é um amplo conceito que inclui várias áreas tecnológicas e irá certamente incluir mais no futuro. Algumas das áreas já existentes são: a Internet of Energy relacionada com a conexão de redes de transporte e distribuição de energia à Internet; Internet of Medical Things (IoMT), que possibilita a monotorização de pacientes; Internet of Industrial Things (IoIT), dedicada a instalações industriais e a Internet of Things (IoT), que foca na conexão de objetos do dia-a-dia (e.g. eletrodomésticos, wearables, transportes, edifícios, etc.) à Internet.

A diversidade de cenários à qual IoT pode ser aplicado, e consequentemente, as diferentes restrições aplicadas a cada dispositivo, levam à criação de uma rede heterogénea composto por diversas tecnologias de comunicação e protocolos a coexistir no mesmo espaço físico. Desta forma, os requisitos chave aplicados às redes IoT são a conectividade e interoperabilidade entre dispositivos. Estes requisitos são atingidos com a adoção de protocolos standard e pilhas de comunicação bem definidas. Com a adoção de pilhas de comunicação standard, a informação processada e transmitida entre dispostos tende a aumentar. Visto que a maioria dos dispositivos conectados possuem escaços recursos, i.e., memória reduzida, baixa capacidade de processamento, pouca energia disponível, o aumento da capacidade de comunicação pode degradar o desempenho destes dispositivos.

Posto isto, para lidar com estes problemas e sem sacrificar outros requisitos importantes, esta dissertação pretende fazer o porting de um sistema operativo IoT, o RIOT, para uma solução reconfigurável, o CUTE mote. O principal objetivo consiste na realização de um estudo sobre os benefícios que as tarefas relacionadas com as camadas de rede podem ter ao serem executadas em hardware via aceleradores dedicados. Estes aceleradores são especialmente projetados para processar e filtrar pacotes de dados provenientes de uma interface radio em redes IoT periféricas.

## Contents

| A            | cknov | wledgments                                | iii  |

|--------------|-------|-------------------------------------------|------|

| $\mathbf{A}$ | bstra | act                                       | vii  |

| $\mathbf{R}$ | esum  | 10                                        | ix   |

| A            | crony | yms                                       | xxiv |

| 1            | Intr  | roduction                                 | 1    |

|              | 1.1   | The Internet of Things                    | . 2  |

|              | 1.2   | Low-end Devices at the Network Edge       | . 3  |

|              | 1.3   | IoT Market                                | . 4  |

|              | 1.4   | IoT Architecture                          | . 7  |

|              | 1.5   | Connectivity and Security                 | . 8  |

|              | 1.6   | IoT Network Stack                         | . 10 |

|              | 1.7   | Operating Systems for Low-end IoT Devices | . 12 |

|              |       | 1.7.1 Requirements for an IoT OS          | . 13 |

|              | 1.8   | Dissertation Structure                    | . 14 |

|              | 1.9   | Conclusion                                | . 15 |

| 2            | Stat  | te of Art                                 | 17   |

|              | 2.1   | Operating Systems for IoT                 | . 18 |

|              |       | 2.1.1 Contiki-OS                          | . 20 |

|              |       | 2.1.2 TinyOS                              | . 22 |

|              |       | 2.1.3 RIOT-OS                             | . 23 |

|              |       | 2.1.4 FreeRTOS                            | . 26 |

|              | 2.2   | Hardware Platforms                        | . 26 |

|              |       | 2.2.1 Texas Instruments                   | . 27 |

|              |       | 2.2.2 Microsemi SmartFusion2              | . 28 |

|              | 2.3   | Evaluation Tools                          | . 30 |

|              |       | 2.3.1 IAR Workbench                       | . 30 |

|              |       | 2.3.2 Libero SoC Design Suite             | . 30 |

|              |       | 2.3.3 Thread-Metric Benchmark Suite       | . 32 |

|                           | 2.4                      | Heterogeneous Architectures                            |  |  |  |  |

|---------------------------|--------------------------|--------------------------------------------------------|--|--|--|--|

|                           | 2.5                      | Conclusion                                             |  |  |  |  |

| 3                         | RIC                      | T-OS Deployment on a Reconfigurable IoT Mote 39        |  |  |  |  |

|                           | 3.1                      | Heterogeneous Architectures for IoT Low-End Devices 40 |  |  |  |  |

|                           | 3.2                      | RIOT-OS on a COTS Solution                             |  |  |  |  |

|                           | 3.3                      | RIOT-OS on a Heterogeneous Mote                        |  |  |  |  |

|                           | 3.4                      | Evaluation                                             |  |  |  |  |

|                           |                          | 3.4.1 Thread-Metric Benchmark Suite on RIOT-OS 51      |  |  |  |  |

|                           |                          | 3.4.2 Thread-Metric Evaluation                         |  |  |  |  |

|                           | 3.5                      | Conclusion                                             |  |  |  |  |

| 4                         | Accelerators Integration |                                                        |  |  |  |  |

|                           | 4.1                      | Acceleration on Low-End IoT Devices                    |  |  |  |  |

|                           | 4.2                      | XIoT Hardware Accelerator                              |  |  |  |  |

|                           | 4.3                      | XIoT deployment in CUTE mote                           |  |  |  |  |

|                           |                          | 4.3.1 XIoT API                                         |  |  |  |  |

|                           |                          | 4.3.2 XIoT Integration in RIOT-OS                      |  |  |  |  |

|                           | 4.4                      | Evaluation                                             |  |  |  |  |

|                           |                          | 4.4.1 Thread-Metrics Evaluation                        |  |  |  |  |

|                           |                          | 4.4.2 RCU Resources Utilization                        |  |  |  |  |

|                           | 4.5                      | Conclusion                                             |  |  |  |  |

| 5                         | Cor                      | clusion and Future Work 77                             |  |  |  |  |

|                           | 5.1                      | Conclusion                                             |  |  |  |  |

|                           | 5.2                      | Future Work                                            |  |  |  |  |

| $\mathbf{B}^{\mathbf{i}}$ | ibliog                   | raphy 81                                               |  |  |  |  |

# List of Figures

| 1.1  | IoT Value at Stake                                                | Ę  |

|------|-------------------------------------------------------------------|----|

| 1.2  | IoT Market forecast: Connected devices 2014-2020                  | 6  |

| 1.3  | The general architecture of the IoT                               | 7  |

| 1.4  | The IoT from an embedded systems point of view                    | 8  |

| 1.5  | 5-layer IoT-ARM Communication Model                               | 11 |

| 2.1  | Contiki-OS architecture stack and supported IoT stack             | 21 |

| 2.2  | TinyOS architecture stack and supported IoT stack                 | 23 |

| 2.3  | RIOT-OS architecture stack and supported IoT stack                | 24 |

| 2.4  | SmartFusion2 Security Evaluation Kit                              | 29 |

| 2.5  | The evolution of FPSoC                                            | 34 |

| 3.1  | CUTE mote architecure                                             | 41 |

| 3.2  | CUTE mote hardware prototype                                      | 42 |

| 3.3  | RIOT-OS structure                                                 | 44 |

| 3.4  | Architecture of the heterogeneous solution                        | 49 |

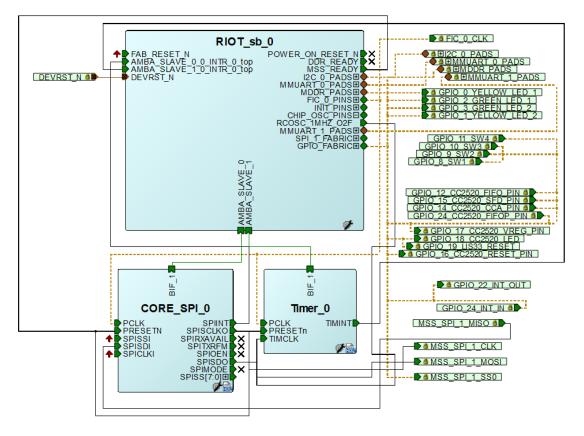

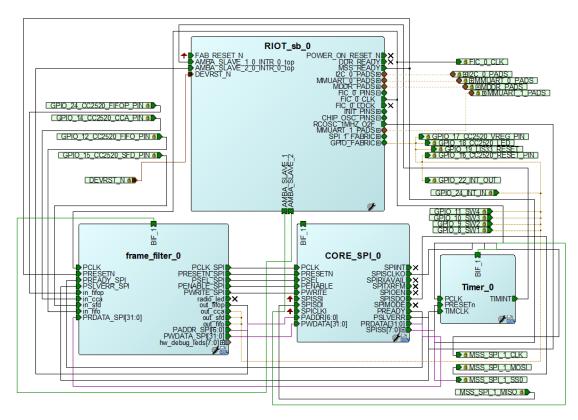

| 3.5  | Heterogeneous architecture layout                                 | 50 |

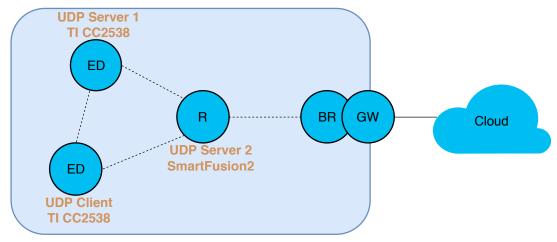

| 3.6  | Evaluation network topology                                       | 54 |

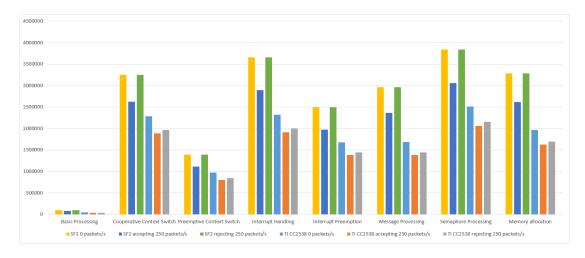

| 3.7  | TI CC2538 Thread-Metric results                                   | 55 |

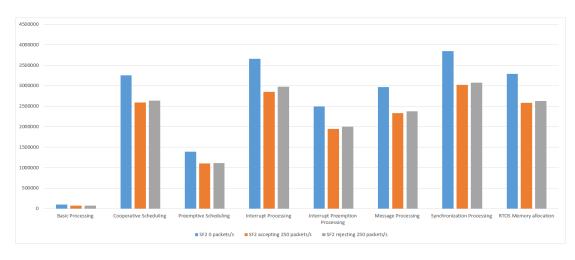

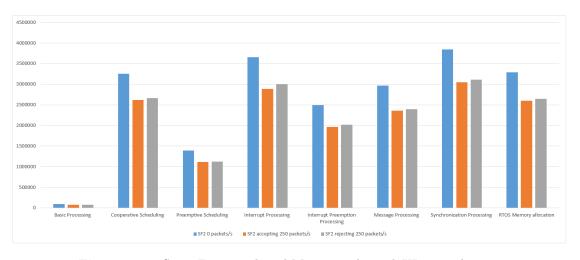

| 3.8  | SmartFusion2 Thread-Metric results                                | 55 |

| 3.9  | SmartFusion2 and TI CC2538 Thread-Metric results                  | 56 |

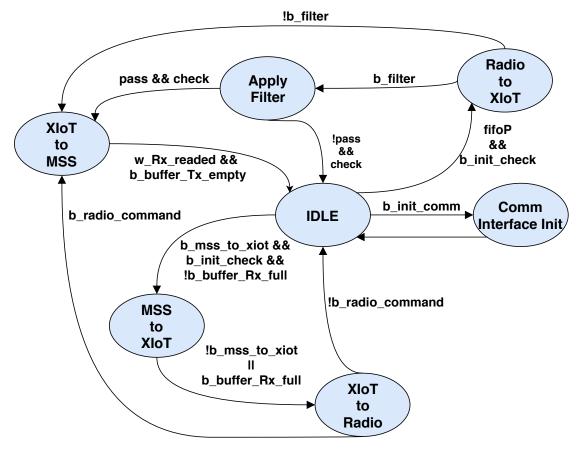

| 4.1  | XIoT main FSM                                                     | 62 |

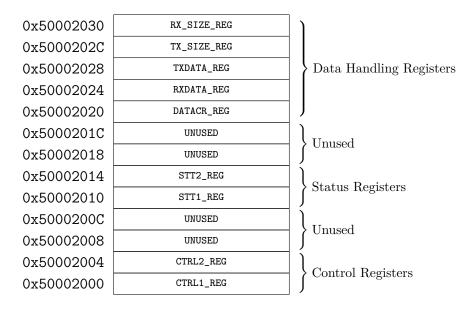

| 4.2  | XIoT peripheral memory address space                              | 64 |

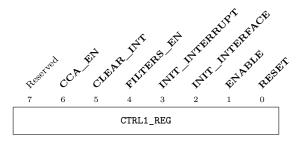

| 4.3  | CTRL1_REG register field                                          | 64 |

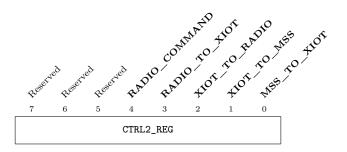

| 4.4  | CTRL2_REG register field                                          | 65 |

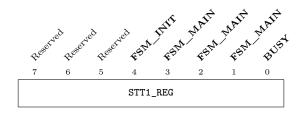

| 4.5  | STT1_REG register field                                           | 65 |

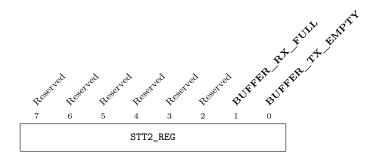

| 4.6  | STT2_REG register field                                           | 66 |

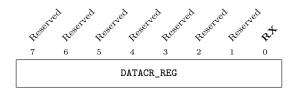

| 4.7  | DATACR_REG register field                                         | 66 |

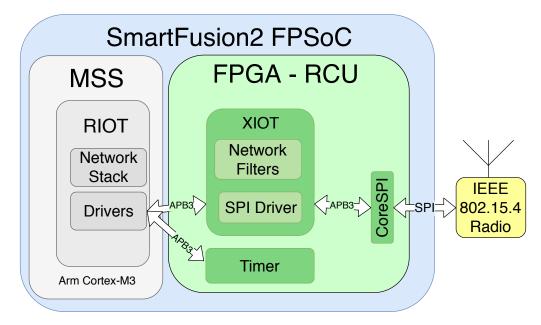

| 4.8  | Architecture of the heterogeneous solution with XIoT              | 67 |

| 4.9  | Heterogeneous architecture with XIoT integration layout           | 67 |

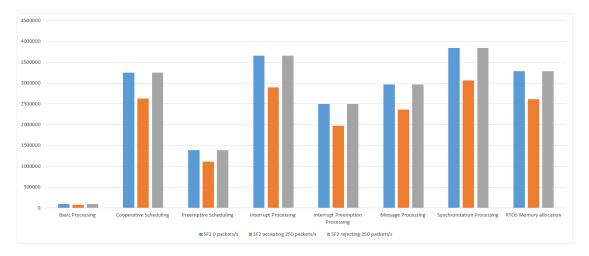

| 4.10 | SmartFusion2 Thread-Metric results with XIoT accelerator and fil- |    |

|      | ter disabled                                                      | 73 |

| 4.11 | SmartFusion2 Thread-Metric results with XIoT accelerator and fil- |    |

|------|-------------------------------------------------------------------|----|

|      | ter enabled                                                       | 74 |

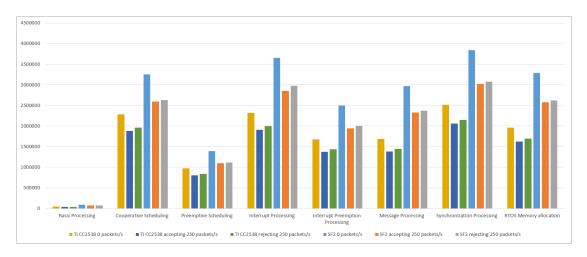

| 4.12 | SmartFusion2 with XIoT and TI CC2538 Thread-Metric results        | 74 |

# List of Tables

| 3.1 | Embedded OSes features comparison      | 43 |

|-----|----------------------------------------|----|

| 4.1 | Synthesis results for the M2S090TS SoC | 75 |

# Listings

| 3.1 | irq_enable function of RIOT-OS's irq_arch file                         | 47 |

|-----|------------------------------------------------------------------------|----|

| 3.2 | $\verb"cpu_switch_context_exit function of RIOT-OS's thread_arch file$ | 47 |

| 3.3 | Reset_Handler function of CMSIS's startup_m2sxxx file                  | 48 |

| 4.1 | Microsemi's HAL set 8-bit register macro                               | 68 |

| 4.2 | Register definition of CTRL1_REG required to use Microsemi's HAL.      | 69 |

| 4.3 | XIoT device driver arrays                                              | 71 |

| 4.4 | Code snippet from the function _init from the cc2520 peripheral        |    |

|     | driver                                                                 | 71 |

| 4.5 | $cc2520\_strobe$ function from the $cc2520$ peripheral driver          | 72 |

| 4.6 | Code snippet from the function $cc2520$ _rx from the $cc2520$ periph-  |    |

|     | eral driver                                                            | 72 |

### Acronyms

6LoWPAN IPv6 over low-power wireless personal area networks

**ADC** analog to digital converter

**AES** advanced encryption standard

AI artificial intelligence

AMBA Advanced Microcontroller Bus Architecture

APB3 Advanced Peripheral Bus v3

**API** application programming interface

ARQ Automatic Repeat Request

ASIC application-specific integrated circuit

**BLA** Black List Address

**BLIP** Berkeley low-power Internet stack

BSP board support package

CCA Clear Channel Assessment

CoAP constrained application protocol

COTS commercial of-the-shelf

**CPS** cyber-physical system

**CPU** central processing unit

CRC cyclic redundancy check

**DFD** duplicate frame detector

**DFF** D flip-flop

**DPA** differential power analysis

**DPM** dynamic power management

**DSP** digital signal processor

**DVFS** Dynamic Voltage and Frequency Scaling

ECC elliptic curve cryptography

EDF earliest deadline first

EM evaluation module

eNVM embedded non-volatile memory

ERCC error correction codes

eSRAM embedded static random-access memory

ETM embedded trace macrocell

**FEC** forward error coding

FIFO first-in-first-out

FPGA field-programmable gate array

FPSoC Field-Programmable System-On-Chip

FPU floating-point unit

FSM finite state machine

**GPIO** general-purpose input/output

**GPOS** general propose operating system

GPU graphics processing unit

**HAL** hardware abstraction layer

**HDL** hardware description language

**HTTP** hypertext transfer protocol

I/O input/output

I2C inter-integrated circuit

IC integrated circuit

ICMP Internet control message protocol

ICMPv6 Internet control message protocol version 6

ICN Information Centric Networking

**IDE** integrated development environment

**IETF** Internet engineering task force

ILA integrated logic analyser

**IoE** Internet of Everything

**IoIT** Internet of Industrial Things

**IoMT** Internet of Medical Things

**IoT** Internet of Things

IoT-ARM Internet of Things - Architectural Reference Model

IP Internet protocol

IPC interprocess communication

**IPHC** Internet protocol header compression

**IPv4** Internet protocol version 4

IPv6 Internet protocol version 6

IRQ interrupt request

**ISR** interrupt service routine

LAN local area network

LE logic elements

**LED** light-emitting diode

**LLN** low-power and lossy network

LPDDR low-power double data rate

LUT lookup table

M2M machine-to-machine

MAC medium access control

MCU microcontroller unit

$\mathbf{MEMS}$  microelectromechanical systems

MLA MAC Layer Accelerator

MMU memory management unit

MPDU Mac Protocol Data Unit

MQTT Message Queuing Telemetry Transport

MSS microcontroller subsystem

NAT network address translation

**NPF** Network Packet Filtering

$\mathbf{NR}$  Network Router

NRE non-recurring engineering

**OS** operating system

PAN personal area network

PHY physical layer

PSR packet sending rate

**PUF** physically unclonable function

RAM random-access memory

RCU reconfigurable computing unit

**RF** radio frequency

**RFID** radio-frequency identification

RFSoC Radio-Frequency System-on-a-Chip

$\mathbf{R}\mathbf{N}\mathbf{G}$  random number generator

**ROM** read-only memory

RPL IPv6 Routing Protocol for Low-Power and Lossy Networks

RTC real-time clock

RTL register-transfer level

RTOS real-time operating system

SerDes fullduplex Serializer/Deserializer

**SEU** single event upset

SHA secure hash algorithms

SoC system on chip

**SPI** serial peripheral interface

**SPPS** Secure Production Programming Solution

**SRAM** static random-access memory

TCB task control block

TCP transmission control protocol

TEE trusted execution environment

**TI** Texas Instruments

UART universal asynchronous receiver-transmitter

UDP user datagram protocol

uIP microIP

WLA White List Address

WLAN wireless local area network

WSN wireless sensor network

$\mathbf{WuR}\,$  wake-up radio

$\mathbf{XMPP}\;$  Extensible Messaging and Presence Protocol

### Chapter 1

### Introduction

"The day science begins to study non-physical phenomena, it will make more progress in one decade than in all the previous centuries of its existence."

—Nikola Tesla

The Internet of Things (IoT) is a new paradigm were the surrounding objects are part of the Internet. This new paradigm allows to sense and actuate on the physical world with ubiquitous and transversal wireless motes, mainly low-end IoT devices that reside in the network edge. Traditionally, the motes were aggregated in a wireless sensor network (WSN) composed by homogeneous devices that could even be disconnected from the Internet. With the rise of IoT, a variety of heterogeneous devices have flooded the network, creating the necessity for connectivity and interoperability, together with processing features capable of handle the evergrowing amount of data transmitted over the network. However, due to the scarce resources and common energy-efficiency constraints of the low-end IoT devices, the accomplishment of connectivity and interoperability are not straight forward, requiring new solutions at the architectural level of the motes.

This first Chapter introduces the content of this dissertation, beginning with an introduction to the Internet of Things in Section 1.1, and followed by a description of the low-end IoT devices at the network edge in Section 1.2. A market analysis is presented in Section 1.3 based on the forecasts of the electronic and communication industries. Section 1.4 presents a general architecture to IoT regarding the flow of information and the embedded system in IoT. In Section 1.5 the two main requirements for IoT low-end devices, connectivity and security are explained. Section 1.6 discussed the shift from WSN to IoT and presents a standard network stack for IoT. Considering the increase complexity on the network edge, Section 1.7 presents the requirements for an IoT-enabled OS suitable for low-end devices. The dissertation structure is explained Section 1.8 and Section 1.9 concludes the Chapter.

### 1.1 The Internet of Things

The concept of Internet of Things (IoT) was first introduced by Kevin Ashton in 1999 [1], and later clarified in [2]. It consists of a major technological revolution that has updated the current Internet infrastructure to a much more advanced computing network. Furthermore, all the physical objects around us will be uniquely identifiable and ubiquitously connected to each other.

The IoT achieved such a magnitude that is now incorporated in a larger concept, the Internet of Everything (IoE). The applications of IoT not only include home appliances, wearables and everyday objects, but can be expanded to a countless number of applications. IoE can be used in cities, enabling monitoring of road traffic, trash, pollution, etc., empowering the concept of smart cities [3]. Smart buildings are another application of the IoE, allowing the monitoring and control of lights, air conditioning, etc. [4]. On the automotive industry, IoE empower not only the existence of connected cars but also the existence of full autonomous vehicles [5]. Other applications of IoE include the monitoring in real time of water quality [6], improvement of supply chains [7], food traceability [8], agriculture [9], and much more.

Nowadays, IoT can be considered a dynamic global network infrastructure that extends the classic Internet. It is composed by myriads of connected devices that can interact and communicate between them, extract information and react to the physical world. Most of the devices that compose this infrastructure reside in the network edge and are the so called "things". They can be defined as physical or virtual objects that have an identity, attributes, and are endowed with communication interfaces. The "things" can acquire and propagate information in the network, communicate with each other, and may have sensors and actuators to interact with the physical world. Some of these "things" may be endowed with intelligence by means of artificial intelligence (AI), allowing them to adapt to the environment and learn from other "things".

The most important activity of the "things" in the network edge is to collect valuable data. In fact, it is only economically viable to turn an object into a "thing", when the value of the data generated is higher than the cost of endowing the object with the needed functionalities. The data value is increasing in today's world, because with reliable data is possible to improve business models, supply chains, transportation systems, etc. In the past data was acquired manually by people, although, they have limited attention and accuracy making this data less reliable. Therefore, empowering objects and machines with computers capable of collect reliable information and make this data available over the Internet, allowing

to see the world as never before and empower endless businesses and services.

The connection of physical objects to the Internet requires the incorporation of suitable computational systems, able to empower such objects with the appropriate processing and communication capabilities. These computational systems fall in the category of low-end embedded systems, mostly tiny small energy-efficient and wireless devices empowered by low-end microprocessors with scarce resources. Even extremely constrained in terms of computing power, available memory, communication, and energy capacities, it is expected that they fulfil the requirements of a cyber-physical system (CPS): (i) reliability, (ii) real-time behaviour, and (iii) an adaptive communication stack to integrate the Internet seamlessly [10].

### 1.2 Low-end Devices at the Network Edge

The typical embedded system that enables the connection of objects to the Internet can be designated as low-end devices. Due to the increasing value of data and due to the characteristics of the low-end devices (small fabric, low-cost and energy efficiency) they are spreading rapidly in this new Internet era. The emergence of devices with these features can be explained resorting to Moore's and Koomey's laws. The Moore's law specify that the transistors number will double every two years on an integrated circuit (IC) [11], which enables the integration of more transistors in the same space and consequently, the existence of more powerful devices occupying less silicon area. Hence, due to the high cost of silicon the price per transistor will also decrease, allowing the existence of an IC with the same performance in a smaller fabric form and lower price.

Related to energy consumption, Koomey's law explicit that the number of computational operations per joule dissipated in an IC is been doubling every 1.57 years, this means that with a fixed computing load, the amount of energy needed will decrease by a factor of one and a half [12]. Usually, low-end devices are deployed in scenarios with limited access and due to the existing number of devices maintenance should be avoided by its difficulty and cost associated. Wherefore, to avoid maintenance, energy-efficiency is required in wireless motes, which commonly run their entire lives in a single charge of a storage device (e.g. batteries, micro-fuel cells, capacitors, etc.) or resorting to harvesting solutions (e.g. solar, flow systems, thermal, etc.). The reduction of power consumption at the IC level has making possible the deployment of myriads of devices, with low maintenance cost and using tiny amounts of energy.

Due to the importance of the "things" on the IoT, the hardware that endows the object with the processing and communication capabilities is a preponderant choice when designing an IoT ecosystem. The constraints of the scenario where the system is deployed largely impact the selection of the hardware platform that can be made, mainly, from three different groups:

- commercial of-the-shelf (COTS): Already-made devices that integrate a central processing unit (CPU) usually equipped with several peripherals such as timers, analog to digital converter (ADC), external memories and even communication interfaces. A COTS solution speeds up the development cycle and requires less non-recurring engineering (NRE) effort. By the other side traditionally COTS devices are not customizable, have lack of extensibility, and usually brings unnecessary hardware to the application, increasing cost, area, and power consumption;

- Custom Platform: Devices that target a particular application, designed and built from the scratch (e.g. application-specific integrated circuit (ASIC)). This solution can achieve the highest performance, and can be built to optimize a desired constraint. More suitable for production in high scales, or when the price per unit is a constraint due to the highest NRE cost in comparison with the other solutions;

- Hybrid Platform: Conjugates the best of the two worlds, providing a built in system and allowing flexibility to the final solution. The NRE cost depends on the level of customization required. These platforms are of special interest to extend an already developed system, implemented in a COTS. Platforms that combine a microcontroller unit (MCU) and field-programmable gate array (FPGA) technology on the same system on chip (SoC) (known as Field-Programmable System-On-Chip (FPSoC) [13]), allows the usage of mature software and hardware, integrating easily new hardware peripherals with minimum efforts. The FPGA technology has gained special attention lately, because they turned more cost-effective, with a smaller footprint, better power consumption efficiency, and higher performance.

#### 1.3 IoT Market

The emergence of new business models and applications has been increasing the potential growing of IoT. Subsequently, this market captivated the attention

of big players in the industry, such as Arm, Intel, Qualcomm, Microsoft, IBM, and many others. In the last years from companies to universities, multiple entities have concentrated their efforts in develop solutions for this emerging concept, ranging from the edge devices to the cloud, developing new hardware, protocols and services.

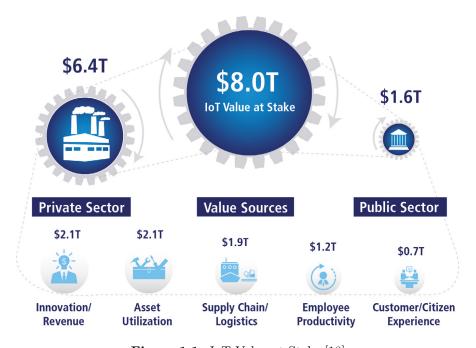

Back in 2009, Cisco presented the IoE, a vast network where all the physical things are connected, Cisco anticipated that this network would potentially rise the number of connected devices to 50 billion, creating a USD 14.4 trillion in Value at Stake [14]. Ericson back to that time, supported the forecast of Cisco presenting the same value of 50 billion connections by 2020 [15]. Later in 20015, Cisco reviewed that the global Internet protocol (IP) networks will increase from 16.3 billion in 2015 to 26.3 billion by 2020 [16]. In 2017 Ericson presented a new forecast, proposing that by 2023 there will be 30 billion connected devices, with 20 billion related to IoT [17]. Furthermore, Ericson with DHL published a report [18] in 2015, stating that IoT by itself, will generate USD 8 trillion worldwide in Value at Stake over the next decade (Figure 1.1).

Figure 1.1: IoT Value at Stake [18].

With a more optimistic forecast, Intel predicts 200 billion devices in the near year of 2020. They expect a fast-growing pace in the IoT world, rising in just five years from 15 billion in 2015 to 200 billion in 2020, pointing out that in 2025 the total worth of IoT technology will reach the USD 6.2 trillion [19].

IHS Markit, a recognized financial services company, envisioned in 2017 that more than 31 billion devices would be connected in 2018. Furthermore, stated that

while the local area network (LAN) and personal area network (PAN) solutions present de facto standards and market stability, the new IoT market presents duplicated and overlapping wireless solutions. Therefore, this fragmented market, leads to IoT vendors increase their shipments in over 20% year-on-year [20].

Futurum, a research and analyst firm, stated in 2017 that the global number of connected devices and objects in operation in 2020 will be between 40 and 50 billion. As a point of reference, they illustrate that Qualcomm, alone, ships roughly a million chips for IoT every single day. Furthermore, their estimations envision a spending in IoT of USD 250 billion in 2020, with 40-45% of that spent in products, and 55-60% in services [21].

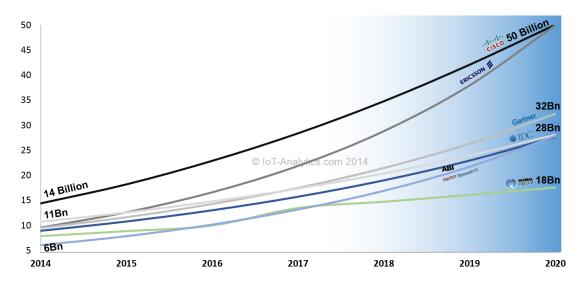

Figure 1.2: IoT Market forecast: Connected devices 2014-2020 [22].

In 2017, Arm stated in a white paper [23] their forecast to the IoT world by 2035. They estimate a production of 1 trillion devices between 2017 and 2035, reaching in 2035 a USD trillion per annum of spends in IoT hardware and services.

The market predictions diverge largely from entity to entity as seen in Figure 1.2. However, what could be extracted from the different envisions is that for every person living on earth, there will be at least 2, maybe even 6 connected things by 2020. The IoT arena will create a revenue opportunity for companies beyond what Apple, Google, and Facebook are selling together today, surpassing the economic output of Germany within the next 10 years [22].

#### 1.4 IoT Architecture

The IoT presents endless opportunities, consequently it has been applied to diverse scenarios such as smart homes, wearables, smart cities, smart grids, automotive industry, agriculture, retail, to name a few [24]. The different scenarios present unique characteristics that constrain the used technologies, network architectures and design approaches.

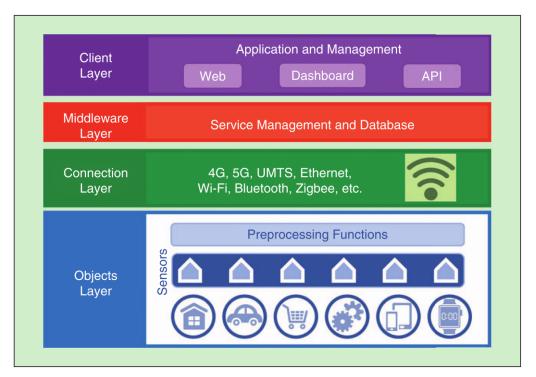

Figure 1.3: The general architecture of the IoT [25].

A general architecture for IoT is shown in Figure 1.3, which consists of a four-layer vertical architecture with bottom-up data flow [26–28]. The layers that compose this stack can be described as: (i) Objects layer, where the physical items reside, they are identifiable and able to acquire data generated by them or by their surroundings. These objects are identifiable with resources such as radio-frequency identification (RFID) tags, and with ability of auto-identification trough medium access control (MAC) addresses or an ID stored in a non-volatile memory; (ii) Connection layer, that connects the physical objects with the middleware layer. The connection resources used are influenced by the communication systems and protocols used, the network topology, the type of data acquisition systems, and the communication capabilities of the devices; (iii) Middleware layer, stores the information acquired in databases, related with the services provided by each physical object. Data mining functions are applied on this layer and decisions made in accordance. Due the big amount of data generated, some IoT applications use

proper firmware to pre-process and filter data before streaming; (iv) Client layer, corresponds to a specific target application. Generates the proper results and actuation in accordance with the middleware layer information. This layer is also responsible for the connection of the object to the environment, users or provide machine-to-machine (M2M) communication. It is on this layer that the IoT is able to create added value, trough providing valuable information, improving safety, mange supply chains and many more depending on each application scenario.

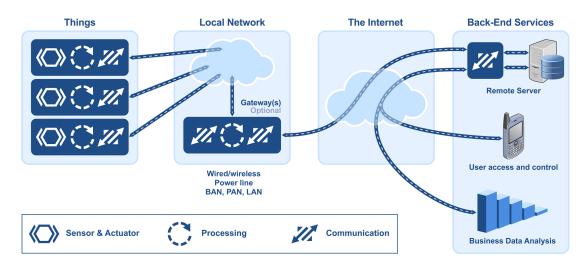

Figure 1.4: The IoT from an embedded systems point of view [29].

The work of this dissertation will focus on the embedded system device that empower IoT at the network edge. Figure 1.4 shows a common topology for IoT from an embedded system point of view. It is composed by four main components: (i) the "thing", an embedded device endowed with processing capabilities, that is able to communicate, sense the physical environment and/or actuate; (ii) the Local Network, that can include a gateway, responsible by perform connectivity aggregation trough collection of data-in-transit, processing, verification and further retransmission to the Internet; (iii) the Internet; (iv) the Back-End Services that comprehend enterprise data systems (Cloud) or private repositories, responsible for saving data for further processing and making it available to authorized users [29].

### 1.5 Connectivity and Security

The IoT is not an interface by itself, it is more a set of frameworks connected in the vast Internet. Even more, the endpoints are built in embedded devices that

are getting cheaper, smaller and by its nature run applications with strong communication requirements. The prevalence of such a big network of interconnected devices will impose new security and privacy threats putting all those devices at a high risk [30]. For these reasons, strong communication and security constraints are applied to these devices.

The communication requirements for the IoT endpoints devices include:

- Connectivity: Possibility of all the endpoint devices to be connected to the network. The transition from Internet protocol version 4 (IPv4) to Internet protocol version 6 (IPv6) allows the connection of 2<sup>128</sup> devices with a unique IP address. The usage of IPv6 augments the security over IPv4 because the first does not use network address translation (NAT), avoiding unnecessary addresses translation and packet modification;

- Interoperability: Ability of exchange and make use of information regardless the used technology. To achieve interoperability is needed the (i) incorporation of multimode radios that allow diverse IoT devices talk to with each other; (ii) software flexibility that enables the support for different standard communication protocols; (iii) strong hardware-based security, as described later;

- **Reachability**: Availability of a node over time on the network. The IoT nodes will be full reachable, with a wide deployment of IPv6, thus allowing the unequivocal identification of the endpoints on the network.

To ensure proper security of the endpoint devices is needed to secure not only the device, trough hardware security, but also the data contained and exchanged by it. The security requirements for the endpoint devices are described as follows:

- Data Security: the security triad or CIA triad stands for confidentiality, integrity and availability. It constitutes the root of trust, in data security for the IoT devices, and is summarized below:

- Confidentiality: Ability to provide confidence on user about information privacy. It is done by preventing unauthorized people to access information. The data privacy can be guaranteed by, for example, encryption and two-step verification;

- Integrity: Guaranty that data will remain unchanged during transmission and reception. Perhaps, if data is modified it must be noticed.

Commonly used methods to verify data integrity are checksum and cyclic redundancy check (CRC);

Availability: Capability to give immediate access to data, to authorized parties, in any condition. It guarantees that the information will be properly saved and accessible. Two methods to guaranty availability are redundancy and failover backup.

- Hardware Security: The cornerstone of embedded system security is to guarantee that only authorized microprocessor code is loaded and executed, consequently, a hardware root of trust is required. Furthermore, a hardware root of trust should provide secure monitoring, secure validation/authentication, storage protection, secure communication and key management. A hardware root of trust can be defined by four basic blocks:

- Protective hardware: Provides a trusted execution environment (TEE) [31,32] to run only privileged software. This is achieved through the implementation of secure measures on the silicon manufacturing phase, with the implementation of unique security keys. Protection to the runtime memory should be implemented to protect the STACK, HEAP and global data;

- Tamper detection and countermeasures: Code loaded from the outside is validated before running on the secure CPU. When a validation fails a tamper is detected triggering the countermeasures, that may include device zeroization, used to permanently erase sensitive data, such as cryptographic keys, device lock, among others;

- Crypto-engines: Dedicated hardware cryptographic accelerators to allow data and communication channels protection, without overload the CPU.

Notwithstanding security being a major concern in IoT, it is let out of the scope of this dissertation. Therefore, this work will only focus on the connectivity of low-end IoT devices.

#### 1.6 IoT Network Stack

The IoT is the expansion of the current Internet services, so it as to accommodate each and every object which exists in this world or likely to exist in the coming future [33]. Although, today's Internet is dependent on IPv4 that is based on a 32-bit addresses, and therefore able to generate only 4,294,967,296 unique addresses. The IPv4 address exhaustion occurred in Feb.3 2011, however it had

been delayed using remapping methods such as NAT [34]. Considered this limitation, IPv6 was developed aiming to have enough addresses to scale the Internet for decades to come, which according the estimates may include 50 billion connected devices by 2020 [34]. IPv6 uses a 128-bit address that empower the generation of  $3.4 \times 10^{38}$  unique addresses, opening the Internet to a new era and allowing the connection of countless devices [34,35].

WSNs at the IoT edge, are mainly composed by oodles of inexpensive low-power devices, with small computing capabilities, scarce memory, and mainly relying on IEEE 802.15.4-based networks. Essentially this network supports low bandwidths, small packet sizes and typically suffers from severe and frequent packet loss [36,37]. In order to endow such devices with IPv6 connectivity, the network stack deployed in IoT require an adaption layer to deal with the constraints of the IEEE 802.15.4 MAC/physical layer (PHY) and thus achieve IPv6 compliance. The IPv6 over low-power wireless personal area networks (6LoWPAN) deals with such limitations, through the introduction of mechanisms of header compression, fragmentation, reassembly, and stateless auto configuration as well as implementing modifications to the neighbour discovery, reducing bootstrapping complexity [38,39]. This adaptation layer allows the big shift from traditional WSN to IoT, thus, enables the usage of IPv6 in such constrained devices, and due to its interoperability and lightweight implementation is being while deployed on constrained embedded systems [40].

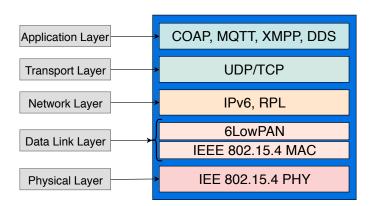

Figure 1.5 presents the network stack proposed by the Internet of Things - Architectural Reference Model (IoT-ARM) [41], which is a standard stack that aims to increase the connectivity and the interoperability among IoT devices [42].

Figure 1.5: 5-layer IoT-ARM Communication Model [42].

Other protocols could be adopted to the network stack, however, the presented in Figure 1.5 are recommended to be used on low-end devices endowed with a low-power radio interface.

1. **Physical Layer**: Is defined on IEEE 802.15.4 standard and suits the needs of the target devices.

- 2. **Data link layer**: The MAC layer provides access to the media and is part of IEEE 802.15.4 protocol. In this layer resides also the 6LoWPAN adaptation layer allowing the usage of IPv6 in resource constrained devices.

- 3. **Network layer**: Address and routes data through the network, traditionally enabled by IPv4, and recently upgraded to support IPv6. The IPv6 Routing Protocol for Low-Power and Lossy Networks (RPL) [43] is a routing protocol, that improves the route of data between autonomous devices in the Internet.

- 4. Transport layer: The user datagram protocol (UDP) and transmission control protocol (TCP) are the transport protocols used in the Internet. Often, TCP is considered too complex for low-power and lossy network (LLN), thus, not suitable for devices with few resources, and demanding for low power consumption. UDP is the most suitable and deployed on IoT scenarios.

- 5. Application layer: The hypertext transfer protocol (HTTP) that is used on the Internet is too complex for constrained nodes, thus alternative mechanisms have been developed for LLN. One of the most important mechanisms is constrained application protocol (CoAP), a web transfer protocol targeting M2M applications, and capable to interoperate with HTTP. CoAP runs over UDP while Extensible Messaging and Presence Protocol (XMPP) and Message Queuing Telemetry Transport (MQTT) run-over TCP.

### 1.7 Operating Systems for Low-end IoT Devices

The complexity of the IoT arena is rising rapidly and the amount of data and protocols that need to be managed is pushing IoT low-end devices out of them comfort zone, thus the integration of a full-fledged OS is required. A general propose operating system (GPOS) such as Linux is so far considered too complex for IoT low-end devices [10]. Besides, the usage of lightweight OS dedicated to WSN in more powerful IoT devices result in less energy-efficient implementations and do not exploit all the devices capabilities [10].

Furthermore, it is desirable that the OS provides capabilities of a modern full-fledged OS, such as native multi-threading, hardware abstraction, dynamic memory management, a friendly application programming interface (API) and

INTRODUCTION 13

at least C or C++ programming languages. Portability and interoperability are important at the OS level, thus open standards and APIs such as POSIX should be adopted. A complete and comprehensible documentation is required to make the best use of the OS and ease application design. Another important point when choosing an OS for IoT is the maturity of the code, widely deployed and tested code with commercial applications and a large community of contributors are more unlikely to have undetected errors, thus open source code should be always a first choice [44].

#### 1.7.1 Requirements for an IoT OS

Due to the characteristics of the IoT low-end devices, an OS suitable for this field of embedded systems must fulfil several requirements and provide modularity and configurability, to be possible his deployment in different hardware platforms and applications. The widespread requirements are:

- Small Memory Footprint: Low-end devices exhibit scarce memory resources, usually a few kilobytes of random-access memory (RAM) and read-only memory (ROM) [45]. Consequently, the OS should have a small footprint maintaining an acceptable performance and convenient API;

- Support for Heterogeneous Hardware: The OS suitable for the IoT need to be able to deal with a heterogeneity of hardware architectures, is desirable to support various MCUs architectures and families from 8 bit to 32-bit architectures, enabling support to devices with different capabilities such as memory management unit (MMU) or floating-point unit (FPU);

- Energy Efficiency: Due to the power constraints of IoT low-end devices, the OS should make use of the power saving modes available on the MCUs, resorting to efficient schedulers policies to switch to sleep modes as soon as possible;

- Real-Time Capabilities: Various applications require precise timing and timely execution, thus the OS should guarantee worst-case execution times and worst-case interrupt latencies;

- Network Connectivity: The need to support multiple link layer technologies and provide communication with other Internet hosts, led to the use of network stacks based on IP protocols directly on IoT devices [46]. Thus, a key requirement for an IoT-OS is offer support for heterogeneous

14 INTRODUCTION

link layer technologies, such as low-power radio and wired technologies. Furthermore, should provide a modular network stack based on standard (open standards are mandatory, such as those specified by Internet engineering task force (IETF)) IP protocols relevant for IoT [46] (a full-fledged TCP/IP implementation as well as a 6LoWPAN stack) that support evolution and integration of multiple network protocols;

• Security: IoT devices can be deployed in critical or industrial infrastructures with life safety implications (in this case certification of all the application including the OS, may be mandatory), in other hand the communication capabilities of this devices entail dangerous, so it should meet high security and privacy standards. Often deployed in critical applications with difficult physical access and high failure cost, these systems must be robust and thus the OS reliable. From a security data point of view the IoT OS should fulfil the CIA triad. Secure mechanisms for software updates must be incorporated and open source used as much as possible [47].

#### 1.8 Dissertation Structure

The remaining of this dissertation is structured as follows:

- Chapter 2 presents an analysis of prominent OS and platforms that enable

the development of this dissertation. Also, analyses the evaluation tools

that allow the development of such a work and presents a literature review

of relevant state-of-art in the development of heterogeneous solutions for IoT

devices.

- Chapter 3 analysis heterogeneous architectures for low-end devices with special focus on an in-house project the CUTE mote. The structure of RIOT-OS is presented in this chapter and described the deployment of such OS on a COTS platform with the usage of IAR Workbench. Furthermore, is presented the heterogeneous architecture developed and the deployment of RIOT-OS in this platform. The chapter concludes with the evaluation of the COTS and heterogeneous solution.

- Chapter 4 presents a discussion of hardware acceleration on low-end IoT devices, followed by the analysis of the MAC Layer Accelerator (MLA) deployed in CUTE mote. Then, several improvements to the hardware accelerator are presented, emerging XIOT, a refactoring of the MLA. Furthermore,

INTRODUCTION 15

this chapter describes the integration of XIOT in RIOT-OS and finalizes with the evaluation of the architecture.

• Chapter 5 concludes the dissertation discussing the obtained results in the different platforms and analyses the advantage of hardware network-related accelerators in low-end IoT devices. For last, are presented future developments for this work.

#### 1.9 Conclusion

This Chapter has introduced the IoT world, with focus on this dissertation core, the low-end devices at the network edge. It was analysed the bottom-up flow of information in IoT and how embedded systems play a critical role in the generation and streaming of information. The two main requirements for embedded systems in the IoT were also discussed, with special attention to the connectivity challenges. To solve those challenges was presented a network stack for the low-end devices in the IoT edge. Knowing that the complexity on the edge is increasing, the low-end IoT devices can benefit from an embedded OS, thus, the requirements for an OS suitable for these devices were discussed. Finally, was described the overall structure of this dissertation. The next Chapter presents relevant state of art and the tolls used during this dissertation.

## Chapter 2

### State of Art

"If I have seen further than others, it is by standing upon the shoulders of giants." - Isaac Newton

This Chapter analyses the existing tools and hardware solutions that allow to develop the work of this dissertation, as well as the current state of art in heterogeneous architectures for low-end devices. Section 2.1 analyses the most prominent and suitable OS for low-end IoT devices in the network edge. Then, Section 2.2 describes the hardware platforms used for the development of the heterogeneous architecture and the COTS solutions used for performance comparison. Section 2.3 presents the main tools that allow the development, test and evaluation of the developed work. The state of the art of heterogeneous architectures is presented in Section 2.4, with special focus on CUTE mote project. Finally, Section 2.5 concludes this Chapter.

#### 2.1 Operating Systems for IoT

Traditional WSN were mainly homogeneous networks with a single connection point, or in some cases even disconnected from the Internet. As seen previously in Section 1.5 and Section 1.6 of Chapter 1, the transition from WSN to IoT requires wireless motes to guarantee connectivity, interoperability and reachability. The accomplishment of these requirements can only be achieved with the integration of an IP compliant network stack in the motes. However, the incorporation of a network stack largely increases the complexity of the software deployed in the IoT devices. To manage such complexity, the integration of an OS in these devices is mandatory, however, due their scarce resources this is not straightforward.

The OSes available for IoT present a variety of features, and even that all of them guarantee in somehow the basic features to create at least a node in a WSN, not all of them fulfil the requirements presented in Subsection 1.7.1. Therefore, the design choices of the OS will impact its behaviour and applications. A summary of the design options of an OS for resource constrained (and connected) embedded device is presented below.

- Architecture: The design structure and modularity of the OS are determined by the adopted architecture, which may be monolithic, microkernel or layered architecture. The monolithic architecture is all compiled into a single system image, resulting in a small OS footprint with reduced overhead in the interaction between modules. Consequently, the low fragmentation and isolation of this architecture makes it difficult to maintain and more prominent to system failures, due to errors in single modules. On the microkernel approach the kernel size is shortened, providing a minimum set of functionalities inside the kernel. The interaction between user and kernel space is provided by the usage of user-level servers. By the fragmentation achieved, the reliability, customization and maintainability are improved in comparison with the monolithic architecture. However, the communication between user and kernel space introduces a degradation of performance. In the layered approach the OS is split into various layers, implementing each of them a functionality. This architecture presents less modularity that the microkernel, however, it is more flexible and reliable than the monolithic design;

- Memory Allocation: As described before, IoT low-end devices have scarce resources, including memory. Therefore, the strategy for memory allocation must have in consideration the available resources, and it can be either static

or dynamic. The static memory allocation is a simple and a useful technique to deal with reduced memory. No memory allocation is done in run time, as drawback it results in an inflexible device. The dynamic strategy makes the system more flexible and allows a better management of the memory space. However, it can be a hard task to be performed by an MCU with reduced resources, mainly because of the absence of MMU that makes the memory management difficult, and decreases the system's security;

- Network Buffer Management: Regarding the specificity of an OS for IoT devices, the usage of a network stack built in a layered fashion creates the necessity of exchanging information between each layer of the stack. This can be done either by reference, or by memory copy. Some OSes present a new approach, where a central memory manager is used to handle the data between layers in a more efficient manner;

- Driver Model and Hardware Abstraction Layer: A clear-cut driver model enables the integration of different peripheral drivers into an application, facilitating further integration of new drivers into the OS. A well-defined hardware abstraction layer empowers the portability between different MCU families and architectures;

- Scheduling Strategy: IoT devices are applied to a wide range of scenarios, both with real-time and non real-time requirements. This enforces the OS to implement proper scheduling policies to fit the application requirements. The scheduler applied to IoT devices should have in consideration the energy consumption as well as the memory usage;

- Programming Model: Two models are dominant in the IoT arena and can be defined either as event-driven or multi-threading. On a programming model based on event-driven, the execution of a task is triggered by an event, e.g., an interrupt. This model is more suitable for devices with scarce resources, and is often implemented by the execution of an event loop, instead of a more complex scheduler and a shared-stack model [44]. In a multi-thread environment, the usage of a scheduler is imperative to manage the execution of threads. This approach enables de development of more complex systems, but requires more powerful hardware resources than the event-driven model;

- Programming Languages and Debugging Tools: The usage of standard programming languages such as ANSI C or C++ simplifies the portability between platforms, and enables the usage of well-established toolchains

and tools (development and debugging). Besides, dialects or OS-specific languages may be used to solve performance and safety-relevant issues that low level languages such as C are not able to solve. Due to the constrained resources of the low-end devices, some of them do not offer debugging interfaces. Alternatively, it can be used the printf() function over a UART or even a light-emitting diode (LED) connected to a general-purpose input/output (GPIO) port to provide debug information;

- Testing: A crucial phase in the development of any application is the testing process, thus the OS should provide facilities to help in this process. The hardness of testing IoT devices arise from their distributed, deeply embedded and often very constrained nature. An extensively used technique to test hardware-related parts, such as device drivers, is the usage of hardware emulation tools, e.g., MSPSim or Emul8 [48]. Network emulators and simulators such as Cooja or ns-2/ns-3, that allow for the integration of OS code, are an asset for such a task [49];

- Feature Set: Two main groups compose the set of features provided by the OS. One comprehends the kernel functionalities, such as timers and synchronization mechanisms, and other the high-level features of the system that might include a shell or cryptographic libraries;

Some available OS solutions to deploy in an IoT device at the network edge include Contiki-OS [50], Tiny-OS [51], Linux, RIOT-OS [52], FreeRTOS [53], Amazon FreeRTOS [54], Mbed OS [55], Mantis [56], Nano-RK [57], NutOS [58], MansoNS [59], MicroC/OS-III [60],  $\mu$ Clinux [61], etc. However, most of them does not fulfil the requirements described in Section 1.7 of Chapter 1. In the remaining of this Section are described in detail the most prominent OS solutions for the low-end IoT devices.

#### 2.1.1 Contiki-OS

Contiki-OS [50] is an OS developed around the microIP (uIP) stack, targets the resource-constrained embedded systems, and it is currently applied in fields such as WSN or IoT. Architecturally, Contiki-OS is implemented in a modular approach, that is close to the layered architecture [62]. OS facilities are provided in the form of services, having their own implementation and interface, which increases the granularity of the OS and decreases the interdependence between system modules.

The programming language adopted to develop Contiki-OS was C, a highly portable language. The supported platforms cover a wide range of resource-constrained devices, including 8-bit AVR platforms, 16-bit and 20-bit MSP430 platforms, and 32-bit Arm Cortex M3 architecture [44].

An event-driven programming model is used in the kernel space, where the event handlers run in the same context and to completion. No priority is assigned to the event handlers, however, they can use internal mechanisms for preemption [63]. In the application space, Contiki provides partial support for multithreading by implementing a lightweight form of threads, which are designated by Protothreads [64]). Those lightweight threads are stack-less and have a very small memory overhead. Besides the partial multithreading support, none sophisticated scheduling algorithm is materialized, consequently the OS does not fulfil the requirements for real-time applications. Contiki provides power saving modes, by switching to the deepest sleeping mode supported, when the OS finishes all the pending tasks.

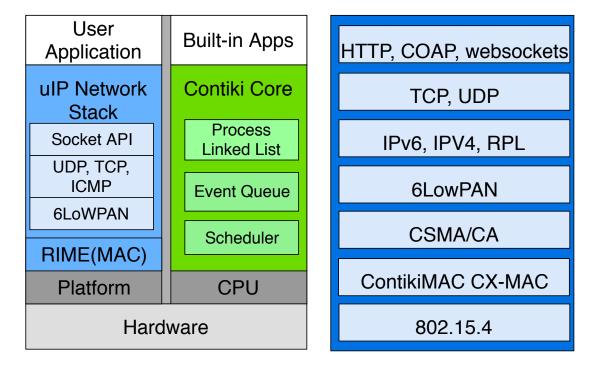

Figure 2.1: Contiki-OS architecture stack and supported IoT stack.

Contiki offers support for dynamic memory allocation. To ensure that no fragmentation happens in the memory, a memory allocator manager is used for compacting memory when there are free blocks in the system. The absence of a memory protection mechanism between different processes makes the overall system unprotected [63].

Contiki provides support to a wide range of protocols used in the IoT communication stack such as IPv6, 6LoWPAN, RPL, and CoAP [44]. An implementation of uIP [65] is provided with a minimum set of features needed to have a minimal TCP/IP stack, compliant with its full implementation on more powerful devices and OSes. This way, low-end devices can interoperate and communicate with remote servers without the need of protocol translation/adaptation in the middle. Another stack supported by Contiki is Rime [66], a lightweight stack able of provide a set of distributed programming abstraction layers. Such stack can be used when a simple and isolated network is needed by the final application. Simulation capabilities are provided in Contiki by Cooja [67], a simulation tool for WSN. Contiki enables the load and unload of individual applications or services at run-time [50], which makes possible the remote upgrade of the system.

The source code of Contiki is available under a BSD license on GitHub with a large community of contributors and forks. A rich API and documentation are available enhancing the development process.

#### 2.1.2 TinyOS

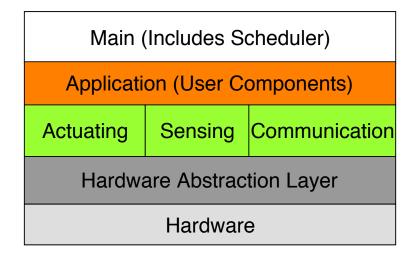

TinyOS [51] is a component-based and application-specific OS designed for WSN, with a low OS footprint targeting very constrained platforms. The OS implements a monolithic architecture and uses a component-based model. According the specificity of the application, the components will compose a static OS image, to be deployed on the mote. A component is an entity that exposes one or more interfaces, consisting of three computational abstractions: commands, events and tasks. This OS provides a single stack and there is no isolation between kernel and user spaces.

The programming model followed by TinyOS is the event driven model, with the addition of TOSThreads [68] in version 2.1, which enabled the support for multithreading. TOSThreads, a preemptive application level thread library for TinyOS, provides the ease programming of a threading model and the efficiency of an event-driven kernel. For these threads a cooperative scheduling algorithm is used, thus the kernel relies on the threads to yield the processor. Consequently, the programmer is responsible by managing concurrency. In TinyOS each thread has to allocate a task control block (TCB) with fixed memory space.

The scheduling algorithm employed by earlier versions of TinyOS relied on a non-preemptive first-in-first-out (FIFO) scheduling algorithm, thus the tasks on this FIFO ran to completion. The task execution is not an atomic process, and it can be interrupted by an interrupt handler, command or event. To be compliant

Figure 2.2: TinyOS architecture stack and supported IoT stack.

with the requirements for real-time applications, later versions of TinyOS implement an earliest deadline first (EDF) scheduling algorithm. However, in this policy there is no guaranty that the deadlines will be meet when the system is overload, compromising the deployment in systems with strong real-time requirements.

Since low-end IoT devices are resources constrained, MMUs are not always present in every device. Thus, TinyOS presents an efficient memory safety method [69] incorporated in the latest versions. In this OS only static memory allocation is used, consequently no heaps, function pointers or virtual memory mechanisms are used.

The OS communication capabilities encompass a Berkeley low-power Internet stack (BLIP) [70], an implementation of the 6LoWPAN stack that include TCP, UDP, Internet control message protocol version 6 (ICMPv6), IPv6, RPL and CoAP. The OS also uses Hydro routing protocol [71] to ensure reliable unicast communication within an IPv6 sub network with lossy links [72].

The set of features of TinyOS comprehend a file system, database [73], security [74] and simulation support provided by TOSSIM [75]. TinyOS uses a C dialect called NesC [76], which is a component-based and event-driven programming language [44]. The source code is provided under a BSD license, with extensive documentation, tutorials and examples.

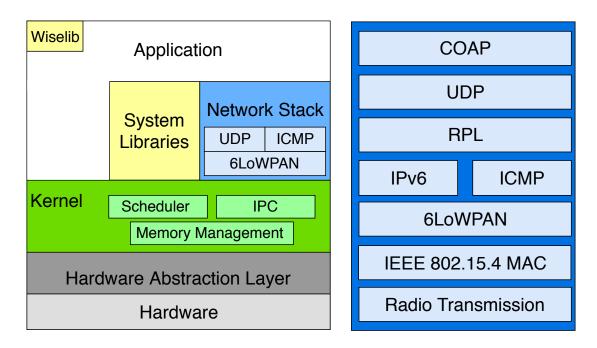

#### 2.1.3 RIOT-OS

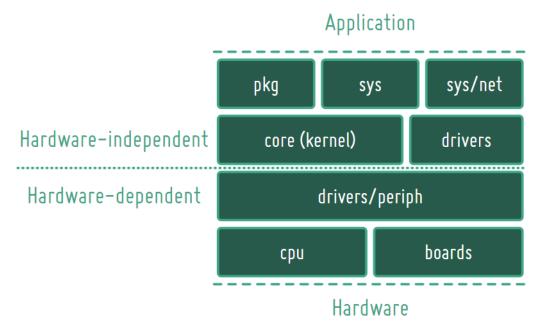

RIOT-OS [52] is an OS developed to fill the gap between WSN OS and full-fledged OS. Aiming to allow easy portability among a wide range of devices,

the OS is implemented in two distinct parts, hardware-dependent and hardware-independent code, with well-defined interface and independence of the modules.

RIOT-OS implements a modular architecture built around a microkernel inherited from FireKernel [77]. It uses a multi-threaded programming model similar to Linux, on which each thread has a unique TCB and its own memory space. The development of the multi-thread model gives special attention to the memory usage, by designing a very small TCB and minimizing the usage of the stack during run time. The use of multi-threading on RIOT-OS is optional, thus, it can be removed and the user application be the only thread running on the system decreasing this way the memory requirements. For thread synchronization and communication RIOT-OS offers mutex, semaphore and messaging queues.

Figure 2.3: RIOT-OS architecture stack and supported IoT stack.

The scheduler algorithm implied in RIOT-OS is based on fixed priorities and preemption. The scheduler policy enforces the thread with the highest priority to run-to-completion, that can only be interrupted by an interrupt request (IRQ). In order to promote energy efficiency, RIOT-OS proposes a tickless scheduler, i.e., it works without any periodic event, aka tickless. The system enters in sleep mode after switching to the idle thread, that will determine the deepest sleep mode possible, and only external events will wake up the system. In brief, RIOT-OS presents soft real-time capabilities [52].

On this OS the use of dynamic memory allocation is only allowed on the user application space. On the kernel side, runtime of O(1) is guaranteed by the

exclusive use of static memory allocation [10].

The OS is written in standard ANSI C language, with some hardware dependent parts written in assembly [44]. RIOT adds support for C++ programming language enabling this way the usage of powerful libraries. The use of standard languages allow to employ well-known toolchains and debugging tools, as well as increase portability features.

RIOT defines a flexible layer-separating architecture [78], incorporating two programming interfaces for the network subsystem, labelled as (i) netdev and (ii) sock. In (i) is offered a generic network driver interface, whereas in (ii) a high-level network interface is provided for applications access [52]. One of the implemented stacks by RIOT is GNRC, the default IP stack [78], based on the standard IP protocols, that supports 6LoWPAN, IPv6, RPL, UDP and CoAP implemented with well-defined interfaces and interprocess communication (IPC) [40]. A port of the full 6TiSCH stack is implemented in the form of OpenWSN [79] and CCN-lite is implemented as a port of the Information Centric Networking (ICN) [44]. On the default network stack, GNRC, a centralized network buffer is used to store packets, headers and other networking meta-data, allowing to transmit only the addresses of the information between the network layers, without need for data copy or duplication of data.

As described in Section 1.7, update over-the-air is an important feature, thus it can be included in RIOT with the integration of a boot-loader and two firmware slots. Through the 6LoWPAN network stack, a RIOT image (featuring a software update module) can be downloaded into the system allowing the reconfiguration. RIOT goes even further by providing a secure update with integrity and authenticity of the downloaded firmware using state of the art public-key crypto and hashing algorithms [52].

RIOT provides a hardware visualizer that allows the compilation and execution of RIOT applications on a host OS. Other hardware simulators can be used to compile and test RIOT such as MSPSim & Cooja [52], IoT-Lab [80] or DES-Testbed [81]. A wide set of features is provided by RIOT, of which stand out a powerful command-line interpreter (a Linux-like shell), a virtual file system and cryptographic libraries. The source code of RIOT is available on GitHub under a LGPL v2.1 license. A consistent documentation is provided in a standard form with the usage of Doxygen. The community around RIOT-OS is quite active through the development of code updates, bug detection and publication of scientific papers and academic works.

#### 2.1.4 FreeRTOS

FreeRTOS [53] is a popular real-time operating system (RTOS) widely deployed in industrial and commercial applications as well as used in several research projects. A large community use this OS and it has been ported for many MCU architectures and platforms. The architecture of FreeRTOS is fairly simple, all the OS is splitted in four files written in C, usually is considered more a threading library than a full-fledged OS [44]. FreeRTOS employs a multi-threading programming model based on tasks, with each task being instantiated statically with its own stack.

The OS presents real-time features provided by the implementation of a preemptive, priority-based round-robin scheduler, and by synchronization objects such as mutexes and semaphores. Since version 7.3.0 a optional tickless mode is supported in the scheduler [44]. Dynamic memory allocation is supported by the OS in five different modes: (i) allocate only, memory cannot be freed, (ii) allocate and free, without coalescent of adjacent free blocks, (iii) wraps of the standard C library malloc() and free() for thread safety, (iv) an algorithm similar to (i), but with coalescent of adjacent free blocks to avoid fragmentation and, (v) an improvement of (iv), with the ability to scatter the heap over several memory sections.

FreeRTOS does not natively provide a network stack, , however multiple stacks from third-party can be used as a supplement to the OS. Ports of network stacks were developed to match with FreeRTOS, of which stand out the adaptation of IwIP and Nabto.

The OS does not define a driver model or abstraction layer, rather it works with vendor supplied board support package (BSP). FreeRTOS does not provide any debug or testing capabilities, instead it resides in third-party solutions, due to the portability of the OS it can easily integrated in standard tools. FreeRTOS offers rich documentation, compromising books, trainings and a broad API. The source code is provided under a GLP license.

#### 2.2 Hardware Platforms

The development of a heterogeneous solution for low-end IoT devices, with the integration of hardware accelerators presents various challenges, as described in [36]. The common constraints for IoT devices, that reside on the network edge include low-price, power consumption, processing capabilities, memory resources, among others. Thus, the following requirements should be considered, not only

in the choice of a platform, but also is desired their accomplishment in the final solution:

- Implement an **IoT-enabled network stack**, that promotes the communication requirements for an IoT device: (i) connectivity, (ii) interoperability, and (iii) reachability;

- Provide **scalability**, to allow the inclusion of new hardware accelerators;

- Provide availability, an important feature for sensitive applications that have the potential to cause harm on persons or goods;

- Empower design **modularity and customization** to facilitate the efficient integration of only the required components, optimizing the usage of resources and power;

- Facilitate **portability**, enabling the fast integration of a heterogeneous set of devices, including different communication interfaces and OS;

- A secure hardware architecture, in a commercially available low-power SoC.

- Data protection mechanisms that enable the accomplishment of the CIA triad requirements identified in Section 1.5.

Having in consideration the requirements previously presented and the hardware solutions described in Section 1.2 of Chapter 1, relevant platforms for this dissertation are analysed in the next two subsections.

#### 2.2.1 Texas Instruments

Texas Instruments (TI) offers a broad portfolio of wireless connectivity devices including the lowest power and longest-range solutions across 14 wireless connectivity standards, certified and third-party modules that allow the quick and efficient development of IoT motes. The more relevant TI solutions for this dissertation are:

• Wireless MCU SoC: The CC2538 and the CC2650 are wireless SoC that combine a powerful Arm Cortex-M3-based MCU and a robust IEEE 802.15.4 radio transceiver. This combination enables the device to handle complex network stacks with security, heavy processing applications, and over-the-air download. Powerful hardware security accelerators enable quick and

efficient authentication and encryption, while leaving the CPU free to handle application tasks. The multiple low-power modes with retention enable quick startup from sleep and minimum energy spent to perform periodic tasks.

- SmartRF transceivers: The CC2420 and CC2520 are true single-chips 2.4 GHz IEEE 802.15.4-compliant RF transceiver designed for low power and low voltage wireless applications, enabling through serial peripheral interface (SPI) interface connectivity in MCUs that do not provide it natively. Extensive hardware support for packet handling, data buffering, burst transmissions, data encryption, data authentication, clear channel assessment, link quality indication and packet timing information are included in the chip.

- Development Platforms: SmartRF05EB, SmartRF06EB offer support for the two MCU described before providing hardware that enables the fast development of IoT solutions. The SmartRF06 Evaluation Board is designed to the CC2538 and other evaluation module (EM) from the same family, providing an integrated XDS100v3 debug probe that allows the download and debugging of software on the CC2538 SoC. This debugger is supported by several integrated development environments (IDEs) such as IAR Workbench and Keil for Arm Cortex-M.

#### 2.2.2 Microsemi SmartFusion2

The FPGA market is accounted for USD 63.05 billion in 2017 and growing at a fast pace, being expected to reach USD 117.97 billion by 2026 [82]. This ebullient market offers a variety of solutions from different suppliers and targets the specificities of a wide range of scenarios. Therefore, a variety of development boards could have been considered to fulfil the requirements stated for low-end IoT devices. From Microsemi, was considered the PolarFire and IGLOO2 FPGA Families [83,84], but both failed in provide a hard-core MCU. The same fact is observed in the LatticeXP2 [85], where only a soft-core can be included. From Xilinx, the Zynq-7000 series comes with an Arm Cortex-A9 [86] that is not appropriated for a low-end device. The low-cost family from Altera the Cyclone V [87] includes also an Arm Cortex-A9, what for the previous reason does not fulfil the requirements specified before. Nevertheless, Microsemi produces the SmartFusion2 [88], a powerful FPSoC that combines an Arm Cortex-M3 MCU and FPGA fabric with power efficiency, exceptional reliability and proven security. This SoC is included in the SmartFusion2 Security Evaluation Kit [89], and provides an

easy and secure platform for the development of cost-optimized designs suiting perfectly the stated hardware requirements.

Figure 2.4: SmartFusion2 Security Evaluation Kit.

This platform includes 90K logic elements (LE) in the FGG484 package (M2S090TS-FGG484), a hard-core up to 166 MHz Arm Cortex-M3 processor, 64 Mb SPI Flash memory and 512 Mb on-board low-power double data rate (LPDDR) static random-access memory (SRAM). Is strengthened with industry-required high-performance communication interfaces such as PCI Express Gen2, fullduplex Serializer/Deserializer (SerDes), RJ45 for 10/100/1000 Ethernet and JTAG/SPI programming interfaces. The board capabilities are extended with embedded trace macrocell (ETM), embedded static random-access memory (eSRAM), embedded non-volatile memory (eNVM), and an extensive cluster of peripherals including CAN, TSE, USB, inter-integrated circuit (I2C), SPI and universal asynchronous receiver-transmitter (UART).

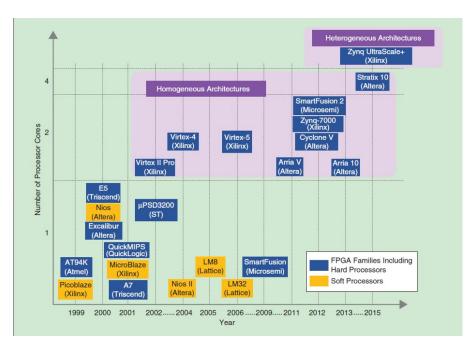

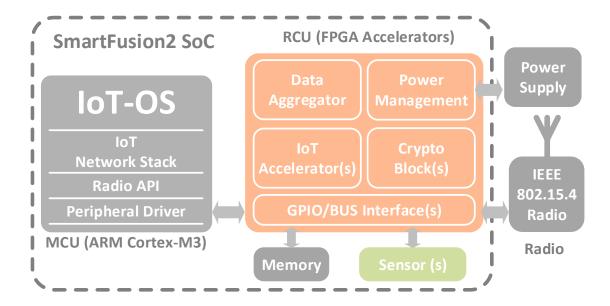

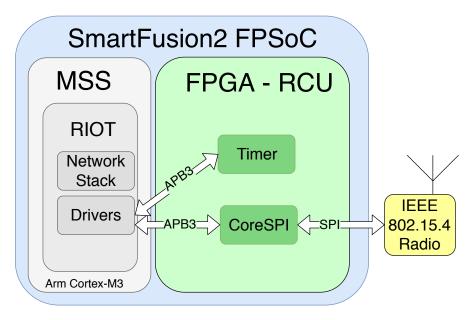

The SmartFusion2 brings to market a total power reduction of approximately 20% to 40% with a typical standby power consumption of 7mW. Improves security with implementation of protection against overbuilding and cloning, and secure boot for both the FPGA and processor. It enables data security by providing elliptic curve cryptography (ECC), SRAM-physically unclonable function (PUF), random number generator (RNG), advanced encryption standard (AES), secure hash algorithms (SHA), differential power analysis (DPA) and by implementing anti-tamper measures. It offers an exceptional reliability for safety critical and mission critical systems through the provision of single event upset (SEU) immune Zero FIT Flash FPGA configuration. More architecture highlights include