# Accelerating Genomic Sequence Alignment using High Performance Reconfigurable Computers

by

Peter Leonard McMahon

Submitted to the Department of Computer Science in fulfillment of the requirements for the degree of

Master of Science in Computer Science

at the

UNIVERSITY OF CAPE TOWN

October 2008

Supervisor: Dr Michelle Kuttel

Advisor: Prof. Yun Song, Computer Science Division, University of California, Berkeley.

#### Abstract

Reconfigurable computing technology has progressed to a stage where it is now possible to achieve orders of magnitude performance and power efficiency gains over conventional computer architectures for a subset of high performance computing applications. In this thesis, we investigate the potential of reconfigurable computers to accelerate genomic sequence alignment specifically for genome sequencing applications.

We present a highly optimized implementation of a parallel sequence alignment algorithm for the Berkeley Emulation Engine (BEE2) reconfigurable computer, allowing a single BEE2 to align simultaneously hundreds of sequences. For each reconfigurable processor (FPGA), we demonstrate a 61X speedup versus a state-of-the-art implementation on a modern conventional CPU core, and a 56X improvement in performance-per-Watt. We also show that our implementation is highly scalable and we provide performance results from a cluster implementation using 32 FPGAs.

We conclude that reconfigurable computers provide an excellent platform on which to run sequence alignment, and that clusters of reconfigurable computers will be able to cope far more easily with the vast quantities of data produced by new ultra-highthroughput sequencers.

# Contents

| 1                                                   | Introduction                                   |                              |                                                              |    |  |  |  |  |  |

|-----------------------------------------------------|------------------------------------------------|------------------------------|--------------------------------------------------------------|----|--|--|--|--|--|

|                                                     | 1.1 Background                                 |                              |                                                              |    |  |  |  |  |  |

|                                                     | 1.2                                            | Objec                        | tives                                                        | 4  |  |  |  |  |  |

|                                                     | 1.3                                            | 3 Thesis Outline and Summary |                                                              |    |  |  |  |  |  |

| <b>2</b>                                            | Background                                     |                              |                                                              |    |  |  |  |  |  |

|                                                     | 2.1                                            | Recon                        | figurable Computing                                          | 8  |  |  |  |  |  |

|                                                     |                                                | 2.1.1                        | Advantages of Reconfigurable Computers                       | 9  |  |  |  |  |  |

|                                                     |                                                | 2.1.2                        | Measuring the Performance of Reconfigurable Computing Sys-   |    |  |  |  |  |  |

|                                                     |                                                |                              | tems                                                         | 11 |  |  |  |  |  |

|                                                     |                                                | 2.1.3                        | The Berkeley Emulation Engine 2                              | 11 |  |  |  |  |  |

|                                                     |                                                | 2.1.4                        | BORPH: A Reconfigurable Computing Operating System           | 12 |  |  |  |  |  |

|                                                     | erating Applications by Exploiting Parallelism | 16                           |                                                              |    |  |  |  |  |  |

| 2.3 Sequence Alignment                              |                                                |                              |                                                              |    |  |  |  |  |  |

|                                                     |                                                | 2.3.1                        | The Needleman-Wunsch Algorithm                               | 20 |  |  |  |  |  |

|                                                     |                                                | 2.3.2                        | The Smith-Waterman Algorithm                                 | 21 |  |  |  |  |  |

|                                                     |                                                | 2.3.3                        | An Optimized Sequence Alignment Algorithm for Genome Re-     |    |  |  |  |  |  |

|                                                     |                                                |                              | sequencing Applications                                      | 23 |  |  |  |  |  |

| 3                                                   | $\mathbf{M}\mathbf{u}$                         | ltiple \$                    | Sequence Alignment Implementation on a Cluster Recon-        | -  |  |  |  |  |  |

|                                                     | figu                                           | Computer                     | <b>25</b>                                                    |    |  |  |  |  |  |

| 3.1 A Streaming Short-read Alignment Implementation |                                                |                              |                                                              |    |  |  |  |  |  |

|                                                     |                                                | 3.1.1                        | Wavefront Parallelism in Dynamic Programming Sequence Align- |    |  |  |  |  |  |

|                                                     |                                                |                              | ment                                                         | 26 |  |  |  |  |  |

|                                                     |                                                | 3.1.2                        | A Cell Update Processing Engine                              | 30 |  |  |  |  |  |

|                                                     |                                                | 3.1.3                        | A Stand-alone Single Alignment Implementation                | 36 |  |  |  |  |  |

|                                                     |                                                | 3.1.4                        | DRAM Interface for Reference Streaming                       | 41 |  |  |  |  |  |

|          | 3.2 A Parallel Multiple Short-read Alignment Implementation $\ldots$ . |                                          |    |  |  |  |  |

|----------|------------------------------------------------------------------------|------------------------------------------|----|--|--|--|--|

|          |                                                                        | 3.2.1 Round-robin FIFO Output Stage      | 43 |  |  |  |  |

|          | 3.3                                                                    | Parallelization Across Multiple FPGAs    | 46 |  |  |  |  |

| 4        | Results and Discussion                                                 |                                          |    |  |  |  |  |

|          | 4.1                                                                    | Single FPGA                              | 51 |  |  |  |  |

|          |                                                                        | 4.1.1 Correctness                        | 51 |  |  |  |  |

|          |                                                                        | 4.1.2 Short-read Length Resource Scaling | 52 |  |  |  |  |

|          |                                                                        | 4.1.3 Performance                        | 54 |  |  |  |  |

|          | 4.2 Cluster                                                            |                                          |    |  |  |  |  |

|          | 4.3                                                                    | Conclusion                               | 60 |  |  |  |  |

| <b>5</b> | Con                                                                    | clusions and Future Work                 | 62 |  |  |  |  |

# List of Figures

| 1.1  | A generic reconfigurable computer architecture                        | 3  |

|------|-----------------------------------------------------------------------|----|

| 2.1  | FPGA and CPU Performance Scaling.                                     | 10 |

| 2.2  | Contributions to Overall (Total) Application Time in a Reconfigurable |    |

|      | Computing System                                                      | 12 |

| 2.3  | BEE2 Architecture                                                     | 13 |

| 2.4  | BEE2 Board                                                            | 14 |

| 2.5  | BORPH Architecture.                                                   | 15 |

| 2.6  | BORPH Mapping to a BEE2.                                              | 16 |

| 2.7  | Simulink Design Flow for BEE2 and BORPH                               | 17 |

| 2.8  | A Model Systolic Array.                                               | 18 |

| 3.1  | "Wavefront Parallelism" in Dynamic Programming Sequence Alignment.    | 27 |

| 3.2  | Systolic Array for Streaming Parallel Sequence Alignment              | 29 |

| 3.3  | Data Dependencies in Antidiagonal Cell Update Computations            | 32 |

| 3.4  | A Cell Update Processing Engine (High Level).                         | 33 |

| 3.5  | Computation Stages in a Processing Engine                             | 34 |

| 3.6  | Subsystem to Compute $C(k-1, l-1) + \gamma(s_k, r_l)$                 | 35 |

| 3.7  | Subsystem to Compute Minimum of Three Values                          | 36 |

| 3.8  | Low-level Details of a Processing Engine                              | 37 |

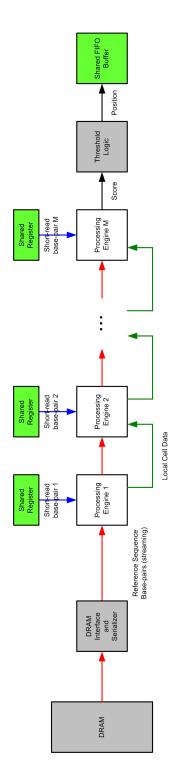

| 3.9  | A Stand-alone Single Alignment Design.                                | 39 |

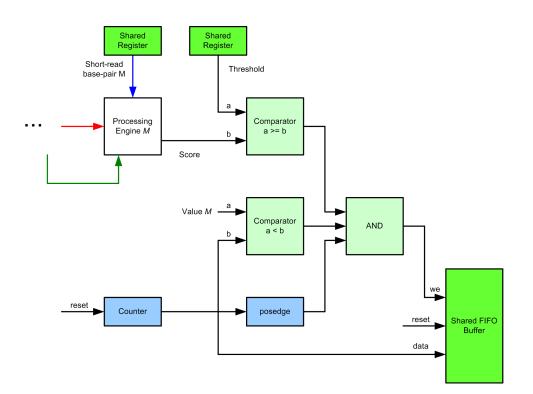

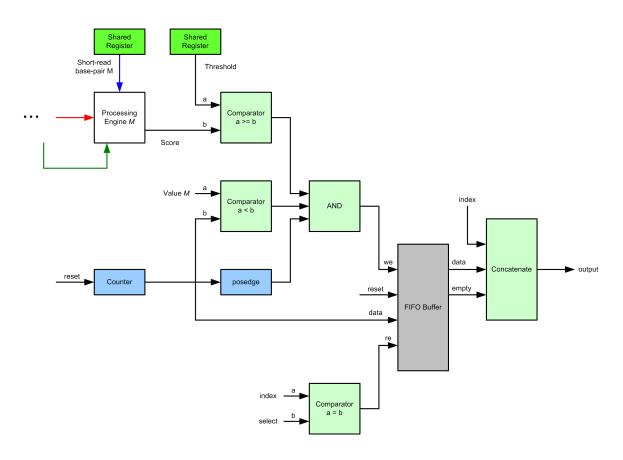

| 3.10 | Score Threshold and FIFO Buffer Output Stage                          | 40 |

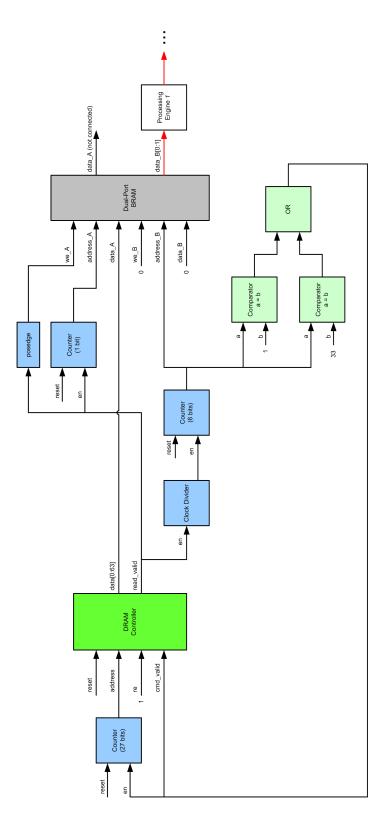

| 3.11 | DRAM Interface and Serializer                                         | 42 |

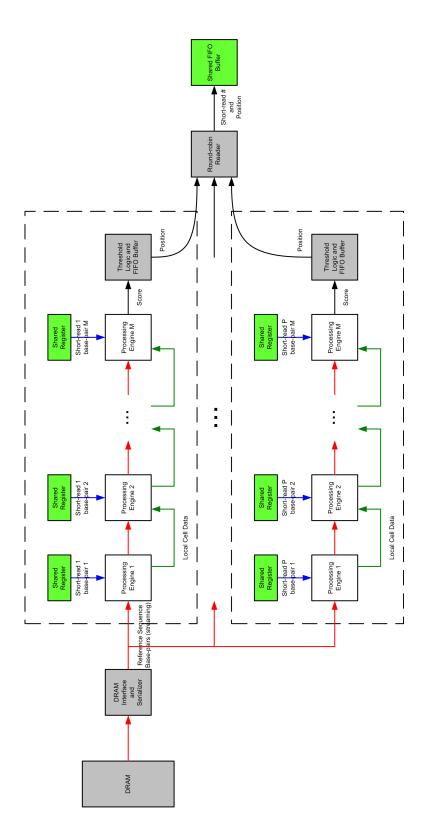

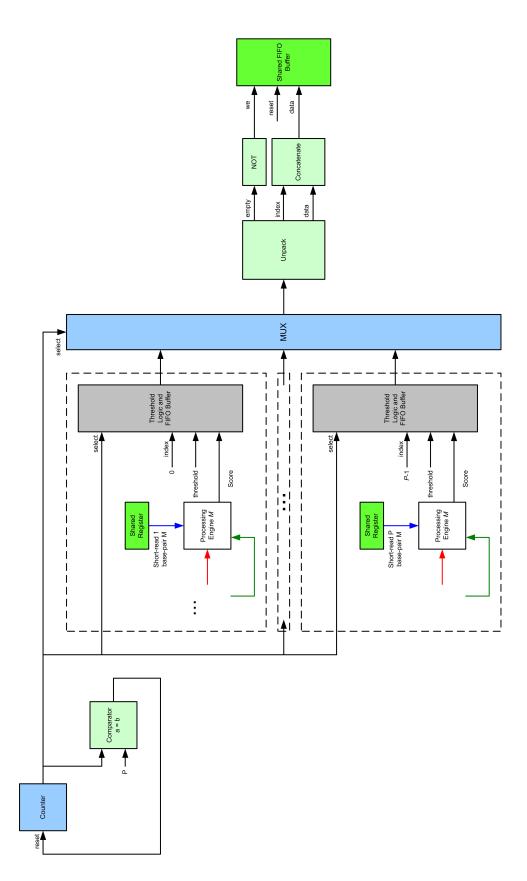

| 3.12 | A Parallel Multiple Alignment Design                                  | 44 |

| 3.13 | Score Threshold and FIFO Buffer Output Stage                          | 45 |

| 3.14 | Round-robin FIFO Reader and Shared FIFO Output Stage                  | 47 |

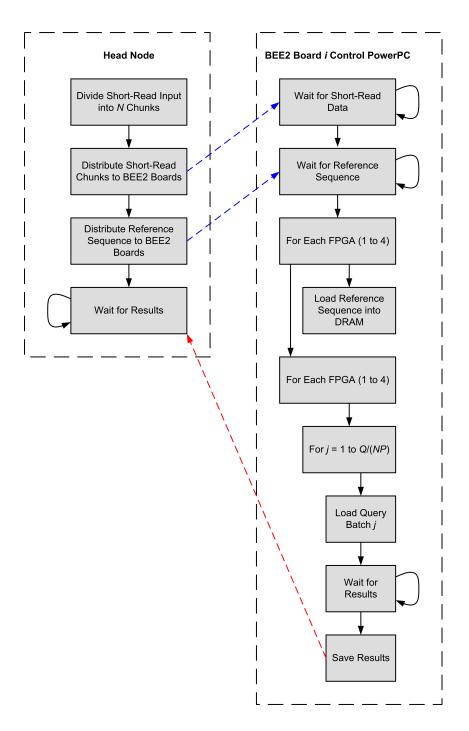

| 3.15 | BEE2 Cluster Architecture.                                            | 48 |

| 3.16 | Cluster Control Software Flow.                                        | 50 |

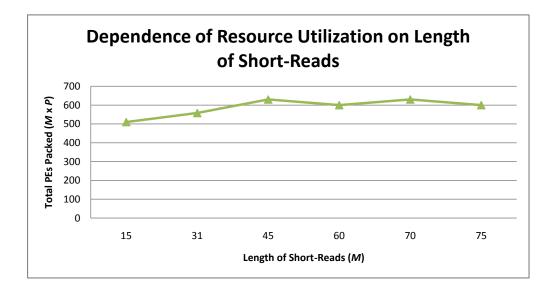

| Graph Showing Resource Utilization as a function of Short-Read Length |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| M                                                                     | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

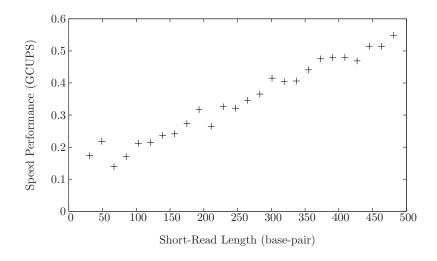

| Speed performance (in GCUPS) of Farrar's code as a function of short- |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| read length.                                                          | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| BEE2 Cluster                                                          | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                       | M.       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       . |

# List of Tables

| 4.1 | Dependence of resource utilization on the length ${\cal M}$ of short-reads | 54 |

|-----|----------------------------------------------------------------------------|----|

| 4.2 | Alignment Performance on a Single FPGA                                     | 57 |

To my teachers.

### Acknowledgements

The project described in this thesis has been a delight to work on, and I'm thrilled to have been involved in it. Foremost thanks goes to my project advisor at Berkeley, Prof. Yun Song, who was responsible for initiating and managing the bulk of the work that I present. This thesis happened by accident — it grew out of work I did for Yun part-time from September 2007 until April 2008. I initially aimed to "help out" with the development of a prototype design for sequence alignment, but I gradually became more involved, and my plan of spending a few days on the project turned into weeks, and then months. I had a great deal of fun learning about sequence alignment, and bioinformatics in general, from Yun during the course of my stay in Berkeley.

Dr Michelle Kuttel has been an excellent mentor to me for several years, so I was very pleased when the opportunity arose for me to work with her more formally. Michelle introduced me to parallel computing when I did a class project with her in 2004, and I've repeatedly used the knowledge I gained from that experience over the remainder of my university education. This thesis draws heavily on insights about parallel computing that I have learned from Michelle over the past few years. I'd also like to thank Michelle for being an excellent advocate for me in my dealings with the university bureaucracy, and for her very thorough reading of earlier drafts of this thesis.

I owe thanks to Prof. Michael Inggs in the Department of Electrical Engineering, Dr Alan Langman at the Karoo Array Telescope (KAT) project, and Dr Dan Werthimer at the Center for Astronomy Signal Processing and Electronics Research (CASPER) at the University of California, Berkeley for their support of me during this thesis. As I have mentioned, this thesis happened as an accident — the reason I was in Berkeley during 2007, and early 2008, was to work on radio astronomy instrumentation for KAT in the CASPER group, so without this official objective, I would never have had the opportunity to do my unofficial work on the sequence alignment project. I owe Dan special thanks for hosting me in Berkeley for 11 months, and for introducing me to much of the reconfigurable computing technology that I use in this thesis.

At Berkeley I worked closely with Henry Chen, Terry Filiba and Vinayak Nag-

pal on this project. Their contributions during our weekly meetings with Yun were invaluable. Henry deserves special mention for the many hours he spent with me helping me learn the Simulink toolflow. Kristian Stevens at the University of California, Davis, was responsible for the conception of the project, and the optimized alignment algorithm, and I'm glad to have worked with him.

Alex Krasnov, from the Berkeley Wireless Research Center<sup>1</sup>, provided several useful ideas (including his suggestion of pipelining the design to obtain greater throughput), but I'm also indebted to him for his very generous help in setting up and teaching me how to operate his BEE2 cluster. Having worked next to Alex for several months, I appreciate how much time and effort (from both him and Dan Burke) went into creating the cluster.

During the course of this project, I solicited and received help from several researchers in the BEE2 community. I'm grateful to Fred Burghardt, Dan Burke, Chen Chang, Greg Gibeling, Jason Manley, Arash Parsa, Brian Richards and Hayden So for their assistance and advice.

Prof. Scott Hazelhurst from the University of the Witwatersrand provided several useful suggestions in his examiner's report, which I have incorporated into this thesis. I thank him for his very comprehensive assessment. Dr Craig Steffen from the University of Illinois at Urbana-Champaign, and Prof. Cathal Seighe from UCT also provided helpful comments on my writeup.

During my Masters I've had excellent administrative support from Regine Lord at UCT, Lee-Ann Bredeveldt and Niesa Burgher at KAT, and Stacey-Lee Harrison at the UCT Postgraduate Funding Office.

I thank my friends and family for their support.

The work in this thesis has been generously supported by the National Research Foundation in the form of a KAT Masters bursary, an NRF M.Sc. Scarce Skills Prestigious SET bursary, KAT travel funding, UCT Postgraduate Funding Office

<sup>&</sup>lt;sup>1</sup>The BWRC is a research centre within the Department of Electrical Engineering and Computer Sciences at the University of California, Berkeley.

support, and U.S. National Science Foundation Grant No. 0619596 and Infrastructure Grant No. 0403427.

### Contributions

The work reported in this thesis had several contributors. In this section, I aim to describe specifically the contributions that I made, and mention who was responsible for the other work that enabled the developments detailed in this thesis.

Prof. Yun Song and Kristian Stevens were responsible for the project idea and the development of the optimized alignment algorithm. Henry Chen, Terry Filiba, Vinayak Nagpal and I met regularly with Prof. Song, and at these meetings Henry, Terry and Vinayak contributed many helpful ideas about overcoming limitations in the tools, and increasing the efficiency of the implementation.

I was responsible for the development of the sequence alignment algorithm implementation for the BEE2. I developed a scalable, lightweight streaming architecture, and verified the functionality of a parallel implementation of 10 simultaneous short-read alignments on a single FPGA. I built the DRAM controller/serializer that streams reference data through the processors. I developed the infrastructure to run alignments on several FPGAs simultaneously, and then to operate on several BEE2s simultaneously.

Henry was responsible for overcoming a limitation<sup>2</sup> in Xilinx System Generator to extend the number of simultaneous alignments to beyond<sup>3</sup> 10.

Terry wrote the optimized SSE CPU code against which the FPGA results are measured.

Alex Krasnov and Brian Richards showed us how to find the minimum of three

<sup>&</sup>lt;sup>2</sup>The limitation was that Xilinx System Generator had an inefficient means of converting Simulink blocks to hardware description language, and as a result there was a practical upper limit on how many blocks in a diagram could be converted. We needed to exceed that limit.

<sup>&</sup>lt;sup>3</sup>With a short-read length of 31 base-pairs, we were able to fit 18 alignment processors onto a single FPGA, thanks to Henry's work.

values in the most efficient way possible.

# Chapter 1

# Introduction

This thesis investigates the extent to which reconfigurable computing technology can be employed to address the computing challenges associated with new ultra-highthroughput genome sequencing technologies. Specifically, we investigate the performance of an optimized parallel sequence alignment algorithm implemented on a modern reconfigurable computer. In this introduction, we provide a brief background to and motivation for this investigation, provide details of the objectives, and outline the content of the thesis.

### 1.1 Background

One of the central goals of molecular genetics is the determination of the genetic basis of human disease. Considerable progress has been made in this regard in recent years; most notably the publication of the human genome in 2001 [1, 2], an effort that took two decades to complete. However, new genome sequencing technology is becoming available (for example, from Illumina [3]; see refs. [9, 10] for a technical discussion) that will dramatically reduce the amount of time it takes to produce sequence data from a sample of DNA. These advances will allow studies of human variation at the genetic level [4]. Such studies hold great promise for enabling important discoveries in determining which nucleotides and genes in the human genome hold information about human susceptibility to particular diseases.

There are considerable computing challenges [10] associated with the new sequencing products that arise due to the huge volumes of data that these machines produce. The human genome consists of approximately 3 billion base-pairs<sup>1</sup>. The most expensive computational task in genome sequencing (using the dominant Whole Genome Shotgun Sequencing technique [7, 8]) is the alignment of short<sup>2</sup> fragments of the genome being sequenced against a reference genome. There may be hundreds of million of such fragments that need to be aligned in order to sequence a single genome. Current approaches to this problem using conventional computers may take tens to hundreds of thousands of CPU hours to complete the alignment requirements for the sequencing of a single human genome [1, 10, 11]. Even large cluster computers with thousands of CPUs may take several weeks to complete the necessary computations. Heuristic approaches, such as BLAST [6], reduce the computational burden, but result in a reduction in accuracy. Details of the dynamic programming-based algorithm that we used are contained in Section 2.3.3.

We have stated that genome sequencing is both an important application, and one that requires vast computational resources. The technology we use in this thesis to tackle this problem is *reconfigurable computing* [12]. A reconfigurable computer is a class of computer that includes a special-purpose processor that can perform specific tasks far more efficiently than a general-purpose processor can, but that is also reconfigurable. It is easy to see how a special-purpose processor can be designed to implement a particular algorithm far more efficiently than is possible using a von Neumann-architecture system. There exists a technology that enables us to build custom, special-purpose processors that can be reconfigured (i.e. reprogrammed) – "Field Programmable Gate Arrays" (FPGAs). FPGA processors provide the flexibility of software and the efficiency of Application Specific Integrated Circuits (ASICs)<sup>3</sup>. FPGAs were invented in 1984 [19], but, until recently, they have not had the required computational resources to compete with CPUs in the arena of high performance computing — their traditional use is to act as "glue logic" on electronic circuit boards, to connect I/O and components, rather than performing the bulk of the necessary computation (which is typically done by microprocessors or specialized digital sig-

<sup>&</sup>lt;sup>1</sup>A "base-pair" can be thought of as a character from the alphabet  $\Sigma = \{A, G, C, T\}$ , and can hence be stored using  $\log_2 |\Sigma| = \log_2 4 = 2$  bits.

$<sup>^{2}</sup>$ Short-read lengths from current sequencing technology range between 10 and 100 base-pairs.

<sup>&</sup>lt;sup>3</sup>It is not actually accurate to claim that FPGAs give the same efficiency as ASICs, since FP-GAs contain a large amount of interconnect to allow for reconfigurability that ASICs do not have. However, FPGAs do provide a comparable level of efficiency versus general-purpose CPUs to that which ASICs provide.

nal processing chips). Proofs-of-concept for FPGA-based reconfigurable computers existed as early as 1990 [45]. However, although projects such as SPLASH [45] and SPLASH 2 [46] successfully demonstrated the concept, the FPGA technology was not yet competitive with CPUs. The first commercially viable reconfigurable computing companies began circa 1996 [47], and more have appeared as FPGA technology has steadily improved.

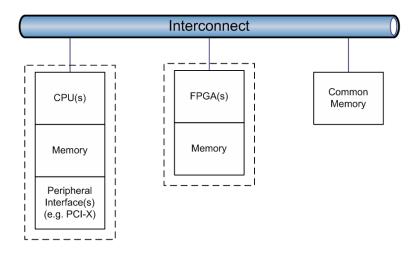

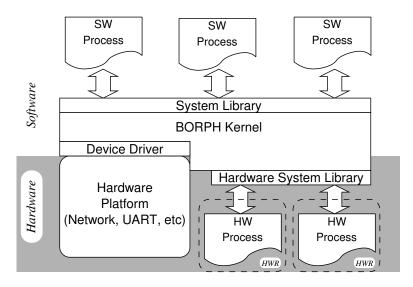

Modern reconfigurable computers typically contain one or more FPGAs and a conventional CPU. The CPU is used to perform control tasks and operations that do not account for a significant percentage of the overall computation time. The CPU is typically used to run an operating system and associated services. Figure 1.1 shows a generic reconfigurable computer architecture. The CPU, FPGA and memory are all connected to a bus, over which the various devices can communicate. A common memory is a mechanism for allowing high-bandwidth communication between the CPU and FPGA. For example, the CPU might pre-process a portion of data and place it in the common memory. The FPGA can then process that data, and write the results back to the common memory, from where the CPU can obtain them.

Figure 1.1: From [41]. A generic reconfigurable computer architecture.

The central challenge in porting applications to reconfigurable computers is the development of efficient FPGA designs that make the best use of the available resources. FPGA designs have traditionally been created using hardware description languages such as VHDL [48] and Verilog [49], which are well-suited to traditional digital design tasks, but are difficult languages in which to express scientific computing algorithms. However, with the considerable increases in FPGA computational capacity that have occurred in recent years, and the subsequent commercial interest in reconfigurable computing, there has been a drive to produce tools for programming FPGAs that are more usable by developers who do not have experience with digital design.

The reconfigurable computing industry now claims successes in various applications areas, including financial modelling [31], bioinformatics [32] and oil and gas exploration (seismic data analysis) [33], amongst others. Of particular relevance to this thesis is the review by Hasan et al. [58] that summarizes recent achievements in Smith-Waterman sequence alignment on modern reconfigurable computers.

In this thesis, we build a sequence alignment implementation for the Berkeley Emulation Engine (BEE2) [14] reconfigurable computer using a tool chain that is based on the MATLAB Simulink graphical programming language [16, 17].

### 1.2 Objectives

The objective of this work was to investigate the performance benefits that can be gained in genomic sequence alignment for resequencing applications with reconfigurable computing technology. Specifically we aimed to:

- 1. Implement an optimized parallel sequence alignment algorithm on a BEE2 reconfigurable computer.

- 2. Extend this single FPGA alignment implementation to an implementation for a cluster reconfigurable computer.

- 3. Analyze the performance of the reconfigurable computer implementation over state-of-the-art software implementations.

The first requirement was to gain familiarity with the BEE2 platform and its associated development tools. Next, we aimed to implement a single sequence alignment custom processing engine. This would then need to be extended to a parallel alignment engine capable of aligning multiple sequences simultaneously. Once the single FPGA parallel alignment implementation was ready, this would be extended to a many-FPGA environment (e.g. a cluster of reconfigurable computers). Finally, we aimed to make an accurate appraisal of the performance of our implementation versus the most efficient alignment implementations for multi-core CPUs currently available.

### **1.3** Thesis Outline and Summary

This thesis is organized as follows:

Chapter 2 provides an introduction to reconfigurable computing, the BEE2 platform, and sequence alignment algorithms. We give an overview of acceleration techniques relevant to sequence alignment. We also present details of an optimized sequence alignment algorithm designed specifically for genome re-sequencing, which is the algorithm we implemented in this thesis.

Chapter 3 presents our implementation of the parallel sequence alignment algorithm on a single FPGA. This implementation is able to simultaneously align tens of short-reads against a reference genome. We give details of the operation of a single alignment processing engine, and of the efficient extension to multiple engines. We discuss our DRAM interfacing mechanism for streaming reference genome data from onboard memory, and our scheme for communication results to the control CPU<sup>4</sup>. We provide performance results, and make comparisons to equivalent software implementations. We also present the extension of our single-FPGA implementation to multiple FPGAs, and further to multiple BEE2 boards in a cluster.

Chapter 4 presents scaling, performance and power results for both our single FPGA and multiple FPGA implementations. We show that our architecture is scalable over a wide range of short-read lengths. We provide performance results from both our single FPGA implementation and from two highly optimized software implementations, and show that a single FPGA can achieve a 61X speedup over a single modern CPU core. We demonstrate that our cluster implementation scales linearly with the number of FPGAs, and show power consumption results that reveal a 56X improvement in performance-per-Watt in the FPGA implementation.

<sup>&</sup>lt;sup>4</sup>The BEE2 runs Linux on an embedded PowerPC in the "Control FPGA". This CPU is used for control – loading programs, changing settings, and monitoring status.

Chapter 5 concludes this thesis, and provides some further analysis of the impact that reconfigurable computers can have on genome sequencing. Projected speedups for sequence alignment using current and near-future FPGA devices are also given.

The contributions of this thesis can be summarized as follows. To our knowledge, we have presented the first use of FPGAs for aligning, in parallel, multiple short sequences against a common long sequence using a dynamic programming-based algorithm. We have also presented the first implementation of and performance results from a new alignment algorithm that is optimized for short-read alignment in resequencing.

# Chapter 2

# Background

This thesis applies the technology and techniques of reconfigurable computing to the problem of sequence alignment. This chapter attempts to provide sufficient background in both areas such that bioinformatics experts can appreciate the reconfigurable computing implementation aspects, and those in the hardware acceleration community can follow the algorithmic aspects. Entire books have been written on both fields, so we can't hope give a comprehensive treatment of either in this chapter. We have provided several standard references that the interested reader can pursue. A comprehensive review of modern reconfigurable computing technology and techniques is available in [21], including several application case-studies.

In recent years, much attention has been given to acceleration of high performance computing applications using inherently parallel architectures. The creation of research centres such as Berkeley's Parallel Computing Laboratory [25] and Stanford's Pervasive Parallelism Laboratory [26] indicates that multicore processors will play a large role in the future. However, there has also been a resurgence of interest in other parallel computing techniques. Most prominent is the use of Graphics Processing Units (GPUs) to perform general-purpose computations [50]. Modern GPUs are effectively programmable many-core processors, albeit with many restrictions (particularly relating to memory hierarchy and arithmetic logic unit functionality) that are a legacy of their former exclusive use in graphics processing. IBM's multi-core Cell processor [51] is another entry into the field that provides yet another alternative parallel architecture for high performance computing applications.

Modern parallel computing technologies can generally be divided into two cat-

egories: replacement processors, and accelerators. Multi-core CPUs from Intel and AMD, and IBM's Cell processors, are intended as general-purpose CPUs that can run as standalone computing engines. Accelerators are designed to complement, rather than replace, existing CPU architectures. For example, GPUs are typically intended only to augment the processing capability of x86 or x64 microprocessor-based machines. In a common usage scenario with a CPU/GPU machine, the CPU stills runs the operating system and much of the application code, but the GPU is used where it can significantly outperform the CPU in operations that constitute a major fraction of the running time of a particular program. For example, if some application makes frequent calls to a Fast Fourier Transform routine, the FFT may be executed on the GPU, since the GPU can perform the FFT computation faster than the CPU can. Reconfigurable computers typically fall into the category of accelerator-based systems: a conventional CPU is paired with one or more FPGAs, which act as accelerators.

### 2.1 Reconfigurable Computing

The concept of a reconfigurable computer was initially proposed by Estrin [22, 23] in 1960. He proposed the development of a machine that contained a regular processor and an array of reconfigurable special-purpose processors. These special-purpose processors would provide excellent performance for the tasks they were tailored to do, but, importantly, could be easily reconfigured to implement different algorithms depending on the program that the computer was running.

It is easy to see how special-purpose hardware could provide more efficient computations than general-purpose processors. However, it was not until the invention of Field Programmable Gate Arrays in the 1980s that a technology existed with which it was possible to build special-purpose processors in hardware, and to be able to reconfigure the hardware for different tasks<sup>1</sup>. The development of the first gener-

<sup>&</sup>lt;sup>1</sup>Application-Specific Integrated Circuits (ASICs) have long been used in single-application devices, such as cellular phones, digital cameras and suchlike, where performance and power efficiency are critical, the tasks it performs are known *a priori*, and there are sufficient volumes to justify the development of a custom chip. However, ASICs are not reprogrammable. FPGAs can, in some sense, be thought of as reprogrammable ASICs, and indeed the computer-aided design tools used

ation of reconfigurable computers occurred in the early 1990s, with projects such as SPLASH [45] and Splash 2 [46]. However, although these projects successfully demonstrated the concepts of reconfigurable computing, FPGA technology had not yet progressed to a point where reconfigurable computers were competitive with contemporary general-purpose microprocessors, let alone the supercomputers of the day.

#### 2.1.1 Advantages of Reconfigurable Computers

In recent years, reconfigurable computing has acquired renewed popularity. This has been driven by many factors – the most important of which are the dramatic increases in the capabilities of modern FPGAs, and the fact that the clock frequencies of general-purpose microprocessors look unlikely to increase much beyond 3GHz. The latter is a result of the so-called "power wall", which provides a practical, physical limit to how much faster we can expect CPUs to run given cooling constraints [20]. This has led to the realization that computing faces a major challenge in moving wholesale to parallel computing, since almost all performance increases in the foreseeable future are likely to come from exploiting parallelism rather than relying on increased clock frequencies. The "Berkeley View" technical report [24] has been a popular call-to-arms to try to address these challenges. However, since FPGAs can be used to exploit parallelism at a much finer-grained level than is possible with multicore CPUs, reconfigurable computing has become an ever-more attractive proposition, or at least one that now warrants serious investigation to determine which problems can be more effectively solved on such machine architectures.

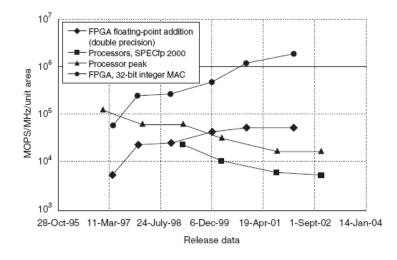

The computational density of FPGAs has improved over CPUs over the past several years, as shown in Figure 2.1. Now that CPU frequency increases can no longer be counted on, the metric of "performance per MHz" has increased in importance. FPGAs offer vastly superior theoretical integer arithmetic performance over CPUs. Of course, just as the "theoretical peak performance" of a CPU is not obtainable in typical applications, so too is it unusual for an application to be able to harnass the full computational power of an FPGA. Nevertheless, the orders-of-magnitude advantage that FPGAs have over CPUs in integer arithmetic density make them promising candidates for investigation of the performance it is possible to achieve in

by the ASIC and FPGA user communities are often very similar.

practice. To illustrate, the Xilinx Virtex 5 SX240T chip contains over 1000 multiplyand-accumulate units, each clockable at up to 550MHz [27]. This yields a peak performance of over 580 billion integer operations per second (580 GOPS). In comparison, the current fastest Intel CPU, the Intel Core 2 Extreme Quad-Core 3.2GHz chip, has a theoretical peak performance of 97 GOPS [28].

Figure 2.1: From [14]. FPGA and CPU Performance Scaling. Integer arithmetic on FPGAs now significantly outperforms CPUs per unit area and frequency.

However, theoretical peak performance is not the only metric of interest to high performance computer designers. Power performance is also an important consideration – in large HPC systems, power consumption and the associated cooling requirements are significant design factors. FPGAs are clocked at far lower frequencies than CPUs (an FPGA is typically clocked at less than 500MHz, whereas modern CPUs are clocked at between 2GHz and 3.5GHz). This leads directly to a significant difference in power consumption, since power consumption is proportional to the operating frequency [20]. Further, the performance of a system with a particular application is increasingly limited by the memory bandwidth available to the chip, rather than the theoretical peak arithmetic performance. This has lead to the so-called "memory wall" phenomenon [20], whereby performance is limited by the speed at which data can be inputted to and outputted from the processor. FPGAs have a benefit over CPUs in this area too, since modern FPGAs contain many I/O pins. The largest Virtex 5 has over 1700 pins, with 960 dedicated to high-speed serial I/O. Major industry vendors such as Cray, SGI and HP now have products including FPGA accelerators, and many smaller hardware vendors have now also appeared on the market, such as SRC, Nallatech, DRC and XtremeData. Reconfigurable computing is certainly not an established technology and at present it seems unlikely that it will achieve broad adoption. However, there has been sufficient success in specific application areas to suggest that FPGAs will have some role to play as accelerators in high performance computing over the next decade. In the next section, we provide an overview of some competing approaches that may come to dominate the computer architecture landscale.

## 2.1.2 Measuring the Performance of Reconfigurable Computing Systems

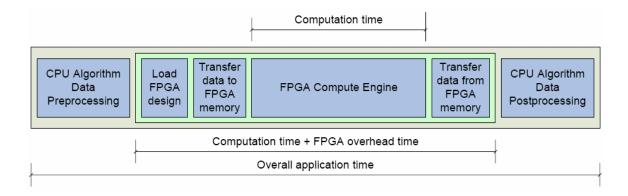

We use the approach of Kindratenko et al. [38] to measure the performance of applications on reconfigurable computing systems. In many applications the "overhead" of pre- and post-processing data, and transferring data between an FPGA and a CPU, is not insignificant, and hence needs to be taken into account. When using FPGAs as accelerators, the total application time depends on several factors besides the time spent by the FPGA performing its computation. Specifically, there is typically preprocessing of data in the CPU before it can be sent to the FPGA. There is time to load the FPGA design, and to then transfer the data to the FPGA. Once the FPGA has performed its computation, the results need to be transferred back to the CPU, and there is often a post-processing stage required before the CPU can use the data. This is illustrated in Figure 2.2.

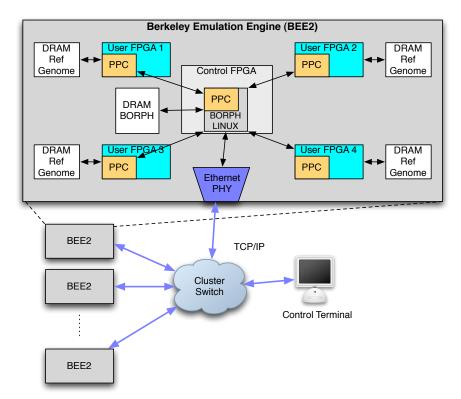

#### 2.1.3 The Berkeley Emulation Engine 2

The BEE2 project [14] developed a reconfigurable computing board design that contains five FPGAs per board, where each FPGA includes two embedded PowerPC microprocessors. The BEE2 system has been used by many groups as a testbed for research on reconfigurable computing and has had significant successes in various application domains, including radio astronomy signal processing [34], systems biology [35] and processor emulation [55]. Programmability has long been a concern for reconfigurable computers and the approach taken with the BEE2 was to allow

Figure 2.2: From [38]. Contributions to Total Computation Time in a Reconfigurable Computing System.

users to program the computer using a MATLAB Simulink-based graphical tool flow [16, 17, 18]. This works well compared to most other programming proposals, which typically rely on extensions (such as [13]) to fundamentally sequential languages to allow the programmer to express parallelism. The graphical tools also ease the learning curve for developers, over writing applications in hardware description languages such as VHDL and Verilog.

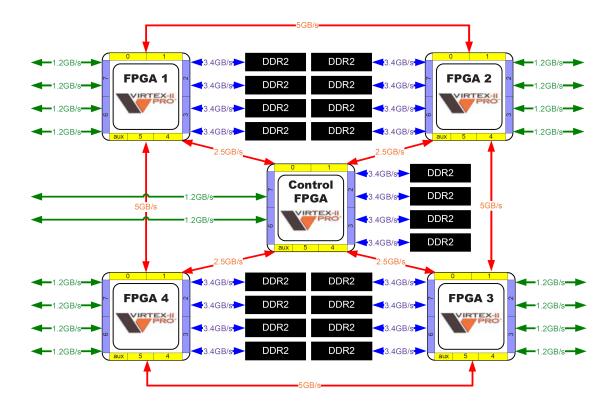

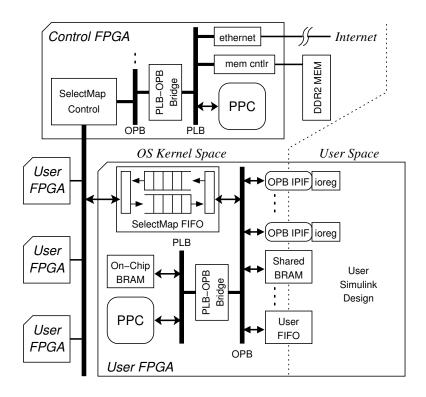

Figure 2.3 shows the high-level architecture of a BEE2 board. The four user FPGAs are each connected to the control FPGA using high-speed on-board links. There is also an on-board interconnect between adjacent user FPGAs. Each FPGA has four associated DRAM banks, which provides a significant amount of memory bandwidth to each chip. Also shown are the high-speed 10 gigabit Ethernet (10GbE) connections that are provided to allow the FPGAs to connect with other 10GbE devices, including other BEE2 boards. Figure 2.4 shows a photograph of a BEE2 board.

# 2.1.4 BORPH: A Reconfigurable Computing Operating System

BORPH [17, 18] is a Linux-based operating system designed to provide abstractions to users that allow reconfigurable computing platforms to be more easily used and programmed. BORPH's first target platform was the BEE2, and it has support for the BEE2's Simulink toolflow [16, 17, 18].

Figure 2.5 shows the high-level BORPH architecture. From a user's perspective,

Figure 2.3: From [15]. BEE2 Architecture.

the important feature to notice in this diagram is that BORPH uses the concept of a "hardware process". A hardware process refers to an FPGA design executing on an FPGA resource, which BORPH presents using a process abstraction. In BORPH, hardware processes behave in exactly the same way as software processes – the process appears in the process list, it is possible to redirect input and output to and from a process, it is possible to kill a process, and so on. BORPH manages the tasks associated with loading the FPGA design inside a "hardware executable" into a BEE2 user FPGA, and transferring data between the processor and the FPGA.

A further useful abstraction that BORPH provides is that of hardware resources in the FPGA. Specifically, it is possible to specify, at FPGA design time, that some registers and memories be "shared". When that FPGA design is loaded with BORPH, the "shared" FPGA resources are made available to the user as files in the /proc/ filesystem. It is therefore possible to interact with the FPGA design in BORPH purely by reading from and writing to files.

Figure 2.6 shows how BORPH operates on a BEE2. BORPH's software primar-

Figure 2.4: From [15]. BEE2 Board Photograph. The four user FPGAs and one control FPGA reside underneath the clearly visible black heatsinks. The DRAM slots (four per FPGA) and CX4 10GbE connectors (front of board) are also clearly visible.

ily executes on the PowerPC in the control FPGA. However, each user FPGA has a lightweight communications infrastructure that allows the control FPGA to communicate with it. BORPH uses the Xilinx SelectMAP bus [30] to reconfigure (reprogram) the user FPGAs as needed. An OPB bus within each FPGA is used to connect the "shared" resources in a particular design to the user FPGA PowerPC and hence ultimately to BORPH running on the control FPGA. BORPH performs all the necessary communications completely transparently.

Figure 2.5: From [18]. BORPH Architecture.

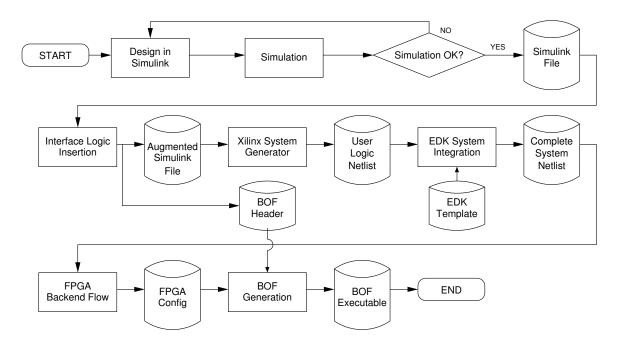

To provide the support for shared resources in BORPH, it is necessary that the Simulink toolflow, which produces user FPGA designs, provide some interface with which BORPH can interact. Therefore, the toolflow has some knowledge of BORPH's requirements built in. Figure 2.7 shows a flow diagram of the tasks in the Simulinkbased design environment. The user first describes his algorithm using the Simulink graphical design tool. Simulink provides a cycle-accurate simulator that lets the user fully debug his design before continuing. Once the design is ready, the toolflow can enter the "build" stage, in which it attempts to create an FPGA bitstream that implements the design described in Simulink. The first stage is the insertion of the interface logic that BORPH requires to communicate with resources that are marked in Simulink as being shared. The Xilinx System Generator product is then effectively used to generate hardware description language from the Simulink design. The Xilinx Embedded Development Kit is used to add support for the embedded PowerPC, and to appropriately connect the relevant buses. The Xilinx FPGA backend flow (ISE)

Figure 2.6: From [18]. BORPH Mapping to a BEE2.

creates a regular FPGA bitstream. Finally metadata about the design (such as the shared resources it contains) is added to the bitstream, and the result is a BORPH-executable file that will run as a hardware process.

# 2.2 Accelerating Applications by Exploiting Parallelism

Just as conventional computers are used in clusters by the high performance computing community, so too is it possible to build clusters of reconfigurable computers [55]. The same approaches to accelerating embarrasingly parallel programs that are used on CPU clusters [52] are equally applicable to reconfigurable computer clusters.

In order to outperform conventional CPUs, reconfigurable computers need to have FPGA designs that are efficient and that exploit parallelism. By "efficient", we mean that the number of clock cycles per algorithmic step should be as small as possible. The clock speed of a modern CPU is typically in the range 2–3GHz. The Virtex II Pro FPGAs on the BEE2 are clocked at 200MHz. Therefore reconfigurable com-

Figure 2.7: From [18]. Simulink Design Flow for BEE2 and BORPH.

puters have to overcome a 10X performance deficit just to reach parity with CPUs. Fortunately it is possible to produce FPGA designs that exploit the parallelism in the dynamic programming approach to sequence alignment, and to perform the requisite computations efficiently.

There is a considerable body of literature concerning parallel algorithms, and the mapping of applications to parallel architectures. Grama et al. [52] provide a comprehensive overview at an introductory level. In this thesis we are primarily concerned with two parallel computing concepts: *systolic arrays* and *embarrassingly parallel algorithms*.

The term "embarrassingly parallel" refers to computational problems where it is easy to decompose the computational load into self-contained subproblems that need little or no communication between them [29]; this is often called "wide" parallelism. Embarrassingly parallel problems are convenient problems to parallelize and they have excellent scalability – typically an embarrassingly parallel algorithm's performance will increase linearly with the number of processors used to execute it. This is in contrast to problems where communication between processors is necessary, which results in performance scaling being sublinear<sup>2</sup>. The problem of aligning many short-

<sup>&</sup>lt;sup>2</sup>In the worst cases, beyond a certain number of processors performance cannot be improved, or

reads against a reference sequence is embarround parallel in the sense that the alignment of each short-read is an independent computational problem.

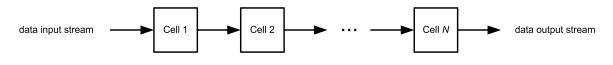

Systolic arrays are a type of parallel architecture in which the processing task is divided amongst several (typically identical) processors in an array; systolic arrays exploit "deep" parallelism. Systolic arrays are characterized by the feature that the data flows synchronously across the array. In the one-dimensional case, data may flow from left-to-right, with each cell receiving input data from its left neighbour and outputting data to its right neighbour, as is shown in Figure 2.8. The cells operate independently of each other, with the exception of the data connections with their neighbours. Systolic arrays provide a convenient method for improving the time complexity of an algorithm at the expense of computational resources (FPGA fabric, in the case of reconfigurable computers). A big advantage of systolic arrays is that they are inherently scalable due to their use of only local connections between cells. In this thesis we use a systolic array design to implement a sequence alignment algorithm.

Figure 2.8: A Model Systolic Array.

### 2.3 Sequence Alignment

The general sequence alignment problem is a type of string matching and alignment problem [59]: given two strings,  $r = r_1 r_2 \dots r_N$  and  $s = s_1 s_2 \dots s_M$ , we want to find the minimum number of (weighted) steps required to transform s into r (or, equivalently, r into s). The possible edits to s are: insertion of new characters, deletion of characters, and substitutions of characters. Typically, we are interested in assessing the similarity between two sequences; the number of edits is a measure of similarity. In this thesis, we are concerned with genomic sequences, which are strings over the alphabet  $\Sigma = \{A, G, C, T\}$ , i.e.  $r_x \in \Sigma$  and  $s_y \in \Sigma$  where  $x = 1, \dots, N$  and  $y = 1, \dots, M$ . Sequence alignment is also routinely performed on protein sequences, which have a

there are severly diminishing returns as you add processors.

different, larger alphabet.

Edits to s may be weighted, so as to prefer one type of edit (e.g. insertions) over another type (e.g. deletions). When assessing a proposed transformation of s to r, we assign integer penalties to each edit:  $\alpha$  for deletions in s,  $\beta$  for insertions in s, and  $\gamma$  for modifications of characters in s.  $\alpha$  and  $\beta$  are constants, but  $\gamma$  may be a function of the character substitution (i.e. character mismatch). We can define the following matrix  $\Gamma$  to specify mismatch penalties:

$$\Gamma = \begin{array}{ccc} A & G & C & T \\ & A \\ & & & \\ G \\ & & C \\ & T \end{array} \begin{pmatrix} \delta_{AA} & \delta_{AG} & \delta_{AC} & \delta_{AT} \\ \delta_{GA} & \delta_{GG} & \delta_{GC} & \delta_{GT} \\ \delta_{CA} & \delta_{CG} & \delta_{CC} & \delta_{CT} \\ \delta_{TA} & \delta_{TG} & \delta_{TC} & \delta_{TT} \end{pmatrix}$$

The matrix elements  $\delta_{XY}$  are integers, and correspond to the penalties of the character X transforming into character Y. If the penalty scheme is negative (i.e.  $\alpha$  and  $\beta$  are negative, and the best alignment is that which has the highest score), then typically  $\delta_{XY} < 0$  when  $X \neq Y$ , and  $\delta_{XY} \geq 0$  when X = Y. The latter case represents a character match, which should be rewarded.

To calculate the mismatch penalty for aligning two positions in the strings s and r, you can perform a simple lookup in the penalty matrix  $\Gamma$ , using the character in s to select the row, and the character in r to select the column. Hence, if you wish to align the *i*th character in string s against the *j*th character in string r, you can compute the penalty  $\gamma(s_i, r_j)$  as  $\gamma(s_i, r_j) = (\Gamma)_{f(s_i)f(r_j)}$  where  $f : \Sigma \to \mathbb{N}$  is defined as the mapping from characters to (identical) row and column indices in  $\Gamma$ :

$$f(x) = \begin{cases} 0 & \text{if } x = \mathbf{A} \\ 1 & \text{if } x = \mathbf{G} \\ 2 & \text{if } x = \mathbf{C} \\ 3 & \text{if } x = \mathbf{T} \end{cases}$$

For example, if the character  $s_i$  is **G** and the character  $r_j$  is **T**, then the penalty is computed as  $\gamma(s_i, r_j) = \gamma(\mathbf{G}, \mathbf{T}) = (\Gamma)_{f(\mathbf{G})f(\mathbf{T})} = (\Gamma)_{13} = \delta_{\mathbf{GT}}$ .

There are finitely many transformations of s to r, but an exhausive search of all

possible transformations results in an exponential time algorithm. Therefore to align long sequences, a different approach is needed.

#### 2.3.1 The Needleman-Wunsch Algorithm

The Needleman-Wunsch algorithm [36] is an application of dynamic programming<sup>3</sup> to the *global alignment* problem. Global alignment is the problem we have just discussed: the transformation of a sequence s to a sequence r.

To quantify the similarity between two sequences, we seek to compute a *similarity* score whose value is based on the optimal transformation of s to r. For each required deletion and insertion of characters in s, we apply a penalty. Furthermore, we apply a penalty whenever the characters in s and r do not match. We denote the deletion penalty as an integer  $\alpha$ , the insertion penalty as an integer  $\beta$ , and the mismatch penalty an integer  $\gamma(s_i, r_j)$  whose value is dependent on the specific mismatch that has occured.

As an example, following that in [60], let us set  $\alpha = -2$ ,  $\beta = -2$ , and  $\gamma(s_i, r_j)$  as:

$$\gamma(s_i, r_j) = \begin{cases} -1 & \text{if } s_i \neq r_j \text{ (mismatch)} \\ 1 & \text{if } s_i = r_j \text{ (match)} \end{cases}$$

When  $\alpha = \beta$ , we may refer to the insertion and deletion penalties simply as the *gap penalty* (which is the penalty for introducing a gap into either sequence, which can be interpreted as an insertion or deletion in s).

If we wish to align two sequences s = AAGCTCAGC and r = ACGGCTAGC, we can see that one potential alignment (with scores) is:

| s      | А  | А  | G  | —  | С  | Т  | С  | А  | G  | С  |     |

|--------|----|----|----|----|----|----|----|----|----|----|-----|

| r      | А  | С  | G  | G  | С  | Т  | _  | А  | G  | С  |     |

| score: | +1 | -1 | +1 | -2 | +1 | +1 | -2 | +1 | +1 | +1 | = 2 |

<sup>&</sup>lt;sup>3</sup>Roughly, dynamic programming is a commonly used technique to solve problems that contain multiple overlapping subproblems. The solution can be computed in a reduced number of steps by keeping track of and using the solutions to already-computed subproblems.

The Needleman-Wunsch algorithm is used to compute the similarity score of the optimal alignment (and to output the alignment). The core part of the algorithm is the calculation of an N + 1-by-M + 1 similarity matrix C, often called the dynamic programming table.  $(C)_{i,j}$  is the optimal similarity score for the alignment of the first i characters of r against the first j characters of s. First set  $(C)_{0,0}$  (the first cell in the matrix) to zero. Next initialize  $(C)_{0,j} = \alpha \times j$  and  $(C)_{i,0} = \beta \times i$ . These represent the penalties for introducing gaps at the start of either sequence. We can complete the matrix using the following definition:

$$(C)_{i,j} = \max \begin{cases} (C)_{i,j-1} + \alpha \\ (C)_{i-1,j} + \beta \\ (C)_{i-1,j-1} + \gamma(s_i, r_j) \end{cases}$$

Again, following the example in [60], if we wish to align the sequences s = AGTCand r = AGTAC, using the same penalties as in the previous example, the completed similarity matrix is:

The similarity score for the alignment of s and r in this case is  $(D)_{N,M} = (D)_{5,4} = +2.$

From the similarity matrix it is possible to derive the alignment that resulted in the optimal score, provided that each element records which neighbour element was used to compute its value. However, here we are interested purely in the computation of similarity scores, and not in the reproduction of the alignments that produce them.

#### 2.3.2 The Smith-Waterman Algorithm

The Smith-Waterman algorithm [37] is a modification of the Needleman-Wunsch algorithm that is used to compute *local alignments*. This is the most popular sequence alignment algorithm, since it allows for the alignment of parts of sequences. In global alignment, it is usually impossible to identify parts of sequences that are similar, since alignments that would identify such similarities will typically have been heavily penalized by misalignments of other parts of the sequences.

#### For example, if we have s = AAATAGTAGGTTGGAATTCCTATTT and

r = GGGGTTCCCAGTACCTAGG, there are two substrings in each sequence that align perfectly (AGTA and CCTA). The Smith-Waterman algorithm can be used to easily reveal such substring alignments (local alignments), where global alignment algorithms will not, in general.

The modifications to the Needleman-Wunsch algorithm that result in the Smith-Waterman algorithm are as follows. First, the initialization of the similarity matrix C is  $(C)_{0,j} = 0$  and  $(C)_{i,0} = 0$ , i.e. each element in the first row and column is set to zero. This removes the penalty for placing gaps at the start of a sequence. Second, the definition of the remaining matrix elements is modified to be:

$$(C)_{i,j} = \max \begin{cases} (C)_{i,j-1} + \alpha \\ (C)_{i-1,j} + \beta \\ (C)_{i-1,j-1} + \gamma(s_i, r_j) \\ 0 \end{cases}$$

Hence no negative values may appear in the Smith-Waterman dynamic programming table. This allows parts of sequences that are similar to accrue positive scores within the matrix. The matrix will then contain several chains of increasing positive values in cases where there are subsequences that can be locally aligned. The final modification in Smith-Waterman results from the aforementioned fact — in Needleman-Wunsch the optimal similarity score is  $(D)_{N,M}$ , but in Smith-Waterman the optimal similarity score (for the best local alignment) is given by the element with the highest value (and is not necessarily  $(D)_{N,M}$ ).

## 2.3.3 An Optimized Sequence Alignment Algorithm for Genome Resequencing Applications

In this thesis we are concerned with the speedup of sequence alignment for genome resequencing [61]. Resequencing is the task of sequencing DNA for an individual when provided with a reference sequence for the species. In resequencing, sequence alignment of many short-reads against a long reference sequence is the dominant consumer of computational resources. Current short-read sequencing technology produces short-reads of length approximately 30 base-pairs [3]. However, it is likely that new techniques will result in the short-read length doubling in the next few years. We assume that the reference sequence length, N, falls in the range  $10^8 \leq N \leq 3 \times 10^9$ , and the short-read length M falls in the range  $30 \leq M \leq 100$ .

In genome resequencing we expect short-reads to represent contiguous regions of the genome being resequenced, but we do not know *a priori* from which location in the genome any given short-read is from. Therefore a suitable sequence alignment algorithm for resequencing is a hybrid of the Needleman-Wunsch and Smith-Waterman algorithms – we want to align the entire short-read, not parts of it, but we do not want to penalize gaps at the start or end of the short-read. The Needleman-Wunsch algorithm with the Smith-Waterman modification to initialize the first row and column in the similarity matrix to zero is suitable.

Stevens and Song [42] have suggested a sequence alignment algorithm based on the Needleman-Wunsch and Smith-Waterman algorithms that is sufficiently flexible for resequencing applications, but is also more efficiently implementable on FPGAs than the Needleman-Wunsch or Smith-Waterman algorithms. They argue that it is not necessary to allow for arbitrary integer penalties. They suggest that the penalties  $\alpha$ ,  $\beta$  and  $\gamma$  be restricted to positive integers in the range [0,3]. The restriction to positive values implies that the matrix definition should select a minimum, rather than maximum, value:

$$(C)_{i,j} = \min \begin{cases} (C)_{i,j-l} + \alpha \\ (C)_{i-1,j} + \beta \\ (C)_{i-1,j-1} + \gamma(s_i, r_j) \end{cases}$$

Furthermore, they suggest that each element in the matrix can be stored using a 6-bit value, provided that saturating logic<sup>4</sup> is used.

The final difference between conventional sequence alignment algorithm implementations and the one presented in this thesis is that we are only required to output the values from the final row in the matrix. In fact for this application, it is sufficient to output only the column positions where the value in the final row is below some threshold T.

In this thesis we implemented Stevens and Song's optimized alignment algorithm.

<sup>&</sup>lt;sup>4</sup>In *b*-bit saturating logic, any register assignment of a value greater than  $2^{b} - 1$  results in the value  $2^{b} - 1$  being stored. The crucial point is that the register saturates rather than wraps.

# Chapter 3

# Multiple Sequence Alignment Implementation on a Cluster Reconfigurable Computer

In this chapter, we present the design and implementation of a custom processor design on a single FPGA that can simultaneously align tens of short-reads against a common reference genome. We implemented this design on a single user FPGA on a BEE2 reconfigurable computer. We then extended it from a single FPGA system to a multiple FPGA system that spans eight BEE2 processing boards. In the multiple FPGA system we replicated the single FPGA design across several FPGAs and implemented a control infrastructure to manage execution. Since the alignment algorithm is embarrassingly parallel, the primary concern in extending the system beyond a single FPGA was ensuring that the overhead from communicating input data to, and results from, the FPGAs does not significantly affect performance as we scale to larger numbers of FPGAs.

## 3.1 A Streaming Short-read Alignment Implementation

As discussed in Chapter 2, aligning multiple short-reads against a reference genome is an embarrassingly parallel problem – it is possible for each alignment to be completed independently of the others. Therefore, the first stage in the development of an FPGA design to simultaneously align multiple short-reads is the development of a design to align a single short-read. This design can be easily extended to support simultaneous multiple alignment.

### 3.1.1 Wavefront Parallelism in Dynamic Programming Sequence Alignment

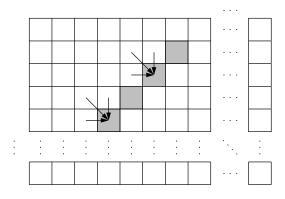

The dynamic programming approach to sequence alignment, as pioneered by Needleman and Wunsch [36], and Smith and Waterman [37], allows for the update of many cells in the dynamic programming table in parallel, provided that appropriate sets of cells are chosen. This is called "wavefront parallelism" because the sets of independent cells appear as "waves". Consider a dynamic programming table<sup>1</sup>, where Ncolumns represent the reference base-pairs, and M rows represent the short-read basepairs. Clearly, it is not possible to compute cell updates for entire rows or columns in parallel, since there are data dependencies between cells in such sets. However, if we choose our sets of cells to be those that are in anti-diagonals, there are no dependencies between cells in a set. This is illustrated in Figure 3.1, which highlights a single anti-diagonal set of cells. This technique was introduced by Lipton and Lopresti in 1985 [39] to build a custom processor for fast string comparisons, and is routinely used in parallelizations of dynamic programming sequence alignment algorithms for FPGAs (see Hoang's pioneering paper [40], and refs. [56, 57, 58] for more recent work).

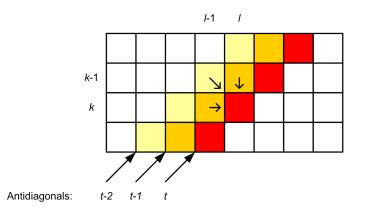

We can see from the staggering in the dynamic programming anti-diagonal scheme that, if the cell on row i for anti-diagonal t needs the reference base-pair from column j, then for the next anti-diagonal, t + 1, the cell on row i + 1 will need the reference base-pair from column j. In addition, in order to update the cell at row k and column l, C(k, l), for anti-diagonal t, we also need the values from cells (k - 1, l - 1), (k - 1, l)and (k, l - 1). These values were calculated during the updates for anti-diagonals t - 1 and t - 2.

This observation has a very important consequence: since the cell updates, when computed in anti-diagonals, only require data from the previous two anti-diagonal

<sup>&</sup>lt;sup>1</sup>The table should have dimensions N + 1-by-M + 1, where the first row and column are each filled with zeros. We use a zero-based indexing notation.

Figure 3.1: From [42]. "Wavefront Parallelism" in Dynamic Programming Sequence Alignment. If cells in the dynamic programming table are updated in anti-diagonals, each update can be calculated in parallel due to the arrangement of the data dependencies (shown as arrows for two example cells).

computations, it is only necessary to store the states of the cells in three anti-diagonals at any point in time. Moreover, the data dependencies exhibit a high degree of spatial and temporal locality (including the dependencies on the reference sequence basepairs), which enables the implementation of the computation using a systolic array that only requires communication between adjacent elements in the array. With the parallel anti-diagonal approach, only approximately 3 anti-diagonals  $\times M$  rows = 3M values need to be simultaneously stored to carry out each short-read alignment. Since typically M = 30 (and we expect M to have an upper bound of 100), the required storage will be 90 bytes<sup>2</sup> per short-read alignment, which can easily be supplied using registers (single-clock latency memory). A serial approach, which computes a single new cell value at each step, would require far less storage, but since low-latency storage for our application of dynamic programming alignment (where M < 100) is not a limiting constraint, we don't need to consider further any potential tradeoffs between space and time complexity.

The following listing is a (C-like) pseudocode description of the anti-diagonal technique<sup>3</sup>, implemented for serial execution. The function compute\_scores outputs the dynamic programming table values from the last row<sup>4</sup>. Three arrays, each of length

<sup>&</sup>lt;sup>2</sup>This value is calculated using the assumption that each cell's value is stored using 8 bits. In practice we use a 6-bit register, so the memory required is actually  $\approx 68$  bytes when M = 30.

$<sup>^{3}\</sup>mathrm{The}$  pseudocode listing is based on a C implementation by Yun Song.

<sup>&</sup>lt;sup>4</sup>Because the mismatch, deletion and insertion penalties are assumed to be positive, in practice

M + 1, are created as storage for the current anti-diagonal (stored in this), the antidiagonal from the previous update (stored in last), and the anti-diagonal from one further previous update (stored in lastlast). The arrays are appropriately initialized, and the remaining pseudocode is the main loop that computes the table values, one anti-diagonal at a time. The innermost for loop computes the value of each cell in a single anti-diagonal; this is the loop that can be parallelized because there are no conflicting data dependencies in this code.

```

function compute_scores(shortread, shortread_length, reference, reference_length)

// declare arrays

int this[shortread_length+1]

int last[shortread_length+1]

int lastlast[shortread_length+1]

// initialize arrays

this[0] = 0

last[0] = 0

lastlast[0] = 0

for i = 1 to shortread_length

this[i] = MAXINTEGER

last[i] = MAXINTEGER

lastlast[i] = MAXINTEGER

// Perform DP table updates

for i = 1 to reference_length+shortread_length-1

// Move anti-diagonal arrays

lastlast = last

last = this

// Update the current anti-diagonal

for j = 1 to shortread_length

// Insertion or deletion

this[j] = min(last[j-1] + INS_PENALTY, last[j] + DEL_PENALTY)

```

```

if (i-j < reference\_length) and (i \ge j) then

```

we will only be interested in the outputs where the dynamic programming table cell value was under some threshold, but we ignore this detail for now.

```

if (shortread[j-1] != reference[i-j]) then // mismatch

this[j] = min(this[j], lastlast[j-1] + MISMATCH_PENALTY)

else // match

this[j] = min(this[j], lastlast[j-1])

print i-shortread_length+1 // output position in reference

print this[shortread_length] // output last row value

```

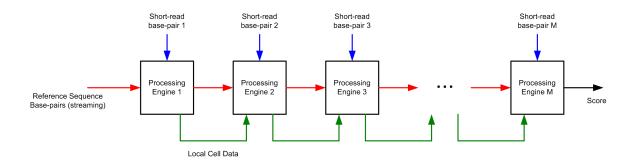

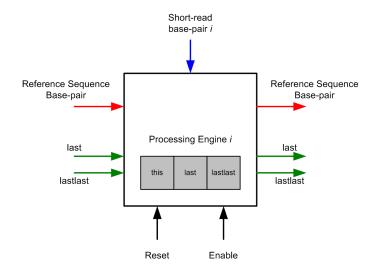

A systolic array can be used to compute the cells of the dynamic programming table in parallel using the wavefront technique. A high-level diagram of such an array is shown in Figure 3.2. Each anti-diagonal has M cells, and each cell can be updated in parallel, so the systolic array consists of M "Processing Engines" (PEs) that each compute a new value for the cell in the row that they are responsible for. PE1 computes the values for row 1, PE2 computes the values for row 2, and so on.

Figure 3.2: Systolic Array for Streaming Parallel Sequence Alignment. Each "Processing Engine" computes a single cell update. The reference sequence is streamed through the Processing Engines. Each PE passes local cell information to the following PE. The output from the final PE is the value for the cell in row M in the dynamic programming table, where the column is that which corresponds to the reference sequence base-pair that has most recently reached the final PE.

The output of the systolic array implementation is very similar to that of the pseudocode implementation: the final PE's output is the cell value for the last row in the dynamic programming table. In the pseudocode there is an explicit output of the column (reference base-pair). In the systolic array implementation, it is necessary to keep track of how many clock cycles have elapsed since the start. From this number it is possible to deduce which column the current output is for. Another subtlety in the systolic array implementation is that the PEs are assumed to continuously compute new values based on their inputs, so there is no explicit start and end to the "program" as there is in a traditional programming implementation. To define a start, we need to reset the registers in the PEs (this corresponds to the initialization steps in the pseudocode). It is then necessary to calculate how many clock cycles a particular alignment is expected to take (and this is deterministic, since the systolic array is not time-slice scheduled – it is always running, and runtime is directly proportional to the length of the reference, N), and to disable output after this many clock cycles have elapsed since beginning an alignment computation.

#### 3.1.2 A Cell Update Processing Engine

In order to update a cell C(k, l), the following information is necessary:

- 1. The values C(k-1, l-1), C(k-1, l) and C(k, l-1).

- 2. The reference base-pair value for column  $l, r_l$ .

- 3. The short-read base-pair value for row  $k, s_k$ .

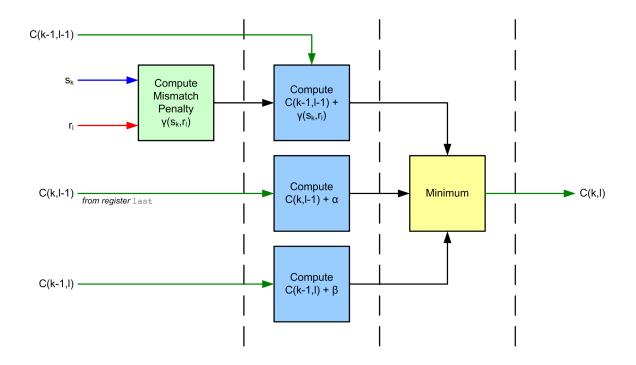

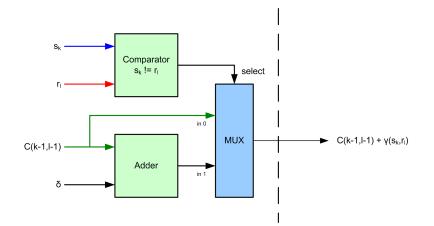

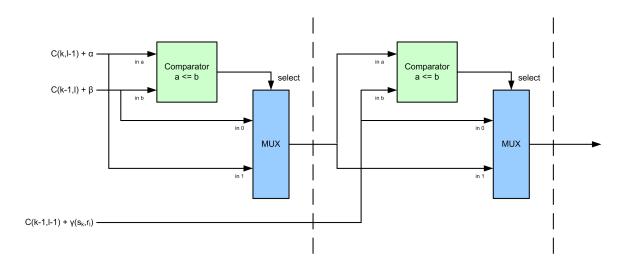

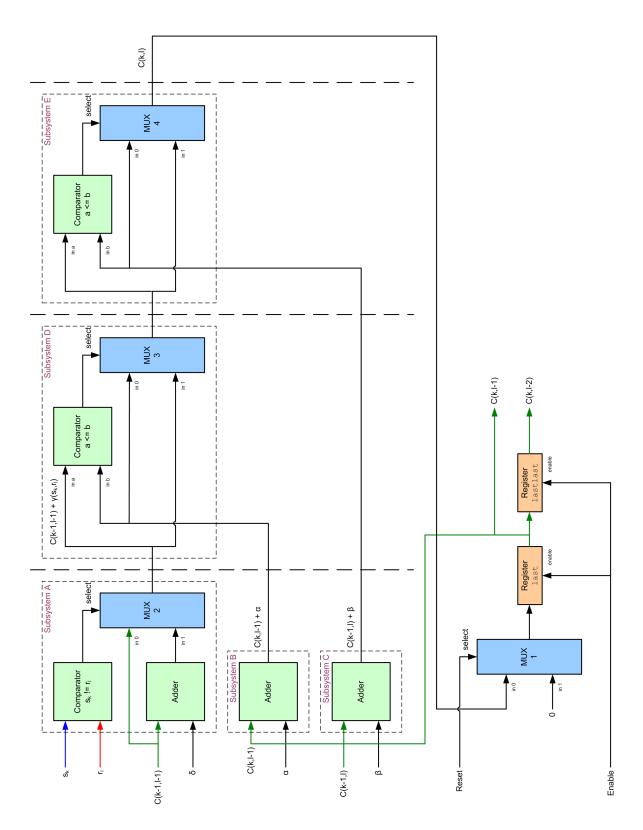

As we have discussed above, these data dependencies are local and allow the possibility of developing an efficient systolic array implementation of the algorithm, whereby values are "streamed" through an array of processing engines. Each processing engine is responsible for updating a single cell, and collectively the array of processing engines updates all the cells in a single anti-diagonal. Each processing engine, over the course of the algorithm's execution, computes the cell updates for a particular row.