## Samuel Santos Pereira

Exploração de Transmissores Integralmente Digitais em Cenários C-RAN

**Exploration of All-Digital Transmitters in C-RAN** Scenarios

### **Samuel Santos Pereira**

## Exploração de Transmissores Integralmente Digitais em Cenários C-RAN

### **Exploration of All-Digital Transmitters in C-RAN** Scenarios

Dissertação apresentada à Universidade de Aveiro para cumprimento dos requisitos necessários à obtenção do grau de Meste em Engenharia Electrónica e de Telecomunicações, realizada sob a orientação científica do Prof. Doutor Arnaldo Silva Rodrigues de Oliveira, Professor Auxiliar do Departamento de Electrónica, Telecomunicações e Informática da Universidade de Aveiro e do Prof. Doutor Paulo Miguel Nepomuceno Pereira Monteiro, Professor Associado do Departamento de Electrónicca, Telecomunicações e Informática da Universidade de Aveiro

### o júri / the jury

| presidente / president       | <b>Professor Doutor Armando Carlos Domingues da Rocha</b><br>Professor Auxiliar do Departamento de Electrónica, Telecomunicações e In-<br>formática da Universidade de Aveiro |  |  |  |  |  |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| vogais / examiners committee | <b>Professor Doutor João Paulo de Castro Canas Ferreira</b><br>Professor Auxiliar da Faculdade de Engenharia da Universidade do Porto (arguente)                              |  |  |  |  |  |

|                              | <b>Arnaldo Silva Rodrigues de Oliveira</b><br>Professor Auxiliar do Departamento de Electrónica, Telecomunicações e In-                                                       |  |  |  |  |  |

formática da Universidade de Aveiro (orientador)

# agradecimentos / acknowledgements

Antes de mais gostaria de agradecer à minha mãe pois foi dela que aprendi o mais importante da vida. Foi também ela que me ajudou incessantemente neste percurso que começou muito antes da universidade. Obrigado, mãe. Gostaria também de agradecer ao resto da minha família e amigos e a todos aqueles que de alguma forma me ajudaram não só neste percurso académico

Um agradecimento em especial para o Ricardo Figueiredo, que foi como um segundo professor em todas as cadeiras que tive. De realçar também a ajuda dada pelo Daniel Dinis e Abel Lorences-Riesgo, com os quais trabalhei e me diverti imenso.

Queria agradecer também aos professores Arnaldo Oliveira e Paulo Monteiro por me terem dado esta oportunidade, bem como ao Instituto de Telecomunicações e a todo os seus funcionários e colaboradores pela disponibilidade e auxílio prestado.

A todos, muito obrigado.

como em todos os aspetos da minha vida.

Este trabalho é financiado pela FCT/MEC através de fundos nacionais e quando aplicável cofinanciado pelo FEDER, no âmbito do Acordo de Parceria PT2020 no âmbito do projeto UID/EEA/50008/2013 e pelo Fundo Europeu de Desenvolvimento Regional (FEDER), através do Programa Operacional Regional de Lisboa (POR LISBOA 2020) e do Programa Operacional Competitividade e Internacionalização (COMPETE 2020) do Portugal 2020 [Projeto 5G com o número 024539 (POCI-01-0247-FEDER-024539)] e pelo Fundo Europeu de Desenvolvimento Regional (FEDER), através do Programa Operacional Competitividade e Internacionalização (COMPETE 2020) do Portugal 2020, Projeto RETIOT, POCI-01-0145-FEDER-016432.

#### Resumo

De modo a acompanhar a sempre crescente exigência de maiores taxas de transmissão, a próxima geração de telecomunicações móveis (5G) irá necessitar de maiores larguras de banda, bem como novas frequências de transmissão com espectro livre capaz de acomodar tais larguras de banda. A subida em frequência é apontada como uma solução para este problema, contudo as baixas áreas de cobertura apresentadas por estas bandas de frequência (mmWave) irão necessitar de uma nova forma de implementar estações base. Estas, por sua vez, terão de existir em maior número e mais próximas. É aqui que a nova arquitetura de redes de acesso radio, C-RAN, pode permitir cumprir com estes requisitos, além de poder baixar o custo de cada estação base e aumentar a sua eficiência energética.

Esta dissertação tem como objetivo a criação de uma ligação ponto a ponto baseada em transmissores integralmente digitais (ADTs) capaz de ser usada para a transmissão de dados no *fronthaul*. Aproveitando os desenvolvimentos recentes nos ADT, a criação de um transmissor integralmente digital com largura de banda elevada é agora possível. Além disto, os agregados de células lógicas reprogramáveis (FPGAs) têm vindo a fornecer cada vez uma maior capacidade de processamento, usando menos energia, tornando o produto final, mais barato e mais eficiente. O recurso à modelação deltasigma ( $\Delta \Sigma M$ ) no ADT poderá reduzir consideravelmente a complexidade da cabeça remota de rádio (RRH).

Neste trabalho a ligação ótica que irá ser usada para enviar os dados no *fronthaul* será baseada num SFP, mas outras técnicas de rádio sobre fibra (RoF) poderão ser também usadas de forma a possibilitar, por exemplo, *upconversion* ótico.

Da conclusão deste trabalho resulta uma ligação ponto a ponto baseada num ADT com um *Error Vector Magnitude* (EVM) sempre abaixo dos 5%, bem como duas arquiteturas de *upconversion* ótico com uma gama possível para o sinal de saída que pode variar entre os 27 GHz e os 63 GHz.

#### Abstract

In order to accommodate the ever-growing demand for higher transmission rates, the next generation of mobile telecommunications (5G) will need larger bandwidths, as well as, new frequencies with available spectrum capable of accommodate such bandwidths. The rise in frequency is being pointed out as a solution for this problem, however, the low coverage areas presented by these frequency bands (mmWave) will require a new way of implementing base stations. Those, in their turn, will exist in higher numbers and closer together. It is where that the new radio access network architecture, C-RAN, may allow for the fulfilment of these requirements, besides also allowing for the reduction in cost of each base station as well as providing an increase in its energy efficiency.

This dissertation aims to create a point-to-point optical link based on All-Digital Transmitters (ADT) capable of being used for data transmission in the fronthaul. Taking advantage of recent developments in ADT, it is now possible to create one with large bandwidths. Besides, the field programmable gate arrays (FPGAs) have been providing each time higher processing capacity using each time less energy, making the final product cheaper and more efficient. Recurring to delta-sigma modulation ( $\Delta \Sigma M$ ), a reduction in the complexity of the remote radio head (RRH) can be achieved.

In this work the optical link that will be used to transport the data through the fronthaul will be based on an SFP. However, other techniques of radio over fibre (RoF) can be used to enable, for example, optical upconversion.

From the conclusion of this work, a point-to-point optical link based on an ADT was achieved with an Error Vector Magnitude (EVM) always lower than 5%. Also, from this work, two optical upconversions were developed with an output frequency range from 27 GHz up to 63 GHz.

# Contents

| Li       | st of | Figures       |          |          |           |     |       |      |  |       |     |   |   |  |   |   |   | $\mathbf{v}$ |

|----------|-------|---------------|----------|----------|-----------|-----|-------|------|--|-------|-----|---|---|--|---|---|---|--------------|

| Li       | st of | Tables        |          |          |           |     |       |      |  |       |     |   |   |  |   |   |   | vii          |

| Li       | st of | Acronyms      |          |          |           |     |       |      |  |       |     |   |   |  |   |   |   | ix           |

| 1        | Intr  | oduction      |          |          |           |     |       |      |  |       |     |   |   |  |   |   |   | 1            |

|          | 1.1   | Background    | d and    | Motiva   | tion .    |     |       | <br> |  |       |     |   | • |  | • |   |   | 1            |

|          | 1.2   | Objectives    |          |          |           |     |       |      |  |       |     |   |   |  |   |   |   | 4            |

|          | 1.3   | Publication   | ns       |          |           |     |       | <br> |  |       |     |   |   |  |   |   |   | 4            |

|          | 1.4   | Document      | Organ    | isation  |           |     | <br>• | <br> |  | <br>• |     | • | • |  |   | • | • | 5            |

| <b>2</b> | Bac   | kground       |          |          |           |     |       |      |  |       |     |   |   |  |   |   |   | 7            |

|          | 2.1   | Introductio   | on       |          |           |     |       | <br> |  |       |     |   |   |  |   |   |   | 7            |

|          | 2.2   | All-digital ' | Transı   | mitters  |           |     |       | <br> |  |       |     |   | • |  | • |   |   | 7            |

|          |       | 2.2.1 Puls    | se Wie   | lth Mo   | dulatio   | n.  |       | <br> |  |       |     |   |   |  |   |   |   | 8            |

|          |       | 2.2.2 Delt    | ta-Sigi  | ma Mo    | dulatio   | n   |       | <br> |  |       |     |   | • |  | • |   |   | 10           |

|          | 2.3   | Radio over    | Fibre    |          |           |     |       | <br> |  |       |     |   |   |  |   |   |   | 12           |

|          | 2.4   | Practical C   | onside   | erations | 3         |     |       | <br> |  |       |     |   | • |  | • |   |   | 17           |

|          |       | 2.4.1 Mul     | lti-giga | abit Tra | ansceiv   | er  |       | <br> |  |       |     |   |   |  |   |   |   | 17           |

|          |       | 2.4.2 Poly    | yphase   | e Imple  | mentat    | ion |       | <br> |  |       |     |   |   |  |   |   |   | 17           |

|          |       | 2.4.3 Erro    | or Vec   | tor Ma   | gnitude   | е.  |       | <br> |  |       |     |   |   |  |   |   |   | 18           |

|          | 2.5   | Final Rema    | ark .    |          |           | ••• |       | <br> |  | <br>• | ••• | • | • |  | • | • | • | 18           |

| 3        | Poir  | nt-to-Point   | Link     |          |           |     |       |      |  |       |     |   |   |  |   |   |   | 19           |

|          | 3.1   | Concept .     |          |          |           |     |       | <br> |  |       |     |   |   |  |   |   |   | 19           |

|          | 3.2   | Modelling a   |          |          |           |     |       |      |  |       |     |   |   |  |   |   |   | 20           |

|          |       | 0             |          |          |           |     |       |      |  |       |     |   |   |  |   |   |   | 20           |

|          |       | 3.2.1         | 1.1      | Filter   |           |     |       | <br> |  |       |     |   |   |  |   |   |   | 20           |

|          |       | 3.2.1         | 1.2      | Upconv   | verter    |     |       | <br> |  |       |     |   |   |  |   |   |   | 22           |

|          |       | 3.2.1         |          | -        | rleavin   |     |       |      |  |       |     |   |   |  |   |   |   | 24           |

|          |       | 3.2.1         |          |          | Sigma N   | -   |       |      |  |       |     |   |   |  |   |   |   | 26           |

|          |       | 3.2.1         |          |          | wing .    |     |       |      |  |       |     |   |   |  |   |   |   | 28           |

|          |       | 3.2.1         |          |          | nitter Si |     |       |      |  |       |     |   |   |  |   |   |   | 30           |

|          |       |               | eiver    |          |           |     |       |      |  |       |     |   |   |  |   |   |   | 31           |

|          |       | 3.2.2         | 2.1      | Downco   | onverte   | r   |       | <br> |  |       |     |   |   |  |   |   |   | 31           |

|          |       | 3.2.2         | 2.2      | Filter   |           |     |       | <br> |  |       |     |   |   |  |   |   |   | 33           |

|              | 3.3   | Hardware Implementation                                          | 35 |

|--------------|-------|------------------------------------------------------------------|----|

|              | 3.4   | Optical Link                                                     | 37 |

|              | 3.5   | Measurements                                                     | 40 |

|              |       | 3.5.1 Electrical Transmission                                    | 41 |

|              |       | 3.5.2 Electrical Back-to-Back                                    | 42 |

|              |       | 3.5.3 Optical Transmission                                       | 44 |

|              |       | 3.5.4 Point-to-Point Link with Optical Transmission              | 46 |

| 4            | Opt   | ical Upconversion                                                | 49 |

|              | 4.1   | Concept                                                          | 49 |

|              | 4.2   | All-digital Transmitter                                          | 50 |

|              | 4.3   | Optical Architecture                                             | 53 |

|              |       | 4.3.1 Dual Carrier Modulated Optical Upconversion Architecture   | 53 |

|              |       | 4.3.2 Single Carrier Modulated Optical Upconversion Architecture | 54 |

|              | 4.4   | Measurements                                                     | 56 |

| <b>5</b>     | Con   | clusion and Future Work                                          | 65 |

|              | 5.1   | Conclusion                                                       | 65 |

|              | 5.2   | Future Work                                                      | 66 |

| $\mathbf{A}$ | Imp   | lementation on System Generator                                  | 67 |

| Bi           | bliog | raphy                                                            | 83 |

# List of Figures

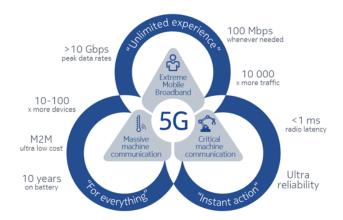

| $1.1 \\ 1.2$ | 5G vision and key performance indicators, copied from [2]                    |

|--------------|------------------------------------------------------------------------------|

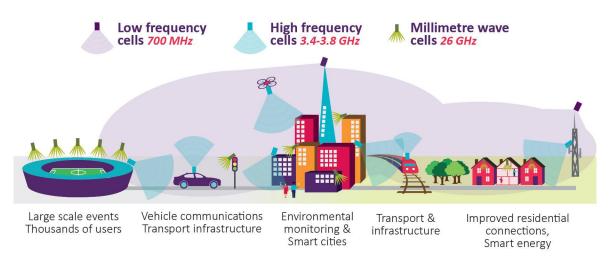

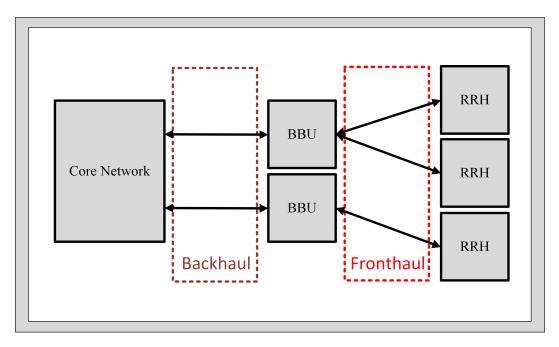

| 1.2<br>1.3   | Cloud radio access network architecture                                      |

| 1.3<br>1.4   |                                                                              |

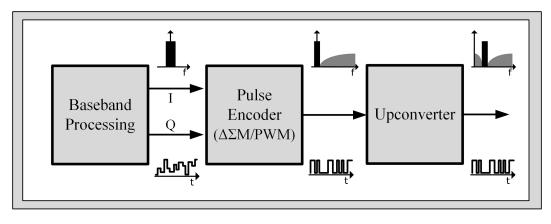

| 1.4          | All-digital transmitter architecture                                         |

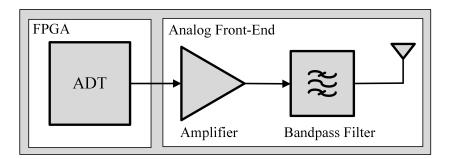

| 2.1          | Transmission chain using an ADT, based on Fig.1 from [12]7                   |

| 2.2          | Pulse width modulation                                                       |

| 2.3          | PWM typical spectrum                                                         |

| 2.4          | Delta-sigma modulation with: a) filter in the feed forward; b) filter in the |

|              | feedback path                                                                |

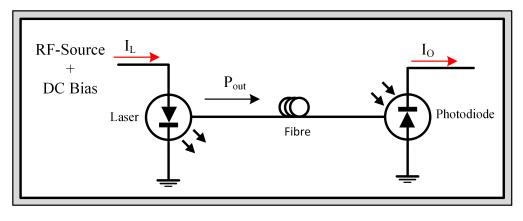

| 2.5          | Optical direct modulation                                                    |

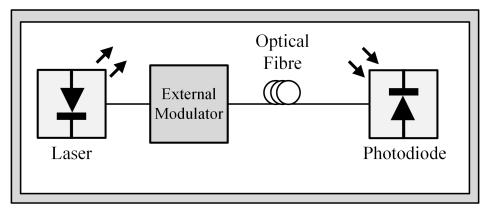

| 2.6          | Optical external modulation                                                  |

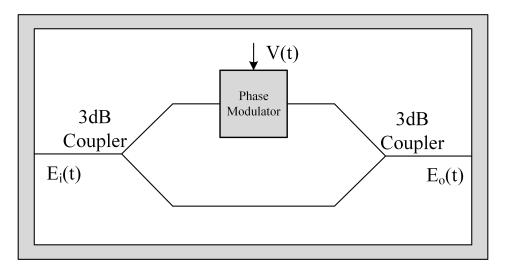

| 2.7          | Single-drive Mach-Zehnder modulator                                          |

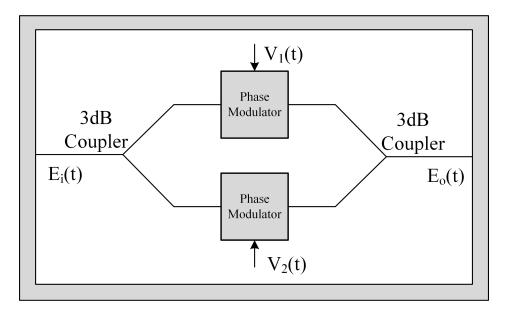

| 2.8          | Dual-drive Mach-Zehnder modulator                                            |

| 2.9          | MGT's data path                                                              |

| 2.10         | MGT's Quad's clock architecture, [30]                                        |

| ~ .          |                                                                              |

| 3.1          | Top-level architecture of the proposed point-to-point link                   |

| 3.2          | ADT's architecture                                                           |

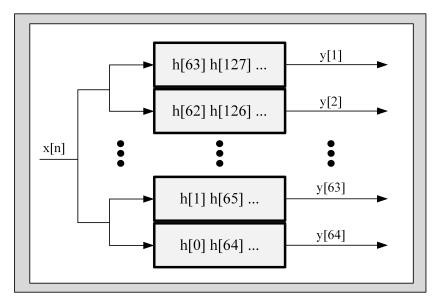

| 3.3          | Interpolation polyphase filter                                               |

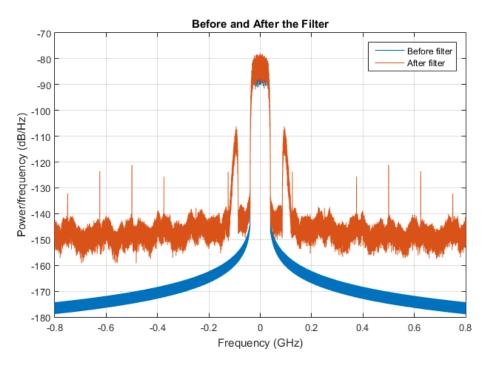

| 3.4          | Spectrum before and after the transmitter filter                             |

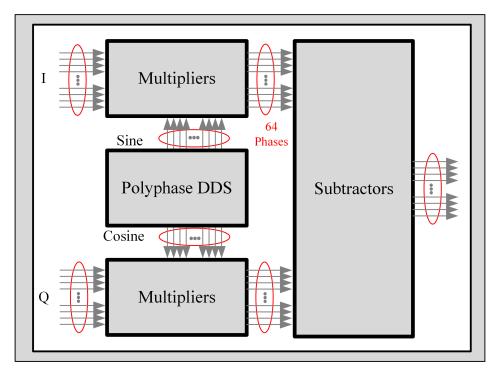

| 3.5          | Upconverter's architecture. 23                                               |

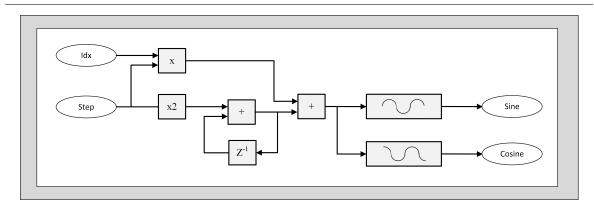

| 3.6          | DDS ROM's implementation and control                                         |

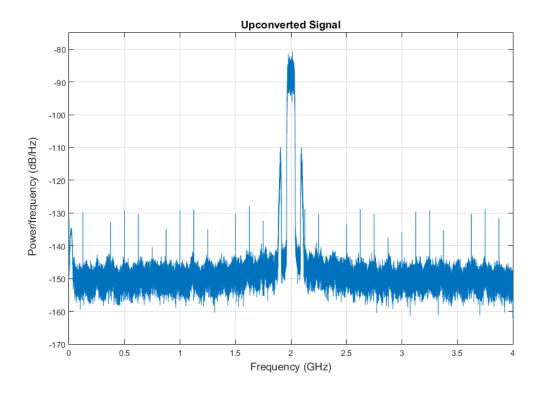

| 3.7          | Spectrum after the upconverter                                               |

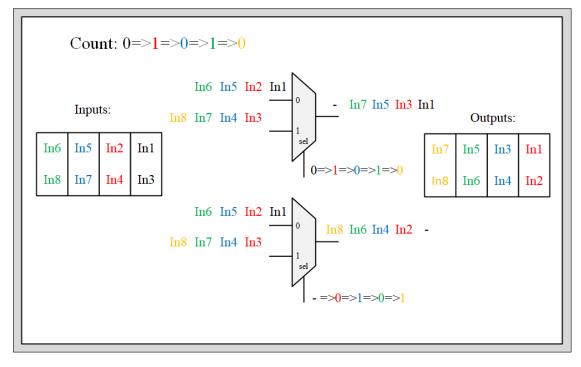

| 3.8          | Schematic of the de-interleaver with two phases                              |

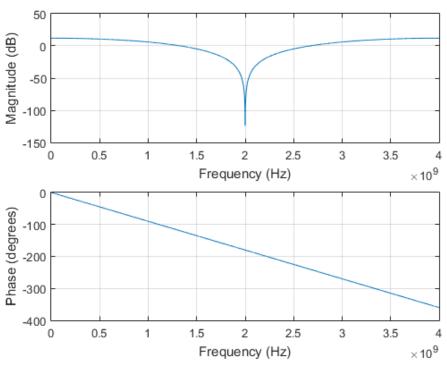

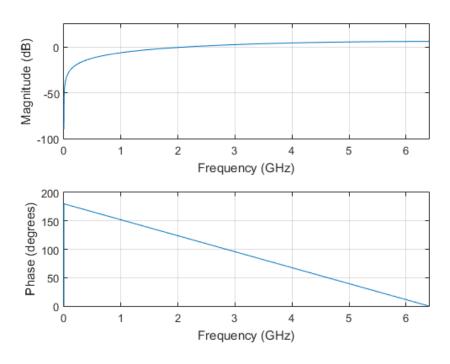

| 3.9          | Frequency response of the NTF                                                |

| 3.10         | $\Delta \Sigma M$ core implementation, figure from [14]                      |

|              | Schematic of the interleaver with two phases                                 |

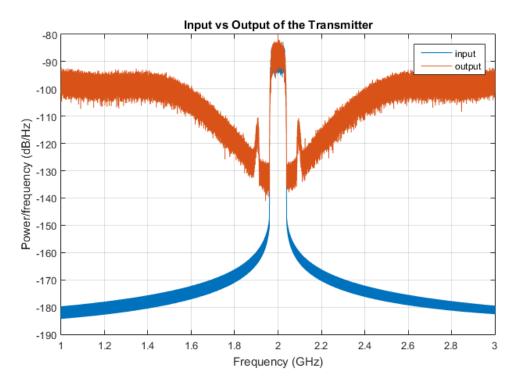

|              | Comparison between the input and output spectrum in the transmitter $30$     |

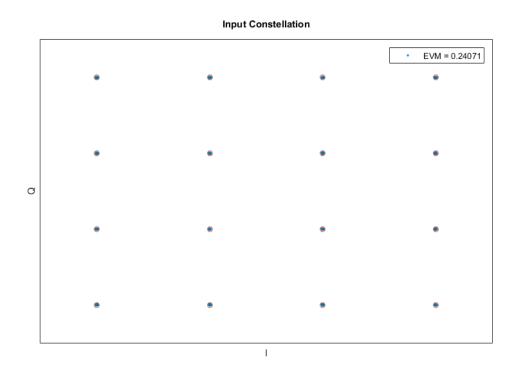

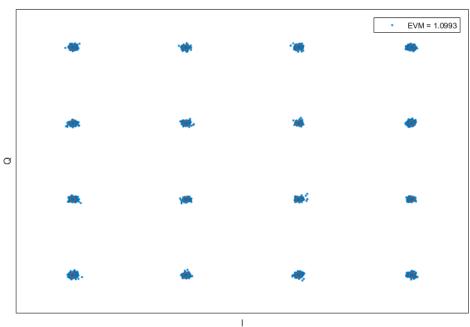

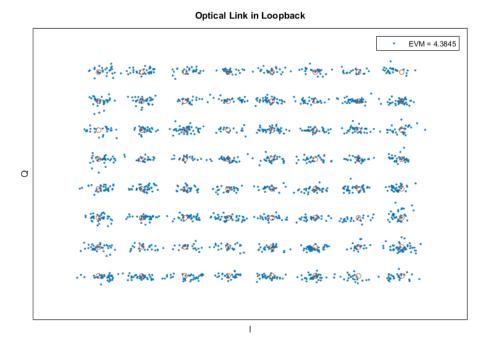

|              | Input constellation with EVM measurement                                     |

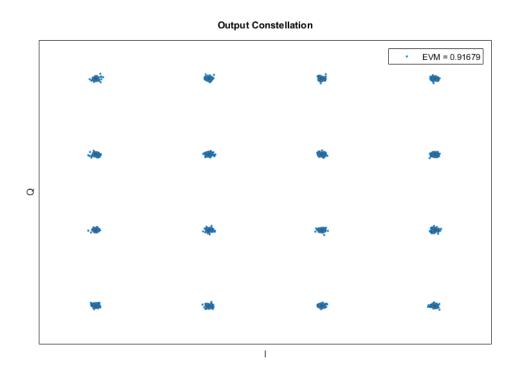

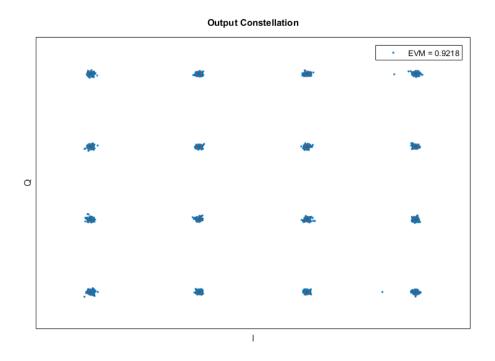

|              | Transmitter's output constellation with EVM measurement                      |

|              | MGT and downconverter architecture                                           |

|              | Downconverter output constellation with EVM measurement                      |

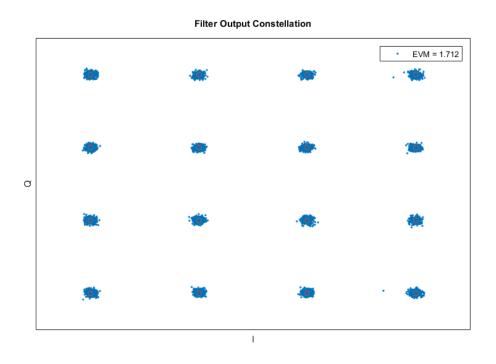

|              | Decimation polyphase filter                                                  |

| 3.18         | Output constellation from the filter                                         |

|              | FPGA kit used in this implementation, Xilinx VCU1283                         |

| 3.20         | Top-level view of the hardware implementation                                |

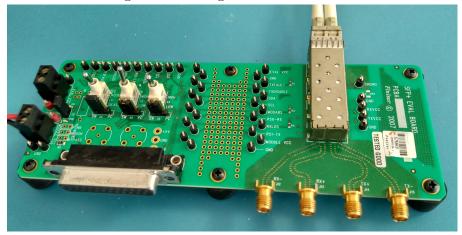

| 3.21 | Image of the SFP+ used                                                                                       | 38       |

|------|--------------------------------------------------------------------------------------------------------------|----------|

| 3.22 | Evaluation board used for the housing of the Small Form-Factor Pluggable                                     |          |

|      | Transceiver (SFP). $\ldots$ | 38       |

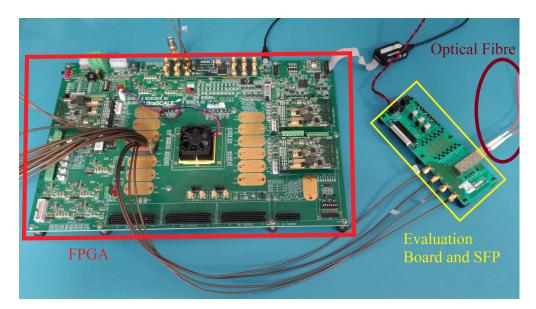

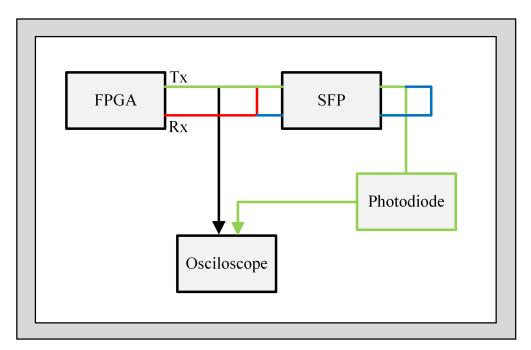

| 3.23 | Experimental setup with the FPGA (red square), evaluation board and SPF+                                     |          |

|      | (yellow square), and optical fibre (brown circle).                                                           | 39       |

| 3.24 | Block diagram of the four measurement points: in black, electrical transmis-                                 |          |

|      | sion, in red, electrical back-to-back, in green, optical transmission and in blue,                           |          |

|      | the point-to-point link with optical transmission.                                                           | 39       |

| 3.25 | FPGA's output with 16-QAM constellation measured in an oscilloscope                                          | 4        |

| 3.26 | FPGA's output with 64-QAM constellation measured in an oscilloscope                                          | 42       |

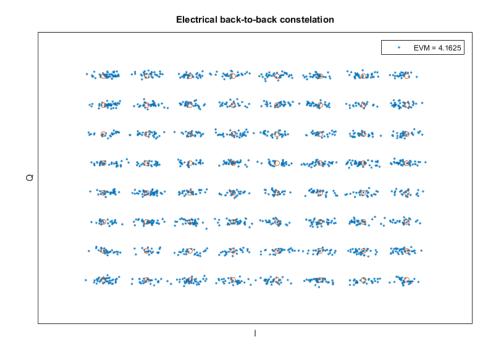

| 3.27 | Electrical loopback with an 16-QAM constellation.                                                            | 4        |

| 3.28 | Electrical loopback with an 64-QAM constellation.                                                            | 44       |

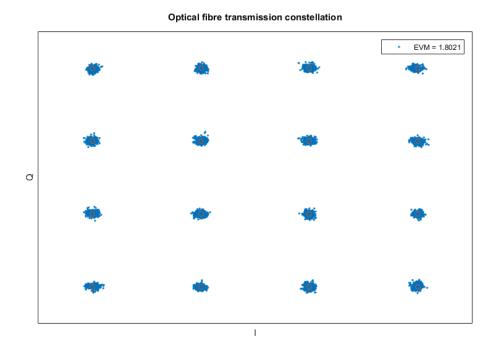

| 3.29 | Optical output with an 16-QAM constellation measured in an oscilloscope.                                     | 4        |

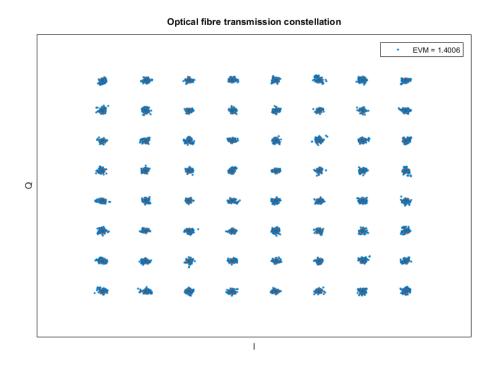

| 3.30 | Optical output with an 64-QAM constellation measured in an oscilloscope.                                     | 4        |

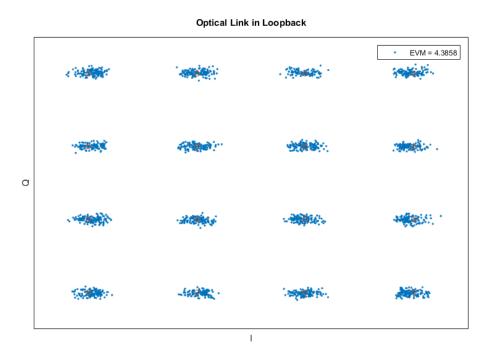

| 3.31 | Final optical link 16-QAM constellation                                                                      | 4        |

| 3.32 | Final optical link 64-QAM constellation                                                                      | 4        |

| 3.33 | Inversion of the stretching present in the constellation                                                     | 4        |

| 4 1  | ADT architecture.                                                                                            | 49       |

| 4.1  |                                                                                                              | 43<br>5( |

| 4.2  | Delta sigma modulation core filter                                                                           |          |

| 4.3  | Frequency and phase response of the NTF.                                                                     | 5        |

| 4.4  | Dual carrier modulated optical upconversion architecture.                                                    | 5        |

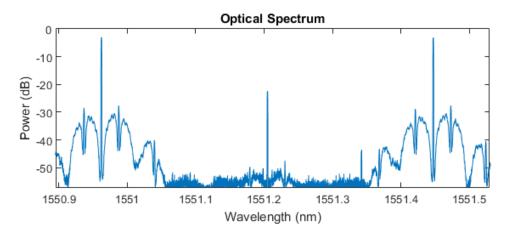

| 4.5  | Optical spectrum of the dual carrier modulated optical upconversion architecture.                            | 5        |

| 4.6  | Single carrier modulated optical upconversion architecture.                                                  | 5        |

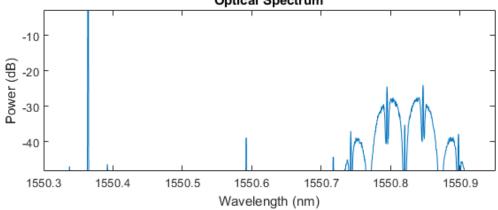

| 4.7  | Optical spectrum of the single carrier optical upconversion architecture                                     | 5        |

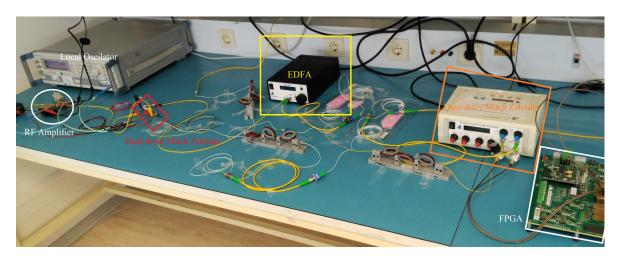

| 4.8  | Experimental setup.                                                                                          | 5        |

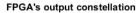

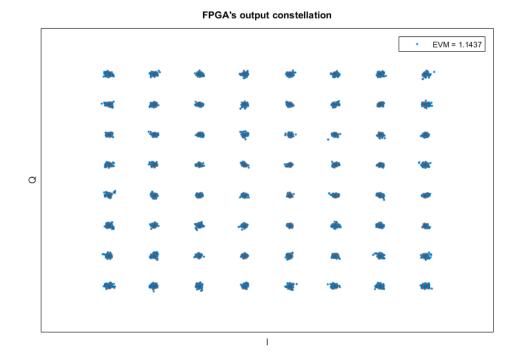

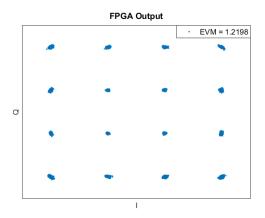

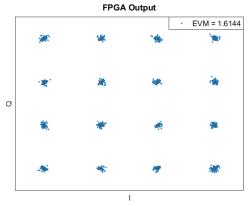

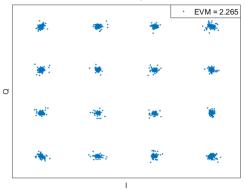

| 4.9  | FPGA output constellation for 16-QAM with 20 Mbaud.                                                          | 5'       |

| 4.10 | FPGA output constellation for 16-QAM with 50 Mbaud.                                                          | 5        |

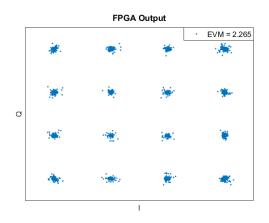

|      | FPGA output constellation for 16-QAM with 100 Mbaud.                                                         | 5'       |

|      | FPGA output constellation for 16-QAM with 100 Mbaud.                                                         | 58       |

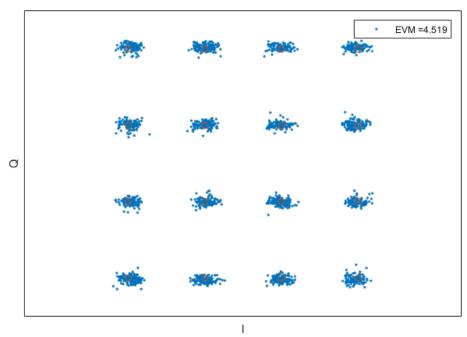

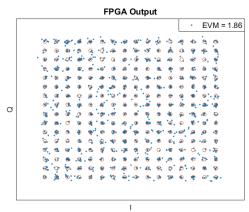

|      | FPGA output constellation for 64-QAM with 100 Mbaud.                                                         | 5        |

|      | FPGA output constellation for 256-QAM with 100 Mbaud.                                                        | 5        |

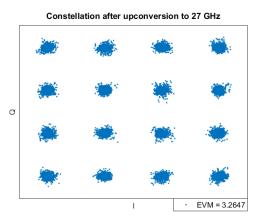

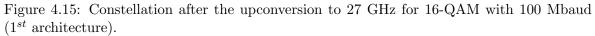

| 4.15 | Constellation after the upconversion to 27 GHz for 16-QAM with 100 Mbaud                                     |          |

|      | $(1^{st} \text{ architecture})$                                                                              | 6        |

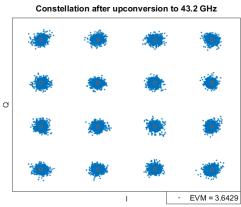

| 4.16 | Constellation after the upconversion to 43.2 GHz for 16-QAM with 100 Mbaud                                   |          |

| –    | $(1^{st} \text{ architecture})$                                                                              | 6        |

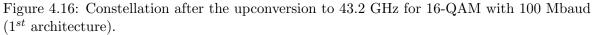

| 4.17 | Constellation after the upconversion to 63.2 GHz for 16-QAM with 100 Mbaud                                   |          |

|      | $(1^{st} \text{ architecture})$                                                                              | 6        |

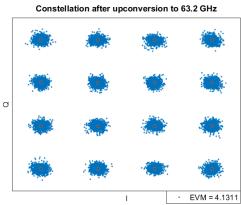

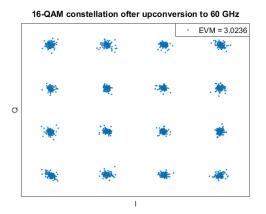

| 4.18 | Constellation after upconversion to 60 GHz for 16-QAM with 100 Mbaud ( $2^{nd}$                              |          |

|      | architecture).                                                                                               | 6        |

| 4.19 | Constellation after upconversion to 60 GHz for 64-QAM with 100 Mbaud ( $2^{nd}$                              | _        |

|      | architecture).                                                                                               | 6        |

| 4.20 | Constellation after upconversion to 60 GHz for 256-QAM with 100 Mbaud ( $2^{nd}$                             |          |

|      | architecture).                                                                                               | 6        |

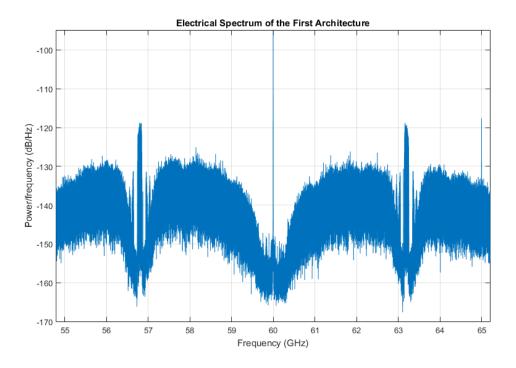

|      | Final spectrum of the dual carrier modulated optical upconversion architecture.                              | 63       |

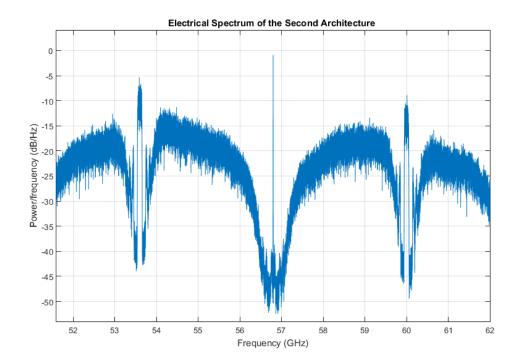

| 4.22 | Final spectrum of the single carrier modulated optical upconversion architecture.                            | 6        |

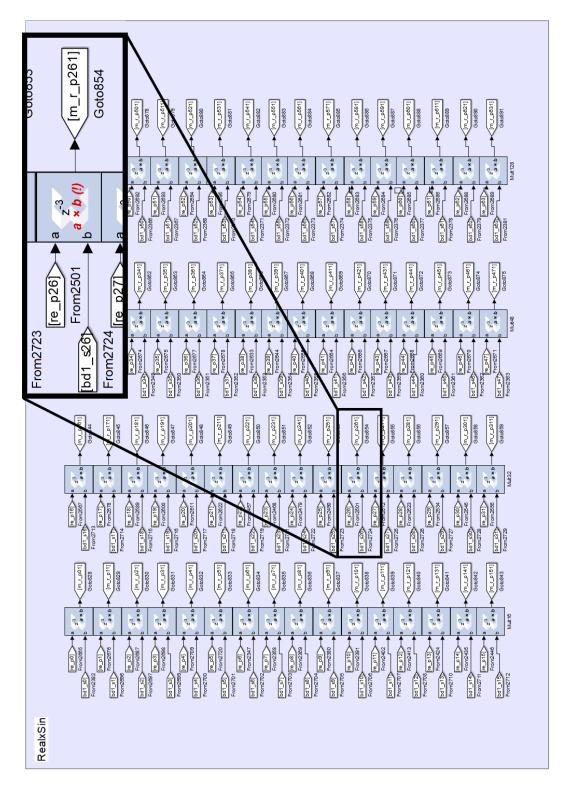

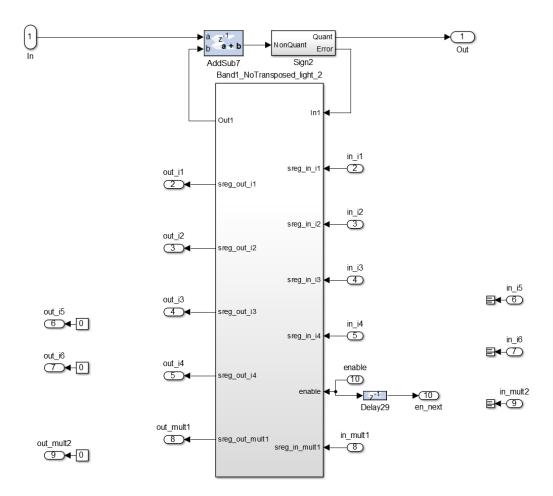

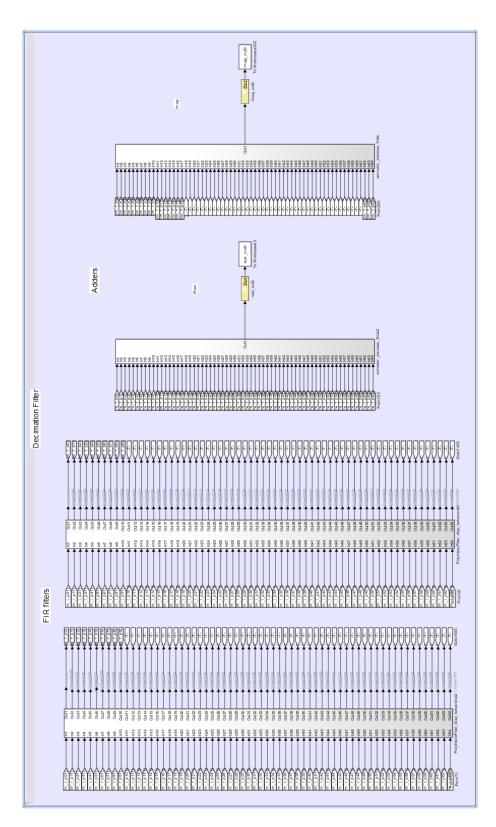

| A.1  | Transmitter top-level architecture                 |

|------|----------------------------------------------------|

| A.2  | Polyphase interpolation filter implementation      |

| A.3  | FIR filter implementation                          |

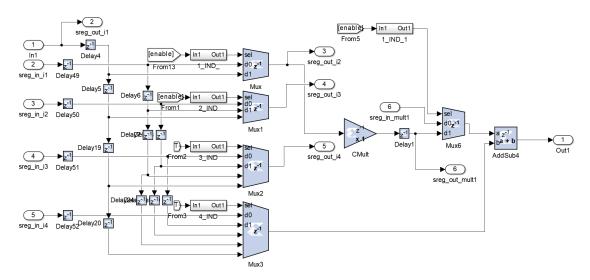

| A.4  | Multipliers polyphase implementation               |

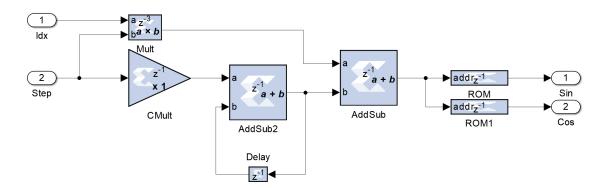

| A.5  | Digital direct syntheses polyphase implementation  |

| A.6  | Digital direct syntheses ROMs implementation       |

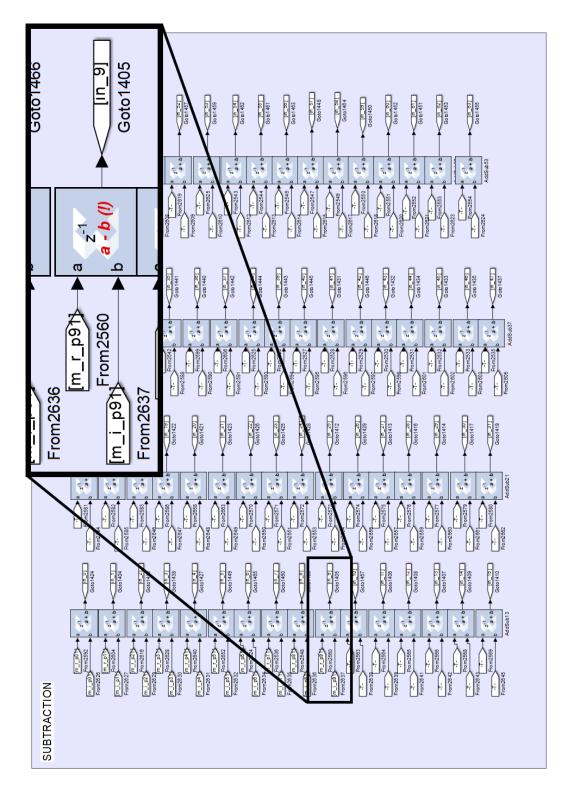

| A.7  | Subtracters polyphase implementation               |

| A.8  | DSM polyphase implementation                       |

| A.9  | DSM core implementation                            |

| A.10 | DSM core filter implementation                     |

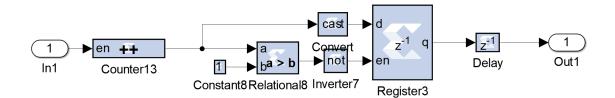

| A.11 | Filter states initiation controller implementation |

| A.12 | DSM's quantizer implementation                     |

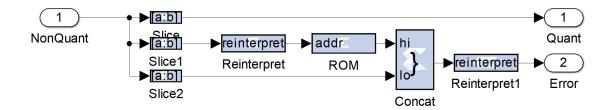

| A.13 | Control implementation                             |

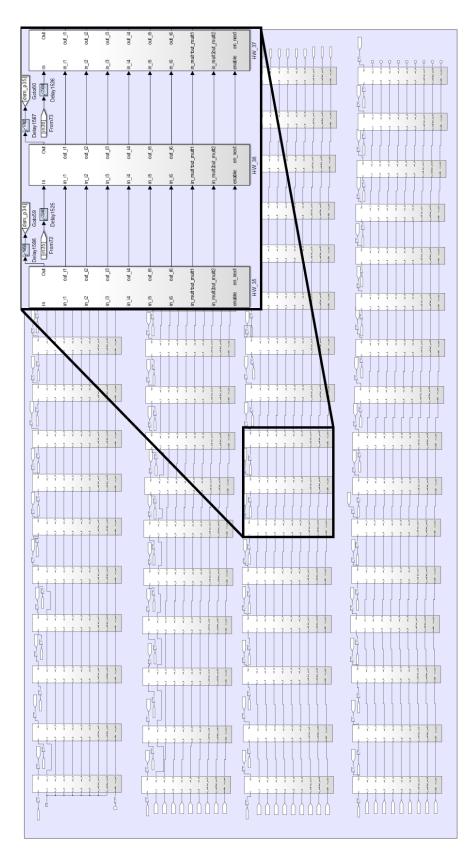

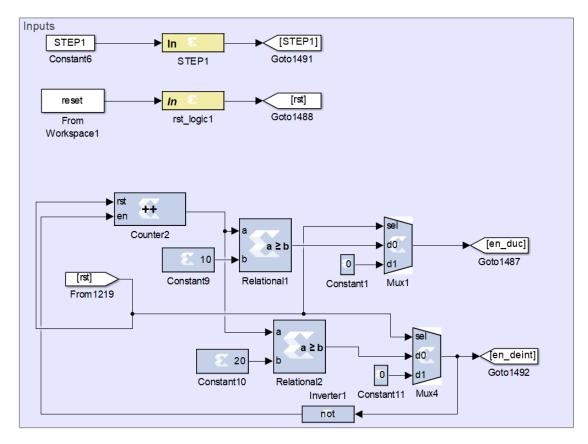

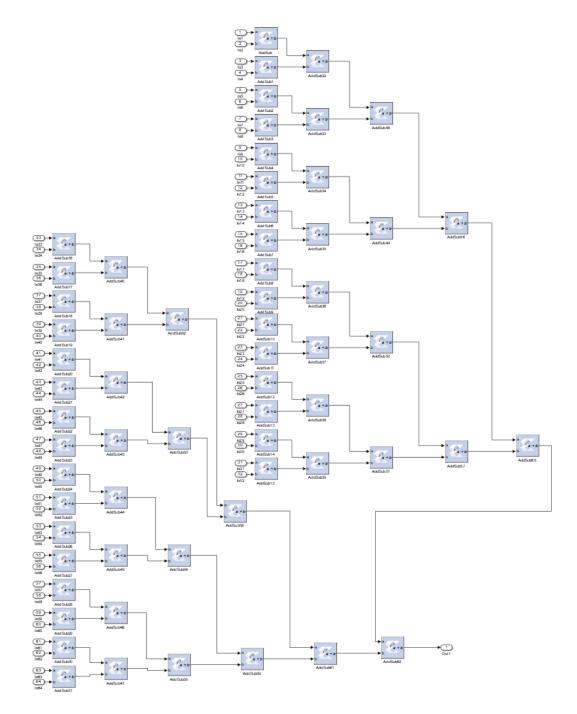

| A.14 | Receiver top-level architecture                    |

| A.15 | Multiplication top-level architecture              |

| A.16 | Multiplication's multiplexer implementation        |

| A.17 | Filter top-level architecture                      |

| A.18 | Filter polyphase implementation                    |

|      | Adders polyphase implementation                    |

# List of Tables

| 3.1 | Utilization values of the Field Programmable Gate Array (FPGA)                 | 37 |

|-----|--------------------------------------------------------------------------------|----|

| 3.2 | EVM Results obtained at the FPGA's output for both 16- and 64-QAM cases.       | 41 |

| 3.3 | EVM results obtained in electrical loopback for both 16- and 64-QAM cases.     | 43 |

| 3.4 | EVM results obtained after optical transmission for both 16- and 64-QAM cases. | 44 |

| 3.5 | Final EVM results.                                                             | 46 |

| 4.1 | Utilization values of the FPGA                                                 | 52 |

# List of Acronyms

| 4                     | <b>.</b>                                |

|-----------------------|-----------------------------------------|

| $\Delta \Sigma M$     | Delta-sigma Modulation                  |

| ADT                   | All-Digital Transmitters                |

| BBU                   | Baseband Unit                           |

| C-RAN                 | Cloud Radio Access Network              |

| CPRI                  | Common Public Radio Interface           |

| DAC                   | Digital-to-Analogue Converter           |

| DDS                   | Direct Digital Syntheses                |

| eCPRI                 | Evolved Common Public Radio Interface   |

| EDFA                  | Erbium Doped Fibre Amplifier            |

| EVM                   | Error Vector Magnitude                  |

| $\operatorname{FIR}$  | Finite Impulse Response                 |

| FPGA                  | Field Programmable Gate Array           |

| $\operatorname{Gsps}$ | Gsamples per second                     |

| HDL                   | Hardware Description Language           |

| IIR                   | Infinite Impulse Response               |

| ILA                   | Integrated Logic Analyser               |

| IoT                   | Internet of Things                      |

| MASH                  | Multi-Stage Noise shaping               |

| MGT                   | Multi-Gigabit Transceiver               |

| MIMO                  | Multiple Input Multiple Output          |

| mmWave                | Millimetre Wave                         |

| Msps                  | Msamples per second                     |

| NTF                   | Noise Transfer Function                 |

| PWM                   | Pulse-width Modulation                  |

| QAM                   | Quadrature Amplitude Modulation         |

| RAM                   | Random Access Memory                    |

| $\mathbf{RF}$         | Radio Frequency                         |

| RoF                   | Radio over Fibre                        |

| ROM                   | Read Only Memory                        |

| RRH                   | Remote Radio Head                       |

| SDR                   | Software Defined Radio                  |

| SFP                   | Small Form-Factor Pluggable Transceiver |

| SNR                   | Signal to Noise Ratio                   |

|                       | 0                                       |

| SOA | Semiconductor | Optical | Amplifier |

|-----|---------------|---------|-----------|

|-----|---------------|---------|-----------|

- SQNR Signal-to-Quantization Noise Ratio

- STF Signal Transfer Function

# Chapter 1

## Introduction

#### **1.1** Background and Motivation

The ever-growing demand for bandwidth in the mobile communications systems has triggered a huge wave of research and development in the field. This, accompanied by environmental issues, has led developers to find not only solutions capable of delivering wider bandwidths, but also to find the ones which use less energy. These two concerns, paired with the need for more flexible architectures, are the backbone of the next generation of wireless communications (5G).

For a successful 5G implementation and deployment, data rates higher than one gigabit per second are expected to be deliver to each user, and, due to the rise of the Internet of Things (IoT), ten thousand or more devices could be connected to a single macrocell [1]. From [1], it is explained that the increase in data rate per user accompanied by the rise in the total connected devices could represent a thousand fold increase in the so called aggregated data rate, which refers to the total data rate in bit/s per unit of area. Another target for 5G is the low latency which is expected to be less then 1 ms. An overview of these requirements for 5G can be seen in the Figure 1.1. A solution to all these problems could arrive from the combined gains of extreme densification of base stations, of larger bandwidth, mostly by migrating into the millimetre wave band, and of the increased spectral efficiency provided

Figure 1.1: 5G vision and key performance indicators, copied from [2].

Figure 1.2: Different 5G bands and their applications, copied from [3].

by Multiple Input Multiple Output (MIMO). The use of multiple frequency bands will also ensure that all scenarios are covered by 5G. The use of low frequencies can give large coverage areas, which are important for rural areas, the high frequency band will provide most of the bandwidth needed in cities specially when inside cars and other transports and finally the millimetre wave band will allow for coverage of large scale events and some other specific cases where high bandwidth is the bigger problem. A depiction of these various frequency bands and their use cases can be seen in Figure 1.2.

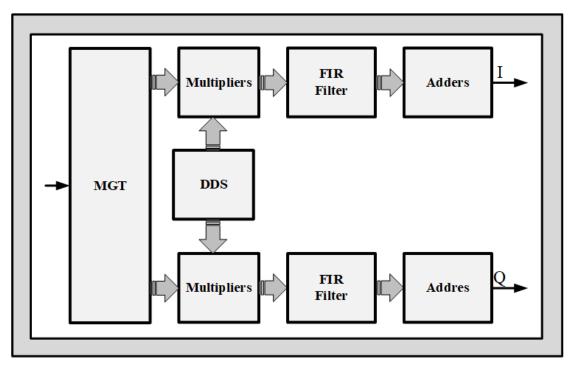

To achieve the solutions mentioned in the previous paragraph, many authors have pointed to Cloud Radio Access Network (C-RAN) as an enabler for the densification of base stations and for the increase in bandwidth [4]. C-RAN is divided into three blocks: the Baseband Unit (BBU), the fronthaul and the Remote Radio Head (RRH). Figure 1.3 is a depiction of a typical C-RAN architecture, where the BBU is connected to one or several RRHs through the frontahul. The BBU is responsible for the baseband processing and the routing of the data to and from the core network. The fronthaul is normally based on an optical fibre or microwave link, however, there are research to make a packages based fronthaul using ethernet. Some of the more conventional architectures for fronthaul implementation also use analog radio over fibre, Common Public Radio Interface (CPRI) or Evolved Common Public Radio Interface (eCPRI) to transmite data between the BBU and RRH. Finally, the RRH is responsible for receiving and sending data to the fronthaul and for the amplification and radiation. This centralized architecture allows for one BBU to control several RRH, which allows for savings in the BBU regarding the air conditioning, site rent and also for a more effective use of the BBU's computational resources. The reduced cost of the RRH makes its massive deployment a possibility, essentially enabling the densification of base stations that was mentioned in the previous paragraph. Despite these advantages, the CPRI architecture presents a few characteristics that may present some challenges and in this work, the focus will be those presented by the fronthaul, where a flexible and low cost solution is needed. Some authors have pointed to a solution based on All-Digital Transmitters (ADT) with a Radio over Fibre (RoF) connection to the RRH [5,6]. In this work an implementation based on this concept will be implemented and tested.

ADTs are an attempt of reaching the ideal Software Defined Radio (SDR) concept intro-

Figure 1.3: Cloud radio access network architecture.

duced by Mitola [7] and have been proposed as an alternative for the traditional transmission chains [8,9]. Facilitated by the rapid rise in capacity of FPGAs, ADTs have become an hot topic [10–16] and many improvements have been made in order to reduce their size and power consumption, while delivering a larger bandwidth and more flexibility in terms of carrier frequency and waveforms. These improvements made to the ADTs are in line with the core problems to be addressed by 5G. The gain in popularity of ADTs had another consequence in the increased number of their use cases and now they can vary from a simple way of replacing a conventional Digital-to-Analogue Converter (DAC) and Radio Frequency (RF) mixer [9], to a noise and dispersion resilient way of transmitting an RF signal through optical fibre [5]. The architecture of an ADT can be seen in Figure 1.4. The ADTs architecture is composed of a baseband processing block, a pulse encoder and an upconverter. In the baseband processing block the received data is divided in the I and Q signals that are than sent to pulse encoder where the *m*-bit data is transformed into an 1-bit equivalent that is then upconverted to RF in the upconversion block. The pulse encoder can be designed based on Pulse-width Modulation (PWM) or Delta-sigma Modulation ( $\Delta \Sigma M$ ). Pulse encoders based on PWM are simpler, while  $\Delta \Sigma M$  based pulse encoders present higher performance at the cost of a higher resource usage.

As mentioned above, the use of optical fibre transmission in conjunction with ADT has already been proposed and some literature have been publicized. In [5], a practical experiment was designed to test the feasibility of such architecture. In the end, the authors of that paper concluded that the use of ADT to create a simple RoF RRH was not only feasible, but also presented characteristics that benefit the signal's propagation in the optical fibre. This type of architecture shows promising features for the use in an optical fronthaul application, and as such some of this work will be dedicated to it.

Another advantage of combining an ADT with optical fibre is the possibility of using optical upconversion in order to migrate the signal created in the ADT into the Millimetre Wave

Figure 1.4: All-digital transmitter architecture.

(mmWave) band. This technique can reduce the complexity when creating an upconverter. This is due to this technique being simpler than a radio frequency mixer for this band.

#### 1.2 Objectives

The general objective of this work is the creation of a fronthaul based on delta-sigma modulation with transmission over optical fibre. To achieve this goal, several smaller objectives, or milestones have been created in order to have a guideline as well as a mean of evaluating the development of the work. Those milestones were the following:

- Creation of an all-digital transmitter based on delta-sigma;

- Incorporation of optical fibre transmission in the created transmitter;

- Creation of a receiver for the all-digital transmitter (all-digital receiver);

- Incorporation of both, the transmitter and receiver, in the same project;

- Addition of fibre transmission between the transmitter and receiver.

For the second milestone, several fibre transmission techniques were explored. Two of those techniques will be presented in this document because they provide a easy way of upconverting the signal from an ADT into the mmWave band. These techniques also resulted in publications which will be describe in the next section.

Finally, with the achievement of all these milestones the author produced an optical fibre point-to-point link with an ADT based on  $\Delta \Sigma M$ .

#### **1.3** Publications

The work done in the scope of this dissertation resulted in the publication of some papers that focused on the use of ADTs paired with optical upconversion and transmission in order to create transmitters to be used in C-RAN scenarios. The two published papers are listed bellow: • Millimetre-Wave Real-Time All-Digital Transmitter with Electro-Optical Upconversion

S. S. Pereira, A. Lourences-Riesgo, D. C. Dinis, A. S. R. Oliveira, J. N. Vieira, and P. Monteiro in ICTON 18 - International Conference on Transparent Optical Networks, pp. 1-4, July 2018.

In this first paper, an optical upconversion technique is used to upconvert the signal from the ADT into mmWave frequency band. Several carrier frequencies were tested from 27 GHz to 63.2 GHz, proving the flexibility of the architecture in terms of the range for the carrier frequency. This technique greatly reduces complexity when compared to transistor based upconverters for this frequency band, while maintaining an equal or higher carrier frequency flexibility.

#### • Real-Time FPGA-Based Delta-Sigma-Modulation Transmission for 60 GHz Radio-over-Fiber Fronthaul

A. Lourences-Riesgo, S. S. Pereira, D. C. Dinis, J. N. Vieira, A. S. R. Oliveira, and P. Monteiro in ECOC 18 - European Conference on Optical Communications, pp. 1-3, September 2018.

In this paper, a working fronthaul based on radio over fibre is presented with upconversion to 60 GHz. This upconversion is used to sift the signal from an ADT into the mmWave band. The use of an ADT in conjunction with optical upconversion has the potential to significantly reduce the RRH complexity when used in a C-RAN scenario. This potential comes from the fact that when the signal reaches the RRH the upconversion happens in the photodiode and the recovery of the original signal from the ADT only needs a bandpass filter. At this point the signal is ready to be amplified and transmitted.

Also in the scope of this dissertation, the work done resulted in an invitation to present at the Vehicular Technology Conference, VTC2018-Spring. The presentation was entitled "C-RAN Enabled Lab Testbeds (from CPRI to Ethernet)" and it was focused on the Flexicell testbed and the subsequent work lines that were in development. Among one of those work lines is the work that was developed during this dissertation, specially the use of ADTs with optical fibre transmission in order to build an all digital based optical fronthaul.

Both the above mentioned publications, as well as the remaining of the work done during this dissertation resulted in the following major contributions:

- Utilization of ADT to the implementation of a point-to-point link;

- Development of two optical upconversion architectures capable of being used with ADT.

#### **1.4** Document Organisation

This dissertation is divided into five chapters. Chapter 1 presents the background, motivations and objectives for this dissertation, it also presents the publications that resulted from this work.

Some concepts that will be needed for a complete understanding of this dissertation are reviewed in chapter 2.

In chapter 3 the simulation and implementation of the optical point-to-point link will be explained. At the end of this chapter there will be a section dedicated to the analysis of the results.

Chapter 4 introduces two different optical upconversion architectures. The two architectures are compared and practical results of both are shown and analysed.

Finally, chapter 5 draws some conclusions about this work and sets some guidelines for possible future work.

Additional information about the implementation of the point-to-point link can be found in Appendix A at the end of this document. In there, the reader can find more details about how the transmitter and receiver were implemented using System Generator.

## Chapter 2

## Background

#### 2.1 Introduction

For a more easy understanding of this dissertation, this chapter presents an overview of some concepts that will be the focus of this work. Starting by an introduction to the ADTs that will contain a description of a typical architecture and a more in-depth review of two types of pulse encoders used, the PWM and the  $\Delta\Sigma M$ . Then, there will be a brief introduction to the concept of radio over fibre accompanied by a theoretical description of some modulation techniques, some modulators and some optical amplifiers. Finally, a section entitled "Practical Considerations" will introduce some concepts such as the concept of Multi-Gigabit Transceiver (MGT) and the importance of using a polyphase implementation instead of a monophase one. Also in this section, the concept of Error Vector Magnitude (EVM) will be reviewed due to its large importance when analysing the results.

#### 2.2 All-digital Transmitters

There are several drivers behind the rise in the adoption of ADTs and one of the most important is the ability of an ADTs to implement a compact radio transmission chain, missing only the amplifier and the bandpass filter. Figure 2.1 has a depiction of a radio transmission chain based on an ADT. Another driver that favours the adoption of ADTs is the capacity of rapid reconfiguration, which makes possible the use of a single ADT to be able of transmitting and receiving several protocols with a vary wide range of characteristics such as different frequency, different bandwidth and different coding. This flexibility of the ADT paired with

Figure 2.1: Transmission chain using an ADT, based on Fig.1 from [12].

the huge capacity of FPGAs allows for the saving in resources, both in capital expenditures and operational expenditure, by not only allowing for a single FPGA to implement several ADT that can be reconfigured as needed, but also because systems not being used can be shut down or passed to other FPGAs which are less occupied.

ADTs, as briefly mentioned in chapter 1, are comprised of three blocks, a baseband processing block, a pulse encoder block and an upconverter block. The relative position of these last two blocks determine if the ADT is an baseband-stage modulator or an RF-stage modulator. If the pulse encoder is placed before the digital upconversion block, the modulator is called a baseband-stage modulator, case depicted in Figure 1.1, when the pulse encoder is placed after the upconversion block, the modulator is called an RF-stage modulator. The choice between the two cases significantly influence the properties of the final ADT. While an RF-stage modulator may presente challanges in terms of layout and timing constrains due to its high sampling rate pulse encoders, according to the state of the art, this is the only configuration that can give some agility in terms of carrier frequency [12]. On the other hand, the use of a baseband-stage modulator can significantly reduce the time and costs of building an ADT. However, the use of a traditional upconversion stage would not maintain the constant envelope presented in the output signal of the encoder block. This problem can be solved by choosing the carrier frequency as one fourth of the serializer's sampling frequency [12]. In this specific case as  $fc = \frac{1}{4}fs$ :

$$e^{\frac{j2\pi fc}{fs}n} = e^{\frac{j\pi}{2}n} = \cos(\frac{\pi}{2}n) + j\sin(\frac{\pi}{2}n)$$

(2.1)

and,

$$\cos(\frac{\pi}{2}n) = [1, 0, -1, 0], n \in [0, 1, 2, 3]$$

(2.2)

$$\sin(\frac{\pi}{2}n) = [0, 1, 0, -1], n \in [0, 1, 2, 3]$$

(2.3)

the final upconversion to this frequency is equivalent to do a replica of the I and Q samples and then arrange the output word in the form:  $[I, \overline{Q}, \overline{I}, Q]$ . With this technique the constant envelope of the signal is preserved.

Nowadays the main research focus is on the pulse encoder and despite the existence of many techniques that can be used in an ADT. Due to their efficiency, PWM and  $\Delta\Sigma M$  are the two most used techniques [17]. These type of pulse encoding techniques rely on oversampling the original signal and then reducing its levels of quantization to a one bit representation. More than one bit representations exist and are applied when a better signal quality is required [18]. In the next sections a brief description of PWM and  $\Delta\Sigma M$  will be presented alongside some advantages and disadvantages of each technique.

#### 2.2.1 Pulse Width Modulation

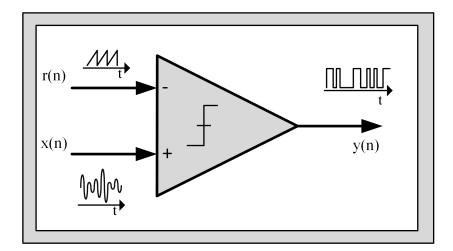

The PWM technique is based on the comparison between the input signal, x(n), and the reference signal, r(n), normally a sawtooth or triangular wave, which results in a two level output signal. Figure 2.1 depicts the working principle of a PWM. In the digital implementation this comparison is really easy to perform and, as long as the input signal has been oversampled, the output contains a good representation of the original signal, which can be recovered using a low-pass filter. The oversampling ratio is a key factor for a good performance of a PWM and the higher it is the better the final result will be. This improvement in the quality

Figure 2.2: Pulse width modulation.

of the output signal is mainly due to the reduced noise floor caused by the oversampling ratio, but there is another advantage of using a higher sapling frequency, which is that, in the frequency domain, the harmonics of the square wave signal are further apart from the original signal making it easier to low-pass filtering the signal. In a practical implementation it is not always possible to increase the sampling frequency, especially when dealing with broadband RF signals. In these cases, polyphase implementations can be used to reduce the clock rate of each phase while maintaining the desired equivalent sampling rate. This approach has the disadvantage of increasing the total digital logic used [17].

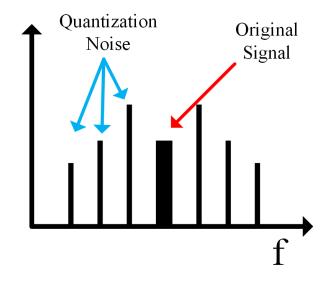

In an ADT implementation, the output signal should have as low noise as possible to reduce the analogue filter requirements. When a PWM-based pulse encoder is used in an ADT, the output signal's spectrum contains not only the original signal's spectrum, but also the harmonics of the square wave of the PWM. A typical PWM spectrum can be seen in Figure 2.2, in it, the quantization noise can be seen in both sides of the original signal's spectrum. This type of output signal's spectrum is not ideal because it requires an analogue filter with an high quality factor. A technique to reduce these harmonics was introduced in [19] and it was able to reduce the first harmonic in more than 50 dB without introducing more complexity than was previously present in a typical PWM based ADT. The solution consists in dividing the time in which the signal is on,  $t_{on}$ , in smaller blocks while preserving the relation  $t_{on}/T$ , where T is the period. This essentially creates square waves with a smaller period and it is known that square waves with smaller period have their harmonics in higher frequencies, away from the original signal's spectrum.

Other state of the art implementations allow for a continuous adjustment of the carrier frequency in the digital domain [12], giving an extra point of flexibility to the ADT. In that paper, the authors were able to achieve a frequency agility in the range from 100 MHz to 6.2 GHz with a frequency resolution of 1.5625 MHz. This kind of frequency agility may be useful for sub-6 GHz 5G applications.

Figure 2.3: PWM typical spectrum.

#### 2.2.2 Delta-Sigma Modulation

Another technique that is very used in the literature as a pulse encoder for ADTs is the delta-sigma modulation. This kind of modulation relies in most of the same principles as PWM, such as oversampling the original signal followed by a reduction in bits per sample. Despite these similarities,  $\Delta \Sigma M$  presents some advantages such as a good SNR, scalability and the general lower quantization noise levels near the desired signal, which makes possible to relax the analogue filtering [12]. This is essential for a good ADT implementation.

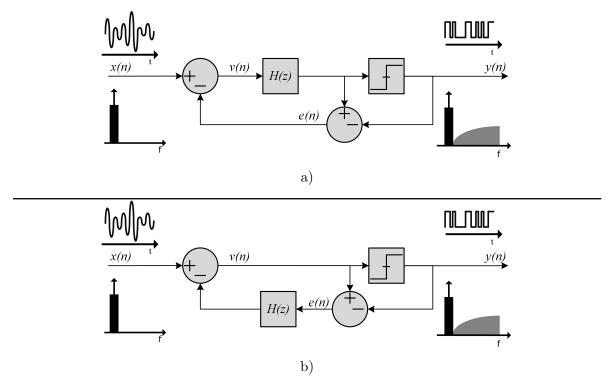

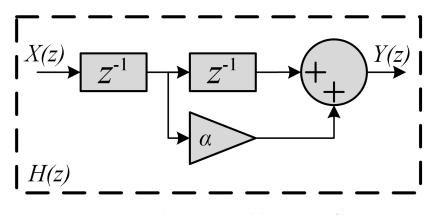

$\Delta\Sigma$ M relies on an error feedback to reduce the added quantization noise to the signal band. This reduction in the quantization noise present in the signal band is determined by the filter, which applies a shaping mechanism to the noise. The type of noise shaping created by the filter imposes the maximum signal bandwidth to a specific Signal to Noise Ratio (SNR). In Figure 2.4, two topologies of a  $\Delta\Sigma$ M are depicted, one with the filter in the feed forward path, a), and other with the filter in the feedback, b). Both are called error feedback structures, because there is a path that feeds the error back into the input. Due to its simplicity these architectures are very attractive for the digital loops of  $\Delta\Sigma$ M [20]. The two topologies have different frequency response characteristics due to the position of the filter. In the figures the input signal is represented by x(n), the output signal is represented by y(n), the filter is represented by H(z) and the error signal is represented by e(n). Considering the z-transform of x(n), v(n), e(n) and y(n) as X(z), V(z), E(z) and Y(z), respectively, the frequency response of the modulator depicted in Figure 2.4 a) can be determine by the following equations:

$$V(z) = X(z) - E(z)$$

(2.4)

$$E(z) = V(z)H(z) - Y(z)$$

(2.5)

substituting V(z) in 2.5 for the one calculated in 2.4, the frequency response of the output

Figure 2.4: Delta-sigma modulation with: a) filter in the feed forward; b) filter in the feedback path.

signal is:

$$Y(z) = X(z)H(z) - E(z)(1 + H(z)) = STF(z)X(z) - NTF(z)E(z)$$

(2.6)

The modulator represented in Figure 2.4 b) has a slightly different frequency response, but the core equations which describe its behaviour are almost identical:

$$V(z) = X(z) - E(z)H(z)$$

(2.7)

$$E(z) = V(z) - Y(z)$$

(2.8)

substituting V(z) in 2.8 for the one calculated in 2.7, the frequency response of the output signal is:

$$Y(z) = X(z) - E(z)(1 + H(z)) = STF(z)X(z) - NTF(z)E(z)$$

(2.9)

Doing a quick comparison between equation 2.6 and 2.9, it is easy to notice the difference, i.e., in 2.6 the input signal X(z) comes multiplied by the filter, H(z), while in 2.9 the input signal is unaltered, this makes the Signal Transfer Function (STF) in equation 2.6, STF(z) = H(z), while in the equation 2.9, STF(z) = 1. Having a STF equal to one means that the signal does not suffers any alteration in the modulator, apart for any delay caused by the adders or by the quantizer. This is very useful when the signal is already in the desired form to be transmitted and only the pulse encoding modulation is missing. In the other hand, having a filter in the feed forward may allow for a simultaneous filtering and pulse encoding of the signal. However, in this case the design of the filter may be more difficult in order to ensure not only the correct noise shaping but also a good filtering of the signal. Analysing now the Noise Transfer Function (NTF), it can be seen that it is the same in both equations, 2.6 and 2.9. This means that both implementations will have the same noise shaping characteristics provided that they have the same filter.

One of the most important characteristics to have in mind when designing a  $\Delta\Sigma$ M is the type of noise shaping that the final implementation will have. As was referred before, the filter is the main block responsible for the NTF and it is possible to derived the type of noise shaping by analysing the NTF. From equation 2.6 or 2.9, it was concluded that the NTF provided by the topologies depicted in Figure 2.4 has the form: NTF(z) = 1 + H(z). With this equality, the filter can be calculated to have the desired frequency response. One of the independent variables that are available for the designer is the order of the filter. A higher order filter will present a more abrupt noise cancellation pattern and also a larger notch, which allows for more useful bandwidth and higer signal quality also known as Signal-to-Quantization Noise Ratio (SQNR). Of course, that choosing a higher order filter modulator will have an increase in the total amount of resources used as well as an increase in the time and effort needed to make the implementation. The implementation of a higher order filter in a  $\Delta\Sigma$ M is a well studied subject [20] and many implementations like the cascade Multi-Stage Noise shaping (MASH) structure have already been successfully implemented [12, 14].

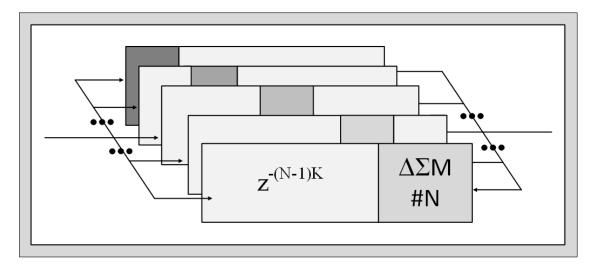

The search for more bandwidth while maintaining a high SNR has lead researchers to increase the sampling rate of the  $\Delta\Sigma$ M. This quickly reached the limit imposed by the clock rate of the digital systems and new solutions were developed in order to increase the sampling rate of the modulator, while maintaining a relative low clock rate. One of these solutions was the use of a multi-core  $\Delta\Sigma$ M. This solution, while looking simple at fist, imposes some challenges such as how to maintain the temporal continuity in the samples processed by each  $\Delta\Sigma$ M core and how to make the initial conditions of each  $\Delta\Sigma$ M core be the same as the core which had computed the previous samples. The first problem was addressed in [21], where two blocks called deinterleaving and interleaving make sure that each core was fed with k samples with time continuity. However, this means that in every k samples a discontinuity in the state of the core  $\Delta\Sigma$ M would occur. This discontinuity causes a decrease in performance by introducing noise spikes in the time domain. This problem was solved in [14] by the introduction of a block called "Synchronous Start-up Control Logic". This block is responsible for saving the final state registers of every modulator and pass it to the next one. This operation occurs every k samples.

Many researchers have been made improvements to  $\Delta\Sigma$ M's figures of merit such as bandwidth [16], SNR [14], and frequency agility [12], others improvements in these figures of merit may be possible with the implementation of techniques such as the lock-ahead time interleaved  $\Delta\Sigma$ M [15] and the borrow-save logic [22]. These techniques will not be explored in this work.

#### 2.3 Radio over Fibre

RoF consists in the modulation of a light source, typically from a laser, with an RF signal, which is then propagated through an optical fibre. The large bandwidth offered by optical fibre made this technique very attractive. This has enabled optical fibre to dominate modern telecommunications, with applications in longhaul (core network, metropolitan network and access network), fronthaul (from the antenna to the base station and in C-RAN scenarios),

Figure 2.5: Optical direct modulation.

inside servers and more recently even inside buildings, offices and homes.

The modulation in a RoF scenario has two main methods, direct modulation and external modulation [23]. Each method has its own advantages and use cases. The direct modulation is the cheapest of the two and it's applied for low bit rate and low distances of transmission. The external modulation presents a better performance in terms of extinction ratio, which is the relation in terms of power between the on and off state, and also allows for complex modulation, which increases the spectral efficiency at the expense of cost.

The use of a direct modulation allows for a simple and cheap implementation of a RoF. Figure 2.5 illustrates the working principle of a direct modulation. The use of an LED makes its implementation very cheap and easy, while also making it reliable when used for low bit rates applications. However, the use of direct modulation using a led is only aplicable in very specific scenarios such as visible light applications. The more typical aplications use a laser such as a VCSEL in order to increase bit rate without adding too much complexity and cost. However, most of these cheap lasers work at a wavelength of 850 nm and at this wavelength transmissions over long distances are not possible. In order to increase the transmission distance it is needed to switch the VCSEL at 850 nm to another laser with an wavelength in the 1550 nm range. This might increase the cost and potentialy making the implementation harder. However, it allows for the transmission over large distances and also enables the transmission of larger data rates, both by increasing the symbol rate and by using higher order modulations. The versatility achieved with this modulation called for a lot of attention and soon various use cases for this technique started to emerge. In radio communications, this enabled the start of the C-RAN research [5], which now has evolved to use more complex modulations schemes due to the ever growing demand for larger bandwidth and to enable the use of optical upconversion to reach the millimetre wave band needed for 5G [24, 25]. Other areas also implemented fibre optics based solutions, and in the car and plane industry plastic fibre optics were adopted due to their electromagnetic immunity and their lighter weight compared with copper solutions [26, 27]. The biggest limitations of the direct modulated lasers are its limited bandwidth, the linearity of the laser, the lower achievable extinction ratio and the frequency chirp, which causes a spectral stretching. All these effects are related to the bias point which must be carefully selected.

Although the use of a good laser enables larger bandwidths and higher order modulations to be transmitted by direct modulation, there are cases where an even better performance

Figure 2.6: Optical external modulation.

is needed, especially when large symbol rates are to be transported through long distances. An improvement in performance can be made by switching to external modulation. This type of modulation enables the achievement of the best performance possible from the light source. The use of an external modulator also allows for an higher extinction ratio, in the case of an amplitude modulation, and it also allows for amplitude and phase modulation or just phase modulation. In the case of the amplitude modulation, the use of an electro-absorption intensity modulator allows for varying the absorption of the light in response to a voltage signal. This modulator works by changing the material absorption coefficient in function with an applied voltage. For the phase modulation the use of a phase modulator allows for a change in the phase of the signal by changing the material refractive index in function with the signal's voltage. Finally, the case which has more advantages, but is also more complex is the IQ modulation. Only with this type of modulation it is possible to achieve higher order modulations like Quadrature Amplitude Modulation (QAM) and so, despite the added complexity and cost, it is the modulation of choice for most telecommunications applications where a high performance is needed. This technique allowed for the exponential increase in the data rates of the backhaul, which enabled the construction of the modern Internet, where video streaming is already possible in both fix or mobile connections.

For the cases used in this work, amplitude modulation is the easiest modulation to implement and doesn't introduce much loss in the RF signal. This good conservation of the signals characteristics is due to the output of the FPGA being a simple two level amplitude-shift keying. For these kinds of signal a simple SFP is enough and, as will be demonstrated later, this is the modulator used for the final project. However, this modulator does not allows for more complex techniques like optical upconversion. For that reason some experiments with the ADT were done using a Mach-Zender Modulator.

A Mach-Zehnder modulator can be single-drive or dual-drive. The modulator depicted in Figure 2.7 is a single-drive Z-cut Mach-Zehnder modulator and it is made up of a phase modulator and two three dB couplers. The change in the phase of the signal in the upper arm caused by the phase modulator will interfere with the unaltered signal that travels through the lower arm. This interference is what causes the amplitude modulation part of a Mach-Zender modulator. The relation between the output power of the modulator and the input voltage V(t) is given by the following equation:

Figure 2.7: Single-drive Mach-Zehnder modulator.

$$E_o(t) = E_i(t) \frac{1 + e^{\frac{j\pi V(t)}{V_{\pi}}}}{2}$$

(2.10)

where  $V_{\pi}$  is the input voltage needed to create an 180 degrees inversion in the output signal. In this case, external modulation, the laser is not changed and so the value of  $E_i(t)$  is a constant.

Despite also being used, the single-drive Mach-Zehnder is not the most used Mach-Zehnder, this title goes to the dual-drive Mach-Zehnder. The architecture of the dual-drive is depicted in the Figure 2.8. This modulator has an extra phase modulator in the lower arm which grants it some advantages over the single-drive, like the easy determination of the RF range of the input signal to achieve the best extinction ratio. To have a better understanding, lets first look to the equation describing the change in the output according to the change in  $V_1(t)$  and  $V_2(t)$ :

$$E_o(t) = E_i(t) \frac{e^{\frac{j\pi V_1(t)}{V_{\pi}}} + e^{\frac{j\pi V_2(t)}{V_{\pi}}}}{2}$$

(2.11)

if the value of  $V_2(t)$  is change to  $V_2(t) = -V_1(t)$ , the resulting equation is:

$$E_o(t) = E_i(t) \frac{e^{\frac{j\pi V_1(t)}{V_\pi}} + e^{-\frac{j\pi V_1(t)}{V_\pi}}}{2} = E_i(t) \cos\left(\frac{\pi V_1(t)}{V_\pi}\right)$$

(2.12)

as can be seen, the resulting equation has the waveform of a cosine function. This mode of operation is called push-pull and can be very useful in the way it has no inherent chirp. This property makes the dual-drive Mach-Zehnder more appealing for high performance telecommunications when compared with the single-drive Z-cut Mach-Zehnder. However, the Z-cut is not the only single-drive Mach-Zehnder and the single-drive X-cut Mach-Zehnder is an alternative single-drive architecture that also presents no chirp [28].

In a radio over fibre implementation, after the modulation, it is normal to implement two more operations before the signal is sent to the fibre, these operations are the amplification and filtering, however, the implementation of such operations is not a rule and there are cases

Figure 2.8: Dual-drive Mach-Zehnder modulator.

where none is implemented. When implemented, such operations serves to accommodate the signal for transmission in the fibre. The amplification makes sure that the signal has enough power to travel through the fibre and reach the receiver above the sensitive power level of the photo-diode. After amplification there's always an increase in the noise floor, to remove it and others unwanted frequencies this signal must be filtered.

There are a few ways to amplify an optical signal, but the two ways that are more important for a RoF scenario are done using an Erbium Doped Fibre Amplifier (EDFA) or a Semiconductor Optical Amplifier (SOA). The EDFA amplifier uses a laser pump as a power source, the output of this laser is combined with the signal using a coupler and then both wavelengths travel through an erbium doped fibre. A different configuration of an EDFA can have the light from the pump travelling in the opposite direction compared to the light from the signal. In this configuration the coupler is placed after the doped fibre instead of before, as was the case of the previous configuration. In both configurations the coupler does not attenuate the signal because the light from the laser pomp is in a different wave length than the light that transports the signal and so the coupler can be design to have the power from both its inputs be sent to the same output. After the coupler both wavelengths travel through an erbium doped fibre, in this fibre the pump wavelength excites electrons to an upper energy levels. As the photons from the signal pass through this doped fibre with the excited electrons, stimulated emission occurs and new photons are released. These photons have the same characteristics as the ones that triggered the stimulated emission and so the final result is an amplification of the original signal. This type of amplifier has good characteristics in terms of low distortion and low added noise, this makes then the ideal choice for high performance applications. However, they tend to be expensive and bulky due to the length of dope fibre that is necessary.

The SOA amplifier relies on the same principle of functioning as a semiconductor laser, but without the reflective coating in the chamber. In a SOA, as in a semiconductor laser, a semiconductor material has its electron population inverted by an electrical source. As the

Figure 2.9: MGT's data path.

input signal travels through the chamber, stimulated emission occurs releasing new photons with the same characteristics as the ones from the input signal. Because the power source is now electrical, a SOA is much cheaper and small than an EDFA. However, SOAs tend to be more non-linear and introduce more noise. Recent developments have resolve the relative small bandwidth of SOAs when compared to an EDFA. In [29] a SOA with 100 nm of optical bandwidth is implemented and tested, achieving a data rate of 115.9 Tb/s.

# 2.4 Practical Considerations

In this section some concepts related to the implementation of the ADT will be reviewed. Starting with the concept of MGT, then the concept of polyphase implementation and finally the concept of EVM.

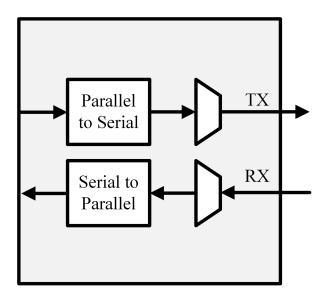

#### 2.4.1 Multi-gigabit Transceiver

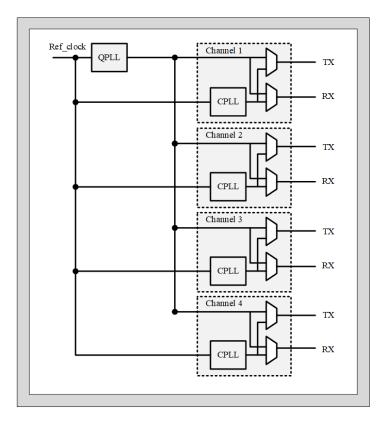

An MGT is an one-bit transceiver that can operate at frequencies higher than 1 gigabit per second. Due to its high frequency output it is normal for this blocks to incorporate both a parallel to serial converter, as well as a serial to parallel converter, as can be seen in Figure 2.9. This types of transceivers are typically arranged in groups of four transceivers called Quads. This Quads have an input clock port in order to have all MGTs being driven by the same clock source. The clock structure of an MGT's Quad can be seen in Figure 2.10.

#### 2.4.2 Polyphase Implementation

When dealing with high sampling frequency signals it is also required to have a high clock frequency. However, there is a technique that allows for the reduction of the clock frequency, maintaining the high sampling rate. This technique is caller polyphase implementation and it is essentially a way of making the processing of the signal in a parallel way. With this type of implementation the clock of the FPGA can be reduced by a factor equal to the number of

Figure 2.10: MGT's Quad's clock architecture, [30].

parallel phases used. This enabled the processing of signals with sampling frequencies in the order of GHz to be processed in FPGAs with clock running at only a few hundreds MHz.

#### 2.4.3 Error Vector Magnitude

EVM is a way of measuring the how close is a received constellation in comparison to the ideal one. During this document, the EVM measurements will be presented in percentage. This type of EVM is calculated using the following equation:

$$EVM(\%) = \sqrt{\frac{P_{error}}{P_{ref}}} \times 100$$

(2.13)

Where  $P_{error}$  is the average of the error vector power and  $P_{ref}$  is the average ideal reference vector power [31].

# 2.5 Final Remark

In this chapter some basic concepts were reviewed. These concepts will be the foundation of the work presented in this document, and despite not all of them being directly used in the final implementation they were crucial to the author's understanding of concepts such as ADTs and RoF.

# Chapter 3

# Point-to-Point Link

### 3.1 Concept

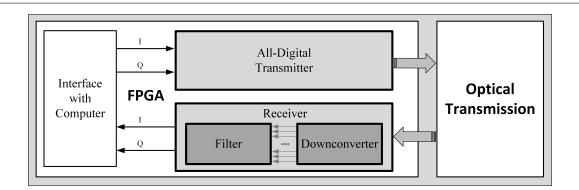

The general idea of this work is the development of an optical fibre point-to-point link with an all-digital transmitter based on delta sigma modulation. This link serves the function of the fronthaul in the implementation of C-RAN architectures for 5G. In order to have a successful fronthaul implementation, this link needs to be capable of receiving the IQ data from the BBU, modulate it, send it through the fibre and retrieve the original information in the other side, RRH. This completes the downlink path, the final implementation should also be capable of sending data from the RRH to the BBU. The maximum length of the fibre transmission is also important because it enables the placement of the RRHs several kilometres apart from the BBU.

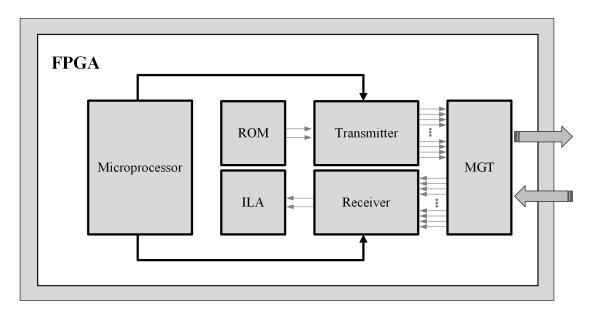

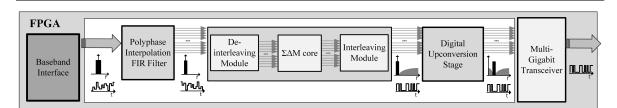

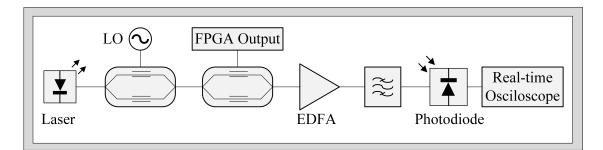

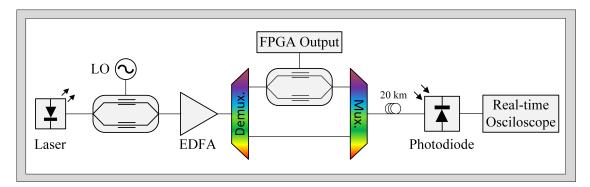

A top-level block diagram of the proposed architecture for this link can be seen in the Figure 3.1. It includes two main parts, the FPGA and the optical transmission. The implementation of the transmitter and receiver was chosen to be made in an FPGA due to its reconfigurability properties, which allied with its huge processing capacity, make the FPGA a convenient platform to test and implement the proposed architecture. Inside the FPGA there are four blocks: the interface with the computer; the all-digital transmitter; the downconverter and the filter. The last two blocks constitute the receiver. In the optical transmission an electro-optical converter is used to convert the signal from the electrical domain into the optical domain. This is followed by an optical fibre which, at the end, has an opto-electrical

Figure 3.1: Top-level architecture of the proposed point-to-point link.

Figure 3.2: ADT's architecture.

converter to return the signal from the optical into the electrical domain in order to be sampled by the FPGA.

In the following sections a detailed description of the implementation process will be discussed, starting with the modelling and simulation part, than the hardware implementation, followed by the optical link description and finally a discussion of the results. The modelling and simulation part of this work was done using System Generator. This was really important because it allowed for a quick iteration process that wouldn't be possible otherwise. This is due to the fact that System Generator runs over Matlab, which allows for a simple and fast testing, as well as an easy visualisation of the results. Another option was to use an Hardware Description Language (HDL), however, both the implementation and testing would be more difficult and time consuming. In the hardware implementation it will be discussed the choices made to the implementation, which, due to the FPGA used in this work being a Xilinx Virtex UltraScale, was done in Vivado. In this section will also be presented a description of the method used for transmitting data to and from the FPGA. In the optical link section an analysis of the optical link's architecture will be made and some other topologies will be compared to the one that was chosen for implementation. Finally, the results obtained when testing this architecture will be presented and analysed.

# **3.2** Modelling and Simulation

For a more easy understanding, this section will be divided into two subsections: one devoted to the transmitter and other to the receiver. The transmitter subsection will also be divided in topics, one for each component in the transmitter and the same will be done for the receiver.

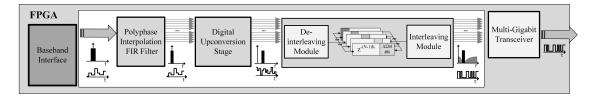

#### 3.2.1 Transmitter

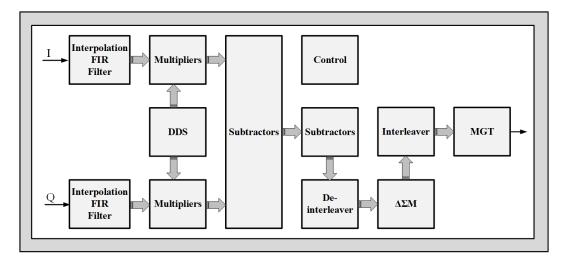

The transmitter subsection will be divided according to the blocks that constitute the transmitter: the filter, the upconverter, the de-interleaving, the  $\Delta\Sigma M$  core and the interleaving. A block diagram of the proposed ADT can be seen in Figure 3.2. The division of this subsection was made so that the order in which the blocks appear in the text is the same as the order that they are arranged in the ADT. The ADT used here is an RF-stage modulator, due to the fact that the upconverter block comes first than the  $\Delta\Sigma M$  core, used as the pulse encoder in this work.

#### 3.2.1.1 Filter

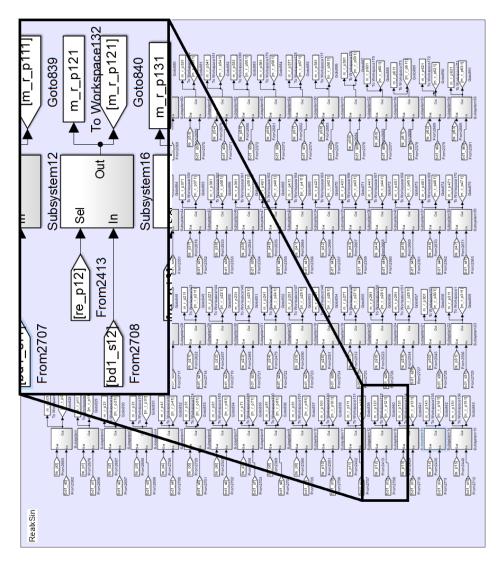

The filter in this transmitter has two functions, interpolate the signal to the sampling frequency imposed by the MGT serialization frequency, in this case 8 GHz, and filter the

Figure 3.3: Interpolation polyphase filter.

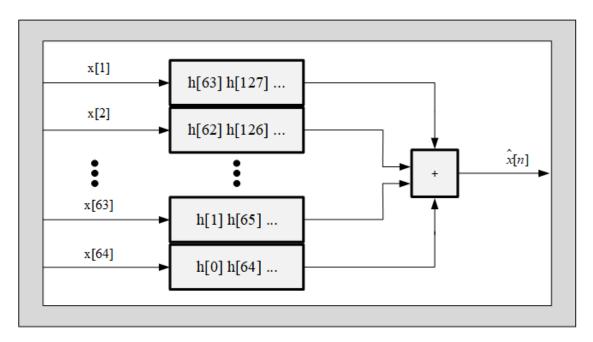

images created by this interpolation. Due to these requirements imposed on the filter, as well as the fact that the output of the filter needs to have the same number of parallel outputs as the number of  $\Delta \Sigma M$  cores, the chosen architecture for the filter was the interpolation polyphase filter. The architecture for this filter can be seen in the Figure 3.3. In it, the input signal is replicated and then fed to all the smaller Finite Impulse Response (FIR) filters, which all have specific coefficients. These coefficients originate from a larger order single phase FIR filter which was previously designed to have the bandwidth equal to the clock rate of the FPGA, 125 MHz. After the design of the original FIR filter, which must have an order satisfying: Order = n \* Number of Phases - 1, where n is a natural number, the coefficients of the original filter are distributed to the smaller filters as depicted in Figure 3.3. This rearrangement of the coefficients of the filter allows for a transformation from a single phase filter to a polyphase one. This polyphase filter has the same frequency response as the single phase with the advantage that each adder and multiplier can work at a frequency n times lower than the multipliers and adders of the single phase filter would have to work. This reduction in the working frequency is crucial to enable the implementation of such filter in an FPGA.

In the final project two filters were used, one for the in phase data (I) and other for the quadrature data (Q). The simulation results of the implemented filters can be seen in Figure 3.4. The data presented in this figure was retrieved from the System Generator using the block "To Workspace" which sends the data to the Matlab workspace. Already in Matlab the only modification done to the signals was the transformation from two real matrices into a single complex matrix followed by a reshape of the matrix into a vector, this transformation is the equivalent of a parallel to serial transformation. Referring once again to Figure 3.4, two signals are visible, one in blue, which represents the original signal given as input to the filter and other in red, which represents the output signal of the filter. Comparing both signals, an increase in the noise floor is clearly visible, but despite the perception that this increase could be a bad thing, in the end, most of it will be under the noise created by the  $\Delta\Sigma M$ , making the attempt to reduce it not a priority for this work. However, this increment in the noise

Figure 3.4: Spectrum before and after the transmitter filter.

floor does influence the performance of the ADT and its suppression could be advantageous for the accomplishment of more demanding requisites. In a closer view, it can be seen that the noise floor's increase results in a slightly decrease in SNR. A second difference between the two signals is the appearance of the two noise spikes near the pass-band. These spikes will reflect in the output, being a limiting factor in the overall performance of the ADT. Finally, a crucial difference between both signals is present in-band. This is observable by the blue stain below the red curve. This means that the filter is distorting the original signal resulting in a reduction of performance.

#### 3.2.1.2 Upconverter

After the filtering stage, the signal is divided into two signals, I and Q, this is not ideal due to the fact that it will need twice as much resources than if it was just one signal. However, the combination of the two signals can not be done in base band due to the overlapping of frequencies. A solution to this problem is presented in the implementation of this upconverter, which is depicted in Figure 3.5. As can be seen in the figure, both I and Q signals are multiplied by a sine and a cosine wave, respectively. Then the result of the multiplications is subtracted from one another. This process is equal to the following equation:

$$U(n) = \sin\left(2\pi n \frac{fc}{fs}\right) I(n) - \cos\left(2\pi n \frac{fc}{fs}\right) Q(n)$$

(3.1)

where U is the upconverted signal, fc is the carrier frequency that the signal is being upconverted to and fs is the sampling frequency. The equation results in a real signal that contains the information of both I and Q signals.

Figure 3.5: Upconverter's architecture.

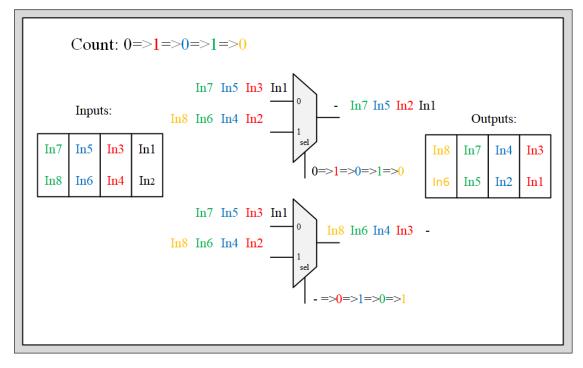

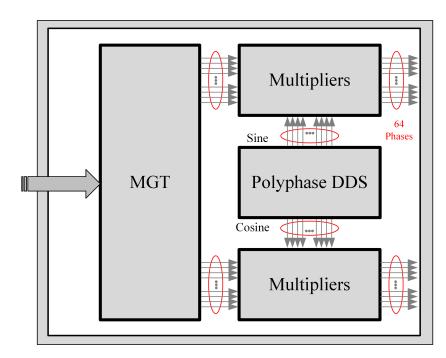

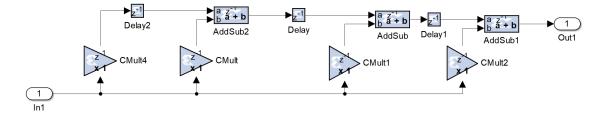

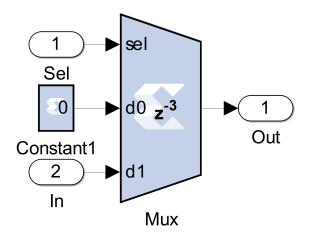

The block named Polyphase DDS, in Figure 3.5, is a polyphase implementation of a Direct Digital Syntheses (DDS). This block is constituted by 64 sub-blocks each one implementing two Read Only Memories (ROMs), one for the sine and other for the cosine wave, and their respective control logic. The implementation of one of these sub-blocks can be seen in Figure 3.6. In each of the ROMs is stored a discreet version of the sine and cosine waves. The control logic makes sure that at each clock 64 consecutive phases from the sine and cosine waves are available at the output of the polyphase DDS. Then the 64 phases of the sine wave go to the multiplication block, where 64 multipliers multiply these inputs with each phase of the I input signal by the each phase of the sine wave. The same is done for the cosine phases and the Q signal.

The Polyphase DDS block also receives a value called *Step*. This value is then fed to the

Figure 3.6: DDS ROM's implementation and control.

Figure 3.7: Spectrum after the upconverter.