**André Isidoro Prata**

Receptores de rádio-frequência melhorados e disruptivos

**Enhanced and Disruptive Radio-Frequency Receivers**

### **André Isidoro Prata**

Receptores de rádio-frequência melhorados e disruptivos

Enhanced and Disruptive Radio-Frequency Receivers

Tese apresentada à Universidade de Aveiro para cumprimento dos requisitos necessários à obtenção do grau de Doutor em Engenharia Eletrotécnica, realizada sob a orientação científica do Prof. Doutor Arnaldo Silva Rodrigues de Oliveira, Professor Auxiliar do Departamento de Electrónica, Telecomunicações e Informática da Universidade de Aveiro e do Prof. Doutor Nuno Miguel Gonçalves Borges de Carvalho, Professor Catedrático do Departamento de Electrónica, Telecomunicações e Informática da Universidade de Aveiro.

Apoio financeiro da Fundação para a Ciência e Tecnologia (FCT) no âmbito de uma bolsa de doutoramento com a referência: SFRH/BD/92746/2013.

### o júri / the jury

Presidente / president

Prof. Doutor Delfim Fernando Marado Torres Professor Catedrático da Universidade de Aveiro

vogais / examiners committee

Prof. Doutor Christian Fager

Professor Associado da Chalmers University of Technology

Prof. Doutor Marco Alexandre Craco Gomes Professor Auxiliar da Universidade de Coimbra

Doutor Sérgio Carlos Conceição Pires

Líder do Grupo de Sistemas e Conceitos Avançados da Ampleon B.V., The Netherlands.

Prof. Doutor Telmo Reis Cunha Professor Auxiliar da Universidade de Aveiro

Prof. Doutor Arnaldo Silva Rodrigues de Oliveira Professor Auxiliar da Universidade de Aveiro (orientador)

### Agradecimentos/ Acknowledgements

Em primeiro lugar quero agradecer aos meus pais, ao meu irmão e aos meus avós pela educação, valores transmitidos e apoio dado ao longo de todos os anos de estudos e formação, pois eles são a peça fundamental para que este doutoramento pudesse ter sido realizado. Agradeço também à minha namorada pelo apoio dado nesta importante fase final de conclusão do doutoramento. Aos meus amigos e colegas de laboratório pelas discussões técnicas, apoio e momentos de descontração.

Aos meus orientadores Professor Arnaldo Oliveira e Professor Nuno Borges de Carvalho, pelas discussões técnicas, conhecimento transmitido, motivação e oportunidades proporcionados.

Ao Instituto de Telecomunicações pelas excelentes condições proporcionadas ao longo da realização deste trabalho de doutoramento.

À Ampleon pelo pela colaboração e contribuições na parte final do trabalho.

À FCT pelo suporte financeiro.

Muito obrigado!

#### Palavras-Chave

Rádios Definidos por Software (SDR), Recetores Digitais, Conversores Analógico-Digital (ADCs), Pré-distorção Digital (DPD), Agregado de Células Lógicas Programáveis (FPGA)

#### Resumo

Este doutoramento endereça principalmente a componente de receção de um transcetor de rádio-frequência (RF), focando-se em arquiteturas de receção de amostragem em RF. Estas são assim consideradas como sendo as mais promissoras para o futuro, em termos de desempenho, largura de banda e agilidade, de acordo com o conhecido conceito de Rádios Definidos por Software (SDR). O estudo considera o uso dos recetores de RF em modo standalone, i.e., recebendo dados desconhecidos provenientes da antena, e também quando usados como caminho de observação para aplicação de linearização de amplificadores de potência (PAs) via pré-distorção digital (DPD), pois atualmente esta é uma técnica fundamental para aumentar o desempenho geral do sistema.

Em primeiro lugar, os conversores analógico-digital de RF são estudados e caracterizados para perceber as suas limitações quando usados em cenários de DPD. Um método de caracterização e pós compensação digital é proposto para obter melhorias de desempenho.

Em segundo lugar, um novo recetor pulsado de um bit baseado em Modulação de Largura de Pulso (PWM) e implementado em Agregado de Células Lógicas Programáveis (FPGA) é endereçado, visando agilidade em frequência, largura de banda analógica e integração de sistema, tirando proveito da implementação em FPGA. Este recetor foi otimizado com base no modelo comportamental teórico da modulação PWM, maximizando a relação sinalruído (SNR) e a largura de banda. O recetor otimizado foi posteriormente avaliado num cenário 5G de uma arquitetura C-RAN e também num cenário em que serve de caminho de observação para DPD.

Finalmente, um breve estudo relativo a caminhos de observação de DPD no contexto de transmissores multi-antena é também apresentado.

Este doutoramento contribui com vários avanços no estado da arte de recetores SDR e no conceito de SDR DPD.

#### **Keywords**

Software Defined Radio, Digital Receivers, Analog-to-Digital Converters, Digital Predistortion, Field Programmable Gate Array

#### **Abstract**

This Ph.D. mainly addresses the reception part of a radio front end, focusing on Radio Frequency (RF) sampling architectures. These are considered to be the most promising future candidates to get better performance in terms of bandwidth and agility, following the well-known Software-Defined Radio (SDR) concept. The study considers the usage of an RF receiver in a standalone operation, i.e., used for receiving unknown data at the antenna, and when used as observation path for Power Amplifier (PA) linearization via Digital Predistortion (DPD), since nowadays this represents a mandatory technique to increase overall system's performance.

Firstly, commercial available RF Analog-Digital-Converters (ADCs) are studied and characterized to understand their limitations when used in DPD scenarios. A method for characterization and digital post-compensation to improve performance is proposed and evaluated.

Secondly, an innovative FPGA-based RF single-bit pulsed converter based on Pulse Width Modulation (PWM) is addressed targeting frequency agility, high analog input bandwidth, and system integration, taking profit of an FPGA-based implementation. The latter was optimized based on PWM theoretical behavior maximizing Signal-to-Noise-Ratio (SNR) and bandwidth. The optimized receiver, was afterwards evaluated in a 5G C-RAN architecture and as a feedback loop for DPD.

Finally, a brief study regarding DPD feedback loops in the scope of multiantenna transmitters is presented.

This Ph.D. contributes with several advances to the state-of-the-art of SDR receiver, and to the so-called SDR DPD concept.

# **Contents**

| Contents                                                                     | i      |

|------------------------------------------------------------------------------|--------|

| List of Figures                                                              | iii    |

| List of Tables                                                               | vi     |

| List of Acronyms                                                             | vii    |

| 1. Introduction                                                              | 1      |

| 1.1. Background and motivation                                               | 1      |

| 1.2. Objective                                                               |        |

| 1.3. Contributions                                                           |        |

| 1.4. Document organization                                                   | 6      |

| 2. State of the Art                                                          | 9      |

| 2.1. Traditional RF receivers architectures overview                         | 9      |

| 2.2. RF ADCs                                                                 | 11     |

| 2.2.1. Comercial RF ADCs                                                     | 11     |

| 2.2.2. Pulsed architectures                                                  | 13     |

| 2.2.2.1. RF-PWM converters working principle                                 | 14     |

| 2.3. Receiver importance in a DPD scenario                                   | 18     |

| 2.3.1. DPD concept                                                           | 18     |

| 2.3.2. Receiver role in DPD scenario                                         | 19     |

| 2.3.2.1. Concurrent multi-band scenarios                                     |        |

| 2.3.2.2. Multi-antenna scenarios                                             |        |

| 2.3.3. DPD models                                                            |        |

| 2.4. Summary and concluding remarks                                          | 25     |

| 3. RF ADCs enhancement in a DPD scenario                                     | 27     |

| 3.1. Evaluation and compensation of the RF ADCs impairments' in a DPD scenar | rio 27 |

| 3.2. RF ADCs enhancement in a dual band DPD scenario                         |        |

| 3.3. Summary and concluding remarks                                          | 36     |

| 4. PWM RF receiver design and applications                                   | 37     |

| 4.1. PWM RF receiver design                                                  |        |

| 4.2. PWM RF receiver optimization                                            |        |

| 4.3. Applications                                                            |        |

| 4.3.1. Remote PWM RF receiver                                                |        |

| 4.3.1. Agile PWM-based DPD feedback loop                                     |        |

| 4.4. Summary and concluding remarks                                          |        |

| ·                                                                            |        |

| 5. Integration and assessment of DPD feedback loops for multi-antenna syste  |        |

| 5.1. Circulator free multi-antenna transmitters                              |        |

| 5.2. Brief assessment of DPD feedback loops for multi-antenna systems        |        |

| 5.3. Summary and concluding remarks                                          | 61     |

| 6. Conclusion and Future work                                                 | 63          |

|-------------------------------------------------------------------------------|-------------|

| 6.1. Conclusion                                                               | 63          |

| 6.2. Future work                                                              |             |

| Appendix – A - Additional DPD models                                          | 65          |

| Appendix – B – MGTs applied for radio receivers                               | 69          |

| Appendix – C - Published papers                                               | 73          |

| Paper C1: Improving DPD Performance by Compensating Feedback Loop Imp         | airments in |

| RF ADCs                                                                       | 73          |

| Paper J1: RF Subsampling Feedback Loop Technique for Concurrent Dua           | l-Band PA   |

| Linearization                                                                 | 79          |

| Paper C2: An agile and wideband all-digital SDR receiver for 5G wireless comm |             |

|                                                                               |             |

| Paper C3: FPGA-based all-digital Software Defined Radio receiver              |             |

| Paper C4: FPGA-based all-digital software defined radio system demonstration  |             |

| Paper C5: All-digital transceivers — Recent advances and trends               |             |

| Paper C6: All-digital Flexible Uplink Remote Radio Head for C-RAN             |             |

| Paper J2: Agile All-Digital RF Transceiver Implemented in FPGA                |             |

| Paper J3: Agile All-Digital DPD Feedback Loop                                 |             |

| Paper C7: Towards Circulator-Free Multi Antenna Transmitters for 5G           |             |

| References                                                                    | 151         |

# **List of Figures**

| Figure 1 – Block diagram of a conventional radio transceiver based on SDR architecture,                 |

|---------------------------------------------------------------------------------------------------------|

| using high speed converters and an observation path for DPD                                             |

| Figure 2 – Block diagram of conventional radio receiver architectures. (a): direct                      |

| conversion receiver; (b): IF conversion receiver; (c): RF sampling receiver                             |

| Figure 3 - Frequency domain illustration of the sampling process over different NZs 12                  |

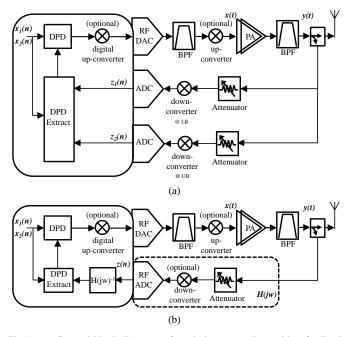

| Figure 4 –Frequency response of RF ADC ADS5400 from TI [23]. (a): Magnitude                             |

|                                                                                                         |

| response presented by TI in [23] (figure taken from [23]). (b): Magnitude and phase                     |

| response measured and presented in [20] (figure taken from [20])                                        |

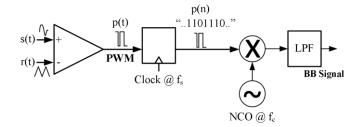

| Figure 5 - Basic block diagram of a PWM converter                                                       |

| Figure 6 – Diagram of an RF PWM converter                                                               |

| Figure 7 – Block diagram of the stochastic-ergodic converter (figure adapted from [31]). 16             |

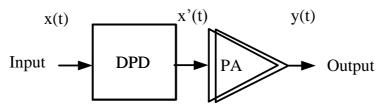

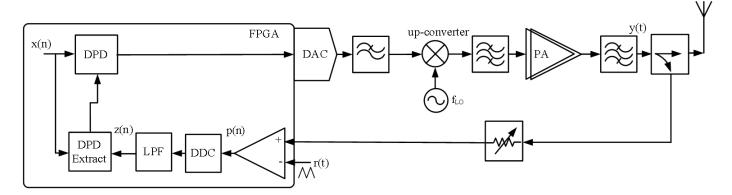

| Figure 8 – Block diagram representing the DPD concept                                                   |

| Figure 9 – AM/AM characteristic plot representing the digital predistorter block, the PA                |

| and the final linear system (DPD+PA) (a), and Spectrum before and after applying DPD                    |

| (b)                                                                                                     |

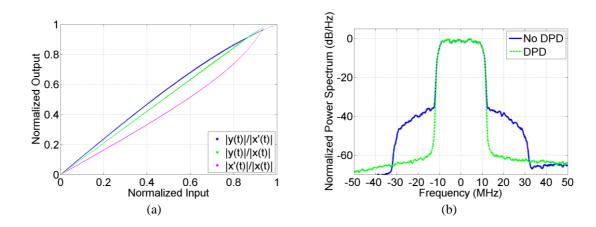

| Figure 10 - Block diagram scheme representing a transmitter with feedback loop for DPD.                 |

|                                                                                                         |

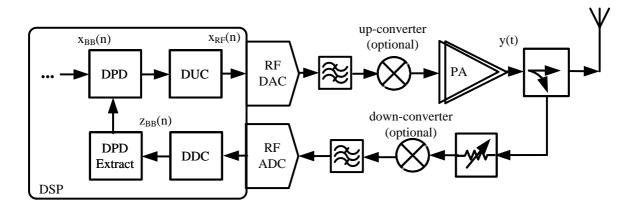

| Figure 11 - General block diagram of a dual band wireless transmitter with a conventional               |

| feedback loop for dual-band DPD                                                                         |

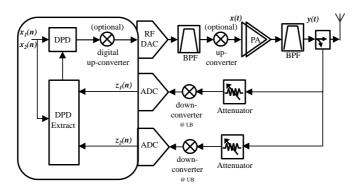

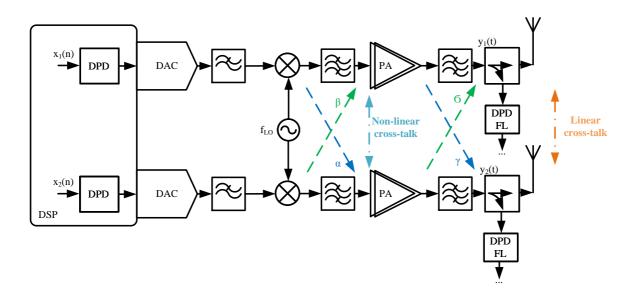

| Figure 12 - Block diagram representation of a 2×M transmitter with LC and NLC cross                     |

| talk. (figure adapted from [50])22                                                                      |

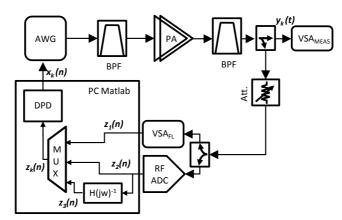

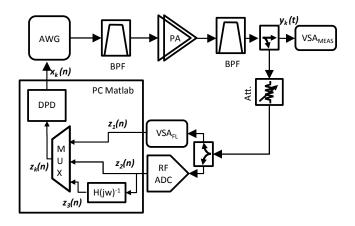

| Figure 13 - Block diagram representation of measurement setup for the evaluation and                    |

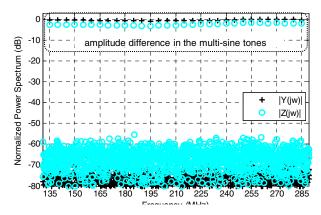

| compensation of the RF ADCs impairments in a DPD scenario                                               |

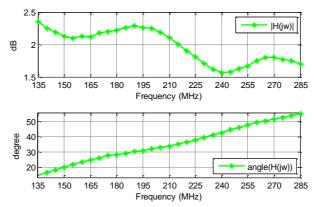

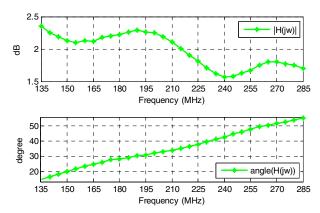

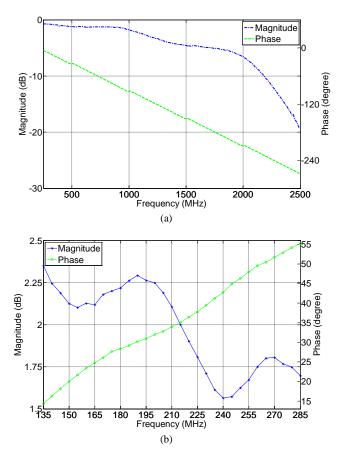

| Figure 14 - Frequency domain representation of amplitude and phase of the $H(jw)^{-1}$                  |

| compensation model. 29                                                                                  |

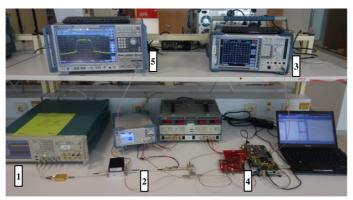

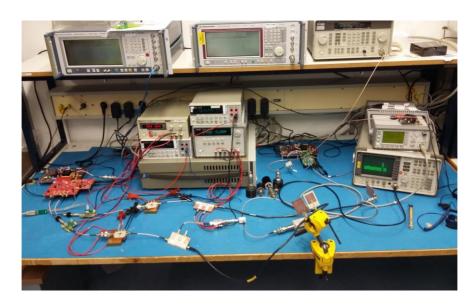

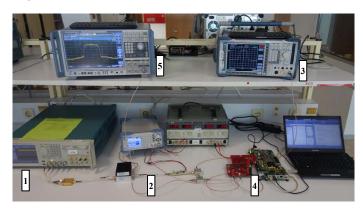

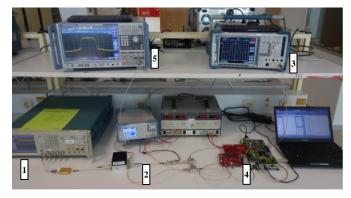

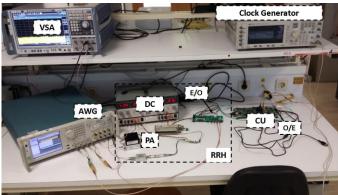

| Figure 15 - Photograph of the laboratorial setup (1- AWG; 2- PA; 3- Spectrum Analyzer                   |

| (SA) to monitor the output of the PA; 4-ADC; 5-VSA for the characterization of the                      |

| feedback loop).                                                                                         |

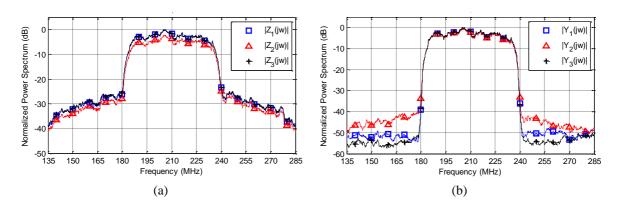

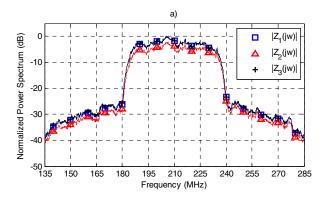

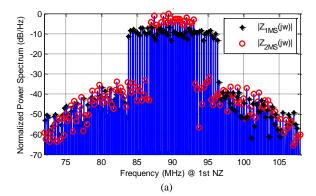

| Figure 16 – (a): Spectrum of the signals from the three feedback loops. (b): Spectrum of                |

|                                                                                                         |

| the PA output after applying DPD with each feedback loop                                                |

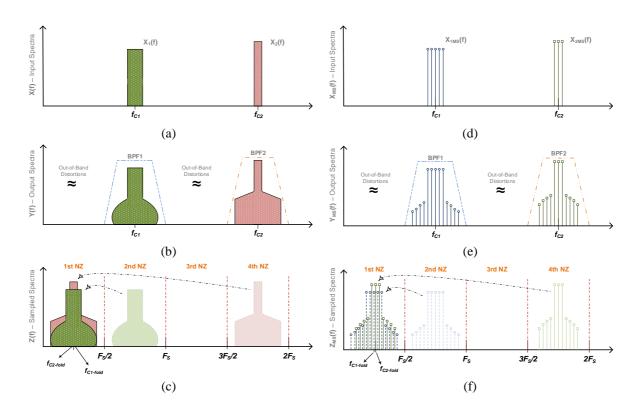

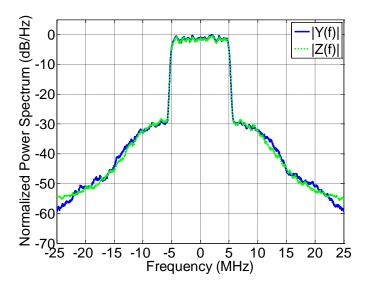

| Figure 17 - (a): Spectrum of the signal $x(t)$ at the input of the PA. (b): Spectrum of the             |

| signal $y(t)$ at the output of the PA. (c): Spectrum of the signal $z(n)$ acquired by the               |

| feedback loop. (d): Spectrum of the signal $x_{MS}(t)$ at the input of the PA. (e): Spectrum of         |

| the signal $y_{MS}(t)$ at the output of the PA. (f): Spectrum of the signal $z_{MS}(t)$ acquired by the |

| RF subsampling feedback loop. 32                                                                        |

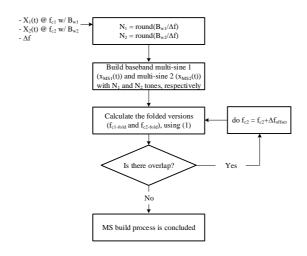

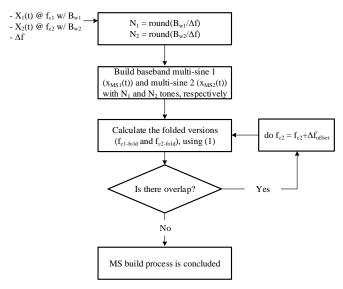

| Figure 18 - Flowchart of the procedure for the construction of the non-overlapping multi-               |

| cinac 33                                                                                                |

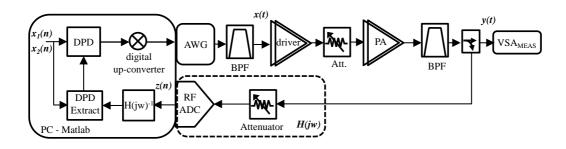

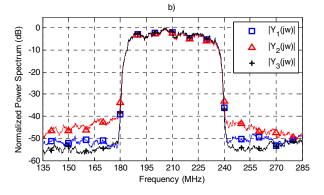

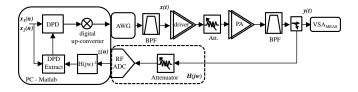

| Figure 19 - Block diagram of the measurement setup                                             |

|------------------------------------------------------------------------------------------------|

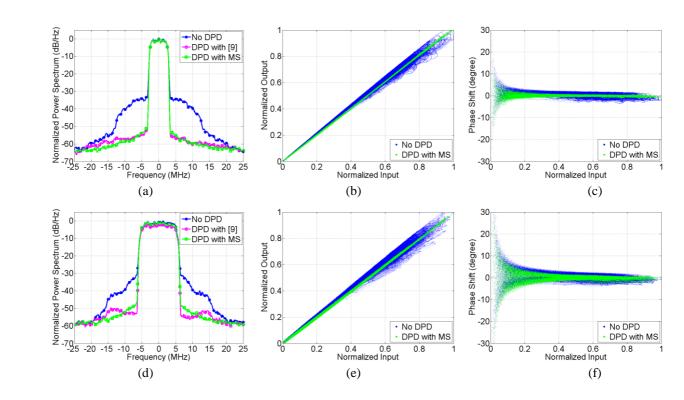

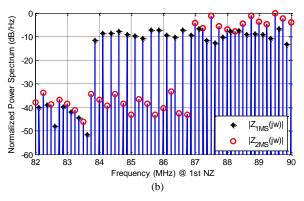

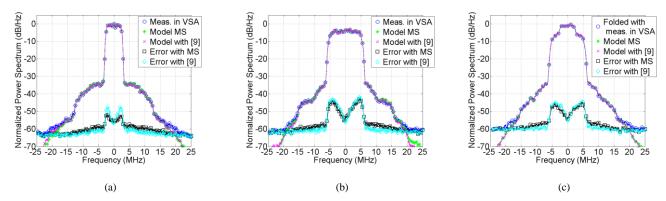

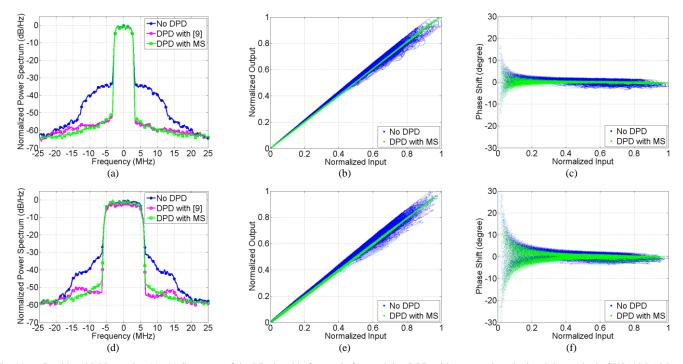

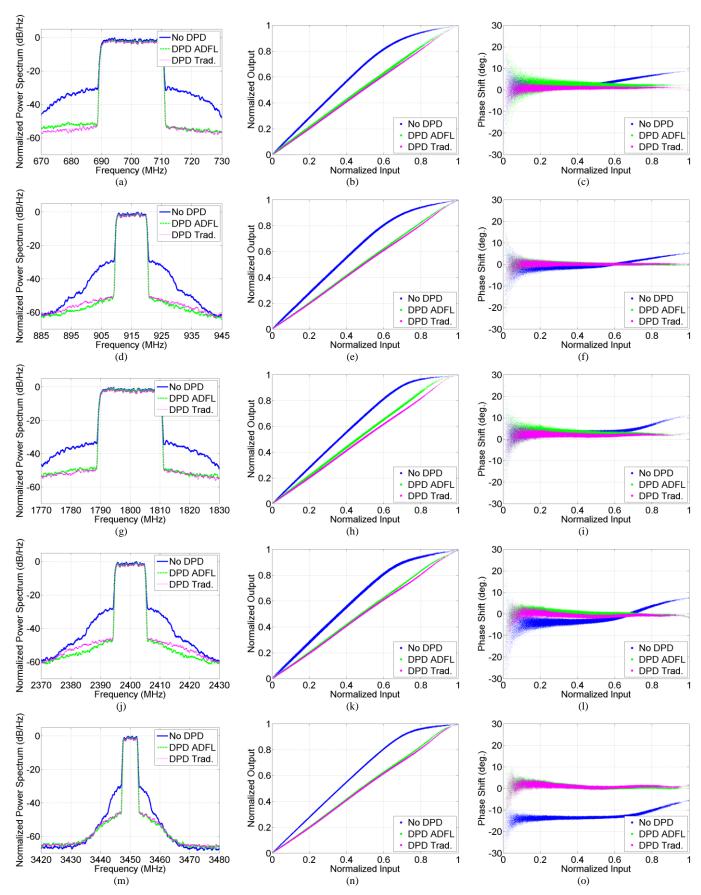

| Figure 20 - Dual band DPD results. (a)-(c) Spectrum of the LB signal before and after          |

| applying DPD with proposed method and the method of [47], AM-AM and AM-PM plots.               |

| (d)-(f) Spectrum of the UB signal before and after applying DPD with proposed method           |

| and the method of [9], AM-AM and AM-PM plots. (MS – non-overlapped statistical                 |

| · · · · · · · · · · · · · · · · ·                                                              |

| approximated multi-sine method).                                                               |

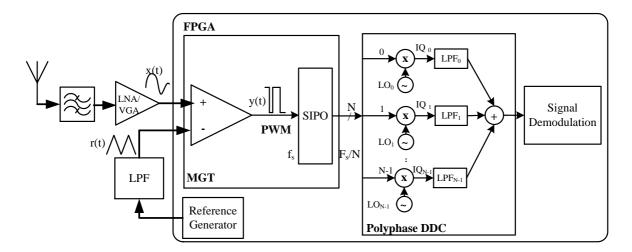

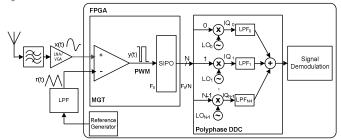

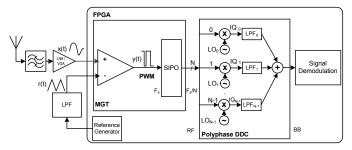

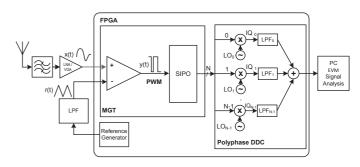

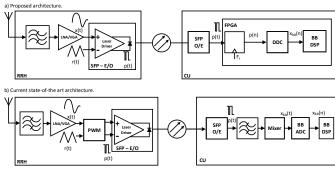

| Figure 21 - Block diagram representation of the proposed SDR architecture based on PWM         |

| using FPGA                                                                                     |

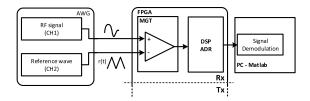

| Figure 22 - Block diagram representation of the laboratorial setup to assembled in order to    |

| validate the proposed architecture of Figure 21                                                |

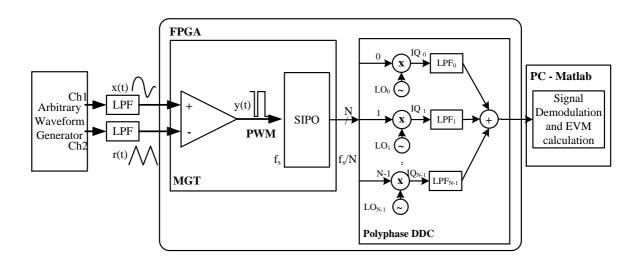

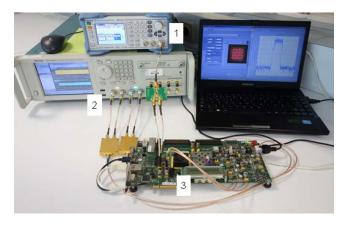

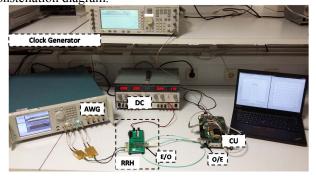

| Figure 23 - Photo of the laboratorial setup. 1 - Clock generator; 2- AWG; 3 - KC705            |

| development kit                                                                                |

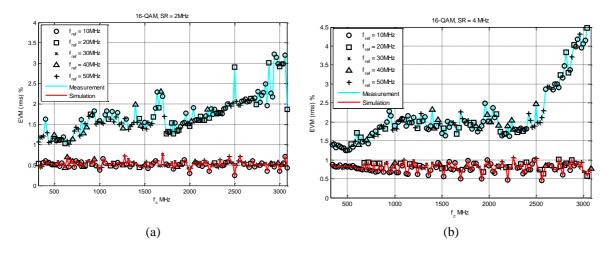

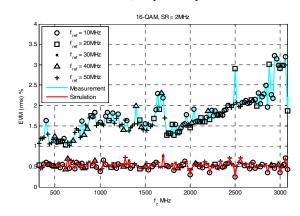

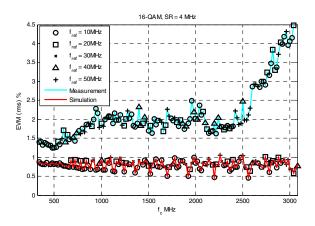

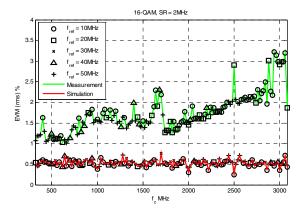

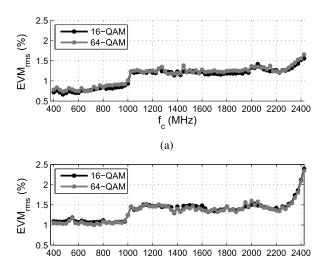

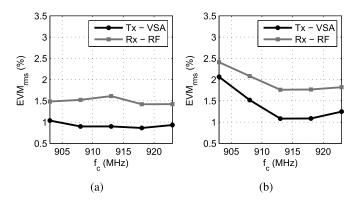

| Figure 24 - Measured and simulated results of a sweep over the carrier frequency using a       |

| 2MHz 16-QAM modulated signal (a) and 4MHz 16-QAM modulated signal                              |

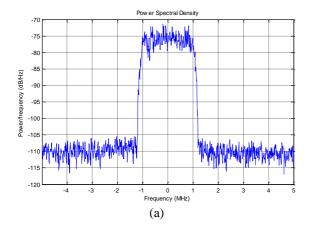

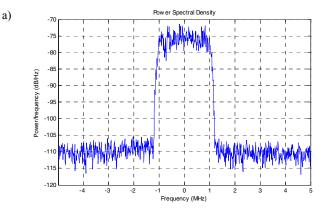

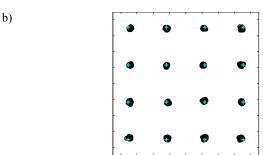

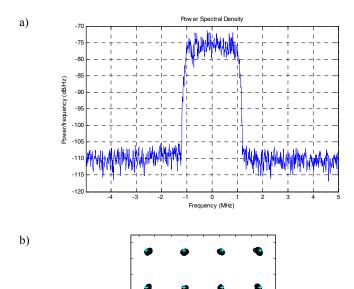

| Figure 25 – (a): Baseband frequency domain representation of an acquired 2 MHz 16-             |

| QAM signal centered at 1800 MHz. (b): Constellation diagram representation of the same         |

|                                                                                                |

| acquisition (EVM <sub>rms</sub> = $1.54 \%$ )                                                  |

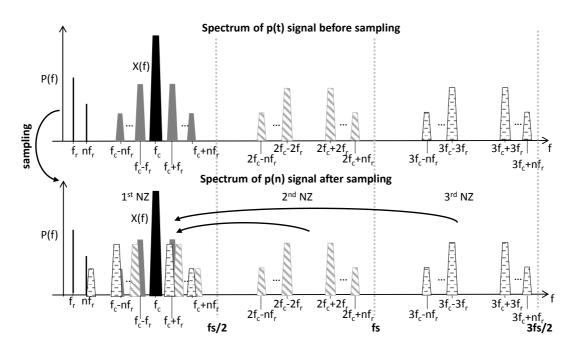

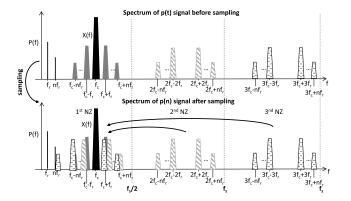

| Figure 26 - Conceptual representation of the PWM signal spectrum, in the first three NZs,      |

| before and after sampling. 42                                                                  |

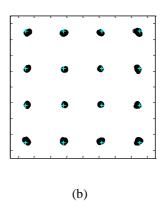

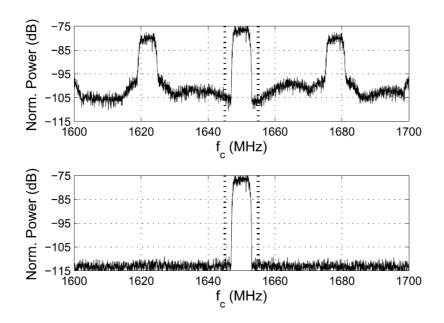

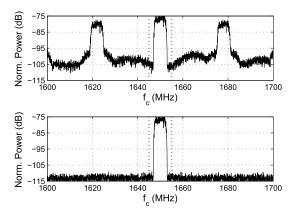

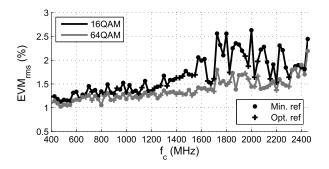

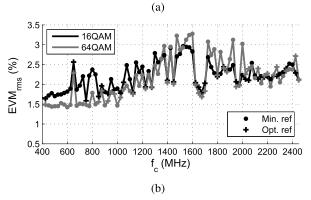

| Figure 27 - Receiver simulation results without and with best reference calculation, top       |

| and bottom plot, respectively                                                                  |

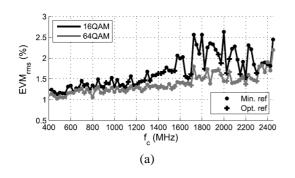

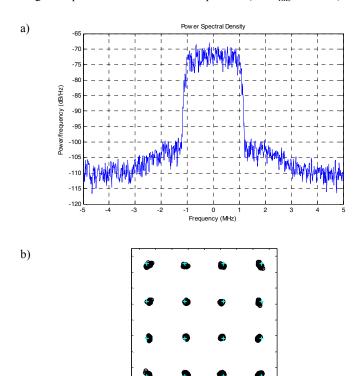

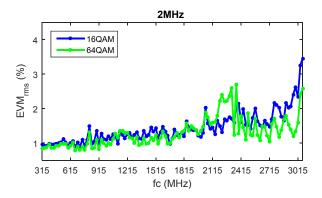

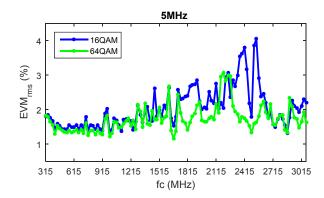

| Figure 28 - Receiver EVM measurement. (a) 2-MHz symbol rate signal. (b) 5-MHz                  |

| symbol rate signal                                                                             |

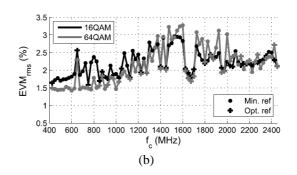

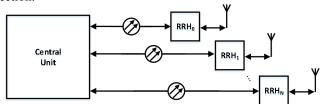

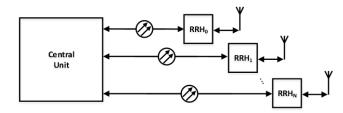

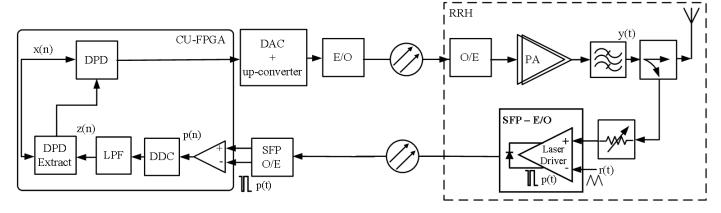

| Figure 29 - C-RAN block diagram scheme composed by a CU connected to several RRHs              |

| through an optical transport layer (fronthaul)                                                 |

| Figure 30 - Comparison between the proposed receiver architecture                              |

| Figure 31 - Photo of the implemented and measurement setup                                     |

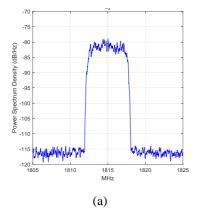

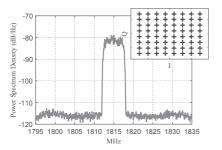

| Figure 32 - Acquisition of a 5 MHz 64-QAM modulated signal centered at 1815 MHz. (a):          |

| Frequency domain representation; (b): Constellation diagram with EVM <sub>rms</sub> of 1.43 %, |

| which corresponds to an SNR of 36.9 dB                                                         |

| •                                                                                              |

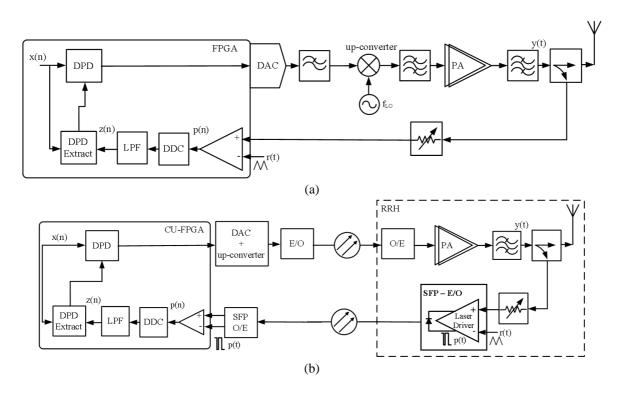

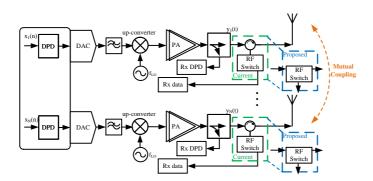

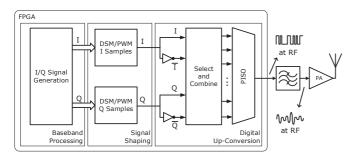

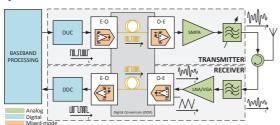

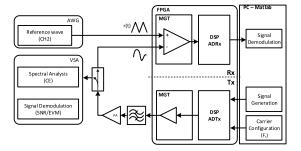

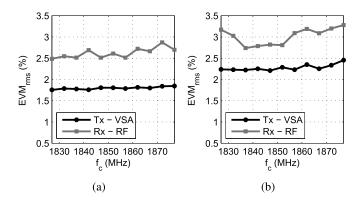

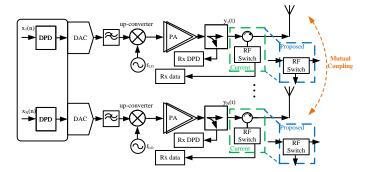

| Figure 33 - Block diagram representation of an RF transmitter with an FPGA-based all-          |

| digital feedback loop receiver for DPD. (a): feedback loop assembled in conventional           |

| architecture and (b): feedback loop assembled in remote architecture based on RRH for C-       |

| RAN                                                                                            |

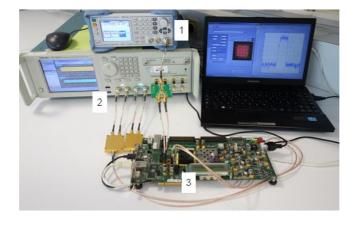

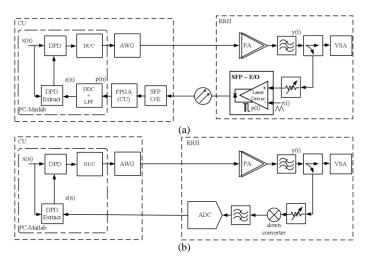

| Figure 34 - Block diagram of the measurement setup All-digital feedback loop                   |

| measurement setup (a) and photo of the laboratorial setup (b)                                  |

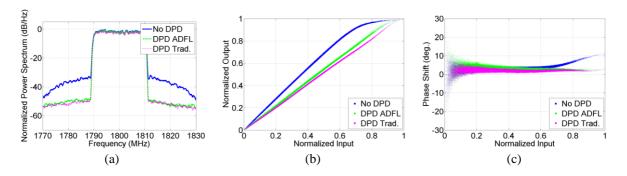

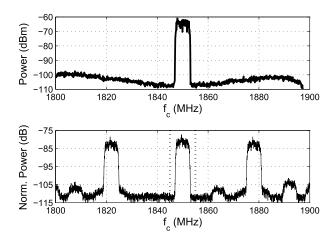

| Figure 35 - DPD results: Spectrum before and after applying DPD with ADFL and with             |

| traditional one, AM-AM and AM-PM plots. (a)-(c) Results with $f_c$ at 1800 MHz and BW          |

| of 20 MHz. [ADFL – all-digital feedback loop; Trad. – Traditional feedback loop] 50            |

| Figure 36 - Multi-antenna transmitter architecture based on conventional approach using        |

| circulators together with RF-switches, and proposed architecture using a single RF-switch      |

| (blue)                                                                                         |

| (DIUC)                                                                                         |

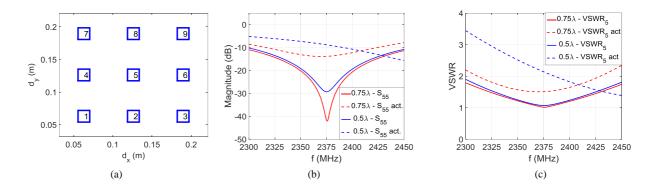

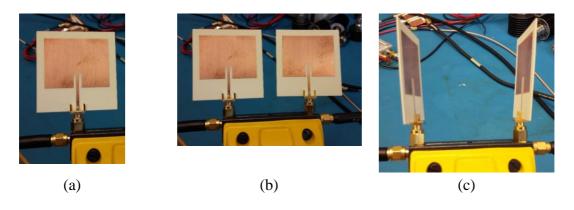

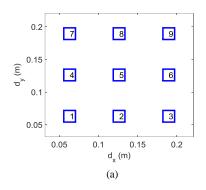

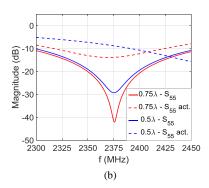

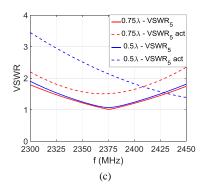

| Figure 37 – (a): 3x3 patch antenna. (b)-(c) Single element and active element (dashed line) |

|---------------------------------------------------------------------------------------------|

| input impedance in patch 5 in terms of S <sub>55</sub> (magnitude) and VSWR55               |

| Figure 38 – Photo of the multi-antenna transmitter setup                                    |

| Figure 39 - Photo of the three different configurations used for the antennas to emulate    |

| different VSWRs                                                                             |

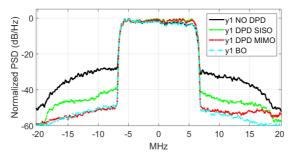

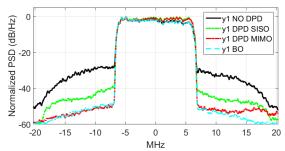

| Figure 40 - Spectrum of the signals for each different test at the coupled port 57          |

| Figure 41 – National Instruments massive MIMO platform from [65]                            |

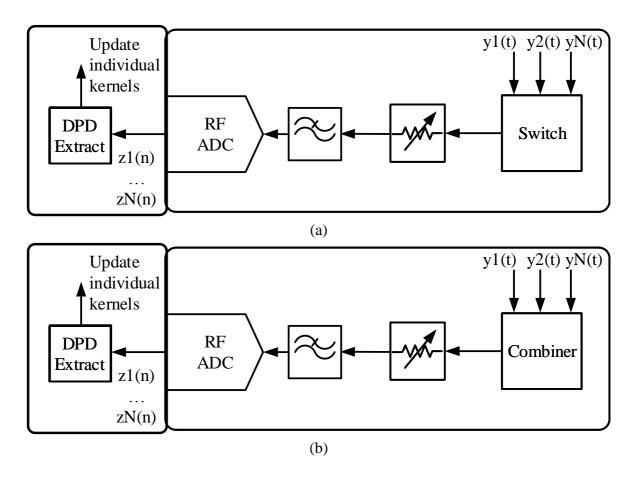

| Figure 42 – Multi-antenna transmitter with one feedback loop per PA                         |

| Figure 43 – Proposed alternatives for DPD feedback loops in multi-antenna transmitters:     |

| (a) switched feedback loop, (b) combined feedback loop                                      |

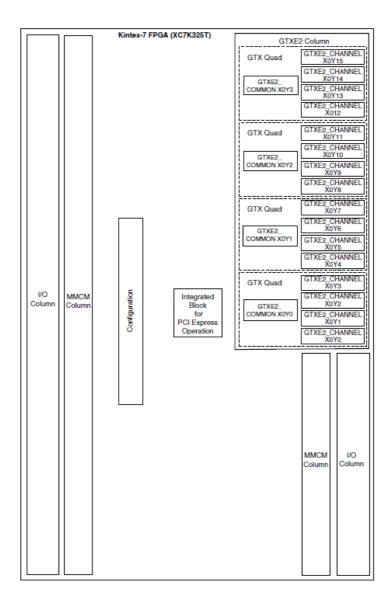

| Figure 44 - Location of the GTX transceivers inside Kintex-7 XC7K325T FPGA (figure          |

| taken from [70])70                                                                          |

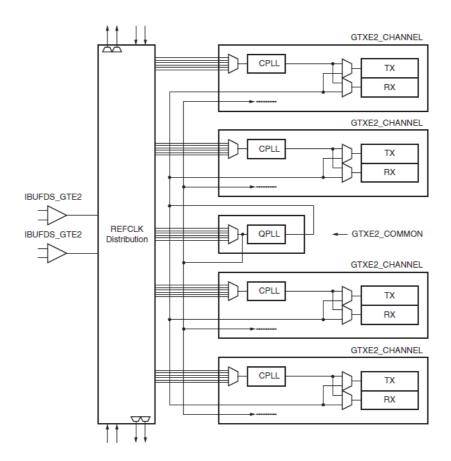

| Figure 45 – Block diagram of a GTX transceiver <i>QUAD</i> (figure taken from [70])71       |

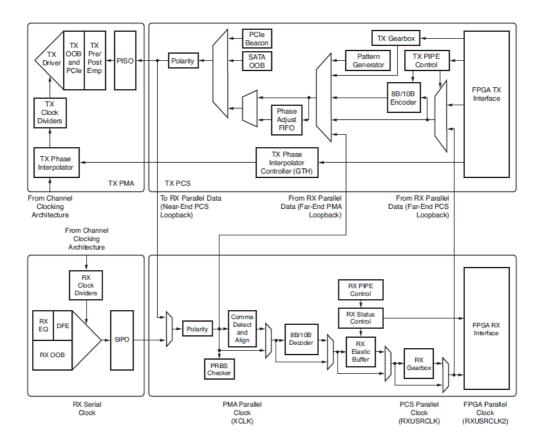

| Figure 46 - Block diagram of the GTXE2_CHANNEL primitive, i.e., a single GTX                |

| transceiver (figure taken from [70])                                                        |

# **List of Tables**

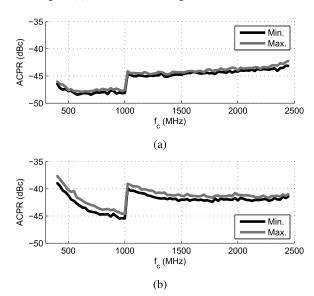

| Table 1 - Measurement results of EVM and ACPR before and after applying DPD    | 35 |

|--------------------------------------------------------------------------------|----|

| Table 2 - Summary of results in Tx1. (*)not possible to demodulate and measure | an |

| EVM value.                                                                     | 58 |

# List of Acronyms

**2-D** Two Dimensional

**ACPR** Adjacent Channel Power Ratio

ADT All-Digital Transmitters

ADC Analog to Digital Converter

AWG Arbitrary Waveform Generator

**BER** Bit Error Rate

**CAPEX** Capital Expenditures

**CU** Central Unit

**C-RAN** Centralized-Radio Access Network

**CM** Cross-Modulation

**CO-MPM** Cross-Over Memory Polynomial Model

DSM Delta Sigma Modulation

DDS Digital Direct Synthesizer

DDC Digital Down-Conversion

DPD Digital Predistortion

DPD Digital Predistortion

D-RoF Digital Radio-over-Fiber

DSP Digital Signal Processor

DAC Digital to Analog Converter

DUC Digital Up-Conversion

**DCR** Direct Conversion Receiver

**E/O** Electro/Optical

**EVM** Error Vector Magnitude

**FPGA** Field Programmable Gate Array

**FoM** Figures of Merit

**FIR** Finite Impulse Response

**GMPM** Generalized Memory Polynomial Model

IC Integrated-Circuit

IF Intermediate FrequencyIMD Intermodulation Distortion

LS Least Squares

LC Linear-Crosstalk

LO Local Oscillator

LUT Lookup Table

LNA Low Noise Amplifier LPE Low Pass Equivalent

**LB** Lower Band

M2M Machine to Machine Communications

MPMMemory Polynomial ModelMGTMulti Gigabit Transceiver

MIMO Multiple-Input Multiple-Output

MS Multi-sine

**NLC** Non-Linear-Crosstalk

NCO Numerical Controlled Oscillator

NZ Nyquist Zone

**OPEX** Operational Expenditures

**PA** Power Amplifier

PFM Pulse Frequency Modulation

PWM Pulse Width Modulation

QoE Quality of Experience

QoS Quality of Service

RF Radio Frequency

RoF Radio-over-Fiber

RRH Remote Radio HeadsSIPO Serial In- Parallel OutSNR Signal to Noise Ratio

SISO Single-Input Single-Output

SFP Small Form-factor Pluggable

SDR Software Defined Radio

SEC Stochastic Ergodic Converter

**SAR** Successive Approximation Register **SMPA** Switched Mode Power Amplifier

SoC System-on-Chip UB Upper Band

VGA Variable Gain AmplifierVSA Vector Signal AnalyzerVSG Vector Signal Generator

VHDL VHSIC Hardware Description Language

**VCO** Voltage Controlled Oscillator

# 1. Introduction

# 1.1. Background and motivation

Since the beginning of this century, a phenomenal growth of mobile communications standards and technologies has been witnessed. Currently, this unprecedented growth is being mainly driven by the huge amount of bandwidth required to answer to the costumers' strong demands on video and multimedia services. To support this ever increasing bandwidth requirements, several successive generations of mobile communications standards have been deployed, from the highly successful GSM (2G) to the current 4G or LTE-A networks. However, currently low power and low bitrate communications are needed for the implementation of the so-called Internet of Things (loT) and, at the same time, very high speed communications are required for the bandwidth-hungry multimedia services. These aspects are two of the main driving forces for the development of the next generation of mobile networks: the so-called 5G. Although many technological aspects are still under debate for the next generation mobile communications it is expected to be delivered around 2020. 5G networks will act as an integrator of the previous standards and it will create a new paradigm in which there will be coexistence of ultra-low power and low-bit rate communications (IoT) with high data rate communications (100Gbps) under high Quality of Service (QoS) and high Quality of Experience (QoE) constraints [1].

In fact, according to current trends, and in addition to the required high data rates, 5G networks will be characterized by cooperative operation between different technologies and heterogeneous networks, denser base station deployments, improved power efficiency and higher levels of connectivity among devices to support the IoT. Therefore, the telecommunications' academia and industry are searching for solutions to deploy 5G networks in an efficient way, capable to answer the previous requirements without significant additional Capital Expenditures (CAPEX) and Operational Expenditures (OPEX) costs for the operators [1]. Several technologies, such as C-RAN (Cloud-Radio Access Network) and small/pico-cell deployment, Massive-MIMO, Software Defined Radio (SDR) and mm-Wave are being pointed out as promising enablers of 5G networks covering a wide range of research topics [1], [2].

Nonetheless, and even considering that the technological characteristics of 5G are still not completely defined, there are key requirements that are common to any past and future standard such as: medium/high power capability, energy efficiency, linearity, bandwidth, radio-frequency (RF) agility in terms of transmission carrier, multi-standard capability, integration/miniaturization and last but not the least important, cost of the devices. All these aspects are constant key optimization targets of the communications sector, mainly in the radio field, which is the focus of this Ph.D. thesis. Regarding these requirements, high power, linearity and efficiency are always highly correlated aspects,

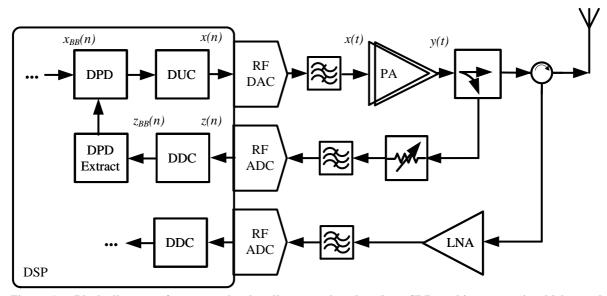

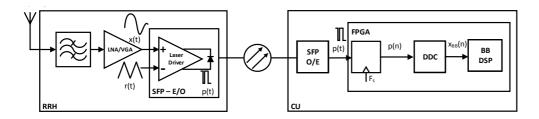

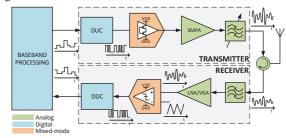

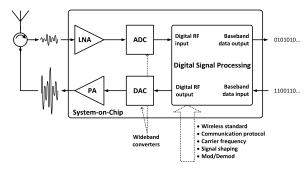

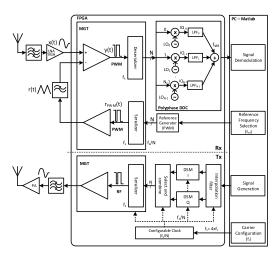

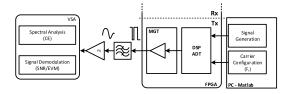

due to the challenges associated with the design of linear and efficient power amplifiers (PAs) [3], [4]. To increase efficiency, PAs are usually operated close to their compression point, which creates non-linear distortion, generating new frequency components (that cannot be radiated) and degrading the in-band signal information. Due to this, techniques of pre-distortion and linearization are often employed, either implemented in digital or analog domain, to simultaneously achieve a linear and efficient system [5]-[7]. This, together with bandwidth and frequency agility are typically the most important metrics in an RF transmitter. On the other hand, receiver's most critical characteristics are usually dynamic range, sensitivity, frequency agility and bandwidth. The dynamic range is fundamental to define the receiver's maximum achievable signal-to-noise ratio (SNR) and the sensitivity allows to characterize the minimum signal power that can be successfully decoded at the receiver's antenna. Both these characteristics strongly depend on the Low Noise Amplifier (LNA). Bandwidth and agility are common key points shared between a transmitter and a receiver and are both associated with the well-known Software Defined Radio (SDR) concept introduced by Mitola in [8], which despite being an already old concept, still represents a challenge. The SDR concept envisions a radio in which high bandwidth waveforms can be completely designed in the digital domain and converted directly into the analog domain at a given carrier frequency  $(f_c)$  also defined in the digital domain, using high speed digital-to-analog converters (DACs). The same is also valid for the receiver, in which a high bandwidth analog-to-digital converter is used to directly sample the RF signal and to, afterwards, apply all the required signal processing tasks in the digital domain. Currently, SDR transmitters are usually implemented recurring to commercial high speed RF DACs [9], however all-digital transmitters (ADTs) based on pulsed converters [10] represent an important research field, since they are associated with high efficient PA topologies [11] and also due to the high integration that these converters enable. Regarding SDR receivers, usually their design is also performed with resort to RF ADCs [9], however digital topologies based on pulsed converters are also being addressed by academia [12]. Within the SDR topic, digital signal processing devices such as common Digital Signal Processors (DSPs) and Field Programable Gate Arrays (FPGAs) play a very important role, since they provide powerful processing capabilities to handle and process the high bandwidth signals. In fact, in the case of FPGAs, these may be even more important due to the fact that nowadays they are already being used to design integrated SDR transmitters [13]. Figure 1 presents a block diagram of an SDR-based radiofrequency transceiver, which uses an additional receiver as observation path (or feedback loop) for digital predistortion (DPD).

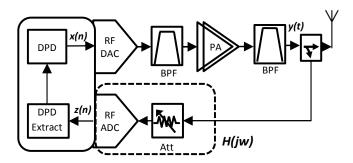

By inspecting Figure 1, one may realize that receiving RF chains are not only used to receive the unknown data that arrives at the antenna, but also to perform PA linearization through DPD, which highlights the RF receiver importance from the system point of view. As already referred previously, DPD is a technique of PA linearization allowing its operation in compression without degrading the signal quality and with benefits of improved efficiency. This technique is based on behavioral modeling, i.e., it requires a set of signals corresponding to the PA input and output x(t) and y(t),

respectively, as represented in Figure 1. Due to this reason, an additional receiver (known as observation path or feedback loop) is required to acquire a replica of the PA output z(n) and allow the extraction of a behavioral model to characterize and subsequently precompensate the PA. As in the case of a normal receiver, the previous highlighted characteristics are also equally important, with exception for the sensitivity since in this case the signal's power at the output of the PA is high. However, in this type of application, the original signal before the PA is known (x(t)), which is an extremely important information that can be used to relax some of the feedback loop requirements. Additionally, as referred in [5], [6] this type of systems should follow the SDR disruptive trends, to reach the so-called SDR DPD system with minimal RF sub-system design and higher integration, through the use of high speed RF converters.

Figure 1 – Block diagram of a conventional radio transceiver based on SDR architecture, using high speed converters and an observation path for DPD.

In conclusion, the main research lines associated with this thesis will be the SDR RF receiver system design and optimization using conventional commercial RF converters and the exploration of disruptive architectures based on pulsed SDR receivers allowing for all-digital SDR platforms. The addressed receivers' target is the normal usage (standalone with antenna) and feedback loop in a DPD scenario, where the relaxation requirements can be further explored to bring costs and energy savings.

# 1.2. Objective

The purpose of this Ph.D. is to study innovative and disruptive ways to improve the most important Figures of Merit (FoMs) of current radio-frequency systems, mainly in the receiver side. However, as previously explained, a radio receiver is also strongly connected with the transmitter enhancement, mainly due to the linearization techniques using DPD

that require an observation path. Therefore, the main questions that this thesis should answer are:

- "How can radio receivers be improved in order to provide increased performance to a standalone receiver?"

- o In the scope of this question, disruptive architectures based on pulsed SDR receivers allowing for all-digital SDR platforms will be studied, designed and evaluated. The main target FoMs in this category are: Error Vector Magnitude (EVM), which is directly correlated with the signal's quality, signal's bandwidth (BW) and frequency agility in terms of carrier frequency.

- "How can a radio receiver be improved to provide enhanced linear and energy efficient transmitters?"

- This second question can be seen as a study of the receiver's usage in a specific application scenario of PA linearization using DPD. The target of this study is to relax the requirements of the receivers typically used in DPD. In order to evaluate the proposed techniques in terms of receiver modifications it is important to evaluate metrics associated with DPD. Therefore in this context, it is important to evaluate not only EVM but also Normalized Mean Squared Error (NMSE) that allows to measure the error of the DPD behavioral model, and Adjacent Channel Power Ratio (ACPR), which allows to evaluate the transmitter linearity and to verify if the spectral masks imposed by the regulators are being met.

In short, the main objective of the work developed in the scope of this Ph.D. is to contribute to the advance of the state-of-the-art of SDR receivers capable to be used in a standalone scenario and as observation path for DPD.

## 1.3. Contributions

The work developed in this Ph.D. brought several contributions for the wireless systems communication community, in the fields of radio frequency receivers and DPD. The published papers, which are presented in the Appendix, strongly support the content of this thesis and are listed as follows:

- [C1] A. Prata, D. C. Ribeiro, P. M. Cruz, A. S. R. Oliveira, and N. B. Carvalho, "Improving DPD performance by compensating feedback loop impairments in RF ADCs," in 2015 IEEE MTT-S International Microwave Symposium, IMS 2015, 2015.

- [C2] A. Prata, A. S. R. Oliveira, and N. B. Carvalho, "An agile and wideband all-digital SDR receiver for 5G wireless communications," in *Proceedings of 18th Euromicro Conference on Digital System Design*, DSD 2015, 2015.

- [C3] A. Prata, A. S. R. Oliveira, and N. B. Carvalho, "FPGA-based all-digital Software Defined Radio receiver," in 2015 25th International Conference on Field Programmable Logic and Applications (FPL), 2015, pp. 1–2.

- [C4] R. F. Cordeiro, A. Prata, A. S. R. Oliveira, N. B. Carvalho, and J. N. Vieira, "FPGA-based all-digital software defined radio system demonstration," in 2015 25th International Conference on Field Programmable Logic and Applications (FPL), 2015, pp. 1–1.

- [C5] A. Prata, R. F. Cordeiro, D. C. Dinis, A. S. R. Oliveira, J. Vieira, and N. B. Carvalho, "All-digital transceivers Recent advances and trends," in 2016 IEEE International Conference on Electronics, Circuits and Systems (ICECS), 2016, pp. 233–236.

- [C6] A. Prata, A. S. R. Oliveira, and N. B. Carvalho, "All-digital Flexible Uplink Remote Radio Head for C-RAN," in 2016 IEEE MTT-S International Microwave Symposium, IMS 2016, 2016, pp. 1–4.

- [C7] A. Prata, S. C. Pires, M. Acar, A. S. R. Oliveira, and N. B. Carvalho, "Towards Circulator-Free Multi Antenna Transmitters for 5G," in 2017 IEEE MTT-S International Microwave Symposium, IMS 2017, 2017, pp. 1–4.

- [J1] A. Prata, D. C. Ribeiro, P. M. Cruz, A. S. R. Oliveira, and N. B. Carvalho, "RF Subsampling Feedback Loop Technique for Concurrent Dual-Band PA Linearization," in *IEEE Trans. Microw. Theory Techn.*, vol. 64, no. 12, pp. 4174–4182, Dec. 2016.

- [J2] A. Prata, J. C. Santos, A. S. R. Oliveira, and N. B. Carvalho, "Agile All-Digital DPD Feedback Loop," in *IEEE Trans. Microw. Theory Techn.*, vol. 65, no. 7, Jul. 2017.

- [J3] R. F. Cordeiro, A. Prata, A. S. R. Oliveira, J. M. N. Vieira, N. B. Carvalho, "Agile All-Digital RF Transceiver Implemented in FPGA," *in IEEE Trans. Microw. Theory Techn.*, vol. x, no. x, pp. 1–12, 2017.

The paper [C1] was the first publication during this Ph.D. work and is related with the study of the impairments of the feedback loop (receiver) in a DPD scenario. This work allowed to understand the main requirements in terms of flatness of the feedback loop, and how its correction can bring several gains in terms of performance. Following this work, the technique associated with paper [J1] was developed, which focuses on how a feedback loop based on RF sampling receivers can be optimized to allow the simultaneous linearization of a dual-band transmitters using a single feedback loop.

The paper [C2] and [C3] have shown the first steps towards an all-digital FPGA based fully integrated receiver, based on RF PWM. In short, these works allowed to demonstrate that is possible to build a highly flexible all-digital receiver using a single FPGA chip. The paper [C4] is a support of a conference live demonstrator of an all-digital transceiver totally implemented in FPGA. The paper [J2] arises as integration of an all-digital transmitter and receiver in the same FPGA chip, and proposing important

optimizing design methodologies for the receiver part, which allowed to improve the metrics obtained in [C2, C3 and C4]. The paper [C5] summarizes the last advances and current challenges in all-digital transceiver design. In [C6], the proposed receiver was evaluated in a C-RAN scenario, which is a very important topic for 5G networks. Finally, the paper [J3] evaluates the usage of the proposed FPGA-based all-digital RF PWM receiver in a DPD scenario, allowing to reach an agile feedback loop for DPD.

The last contribution was the paper [C7], which focuses on the problems associated with circulator-free multi-antenna transmitters and how to solve them by implementing a digital pre-compensation algorithm.

# 1.4. Document organization

The thesis document was organized in six main chapters as follows:

#### 1. Introduction

• The first chapter presents the background, motivation, main objective and document organization of this Ph.D. thesis.

#### 2. State-of-the-Art

In the second chapter an overview of the state-of-the-art regarding SDR RF receivers based on conventional ADCs and pulsed architectures is presented. This chapter contains a system level overview about DPD, highlighting the importance of the receiver (observation path) in such application. Additionally, several important research topics that were addressed within Ph.D. work are identified in this chapter.

### 3. RF ADCs enhancement in a DPD scenario

• In this chapter the first part of this Ph.D. work is addressed focusing on enhancing the DPD performance by using a suitable characterization and post-compensation of the feedback loop. Additionally, a technique to relax the feedback loop requirements in a dual-band transmission scenario is presented and evaluated.

#### 4. PWM RF receiver design and applications

• The fourth chapter of this thesis presents a disruptive RF PWM all-digital receiver based on FPGA. The receiver's design details are explained and its performance is evaluated in two application scenarios, which include the normal usage (standalone with antenna) and feedback loop in a DPD scenario.

### 5. Integration and assessment of DPD feedback loops for multi-antenna systems

• In this chapter the last part of this Ph.D. research work is addressed, which focuses on one of the most important topics for 5G: the multi-antenna systems, in which integration and scalability are very important metrics to study and evaluate.

### 6. Conclusion and future work

• The last chapter concludes this thesis document and gives some insights regarding potential future work in this field from the author's point of view.

# 2. State of the Art

Considering that the focus of this work is on the receiving branch of a radio system it is important to give an overview of its architecture fundamentals from the most traditional ones up to the most recent and disruptive, which is done in the sub-section Traditional RF Receivers Architectures Overview.

Afterwards, a special focus on the RF sampling architectures using both commercial ADCs and pulsed architectures is given, since these are the ones that allow to reach higher flexibility, bandwidth and avoid the analog impairments.

Finally, this chapter is concluded with the application scenario of DPD, by highlighting the importance of the RF receiver in such system. Additionally, a brief overview over DPD concepts and PA linearization is also given.

## 2.1. Traditional RF receivers architectures overview

Usually, modern RF receivers applied in digital communications can be organized in three different topologies:

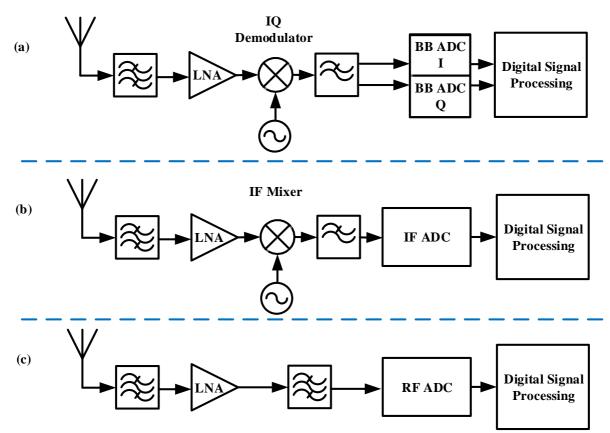

- 1. Direct conversion receiver (DCR), or zero-Intermediate Frequency (IF) receiver, uses an analog I/Q (in phase and quadrature components) demodulator to down convert the signal directly to base band followed by two ADCs to acquire the I/Q components (Figure 2 (a));

- 2. Down-conversion from RF to IF and IF sampling with digital I/Q down-conversion (DDC) (Figure 2 (b));

- 3. RF sampling receiver, in which the signal is directly digitized at the RF stage, followed by a fully digital DDC (Figure 2 (c)).

Figure 2 presents a block diagram of the three main categories of RF receivers. The first presented architecture (Figure 2 (a)), is probably the most widely used due to its versatility and acceptance for narrowband communications. However, this architecture comprises problems regarding the imbalance of the analog I/Q demodulator, Local Oscillator (LO) feedthrough, mixer non-linear behavior, and other impairments caused by the analog components such as non-flat gain and non-linear phase response. Nevertheless, some of these impairments may be solved with post-compensation in digital domain after a proper characterization and calibration procedure.

The second architecture (Figure 2 (b)), IF-sampling receiver, does not suffer from I/Q imbalance problems, since I/Q demodulation is performed in digital domain. When I/Q demodulation is digitally implemented, the process is usually known as digital down-conversion (DDC), in which the LO is now a Numerical Controlled Oscillator (NCO) or Digital Direct Synthesizer (DDS). In addition, to avoid the I/Q imbalance problem, the usage of a DDC allows for improved resolution in terms of down-conversion frequency. However, LO feedthrough, mixer non-linear behavior, as also non-flat frequency response

of the analog components are still present. In short, both first and second architectures have flexibility depending on the frequency range of the mixers, have limited bandwidth, and require compensation techniques to mitigate the imbalance as also other analog components non-ideal behavior.

Figure 2 – Block diagram of conventional radio receiver architectures. (a): direct conversion receiver; (b): IF conversion receiver; (c): RF sampling receiver.

The final one (Figure 2 (c)) is closer to the ideal SDR concept [8], with reduced number of analog components and presenting high flexibility and also supporting wideband signals operation. Nevertheless, this architecture requires high-speed ADCs which may be expensive and may present high power consumption. In respect to flexibility and to cope with high bandwidth, this is the preferable architecture, taking profit of the high efficient and accurate digital signal processing techniques, avoiding the analog impairments and mismatches [14]. However, it is important to realize that this architecture may also present non-flat frequency response over a high operation bandwidth, which may require digital post compensation.

## 2.2. RF ADCs

According to the previous section, it can be understood that to achieve flexibility and wide bandwidth operation, the most suitable RF receiver is the RF sampling architecture, in which the analog-to-digital converter (ADC) is the fundamental system element. In this chapter, the RF ADCs are addressed and separated into two main groups, which are the general purpose commercial available RF ADCs and the pulsed ADCs based on Delta-Sigma Modulation (DSM), Pulse Width Modulation (PWM) or even Pulse Frequency Modulation (PFM).

### 2.2.1. Comercial RF ADCs

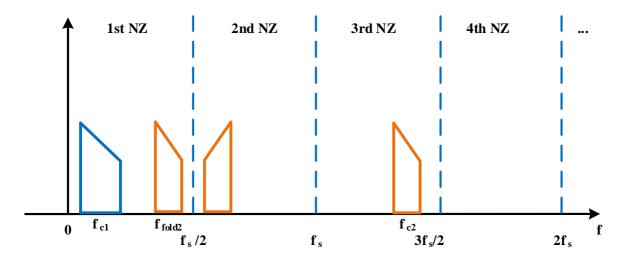

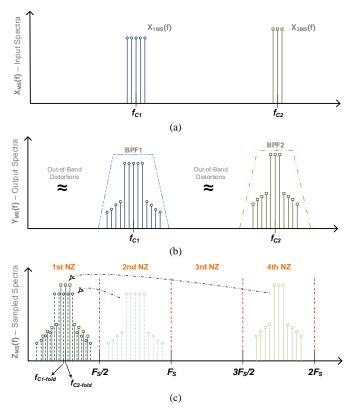

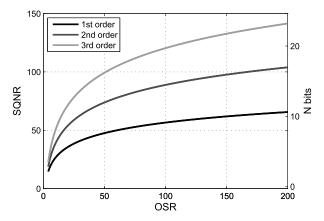

Current commercial RF ADCs have reached the order of a few GHz both in sampling frequency as in input bandwidth [15], [16]. These types of converters can be used in a wide range of applications such as multi-band and multi-mode RF receivers, cellular receivers, phased array radars, electronic warfare, broadband wireless, high-speed digitizers, microwave and millimeter-wave receivers, optical communications, among others. Usually, these wideband on-chip high speed converters are based on flash and interpolated folding architectures [17], which are known for allowing high sampling rates. Additionally, depending on the sampling frequency  $(f_s)$  and carrier frequency  $(f_c)$  location, these converters can be used in direct sampling  $(f_s > 2f_c \text{ and } f_s > 2BW)$  or in bandpass sampling ( $f_s < 2fc$  and  $f_s > 2BW$ ) configurations, which is a consequence of the well-known Nyquist Theorem [18]. Figure 3, presents a frequency domain illustration of the sampling process depending on the location of the carrier relatively to the sampling frequency, which imposes the Nyquist Zone (NZ) where the signal is sampled from [18]. One may realize that the blue signal (centered at  $f_{cl}$ ) is originally sampled from the first NZ, while the orange signal (centered at  $f_{c2}$ ) is sampled from the 3<sup>rd</sup> NZ, folding afterwards at the first NZ at  $f_{fold2}$ . The folding frequency is given by the following expression (1):

$$f_{fold} = \left| f_c - \left| \frac{f_c}{f_s} \right| f_s \right| \tag{1}$$

where  $f_{fold}$  is the folding frequency in the 1<sup>st</sup> NZ, |... | is the absolute value and [...] is the rounding operation towards the nearest integer [19]. One may realize the importance of filtering requirements either in direct sampling and bandpass sampling in order to avoid aliasing effects [18].

Figure 3 - Frequency domain illustration of the sampling process over different NZs.

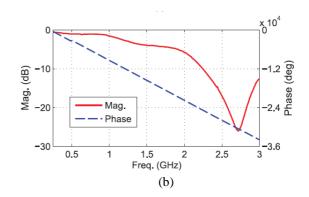

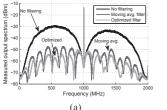

To get the maximum performance over wideband operation, the behavior of these converters must be well understood through adequate characterization procedures. In [19]-[22] a measurement setup for linear and non-linear characterization of RF converters has been presented and intensively studied. The proposed measurement platform allows to perform a system characterization from the analog to the digital domain, in the case of ADCs and the opposite in the case of DACs. Interesting results were presented, in which allow to conclude that the performance over several NZs can be quite reasonable in terms of linearity, however presenting some gain non-flatness. Figure 4 presents the frequency response of a 1 GSample RF ADC (ADS5400) designed by Texas Instruments (TI) [23]. Figure 4(a) presents the magnitude response of the ADC presented in the device datasheet and measured by TI. Figure 4(b) presents the ADC evaluation board frequency response in both magnitude and phase measured following the procedures presented in [20]. Regarding the magnitude response, the 3 dB cutoff frequency seems to be similar in both graphs, i.e., around 2 GHz. At frequencies higher than 2 GHz the results from Figure 4(b) present a higher degradation, because it is a measurement of the evaluation board, including losses in the input balun, connectors and transmission lines, while in Figure 4(a) is presented an on chip device measurement. Additionally, it is important to note the phase measurement capability of the method presented in [20], and according to Figure 4(b) it is possible to verify that the RF ADC evaluation board presents a linear phase response.

Figure 4 –Frequency response of RF ADC ADS5400 from TI [23]. (a): Magnitude response presented by TI in [23] (figure taken from [23]). (b): Magnitude and phase response measured and presented in [20] (figure taken from [20]).

Nevertheless, the previous non-ideal behavior will impose system performance degradation in terms of Error Vector Magnitude (EVM), demanding for digital equalization, i.e., pre-compensation in the DAC case and post-compensation in the ADC case. The study of the impact of such impairments when these receivers are used in DPD scenarios is one of the tasks of this Ph.D. work.

Last but not least, usually this type of converters are expensive and responsible for a considerable energy consumption reducing the overall system's efficiency [24]. This difference is even more evident when compared to the traditional baseband converters, as was analyzed in [24]. Furthermore, when it is necessary to reach frequencies higher than approximately 4 GHz it is necessary to choose mixer-based architectures, and it is not possible anymore to sample the signal directly with a RF ADC increasing even more the overall system's cost and bill of materials.

## 2.2.2. Pulsed architectures

As it has been seen so far, at the receiver side, to achieve flexibility and wider bandwidth in the RF chain, the ADC is of paramount importance, by allowing the use of digital signal processing techniques and avoiding analog impairments. In this sub-section analog-to-digital converters based on pulsed architectures, or single-bit converters, which represent a kind of disruptive topologies will be addressed.

Recently there are arising new possibilities to build RF ADCs: based on delta-sigma modulation (DSM) [12], pulse-width modulation (PWM) [25] or pulse frequency modulation (PFM) [26], [27]. All these types of ADCs share the common basis of being single-bit ADCs, i.e., they all deal with a digital pulsed representation of the analog signal. The DSM ADCs are well known in audio applications, where they provide very high resolution [14]. Some research is being done in order to apply these ADCs in the RF world, as presented in [12]. Even though good figures of merit that have been obtained in

[12], the need for a low latency feedback path can impose several limitations in terms of increasing the effective sampling frequency.

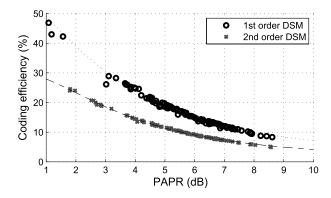

The PWM ADCs comprise a single comparator, whose inputs are the analog signal and a known reference (usually a triangular wave), generating a PWM representation of the signal [28]. They are commonly used in low-frequency power applications [28]. Nevertheless, recently they are also being brought to the RF world, as presented in [25]. However, the presented results reveal a weak signal-to-noise ratio (SNR) due to the PWM strong non-linear behavior and make use of high speed comparators, which are high cost components.

A PFM ADC is achieved using a Voltage Controlled Oscillator (VCO) as input for the analog signal [26]. These types of ADCs present high undesirable non linearities related to the VCO behavior, which have been addressed by the scientific community through the use of feedback loops or digital calibration [27].

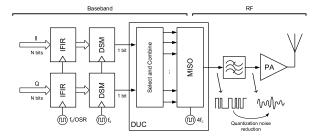

Due to the highly digital intensive circuit topology of the previously described ADCs architectures they are all promising candidates for modern all-digital receivers' architectures. Additionally, since the previous described architectures have a strong foundation on pulse shaping modulations these topologies are very attractive to be implemented in an FPGA-chip, allowing for higher levels of integration and cost reduction. As already stated, one of the objectives of this Ph.D. work is to take profit of the powerful DSP FPGA capabilities as also its very high speed I/Os in order to build RF ADC converters recurring to the state-of-the-art FPGA chips, similarly to what has already been done for the transmitter case [13], [29], [30]. In fact, to the best of the author's knowledge, this will be the first work trying to build such a type of RF ADC converters using directly an FPGA chip, without any external components. Therefore, due to this reason, and because the PWM converters seem to be the most feasible approach to get such a type of integration, and, as well as to be able to focus on important application scenarios such as DPD, it was decided to focus exclusively in this type of converters. Therefore, the next sub-section addresses the PWM modulation process and presents the state-of-the-art of this type of converters, while the DSM and VCO can be seen as possible future work to follow this thesis.

### 2.2.2.1. RF-PWM converters working principle

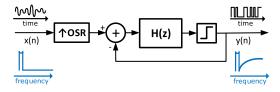

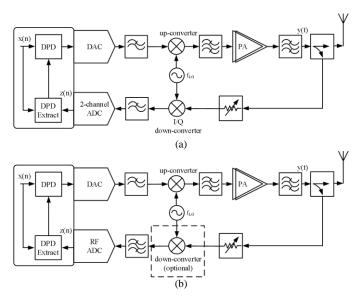

An ADC comprises two main processes: sampling and quantization, corresponding to discretization in both time and amplitude, respectively. In this section the PWM ADC working principle will be addressed focusing in both of these aspects.

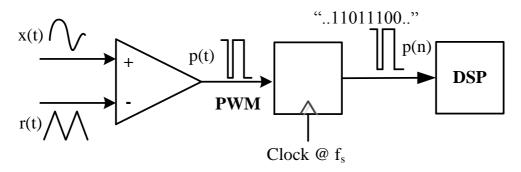

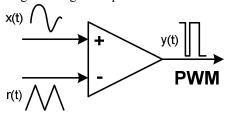

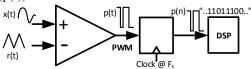

A PWM ADC is mainly based on a comparison between two signals: the desired analog signal (x(t)) and a reference signal (r(t)) (usually triangular or sawtooth), generating a PWM representation of the desired signal (p(t)), as presented in the block diagram of Figure 5. Following the comparator there is a register responsible to sample and discretize the PWM signal. Thereafter, the signal is available for further processing in the digital

domain. The comparator has the same behavior as the sign(...) function acting as a single-bit quantizer, which can be mathematically expressed as:

$$p(t) = sign(x(t) - r(t))$$

(2)

in which, x(t) is the input signal, r(t) is the reference signal and considering the sign function defined as:

$$sign(x(t) - r(t)) = \begin{cases} -1, & \text{if } x(t) - r(t) < 0 \\ +1, & \text{if } x(t) - r(t) > 0. \end{cases}$$

(3)

Figure 5 - Basic block diagram of a PWM converter.

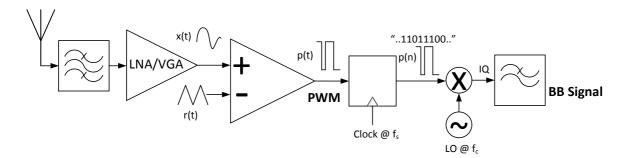

Taking into account that the focus of this Ph.D. work is on RF ADC converters it is necessary to impose some modification to the Figure 5 to obtain the RF PWM converter. Figure 6 presents the generic block diagram architecture of a RF PWM receiver, where the signal x(t) represents the RF signal received at the antenna after filtering and low noise variable gain amplification (LNA/VGA). The x(t) signal is one of the inputs of a comparator, while the other is a reference signal (r(t)), producing a PWM representation of the analog signal at the output of the comparator. Following the comparator there is a register responsible to sample and discretize the PWM signal. Thereafter, the signal is available for further processing regarding digital down conversion and filtering in order to recover the baseband signal's information.

Figure 6 - Diagram of an RF PWM converter.

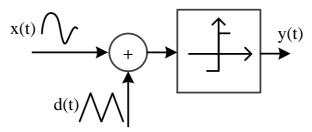

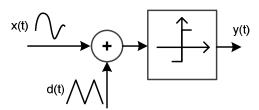

The proposed way to implement the conversion (PWM) is similar to the stochastic ergodic converter (SEC) presented in [31], which was a popular idea in the '60s to build low cost and low frequency ADCs. However, at the time, due to the lack of enabling technology, the idea was abandoned and sigma-delta converters were preferred [31]. This converter is mainly based on adding a dithering waveform to an analog signal and then feeding it to a single bit quantizer, as it is presented in Figure 7. The theoretical demonstration of this converter can be developed based on statistical quantization theory [32], which shows that if the dithering signal presents uniform distribution, the input signal will be equally quantized, i.e., the mean of the input signal will be contained in the output quantized signal, allowing its recovering. A common selection for the dithering wave is a triangular or sawtooth wave, since both present uniform amplitude distributions [31], [32]. This dithering wave can be directly transposed for the PWM RF ADC, playing the same role as the reference signal (r(t)), which should also present uniform amplitude distribution.

Figure 7 – Block diagram of the stochastic-ergodic converter (figure adapted from [31]).

After the quantization process, it is necessary to discretize the signal, that despite of already being represented in two well defined levels, it is not a discrete-time representation. There are at least two ways to discretize this signal: uniformly or not uniformly. The latter leads to a non-uniform sampling process, which is the method used in level-crossing ADCs [31]. However, this requires challenging interpolation methods to restore a uniform sampling rate, which falls out of the scope of this work. The uniform sampling is simpler and can be easily implemented by directly sampling the two-level signal at a constant clock frequency, which should be high enough to register all the

possible PWM transitions. Related to this process, there are two important characteristics, which are the reference frequency  $(f_r)$  and the sampling frequency  $(f_s)$  of the sampler after the comparator, that define the maximum bandwidth of the signal to be acquired. The latter two variables will also impose the converter's resolution, since the ratio between the effective sampling frequency  $(f_s)$  and the reference signal frequency  $(f_r)$  indicates the number of PWM levels and therefore, the number of bits of the converter and its signal-tonoise ratio (SNR), as follows:

$$N_{bits} = \log_2 N_{quatization \ levels} = \log_2 \frac{f_s}{f_r}$$

(4)

$$SNR = 6.02N_{bits} + 1.76 \tag{5}$$

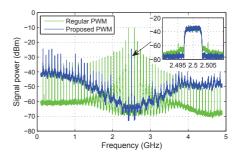

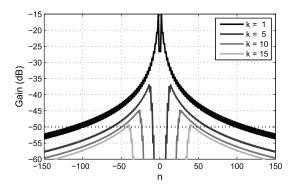

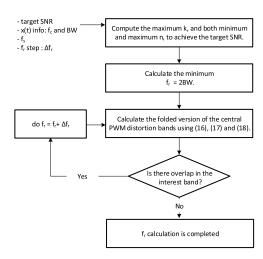

The previous relationships indicate that the higher the ratio between the sampling frequency and the reference signal, the higher will be the converter effective resolution. Therefore, we may consider that the limit for the  $f_s$  will be imposed by the maximum frequency allowed by a given technological process or by a set of requirements such as resolution or power consumption of a certain application. Nonetheless, and without loss of generality, the  $f_s$  is assumed to be fixed at the maximum achievable value to provide the maximum resolution. Thereafter, considering an analog signal occupying a given bandwidth (BW), it is important to select the minimum reference signal frequency to provide the higher resolution. While a selection of a minimum reference frequency of 2BW for a sawtooth waveform and of BW for a triangular waveform allows achieving the same resolution, it creates a different harmonic content in the PWM spectrum [33]. The sawtooth wave puts the first distortion band closer to the interest band, making the triangular wave a preferable way to acquire the signal and to provide a relaxation of the filtering requirements in the DDC chain. However, due to the uniform sampling imposed at the output of the comparator, this selection is not as trivial as previously stated, since the analog signal (x(t)) is an RF signal and not a baseband as usually in this type of converters. The PWM modulation process is highly non-linear, creating a huge amount of distortion. The PWM waveform is a square wave with variable duty-cycle, which presents an infinite spectrum. Therefore, after uniform sampling, aliasing will occur in the first Nyquist Zone (NZ) that may degrade the SNR if the distortion falls into the band of interest. This fact will demand to choose a proper reference signal, depending on the signal to acquire, which is one of the topics that will be addressed in this Ph.D. work, and at the best of the author knowledge has never been addressed focusing RF PWM converters.

After addressing the PWM process is possible to discuss in more detail the only RF PWM receiver published at the time that this Ph.D. started (2013): [25]. In [25] high speed comparators were used to generate the PWM representation and afterwards an FPGA-chip was used to gather the two-level signal and build the remaining receiver. This work does not present any procedure or analysis to get the PWM reference frequency. As already referred, one of the tasks of this Ph.D. work is to obtain the best reference frequency to

optimize the receiver figures-of-merit. Moreover, several other improvements are planned to be studied and implemented during this work, as for instance the usage of the FPGA IOs to be used directly as comparators.

Following similar reasoning, it is also important to refer several past approaches to build FPGA-based converters. In [34], [35], Xilinx released an application note to design a DSM low frequency DAC and ADC using directly the general purpose FPGA IOs. Additionally, Lattice Semiconductor [36] also released a similar application note just for ADCs based on DSM or Successive Approximation Register (SAR). The target of both these applications is low frequency and low bandwidth scenarios, which is exactly the opposite of the RF communication world, in which the carrier frequency is high and the required signal's bandwidth is successively increasing. However, at the same time the current state-of-the-art FPGA IOs sampling rate are increasing being able to reach 28Gbps, which completely changes the paradigm allowing to explore its usage for RF receivers, similarly to what has already been done for the transmitters [10], [13].

# 2.3. Receiver importance in a DPD scenario

Nowadays, the usage of DPD systems is widely spread over base station cellular infrastructure that use high power amplifiers, in which efficiency and linearity are a mandatory requirement [6]. However, even in mobile terminals low-complexity DPD structures are used to get improved transmission system performance [37], [38].

## 2.3.1. DPD concept

In order to get the best possible efficiency RF PAs are operated close to the compression or even sometimes a few dB magnitude levels above the 1 dB compression point. Consequently, non-linear in-band and out-band distortion will be generated, degrading the signal quality and emitting signal components in spectrum that may be allocated to other users. The easiest solution to avoid the non-linear distortion generation is to operate the PA in a back-off region, with the inherent drawback of a huge efficiency reduction. Therefore, a possible solution is to apply linearization techniques, in order to somehow modify the PA input signal, to get a distortion- free output while keeping the operation close to the best efficiency point. There are two ways to implement linearization techniques: in analog or in digital domain. Whereas both these ways are currently used, however DPD is more spread over base station cellular communications because it represents a cheaper and more flexible solution rather the analog linearization [5]. The analog linearization is completely out of the scope of this thesis, however if the reader is interested in such a topic more information can be found in [5].

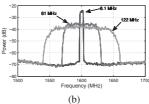

Figure 8, represents a block diagram of the principle of PA linearization using DPD, in which there is a DPD block before the PA that is responsible to apply a given transfer function corresponding to the inverted behavior of the PA distortion that will pre-

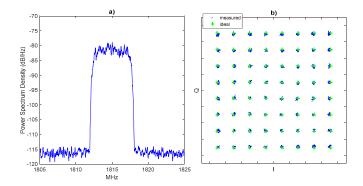

compensate for the PA distortion. Following Figure 9(a) it is also possible to understand the different transfer functions of the DPD block and the PA block, in which the PA enters in the compression and the DPD expands the gain to compensate the PA compression, to obtain a linear system [7]. Additionally, Figure 9(b) presents the spectrum of the signal before and after applying DPD, where it is possible to observe the bandwidth expansion due to the PA non-linear behavior (spectral regrowth) and its correction with DPD. This bandwidth expansion limit is usually monitored with a metric defined as Adjacent Channel Power Ratio (ACPR) [39], that measures the ratio between the total power at the adjacent channels (high and low) and the power at the fundamental channel. The current LTE standard imposes an ACPR limit of 45 dBc.

Figure 8 – Block diagram representing the DPD concept.

Figure 9 - AM/AM characteristic plot representing the digital predistorter block, the PA and the final linear system (DPD+PA) (a), and Spectrum before and after applying DPD (b).

#### 2.3.2. Receiver role in DPD scenario

In practice, to apply DPD it is required to use a behavioral model, to mimic the inverse of the non-linear PA response. In order to model this inverse behavior, the low pass equivalent (LPE) signal representation of both input (xBB(n)) and output (yBB(n)) of the PA are required [6], [40], which imposes the need for a system that acquires the PA output, i.e., an RF receiving path. Such a system is usually made of transmitter section with a PA followed by a coupler, that will be a connected to a digital receiving path (known as observation path or feedback loop), as presented in Figure 10. Despite an RF ADC is

represented in Figure 10 any other receiver topology as presented before could be used. This receiver path should be able to sample a replica of the output of the PA without any degradation, i.e., according to Figure 10 the signal  $z_{BB}(n)$  should be the closest possible replica of the LPE of y(t). Therefore, it is of paramount importance to have a linear and flat feedback loop to not compromise the DPD performance. Once again it is important to realize that ADCs are also a key element in modern digital communication transmitters, where they play a fundamental role in the feedback loop of DPD architectures. Additionally, the importance of the receiver impairments and its impact on the DPD performance was also evaluated in this Ph.D. work.

Figure 10 - Block diagram scheme representing a transmitter with feedback loop for DPD.

From the point of view of receiver optimization, which is the focus of this thesis, there are two more important scenarios in which the feedback path plays an important role which are:

- Multi-band applications, in which one PA is used to concurrently amplify two or more different frequency spectrum bands.

- MIMO scenarios, in which multiple transmitter branches are used to concurrently transmit at the same frequency codified signals, with the target of improving the bit error rate (BER) at the receiver side (MIMO transmit diversity mode), or with the target of increasing overall system transmission rate (MIMO spatial multiplexing mode).

#### 2.3.2.1. Concurrent multi-band scenarios

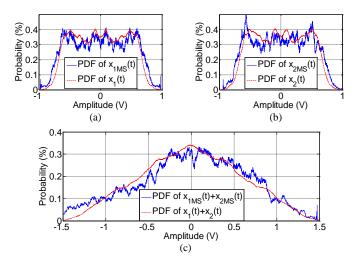

Current wireless communications standards strongly depend on multiple carrier aggregation, in order to increase the communication throughput. In this way, to gather the maximum power efficiency, this has led to the use of a single amplifier for multiple band amplification, instead of using multiple amplifiers tuned at each specific frequency [41], [42]. However, in a multiple band scenario the implementation of DPD algorithms and feedback loops is not as straightforward as in a single band case. Considering a dual-band

scenario, first of all the non-linear contributions are now not only from the intermodulation distortion (IMD) products but also from the cross-modulation (CM) mixtures between the two bands that must be considered in the DPD design, so a 2D (two dimensional) model for the PA is mandatory to get improved performance [43]. Several research works have been done in order to look for effective 2D modeling structures, such as [43], [44] (more details about modeling structure are presented in the next section). Secondly, the feedback loop has now to acquire two bands concurrently at the output of the PA, which is at least twice of the required bandwidth in the single band case. A conventional architecture is usually made of two parallel feedback loops acquiring separately the lower band (LB) and upper band (UB) (Figure 11). This matter was also recently addressed by the scientific community by trying to reduce the needs of two feedback loops. In [45], [46], a single feedback loop strategy is presented by acquiring the multiple bands in different time slots. Another recent contribution in [47] develops a new approach called down-converted carrier co-location (DC<sup>3</sup>). However, it requires two external mixers in the feedback path to place both bands at a specific location. Another possibility for the feedback loop is to use RF subsampling ADCs, such as presented in [48], where by changing the sampling frequency of the ADC allows to avoid the aliasing of the different bands, and thus, all the signal components can be recovered. In the scope of this Ph.D. a solution for this problem was also proposed.

Figure 11 - General block diagram of a dual band wireless transmitter with a conventional feedback loop for dualband DPD.

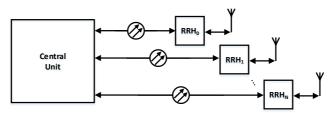

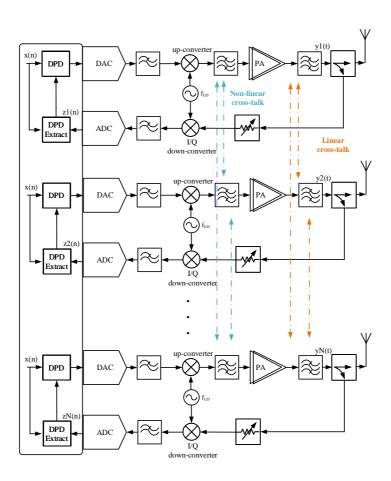

#### 2.3.2.2. Multi-antenna scenarios

Multi-antenna transmitters, all considered as MIMO transmitters, inherited all the problems already existent in the common SISO transmitters and present additional ones. For instance, both transmitters are expected to operate at the same frequency to provide either transmit diversity or spatial multiplexing. Thus, it is expectable that the transmitters suffer from interference between each other, due to the leakage of sharing the same LO. Additionally, higher degrees of integration in the same Integrated Circuit (IC) are expected, which will also lead to higher levels of crosstalk between different RF lanes.

Last but not least, the antennas proximity may exacerbate mutual-coupling issues between each other, which can also be seen as crosstalk or interference. This problem will be even worse when considering a higher number of transmitters, as it is expected in the Massive MIMO scenario [1].

Therefore, by considering all the main sources of crosstalk, it is important to understand that linear-crosstalk (LC) and non-linear cross talk (NLC) may occur, as depicted in Figure 12. This separation is done considering that the cross-talk occurring before the PA, will create new distortion components due to the cross-terms between the main signal and the cross-talk. On the other hand, the cross-talk occurring after the PA is usually considered to be linear. However, it is important to state that this may also create non-linear distortion due to the possible load variations at the output of the PA, however this is an open question that falls out of the scope of this thesis.

Figure 12 - Block diagram representation of a  $2\times M$  transmitter with LC and NLC cross talk. (figure adapted from [50]).

Focusing on Figure 12, it is possible to model the output of each PA in the following way:

$$y_1(t) = f_{PA1}(x_1(t) + \beta x_2(t)) + f_{PA2}(x_2(t) + \alpha x_1(t))6$$

(6)

$$y_2(t) = f_{PA2}(x_2(t) + \alpha x_1(t)) + f_{PA1}(x_1(t) + \beta x_2(t))\gamma \tag{7}$$

in which  $x_I(t)$ ,  $x_2(t)$ ,  $y_I(t)$ ,  $y_2(t)$  are the input/output of PA1 and PA2, respectively,  $f_{PAI}(...)$  and  $f_{PA2}(...)$  represents the non-linear function of each PA, and the  $\alpha$ ,  $\beta$ , 6 and  $\gamma$  represent the crosstalk accordingly to Figure 12. The presence of these interactions between lanes requires suitable modeling topologies to fit this problem, that is considerably different from the typical SISO one. In line with this issue, several research works have been proposed to provide a reasonable modeling formulation to efficiently address these problems [49]–[52].

Within this context, the relaxation of the feedback loop requirements is of paramount importance, since it would be desirable not have a one-to-one parity between number of transmitter lanes and number of observation paths for DPD. A simplification in the number of feedback loops or even in their requirements would allow to save costs and to enable scalable Massive MIMO approaches. In this context the work presented in [53] proposed a feedback that would acquire the combination of the PA outputs in a dual MIMO transmitter, instead of the individual feedback per PA. However, only simulation results were presented, which is still far away from the formal validation of this proposal. The study of the DPD feedback loop problem in multi-antenna transmitters was the last topic addressed in this Ph.D. thesis.

#### 2.3.3. DPD models

This sub-section presents a brief summary about the mathematical formulation of one of the most used DPD models, i.e., the Memory Polynomial Model (MPM). Additionally in the Appendix – A - Additional DPD models, the reader may find more details about DPD models, addressing both SISO models for single band PAs, SISO models for dual band PAs and MIMO models for MIMO application scenarios. All the models are presented focusing on a forward model perspective, in which, x(n) is the input of the PA and y(n) its output. However, for DPD purposes an indirect learning architecture (ILA) using post inversion as suggested in [40] was considered.

#### **SISO Memory Polynomial Model**

The SISO Memory Polynomial Model (MPM) is usually a quite effective model in terms of tradeoff between complexity and performance and its mathematical formulation is presented as follows [40]:

$$y(n) = \sum_{m=0}^{M} \sum_{k=0}^{\frac{K+1}{2}} h_{(m,k)} x(n-m) |x(n-m)|^{2k}$$

(8)

where, x(n) is the PA LPE input signal, y(n) is the PA LPE output signal, M is the memory depth, K is maximum order of nonlinearity and  $h_{(m,k)}$  are the PA forward model coefficients [40].

Considering the matrix notation for the former equation can be elaborated as:

$$\tilde{y} = XH \tag{9}$$

$$X = [X_0 \quad X_1 \quad \dots \quad X_K] \tag{10}$$

$$X_K = [x(0)|x(0)|^{2K}.. \quad x(n-m)|x(n-m)|^{2K} \quad .. \quad x(N)|x(N)|^{2K}.. \quad x(N-m)|x(N-m)|^{2K}]^T$$

(11)

, where  $\tilde{y}$  is the measured data at the output of the transmitter, N is the total number of signal samples, X is the regression matrix containing all the basis function of x(n), and H is the matrix containing the model coefficients, which can be solved in a Least Squares (LS) sense [40]:

$$H = (X^H X)^{-1} X^H \tilde{y} \tag{12}$$

In which  $(.)^H$  is the Hermitian transpose.

For the case of DPD, the inverse model  $(H_i)$  should be obtained in the following way:

$$\tilde{x} = YH_i \tag{13}$$

$$Y = \begin{bmatrix} Y_0 & Y_1 & \dots & Y_K \end{bmatrix} \tag{14}$$

$$Y_K = [y(0)|y(0)|^{2K}.. \quad y(n-m)|y(n-m)|^{2K} \quad .. \quad y(N)|y(N)|^{2K}.. \quad y(N-m)|y(N-m)|^{2K}]^T (15)$$

, where  $\tilde{x}$  is the measured data at the input of the transmitter, X is the regression matrix containing all the basis function of y(n), and H is the matrix containing the coefficient models, which can again be solved in a LS sense [40]:

$$H_i = (Y^H Y)^{-1} Y^H \tilde{\chi} \tag{16}$$

Then, after building the regression matrix of the inputs X the pre-distorted replica can be defined as:

$$\chi_{PD} = XH_i \tag{17}$$

An important note to highlight is the number of coefficients (or basis functions) of the SISO MPM model, that can be given by:

$$N_{Coefs\,MPM} = (M+1)\left(\frac{K+1}{2}\right) \tag{18}$$

# 2.4. Summary and concluding remarks

In this chapter a state-of-the-art review about RF receivers was presented, in which, RF sampling architectures were considered to be the most promising future candidates to get better performance in terms of bandwidth and agility, following the well-known SDR concept. During this review, several research challenges of these architectures were addressed, considering the usage of a RF receiver in a standalone operation, i.e., used for receiving unknown data at the antenna, and when used as observation path for PA linearization via DPD.

The identified challenges were addressed in this Ph.D. work focusing on innovative and disruptive ways to improve important FoMs of current RF systems.