# Materials, Device, and System Integration of Amorphous Oxide Semiconductor TFTs

# Guangyu Yao

Department of Engineering University of Cambridge

This dissertation is submitted for the degree of Doctor of Philosophy

Robinson College

Jan 2019

## Declaration

I hereby declare that except where specific reference is made to the work of others, the contents of this dissertation are original and have not been submitted in whole or in part for consideration for any other degree or qualification in this, or any other university. This dissertation is my own work and contains nothing which is the outcome of work done in collaboration with others, except as specified in the text and Acknowledgements. This dissertation contains fewer than 65,000 words including appendices, bibliography, footnotes, tables and equations and has fewer than 150 figures.

Guangyu Yao

## Acknowledgements

First of all, I would like to extend my sincere gratitude to Dr. Sanjiv Sambandan for advising my doctoral research. I am extremely thankful for his help in the completion of this thesis, and he was there when I needed it most. I would also like to thank Prof. Arokia Nathan for his instructive advice and useful suggestions on my research.

I would like to acknowledge my advisor, Prof. Andrew Flewitt, for his generous support. Most of my research resources, including cleanroom tickets, consumables, and measurement equipment, were supported by Prof. Flewitt. Without the help and support that I received from him, the completion of this thesis would have been impossible.

Furthermore, I would like to thank Prof. Xiaojun Guo for being my constant source of knowledge and support. Through his patient guidance, I was able to build the first organic TFT six years ago. He shared his vision on the promising future of electronics and offered me the opportunity and belief I needed to move forward. I would also like to thank Prof. Henning Sirringhaus for sharing the UPS and XPS equipment with us. The valence band data extracted with the help of Chris Amey meant a great deal to me and my research. I also thank Dr. David Hasko for instructing me on how to run semiconductor characterisation experiments.

I would like to acknowledge all the members of the Hetero-genesys group. In particular, I thank Dr. Hanbin Ma, who helped familiarize me with most of the equipment in CAPE and Nanoscience. He always supported me as a reliable teammate and a true friend. In addition, Dr. Hyung Choi provided many suggestions on experimental design. Dr. Joog Wu Jin taught me how to anodic bond. I would also like to thank Niels van-Fraassen, who was a PhD student that I mentored for two years. He helped me with my experiments and has proven himself as a hardworking and intelligent teammate. I believe he will become a great engineer and I wish him all the best. Mohamad Hazwan Mohd Daut helped me design experiments on MIS diodes and Schottky contacts. Constantinos Tsangarides helped me take SEM pictures. Xiang Cheng, Chen Jiang, Yang Su, and I had very productive discussions. One of our visiting students, Joana Cerdeira from Universidade NOVA de Lisboa, helped us with the XRD measurements.

In addition, I would like to thank all the technicians within CAPE and Nanoscience: Neil Laurence, Kasia Surowiecka, Mark Furbank, Duncan Bulman, Adrian Ginn, etc. From my point of view, even though it was not the most advanced cleanroom, you made it the best cleanroom in the world. Thank you for your support and assistance over the past four years.

Most importantly, I would like to thank all my friends, including colleagues that have not been mentioned above. Girish Rughoobur: thank you for making the time in the cleanroom less boring; life was a little bit of a struggle after you left Cambridge. Juan Antonio Rubio Lara: I admire your optimism and the way you look at things. Ruizhi Jack and Larry: thank you for sharing so much useful information with me. Xiangwen, Boyang, William, Tianwei, Shawn, Ruinan and all my other friends: thank you for joy you brought to me.

I want to thank Cambridge Trust and CSC for generously funding my PhD. I would also like to thank Robinson college, which always made me feel at home.

Finally, my deepest gratitude goes to my family members for always taking my side and supporting me with every decision that I made. Though they may not care about differences among transistors, their hugs and smiles are my biggest motivation.

### Abstract

Amorphous oxide semiconductor (AOS) thin-film transistors (TFTs) have great potential for use in the next-generation of electronics. AOS TFTs can be used to fabricate circuits and sensors on various substrates, due to unique properties, including high mobility, excellent uniformity, and it requiring a low-temperature process. Currently, indium gallium zinc oxide (IGZO) is the predominant AOS used in the display industry as a TFT semiconductor. Although the IGZO technology is very mature, the development of AOS continues. Additional AOSs are being investigated to reduce cost and improve stability. Considering availability and the potential of materials, indium silicon oxide (ISO) was selected for this project. ISO uses silicon to suppress the instability originating from the oxygen vacancy. The silicon-oxygen bond has a higher dissociation energy, which improves retention of oxygen atoms in the film, and thus, increases the transistor's stability.

This detailed study follows a bottom-up approach. It starts with the fabrication and characterisation of materials. Basic material properties of the ISO film are discussed within, including amorphicity, bandgap, stoichiometry, and Hall-effect parameters. Based on the characterisation results, different deposition recipes for the TFT were developed and tested. The interface quality and etching selectivity were investigated. Uniformity and stability data were extracted from a TFT array using the developed photo-lithography process, which was used to verify and quantitate the capability of the process in system integration and circuit design. A Monte-Carlo simulation environment was established based on the extracted data. The two urgent challenges in all-TFT analogue circuit design, the lack of proper active load and the large parasitic capacitance, were investigated. In-depth analysis on these two issues and applicable solutions were presented. Investigation on system integration of TFT circuits and sensors were conducted, since the device demonstrated the required performance and uniformity. An all-TFT differential-input amplifier was designed and verified, as the first mixed signal all-TFT circuit.

# **Table of Contents**

| List | of figur | es                                            | 7  |

|------|----------|-----------------------------------------------|----|

| List | of table | S                                             | 11 |

| Non  | nenclatu | re                                            | 12 |

| 1.   | Intro    | duction                                       | 14 |

|      | 1.1.     | Motivation                                    | 14 |

|      | 1.2.     | Background                                    |    |

|      | 1.3.     | Dissertation Outline                          | 20 |

| 2.   | TFT      | Fabrication                                   | 22 |

|      | 2.1.     | Semiconductor Characterisation                | 22 |

|      |          | 2.1.1. X-Ray Diffraction Spectroscopy         | 22 |

|      |          | 2.1.2. Scanning Electron Microscope           | 24 |

|      |          | 2.1.3. Ultraviolet–Visible Spectroscopy       | 24 |

|      |          | 2.1.4. Ultraviolet Photoemission Spectroscopy | 26 |

|      |          | 2.1.5. Energy-dispersive X-ray spectroscopy   | 27 |

|      |          | 2.1.6. Hall Effect Measurements               |    |

|      | 2.2.     | Fabrication Process                           | 29 |

|      |          | 2.2.1. Selective Etching                      | 29 |

|      |          | 2.2.2. TFT Structure and Fabrication Process  | 31 |

|      |          | 2.2.3. TFT on Plastic                         | 33 |

|      | 2.3.     | TFT Characterisation                          | 36 |

|      |          | 2.3.1. Dielectric Layer                       | 36 |

|      |          | 2.3.2. Metal-Semiconductor Contact            | 39 |

|      |          | 2.3.3. Semiconductor Optimisation             | 41 |

| 3.   | Unifo    | ormity and Stability of TFT                   | 46 |

|      | 3.1.     | Parameter Extraction Toolkit                  | 46 |

|      | 3.2.     | Uniformity                                    | 48 |

|      |          | 3.1.1. Intra-Wafer Uniformity                 | 48 |

|      |          | 3.1.2. Batch-to-Batch Uniformity              | 50 |

|      |          | 3.1.3. Monte Carlo Simulation Environment     | 51 |

|      | 3.3.     | Stability                                     | 52 |

|      |         | 3.2.1.    | Bias-Stability                                                   | 52   |

|------|---------|-----------|------------------------------------------------------------------|------|

|      |         | 3.2.2.    | Photo-Stability                                                  | 56   |

| 4.   | Over    | coming    | the TFT Non-idealities on Analogue Circuits                      | 58   |

|      | 4.1.    | Lack      | of Proper Active Load                                            | 58   |

|      |         | 4.1.1.    | Limitations of Conventional Structures                           | 58   |

|      |         | 4.1.2.    | Monotype Active Load Structures                                  | 59   |

|      |         | 4.1.3.    | Gain Boosting Techniques                                         | 61   |

|      |         | 4.1.4.    | Active Loads for the ISO TFT                                     | 63   |

|      | 4.2.    | Large     | Parasitic Capacitances                                           | 65   |

|      |         | 4.1.5.    | TFT Layout                                                       | 67   |

|      |         | 4.1.6.    | Capacitive and Inductive Peaking                                 | 68   |

| 5.   | All-T   | TFT Amp   | plifier                                                          | 71   |

|      | 5.1.    | Desigr    | 1 Goals                                                          | 71   |

|      | 5.2.    | Ampli     | fier Design                                                      | 73   |

|      | 5.3.    | Simul     | ation                                                            | 76   |

|      |         | 5.3.1.    | DC Operating Point and Static Power Consumption                  | 78   |

|      |         | 5.3.2.    | Gain, Bandwidth, and Phase Margin                                | 79   |

|      |         | 5.3.3.    | <b>Output Dynamic Range, Signal Distortion, and Slew 1</b><br>80 | Rate |

|      |         | 5.3.4.    | Monte Carlo Simulation Results                                   | 83   |

|      | 5.4.    | Layou     | it and Fabrication                                               | 84   |

|      | 5.5.    | Measu     | rement Results                                                   | 85   |

|      |         | 5.4.1.    | Measurement Kit                                                  | 85   |

|      |         | 5.4.2.    | Capacitor Array                                                  | 87   |

|      |         | 5.4.3.    | Output Stage                                                     | 88   |

|      |         | 5.4.4.    | Proposed Amplifier                                               | 90   |

| 6.   | Conc    | lusions a | and Future Work                                                  | 94   |

| Refe | erences |           |                                                                  | 100  |

| Арр  | endix A | •••••     |                                                                  | 107  |

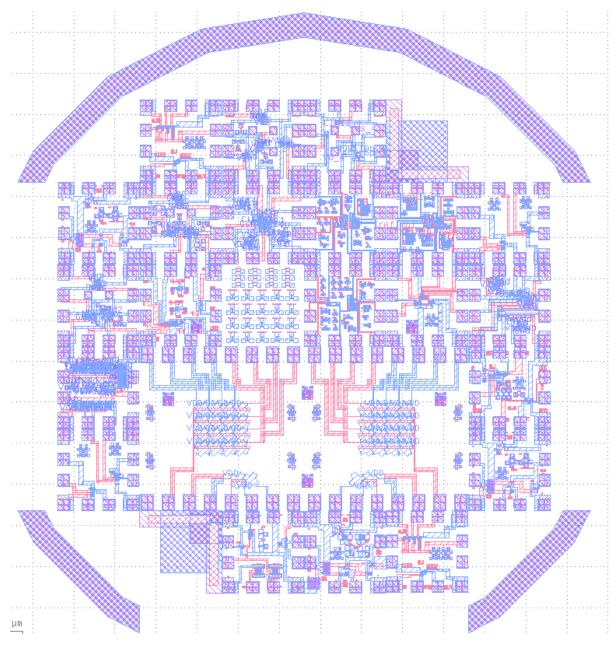

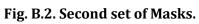

| Арр  | endix B | •••••     |                                                                  | 110  |

| Арр  | endix C | •••••     |                                                                  | 114  |

|      |         |           |                                                                  |      |

# List of figures

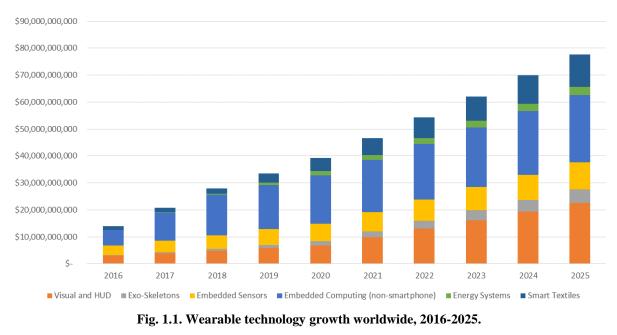

- 1.1. Wearable technology growth worldwide, 2016-2025.

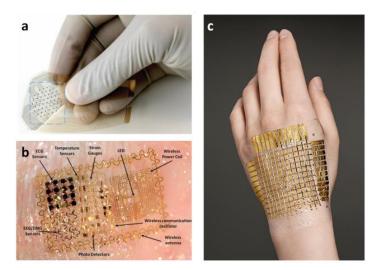

- 1.2. Sensor platform proof of concepts: (a) smart bandage, (b) skin-like/tattoolike sensor, (c) artificial skin.

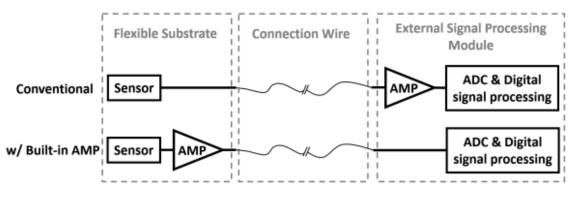

- 1.3. Built-in pre-amplifier for sensors.

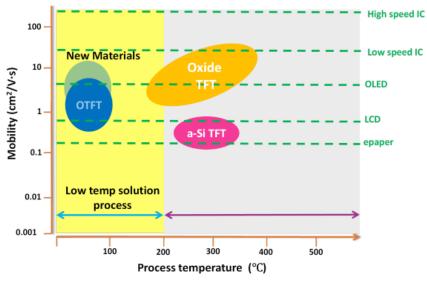

- 1.4. Mobility and process temperature of different types of TFTs.

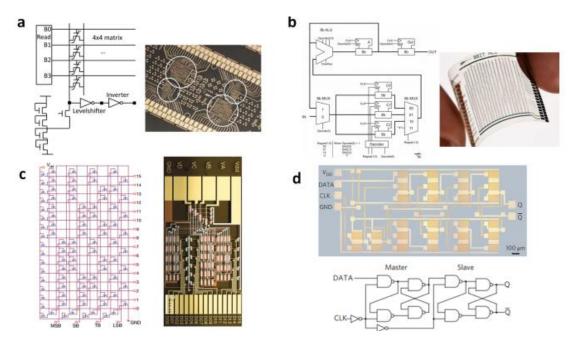

- 1.5. State-of-art digital circuits: (a) non-volatile re-addressable memory, (b) 8-bit

40-instructions-per-second microprocessor, (c) a 4-bit decoder, and (d) a master-slave delay flip-flop.

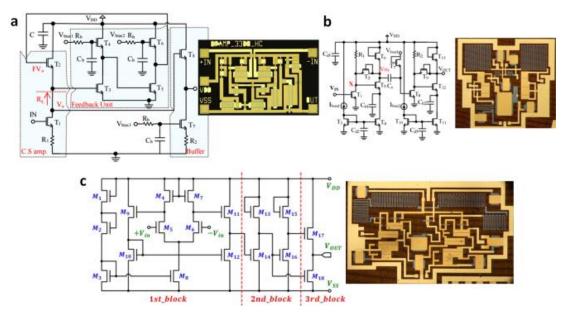

- 1.6. State-of-art analogue circuits: (a) a high gain amplifier, (b) a Cherry-Hooper amplifier, and (c) a three-stage operational amplifier.

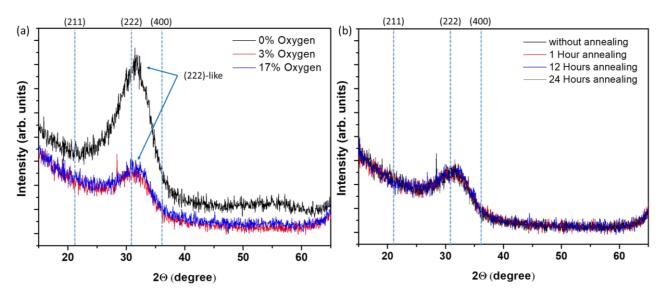

- 2.1. XRD data of (a) the as-deposited ISO films with different oxygen flow rate ratios and (b) the 3% oxygen films under different annealing conditions.

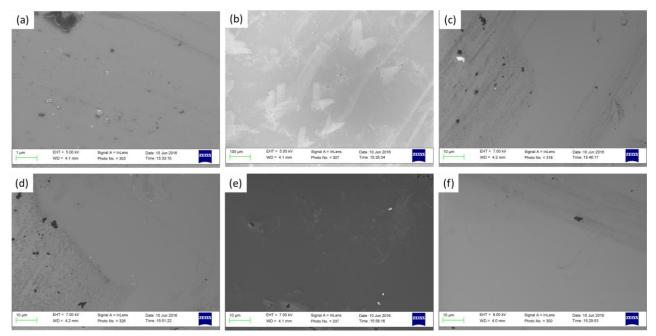

- 2.2. SEM pictures of the as-deposited ISO films with varying oxygen ratios: (a) 0%, (b) 3%, and (c) 17%; SEM pictures of the 3% oxygen ratio ISO film annealing for (c) one hour, (d) 12 hours, and (e) 24 hours.

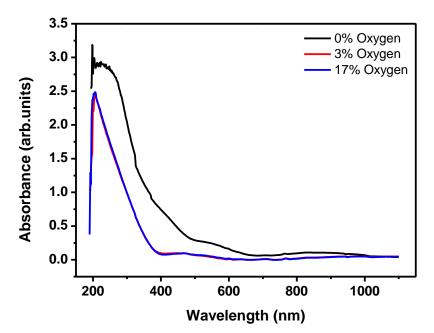

- 2.3. Optical absorption spectrum of the ISO film with varying oxygen ratios.

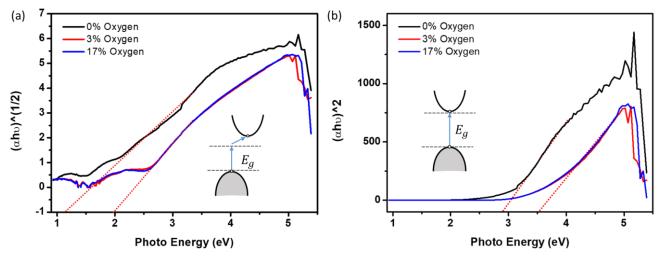

- 2.4. Tauc plot of the ISO film assuming that the transitions type is: (a) allowed indirect and (b) allowed direct.

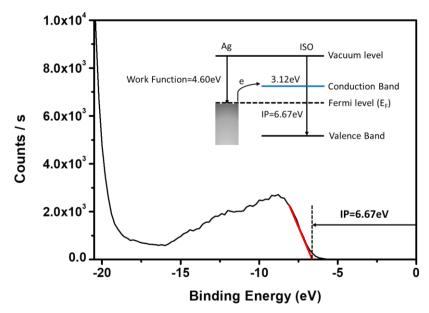

- 2.5. UPS low binding energy edge of the ISO thin film on a silicon substrate, inset figure is the schematic band diagram for the ISO/Ag

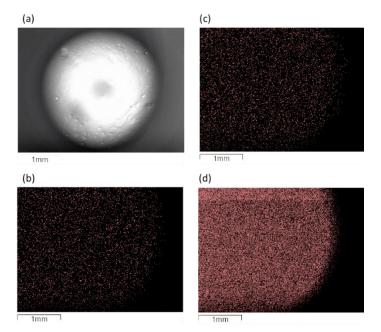

- 2.6. EDS elemental mapping: (a) selected area on the sample, (b) O mapping, (c) In mapping, and (d) Si mapping.

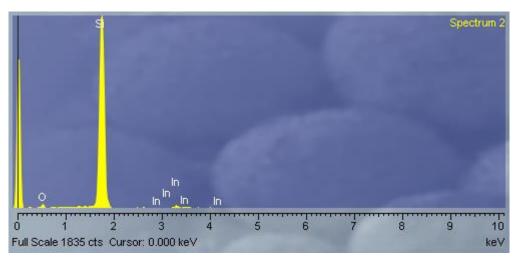

- 2.7. Energy dispersed electron spectra of the ISO film.

- 2.8. Fabrication process for the In-Si-O TFT.

- 2.9. An example of the design rules.

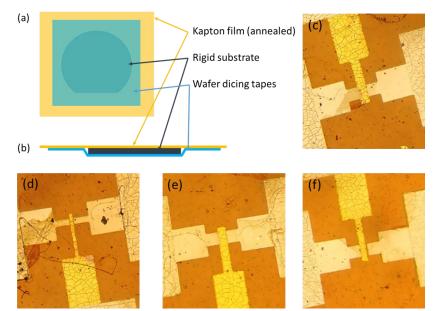

- 2.10. (a) The Kapton HN sheet was heated for two hours at 200 °C. (b) The yield test regions on the 3-inch TFT array masks. (c), (d), (e), and (f) are photos of the selected transistors in the yield test regions.

- 2.11. (a) Top-view and (b) cross-sectional view of the proposed solution to plastic shrinkage. (c), (d), (e), and (f) are photos of the selected transistors in the yield test regions on the substrate.

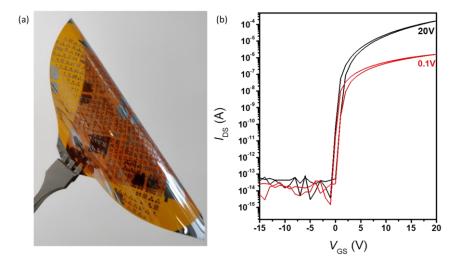

- 2.12. (a) The ISO TFT array on a Kapton HN sheet. (b) Typical performance of the TFT on plastic.

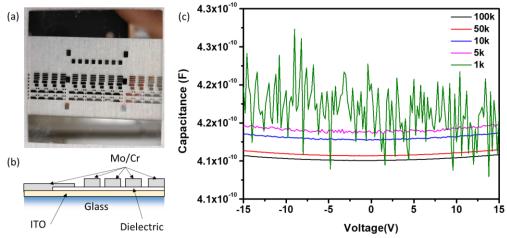

- 2.13. (a) Picture and (b) cross-sectional view of the capacitor array. (c) C-V measurement of a capacitor in the array at different frequencies.

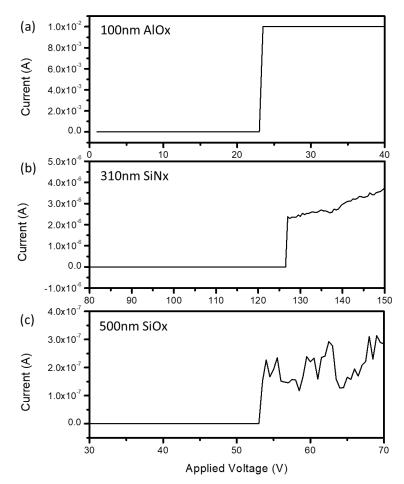

- 2.14. Results from dielectric breakdown testbench for (a) 100 nm AlO<sub>x</sub>, (b) 310 nm SiN<sub>x</sub>, and (c) 500 nm SiO<sub>x</sub>.

- 2.15. Conduction mechanism for the Mo/ISO contacts.

- 2.16. (a) Two samples for the contact resistance measurement. (b) Cross-sectional view of the samples. (c) I-V characteristics of the Mo/ISO contacts with various semiconductor deposition recipes.

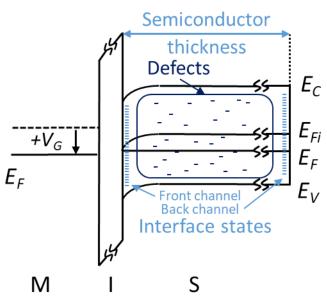

- 2.17. Possible interface state and defect locations in the In-Si-O bandgap diagram.

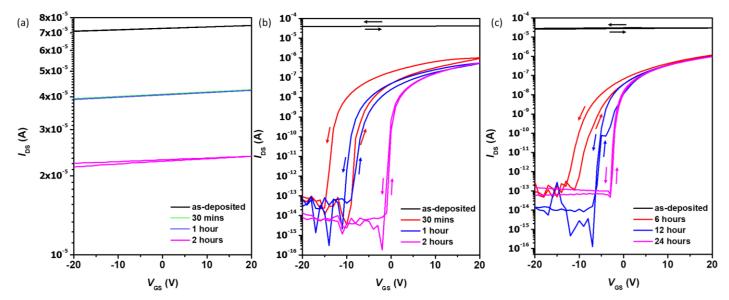

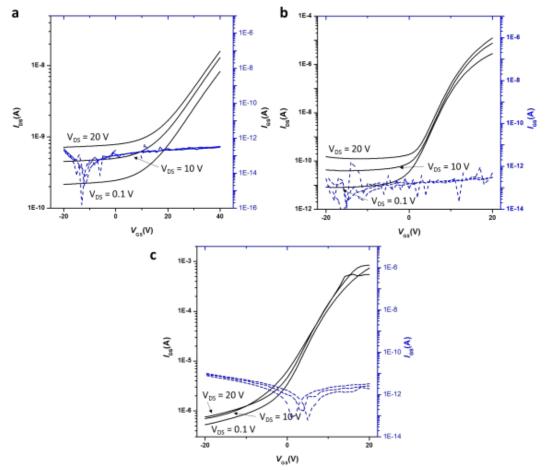

- 2.18. The transfer characteristics at  $V_{DS}=10V$  for (a) the ISO TFT annealed in nitrogen (glove box) at 200°C, (b) the ISO TFT annealed in atmosphere at 200°C, and (c) the ISO TFT annealed in atmosphere at 150°C.

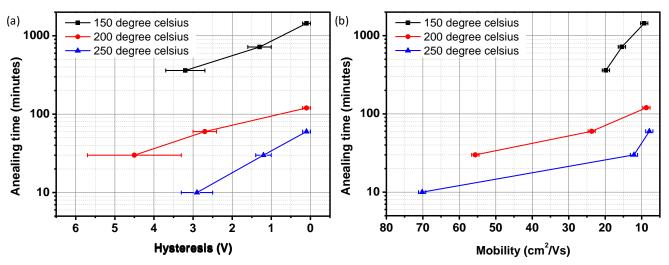

- 2.19. Transistor properties of ISO TFT over various annealing temperatures, showing changes in (a) hysteresis and (b) mobility.

- 2.20. (a) The transfer characteristics of the ISO TFTs with different channel thicknesses at  $V_{DS}$ =10V. (b) The corresponding extracted mobility and threshold voltage.

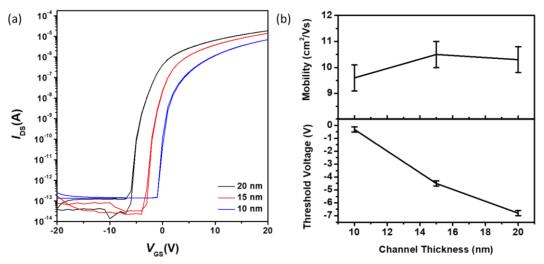

- 3.1. GUI of the parameter extraction toolkit for a universal TFT model

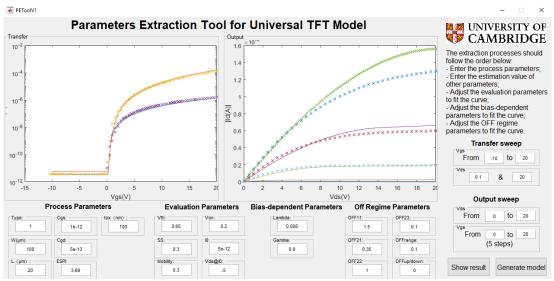

- 3.2. Test regions and stamp design of the TFT array on a 4-inch substrate.

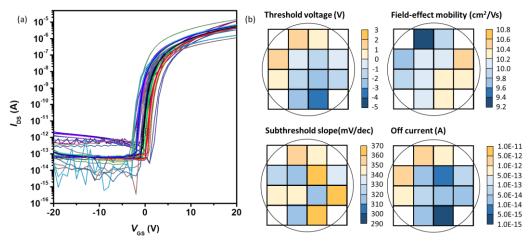

- 3.3. (a) The transfer characteristics of 16 ISO TFTs distributed across a 4-inch glass substrate at  $V_{DS}$ =10V. (b) Extracted ISO TFT parameters, in the form of wafer spatial distribution maps.

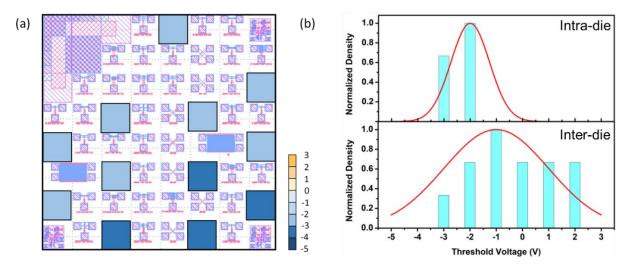

- 3.4. (a) Intra-die threshold voltage mapping. (b) Comparison of the intra-die and inter-die variations.

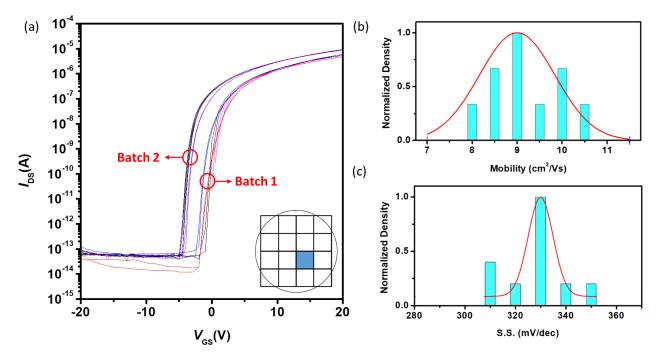

- 3.5. (a) Comparison of 10 selected transfer characteristics from two batches of the TFT array, insert is the position of the selected die. The batch-to-batch (b) mobility and (c) subthreshold swing variations.

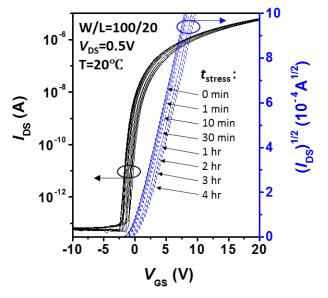

- 3.6. Evolution of bias stress on the transfer characteristics of the ISO TFT at 20°C.

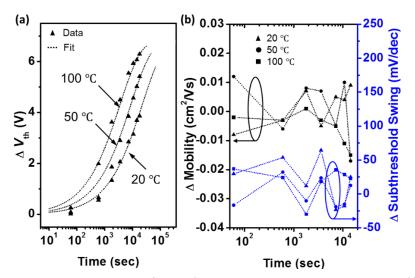

- 3.7. Parameters extracted from bias stress measurements at three different temperatures: (a) threshold voltage shift versus stress time, and (b) mobility and subthreshold swing shift versus stress time.

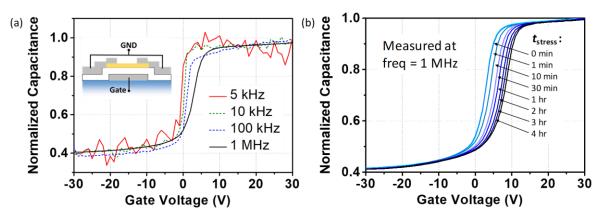

- 3.8. (a) C-V characteristics as a function of frequency for the ISO TFTs, insert is the TFT configuration. (b) Evolution of bias stress on the C-V characteristics at 20°C.

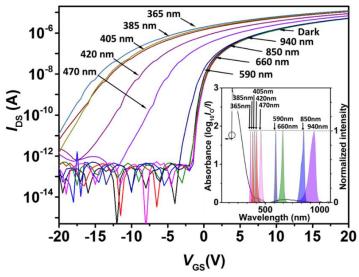

- 3.9. Transfer characteristics of ISO TFTs under exposure to light at different wavelengths, insert is the UV-Vis absorbance of the ISO film and normalized spectroscopy of the LED intensities, the spectral data of LEDs were adapted from Thorlabs datasheets.

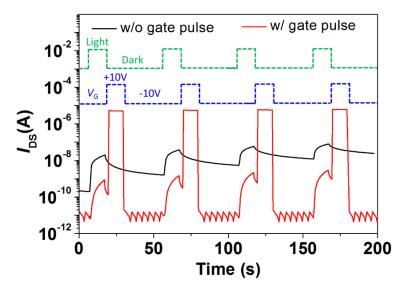

- 3.10. Generation, recovery, and elimination of persistent photoconductivity at 20V V<sub>DS</sub> under exposure to pulse illumination.

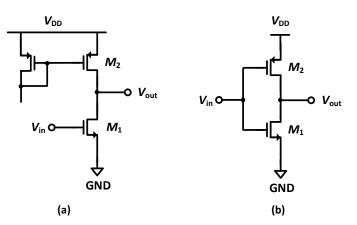

- 4.1. Active load for an amplifier. (a) Amplifier with current mirror as active load.(b) Class AB amplifier.

- 4.2. Pseudo-CMOS amplifier

- 4.3. Small signal equivalent circuit of the pseudo-CMOS.

- 4.4. Structures of (a) the current starving and (b) current cancellation techniques.

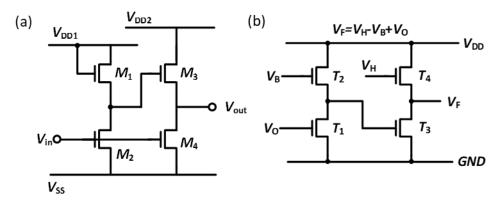

- 4.5. Bootstrapping diode-connected active load: (a) schematic, and (b) small-signal equivalent circuit.

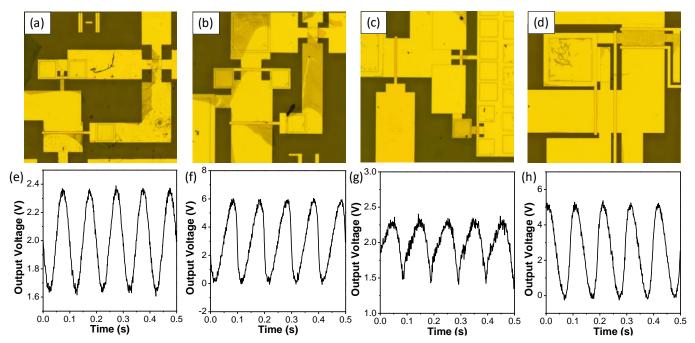

- 4.6. Pictures of (a) diode-connected load amplifier, (b) depletion load amplifier, (c) bootstrapping load amplifier, and (d) pseudo-CMOS amplifier. (e), (f), (g), and (h) are the corresponding output signals of the amplifiers with sine wave input signals.

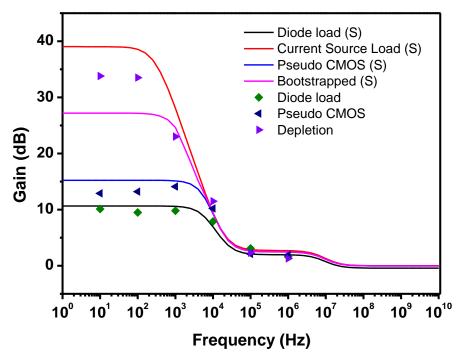

- 4.7. Performance comparison of the active loads, lines represent simulation results and the scattered points are measured data.

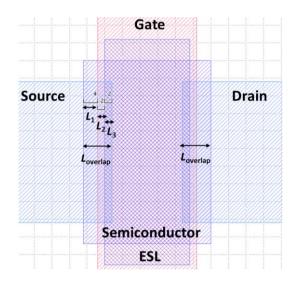

- 4.8. Top view of the ISO TFT layout, showing the overlap between layers.

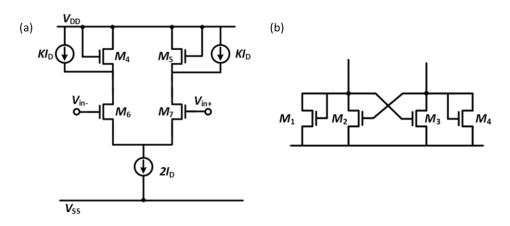

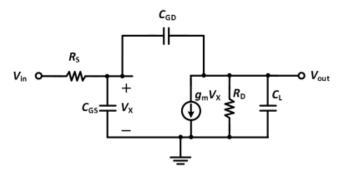

- 4.9. Small-signal equivalent circuit of common-source TFT amplifier.

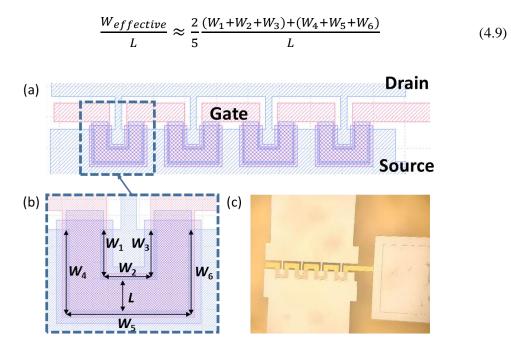

- 4.10. (a) Top view of the island-structure TFT. (b) Top view of the single cell in the TFT. (c) Picture of the island-structure TFT.

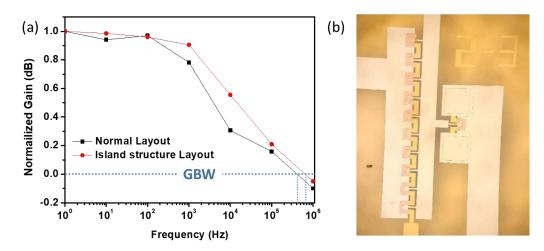

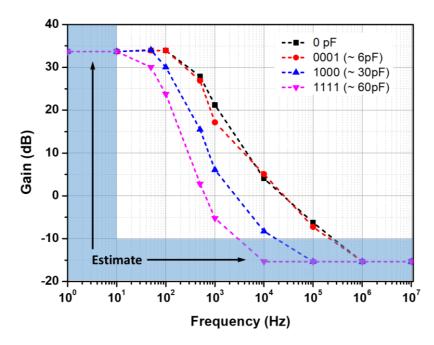

- 4.11. (a) Bode plot comparison of the normal layout and the island structure diodeconnected amplifier layout. (b) Top view of the island-structure diodeconnected amplifier layout.

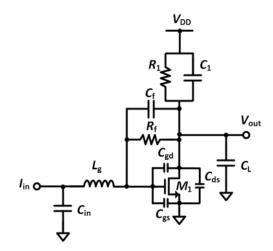

- 4.12. TIA with gate peaking inductor.

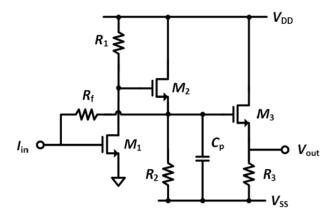

- 4.13. Circuit schematic of capacitive peaking TIA.

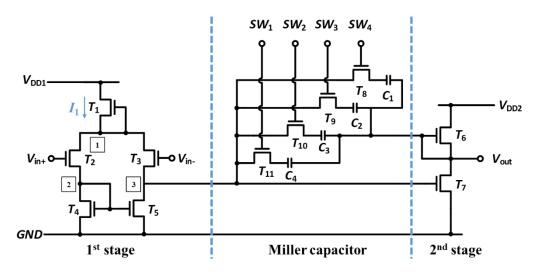

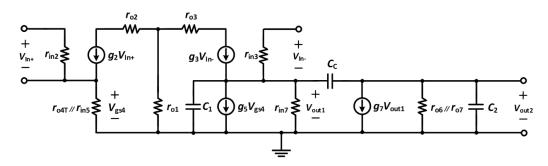

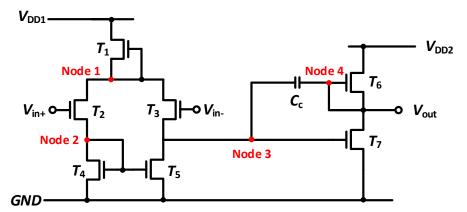

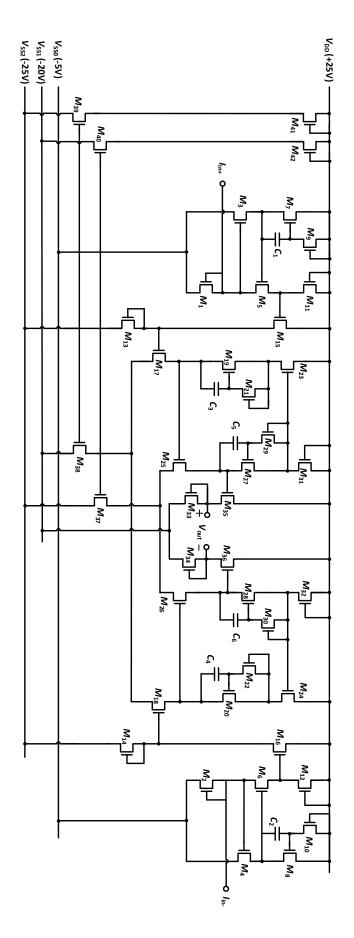

- 5.1. Schematic of the proposed all-TFT amplifier.

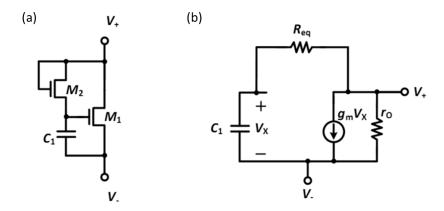

- 5.2. Simplified small-signal equivalent circuits of the all-TFT amplifier

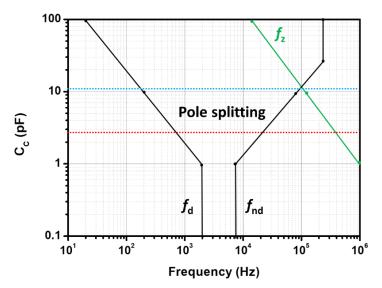

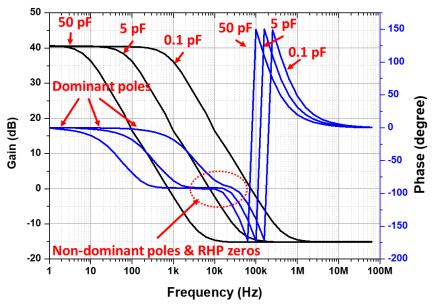

- 5.3. Relationship between compensation capacitor and zero/poles of the proposed amplifier.

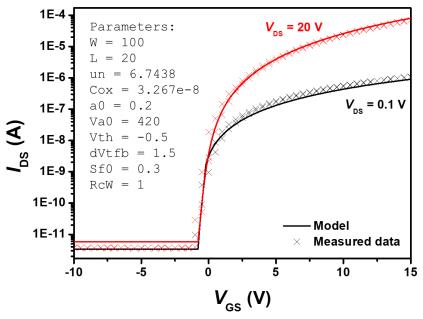

- 5.4. The ISO TFT model used in the simulation.

- 5.5. Schematic of the all-TFT amplifier used in the simulation.

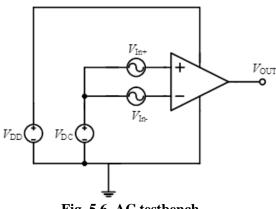

- 5.6. AC testbench.

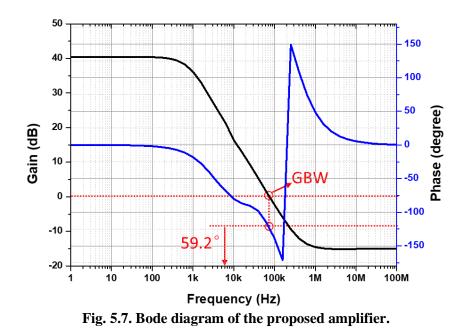

- 5.7. Bode diagram of the proposed amplifier.

- 5.8. The impact of the compensation capacitor on the Bode diagram.

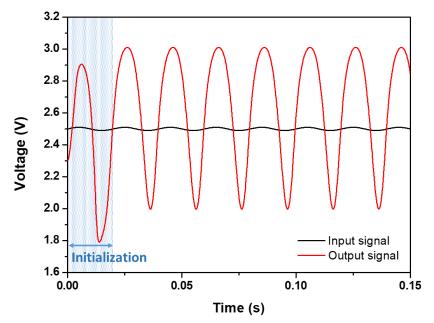

- 5.9. Input and output signals in the simulation.

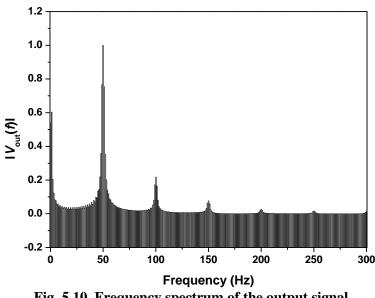

- 5.10. Frequency spectrum of the output signal.

- 5.11. Slew rate of the proposed amplifier.

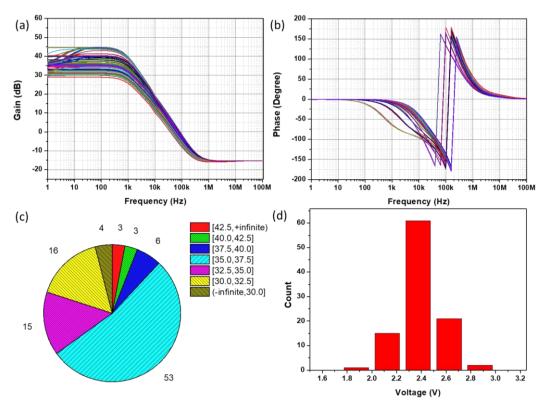

- 5.12. Monte Carlo simulation: (a) gain, (b) phase, (c) DC gain, and (d) output voltage level statistics.

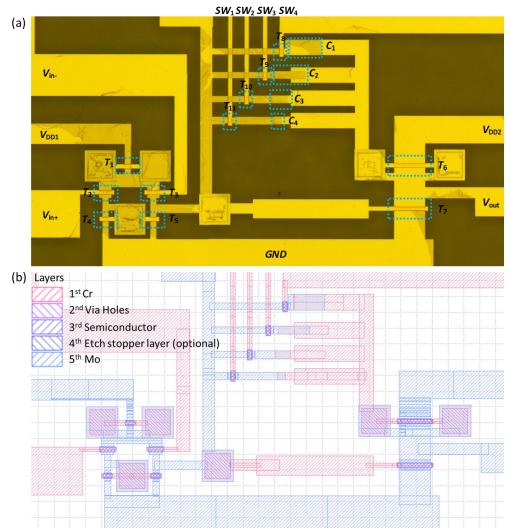

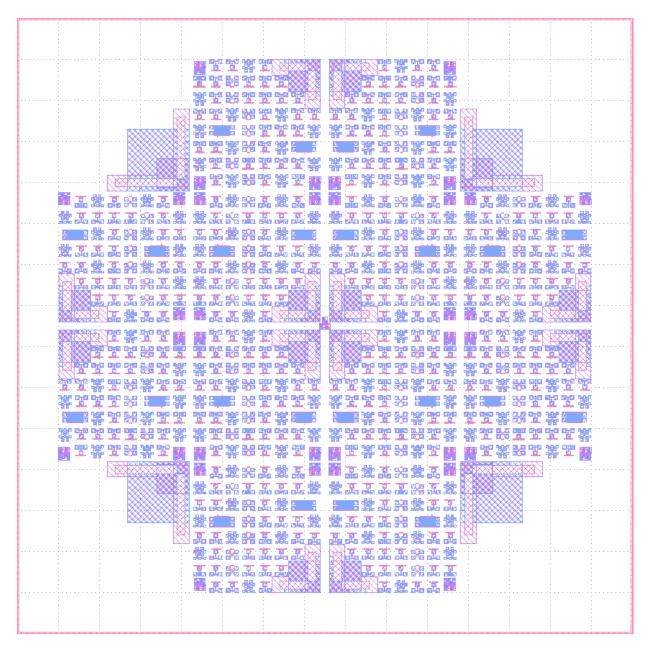

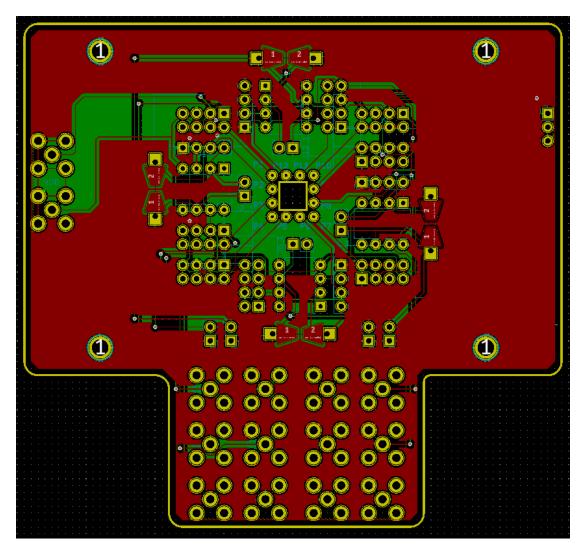

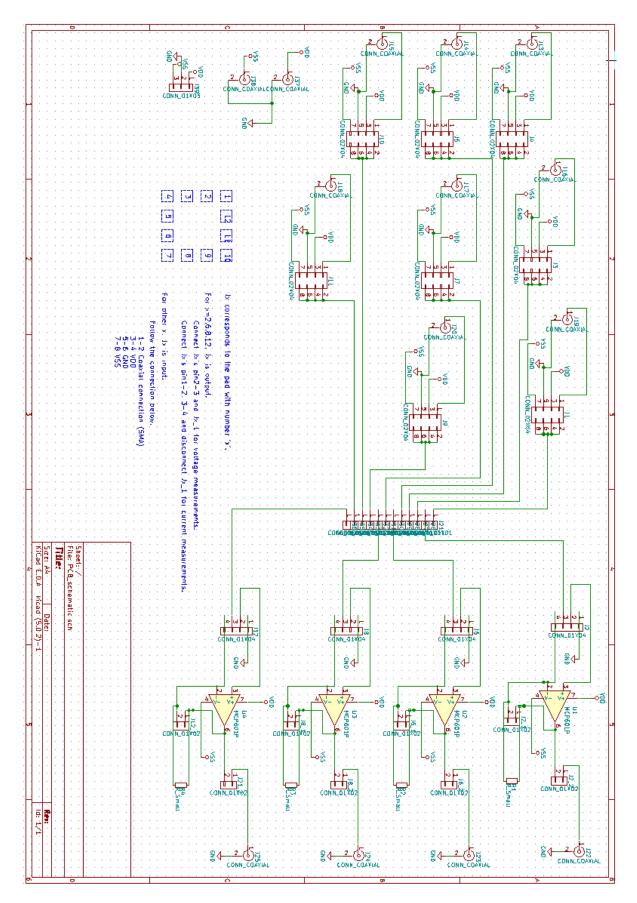

- 5.13. (a) Photo of the glass substrate on which the amplifier was formed, (b) layout design of the amplifier.

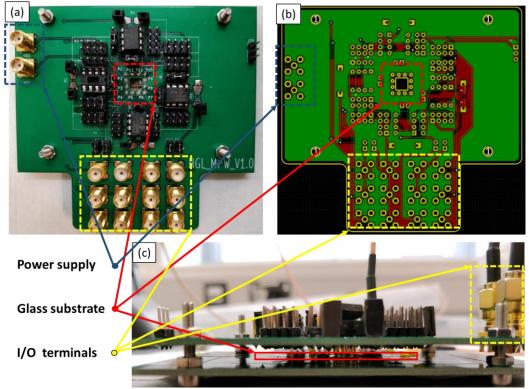

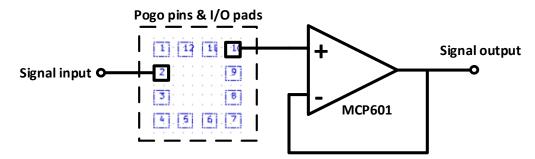

- 5.14. (a) Top view, (b) layout, and (c) cross-sectional view of the measurement kit.

- 5.15. Simplified schematic of the measurement kit.

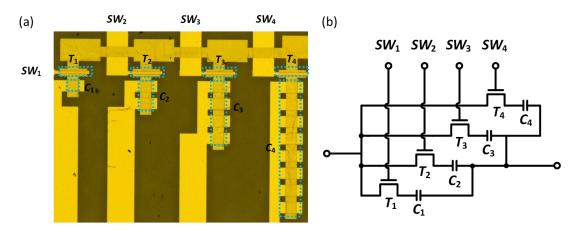

- 5.16. (a) Photo of the capacitor array and its (b) circuit diagram.

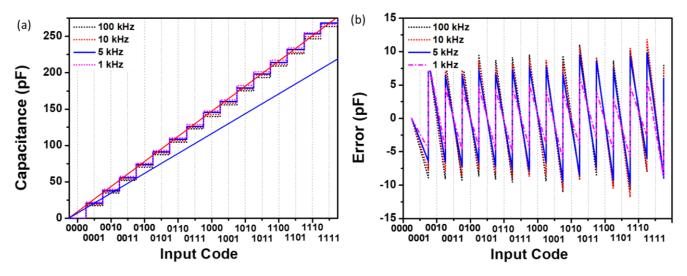

- 5.17. (a) Capacitance and (b) the quantisation error of the capacitor array.

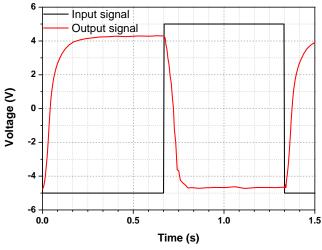

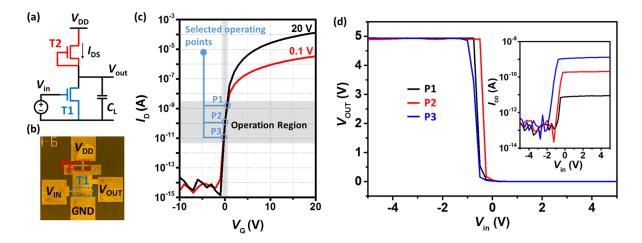

- 5.18. (a) Schematic, (b) photo, (c) sub-threshold operating points, and (d) the corresponding input/output characteristics of the output stage.

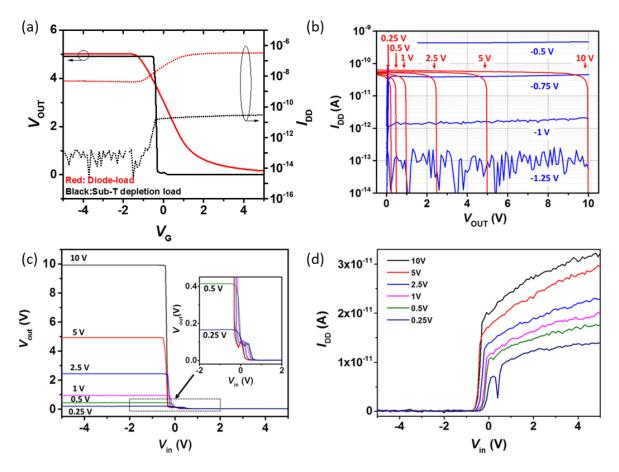

- 5.19. (a) Comparison between diode-load and sub-threshold depletion load. (b)Output characteristics of the load transistor and the driving transistor. (c)Output signals of the amplifier and its (d) corresponding operating currents.

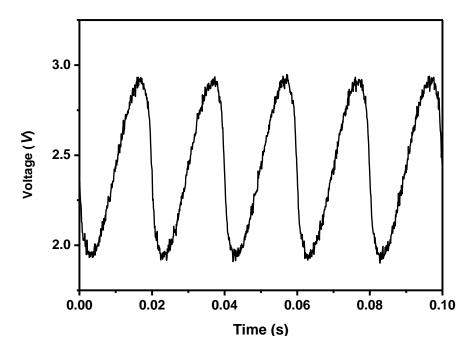

- 5.20. Output signal of the proposed amplifier with a 50 Hz, ±12.5 mV pk-pk input sine wave.

- 5.21. Bode diagram of the proposed amplifier.

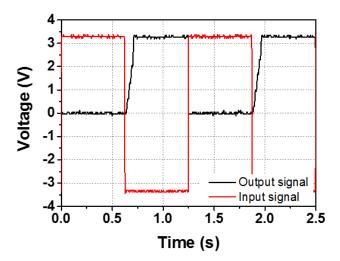

- 5.22. Slew-rate testbench for the proposed amplifier.

# List of tables

- 2.1. Thickness of the deposited films on 4-inch substrates

- 2.2. Etching techniques details.

- 2.3. Selective etching that protects the bottom layer.

- 2.4. Misalignment in the yield test regions on the sample.

- 2.5. Measurement results of the deposited dielectric layers.

- 2.6. Verified ohmic metal-semiconductor contacts.

- 3.1. Statistical data for the Monte Carlo analysis.

- 4.1. Performance of common-source amplifiers with different active loads.

- 5.1. Target specifications for the all-TFT amplifier.

- 5.2. Dimensions of the TFTs in the proposed amplifier.

- 5.3. Node voltages, static current, and power consumption under different second stage supply voltages.

- 5.4. THD of the output signal at different output ranges.

# Nomenclature

## Symbols

| λ  | Wave length           |

|----|-----------------------|

| Ω  | Ohm                   |

| σ  | Standard deviation    |

| er | Relative permittivity |

| 03 | Vacuum permittivity   |

| q  | Elementary charge     |

| h  | Planck constant       |

|    |                       |

## Acronyms/Abbreviations

| MOSFET | Metal-Oxide-Semiconductor Field-Effect Transistor |

|--------|---------------------------------------------------|

| HUD    | Head-up Display                                   |

| PCB    | Printed Circuit Board                             |

| TFT    | Thin Film Transistor                              |

| AOS    | Amorphous Oxide Semiconductor                     |

| ISO    | Indium-Silicon-Oxide                              |

| RF     | Radio Frequency                                   |

| XRD    | X-ray diffraction                                 |

| JCPDS  | Joint Committee on Powder Diffraction Standards   |

| SEM    | Scanning electron microscope                      |

| UV-Vis | Ultraviolet-visible spectroscopy                  |

| DFT    | Density Functional Theory                         |

| UPS    | Ultraviolet photoelectron spectroscopy            |

| IP     | Ionization potential                              |

| EDX    | Energy-dispersive X-ray spectroscopy              |

| SD     | Standard deviation                                |

|        |                                                   |

| MIS    | Metal-Insulator-Semiconductor           |

|--------|-----------------------------------------|

| GUI    | Graphical User Interface                |

| CMOS   | Complementary Metal Oxide Semiconductor |

| ADC    | Analog-to-Digital Converter             |

| RHP    | Right half-plane                        |

| GBW    | Gain-bandwidth product                  |

| HF     | Hydrofluoric                            |

| TLC    | Tap-limited conduction                  |

| FFT    | Fast Fourier Transform                  |

| THD    | Total Harmonic Distortion               |

| Op-amp | Operational amplifier                   |

| SNR    | Signal-to-noise ratio                   |

| DAC    | Digital-to-Analog Converter             |

|        |                                         |

# Chapter 1

# Introduction

This chapter provides the background for amorphous oxide semiconductor (AOS) thin-film transistors (TFT), and discusses the motivation to develop the In-Si-O TFT photo-lithography process and all-TFT circuit. In Section 1.1, the promising future of TFT is revealed. The developing trends for TFT applications, mainly sensors and the unique properties of all-TFT integrated circuits, along with potential applications, are provided. Section 1.2 reviews the background of AOS TFTs and all-TFT circuits. Overall objectives of this dissertation are given in Section 1.3.

### **1.1.** Motivation

AOS TFTs have already become the sole choice for large area-based applications, including screens and large-area imaging [1]–[3]. Unlike Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET), the development of TFTs largely relies on new application scenarios, as opposed to more advanced fabrication processes for a smaller device [4]. Therefore, it is imperative to explore new avenues for TFT applications.

With the recent popularization of smart phones, wearables, and portable sensing platforms, flexible electronics and sensors have attracted worldwide attention [5]–[7]. A large number of gadgets, accessories, and wearable electronics emerged for mobile devices; this phenomenon expanded the flexible electronics and sensor market dramatically. According to the Wearable Robotics Association, from 2016 to 2025, the global market forecast for wearable technologies is expected to have a 21.1% compounded annual growth rate. The visual/Head-up Display (HUD) and smart textiles market will contribute most of the growth and will continue to lead other sectors in terms of sales and growth. These two technologies provide more interactive response

and feedback to users than the current technologies. TFTs are likely to be widely used in display-related and textile-related electronics [8]–[10].

At the same time, concepts such as the Internet-of-things (IoT) and wireless sensor networks (WSN) continue to heat up the sensor market [11]–[14]. It is predicted that sensors will become one of the biggest businesses in the history of wearable electronics. With a growing demand for health and environmental monitoring, a sensor platform that can measure the physical response of the wearer and status of his/her surrounding environment becomes essential for portable electronics. Consequently, building such a platform has aroused intense interest in both academia and industry [15], [16].

Source: Wearable Robotics Association

In order to meet the future demand in a variety of fields, the next generation of electronics requires significant improvements in sensitivity, specificity, and comfortability [17]–[20]. Conventional electronic modules are typically based on printed circuit board (PCB) and silicon chips, which are inflexible and bulky. For instance, the set-up procedures of a conventional sensor require conductive gel, tape, or wires to ensure proper contact between the hardware and the objective surface, which is not only time-consuming, but it also constrains the movement of the wearer. An ideal sensor platform for wearable electronics should be skin-like; more specifically, the sensor platform should be ultrathin, flexible, stretchable, and even self-healing [21][22]. Several concepts of future sensor platforms are shown in Fig. 1.2, including the smart bandage [23], a skin-like/tattoo-like sensor [24], and artificial skin [25]. These

platforms were designed to continuously monitor uterine contractions, heart rate, oxygen levels, and body temperature [26], [27]. The platforms must also integrate different types of sensors, wireless communication modules, and related circuits [28].

Fig. 1.2. Sensor platform proof of concepts: (a) smart bandage [23], (b) skin-like/tattoolike sensor [24], (c) artificial skin [25].

Many advances have already been made to improve sensing techniques, including new transduction mechanisms, different structural designs, and innovative materials [29]–[31]. Unfortunately, signal processing circuits for sensors have not received as much attention, even though a carefully designed configuration can greatly boost the performance of sensors. The signal conditioning circuits alone can dramatically compromise performance under certain conditions [32]. As shown in Fig.1.3, the signal conditioning circuit, usually an amplifier, is not fabricated on the same substrate as the sensor. In most cases, the sensor and the amplifier are two separate components connected by wires. The major disadvantage of this configuration is that the thermal noise generated on the connection wire is also amplified [33].

Fig. 1.3. Built-in pre-amplifier for sensors.

To avoid thermal noise amplification, the most straightforward solution is to move the amplifier to the front-end, which can dramatically increase the signal-to-noise ratio. Maximum performance of such configuration can be obtained when the amplifier is fabricated on the same substrate as the sensors. In addition to thermal noise, commonmode noise generated from an external source may compromise the performance of the amplifier. For long-distance connection wires, screened or twisted-pair cabling is used to cancel out the external electromagnetic interference [34]. However, for wearable electronics based on thin film techniques, the realisation of screened/twisted pair cabling is not practical and the wire length is relatively short [35]. Therefore, a differential input pair is used to suppress the common-mode noise generated on a medium-distance connection wire [36].

However, building circuit components based on a flexible substrate is not an easy task [37]. The electrical properties and fabrication techniques of elastic materials, mostly thin-film materials, are very poor compared to conventional III-V semiconductors [38]. Traditionally, much of the preliminary work in thin-film electronics centred around area-intensive applications, such as flat panel displays and photovoltaics [39], [40]. These applications are less sensitive to component performance, but require the capability to cover a large area. In recent years, rapid development of thin-film materials has led to a great improvement in thin film electronics. The involvement of new materials, including metal-oxide, organic, one-dimension, and two-dimension materials has boosted the performance of thin-film electronic components, which are now used in conventional applications with uniquely advantageous performance benefits [41]–[44].

The scope of applications envisioned for thin-film electronics is expanding substantially, especially in novel concepts, such as an integrated sensor, printed radio frequency identification, and electroluminescent phosphor [45]–[48]. Thin-film electronics offer low cost, large area compatibility, high scalability, and extreme potential for flexibility. Most notably, field-effect transistors based on TFTs can be fabricated at low temperatures on a variety of substrates [49], [50]. In addition, the intrinsic mobility of the semiconductor materials used in TFTs has increased exponentially over the past few decades [51]. Today's commercially available thin-film semiconductors have mobility performance in the range of 1 cm<sup>2</sup>/Vs to 20 cm<sup>2</sup>/Vs. Fig 1.4 summarizes data collected by Plastic Logic. It shows the mobility and process temperature of different types of TFTs. Although the mobility remains low, especially

at low fabrication temperatures, some TFTs can be used to design simple circuits. As performance increases, TFTs will become a more attractive option for the design and fabrication of flexible electronic external circuits [52], [53].

Fig. 1.4. Mobility and process temperature of different types of TFTs. Source: Plastic Logic

### 1.2. Background

AOSs have been investigated extensively as a promising semiconductor for nextgeneration electronics TFTs. The AOS has many appealing properties, including low processing temperature, large-area uniformity, wide bandgap, high transparency, and high mobility [54]. Amorphous indium oxide (a-InO<sub>x</sub>)-based semiconductors are believed to be the most promising semiconductors for TFT [55]. Previous reports on a-InO<sub>x</sub> detailed the following types: InGaZnO, InSnZnO, InZnO, InWO, InYO and InSiO TFTs [56]–[58].

Among all the a-InO<sub>x</sub> TFTs, IGZO is the most widely used semiconductor in both industry and academia. The IGZO TFT was first proposed in 2004. Its high mobility is attributed to the direct overlap of the isotropic s orbitals of its indium atoms [59]. Its crystallization and hall mobility can be controlled by changing the composition of the film. Gallium, which has different ionic charges and sizes, is mixed into the film to form amorphous phases and suppress the formation of oxygen vacancy, thus reducing instability. Increasing the indium content can boost the intrinsic mobility. The best stoichiometry of In:Ga:Zn:O occurs at ratios of 1:1:1:4 or 2:2:1:7. The electrical properties of the film can be moderately changed near the best recipe, allowing

engineers to adjust the material to meet different requirements [60]–[62]. However, IGZO is not perfect, and suffers from instability. The IGZO TFT is sensitive to bias/current stress, temperature, light illumination, and water vapour exposure [63]–[66]. It is widely accepted that oxygen vacancy acts as a hole trap, and is a major contributor to the instability issue. To suppress the impact of oxygen vacancy on the transistor's performance, one or more cations in IGZO must be replaced with other materials [67].

Recently, Shinya *et al.* reported a new material, the In-Si-O (ISO) [68]. ISO uses silicon to suppress the instability originating from the oxygen vacancy. The silicon-oxygen bond has higher dissociation energy, which improves the retention of oxygen atoms in the film, and thus increases stability. The ISO TFTs were fabricated with stencil shadow masks on a silicon substrate, and the deposition of ISO was by DC sputtering. By varying the silicon oxide content, field-effect mobility was regulated from 5 cm<sup>2</sup>/Vs to 30 cm<sup>2</sup>/Vs. Changing the argon-to-oxygen ratio during sputtering adjusted mobility, threshold voltage, and subthreshold swing over a certain range [69]–[71]. These features show great potential for TFT-based circuits and systems.

Fig. 1.5. State-of-art digital circuits: (a) non-volatile re-addressable memory [72], (b) 8bit 40-instructions-per-second microprocessor [73], (c) a 4-bit decoder [74], and (d) a master-slave delay flip-flop [75].

In terms of all-TFT circuits, Fig. 1.5 shows the state-of-art, which includes non-volatile re-addressable memory [72], an 8-bit 40-instructions-per-second microprocessor [73], a 4-bit decoder [74], and a master-slave delay flip-flop [75]. The

performance of these circuits (i.e. the clock rate) is on par with MOSFET technology from fifty years ago.

For analogue TFT circuits, the state-of-art is demonstrated in Fig. 1.6 [76]–[78]. Although some specifications of the amplifiers are acceptable, specifications including bandwidth, input and output impedance usually cannot meet practical needs. Drawbacks of TFT circuits can be traced back to the properties and fabrication processes of thin film transistors. Low intrinsic mobility and high threshold voltage lead to low transconductance, which is usually on the order of 10<sup>-6</sup> Siemens, while an MOS transistor can reach 10<sup>-3</sup> Siemens. Therefore, to obtain an equivalent gain, the load in a TFT amplifier will need to be at least a thousand times larger than that in a MOSFET amplifier.

Fig. 1.6. State-of-art analogue circuits: (a) a high gain amplifier [76], (b) a Cherry-Hooper amplifier [77], and (c) a three-stage operational amplifier [78].

### **1.3.** Dissertation Outline

The objective of this dissertation is to investigate the remaining challenges associated with the ISO material, device, and system integration. The outline of this dissertation is as follows. **Chapter 2** details ISO TFT development and characterisation. Basic material properties of the ISO film are discussed, including amorphicity, bandgap, stoichiometry, and Hall-effect parameters. **Chapter 3** presents the uniformity and stability data from a TFT array using the photo-lithography process. Origins of the threshold voltage shift in bias-stress measurement are carefully evaluated using C-V

and field-effect measurements. The spatial and temporal variations of ISO TFT are used to verify and quantitate the capability of the process in system integration and circuit design. A Monte-Carlo simulation environment was established based on the extracted data. **Chapter 4** addresses two of the most urgent challenges in all-TFT analogue circuit design, which are the lack of proper active load and the large parasitic capacitance. Indepth analysis of these two issues and applicable solutions are given. **Chapter 5** presents the process of designing, simulating, and fabricating an all-TFT amplifier. A 4-bit capacitor array was successfully integrated into the amplifier. Design strategy, simulation results, layout design, and measurement results are given in this chapter. **Chapter 6** summarizes the results obtained in this dissertation and discusses the novelty of this research. The outlook for future extension of this study is provided as well.

# **Chapter 2**

# **Indium-Silicon-Oxide TFT**

This chapter describes how the Indium-Silicon-Oxide (ISO) TFT was developed. Section 2.1 provides material characterisation results of the ISO using different techniques. Section 2.2 introduces the four-mask/six-mask process as well as the plastic process. Methods adopted to improve robustness are also given in this section. Section 2.3 provides characterisation results of the ISO TFTs.

### 2.1. Semiconductor Characterisation

Semiconductors, the vehicle and valve of electron flow, are the most important component of the TFT device. The characteristics of the materials are essential and prerequisite to building an outstanding TFT. In this section, the characteristics of deposited ISO film are examined.

#### 2.1.1. X-Ray Diffraction Spectroscopy

X-ray diffraction (XRD) measurements are widely used to validate whether a deposited film is amorphous [79]. Using this technique, the correlations between the semiconductor's microstructure, the deposition conditions, and the annealing conditions were investigated.

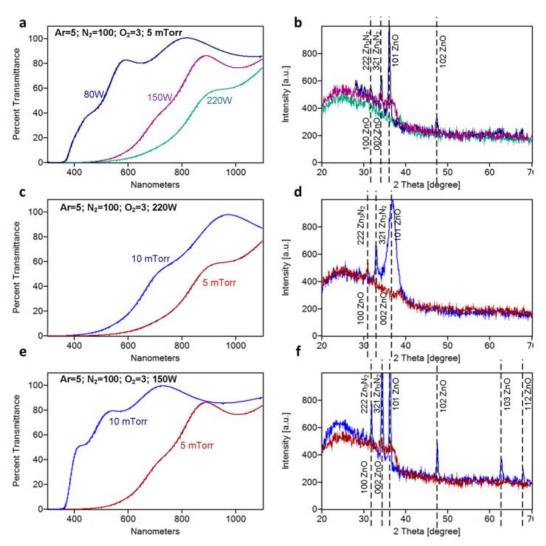

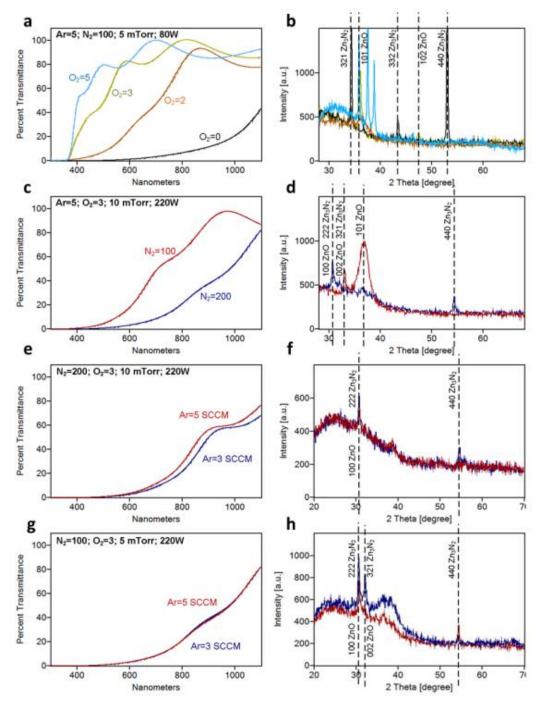

The ISO thin films were grown on an Si substrate using radio frequency (RF) sputtering employing a 90%  $In_2O_3$ , 10% SiO<sub>2</sub> ceramic target. The RF power of the electron guns was 150 W, and the ISO films were sputtered in a 4 mTorr atmosphere. The O<sub>2</sub>:(O<sub>2</sub>+Ar) flow rate ratio varied from 0% to 17%. During the sputtering, the ISO target was constantly moving/rotating to obtain uniformly coated films. By varying the

deposition time, the film thickness was fixed to 100nm. Prior to the deposition, the Si substrates were cleaned in an ultrasonic cleaner with de-ionized water, acetone, and isopropyl alcohol. Three different deposition conditions, namely three oxygen flow rate ratios were used to fabricate samples for the XRD measurements: 0%, 3%, and 17%. The samples were diced into 12 smaller pieces so that the impact of annealing conditions could be investigated as well. Four annealing conditions were tested: without annealing, one-hour of annealing at 150°C, 12 hours of annealing at 150°C, and 24 hours of annealing at 150°C.

The XRD measurements were conducted with the assistance of Joana Cerdeira at the Faculty of Sciences and Technology, Campus of Caparica. The equipment used was a PANalytical X'Pert PRO with Cu K $\alpha$  radiation ( $\lambda$ =1.540598 Å). Fig. 2.1 (a) compares the XRD data of the as-deposited ISO films with different recipes. Peaks at 31.3° were found in all films. According to the Joint Committee on Powder Diffraction Standards (JCPDS), 21.5° (211), 30.6° (222), and 35.5° (400) were assigned to the XRD 2 $\theta$  peaks of the cubic phase, c-In<sub>2</sub>O<sub>3</sub>. 31.3° is classified as a (222)-like peak. The (222) peak is asymmetric and broad, due to an overlap of two adjacent peaks or inhomogeneous strain. Compared with the 0% oxygen as-deposited sample, the 3% and 17% oxygen as-deposited samples had much weaker (222)-like peaks.

Fig. 2.1. XRD data of (a) the as-deposited ISO films with different oxygen flow rate ratios and (b) the 3% oxygen films under different annealing conditions.

Fig. 2.1 (b) shows the XRD data of the 3% oxygen ISO films under different annealing conditions. The annealing used an IKA hot plate (metal plate) in atmosphere. The temperature uniformity and stability of the hot plate were verified with a thermometer.

Similar trends were also found in the 0% and 15% annealing experiments. Thus, the 150°C annealing did not cause any crystallization changes in the ISO film.

Based on the XRD data, when there was no oxygen in the chamber during deposition, a very small amount of the polycrystalline ISO was found in the deposited film. Thus, feeding oxygen into the chamber can effectively reduce the polycrystalline. The 3% and 17% oxygen ratio deposited ISO was amorphous with and without 150°C annealing.

#### 2.1.2. Scanning Electron Microscope

A scanning electron microscope (SEM) was used to verify the conclusion in the previous section. The monocrystalline ISO grain was 20nm in size, which is detectable by SEM [80], [81]. The SEM photos were taken at Cambridge using a ZEISS SEM. As shown in Fig. 2.2, no visible crystalline grains or boundaries were found in the SEM pictures. Thus, all the deposited films were amorphous.

Fig. 2.2. SEM pictures of the as-deposited ISO films with varying oxygen ratios: (a) 0%, (b) 3%, and (c) 17%; SEM pictures of the 3% oxygen ratio ISO film annealing for (c) one hour, (d) 12 hours, and (e) 24 hours.

#### 2.1.3. Ultraviolet–Visible Spectroscopy

Ultraviolet–visible spectroscopy (UV-Vis) can be used to characterise the optical bandgap properties of amorphous materials. For inorganic semiconductors, there is very little interaction between electrons and holes; i.e. the exciton binding energy is very

small. Therefore, the optical bandgap and electronic bandgap are essentially identical [82].

The samples used in the measurement were annealed at 150°C for one hour. The measurement equipment was the Unicam UV4 UV/Vis Spectrophotometer. Fig. 2.3 shows the optical absorption spectrum of the ISO film with varying oxygen ratios. The 0% oxygen sample had a slightly higher absorbance than the 3% and 17% samples. The absorbance peaks became insignificant when the wavelength was longer than 500nm. Applying the Tauc method gives the relationship between optical bandgap and photon energy:

$$(hv\alpha)^{1/n} = A(hv - E_q) \tag{2.1}$$

where hv is the photon energy,  $\alpha$  is the absorption coefficient, A is the transition constant, and n is the power factor.

Fig. 2.3. Optical absorption spectrum of the ISO film with varying oxygen ratios.

With the band structure unknown, both allowed indirect and allowed direct transitions of the electrons were considered. Fig. 2.4 (a) shows the allowed indirect transition Tauc plot. The optical bandgap of the 0%, 3%, and 17% oxygen samples were 1.23eV, 1.97eV, and 1.97eV, respectively. In terms of the allowed direct transition scenario, the Tauc plot is shown in Fig. 2.4 (b). The optical bandgap of the 0%, 3%, and 17% oxygen samples were 2.83eV, 3.55eV, and 3.55eV, respectively.

Taking the 3% oxygen sample as an example, its electronic bandgap would likely fall between the allowed direct and indirect transition scenarios, which is [1.97eV,

3.55eV]. Previous reports suggested that the conventional energy band dispersion model for metal oxides was applicable to the ISO. Thus, allowed direct was assumed to be the transition type of the ISO film in this dissertation. Density functional theory (DFT) simulations will be used to obtain a more accurate band structure in the future.

Fig. 2.4. Tauc plot of the ISO film assuming that the transitions type is: (a) allowed indirect and (b) allowed direct.

#### 2.1.4. Ultraviolet Photoemission Spectroscopy

Ultraviolet photoelectron spectroscopy (UPS) measures the kinetic energy spectra of photoelectrons emitted by molecules that have absorbed ultraviolet photons [83]. It is used to determine the relative position of the ISO's valence band. The equipment used for UPS measurements was an Escalab 250Xi along with the near ambient pressure (NAP) X-ray photoemission spectroscopy (XPS) system. The sample prepared for the UPS measurement was a 3% oxygen ISO film deposited on a silicon substrate. The sample was annealed at 150°C for one hour. A thin layer of Ag was sputtered on the sample as the reference electrode.

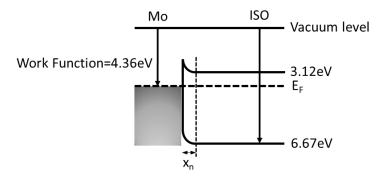

Fig. 2.5 shows the UPS measurement results. The ionization potential (IP) of the ISO film is the energy separation between the vacuum level and the valence band's maximum. The IP value can be extracted from the intercept between the x-axis and the red fitting line of the first peak, which was 6.67 eV. From the previous section, the bandgap for allowed direct transition was 3.55 eV. Adding this value to the valence band minimum obtained the conduction minimum, which was 3.12 eV. The schematic band diagram of the ISO film is shown in the inset figure below.

Fig. 2.5. UPS low binding energy edge of the ISO thin film on a silicon substrate, inset figure is the schematic band diagram for the ISO/Ag

#### 2.1.5. Energy-dispersive X-ray spectroscopy

Energy-dispersive X-ray spectroscopy (EDX) provides elemental analysis and chemical characterisation of the ISO sample [84]. The measurement equipment was an INCA EDX, and the sample was a 3% oxygen ISO film deposited on a silicon substrate that had been annealed for one hour. Fig. 2.6 shows the EDS elemental mapping, where oxygen, indium, and silicon were uniformly distributed throughout the material.

Fig. 2.6. EDS elemental mapping: (a) selected area on the sample, (b) O mapping, (c) In mapping, and (d) Si mapping. *Gamma adjusted for better image quality*

EDX spectra of the ISO film is shown in Fig. 2.7. Since no other elements were found, the sample was not contaminated during the fabrication process. Removing the background interference, the stoichiometric expression of the material was In<sub>9</sub>SiO<sub>14.02</sub>.

Fig. 2.7. Energy dispersed electron spectra of the ISO film.

#### **2.1.6.** Hall Effect Measurements

The electrical properties of the ISO film were investigated by Hall effect measurements. The equipment used was an MMR Hall and Van der Pauw Measurement System. The measurement temperature was 26°C. All films exhibited n-type conduction. The as-deposited 3% film possessed a carrier concentration of  $2.80 \times 10^{19}$  cm<sup>-3</sup>, a Hall mobility of 2.16 cm<sup>2</sup>/(V·s), a resistivity of 0.1031  $\Omega$ ·cm, and a Hall coefficient of 0.22 cm<sup>3</sup>/Coul. The measurement error, or the observation error of the machine, was 20%. The other recipes used in the previous sections with different annealing conditions were also tested, but the variations were in the range of the observation error. Thus, the effect of different recipes and annealing conditions on Hall Effect measurements will not be discussed, since the variation was too small.

Generally speaking, carrier density was very sensitive to defect structure. If the films remained amorphous after annealing, increasing the annealing temperature and time could possibly reduce defects, thus increasing the carrier density. For amorphous metal oxide semiconductors, the Hall mobility, carrier concentration, and resistivity of the IGZO thin films are believed to be dependent on deposition power. The lower the deposition power, the better the film quality (less defects).

### 2.2. Fabrication Process

The ISO TFTs used in this work were developed at The Centre for Advanced Photonics and Electronics (CAPE) and The Nanoscience Centre. In this section, the limitations of the equipment are discussed, along with the design and development of the TFT process.

#### 2.2.1. Selective Etching

Most of the equipment used in this work was designed for research or prototype verification, and had very little control of uniformity. It was essential to determine the limits of the machines and to design suitable processes to improve robustness. First, the uniformity of the deposited films was tested. Different films were deposited on single-side polished 4-inch glass/silicon substrates. Nine different positions (a  $3\times3$  array, one in the centre, and the rest at intervals of 2.5 cm) were used to collect thickness data. A Dektak XT Profilometer was used to measure the film thickness.

As shown in Table 2.1, 10 films were measured. Cr and Mo were deposited by a Precision Atomics DC sputter. The other films were deposited by the MVSystems Cluster tools. Compared to the other films, the semiconductor (ISO, ZnON) and the  $AlO_x$  films had much smaller standard deviations. This was because the RF sputter chamber had a rotating stage to ensure the deposited semiconductor film was uniform. In addition, the working mechanism of the ALD ensured that the  $AlO_x$  thickness across the substrate was controlled precisely by varying the number of cycles.

| Deposited films                                                               | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   | 9   | Mean | SD    |

|-------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|-------|

| Cr (DC Sputter)                                                               | 212 | 215 | 245 | 230 | 221 | 238 | 239 | 231 | 244 | 231  | 12.22 |

| Mo (DC Sputter)                                                               | 318 | 344 | 350 | 364 | 363 | 331 | 337 | 319 | 374 | 344  | 20.04 |

| SiN <sub>x</sub> (SiH <sub>4</sub> :H <sub>2</sub> :NH <sub>3</sub> =1:40:10) | 245 | 249 | 271 | 254 | 281 | 258 | 235 | 259 | 253 | 256  | 13.63 |

| SiN <sub>x</sub> (SiH <sub>4</sub> :H <sub>2</sub> :NH <sub>3</sub> =1:40:20) | 285 | 315 | 309 | 309 | 335 | 319 | 287 | 313 | 317 | 310  | 15.59 |

| SiO <sub>x</sub> (SiH <sub>4</sub> : N <sub>2</sub> O=1:5, 20W)               | 271 | 289 | 287 | 266 | 321 | 282 | 250 | 299 | 287 | 284  | 20.27 |

| SiO <sub>x</sub> (SiH <sub>4</sub> : N <sub>2</sub> O=1:5, 15W)               | 295 | 334 | 332 | 309 | 352 | 320 | 292 | 327 | 337 | 322  | 19.99 |

| ISO                                                                           | 296 | 317 | 302 | 307 | 321 | 301 | 304 | 321 | 316 | 309  | 9.42  |

| ZnON                                                                          | 318 | 329 | 333 | 321 | 339 | 322 | 344 | 328 | 337 | 330  | 8.87  |

| $AlO_x$ (150°C, 1.0s purge)                                                   | 271 | 278 | 289 | 276 | 282 | 286 | 282 | 282 | 280 | 281  | 5.32  |

| AlO <sub>x</sub> (150°C, 1.2s purge)                                          | 286 | 287 | 298 | 310 | 295 | 294 | 298 | 291 | 307 | 296  | 8.18  |

Table 2.1. Thickness (nm) of the deposited films on 4-inch substrates

Among all the layers of TFT, the semiconductor and insulator are the most important. Variations in thickness can have direct impact on device performance. Fortunately, the semiconductor layer and the dielectric layer (AlO<sub>x</sub>) had already been verified as uniform across the 4-inch substrate. Other films had slightly larger standard deviations.  $SiN_x$  and  $SiO_x$  were used as passivation layers in this work, which were much less sensitive to uniformity. As long as the metals were still conducting and the work function remained unchanged, the change in thickness at the source/drain did not have any physical impact on the performance of the TFTs.

Secondly, the etching techniques were characterised. Table 2.2 shows the details of the wet/dry etching used in this work. Etch rates were calculated using the average thickness divided by the time it took to completely remove the film from the substrate. Large variations were observed among the different films using the same etching technique. For example, the ISO and  $AlO_x$  could not easily be dry etched, but the  $SiO_x$  and  $SiN_x$  were easily removed using the same technique.

| Method  | Material                                                         | Chemicals/Process conditions               | Etch rate<br>(nm/s) |

|---------|------------------------------------------------------------------|--------------------------------------------|---------------------|

|         | AlO <sub>x</sub>                                                 | Buffered oxide etchant (HF)                | 0.17                |

|         | SiO <sub>x</sub>                                                 | <b>Buffered oxide etchant (HF)</b>         | 0.63                |

|         | SiN <sub>x</sub>                                                 | <b>Buffered oxide etchant (HF)</b>         | 1.67                |

|         | Mo/Cr                                                            | Buffered oxide etchant (HF)                | 0.00                |

| Wet     | ISO                                                              | Buffered oxide etchant (HF)                | 99.99               |

| etching | ISO                                                              | HCl (1.2%)                                 | 0.17                |

| ••••    | AlO <sub>x</sub> / SiO <sub>x</sub> /<br>SiN <sub>x</sub> /Cr/Mo | HCl (1.2%)                                 | 0.00                |

|         | Cr                                                               | Cr etchant (Sigma-Aldrich)                 | 0.11                |

|         | ISO                                                              | Cr etchant (Sigma-Aldrich)                 | 99.99               |

|         | SiN <sub>x</sub> /SiO <sub>x</sub> /AlO <sub>x</sub>             | Cr etchant (Sigma-Aldrich)                 | 0.00                |

|         | Мо                                                               | CF4:50 sccm; 150 mTorr; 100 W              | 0.06                |

|         | Cr                                                               | CF <sub>4</sub> :50 sccm; 150 mTorr; 100 W | 0.00                |

| Dry     | ISO/ZnON                                                         | CF <sub>4</sub> :50 sccm; 150 mTorr; 100 W | 0.00                |

| etching | AlO <sub>x</sub>                                                 | CF <sub>4</sub> :50 sccm; 150 mTorr; 100 W | 0.00                |

|         | SiO <sub>x</sub>                                                 | CF4:40 sccm O2:10 sccm; 150 mTorr; 100 W   | 0.83                |

|         | SiN <sub>x</sub>                                                 | CF4:45 sccm O2:5 sccm; 150 mTorr; 100 W    | 1.00                |

Table 2.2. Etching techniques details.

It should be noted that the semiconductor films used in this work were very sensitive to acid. The semiconductor films were etched off as soon as the substrate was soaked into the acid. In most cases, if the acid was strong (e.g. undiluted), the semiconductor dissolved into the acid even if it was covered by a photoresist. Wet

etching became a lift-off process in such circumstances. The residual photoresist did not dissolve in the acid, and the remaining photoresist after wet etching caused great difficulty in the following steps. Through multiple experiments, it was found that 1.2% HCl was the most suitable wet etching solution (i.e. no lift-off observed, acceptable etch rate) for the ISO film.

The selectivity of etching provided an opportunity to compensate for the nonuniformity originating from the equipment. If properly used, selectivity could not only keep the previous layers undamaged, but could also increase the tolerance for mistakes in fabrication. The combination of two layers using selective etching to pattern the top layer is given in Table 2.3. The chemicals/process conditions in the table ensured that the bottom layer was not damaged during the etching. These combinations were heavily relied upon to improve the robustness and yield of the TFT process.

| Materials                          |                                    | Etching    |                                                                                                    |  |  |  |

|------------------------------------|------------------------------------|------------|----------------------------------------------------------------------------------------------------|--|--|--|

| Top (The layer to be patterned)    | Bottom                             | techniques | Chemicals/Process conditions                                                                       |  |  |  |

| Cr                                 | Glass substrate                    | Wet        | Cr etchant (Sigma-Aldrich)                                                                         |  |  |  |

| Мо                                 | Glass substrate                    | Dry        | CF <sub>4</sub> :50 sccm 150 mTorr 100 W                                                           |  |  |  |

| AlO <sub>x</sub>                   | Mo/Cr                              | Wet        | Buffered oxide etchant (HF)                                                                        |  |  |  |

| SiO <sub>x</sub> /SiN <sub>x</sub> | Mo                                 | Wet        | Buffered oxide etchant (HF)                                                                        |  |  |  |

| SiO <sub>x</sub> /SiN <sub>x</sub> | Cr                                 | Dry/Wet    | CF <sub>4</sub> :40 sccm O <sub>2</sub> :10 sccm; 150 mTorr<br>100 W / Buffered oxide etchant (HF) |  |  |  |

| ISO                                | AlO <sub>x</sub>                   | Wet        | HCl (1.2%)                                                                                         |  |  |  |

| ISO                                | SiO <sub>x</sub> /SiN <sub>x</sub> | Wet        | HCl (1.2%)                                                                                         |  |  |  |

| ISO                                | Mo/Cr                              | Wet        | HCl (1.2%)                                                                                         |  |  |  |

| Cr                                 | ISO                                | -          | -                                                                                                  |  |  |  |

| Мо                                 | ISO                                | Dry        | CF <sub>4</sub> :50 sccm; 150 mTorr; 100 W                                                         |  |  |  |

Table 2.3. Selective etching that protects the bottom layer.

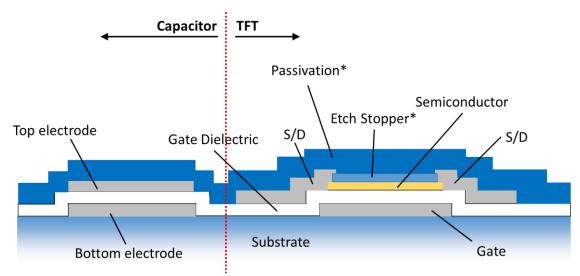

#### 2.2.2. TFT Structure and Fabrication Process

The TFT structure has large impact on its electrical performance. A well-designed structure can increase the efficiency of both TFT fabrication and device development [85]. There are two major considerations for device structure: the impact on device performance (performance optimisation) and the simplicity of the manufacturing process. For field effect transistors, there are four types of device structures: top-gate bottom-contact (staggered), bottom-gate top-contact (inverted staggered), top-gate top-contact (coplanar), and bottom-gate top-contact (inverted coplanar). Compared with other structures, the bottom-gate top-contact structure deposits the gate dielectric and semiconductor without breaking the vacuum between the two processes. A clean

interface, which determines the subthreshold swing, can be easily obtained using this method. Based on prior TFT development experience, the subthreshold swing was the most difficult specification to improve. Therefore, bottom-gate top-contact was selected as the structure used to develop the ISO TFT.

As shown in Fig. 2.8, a four-mask/six-mask process was used for bottom-gate topcontact TFT fabrication. First, a 100 nm Cr film was deposited by DC sputtering, which was defined by photolithography with chromium etchant as gate electrodes. A 120 nm AlO<sub>x</sub> layer was then deposited by ALD at 150°C. Without breaking the vacuum, a 10 nm In-Si-O layer was deposited by RF-sputtering at room temperature. The sample was patterned with buffered hydrogen fluoride and hydrogen chloride to form via holes and semiconductor regions, respectively. Finally, a 100 nm Mo layer was deposited and defined by reactive-ion etching (RIE) for source and drain electrodes. The region without semiconductor and etch stopper layers was used as a capacitor in the TFT circuit.

Fig. 2.8. Fabrication process for the In-Si-O TFT (\* marks the optional layers in the sixmask process).

The etch stopper and passivation layers (marked with \*) were also available in the six-mask process. Theoretically, fabrication with the etch stopper could have better process control at the sacrifice of throughput. The etch stopper could also protect the back interface of the channel from plasma damage, thus reducing the trap density. The optimised active layer thickness could be different for the devices with and without etch stopper layers.

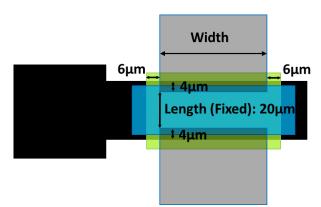

A set of rules (mainly the safe margins) were defined that summarised empirical experience with the TFT fabrication process, providing guidance on layout and circuit design. Based on these rules, high yield of TFT circuits/arrays over a 3-inch glass substrate was guaranteed. This set of design rules was initially generated for simultaneous fabrication of a series of TFT circuits. In general, it is much more conservative than the most advanced process. Fig. 2.9 shows the design rules in the fifth mask. The critical dimensions shown in the graph were generated after obtaining experience with TFT fabrication and the limitations of the photolithography machine (MJB4 Suss Microtec). To summarize, the channel length was fixed to 20  $\mu$ m for all TFTs, the minimum overlap among layers (alignment safe margin) was 2  $\mu$ m, and the minimum distance between track centres was 50  $\mu$ m.

Fig. 2.9. An example of the design rules (the fifth mask).

#### 2.2.3. TFT on Plastic

The demand for flexible electronics has driven the development of TFT on flexible substrates. The proposed TFT process features low fabrication temperature, which is ideal for a flexible substrate. The possibility of applying the full-photolithography TFT process to plastic substrates was explored. The substrate used was the DuPont<sup>TM</sup> Kapton HN thermal insulating film, which can withstand temperatures up to 400°C (much higher than the proposed process temperature). For a low-temperature process, fabricating a single TFT device on plastic is not challenging as long as the process temperature is controlled below the melting point of the substrate. The photolithography alignment and the yield of TFTs become obstacles, due to the shrinkage of the plastic, especially for a large plastic sheet.

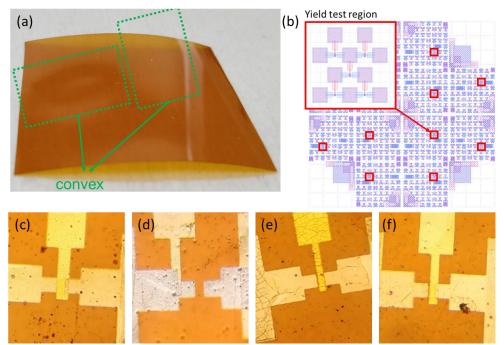

The pressure built up inside the plastic during fabrication was released when it was heated [86]. According to the DuPont<sup>TM</sup> Kapton HN general specifications, the

shrinkage along the machine direction and transverse direction was less than 0.35% when the film was conditioned by freely suspending it for two hours in an oven controlled to 200°C. Repeating the same experiments, the Kapton HN sheet was annealed as shown in Fig. 2.10 (a). The shrinkage was not uniform, but randomly distributed on the surface of the plastic sheet.

First, alignment marks were added to the plastic sheet, but the misalignments were too small to be observed. To further investigate the shrinkage, the standard four-mask process was used to fabricate a TFT array on the Kapton HN sheet. As shown in Fig. 2.10 (b), 12 yield test regions were used to evaluate the impact of the shrinkage. Large variations in the alignment were found. Pictures of four typical scenarios were taken: Fig. 2.10 (c), (e), and (f) had relatively small misalignments, while the gate and source/drain were completely misaligned in 2.10 (d). Misalignment data (the distance between centres of the TFT on two masks) are summarized in Table 2.4.

Fig. 2.10. (a) The Kapton HN sheet was heated for two hours at 200°C. (b) The yield test regions on the 3-inch TFT array masks. (c), (d), (e), and (f) are photos of the selected transistors in the yield test regions.

| Position     | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   | 9   | 10   | 11   | 12   |

|--------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|

| Misalignment | 7.3 | 2.6 | 2.2 | 3.6 | 2.6 | 0.8 | 1.3 | 1.4 | 8.9 | 18.9 | 45.1 | 20.7 |

| (µm)         |     |     |     |     |     |     |     |     |     |      |      |      |

Table 2.4. Misalignment in the yield test regions on the sample.

The large variations in misalignment proved that the shrinkage problem could not be solved by using a set of scaled-down masks. Possible solutions were most likely in the process before fabrication. If the shrinkage from fabrication could be decreased to that seen before alignment (photolithography), the misalignment would be greatly reduced.

The most fitting solution started by annealing the Kapton film for two hours at 200°C to release the built-in pressure. A rigid substrate, usually a silicon wafer, was used as the backplane to keep the film from deforming. Finally, wafer dicing tapes were used to keep the rigid substrate firmly attached to the Kapton film. The top-view and cross-sectional view of this method are shown in Fig. 2.11 (a) and (b). Wafer dicing tapes have weak adhesion, which will not alter the pressure along the Kapton film when the temperature changes, such that it can be easily peeled off after fabrication. With this method, the masks were aligned. Fig. 2.11 (c), (d), (e), and (f) show four selected TFTs in the yield test region. The misalignment for all TFTs on the substrate was within 4  $\mu$ m, which is comparable with the process on glass.

Fig. 2.11. (a) Top-view and (b) cross-sectional view of the proposed solution to plastic shrinkage. (c), (d), (e), and (f) are photos of the selected transistors in the yield test regions on the substrate (improved method).

Fig. 2.12 (a) shows the TFT array that was fabricated on plastic at CAPE. The TFTs on the sample were still functional after bending 100 times to a 1 cm bending radius. The typical performance of TFT on plastic is shown in Fig. 2.10 (b). Hysteresis (<0.5V) was observed in the transfer characteristics. The potential causes of the

hysteresis include annealing temperature too low to remove the defects and the large surface roughness of the plastic increasing traps at interfaces. The potential causes of hysteresis will be analysed and discussed in the third chapter.

Fig. 2.12. (a) The ISO TFT array on a Kapton HN sheet. (b) Typical performance of the TFT on plastic.

Although the TFT array was successfully fabricated on plastic, it should be noted that circuits cannot be fabricated on plastic, due to the lack of technique to pattern via holes. Wet etching with Hydrofluoric (HF) was used to pattern the  $AlO_x$  in the standard process on glass. Unfortunately, this method did not work on plastic. When the plastic was soaked in HF, the entire layer of  $AlO_x$  dissolved into the solution. Residual HF on the plastic also made this process too dangerous to be used. New etching methods and materials will continue to be sought for the TFT process on plastic.

### 2.3. TFT Characterisation

This section discusses the results of a group of experiments used to characterise the TFT. Trial and error experiments are not presented, and repeated measurements have also been removed. Thus, this section presents a simplified device development process.

### 2.3.1. Dielectric Layer

TFT performance is mainly governed by speed and power. Speed depends upon the drive current or the drain current. Ideally, it should be increased, while decreasing the transistor's static power consumption. The total TFT leakage, of which the gate leakage is a major component, dictates the static power consumption. The level-1 model, or the quadratic model, reveals that the drain current of the field-effect transistor is proportional to  $\frac{\varepsilon_r}{t_{ox}}$ , where  $\varepsilon_r$  is the relative permittivity and  $t_{ox}$  is the dielectric thickness. Theoretically, thin dielectric layers with high relative permittivity can boost the drain current. This is equivalent to an increase in the field-effect mobility. A thinner dielectric layer has a less effective potential barrier to the exchange of charge carriers between the TFT channel and the gate electrode. This results in a higher gate leakage current, because of the direct tunnelling mechanism. The dielectric strength that determines the breakdown voltage is also essential to determining the maximum operating voltage of the TFT.

Fig. 2.13 (a) and (b) show the capacitor array that was fabricated for the dielectric layer testbench. ITO-coated glasses were used as the substrates. First, the edges of the substrates were covered with shadow mask so that the bottom electrode could be easily accessed. The dielectric layer was then deposited. The top electrodes were Mo or Cr, which were patterned during sputtering with a shadow mask. Experiments showed that the thickness of the dielectric layers had to be greater than 50 nm, otherwise the majority of the capacitors were short-circuited, likely caused by dust on the sample or defects in the deposited dielectric layers.

C-V measurements determined the capacitance of the samples that functioned properly. Multiple frequencies were used so that frequency-related characteristics were obtained. Fig. 2.13 (c) shows a typical C-V measurement result in the array. The low-frequency C-V curve had greater noise and slightly higher capacitance. The average capacitance at different frequencies was used to analyse the dielectric layer.

Fig. 2.13. (a) Picture and (b) cross-sectional view of the capacitor array. (c) C-V measurement of a capacitor in the array at different frequencies.

Dielectric strength and leakage current density were measured with the breakdown testbench. Two terminals of the capacitor were connected to a Keithley 4200s SMU. The voltage applied to the capacitor was increased until a large leakage current was observed (breakdown of the dielectric layer). The leakage current density was calculated by dividing the leakage current before breakdown by the total area of the capacitor. Fig. 2.14 shows the measurement results for several frequencies using the following recipes for TFT fabrication: 100nm AlO<sub>x</sub>, 310nm SiN<sub>x</sub> and 500nm SiO<sub>x</sub>. Measurement results on the dielectric layers are summarized in the Table 2.5.

Fig. 2.14. Results from dielectric breakdown testbench for (a) 100nm AlO<sub>x</sub>, (b) 310nm  $SiN_x$ , and (c) 500nm SiO<sub>x</sub>.

The data in Table 2.5 are from the selected films with the highest quality; however, the calculated dielectric constants of the deposited films were smaller than the theoretical values. This could be due to measurement errors in the film thickness, or further improvements to the deposition machine may be needed, which was not realistic for the cluster tools used. In this work, other methods to improve device performance are investigated.

| Dielectric              | Cap (pF) | Relative<br>Error (%) | Thickness<br>(nm) | Area<br>(μm²) | Dielectric<br>Constant | Breakdo<br>wn<br>Voltage<br>(V) | Dielectric<br>strength<br>(V/m) | Leakage<br>current<br>density<br>(A/ µm <sup>2</sup> ) |

|-------------------------|----------|-----------------------|-------------------|---------------|------------------------|---------------------------------|---------------------------------|--------------------------------------------------------|

| SiNx SiH <sub>4</sub> : | 104      | 1.15                  | 256               | 880,838       | 3.42                   | 155                             | 6.04E5                          | 1.56E-16                                               |

| NH <sub>3</sub> =1:10   | 101      | 1110                  | 200               |               |                        | 100                             | 010120                          |                                                        |

| SiNx SiH <sub>4</sub> : | 114      | 1.75                  | 310               | 880,838       | 4.53                   | 127                             | 4.09E5                          | 1.84E-16                                               |

| NH <sub>3</sub> =1:20   |          | 1.75                  | 510               | 000,000       | ч.55                   | 127                             | 4.0725                          | 1.0+L-10                                               |

| AlO <sub>x</sub> @      | 418      | 1.43                  | 120               | 880,838       | 6.43                   | 23                              | 2.3E5                           | 6.53E-17                                               |

| 150°C                   |          | 1.43                  | 120               | 000,000       | 0.45                   | 25                              | 2.565                           | 0.551-17                                               |

| SiO <sub>2</sub>        | 66       | 3.03                  | 500               | 880,838       | 4.23                   | 53.5                            | 1.7E5                           | 1.44E-17                                               |

Table 2.5. Measurement results of the deposited dielectric layers.

### 2.3.2. Metal-Semiconductor Contact

Interface properties of the metal-semiconductor have a strong influence on TFT performance. Contact resistance at the interface between the source/drain electrode and the semiconductor can affect carrier movement [87]. Assuming other conditions are the same, the transistor with Schottky contacts required more source-drain voltage to attain the same current level as the transistor with ohmic contacts [88], [89]. Previous reports showed that a Schottky-contact transistor had a bend at the beginning of its output characteristics [90], which was caused by the diode behaviour of the two barriers at the metal-semiconductor interfaces. From the perspective of a circuit designer, this bend reduces the linearity of conventional analogue circuits and increases power consumption of conventional digital circuits. Hence, the barrier height and the width between the source/drain electrode and the semiconductor should be minimised.

Fig. 2.15. Conduction mechanism for the Mo/ISO contacts.

Based on the characterisation results of the ISO film in section 2.1.4, the conduction mechanism for the Mo/ISO contact is shown in Fig. 2.15. Generally speaking, there are two types of conduction mechanisms for metal/semiconductor

contact: thermionic emission and field emission. Thermionic emission occurs in a wide space charge region, where electrons must jump the potential barrier by emission over the maximum. Conversely, electrons can tunnel through the thin potential barrier in field emission. The equation for the width of the space charge region follows equation 2.1:

$$X_n = \sqrt{\frac{2\varepsilon_s \varepsilon_0 \Phi_i}{qN}} \tag{2.1}$$

where  $\varepsilon_s$  is the relative permittivity of the ISO,  $\Phi_i$  is the built-in voltage, and N is the carrier concentration. When the space charge region,  $x_n$ , is smaller than 2.5 nm, electrons can tunnel through the barrier. Using the data obtained from the Hall effect measurement, the relative permittivity of ISO is given by:

$$\varepsilon_s \le \frac{X_n^2 qN}{2\Phi_i} = 24.91 \tag{2.2}$$

The permittivity of alloy materials  $A_{1-x}B_x$  were interpolated from the values of the basic materials as a quadratic function of x:

$$\varepsilon_s{}^{AB} = (1-x)\varepsilon_s{}^A + x\varepsilon_s{}^B + (1-x)xC_\sigma \tag{2.3}$$

where  $C_{\sigma}$  is referred to as a nonlinear or bowing parameter. It is very unlikely that the relative permittivity of ISO would exceed 24.91, since the relative permittivity of SiO<sub>2</sub> and In<sub>2</sub>O<sub>3</sub> are 3.9 and 9.0, respectively.

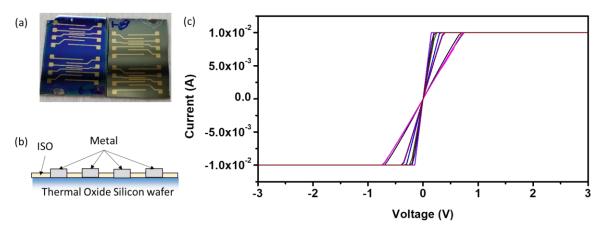

Fig. 2.16. (a) Two samples for the contact resistance measurement. (b) Cross-sectional view of the samples. (c) I-V characteristics of the Mo/ISO contacts with various semiconductor deposition recipes.

To verify this hypothesis, metal-semiconductor-metal devices were built on thermal oxide silicon wafers. First, a thick layer of metal, usually more than 300 nm, was deposited and patterned by a shadow mask. A thinner layer of ISO (50 nm) then followed. The picture and cross-sectional view of the sample are shown in Fig. 2.16 (a)

and (b), respectively. Fig. 2.16 (c) shows the I-V characteristics of the Mo/ISO contacts, where no diode behaviour was found. A wide range of ISO recipes were tested, all of which showed ohmic-contact behaviour.

Apart from the Mo/ISO contact, other available metals were tested at CAPE. All were ohmic-contact. The information is summarised in Table 2.6.

| Metal | Work                  | ISC      | Americaling        |                     |                                             |

|-------|-----------------------|----------|--------------------|---------------------|---------------------------------------------|

|       | function of the metal | RF power | O2:Ar flow<br>rate | Chamber<br>pressure | <ul> <li>Annealing<br/>condition</li> </ul> |

| Мо    | -<br>4.36 -<br>-      | 150      | 50:3               | 4 mTorr             | -                                           |

|       |                       | 150      | 50:3               | 4 mTorr             | 2 Hr, 150°C                                 |

|       |                       | 150      | 50:3               | 4 mTorr             | 2 Hr, 200°C                                 |

|       |                       | 150      | 50:10              | 4 mTorr             | 2 Hr, 200°C                                 |