## Performance Driven Global Routing Through Gradual Refinement

JIANG HU<sup>a,\*</sup> and SACHIN S. SAPATNEKAR<sup>b,†</sup>

<sup>a</sup>Department of EE, Texas A&M University, College Station, TX 77843-3128, USA; <sup>b</sup>Department of ECE, University of Minnesota, Minneapolis, MN 55455, USA

(Received 15 March 2001; Revised 30 January 2002)

We propose a heuristic for VLSI interconnect global routing that can optimize routing congestion, delay and number of bends, which are often competing objectives. Routing flexibilities under timing constraints are obtained and exploited to reduce congestion subject to timing constraints. The wire routes are determined through gradual refinement according to probabilistic estimation on congestions so that the congestion is minimized while the number of bends on wires is limited. The experiments on both random generated circuits and benchmark circuits confirm the effectiveness of this method.

Keywords: VLSI; Deep-submicron; Interconnect; Timing-optimization; Physical-design; Global routing

## INTRODUCTION

Global routing is an important stage in VLSI physical design, in which a given set of global nets is routed coarsely, in an area that is conceptually divided into small regions called routing cells. For each net, a routing tree is specified only in terms of the cells through which it passes. With interconnects playing an increasingly dominant role in determining circuit performance, it is becoming even more important than ever to perform the global routing task in a methodical, efficient and optimal manner, so that performance-critical nets and long-distance nets can be routed in such a way that constraints on timing, congestion and reliability are met. In this paper, we will propose a new approach to enhance the quality of global routing.

For a boundary between two neighboring cells, the number of available routing tracks across it, called its supply, is limited. One fundamental goal of global routing is to minimize the congestion so that the number of nets across each boundary does not exceed its supply, i.e. no overflow occurs. Since minimizing congestion is very hard to achieve and is essential for global routing, it has long been a focus of research in global routing [1-11]. In the sequential approach, the nets are routed one after another.

In Ref. [1], for each net, a minimum weighted Steiner tree spanning the grid graph is sought to minimize the congestion, with the weights being proportional to the density of wires in each routing cell. The sequential approach requires the nets to be routed in some order, on which the quality of the solution depends. As a solution to avoid this ordering problem, the hierarchical method [2-4] recursively splits the routing region into successively smaller parts. At each hierarchical level, all of the nets are routed simultaneously and refined in the next hierarchical level until the lowest level of the hierarchy is reached. Sometimes the entire global routing problem is formulated and solved through linear programming followed by a randomized rounding [5]. Another method is the application of multicommodity flow model [6,7], in which the fractional solutions are rounded to obtain the routing solutions. For global routing on standard cell designs, the work in Ref. [8] proposed an iterative deletion technique to avoid the net ordering problem. The works of Refs. [9-11] first route each net independently, then rip up the wires in congested areas and reroute them to spread out the routing density. The rip-up-and-reroute (RR) technique is very practical and popular in industrial applications.

<sup>\*</sup>Corresponding author. Tel: +1-979-847-8768. E-mail: jianghu@ee.tamu.edu

<sup>&</sup>lt;sup>†</sup>Tel.: +1-612-625-0025. Fax: +1-612-625-4583. E-mail: sachin@mail.ece.umn.edu

When interconnect becomes a performance bottleneck in deep submicron technology, merely minimizing congestion is not enough. In the later works of Refs. [12-14], interconnect delays are explicitly considered during global routing. In Ref. [12], each net is initially routed in SERT-C [15], after which the congested area is ripped up and rerouted by applying a multicommodity flow algorithm locally. In Ref. [13], the delay issues are considered more strictly. Beginning with a set of routing trees satisfying timing constraints for each net, a multicommodity flow method is applied to choose a single routing tree for each net, such that the congestion is minimized. At places where overflow occurs, the wires are ripped up and rerouted through a maze routing procedure in which the timing objective is combined with wirelength and congestion. Recently, a timing-constrained global routing scheme is proposed in Ref. [14]. This method obtains routing flexibilities under timing constraints and exploits them through a combination of hierarchical bisection and network flow algorithm.

Besides congestion and timing, the number of bends for each wire needs to be limited. A wire bend usually implies a switching of layers, which involves via resistance that adds to the delay and reduce reliability. In addition, vias will consume more wiring space because of their larger pitch requirement. In Ref. [4], a hierarchical global routing algorithm is proposed to control to number of vias for each wire. There are many other works in routing to minimize the number of vias, especially for MCM and PCB design, such as V4R [16].

In global routing, congestion, delay constraints and control of the number of vias are often competing objectives. In order to avoid congestion, some wires must make detours and the signal delay will consequently suffer. Controlling the number of vias will reduce the capability of a wire to avoid congestion and a large number of vias will also affect the delay performance. Our work is an effort to minimize the congestion while satisfying timing constraints and limiting the number of vias for each wire in global routing. To the best of our knowledge, this is the first work to optimize all these three objectives simultaneously in global routing.

Similar to the work of Ref. [14], we obtain routing topology flexibilities under bounded delays through deferred decision making and trade them into congestion reduction under timing constraints. However, our tradeoff method is a probability-based gradual refinement which is different from that of Ref. [14]. Moreover, we integrate restrictions on wire routes with the refinement so that the number of bends on wires can be bounded. The work of Ref. [14] has only limited control over this and there is no obvious extension of the work to bound the number of bends on wires. Imposing the restriction on number of bends naively on the algorithm of Ref. [14] would make the bend resource allocation biased to the decisions in higher hierarchical levels and the routings in lower hierarchical levels may become unnecessarily unachievable. Although our objective is complex, our method is simple and the experimental results on both random and benchmark circuits confirm that it is effective in achieving all three objectives simultaneously. A preliminary version of this work was published in Ref. [17].

## **DEFINITIONS AND PROBLEM FORMULATION**

We are given a set of nets  $\mathcal{N} = \{N^1, N^2, \ldots\}$ , with each net  $N^i$  being defined by a source node  $v_0^i$  and a set of sink nodes  $V_{\text{sink}}^i = \{v_1^i, v_2^i, \dots, v_p^i\}$ . A routing problem for a net N (we omit the net index for simplification without loss of generality) is to find a set of Steiner nodes  $V_{\text{Steiner}} = \{v_{p+1}, v_{p+2}, \dots, v_{p+q}\}$  and a set of edges  $E = \{e_1, e_2, \dots, e_{p+q}\}$  to construct a tree T(V, E), where  $V = v_0 \cup V_{\text{sink}} \cup V_{\text{Steiner}}$ , such that E spans all of the nodes in V. The location for a node  $v_i$  is specified by its coordinates  $x_i$  and  $y_i$ , and an edge in E is uniquely identified by the node pair  $(v_i, v_k)$ , the notation  $e_{ik}$  or  $e_k$ interchangeably. We assume  $v_i$  is the upstream end of this edge. The edge length  $l_{ik}$  is given by the Manhattan distance between the two nodes, which is  $|x_i - x_k| +$  $|y_i - y_k|$ . In order to make our presentation clearer, we define the following terms:

DEFINITION 1 In a routing tree, a *backbone node* is the source node, or a sink node, or a Steiner node with degree greater than 2 (we treat a bend node as a Steiner node with degree two).

DEFINITION 2 In a routing tree T(V, E), a backbone wire is a set of consecutively adjoined edges  $\{(v, u_1), (u_1, u_2), (u_2, u_3), \dots, (u_m, w)\}$ , where  $v, w \in V$  are backbone nodes and  $\{u_1, u_2, \dots, u_m\} \in V$  are not backbone nodes.

If the delay at an arbitrary sink  $v_a$  is  $t(v_a)$  and its required arrival time (RAT) is RAT $(v_a)$ , then the delay slack  $s(v_a) = \text{RAT}(v_a) - t(v_a)$ . The timing slack  $\mathscr{G}(T^i)$ for a routing tree  $T^i$  on the net  $N^i$  is the minimum delay slack among all the sinks in this net.

As in conventional global routing, we tessellate the entire routing region for  $\mathcal{N}$  into an array of uniform rectangular cells. We represent this tessellation as a graph called the grid graph  $G(V_G, E_G)$ , where  $V_G = \{g_1, g_2, ...\}$  corresponds to the set of grid cells, and a grid edge  $b_{ij} = (g_i, g_j) \in E_G$  corresponds to the boundary between two adjacent grid cells  $g_i, g_j \in V_G$ . There are a limited number of routing tracks across any grid edge, *b*, called the *supply* of the grid edge and expressed as s(b). During the routing, the number of tracks occupied by wires across a grid edge *b* is designated as the *demand*, d(b). The *overflow*  $f_{ov}(b)$  at grid edge *b* is defined by:

$$f_{\rm ov}(b) = \begin{cases} d(b) - s(b), & d(b) > s(b) \\ 0, & \text{otherwise} \end{cases}$$

(1)

The *demand density* for a grid edge b is defined as  $\mathcal{D}(b) = d(b)/s(b)$ . We use the maximum demand

596

density  $\mathscr{D}_{\max} = \max_{b \in E_G} \{\mathscr{D}(b)\}$  and total overflow  $\mathscr{F}_{ov} = \sum_{\forall b \in E_G} f_{ov}(b)$  to evaluate the congestions in the final results.

For a given set of nets  $\mathcal{N}$  and a grid graph G over the area of  $\mathcal{N}$ , our objective is to construct routing trees  $T^i$  for every  $N^i \in \mathcal{N}$ , such that  $\mathcal{S}(T^i) \ge 0$ , number of bends on each backbone wire is no greater than 5 and the congestion is minimized in terms of  $\mathcal{D}_{max}$  and  $\mathcal{F}_{ov}$ .

## DELAY ESTIMATION AND ASSUMPTIONS

In this work, we use the  $\pi$  RC model for wires, RC switch model for drivers and Elmore delay model for delay calculation [18,19], all of which are common approaches in timing driven routing methods. Although occasional large errors limit the accuracy of the Elmore delay for critical nets [20], it has a role in global routing because of its fidelity [15] and simplicity, and is a reasonable model considering that the routing in global stage is rough and the number of nets may be very large. The extra delays from vias are neglected here because of the same reason, and besides, the number of vias is bounded in our method. The driver resistance, wire capacitance, wire resistance, sink load capacitance and RAT for each sink are given input to our algorithm. We consider the two-layer routing situation, where one layer is for horizontal wires and the other is for vertical wires. We assume that the per unit length wire capacitance and wire resistance for two layers are very close.

# ROUTING FLEXIBILITIES UNDER TIMING CONSTRAINTS

In this section, we will explore the routing flexibilities under timing constraints. Usually there are many routing tree topologies that can satisfy the RAT for each sink in a net, if the RAT is in a reasonable range. For example, both PTree [21] and RAT-Tree [22] can generate a set of routing topologies satisfying timing constraints. Such timingconstrained routing flexibilities are exploited in the global routing work in Ref. [13]. In this work, we will use some other types of routing flexibilities including: soft edges, Z-edges, slideable Steiner nodes (SSN) and edge elongation. Most of these are proposed in Refs. [14,20] and will be summarized here for completeness.

## Soft Edges

Since a routing tree will be built in rectilinear space finally, each edge must be either horizontal or vertical. Thus, two nodes  $v_i, v_j \in V$  with their coordinates  $x_i \neq x_j$ and  $y_i \neq y_j$  are usually connected with one horizontal edge and one vertical edge in an L-shape. Between any two such nodes, there are always two L-shaped connections and many other connections with same wirelength if the number of bends is not restricted. They can be regarded to have same delay performance in global routing, since the routes are specified coarsely, especially when the number of bends is limited. This timing-constrained routing flexibility is expressed through the concept of a soft edge defined as follows.

DEFINITION 3 A *soft edge* is an edge connecting two nodes  $v_i, v_i \in V$ , such that:

- 1.  $x_i \neq x_j$  and  $y_i \neq y_j$ ,

- 2. its edge length  $l_{ij} = |x_i x_j| + |y_i y_j|$ ,

- 3. the precise edge route between  $v_i$  and  $v_j$  is not determined.

We will refer to the traditional edges in a rectilinear tree with fixed orientations as *solid edges*. It has been shown in Refs. [14,20] that the concept of a soft edge is useful in both single net performance-driven and multi-net global routing.

## Z-edges

When the number of bends along a route connecting two nodes is restricted to be no greater than two and its path length to be the Manhattan distance between the two nodes, this route can only be straight, L-shaped or Z-shaped. A *Z-edge* is an edge that can take only such a route. Even though the routing flexibility from a *Z*-edge is less than that of a soft edge, this flexibility can preserve timing performance with bounded number of bends.

#### Slideable Steiner Node (SSN)

The work of MVERT [23] shows that using non-Hanan Steiner nodes can help to improve the routing tree performance, if the objective is to minimize total wirelength subject to timing constraints. In Ref. [20], this non-Hanan optimization technique is extended to routing in soft edges.

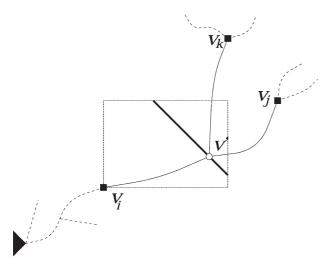

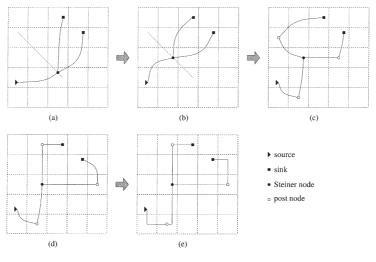

We will use the example in Fig. 1, to describe another timing-constrained routing flexibility. If the optimal Steiner node v' among nodes  $v_i, v_j$  and  $v_k$  is off the Hanan grid as depicted in Fig. 1, the location of v' is specified by the Manhattan distance from the upstream end  $v_i$  to v' in Refs. [20,23]. In fact, there are often many points with the same distance. The set of locations for a distance form a segment of locus as illustrated by the thickened segment in Fig. 1. When we slide the Steiner node v' along this locus, the length of its incident edges are preserved and so does the delay at each sink. Similar to the rationale for soft edges, we only specify this locus instead of a point for this Steiner node and call it as SSN.

#### **Edge Elongation**

Besides soft edge, Z-edges and SSN, we use another simple timing-constrained routing flexibility. After

FIGURE 1 An example of a slideable Steiner node (SSN).

performance-driven routing for a net, it is possible that the timing slack of the routing tree is still positive. This positive slack can be consumed through edge elongation to provide more routing flexibilities under timing constraints.

The maximum allowed elongation  $\Delta l_{ij}$  for routing edge  $e_{ij}$  can be computed under the Elmore delay model. The length of a routing path from source  $v_0$  to a node  $v_i \in V$  is denoted as  $p_i$ , and the shared path length for two nodes  $v_i, v_j \in V$  from the source is expressed as  $p_{ij}$ . For any sink  $v_k \in V$ , we can compute the maximum  $\Delta l_{ij}$  such that the delay slack  $s(v_k)$  is non-negative. If  $v_k \notin T_i$ , i.e.  $v_k$  is not in downstream of  $v_i$ ,

$$\Delta l_{ij} = \frac{s(v_k)}{(R_d + \hat{r}p_{ik})\hat{c}} \tag{2}$$

where  $R_d$  is the driver resistance,  $\hat{r}$  and  $\hat{c}$  are the wire resistance and capacitance per unit length. If  $v_k \in T_i, \Delta l_{ij}$

satisfies the following equation:

$$s(v_k) = f(\Delta l_{ij})$$

$$= (R_d + \hat{r}p_i)\hat{c}(\Delta l_{ij}) + \frac{1}{2}\hat{r}\hat{c}(2l_{ij}(\Delta l_{ij}) + (\Delta l_{ij})^2)$$

$$+ \hat{r}(\Delta l_{ij})C_j, \qquad (3)$$

where  $C_j$  is the total downstream capacitance from  $v_j$ . This equation can be solved to obtain the  $\Delta l_{ij}$ . In the case of double roots for this equation, we choose the one where the slope of function  $f(\Delta l_{ij})$  is positive, since the delay slack should be monotonically increasing with respect to the allowed elongation. We compute  $\Delta l_{ij}$  for all the sinks in the routing tree and choose the minimum value as a safe value. Note that different edge may have different value of maximum allowed elongations.

## APPROXIMATED CONGESTION ESTIMATION

In addition to the traditional congestion metrics, we use a couple of other approximate estimation methods during different phases of global routing, all of which will be introduced in details as follows.

#### **Primitive Demands**

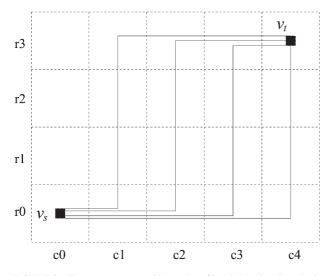

The *demand* defined in "Definitions and problem formulation" section is based on the wire routes in solid edges. However, we arrive at a rough estimation of the congestion from soft edges. We use the concept of *primitive demand* to indicate the possibility of wires crossing a grid edge. This is demonstrated in the example in Fig. 2, in which the dashed segments represent the tessellation by the grid graph, *G*. The bounding box for a soft edge  $e_{ij}$  is obtained as the dotted rectangles and denoted as  $B_{ij}$ . In Fig. 2a, there are three vertical boundary segments at  $x = x_2$  overlapping with  $B_{ij}$  and only one of them is crossed by  $e_{ij}$  in the final route. Therefore, we

FIGURE 2 Examples of primitive demand. (a) Each grid edge corresponds to a horizontal (vertical) thickened boundary segment has primitive demand of 1/4(1/3). (b) Each grid edge corresponds to a thickened boundary segment has primitive demand of 1.

FIGURE 3 Enumerate routes with number of bends less than 3 to obtain probabilistic demand.

define the primitive demand incurred by  $e_{ij}$  over the grid edge corresponding to each of these three boundary segments as 1/3. Similarly, each grid edge for a thickened horizontal (vertical) boundary segment in Fig. 2a has a primitive demand of 1/4(1/3). We refer to the demand, as defined in "Definitions and problem formulation" section, as the *determined demand*, which actually is a special case of the primitive demand. A primitive demand for a soft edge is equivalent to its determined demand when its value aggregates to 1, as in Fig. 2b. If we denote the primitive demand incurred by routing edge  $e_{ij}$  over grid edge *b* as  $d_{prim}(b, e_{ij})$ , then:

$$d_{\text{prim}}(b) = \sum_{\forall B_{ij} \text{ intersecting } b} d_{\text{prim}}(b, e_{ij}) \qquad (4)$$

DEFINITION 4 If the bounding box  $B_{ij}$  of an edge  $e_{ij}$  passes through *m* rows and *n* columns in the grid graph *G*, the *primitive demand*  $d_{\text{prim}}(b, e_{ij})$  from  $e_{ij}$  on each grid edge *b* corresponding to a vertical(horizontal) boundary overlap with  $B_{ij}$  is 1/m(1/n).

#### **Probabilistic Demands**

The possible routes of a Z-edge are easier to enumerate and a congestion estimation better than the *primitive demand* can be obtained accordingly. In this scenario, we adopt a probabilistic estimation which is similar to Refs. [24,25] and will be illustrated in the example in Fig. 3. Without loss of generality, we can arbitrarily specify one end of the soft edge as source node  $v_s$  and the other end as target node  $v_t$ , and denote the grid cell in which they are located as  $(r_s, c_s)$  and  $(r_t, c_t)$ , respectively. We use r and c to represent row and column indices. Through simple enumeration, we can conclude that: LEMMA 1 There are  $Z = |r_t - r_s| + |c_t - c_s|$  monotone routes with number of bends no greater than 2 between two grid cell  $(r_s, c_s)$  and  $(r_t, c_t)$  in a grid graph.

For example, there are seven possible route for the Z-edge in Fig. 3. In our congestion estimation, we assume a uniform probability distribution for these routes, i.e. every route has the same chance to be chosen in later stages. Then, we can obtain the probability that a grid edge is crossed by the soft edge, again through simple enumeration. To simplify the description, we initially consider only those routes that leave source node  $v_s$ horizontally toward the target node. Obviously, there are  $|c_t - c_s|$  such routes which are depicted in Fig. 3. For each horizontal grid edge above the grid cells  $\{(r_i, c_i) | r_s \leq$  $r_i < r_t, c_s < c_i \le c_t$ }, there is one route across it. Thus, in the example of Fig. 3, the probability that the soft edge runs across the horizontal grid edge above cell  $(r_1, c_2)$  is 1/7. For each vertical grid edge to the right of grid cell  $(r_s, c_i), c_s \leq c_i < c_t$ , the probability is  $|c_t - c_i|/Z$ . For example, the probability that the wire run across the vertical grid edge to right of grid cell  $(r_0, c_1)$  is 3/7. The probability at other grid edge can be counted similarly. Based on these probabilities, we define the probabilistic demand as follows:

DEFINITION 5 The *probabilistic demand* from a Z-edge  $e_{ij}$  to a grid edge *b* is the probability that Z-edge run across this grid edge, and is denoted as  $d_{prob}(b, e_{ij})$ .

## ALGORITHMS

## **Algorithm Motivation**

It is well-known that even minimizing only congestion for only 2-pin nets is an NP-complete problem, and considering timing constraints and the number of bends makes the problem even harder. Our strategy is to obtain the required timing performance first and then concentrate on optimizing the congestion and the number of bends while preserving the timing performance obtained. Therefore, we initially route each net individually through timing driven algorithms without considering congestion or the number of bends. We use soft edges and SSN in this phase so that the routing result is composed of only backbone nodes and every backbone wire is a single edge.

In the second phase, we will try to specify the details for the SSN and backbone wires in an effort to minimize congestion and control the number of bends on each backbone wire. The strategy here is to refine the route gradually according to available congestion information, even this information is ambiguous.

We can compare the underlying mechanism with the sequential and RR approach. In the sequential approach, the earlier routing steps are performed without any knowledge of the locations of the subsequent nets, and are therefore somewhat blindfolded. The routing of nets that are considered later is based on the routes of previous nets, which may be suboptimally placed, due to this false

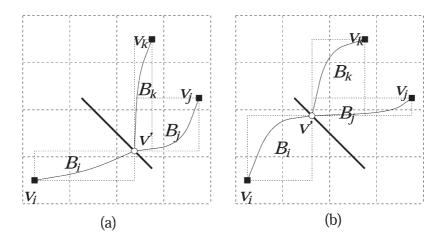

FIGURE 4 When an SSN slides along its locus, the bounding boxes of its incident edges change as well as the primitive demands.

feedback. Similarly, RR, which proceeds according to the locations of other nets, may also be suboptimal. Due to its iterative nature, RR method has the ability to correct the false feedback gradually and may become successful in reducing congestion after many iterations. However, the efficacy of RR may be hindered if constraints on timing and the number of bends are imposed.

Fortunately, our method can obtain some rough congestion estimation based on the locations of soft edges after phase one. This estimation is by no means completely accurate, but it is better than no feedback or incorrect feedback. Since we know that this estimation is not entirely accurate, we will not fix the route completely in one step. Instead, we will settle a part of the route to obtain a better congestion estimation and complete the routes gradually to avoid blindfolded or incorrect decision.

## Algorithm

Our algorithm includes two phases:

- i) Timing-driven routing for each net individually without considering congestion or number of bends.

- Specifying the route for each backbone wire obtained in phase I so that congestion is minimized subject to timing constraints and bends constraints.

In phase I, we route each net through the MVERT [23] algorithm using soft edges and SSN so that the timing constraints can be satisfied and the resulting routing tree consists of only backbone nodes and each backbone wire is either a solid edge or a soft edge.

After phase I, we can obtain a rough estimation of congestions through the concept of *primitive demand* defined in "Primitive demands" section. The first step in phase II is to fix the position of each SSN to minimize the peak primitive demand density. Recall that when an SSN slides along a locus of points, the lengths of its incident edges are not changed, and nor is the delay at any sink.

An example of a sliding Steiner node is illustrated in Fig. 4, and it can be seen that the bounding boxes of the incident edges, denoted by  $B_i$ ,  $B_j$  and  $B_k$ , are changed after the sliding of the SSN. In Fig. 4, when the Steiner node v' is slid toward northwest from (a) to (b), the bounding box  $B_i$  becomes thinner and taller and the vertical (horizontal) primitive demand incurred by  $(v_i, v, ')$  on each horizontal (vertical) cell boundary overlaps with  $B_i$  may be larger (smaller). The effect of this move on  $B_j$  and  $B_k$  is the opposite. Through a linear search for all the grid cells that the locus of the SSN intersects, we can find a grid cell to fix the position of the SSN such that the maximum demand density among the grid edges involved is minimized.

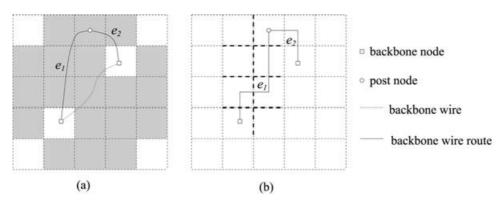

After fixing the SSN, we will make two sweeps of all the backbone wires in a constant order to specify their routes. Instead of specifying the complete route immediately in one step, we first only specify one grid cell that the backbone wire has to pass through. Note that neither of the end nodes of this backbone wire can be within this grid cell. We insert a pseudo node, which we call the post node in the backbone wire within this selected grid cell. For example, in Fig. 5a, a post node represented by a small circle is inserted into the backbone wire represented by a dotted curve. Before choosing the grid cell for the post node, we need to choose the candidate grid cells that will be considered. The routing flexibility from edge elongation is utilized here. For a backbone wire  $e_{ij}$ with edge length  $l_{ij}$ , we calculate the maximum allowed elongation  $\Delta l_{ij}$  under timing constraints as in "Edge elongation" section. If we insert a post node  $v_k$  into  $e_{ij}$ , the location of  $v_k$  must satisfy  $l_{ik} + l_{kj} \leq l_{ij} + \Delta l_{ij}$ . In Fig. 5a, the candidate grid cells are shaded.

Similarly, a formerly solid edge can also be elongated to reduce congestion. Thus, we see that a solid edge is not exactly solid any more, and can have some routing flexibility as well. Note that the maximum allowed elongation for each backbone wire is calculated dynamically, since the allowed elongations for backbone wires in a same routing tree depend on each other. GLOBAL ROUTING

FIGURE 5 Examples for setting post node for a backbone wire.

After the post node is inserted, the former backbone wire is split into two sub-edges. We specify that each subedge can be only a Z-edge so that we can bind the number of bends for each backbone wire. In our implementations, we set this bound to five. Different choices on the location of the post node and the routes of its two Z-edges usually provide us with plenty of routing flexibilities under restrictions on timing and number of bends on wires. Moreover, we can obtain a better estimation of the congestion by using the probabilistic demand defined in "Probabilistic demands" section. We choose the post node so as to minimize the congestion cost for the two subedges. Before setting the post node for a backbone wire  $e_i$ , we need to remove the primitive demand generated from the soft edge of  $e_i$ . Then, the congestion cost of a sub-edge  $e_i$  is defined as:

$$\operatorname{cost}(e_j) = \sum_{\forall b \quad \text{intersecting bounding box of}} \mathcal{D}(b)^2$$

$$\times d_{\operatorname{prob}}(b, e_j). \tag{5}$$

Recall that  $\mathcal{D}(b) = d(b)/s(b)$  is the demand density at boundary *b* and  $d_{\text{prob}}(b, e_j)$  is the probability that the Z-edge  $e_j$  runs across boundary *b*. In the example in Fig. 5b, the cost of edge  $e_1$  is the summation of the estimated costs from thickened grid edges. Setting a post node will not exclude the case that a backbone wire is in a direct L-shaped connection, since it is possible that the post node is the bend node and two Z-edges are straight solid edges.

After setting the post node, we generate the probabilistic demands from the two new Z-edges. The process of setting the post node is performed for each backbone wire in every routing tree, which is the first sweep. During this sweep, the backbone wires that have been processed are Z-edges while those have not been processed are still soft edges. Thus, in the congestion cost computation, both primitive and probabilistic demand may co-exist at a same time. Therefore, we multiply the primitive demand by a penalty coefficient of less than one to make its contribution weaker than that of the probabilistic demand.

After post nodes have been selected for all of the backbone wires, all of the demands become probabilistic

demands. Based on this improved congestion estimation, we start the second sweep for all backbone wires to specify their routes in the same order as in previous sweep. For each backbone wire, we recomputed its post node before fixing the routes of its two Z-edges. A backbone wire appears early in the order list may have a poor post node location in the previous sweep, since this location is chosen according to mostly primitive demands. In this second sweep, this backbone wire has a chance to adjust its post node location from more accurate congestion information. The procedure of recomputing the post node is the same as in previous sweep. We choose the route for a Z-edge  $e_j$  to minimize congestion in term of a cost defined as:

$$cost(e_j) = \sum_{\forall b \text{ intersecting route of } e_j} \mathscr{D}(b)^2.$$

(6)

The minimum cost route can be found through simple enumeration in a manner similar to calculating the probabilistic demand in "Probabilistic demands" section. After fixing the routes for each backbone wire, its probabilistic demand is replaced by determined demand. The complete algorithm is called ZigPuzzle and summarized in Fig. 6. A simple example is given in Fig. 7 to illustrate the algorithm flow. For each net, an MVERT tree is constructed in Phase I, as shown in Fig. 7a. In Fig. 7b, each SSN is slid to a position to minimized the peak primitive demand at the beginning of Phase II. Then, a post node for each backbone wire is searched like in Fig. 7c to minimized the estimated congestion (line 5-7 in Phase II of Fig. 6). After the post nodes are found for every backbone wire, a more accurate estimation on the congestions is generated. Finally, the post node for each backbone wire is recomputed (line 11 in Phase II of Fig. 6) based on the updated congestion information as shown in Fig. 7d and the route for each Z-edge is found to complete the global routing (Fig. 7e).

For a net with *n* sinks, the computational complexity of the MVERT algorithm in Phase I is about  $O(n^4)$  [23]. If there are *N* nets in a circuit and the maximum number of sinks for each net is  $n_{\text{max}}$ , the complexity of the Phase I in our method is  $O(N \cdot n_{\text{max}}^4)$ . In Phase II, the computationally

| Algorithm: $\mathbf{ZigPuzzle}(\mathcal{N}, G)$                      |

|----------------------------------------------------------------------|

| <b>Input:</b> A set of nets $\mathcal{N}$ , grid graph $G(V_G, E_G)$ |

| <b>Output:</b> $T^i$ for each $N^i$ min congestion                   |

| s.t. timing constraints, $\leq 5$ bends per backbone wire            |

| Phase I                                                              |

| 1. For each $N^i \in \mathcal{N}$                                    |

| 2. $T^i \leftarrow \text{MVERT}(N^i)$                                |

| Phase II                                                             |

| 1. Generate primitive demand for each backbone wire                  |

| 2. Fix all of the SSNs, min peak demand density                      |

| 3. For each tree $T^i$                                               |

| 4. For each backbone wire $e^i_{jk} \in T^i$                         |

| 5. Remove its primitive demand                                       |

| 5. Compute max elongation $\Delta l_{jk}$ without timing violation   |

| 6. Find candidate grid cells for post node                           |

| 7. Search a post node, min congestion cost                           |

| 8. Generate probabilistic demand from two Z-edges                    |

| 9. For each tree $T^i$                                               |

| 10. For each backbone wire $e^i_{ik} \in T^i$                        |

| 11. Recompute its post node                                          |

| 12. Remove its probabilistic demand                                  |

| 13. Fix routes for two Z-edges, min congestion cost                  |

| 14. Generate determined demands from two Z-edges                     |

FIGURE 6 Algorithm.

dominating step is to find the post for each backbone wire. In the worst case, where the two ends of the backbone wire are located at two corner grid cells diagonally opposite to each other on the grid graph, the search for the best post node is performed at almost every grid cell and the congestion estimation on every grid edge is updated to calculate the cost. Since the search on a post node is performed on every backbone wire, the complexity in Phase II is  $O(N \cdot n_{\max} \cdot m^2)$  if there are *m* grid cells in the grid graph. Normally, the aforementioned worst case occurs only on a very small portion of the backbone wires, hence, this complexity is a very loose bound. The complexity of the whole algorithm is  $O(\max(N \cdot n_{\max}^4, N \cdot n_{\max} \cdot m^2))$ .

TABLE I Description of test circuits

| Circuit | No. of modules | No. of nets | No. of pins |  |  |

|---------|----------------|-------------|-------------|--|--|

| ami33   | 33             | 85          | 442         |  |  |

| xerox   | 10             | 203         | 696         |  |  |

| ami49   | 49             | 390         | 913         |  |  |

| es1     | -              | 1109        | 2464        |  |  |

| es2     | -              | 2100        | 4576        |  |  |

| es3     | _              | 3107        | 6817        |  |  |

## **EXPERIMENTAL RESULTS**

We have implemented ZigPuzzle global routing in C++ and conducted experiments on a SUN Ultra-10 workstation. The circuits that we tested includes *ami33*, *ami49* and *xerox* whose netlists are from the CBL/NCSU benchmark suite and the placements were provided to us [27] through running a simulated annealing based tool [28]. In order to test our method on larger instances, three other sets of nets are randomly generated. The statistics of these testcases are shown in Table I. For some circuits, more than one set of netlists is obtained through different placement. For example, there are two sets of netlists for circuit of *ami49* and *xerox*. Each result is measured in terms of two congestion metrics: total overflow  $\mathscr{F}_{ov}$  and maximum demand density  $\mathscr{D}_{max}$ .

For comparisons, we also implemented three variations of RR global routing algorithm. In the base version of RR, we initially route each net separately in MVERT same as in phase I of ZigPuzzle but using solid edges. Then, we rip up every backbone wire in the region with wire overflow, and reroute them through maze routing to minimize congestion cost which is same as in Eq. (6) except that the demand is determined. Three variations are: RR + B (RR with bends control), RR + T (timing-constrained RR) and RR + B + T (timing-constrained RR with bends control).

FIGURE 7 An example of the algorithm flow.

GLOBAL ROUTING

| Circuit | Grid size      | E    | RR + B                      |                      | RR + T |                             | RR + B + T           |       | ZigPuzzle                   |                      |                             |                      |        |

|---------|----------------|------|-----------------------------|----------------------|--------|-----------------------------|----------------------|-------|-----------------------------|----------------------|-----------------------------|----------------------|--------|

|         |                |      | $\mathcal{F}_{\mathrm{ov}}$ | $\mathcal{D}_{\max}$ | vio    | $\mathcal{F}_{\mathrm{ov}}$ | $\mathcal{D}_{\max}$ | ben   | $\mathcal{F}_{\mathrm{ov}}$ | $\mathcal{D}_{\max}$ | $\mathcal{F}_{\mathrm{ov}}$ | $\mathcal{D}_{\max}$ | CPU(s) |

| ami33.1 | $22 \times 36$ | 489  | 0                           | 1.00                 | 5      | 1                           | 1.20                 | 12    | 1                           | 1.20                 | 0                           | 1.00                 | 15.8   |

| xerox.1 | $54 \times 55$ | 587  | 0                           | 1.00                 | 6      | 5                           | 1.14                 | 14    | 5                           | 1.14                 | 0                           | 0.86                 | 16.1   |

| xerox.2 | $54 \times 61$ | 571  | 0                           | 1.00                 | 6      | 2                           | 1.06                 | 12    | 2                           | 1.06                 | 2                           | 1.06                 | 23.3   |

| ami49.1 | $40 \times 41$ | 594  | 1                           | 1.10                 | 34     | 0                           | 1.00                 | 18    | 5                           | 1.10                 | 0                           | 1.00                 | 29.8   |

| ami49.2 | $52 \times 53$ | 593  | 0                           | 1.00                 | 38     | 0                           | 1.00                 | 14    | 51                          | 1.80                 | 2                           | 1.10                 | 25.9   |

| test1   | $52 \times 52$ | 1468 | 4                           | 1.29                 | 34     | 0                           | 1.00                 | 17    | 58                          | 1.21                 | 1                           | 1.07                 | 207    |

| test2   | $53 \times 53$ | 2648 | 5                           | 1.13                 | 28     | 0                           | 1.00                 | 17    | 107                         | 1.12                 | 0                           | 1.00                 | 562    |

| test3   | $52 \times 52$ | 3992 | 4                           | 1.16                 | 35     | 0                           | 1.00                 | 20    | 63                          | 1.14                 | 0                           | 1.00                 | 1013   |

| average | $47 \times 50$ | 1368 | 1.8                         | 1.09                 | 23     | 1                           | 1.05                 | 16    | 36.5                        | 1.22                 | 0.6                         | 1.01                 | 237    |

| Comp    |                |      | 3 ×                         | $1.05 \times$        |        | $1.67 \times$               | $1.03 \times$        | 3.2 × | 61 ×                        | $1.20 \times$        |                             |                      |        |

TABLE II Experimental results, vio is number of nets with timing violations and ben is the maximum number of bends on a backbone wire

In order to control the number of bends in RR, we replace the cost in maze routing with a weighted sum of congestion and number of bends. We run the RR + B with several different values of weight and choose the result that provides the best congestion, while assuring that the number of bends for each backbone wire is no greater than five, which is same as in ZigPuzzle. In RR + T, the timing constraints are imposed on the wirelength for each backbone wire. Both of these methods are combined in obtaining the results for the RR + B + T case.

The experimental results are shown in Table II. Column 4-6 are results from RR + B, whose number of bends is bounded to be no more than five for each backbone wire. Its congestion results are generally good with limited wire overflows in large circuits. However, it does not have the capability to satisfy timing constraints and there are always a number of nets have timing violations as indicated in column 6. The results from RR + T is given in column 7-9, where the congestion is good subject to timing constraints, but the maximal number of bends per backbone wire can be very large (in a range of 12-20). When we impose both timing and bends constraints directly on RR, the results in column 10 and 11 shows that the congestion can be very poor especially in large circuits. On the other hand, our ZigPuzzle can optimize congestion subject to timing and bend constraints, and works well in both small and large circuits. In the last row of the table, the results from RR are compared with that of ZigPuzzle.

The rightmost column lists the CPU time in seconds. Since a circuit may include many multi-pin nets, it would be more interesting to evaluate the CPU time for each 2-pin net as a normalized comparison. Column 3 lists the number of backbone wires in each circuit. It is easy to regard these backbone edges as decomposition into 2-pin nets. Therefore, we can get the average CPU time for a 2-pin net is 0.2 s.

In our approach, we use primitive demand to estimate the congestions from soft edges. Instead of this, we can use a probabilistic estimation similar to that in "Probabilistic demands" section for soft edges by using the technique described in Ref. [26], and it may initially seem that this would provide a more accurate estimate of congestion. We have also performed experiments using this approach. However, we find that this approach takes a longer CPU time and often produces worse results. This increased CPU is not unexpected, since the computation related to probabilistic estimation will be more computationally intensive than primitive demand calculations, especially when the allowed number of bends is large. In addition, a backbone wire could be elongated at a later stage, and therefore, the increased accuracy obtained from probabilistic estimation at current stage may become meaningless later. The spirit of primitive demand is to catch a rough estimation in a quick operation and our experiments have demonstrated that it is better than a more sophisticated measure at the early stage of global routing.

#### CONCLUSION

We propose a new heuristic to improve the quality of global routing. In addition to exploiting timing constrained routing flexibilities, we apply a simple gradual refinement method based on probabilistic congestion estimation, which leads to simultaneous optimization on congestion, timing and number of bends. In future, the computational speed needs to be improved further to accommodate the more and more complicated designs.

#### Acknowledgements

The authors would like to thank Dr Hai Zhou for providing the placements of the testcases.

## References

- Chiang, C. and Sarrafzadeh, M. (1990) "Global routing based on Steiner min-max trees", *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems* 9(12), 1318–1325.

- [2] Burstein, M. and Pelavin, R. (1983) "Hierarchical wire routing", IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems CAD-2(4), 223–234.

- [3] Marek-Sadowska, M. (1984) "Global router for gate array", Proceedings of the IEEE International Conference on Computer Design, 332–337.

- [4] Cho, J.D. and Sarrafzadeh, M. (1998) "Four-bend top-down global routing", *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems* 17(9), 793–802.

- [5] Raghavan, P. and Thompson, C.D. (1991) "Multiterminal global routing: a deterministic approximation scheme", *Algorithmica* 6, 73–82.

- [6] Carden, IV, R.C., Li, J. and Cheng, C.-K. (1996) "A global router with a theoretical bound on the optimal solution", *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems* 15(2), 208–216.

- [7] Albrecht, C. (2000) "Provably good global routing by a new approximation algorithm for multicommodity flow", *Proceedings* of the ACM International Symposium on Physical Design, 19–25.

- [8] Cong, J. and Preas, B. (1992) "A new algorithm for standard cell global routing", *Integration—The VLSI Journal* 14, 49–65.

- [9] Ting, B.S. and Tien, B.N. (1983) "Routing techniques for gate array", *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems* CAD-2(4), 301–312.

- [10] Nair, R. (1987) "A simple yet effective technique for global wiring", *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems* CAD-6(2), 165–172.

- [11] Lee, K.W. and Sechen, C. (1991) "A global router for sea-of-gate circuits", *Proceedings of the European Design Automation Conference*, 242–247.

- [12] Wang, D. and Kuh, E.S. (1996) "Performance-driven interconnect global routing", *Proceedings of the IEEE Great Lakes Symposium* on VLSI, 132–136.

- [13] Huang, J., Hong, X.-L., Cheng, C.-K. and Kuh, E.S. (1993) "An efficient timing-driven global routing algorithm", *Proceedings of* the ACM/IEEE Design Automation Conference, 596–600.

- [14] Hu, J. and Sapatnekar, S.S. (2000) "A timing-constrained algorithm for simultaneous global routing of multiple nets", *Proceedings of the IEEE/ACM International Conference on Computer-Aided Design*, 99–103.

- [15] Boese, K.D., Kahng, A.B., McCoy, B.A. and Robins, G. (1995) "Near-optimal critical sink routing tree constructions", *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems* 14(12), 1417–1436.

- [16] Khoo, K.-Y. and Cong, J. (1995) "An efficient multilayer MCM router based on four-via routing", *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems* 14(10), 1277–1290.

- [17] Hu, J. and Sapatnekar, S.S. (2001) "Performance driven global routing through gradual refinement", *Proceedings of the IEEE International Conference on Computer Design*, 481–483.

- [18] Elmore, W.C. (1948) "The transient response of damped linear network with particular regard to wideband amplifiers", *Journal of Applied Physics* 19, 55–63.

- [19] Rubinstein, J., Penfield, P. and Horowitz, M.A. (1983) "Signal delay in RC tree networks", *IEEE Transactions on Computer-Aided Design* CAD-2(3), 202–211.

- [20] Hu, J. and Sapatnekar, S.S. (2000) "Algorithms for non-Hananbased optimization for VLSI interconnect under a higher-order AWE model", *IEEE Transactions on Computer-Aided Design* 19(4), 446–458.

- [21] Lillis, J., Cheng, C.K., Lin, T.T. and Ho, C.Y. (1996) "New performance driven routing techniques with explicit area/delay

tradeoff and simultaneous wire sizing", *Proceedings of the 33rd* ACM/IEEE Design Automation Conference June, 395–400.

- [22] Cong, J. and Koh, C.K. (1997) "Interconnect layout optimization under higher-order RLC model", *Proceedings of the IEEE/ACM International Conference on Computer-Aided Design*, 713–720.

- [23] Hou, H., Hu, J. and Sapatnekar, S.S. (1999) "Non-Hanan routing", *IEEE Transactions on Computer-Aided Design* 18(4), 436–444.

- [24] Chen, H.-M., Zhou, H., Yang, F.Y., Yang, H.H. and Sherwani, N. (1999) "Integrated floorplanning and interconnect planning", *Proceedings of the IEEE/ACM International Conference on Computer-Aided Design*, 354–357.

- [25] Sarkar, P., Sundararaman, V. and Koh, C.-K. (2000) "Routabilitydriven repeater block planning for interconnect-centric floorplanning", *Proceedings of the ACM International Symposium on Physical Design*, 186–191.

- [26] Kusnadi and Carothers, J.D. (1999) "A method of measuring nets routability for MCM's general area routing problems", *Proceedings* of the ACM International Symposium on Physical Design, 186–192.

- [27] Zhou, H. (2000) "Personal communication".

- [28] Wong, D.F. and Liu, C.L. (1986) "A new algorithm for floorplan design", Proceedings of the ACM/IEEE Design Automation Conference, 101–107.

Jiang Hu received the B.S. degree in optical engineering from Zhejiang University, Hangzhou, China, in 1990, the M.S. degree in physics from the University of Minnesota, Duluth, in 1997, and the Ph.D. degree in electrical engineering from the University of Minnesota, Minneapolis, in 2001. He has been with IBM Microelectronics Division working on VLSI CAD tools development. He is currently an assistant professor in the Department of EE at the Texas A&M University. His research interest is on VLSI physical design, especially on interconnect routing, optimization and planning. Dr Hu received a best paper award at the Design Automation Conference in 2001.

Sachin Sapatnekar received his B.Tech. from Indian Institute of Technology, Bombay in 1987, M.S. from Syracuse University in 1989 and Ph.D. from University of Illinois at Urbana-Champaign in 1992. From 1992 to 1997, he was an assistant professor in Department of ECE at Iowa State University. He is currently professor in Department of ECE at University of Minnesota. His research interest is on VLSI CAD, concentrating on timing, power and layout issues. He is a recipient of the NSF Career Award and Best Paper awards at DAC97, ICCD98 and DAC01.

## 604

Rotating Machinery

Journal of Sensors

International Journal of Distributed Sensor Networks

Journal of Electrical and Computer Engineering

International Journal of

Aerospace

Engineering

International Journal of Chemical Engineering

Advances in Civil Engineering

International Journal of Antennas and Propagation

Hindawi

Submit your manuscripts at http://www.hindawi.com

Active and Passive Electronic Components

Shock and Vibration

Advances in Acoustics and Vibration