## ABSTRACT

# Title of Dissertation:INTEGRATED INDUCTIVE AND CONDUCTIVE<br/>CHARGING SYSTEM FOR ELECTRIC VEHICLES

Arun Sankar Uma Sankar, Doctor of Philosophy, 2019.

Dissertation directed by:

Prof. Alireza Khaligh, Associate Professor, Department of Electrical and Computer Engineering

The global electric vehicle (EV) market acceleration is facilitated by supporting policies deployed by governments and cities to reap multiple benefits in the fields of transport decarbonization, air pollution reduction, energy efficiency and security. Currently conductive chargers are a customary method of storing electric energy into the storage elements present onboard of an EV which is inadequate in supporting complete autonomy. The thriving inclination towards design of autonomous vehicles have shaped wireless charging as an attractive solution in favor of complete autonomy. As long as the wireless charging infrastructure as well as interoperability standards are not completely developed, wired and wireless chargers have to co-exist onboard the vehicles for user convenience. Incorporation of an entire parallel wireless charging system on-board an EV, either during manufacturing or after-market increases size, weight, or cost, while declining the electric range of vehicle. The current requisite for multiple on-board charging options motivates the necessity for a solution for efficiently integrating wired and wireless charging systems.

In this PhD research we propose multiple charging architectures capable of integrating inductive and conductive charging systems. The proposed architectures merge

the output rectifying stage of an inductive charging system to the existing on-board charger eliminating the additional weight and volume associated with a wireless charger. Since the proposed system involves multiple power conversion stages, a system level study is carried out to select feasible topologies capable of maximizing the efficiency of an integrated system. Additionally, an extended harmonic approximation (EHA) technique is introduced to increase the accuracy of a resonant converter model facilitating the optimized design parameter selection of an inductive charging system. Furthermore, a novel analog synchronous rectification circuit is proposed and designed to enable active rectification maximizing power transfer efficiency.

For proof of concept verification, a laboratory prototype of a 3.3kW Silicon Carbide (SiC) based integrated wireless charger is developed that can be interfaced to a variable input voltage (85-265 Vrms) 50/60Hz AC grid. According to the experimental measurements, the charger draws an input current with total harmonic distortion of 1.3% while achieving an overall efficiency of 92.77% at rated output power.

## INTEGRATED INDUCTIVE AND CONDUCTIVE CHARGING SYSTEM FOR ELECTRIC VEHICLES

by

Arun Sankar Uma Sankar

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park, in partial fulfillment of the requirements for the degree of Doctor of Philosophy 2019

Advisory Committee: Professor Alireza Khaligh, Chair/Advisor Professor Robert Newcomb Professor Neil Goldsman Professor Kevin Daniels Professor Patrick McCluskey, Dean's Representative © Copyright by Arun Sankar Uma Sankar 2019

## Acknowledgments

First of all, I would like to thank my PhD advisor Prof. Alireza Khaligh, for his valuable advice and mentorship throughout my research. During the past few years at University of Maryland, Prof. Khaligh not only introduced me to high quality research in power electronics, but also educated me on various practical perspectives to be considered while analyzing research problems. He has been a constant support during my failures and motivated me to strive towards success. I would really like to thank him for his valuable advices which has helped in my professional development.

I would also like to thank Prof. Robert Newcomb, Prof. Neil Goldsman, Prof. Kevin Daniels and Prof. Patrick McCluskey for kindly taking out their valuable time to be a part of my PhD committee. Thank you for your interest in my work.

I would also like to thank all of my present and former lab mates at MPEL (Ayan Mallik, Weisheng Ding, Akshay Singh, Jiangheng Lu, Michael D'Antonio, Peiwen He, Zeyu Zhang, Shenli Zou, Shiladri Chakraborty, Apurv Kumar Yadav, Bin Wu, Chuan Shi) for their time in regular technical discussions and helping in debugging hardware at rough times. These productive discussions always helped me to learn more and think outside the box for finding solutions.

Very special thanks and sincere gratitude to my parents for their constant support, encouragement, motivation and belief in me throughout by studies. I would also like to thank my brother, friends and teachers who have motivated me throughout my life to pursue my dreams and achieve this degree. Furthermore, this work has been sponsored by the US National Science Foundation grant numbers 1507546, 1602012 and UM Ventures Seed grant which are gratefully acknowledged.

## Contents

| Chapter 1 | 1: Introduction                                               |

|-----------|---------------------------------------------------------------|

| 1.1       | EV Market 1                                                   |

| 1.2       | EV Architecture                                               |

| 1.3       | Charging Structures                                           |

| 1.3.1     | Conductive charging 6                                         |

| 1.3.2     | 2 Inductive charging                                          |

| 1.3.3     | 3 Capacitive charging 10                                      |

| 1.4       | Thesis Objectives 12                                          |

| 1.5       | Major Contributions                                           |

| 1.6       | Synopsis of the dissertation15                                |

| Chapter 2 | 2: Integrated wireless charging system architecture           |

| 2.1       | Background review of existing integrated charging solutions   |

| 2.2       | Proposed Integrated Wired and Wireless Charging Architecture  |

| 2.2.1     | Solution I                                                    |

| 2.2.2     | 2 Solution II                                                 |

| 2.2.3     | 3 Solution III                                                |

| 2.3       | System level implementation structures for proposed solutions |

| 2.4       | Summary                                                       |

| Chapter 3 | 3: Design and Evaluation of Off-board AC-DC Conversion Stage  |

|   | 3.1     | Introduction                                              | 33 |

|---|---------|-----------------------------------------------------------|----|

|   | 3.2     | Off-board system design                                   | 33 |

|   | 3.1     | Selection of input conditioning stage                     | 33 |

|   | 3.1     | 1.1 Basic operation principle and design details          | 36 |

|   | 3.1     | 1.2 Discussions                                           | 40 |

|   | 3.2     | Loss Comparison                                           | 41 |

|   | 3.2     | 2.1 Capacitor Selection                                   | 41 |

|   | 3.2     | 2.2 Design of input inductor                              | 42 |

|   | 3.2     | 2.3 Switching Loss evaluation                             | 47 |

|   | 3.3     | Selected Topology                                         | 48 |

|   | 3.4     | Modeling and control                                      | 49 |

|   | 3.4     | A.1 Averaged large-signal model of totem pole PFC circuit | 50 |

|   | 3.4     | Averaged Small Signal model for totem pole PFC            | 52 |

|   | 3.4     | 4.3       Steady state model                              | 53 |

|   | 3.4     | Linearized small signal and s-domain models               | 54 |

|   | 3.4     | 1.5   Design of Control System                            | 55 |

|   | 3.5     | Simulation Results                                        | 61 |

|   | 3.6     | Experimental Verification                                 | 62 |

|   | 3.7     | Summary                                                   | 66 |

| C | Chapter | r 4: Design and development of DC-DC Wireless Stage       | 67 |

| 4.1 Fu     | undamentals of Inductive power transfer                           | . 67 |

|------------|-------------------------------------------------------------------|------|

| 4.2 C      | ompensation Topologies                                            | . 69 |

| 4.3 In     | ductive coil modeling                                             | . 71 |

| 4.4 M      | lodeling of DC/DC stage                                           | . 74 |

| 4.4.1      | FHA Analysis                                                      | . 77 |

| 4.4.2      | Extended Harmonics analysis                                       | . 82 |

| 4.4.3      | Selection of Parameters                                           | . 87 |

| 4.5 Co     | ontrol Strategy                                                   | . 90 |

| 4.5.1      | Pulse frequency modulation (PFM) control                          | . 91 |

| 4.5.2      | Primary side phase shift control                                  | . 92 |

| 4.6 Si     | mulation Results                                                  | . 94 |

| 4.7 Ez     | xperimental Verification                                          | . 96 |

| 4.8 Su     | ummary                                                            | 100  |

| Chapter 5: | Analog Synchronous Rectification based Integrated Charging System | 102  |

| 5.1 Sy     | ynchronous Rectification (SR)                                     | 103  |

| 5.1.1      | Lead compensation network                                         | 105  |

| 5.1.2      | Gain circuit                                                      | 108  |

| 5.1.3      | Comparator circuit                                                | 109  |

| 5.1.4      | Complementary pulse + dead band generation                        | 111  |

| 5.1.5      | Implementation of the proposed SR circuit                         | 112  |

| 5.2 Experimental Verification of Analog SR circuit |                                                                              |  |  |  |

|----------------------------------------------------|------------------------------------------------------------------------------|--|--|--|

| 5.3                                                | Experimental verification of integrated wireless charging solution 116       |  |  |  |

| 5.4                                                | Summary 119                                                                  |  |  |  |

| Chapter                                            | 6: Conclusion and Future Research Work 120                                   |  |  |  |

| 6.1                                                | Conclusions 120                                                              |  |  |  |

| 6.2                                                | Future Work 121                                                              |  |  |  |

| 6.2.                                               | .1 Secondary side control of series compensated wireless system with reduced |  |  |  |

| com                                                | nmunication requirements 121                                                 |  |  |  |

| 6.2.                                               | .2 Multi-objective optimization of integrated wireless charging system 122   |  |  |  |

| Chapter                                            | 7: Bibliography 124                                                          |  |  |  |

## **List of Figures**

| Fig. 1.1 Power electronic interfaces onboard a plug-in hybrid vehicle                 | . 2        |

|---------------------------------------------------------------------------------------|------------|

| Fig. 1.2 Typical charging elements of an EV equipped with conductive and inductive    |            |

| charging                                                                              | . 5        |

| Fig. 1.3 Typical structure of on-board charger                                        | . 6        |

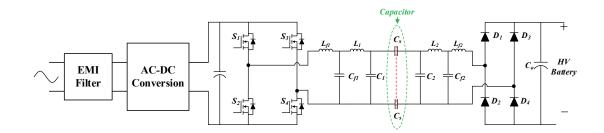

| Fig. 1.4 High efficiency vehicle charger proposed in [11]                             | . 7        |

| Fig. 1.5 Bidirectional PWM resonant converter proposed in [12]                        | . 7        |

| Fig. 1.6 Dual stage OBC structure proposed by researchers in [13]                     | . 8        |

| Fig. 1.7 Typical structure of an IPT system for EV charging                           | . 8        |

| Fig. 1.8 IPT system employing a dual stage structure with voltage fed high frequency  |            |

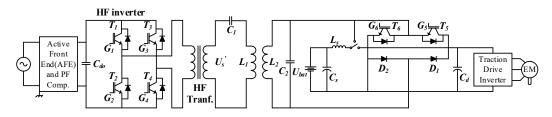

| inverter network                                                                      | . 9        |

| Fig. 1.9 IPT system employing a current source fed high frequency inverter[32]        | 10         |

| Fig. 1.10 IPT charger employing multi-phase inductively coupled wireless converter[34 | <b>i</b> ] |

|                                                                                       | 10         |

| Fig. 1.11 Typical structure of a CPT system for EV charging                           | 11         |

| Fig. 1.12 CPT structure presented by researchers in [35]                              | 11         |

| Fig. 1.13 CPT structure presented by researchers in [36]                              | 12         |

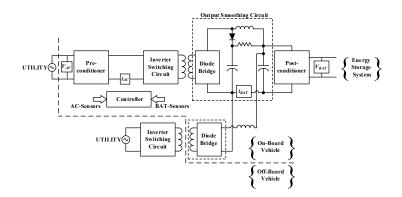

| Fig. 2.1 Integrated configuration 1 proposed in [38]                                  | 18         |

| Fig. 2.2 Integrated configuration 2 proposed in [38]                                  | 19         |

| Fig. 2.3 Integrated configuration proposed in [2-3]                                   | 19         |

| Fig. 2.4 Integrated configuration proposed in [2-4]                                   | 20         |

| Fig. 2.5 Proposed Integration solution I at power factor correction stage of onboard  |            |

| charger                                                                               | 21         |

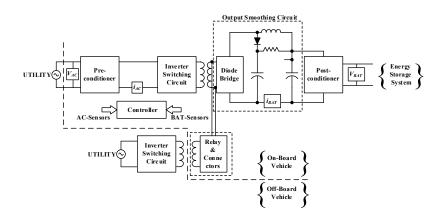

| Fig. 2.6 Proposed solution II                                                         | 25         |

| Fig. 2.7 Proposed Integration solution III                                            | 25         |

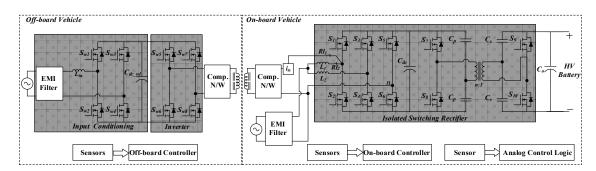

| Fig. 2.8 System Level implementation of Solution I                                    | 28         |

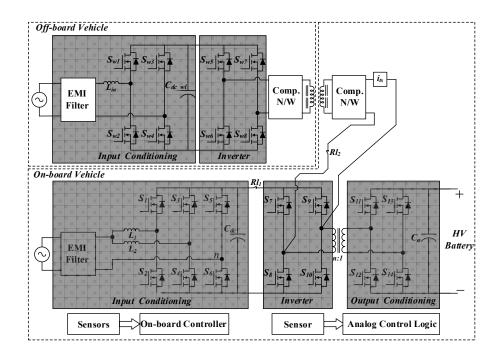

| Fig. 2.9 System level implementation of Solution II                                   | 30         |

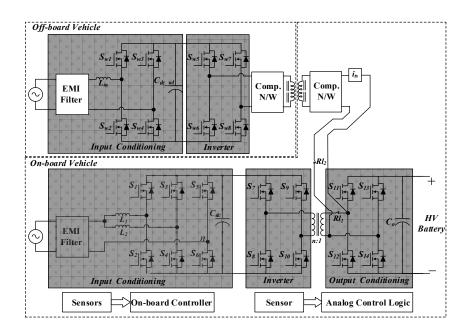

| Fig. 2.10 System level implementation of Solution III                                                  | 31 |

|--------------------------------------------------------------------------------------------------------|----|

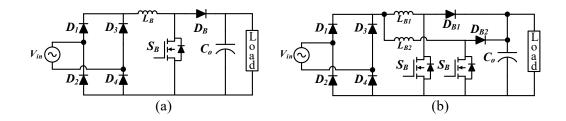

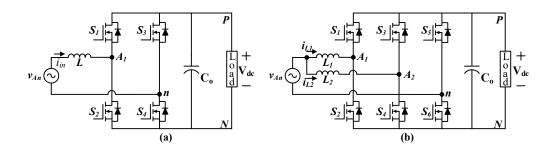

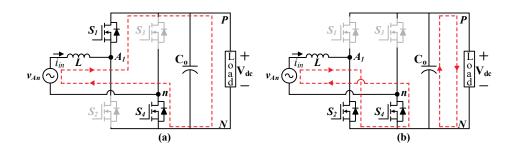

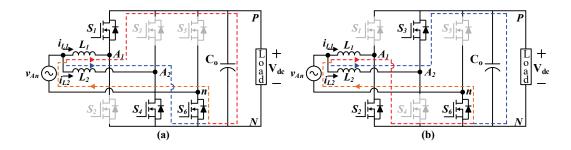

| Fig. 3.1 Traditional PFC topology (a) boost PFC (b) interleaved boost PFC                              | 35 |

| Fig. 3.2 Bridgeless boost-derived topologies (a) Totem pole or H-bridge (b) Interleaved                | ł  |

| totem pole                                                                                             | 36 |

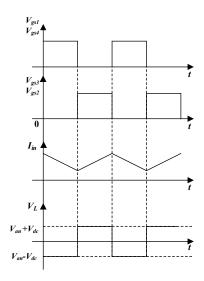

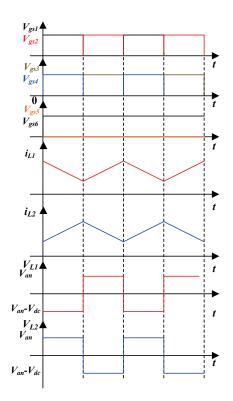

| Fig. 3.3 Key operating waveforms under H-bridge switching scheme                                       | 37 |

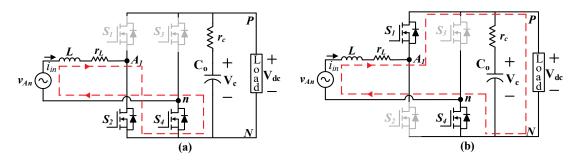

| Fig. 3.4 Power flow during AC positive half-cycle under H-bridge operation (a)                         |    |

| Discharging cycle (b) Charging cycle                                                                   | 37 |

| Fig. 3.5 Key operating waveforms for positive half-cycle under totem pole switching                    |    |

| scheme                                                                                                 | 38 |

| Fig. 3.6 Power flow during AC positive half-cycle under totem pole operation (a)                       |    |

| Discharging cycle (b) Charging cycle                                                                   | 39 |

| Fig. 3.7 Power flow path for AC positive half-cycle (a) <i>L</i> 1 discharging <i>L</i> 2 charging (b) |    |

| <i>L</i> 1 charging <i>L</i> 2 discharging                                                             | 39 |

| Fig. 3.8 Key operating waveforms for positive half-cycle operation with interleaved                    |    |

| totem pole-structure                                                                                   | 40 |

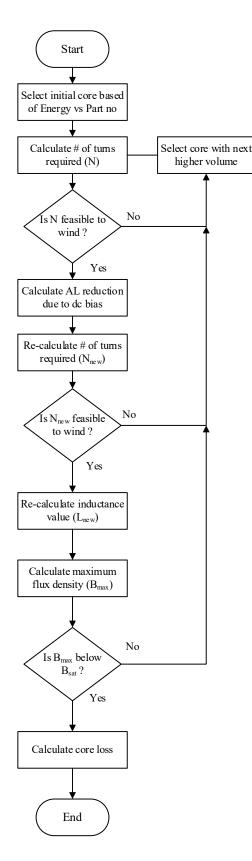

| Fig. 3.9 Inductor design flowchart                                                                     | 46 |

| Fig. 3.10 Totem pole PFC equivalent circuit of operation positive half-cycle (a) D period              | od |

| (b) (1-D) period                                                                                       | 50 |

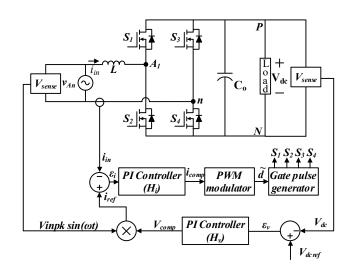

| Fig. 3.11 Totem pole PFC dual loop control structure                                                   | 56 |

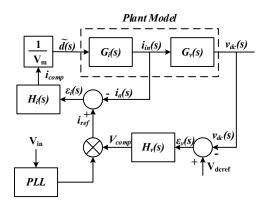

| Fig. 3.12 Small signal control block diagram for totem pole converter                                  | 57 |

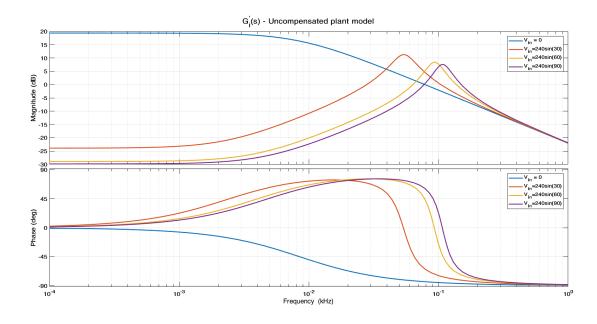

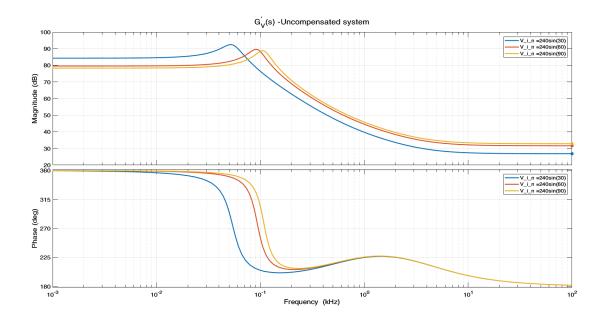

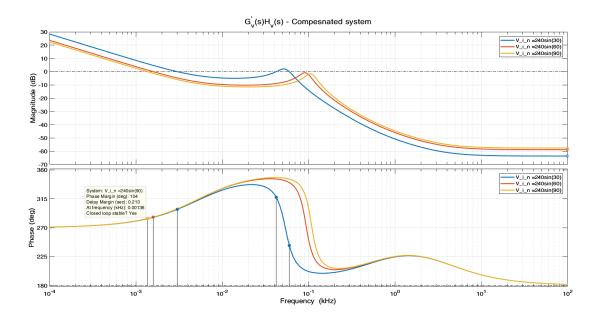

| Fig. 3.13 Bode plot: Uncompensated plant model for current loop                                        | 58 |

| Fig. 3.14 Bode plot: Compensated plant model for current loop                                          | 59 |

| Fig. 3.15 Bode plot: Uncompensated voltage transfer function                                           | 60 |

| Fig. 3.16 Bode plot: Compensated open loop transfer function                                           | 60 |

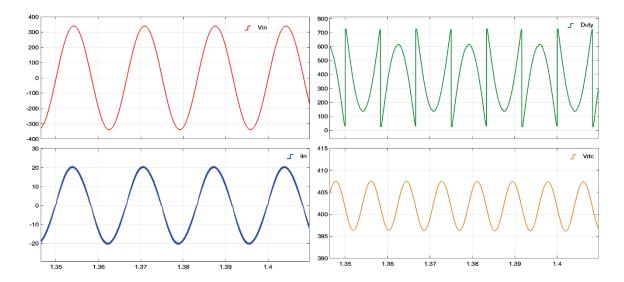

| Fig. 3.17 Key Operating waveforms for Totem-pole scheme at 3.3kW (a) Input voltage                     |    |

| $(V_{in})$ (b) Input current $(i_{in})$ (c) Duty ratio(D) (d) Output Voltage $(V_{dc})$                | 61 |

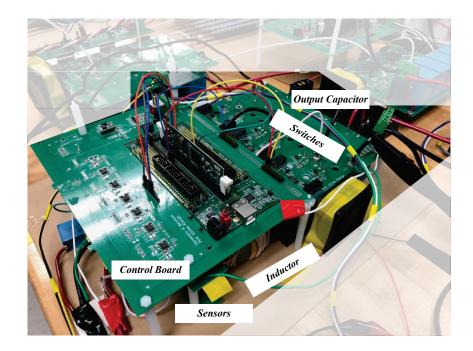

| Fig. 3.18 Laboratory implemented prototype of 3.3kW PFC                                                | 62 |

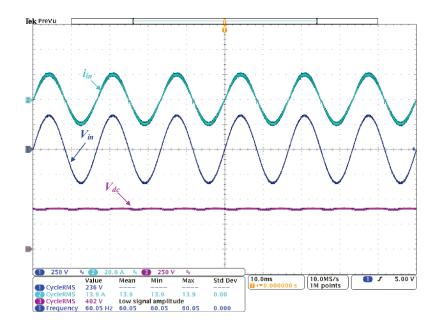

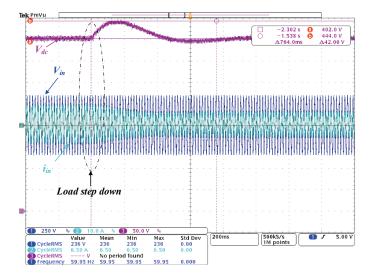

| Fig. 3.19 Key operating waveforms for totem pole PFC @ $V_{in}$ =240Vrms, $V_{dc}$ =400V,                 |

|-----------------------------------------------------------------------------------------------------------|

| $P_{out}$ = 3.3 kW output power                                                                           |

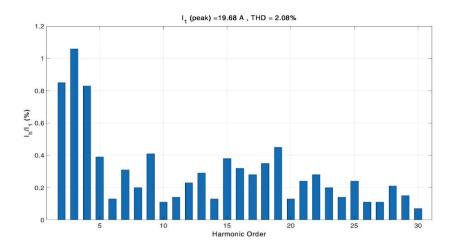

| Fig. 3.20 Harmonic spectrum of input current under nominal voltage and full load                          |

| condition                                                                                                 |

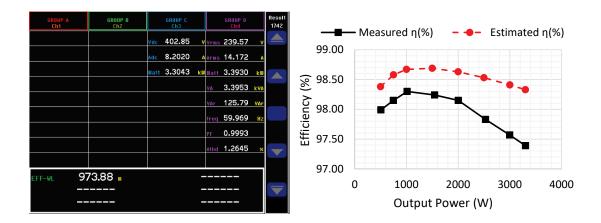

| Fig. 3.21 (a) Tektronix power measurements (b) Estimated vs Measured efficiency plot over the power range |

|                                                                                                           |

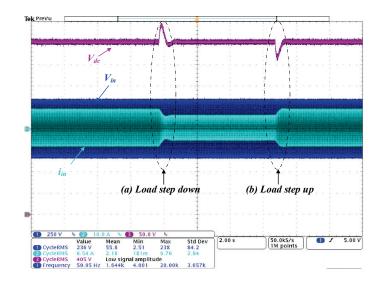

| Fig. 3.22 PFC transient results (a) Load step from 1.5 kW to 1 kW (b) Load step from 1                    |

| kW to 1.5 kW                                                                                              |

| Fig. 3.23 Key transient waveforms under load step from 1.5kW to 1kW                                       |

| Fig. 4.1 Wireless DC-DC power transfer stage of inductive charging circuit                                |

| Fig. 4.2 Inductive power transfer technique principle of operation                                        |

| Fig. 4.3 Basic compensation topologies (a) Series-Series (SS) (b) Series- Parallel (SP) (c)               |

| Parallel-Parallel (PP) (d) Parallel-Series(PS)                                                            |

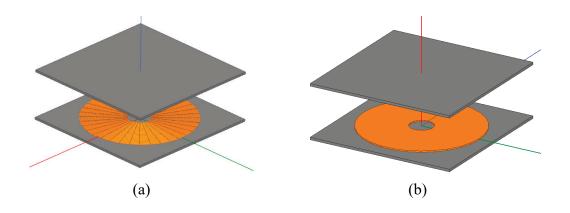

| Fig. 4.4 (a) Planar coil structure with spiral windings (b) Simplified coil model with                    |

| single-turn lumped model for finite element analysis (FEA)                                                |

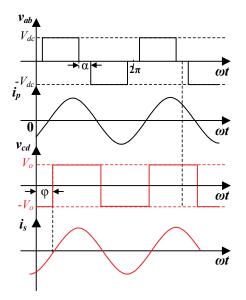

| Fig. 4.5 Key operating waveforms of DC-DC Converter                                                       |

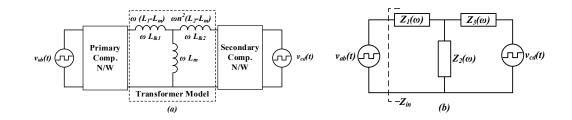

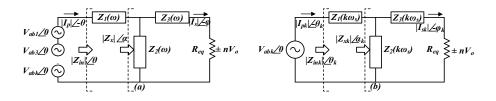

| Fig. 4.6(a) Generalized AC equivalent circuit (b) Simplified equivalent model76                           |

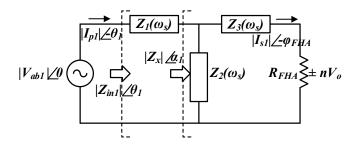

| Fig. 4.7 FHA model for wireless DC-DC converter77                                                         |

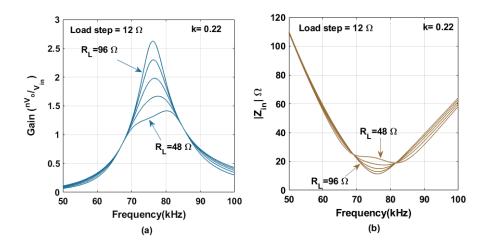

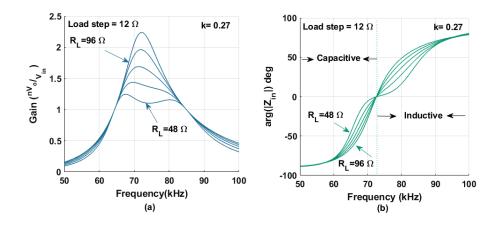

| Fig. 4.8 Frequency characteristics of IPT system designed (a) Voltage gain <i>GnFHA</i> (b)               |

| Magnitude of input impedance $ Zin $ (c) angle of input impedance $< Zin80$                               |

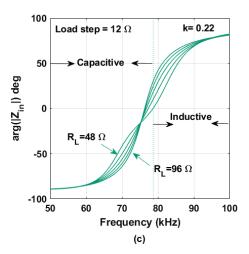

| Fig. 4.9 Normalized DC gain curve for SS compensated System                                               |

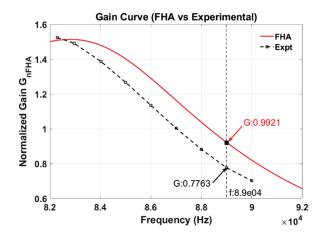

| Fig. 4.10(a) Generalized Extended Harmonic Model (b) k <sup>th</sup> harmonic model 83                    |

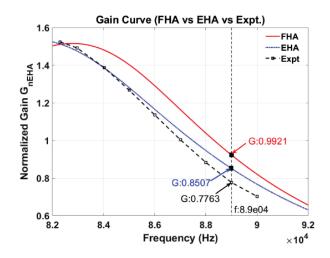

| Fig. 4.11 Normalized DC gain curve comparison for SS compensated system                                   |

| Fig. 4.12 Frequency characteristics of initial IPT system (a) Voltage gain GnFHA (b)                      |

| angle of input impedance < <i>Zin</i>                                                                     |

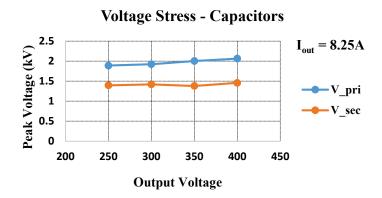

| Fig. 4.13 Voltage stress evaluation on resonant capacitors                                                |

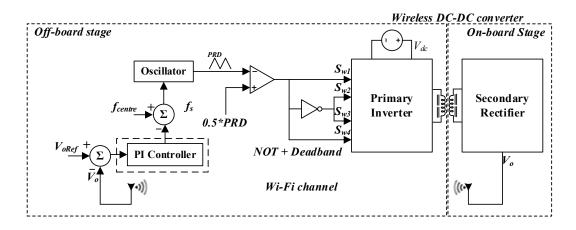

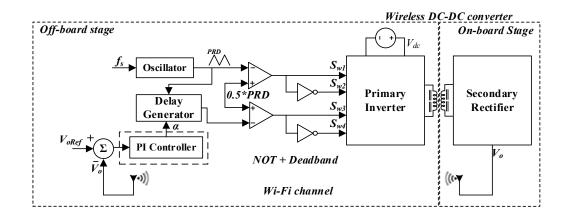

| Fig. 4.14 Control block diagram for PFM92                                                                 |

| Fig. 4.15 Control block diagram for primary side phase control                           |

|------------------------------------------------------------------------------------------|

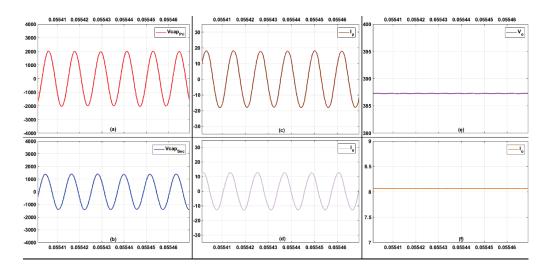

| Fig. 4.16 Wireless DC-DC simulation using initial parameters @ 85 kHz (a) Primary        |

| resonant capacitor voltage (b) Secondary resonant capacitor voltage (c) Primary tank     |

| current (d) Secondary tank current (e) Output voltage (f) Output current                 |

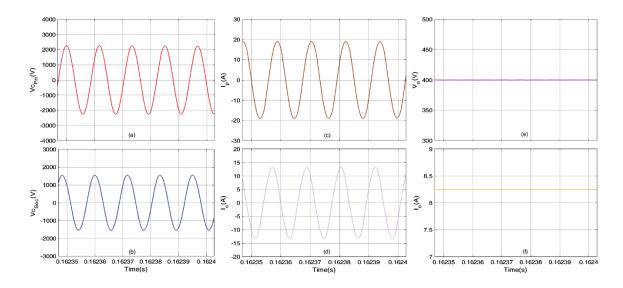

| Fig. 4.17 Wireless DC-DC simulation based on laboratory prototype @ 85 kHz (a)           |

| Primary resonant capacitor voltage (b) Secondary resonant capacitor voltage (c) Primary  |

| tank current (d) Secondary tank current (e) Output voltage (f) Output current            |

| Fig. 4.18 Initial laboratory prototype of wireless DC-DC converter                       |

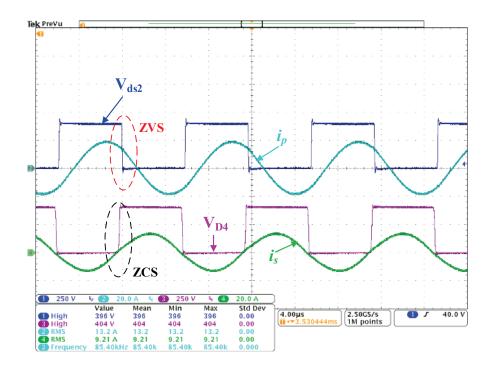

| Fig. 4.19 Key Operating waveforms of wireless DC-DC stage                                |

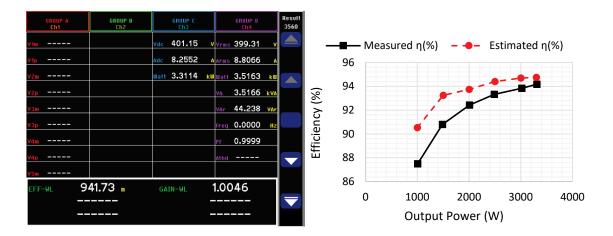

| Fig. 4.20(a)Efficiency measurement from Tektronix power analyzer (b)Estimated vs         |

| Measured efficiency over load range                                                      |

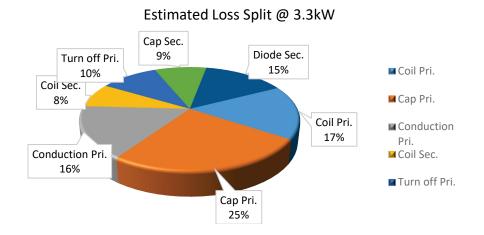

| Fig. 4.21 Wireless DC-DC converter estimated loss split @ 3.3kW 100                      |

| Fig. 5.1 Proposed analog SR block diagram                                                |

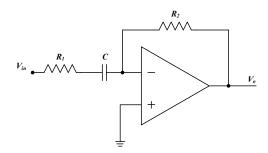

| Fig. 5.2 Proposed lead compensation network 105                                          |

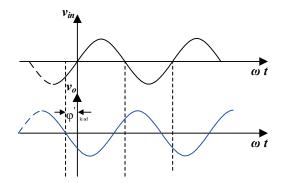

| Fig. 5.3 Key operating waveforms of the proposed compensation network 106                |

| Fig. 5.4 Phase relationship between input and output waveform of proposed lead           |

| compensator                                                                              |

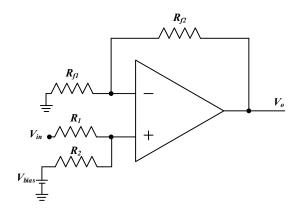

| Fig. 5.5 Non-inverting summing amplifier circuit                                         |

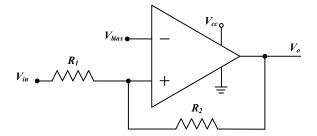

| Fig. 5.6 Analog comparator circuit with hysteresis band 110                              |

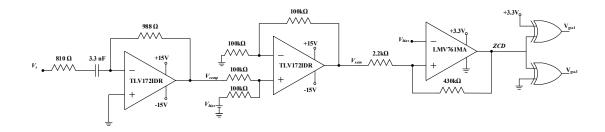

| Fig. 5.7 Schematic diagram of the proposed analog synchronization circuit 113            |

| Fig. 5.8 Experimental prototype of proposed analog SR stage 113                          |

| Fig. 5.9 Wireless DC-DC equivalent circuit with active rectification                     |

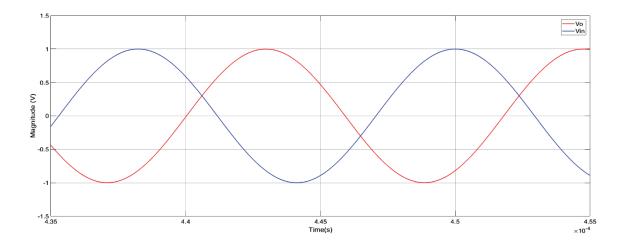

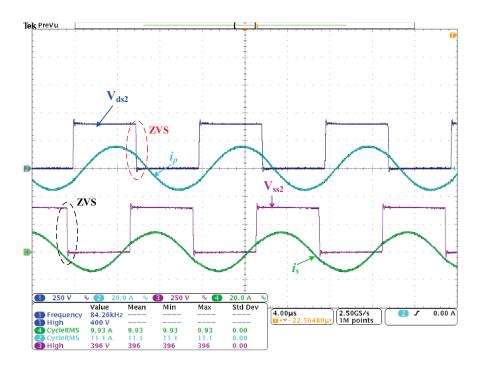

| Fig. 5.10 Key operating waveforms of wireless DC-DC stage with active rectification 114  |

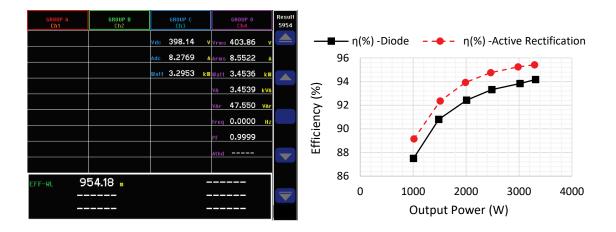

| Fig. 5.11 (a) Power analyzer measurements (b) Efficiency comparison between wireless     |

| DC-DC stage with diode rectification and proposed active rectification 115               |

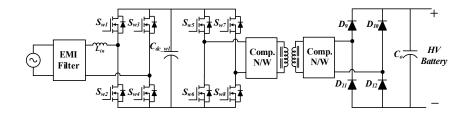

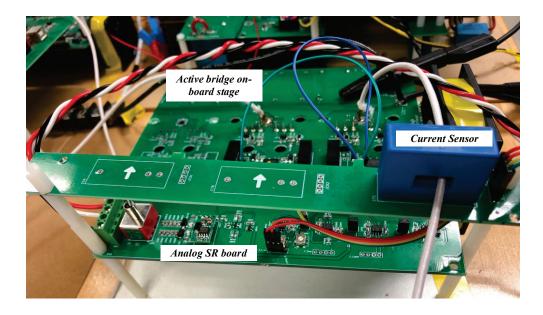

| Fig. 5.12 System level implementation of charging solution III 116                       |

| Fig. 5.13 Equivalent circuit of operation for wireless charging mode of solution III 116 |

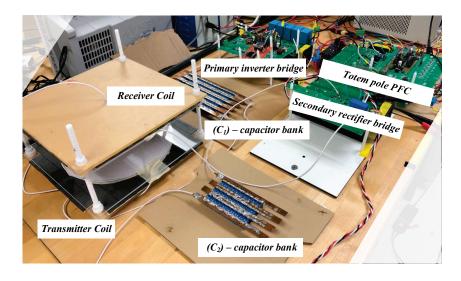

| Fig. 5.14 Test setup for verification of integrated charging solution 11           | 7 |

|------------------------------------------------------------------------------------|---|

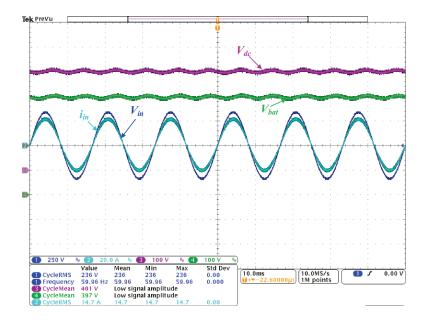

| Fig. 5.15 Key operating waveforms of integrated wireless DC-DC stage with OBC 11   | 7 |

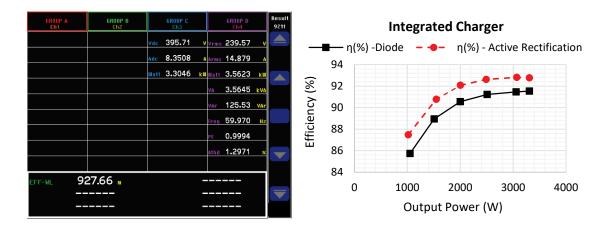

| Fig. 5.16 (a) Efficiency measurement from power analyzer (b) Efficiency comparison |   |

| between integrated charger employing diode rectification with charger employing    |   |

| proposed active rectification11                                                    | 9 |

## List of Tables

| Table 1.1 EVSE Classification in North American market [1]       4                 |

|------------------------------------------------------------------------------------|

| Table 1.2 J2954/1 proposed WPT Power classes for inductive charging [8]       5    |

| Table 3.1 Key charger specifications                                               |

| Table 3.2 Key characteristics of topologies under evaluation       41              |

| Table 3.3 Inductor design constraints    44                                        |

| Table 3.4 Final designed inductor with loss analysis    45                         |

| Table 3.5 Switching loss estimation    48                                          |

| Table 3.6 Loss comparison of PFC topologies under evaluation       49              |

| Table 3.7 Mathematical Expressions for half cycle operation       50               |

| Table 4.1 Parameters of reference coil developed in lab    73                      |

| Table 4.2 Equivalent Model Parameters for basic compensation topologies         76 |

| Table 4.3 Initial parameters for IPT system design    89                           |

| Table 4.4 Final resonant tank parameters    90                                     |

| Table 4.5 IPT System parameters for laboratory prototype                           |

| Table 4.6 Key Components enabling lab prototype development       96               |

| Table 4.7 Parameters generating major loss in Wireless DC-DC stage       99        |

| Table 5.1 Compensation parameters required to generate $\varphi$ lead' 107         |

| Table 5.2 Truth table for XOR based control signal generation                      |

| Table 5.3 Key components selected for SR design                                    |

| Table 5.4 Key parameters of system under test    118                               |

## **Chapter 1: Introduction**

## 1.1 <u>EV Market</u>

Dynamic market acceptance of electric vehicles has ensued in recent years leading to a global stock of 3.1 million electric passenger cars in 2017, an increase of 57% from the previous year [1]. The global EV market spurt is facilitated by supporting policies deployed by governments and cities to reap multiple benefits in the fields of transport decarbonization, air pollution reduction, energy efficiency and security[2]. Increased sales volumes together with growing competition in the development of new technologies act as motivating factors for continuous reductions in the cost of manufacturing key components of an EV. Cost reductions in EV-related technologies further support their affordability compared with internal combustion engine vehicles.

## 1.2 EV Architecture

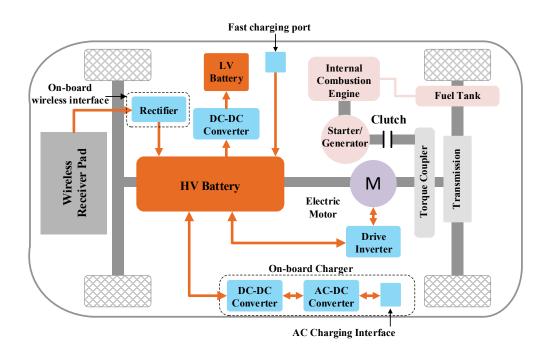

In comparison to conventional gasoline vehicles, EVs are typically powered by one or more electric motors as an alternative to an internal combustion engine (ICE). Large battery packs are used in EVs to store electric energy and are energized from the grid through plugin charging systems. Hybrid electric vehicles (HEVs) can be powered by both fossil and electric energies. Typically, an ICE and an electric motor with a battery pack are included in HEVs. The battery pack is charged through the ICE, not the grid, therefore, HEVs do not have plug-in charging systems[3].Plug-in hybrid electric vehicles (PHEVs) also have both ICE and electric motors. However, in comparison to HEVs, the battery pack of PHEVs can be charged through both the ICE and the grid. Therefore, plug-in charging systems are required in PHEVs. A figurative PHEV power system architecture is presented in Fig. 1.1, which consists of an electric motor, a drive inverter, a high voltage (HV) battery pack, a 12 V low voltage (LV) auxiliary battery, onboard charger (OBC) and wireless charging interface. Furthermore, an internal combustion engine is present on-board fueled by gasoline and attached to the axle through a torque coupler [4]. The electric motor serves a dual purpose in this architecture namely propulsion and regeneration. In propulsion mode, the electric motor propels the vehicle with the help of energy stored in the HV battery. The drive inverter transforms dc output of the battery to the required AC input to drive the motor. In regenerative mode, the motor acts as a generator recovering the breaking power and storing it in the HV battery. Thus the drive inverter operates in a bidirectional fashion as shown in Fig. 1.1 below.

Fig. 1.1 Power electronic interfaces onboard a plug-in hybrid vehicle

A LV battery of 12V is also typically present on-board the vehicle which supplies the auxiliary loads such as air conditioning system, music system, mobile chargers, lights and

control interfaces of various on-board elements. In case of gasoline engines the starter/generator charges the auxiliary battery during propulsion while in electric vehicles there is additional on-board dc-dc converters present which facilitate high voltage to low voltage power conversion in a unidirectional fashion.

Conventionally, an on-board wired charger is an essential component of an EV aiding the charging of the main traction battery. The two charging interfaces on-board the vehicle are presented in Fig. 1.1 categorized as (i) AC charging and (ii) DC fast charging. The various classification of charging levels and the corresponding standard [1] used by electric vehicle supply equipment (EVSE) in North America are presented in Table 1.1.

Typical OBCs available in market are Level 1 or Level 2, they use the on-board AC-DC interface to convert the input single phase grid voltage to HV battery voltage typically in the range of 400V. Since, the battery voltage is dependent on the state of charge (SOC) the on-board charger needs to regulate the output voltage to variable battery voltage specifications while isolated from the grid. Furthermore, due to addition of on-board interfaces for power conversion the weight and volume of these chargers have to be minimized to increase the electric range of the vehicle. In this regards, multiple topologies have been proposed to integrate on-board power electronic interfaces [5].

Newer vehicles are equipped with DC fast charging capabilities which supplies a large amount of dc current directly to battery charging at very fast rates. The AC-DC conversion stage for DC fast chargers are placed off-board the vehicle and requires additional infrastructure to enable this charging. Even though a DC fast charger is very convenient for charging it requires a huge financial investment for widespread deployment [5].

|              | Conventional<br>Plugs | Slow Chargers              | Fast Chargers                       |                                                |

|--------------|-----------------------|----------------------------|-------------------------------------|------------------------------------------------|

| Level        | Level 1               | Level 2                    | Lev                                 | vel 3                                          |

| Current      | AC                    | AC                         | AC, triphase                        | DC                                             |

| Power Rating | $\leq$ 3.7 kW         | $\leq$ 22 kW               | >22kW and<br>≤43.5 kW               | Currently < 200 kW                             |

| Plug Type    | SAE J1772 Type<br>1   | SAE J1772<br>Type 1, Tesla | SAE J3068<br>(under<br>development) | CCS Combo<br>1 (SAE J1772<br>& IEC 62196-<br>3 |

Table 1.1 EVSE Classification in North American market [1]

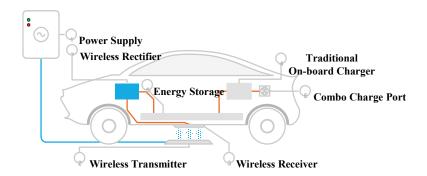

Recently wireless charging of EVs has gained popularity due to its safety, convenience, and compatibility with fully autonomous driving technology [6]. Wireless charging typically employs either near field or far field electromagnetic (EM) fields for energy transfer. Far field EM power transfer is employed for long distance transmission while EVs typically employ near field power transfer as the air gap distance is less than a couple of centimeter's [7]. The typical on-board components of a wireless charging system are illustrated in Fig. 1.1. A receiver pad is attached to the vehicle which receives power from a transmitting pad through inductive or capacitive field that generates AC voltage. The received voltage is rectified with the help of an on-board rectifier to charge the HV battery. Similar to conductive charging solutions wireless standards are under development to define power levels, classify the efficiency requirements as well as provide guidelines for interoperability between various charging structures [6] - [8]. Table 1.2 summarizes the key requirements imposed by the SAE J2954/1 standard which is under improvement. The

different structures enabling wireless charging will be comprehensively reviewed in the following section.

| Characteristics                                                     | WPT Power Class |         |              |        |

|---------------------------------------------------------------------|-----------------|---------|--------------|--------|

|                                                                     | WPT1            | WPT2    | WPT3         | WPT4   |

| Maximum<br>input volt amps                                          | 3.7 kVA         | 7.7 kVA | 11.1 kVA     | 22 kVA |

| Minimum<br>efficiency<br>target                                     | >85%            | >85%    | >85%         | TBD    |

| Minimum<br>target<br>efficiency at<br>offset position               | >80%            | >80%    | >80%         | TBD    |

| Frequency85 kHz within international frequency band (81.38 – 90 kHz |                 |         | 38 – 90 kHz) |        |

*Table 1.2 J2954/1 proposed WPT Power classes for inductive charging* [8]

## 1.3 Charging Structures

The various on-board charging interfaces of a conventional electric vehicle equipped with both wireless and conductive charging stages is presented in Fig. 1.2.

Fig. 1.2 Typical charging elements of an EV equipped with conductive and inductive charging

## 1.3.1 Conductive charging

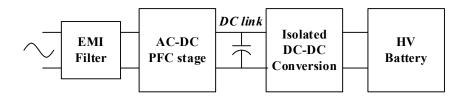

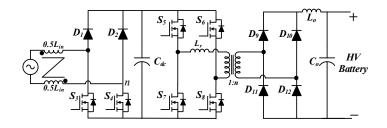

A typical EV charger configuration is shown in Fig. 1.3 which consists of an AC-DC power factor correction (PFC) stage in cascade to an isolated DC-DC converter. The front-end PFC circuit aids in achieving a unity power factor (PF) at the grid side while regulating the output DC voltage to a specified value. Researchers have tried to improve the performance of this stage by proposing different topologies and control techniques[9]- [10]. The most widely accepted PFC topology adopted in single-phase OBCs are boost-derived PFCs due to their continuous input current characteristics and superior EMI performance, compared to buck-derived PFC topologies whose EMI filters are usually bulky with high losses due to the discontinuous input current operation.

Fig. 1.3 Typical structure of on-board charger

An isolated DC-DC stage is necessary to provide isolation between grid and HV battery. Two classes of topologies are widely used for this purpose, (i) Pulse Width Modulated (PWM) converters including phase-shifted full bridge converter (PSFB) and dual-active full bridge converter (DAB) (ii) Pulse frequency modulated (PFM) converters comprising of different styles of resonant converters like LLC, LCC, CLLC. These converters operate with a fundamental difference in control technique but share several common characteristics such as capability of wide gain operation, ability to achieve soft switching technique namely zero voltage switching (ZVS) for MOSFETs. A high efficiency two stage vehicle charger with bridgeless boost PFC circuit in cascade with phase shifted full bridge structure shown in Fig. 1.4 was developed by researchers in [11]. The proposed charger is unidirectional due to the secondary diode bridge but can easily be made bidirectional by replacing with a synchronous rectified bridge. The unidirectional charger proposed achieved a peak efficiency of 95% while operating at 200 kHz.

Fig. 1.4 High efficiency vehicle charger proposed in [11]

A 97.2% efficiency is recorded for the isolated DC-DC conversion stage for a bidirectional PWM resonant converter proposed by researchers in [12] for EV charging application. The modified PWM resonant converter structure is presented in Fig. 1.5.

Fig. 1.5 Bidirectional PWM resonant converter proposed in [12]

Researchers in [13] have proposed a dual stage structure with interleaved totem pole PFC in cascade with a half-bridge CLLC converter as a feasible solution for OBC. The proposed OBC structure is presented in Fig. 1.6, where the use of a variable dc link voltage improves overall efficiency of the circuit. The proposed circuit claims a peak efficiency of over 94% at 2 kW output.

Fig. 1.6 Dual stage OBC structure proposed by researchers in [13]

Additionally, multiple bidirectional resonant converters suitable for OBC design with variable dc link voltage are proposed by researchers in [14]. An electrolytic capacitor-less bidirectional structure employing harmonic compensation was proposed by researchers in [15] for power dense OBC design.

## 1.3.2 Inductive charging

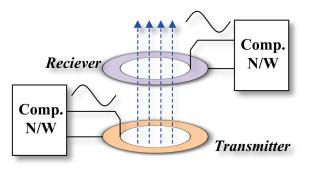

The inductive power transfer (IPT) system uses the near field magnetic resonance principle to transfer power wirelessly from a transmitter pad to a receiver pad with large air gap.[16] A typical block diagram representation of the various stages involved in an IPT system is illustrated in Fig. 1.7.[17]

Fig. 1.7 Typical structure of an IPT system for EV charging

The off-board components designated in Fig. 1.7 facilitate the conversion of grid voltage AC to an intermediate DC voltage which is converted to a high frequency AC (HF-AC) voltage to be magnetically coupled with the on-board components. The AC-DC conversion stage is similar to the front-end PFC stage of a conductive charger. The topologies

discussed in the previous section are equally appropriate for design of this system. Detailed review and topology selection for this stage is carried out in Chapter 3.

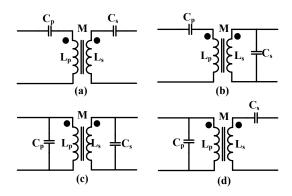

Figure 1.8 summarizes the most common structure used by researchers for IPT charging system for EV[16], [18]–[22]. The basic structure uses an active front end rectifier followed by a voltage fed high frequency inverter. Various compensation topologies are employed to improve the power transfer capability as well as the tolerance of the system to misalignment conditions [23]–[26]. A detailed analysis of various basic compensation topologies is carried out in chapter 3. Different coil structures are also proposed by researchers to improve the coupling between the coils while reducing the weight and size of coil. [22], [27]–[31]. The secondary side of the wireless stage uses a diode bridge to rectify the high frequency AC voltage generated from the receiver to charge the battery.

Fig. 1.8 IPT system employing a dual stage structure with voltage fed high frequency inverter network

An alternative topology for high frequency DC-AC conversion using current fed inverter is proposed by researchers in [32], [33]. The current topology inherently provides lower current stress and short circuit protection. The main disadvantage of this topology is the use of a large inductor at the input side to generate the current source leading to increased volume, additional losses and increased cost of the system[6], [32]. The current fed structure also requires an on-board rectification stage to convert high frequency AC - DCin order to charge the battery.

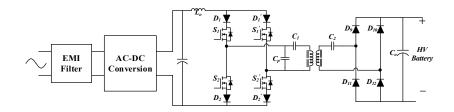

*Fig. 1.9 IPT system employing a current source fed high frequency inverter*[32]

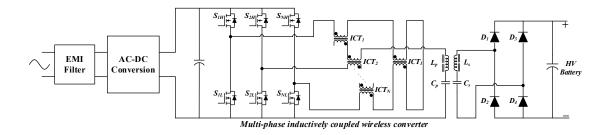

A topology employing a multi-phase series connected converter to power an IPT system was proposed by researchers in [34] capable of enabling high power IPT solutions. The proposed system can be extended to an n-phase input with a series connected output current transformer which can individually control the phase of each leg to facilitate soft switching operation. The system is compensated with a series-series (SS) structure. On the output side of the converter a bridge rectifier is used to convert the high frequency AC back to DC. Even though the proposed system is feasible for high power applications it requires multiple current transformers as well as a complex phase shifting control technique increasing the overall cost of the system [6].

Fig. 1.10 IPT charger employing multi-phase inductively coupled wireless converter[34]

## 1.3.3 *Capacitive charging*

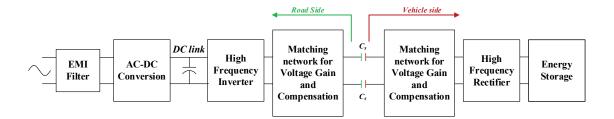

A capacitive power transfer (CPT) system is an alternative structure employing the near field magnetic resonance principle to transfer power wirelessly from a transmitter pad to a receiver pad with large air gap. A typical block diagram representation of the various stages involved in an CPT system is illustrated in Fig. 1.11 [35].

Fig. 1.11 Typical structure of a CPT system for EV charging

The vehicle side components designated in Fig. 1.11 facilitate the conversion of grid voltage AC to an intermediate DC voltage which is converted to a high frequency AC (HF-AC) voltage to be capacitievly coupled to the vehicle side components. The AC-DC conversion stage is similar to the front-end PFC stage of a conductive charger but present off-board the vehicle. Since, the capacitance formed by parallel plate structures is very low in value multi-MHz frequency operation is required for enabling resonant power transfer.

Fig. 1.12 CPT structure presented by researchers in [35]

Fig. 1.12 presents the CPT topology proposed by researchers in [35] capable of transferring 589W of power across an air gap of 12 cm with the help of a 6.78MHz switching operation. The proposed topology uses an H-bridge structure at the input inverter stage along with a LCC compensation network providing soft-switching characteristics to reduce switching losses at high frequency operation. The power transferred through the electric field in an air gap generates the secondary current which is rectified with the help of a diode rectifier to supply the high voltage battery.

Fig. 1.13 CPT structure presented by researchers in [36]

A double sided LCC compensation based CPT system was proposed by researchers in [36]. The proposed system has reported efficiency of 90.8% for dc-dc stage alone at an air gap of 150mm when transferring 2.4kW power. The proposed converter uses a switching frequency of 1MHz with coupling capacitive pads of 610mm x 610 mm in size. In this thesis, a CPT system is not considered for integration with conductive charger majorly because of the multi-MHz operation requirement which enforces more modification to on-board components for efficient operation. Additionally, the CPT system depends on the permittivity between the metal plates which could potentially be affected by the presence of environmental factors such as humidity.

#### 1.4 <u>Thesis Objectives</u>

Currently wired charging is the customary method of delivering electric energy to the storage elements present onboard of EVs. Thriving inclination towards design of autonomous vehicles have shaped wireless charging as an attractive solution in favor of complete autonomy. Until the wireless charging infrastructure as well as interoperability standards are completely developed, wired and wireless chargers have to co-exist onboard the vehicles for user convenience. Current solutions for wireless charging requires additional components onboard the vehicle leading to increased size, weight and volume.

Incorporation of an entire parallel wireless charging system on-board an EV, either during manufacture or after-market shrinks the electric range of vehicle.

The need for co-existence of power electronic interfaces for wired and wireless chargers onboard the vehicle leads to an opportunity to develop integrated solutions. Typical OBC configuration includes an active bridge which can potentially act as a rectifier stage of wireless system. This removes the need of additional power electronics onboard the vehicle for wireless power conversion, as well as reduces cooling and cabling requirements of wireless system.

Subsequently, the major research problems on which research effort has been focused in this work are briefly as follows:

- Development of novel integration architectures to combine conductive and inductive charging system for electric vehicles

- Conducting optimized designs for different integral power conversion stages i.e. (i)

off-board components including power factor correction rectifier, primary side

wireless compensation network, inductive coil and (ii) vehicle onboard components

including a secondary side compensation network and a rectifying stage.

- An extended harmonic analysis (EHA) method for analyzing the inductive power transfer system with multiple resonant frequencies, which will lead us in obtaining the voltage gain and calculating the component stresses of the wireless stage with higher accuracy at an operating frequency different from either of the resonant frequencies.

- Development of a novel analog circuit based phase synchronization method, which controls the switching of the devices of the onboard rectifying stage and ensures

zero voltage switching (ZVS) of all the devices without adding any sampling error based complexity unlike a digital controller and facilitates enhancement of power stage conversion efficiency.

## 1.5 Major Contributions

The main contributions of this research work are as listed below

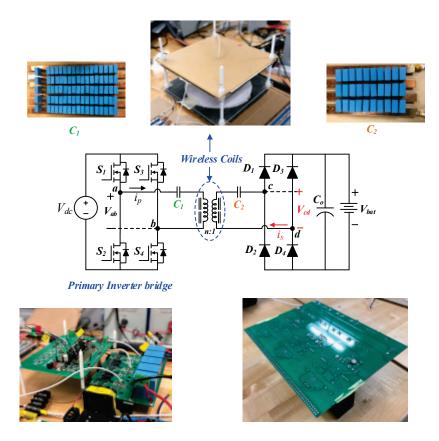

- Three novel architectures capable of integrating on-board components of wireless chargers to the existing wired chargers are proposed. Among the proposed solutions, solution III is selected to evaluate the system in laboratory as it require minimum power conversion stages.

- 2) A comprehensive loss evaluation of various bridgeless power factor correction (PFC) circuits are carried out to select an off-board AC-DC conversion stage for the development of a 3.3kW integrated charging structure. The totem pole PFC structure exhibits minimum loss for 3.3 kW operating condition and hence is selected for implementation. A detailed small signal averaged model including the effects of series resistance in input inductor and output capacitor is developed to design the dual loop control structure. As a proof of concept, a laboratory prototype of the totem pole PFC is built, which achieves a full load efficiency of 97.39% while drawing input current with a power factor of 0.9993 and THD of 2.08% at a nominal grid voltage of 240  $V_{rms}$ .

- 3) A wireless DC-DC stage capable of transferring 3.3 kW over an air gap of 10cm is developed in lab to evaluate the proposed charging system. A set of wireless coils using ferrite back plates are designed and manufactured in lab based on ANSYS Maxwell simulations. An EHA based modeling approach is used to analyze the

stress of various resonant components. The designed passive rectification based wireless DC-DC stage achieves a full-load efficiency of 94.2%

- 4) To improve the overall efficiency of proposed charging system an analog synchronous rectification circuit is proposed which uses secondary side sensed current to auto synchronize the active bridge of on-board charger. The proposed synchronization structure can enable secondary ZVS operation by generating programmed phase lead. To evaluate the improvement in efficiency by using the proposed analog circuit, a wireless DC-DC with active rectification is implemented which achieves a full load efficiency of 95.42 %. An efficiency improvement of >1.25% is achieved by active rectifier based solution compared to passive rectification over the load range.

- 5) Finally, the proposed integrated wireless charger is implemented using various building blocks developed by this work. A laboratory prototype is realized to evaluate the overall system characteristics. The integrated wireless charger was able to transfer 3.3kW power from grid to load with a conversion efficiency of 92.77% while drawing input current with a power factor of 0.9994 and 1.3% THD.

## 1.6 Synopsis of the dissertation

In Chapter 2, a comprehensive review of existing integrated conductive and inductive charger solutions are carried out. Multiple integration architectures capable of on-board topological integration of conductive and inductive chargers are proposed. Furthermore, system level implementation structures based on the proposed architectures are introduced. In Chapter 3, the key design considerations of an off-board input rectification stage for the proposed integrated chargers are introduced. A comprehensive review of various active

front end converters is carried out; a critical loss comparison study is completed to select the most suitable topology for the charger specifications. Detailed small single modeling of the selected topology is carried out to design a suitable control structure capable of meeting the charger requirements. A laboratory prototype of the selected single phase rectifier is implemented and evaluated to validate the proposed solution.

In Chapter 4, the overall design of a wireless dc-dc stage is presented, where a brief introduction to IPT technology as well as a comprehensive review of various compensation structures are carried out to select a suitable compensation topology for the proposed charger. The design of charging coils or pads form a critical component in enabling an IPT system. Hence, various coil structures are reviewed and a suitable topology is selected for implementing laboratory level prototype based on design specifications. In order to design the compensation network a system level modeling of the wireless dc-dc conversion stage is carried out with the help of a fundamental harmonic approximation (FHA) technique. The inaccuracies in the developed system based on FHA model led to the development of a novel extended harmonic approximation (EHA) modeling method for accurate design of an IPT system. A laboratory prototype of the wireless DC-DC stage is developed and evaluated to substantiate the proposed design.

In Chapter 5, an analog synchronous rectification circuit is proposed to enable active rectification of wireless on-board rectifier. The proposed solution eliminates the need of any onboard microcontroller or high frequency synchronization signal transmission from the primary side to enable active rectification. As a proof of concept verification, a laboratory prototype is developed and assessed to quantify the improvement in system

efficiency. Additionally, an integrated wireless charger proposed in Chapter 2 is successfully built and evaluated to demonstrate the feasibility of the proposed solution.

Finally, in Chapter 6, relevant conclusions from the research work performed are summarized and several future research topics for further performance enhancement of the proposed charging structures are discussed in brief.

## **Chapter 2: Integrated wireless charging system architecture**

## 2.1 <u>Background review of existing integrated charging solutions</u>

The strict volume and weight requirements imposed by automobile industry has always favored integration of components onboard the vehicle. The trend for integration is a potential reason for proposing the concept of an integrated wireless/onboard charger solution with a smaller battery pack reducing cost and weight of vehicle as a potential future trend [37]. Active research is being carried out by industries and research groups to develop such an integrated wireless charging solution.

Tesla Motors, Inc. currently holds a patent [38]for integration of inductive and conductive charging system with two different architectures. Fig. 2.1 illustrates a generalized block diagram from [38] where the integration takes place at the output stage of converter. The inductive and conductive system are two independent system without any reduced components leading to high volume requirement. The output battery can be simultaneously charged by both methods leading to a higher charging rate but at the expense of more cost and weight of charging system.

Fig. 2.1 Integrated configuration 1 proposed in [38]

An alternative solution is proposed in patent [38] as presented in Fig. 2.2 which integrates the output of wireless stage to the isolation transformer of conductive stage with help of power connectors and contactors. They have proposed the use of primary stage diode bridge to charge the output battery. The use of diode bridge as well as no provision for compensation network for wireless charging path will lead to a very low operation efficiency.

Fig. 2.2 Integrated configuration 2 proposed in [38]

Fig. 2.3 illustrates the integration of the wireless rectifier stage to the drive train boost converter as proposed by researchers in [39]. The proposed wireless system requires additional diodes to be included in the drive train circuit and leads to lower efficiency due to the conduction loss. Additionally the conductive charging system is still on-board the vehicle as an independent solution.

Fig. 2.3 Integrated configuration proposed in [2-3]

An alternative integration solution proposed by researchers in [40] illustrated in Fig. 2.4 uses a coupled magnetic structure that integrates the isolation transformer of plugin charger and receiver coil of inductive system. The coupled design leads to constrained parameters for both conductive and inductive charging system reducing the range of operation. Moreover, the design of isolation transformer for plugin charger with the help of ferrite plate structure leads to a lower coupling than a conventional transformer if proper design constrains are not met. Non-optimized design of transformer due to additional constraints introduced by wireless integration can impact the overall efficiency of conductive charging system.

Fig. 2.4 Integrated configuration proposed in [2-4].

#### 2.2 <u>Proposed Integrated Wired and Wireless Charging Architecture</u>

In this thesis, we propose a topological integration solution with existing onboard charger that reuses the existing components onboard and facilitate conductive and inductive charging independently. The aim of this charging integration is to reduce the overall weight and volume of required power electronics components onboard the vehicle. The proposed charging architecture can be classified into three different solutions based on the position of integration.

# 2.2.1 Solution I

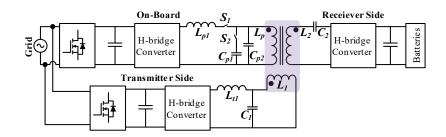

Fig. 2.5 illustrates the proposed integration solution I of inductive and conductive charging system with the help of an interfacing circuit. The interfacing circuit that helps to bridge the inductive and conductive charging system is introduced before the isolated switching rectifier stage. The inductive charger reuses the switching elements of isolated switching rectifier to convert the high frequency AC output from compensation network to DC to be supplied to the energy storage element.

Fig. 2.5 Proposed Integration solution I at power factor correction stage of onboard charger

The main components of charging system deployed on-board vehicle as a part of Solution I are

<u>Input filtering stage</u>: The input from grid is connected to an EMI filtering stage of onboard stage using charging interface meeting SAE J1772 standard for grid connected system. The filtering stage may additionally include passive storage, decoupling elements required for operation of the circuit. This stage is mandatory for all the solutions proposed above to meet the current quality requirements. In Solutions II and III this stage is merged with the input conditioning stage.

*Interfacing circuit*: The interfacing circuit which acts as a bridge between inductive and conductive stage uses a combination of relays and connectors to provide the necessary

isolation required for independent operation of individual chargers. The interfacing circuit that helps to bridge the inductive and conductive charging system is introduced before the isolated switching rectifier stage for solution I.

<u>Isolated switching rectifier</u>: This stage acts as the main power factor correction (PFC) circuit which helps in rectifying AC input from grid to DC output with isolation. The major requirement of this stage for the proposed integration solution is presence of a rectifying bridge structure to act as secondary receiving side of inductive stage. Different combination of circuits could be used as a potential solution for this stage. Proposed solutions could be single stage or dual stage which meets the requirement of isolation and rectifying bridge structure.

<u>Output conditioning circuit</u>: The output of the isolated switching rectifier stage is connected to a conditioning circuit that can be passive or active depending on the requirement of energy storage device. The passive components could be capacitive or inductive in nature. Active circuits may include and is not limited to active buffering circuits or additional step up or step down converters to provide necessary voltage transformation.

<u>On-Board Controller</u>: An onboard controller provides the necessary switching signals to the interfacing circuit and rectifier circuit based on feedback signals from various sensors in circuit. The control logic depends on the isolated switching rectifier topology selected and may use different techniques such as pulse width modulation (PWM) control, pulse frequency modulation (PFM) control, phase shift modulation control or a hybrid structure including one or more control schemes based on requirement of charger. Additionally wireless communication channels maybe integrated to the system to provide communication between off board and on board systems.

<u>Analog Control logic</u>: Additional analog control logic maybe included to existing onboard chargers or could be integrated to onboard controller for providing control signals to bridging circuit for efficient operation of inductive charger. Analog circuit includes current sensors, high speed comparator circuit, buffer interface, signal multiplexer, gate drive circuits and necessary interfacing connectors depending on selected topology.

<u>*Comp. N/W*</u>: Compensation network is a crucial component for on-board as well as offboard stages of wireless system to improve the power transfer ability by proper compensation logic. The compensation network may include passive component such as inductors and capacitors or active components that vary the effective impedance based on additional control logic.

<u>Receiving Coils</u>: Wireless receiving coils are placed on-board which is connected to the interfacing circuit through the compensation network. Different structures of wireless coils are possible based on the requirements of design.

*Energy Storage*: Energy storage element to be supplied could be a single battery source or a combination of different configuration of sources based on the selected topology.

Similarly, Off-board components are required for the operation of inductive stage which mainly includes

<u>Input conditioning & Switching Inverter stage</u>: The AC voltage from grid is converted to DC to be supplied to the switching inverter with the help of this circuit. This stage includes conditioning circuit such as EMI filter, storage elements and necessary switching elements to provide the voltage conversion. In case of a dual stage cascaded structure the input

conditioning stage deals with PFC operation while the inverter stage provides the necessary DC to AC voltage conversion at higher frequency. The switching inverter stage could be potentially integrated to the input conditioning stage in a single stage structure and can energize wireless transmitting coils through compensation network.

<u>*Transmission Coils*</u>: Wireless transmitting coils are placed off-board which is connected to primary grid through compensation network and associated switching structure. Different coil structures are possible based on the requirements of design.

<u>Off-Board Controller</u>: An off-board controller provides the necessary switching signals to the input conditioning stage and switching inverter network based on feedback signals from various sensors in circuit. The control logic depends on the chosen topology and could potentially employ techniques such as pulse width modulation (PWM), pulse frequency modulation (PFM), Phase shift control or a hybrid control scheme using one or more schemes. Additionally wireless communication channels, positioning control systems maybe integrated to provide communication between off board controller and on board systems.

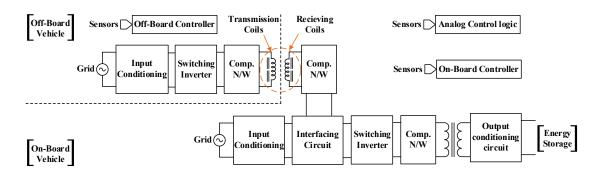

#### 2.2.2 Solution II

An alternate charging architecture (Solution II) is illustrated in Fig. 2.6, where AC output from receiving coil after compensation is supplied to the isolation transformer of conductive charger with the help of proper interfacing circuit structure. The proposed Solution II introduces additional level of isolation from grid stage but reduces the stages of power conversion improving conversion efficiency.

Fig. 2.6 Proposed solution II

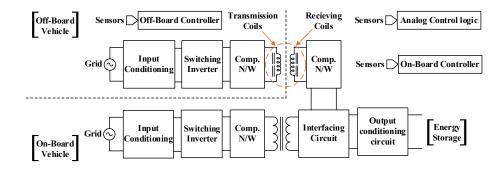

# 2.2.3 Solution III

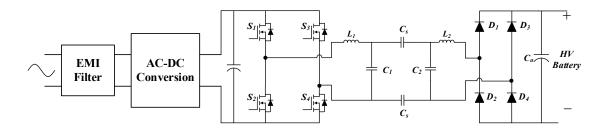

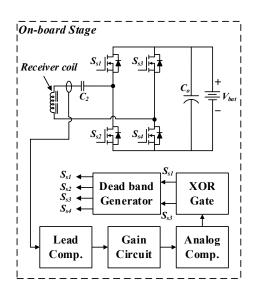

An extension to Solution II is presented in Fig. 2.7 .The proposed bridging is introduced after the isolation transformer of conductive charger. Solution III uses the output conditioning circuit rectification stage to converter the high frequency AC supplied from compensation network to DC.

Fig. 2.7 Proposed Integration solution III

The main components of the proposed solutions II and III are summarized below:

<u>Input Conditioning & Switching Inverter Stage</u>: The Isolated switching rectifier stage presented as a part of Solution I is decoupled into two parts for Solution II and Solution III. Input conditioning stage merges the PFC stage as well as the EMI filter and provide a grid interface to meet the required standards. The DC output of input conditioning stage is connected with the help of interface circuit to a switching inverter to generate high frequency AC signal. Alternatively a single stage structure could be used for Solution III where the switching inverter network is merged with input conditioning circuit and directly provides high frequency AC signal from input grid voltage.

<u>*Comp. N/W*</u>: Compensation network is an essential part of off-board and onboard stage, which helps in improving power transfer capability. This stage also helps in improving efficiency by introducing soft switching characteristics to the circuit. The compensation network may include passive component such as inductors and capacitors or active components that vary the effective impedance based on additional control logic.

*Interfacing circuit*: The interface circuit uses combination of relays, connectors and active devices to provide the necessary isolation required for operation of individual chargers. It may include passive compensation networks required as a part of conductive stage. The interfacing circuit is introduced before the isolation stage of the onboard charger topology in case of Solution II and hence inherently provides an extra level of isolation to the inductive stage. Alternatively, Solution III introduces bridging after the isolation transformer but removes the additional constraints on transformer design imposed by integration proposed in Solution II.

<u>Output conditioning circuit</u>: The output of the isolating transformer is connected to a conditioning circuit that can be passive or active depending on the requirement of energy storage device. The passive components could be capacitive or inductive in nature which can act as storage components or filtering components in case of resonant based structures. Active components may include active buffering circuits or additional step up or step down converters to provide necessary voltage transformation.

*Energy Storage*: Energy storage element to be supplied could be a single battery source or a combination of different configuration of sources based on the selected topology.

<u>On-Board Controller</u>: An onboard controller provides the necessary switching signals to the input conditioning stage, switching inverter and interfacing circuit based on feedback signals from various sensors in circuit. The control logic depends on the chosen topology and could potentially employ techniques such as pulse width modulation (PWM), pulse frequency modulation (PFM), Phase shift control or a hybrid control scheme using one or more schemes. Additionally wireless communication channels maybe required to provide communication between off board controller and on board systems for power flow control.

<u>Analog Control logic</u>: Additional analog control logic maybe included to existing onboard chargers or could be integrated to onboard controller for providing control signals to bridging circuit for efficient operation of inductive charger. Analog circuit includes a combination of sensors, high speed comparator circuit, buffer interface, signal multiplexer, gate drive circuits and necessary interfacing connectors depending on selected topology.

<u>Off-Board Controller</u>: An off-board controller provides the necessary switching signals to the input conditioning stage and switching inverter network based on feedback signals from various sensors in circuit. The control logic depends on the chosen topology and could potentially employ techniques such as pulse width modulation (PWM), pulse frequency modulation (PFM), Phase shift control or a hybrid control scheme using one or more schemes. Offboard controller integrates wireless communication channels along with position control systems to facilitate power flow control to vehicle systems. <u>*Transmission Coils*</u>: Wireless transmitting coils are placed off-board which is connected to primary grid through compensation network and associated switching structure. Different coil structures are possible based on the requirements of design.

<u>Receiving Coils</u>: Wireless receiving coils are placed on-board which is connected to the interfacing circuit through the compensation network. Different structures of wireless coils are possible based on the requirements of design.

#### 2.3 <u>System level implementation structures for proposed solutions</u>

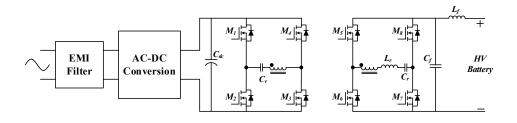

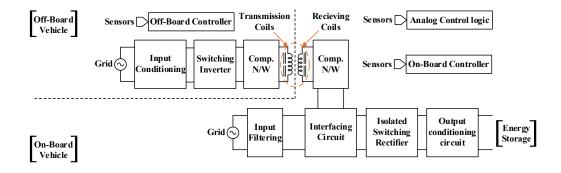

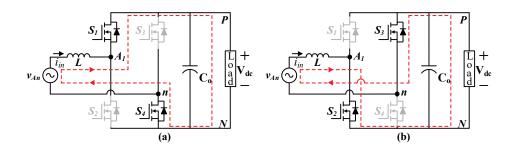

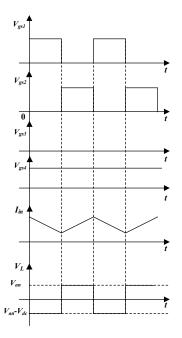

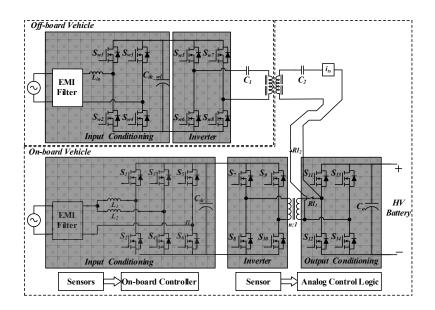

Fig. 2.8 presents one of the feasible topology derived from Solution I, where the selected isolated switching network is an interleaved totem pole PFC cascaded with a half bridge CLLC converter (HB-CLLC). The output of HB-CLLC converter is fed to a capacitor which acts as the output conditioning circuit. Inductive charger uses a dual stage cascaded converter, where again a totem pole PFC circuit acts as input conditioning stage followed by a full bridge switching inverter exciting the transmission coil through a compensation network. The receiving coil is powered by transmitting coil and supplies energy to a compensation network which is integrated to conductive stage with the help of interfacing relays  $Rl_1$  and  $Rl_2$ . The analog control logic supplies the necessary driving pulse to the input bridge for efficient operation of wireless rectifier. More detailed analysis and selection methodology will be presented in following chapter.

Fig. 2.8 System Level implementation of Solution I

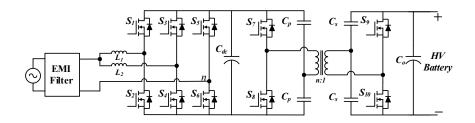

Solution II integrates the wireless charger at the isolation stage of conductive charger onboard the vehicle as presented in Fig. 2.9. The input conditioning stage of onboard charger uses an interleaved totem pole structure connected in cascade with the primary full bridge switching inverter of an a dual active bridge (DAB) converter. The secondary output bridge of DAB along with dc capacitor acts as the output conditioning circuit supplying the high voltage (HV) battery. Off-board stage of inductive charger uses a dual stage cascaded converter, where a totem pole PFC circuit acts as input conditioning stage followed by a full bridge switching inverter exciting the transmission coil through a compensation network. The receiving coil is powered by transmitting coil and supplies energy to a compensation network which is integrated to conductive stage with the help of interfacing relay  $Rl_2$ . An additional relay  $Rl_1$  is required to isolate the dc link of PFC circuit to prevent voltage buildup during operation of inductive circuit. The analog control logic supplies the necessary driving pulse to the input bridge for efficient operation of wireless rectifier. This solution introduces additional constraints in the design of DAB transformer as the magnetizing inductance and leakage inductance lies in active power path of inductive secondary circuit. Due to the constrained design this solution is not further pursued in the following chapter.

Fig. 2.9 System level implementation of Solution II

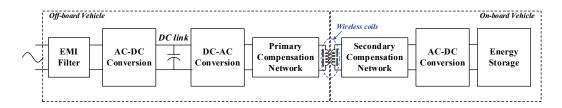

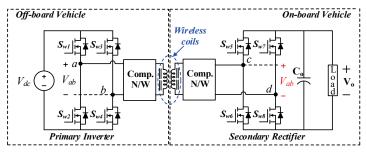

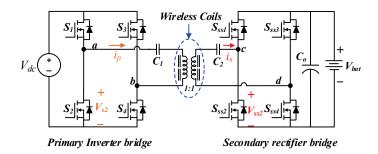

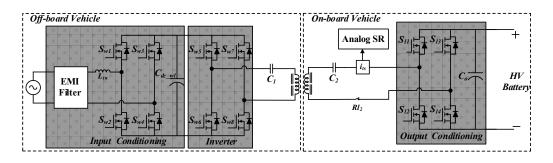

Fig. 2.10 presents a feasible system topology for Solution III. The inductive receiver output is integrated after the isolation stage of conductive charger onboard reusing the output switching bridge for rectification. Similar to solution II input conditioning stage of onboard charger uses an interleaved totem pole structure connected in cascade with the full bridge switching inverter of an a dual active bridge (DAB) converter. The output bridge of DAB along with dc capacitor acts as the output conditioning circuit supplying the high voltage (HV) battery which makes integration possible for this solution. A dual stage cascaded converter structure is used in off-board stage of inductive charger, where a totem pole PFC circuit acts as input conditioning stage followed by a full bridge switching inverter exciting the transmission coil through a compensation network. The receiving coil is powered by transmitting coil using magnetic field and supplies energy to a compensation network which is integrated to conductive stage with the help of interfacing relays  $Rl_1$  and  $Rl_2$ . Relay  $Rl_1$  isolates the transformer and primary side completely from power path and

hence there is no restriction imposed on the design of DAB transformer. The extra isolation introduced by the high frequency DAB transformer in case of Solution II is lacking in this solution but the wireless coils inherently introduces isolation between off-board and onboard charging elements which makes extra isolation an optional requirement. This solution can potentially give similar efficiency as that of an independent wireless system as no extra stages of conversion are added to the power flow.

Fig. 2.10 System level implementation of Solution III

#### 2.4 Summary

In this chapter, a comprehensive review have been carried out on the existing integrated conductive and inductive wireless charging solutions proposed by industries and research groups. Three different architectures for developing integrated inductive and conductive charging solutions are presented, classified based on position of integration of two stages. Solution I and III does not impose any additional constraints on conductive charging components while Solution II imposes additional constraints on the design of isolation transformer parameters. Solution III has the potential of highest efficiency among the three proposed architectures, since no extra power conversion stage is introduced in inductive charging path compared to an independent wireless charging system. Finally, feasible system level implementation topologies for various architectures are introduced. In order to understand the rationale behind the selection of various structures presented as a part of system level implementation of proposed solution detailed loss analysis and topology selection is carried out in the following chapter.

# Chapter 3: Design and Evaluation of Off-board AC-DC Conversion Stage

#### 3.1 Introduction

The basic architectures capable of integrating inductive and conductive charging of electric vehicle were introduced in previous chapter. The complete system includes various stages of power conversion which has to be individually optimized to maximize the overall efficiency of system. The system includes both off-board as well as on-board components which needs to be cautiously designed to meet power transfer requirement. The target system proposed to be developed in laboratory focuses on charging a plugin hybrid electric vehicle (PHEV) with smaller battery capacity.

#### 3.2 Off-board system design

The proposed integrated charger system requires off-board components to energize the wireless transmission stage. As presented in chapter 2 the off-board system transforms single phase AC grid voltage to DC voltage with the help of input conditioning stage. The output of AC-DC stage is supplied to a switching inverter connected in cascade to generate high frequency AC energizing the transmitting coil through appropriate compensation topology. The proposed charger is designed based on the key parameters listed in Table 3.1 derived from commercially available charging solutions meeting various standards of charging [8]-[9].

# 3.1 Selection of input conditioning stage

The input conditioning stage of wireless charger is an active front end rectifier or power factor correction (PFC) circuit that ensure the current drawn from the utility grid has low

distortion ensuring high power quality and high power factor [9]. As required by the Europe standard IEC 61000-3-2 [41], any power converter connected to the grid with power consumption over 75W needs to have front-end PFC stage to meet the harmonic regulation standards. Similarly, in US SAE J2894 [42], the U.S. National Electric Code (NEC) 690 [43] standards specifies the power quality requirements of any interface connected to grid.

| Parameter                                                | Value                      |  |

|----------------------------------------------------------|----------------------------|--|

| Input voltage range (single Phase)                       | 85 - 265 Vrms              |  |

| Output battery voltage range                             | $250-400 \mathrm{~V}$      |  |

| Maximum output power rating                              | 3.3 kW                     |  |

| Maximum output current                                   | 8.25 A                     |  |

| Maximum input current (rms)                              | 15.1 A (@ nominal voltage) |  |

| PFC target efficiency                                    | 97.5 %                     |  |

| Maximum input current Total<br>Harmonic Distortion (THD) | < 5 %                      |  |

| Target integrated charger efficiency                     | 92 %                       |  |

Table 3.1 Key charger specifications

In order to charge the battery under varying voltages, supplied from universal input voltage range as specified in Table 3.1 boost derived PFC topologies are appropriate candidates for evaluation. Traditional boost based PFC topologies presented in Fig. 3.1(a) and Fig. 3.1(b) use a diode bridge in cascade with boost converter to generate high quality input current. Even though high quality current with minimum distortion can be generated, the diode bridge causes significant power loss leading to significant drop in efficiency as well as increased cooling requirements leading to reduced power density [10], [44].

Fig. 3.1 Traditional PFC topology (a) boost PFC (b) interleaved boost PFC

Boost-derived bridgeless converters are an attractive option to meet the requirements of high efficiency, high power density and high power quality AC-DC conversion. The bridgeless topologies have lower conduction losses due to reduced number of semiconductor devices in current path leading to high efficiency operation [10], [44]. Even though adopting bridgeless PFC circuits leads to higher efficiency, they inherently introduces a considerable amount of conducted common mode (CM) noise compared to a conventional diode bridge PFC due to the presence of high frequency switch node voltage between line ground and output ground [45]. Electromagnetic interference (EMI) compliance is a critical requirement for any grid connected converter [46]–[48]. In this regard, various active and passive methods have been proposed to reduce the CM noise generated by bridgeless circuit[47]-[49]. In order to meet the key design constraints listed above, the two most suitable topologies among the alternatives presented in [10], [44] have been selected for evaluation. A quantitative loss analysis along with a qualitative volume analysis is carried out to select the appropriate topology for implementation on laboratory prototype from among two topologies presented in Fig. 3.2.

Fig. 3.2 Bridgeless boost-derived topologies (a) Totem pole or H-bridge (b) Interleaved totem pole

# 3.1.1 Basic operation principle and design details

The primary objective of any PFC rectifier is to shape the input current to follow input voltage with same phase and frequency. A bridge network of MOSFETs helps in shaping the grid current to follow a pure sinusoidal reference by driving each switching leg with complementary pulses separated by a dead band. The input inductor helps in boosting the voltage and filtering the input current's harmonic content. Depending on the switching scheme as well the topology the operation of the boost-derived topologies presented in Fig. 3.2 are evaluated below.

### 3.1.1.1 H-bridge

The overall structure of a single phase H-bridge PFC is presented in Fig. 3.2 (a). The key operating waveforms under this switching are presented in Fig. 3.3. In case of H-bridge operation, there are two switching operation per switching cycle charging and discharging the input inductor.

Fig. 3.3 Key operating waveforms under H-bridge switching scheme