## UCC Library and UCC researchers have made this item openly available. Please let us know how this has helped you. Thanks!

| Title                                                                                                                                    | Reliable chip design from low powered unreliable components                      |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--|--|

| Author(s)                                                                                                                                | Grandhi, Satish Kumar                                                            |  |  |

| <b>Publication date</b>                                                                                                                  | 2019                                                                             |  |  |

| Original citation Grandhi, S. K. 2019. Reliable chip design from low powered unreliable components. PhD Thesis, University College Cork. |                                                                                  |  |  |

| Type of publication                                                                                                                      | Doctoral thesis                                                                  |  |  |

| Rights                                                                                                                                   | © 2019, Satish Kumar Grandhi.  http://creativecommons.org/licenses/by-nc-nd/3.0/ |  |  |

| Embargo information                                                                                                                      | Not applicable                                                                   |  |  |

| Item downloaded from                                                                                                                     | http://hdl.handle.net/10468/8610                                                 |  |  |

Downloaded on 2021-11-27T09:52:38Z

# Reliable Chip Design from Low Powered Unreliable Components

**Author: Satish Kumar Grandhi**

Supervisor: Dr. Emanuel M. Popovici

Department of Electrical and Electronic Engineering, School of Engineering Head of School: Prof. William Marnane

A Thesis Submitted to the National University of Ireland, Cork, in Fulfillment of the Requirements for the Degree of Doctor of Philosophy

September 2019

| T 1111 ( 1 1 ) |                                                    | · 1 · 1 · 1 · 1 · 1 · 1 | DI 16 V 1              |

|----------------|----------------------------------------------------|-------------------------|------------------------|

|                | ze this thesis to my spir<br>zami Srila Prabhupada |                         | e grace Bhakti Vedanta |

|                |                                                    |                         |                        |

|                |                                                    |                         |                        |

|                |                                                    |                         |                        |

|                |                                                    |                         |                        |

|                |                                                    |                         |                        |

|                |                                                    |                         |                        |

|                |                                                    |                         |                        |

|                |                                                    |                         |                        |

|                |                                                    |                         |                        |

|                |                                                    |                         |                        |

|                |                                                    |                         |                        |

|                |                                                    |                         |                        |

|                |                                                    |                         |                        |

#### **Declaration**

I hereby declare that except where specific reference is made to the work of others, the contents of this dissertation are original and have not been submitted in whole or in part for consideration for any other degree or qualification in this, or any other university. This dissertation is my own work and contains nothing which is the outcome of work done in collaboration with others, except as specified in the text and acknowledgements.

**Declaration1**: Part of the CPEP based reconvergent fanout analysis was done by my colleague Bo Yang [1] [2]. This is covered in Section 3.3.6.

**Declaration2**: Mathematical analysis of the CPE methodology was done with Dr. Savin Valentin, CEA LETI [3] [4]. This is covered in section 5.4.

Author: Satish Kumar Grandhi

September 2019

#### **Abstract**

The pace of technological improvement of the semiconductor market is driven by Moore's Law, enabling chip transistor density to double every two years. The transistors would continue to decline in cost and size but increase in power. The continuous transistor scaling and extremely lower power constraints in modern Very Large Scale Integrated(VLSI) chips can potentially supersede the benefits of the technology shrinking due to reliability issues. As VLSI technology scales into nanoscale regime, fundamental physical limits are approached, and higher levels of variability, performance degradation, and higher rates of manufacturing defects are experienced. Soft errors, which traditionally affected only the memories, are now also resulting in logic circuit reliability degradation. A solution to these limitations is to integrate reliability assessment techniques into the Integrated Circuit(IC) design flow. This thesis investigates four aspects of reliability driven circuit design: a)Reliability estimation; b) Reliability optimization; c) Fault-tolerant techniques, and d) Delay degradation analysis.

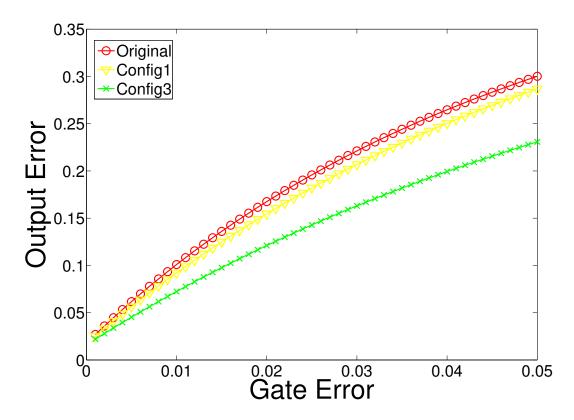

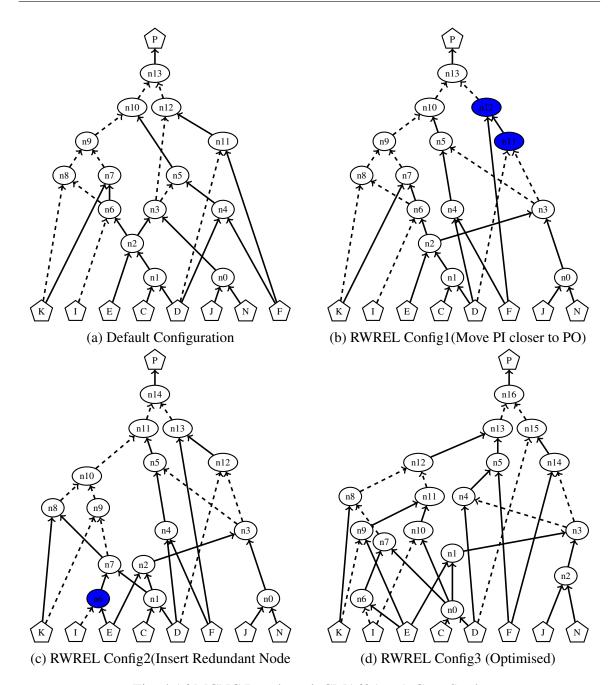

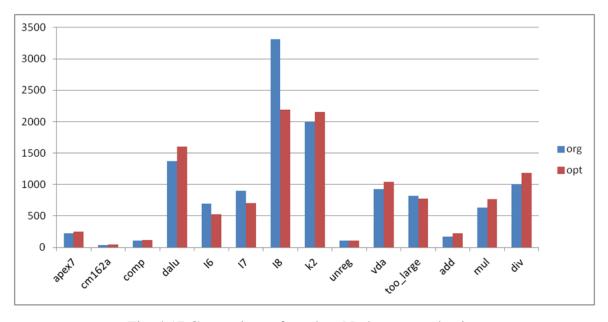

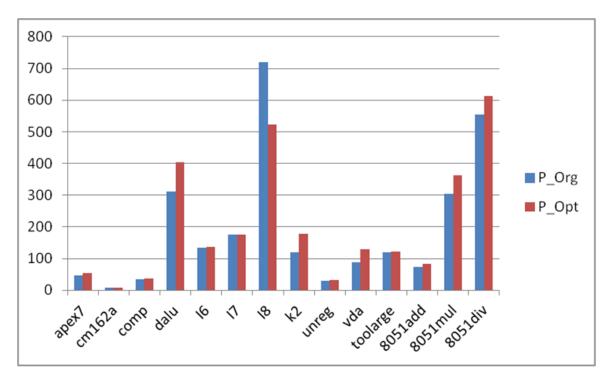

To guide the reliability driven synthesis and optimization of combinational circuits, highly accurate probability based reliability estimation methodology christened **Conditional Probabilistic Error Propagation(CPEP)** algorithm is developed to compute the impact of gate failures on the circuit output. CPEP guides the proposed rewriting based logic optimization algorithm employing local transformations. The main idea behind this methodology is to replace parts of the circuit with functionally equivalent but more reliable counterparts chosen from a precomputed subset of Negation-Permutation-Negation(NPN) classes of 4-variable functions. Cut enumeration and Boolean matching driven by reliability-aware optimization algorithm are used to identify the best possible replacement candidates. Experiments on a set of MCNC benchmark circuits and 8051 functional microcontroller units indicate that the proposed framework can achieve up to 75% reduction of output error probability. On average, about 14% SER reduction is obtained at the expense of very low area overhead of 6.57% that results in 13.52% higher power consumption.

The next contribution of the research describes a novel methodology to design fault tolerant circuitry by employing the error correction codes known as **Codeword Prediction Encoder(CPE)**. Traditional fault tolerant techniques analyze the circuit reliability issue from a static point of view neglecting the dynamic errors. In the context of communication and

storage, the study of novel methods for reliable data transmission under unreliable hardware is an increasing priority. The idea of CPE is adapted from the field of forward error correction for telecommunications focusing on both encoding aspects and error correction capabilities. The proposed Augmented Encoding solution consists of computing an augmented codeword that contains both the codeword to be transmitted on the channel and extra parity bits. A Computer Aided Development(CAD) framework known as CPE simulator is developed providing a unified platform that comprises a novel encoder and fault tolerant LDPC decoders. Experiments on a set of encoders with different coding rates and different decoders indicate that the proposed framework can correct all errors under specific scenarios. On average, about 1000 times improvement in Soft Error Rate(SER) reduction is achieved.

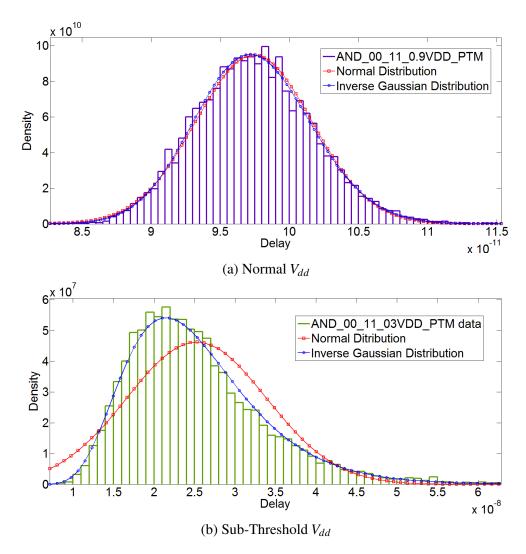

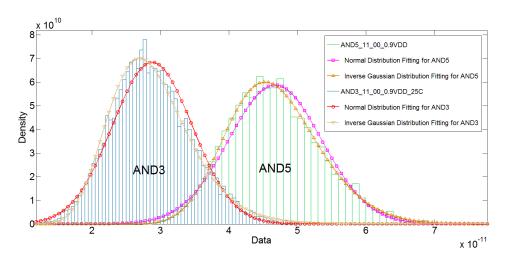

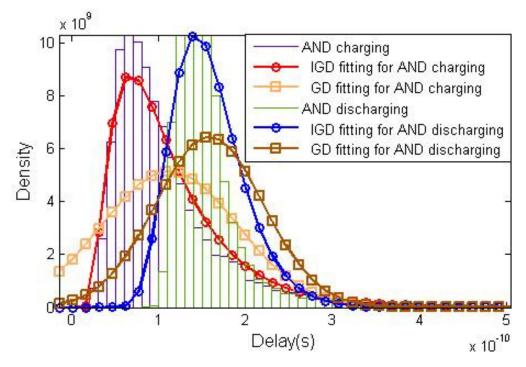

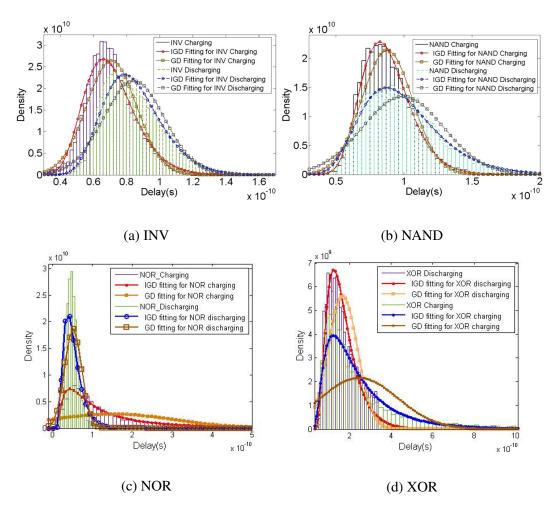

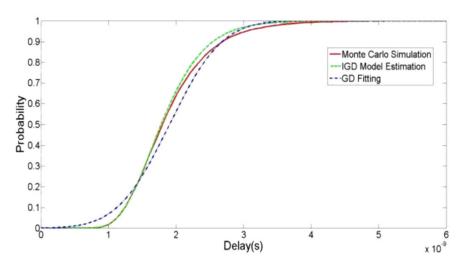

Last part of the research is the Inverse Gaussian Distribution(IGD) based delay model applicable to both combinational and sequential elements for sub-powered circuits. The Probability Density Function(PDF) based delay model accurately captures the delay behavior of all the basic gates in the library database. The IGD model employs these necessary parameters, and the delay estimation accuracy is demonstrated by evaluating multiple circuits. Experiments results indicate that the IGD based approach provides a high matching against HSPICE Monte Carlo simulation results, with an average error less than 1.9% and 1.2% for the 8-bit Ripple Carry Adder(RCA), and 8-bit De-Multiplexer(DEMUX) and Multiplexer(MUX) respectively.

#### **Acknowledgements**

Doing a Ph.D. is a journey of self-discovery which can be very rewarding and enlightening. It's a time to take charge of one's learning and to develop a broad set of valuable new skills. Like any long journey, though, it's not without hardship. My Ph.D. research started when I left Cypress Semiconductors, Bengaluru India back in 2013 and moved to Cork. In the intervening three years, my life has changed dramatically. I believe that every person one meets leaves signs on our road to improvement. I was lucky to meet many such beautiful people during my research. This work was supported by the Seventh Framework Programme of the European Union, under Grant Agreement number 309129 (i-RISC project).

First, I would like to thank my supervisor Dr. Emanuel Popovici for giving me the opportunity to pursue my doctoral studies on an intriguing subject such as VLSI EDA. Thanks for giving me the chance to travel around the world and visit many interesting places over the years and finally thanks for all the help, support and encouragement that he gave me during my Ph.D. studies.

To my i-RISC research group members: Prof Sorin Cotofona, TU Delft has been my second supervisor. His amazing command over the subject and the amazing sense of humor dazzles me. I was fortunate to have worked directly with Dr. Savin Valentin, CEA LETI and learn a bit about LDPC coding techniques from his decades of working experience. I was also very fortunate to have three post-docs supervising me at different time periods. Dr. Chen made me feel comfortable with the new place when I started my Ph.D. journey. Then, Dr. Christian Spagnol builds the foundation of my research and helped me in publishing quite a few papers. Last, but not the least, Dr. Elsa Dupraz came at the end of my Ph.D. and helped me to solve on some of the pending problems. I am very thankful for many discussions we had, about our research work and beyond. It takes a considerable amount of effort and perseverance, to come to the point where only acknowledgments are left to be included in the dissertation. They have helped me reach this point

My labmates need special mention for bearing me for three years. Bruno, Fiona, BO, Nasim, Alan, and David: Thank you, folks, for all the fun chats. Thanks to all the staff of the Electric and Electronic Engineering Department for all the help, assistance and kindness. I was also fortunate to make some good friends from my Indian community. Prasanna, Charles,

Umanath, and Preethi I must have bugged you a lot. It is not over, get ready for more for the rest of life. Time spent with my local Telugu batch was the best moment of this three years. Thanks, guys for the fun games and the spicy Indian food. To my family, I am grateful for the most important signs in my life that made it more comfortable when deciding which turns to take. Last but not the least, my beautiful wife Susheela who has been most supportive during the whole editing of the thesis.

#### **Publications**

The thesis is based in part on the following publications:

- **J2**: **Grandhi, S.**, Yang, B., Spagnol, C., Gupta, S. and Popovici, E., 2016. An EDA Framework for Reliability Estimation and Optimization of Combinational Circuits. Journal of Low Power Electronics, 12(3), pp.242-258.

- **J1**: Chen, J., Cotofana, S., **Grandhi, S.**, Spagnol, C. and Popovici, E., 2015. Inverse Gaussian distribution based timing analysis of Sub-threshold CMOS circuits. Microelectronics Reliability, 55(12), pp.2754-2761.

- C7: Yang, B., Grandhi, S., Spagnol, C., Popovici, E. and Cotofana, S., 2016, June. An approach for digital Circuit Error/Reliability Propagation Analysis based on Conditional Probability. In 2016 27th Irish Signals and Systems Conference, pp.1-6.

- C6: Dupraz, E., Savin, V., Grandhi, S., Popovici, E. and Declercq, D., 2016, May. Practical LDPC encoders robust to hardware errors. In 2016 IEEE International Conference on Communications, pp.1-6.

- C5: Grandhi, S., Dupraz, E., Spagnol, C., Savin, V. and Popovici, E., 2016, May. CPE: Codeword Prediction Encoder. In 2016 21th IEEE European Test Symposium, pp.1-2.

- C4: Grandhi, S., McCarthy, D., Spagnol, C., Popovici, E. and Cotofana, S., 2015, October. Rost-c: Reliability driven optimisation and synthesis techniques for combinational circuits. In 2015 33rd IEEE International Conference on Computer Design, pp.431-434.

- C3: Grandhi, S., Spagnol, C., Chen, J., Popovici, E. and Cotafona, S., 2014, September. Reliability aware logic synthesis through rewriting. In 2014 27th IEEE International System-on-Chip Conference, pp.274-279.

- C2: Grandhi, S., Spagnol, C. and Popovici, E., 2014, June. Reliability analysis of logic circuits using probabilistic techniques. In 2014 10th Conference on Ph. D. Research in Microelectronics and Electronics, pp.1-4.

- C1: Chen, J., Spagnol, C., **Grandhi, S.**, Popovici, E., Cotofana, S. and Amaricai, A., 2014, July. Linear compositional delay model for the timing analysis of sub-powered combinational circuits. In 2014 IEEE Computer Society Annual Symposium on VLSI, pp.380-385.

## **Table of contents**

| Li | st of f | igures    |                                                                                                                | xiii |

|----|---------|-----------|----------------------------------------------------------------------------------------------------------------|------|

| Li | st of t | ables     |                                                                                                                | xvi  |

| No | omeno   | clature   |                                                                                                                | xvii |

| 1  | Intr    | oductio   | on Carlos Ca | 1    |

|    | 1.1     | VLSI      | Design, Automation and Reliability                                                                             | 1    |

|    | 1.2     | Object    | tives and Thesis Contributions                                                                                 | 3    |

|    |         | 1.2.1     | Research Objectives                                                                                            | 3    |

|    |         | 1.2.2     | Thesis Statement                                                                                               | 3    |

|    |         | 1.2.3     | Circuit Representation and Modification                                                                        | 4    |

|    |         | 1.2.4     | Reliability Estimation and Analysis                                                                            | 5    |

|    |         | 1.2.5     | Reliability Driven Logic Optimization                                                                          | 6    |

|    |         | 1.2.6     | Fault Tolerant Graph Augmentation                                                                              | 7    |

|    |         | 1.2.7     | PDF based Delay Degradation Analysis                                                                           | 8    |

|    | 1.3     | The Re    | esearch Framework                                                                                              | 9    |

|    | 1.4     | Conclu    | usions                                                                                                         | 11   |

| 2  | Reli    | ability i | in Logic Circuit Design                                                                                        | 13   |

|    | 2.1     | Introdu   | uction                                                                                                         | 13   |

|    |         | 2.1.1     | Understanding Reliability                                                                                      | 14   |

|    |         | 2.1.2     | Transient faults in logic circuits                                                                             | 16   |

|    | 2.2     | Reliab    | oility Estimation                                                                                              | 17   |

|    | 2.3     | Reliab    | oility Aware Logic Synthesis                                                                                   | 19   |

|    | 2.4     | Fault 7   | Tolerant Techniques                                                                                            | 20   |

|    | 2.5     | Static    | Timing Analysis                                                                                                | 21   |

|    | 26      | Conclu    | ucione                                                                                                         | 22   |

Table of contents x

| 3 | Reli | ability I | Estimation                                    | 24 |

|---|------|-----------|-----------------------------------------------|----|

|   | 3.1  | Introdu   | action                                        | 24 |

|   |      | 3.1.1     | Main Contributions and Outline                | 24 |

|   | 3.2  | Simula    | ation Based Reliability Computation           | 25 |

|   |      | 3.2.1     | Mersenne Twister and Random Number Generation | 25 |

|   |      | 3.2.2     | Gate Error Model                              | 26 |

|   |      | 3.2.3     | The Methodology                               | 26 |

|   |      | 3.2.4     | Limitations                                   | 28 |

|   | 3.3  | CPEP:     | Conditional Probabilistic Error Propagation   | 29 |

|   |      | 3.3.1     | The Data Structure                            | 29 |

|   |      | 3.3.2     | Gate Error Models                             | 30 |

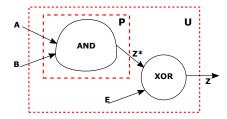

|   |      | 3.3.3     | 2-Input Ideal AND Gate                        | 31 |

|   |      | 3.3.4     | Intrinsic Gate Error Effects                  | 32 |

|   |      | 3.3.5     | Ideal inverter                                | 33 |

|   |      | 3.3.6     | Re-convergent Fanout                          | 34 |

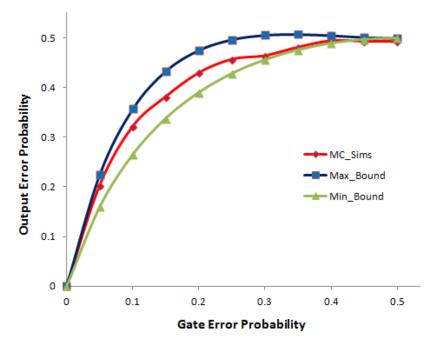

|   |      | 3.3.7     | Bounding Node Error Probability               | 35 |

|   |      | 3.3.8     | CPEP based Analysis                           | 35 |

|   |      | 3.3.9     | CPEP extension to other Gates                 | 37 |

|   |      | 3.3.10    | Limitations                                   | 38 |

|   | 3.4  | CAD       | Tool: Reliability Evaluator                   | 38 |

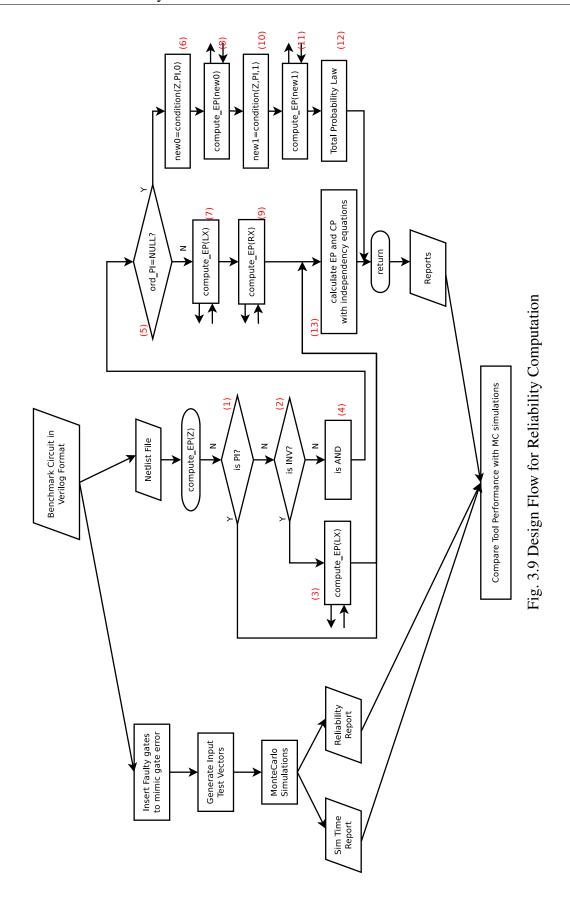

|   |      | 3.4.1     | Computation Algorithm                         | 39 |

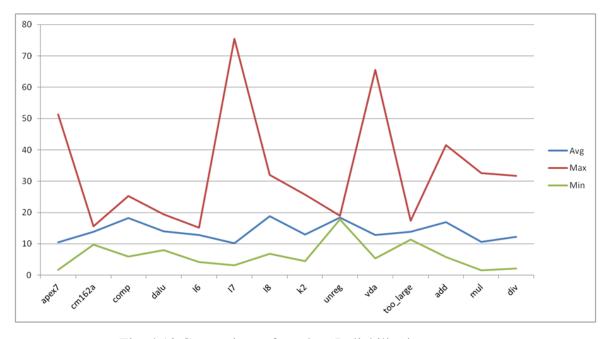

|   |      | 3.4.2     | Simulation Results                            | 40 |

|   | 3.5  | Conclu    | asions                                        | 43 |

| 4 | Reli | ability A | Aware Logic Synthesis                         | 44 |

|   | 4.1  | Introdu   | action                                        | 44 |

|   |      | 4.1.1     | Main Contributions and Outline                | 45 |

|   | 4.2  | ABC:      | Open Source EDA tool                          | 46 |

|   |      | 4.2.1     | AND Invert Graphs                             | 46 |

|   |      | 4.2.2     | ABC Tool                                      | 48 |

|   | 4.3  | Rule b    | ased Rewriting                                | 49 |

|   |      | 4.3.1     | Local Transformation Rules                    | 50 |

|   |      | 4.3.2     | Exhaustive Analysis of Rules                  | 53 |

|   |      | 4.3.3     | The CAD algorithm                             | 54 |

|   | 4.4  | Experi    | mental Results                                | 59 |

|   |      | 4.4.1     | Case study                                    | 59 |

|   |      | 4.4.2     | Evaluation of MCNC Benchmark Circuits         | 60 |

Table of contents xi

|   | 4.5 | Cut Ba  | ased AIG Rewriting                |

|---|-----|---------|-----------------------------------|

|   |     | 4.5.1   | The CAD Algorithm                 |

|   | 4.6 | Experi  | mental Results                    |

|   |     | 4.6.1   | CM162a – A Case Study             |

|   |     | 4.6.2   | Evaluation of Benchmark Circuits  |

|   | 4.7 | Conclu  | asions                            |

| 5 | CPE | : Code  | eword Prediction Encoder 73       |

|   | 5.1 | Introdu | uction                            |

|   |     | 5.1.1   | Main Contributions and Outline    |

|   | 5.2 | LDPC    | Codes and Error Models            |

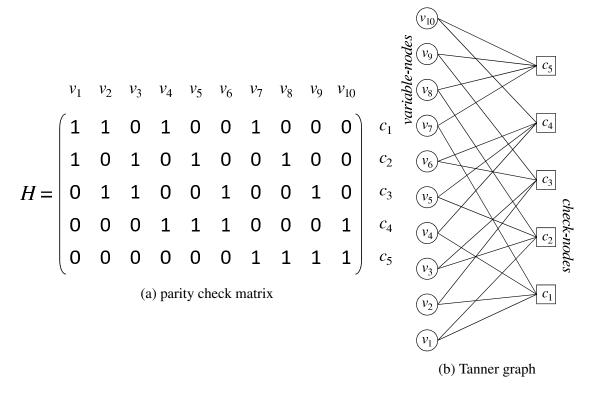

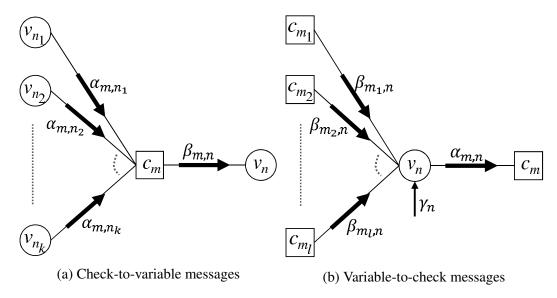

|   |     | 5.2.1   | LDPC codes                        |

|   |     | 5.2.2   | LDPC Encoding and Decoding        |

|   |     | 5.2.3   | Gate Error Model                  |

|   | 5.3 | Codew   | vord Prediction Encoder (CPE)     |

|   | 5.4 | CPE M   | Mathematical Analysis         81  |

|   |     | 5.4.1   | CPE Cost Analysis                 |

|   |     | 5.4.2   | Notation and Conventions          |

|   |     | 5.4.3   | Cost analysis for Area/Power      |

|   |     | 5.4.4   | Error Correction Capacity         |

|   |     | 5.4.5   | CPE and Modular Redundancy        |

|   | 5.5 | CPE S   | imulator and CAD Automation       |

|   |     | 5.5.1   | CPE Core Architecture             |

|   |     | 5.5.2   | Criticality Threshold             |

|   |     | 5.5.3   | Pre-Processing                    |

|   |     | 5.5.4   | Netlist Format                    |

|   |     | 5.5.5   | CPE Simulator         93          |

|   | 5.6 | Experi  | mental Results                    |

|   |     | 5.6.1   | Critical Nodes                    |

|   |     | 5.6.2   | Impact of Decoder Configuration   |

|   | 5.7 | CPE fo  | or Fault Prone Boolean Functions  |

|   |     | 5.7.1   | Encoding Mechanism                |

|   | 5.8 | Experi  | mental Results                    |

|   |     | 5.8.1   | Critical Nodes                    |

|   |     | 5.8.2   | Area Overhead                     |

|   |     | 5.8.3   | NMR Vs. CPE                       |

|   |     | 5.8.4   | Impact of LDPC code sizes on Area |

Table of contents xii

|    |        | 5.8.5   | Case Study                                                  | 102 |

|----|--------|---------|-------------------------------------------------------------|-----|

|    | 5.9    | Conclu  | asions                                                      | 104 |

| 6  | Dela   | v Degr  | adation Analysis                                            | 105 |

| Ū  | 6.1    | •       | uction                                                      |     |

|    |        | 6.1.1   | Main Contributions and Outline                              |     |

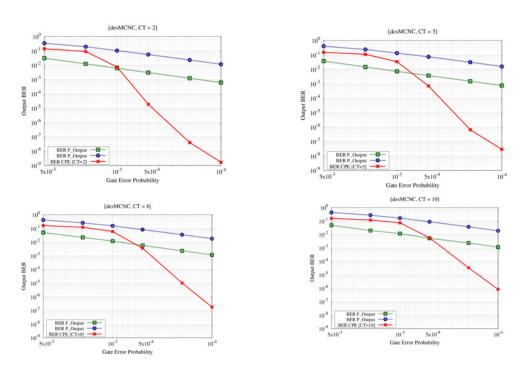

|    | 6.2    |         | y Cells Simulation Methodology                              |     |

|    |        | 6.2.1   | Library Characterization                                    |     |

|    |        | 6.2.2   | Timing Verification                                         |     |

|    |        | 6.2.3   | Simulation Methodology                                      |     |

|    | 6.3    | Linear  | Compositional Delay Model                                   |     |

|    |        | 6.3.1   | Flexibility (universality) of IGD model                     |     |

|    | 6.4    | IGD B   | assed Delay Model for Combinational and Sequential circuits |     |

|    |        | 6.4.1   | Typical timing path in synchronous CMOS circuits            |     |

|    |        | 6.4.2   | Combinational Gates - INV, NAND, NOR & XOR                  |     |

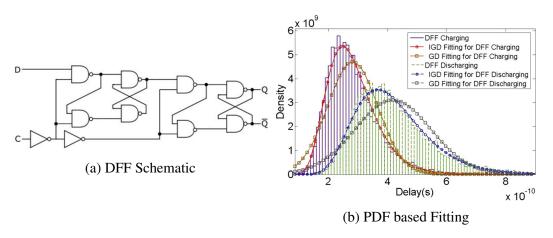

|    |        | 6.4.3   | Sequential Circuits- Master Slave DFF                       | 114 |

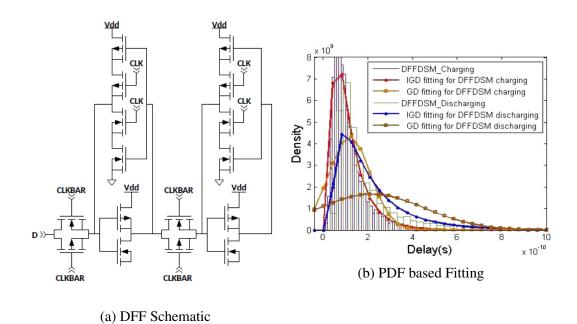

|    |        | 6.4.4   | Sequential Circuits- Sub-Threshold DFF                      |     |

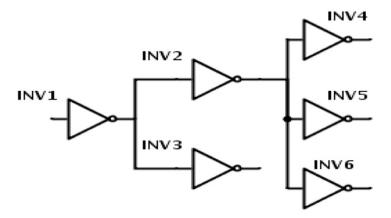

|    | 6.5    | Fan-ou  | at Aware IGD Model                                          | 116 |

|    |        | 6.5.1   | Fan-out effect estimation methodology                       | 117 |

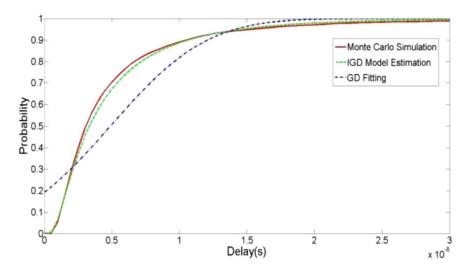

|    |        | 6.5.2   | Transition time effect estimation methodology               | 118 |

|    |        | 6.5.3   | The FOC and FOP effects                                     |     |

|    |        | 6.5.4   | Model Validation for Synchronous Circuits                   | 120 |

|    | 6.6    | Conclu  | usions                                                      | 123 |

| 7  | Sum    | ımarv a | and Future work                                             | 125 |

| ′  | 7.1    | •       |                                                             |     |

|    | 7.1    | 7.1.1   | butions                                                     |     |

|    |        | 7.1.2   | Inverse Gaussian Distribution Based Timing Analysis         |     |

|    |        | 7.1.3   | ROST-C: Reliability driven Optimization and Synthesis       |     |

|    |        | 7.1.4   | Error Coding Driven Graph Augmentation                      |     |

|    |        | 7.1.5   | Boole-Shannon Limit of noisy combinational logic            |     |

|    | 7.2    |         | Work                                                        |     |

|    |        | 1 61610 |                                                             | .27 |

| Re | eferen | ces     |                                                             | 131 |

# List of figures

| 1.1 | Four significant areas of current research                     | 4  |

|-----|----------------------------------------------------------------|----|

| 1.2 | Different Data-structures                                      | 5  |

| 1.3 | Reliability Estimation Flow                                    | 6  |

| 1.4 | Reliability Driven Circuit Optimization Example                | 7  |

| 1.5 | The Codeword Prediction Encoder(CPE) flow                      | 8  |

| 1.6 | PDF propagation and Methodology                                | 9  |

| 1.7 | The IRISC Project Details                                      | 10 |

| 1.8 | The Complete Flow                                              | 12 |

| 2.1 | Classification of Reliability                                  | 14 |

| 3.1 | Gate Error Model for GLS based technique                       | 26 |

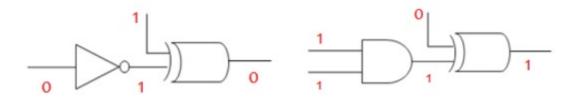

| 3.2 | Unreliable Data transmission through on Inverter and AND Gates | 27 |

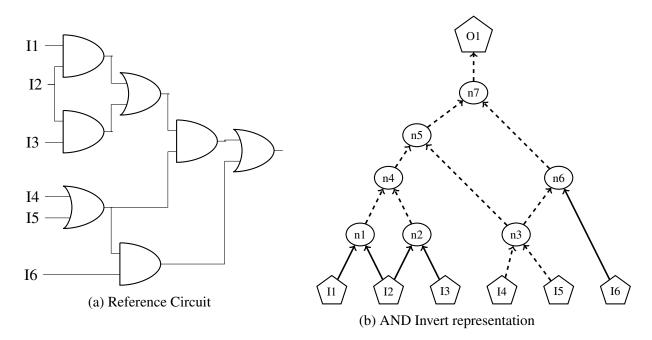

| 3.3 | And Inverter representation of Combinational Circuit           | 29 |

| 3.4 | Unreliable AND Gate Model                                      | 30 |

| 3.5 | Unreliable Inverter Model                                      | 33 |

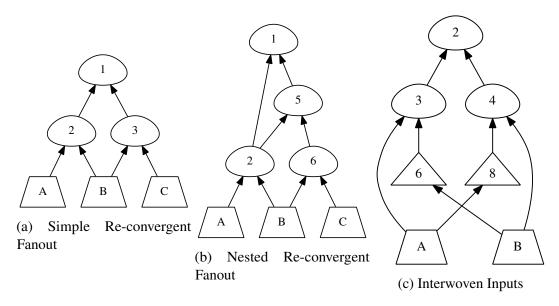

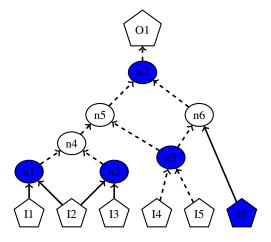

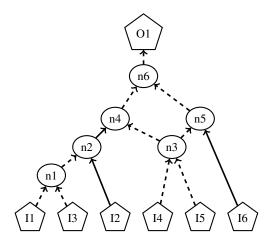

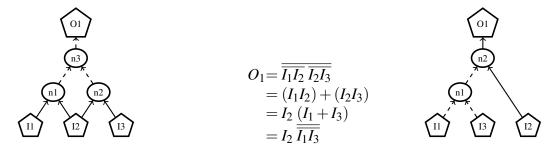

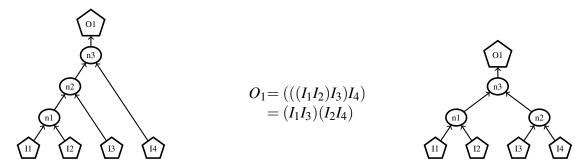

| 3.6 | Re-convergent Fanout Structures                                | 34 |

| 3.7 | Bounding Error                                                 | 35 |

| 3.8 | B9 Benchmark Circuit Error Bounds                              | 36 |

| 3.9 | Design Flow for Reliability Computation                        | 41 |

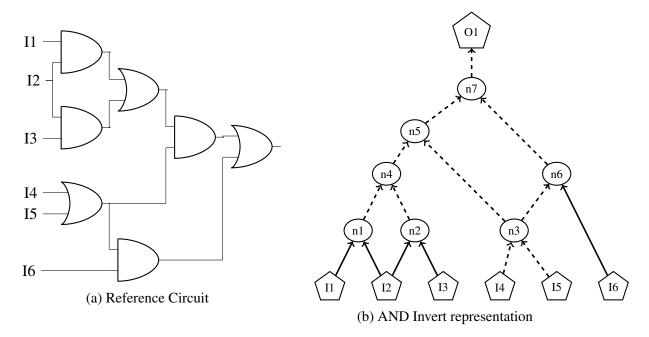

| 4.1 | And Inverter representation of Combinational Circuit           | 47 |

| 4.2 | Cut Example                                                    | 47 |

| 4.3 | Boolean Equivalent                                             | 48 |

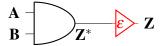

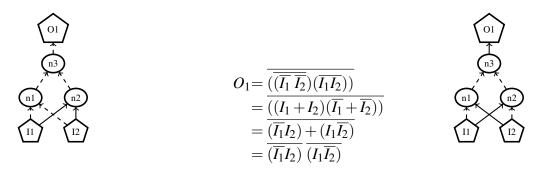

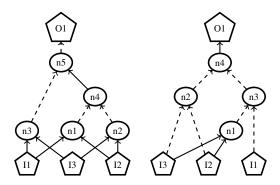

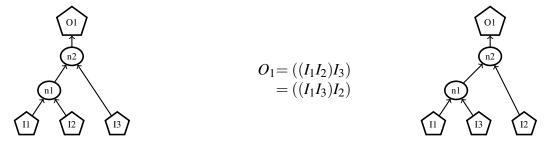

| 4.4 | Logic Transformation Rule1                                     | 50 |

| 4.5 | Logic Transformation Rule2                                     | 51 |

| 4.6 | Logic Transformation Rule3                                     | 51 |

| 4.7 | Logic Transformation Rule4                                     | 52 |

| 18  | Logic Transformation Pule5                                     | 52 |

List of figures xiv

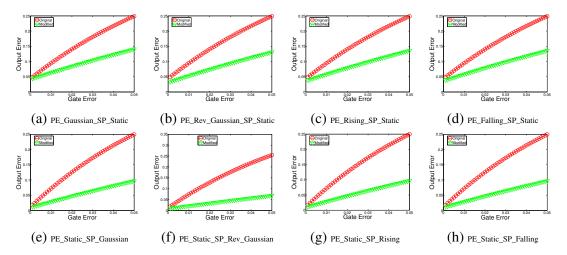

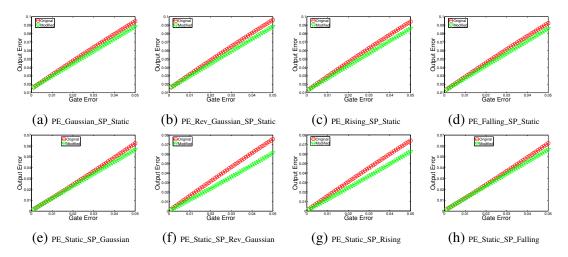

| 4.9  | All simulation results for Rule1                                                   |

|------|------------------------------------------------------------------------------------|

| 4.10 | All simulation results for Rule2                                                   |

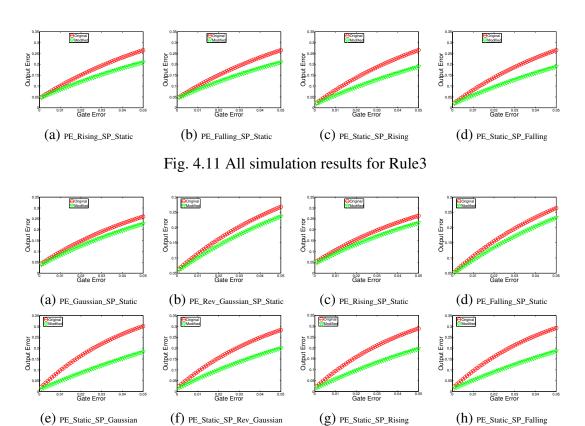

| 4.11 | All simulation results for Rule3                                                   |

| 4.12 | All simulation results for Rule4                                                   |

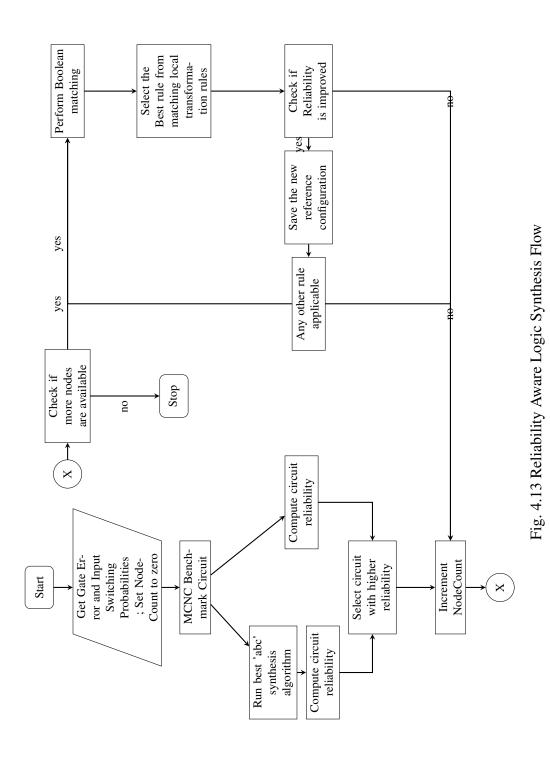

| 4.13 | Reliability Aware Logic Synthesis Flow                                             |

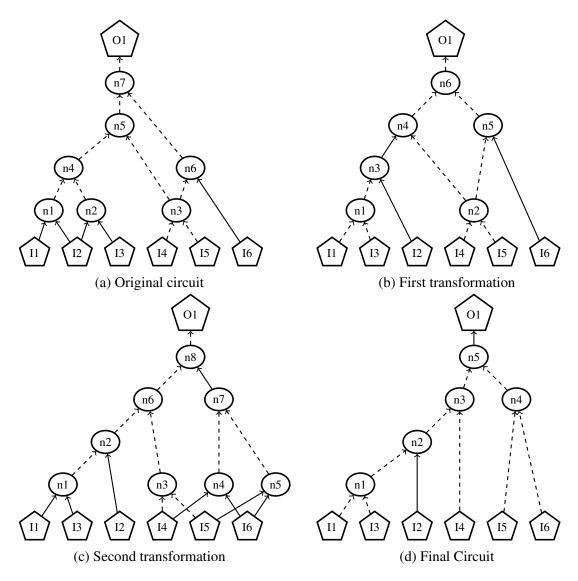

| 4.14 | Application of logic transformation rule-set on the original Circuit 60            |

| 4.15 | Comparison of results                                                              |

| 4.16 | MCNC Benchmark CM162A – A Case Study                                               |

| 4.17 | Comparison of results: Node count reduction                                        |

| 4.18 | Comparison of results: Power reduction                                             |

| 4.19 | Comparison of results: Reliability improvement                                     |

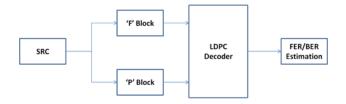

| 5.1  | Methodology of Codeword Prediction Encoder                                         |

| 5.2  | Data transmission scheme                                                           |

| 5.3  | LDPC Codes                                                                         |

| 5.4  | LDPC message computation                                                           |

| 5.5  | Gate Error Model.         79                                                       |

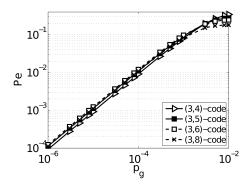

| 5.6  | Encoding error probability $P_e$ with respect to gate error probability $p_g$ . In |

|      | the legend, the $(3,x)$ -code represents the code with $d_v = 3$ and $d_c = x$ 80  |

| 5.7  | First encoding solution                                                            |

| 5.8  | The CPE approach                                                                   |

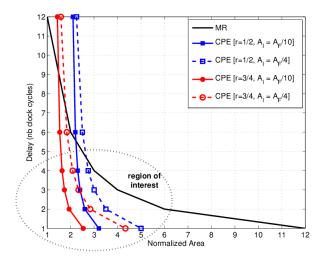

| 5.9  | Delay vs. normalized area for MR and CPE schemes with various unrolling            |

|      | factors                                                                            |

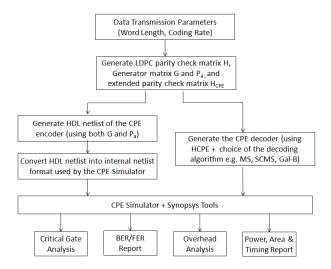

| 5.10 | The CPE Tool Architecture                                                          |

| 5.11 | The CPE CAD flow                                                                   |

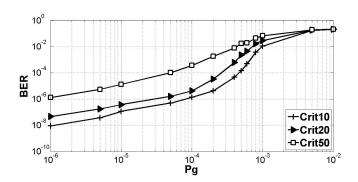

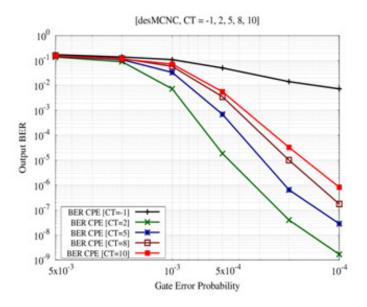

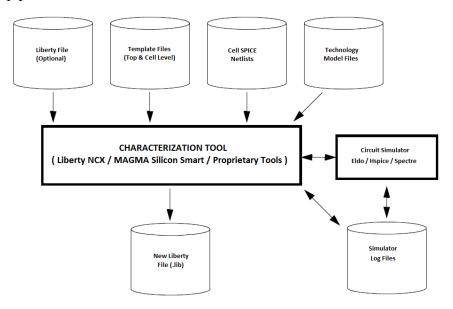

| 5.12 | Critical Threshold impact on Output BER                                            |

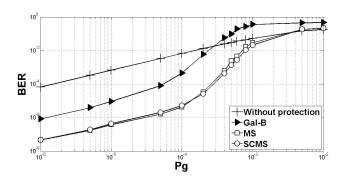

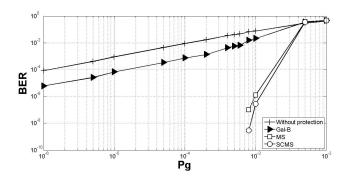

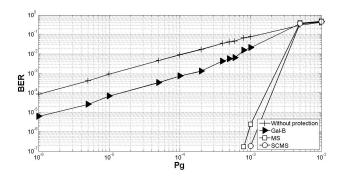

| 5.13 | Decoder Configuration impact on Output BER                                         |

| 5.14 | CPE error free scenario employing faulty decoder                                   |

| 5.15 | CPE error free scenario employing perfect decoder                                  |

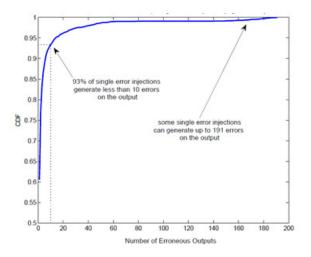

| 5.16 | CDF of the number of erroneous outputs generated by one single error injection 98  |

| 5.17 | CDF plot of criticality degree                                                     |

| 5.18 | Critical node count for different Linear and Non-Linear circuits 100               |

| 5.19 | Area overhead due to parity augmentation                                           |

| 5.20 | Performance of NMR Vs CPE                                                          |

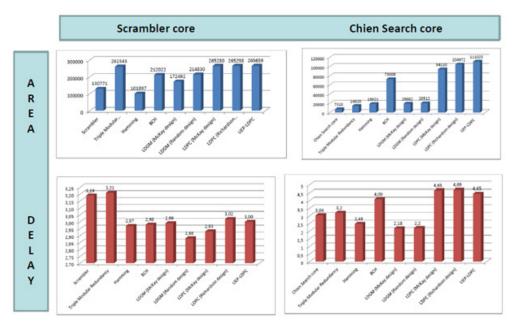

| 5.21 | Area and timing Analysis on IP cores using CPE methodology 102                     |

| 5.22 | Output BER for various Criticality thresholds                                      |

| 5.23 | Detailed plots for output error on F, P and decoder output nodes 103               |

List of figures xv

| 6.1  | Library Characterization Flow                                           |

|------|-------------------------------------------------------------------------|

| 6.2  | IGD and GD fittings for 2 Input AND gate                                |

| 6.3  | Seven AND gate chain                                                    |

| 6.4  | IGD vs GD fitting for 2-input AND gate with only supply variation 112   |

| 6.5  | IGD and GD fittings for basic gates charging and discharging events 114 |

| 6.6  | IGD and GD fittings for DFF charging and discharging events             |

| 6.7  | IGD and GD fittings for Sub-threshold based DFF architecture            |

| 6.8  | A sample circuit with FOC= 3 and FOP= 2                                 |

| 6.9  | DFFs +8-bit RCA CDFs                                                    |

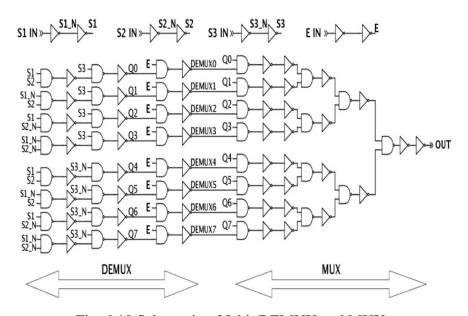

| 6.10 | Schematic of 8-bit DEMUX and MUX                                        |

| 6.11 | DFFs +8-bit DEMUX and MUX CDFs                                          |

## List of tables

| 3.1 | Ideal AND Gate with Unreliable Inputs                                               | 32  |

|-----|-------------------------------------------------------------------------------------|-----|

| 3.2 | Faulty AND Gate with Unreliable Inputs                                              | 33  |

| 3.3 | MCNC Benchmark Circuits Based Accuracy and Performance Evaluation                   |     |

|     | for different gate errors $(\mathcal{E})$                                           | 42  |

| 4.1 | Scenarios used for rules analysis                                                   | 54  |

| 4.2 | MCNC Benchmark Circuits Performance Evaluation (gate error: $\varepsilon = 0.05$ .) | 62  |

| 4.3 | RWREL Performance Evaluation on different Benchmark Circuits (Gate                  |     |

|     | error $\varepsilon = 0.001$ )                                                       | 68  |

| 4.4 | Area, Delay and Power Analysis – A comparative Study                                | 69  |

| 5.1 | CPE Netlist Representation                                                          | 92  |

| 5.2 | Critical Gate count for different encoding schemes                                  | 95  |

| 6.1 | $\mu$ and $\lambda$ for NAND, INV and DFF                                           | 115 |

| 6.2 | INV & NAND FOC key parameter values                                                 | 117 |

| 6.3 | FOP effect on output transition time (all values in ps)                             | 118 |

| 6.4 | FOP effect on key parameters for INV                                                | 119 |

| 6.5 | FOP effect on key parameters for NAND                                               | 120 |

| 6.6 | DFFS +8-BIT RCA CDF deviations                                                      | 122 |

| 67  | DFFS +8-BIT DEMUX and MUX CDF deviations                                            | 123 |

### **Nomenclature**

#### **Acronyms / Abbreviations**

| in o i ma invert Graping | AIG | And | Invert | Grap! | hs |

|--------------------------|-----|-----|--------|-------|----|

|--------------------------|-----|-----|--------|-------|----|

ATPG Automatic Test Pattern Generation

BER Bit Error Rate

BLIF Berkeley Logic Interchange Format

BN Bayesian Networks

**BSC** Binary Symmetric Channel

CCS Composite Current Source

CDF Cumulative Distribution Functions

CNFET Carbon Nanotube Field-Effect Transistors

CPEP Conditional Probabilistic Error Propagation

CT Criticality Threshold

DRM Dynamic Reliability Management

DTA Dynamic Timing Analysis

DWAA Dynamic Weighted Average Algorithm

ECC Error Correcting Codes

EMI Electro-Magnetic Interference

FA Full Adder

Nomenclature xviii

FER Frame Error Rate

FO Fan-Out

GALB Gallager B

GD Gaussian Distribution

GLS Gate Level Simulation

HCI Hot Carrier Injection

IC Integrated Circuits

IEEE Institute of Electrical and Electronics Engineers

LDGM Low Density Generator Matrix

LDPC Low-Density Parity-Check

LDPC Low-Density Parity-Check

LER Line Edge Roughness

LUT Look Up Table

MC Monte-Carlo

MCNC Microelectronics Centre of North Carolina

MCSTA Monte Carlo Static Timing Analysis

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

MP Modular Redundancy

MRF Markov Random Fields

MS Min-Sum

MT Mersenne Twister

NBTI Negative Bias Temperature Instability

NLDM Non Linear Delay Model

PDD Probabilistic Decision Diagrams

Nomenclature

PGM Probabilistic Gate Model

PI Primary Inputs

PO Primary Outputs

PRNG Pseudo-Random Number Generator

PTM Predictive Transistor Models

PTM Probabilistic Transfer Matrices

PVT Process, Voltage, and Temperature

R2R Register to Register

RAR Redundancy Addition and Removal

*RDF* Random Dopant Fluctuations

RMR R-fold Modular Redundancy

RTL Register Transfer Language

SAIF Switching Activity Interchange Format

SCMS Self-Corrected Min-Sum

SER Soft Error Rate

SEU Single Event Upsets

SPRA Signal Probability Reliability Analysis

SSTA Statistical Static Timing Analysis

STA Static Timing Analysis

TGMS Transmission-Gate Master-Slave

TMR Triple Modular Redundancy

VHDL VHSIC Hardware Description Language

## Chapter 1

### Introduction

#### 1.1 VLSI Design, Automation and Reliability

Computing technology is the cornerstone of modern day human progress. Digital systems permeate all areas of our lives, from personal computers, through automotive applications and medical systems, to common house appliances. Although these digital systems provide greater productivity and flexibility, they cannot be fault-free. In this regard, the semiconductor industry has driven more than five decades of improvements in its products mainly thanks to scaling trends. Technology scaling is leading to a decrease in device geometry and the increase in clock frequencies, resulting in a significant increase in the incidence of transient errors [5]. Thus, although technology trends allowed for easily obtained low-cost, high-performance microprocessors, the critical issue for these processors is to satisfy the requirements of dependable computing.

Traditional Very-Large-Scale Integration(VLSI) design methodologies and Electronic Design Automation(EDA) tools are centered around fulfilling timing, power, and area constraints or on achieving acceptable trade-offs among those [6] [7]. However, as the Complementary Metal-Oxide-Semiconductor(CMOS) technology entered the nanometer era, such an approach can no longer cover all the relevant design aspects. Technology scaling has precipitated higher operating speeds, lower operating voltages, and lower operating noise margins; all of which contribute to reduced switching energies, allowing legitimate logic signals to be readily overwhelmed by single-event-induced charge-collection transients [8]. Nanotechnology specific issues, e.g., power supply voltage reduction, the higher impact of the process parameter and temperature variations, resulting in increased device failure rates, making CMOS Integrated Circuits(IC) less reliable [9] [10].

As power usage is proportional to the square of voltage, operating at very low voltages offers a potential for significant power savings [11] [12]. However, this would mean the sup-

ply voltage is significantly below the transistor threshold voltage, and it is well known that in this weak inversion regime, Metal-Oxide-Semiconductor Field-Effect Transistor(MOSFET) transistors exhibit high voltage gain but very low currents [12]. There are many possible ways in which a sub-threshold circuit may become unreliable. The simplest is due to noise, made worse by leakage induced noise. Stuck-at or similar persistent faults can occur due to process variations [9] [10], either statically or dynamically (dependent on temperature and voltage). This behavior is inherent as silicon doping is a stochastic process, and in small process geometries, a tiny number of dopant atoms can be present in a MOSFET transistor channel. Thus, the stochastic process does not necessarily average out, leading to nearby MOSFET's having very different electrical properties and by implication switching behaviour [11].

The scaling of device feature sizes, operating voltages, and design margins raises a great concern about the susceptibility of circuits to transient faults [13] [14] [15] [16] [17] [18], which can be caused by different physical phenomena (e.g., energetic particle hits originating from cosmic rays, capacitive coupling, electromagnetic interference, power transients) [17]. As technology scales further, variations become prominent as well. The technology nodes below 90nm also referred to as deep sub-micron, experience higher levels of device parameter variations, which are changing the design problem from deterministic to probabilistic [19]. Reliable operation of digital systems is severely challenged, thus pointing to the use of fault tolerance driven design methodologies, not only for the mission or life-critical applications but also, for regular, mass-market applications. To allow for the efficient design of a system that can tolerate faults, a first natural step includes understanding the source of induced errors, but most importantly, their modeling and analysis for guiding the design processes.

When considering transient faults, it is important to note the following: (i)Not all transient faults lead to errors and (ii)Not all errors lead to system failures [5]. In this thesis, the focus is on the first claim estimating the likelihood that a transient fault at the output of an internal gate will lead to an error at primary outputs. The primary goal of this thesis is to allow for accurate modeling and efficient estimation of the susceptibility of combinational circuits to transient faults, including the impact of process parameter variation. Intensive research has been done so far around analysis of transient faults in combinational and sequential circuits [9] [10] [13] [14] [15] [16] [17] [18]. One obvious approach is to inject the fault into the given node of the circuit and simulate the circuit for different input vectors to find whether the fault propagates [20] [8] [21] [22]. However, this approach becomes intractable for larger circuits with a larger number of inputs and thus gives way to approximate approaches that use analytical methods to evaluate circuit susceptibility to transient faults. The proposed framework can be used to reduce the cost of applying various techniques for error detection and correction.

Another unreliability mechanism is unpredictable timing. In [23], it was indicated that sub-powered gate arrival times follow inverse Gaussian distributions, with a long calculation completion time tail. In a practical system, a gate chain has a certain allowed slack, and if individual gate completion times change this may be exceeded, and errors may occur. Even a small error probability at the level of individual gates might result in a significant error probability at the circuit final outputs [24]. It is noted that this tendency is not CMOS specific, as even the most promising post-silicon devices, e.g., Carbon Nanotube Field-Effect Transistors (CNFETs) that are considered to replace CMOS eventually suffer from various amounts of statistical variation in device behavior, potentially leading to a lack of reliability [10]. As a result, reliability is turning out into an important design metric sharing equal importance with the other existing design metrics. Consequently, design time reliability assessment and optimization is becoming a mandatory IC design flow step which targets the reliability improvement for circuits/systems built with unreliable components.

#### 1.2 Objectives and Thesis Contributions

This section lists the research objectives and several important contributions of this work in modeling and analysis of transient faults.

#### 1.2.1 Research Objectives

The first objective of this research is the achievement of systematic synthesis and optimisation of reliable circuits, culminating with a multi-objective circuit design optimization, with respect to its size, energy consumption, latency, and all driven by reliability. This includes various tasks like reliability estimation model, reliability optimisation algorithms and delay degradation timing analysis.

The second objective of this research is a fundamental study on the effectiveness of integrating error correcting codes into the structural (Boolean network) implementation of the circuit logical functionality.

#### 1.2.2 Thesis Statement

This research presents a systematic Electronic Design Automation(EDA) methodology to model the propagation of errors through combinational circuits, optimization, and fault tolerant techniques to improve circuit reliability, and delay degradation analysis. The propagation of transient faults in combinational circuits can be efficiently and accurately modeled using probabilistic symbolic forms the foundation of a computational framework. This framework

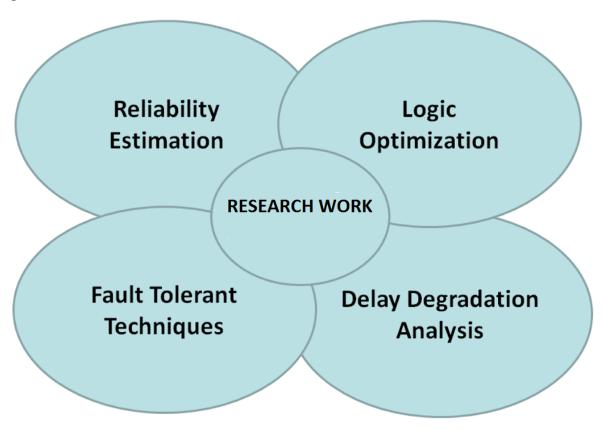

can include (i) modeling of transient fault propagation, irrespective of the transient fault origin, (ii) the impact of variability sources on fault propagation and (iii) reliability driven logic optimization and fault tolerant techniques. The main research work presented as part of this thesis is divided into four significant areas as illustrated in Fig. 1.1. More details are provided in the next sub-section.

Fig. 1.1 Four significant areas of current research

#### 1.2.3 Circuit Representation and Modification

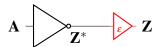

Over the years, several academic EDA tools [25] [26] [27] have been proposed that provide a programming environment and a stable platform for research in logic synthesis, and power optimization as well as to implement new algorithms. In all these academic tools, data structures and algorithms largely determine the tool efficiency in providing support for implementing new features. AIG is employed as the data structure and ABC as the platform to develop and implement all the reliability related algorithms. ABC [28], which is a logic synthesis and verification tool that performs scalable logic optimization based on And-Invert-Graph(AIG) [29].

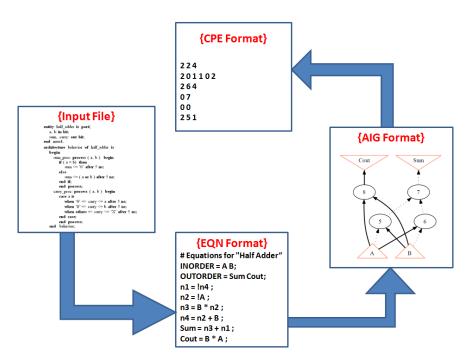

Fig. 1.2 Different Data-structures

As part of the research, A tool has been developed that converts the input Verilog file into multiple internal formats as described in Fig. 1.2. The tool accepts high-level description (e.g., Berkeley Logic Interchange Format(BLIF), VHSIC Hardware Description Language(VHDL), Verilog) of a generic function as an input. It then translates it into the ".eqn" intermediate format and then generates the corresponding AIG representation. During the process of modifying the circuit representation, the logical equivalence of the original and new circuit is guaranteed by adopting various formal verification techniques.

#### 1.2.4 Reliability Estimation and Analysis

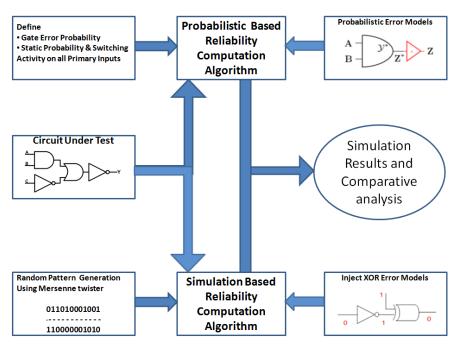

Reliability analysis of logic circuits deals with the computation of the impact that gate errors might have on the circuit Primary Outputs(PO). The reliability measures and models (error/energy/power/etc.) are central to designing tools and methodologies. Plain reliability analysis based on HSPICE Monte Carlo simulation is not feasible on real-time circuits due to its prohibitive computation time and computing resource requirements. Several analytical approaches were previously proposed [30]. In this research, the circuits are represented in the AIG format creating the need for novel reliability computation algorithm, with the prime focus being AND and INVERTER gates. Two different methodologies are devised based on simulation-based approach and the probabilistic error gate model-based approach. Fig. 1.3 depicts the complete flow of the reliability analysis tool.

Fig. 1.3 Reliability Estimation Flow

Both the probabilistic and simulation-based reliability computation algorithms are applied on the circuit under test. The probabilistic based methodology emulated all the gates with the probabilistic error models and based on input switching activity, static probability, and gate error values, it computes the expected reliability of the output node. The simulation-based algorithm appends all the gates with an XOR gate to randomly toggle the output value to insert an error randomly. To overcome the default random generator function limitations, the Mersenne twister is used to generate highly random test patterns, which highly facilitates in computing the final output reliability [31]. The final output reports from both these models are compared to define the accuracy of the probabilistic gate error model. Though very accurate, the simulation methodology is very expensive regarding execution time, which might preclude its utilization on large circuits. Eventually, it is a trade-off between accuracy and speed when choosing one of these two algorithms.

#### 1.2.5 Reliability Driven Logic Optimization

Logic optimization and synthesis is the process of taking in a higher-level circuit representation and translating it into real logic gates. The main focus is to develop reliability driven systematic synthesis and optimization methodologies, ideally culminating in multi-objective circuit design optimization. The introduction of reliability as circuit figure of merit leads to a 4-dimensional (area, delay, power, reliability) solution space and has a tremendous influence

on the complexity of the synthesis process. As part of the research, two optimisation techniques employing primitive rewriting techniques [32] are developed with improving circuit reliability as the end goal. A rewriting algorithm is a methodology where small sections of the circuit are identified and are replaced with logical functional equivalent's that improves given constraint(reliability in this case).

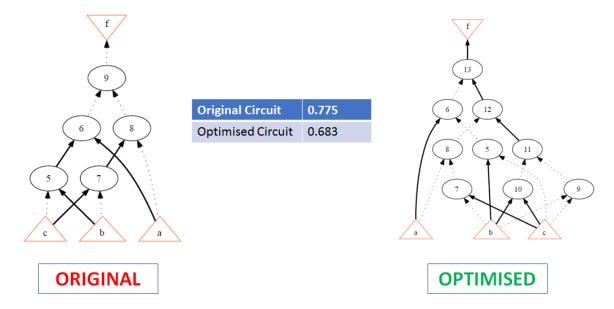

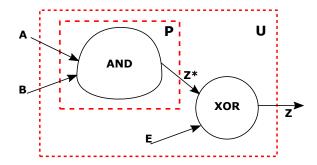

Fig. 1.4 Reliability Driven Circuit Optimization Example

Fig. 1.4 depicts the optimised circuit derived from the original circuit after employing a set of logic transformations. The reliability estimation algorithm is used to pick the logic transformation that provides the highest reliability improvement. This process continued until no more rules can be applied on a given node. The logic network describing the function is updated during each iteration of the optimization algorithm. The similar set of operations are employed on all the nodes in the circuit thereby obtaining the most optimised circuit.

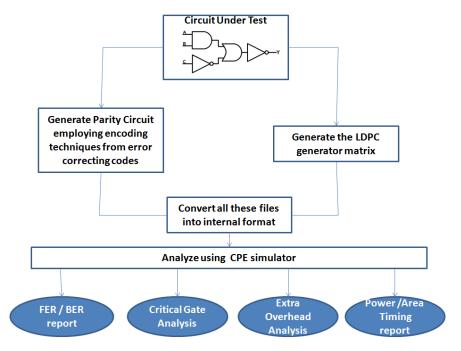

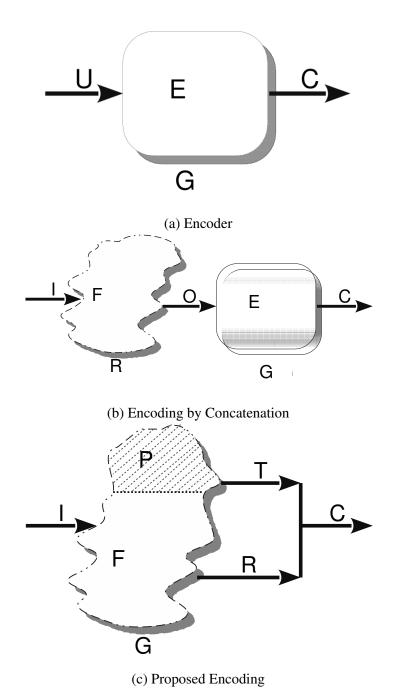

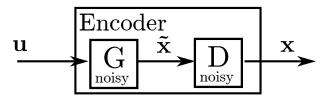

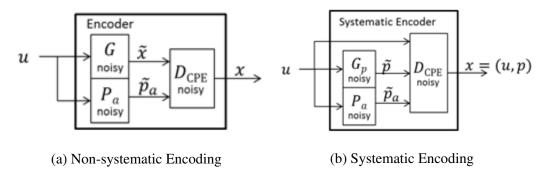

#### 1.2.6 Fault Tolerant Graph Augmentation

Fault tolerant technique is a fundamental study of integrating error-correcting codes into the structural (Boolean network) implementation of the circuit logical functionality that improves circuit reliability. The focus of this approach is not on changing the combinational logic but on augmenting it to enable the retrieval of the correct output even if errors have occurred inside the circuit. This work introduces new reliability driven fault tolerant methodology known as Codeword Prediction Encoder (CPE). Redundant logic is added by using Error Correcting Codes(ECC) based architectures thus enabling to retrieve the correct output and thereby

improving the circuit reliability. Some potential links between the logical representation of a digital circuit and error correcting codes to generate fault tolerant implementation of the logical functionality of the circuit are studied.

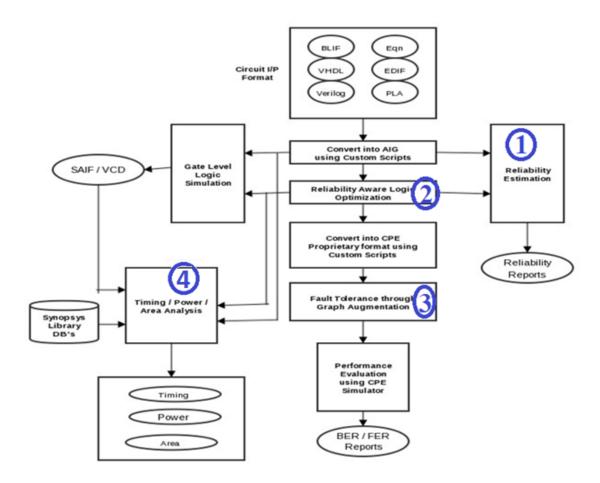

Fig. 1.5 The Codeword Prediction Encoder(CPE) flow

CPE methodology takes the input function netlist and translates it into an AND Invert set of equations for further manipulation and analysis of the number of gates and longest path modifications as shown in Fig. 1.5. An ECC scheme informs the logic network annotation. The two classes of logic functions identified in the research are linear or non-linear functions where linear functions can be described similarly as a linear code(vector-matrix multiplication). The resulting annotated logic network is then decoded using an additional logic network associated with the chosen ECC.

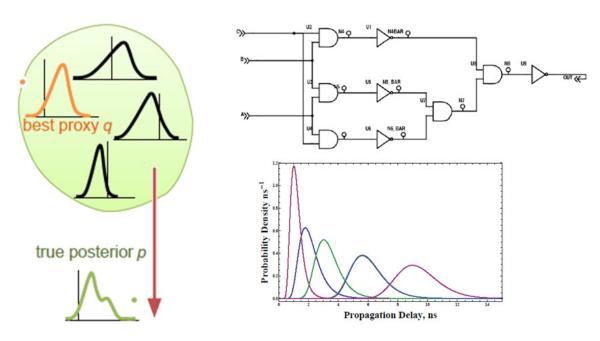

#### 1.2.7 PDF based Delay Degradation Analysis

In semi-custom VLSI design flow, predefined standard logic cells are characterized to generate timing models that are extensively used in Static Timing Analysis(STA) [33]. STA computes timing delays on the critical paths that determines the maximum clock frequency at which the chip can safely operate. A comprehensive delay approximation methodology based on Inverse Gaussian Distribution(IGD) is proposed.

The main idea behind the proposal is first to gather the necessary gate key parameters utilizing Monte Carlo simulations and then linearly extrapolate (propagate) them through the

Fig. 1.6 PDF propagation and Methodology

logic network at the circuit level as shown in Fig. 1.6. A Look Up Table(LUT) for all the gates in the library is maintained to capture these critical parameters. The effect of fan-out value and input transition time on the gate delay is also taken into consideration and applies to the following components as well. The proposed analytical PDF delay model is highly accurate for both nominal and sub-threshold supply voltages. Experimental results indicate that the proposed method provides a very close match with Monte-Carlo(MC) simulations reporting the worst case average error of less than 3% while saving run-time by up-to 50 times order of magnitude.

#### 1.3 The Research Framework

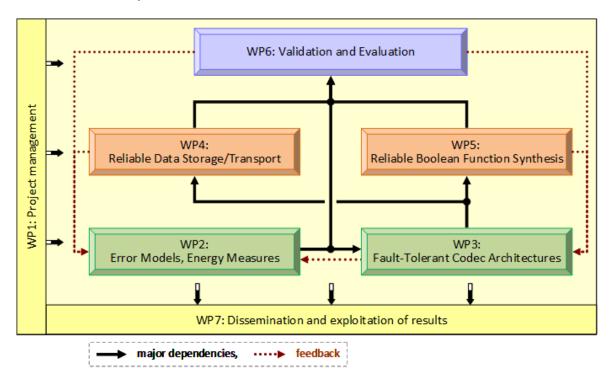

This research work is part of a bigger project called i-RISC(www.i-risc.eu). The i-RISC project targets a foundational breakthrough towards reliable, fault-tolerant chip design from unreliable components, which is a crucial issue for the long-term development of computing technology. The research novelty emerges from the synergistic utilization of (1) information theory and coding techniques, traditionally utilized to improve the communication systems reliability and (2) circuit and system theory and design techniques to create reliable/ predictable hardware. The aim is to enable the development of innovative fault-tolerant solutions at both circuit and system level that are fundamentally rooted in mathematical models, algorithms, and techniques from information and coding theory. Fig. 1.7 describes

the five major components involved in this project. This research strictly confines to reliable Boolean function synthesis.

Fig. 1.7 The IRISC Project Details

The design flow that aims to connect different problems addressed through this research consists of several academic tools developed in-house, within the scope of the current research, that are integrated alongside several industrial tools. The complete design flow is presented in Fig. 1.8 connecting the four major contributions described earlier. The design flow outlines the path of a digital circuit from the Register Transfer Level(RTL) to the final error resilient technology mapped gate-level netlist followed by reliability, power, delay and area reports. Some of the important steps in this flow are as follows:

- Step 1: Converting the accepted form (BLIF, Verilog, VHDL) of input file format into AIG.

- Step 2: Run the Reliability driven logic optimization tools to synthesize gate level netlist.

- Step 3: Reliability analysis is performed to compute the improvement achieved regarding error resilience. Reliability details of every node in the network are dumped into an output file.

1.4 Conclusions

• Step 4: Gate level simulations are performed to dump the switching activity details. These are saved in the standard Switching Activity Interchange Format(SAIF) format.

- Step 5: Using netlist from steps 1 and 2 and the switching reports from step 4, Synopsys design compiler tool is invoked to perform the power, area and timing analysis. Comparative studies are performed to report the savings or overhead because of the new netlist.

- Step 6: The LDPC encoding scheme is implemented on the resulting reliability optimised netlist. Its functionality drives the parity circuit augmented onto the circuit under test.

- Step 7: Convert all the netlist combinational circuit, parity, and the LDPC decoder into the internal proprietary format understood by the Codeword Prediction Encoder(CPE) simulator.

- Step 8: The CPE simulator is invoked to perform the encoding decoding simulations. All the reports comprising of the Frame Error Rate(FER)/Bit Error Rate(BER) analysis, critical node count, etc. are reported at this stage.

- Step 9: Perform delay degradation analysis on both the original netlist and the optimised netlist. This works as another yardstick to validate the synthesis tool.

#### 1.4 Conclusions

In this chapter, the bigger picture of the challenges posed by miniaturization and reliability is presented. Some introductory topics which provide a backdrop for the research presented in subsequent chapters were covered. Reliability was introduced, followed by a discussion of different types of errors which helped in identifying several challenges associated with CMOS scaling. Also, the larger framework, namely iRISC FET-Open project, in which the current research is part of, is also presented.

Chapter 2 provides a literature survey covering aspects of the current research. Chapter 3 describes the reliability estimation techniques and the theoretical background involved in this thesis. Chapter 4 describes the reliability driven optimization techniques for combinational circuits. Chapter 5 describes the Low-Density Parity Check(LDPC) codes based fault tolerant technique called Codeword Prediction Encoder. Chapter 6 describes the Probability Density Function(PDF) based delay degradation analysis and the corresponding methodology. Finally, chapter 7 concludes this thesis by providing directions for future research.

1.4 Conclusions 12

Fig. 1.8 The Complete Flow

### Chapter 2

### Reliability in Logic Circuit Design

The ongoing miniaturization of data processing and storage devices and the imperative of low-energy consumption can only be sustained through low-powered components. Lower supply voltages and variations in the technological process of emerging nanoelectronics devices make them inherently unreliable. Consequently, the nanoscale integration of chips built out of unreliable components has emerged as one of the most critical challenges for the next-generation electronic circuit design. To make such nanoscale integration economically viable, new solutions for efficient and fault-tolerant data processing and storage must now be invented.

The current research targets a foundational breakthrough towards reliable, fault-tolerant chip design from unreliable components, which is a crucial issue for the computing technology long-term development. The research novelty emerges from the synergistic utilization of (1) information theory and coding techniques, traditionally utilized to improve the communication systems reliability and (2) circuit and system theory and design techniques, in order to create reliable/ predictable hardware. The aim is to enable the development of innovative fault-tolerant solutions at both circuit- and system-level that are fundamentally rooted in mathematical models, algorithms, and techniques from information and coding theory.

#### 2.1 Introduction

Device reliability was first studied in the early sixties when increasingly complex integrated systems were developed and fabricated. Conferences such as the first international reliability physics symposium (IRPS 1962, Chicago) was the first attempts to bring engineers and scientists together from all over the World to study the physics behind various failure effects. To overcome scaling limitations of devices fabricated in ultra-scaled CMOS processes, changes in device structures, processing materials, and processing conditions have been

2.1 Introduction

introduced. These changes have drastically increased the complexity of nanometer CMOS technologies.

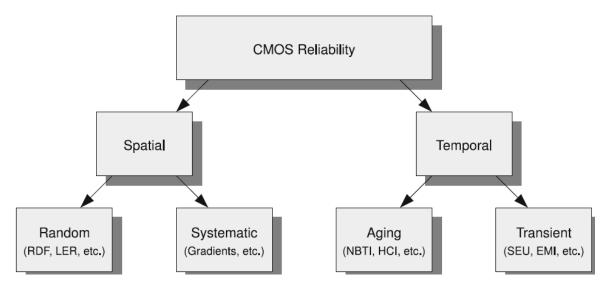

Fig. 2.1 Classification of Reliability

Fig. 2.1 illustrates how nanometer CMOS reliability issues can be categorized into spatial and temporal unreliability effects. Spatial unreliability effects are immediately visible right after production and are fixed in time. Spatial unreliability effects can be random (e.g., Random Dopant Fluctuations (RDF), Line Edge Roughness (LER), etc.) or systematic (e.g., gradient effects, etc.). The results depend on the circuit layout, the neighboring environment, process conditions, and the impact the geometry and structure of the circuit and can lead to yield loss. This yield loss can be functional or parametric, i.e., resulting in malfunctioning circuits or circuits with degraded performance respectively. Temporal unreliability effects, on the other hand, are time-varying and change depending on operating conditions such as the operating voltage, temperature, switching activity, presence and activity of neighboring circuits. A difference is made between wear out or aging effects (e.g., Hot Carrier Injection (HCI), Negative Bias Temperature Instability(NBTI), etc.) and transient effects (e.g., Electro-Magnetic Interference (EMI), Single Event Upsets (SEU), etc.) [9] [34].

#### 2.1.1 Understanding Reliability

A clear understanding of several concepts and terminology related to reliability is needed to proceed with the understanding of the methodologies which are applied to guarantee optimal operation of VLSI systems, fault tolerance, and circuit architectures implementing them. Basic terms such as reliability, fault tolerance, faults, and fault modeling are introduced and explained in detail. For more in-depth details, refer to [35].

2.1 Introduction

**Reliability** is defined according to IEEE [36] as the ability of a system or component to perform its required functions under stated conditions and for a specified period. The process yield of a manufacturing process is defined as the fraction, or percentage, of acceptable parts among all parts that are fabricated [35]. A system failure occurs or is present when the service provided by the system differs from the specified service or the service that should have been offered. The following three terms are crucial and related to system failure and thus need to be clearly defined, which are named defect, error, and fault.

A **defect** in an electronic system is the unintended difference between the implemented hardware and its intended design. Some typical defects of VLSI chips may be related to process, material, aging effects. The existence or emergence of defects reduces yield [35]. A wrong output signal produced by a defective system is called an **error**. An error is an effect whose cause is some defect. Errors can be classified into three main groups, namely permanent, intermittent, and transient errors, according to their stability and concurrence [35]. A **fault** is a representation of a defect at the abstracted functional level. A fault is present in the system when a physical difference is observed between the "good" or "correct" system and the actual system. The most common faults in a chip are spots and bridging faults caused by silicon impurities, lithography, and process variations [35].

Faults, errors, and failures operate according to a specific mechanism often known as the Fault-Error-Failure chain [37]. In other words, the failure occurs when the delivered service deviates from the specified function, because the system was erroneous, and the cause of an error is a fault. An error is a manifestation in the system of a fault, and a failure is a manifestation on the service of an error [38]. More specifically, one can classify hardware faults that occur during the system operation by their duration into [39]:

- Permanent faults, caused by irreversible device failures within a component due to damage, fatigue, or improper manufacturing. Once a permanent fault occurs, the faulty component can be restored only by replacement, or if possible, by repair.

- Transient faults, triggered by environmental conditions (e.g., voltage fluctuations, electromagnetic interference, radiation, etc.). These events typically have a short duration, and rarely do any lasting damage to the component affected, although they can induce an erroneous state in the system for an abbreviated period. Studies have shown that transient faults occur far more often than permanent ones and are also much harder to detect [5].

- Intermittent faults, caused by unstable hardware or different hardware states, tend to oscillate between periods of erroneous activity and dormancy. Replacement or redesign can repair them.

2.1 Introduction 16

Since the focus of this research is on transient faults modeling, and the analysis of their impact on circuit reliability, the following sections describe in more details the sources of transient faults, their implications for logic circuit reliability.

#### 2.1.2 Transient faults in logic circuits

Internal or external events can cause transient faults, and generally, manifest themselves as a transient pulse at the output of a logic cell. Externally induced transient faults, stemming from cosmic rays, reaction with Earth's atmosphere or radioactive decay of device packaging, have received most of the attention in recent years, and are claimed to be one of the major concerns for future technology nodes [14] [15].

If a transient fault is generated in a memory cell, or in a memory element (flip-flop, latch), an error resulting from this fault can immediately occur. Otherwise, the created pulse propagates through the circuit and causes an error once the memory cell or memory element latches it. An error caused by a transient fault is often called "soft", because if a failure results in the end effect of this fault, only the data is destroyed. In contrast to this, "hard" errors stem from permanent or intermittent faults that result from the damage in the internal structure of semiconductor material [5].

Once a transient fault occurs at the output of a gate within the circuit, it may propagate through the circuit on more than one path, resulting in re-convergent glitches at different inputs of the same gate in the fanout cone of original gate, or causing more than one soft error at the outputs of the circuit. A significant aspect of transient fault propagation through logic circuits is the set of masking factors that can prevent the fault from propagating to the outputs of the circuit. These masking factors, logical, electrical and latching-window masking [40], are described below.

Logical masking: Logical masking refers to the ability of a logic gate to tolerate faults occurring on its inputs on account of its inherent nature/functionality [40]. Consider a two-input AND gate. When the transient fault propagates to the input port of this gate, on its path through the circuit, if the other input port is tied low controlling value, it would mask the fault from propagating through the gate and, consequently, prevent it from propagating further on that path. It is important to note that different gate types have different logical masking strength. In other words, an inverter will always logically propagate a glitch, since there is only one input carrying the glitch. But, the probability of propagating the glitch through AND, OR, NAND and NOR gate is the same and depends on the number of inputs, while again, a glitch will always propagate through gates XOR and XNOR due to their logic function.

Electrical masking: Electrical masking happens when subsequent logic gates attenuate the voltage transient resulting from a particle strike because of the electrical property of the logic gate [40]. Due to the relation between electrical properties of gates and the size of the pulse representing the transient fault, the fault would be attenuated by the gates it propagates through. This may result in the disappearance of the fault before it reaches any or some of the outputs of the circuits, or it may decrease the duration and amplitude of the fault such that it is not large enough to cause a bit flip in a memory cell or memory element, once it arrives at their inputs. Gates that have more substantial delays, such as XOR and XNOR gates, will attenuate glitches more, while an inverter usually attenuates glitches much less. If the glitch is tiny, compared to the delays of gates it propagates through, it will always be attenuated. On the other hand, if the glitch is very large, compared to gate delays, it will still propagate to outputs.

Latching-window masking: When the transient fault arrives at the input of a memory cell or a memory element, it will be latched only if it arrives on time to satisfy setup and hold time conditions [40]. This depends on the time when the fault occurred inside the circuit, on the location where it occurred (that is, how far that location is from the memory cell or memory element), on the size of the pulse at the occurrence site, the clock cycle and the setup and hold time values.

# 2.2 Reliability Estimation

Logic circuit reliability analysis attempts to evaluate the impact that the gate errors could have on the circuit Primary Outputs (PO) correctness. Von Neumann pioneered the art of probabilistic error analysis and defined any system to be reliable only if the probability of its correct output is greater than a certain threshold [41]. The traditional approach to reliability analysis begins with simple SPICE simulations to estimate the circuit error probability. However, for most of the practically relevant circuits, simple reliability analysis based on SPICE Monte Carlo simulations is not feasible due to prohibitive computation time and excessive resource requirements. The impact of faults can be investigated through simulation. While faults can be simulated accurately only at the circuit level of abstraction, there are existing proposals that inject the fault at a high level of abstraction for early performance exploration [42] [43].

Complementing the simulation methods, various probabilistic analytical approaches to evaluate the circuit reliability have been proposed. The Probability Element (ProxEl) method was introduced in [44] to alleviate the typical problems encountered by Monte Carlo simulation and partial differential equations. In [45], the authors introduced the

Probabilistic Transfer Matrices (PTM) formalism, which relies on an exhaustive listing of the gate inputs/outputs, allowing simultaneous and exact reliability evaluation over all possible input combinations. Another analytical reliability estimation approach relies on the Probabilistic Gate Model (PGM) [46] [47] [48]. While it is applicable to potentially any gate and failure, the method assumes that the gate input/output signals are statistically independent, which leads to approximate reliability results. In [48], the correlations in the input signals or caused by re-convergent fan-outs are addressed by sequentially decomposing and recursively treating each fan-out, at the expense of increasing the computational time exponentially with the number of re-convergent fan-outs. In [30], the authors propose three scalable algorithms for reliability assessment. Notably, the single-pass reliability analysis algorithm can: (i) accurately evaluate the reliability of circuits without convergent fan-out and (ii) to assess approximately the reliability of circuits exhibiting spatial correlations, by computing pairwise correlation coefficients of dependent signals. The algorithm is based on expressing the error at a gate output as the cumulative effect of the intrinsic, local gate error component and an error component attributed to the failures of the gates in its fan-in cone. The single pass method is extended in [49] to multiple passes for reliability evaluation of sequential circuits. The Signal Probability Reliability Analysis (SPRA) method was proposed in [50] [51] embeds the cumulative effect of multiple, simultaneous errors in a circuit, in the form of a bit-flip error at the output of a faulty gate.

Also, Bayesian Networks (BNs) have been applied in the context of circuit reliability evaluation [52] [53]. BNs, whose underlying semantics are based on directed graphs, allows one to capture both the temporal and spatial circuit dependencies comprehensively, providing an exact and minimal probabilistic model for reasoning and inference in causal logic networks. The Markov Random Fields (MRFs) based reliability evaluation approach presented in [54], employs the Gibbs distribution to characterize the reliability in terms of entropy and the noise in terms of thermal energy. While being suitable for reliability assessment of small circuits or of conventional redundant architectures, such as NAND multiplexing and triple modular redundancy [55], for arbitrary multilevel logic circuits, the MRF-based approach becomes computationally intensive because the minimization technique in the Gibbs distribution function has a substantial number of variables.

In general, the reliability estimation techniques are based on either simulation method or probabilistic methodology. The complexity and accuracy of simulation-based techniques strongly depend on the scale of circuit and test vector selection [52]. As discussed, several analytical methods such as those using Probabilistic Transfer Matrices(PTMs) [56], Probabilistic Gate Models(PGMs) [48] and Probabilistic Decision Diagrams(PDDs) [57] have already been proposed to investigate behavior of circuits under faults. PTM suffers from

massive matrix storage and manipulation overhead that results in its inapplicability to large circuits. Another approach based on Bayesian networks was proposed in [53]. Though they apply to medium scale circuits, manipulating Bayesian networks for large circuits has been seen to be intractable. One of the best approaches to date was described in [30], with minor limitations. For example, the observability based algorithm efficiency is directly linked to the ability to observe internal nodes. From VLSI testing principles, it is understood that as the circuits grow larger and larger, the complexity of observing a node turns out to be more time-consuming. In the same work, the single pass reliability analysis algorithm is proposed which provides excellent results for circuits without re-convergent fan-out. But, the computational complexity increases as the number of correlation coefficients increases.

# 2.3 Reliability Aware Logic Synthesis

Traditional logic synthesis methodologies and EDA tools are centered on fulfilling timing, power, and area constraints or on achieving acceptable trade-offs among those [Pedram96] [Mehrotra11]. However, as the Complementary Metal-Oxide-Semiconductor (CMOS) technology entered the nanometer era, such an approach cannot cover any longer all the relevant design aspects. Technology scaling has precipitated higher operating speeds, lower operating voltages, and lower operating noise margins; all of which contribute to reduced switching energies, allowing legitimate logic signals to be readily overwhelmed by single-event-induced charge-collection transients [Dodd03]. Nanotechnology specific issues, e.g., power supply voltage (Vdd) reduction, the higher impact of the process parameter and temperature variations, resulting in increased device failure rates, making CMOS Integrated Circuits (ICs) less reliable [Borkar05] [Constantinescu03].

In the era of deep sub-micron CMOS technology, spatial and temporal variability is resulting in less predictable device behavior [9]. Stochastic logic delay variation on par with the nominal delay can occur due to the local (or intra-die or within-die) variations in transistor  $V_{th}$  [58]. Further, circuits operated in the near or sub-threshold region to achieve substantial power savings results in an increased amount of output Soft Error Rate (SER). Given the combined effect of variability and aging mechanisms, it is evident that the state of the art CMOS gates is highly unreliable. A variety of system/circuit level techniques like Dynamic Reliability Management (DRM), and inexact computing [59], [60], [61] have already been proposed to overcome reliability related concerns. These techniques are at a higher abstract level and do not leverage the significant gains that are achieved by employing graph modification/altering techniques. Reliability driven logic synthesis is one area that has not received much attention but is gaining a lot of importance

in the last few years. In [62], the circuit output Soft Error Rate (SER) is reduced through localized circuit restructuring by taking advantage of don't care based re-synthesis and local rewriting. In [63], a technique to improve the circuit robustness to soft errors based on Redundancy Addition and Removal (RAR) by eliminating gates with a large contribution to the overall SER is proposed. Efficient algorithms for synthesizing approximate circuits for simultaneous masking of logical and timing errors were proposed in [64]. Automatic Test Pattern Generation(ATPG) based rewiring method, yet structurally-different implementations to reduce the SER was implemented in [65].

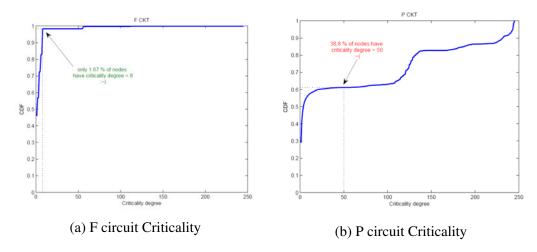

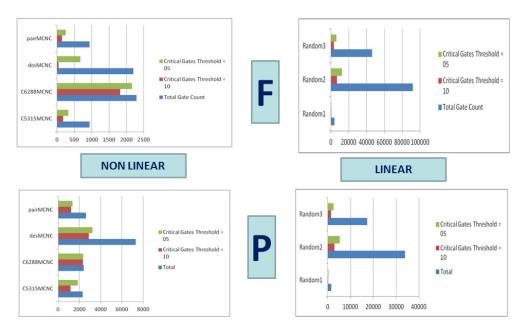

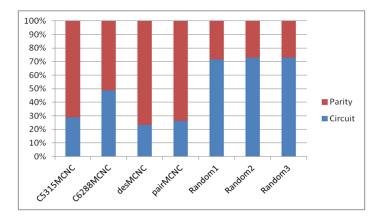

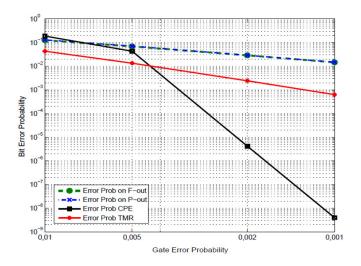

# **2.4** Fault Tolerant Techniques