## DESIGN FOR TESTABILITY METHOD AT REGISTER TRANSFER LEVEL

NORLINA PARAMAN

A thesis submitted in fulfilment of the requirements for the award of the degree of Doctor of Philosophy (Electrical Engineering)

> Faculty of Electrical Engineering Universiti Teknologi Malaysia

> > OCTOBER 2016

To my beloved family.

#### ACKNOWLEDGEMENT

Alhamdulillah, thanks to Allah SWT to give me strength and good health for making this project successful. Special thanks goes to my supervisors Assoc. Prof. Dr. Ahmad Zuri Sha'ameri, Dr. Ooi Chia Yee and Prof. Dr. Hideo Fujiwara, for allowing me to carry out this study under their supervision and for their inspiration, encouragement, knowledge, support and constructive comments throughout this work. Not forget to my husband, daughter, parents and siblings for their pray, love and encouragement to finish my studies. Special thanks to my research colleagues: Ismahani, Rabia, Zahara, Hasliza and Izam to all of those who supported me in any aspect during the completion of the project.

#### ABSTRACT

The testing of sequential circuit is more complex compared to combinational circuit because it needs a sequence of vectors to detect a fault. Its test cost increases with the complexity of the sequential circuit-under-test (CUT). Thus, design for testability (DFT) concept has been introduced to reduce testing complexity, as well as to improve testing effectiveness and efficiency. Scan technique is one of the mostly used DFT method. However, it has cost overhead in terms of area due to the number of added multiplexers for each flip-flop, and test application time due to shifting of test patterns. This research is motivated to introduce non-scan DFT method at register transfer level (RTL) in order to reduce test cost. DFT at RTL level is done based on functional information of the CUT and the connectivity of CUT registers. The process of chaining a register to another register is more effective in terms of area overhead and test application time. The first contribution of this work is the introduction of a non-scan DFT method at the RTL level that considers the information of controllability and observability of CUT that can be extracted from RTL description. It has been proven through simulation that the proposed method has higher fault coverage of around 90%, shorter test application time, shorter test generation time and 10% reduction in area overhead compared to other methods in literature for most benchmark circuits. The second contribution of this work is the introduction of built-in self-test (BIST) method at the RTL level which uses multiple input signature registers (MISRs) as BIST components instead of concurrent built-in logic block observers (CBILBOs). The selection of MISR as test register is based on extended minimum feedback vertex set algorithm. This new BIST method results in lower area overhead by about 32.9% and achieves similar higher fault coverage compared to concurrent BIST method. The introduction of non-scan DFT at the RTL level is done before logic synthesis process. Thus, the testability violations can be fixed without repeating the logic synthesis process during DFT insertion at the RTL level.

#### ABSTRAK

Pengujian litar jujukan lebih kompleks berbanding litar gabungan kerana ia memerlukan jujukan corak ujian untuk mengesan kerosakan di dalam litar jujukan. Kos pengujiannya meningkat dengan kerumitan litar-bawah-pengujian (CUT) jujukan. Oleh itu, konsep rekabentuk untuk pengujian telah diperkenalkan untuk mengurangkan kerumitan pengujian dan juga untuk memperbaiki keberkesanan dan kecekapan pengujian. Teknik pengimbas adalah satu kaedah rekabentuk untuk kebolehujian yang selalu digunakan. Walau bagaimanapun, ia mempunyai overhed kos dari segi kawasan kerana bilangan tambahan pemultipleks untuk setiap flipflop, dan penggunaan masa ujian yang disebabkan oleh penganjakan corak ujian. Motivasi kajian ini memperkenalkan kaedah rekabentuk untuk kebolehujian bukan pengimbas di aras pindahan daftar (RTL) untuk tujuan mengurangkan kos pengujian. Rekabentuk untuk kebolehujian di aras RTL dilakukan berdasarkan maklumat fungsi CUT dan kaitan penyambungan CUT di antara daftar. Proses perantaian daripada satu daftar kepada daftar lain lebih berkesan dari segi overhed kawasan dan penggunaan masa ujian. Sumbangan pertama kerja ini ialah pengenalan kaedah rekabentuk untuk kebolehujian tanpa-pengimbas di aras RTL yang mempertimbangkan maklumat keboleh kawalan dan keperhatian terhadap CUT yang boleh diekstrak daripada huraian RTL. Ia telah dibuktikan melalui keputusan simulasi yang kaedah ini mempunyai liputan kerosakan yang lebih tinggi, sekitar 90%, penggunaan masa ujian yang lebih rendah, penjanaan masa ujian yang lebih rendah dan pengurangan 10% terhadap overhed kawasan berbanding dengan kaedah lain di literatur kebanyakan litar tanda aras. Sumbangan kedua kerja ini ialah pengenalan kaedah ujian-sendiri terbina-dalam di aras RTL yang menggunakan daftar tandatangan berbilang input sebagai komponen ujiansendiri terbina-dalam dan bukannya pemerhati blok logik terbina-dalam serempak. Pemilihan daftar tandatangan berbilang input sebagai daftar ujian berdasarkan algoritma set bucu minimum lanjutan. Kaedah baru ujian-sendiri terbina-dalam ini menghasilkan overhed kawasan yang lebih rendah sebanyak 32.9% dan mencapai liputan kerosakan yang lebih tinggi berbanding dengan kaedah ujian-sendiriterbina-dalam serempak. Pengenalan rekabentuk untuk kebolehujian tanpapengimbas di aras RTL dilakukan sebelum proses sintesis logik. Oleh itu, perlanggaran kebolehujian boleh diperbaiki tanpa mengulangi proses sintesis logik semasa penambahan rekabentuk untuk kebolehujian di aras RTL.

## **TABLE OF CONTENTS**

| CHAPTER | TITLE |                              | PAGE  |

|---------|-------|------------------------------|-------|

|         | DEC   | LARATION                     | ii    |

|         | DED   | ICATION                      | iii   |

|         | ACK   | NOWLEGEMENT                  | iv    |

|         | ABS   | ГКАСТ                        | v     |

|         | ABS   | ГКАК                         | vi    |

|         | TAB   | LE OF CONTENTS               | vii   |

|         | LIST  | OF TABLES                    | xi    |

|         | LIST  | <b>COF FIGURES</b>           | xii   |

|         | LIST  | <b>COF ABBREVIATIONS</b>     | XV    |

|         | LIST  | <b>TOF LISTINGS</b>          | xvii  |

|         | LIST  | <b>TOF SYMBOLS</b>           | xviii |

|         | LIST  | <b>COF APPENDICES</b>        | xix   |

| 1       | INTI  | RODUCTION                    | 1     |

|         | 1.1   | Background                   | 1     |

|         | 1.2   | Problem Statement            | 3     |

|         | 1.3   | Objectives                   | 5     |

|         | 1.4   | Scope of Work                | 5     |

|         | 1.6   | Contributions                | 6     |

|         | 1.7   | Organization of Thesis       | 7     |

| 2       | LITI  | ERATURE REVIEW               | 8     |

|         | 2.1   | Introduction                 | 8     |

|         | 2.2   | Design for Testability (DFT) | 8     |

|     | 2.2.1 Scan-Based DFT                      | 11 |  |  |

|-----|-------------------------------------------|----|--|--|

|     | 2.2.2 Non-Scan Based DFT                  | 12 |  |  |

|     | 2.2.3 Built-in Self-Test                  | 14 |  |  |

| 2.3 | Research Works on DFT                     | 18 |  |  |

|     | 2.3.1 Scan-Based and Non-Scan DFT         | 18 |  |  |

|     | 2.3.2 BIST                                | 25 |  |  |

| 2.4 | Summary                                   | 30 |  |  |

| THR | RU-TESTABLE REGISTER TRANSFER             |    |  |  |

| LEV | VEL CIRCUITS                              | 31 |  |  |

| 3.1 | Introduction                              | 31 |  |  |

| 3.2 | Thru Function                             | 31 |  |  |

| 3.3 | R-graph : Circuit Representation          | 33 |  |  |

| 3.4 | Thru Testability of RTL Circuit 3:        |    |  |  |

| 3.5 | Design for Thru-Testability Algorithm     | 38 |  |  |

|     | 3.5.1 Thru Function Extraction Algorithm  | 41 |  |  |

|     | 3.5.2 R-graph Modelling Algorithm         | 43 |  |  |

|     | 3.5.3 MFVS Derivation Algorithm           | 45 |  |  |

|     | 3.5.3.1 Modified MFVS Algorithm           | 47 |  |  |

|     | 3.5.4 Modified R-graph with DFT Algorithm | 50 |  |  |

|     | 3.5.5 VHDL with DFTT Algorithm            | 51 |  |  |

| 3.6 | Case Study of RTL Design for DFTT         | 52 |  |  |

|     | 3.6.1 GCD Circuit                         | 52 |  |  |

|     | 3.6.1.1 Thru Function Extraction of       |    |  |  |

|     | GCD                                       | 55 |  |  |

|     | 3.6.1.2 R-graph Modelling of GCD          | 55 |  |  |

|     | 3.6.1.3 MFVS Derivation of GCD            | 56 |  |  |

|     | 3.6.1.4 Modified R-graph with DFT of      |    |  |  |

|     | GCD                                       | 57 |  |  |

|     | 3.6.1.5 VHDL with DFTT of GCD             | 59 |  |  |

3

|   |     | 3.6.2 ITC'99 Circuit : b10 (Voting System)  | 61 |

|---|-----|---------------------------------------------|----|

|   |     | 3.6.2.1 Thru Function Extraction of         |    |

|   |     | b10                                         | 65 |

|   |     | 3.6.2.2 R-graph Modelling of b10            | 66 |

|   |     | 3.6.2.3 MFVS Derivation of b10              | 66 |

|   |     | 3.6.2.4 Modified R-graph with DFT           |    |

|   |     | of b10                                      | 67 |

|   |     | 3.6.2.5 VHDL with DFTT of b10               | 68 |

|   | 3.7 | Summary                                     | 72 |

| 4 | RED | UCED BIST-ABLE REGISTER TRANSFER            |    |

|   | LEV | EL CIRCUITS                                 | 73 |

|   | 4.1 | Introduction                                | 73 |

|   | 4.2 | Classification of BIST-able RTL Circuits    | 73 |

|   | 4.3 | Extended R-graph Modelling                  | 79 |

|   | 4.4 | Optimization of Cost Area                   | 80 |

|   | 4.5 | Extended Modified MFVS                      | 82 |

|   | 4.6 | Reduced BIST Algorithm                      | 83 |

|   |     | 4.6.1 Extended R-graph Modelling Algorithm  | 85 |

|   |     | 4.6.2 Extended Modified MFVS Algorithm      | 88 |

|   | 4.7 | Case Study of RTL Design for Reduced BIST : |    |

|   |     | GCD Circuit                                 | 89 |

|   |     | 4.7.1 Extended R-graph of GCD               | 89 |

|   |     | 4.7.2 Extended Modified MFVS of GCD         | 90 |

|   |     | 4.7.3 VHDL with Reduced BIST of GCD         | 90 |

|   | 4.8 | Summary                                     | 93 |

| 5 | SIM | ULATION RESULTS                             | 94 |

|   | 5.1 | Introduction                                | 94 |

|   | 5.2 | Benchmark Circuits                          | 94 |

|   | 5.3 | Simulation Setup                            | 96 |

|   | 5.4 | Simulation Results of DFTT                  | 97 |

|     | 5.4.1  | Case Study : GCD Circuit                | 97  |

|-----|--------|-----------------------------------------|-----|

|     |        | 5.4.1.1 Functional Simulation Results   |     |

|     |        | of GCD                                  | 97  |

|     |        | 5.4.1.2 ATPG Results of GCD             | 98  |

|     | 5.4.2  | Case study : ITC'99 Benchmark Circuits  | 103 |

|     |        | 5.4.2.1 Functional Simulation Results   |     |

|     |        | of b10 (Voting System Circuit)          | 103 |

|     |        | 5.4.2.2 ATPG Results of ITC'99 Circuits | 104 |

| 5.5 | Simul  | ation Results of Reduced BIST           | 110 |

|     | 5.5.1  | Case Study : GCD Circuit                | 111 |

|     |        | 5.5.1.1 Functional Simulation Results   |     |

|     |        | of GCD                                  | 111 |

|     |        | 5.5.1.2 ATPG Results of GCD             | 112 |

|     | 5.5.2  | Simulation Results of ITC'99 Circuits   | 114 |

| 5.6 | Comp   | parison of Two Proposed DFT Methods     |     |

|     | (DFT1  | and Reduced BIST)                       | 121 |

| 5.7 | Sumn   | hary                                    | 123 |

|     |        |                                         |     |

| CON | CLUSI  | ON                                      | 124 |

| 6.1 | Introd | uction                                  | 124 |

| 6.2 | Contr  | ibutions                                | 124 |

|     | 6.2.1  | RTL Non-Scan DFT Method                 | 124 |

|     | 6.2.2  | RTL BIST Method                         | 125 |

| 6.3 | Direct | tions for Future Works                  | 126 |

|     | 6.3.1  | Combining Both Proposed Methods         | 126 |

|     | 6.3.2  | Considering Power Consumption           | 126 |

|     | 6.3.3  | Reducing Pin Overhead                   | 127 |

|     | 6.3.4  | Test Development Time                   | 127 |

| 6.4 | Summ   | nary                                    | 127 |

| REFERENCES     | 128 |

|----------------|-----|

| Appendix A - D | 134 |

# LIST OF TABLES

| TABLE NO. | TITLE                                              | PAGE |

|-----------|----------------------------------------------------|------|

|           |                                                    |      |

| 2.1       | Test sequence of $p(x) = 1 + x + x^3$              | 16   |

| 2.2       | Operation of CBILBO                                | 18   |

| 2.3       | Summary of non-scan DFT method at RTL              | 23   |

| 2.4       | Summary of BIST at RTL                             | 29   |

| 5.1       | Characteristics of GCD                             | 95   |

| 5.2       | Characteristics of ITC'99 benchmark circuits       | 96   |

| 5.3       | Comparison on ATPG results of GCD                  | 99   |

| 5.4       | Comparison on fault coverage (%)                   | 105  |

| 5.5       | Comparison on area overhead                        | 107  |

| 5.6       | Comparison on test application time (clock cycles) | 108  |

| 5.7       | Comparison on test generation time (second )       | 109  |

| 5.8       | Comparison on pin overhead                         | 110  |

## LIST OF FIGURES

| FIGURE NO | . TITLE                                       | PAGE |  |

|-----------|-----------------------------------------------|------|--|

| 1.1       | Testing flow in VLSI realization process      | 3    |  |

| 2.1       | Design flow for DFT insertion at gate level   | 10   |  |

| 2.2       | Design flow for DFT insertion at RTL          | 10   |  |

| 2.3       | Scan-based DFT structure                      | 12   |  |

| 2.4       | Improved controllability by adding MUX        | 13   |  |

| 2.5       | Improved observability by adding AND gate and |      |  |

|           | XOR gate                                      | 14   |  |

| 2.6       | BIST architecture                             | 15   |  |

| 2.7       | An LFSR of $p(x) = 1 + x + x^3$               | 15   |  |

| 2.8       | Response analyser using LSFR                  | 16   |  |

| 2.9       | An architecture of MISR                       | 17   |  |

| 2.10      | An architecture of CBILBO                     | 17   |  |

| 2.11      | Test-per-scan scheme                          | 26   |  |

| 2.12      | Test-per-clock scheme                         |      |  |

| 2.13      | CBILBO solution                               | 27   |  |

| 3.1       | Thru function                                 | 33   |  |

| 3.2       | R-graph                                       | 34   |  |

| 3.3       | Modified R-graph modelling                    | 35   |  |

| 3.4       | Thru path of R-graph                          | 36   |  |

| 3.5       | Thru-testable RTL                             | 38   |  |

| 3.6       | Flowchart of DFTT and its evaluation          | 40   |  |

| 3.7       | Flowchart of thru function extraction         | 42   |  |

| 3.8       | Flowchart of subroutine A (thru function)     | 43   |  |

| 3.9       | Flowchart of R-graph modelling                | 44   |  |

| 3.10 | Flowchart of subroutine A (R-graph)                  | 45 |

|------|------------------------------------------------------|----|

| 3.11 | Compress graph subroutine by Chakradhar's algorithm  | 47 |

| 3.12 | Modified compress graph subroutine                   | 49 |

| 3.13 | Flowchart of modified R-graph with DFT               | 50 |

| 3.14 | Flowchart of VHDL with DFTT                          | 51 |

| 3.15 | Input output block diagram of GCD                    | 52 |

| 3.16 | Functional block diagram of GCD                      | 53 |

| 3.17 | Thru function result of GCD                          | 55 |

| 3.18 | R-graph modelling result of GCD                      | 56 |

| 3.19 | MFVS derivation result using Perl of GCD             | 57 |

| 3.20 | MFVS register of GCD                                 | 57 |

| 3.21 | Thru paths of GCD                                    | 58 |

| 3.22 | Input output block diagram of b10                    | 61 |

| 3.23 | Thru functions result of b10                         | 65 |

| 3.24 | R-graph modelling result of b10                      | 66 |

| 3.25 | MFVS register of b10                                 | 67 |

| 3.26 | Thru path of b10                                     | 68 |

| 4.1  | Primitive BIST-able RTL circuit                      | 74 |

| 4.2  | Concurrent BIST-able RTL circuit                     | 76 |

| 4.3  | Reduced BIST-able RTL circuit                        | 78 |

| 4.4  | Extended R-graph                                     | 80 |

| 4.5  | Area overhead for 1-bit register of MISR             | 81 |

| 4.6  | Area overhead for 1-bit register of transparent MISR | 81 |

| 4.7  | An extended R-graph with cost area                   | 91 |

| 4.8  | Reduced BIST and its evaluation                      | 84 |

| 4.9  | Flowchart of extended R-graph modelling              | 85 |

| 4.10 | Flowchart of subroutine A (extended R-graph)         | 86 |

| 4.11 | Flowchart of subroutine B (extended R-graph)         | 87 |

| 4.12 | Flowchart of extended modified MFVS                  | 88 |

| 4.13 | Extended R-graph result                              | 89 |

| 4.14 | Extended modified MFVS result                        | 90 |

| 5.1  | Functional simulation of original GCD circuit        | 98 |

|      |                                                      |    |

| 5.2  | Functional simulation of modified GCD circuit with |     |

|------|----------------------------------------------------|-----|

|      | DFTT                                               | 98  |

| 5.3  | ATPG result on fault coverage of DFTT              | 99  |

| 5.4  | Synthesis report on area of DFTT                   | 100 |

| 5.5  | Synthesis report on area of original circuit       | 100 |

| 5.6  | Test pattern generated from Tetramax tools         | 102 |

| 5.7  | Result on test application time of GCD_DFT circuit | 102 |

| 5.8  | Result on test application time of original GCD    |     |

|      | circuit                                            | 103 |

| 5.9  | Functional simulation of original b10              | 104 |

| 5.10 | Functional simulation of modified b10 circuit with |     |

|      | DFTT                                               | 104 |

| 5.11 | Synthesis report on fault coverage of b03          | 106 |

| 5.12 | Synthesis report on area of b03                    | 107 |

| 5.13 | Functional simulation of original GCD              | 112 |

| 5.14 | Functional simulation of modified GCD circuit with |     |

|      | reduced BIST                                       | 112 |

| 5.15 | Area overhead of GCD                               | 113 |

| 5.16 | Fault coverage versus test application time of GCD | 114 |

| 5.17 | Area overhead for concurrent BIST and reduced BIST | 115 |

| 5.18 | Fault coverage versus test application time of b01 | 116 |

| 5.19 | Fault coverage versus test application time of b02 | 117 |

| 5.20 | Fault coverage versus test application time of b03 | 117 |

| 5.21 | Fault coverage versus test application time of b06 | 118 |

| 5.22 | Fault coverage versus test application time of b09 | 118 |

| 5.23 | Fault coverage versus test application time of b10 | 119 |

| 5.24 | Fault coverage versus test application time of b11 | 119 |

| 5.25 | Fault coverage versus test application time of b13 | 120 |

| 5.26 | Fault coverage versus test application time of b14 | 120 |

| 5.27 | Area overhead for both proposed methods            | 121 |

| 5.28 | Pin overhead for both proposed methods             | 122 |

| 5.29 | Test application time for both proposed methods    | 123 |

## LIST OF ABBREVIATIONS

| AO     | - | Area Overhead                            |

|--------|---|------------------------------------------|

| ATE    | - | Automatic Test Equipment                 |

| ATPG   | - | Automatic Test Pattern Generation        |

| BIST   | - | Built-In Self-Test                       |

| CBILBO | - | Concurrent Built-In Logic Block Observer |

| CLB    | - | Combinational Logic Block                |

| CUT    | - | Circuit-Under-Test                       |

| DFT    | - | Design for Testability                   |

| FF     | - | Flip-Flop                                |

| IC     | - | Integrated Circuit                       |

| ITC    | - | International Test Conference            |

| LFSR   | - | Linear Feedback Shift Register           |

| LBIST  | - | Logic Built-In Self-Test                 |

| MUX    | - | Multiplexer                              |

| MFVS   | - | Minimum Feedback Vertex Set              |

| PI     | - | Primary Input                            |

| РО     | - | Primary Output                           |

| RA     | - | Response Analyser                        |

| RTL    | - | Register Transfer Level                  |

| SFF    | - | Scan Flip-Flops                          |

| TC     | - | Test Control                             |

| TEM    | - | Time Expansion Model                     |

| TTL    | - | Transistor-Transistor Logic              |

| TPG    | - | Test Pattern Generator                   |

| VHDL   | - | Very High Speed Integrated Circuit HDL   |

| VLSI   | - | Very Large Scale Integration             |

|        |   |                                          |

## XOR - Exclusive-OR

# LIST OF LISTINGS

| LISTING NO. |    | . TITLE                       | PAGE |

|-------------|----|-------------------------------|------|

| 3           | .1 | MFVS algorithm                | 46   |

| 3           | .2 | Modified MFVS algorithm       | 48   |

| 3           | .3 | VHDL of GCD                   | 54   |

| 3           | .4 | VHDL with DFTT of GCD         | 60   |

| 3           | .5 | VHDL of b10                   | 64   |

| 3           | .6 | VHDL with DFTT of b10         | 72   |

| 4           | .1 | VHDL with reduced BIST of GCD | 93   |

# LIST OF SYMBOLS

| $X_O$     | - | Inputs of LFSR      |

|-----------|---|---------------------|

| $Z_{0-3}$ | - | Outputs of LFSR     |

| $Q_{0-3}$ | - | State of LFSR       |

| $\wedge$  | - | AND logic operation |

| $\lor$    | - | OR logic operation  |

| 7         | - | NOT logic operation |

| =         | - | Equal               |

# LIST OF APPENDICES

## APPENDIX

## TITLE

## PAGE

| A | Publications                          | 134 |

|---|---------------------------------------|-----|

| В | Simulation Results                    | 136 |

| С | RTL ITC'99 Benchmark Circuits in VHDL | 140 |

| D | Algorithm of DFTT and Reduced BIST    | 155 |

#### CHAPTER 1

#### **INTRODUCTION**

#### 1.1 Background

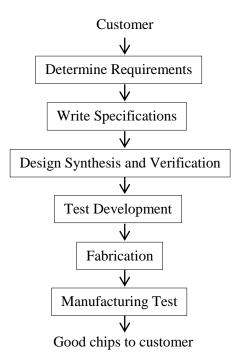

Nowadays, an integrated circuit (IC) can simply have millions of gates and thus, its design becomes more complex. According to Moore's Law, the number of components per chip doubles roughly every 24 months. Design performance has improved following Moore's Law but testing suffers from tremendous pressure to keep up with the new semiconductor technology without impacting the design and production costs. Figure 1.1 depicts the manufacturing test is performed on chips before delivering to customers. Prior to that, test development is accomplished to obtain test data to be used in manufacturing test, such as test patterns and expected test responses. IC testing is an important step to identify the correctness of manufactured circuits. Furthermore, testing is definitely essential to ensure high yield of good quality product. Fault coverage is an indicator of testing quality. High fault coverage obtained using standard commercial automatic test pattern generator (ATPG) is important because the test vectors could filter out most of the defective IC. However, it is difficult to achieve high fault coverage in some sequential circuits. In order to obtain high fault coverage that becomes a major concern in testing, design for testability (DFT) is introduced.

DFT refers to a method that augments a given circuit to become easily testable. In other words, DFT is used to improve the testability of the circuit. Basically, four parameters are needed to be measured when introducing DFT: (1) fault coverage, (2) test generation time, (3) test application time and (4) area

overhead. Among these four parameters, although area overhead is incurred, DFT improves fault coverage, test application time and test generation time.

Fault coverage is the ratio of the number of faults detected to the total number of faults. Fault coverage is measured using fault model such as stuck-at fault, stuck-at-open, path delay and bridging fault. Stuck-at-fault model is the most common model in logic circuits (Adallatif, 2009). Equation 1.1 shows the fault coverage measurement.

# Fault coverage = $\frac{detected fault}{total faults}$ (1.1)

Test generation time is the computation time needed to generate test patterns. Normally, test generation time for sequential circuit is longer than that of combinational circuit. This is because of the feedback path in the sequential circuit. Test application time is the total time required to apply test patterns on the circuitunder-test (CUT) and capture its test responses. Test application time of circuits augmented by DFT method called partial scan (Cheng and Agrarwal, 1990) is shorter than the full scan design because the length of the scan chain is reduced in the former. Another parameter, area overhead, is defined as the ratio of extra gates added to the total number of original circuit gates. For example, extra multiplexers are considered as area over when they are added to the CUT under partial scan method to improve the testability of the CUT. Therefore, the area of multiplexers are considered as extra area that needs to be calculated.

Since the trend of top-down design has become more popular, process of introducing DFT is also moved from gate level to RTL aiming at further improving the test generation time and area overhead. DFT method can be categorised into scan, non-scan and BIST. Each category can be applied at both RTL and gate level except full scan method that included is applied at gate level only. DFT at RTL is applied in early design before generating netlist process (Greene and Samiha, 2002).

Figure 1.1 Testing flow in VLSI realization process (Bushnell and Agrawal, 2002)

### **1.2 Problem Statement**

Sequential circuit consists of combinational logic and flip-flops. Different from combinational circuit which needs only a single test vector to detect a fault, the testing of sequential circuit is more complex because it needs a sequence of vectors to detect a fault in a sequential circuit. The sequence of vectors is generated by initializing a circuit to a known state, activate the fault and propagate the fault to a primary output. Its test cost will be increased accordingly due to the complexity of testing sequential circuit. Therefore, DFT concept has been introduced to reduce the testing complexity, as well as to improve testing effectiveness which is always measured by test application time, fault coverage and test generation time. DFT of scan technique such as full scan and partial scan [16] is one of the popular methods. However, it has limitations of area overhead due to number of added multiplexer at each flip-flop and test application time due to shifting of test pattern. Based on the problems discussed above, two research questions are raised: (1) Can the area overhead of DFT be further reduced? (2) Can the test application time of DFT be further shortened? To answer the questions, first, the root cause of each problem should be identified and discussed. Area overhead is the first issue need to be addressed. Area overhead is incurred due to the addition of multiplexers into selected flip-flop to enhance the controllability and observability of the storage element such as flip-flop in scan technique. When the DFT is done at gate level, the addition of multiplexer is merely determined by the structural information such as feedback loop of the sequential circuit. This can be avoided if functional information at the RTL design of the CUT is known during DFT. High area overhead will be incurred if extra sequential circuit, known as test plan, is added between controller and data path like approach by Ohtake, Wada, Masuzawa and Fujiwara (2000). Test plan is required to generate test patterns to data path. They also insert multiplexer if necessary during generation of control path and observation path.

The second issue addressed is test application time. Chaining a scan flipflop to another scan flip-flop based on only structural information is the main factor that leads to the long test application time. If functional information such as registers' connectivity is known during DFT, chaining a register to another register more effectively in term of area overhead and test application time is possible and this allows RTL non-scan DFT that generally has shorter test application time.

However, RTL non-scan DFT method still requires expensive automatic test equipment (ATE) to provide external test patterns and to observe the test responses. Besides ATE cost incurred from basic components in tester such as probe card and interface card, ATE cost also includes yearly maintenance cost. Furthermore, high performance ATE is essential especially testing of timing defects. On contrary, the built-in self-test (BIST) method does not require external test patterns. It can generate the test patterns by itself through the test pattern generator integrated into the circuit. However, the BIST approach suffered from the area overhead if using concurrent built in logic block observer (CBILBO) as test register which can operates as test pattern generator and test response compacter. The BIST approach also has drawback of long test application time based on test-per-scan scheme because each test pattern needs to be scanned in and scanned out through the register.

The main challenge of DFT insertion is how to reduce test cost by obtaining high fault coverage with an acceptably less test application time, test generation time and low area overhead without incurring unacceptably low fault coverage. In other words, fault coverage is a more crucial parameter need to be considered compared to area overhead, test application time and test generation time. However, there is a trade-off between fault coverage and test application time and between fault coverage and area overhead. It is also possible to obtain high fault coverage and low area overhead and short test application time.

#### 1.3 Objectives

The objectives of this research are:

- i. To develop a RTL non-scan DFT method that has high fault coverage, low area overhead, low test application time and low test generation time.

- ii. To develop a RTL BIST method that has high fault coverage and low area overhead.

#### **1.4** Scope of Work

The scope of the research covers the following:

- a) Focus on introducing non-scan RTL DFT method.

- b) RTL design that written in VHDL description.

- c) ITC'99 circuits and RTL design circuit like greatest common division (GCD) is used as benchmark circuits to show the effectiveness of the proposed method.

- d) Stuck-at-fault model is used as fault model.

- e) The tools like Altera Quartus, Design Vision, Tetramax, VHDL and Perl script are used in this research.

- f) This research considers functional test; parametric test is out of scope of this work.

#### **1.5** Contributions

This thesis has two main contributions. The first contribution is the introduction of a non-scan DFT method at RTL that considers the information of controllability and observability of CUT that is extractable from RTL description. The information at RTL is extracted in order to reduce the extra hardware such as multiplexers to make the CUT easily tested. Therefore, the area overhead of the proposed non-scan RTL DFT can be reduced. High fault coverage, less test application time and less test generation time are achieved compared to the previous method.

The second contribution is the introduction of BIST technique at RTL, which is using multiple input signature register (MISR) as BIST component instead of CBILBO. The BIST component selection is based on the new concept of extended minimum feedback vertex set (extended MFVS), where a number of registers is selected to be BIST component such that minimum cost function of hardware overhead is considered. MISR can still generate test patterns and compact test responses simultaneously similar to CBILBO. By using MISR, definitely area overhead can be reduced. All combinational blocks are tested simultaneously such that the test application time is short. This new BIST method results in lower area overhead and slightly lower fault coverage compared to the concurrent BIST-able method for all the benchmark circuits.

#### REFERENCES

- A. Balakrishnan and S.T. Chakradhar. (1996). Sequential Circuits with Combinational Test Generation Complexity. *Proceeding International Conference on VLSI Design*. 111 - 117.

- A. P. Stroele and H. J. Wunderlich. (1998). Hardware-Optimal Test Register Insertion. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems. 531 - 539.

- Adallatif S. Abuissa (2009). Low *Power High Fault Coverage Test Techniques* for Digital VKSI Ciruits. Ph.D. Thesis. University of Birmingham.

- B.Koenemann, J.Mucha and G.Zwiehoff. (1979). Built-in Logic Block Observation Techniques. *in IEEE Test Conference*. 37 - 41.

- Bin Zhou, Li-yi Xiao, Yi-Zheng Ye and Xin-Chun Wu. (2011). Optimization of Test Power and Data Volume in BIST Scheme Based on Scan Slice Overlapping. *Journal of Electronic Testing:Theory and Applications*. 43 56.

- Bruce S. Greene and Samiha Mourad. (2002). Partial Scan Testing on the Register-Transfer Level. *Journal of Electronic Testing: Theory and Applications*. 613 626.

- C. Y. Ooi and H. Fujiwara. (2004). Classification of Sequential Circuits Based on tk Notation. *in Proceeding IEEE 13th Asian Test Symposium*. 348 -353.

- C. Y. Ooi and H. Fujiwara. (2006). A New Scan Design Technique Based on Pre-Synthesis Thru Functions. *Proceeding of 15th IEEE Asian Test Symposium.* 163 - 168.

- C. Y. Ooi, T. Clouqueur, and H. Fujiwara. (2005). Classification of Sequential Circuits Based on τk Notation and Its Applications. *IEICE Transactions Inf. Syst.* 2738 - 2747.

- C.Y. Ooi and H. Fujiwara. (2011). A New Design-for-Testability Method Based on Thru-Testability. *Journal of Electronic Testing:Theory and Applications*. 583 - 598.

- Chakradhar ST, Balakrishnan A and Agrawal V. D. (1994). An Exact Algorithm for Selecting Partial Scan Flip-Flops. *in Proceeding 31st Design Automation Conference*. 81 - 86.

- Chia Yee Ooi and Fujiwara H. (2006). A New Class of Sequential Circuits with Acyclic Test Generation Complexity. *IEEE International Conference on Computer Design.* 425 - 431.

- D. Bhattacharya, T.R, Viswanathan and K. Laker. (1997). Integrated Circuit Testing for Quality Assurance in Manufacturing: History, Current Status and Future Trends. *IEEE Transaction on Circuit and System II: Analog and Digital Signal Processing*. 610 - 633.

- D.H. Lee and S.M. Reddy. (1990). On Determining Scan Flip-Flops in Partial-Scan Designs. *in Proceeding International Conference on CAD*. 322 - 325.

- Elham Khayat Moghaddam (2011). On Low power Test and Low Power Compression Techniques. Ph.D. Thesis. University of Iowa.

- Eric Larsson (2000). An Integrated System-Level Design for Testability Methodology. Ph.D. Thesis. University of Linkoping.

- F.Hsu, K. M. Butler and J. H. Patel. (2001). Case Study on The Implementation of The ILS Architecture. International Test Conference. 538 - 47.

- Fujiwara H, Iwata H, Yoneda T and Ooi Y. (2008). A Non-Scan Design-for-Testability Method for Register-Transfer-Level Circuits to Guarantee Linear-Depth Time Expansion Models. *IEEE Transactions Computer-Aided Design Integrated Circuits Systems*. 1535 - 1544.

- H. Iwata, T. Yoneda, S. Ohtake and H. Fujiwara. (2005). A DFT Method for RTL Data Paths Based on Partially Strong Testability to Guarantee Complete Fault Efficiency. *Proceeding IEEE 14th Asian Test* Symposium. 306 - 311.

- H. Wada, T. Masuzawa, K. K. Saluja and H. Fujiwara. (2000). Design for Strong Testability of RTL Data Paths to Provide Complete Fault Efficiency. *in Proceeding International Conference on VLSI Design*. 300 - 305.

- H.M. Harmanani. (2010). Estimating Test Cost During Data Path and Controller Synthesis with Low Power Overhead. *Canadian Conference* on Electrical and Computer Engineering. 1 - 5.

- Haidar M. Harmanani and Aouni Hajar. (2007). Concurrent BIST Synthesis and Test Scheduling using Genetic Algorithms. *International Journal of Computers and Applications*. 132 - 142.

- Hong Xiao. (2012). *Introduction to Semiconductor Manufacturing Technology*. SPIE PRESS Bellingham. : Washington USA Publishers.

- Hongxia Fang, Krishnendu Chakrabarty and Hideo Fujiwara. (2010). RTL DFT

Techniques to Enhance Defect Coverage for Functional Test Sequence.

Journal of Electronic Testing: Theory and Applications. 151 164.

- I. Ghosh, N. K. Jha and S. Bhawmik. (1998). A BIST Scheme for RTL Controller-Data Paths Based on Symbolic Testability Analysis. *in Proceeding Design Automation Conference*. 554 - 559.

- I. Hamzaoglu and J. H. Patel. (1999). Reducing Test Application Time for Full Scan Embedded Cores. *International Symposium of Fault-Tolerant Comp.* 260 - 267.

- Jamuna. S. Implementation of BIST Structure using VHDL for VLSI Circuits. International of Engineering Science and Technology. 2011. 5041-5048.

- K Usami, K Seki and H Yokohama. (2000). A Non-Scan Testable Design of Sequential Circuits. IEICE Technical Report. 73 - 79.

- K. Kim, D.S. Ha and J.G. Tront. (1988). On using Signature Registers as Pseudorandom Pattern Generators in Built in Self Testing. *IEEE Transactions Computer-Aided Design*. 919 - 928.

- K. T. Cheng and V. D. Agrarwal. (1990). A Partial Scan Method for Sequential Circuits with Feedback. *IEEE Transaction Computer*. 544 -548.

- K. Yamaguchi, H.Wada, T. Masuzawa and H.Fujiwara. (2001). A BIST Method Based on Concurrent Single-Control Testability of RTL Data Paths for BIST. *Proceeding 10th Asian Test Symposium*. 313 - 318.

- K.-J. Lee, W.-C. Lien, and T.-Y. Hsieh. (2011). Test Response Compaction Via Output Bit Selection. *IEEE Transactions Computer-Aided Design*. 1534 - 1544.

- Kenichi Yamaghuci, Michiko Inoue and Hideo Fujiwara. (2007). Test-per-Clock BIST with Low Overhead. *Inc. Electronics and Communications in Japan.* 47 - 58.

- L. H. Goldstein. (1979). Controllability/Observability Analysis of Digital Circuits. IEEE Transaction on Circuits and Systems. 685 – 693.

- Laung-Terng Wang, Cheng-Wen Wu and Xiaoqing Wen. (2006). VLSI Test Principles and Architectures Design for Testability. () Morgan Kaufmann Publishers.

- Lien Wei Cheng, Lee Kuen Jong and Hsieh Tong Yu. (2012). A Test-per-Clock LFSR Reseeding Algorithm for Concurrent Reduction on Test Sequence Length and Test Data Volume. *Proceeding 12<sup>th</sup> Asian Test Symposium.* 278 - 283.

- M. Banga, N. Rahagude and M.S. Hsiao. (2011). Design-for-Test Methodology for Non-Scan At-Speed Testing. DATE. IEEE Computer Society.

- M. S. Hsiao and M. Banga. (2009). Kiss the Scan Goodbye: A Non-Scan Architecture for High Coverage, Low Test Data Volume and Low Test Application Time. Asean Test Symposium. 225 - 230.

- M.E.J. Obien and H. Fujiwara. (2009). A DFT Method for Functional Scan at RTL. Proceeding IEEE 10<sup>th</sup> IEEE Workshop on RTL and High Level Testing. 6 - 15.

- M.E.J. Obien, S. Ohtake and H. Fujiwara. (2011). F-Scan: A DFT Method for Functional Scan at RTL. *IEICE Transactions on Information and System.* 104 - 113.

- Martin Rudolph. (1990). Feedback-Testing by using Multiple Input Signature Registers. *Journal of Electronic Testing: Theory and Applications*. 213 - 219.

- Michael L. Bushnell and Vishwani D. Agrawal. (2002). Essential of Electronic Testing for Digital, Memory & Mixed-Signal VLSI Circuits. () Kluwer Academic Publishers.

- Nassar D.A and Salama A.E. (2002). A heuristic DSP BIST Insertion Algorithm with Minimum Area Overhead. *IEEE International Symposium on circuits and Systems*. 585 - 588.

- Nicola Nicolici (2000). Power Minimisation Techniques for Testing Low Power VLSI Circuits. Ph.D. Thesis. University of Southampton.

- Orailoglu, A. (1997). Michroarchitectural Synthesis for Rapid BIST Testing. IEEE Transaction on Computer-Aided Design of Integrated Circuits and Systems. 573 - 586.

- Ozgur Sinanoglu and Vishwani D. Agrawal. (2013). Eliminating the Timing Penalty of Scan. *Journal of Electronic Testing: Theory and Applications*. 103 - 114.

- Pomeranz I and Reddy SM. Autoscan. (2005). A Scan Design without External Scan Inputs or Outputs. *IEEE Transactions Very Large Scale Integrated System.* 1087 - 1095.

- R. B. Norwood and E. J. McCluskey. (1996). Orthogonal Scan: Low Overhead Scan for Data Paths. *in Proceeding of International Test Conference*. 659 - 668.

- R. B. Norwood and E. J. McCluskey. (1997). High Level Synthesis for Orthogonal Scan. in Proceeding of 15th VLSI Test Symposium. 370 -375.

- R. Gupta, and M.A. Breuer. (1990). The BALLAST Methodology for Structured Partial Scan Design. *IEEE Transactions Computing*. 538 -544.

- S Dey and M Potkonjak. (1994). Non-Scan Design-for-Testability of RT-Level

Data Paths. ACM International Conference on Computer-Aided Design.

640 645.

- S Lei, Z Wang, Z Liu and F Liang. (2010). A Unified Solution to Reduce Test Power for Test-per-Scan Schemes. *IEICE Electronics Express*. 1364 -1369.

- S. Battacharya and S. Day. (1996). H-SCAN: A High Level Alternative to Full Scan Testing with Reduced Area and Test Application Time. *in Proceeding of the IEEE VLSI Symposium*. 74 - 80.

- S. Bhawmik, C. Lin, K. Cheng, and V. Agrawal. (1991). PASCANT: A Partial Scan and Test Generation System. *in Proceeding Of the Custom Integrated Circuits Conference*. 1731 - 1734.

- S. Dey, A. Raghunathan and K. Wagner. (1998). Design for Testability at the Behavioral and Register-Transfer Levels. *Journal of Electronic Testing: Theory and Applications*. 79 - 91.

- S. Narayanan, R. Gupta, and M. Breuer. (1993). Optimal Configuring of Multiple Scan Chains. *IEEE Transactions On Computer-Aided Design*. 1121 - 1131.

- S. Ohtake, H. Wada, T. Masuzawa and H. Fujiwara. (2000). A Non-Scan DFT Method at Register-Transfer Level to Achieve Complete Fault Efficiency. *in Proceeding Asia and South Pacific Design Automation Conference.* 599 - 604.

- S. Ohtake, T. Masuzawa and H. Fujiwara. (1998). A Non-Scan DFT Method for Controllers to Achieve Complete Fault Efficiency. *in Proceeding of the 7th Asian Test Symposium*. 204 - 211.

- S. S. K. Chiu and C. Papachristou. (1991). A Built-In-Self-Testing Approach for Minimizing Hardware Overhead. *Proceeding International Test Conference*. 282 - 285.

- S. T. Chakradhar, S. Kanjilal and V. D. Agrawal. (1993). Finite State Machine Synthesis with Fault Tolerant Test Function. *Journal of Electronic Testing:Theory and Applications.* 57 - 69.

- Sato, H. Yamaguchi, M. Matsuzono and S.Kajihara. (2011). Multi-Cycle Test with Partial Observation on Scan-Based BIST Structure. Asian Test Symposium. 54 - 59.

- T.Masuzawa, M.Idutsu, H.Wada and H.Fujiwara. (2000). Single-Control Testability of RTL Data Paths for BIST. *Proceeding 9th Asian Test* Symposium. 210 - 215.

- Takabatake K, Masuzawa T, Inoue I and Fujiwara H. (1997). Non-Scan Design for Testable Data Paths using Thru Operation. Proceeding of the ASP-DAC Asia and South Pacific Design Automation Conference. 313 -318.

- V. Chickermane and S. M. Reddy. (1990). An Optimization Based Approach to The Partial Scan Design Problem. *in Proceeding International Test Conference*. 377 - 386.

- WC Lien, KJ Lee, TY Hsieh, K. Chakrabarty and TH Wu. (2013). Counter-Based Output Selection for Test Response Compaction. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems. 152 - 164.

- Xiang D and Patel JH. (2004). Partial Scan Design Based on Circuit State Information and Functional Analysis. *IEEE Transactions Comput.* 276 - 287.

- Yu Huang, Chien-Chung Tsai, N. Mukherjee, O. Samman, D. Devries, Cheng,Wu-Tung and S.M. Reddy. (2001). On RTL Scan Design. in Proceeding International Test Conference. 728 - 737.