JIEM, 2019 – 12(1): 176-200 – Online ISSN: 2013-0953 – Print ISSN: 2013-8423

https://doi.org/10.3926/jiem.2765

# Application of Fuzzy Integrated FMEA with Product Lifetime Consideration for New Product Development in Flexible Electronics Industry

Kelvin P.L. Pun<sup>1,2</sup>, Jason Rotanson<sup>2</sup>, Chee-Wah Cheung<sup>2</sup>, Alan H.S. Chan<sup>1</sup>

<sup>1</sup>Department of SEEM, City University of Hong Kong (Hong Kong)

<sup>2</sup>Compass Technology Co Ltd (Hong Kong)

polpun2222-v@my.cityu.edu.hk, jason\_rotanson@cgth.com, cheecheung@cgth.com, meachan@cityu.edu.hk

Received: October 2018 Accepted: January 2019

#### Abstract:

**Purpose:** the aim of this paper is to minimize the risks of new product development and shorten time-to-market, particularly for high-tech enterprise where the complexity of the product generates vast amount of failure mode.

**Design/methodology/approach:** first, the concept of Critical Consideration Factor (CCF) is introduced based on product-specific technical characteristics, expected lifetime, and yield requirement to identify and prioritize the critical failure mode in the subsequent Failure Mode and Effect Analysis (FMEA), followed by process characterization on the high-risk failure mode and Critical Parameter Management (CPM) practice to realize a robust mass production system of the developed technology. The application on the development of advanced flexible substrate and surface finishes fabrication technique is presented.

*Findings:* through the proposed methodology, the risk level of each potential failure mode can be accurately quantified to identify the critical variables. With process characterization, reliability of the product is ensured. Consequently, significant reduction in development resources and time-to-market can be achieved.

**Practical implications:** the development strategy allows high tech enterprises to achieve a balanced ecosystem in which value created through adaption of new technology/product can be thoroughly captured through commercialization in a timely manner with no field failure.

**Originality/value:** the proposed development strategy utilizes a unique approach with thorough considerations that enables high tech enterprise to deliver new product with rapid time-to-market without sacrificing product lifetime reliability, which is key to achieve competitive advantage in the highly dynamic market.

**Keywords:** new product development, risk management, failure mode and effect analysis, critical parameter management, advanced manufacturing, industry 4.0

### To cite this article:

Pun, K.P.L., Rotanson, J., Cheung, C., & Chan, A.H.S. (2019). Application of fuzzy integrated FMEA with product lifetime consideration for new product development in flexible electronics industry. *Journal of Industrial Engineering and Management*, 12(1), 176-200. https://doi.org/10.3926/jiem.2765

### 1. Introduction

### 1.1. New Product Development

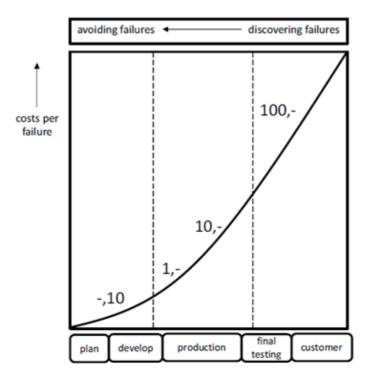

To remain sustainable and profitable, high tech enterprises face multiple challenges in competitive business environments and rapid changes in market demand. One of the key success factors is continuous investment in R&D to create value by commercializing technology into products, setting industry standards, and effectively deterring the entry of rivals (Zahra, 1996). With ever increasing customer expectations, time becomes the critical factor in the development of new technology. Manufacturers are required to achieve short development cycles and consequently time-to-market, while simultaneously offering cost advantages and scalability. Opportunities from NPD also incur huge risks, in which unpredictable obstacles can arise during mass production that lead to unstable yield loss and impede product commercialization. Managing NPD is a vital and challenging process, as it involves extensive financial and human resources (Bhuiyan, 2011). In fact, a considerable number of products never make it to the market, with a failure rate of 25% to 45% (Mosley, 1994; Crawford, 1987). Avoiding failure is paramount in the development of technical products. The earlier the failure detection, the more economic loss can be avoided (Figure 1) and the faster commercialization can be achieved (Würtenberger, Kloberdanz, Lotz & Von Ahsen, 2014). In addition to the cost, commercialized products that experience field failure during their product lifetime will negatively affect customer experience, not to mention possible liability issue. Therefore, solving these unforeseeable problems is critical to achieve successful technology transfer. Indeed, organizations need to employ a multidimensional development strategy to ensure that the value created is in equilibrium with the value captured (Rajan, 2016).

Figure 1. Cost per failure that increase logarithmically at different development stage (Würtenberger et al., 2014)

Success of the NPD process requires synergy from cross-functional teams, management support, and conducive organizational structure to achieve the desired product performance, speed to market, and development cost (Schimmoeller, 2010). Quality improvement tools, such as quality function deployment (QFD), benchmarking, conjoint analysis, and FMEA have been investigated by previous researchers. FMEA in particular, has been used in numerous development strategy frameworks. For example, Belu, Rachieru, Militaru & Anghel (2012) demonstrated the application of design FMEA with functional analysis in new product development stage.

Doğan and Cebeci (2016) integrated the use of QFD to generate FMEA based on customer requirement in NPD process. These studies, despite being able to detect possible risks beforehand, do not ensure a robust system that is ready for mass production while taking into account product lifetime reliability. Natarajan, Senthil, Devadasan, Mohan and Sivaram (2013) implemented quality and reliability on to new product development process, however the methodology presented is not quantitative as it focuses on systematically achieving certain milestone on the product development. Moreover, methodology in traditional FMEA is highly debatable due to the subjective rating as well as questionable weighting and calculation formula. Various methods have been proposed to improve FMEA such as using grey relational analysis and fuzzy logic based on safety, quality, and cost (Baynal, Sari & Akpinar, 2018; Banduka, Tadić, Mačužić and Crnjac, 2018). Therefore, there is a need for novel development strategy based on FMEA that takes into account product quality & reliability from the technical aspect through quantitative analysis to intelligently manage and optimize development resources to reduce development time.

# 1.2. The Flexible Electronics Industry

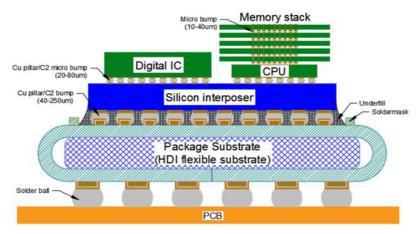

Increasing demand for advanced electronic products with a smaller form factor, multi-functionality, higher performance, and lower overall cost has driven the semiconductor industry to continuously innovate emerging advanced packaging technologies using flexible substrates. The electronic packaging field constitutes a highly sophisticated area that necessitates specific expertise on numerous levels. Choosing the optimal process equipment and materials, combined with innovative design solutions that address thermal, mechanical, and electrical issues will be the key success factors. Figure 2 shows the construction of an advanced electronic package with heterogeneous integration. From top to bottom, the package consists of die (integrated circuit/ IC)/component, IC level interconnect, package level interconnect (1st level), substrate, board level interconnect (2nd level), and the main board itself.

Figure 2. Heterogeneous integration in an advanced electronic package (Pun, Islam, Rotanson, Cheung & Chan, 2018a)

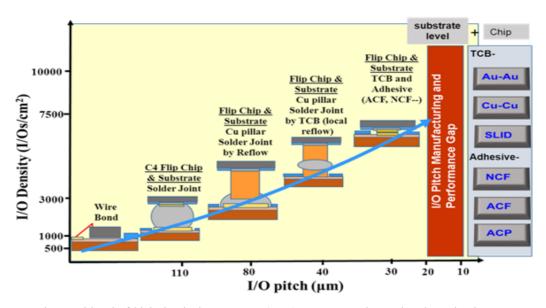

With such heterogeneity in a microsystem, various components are integrated by different kinds of materials and interfaces in a compact space. The reaction between these materials and the environment determines manufacturability, functionality, and reliability. With the extant trend that is shifting towards the "More than Moore" law, 3D IC integration using through silicon via (TSV) has been developed for higher density and shorter signal propagation (Pangracious, Marrakchi & Mehrez, 2015). To enable this, packaging substrate is essential to fan out the compact circuitries between the 3D IC module and the main board, so that thermal expansion mismatch can be minimized, and a less dense main board is required (lower cost) (Lau, 2015). Moreover, scaling of silicon devices is reaching its physical limit (Nawrocki, 2010). Interconnect technology is also growing at a rapid pace (Figure 3). Therefore, diversification of semiconductor products is predicted to create new competition in advanced packaging substrates and their interconnect technologies. Advanced packaging will be the critical enabler of a wide variety of devices in many applications, such as

OLED/AMOLED, LCD/TFT displays, smart wearables, medical imaging, and hyperconnected cloud (HyCC) for the internet of things (IoTs). However, integration of more components and material interfaces on advanced package configurations, such as system-in-package (SiP), package-on-package (PoP), and 3D IC integration modules will increase potential failure modes in an exponential manner. These failure modes (especially highly critical ones) must be eliminated early during the development stage, as conducting failure analysis after product commercialization involves another set of huge resources, and often necessitates design changes and engineering change notices (ECN) on many levels due to system complexity. Furthermore, encountered field failures will incur major losses for enterprises in terms of liability, cost, reputation, etc. Therefore, product lifetime performance must constitute a top priority.

Figure 3. Trend of high-density interconnect (HDI) to support advanced package development

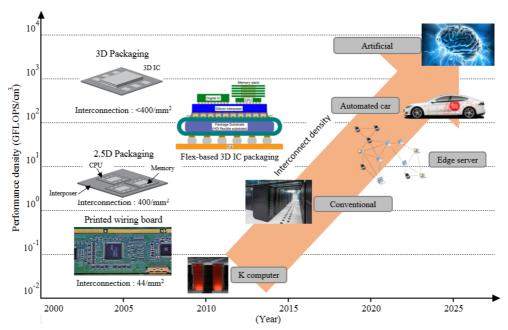

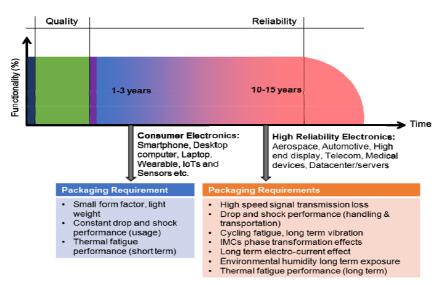

With the demanding product features, along with the rapid change of trend in electronics industry (Figure 4), market research is essential to ensure new product development process is targeting the relevant market segment that benefits both the consumer and organizations. Based on these emerging market trends, three main fields are identified:

- Display market: Future display modules are also moving towards the integration of display driver IC and touch controller IC, which benefits design, manufacturing, size reduction, and performance (Synaptics, 2014). This integration means that more functionalities can be incorporated into a single IC, which also requires a COF (Chip-on-film) with an increasingly finer pitch. Expected product lifetime: <5 years.</li>

- 2. **Medical devices market:** The medical field demands high performance reliability and ultra-compact module integration using system in package (SiP) and package on package (PoP) which involve multiple assembly processes. Such configurations necessitate advanced packaging solutions, in terms of interconnect density, pitch, and substrate line/space scalability. Expected product lifetime: 10-15 years.

- 3. Hyperconnected Cloud Computing (HyCC): In the coming IoTs (Internet of Things) era, all kinds of data will be collected, transmitted, stored, and analysed in an enormous virtual space to generate new values and finally be displayed for end users. Translating this in terms of packaging requirement, a fine line/spacing packaging substrate having short wiring between devices is needed to minimize signal propagation delay while reducing package size. Furthermore, as transmission speed is also increasing for these applications, smooth conductor roughness and low dielectric constant become essential to minimize conductor loss (skin effect) and dielectric loss, respectively. Expected product lifetime: 10-15 years.

Figure 4. Device packaging technology for servers (Aoki, 2017)

# 1.3. Proposed State-of-the-Art Technology

Taking the existing technical challenges involved in the electronic packaging requirement in emerging products into account, the following technologies related to flexible substrate are developed:

- 1. Flexible circuit fabrication with Fully Additive Process (FAP): The substrate is an integral part of packaging, as it serves as the backbone of electronic devices by interconnecting all components mechanically and electrically. A flexible substrate is typically fabricated by a subtractive or semi-additive process (SAP or MSAP, respectively), which possesses limitations on meeting circuit density below 20 um pitch, which limit package miniaturization. A fully additive process (FAP) has been developed and proven to outperform the conventional process in terms of functional performance and overall process steps/cost.

- 2. Advanced Surface Finishing with Electroless Ni/Electroless Pd/Immersion Au (ENEPIG): Surface finish plays a vital role in the final steps of substrate fabrication since it not only protects the exposed copper circuit, but also affects the final interconnection performance due to the interfacial reaction of the surface finishing material during the assembly process. ENEPIG is a promising solution to address the reliability and miniaturization requirement of future electronics due to the low overall thickness and electroless plating method that simplifies process steps.

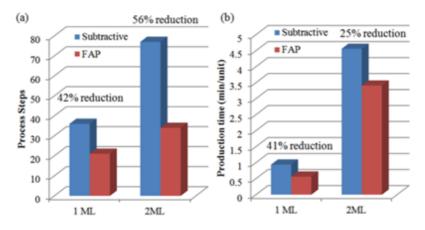

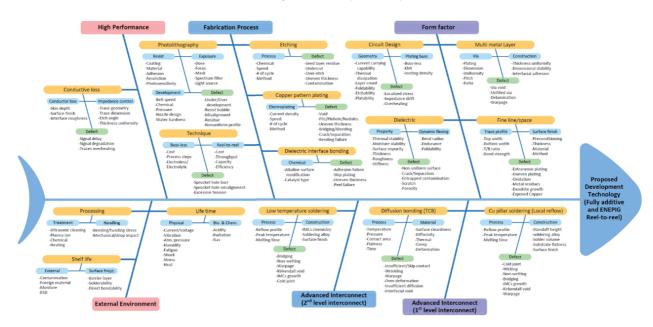

List of technical features to be addressed in the development of the two technologies is shown in Figure 5. Combining these two technologies in a reel-to-reel form with the latest interconnect technology constitutes a unique approach to realize an advanced electronic packaging system while achieving considerable process steps and cycle time reduction, as shown in a comparative study of our production line (Figure 6). These two technologies are promising to support advanced interconnect technologies, including direct diffusion bonding and copper pillar soldering (1st level interconnect) and low temperature soldering (2nd level interconnect).

Due to the high level of complexity and precision required on the development of the two mentioned technologies, a vast amount of technical challenges/failure mode is to be expected prior to mass production. Solving the large amount of failure modes is unrealistic due to the prolonged development time/time-to-market, which significantly deteriorates the competitiveness of high-tech enterprises. In this paper, a unique development strategy for robust technology transfer is presented and applied to the development of the new flexible electronics substrate fabrication and surface finishing technology.

Figure 5. Features of the proposed state-of-the-art technology in fulfilling the latest product technical requirement

Figure 6. (a) Process steps reduction; (b) Production time reduction with the proposed development technology as compared to conventional process

### 2. Proposed NPD Methodology

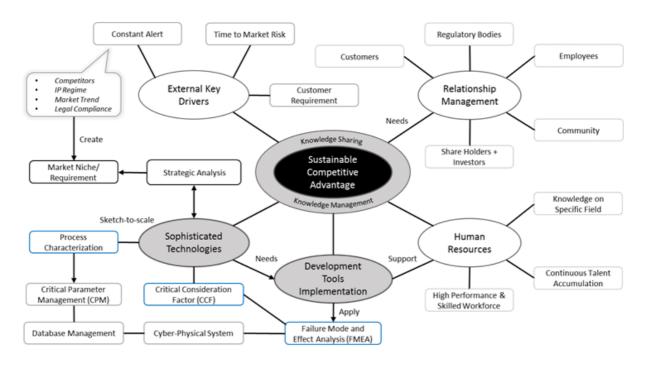

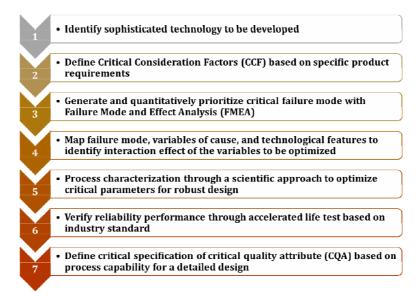

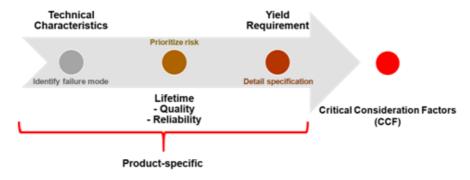

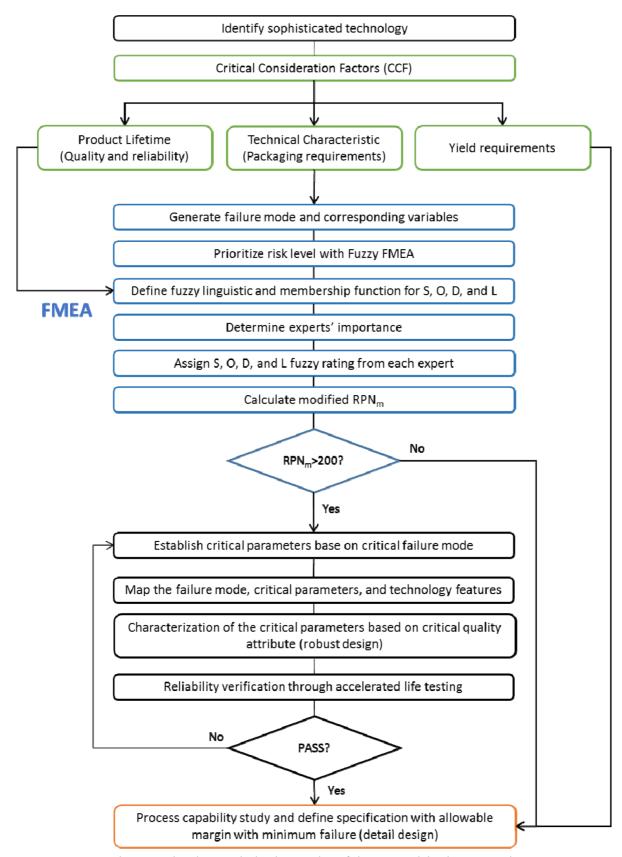

Figure 7 shows all the factors affecting the competitiveness of high-tech enterprise including external key drivers, relationship management, human resources, development tools, and sophisticated technology. This work focuses on the development of state-of-the-art technology and the corresponding development tools to streamline and accelerate the new technology development through a unique approach that enables NPD process with high product reliability while enhancing time to market. Figure 8 shows the steps of the proposed development tools methodology. The main key to achieve this to prevent failure occurrences earlier during the development stage through optimizations of the related variables. Critical consideration factors (CCF) are first defined based on the unique product features that are specific to the end application, with respect to technical characteristics, lifetime, and yield requirements, as shown in Figure 9.

Figure 7. Factors affecting competitive advantage of high-tech enterprises

Figure 8. Overview of the development tools methodology

Figure 9. Elements of critical consideration factors

From the technical characteristics, all potential failure modes, with causative variables and quality attributes, can be identified. Risk priority can then be determined by utilizing the FMEA method. The complexity of emerging products generates large amounts of failure modes that must be accurately prioritized. Fuzzy logic is one of the most powerful tools in artificial intelligence (AI) to improve decision making concerning uncertain phenomenon, which is suitable to minimize the subjectivity of traditional FMEA. In this paper, fuzzy logic is used on the FMEA by integrating the new element of product lifetime (L) in addition to conventional severity (S), occurrence (O), and detectability (D) to calculate the modified risk priority number (RPN<sub>m</sub>). Next, by setting a certain threshold, the failure mode can be classified based on risk level. As critical failure modes constitute the major concern that might hinder the adoption of new technology for mass production, their corresponding causative variables are then set to be the critical process parameter (CPP). The CPP needs to be managed through extensive process characterization in a scientific manner for robust design, and corresponding specifications need to be defined for a detailed design. Here, it is important to understand the relationship of the variables in the failure mode, as well as the correlated key technology features. Through critical parameter management (CPM), a robust system can be established by consistently employing the optimized parameters that fulfil the critical quality attribute (CQA) and reliability requirement throughout mass production. The result will also need to be well documented in an interconnected database network. Furthermore, with the advancement of Industry 4.0, a cyber-physical system (CPS) that connects digital and physical workflow allows for effective implementation of the robust system. This leads to realization of smart products that possess a high degree of autonomy in terms of its own operation, coordination and diagnosis, as the product has information/knowledge to understand itself, its environment, and its users throughout the lifecycle (Nunes, Pereira & Alves, 2017). With the proposed strategy, efficient implementation of new technology with minimum risk can be achieved to precisely fulfil the latest market niche in a timely fashion.

# 3. Implementation on the Proposed Technology

This section presents the implementation of the development tools in the development of the advanced substrate fabrication and surface finishing technology.

# 3.1. Critical Consideration Factor (CCF) Identification and Fuzzy Failure Mode and Effect Analysis (FMEA)

Figure 10 shows the flowchart of the CCF integration to FMEA, as well as CPM. To determine CCF, product requirements have to be fully understood according to the application by identifying the three elements presented in Figure 9. First, the technical characteristics must be defined based on the packaging requirements, i.e., the material, process, and design involved on each of the interfaces in the packaging configuration. Second, the expected lifetime of the product has to be identified to determine the necessary quality and reliability level, as shown in Figure 11 (Lee, Bieler, Kim & Ma, 2015). In this paper, high reliability products are targeted based on market needs. Finally, the yield requirement, which depends on the particular market and business model, have to be taken into account when determining the specifications. Defining CCF based on this can make a great difference in allocating development resources efficiently. With appropriate considerations, an efficient, yet accurate, development process can be achieved. First, the variables with resulting failure modes are determined based on the technical characteristics of the proposed technology. This is represented in the diagram in Figure 12.

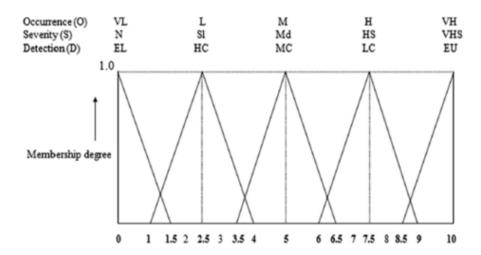

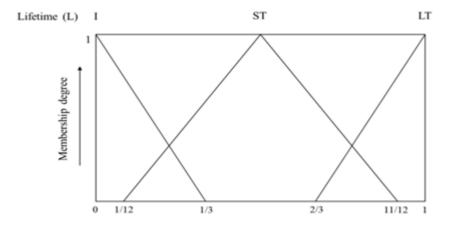

These factors must be complete, as any items missed will emerge as failure modes in later stages entering mass production. Based on this diagram, a list of failure modes with causative variables and resulting quality attributes are presented in Appendix A. For a more precise failure mode risk prioritization, fuzzy logic is employed to address the subjectivity of traditional FMEA, and includes a new element of product lifetime (L). All of the ratings are given based on five experts from research and development (R&D), production engineering (PE), and quality assurance (QA) teams with at least 10 years of experience in the relevant area of expertise. First, the fuzzy linguistic variable is assigned based on a triangular fuzzy number (TFN) on each of the S, O, D, and L variables. The assignment description and membership function are shown in Tables 1 and 2 and Figures 13 and

14, respectively. Concerning the lifetime variable, the assignment is adjustable depending on the target product requirement. Here, the membership degree increases with lifetime, as we are targeting high reliability electronic products.

Figure 10. Flowchart on the implementation of the proposed development tools

Figure 11. Quality and reliability considerations for consumer electronics and high reliability electronics (Lee, 2015)

Figure 12. Factors and failure mode of the proposed technology development

| Factors        |                       | F                    | uzzy linguistic term  | 18                    |                          |

|----------------|-----------------------|----------------------|-----------------------|-----------------------|--------------------------|

| Severity (S)   | None<br>(N)           | Slight<br>(Sl)       | Moderate<br>(Md)      | High severity<br>(HS) | Very high severity (VHS) |

| Occurrence (O) | Very low<br>(VL)      | Low<br>(L)           | Medium<br>(M)         | High<br>(H)           | Very high<br>(VH)        |

| Detection (D)  | Extremely likely (EL) | High chances<br>(HC) | Moderate chances (MC) | Low chances<br>(LC)   | Extremely unlikely (EU)  |

| Fuzzy number   | 0,0,1.5               | 1,2.5,4              | 3.5,5,6.5             | 6,7.5,9               | 8.5,10,10                |

Table 1. Fuzzy linguistic variable assignment for S, O, and D

Figure 13. Fuzzy linguistic membership function for severity, occurrence, and detection (Kirkire, Rane & Jadhav, 2015)

| Factors      | Fu             | zzy linguistic teri | ms                |

|--------------|----------------|---------------------|-------------------|

| Lifetime     | Initial<br>(I) | Short-term<br>(ST)  | Long-term<br>(LT) |

| Fuzzy number | 0,0,1/3        | 1/12,1/2,11/12      | 2/3,1,1           |

Table 2. Fuzzy linguistic variable assignment for L

Figure 14. Fuzzy linguistic membership function for lifetime

The weight of experts that reflects their influence on the risk evaluation is then calculated using the following equation:

$$w_{tmk} = \frac{E_{tmk}}{\sum_{k=1}^{n} E_{tmk}} \tag{1}$$

where *tmk* is the *kth* team member; and E is the expertise. The weights of the experts are presented in the following table.

| Team member | 1   | 2    | 3   | 4    | 5   |

|-------------|-----|------|-----|------|-----|

| Weight      | 0.3 | 0.25 | 0.2 | 0.15 | 0.1 |

Table 3. Weight assignment of each team member

Assignment of the fuzzy linguistic variable is shown in Appendix B. The fuzzy linguistic terms are calculated based on the methodology developed by Kirkire et al (2015), as shown in the following:

$$S_{ij}^{n} = \left(SL_{ij}^{n}, SM_{ij}^{n}, SU_{ij}^{n}\right), S_{ij}^{n} \in T,$$

where

$$0 \leq SL_{ij}^{n} \leq SM_{ij}^{n} \leq SU_{ij}^{n} \leq 10$$

(2)

$$O_{ij}^{n} = \left(OL_{ij}^{n}, OM_{ij}^{n}, OU_{ij}^{n}\right), O_{ij}^{n} \in T,$$

where

$$0 \le OL_{ii}^{n} \le OM_{ii}^{n} \le OU_{ii}^{n} \le 10$$

(3)

$$D_{ij}^{"} = (DL_{ij}^{"}, DM_{ij}^{"}, DU_{ij}^{"}), D_{ij}^{"} \in T,$$

where

$$0 \le DL_{ij}^{"} \le DM_{ij}^{"} \le DU_{ij}^{"} \le 10$$

(4)

$$L_{ij}^{"} = (L L_{ij}^{"}, L M_{ij}^{"}, L U_{ij}^{"}), L_{ij}^{"} \in S,$$

where

$$0 \leq L L_{ij}^{"} \leq L M_{ij}^{"} \leq L U_{ij}^{"} \leq 1$$

(5)

$$S_{ij} = S_{ij}^{1} \times W_{lm1} + S_{ij}^{2} \times W_{lm2} + \dots + S_{ij}^{n} \times W_{lmn}$$

(6)

$$O_{ij} = O_{ij}^{1} \times W_{lm1} + O_{ij}^{2} \times W_{lm2} + \dots + O_{ij}^{n} \times W_{lmn}$$

(7)

$$D_{ij} = D_{ij}^{1} \times W_{lm1} + D_{ij}^{2} \times W_{lm2} + \dots + D_{ij}^{n} \times W_{lmn}$$

(8)

$$L_{ij} = L_{ij}^{1} \times W_{lm1} + L_{ij}^{2} \times W_{lm2} + \dots + L_{ij}^{n} \times W_{lmn}$$

(9)

Where  $S_{ij}^n$ ,  $O_{ij}^n$ ,  $O_{ij}^n$  and  $L_{ij}^n$  are the severity, occurrence, detectability, and lifetime, respectively, assigned by n experts for interface of i and risk of j;  $S_{ij}^n \in T$ ,  $O_{ij}^n \in T$ ,  $O_{ij}^n \in T$  and  $L_{ij}^n \in S$  are the membership function of the triangular fuzzy number  $S_{ij}$ ,  $O_{ij}$ ,  $O_{ij}$  respectively;  $L_{ij}$  is the severity, occurrence, detectability, and lifetime value of experts' opinion for interface i and risk j;  $W_{imk}$  is the weight of kth team member; and n is the number of experts. Fuzzy numbers on the probability of S, S, S, S, and S are aggregated by equations (6)-(9) (Lin, Liu, Liu & Wang, 2013). Next, these fuzzy numbers are defuzzified into numerical values by the following equation:

$$DS_{k} = \frac{\left[\left(SU_{k} - SL_{k}\right) + \left(SM_{k} - SL_{k}\right)\right]}{3} + SL_{k} \forall k$$

$$\tag{10}$$

$$DO_{k} = \frac{\left[\left(OU_{k} - OL_{k}\right) + \left(OM_{k} - OL_{k}\right)\right]}{3} + OL_{k} \forall k$$

$$\tag{11}$$

$$DD_{k} = \frac{\left[\left(DU_{k} - DL_{k}\right) + \left(DM_{k} - DL_{k}\right)\right]}{3} + DL_{k} \forall k$$

$$(12)$$

$$DL_{k} = \frac{\left[\left(LU_{k} - LL_{k}\right) + \left(LM_{k} - LL_{k}\right)\right]}{3} + LL_{k} \forall k$$

$$\tag{13}$$

Where  $DS_k$ ,  $DO_k$ ,  $DD_k$  and  $DL_k$  are the defuzzified severity, occurrence, detectability, and lifetime fuzzy sets, respectively. Finally, the modified RPN can be calculated using the equation below:

$$RPN_m = DS_k \times DO_k \times DD_k \times DL_k \tag{14}$$

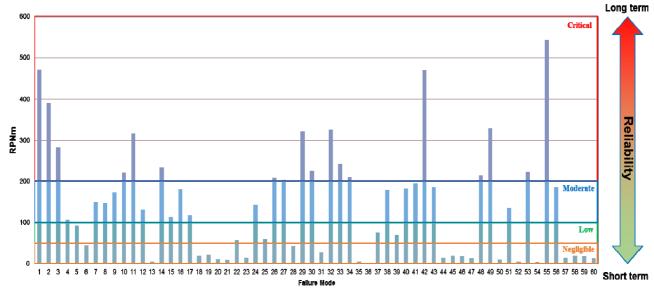

Based on this  $RPN_m$ , the failure mode is classified as follows: above 200 is set to be critical risk; between 100 to 200 is set to be moderate risk; between 50 to 100 is set to be low risk; and below 50 is set to be negligible risk. In this study, 19 critical failure modes have been identified out of a total of 61 failure modes (Figure 15).

Figure 15. Failure mode RPN in the development of advanced flexible substrate

# 3.2. Process Characterization and Critical Parameter Management

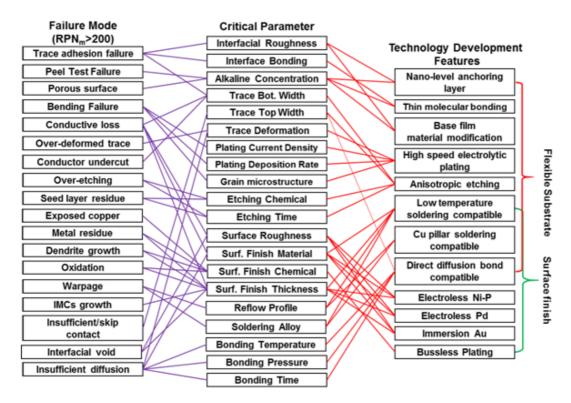

After the critical failure modes have been determined, the critical parameters are then identified from the causative variables. The relationship between these failure modes, critical parameters, and technological features need to be accurately mapped to elucidate the influence and interaction of each parameter, as shown in Figure 16.

Figure 16. Correlation between high priority failure mode, critical parameter, and technology development features

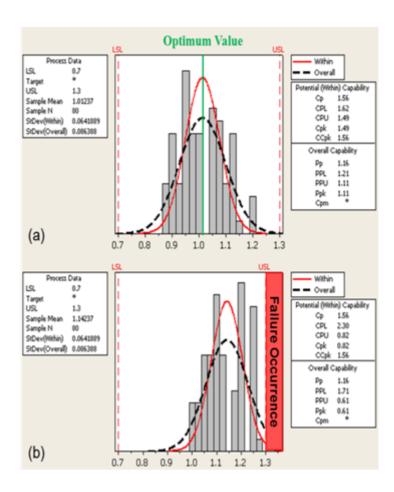

The next step is to perform process characterization on each of the critical parameters to determine the optimal value so that a robust design of the system can be established. This characterization has to be performed with a scientific methodology with an appropriate design of experiment (DOE). For each DOE, the range of the critical parameter has to be first determined based on existing data or from the literature. Defining this is crucial, as a range that is too wide will cost more resources and unnecessarily lengthen the development time. The optimization result will be based on the resulting critical quality attribute, which is also quantified in-depth with the appropriate scientific tool. The scope of the optimization should also consider interaction effects between each variable to ensure that there are no contradicting failure modes that emerged from the same critical parameter. Table 5 presents the result of critical parameter optimization based on the critical quality attribute criteria for the development of reel-to-reel FAP and ENEPIG. All of the results from the DOE must also be included in the interconnected database. Determining the optimum critical parameters constitutes the core of this development strategy since it allows the system to produce the most desired result and consequently minimize or eliminate any failure mode to meet even the most demanding specifications of the critical quality attribute. Depending on the application, a product will have a certain window of acceptable CQA. Meeting this specification is typically quantified by Cpk as a process capability index, which describes the extent to which the mean of the process lies in the middle of the specification upper and lower limit. Essentially, the higher the Cpk, the better the system is capable of meeting the required specification, leading to a robust process. Figure 17 shows the consequence of a CPP that has not been properly optimized. It can be seen that with the same machine capability, there is still a chance/window for failure to occur when CPP is not optimized.

Figure 17. Process capability of trace top/bottom ratio (a) robust design with CPM and (b) uncontrolled system design with occurrence of failure

Figure 18. Detailed specification based on process capability

|                                                                                           | Fuzzy FMEA                    |                                             | Pro              | cess Charact     | erization                                       |                                                                   |                                                       | Verification<br>SED)  |

|-------------------------------------------------------------------------------------------|-------------------------------|---------------------------------------------|------------------|------------------|-------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------|-----------------------|

| Technological<br>Features                                                                 | Sorted Failure<br>Mode        | Parameter                                   | Range<br>Studied | Optimum<br>Value | Parameter                                       | Target                                                            | Condition                                             | Method/<br>Tools      |

|                                                                                           | Interfacial void              | Temperature                                 | 180-340°C        | 320°C            |                                                 |                                                                   |                                                       |                       |

|                                                                                           | Insufficient diffusion        | Pressure                                    | 55-175 Mpa       | 155 Mpa          | Shear strength                                  | >50 MPa                                                           | Temperature<br>Humidity                               |                       |

| Metallurgy                                                                                | Insufficient/<br>skip contact | Time                                        | 1-11 s           | 10 s             |                                                 |                                                                   | Storage<br>(60°C/60%<br>RH for                        | FIB cross-<br>section |

| diffusion bond<br>compatible<br>(Pun, Dhaka,                                              | Exposed copper                | Ni Thickness                                | 1-3 um           | 3.0 um           | Trace peeled off<br>(peel test failure<br>mode) | 100%                                                              | 1000 h)                                               |                       |

| Cheung & Chan,<br>2017a)                                                                  | Metal residue                 | Pd Thickness                                | 0.05-0.4 um      | 0.4 um           | Bonding<br>misalignment                         | <2 um                                                             | Thermal                                               |                       |

|                                                                                           | Dendrite growth               | Au Thickness                                | 0.04-0.07<br>um  | 0.04 um          | Void formation                                  | Evilly clamants                                                   | Shock Test<br>(125°C to<br>-40°C for                  | Electrical test       |

|                                                                                           | Oxidation                     | Surface<br>roughness (Ra)                   | 90-150 nm        | <100 nm          | void formation                                  | Fully shrunk                                                      | 1000 cycles)                                          |                       |

|                                                                                           | IMCs growth                   | Ni Thickness                                | 1-1.3 um         | 1 um             | Overall IMCs<br>thickness after                 | <4 um                                                             |                                                       |                       |

| Cu pillar micro                                                                           | Exposed copper                |                                             |                  |                  | isothermal aging                                |                                                                   |                                                       |                       |

| bump(C2)<br>compatible                                                                    | Metal residue                 | Pd Thickness                                | 0.05-0.4 um      | 0.05-0.2 um      | Critical IMCs<br>formed                         | (Pd,Cu,Au)Sn <sub>4</sub><br>(Cu,Ni) <sub>6</sub> Sn <sub>5</sub> | Thermal aging 150°C                                   | SEM/EDX<br>& cross-   |

| (Pun, Islam,<br>Cheung & Chan,<br>2017b)                                                  | Dendrite growth               |                                             |                  |                  | Die peel failure interface                      | Within solder side                                                | for 1000 h                                            | sectioning            |

| ,                                                                                         | Oxidation                     | Au Thickness                                | 0.04-0.2 um      | 0.04-0.07 um     | Growth rate constant of IMCs                    | $<2x10^{-14} \text{ cm}^2/\text{s}$                               |                                                       |                       |

|                                                                                           | IMCs growth                   | Ni Thickness                                | 1-4 um           | 1-1.5 um         | Shear strength                                  | >1000 gf                                                          |                                                       |                       |

| T t                                                                                       | Exposed copper                | Pd Thickness                                | 0.04-0.7         | 0.15-0.2 um      | Failure mode                                    | 100% solder on interface                                          | E-+ 4-4                                               |                       |

| Low temperature solder compatible                                                         | Metal residue                 |                                             |                  |                  |                                                 | interface                                                         | Extended reflow at                                    | SEM/EDX<br>& cross-   |

| (Sn-Bi-Ag)<br>(Pun et al., 2018a)                                                         | Dendrite growth               | Au Thickness                                | 0.03-0.05<br>um  | 0.04 um          | Critical IMCs<br>formed                         | (Ni,Cu) <sub>3</sub> Sn <sub>4</sub>                              | 175°C for<br>120 mins                                 | sectioning            |

|                                                                                           | Oxidation                     |                                             |                  |                  | Ni consumption                                  | 0.009 um/min<br>reflow                                            |                                                       |                       |

|                                                                                           | Trace adhesion failure        |                                             |                  |                  | PAA layer<br>thickness                          | <5 nm                                                             | Temperature<br>Humidity<br>Storage<br>(85°/85% RH)    | TEM inspection        |

| Base film<br>modification and<br>nano-level<br>chemical bonding<br>(Pun, Ali,<br>Kohtoku, |                               | Modifier<br>concentration<br>(on polyimide) | 15-40 mL/L       | 25 mL/L          | Carboxyl<br>bonding                             | >3%                                                               | Low<br>Temperature<br>Storage<br>(-40°C for 500<br>h) | XPS analysis          |

| Cheung, Chan &<br>Wong, 2018b)                                                            | Peel test failure             |                                             |                  |                  | Amide bonding                                   | >6%                                                               | Hight<br>Temperature<br>Storage (150°C<br>for 500h)   |                       |

|                                                                                           |                               |                                             |                  |                  |                                                 |                                                                   |                                                       | Peel test             |

|                                              | Fuzzy FMEA                   |                             | Pro               | cess Charact     | erization                                                  |                                        |                                                                                               | Verification<br>SED)  |

|----------------------------------------------|------------------------------|-----------------------------|-------------------|------------------|------------------------------------------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------|

| Technological<br>Features                    | Sorted Failure<br>Mode       | Parameter                   | Range<br>Studied  | Optimum<br>Value | Parameter                                                  | Target                                 | Condition                                                                                     | Method/<br>Tools      |

|                                              | Porous surface               |                             |                   |                  | Peel strength                                              | >0.6 kN/m                              | Moisture<br>Senstivity Level<br>3 (-60°C to<br>60°C for<br>48 h and 3x<br>reflow at<br>254°C) |                       |

|                                              | Signal delay/                |                             |                   |                  | Ni-P layer<br>coverage                                     | 100%                                   | Thermal Shock<br>Test<br>(125°C to                                                            | SEM                   |

|                                              | propagation                  |                             |                   |                  | Thickness                                                  | 100-110 nm                             | -40°C for 500 cycles)                                                                         | inspection            |

|                                              | Bending                      | Plating rate                | 0.2-0.6<br>um/min | 0.2 um/min       | Grain size                                                 | >2 um                                  |                                                                                               |                       |

|                                              | endurance failure            | Current density             | 1-2.5 ASD         | 1 ASD            | Bending endurance                                          | >35 cycles                             | Heat treatment (200°C                                                                         | SIM cross-            |

| plating (Pun et al., 2018b)                  |                              | Temperature                 | 315-375°C         | 345°C            | Strain                                                     | <0.2                                   | and 300°C for 24 h)                                                                           | sectioning            |

|                                              | Over-deformed trace          | Pressure                    | 120-160<br>MPa    | 140 MPa          | Interfacial<br>microstructure<br>of Au-Au                  | Interlocking<br>nano-twin<br>structure |                                                                                               |                       |

|                                              |                              |                             |                   |                  | Insulation resistance                                      | >10 <sup>5</sup> Ohms                  |                                                                                               |                       |

|                                              | Conductor<br>undercut        |                             |                   |                  | Insulation<br>resistance after<br>thermal humidity<br>bias | >10 <sup>5</sup> Ohms                  |                                                                                               |                       |

| Isotropic etching                            | Over-etching                 | Etching time                | 60-75 s           | 75 s             | Standard<br>deviation of<br>impedance                      | <1                                     | Temperature<br>Humidity Bias<br>(85°C/85%                                                     | Insulation resistance |

| (Pun et al., 2018b)                          |                              |                             |                   |                  | T/B ratio                                                  | ~1                                     | RH/20 VDC)                                                                                    | measurement           |

|                                              |                              |                             |                   |                  | Cpk of T/B<br>ratio                                        | >1.33                                  |                                                                                               |                       |

|                                              | Seed layer residue           | ue                          |                   |                  | Line/space<br>scalability                                  | <8/8 um                                |                                                                                               |                       |

|                                              |                              |                             |                   |                  | Cpk of line/space                                          | >1.33                                  |                                                                                               |                       |

| Signal<br>performance<br>(Pun et al., 2018b) | Signal delay/<br>propagation | Interface<br>roughness (Rq) | 40-320 nm         | 40-70 nm         | Conductor loss<br>factor (Ksr)                             | <1.05                                  | N,                                                                                            | /A                    |

Table 5. Critical parameter optimization based on the critical quality attribute criteria

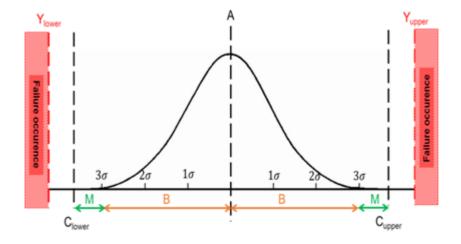

After the process characterization, the optimal value and the acceptable process window with minimum failure can be obtained. For each critical parameter identified, the optimal value is further verified in terms of the reliability through the relevant accelerated life testing. Once the reliability is guaranteed, the optimal value is run on the production line to simulate high volume production. From this, the variation from unit-to-unit and batch-to-batch can be identified to determine the machine process capability. Depending on the target sigma level, the detail specification can be determined by fulfilling the following equations:

$$C_{upper} = (A+B) + M \tag{15}$$

$$C_{lower} = (A-B) - M \tag{16}$$

$$|C_{upper} - Y_{upper}| \ge \sigma, C_{lowerr} - Y_{lower} \ge \sigma$$

(17)

where A is the optimal value from process characterization;  $Y_{upper}$  and  $Y_{lower}$  are the upper and lower limit before the occurrence of failure, respectively; B is half of the target sigma level;  $C_{upper}$  and  $C_{lower}$  are the lower and upper specification, respectively; and M is the margin allowed for the specification as shown in Figure 18. Allowing this margin is crucial so that room for error exists, which means that even though the process is outside of the sigma level standard, failure will still not occur. Obviously, the margin should be adjusted depending on the process capability, targeted sigma level, and yield requirement.

Finally, the robust system has to be followed up by appropriate operational management practices so that the optimum design can be carried out consistently throughout production. Critical parameter management is one excellent practice to assure that system robustness is maintained through detail specification, proper documentation, and in line quality control (QC) (Clausing, Frey & Systems Engineering, 2010). With a manufacturing and production implementation plan for the critical parameters, quality evaluation, and changes in the control plan, the value created through robust design can be delivered to the customer.

### 4. Conclusion

Enabling robust technology transfer with minimum time-to-market constitutes the key to enhance business competitiveness in high tech enterprises. With increasing complexity and diversification of products to meet future market demands, a higher risk of failure is inevitable at the NPD stage. Field failure is particularly detrimental to manufacturers, as failure occurs on the customer's premise. This paper established a unique methodology of prioritizing critical failure mode by embedding the product long term reliability into consideration using fuzzy-based FMEA. The methodology is implemented on the development of advanced flexible substrate in the flexible electronics industry. It has been demonstrated that the methodology is capable of capturing the critical failure mode and consequently can be prevented through process characterization on the critical parameters. Finally, the reliability is also verified following the industry standard to ensure desirable and consistent performance throughout product lifetime. Therefore, a balanced ecosystem of innovation can be realized by ensuring that the value created through new product development is thoroughly captured by commercialization in a timely manner.

### Acknowledgement

The authors would like to acknowledge the support provided by the Compass Technology Co., Ltd.

### **Declaration of Conflicting Interests**

The authors declared no potential conflicts of interest with respect to the research, authorship, and/or publication of this article.

### **Funding**

The authors received no financial support for the research, authorship, and/or publication of this article.

### References

Aoki, S. (2017). Devices, Materials, and Packaging Technologies for Hyperconnected Cloud. FUJITSU Sci Tech J, 53(2), 3-8.

Banduka, N, Tadić, D., Mačužić, I., & Crnjac, M. (2018). Extended process failure mode and effect analysis (PFMEA) for the automotive industry: The FSQC-PFMEA. *Advances in Production Engineering & Management*, 13(2), 206-215. https://doi.org/10.14743/apem2018.2.285

- Baynal, K., Sari, T., & Akpinar, B. (2018). Risk management in automotive manufacturing process based on FMEA and grey relational analysis: A case study. *Advances in Production Engineering & Management*, 3(1), 69-80. https://doi.org/10.14743/apem2018.1.274

- Belu, N., Rachieru, N., Militaru, E., & Anghel, D. (2012). Application of FMEA method in product development stage. *Academic Journal of Manufacturing Engineering*, 10(3), 12-19.

- Bhuiyan, N. (2011). A Framework for successful new product development. *Journal of Industrial Engineering and Management*, 4(4), 746-770. https://doi.org/10.3926/jiem.334

- Clausing, D., Frey, D., & Systems Engineering (2010) Massachusetts Institute of Technology: MIT Open Course Ware. Creative Commons BY-NC-SA. <a href="http://ocw.mit.edu">http://ocw.mit.edu</a>

- Crawford, C. (1987). New product management (2nd ed.). Illinois: Richard D. Irwin.

- Doğan, O., & Cebeci U. (2016). A methodology for new product development by using QFD, FMEA and its application in metal plating industry. In 16th Production Research Symposium. At Istanbul, Turkey.

- Kirkire, M.S., Rane, S.B., & Jadhay, J.R. (2015). Risk management in medical product development process using traditional FMEA and fuzzy linguistic approach: a case study. *Journal of Industrial Engineering International*, 11(4), 595-611. https://doi.org/10.1007/s40092-015-0113-y

- Lau, J.H. (2015). 3D IC Integration and Packaging. McGraw Hill Professional.

- Lee, T., Bieler, T.R., Kim, C., & Ma, H. (2015). Fundamentals of Lead-Free Solder Interconnect Technology From Microstructures to Reliability. Boston, MA: Springer US.

- Lin, Q.L., Liu, L., Liu, H.C., & Wang, D.J. (2013). Integrating hierarchical balanced scorecard with fuzzy linguistic for evaluating operating room performance in hospitals. *Expert Systems with Applications*, 40(6), 1917-1924. https://doi.org/10.1016/j.eswa.2012.10.007

- Mosley, T. (1994). Winning at new products: Accelerating the process from idea to launch (2nd ed.) by Robert G. Cooper. Reading, MA: Addison-Wesley Publishing Company, 1993. 358. *Journal of Product Innovation Management*, 11(4), 369-370. https://doi.org/10.1016/0737-6782(94)90105-8

- Natarajan, M., Senthil, V., Devadasan, S.R., Mohan, N.V. & Sivaram, N.M. (2013). Quality and reliability in new product development. *Journal of Manufacturing Technology Management*, 24 (8), 1143-1162. https://doi.org/10.1108/JMTM-03-2011-0022

- Nawrocki, W. (2010). Physical limits for scaling of integrated circuits. *Journal of Physics: Conference Series*, 248(1), 012059. https://doi.org/10.1088/1742-6596/248/1/012059

- Nunes, M.L., Pereira, A., & Alves, A. (2017). Smart products development approaches for Industry 4.0. *Procedia Manufacturing*, 13, 1215-1222. https://doi.org/10.1016/j.promfg.2017.09.035

- Pangracious, V., Marrakchi, Z., & Mehrez, H. (2015) Three-Dimensional Design Methodologies for Tree-based FPGA Architecture (13-41). Springer. https://doi.org/10.1007/978-3-319-19174-4

- Pun, K.P., Dhaka, N.S., Cheung, C., & Chan, A.H. (2017a). Effect of ENEPIG metallization for solid-state gold-gold diffusion bonds. *Microelectronics Reliability*, 78, 339-348. https://doi.org/10.1016/j.microrel.2017.09.019

- Pun, K.P., Islam, M.N., Cheung, C.W., & Chan, A.H. (2017b). Solid-state growth kinetics of intermetallic compounds in Cu pillar solder flip chip with ENEPIG surface finish under isothermal aging. *Journal of Materials Science: Materials in Electronics*, 28(17), 12617-12629. https://doi.org/10.1007/s10854-017-7086-0

- Pun, K.P., Islam, M.N., Rotanson, J., Cheung, C., & Chan, A.H. (2018a). Enhancement of Sn-Bi-Ag Solder Joints with ENEPIG Surface Finish for Low-Temperature Interconnection. *Journal of Electronic Materials*, 47(9), 5191-5202. https://doi.org/10.1007/s11664-018-6385-4

Pun, K.P., Ali, L., Kohtoku, M., Cheung, C., Chan, A.H., & Wong, C.P. (2018b). Latest advancement of fully additive process for 8 µm ultra-fine pitch chip-on-film (COF) by nano-size Ni–P metallization. *Journal of Materials Science: Materials in Electronics*, 29(8), 6937-6949. https://doi.org/10.1007/s10854-018-8680-5

Rajan R. (2016). Advancing Technological Innovation to Enable IoT's Long Tail. Global Foundries. Available at: <a href="http://www.semiconwest.org/sites/semiconwest.org/files/data15/docs/Rajeev%20Rajan\_GF.pdf">http://www.semiconwest.org/sites/semiconwest.org/files/data15/docs/Rajeev%20Rajan\_GF.pdf</a>

Schimmoeller, L.J. (2010). Success Factors of New Product Development Processes. *Advances in Production Engineering & Management*, 5(1), 25-32.

Synaptics (2014). White Paper: Latest Advances in Touch and Display Integration for Smartphones and Tablets. Synaptics Incorporated. https://www.synaptics.com/sites/default/files/touch-display-integration-smartphones-tablets.pdf

Würtenberger, J., Kloberdanz, H., Lotz, J., & Von Ahsen, A. (2014). Application of the fmea during the product development process – dependencies between level of information and quality of result. In *DS 77: Proceedings of the DESIGN, 13th International Design Conference* (417-426). Dubrovnik, Croatia.

Zahra, S.A. (1996). Technology strategy and financial performance: Examining the moderating role of the firms competitive environment. *Journal of Business Venturing*, 11(3), 189-219. https://doi.org/10.1016/0883-9026(96)00001-8

# **Appendix**

Appendix A. List of failure modes

| Component | No. | Potential<br>Failure Mode | Effect of<br>Failure Mode | Causative<br>Variables            | Quality<br>Attribute               | Method of<br>Detection             | $RPN_m$ | Risk<br>Level |

|-----------|-----|---------------------------|---------------------------|-----------------------------------|------------------------------------|------------------------------------|---------|---------------|

|           |     |                           |                           | Interfacial roughness             | Bonding<br>molecule<br>composition | Surface<br>profilometer            |         |               |

|           | 1   | Trace adhesion failure    | Trace peeled off          | Interface<br>bonding<br>mechanism | Anchoring layer                    | XPS analysis<br>on bond<br>content | 470.10  | Critical      |

|           |     |                           |                           | Trace geometry (bottom width)     | thickness                          | Cross<br>sectional<br>analysis     |         |               |

|           | 2   | Peel test failure         | Trace peeled off          | Alkaline concentration            | Peel strength                      | Peel strength test                 | 390.10  | Critical      |

|           | 3   | Porous surface            | Skip pattern<br>build up  | Alkaline concentration            | Modification layer coverage        | SEM inspection                     | 282.53  | Critical      |

| Base Film | 4   | Entrapped contamination   | Skip pattern              | Chemical impurity level           | Contaminant                        | SEM/EDX                            | 106.35  | Moderate      |

|           |     | Contamination             | build up                  | Handling                          | content                            | analysis                           |         |               |

|           |     |                           |                           | Roller alignment                  |                                    |                                    |         |               |

|           | 5   | Scratch                   | Open trace                | Particle deposition               | Scratch density                    | Visual inspection                  | 91.46   | Low           |

|           |     | Scratch                   | Орен пасс                 | Handling                          | Scratch density                    |                                    | 71.40   | Low           |

|           |     |                           |                           |                                   |                                    | Electrical simulation              |         |               |

|           | 6   | Crack/separatio           | Open trace                | Reel tension                      | Crack/separatio<br>n density       | Visual inspection                  | 44.26   | Negligible    |

|           | 7   | Skip/uneven plating       | Skip pattern<br>build up  | Chemical concentration            | Exposed PI region                  | Visual inspection                  | 149.71  | Moderate      |

|           | 8   | Warpage                   | Open trace                | Heat treatment profile            | Surface flatness<br>after reflow   | Flatness<br>measurement            | 146.95  | Moderate      |

| Component            | No. | Potential<br>Failure Mode                | Effect of Failure Mode                     | Causative<br>Variables                        | Quality<br>Attribute     | Method of<br>Detection  | $RPN_m$ | Risk<br>Level |

|----------------------|-----|------------------------------------------|--------------------------------------------|-----------------------------------------------|--------------------------|-------------------------|---------|---------------|

|                      |     |                                          |                                            | CTE mismatch                                  |                          |                         |         |               |

|                      | 9   | Non uniform surface                      | Skip pattern<br>build up                   | Incoming                                      | Surface defect           | SEM                     | 173.37  | Moderate      |

|                      |     | morphology                               | Incompatibility for high speed application | material defect                               | density                  | inspection              | 173.37  | Wodciate      |

|                      |     |                                          |                                            | Current density                               | Bending cycle            | Mandrel test            |         |               |

|                      | 10  | Bending<br>endurance<br>failure          | Trace crack                                | Deposition rate                               | Bending cycle            | SEM inspection          | 220.5   | Critical      |

|                      |     | ranure                                   |                                            | Grain<br>microstructure                       | (annealed)               | FIB cross<br>sectioning |         |               |

|                      |     | Signal                                   | Incompatibility                            | Surface<br>roughness<br>(skin depth)          |                          | Surface<br>profilometer |         |               |

|                      | 11  | delay/propagati<br>on Conductive<br>loss | for high speed<br>application              | Surface finish<br>(material and<br>thickness) | Loss factor              | Electrical simulation   | 316.60  | Critical      |

|                      |     |                                          |                                            | Trace undercut                                | ]                        |                         |         |               |

|                      | 12  | Trace                                    | 75 1                                       | Operating current                             | Thermal                  | Thermal                 | 120.24  | N. 1          |

|                      | 12  | overheating                              | Trace crack                                | Trace surface area                            | dissipation rate         | simulation              | 130.34  | Moderate      |

|                      |     | Surface                                  |                                            | Current density                               |                          |                         |         |               |

| Cu                   | 13  | abnormities                              | Open/short                                 | Deposition rate                               | Surface defect           | SEM                     | 5.09    | Negligible    |

| Metallization        |     | Pits/Pinhole/N odules                    | circuit                                    | Chemical bath impurity                        | density                  | inspection              | 3.07    | regigioie     |

|                      | 14  | Over-deformed                            | Intermittent                               | Plastic deformation                           | Strain                   | Cross section analysis  | 233.30  | Critical      |

|                      | 14  | trace                                    | connection                                 | characteristic                                | Strain                   | SEM inspection          | 233.30  | Chucai        |

|                      | 15  | Via micro-void                           | Signal integrity                           | Deposition rate                               | Void density             | Cross section           | 112.50  | Moderate      |

|                      |     | via illicio-vold                         | Signal integrity                           | Residue                                       | Void size                | analysis                | 112.50  | Moderate      |

|                      |     | Non-Fully filled                         |                                            | Sidewall residue                              |                          | Cross section           |         |               |

|                      | 16  | via                                      | Signal integrity                           | Polyimide<br>melting                          | Via volume               | analysis                | 179.82  | Moderate      |

|                      |     | Uneven plating                           | Not bondable                               | Residue deposit                               | Surface flatness         | Surface                 | 44450   |               |

|                      | 17  | thickness                                | surface                                    | Skip seed layer<br>plating                    |                          | profilometer            | 116.58  | Moderate      |

|                      | 18  | Broken via<br>sidewall                   | Open circuit                               | Metallization integrity                       | Sidewall defect          | Electrical<br>test      | 19.40   | Negligible    |

|                      | 19  | Bridging (bleeding)                      | Short circuit                              | Resist adhesion                               | Insulation resistance    | Electrical test         | 21.60   | Negligible    |

| Photolithogra<br>phy | 20  | Resist bubbles                           | Open/short<br>circuit                      | Coater air entrapment                         | Resist surface<br>defect | Visual inspection       | 11.37   | Negligible    |

|                      |     |                                          |                                            | Lamination temperature                        |                          |                         |         |               |

|                      |     |                                          |                                            | Lamination pressure                           |                          |                         |         |               |

| Component                   | No.             | Potential<br>Failure Mode       | Effect of Failure Mode | Causative<br>Variables        | Quality<br>Attribute                      | Method of<br>Detection    | $RPN_m$ | Risk<br>Level |

|-----------------------------|-----------------|---------------------------------|------------------------|-------------------------------|-------------------------------------------|---------------------------|---------|---------------|

|                             |                 |                                 |                        | Lamination time               |                                           |                           |         |               |

|                             | 21              | Under/over<br>development       | Open/short             | Resist thickness uniformity   | Resist opening width                      | Visual inspection         | 9.18    | Negligible    |

|                             |                 | асторинен                       | Circuit                | Exposure time                 | wictur                                    | nispection                |         |               |

|                             | 22              | Residue<br>deposition           | Open traces            | Chemical bath impurity        | Residue content                           | SEM inspection            | 56.94   | Low           |

|                             | 23              | Exposure<br>Misalignment        | Open/short<br>circuit  | Sprocket hole damage          | Alignment                                 | Visual inspection         | 13.57   | Negligible    |

|                             |                 | Non-uniform                     |                        | Exposure energy source        | Resist feet<br>dimension                  |                           |         |               |

|                             | 24              | profile<br>(Feet<br>Protrusion) | Trace peeled off       | Exposure energy dose          | T/B ratio                                 | SEM<br>inspection         | 142.49  | Moderate      |

|                             |                 |                                 |                        | Resist material               |                                           |                           |         |               |

|                             | 25              | Chemical contaminant            | Solder resist adhesion | Chemical bath impurity        | Contaminant content                       | Tape test                 | 58.38   | Low           |

|                             | 26              | Conductor undercut              | Trace peeled off       | Trace geometry (bottom width) | T/B ratio                                 | FIB cross<br>sectioning   | 208.36  | Critical      |

|                             | 27              | Over-etching                    | Impedance<br>deviation | Etching chemical              | Impedance consistency                     | Cross                     | 203.20  | Critical      |

| Seed layer                  |                 |                                 | deviation              | Etching time                  | Line/space                                | sectioning                |         |               |

| removal                     | 28              | Uneven<br>thickness             | Trace crack            | Etching chemical              | Surface flatness                          | Visual inspection         | 42.11   | Negligible    |

|                             | Seed layer meta |                                 |                        | Etching chemical              | Insulation resistance                     | Insulation                |         |               |

|                             | 29              | residue                         | Short circuit          | Etching time                  | Insulation<br>resistance<br>(after aging) | resistance<br>measurement | 321.48  | Critical      |

|                             | 30              | Exposed copper                  | Corrosion              | Plating chemical              | Copper coverage                           | SEM/EDX<br>analysis       | 224.99  | Critical      |

|                             | 31              | Extraneous plating              | Short circuit          | Plating thickness             | Surface finishing coverage                | Visual inspection         | 27.40   | Negligible    |

| Surface<br>Finishing        | 32              | Metal residue                   | Short circuit          | Disting this base             | Insulation resistance                     | SEM inspection            | 325.36  | Critical      |

| Timsting                    | 33              | Dendrite<br>growth              | Short circuit          | Plating thickness             | Insulation resistance                     | Accelerated aging test    | 242.18  | Critical      |

|                             | 34              | Oxidation                       | Open trace             | Plating chemical              | Oxide content                             | Accelerated aging test    | 209.44  | Critical      |

|                             |                 |                                 |                        |                               |                                           | XPS analysis              |         |               |

|                             | 35              | Sprocket hole                   | Open/short             | Punching pressure             | Sprocket hole                             | Visual                    | 4.50    | Negligible    |

| Reel-to-reel                |                 | burr                            | circuit                | Punching tool residue         | dimension                                 | inspection                | 1.50    | - regugiore   |

| with buss-less<br>technique | 36              | Sprocket hole misalignment      | Wrong registration     | Punching<br>misprogram        | Registration accuracy                     | Visual inspection         | 1.87    | Negligible    |

| accamaque                   | 37              | Evcessive                       | Broken film            | Roller speed<br>mismatch      | Mechanical<br>defect                      | Visual inspection         | 74.95   | Low           |

|                             |                 | CHSIOH                          |                        | Film thickness                | ucicci                                    | шересион                  |         |               |

| Circuit<br>Design           | 38              | Localized stress                | Trace cracking         | Geometry changes              | Bending location                          | Bend test                 | 178.98  | Moderate      |

| Component                          | No. | Potential<br>Failure Mode | Effect of Failure Mode                  | Causative<br>Variables                   | Quality<br>Attribute        | Method of<br>Detection   | $RPN_m$  | Risk<br>Level |

|------------------------------------|-----|---------------------------|-----------------------------------------|------------------------------------------|-----------------------------|--------------------------|----------|---------------|

|                                    | 39  | Impedance drift           | Signal<br>degradation                   | Trace dimension                          | Impedance consistency       | Impedance<br>measurement | 70.07    | Low           |

|                                    | 40  | Overheating               | Trace cracking                          | Thermal dissipation area Signal current  | Thermal dissipation rate    | Thermal simulation       | 182.32   | Moderate      |

|                                    | 41  | Warpage                   | Open solder                             | Reflow profile                           | Surface flatness            | Visual inspection        | 194.52   | Moderate      |

|                                    | ,-  | 181                       | joint                                   | Soldering alloy                          | after reflow                | Electrical test          | 37 1.02  |               |

|                                    |     |                           |                                         | Surface finish (thickness)               | IMCs thickness              | Cross sectioning         |          |               |

|                                    | 42  | DAC 4                     | District                                |                                          | Critical IMCs               | SEM/EDX<br>analysis      | 460.27   | Critical      |

|                                    | 42  | IMCs growth               | Brittle joint                           | UBM consumption rate                     | IMCs growth rate            | Accelerated              | 469.27   | Crucai        |

| Copper Pillar                      |     |                           |                                         |                                          | Die peel failure<br>mode    | aging test               |          |               |

| Soldering (1st level interconnect) | 42  | TC: 1 1 11 : 1            | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | Surface finish (thickness)               | Void dimension              | Cross sectioning         | 404.05   | 36.1          |

|                                    | 43  | Kirkendall void           | Joint reliability                       | Reflow profile                           | Void dimension              | SEM inspection           | 184.85   | Moderate      |

|                                    | 44  | Bridging                  | Short circuit                           | Solder volume                            | Soldering spacing           | Electrical test          | 13.96    | Negligible    |

|                                    | 45  | Non-wetting               | Open joint                              | Surface contamination                    | Contaminant content         | Electrical test          | 19.46    | Negligible    |

|                                    | 46  | Cold joint                | Open joint                              | Reflow profile Soldering alloy           | Melted solder volume        | Electrical test          | 17.59    | Negligible    |

|                                    | 47  | Wicking                   | Open joint                              | Reflow profile                           | Gold plating                | Electrical               | 13.30    | Negligible    |

| Thermo-                            |     | Insufficient              | 1 /                                     | Surface finish  Trace contact            | coverage                    | test                     |          | 8.8           |

| compression<br>Bonding             | 48  | contact/skip<br>contact   | Open joint                              | area (top width)                         | Alignment offset            | X-ray<br>inspection      | 213.25   | Critical      |

| (1st level interconnect)           | 49  | Interfacial void          | Joint reliability                       | Surface finish (thickness)               | · Void formation            | FIB cross                | 328.67   | Critical      |

|                                    | 42  | interfacial void          | Joint renability                        | Surface roughness                        | void iorniauon              | sectioning               | 320.07   | Chucai        |

|                                    | 50  | Substrate                 | Trace crack                             | Reflow peak temperature                  | Substrate                   | Flatness                 | 9.90     | Negligible    |

|                                    |     | warpage                   |                                         | Reflow ramp rate                         | flatness                    | measurement              |          |               |