# Low Energy DRAM Controller for Computer Systems

# Alberto González Trejo

Adrián Cristal Kestelman Marco Antonio Ramírez Salinas

This dissertation is submitted for the degree of Master in Innovation and Research in Informatics at the Universitat Politècnica de Catalunya

© Copyright Alberto González Trejo The material in this publication is protected by copyright law.

Title: Research thesis at the Universitat Politècnica de Catalunya

Author: Alberto González Trejo

### Acknowledgements

First of all, as always, I want to say thanks to my family, who have always been my source of inspiration, motivation and I will always take care of them.

I am very grateful with the Universitat Politècnica de Catalunya and the Instituto Politécnico Nacional, for provide me education and the opportunity to meet and collaborate with many incredible people, I am really thankful for this opportunity.

Last but not least, I really appreciate the support that CONACYT, a mexican government institution, provided me by means of a scholarship, allowing me to study abroad.

"Try not to become a man of success. Rather become a man of value."

Albert Einstein

### **Abstract**

"The Memory System: You can't avoid it, you can't ignore it, you can't fake it."

Bruce Jacob

The performance characteristics of modern DRAM memory systems are primarily impacted for two attributes: the device data rate and the row cycle time. Modern commodity DRAM devices data rates and row cycle times are scaling at different rates with each succesive generation (SDRAM, Open page DRAM, DDR, DDR2, DDR4). As a result, the performance characteristics of modern DRAM memory systems are becoming more difficult to evaluate, and at the same time the called *memory wall*, which points out the gap between the increment on CPU clock frequency and the lower increment in memory speed, is limiting the performance of modern computer systems, which are mainly memory intensive.

The memory controller is the part of the main memory system that is in charge of assuring the proper operation of the DRAM devices and at the same time, it manages the flow of data into and out the DRAM devices. However, due to the complexity of DRAM memory access protocols, the large number of timing parameters, the large number of combinations of memory system organizations, different workload characteristics and different design goals, the design of this specific part of the main memory system has as much freedom as the design space of a processor that implements a specific Instruction Set Architecture.

This specific part of the main memory system is specially treated as a *black box* since its implementation is mainly provided by the same companies that manufacture the computer systems chips (ASICs or FPGAs). This situation leads to a lack of knowledge of how this specific device controller really works.

In this work, we leverage an open source simulation framework to evaluate different memory scheduling algorithms, which allows us to choose the one that performs better in terms of power consumption.

As a result, we provide an architectural design of a memory controller, which is implemented in Verilog and tested on a FPGA platform.

Last but not least, this work provides a thoroughly journey of how a DRAM memory system works and how feasible it is to jump from a simulation framework to the world of actual implementation of a DDR3 DRAM memory controller.

# **Contents**

| Acknowledgements |        |                                                         |     |

|------------------|--------|---------------------------------------------------------|-----|

| Al               | bstrac | et e                                                    | iii |

| 1                | Intr   | oduction                                                | 1   |

|                  | 1.1    | Motivation                                              | 2   |

|                  | 1.2    | Organization of this dissertation                       | 3   |

| 2                | The    | oretical Background                                     | 4   |

|                  | 2.1    | Main memory subsystem                                   | 4   |

|                  | 2.2    | DRAM Devices                                            | 5   |

|                  | 2.3    | DRAM Memory System Organization                         | 8   |

|                  | 2.4    | DRAM Memory Access Protocol                             | 10  |

|                  |        | 2.4.1 Basic DRAM Commands                               | 10  |

|                  |        | 2.4.2 DRAM Command Interactions                         | 18  |

|                  |        | 2.4.3 Minimum Scheduling Distances                      | 30  |

|                  |        | 2.4.4 Power Constraints                                 | 31  |

|                  | 2.5    | DDR3 SDRAM Protocol                                     | 34  |

|                  | 2.6    | DDR3 memory low power modes                             | 37  |

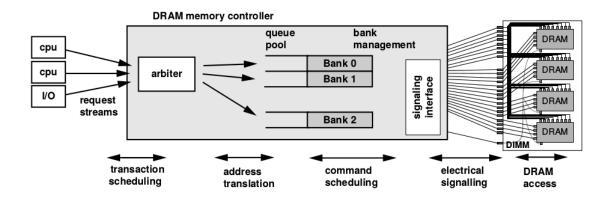

|                  | 2.7    | DRAM Memory Controller                                  | 38  |

|                  |        | 2.7.1 Row Buffer Management Policy                      | 41  |

|                  |        | 2.7.2 Address Mapping Policies                          | 42  |

|                  |        | 2.7.3 DRAM metrics                                      | 42  |

|                  |        | 2.7.4 Memory Scheduling                                 | 43  |

|                  | 2.8    | Related work                                            | 45  |

|                  |        | 2.8.1 Power and energy oriented schedulers              | 46  |

|                  |        | 2.8.2 Related work summary                              | 46  |

| 3                | Met    | hodology                                                | 47  |

|                  | 3.1    | Simulation framework                                    | 47  |

|                  |        | 3.1.1 Power Model                                       | 49  |

|                  | 3.2    | Traffic generators                                      | 51  |

|                  | 3.3    | PARSEC Benchmarks                                       | 51  |

|                  | 3.4    | Memory Controller proposal                              | 52  |

|                  |        | 3.4.1 Delayed Adaptive Closed Page Policy               | 52  |

|                  |        | 3.4.2 Write Drain Policy Exploiting Row Buffer Locality | 52  |

| V |

|---|

|   |

| 4  | Eva    | luation |                    | 55 |

|----|--------|---------|--------------------|----|

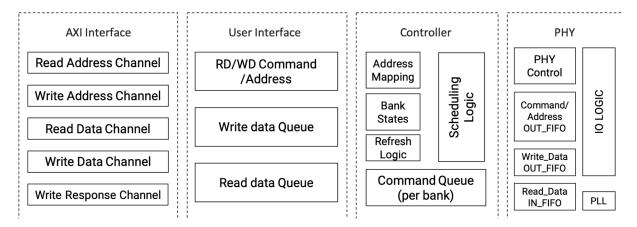

| 5  | Imp    | lementa | ation              | 63 |

|    | 5.1    | Actual  | implementation     | 64 |

|    |        | 5.1.1   | AXI Interface      |    |

|    |        | 5.1.2   | User Interface     | 65 |

|    |        | 5.1.3   | Controller         |    |

|    |        | 5.1.4   | PHY                |    |

|    |        | 5.1.5   | Simulation results |    |

| 6  | Con    | clusion |                    | 72 |

| Bi | bliogi | raphy   |                    | 73 |

# **List of Figures**

| 2.1  | 64 Mbit Fast Page Mode DRAM Device (4096 x 1024 x 16)                   | 6  |

|------|-------------------------------------------------------------------------|----|

| 2.2  | Data I/O in a DDR SDRAM devices illustrating 2-bit prefetch             | 7  |

| 2.3  | Systems with a single memory controller and different data bus widths   | 8  |

| 2.4  | Memory system with 2 ranks of DRAM devices                              | 9  |

| 2.5  | Command and data movement on a generic SDRAM device                     | 11 |

| 2.6  | Different phase of an abstract DRAM command in a generic DRAM device.   | 11 |

| 2.7  | Row access command and timing.                                          | 13 |

| 2.8  | Column read command and timing                                          | 13 |

| 2.9  | Column Write command and timing.                                        | 14 |

| 2.10 | Row precharge command and timing                                        | 15 |

| 2.11 | Row refresh timing.                                                     | 16 |

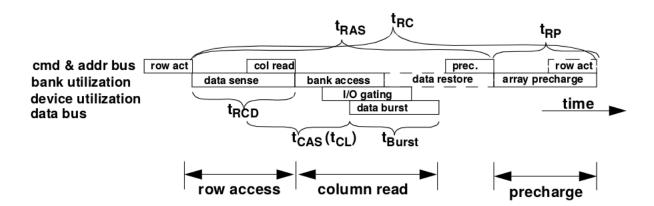

| 2.12 | One read cycle in a "close-page" memory system                          | 17 |

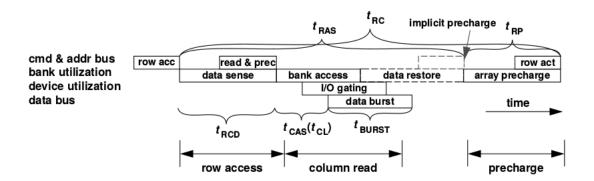

|      | A read cycle with a row access command and a column-read-and-precharge  |    |

|      | command.                                                                | 18 |

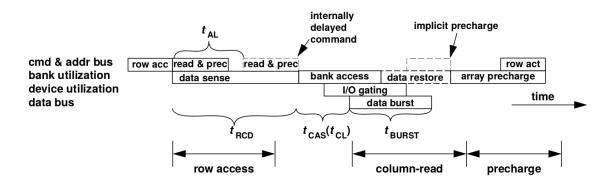

| 2.14 | Posted CAS defers CAS commands in DRAM devices by a preset delay        |    |

|      | value, $t_{AL}$                                                         | 19 |

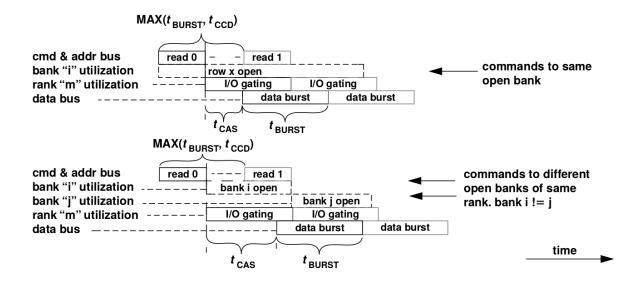

| 2.15 | Consecutive column-read commands to the same bank, rank, and channel    | 20 |

| 2.16 | Read to precharge command timing.                                       | 20 |

| 2.17 | Consecutive column-read commands to different rows of the same bank:    |    |

|      | best-case scenario                                                      | 21 |

| 2.18 | Consecutive column-read commands to different rows of the same bank:    |    |

|      | worst-case scenario.                                                    | 21 |

| 2.19 | Consecutive DRAM read commands to different banks, bank conflict, no    |    |

|      | command reordering.                                                     | 22 |

| 2.20 | Consecutive DRAM read commands to different banks, bank conflict, with  |    |

|      | command reordering.                                                     | 23 |

|      | Consecutive column-read commands to different ranks                     | 24 |

|      | Consecutive column-write commands to different ranks                    | 24 |

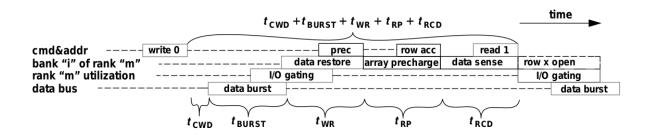

|      | Consecutive write commands, bank conflict, best cases                   | 25 |

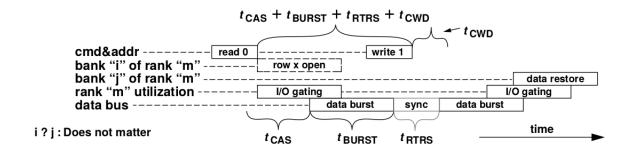

|      | Write command following read command to open banks                      | 26 |

| 2.25 | Write command following read command to same bank: bank conflict, best  |    |

|      | case                                                                    | 26 |

| 2.26 | Write command following read command to different banks: bank conflict, |    |

|      | best case                                                               | 27 |

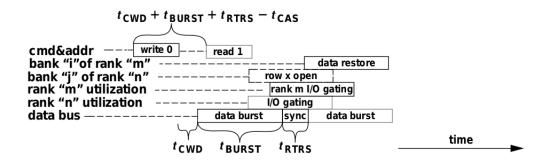

|      | Read following write to the same rank of DRAM devices                   | 28 |

| 2.28 | Read following write to different ranks of DRAM devices                 | 28 |

LIST OF FIGURES vii

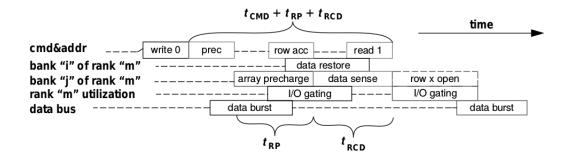

| 2.29 | Read following write to different rows of the same bank: best case    | 29 |

|------|-----------------------------------------------------------------------|----|

| 2.30 | Read following write to different banks, bank conflict, best case     | 30 |

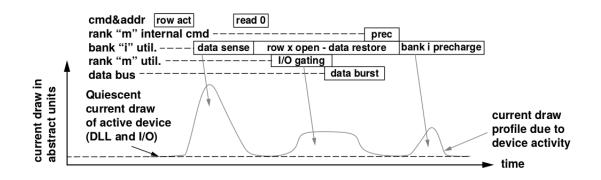

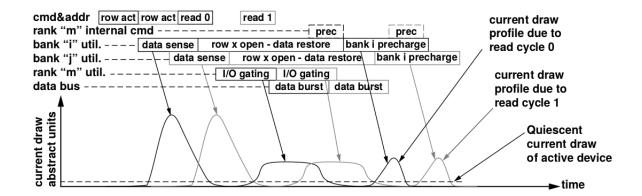

| 2.31 | Current profile of a DRAM read cycle                                  | 32 |

| 2.32 | Current profile of two pipelined DRAM read cycles                     | 33 |

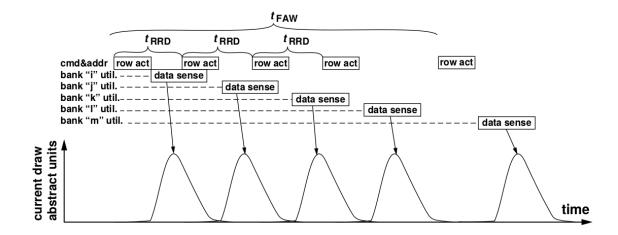

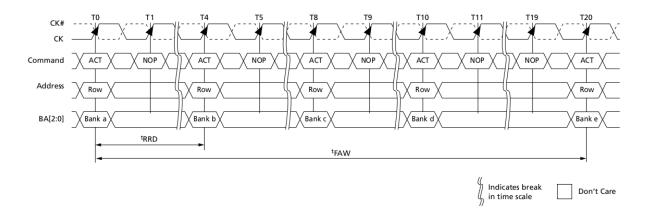

| 2.33 | Maximum of four row activations in any $t_{FAW}$ time frame           | 34 |

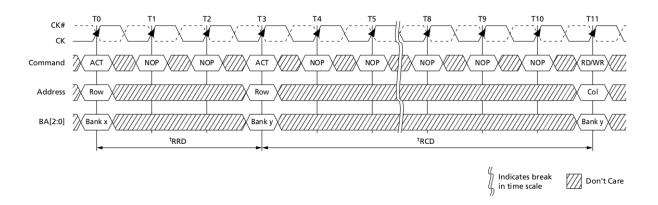

| 2.34 | ACTIVATE command meeting $t_{RRD}$ and $t_{RCD}$                      | 35 |

|      | $t_{FAW}$ example                                                     | 35 |

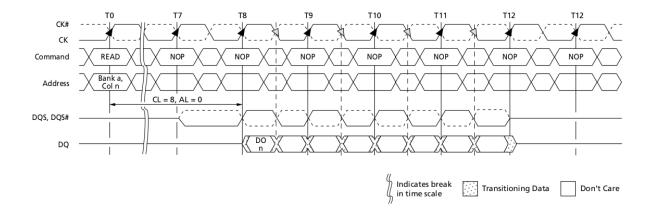

| 2.36 | Read latency.                                                         | 36 |

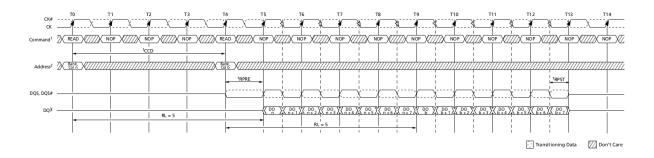

|      | Consecutive READ bursts (BL8)                                         | 36 |

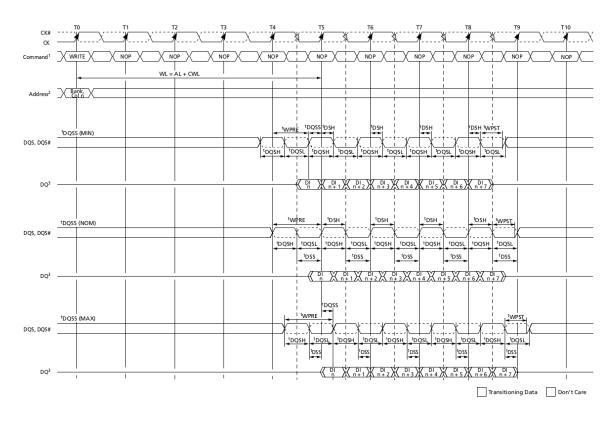

|      | WRITE Burst.                                                          | 37 |

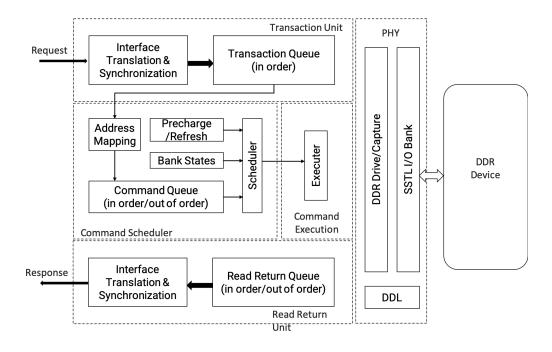

| 2.39 | Abstract DRAM memory controller.                                      | 40 |

| 2.40 | Thread Fair scheduler decision flowchart                              | 45 |

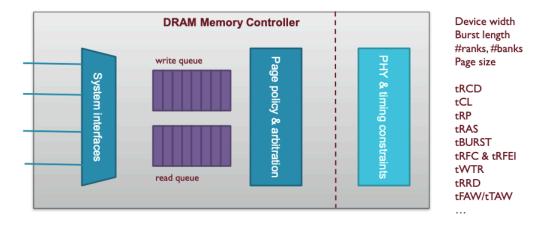

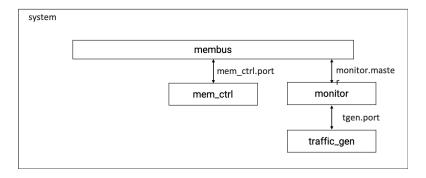

| 3.1  | gem5 DRAM memory controller model                                     | 47 |

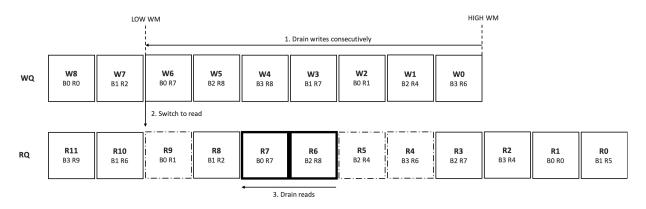

| 3.2  | Conventional Write Drain Policy.                                      |    |

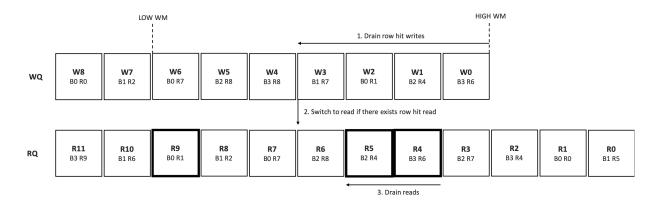

| 3.3  | Proposed Write Drain Policy.                                          | 54 |

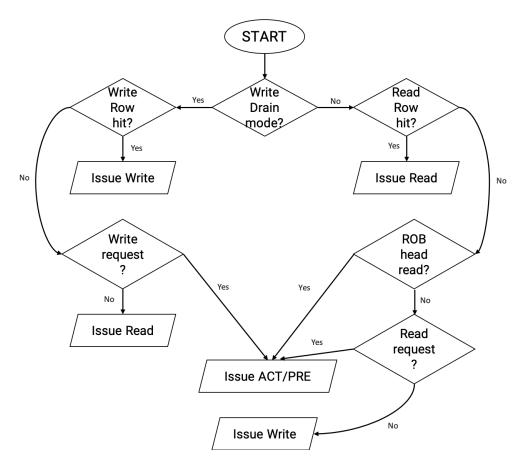

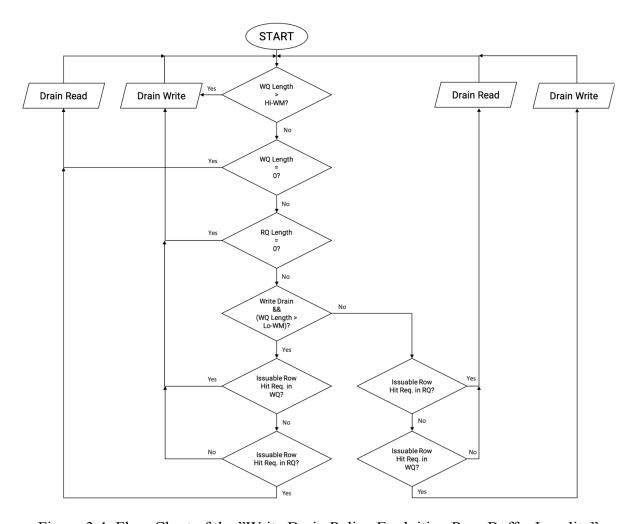

| 3.4  | Flow Chart of the "Write Drain Policy Exploiting Row Buffer Locality" | 54 |

| 4.1  | gem5 simple simulation setup.                                         | 55 |

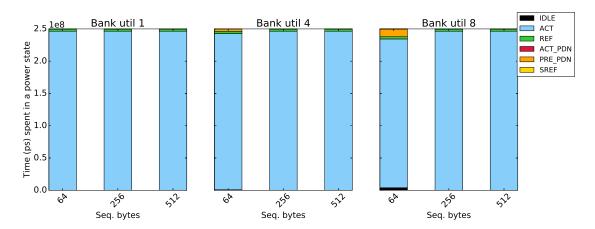

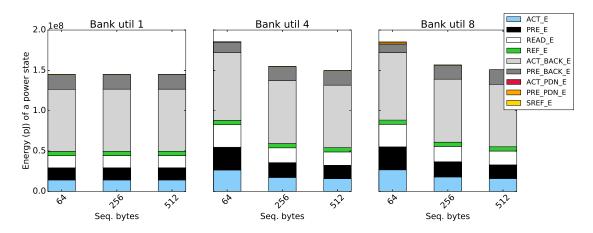

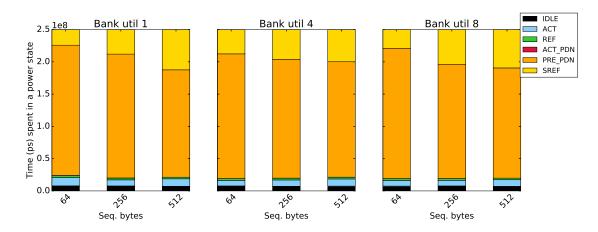

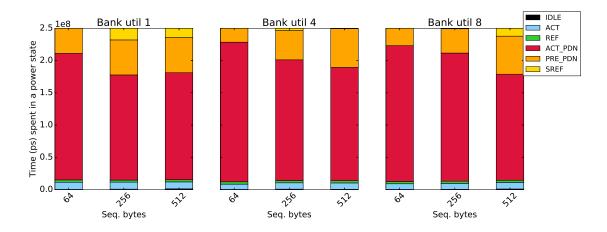

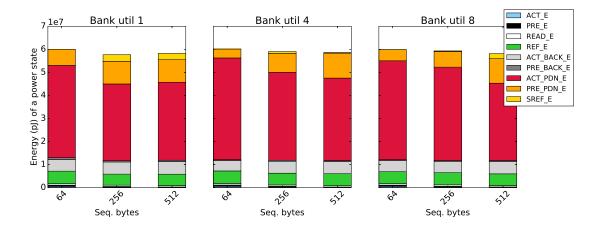

| 4.2  | FCFS - Time spent in power states - very dense traffic.               |    |

| 4.3  | FCFS - Energy consumed by power states - very dense traffic           | 58 |

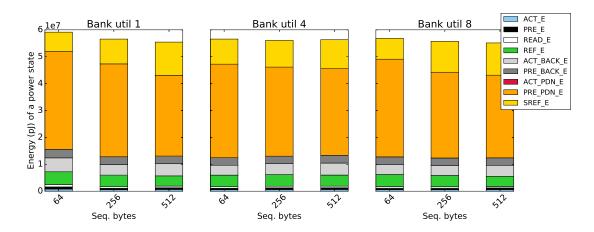

| 4.4  | FCFS - Time spent in power states - sparse traffic                    | 58 |

| 4.5  | FCFS - Energy consumed by power states - sparse traffic               | 59 |

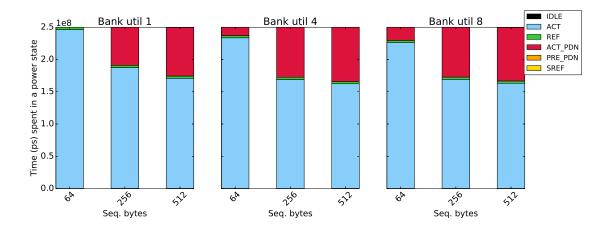

| 4.6  | FR-FCFS - Time spent in power states - dense traffic                  | 59 |

| 4.7  | FR-FCFS - Energy consumed by power states - dense traffic             | 60 |

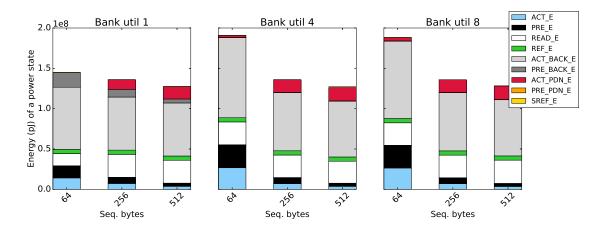

| 4.8  | FR-FCFS - Time spent in power states - sparse traffic                 | 60 |

| 4.9  | FR-FCFS - Energy consumed by power states - sparse traffic            | 61 |

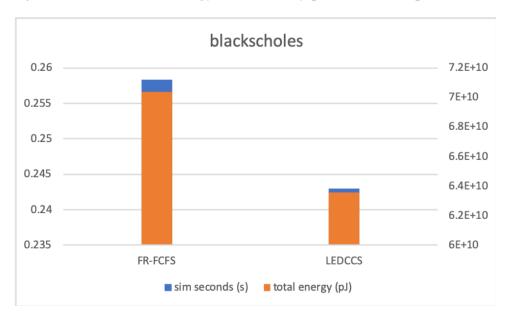

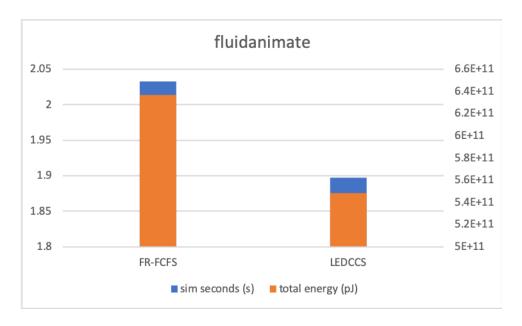

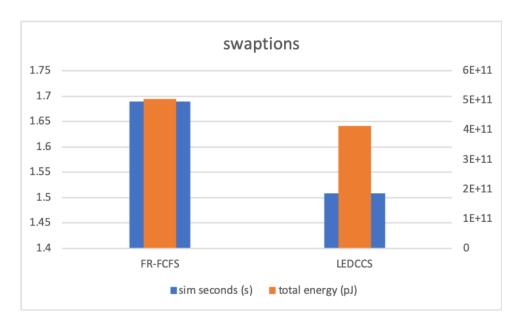

| 4.10 | blackscholes                                                          | 61 |

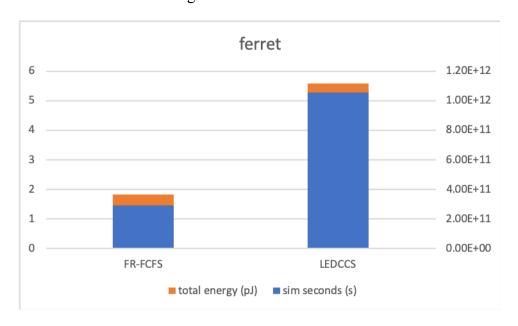

| 4.11 | ferret                                                                | 61 |

| 4.12 | blackscholes                                                          | 62 |

| 4.13 | ferret                                                                | 62 |

| 5.1  | DRAM memory controller architecture.                                  | 63 |

| 5.2  | Actual implementation of DDR3 Memory Controller                       | 64 |

| 5.3  | Bank Management Logic                                                 | 66 |

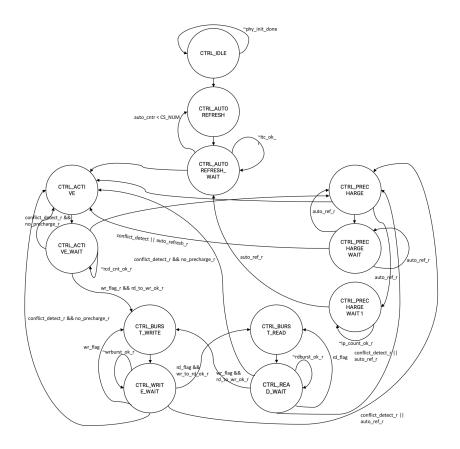

| 5.4  | Controller State Machine Logic.                                       | 68 |

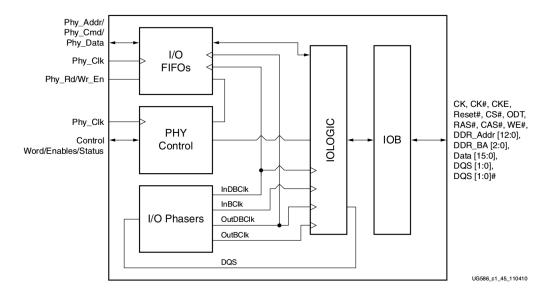

| 5.5  | Single Bank DDR2/DDR3 PHY Block Diagram.                              | 68 |

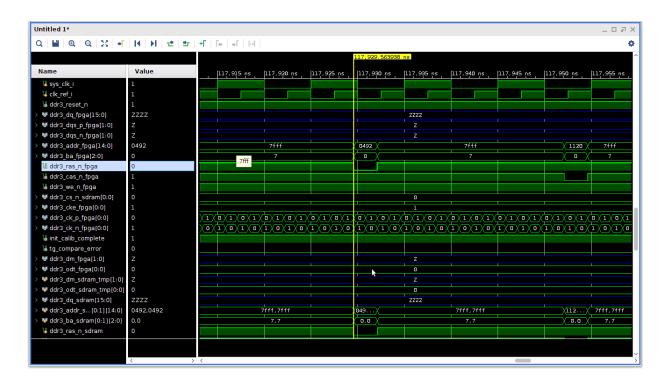

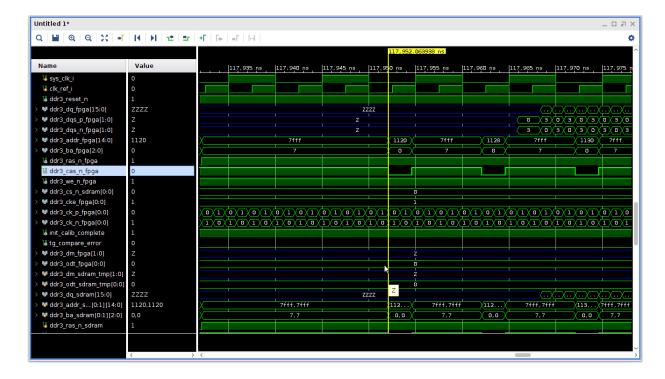

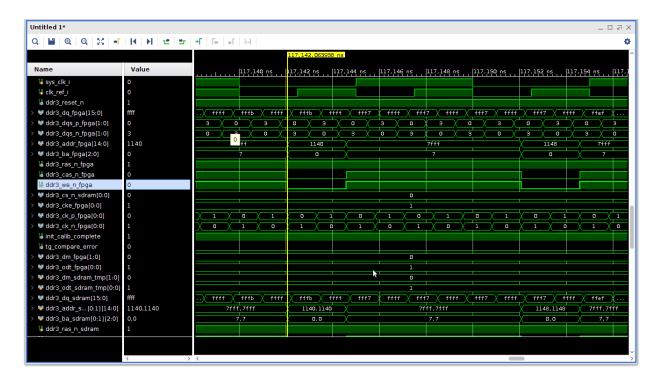

| 5.6  | Activate command.                                                     | 69 |

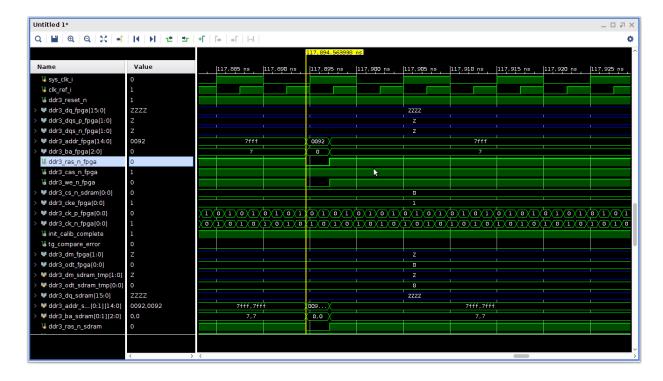

| 5.7  | Read command.                                                         | 69 |

| 5.8  | Write command                                                         | 70 |

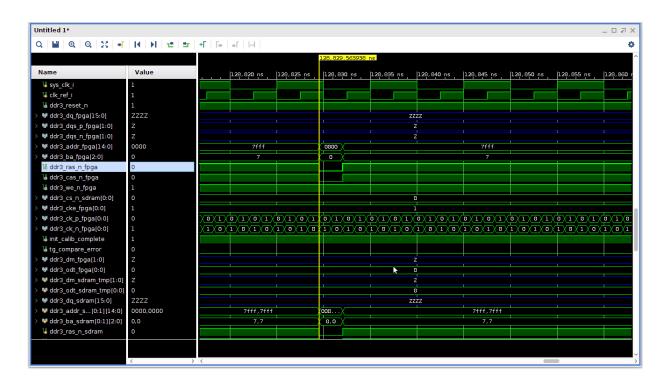

| 5.9  | Precharge command                                                     | 70 |

| 5.10 | Refresh command                                                       | 71 |

# **List of Tables**

| 2.1 | Summary of timing parameters used in generic DRAM access protocol     | 12 |

|-----|-----------------------------------------------------------------------|----|

| 2.2 | Minimum timing for consecutive read and write transactions: open-page | 31 |

| 3.1 | gem5's DRAM model controller parameters                               | 48 |

| 4.1 | gem5's DRAM model controller parameters                               | 56 |

| 4.2 | Traffic parameters in each memory configuration                       | 57 |

| 4.3 | FCFS memory controller configuration.                                 | 57 |

| 4.4 | FR-FCFS memory controller configuration                               | 60 |

| 5.1 | gem5's DRAM model controller parameters                               | 67 |

# Chapter 1

### Introduction

MICROSE Laboratory at *Centro de Investigación en Computación del Instituto Politécnico Nacional*, in Mexico city, has been working along the last 6 years developing innovative high performance computer architectures targetting FPGA-SoC. *Lagarto SoC* is an academic project which is aimed to create an educational environment on computer architecture and operating systems, ranging from high school to graduate school. This thesis is part of this effort.

The memory system behavior has become a focal point of computer architecture research. This is due this part of a computer system is a performance and energy bottleneck in almost all applications. Nowadays, system designers, application developers and many technological trends are pointing to the same direction: more capacity, bandwidth, efficiency and reliability out of the memory system is a must [1].

Recent research ranges from studies of smarter memory controllers and other recent work looks at the performance of different commercial DRAMs at the architectural level, and a wide range of DRAM bus and memory controller organizations at the system level. DRAM performance has relied on technology improvements and only bandwidth-related improvements on architecture.

The continuing increase of data intensive applications are today one of the main concerns regarding main memory systems. This is due mainly two reasons, one is the key design between the power consumed by the main memory system by itself and the other is the QoS (Quality of Service) that has to be delivered in order to be able to leverage the peak features that current modern DRAM devices like DDR3 provide to system designers.

DRAM provides parallelism by means of certain number of banks which operate concurrently. According to [2] all banks in a DRAM chip share the same data, address and command buses. In addition, a number of DRAM devices (8 in DDR3) can be connected to the same bus, this organization is called a *rank*, in order to improve parallelism. The complex internal organization of DRAMs leads to a cumbersome list of timing constraints that govern DRAM behavior.

A typical DDR memory is arranged in banks having multiple rows and columns along with prefetch buffers. For any data transaction, the memory address is split into bank address, row

1.1 Motivation 2

address and column address. The performance advantages of the DDR memory are mainly due to its prefetch architecture with burst oriented operation, which allows to exploit the Dual Rate data transfer intrinsic on these devices, where a memory access to a particular row of a bank causes the prefetch buffer to grab a set of adjacent data words and subsequently burst them on I/O pins on each edge of the data transfer memory clock, without requiring individual column addresses. Thus the higher the size of prefetch buffers, the higher is the bandwidth. Higher bandwidth is also achieved by creating modules with multiple DDR memory chips.

A modern DRAM memory controller employs diverse mechanisms to alleviate the complexity of DRAM devices, those sophisticated mechanisms are address mapping, memory scheduling algorithms and power management optimizations. All these mechanisms work together in order to improve the efficiency of a DRAM memory system.

#### 1.1 Motivation

A state of the art main memory system is composed by a technology device like DDR3 DRAM, and also by a sophisticated memory controller that aims to deliver, between other things, maximum bandwidth. The aim of a DRAM memory controller is to ensure the correct operation of the DRAM module regarding refresh and timing requirements, by issuing commands to the DRAM chip to initiate the active, precharging and I/O phases. A small, seemingly inconsequential change in the sequence or timing commands to the DRAM can result in a huge change in the bandwidth we can get out of the DRAM memory system. Since memory bandwidth is often the bottleneck for critical memory intensive tasks, the change in bandwidth quickly becomes a change in system performance. Unfortunately, the command sequence and timing come from a complex interaction of the application and system software, the various elements of the system hardware, including cache controllers, memory managers, direct memory access (DMA) controllers, accelerators and the DRAM controller. This situation gets more complicated as *Systems on Chip* grow more powerful and complex.

In this work, a low power DRAM memory controller analysis, design and implementation is presented. The aim of this work is to provide a thoroughly journey through how a DRAM memory system works, the analysis of the features of a memory controller which we can take hand to lower power consumption, and also the development of a functional IP is presented.

This dissertation also utilizes a simulation framework based on gem5, which allows us to perform trace based simulation and full system simulation with an event-based memory controller model.

The aim of this work is to provide a complete framework of how a DDR3 DRAM memory controller is designed, ranging from simulation to implementation perspective. We make the following contributions on this thesis:

- We analyze the main memory system in detail.

- We propose a memory scheduling algorithm that optimizes power consumption.

- We contribute to the open source community and provide a basic open source DDR3 Memory Controller targeting FPGA.

- Design and implementation of an interface with the SoC Lagarto.

### 1.2 Organization of this dissertation

In this work a methodical analysis of a DRAM memory system is presented, this is done with the aim of providing enough background information of the tasks a DRAM memory controller is in charge of. In the first chapter, a brief introduction of this work is presented.

In the second chapter, the theoretical background of this work is presented, starting with the main memory subsystem description and the underlying technology of DRAM devices, afterwards the DRAM memory access protocol is described in detail. Also in this chapter the low power modes present on DRAM technology like DDR3 are described, and a generic DRAM memory controller is depicted, giving special attention to the row buffer management and address mapping policies, DRAM metrics and the memory scheduling algorithms; the related work is also presented in this chapter.

The methodology followed in this work is presented in chapter 3. In here the simulation framework, the traces used to evaluate the memory controller proposal and the description of the workloads are described, the memory controller proposal is described in detail in this chapter. The evaluation of the proposal and the results obtained out of the execution of the workloads and trace simulations are presented in chapter 4.

In chapter 5 the actual implementation of the memory controller targeting FPGA is presented. The architectural design and microarchitecture is described. Also, the interface with *SoC Lagarto* is presented. In chapter 6, the conclusions and future work of this thesis are presented.

# Chapter 2

# **Theoretical Background**

In order to ease the understanding of this work, it is provided the needed theoretical background in this section. The contents of this chapter is heavily based on the book "Memory Systems: Cache, DRAM, Disk" by Jacob et al. [3]. This chapter describes the organization of the main memory subsystem and the DRAM technology in specific, giving as example a generic Fast Page Mode DRAM, since current DRAM devices are mainly based on this DRAM architecture. The DRAM memory system organization is described, taking into account different organizations and remarking the DRAM access protocol, the specific DDR3 device operation is presented, and at the end, the description of the memory controller. Also, this chapter describes specifically the architecture of DDR3 devices, since this is the target DRAM device of the final implementation.

The limited goal of this chapter is to provide a broad overview of the functionality of DRAM devices and memory controllers. With the understanding of these fundamentals we can advance in deeper discussions about architectural trade-offs of a memory controller, and memory scheduling algorithms.

### 2.1 Main memory subsystem

The memory subsystem is an important component in all computer systems, this is due this part of computer systems accounts for an important fraction of the computing time and energy consumption. When a processor fails to fetch data from caches, the LLC sends a request to the memory controller. This memory controller is connected to DRAM devices, for example to DIMMs (Dual In-line Memory Module) via memory channels. Then, the memory controller manages a queue of pending memory requests and it's in charge of the scheduling of this requests, always obeying the timing constraints imposed by the DRAM technology.

In a conventional memory system, a memory controller on a processor (same chip) is connected to Dual In-line Modules (DIMMs) via an off-chip electrical memory channel. A modern DDR3 memory channel typically has a 64-bit data bus and a 23-bit address/command bus that can support 1-2 DIMMs. Each DIMM is typically organized in 1-4 ranks. When the memory controller issues a request for a cache line, all DRAM chips in a rank work together to service the request, i.e., a cache line is striped across all chips in a rank. A rank and its constituent DRAM chips are also partitioned into multiple (4-16) banks. Each bank

2.2 DRAM Devices 5

can process a different cache line request in parallel, but all banks in the active rank must sequentially share the data and command wires of the memory channel. JEDEC, the leading developer of standards for the solid-state industry, is in charge of regulating the emerging memory technologies. [2]

#### 2.2 DRAM Devices

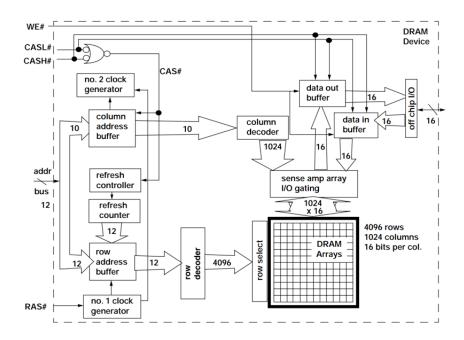

Figure 1. illustrates the organization and structure of an FPM DRAM device. Internally, the DRAM storage cells in the FPM DRAM device shown in Figure 1 are organized as follows: 4096 rows, 1024 columns per row, and 16 bits of data per column. In this device, each time a row access occurs, a 12 bit address is placed on the address bus and the *row address strobe* (RAS) is asserted by an external memory controller; RAS signal is known as row-address strobe. Inside the DRAM device, the address on the address bus is buffered by the row address buffer and then sent to the row decoder. The row decoder then accepts the 12-bit address and selects 1 of 4096 rows of storage cells. The data values contained in the selected row of storage cells are then sensed and maintained in the array of sense amplifiers.

Each row of DRAM cells in this chip consists of 1024 columns and each column is 16 bits wide. That means, a 16 bit wide column is the basic addressable unit of memory in this device, and each column access that follows the row access would ordinary access (read or write) 16 bits of data from the same row of DRAM. The way that a column access is engaged is similar to the row access in that the memory controller would be place a 10 bit address on the address bus, but this time the *column access strobe* (CAS) siganl would be asserted. Internally, the DRAM chip then takes the 10 bit column address, decodes it and uses it to select one column out of 1024 available. The data for that column is then placed onto the data bus or overwritten with data from the data bus depending on the *write enable* (WE) signal.

All DRAM devices, from the FPM DRAM device to modern DDRx SDRAM devices, have similar basic organization. All DRAM devices have one or more arrays of DRAM cells organized into a number of rows and columns, with a column being the smallest unit of addressable memory. All DRAM devices also have some logic circuit that control the timing and sequence how the device operates. In the case of the the FPM DRAM device shown in Figure 1, the chip has internal clock generators as well as built-in refresh controller. In most cases, the DRAM device itself controls the relative timing of the sequence of events for a given action. The FPM DRAM device also keeps the address of the next row that needs to be refreshed, so when the memory controller asserts a new refresh command to the DRAM device, the row address to be refreshed can be loaded from internal refresh counter rather than having to load a separate row address from the off chip address bus. Also, pin usage has always been restrictive on DRAM devices. As a result, modern DRAM devices move data onto and off the device through a set of bi-directional input-output pins connected to the system. [3]

All DRAM devices contain some basic logic control circuitry to direct the movement of data onto, within, and off DRAM devices. This essential control logic accepts externally asserted signal and control, and then orchestrates a timed sequences of internal control signals to di-

2.2 DRAM Devices 6

Figure 2.1: 64 Mbit Fast Page Mode DRAM Device (4096 x 1024 x 16).

rect movement of data on the FPM DRAM device illustrated in Figure 1.

Modern DRAM devices are controlled by synchronous state machines whose behavior depends on the input values of the command signals as well as the values contained in the programmable mode register in the control logic. Some parameters as CAS latency, burst type, burst length and low power modes are some examples of this configurable features. The value of the burst type determines the ordering of the data returned by the SDRAM device. The burst length determines the number of columns that a SDRAM device will return to the memory controller within a single read command.

DRAM devices are classified by the number of data bits in each device and typically that number quadruples from generation to generation. Also, in a given generation, a DRAM device may be configured with a different data bus width. For example, we can have a specific configuration of a 1 Gbit DDR2 SDRAM device with 16,384 rows per bank and each row consists of 8,192 bits. In the x8 configuration, we have 16,384 rows and each row consists of 1024 columns. This configuration is denoted as **256 Meg x 8**. The different configurations lead to a different number of bits per bitline, different numbers of bit per row activation, and different number of bits per column access. Also, the differences in current consumption characteristics in turn leads to difference in timing parameters designed to limit peak power consumption characteristics of DRAM devices.

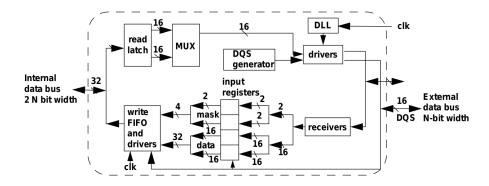

The well known N-bit prefetch in SDRAM devices, implies that each time a column read command is issued by the memory controller, the control logic determines the duration and ordering of the data bursts, and each column is moved separately from the sense amplifiers through the I/O latches to the external data bus. However, the separate control of each column limits the operating data rate of the DRAM device. This leads the following result, in successive generations of SDRAM, specially in DDRx SDRAM devices, successively large

2.2 DRAM Devices 7

numbers of bits are moved in parallel from the sense amplifiers to the read latch, and the data is then pipelined through a multiplexor to the external data bus. Figure 2. illustrates the data I/O structure of a DDR SDRAM device.

Figure 2.2: Data I/O in a DDR SDRAM devices illustrating 2-bit prefetch

Figure 2 shows that given the width of the external data bus as N, 2N bits are moved from the sense amplifiers to the read latch, the 2N bits are then pipelined through the multiplexors to the external bus. In DDR3 SDRAM devices, the number of bits prefetched by the internal data bus is 4N. The downside of the N bit prefetch architecture is that it is not possible to support short bursts, meaning that, in DDR3 devices, a minimum burst length of 8 columns of data are accessed per column read command.

DDR stands for Double Data Rate, this means data is transferred on both the rising and falling edges of the clock signal. This means that the transfer rate is roughly twice the speed of the I/O bus clock. For example, if the I/O bus clock runs at 800 MHz per second, then the effective rate is 1600 Megatransfers per second (MT/s), this is due there are 800 million rising edges per second and 800 million falling edges per second of a clock signal running at 800 MHz. The transfer rate refers to the number of operations transferring data that occur in each second in the data-transfer channel.

DDR architecture is aimed to achieve high-speed operation. The memory operates using a differential clock provided by the controller. Commands are registered at every positive edge of the clock. A bidirectional data strobe (DQS) is transmitted along with the data during reads and by the controller during writes. DQS is edge aligned with data for reads and center aligned with data for writes.

Read and write accesses to the DDR3 SDRAM devices are burst oriented. Accesses begin with the registration of an active command, which is then followed by a read or write command. The address bits registered with the active command are used to select the bank and row to be accessed. The address bits registered with the read or write command are used to select the bank and the starting column location for the burst accesses.

As we can see in the following table, memory vendors use different terminology to advertise their chips, sometimes we can find that bandwidth is indicated as MHz, other times is is expressed as time transfer per second in megabytes.

To calculate the data transmission rate, the transfer rate has to be multiplied by the information channel width, meaning

Channel width

$$*$$

transfer rate = **bits** transferred/second (2.1)

### 2.3 DRAM Memory System Organization

In the context of a complete memory system, the organization and operation of multiple devices is important to examine since this is how current DRAM memory subsystems actually work. The parallel growth rates in DRAM device storage capacity and DRAM memory system capacity have dictated system designs in that multiple DRAM devices must be interconnected together to form larger memory systems for most computer systems.

The organization of multiple DRAM devices into a memory system can impact the performance of the memory systems in such ways as latency, operating datarates, and bandwidth. This is why it is important to present the organization of such systems in detail. In modern DRAM memory systems, commodity non-ECC DRAM memory modules are standardized with 64-bit wide data busses, and the 64-bit data bus width of the memory module matches the data bus width of a typical personal computer system controller.

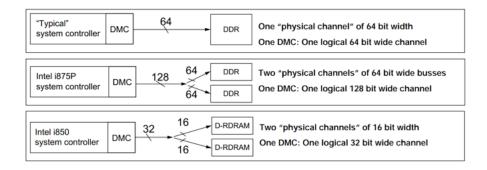

Figure 2.3 shows 3 different single memory controller configurations. The one called "Typical system controller" consists of a single physical memory channel, which is controlled by a single DRAM memory controller.

Figure 2.3: Systems with a single memory controller and different data bus widths.

In the example labelled as *Intel i875P*, the memory controller connects to a single memory channel with a 128 bit wide data bus, but since commodity DRAM module have a 64 bit wide data bus, it is necessary to use a configuration called paired-memory-module which is also referred as dual-channel configuration. It is important to note that since there is only one memory controller, both DRAM modules operate in parallel to store and retrieve data through the 128 bit wide data bus, so in fact, the paired-memory module configuration is in fact a 128 bit wide single channel memory system.

Modern DRAM memory systems with one DRAM memory controller and multiple physical channels of DRAM devices such as those illustrated in Figure 2.3 are typically designed with

the physical channels operating in lockstep with respect to each other.

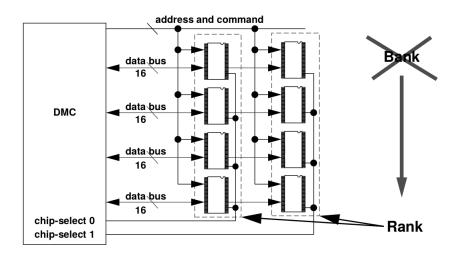

We define a **rank** essentially as a set of one or more DRAM devices that operate in lockstep in response to a given command. Those DRAM devices are controlled with the same command and address buses. Figure 2.4 illustrates a configuration of 2 ranks of DRAM devices, note that address and command buses are connected to every DRAM device in the memory system, but the wide data bus is partitioned and connected to different DRAM devices.

Figure 2.4: Memory system with 2 ranks of DRAM devices.

We use the word **bank** to denote an independent memory array inside a DRAM device. Figure 2.4 shows an SDRAM device with 4 banks of DRAM arrays. Modern DRAM devices contain multiple banks so that multiple, independent accesses to different DRAM arrays can occur in parallel. In this design, each bank of memory is an independent array that can be in different phases of a row access cycle, as we will show in the following sections. Some common resources, such as I/O gating that allows access to the data pins, must be shared between different banks. However, the multi-bank architecture allows commands such as read requests to different banks to be pipelined. Also, multiple banks in a given DRAM device can also be precharged or refreshed in parallel, depending on the design of the DRAM device.

We can think of a **row** in DRAM devices as the group of storage cells that are activated in parallel in response to a row activation command. As we already mentioned, multiple DRAM devices are typically connected in parallel as ranks of memory. The effect of having such configuration (rank of DRAM devices operating in lockstep) is that a row activation command will activate the addressed row in all DRAM device of a given rank of memory. This arrangement means that the size of a row is multiplied by the number of DRAM devices in a given rank, and a DRAM row spans across the multiple DRAM devices of a given rank of memory. A row is also called a *DRAM page*, since a row activation command in essence activates a page of memory. DRAM pages are typically several kilobytes in size, and they are cached at the sense amplifiers until a subsequent precharge command is issued by the DRAM memory controller.

In DRAM memory systems, a **column** of data is the smallest independently addressable unit

of memory. In memory systems such as DDRx, the size of a column of data is the same as the width of the data bus. In DDRx SDRAM memory systems, each column access command loads and stores multiple columns of data depending on the programmed burst length. For example, in a DDR3 DRAM device, each memory read command returns a minimum of 8 columns of data.

### 2.4 DRAM Memory Access Protocol

In this section, the DRAM memory access protocol is examined thoroughly. A memory access protocol defines commands that a DRAM memory controller uses to manage the movement of data on DRAM devices in the memory system. We examine a generic DRAM access protocol by focusing on basic DRAM commands common to all commodity DRAM devices.

#### 2.4.1 Basic DRAM Commands

In this section, five basic commands are described. The descriptions if the basic commands form the foundation of the DRAM memory access protocol, also the interaction of the basic DRAM commands are then used to determine latency response and sustainable bandwidth characteristics of DRAM memory systems.

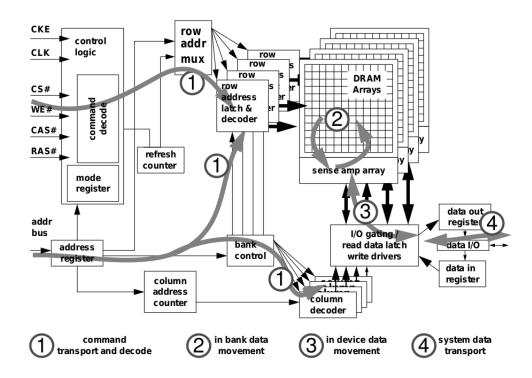

Figure 2.5 illustrates a generic SDRAM device which is used to define the basic memory access protocol. Different phases of operation occurs on the DRAM devices to facilite the movement of data for each command. The generic DRAM access protocol described in this section is based on a resource usage model. That is, the generic DRAM access protocol assumes that two different commands can be fully pipelined on a given DRAM device as long as they do not require the use of a shared resource at the same time, and that there are no additional constraints beyond the immediate resource sharing constraint, like  $t_{RRD}$  and  $t_{FAW}$ .

Figure 2.5 illustrates four overlapped phases of operation for an abstract DRAM command. In phase one, the command is transported through the address and command buses and decoded by the DRAM device. In phase two, data is moved within a bank, either from the cells to the sense amplifiers or from the sense amplifiers back into the DRAM arrays. In phase three, the data is moved through the shared I/O gating, read latches and write drivers. In phase four, data is placed onto the data bus by the DRAM device or the memory controller. Since the data bus may be connected to multiple ranks of memory, no two commands to different ranks of memory can use the shared data bus at the same time.

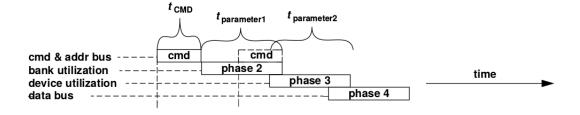

Figure 2.6 illustrates an abstract progression of a generic DRAM command. The time period that it takes to transport the command from the DRAM controller to the DRAM device is illustrated and labelled as  $t_{CMD}$ . Figure 2.6 also illustrates  $t_{parameter}$ , a generic timing parameter that measures the duration of "operation 1". In this text, the timing of operation is measured from the end of the command transport stage until the end of the operation itself <sup>1</sup>. In cases where the duration of an operation limits the timing of command issuance,

$<sup>^{1}\</sup>mathrm{CAS}$  command excepted.  $t_{CAS}$  denotes the beginning of the CAS command to the beginning of the data transport phase.

Figure 2.5: Command and data movement on a generic SDRAM device.

$t_{parameter}$  then defined the minimum time that commands may be placed onto the command and address bus. As a result,  $t_{parameter}$  also denotes the minimum time that must pass between the start of two commands whose relative timing is limited by the duration of an operation measured by  $t_{parameter}$ .

Figure 2.6: Different phase of an abstract DRAM command in a generic DRAM device.

The examination of the DRAM access protocol begins by a definition of the timing parameters. Table 2.1 summarizes the timing parameters used in the description of the DRAM memory access protocol. The timing parameters summarized in table 2.1 is far from a complete set of timing parameters used in the description of a modern memory access protocol. Nevertheless, the timing parameters described here is a minimum set of timing parameters whose use is sufficient to characterize and illustrate important interactions in modern DRAM memory systems.

#### **Row Access Command**

Figure 2.7 abstractly illustrates the progression of a generic row access command, also know as row activation command. The purpose of a row access command is to move data from the

| Parameter   | Description                                                                                                                                                            |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $t_{BURST}$ | Data <b>Burst</b> duration. The time period that data burst occupues on the data bus. Typically 4 or 8 beats of data. In DDR SDRAM, 4 beats of data occupies 2 cycles. |

| $t_{CAS}$   | Column Access Strobe. Time interval between columnd access command and data returned by DRAM device(s). Also known as $t_{CL}$ .                                       |

| $t_{CMD}$   | Command transport duration. Time period that a command occupies on the command bus as it is transported from the DRAM controller to the DRAM devices.                  |

| $t_{CWD}$   | Column Write Delay. Time interval between issuance of column write command and placement of data on data bus by the DRAM controller.                                   |

| $t_{DQS}$   | <b>D</b> ata Strobe turnaround. Used in DDRx SDRAM memory systems. 1 full cycle in DDRx SDRAM.                                                                         |

| $t_{FAW}$   | Four (row) bank Activation Window. A rolling time frame in which a maximum of four bank activation may be engaged. Limits peak current profile.                        |

| $t_{RAS}$   | Row Access Strobe. Time interval between row access command and data restoration in DRAM array. After $t_{RAS}$ , DRAM bank could be precharged.                       |

| $t_{RC}$    | Row Cycle. time interval between accesses to different rows in a given bank. $t_{RC} = t_{RAS} + t_{RP}$ .                                                             |

| $t_{RCD}$   | Row to Column command Delay. Time interval between row access command and data ready at sense amplifiers.                                                              |

| $t_{RFC}$   | Refresh Cycle Time. Time interval between Refresh and Activation command.                                                                                              |

| $t_{RRD}$   | Row activation to Row activation Delay. Minimum time interval between two row activation commands to the same DRAM device. Limits peak current profile.                |

| $t_{RP}$    | Row Precharge. Time interval that it takes for a DRAM array to be precharged and be ready for another row access.                                                      |

| $t_{WR}$    | Write Recovery time. Minimum time interval between end of a write data burst and the start of a precharge command. Allows sense amplifiers to restore data to cells.   |

Table 2.1: Summary of timing parameters used in generic DRAM access protocol.

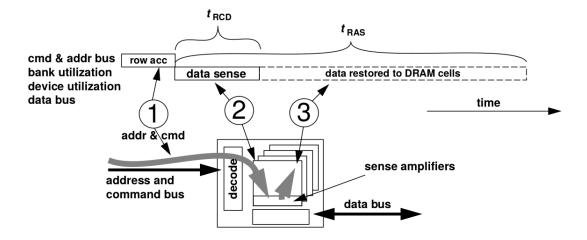

DRAM arrays to the sense amplifiers. Two timing parameters are associated with a row access command:  $t_{RCD}$  and  $t_{RAS}$ . The time it takes for the row access command to move data from the DRAM cell arrays to the sense amplifiers is know as the Row Column (Command) Delay,  $t_{RCD}$ . After  $t_{RCD}$ , an entire row of data is held in the sense amplifiers. At that time, a column read or write access commands can be engaged to move data between the sense amplifiers and the memory controller through the data bus.

After  $t_{RCD}$  time, data is available at the sense amplifiers, but not yet restored to the DRAM cells. A row access command discharges the DRAM cells to the accessed row. As a result, the row of data must be restored from the sense amplifiers back into the DRAM cells before the sense amplifiers can be used to sense the data in a different row. The time it takes for a row access command to discharge and restore data from the row of DRAM cells is known as the Row Access Strobe latency or  $t_{RAS}$ . After  $t_{RAS}$ , the sense amplifiers are assumed to have completed the data restoration process, and the DRAM array can be precharged for another

Figure 2.7: Row access command and timing.

row access to the same bank.

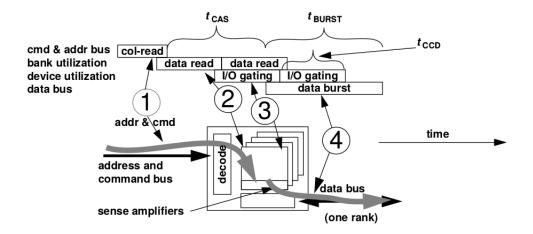

#### **Column Read Command**

Figure 2.8 abstractly illustrates the progression of a column read command. A column read command moves data from the array of sense amplifiers of a given bank to the memory controller. There are two timing parameters associated with a column read command:  $t_{CAS}$  and  $t_{Burst}$ . The time it takes for the DRAM device to place the requested data onto the data bus after issuance of the column read command is known as the Column Access Strobe latency ( $t_{CAS}$ , or  $t_{CL}$ ). After  $t_{CAS}$ , the requested data is moved from the sense amplifiers onto the data bus, the into the memory controller. Modern memory systems move data in relatively short bursts, typically occupying 2, 4 or 8 beats on the data bus. To maintain consistency in the description of the access protocol, the duration of the data burst is described in terms of a time duration rahter than the number of clock cycles. The data burst duration is labelled in Figure 2.8 as  $t_{Burst}$ .

Figure 2.8: Column read command and timing.

Figure 2.8 shows that the column read command goes through 4 separate overlapping phases. In phase one, the command is transported on the address and command bus then decoded by

the DRAM device. In phase two, the appropriate columns of data is retrieved from the sense amplifier array of the selected bank and moved to the I/O gating. In phase three, the data flows through the I/O gating and out to the data bus. In phase four, the data occupies the data bus for time duration of  $t_{Burst}$ .

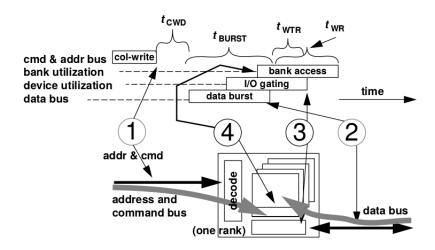

#### **Column Write Command**

Figure 2.9 abstractly illustrates the progression of a column write command. A column write command moves data from the memory controller to the sense amplifiers of a given bank. The column write command goes through a similar set of overlapped phases as the column read command. However, due the fact that the direction of the data movement differs between a read command and a write command, the ordering of the phases is reversed.

Figure 2.9: Column Write command and timing.

In Figure 2.9, phase one shows that the column address and column write command is placed on the address and command bus. In phase two, the data is placed on the data bus by the memory controller. The in phase three, the data flows through the I/O gating, and in phase four, the data reaches the sense amplifiers in the appropriate bank. One timing parameter associated with a column write command is  $t_{CWD}$ , command write delay. Column write delay is the delay between the time when the column write command is issued and the write data moved onto the data bus by the memory controller. Different memory access protocols have different settings for  $t_{CWD}$ . Figure 2.9 also illustrates  $t_{WR}$ , the write recovery time. The write recovery time denotes the time between the end of the data burst and the completion of the movement of data into the DRAM arrays.

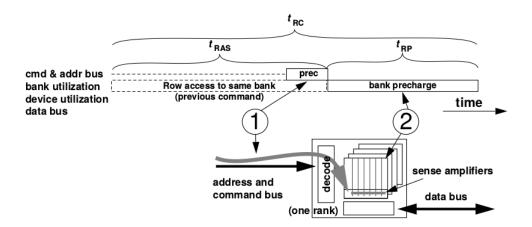

#### **Precharge Command**

Accessing data on a DRAM device is a two step process. A row access command moves data from the DRAM cells to the array of sense amplifiers. The data remains in the array of sense amplifiers for one or more column access commands to move data to and from the DRAM devices to the DRAM controller. In this context, a precharge command completes the sequence as it resets the array of sense amplifiers and the bitlines and prepares the sense amplifiers for another row access command. Figure 2.10 illustrates the progression of

a precharge command.

Figure 2.10: Row precharge command and timing.

Figure 2.10 shows that in the first phase, the precharge command is sent to the DRAM device, and in phase two, the selected bank is precharged. The timing parameter associated with the (row) precharge command is  $t_{RP}$ . The two row-access related timing parameters,  $t_{RP}$  and  $t_{RAS}$  can be combined to form  $t_{RC}$ , the row cycle time. The row cycle time of a given DRAM device denotes the speed at which the DRAM device can bring data from the DRAM cell arrays into the sense amplifiers, restore the data to the DRAM cells, the precharge the bitlines to the reference voltage level and made ready for another row access command. The row cycle time is the fundamental limitation to the speed at which data may be retrieved from different rows within the same DRAM bank.

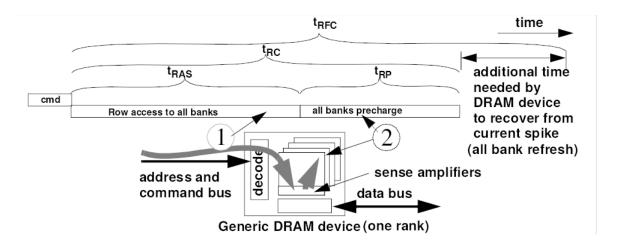

#### **Refresh Command**

The word DRAM is an acronym that stands for Dynamic Random Access Memory. The reason that the memory is referred as "dynamic" is that the electrical charge retained by the storage capacitor gradually leaks as the time passes, and data stored in DRAM cells must be occasionally read out and restored to full value. A DRAM refresh command accomplishes the task of data readout and restoration to full value into the DRAM cells. As long as the time interval between refresh commands is shorter than the worst case time period in which data in storage cells deteriorate to indistinguishable values, DRAM refresh commands can be used to overcome leaky DRAM cells and maintain functionality of the DRAM storage system. The drawback to the refresh mechanism is that refresh commands consume bank bandwidth and power. As a result, there are a number of different refresh mechanism used by different systems, some are designed to minimize controller complexity while others are designed to minimize bandwidth impact.

DDR3 SDRAM devices require Refresh cycles at an average periodic interval of  $t_{REFI}$ . All banks of the SDRAM must be precharged and idle for a minimum of the precharge time  $t_{RP_{min}}$  before the Refresh Command can be applied. To simplify refresh management, each DRAM device has an internal refresh counter that tracks the rows to be refreshed during the next refresh operation. Normal memory operations resume only after the completion of an

Auto-Refresh command, when the refresh cycle has completed, all banks of the SDRAM will be in the precharged (idle) state. A delay between the Refresh Command and the next valid command must be greater than or equal to the minimum Refresh cycle time  $t_{RFC_{min}}$ , and this parameter depends on memory density.

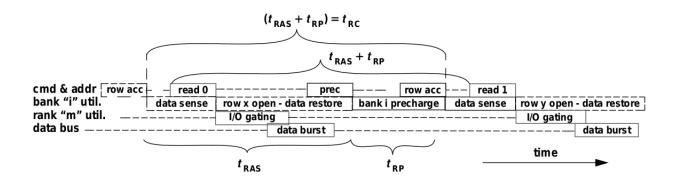

Figure 2.11 illustrates a basic refresh command that allows the DRAM controller to send a single refresh command to refresh one row in all banks. When a basic refresh command is issued, the DRAM device takes a row address from an internal register, then sends the same row address to all banks to be refreshed concurrently. The single refresh command to all banks take one refresh cycle time to complete. Figure 2.11 also illustrates that the refresh cycle time  $t_{RFC}$ , is at least equal to the row cycle time  $t_{RC}$ , and in many cases, much longer than  $t_{RC}$ .

Figure 2.11: Row refresh timing.

The refresh command illustrates one weakness of the resource usage model in that according to the strict interpretation of the resource usage model, a DRAM controller should be able to issue a refresh command to a DRAM device every row cycle time. However, Figure 2.11 shows that the DRAM device can issue the basic refresh command only once every refresh cycle time, and that refresh cycle time is longer than the row cycle time. The reason that the resource usage model fails in this case is because the basic bank-concurrent refresh cycle is power-limited, and the DRAM device needs more time for the current spike induced by the concurrent refresh of all banks in a given DRAM device to settle before another refresh or row activation command can be engaged.

In modern DRAM memory systems, depending on the refresh requirement of the DRAM devices, the memory controller typically injects one row refresh command once every 64 milliseconds for each row in a bank. That is, in a DRAM device with 8192 rows per bank and 64ms refresh cycle requirement, 8192 refresh commands are issued every 64 ms to a DRAM device to refresh one row in all banks concurrently. Depending on the design of the memory controller, the 8192 refresh commands may be issued consecutively or evenly distributed throughout the 64 ms time period.

#### A Read Cycle

Figure 2.12 illustrates a read cycle in a generic DRAM memory system. In modern DRAM devices, each row access command brings thousands of bits of data in parallel to the array of sense amplifiers in a given bank. A subsequent column read command then brings tens or hundreds of those bits of data through the data bus into the memory controller. For applications that are likely to stream through memory, keeping thousands of bits of a given row of data active at the sense amplifiers means that subsequent memory reads from the same row do not have to incur the latency or energy cost of another row access. In contrast, applications that are not likely to access data in adjacent locations favor memory systems that immediately precharges the DRAM array and prepares the DRAM bank for another access to a different row.

In figure 2.12, a sequence of commands in an abstract memory system designed for applications that do not to benefit from keeping rows of data in the sense amplifiers for subsequent accesses is illustrated. As show in Figure 2.12, data is brought in from the DRAM cells to the sense amplifiers by the row access command. After  $t_{RCD}$ , data from the requested row has been resolved by the sense amplifiers, and a subsequent column read command can then be issued by the memory controller. After  $t_{CAS}$ , the DRAM chip begins to return data on the data bus. Concurrent with the issuance of the column read command, the memory device actively restores data from the sense amplifiers to the DRAM cells, and after  $t_{RAS}$  from the initial issuance of the row access command, the DRAM cells would be ready for another row access.

Figure 2.12: One read cycle in a "close-page" memory system.

Collectively, memory systems that immediately precharges a bank to prepare it for another access to a different row are known as **close-page** memory systems. Memory systems that keep rows active at the sense-amplifiers are known as **open-page** memory systems.

#### **Complex Commands**

Some DRAM devices support commands that perform more complex series of actions. Figure 2.13 shows the same sequence of DRAM commands as presented in Figure 2.12, however, the simple column-read command is replaced with a compound *column-read-and-precharge* command. As the name implies, the latter command combines a column-read com-

mand and a precharge command into a single command. The advantages of a column-readand-precharge command is that for close-page memory systems that precharge the DRAM bank immeadiately after a read command, the column-read-and-precharge command reduces the bandwidth requirement on the command and address bus. The implicit advantage of a combined command comes from the memory controller is now able to place a different command on the address and command bus that a separate precharge command would have otherwise occupied.

Figure 2.13: A read cycle with a row access command and a column-read-and-precharge command.

Figure 2.13 shows a colum-read-and-precharge command as issued by the memory controller to the DRAM device in the earliest time slot possible after the row access command while still respecting the  $t_{RCD}$  timing requirement, but the implicit precharge command is delayed so that it does not violate the  $t_{RAS}$  timing requirement.

Another type of complex command supported by DDR3 SDRAM memory system is the posted-CAS command. The posted-CAS command is simply a delayed column access command. Figure 2.14 abstractly illustrates a posted-CAS command. The posted CAS command is simply an ordinary column access (read or write) command that can be issued to the DRAM device before  $t_{RCD}$  for the row activation command has been satisfied. The DRAM device internally delays the action of the CAS command. The number of delay cycles for the posted CAS command is pre-programmed into the DRAM device. The advantage of the posted CAS command is that it allows a DRAM memory controller to issue the column access command immediately after the row access command.

#### 2.4.2 DRAM Command Interactions

By using the resource usage model, DRAM commands can be scheduled consecutively subject to availability of shared on-chip resources such as sense amplifiers, I/O gating multiplexors, and the availability of off-chip resources such as the command, address and data buses. However, even with the availability of some shared resources, some other considerations have to be taken into account when scheduling DRAM commands.

This section examines read and write commands in a memory system with simplistic openpage and close-page row buffer management policies. In a memory system that implements

Figure 2.14: Posted CAS defers CAS commands in DRAM devices by a preset delay value,  $t_{AL}$ .

the open-page and close-page row buffer management policies. In a memory system that implements the open-page row buffer management policy, once a row is opened for access, the array of sense amplifiers continues to hold an entire row of data for subsequent column read and write accesses to the same row. Open-page memory systems rely on workloads that access memory with some degree of spatial locality so that multiple column accesses can be performed to the same row and minimizes the number of DRAM row cycles. In an open-page memory system, DRAM command sequence for a given request depends on the state of the memory system, and the dynamic nature of the command sequences in open-page memory systems means there are larger numbers of possible DRAM command interactions and memory system state combinations in an open-page memory system than the number of DRAM command interactions in a close-page memory system. This leads to a more complex command interactions and higher degree of difficulty in scheduling command sequences in open-page memory systems. The detailed examination of DRAM command combinations enables the creation of a table that summarizes the minimum scheduling distances between DRAM commands. The summary of minimum scheduling distances in turn enables performance analysis of DRAM memory systems later on.

#### **Consecutive Reads to Same Rank**

In modern DDR DRAM systems, read commands to the same open row of memory in the same bank, rank, and channel can be pipelined and scheduled consecutively subject to the availability of the data bus. Figure 2.15 shows two read commands, labelled as read 0 and read 1, pipelined consecutively. As illustrated in Figure 2.15,  $t_{CAS}$  after a read command is placed onto the command and address bus, the DRAM devices begins to return data on the data bus. Since column read commands to the same open bank of the same rank can be pipelined consecutively, and the limitation on the scheduling of these commands is the duration of the data burst on the data bus, it follows that consecutive DRAM read commands to the same row of the same bank of memory can be scheduled every  $t_{Burst}$  time period.

In DDR3 DRAM memory systems, read commands to open rows in different banks within the same rank of memory can also be pipelined consecutively. Similar to consecutive column read commands to the same bank of the same rank of memory, DRAM column read commands can be scheduled to different open banks within the same rank of memory once

Figure 2.15: Consecutive column-read commands to the same bank, rank, and channel.

every  $t_{Burst}$  time period, as shown in Figure 2.15.

#### **Read to Precharge Timing**

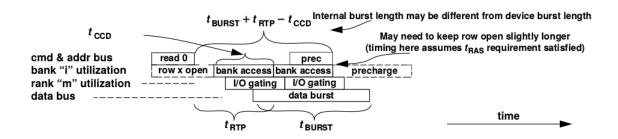

Figure 2.16 illustrates the minimum command timing for a precharge command that immediately follows a column-read command. The formula for minimum command timing is defined as  $t_{Burst} + t_{RTP} - t_{CCD}$ . We can notice that essentially, the timing parameter  $t_{RTP}$  itself specifies the minimum amount of time that is needed between a column-read command and a precharge command.

Figure 2.16: Read to precharge command timing.

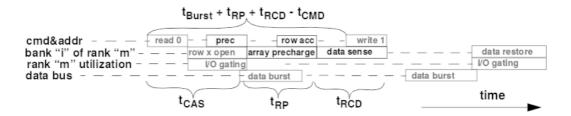

#### Consecutive Reads to Different Rows of Same Bank

Read commands to different rows within the same bank would incur the cost of an entire row cycle time as the current DRAM array must be precharged and a different row activated by the array of sense amplifiers.

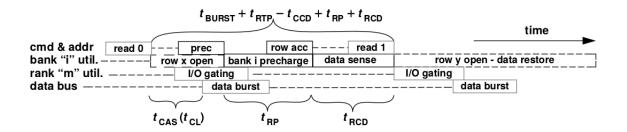

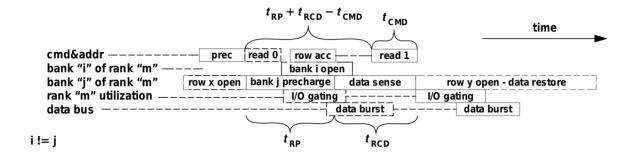

Best Case Scenario: Figure 2.17 illustrates the timing and command sequence of two consecutive read requests to different rows within the same bank of memory array. In this sequence, the first read command, labelled as read 0 is issued, the array of sense amplifiers must be

precharged before a different row to the same bank can be accessed. After a time period  $t_{RP}$  from the issuance of a precharge command, a different row access command can then be issued, and time period  $t_{RCD}$  after the row access command, the second read command labelled as read 1 can then proceed. Figure 2.17 illustrates that consecutive column read accesses to different rows within the same bank could at best be scheduled with minimum timing of  $t_{Burst} + t_{RP} + t_{RCD}$ .

Figure 2.17: Consecutive column-read commands to different rows of the same bank: best-case scenario.

Worst Case Scenario: Figure 2.18 illustrates the best case timing of two consecutive read commands to different rows of the same bank. However, in the case that data from the current row had not yet been restored to the DRAM cells, a precharge command cannot be issued until  $t_{RAS}$  time period after the previous row access command to the same bank. In contrast to the best case scenario shown in Figure 2.17, Figure 2.18 shows the worst case timing for two consecutive read commands to different rows of the same bank where the first column command was issued immediately after a row access command. In this case, the precharge command cannot be issued immediately after the first column read command, but must wait until  $t_{RAS}$  time period after the previous row access command has elapsed. Then,  $t_{RP}$  time period after the precharge command, the second row access command could be issued, and  $t_{RCD}$  time period after that row access command, the second column read command completes this sequence of commands.

Figure 2.18: Consecutive column-read commands to different rows of the same bank: worst-case scenario.

The difference between the two different scenarios means that a DRAM memory controller must keep track of the timing of a row access command and delay any row precharge command until the row restoration requirement has been satisfied.

#### Consecutive Reads to Different Banks: Bank Conflict

In this section we examine the case of consecutive read requests to different banks with the second request hitting a bank conflict against an active row in that bank. This scenario has several different combinations of possible minimum scheduling distances that depend on the state of the bank as well as the capability of the DRAM controller to re-order commands between different transaction requests.

#### Without Command Re-Ordering

Figure 2.19 illustrates the timing and command sequence of two consecutive read requests to different banks of the same rank, and the second read request is made to a row that is different than the active row in the array of sense amplifiers. There are three implicit assumptions in Figure 2.19. The first assumption made is that both banks i and j are open, where bank i is different from bank j. The second read request is made to bank j, but to different row than the row of data presently held in the array of sense amplifiers of bank j. In this case, the precharge command to bank j can proceed concurrently with the column read access to a bank i. The second assumption made in Figure 2.19 is that the  $t_{RAS}$  requirement had been satisfied in bank j, and bank j can me immediately precharged. The third and final assumption is that the DRAM controller does not support command or transaction re-ordering between different transaction requests. That is, all of the DRAM commands associated with the first request must be scheduled before any DRAM commands associated with the second request can be scheduled.

Figure 2.19: Consecutive DRAM read commands to different banks, bank conflict, no command reordering.

Figure 2.19 shows that due to the bank conflict, the read request to bank j is translated into a sequence of three DRAM commands. The first command in the sequence precharges the sense amplifiers to bank j, the second command brings the selected row to the sense amplifiers, and the last command in the sequence performs the actual read request and returns data from the DRAM devices to the DRAM controller. Figure 2.19 illustrates that consecutive read requests to different rows, with the second row hitting a bank conflict, given that the DRAM command sequences cannot be dynamically re-ordered, then the two requests can be at best be scheduled with the minimum timing distance of  $t_{CMD} + t_{RP} + t_{RCD}$ .

Figure 2.20 shows that the DRAM memory system can obtain bandwidth utilization if the DRAM controller can interleave or re-order DRAM commands from different transaction requests. Figure 2.20 shows the case where the DRAM controller allows the precharge command for bank j to proceed ahead of the column read command for the transaction request to bank i. In this case, the column read command to bank i can proceed in parallel with the precharge command to bank j, since these two commands utilize different resources in different banks. To obtain the better utilization of the DRAM memory system, the DRAM controller must be designed with the capability to re-order and interleave commands from different transaction requests. Figure 2.20 shows that in the case the DRAM memory system can interleave and re-order DRAM commands from different transaction requests, the two column read commands can be scheduled with the timing of  $t_{RP} + t_{RCD} - t_{CMD}$ . Figure 2.20 thus illustrates one way that a DRAM memory system can obtain better bandwidth utilization with advanced DRAM controller designs.

Figure 2.20: Consecutive DRAM read commands to different banks, bank conflict, with command reordering.

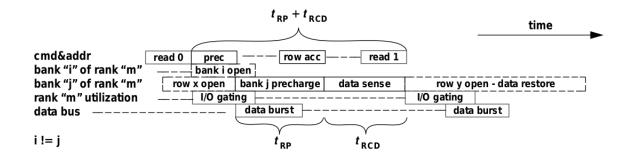

#### **Consecutive Read Requests to Different Ranks**

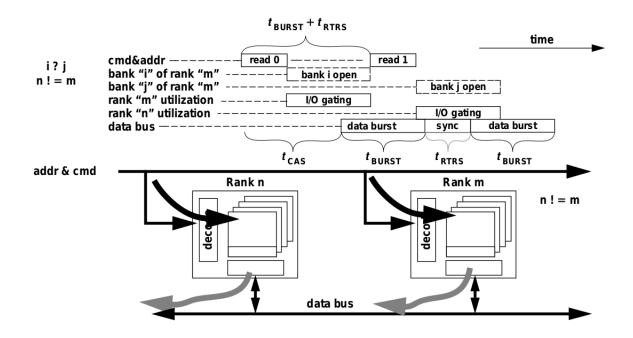

Consecutive read commands to the open banks of the same rank of a DRAM device can be issued and pipelined consecutively. However, consecutive read commands to different ranks of memory may not be issued and pipelined back to back depending on the system level synchronization mechanism and the operating data rate of the memory system. Figure 2.21 illustrates the timing and command sequence of two consecutive read commands to different ranks. In Figure 2.21, the read-write data strobe re-synchronization time is labelled as  $t_{DQS}$ . For relatively low frequency SDRAM memory systems, data synchronization strobes are not used, and  $t_{DQS}$  is zero. However, for DDR3 SDRAM memory systems, the use of a system level data strobe signal shared by all of the ranks means that the  $t_{DQS}$  data strobe re-synchronization penalty is non-zero.

#### **Consecutive Write Requests: Open Banks**

Differing from the case of consecutive column read commands to different ranks of DRAM devices, consecutive column write commands to different ranks of DRAM devices can be pipelined consecutively in modern DRAM memory systems. The difference between consecutive column write commands to different ranks of DRAM devices and consecutive column

Figure 2.21: Consecutive column-read commands to different ranks.

read commands to different ranks of DRAM devices is that in case of consecutive column read commands to different ranks of DRAM devices, one rank of DRAM devices must first send data on the shared data bus, give up control of the shared data bus, then the other rank of DRAM devices must then take control of the shared data bus and send its data to the DRAM memory controller. In the case of the consecutive column write commands to different ranks of memory, the DRAM memory controller sends the data to both ranks of DRAM devices without needing to give up control of the shared data bus to another bus master. Figure 2.22 shows two write commands to different ranks, labelled as write 0 and write 1, pipelined consecutively, and consecutive column write commands to open banks of memory can occur every  $t_{Burst}$  cycles without needing any idle time on the data bus.

Figure 2.22: Consecutive column-write commands to different ranks.

#### **Consecutive Write Requests: Bank Conflicts**

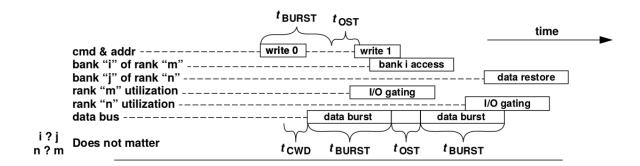

Similar to the case of consecutive read requests to different rows of the same bank, consecutive write requests to different rows of the same bank must also respect the timing requirements of  $t_{RAS}$  and  $t_{RP}$ . Additionally, column write commands must also respect the

timing requirements of the write recovery time  $t_{WR}$ . In case of write commands to different rows of the same bank, the write recovery time means that the precharge cannot begin until the write recovery time has allowed data to move from the interface of the DRAM devices through the sense amplifiers into the DRAM cells. Figure 2.23 shows two of the best case timing of two consecutive write requests made to different rows in the same bank. The minimum scheduling distance between two write commands to different rows of the same bank is  $t_{CWD} + t_{Burst} + t_{WR} + t_{RP} + t_{RCD} - t_{CMD}$ .

Figure 2.23: Consecutive write commands, bank conflict, best cases.

Figure 2.23 also shows the case where consecutive write requests are issued to different ranks of DRAM devices with the second write request resulting in a bank conflict. In this case, the first write command proceeds, and assuming that bank j for rank n had previously satisfied the  $t_{RAS}$  timing requirement, the precharge command for a different bank or different rank can be issued immeadiately. Similar to the case of the consecutive read requests with bank conflicts to different banks, bank conflicts to different banks and different ranks for consecutive write requests can also benefit from command re-ordering.

#### Write Request Following Read Request: Open Banks

Similar to consecutive read commands and consecutive write commands, the combination of a write command that immediately follows a read command can be scheduled consecutively subject to the timing of the respective data bursts on the shared data bus. Figure 2.24 illustrates a write command that follows a read command and shows that the internal data movement of the write command does not conflict with the internal data movement of the read command. As a result, a column write command can be issued into the DRAM memory system after a column read command as long as the timing of data burst returned by the DRAM device for the column read command does not conflict with the timing of the data burst sent by the DRAM memory controller of the DRAM device. Figure 2.24 shows that the minimum scheduling distance between a read command that follows a read command is  $t_{CAS} + t_{Burst} + t_{DQS} - t_{CWD}$ .

Figure 2.24: Write command following read command to open banks.

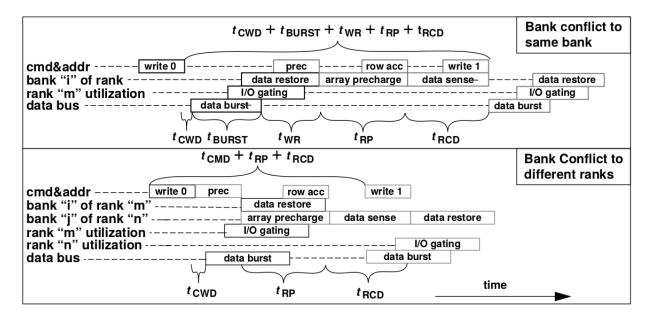

#### Write Following Read: Same Bank, Conflict, Best Case

Figure 2.25 illustrates the best case scenario for a write request that follows a read request to the same bank, but to different rows. In the best case scenario presented in Figure 2.25, data in the row accessed by the read request has already been restored to the DRAM cells. That is, the  $t_{RAS}$  timing requirement has already been sastisfied for the row held by bank "i" before the read command illustrated in Figure 2.25 was issued into the DRAM memory system. Figure 2.25 shows that under this condition, the precharge command can be issued consecutively to the column read command. The row access command to the different row in bank i can then be issued into the DRAM memory system after the DRAM array in abnk i is precharged. The column write command can then proceed after time  $t_{RCD}$  following the row access command. Figure 2.25 thus shows that a read request that follows a read request to different rows of the same bank can at best occur wih the minimum scheduling distance of  $t_{Burst} + t_{RP} + t_{RCD} - t_{CMD}$ .

Figure 2.25: Write command following read command to same bank: bank conflict, best case

Figure 2.25 shows the best case timing of the scenario where a read request that follows a read request to different rows of the same bank. The best case scenario assumes that the  $t_{RAS}$  timing requirement has been satisfied for bank i. In worst case that the read command was in fact issued immediately after the preceding row access command, the  $t_{RAS}$  timing requirement must be satisfied before the precharge command can be issued. In the worst case scenario, the minimum scheduling distance between the column read command and the column write command that follows it increases to an entire row cycle  $t_{RC}$ .

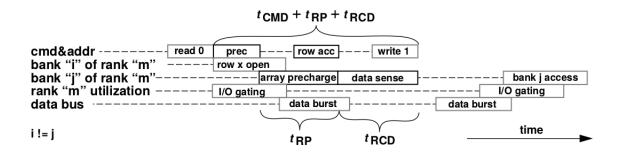

#### Write Following Read: Different Banks, Conflict, Best Case

Figure 2.26 illustrates the case where a write request follows a read request to different banks. Figure 2.26 shows that the column read command is issued to bank i, the column write com-

mand is issued to bank j, and i is different from j. In the common case, the two commands can be pipelined consecutively with the minimum scheduling distance shown in Figure 2.24. However, the assumption given in Figure 2.26 is that the write command is a write command to a different row than the row currently held in bank j. As a result, the DRAM memory controller must first precharge bank j and issue a new row access command to bank j before the column write command in bank j had already been restored to the DRAM cells, and more than  $t_{RAS}$  time period had elapsed since row was initially accessed. figure 2.26 shows that under this condition, the read command and the write command that follows it to a different bank can best scheduled with the minimum scheduling distance of  $t_{CMD} + t_{RP} + t_{RCD}$ .

Figure 2.26: Write command following read command to different banks: bank conflict, best case

Figure 2.26 shows the case where the ordering between DRAM commands from different requests is strictly observed. In this case, the precharge command sent to bank j is not constrained by the column read command to bank i. In a memory system with DRAM memory controllers that support command re-ordering and interleaving DRAM commands from different transaction requests, the efficiency of the DRAM memory system in scheduling a write request with a bank conflict that follows a read request can be increased.

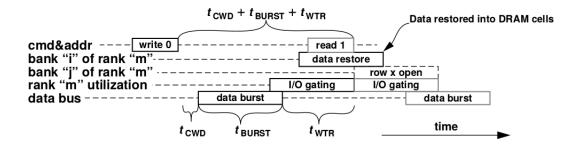

#### Read Following Write to Same Rank, Open Banks

Figure 2.27 shows the case for a column read command that follows a column write command to open banks in the same rank of DRAM devices. The difference between a column read command and a column write command is that the direction of data flow within the selected DRAM devices is reversed with respect to each other. The importance in the direction of data flow can be observed when a read command is scheduled after a write command to the same rank of DRAM devices.

Figure 2.27 shows that the difference in the direction of data flow limits the minimum scheduling distance between the column write command and the column read command that follows the same rank of devices. Figure 2.27 also shows that after the DRAM controller places the data onto the data bus, the DRAM device must make use of the shared I/O gating resource in the DRAM device to move the write data through the buffers into the proper columns of the selected bank. Since the I/O gating resource is shared between all banks within a rank of DRAM devices, the sharing of the I/O gating device means that a read command that follows a write command to the same rank of DRAM devices must wait

Figure 2.27: Read following write to the same rank of DRAM devices.

until the write command has been completed before the read command can make use of the shared I/O gating resources regardless of the target or destination bank ID's of the respective column access commands.

Figure 2.27 shows that the minimum scheduling distance between a write command and a subsequent read command to the same rank of memory is  $t_{CWD} + t_{Burst} + t_{WR} - t_{CMD}$ . In order to alleviate the write-read turnaround time illustrated in Figure 2.27, some high performance DRAM devices have been designed with write buffers so that as soon as data have been written into the write buffers, the I/O gating resource can be used by another command such as a column read command.

### Read Following Write to Different Ranks, Open Banks