# Maximum Voltage Decision Maker Circuit with Shift Register as a Robot

Ganesh Adhikari\*

Associate Professor, Electronics and Communication Department & Computer Engineering Nepal College of Information Technology, Balkumari, Lalitpur, Kathmandu, Nepal \*Email: ganeshpa@nec.edu.np DOI: http://doi.org/10.5281/zenodo.2557988

#### Abstract

The article presents a concept of designing a maximum voltage decision making circuit supporting decision-making processes in selecting maximum voltage(out of many voltages) and further that voltage uses by multidirectional shift Register (acts as a Robot) to shift the value in different directions. The purpose of the system is to help in making decision to select maximum voltage by circuit itself (instead of manually by some human being) and further support to develop technique to shift bit value of voltage with provision of selection lines (robot concept based) in different directions based on requirements. Basic purposes and assumptions regarding the design and development of this system as well as a description of its operation have been presented.

Keywords: MUX, Shift register, Maximum voltage decision making circuit, Latches and Flipflop, Interfacing, Timing diagram

#### **INTRODUCTION**

In 21<sup>st</sup> Century, Manual concept of selecting higher voltage assumed to time consuming, one of the tedious process and under categories comes the of impracticable applications.

Thus Maximum voltage decision making circuit is an efficient solution for selecting higher voltage. Circuit designers are faced with challenge of developing system with increasing functionality and complexity while under demanding power and timeto-market constraints. Such system often requires maximum voltage decision making circuit to allow interfacing among MUX, Maximum voltage decision making circuit, and Shift Register built from different process technologies. It helps to find exact solution you need. The choice of proper "Robotic device concept" depends on many factors and will affect the performance and efficiency of the circuit.

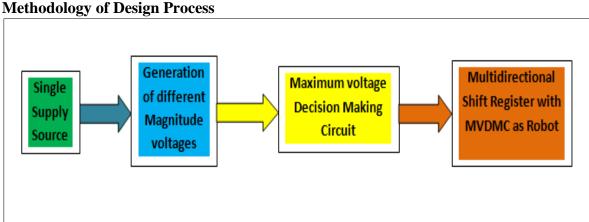

Figure 1: Illustration of Methodology Adopted in Design Process.

The methodology process involves in first phase; the circuit is designed to generate different magnitude voltages that act as input to maximum voltage decision circuit. In second phase, these magnitudes of different voltages are compared; and higher magnitude of voltage is selected by Maximum voltage decision circuit. Further in the third phase, A shift register circuit with MVDMC is designed to act as Robot where in this voltage used by shift Register becomes capable of shifting the value in different directions up, down, hold static, east, west, north, and south based on system requirement with provision of selection line and ultimately acts as a Robot.

### Concept of Developing a Different Magnitude Voltage

A concept is developed to generate different magnitude voltages from a single voltage source. Three step up transformers are used to generate three different magnitude voltages by using the concept of transformer relation as;

5V5V10V10V10V15V

Figure 2: Three Step up Transformers are Used to Generate 3 Different Magnitude Voltages.

# Concept of Developing Maximum Voltage Decision Making Circuit

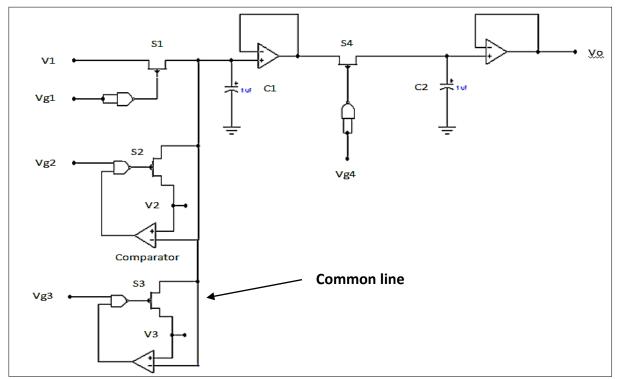

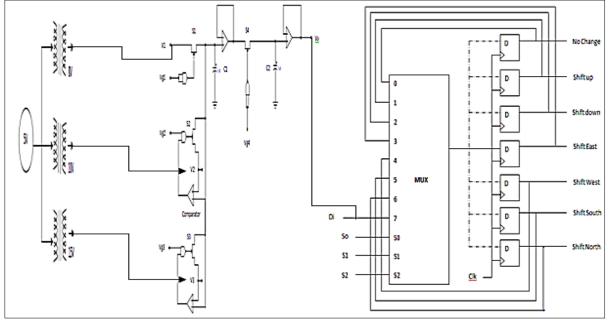

A concept is developed to design maximum voltage decision making circuit wherein different magnitude of voltages are compared with available voltages and the circuit selects higher magnitude of voltage, further transfer it to at output line. As shown in the circuit Figure 3, the input voltages V1, V2 &V3 are to be compared and the largest value has to be presented at the output at Vo.

To understand the circuit operation concept in elaborated form, Let V1 = 8V, V2 = 10V and V3 = 15V. First V1 is compared with V2. To compare V1 with V2, Switch S1 is closed for time 0 to T, Capacitor C1 charges to V1.During time interval T & 2T, V2 are compared with V1 in comparator 1.

If V2 > V1, the comparator output is +Ve. NAND gate N2 output is logic '0' closes the switch S2, now capacitor charges to V2. If V2 < V1, S2 remains open and the capacitor voltage remains at V1.

Now the common line becomes at higher voltage. Now this higher voltage V2 is compared with V3 in comparator 2; during time interval 2T & 3T. If V3 > V2, the comparator output becomes +Ve. NAND gate N3 output becomes at logic '0' closes

the switch S3, now capacitor charges to V3. If V3 < V2, S3 remains open and the capacitor voltage remains at V2.

At t = 3T, S4 closes & capacitor C2 charges to VC1 (max), The output is at VC1 (max), the output voltage Holds this value until t = 7T, at that time the voltage on C2 changes to the new value of VC1 (max).

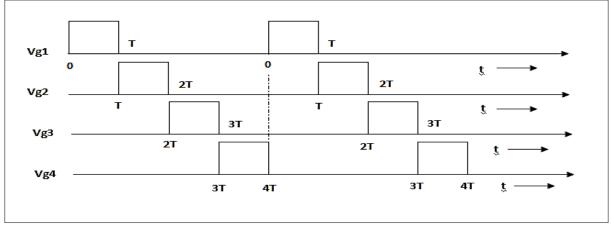

A 4-stage ring counter can be used to generate the gate pulses Vg1, Vg2, Vg3 & Vg4. By extending the above concept (N - 1) comparators and (N+1) gate pulses are needed to compare N-signals.

Figure 3: Maximum Voltage Decision Making Circuit.

Figure 4: Timing Diagram MVDMC.

# Concept of Developing Multi Directional Shift Register

A concept is developed and accordingly a system is designed wherein A Register

becomes capable of shifting binary data in multiple directions.

| Table 1: | Function | for typical | stages. |

|----------|----------|-------------|---------|

|          |          |             |         |

| Mode Control |           | ontrol    | <b>Bagistan</b> Operation |  |

|--------------|-----------|-----------|---------------------------|--|

| <b>S2</b>    | <b>S1</b> | <b>S0</b> | <b>Register Operation</b> |  |

| 0            | 0         | 0         | No change                 |  |

| 0            | 0         | 1         | Shift up                  |  |

| 0            | 1         | 0         | Shift down                |  |

| 0            | 1         | 1         | Shift East                |  |

| 1            | 0         | 0         | Shift West                |  |

| 1            | 0         | 1         | Shift South               |  |

| 1            | 1         | 0         | Shift North               |  |

| 1            | 1         | 1         | Parallel Load             |  |

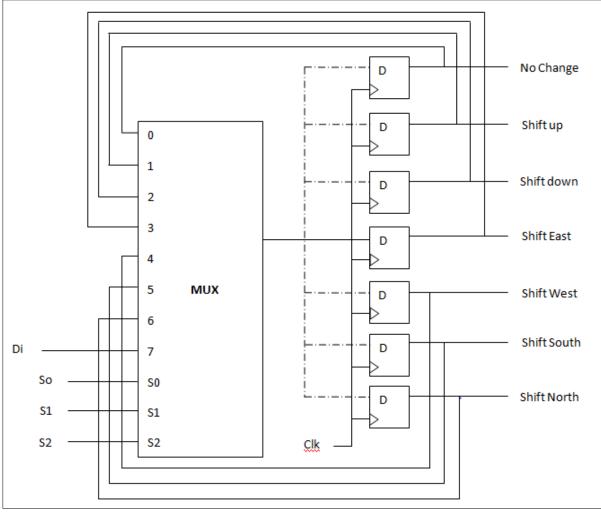

The three selections inputs S2, S1, and S0 select one of the multiplexer inputs for the

D Flip-flop. The selection line controls the mode of operation of the Register according to function Table 1. When the mode control S1, S1, S0 = 000, the multiplexer input 0 is selected and this form path each flip-flop output into its own input. The next clock transition transfer into each flip-flop the binary value it held previously and no change of state occurs.

Figure 5: Multidirectional Shift Register.

When S2, S1, S0 = 001, the terminal marked 1 on the multiplexer has a path to the D input of each flip-flop. These paths cause a shift up operation.

Similarly, the process is repeated for different values of S2, S1, S0 as 010, 011, 100, 101, and 110, ultimately results into shift operations as shift down, shift East, Shift West, Shift South, and shift North.

When S2, S1, S0 = 111, the binary information on each parallel input line is

transferred into the corresponding flipflop, resulting into parallel load.

**Complete Circuit Design via Interfacing**

The complete circuit design for *"Maximum* voltage decision making circuit with Shift Register as a Robot" is obtained through interfacing of three circuit as i) Single source to multiple voltages generating circuit, ii) Maximum voltage decision making circuit, and iii) Multiple Register shift circuit.

Figure 7: MVDMC with shift Register circuit as Robot.

# CONCLUSION

The complete circuit design results into successfully converting "A maximum voltage decision making circuit with shift register acting as a Robot" capable of shifting the data value in different direction based on requirement within the system. This design concept to shift data in different direction based on requirement within a system is one of most relevant applications, to meet Circuit designer's challenge of developing system with increasing functionality and complexity while under demanding power and timeto-market constraints. MAT JOURNALS

#### REFERENCES

- 1. Taub. H & Schilling D. Digital Integrated Electronics. *Tata McGraw Hill – Latest edition*. 2015.

- 2. Hodges D.A. & Jackson H.G. Analysis and design of Digital Integrated Circuits. *Tata McGraw Hill – Latest edition*. 2016.

- 3. Ganesh Adhikari. Text book of *"Digital Integrated Electronics"* Sukunda Publication Nepal, 2011.

- Ganesh Adhikari. Text book of "Logic circuit and Modern Digital Techniques" Sukunda Publication Nepal, 2013.

5. Mano, M. Morris. Digital Logic and Computer Design, Prentice Hall, Latest edition, 2016.

#### Cite this article as:

Ganesh Adhikari. (2019). Maximum Voltage Decision Maker Circuit with Shift Register as a Robot (Version MUX, Shift register, Maximum voltage decision making circuit, Latches and Flip-flop, Interfacing, Timing diagram). Journal of Control and Instrumentation Engineering, 5(1), 1–6. http://doi.org/10.5281/zenodo.2557988