Graduate Theses, Dissertations, and Problem Reports

2004

# PIC 18F452 implementation of digital filters

Vikram A. Bose-Mullick West Virginia University

Follow this and additional works at: https://researchrepository.wvu.edu/etd

#### **Recommended Citation**

Bose-Mullick, Vikram A., "PIC 18F452 implementation of digital filters" (2004). *Graduate Theses, Dissertations, and Problem Reports.* 1418.

https://researchrepository.wvu.edu/etd/1418

This Thesis is protected by copyright and/or related rights. It has been brought to you by the The Research Repository @ WVU with permission from the rights-holder(s). You are free to use this Thesis in any way that is permitted by the copyright and related rights legislation that applies to your use. For other uses you must obtain permission from the rights-holder(s) directly, unless additional rights are indicated by a Creative Commons license in the record and/ or on the work itself. This Thesis has been accepted for inclusion in WVU Graduate Theses, Dissertations, and Problem Reports collection by an authorized administrator of The Research Repository @ WVU. For more information, please contact researchrepository@mail.wvu.edu.

#### PIC 18F452 IMPLEMENTATION OF DIGITAL FILTERS

#### Vikram A Bose-Mullick

Thesis Submitted to the college of Engineering at West Virginia University in partial fulfillment of the requirements for the degree of

> Master of Science in Electrical Engineering

Powsiri Klinkhachorn, Ph.D., Committee Chairperson Roy Nutter, Ph.D. Robert McConnell, Ph.D.

**Lane Department of Computer Science and Electrical Engineering**

Morgantown, West Virginia 2004

Keywords: Microchip PIC, 18F452, FIR filter, LMS, Adaptive Filter, Noise Cancellation, Echo Cancellation, Filter Design

Copyright 2004 Vikram A Bose-Mullick

# **ABSTRACT**

#### PIC 18f452 implementation of digital filters

#### Vikram A Bose-Mullick

This research hopes to explore the computational limits of the PIC18f452 chip by encompassing the designing and implementation of two types of filters for the PIC 18F452 microcontroller. The main purpose of this research is to implement a floating-point least mean square (LMS) error adaptive filter and its secondary goal is a fixed-point implementation of finite impulse response (FIR) filter. FIR filters are specified via a graphical user interface (GUI) and upon demand, optimized C-language code is generated for the popular CCS PIC C-Compiler. In is the intent of this research to learn whether FIR filters can be made computationally viable on the PIC18 chips, can they run stably with reliable and repeatable performance? What is the minimum execution time possible at the processing limits of the chip? And how is filter attenuation affected when taps are scaled down from floating-point to fixed point? For the floating point LMS filter it desired to explore the relationship between sampling-rate and filter order and to develop a hardware optimized floating point library for general use. The minimum execution time for the LMS filter achieved during this research is 26.7 µs per order. The FIR filter code generation software developed during this study allows graphical specification, inspection of response curves. It ultimately presents three options for automatic code generation - program-space efficient code (uses minimum code space), data-memory efficient code (uses minimum RAM) and speed-efficient code (optimized for quickest execution), thereby allowing up to a 75th order FIR filter with the best execution time of 800ns per MAC cycle achieved at the bit-depth of 8-bit samples and 8-bit taps. The filter tap conversion from floating-point format to 8-bit fixed point reduced the attenuation by an average of 28%. In general, both filters gave a strong performance with consistent, reliable and repeatable results.

# **DEDICATION**

Both small and large, to everyone that made a difference. Above all, I dedicate my work to my kind and loving family.

## **ACKNOWLEDGEMENT**

I wish to express my deepest possible thanks to Dr Powsiri Klinkhachorn my advisor and dear friend, for his excellent guidance and boundless friendship. Even though I've never received an 'A' from him, I have no regrets because I have learned more in his classes than all my 'A's put together.

A special thanks to Dr. Roy Nutter for bringing microprocessors into my depth of field through his innovative lectures, inspiring chats and for showing us the value of journals and periodicals. They contained the very first sparks that led to my intense love of the subject.

I express my deep appreciation for to Dr. McConnell from whom I learned the fundamentals for analog and digital without which nothing is possible.

Thank you gentleman for your generosity of spirit, for your infinite kindness you're your constant support and finally for making the time to serve in my committee.

A special thanks to my friend Tal Gottesman for filling in and picking up the slack during during zillions of hours that were spent putting this document together.

Finally my thanks to Braxton Lewis and my boss Dr. McCawley for all their constant help and support.

# TABLE OF CONTENTS

| Abstractii                                          |

|-----------------------------------------------------|

| Dedication iii                                      |

| Acknowledgementsiv                                  |

| Table of contents                                   |

| List of Figuresviii                                 |

| List of Tablesxii                                   |

| List of Symbols / Nomenclaturexiii                  |

| CHAPTER 1: INTRODUCTION                             |

| 1.1 Personal Motivation1                            |

| 1.2 Signal Processing using the PIC 18F4522         |

| 1.3 Digital Filters Vs Analog Filters3              |

| 1.4 PIC 18 Microcontroller Family3                  |

| 1.5 Detailed Research Objectives and Contributions4 |

| 1.6 Organization6                                   |

| CHAPTER 2: LITERATURE SURVEY7                       |

| 2.1 Classification of Filtering Methods7            |

| 2.2 Digital Filters7                                |

| 2.3 Non-Recursive Type Digital Filters8             |

| 2.4 Switching type digital filters9                 |

| 2.5 Adaptive Filters9                               |

| 2.6 Least Mean Squared Error (LMS)10                |

| 2.8 Implementation of a digital filter              |

| HAPTER 3: IMPLEMENTATION DETAILS                             |

|--------------------------------------------------------------|

| 3.1 Finite Impulse Response (FIR)1                           |

| 3.2 Implementation Background1                               |

| 3.3 FIR Filter Implementation1                               |

| 3.3.1 User specification1                                    |

| 3.3.2 Filter Tap Generation2                                 |

| 3.3.3 Coefficient Scaling2                                   |

| 3.3.4 Code generation2                                       |

| 3.3.5 Buffering Data2                                        |

| 3.3.6 Sampling: Analog to Digital Conversion3                |

| 3.3.7 Filter Calculations3                                   |

| 3.3.8 Implementation for Shortest Execution Time4            |

| 3.3.9 Implementation for Efficient RAM utilization5          |

| 3.3.10 Implementation for Min Program Memory5                |

| 3.4 Implementation of the floating-point LMS filter5         |

| 3.5 The compilers floating point system5                     |

| 3.6 Floating-Point Word lengths5                             |

| 3.6.1 Algorithm developed for FP multiplication5             |

| 3.6.2 Calling FP Addition function in C-language6            |

| 3.6.3 Algorithm developed for floating-point addition6       |

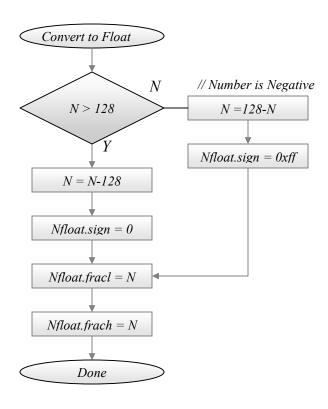

| 3.6.4 Converting integer to floating-point format6           |

| 3.7 Implementation of a 4 <sup>th</sup> order LMS algorithm6 |

| 3.7.1 Sampling noise and reference for LMS filter6           |

| 3.7.2 Program Outline for 4 <sup>th</sup> order LMS filter6  |

| 3.8 Hardware Test Circuit7                                   |

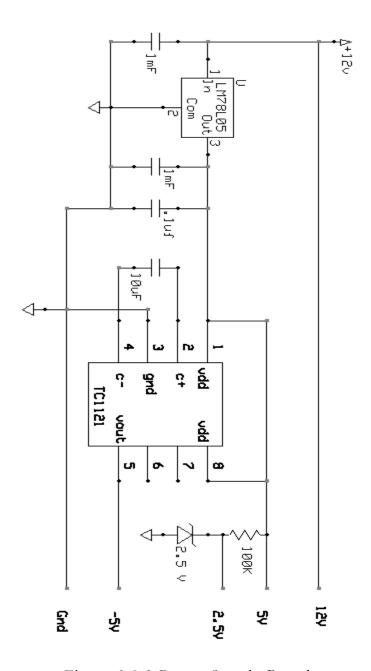

| 3.9 Detailed Schematic of the Power Supply7                  |

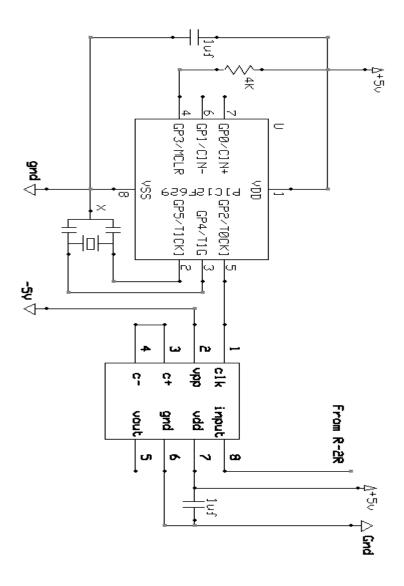

3.10 Detailed Schematic: Smoothing Filter......75

3.11 Detailed Schematic: Signal Conditioning Board......76

3.12 Detailed Schematic: Signal Processing Board ......77

3.13 Photograph of PIC18F452 based Filter......78

| CHAPTER 4: RESULTS FROM REAL-TIME 79                   |

|--------------------------------------------------------|

| 4.1 FIR FILTER: Data Acquisition Setup79               |

| 4.2 FIR FILTER: Real-Time Testing Results80            |

| 4.3 LMS FILTER: Test Scenario 186                      |

| CHAPTER 5: AnaLySis & CONCLUSIONS                      |

| 5.1 FIR filter performance summery92                   |

| 5.2 LMS filter performance summary94                   |

| 5.3 Conclusions and future work95                      |

| APPENDIX99                                             |

| A USERS MANUAL FOR FIR FILTER DESIGN99                 |

| B MATLAB CODE FOR FIR FILTER DESIGN SOFTWARE109        |

| C CODE FOR 4 <sup>th</sup> ORDER FLOATING POINT LMS130 |

| D CODE FOR SWITCHED CAP CLOCK SOURCE143                |

| E C-CODE FOR LDC ON PORT C145                          |

| VITA148                                                |

# LIST OF FIGURES

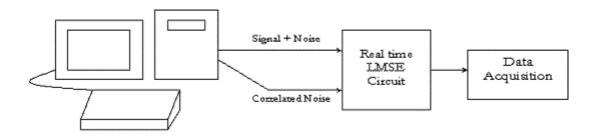

| Figure 1.5.1 Topology for Real-Time LMS Circuit Testing 4                  |

|----------------------------------------------------------------------------|

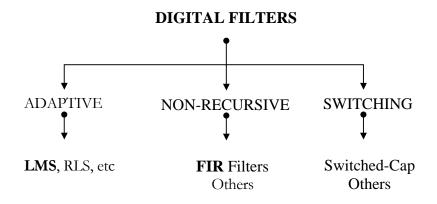

| Figure 2.1.1 Classification of Signal filtering methods                    |

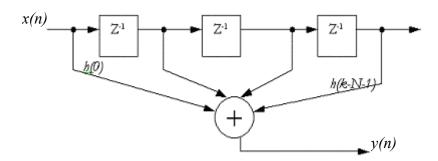

| Figure 2.3.1 The transversal topology of the FIR filter 8                  |

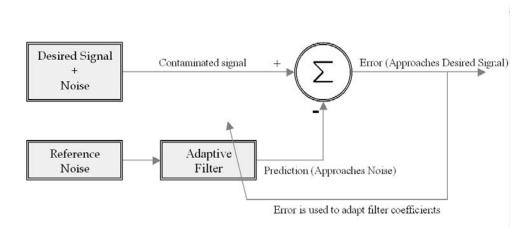

| Figure 2.6.1 LMS filter Topology                                           |

| Figure 2.7.1 Standard Implementation of LMS Filter                         |

| Figure 2.8.1 Standard Implementation of Digital Filter                     |

| Figure 2.8.2 Digital Signal Processing overview                            |

| Figure 3.1.1 FIR filter block Diagram                                      |

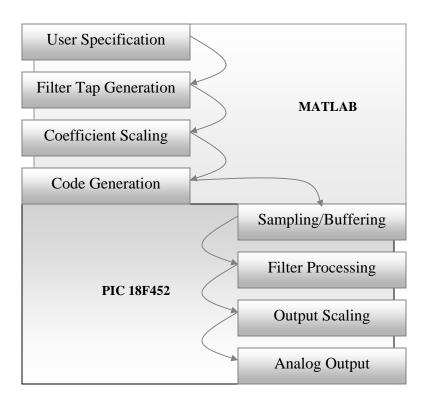

| Figure 3.3.2 FIR filter creation stages                                    |

| Figure 3.3.2 Digital Signal Processing overview                            |

| Figure 3.3.3 Frequency/phase review curves & code generation               |

| Figure 3.3.4 Section of C-Code generated                                   |

| Figure 3.3.5 Intended LPF parameters                                       |

| Figure 3.3.6 Skeleton code needed for Filter                               |

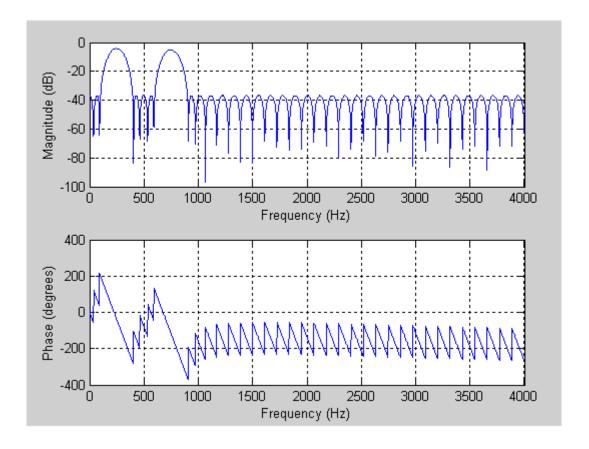

| Figure 3.3.7 Frequency and phase response plot                             |

| Figure 3.3.8 Frequency and phase response plot                             |

| Figure 3.3.9 Eight-Bit scaled coefficients                                 |

| Figure 3.3.10 Circular buffer: Used to store ADC values for FIR filter. 25 |

| Figure 3.3.11 Algorithm developed to load circular buffer                  |

| Figure 3.3.12 Step 1: Data element 0 is loaded and pointer decrements 26   |

| Figure 3.3.13 Step 2: Data element 1 is loaded and pointer decrements 27   |

| Figure 3.3.14 Step 3: Data element 3 is loaded and EOB is reached 27       |

| Figure 3.3.15 Step 4: Element 4 is loaded and ptr is pre-decremented 27    |

| Figure 3.3.16 Element 4 is unloaded from buffer and BOB is reached 28      |

| Figure 3.3.17 Pointer is relocated to EOB and 3 is pulled                  |

| Figure 3.3.18 Data element 1 is pulled                                     |

| Figure 3.3.19 Algorithm used to pull data from the circular buffer 29      |

| Figure | 3.3.20  | Topology of the Double Circular Buffers                                                                                  | 30 |

|--------|---------|--------------------------------------------------------------------------------------------------------------------------|----|

| Figure | 3.3.21  | Data Element 1 is loaded to both buffers                                                                                 | 30 |

| Figure | 3.3.22  | Data Elements 1-5 are loaded to buffer                                                                                   | 31 |

| Figure | 3.3.23  | Buffer Data Ready to be unloaded                                                                                         | 32 |

| Figure | 3.3.24  | Pointer FSR1 is relocated to same location as FSR0                                                                       | 32 |

| Figure | 3.3.25  | FSR1 pre-increments and unloads data element 5                                                                           | 33 |

| Figure | 3.3.26  | Algorithm for loading the adjacent circular buffers                                                                      | 34 |

| Figure | 3.3.27  | Assembly routine written to load the buffers                                                                             | 34 |

| Figure | 3.3.28  | Algorithm used to unload from adjacent circular buffers.                                                                 | 35 |

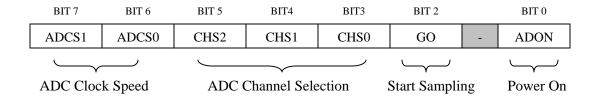

| Figure | 3.3.29  | Description of the ADCON0 Register                                                                                       | 37 |

| Figure | 3.3.30  | Description of the ADCON1 Register                                                                                       | 37 |

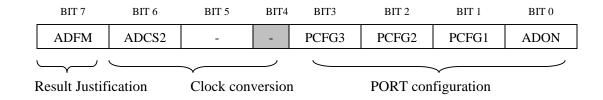

| Figure | 3.3.31  | Reading Only ADRESH will scale down to 8-bit                                                                             | 38 |

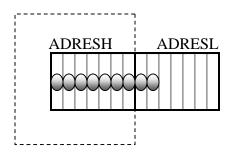

| Figure | 3.3.32  | RAM used by the FIR filtering scheme                                                                                     | 42 |

| Figure | 3.3.33  | Description of the T1CON Register                                                                                        | 43 |

| Figure | 3.3.34  | Word space dedicated to storing MAC result                                                                               | 45 |

| Figure | 3.3.36  | Multiply by 256 algorithm                                                                                                | 46 |

| Figure | 3.3.37  | Multiply by 128: Single Right shift of each byte                                                                         | 46 |

| Figure | 3.3.38  | Buffer setup for storing ADC samples                                                                                     | 47 |

| Figure | 3.3.39  | Buffer setup for storing Coefficients                                                                                    | 47 |

| Figure | 3.3.40  | 24-Bit Result store for MAC operation                                                                                    | 47 |

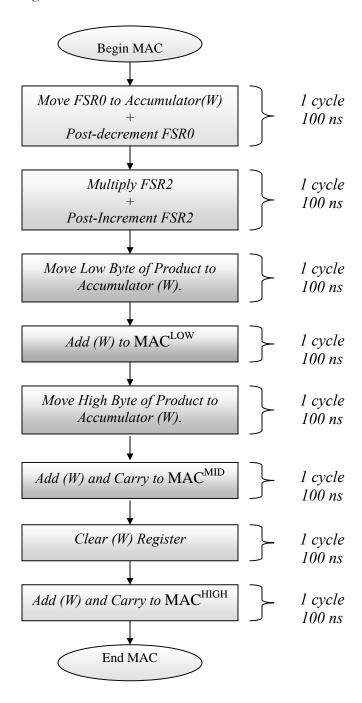

| Figure | 3.3.41  | Multiply-Accumulate Algorithm                                                                                            | 48 |

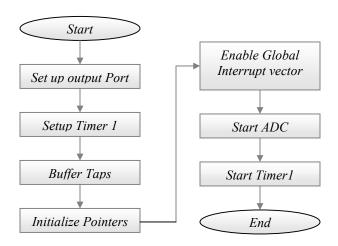

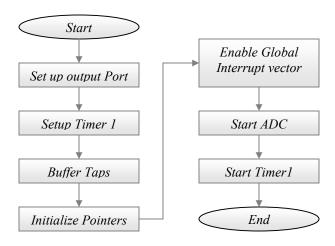

| Figure | 3.3.42  | Initialization Routine for Fastest Execution                                                                             | 49 |

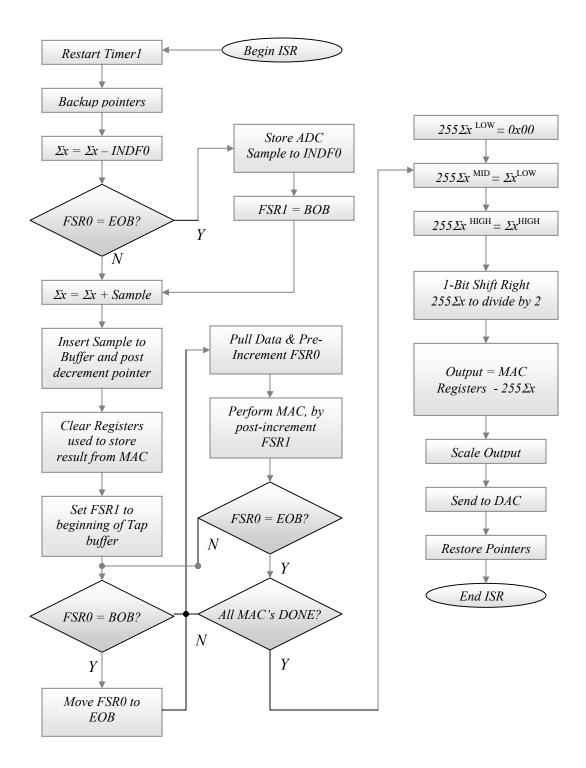

| Figure | 4.3.43  | Fastest Execution Implementation for PIC 18f452                                                                          | 50 |

| Figure | 4.3.44  | RAM efficient Implementation for PIC 18f452                                                                              | 51 |

| Figure | 4.3.45  | RAM Efficient Implementation for PIC 18f452                                                                              | 52 |

| Figure | 4.3.46  | Minimum Program Size Implementation                                                                                      | 53 |

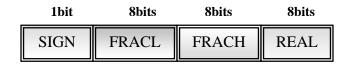

| Figure | 3.6.1   | Assigned Word Length for Floating Point Format                                                                           | 55 |

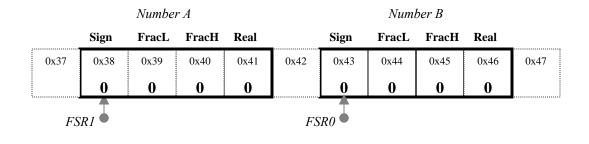

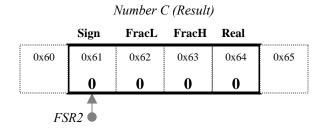

| Figure | 3.6.2   | Memory footprint of floating point numbers                                                                               | 57 |

| Figure | 3.6.3 I | Developed Algorithm for Multiplication                                                                                   | 58 |

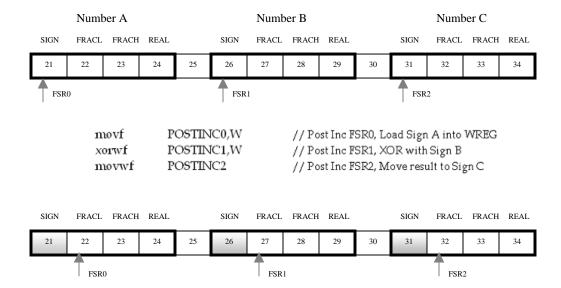

| Figure | 3.6.4 1 | Multiplication Step 1: $\mathbf{C}^{\text{sign}} = \mathbf{A}^{\text{sign}} \times \text{XOR } \mathbf{B}^{\text{sign}}$ | 59 |

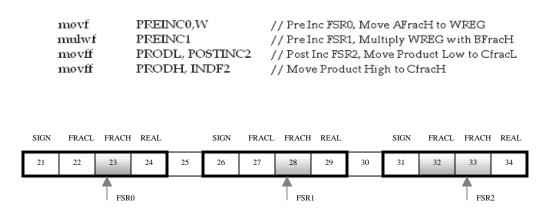

| Figure | 3.6.5   | Multiplication Step 2: $\mathbf{C} < \text{FracL}$ : FracH> = $A^{\text{fracH}} * B^{\text{fracH}}$ .                    | 59 |

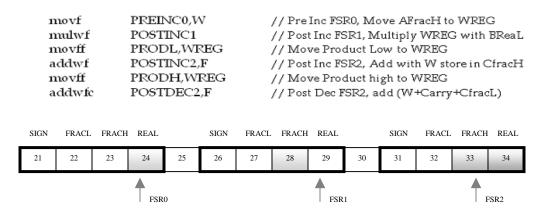

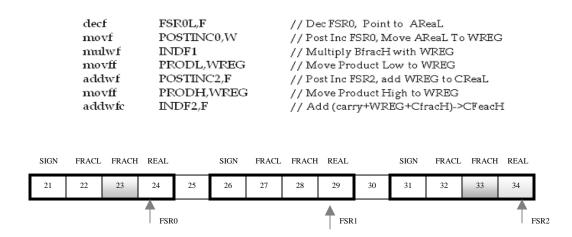

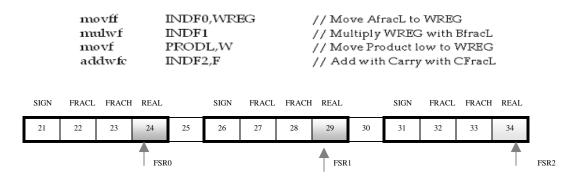

| Figure | 3.6.6 Multiplication Step 3: A <sup>Real</sup> * B <sup>FracH</sup> | 60 |

|--------|---------------------------------------------------------------------|----|

| Figure | 3.6.7 Multiplication Step 4: A <sup>FracH</sup> * B <sup>Real</sup> | 60 |

| Figure | 3.6.8 Multiplication Step 5: A <sup>Real</sup> * B <sup>Real</sup>  | 61 |

| Figure | 3.6.9 C-Code for floating point multiplication                      | 61 |

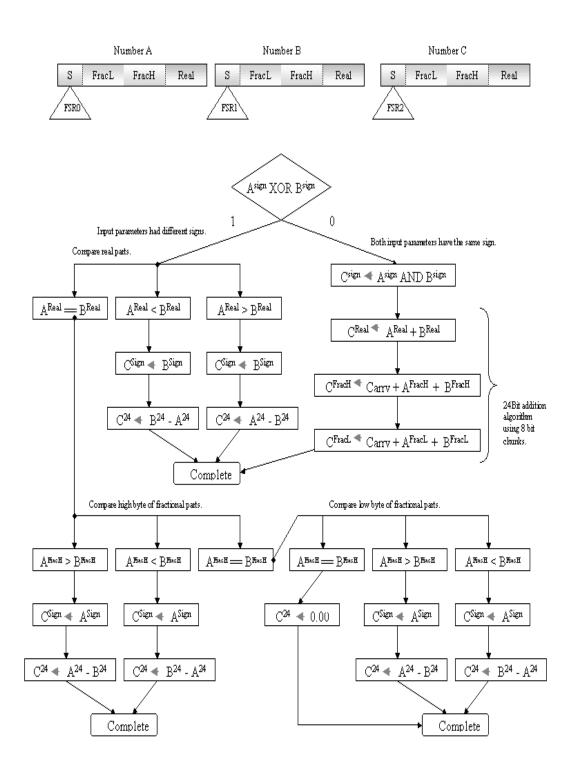

| Figure | 3.6.10 C-Code for floating point addition                           | 62 |

| Figure | 3.6.11 Developed Algorithm for Addition                             | 63 |

| Figure | 3.6.12 Developed Algorithm for Multiplication                       | 64 |

| Figure | 3.7.1 Fourth Order LMS Filter                                       | 65 |

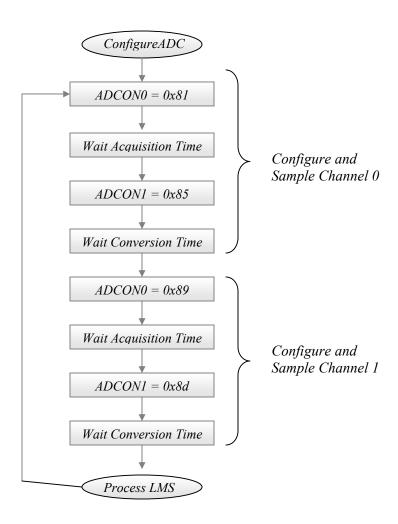

| Figure | 3.7.2 Sampling for LMS                                              | 66 |

| Figure | 3.7.3 Configuring ADC for Sampling Two Channels                     | 67 |

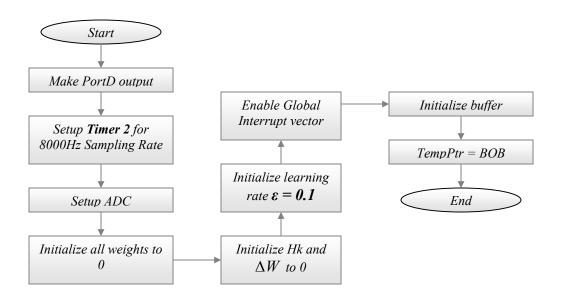

| Figure | 3.7.4 Initialization Routine for LMS                                | 68 |

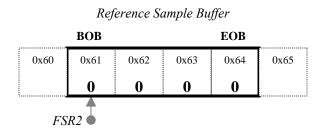

| Figure | 3.7.5 Four element ADC sample byffer for LMS                        | 69 |

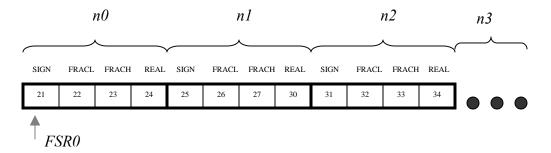

| Figure | 3.7.6 Arangements of Structs in Memory                              | 70 |

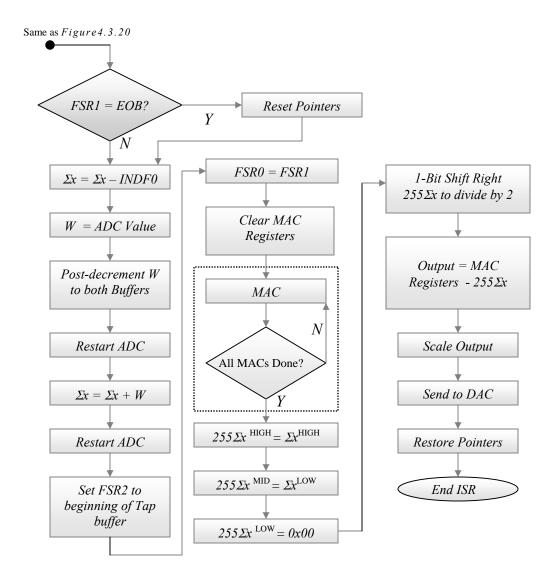

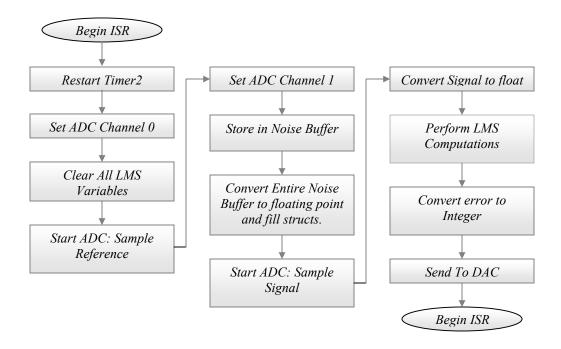

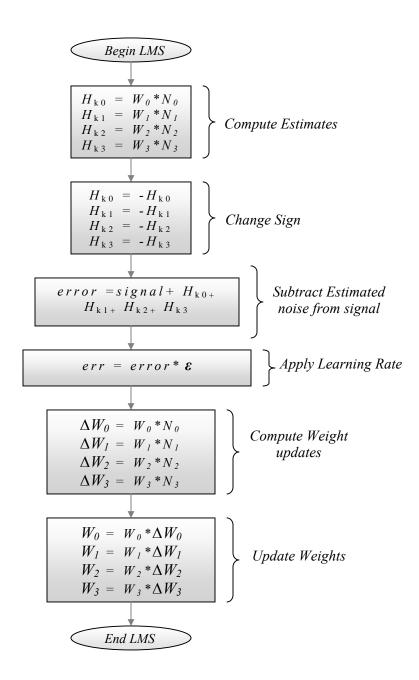

| Figure | 3.7.8 Level 2 Flow Diagram for LMS                                  | 71 |

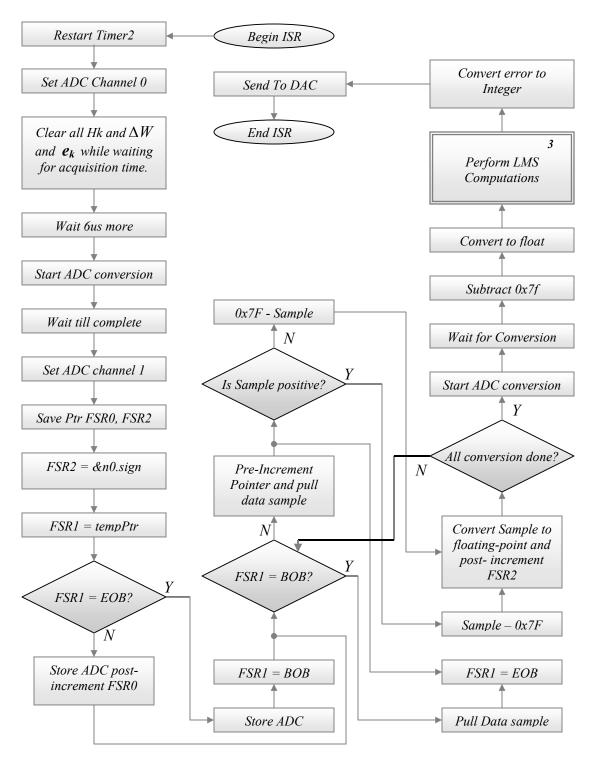

| Figure | 3.7.9 Level 3 Flow Diagram for LMS                                  | 72 |

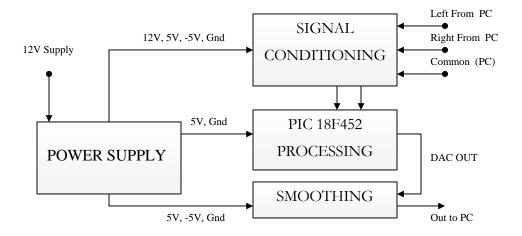

| Figure | 3.8.1 Block Overview of Circuit                                     | 73 |

| Figure | 3.8.2 Power Supply Board                                            | 74 |

| Figure | 3.8.3 Smoothing Filter for R-2R Ladder                              | 75 |

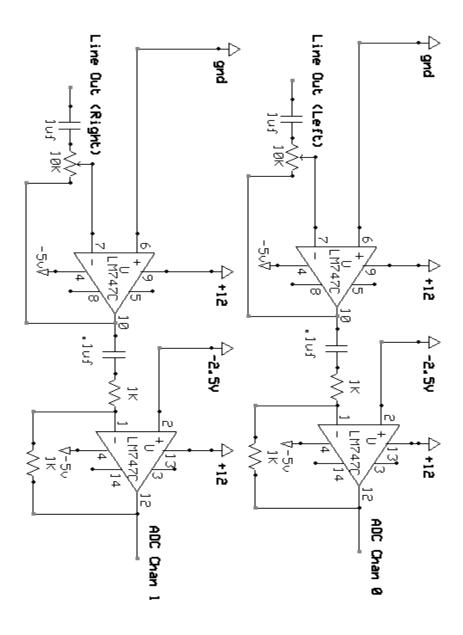

| Figure | 3.8.4 Signal Conditioning Block                                     | 76 |

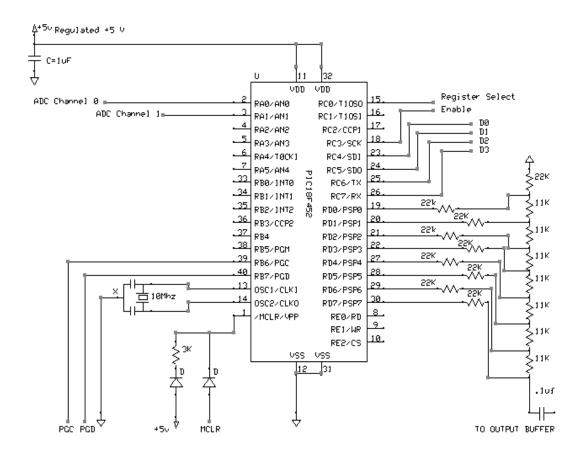

| Figure | 3.8.4 Block Overview of Circuit                                     | 77 |

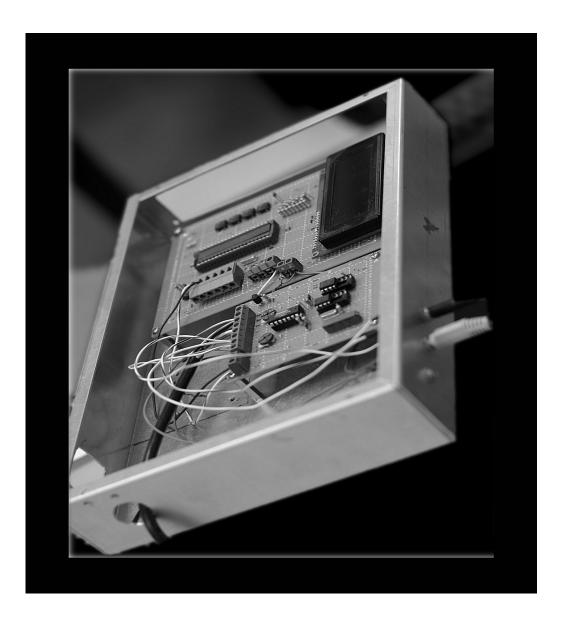

| Figure | 3.8.5 Photograph of Test Board                                      | 78 |

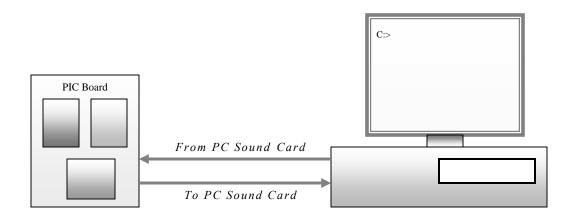

| Figure | 4.4.1 Basic setup for low-cost data acquisition                     | 79 |

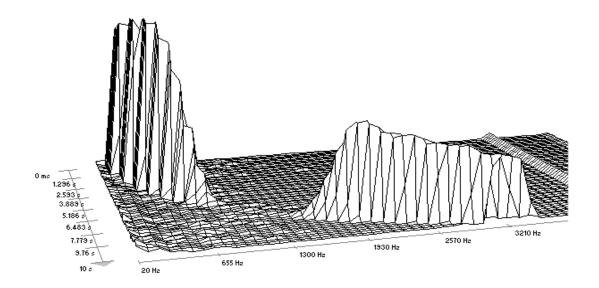

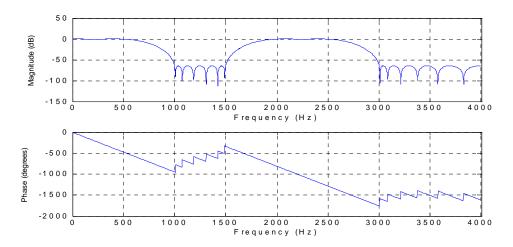

| Figure | 4.2.1 Response Curves of Intended Filter                            | 80 |

| Figure | 4.2.2 Test Signal: Constant Power Sweep [200Hz-4000Hz]              | 81 |

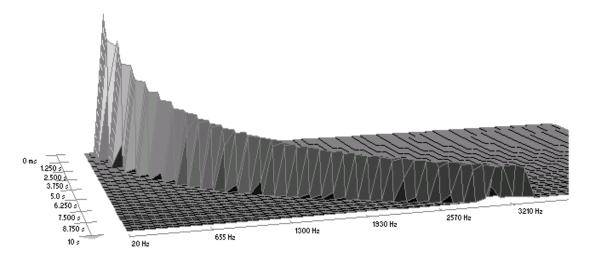

| Figure | 4.2.3 Filter Performance on PIC18F452 Chip                          | 81 |

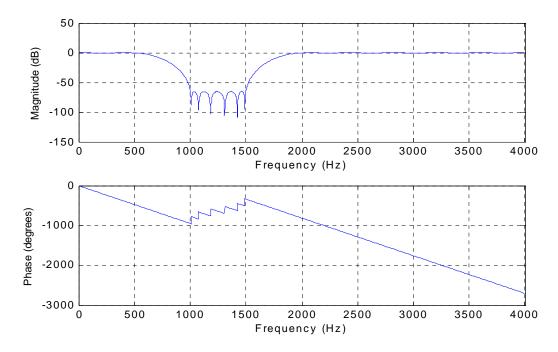

| Figure | 4.2.5 Measured BSF Frequency and Amplitude Response                 | 83 |

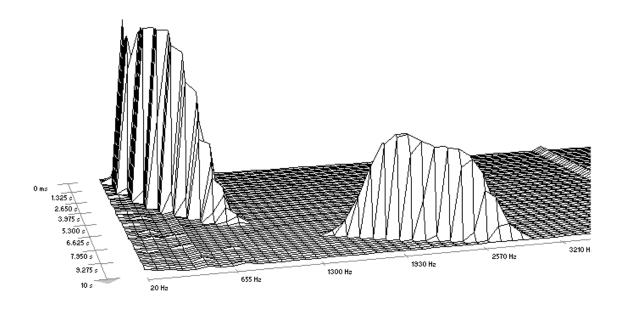

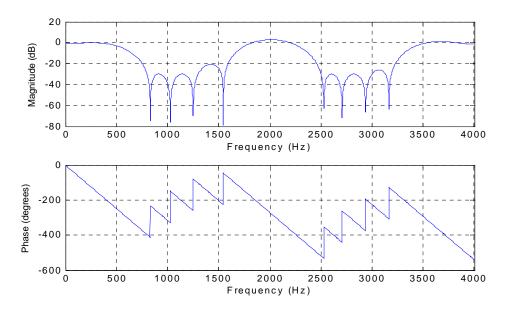

| Figure | 4.2.6 MBF 1 Filter Specifications for Band Pass filter              | 84 |

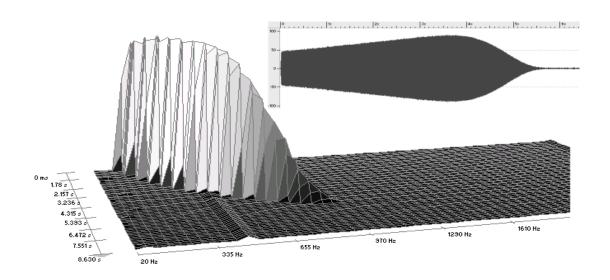

| Figure | 4.2.7 Frequency and Amplitude response from PIC18F452               | 84 |

| Figure | 4.2.8 MBF 2 Filter Specifications for Band Pass filter              | 85 |

| Figure | 4.2.9 Frequency and Amplitude response from PIC18F452               | 85 |

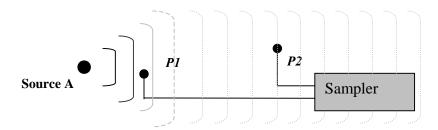

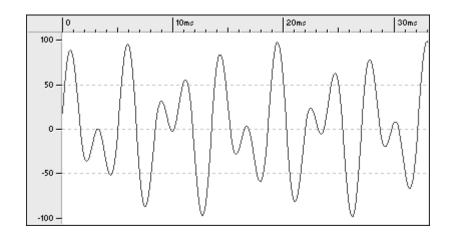

| Figure 4.3.1 | Sampling Source A at P1 and P2                          | 86 |

|--------------|---------------------------------------------------------|----|

| Figure 4.3.2 | Source B is added to the scene                          | 86 |

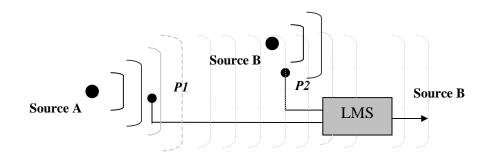

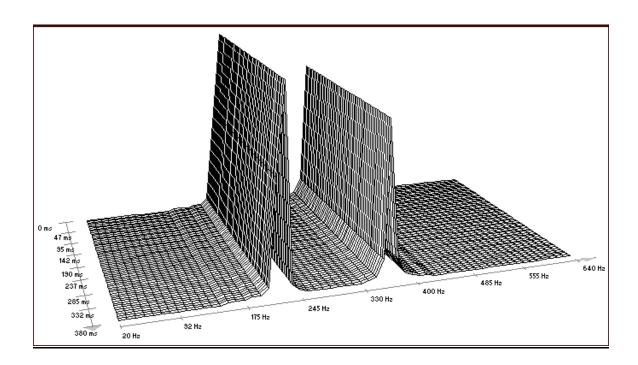

| Figure 4.3.3 | Approximation of Signal at p2                           | 87 |

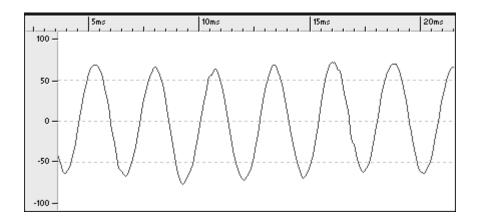

| Figure 4.3.4 | Time domain graph of signal at p2                       | 88 |

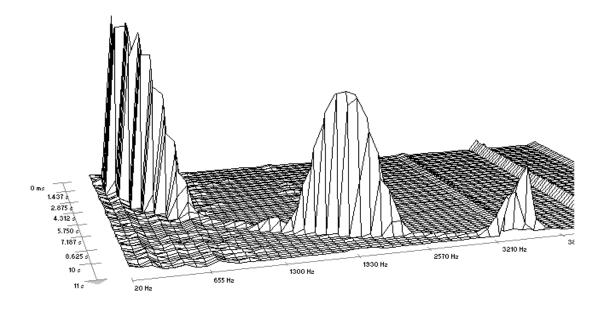

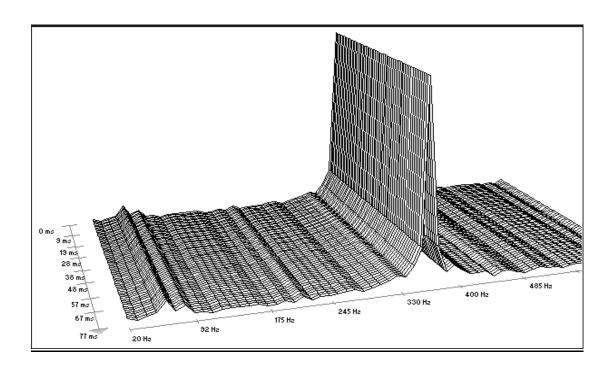

| Figure 4.3.5 | Frequency domain graph of signal at p2                  | 88 |

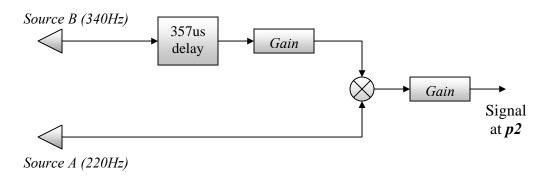

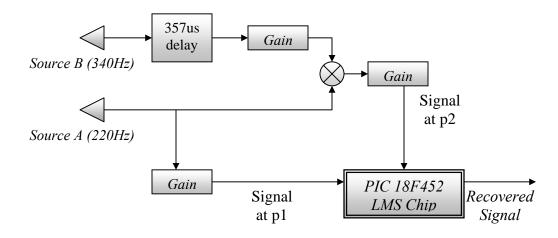

| Figure 4.3.6 | Real-time test topology                                 | 89 |

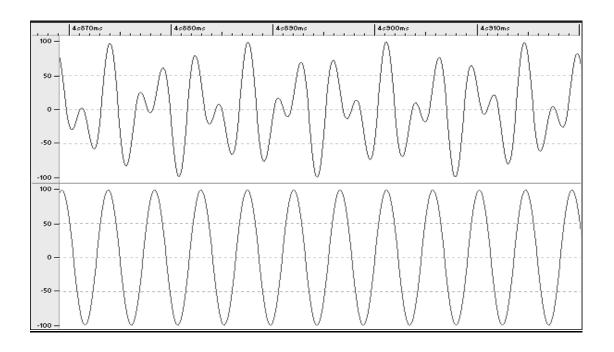

| Figure 4.3.6 | Signal p2 (top) and Reference p1 sampled by ADC         | 89 |

| Figure 4.3.7 | Signal Recovered by the PIC chop (source B: 340 Hz)     | 90 |

| Figure 4.3.8 | Signal Recovered in frequency domain (source B: 340 Hz) | 91 |

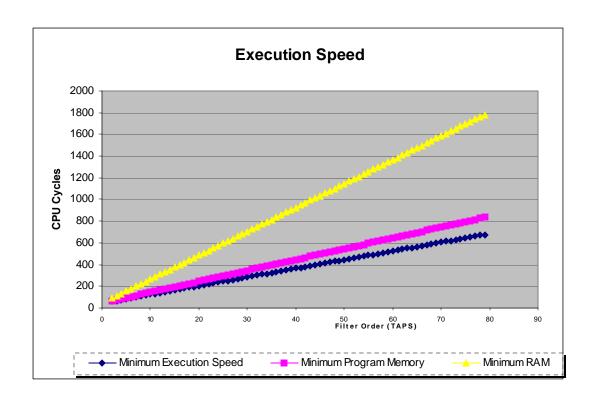

| Figure 5.1 C | omparison of exec speed for different implementations   | 94 |

# LIST OF TABLES

| Table 3.2.1 | Multiplication Speeds published by Manufacturer | 16  |

|-------------|-------------------------------------------------|-----|

| Table 3.6.1 | Floating point algorithms developed for LMS     | 56  |

| Table 5.1 I | LMS Sampling Rate vs Filter Taps                | .95 |

# LIST OF NOMENCLATURE

| 1. MCU Microcontroller Unit.                                    |

|-----------------------------------------------------------------|

| 2. DSP Digital Signal Processor.                                |

| 3. ADC Analog to Digital Converter.                             |

| 4. DAC Digital to Analog Converter.                             |

| 5. PWMPulse Width Modulation.                                   |

| 6. LMS Least Mean Squared.                                      |

| 7. FIR Finite Impulse Response.                                 |

| 8. IIR Infinite Impulse Response.                               |

| 9. ALU Arithmetic Logic Unit.                                   |

| 10. MIPS Millions of Instructions per Second.                   |

| 11. MACMultiply and Accumulate.                                 |

| 12. SMDSurface Mount Technology.                                |

| 13. RAM Random Access Memory/Read Write Memory.                 |

| 14. EEPROM.Electrically Erasable Programmable Read Only Memory. |

| 15. FFTFast Fourier Transform.                                  |

| 16. GUI                                                         |

| 17. ISRInterrupt Service Routine.                               |

| 18. EOBEnd of Buffer.                                           |

| 19. BOBBeginning of Buffer.                                     |

| 20. FSR                                                         |

#### CHAPTER 1: INTRODUCTION

#### 1.1 Personal Motivation

My fascination with single chip microcontrollers began with my undergraduate days and has remained consistent ever since. In a world where minimalism is the catchword, they fit the role perfectly, being a cost effective way to elegantly solve complicated problems, thereby making so many aspects of electronics and software accessible to engineers and students as well. During my undergraduate and graduate years I participated in projects involving electronics and circuit design and always enjoyed finding new opportunities for microcontroller based solutions. With circuits getting more and more complex, filters must be installed to control noise and dealing with filters meant having to look for the right capacitors and the right resistors, op amps and repeating the same tedium all over again, especially if it was determined that a new set of filtering specifications were required. The alternative to a true digitalfilter is to use a switched capacitor filter but those are usually not as clean as analog filters and require a clock signal that adds switching noise; with an additional circuit component drawing power, occupying space and incurring an explicit monetary cost.

It is here that the Finite Impulse Response (FIR) filters step in, being an attractive alternative to using analog filters and switched capacitor digital filters. I learned about them in theory and conducted a couple of Matlab simulations before realizing that these are ideal for use with microcontroller projects. They impose no additional monetary cost upon the circuit; can be easily reconfigured by changing code, without any lag in performance with time. The challenge is to do a very efficient implementation for the PIC 18 architecture so it becomes possible for the filter to function as a supplementary application, thereby, providing

an intuitive graphical interface that will allow anyone to easily generate these filters using a simple point and click system. However, not all noise problems can be solved by using FIR filters.

Sometimes due to the nature of the noise, especially if it is correlated, it is impossible for an ordinary (fixed-band) filter to remove it, because both the signal and noise occupy the same frequency range. For instance, if the echo of the signal was the source of noise, then the echo could not be removed simply by suppressing its frequencies, because the echo and the source have a strong correlation. In cases like these, adaptive filters are used to reduce noise. The least mean squared (LMS) error is a commonly used adaptive noise cancellation algorithm that is ideal for this purpose because it is a good compromise between computational complexity and performance.

.

## 1.2 Signal Processing using the PIC 18F452 Microcontroller

Microcontrollers such as PIC chips which run at speeds up to 10 MIPS (million instructions per second) are useful for gaining valuable practical experience with low bandwidth signal processing ideas. What makes them so convenient is the wealth of built in hardware, which can sample signals, perform ADC conversions and contain multiple timers for accurate timing. Moreover, there are a number of low cost compilers making the package available under \$6.00 per chip [4] and as low as \$175 for a C-Compiler and an in-circuit programmer for \$75 [2], making it feasible cost-wise as well.

## 1.3 Digital Filters Vs Analog Filters

Digital filters have several advantages and disadvantages over their analog counterparts. The main advantage of digital filters is that they occupy no physical space as they are implemented completely in software and operate by applying a mathematical algorithm designed to produce the filtering effect. Since digital filters need no physical components i.e., capacitors and resistors, their performance does not degrade with age or respond to ambient environmental conditions. Another major advantage is that some digital filter (FIR filters) can have a unique property called linear phase response, which is critical in many communications applications. Analog filters presently, have a much greater dynamic range however, than digital filters because they are not limited by factors like sampling rate and computation speed [5].

### 1.4 PIC 18 Microcontroller Family

Microchip Technologies manufactures a popular line of micro controllers known as Peripheral Interface Controller or PIC chips. The PIC 18F452, released in May 2002, is currently one of their fastest chips [3]. At the core of this chip is an 8-bit RISC based ALU that can process 10 MIPS at 40 MHz. Its design is based on Harvard architecture, allowing it to have separate data and program memories. Its memory is divided into 32 KB of flash based program memory and 1.5 KB of volatile data memory (RAM) as well as 256 Bytes of EEPROM. PIC chips have a RISC based instruction set consisting of a small yet seminal set of instructions, most of which are single cycle, thereby making them fast executing and easy to program. Other valuable devices such as analog to digital converters, pulse width modulation, multiple timers, I/O Ports are all integrated within the same chip that also contain hardware support for several popular serial communication protocols

such as I<sup>2</sup>C, SPI and UART. Running at 40 MHz, it takes the 18F452 chip 100ns to multiply two bytes and compute a 16-bit result. The other noted feature that makes this chip viable for signal processing applications is that, it contains multiple hardware pointers that allow very fast access to data stored within the chips' RAM.

#### 1.5 Detailed Research Objectives and Contributions

The main focus of this research will be to test and validate the PIC chips' ability to implement a real-time floating-point LMS based Adaptive filter, which is a very useful way to deal with noise that is too closely related to the signal for conventional band compensating filters to handle.

1. A suitable general-purpose, adaptive noise cancellation circuit will be designed, that is both cost effective and customizable to serve several different applications. The circuit will be tested using test signals generated by a PC sound card as shown in Figure 1.5.1. This will allow the modeling of different types of noise and to test various signal to noise ratios. The circuit will process the signals in real-time and the results will be measured using a data acquisition system. Analysis of the recorded data should reveal the effective noise reduction versus noise reductions predicted via simulations.

Figure 1.5.1 Topology for Real-Time LMS Circuit Testing

- 2. During the course of this research, software will be developed to benefit the users of the popular CCS PIC Compiler. The software will include a modular library for PIC 18XXX with optimized floating-point math support. Although the compiler is inherently capable of handling floating-point data, it performs common floating-point operations such as addition, subtraction, and multiplication at an alarmingly slow rate rendering it unpractical for real-time applications. Therefore, another aim of this research will be to develop a modular library that will provide a faster alternative to the compilers built in floating-point system.

- 3. The secondary focus of this research will be to test and validate the PIC chips' ability to implement a real-time fixed-point FIR filter, which is a very practical idea, because it can be seamlessly used in countless applications where noise and the signal of interest occupy separate frequency bands.

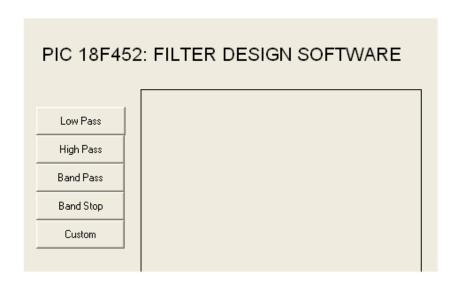

- 4. A Graphical User Interface (GUI) will be developed that allow users to design various types of FIR filters, such as Low-Pass, High-Pass, Band Pass, Notch or any combination of the above, in short, multi-band filters. The user may design the filter by taking a point and click approach to specifying band-edges, attenuations, sampling rate etc. and the software will show users the respective frequency and phase response graphs. Once the user is satisfied with the filter they have designed, the software will present them with several realization options, thereby allowing them to decide whether they want the filter optimized for execution speed, or conservative RAM usage or conservative programmemory usage. Ultimately, optimized C language source code is generated that is ready to be compiled for either PIC 18F452 chip or the smaller PIC 18F252 chip or easily adapted for the remaining chips in the PIC 18FXXX family by a moderately experienced programmer. Finally, the GUI will generate a diagram of the test circuit needed to install the filter code.

5. Each type of FIR filter created by the software will be evaluated independently by applying a constant-power frequency sweep generated by a filter test program. The real-time output of the filter will be recorded by a data acquisition system and its performance will be analyzed though PC based data analysis tools such as FFT.

# 1.6 Organization

Chapter two will cover a literature review and theoretical background of existing techniques for digital filter implementation for both LMS and FIR filters. Chapter three will constitute the implementation details for both the filters. Chapter four will present results and analysis and chapter five will contain recommendation for future work. An appendix is provided that contains all codes written during this exploration and a user's manual for the filter design of the GUI.

#### CHAPTER 2: LITERATURE SURVEY

## 2.1 Classification of Filtering Methods

The earliest filters were analog filters. In recent years, digital filters have gained popularity due to the lowering cost of microprocessors and the increased level of convenience and flexibility offered by digital filters. Advances in technology allowed them to function at a faster speed and now they are rapidly approaching the large dynamic range of analog filters [5]. A broad classification of Digital filters is presented in Figure 2.1.1.

Figure 2.1.1 Classification of Signal filtering methods

## 2.2 Digital Filters

A digital filter is a discrete-time linear system that operates on an input sequence, modifies it, and produces the output sequence. The input sequence is usually obtained by digitizing a signal, thereby converting it into discrete time, with the output sequence being transformed back into an analog signal through an appropriate digital to analog process. The steadily reducing cost of portable computation is

thereby making a direct contribution to the rise of popularity of digital filters.

## 2.3 Non-Recursive Type Digital Filters

The most commonly used Non-Recursive filter is the FIR filter. The weights of this type of digital filters are constant and are computed at design time. Since the weights remain constant, the stability of FIR filters can be guaranteed. However, they can have several topologies — the transversal topology as shown in Figure 2.3.1 being the most common type and the one used for this research [9].

Figure 2.3.1 The transversal topology of the FIR filter

The transversal FIR filter is characterized by the following equation.

$$y(n) = \sum_{k=0}^{N-1} h(k) * x(n-k)$$

(2.1)

Where,

x(n): discrete time elements of the sampled signal

y(n): is the computed output of the FIR filter

h(k): are the coefficients of the filter also knows as filter-taps

Linear convolution of the filter coefficient with the sampled signal produces the filtering effect. Since multiplication and addition are the only mathematical operations involved with the FIR filter, this process is ideally suited for use within the PIC 18F452 microcontroller. The clear advantage of using FIR filters is the radical alteration in its frequency compensation, which can be achieved by simply providing the system with a new set of filter coefficients. Another interesting property of FIR filters is that, they are the only type of filter that can have a true linear phase response. Since this research deals exclusively with the implementation aspects of FIR filters, it is assumed that the coefficients of the filter have already been computed. For more theoretical details regarding obtaining filter coefficients refer to [7].

### 2.4 Switching type digital filters

The switched capacitor filter is a common type of switching filter. Switching type digital filters are a convenient alternative to using high order analog filters. They are packaged for convenient use and typically require a clock signal and power to operate. Most are strictly low-pass filters; others can be programmed by additional resistors, to be used as band pass and notch filters. However, this convenience comes at the expense of additional monetary cost and components and having to deal with the inescapable incurrence of switching noise [1].

# 2.5 Adaptive Filters

One of the most successful adaptive algorithms is the LMS filter developed by Widrow [14]. LMS, sometimes known as LMSE is excellent for dealing with correlated noise where noise and the signal are too much alike to be filtered using ordinary band-compensating filters such as low-pass, band-pass etc. Such filters are commonly referred to as adaptive

filters and they are used in applications such as, echo-cancellation over communication lines, noise-cancellation, Electro-cardiogram (ECG) in pregnant mothers, suppressing machine noises in mines and countless other applications.

## 2.6 Least Mean Squared Error (LMS)

The LMS filter is based on the steepest decent algorithm where the weight vector is updated from sample to sample as follows:

$$W_{k+1} = W_k - \mu \nabla_k \tag{2.2}$$

where,

Wk: Is the weight vector

$\nabla_k$ : Is the true gradient vector

$\mu$ : Rate of convergence also referred to as learning rate

The LMS algorithm is a practical method of obtaining estimates of the filter weights Wk in real time. The Widrow-Hopf LMS algorithm for updating weights from sample to sample is given by:

$$W_{k+1} = W_k + 2\mu e_k X_k \tag{2.3}$$

where,

$$ek = y_k - W_K^T X_k \tag{2.4}$$

ek: Is the error term

$X_k$ : Is the correlated noise vector

LMS algorithm above does not require prior knowledge of the signal statistics, but instead uses instantaneous estimates to tune the filter. The weights obtained by the LMS algorithm only estimates, but these

estimates improve gradually with time as the weights are adjusted and the filter adapts itself to the characteristics of the signals. Eventually, the weights converge. The condition for convergence is,

$$0 < \mu < \frac{1}{\lambda \max} \tag{2.5}$$

where,

$\lambda$ max: Is the maximum Eigen value of covariance matrix.

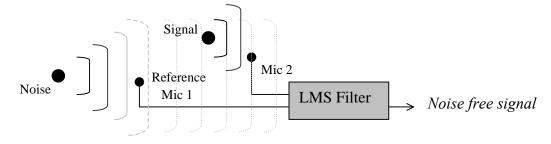

The main objective in adaptive noise cancellation is to produce an optimum estimate of the correlated noise in the contaminated signal. This is done by the simultaneous sampling of two signals — one being the signal of interest to be filtered and the other being the source of correlated noise, referred to as the reference. The adaptive filter in Figure 2.6.1 uses the reference to predict the degree of contamination in the signal of interest by the process of correlation.

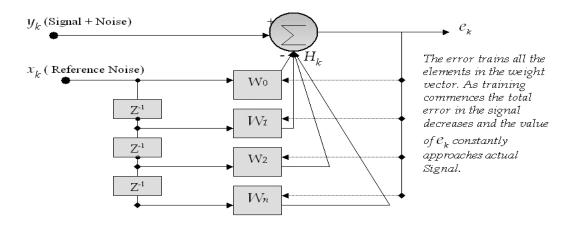

Figure 2.6.1 LMS filter Topology

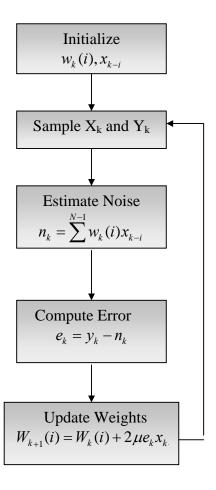

The adaptive filter attempts to predict the amplitude and phase of the noise present in the contaminated signal by correlating the reference with the contaminated signal. The prediction of the adaptive filter constantly approaches the actual noise present in the contaminated signal. With the error signal continuously being used to tune the filter, it gradually approaches the desired signal. Figure 2.7.1 shows a flow diagram for the LMS filter algorithm.

Figure 2.7.1 Standard Implementation of LMS Filter

## 2.8 Implementation of a digital filter

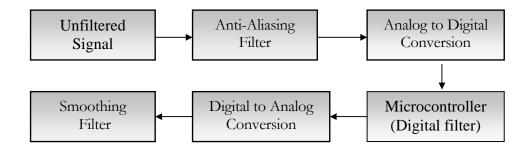

Digital filters are a natural choice for circuits that are interfaced to or controlled by a microcontroller. Part of the microcontroller's computing power may be dedicated to filtering the sampled input signals. Figure 2.8.1 is a block diagram for typical digital filter implementation.

Figure 2.8.1 Standard Implementation of Digital Filter

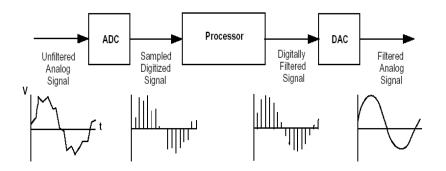

The Anti-Aliasing filter is a low-pass filter designed with a cutoff that is at least half the sampling rate of the analog to digital converter (ADC). This is used to prevent sampling of frequencies above Nyquist rate [6]. A smoothing filter is another low-pass filter that is used to reduce the harmonic distortion resulting from the quantization process. An illustration of the described process is presented in Figure 2.8.2.

Figure 2.8.2 Digital Signal Processing overview

#### CHAPTER 3: IMPLEMENTATION DETAILS

Implementation details for the fixed-point FIR filter are discussed first followed by the implementation details for the more complicated floating-point LMS filter.

### 3.1 Finite Impulse Response (FIR)

Development of a FIR filter generally involves two distinct phases. The first one is the design phase and the other is the realization phase. The design phase involves specifying filter characteristics such as bandedges, frequency-response and phase-response etc. and finally derives the filter coefficients for the intended filter. There are several ways to obtain filter coefficients. For this research the Matlab filter design toolbox was used to generate them. In FIR filters, the same hardware can be used to realize many different types of filters. It can be seamlessly reconfigured from a low-pass to band-pass to notch or a combination of all of them by simply supplying a new set of coefficients. The implementation discussed in this study is optimized for the PIC 18F452 instruction set although it is flexible enough to be easily adapted to other inexpensive microcontrollers with similar hardware.

The software developed for building FIR filters includes a program that allows users to visually specify the filter parameters. Once the filter has been finalized, optimized code will be automatically generated for the PIC 18F452 processor. Since the filter is usually used as a supplementary application, it must be designed to co-exist with a main application. The proposed implementation uses only a fraction of the microcontrollers' total computational capacity and the remaining cycles are reserved for the main application. Additionally, the implementation scheme is easy to reconfigure without making changes in hardware.

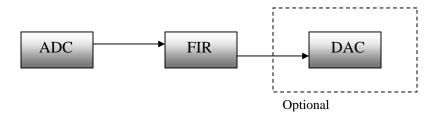

The second phase is the realization phase. This involves the selection of an appropriate platform upon which the filter will be implemented. In this case the platform desired is the PIC 18F452 chip. Real-time implementation involves three distinct processes — firstly the analog-to-digital conversion of a signal; followed by mathematical processing by the filtering algorithm; and finally, if needed the obtained results have to be transformed back into an electrical signal using a suitable digital-to-analog conversion technique. All three processes mentioned above must be performed within a proper time constraint or the result becomes invalid. For instance, if we are sampling a signal at 4000Hz then our worst-case time is 1/4000Hz or 250us. All filter computations must be completed within the time window of 250us. The block diagram of the FIR filter is presented in Figure 3.1.1.

Figure 3.1.1 FIR filter block Diagram

## 3.2 Implementation Background

Three different implementation strategies are provided to the user as options, each with its advantages and drawbacks. They are minimum RAM implementation, minimum program memory implementation and minimum execution time implementation. Each will be discussed in detail in the following sections.

Implementation aims to take advantage of the PIC chip's hardware architecture and instruction sets. The PIC 18F452 chip has certain features in its hardware that makes it a good choice for filtering

applications. The following restrictions were used while implementing the FIR filter algorithm in order to maximize the filter throughout.

1. Multiplication operations are restricted to unsigned integer data only. The Table 3.2.1 is a summary of manufacturer published multiplication-performance for the PIC 18F452 chip [10]. Table 3.2.1 outlines the speed gain from using the hardware multiplier and by favoring unsigned-multiplication operations instead of signed multiplication operations. Time<sub>H</sub> is the time needed performing hardware multiplication and Time<sub>S</sub> is the time needed to perform software multiplication.

Table 3.2.1 Multiplication speeds for PIC18452

| ROUTINE        | METHOD            | Time <sub>H</sub> /Time <sub>S</sub> | Speedup |

|----------------|-------------------|--------------------------------------|---------|

| 8x8 Unsigned   | Hardware/Software | 100ns/6.9µs                          | 6900%   |

| 8x8 Signed     | Hardware/Software | 600ns/9.1µs                          | 1500%   |

| 16x16 Unsigned | Hardware/Software | 2.4µs/24µs                           | 1000%   |

| 16x16 Signed   | Hardware/Software | 3.6µs/25.4µs                         | 1400%   |

- 2. The analog to digital converter is used with 8-bit resolution. Even though the built in ADC on the PIC chip is capable of sampling up to 10-bit resolution, the PIC memory and ALU are both 8-bit wide. It is therefore most efficient in handling 8-bit data. Hence, all filter coefficients and ADC data will be restricted to 8-bit resolution.

- 3. All memory references are made using indirect addressing. The PIC 18F452 chip contains three hardware pointers. FSR0, FSR1, FSR2, each being 12 Bits and capable of covering the entire RAM size for the PIC 18 family (up to 4096 bytes for PIC18f2515). By shortening the range of these pointers to 8-bits we can gain efficiency at the expense of smaller memory coverage. The pointer space will be restricted to 8-bits to cover

256 bytes of RAM or a single bank of RAM. This means that all our buffers and other dynamically allocated areas of RAM have to be confined to 256 bytes of memory.

# 3.3 FIR Filter Implementation

FIR filter implementation scheme on the PIC 18F452 chip can be categorized using the following major steps shown in Figure 3.3.1.

Figure 3.3.2 FIR filter creation stages

## 3.3.1 User specification

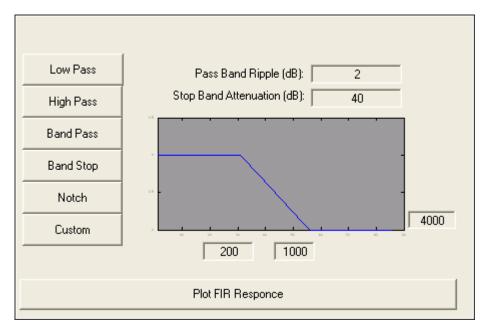

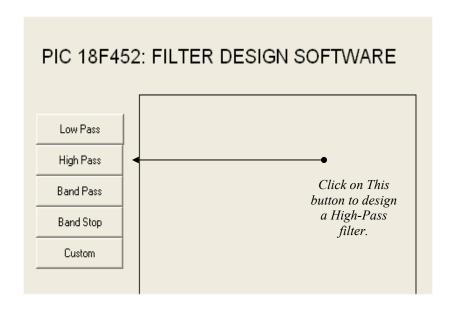

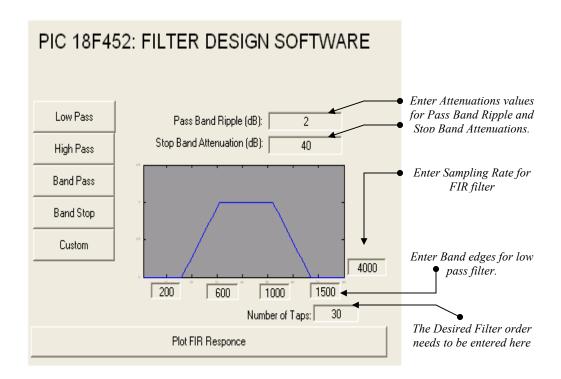

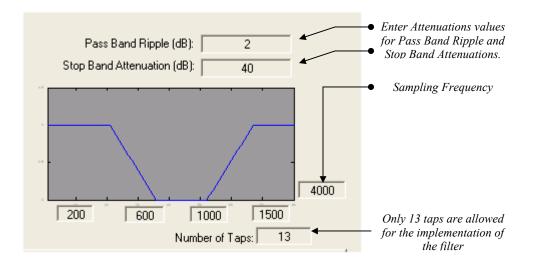

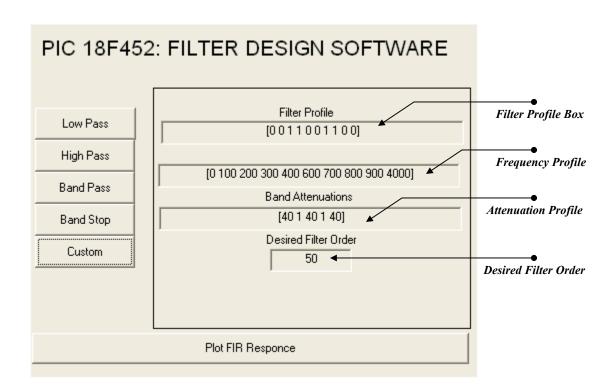

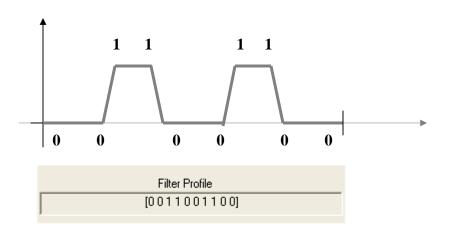

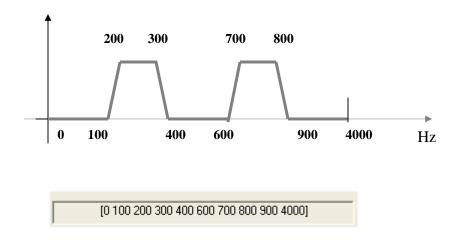

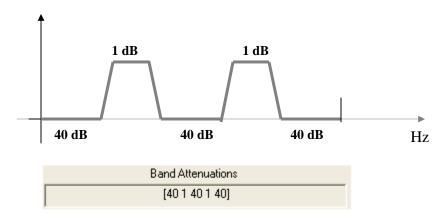

The very first logical step to making a filter is to specify filter parameters such as band edges, attenuations and ripples. To this end, the following interface was developed to allow a user to specify the type and exact parameters of the filter to be designed. Figure 3.3.2 is a snapshot of the developed filter making software.

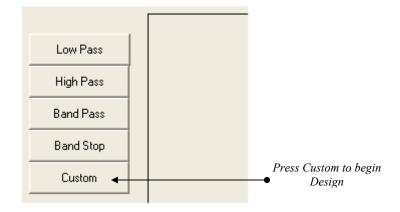

Figure 3.3.2 Digital Signal Processing overview

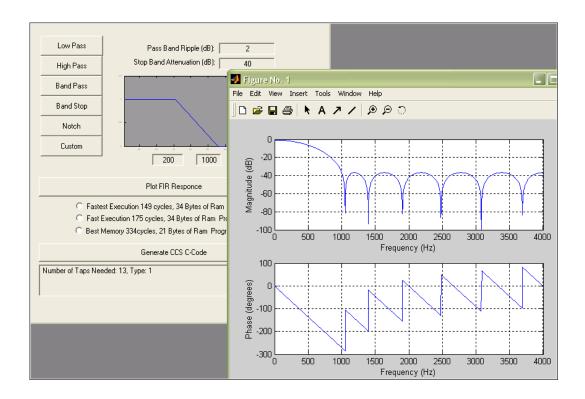

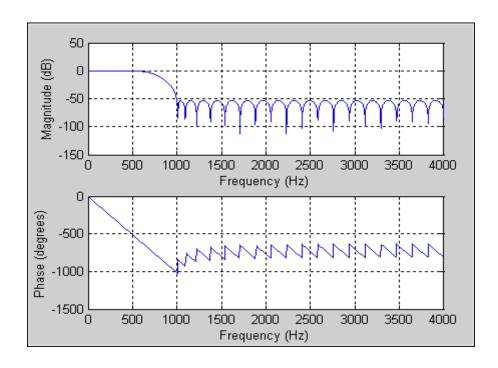

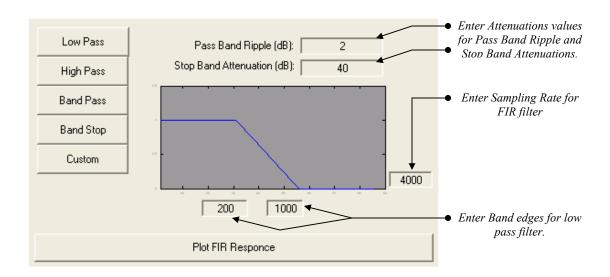

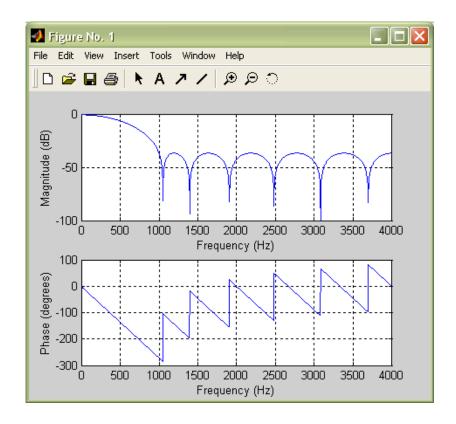

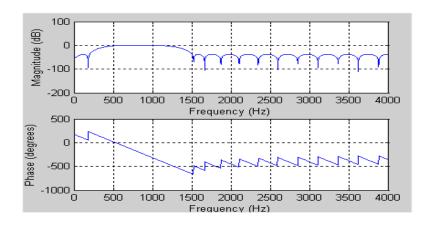

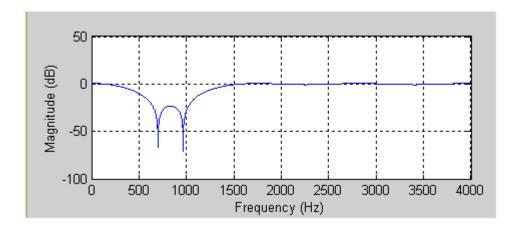

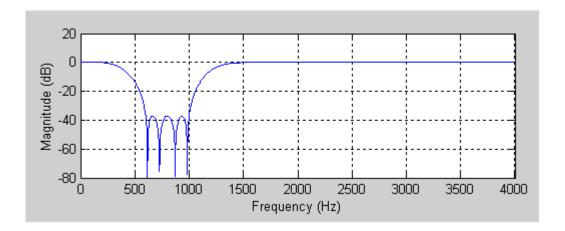

By making use of the menus the user can select from the range of filters that can be generated for real-time implementation. The available options are low-pass, high-pass, band-pass, band-stop, notch and custom. Once the type of filter is decided, the user can specify parameters such as band edges and attenuations by filling in the appropriate boxes. Before the user is allowed to generate code, the frequency and phase response for the desired filter circuit must be reviewed. The software automatically calculates the exact filter order required to achieve filtering requirements. The filter coefficients are calculated using the Remez exchange [8] method for optimal tap generation for low-pass and high-pass configurations. Figure 3.3.3 shows the frequency and phase response curves as well as the different code generation options available to the user. If satisfied the user may generate the desired filter.

Figure 3.3.3 Frequency/phase review curves & code generation options

Once a satisfactory design is achieved the user is given three options for code generation. Finally C-language code, as shown in Figure 3.3.4, is generated that is ready to be compiled or edited.

```

#include <18f452.h>

#use delay(clock = 40000000)

#fuses H4,PUT,NOWDT

const int filter_length = 13;

const int taps[filter_length] = {20,35,58,83,106,121,127,121,106,83,58,35,20};

// PIC 18F452 Register MAP.....

// ACCUMULATOR ADDRESS

#byte

WREG = OxFE8

// Register Stores the Carry Bit

#byte

PRODL =0xff3

// Product Low Byte

PRODH =0xff4

#byte

// Product High Byte

#byte

ADRESL = Oxfc3

// Low Byte for ADC Sample

#byte

ADRESH = Oxfc4

// High Byte for ADC Sample

#byte

STATUS = 0xfd8

// Status Register

```

Figure 3.3.4 Section of C-Code generated

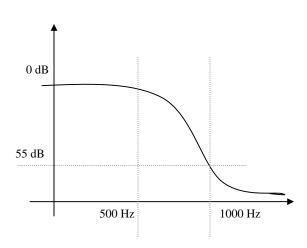

## 3.3.2 Filter Tap Generation

The Matlab filter design toolbox [13] was used to generate filter coefficients. This toolbox contains a set of functions that allow users to conveniently make and test different types of filters. If for example, a low-pass filter was desired with the characteristics given in Figure 3.3.5 and Figure 3.3.6 is the skeleton Matlab-code needed to generate it.

Sampling Frequency of 8000Hz

Pass band frequency of 500Hz

Stop Band frequency of 1000Hz

Pass band ripple of .05 dB

Stop band ripple of 55 dB

Figure 3.3.5 Intended LPF parameters

```

function lpf_test()

23456789

*FIR low pass filter Specifications

Pass = 500:

t Pass band frequency: 400 Hz

Stop - 1000;

% Stop band frequency: 1000 Hz

Fs = 8000;

% Sampling frequency: 8000 Hz

% Pass band ripple: 0.05 dB

Rp = .05:

Rs = 55;

% Stop band gain: -55 dB

10

11

f = [0 Pass Stop Fs/2]/Fs*2;

% Parameter Specification Vector

12

n = [1 1 0 0];

% Profile Vector (filter shape)

13

devs = [(10^(Rp/20)-1)/(10^(Rp/20)+1) 10^(-Rs/20)];

14

w = [1 1]*max(devs)./devs;

15

₹ Coefficient Estimation

16

n = remezord([Pass Stop],[1 0],devs,Fs); order = max(3,n);

17

b = remez(order+1,f,n,w); disp(['Taps needed: ',nun2str(n)]);

18

a = 1;

19

20

% Plot Frequency and Phase graphs

21

[H,V,S] = freqz(b,a,max(2048,nextpow2(5*max(length(b),length(a)))),Fs);

22

freqzplot(H, W, S);

```

Figure 3.3.6 Skeleton code needed for Filter

The skeleton code presented in Figure 3.3.6 upon execution will produce the graphs for both phase response and frequency response in Figure 3.3.7.

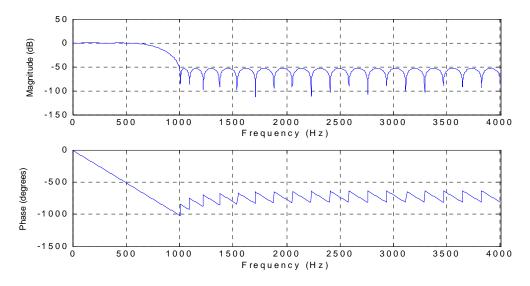

Figure 3.3.7 Frequency and phase response plot

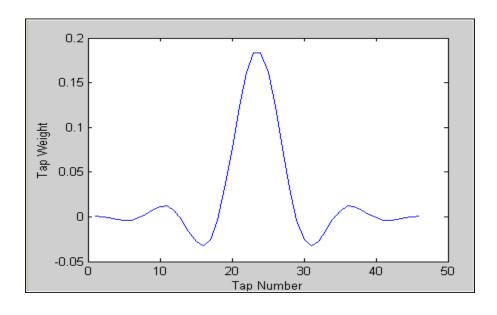

The filter tap coefficients generated by Matlab are as plotted next:

Figure 3.3.8 Frequency and phase response plot

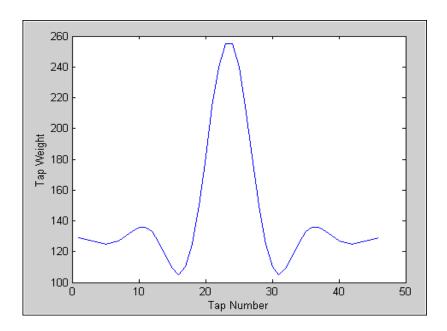

## 3.3.3 Coefficient Scaling

The tap coefficients computed by Matlab are computed in floating point format ranging from [-1.0,1.0]. Before they can be used in the PIC chip they need to be converted into 8-bit fixed-point format and made unsigned. The following scaling function apply the to achieve this:

$$scaled \_tap_n = ceiling \left\{ \frac{floating \_tap_n}{\max(floating \_tap)} * 127 \right\} + 128$$

(3.1)

Each tap coefficient provided by Matlab is first normalized to the range [-1.00,1.00], then multiplied by 127 and rounded to the higher integer. Finally 128 is added to each tap to make it positive. After the scaling function is applied, the [-1.00,1.00] range becomes [0,255], shown in Figure 3.3.9 and now unsigned integers.

Figure 3.3.9 Eight-Bit scaled coefficients

### 3.3.4 Code generation

Once the filter parameters are established and all decisions involving implementation details are complete, compiler ready C-language source code for the CCS PIC C is generated based on a set of three different templates. Each template is a specialized implementation scheme optimized to produce a different flavor.

- 1. Minimum Ram: The c-code generated using this template makes minimal demand on RAM.

- 2. Minimum Program Size: This template minimizes the program size.

- 3. Minimum Execution Time: This template produces code that achieves higher execution speed.

If the PIC chip is dedicated to performing signal filtering only then either implementation scheme is suitable. However if the FIR filter is used as a supplementary application that runs along side a primary application then it competes for the same recourses as the main application. Thus it may be useful for the user to use the parametric optimizations. To facilitate the selection of which type of optimization is suitable the user interface provides exact values for RAM, program memory and execution time with each option. The optimizations in RAM, execution speed and program size were all derived using a combination different buffering techniques, loop unrolling, and inline assembly language routines for the real-time components. Each is discussed in detail in the following sections.

### 3.3.5 Buffering Data

Once Matlab has generated the filter coefficients, they need to be accommodated within the PIC memory. Additionally, the constant stream of data from the PIC ADC must be accommodated in memory with the exact chronological sequence in which it was sampled. The buffering scheme for tap coefficients is discussed first.

The tap coefficients are stored in the PIC in the form of a look-up table in its program memory. Before filtering begins, the entire table is copied to the RAM and marked with a hardware pointer. Managing coefficients is not complicated because the number of taps is finite and the list is static (needs to be initialized only once).

Buffering the ADC data is a far more interesting problem. There are several complications that have to be dealt with. The finite impulse response filter is quite simply the linear convolution between a constant set of filter taps and a discrete time capture of a signal. For example, say, the desired filter has 30 tap coefficients then we would need to capture and store not only a latest sample of the signal, but the previous 29 samples as well. To achieve this, two different buffering schemes were explored. The first one used a traditional one-dimensional circular buffer [11]. This technique uses less memory but lengthens the cycle of computations. The second technique used two adjacent one-dimensional circular buffers [12]. This technique uses more RAM than the first, but allows the speed of the filter to approach its shortest possible computation time on the PIC 18F452 chip (using 8-bit taps and 8-bit data).

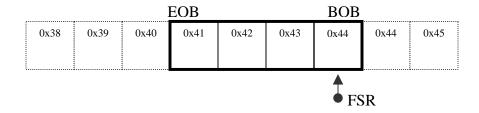

1. Circular buffer implementation on PIC 18F452: A circular buffer is a memory allocation scheme where memory is reused (reclaimed) when an index is incremented to a multiple of the buffer size. The modulo

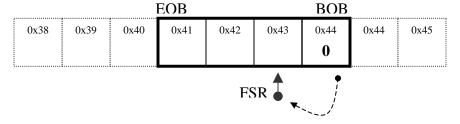

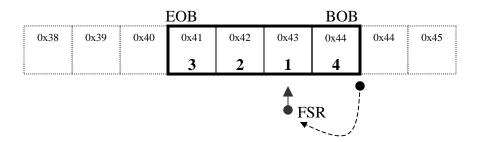

nature of a circular buffer maintains data in a queue form (chronological order) at all times without overrunning its allocated memory or the need for re-ordering. The elegance of this type of memory allocation is that the very same pointer that is used to queue data is efficiently used to dequeue it and due to its modulo nature, the dequeueing pointer automatically terminates at the point of insertion of the next sample. On a PIC chip, the buffer that was used is illustrated in Figure 3.3.10. Oldest sample is written over the newest sample and File Select Register (FSR) is the hardware pointer used to load and unload data. The illustrated circular buffer holds four elements — EOB marks end-of-buffer, BOB marks beginning-of-buffer, the numeric values in the figure are RAM locations and the sample buffer occupies memory locations from 0x41 to 0x44.

Figure 3.3.10 Circular buffer: Used to store ADC values for FIR filter

While loading the buffer the pointer FSR could be at any location within the buffer, so before the sample is stored, it is crucial to first check if the pointer has reached EOB. If it is the very first sample then the received data is placed at the BOB or location 0x44 and the pointer is post-decremented to location 0x43. In PIC18 assembly, the hardware pointer FSR can load data and post-decrement in a single cycle by using the POSTDEC register. There is no post-increment feature to the hardware pointer system; hence, the BOB is at a higher memory location than the EOB. When the FSR pointer has been reached, the EOB is simply reset to BOB. Based on this concept, the newest data sample automatically replaces the oldest data sample.

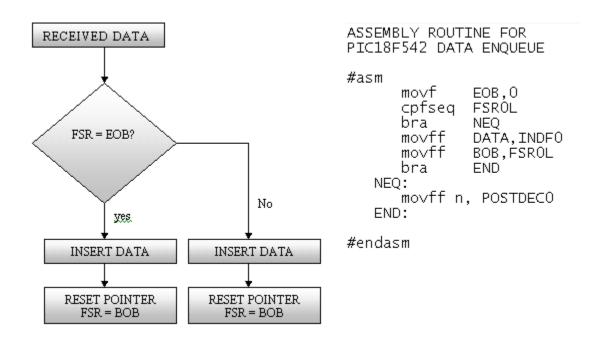

Illustrated in Figure 3.3.11 is a flowchart showing the process of loading the circular buffer as well as the assembly code written to achieve it.

Figure 3.3.11 Algorithm developed to load circular buffer

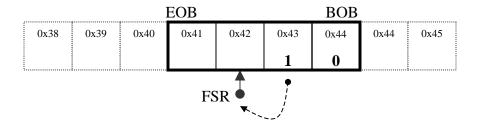

If the ADC was capturing a ramp in the form of digital data ranging from 0 to 6 then the buffer would load in the following way: The first data point '0' will be stored at the BOB and the pointer is decremented as illustrated in Figure 3.3.12. The next sampled data point '1' is stored in the location pointed by data pointer FSR and the pointer is decremented as shown in Figure 3.3.13.

Figure 3.3.12 Step 1: Data element 0 is loaded and pointer decrements

Figure 3.3.13 Step 2: Data element 1 is loaded and pointer decrements

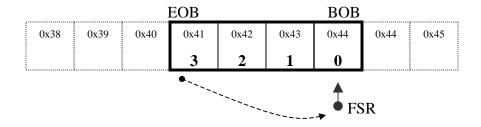

By the time '3' is sampled the buffer is full and EOB is reached as shown by the illustration. '3' is stored at EOB and the pointer is reset to the BOB. Now notice the pointer is at the oldest element as shown in Figure 3.3.14.

Figure 3.3.14 Step 3: Data element 3 is loaded and EOB is reached

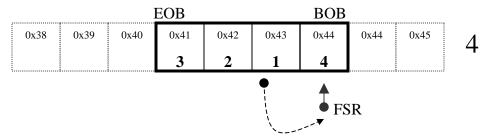

When '4' is captured it replaces the oldest element in the buffer and the pointer FSR is incremented as normal as shown in Figure 3.3.15.

Figure 3.3.15 Step 4: Element 4 is loaded and pointer is pre-decremented

In order to pull data from the buffer, the pointer FSR would simply travel in the opposite direction and data will be obtained in the exact opposite order to which it had entered. Before each the pointer is advanced it must first check for the BOB or it will travel beyond the buffer. If BOB is reached the pointer is relocated to EOB. In order to extract data the pre-increment function of the pointer is used so data is pulled and pointer is advanced in a single-cycle. To illustrate the process the pointer is pre-incremented to 0x44 and '4' is pulled as illustrated in Figure 3.3.16.

Figure 3.3.16 Element 4 is unloaded from buffer and BOB is reached

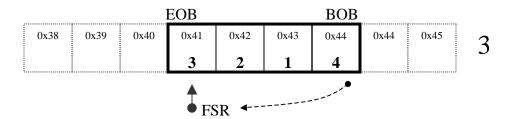

Note the pointer FSR is at the beginning-of-buffer so it is first relocated to the EOB and then the data pulled is '3' as illustrated in Figure 3.3.17.

Figure 3.3.17 Pointer is relocated to EOB and 3 is pulled

Pointer is pre-incremented to 0x42 and '2' is pulled followed by '1' and after four iterations the pointer FSR has automatically terminated at

the entry point where the next incoming data sample is to be placed as shown in Figure 3.3.18.

Figure 3.3.18 Data element 1 is pulled

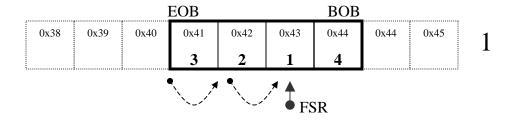

Data went into the buffer in the order {1,2,3,4} and came back out {4,3,2,1}. The formal algorithm and assembly code is in Figure 3.3.19.

Figure 3.3.19 Algorithm used to pull data from the circular buffer

2. Double circular buffer implementation on PIC 18F452: In the second buffering technique two adjacent circular buffers are used in such a way that the second one begins exactly where the first one ends. Every time a fresh sample is made, it is placed in both buffers in place of the

oldest sample respectively. Each buffer will have it's own pointer and both buffers will contain the exact data at any given time. [8]

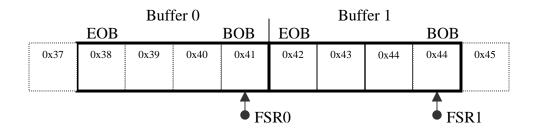

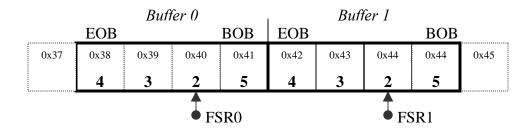

This buffering scheme has a very useful advantage over the previous one because the unloading pointer does no longer need to check for the end of buffer (EOB). Figure 3.3.20 of the buffering scheme might explain the process more clearly.

Figure 3.3.20 Topology of the Double Circular Buffers

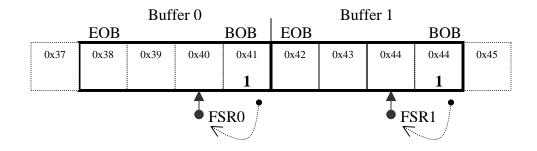

Once again the same data is being stored in the buffer, each data element is stored in the same respective place in both buffers. If the first sample element is '1' then both buffers will store the data and post-decrement in the same manner as if each was an independent buffer.

Figure 3.3.21 Data Element 1 is loaded to both buffers

Since both pointers move in tandem, only one needs to be checked for EOB and although this technique takes a little more time to load, it saves a lot more time during the unload. Since FIR filtering involves only a single load and N number of unloads (N being the number of coefficients), over all this technique produces a tremendous savings in computation time for each FIR output calculation.

After '1' the next data sample is '2' then '3' then '4' followed by '5' and the buffer will fill in the manner illustrated in Figure 3.3.22.

Figure 3.3.22 Data Elements 1-5 are loaded to buffer

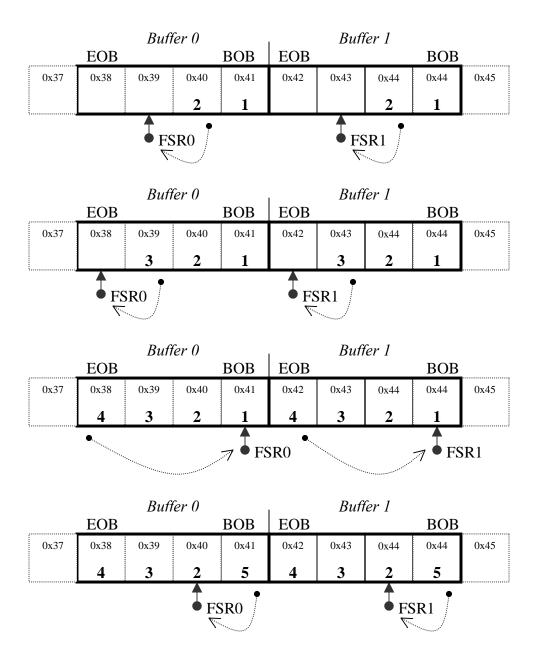

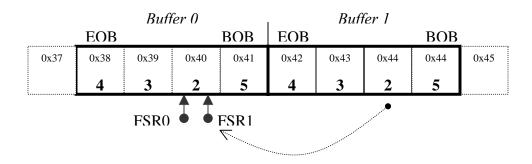

Unloading data from the buffer involves a slightly different technique than what is used for a single buffer. Since the FIR filtering algorithm involves a convolution operation, after every fresh sample is stored the filter needs to unload each data point in reverse chronological order to perform computation. Since the size of the buffer is known, say N, there is no need to test of end-of-buffer or beginning-of-buffer while pulling the data because pointer FSR1 can now simply cross over from its own buffer into the adjacent one and always find the chronologically correct sample, sitting beyond the barrier of the adjoining buffer. To illustrate the point say we wanted to pull data from the current buffer. The last data sample stored was '5' as shown in Figure 3.3.23.

Figure 3.3.23 Buffer Data Ready to be unloaded

Data can be pulled in ascending order or descending order depending on which of the two pointers are used. For FIR filter calculations the order of the sample is not important because the coefficients are symmetric. If descending order were desired we would first relocate FSR1 to the same location as FSR0 as shown in Figure 3.3.24.

Figure 3.3.24 Pointer FSR1 is relocated to same location as FSR0

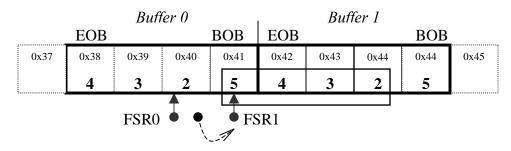

All that remains now is to pre-increment the pointer and pull the respective data sample from each location the pointer passes till it returns to the position it started (location 0x44).

The first data sample to be removed is '5' as the pointer FSR1 preincrements from location 0x40 to 0x41, both operation in one cycle as shown in Figure 3.3.25.

Figure 3.3.25 FSR1 pre-increments and unloads data element 5

Notice that data samples '5','4','3' and '2' are in chronological order across both buffers. Since the buffer size is a constant, 4, then four blind pre-increment operations will unload the buffer and the pointer will automatically be returned to the point of insertion of the next sample. Using this method neither EOB nor BOB needs to be checked while unloading the buffer.

The Figure 3.3.26 shows the flow-chart describing the algorithm for loading the adjacent circular buffers and Figure 3.3.27 shows the assembly language code written to implemented it.

Figure 3.3.26 Algorithm for loading the adjacent circular buffers

```

// Assembly code to load data into adjecent circular buffers

#asm

// Check for End of Buffer

mov

EOB, W

cpfseq

FSR0L

bra

NEQ

// If end of buffer is not reached goto NEQ:

else

// move data into last pointed location

// move data into last pointed location

// Reset FSRO to Begining of buffer0

// Reset FSR1 to Begining of buffer1

movff

DATA, INDFO

movff

DATA, INDF1

movff

BOBO,FSROL

BOB1,FSR1L

movff

end

bra

NEQ:

// Load data to Buffer0 and post-decrement

// Load data to Buffer1 and post-decrement

movff

DATA, POSTDECO

movff

DATA, POSTDEC1

END:

#endasm

```

Figure 3.3.27 Assembly routine written to load the buffers

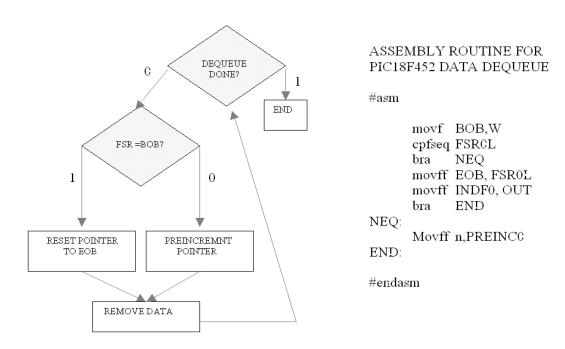

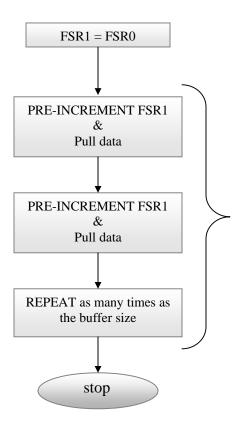

The flowchart outlines the algorithm for pulling data from the buffers is shown in Figure 3.3.28:

Figure 3.3.28 Algorithm used to unload from adjacent circular buffers

# 3.3.6 Sampling: Analog to Digital Conversion on 18F452

The most convenient option for analog to digital conversion is by using the integrated ADC module. The built in analog to digital converter uses a successive approximation algorithm and is capable of converting an analog voltage into a proportional 10-bit number. The ADC is capable of a maximum sampling rate of 52KHz for 10Bit conversions. For 8-Bit conversions, the maximum sampling rate is 62.5KHz at same temperature and impendence [10].

The value sampled by the ADC is stored in the register pair ADRESH/ADRESL. Each is 8 bits, ADRESH contains the high-byte and ADRESL holds the low-byte. In order to configure the ADC module the ADC control register pair ADCON0 and ADCON1 must be set with appropriate values.

The analog-to-digital converter module has eight input channels for the PIC 18F452. Each input is a separate channel multiplexed with a common converter. This allows sampling of several different sources in any specified order. Since there is only one analog-to-digital converter simultaneous sampling is not possible using the internal ADC module. The minimum wait time between the sampling of any two channels is called acquisition time. The acquisition time is a function of the ambient temperature and the source impedance. The maximum recommended source impedance or input impedance for analog sources is 2.5K. For the FIR filter only one channel is needed but for the adaptive filter two channels must be sampled nearly simultaneously.

The first task to setting up the ADC is to setup the control register pair ADCON0 and ADCON1. Both registers are eight bits wide and allow unrestricted read/write operations. The ADCON0 register controls ADC clock options, channel selection, and the bit GO/DONE in the ADCON0 register can be polled in order to check if analog to digital conversion is complete. The ADCON1 register controls the remaining clock options, shared with ADCON0 and selects which pins are configured as digital and which are analog. In order to setup the internal ADC both registers must be loaded with the appropriate values.

Configuring ADCON0 involves setting five bits on the register. The following is the contents of the ADCON0 Register shown in Figure 3.3.29.

Figure 3.3.29 Description of the ADCON0 Register

The ADC clock is derived from the main external oscillator. The PIC chip can run up to 40Mhz but the ADC clock cannot exceed 625KHz. Therefore the PIC must use a clock divide to scale the 40MHz external frequency to 625KHz, a factor of 64. Hence the ADCS1 and ADCS0 are 1, 0 to make the clock divider equal to 64. The channel for FIR filter is channel-0 hence the CHS2, CHS1, CHS0 are 0,0,0 and ADON is 1.

$$ADCON0 = <1 \ 0 \ 0 \ 0 \ 1 \ 0 \ 1 > or \ 0 x 85$$

The ADCON1, shown in Figure 3.3.30, is set in a similar manner as ADCON0 and it contains:

Figure 3.3.30 Description of the ADCON1 Register

The ADC stores a 10-bit result in two 8-bit registers. The ADFM bit selects if the result is left justified or right justified. Since the FIR filter

is going to use 8-bit samples instead of 10-bit samples, ADFM will be set to 0 to make the result left justified. A simple way to get a fast 8-bit approximation of the 10-bit sample is to only read the *ADRESH* register as illustrated in Figure 3.3.31.

Figure 3.3.31 Reading Only ADRESH will scale down to 8-bit

The ADCS2 bit is set to 1 to make the clock divide equal to 64 as discussed before. Bits <PCFG3, PCFG2, PCFG1, PCFG0> are set to 1,1,1,0 respectively. This allows pins A0 to be analog while all other pins are made digital. Since technically only a single analog pin is required to make a FIR filter. If more analog pins are needed then this register needs to be changed. The ADCON1 register is loaded with the following:

#### ADCON1 = <0.1001110 > or 0x4E

$V_{\scriptscriptstyle DD}$  and  $V_{\scriptscriptstyle SS}$  are used as voltage references with this configuration.

The FIR filters performance depends not only on sampling signals accurately but also on a chips ability to maintain a constant sampling rate. To this end, one of the PIC chips three hardware timers; timer1 is dedicated to performing analog to digital conversion at a periodic rate. This is a 16-bit timer that derives its timing from the external clock source and interrupts the PIC chip when it overflows. Once the timer is engaged it counts from 0 till 65535 at the what ever speed it been clocked and at the end of its count generates an interrupt.

In order to make a constant sampling rate the timer is not allowed to start from 0 but instead made to start from some offset value from which it will pass 65535 at a predictable interval since the clock speed to the timer is known. This offset value is calculated using the following way:

$$timer1\_offset = 65535 - \frac{external\_osc}{4 * prescaler * sampling\_rate}$$

(3.2)

In this case, the external oscillator (external-osc) is 40 MHz and the user determines the sampling rate in the design stage.

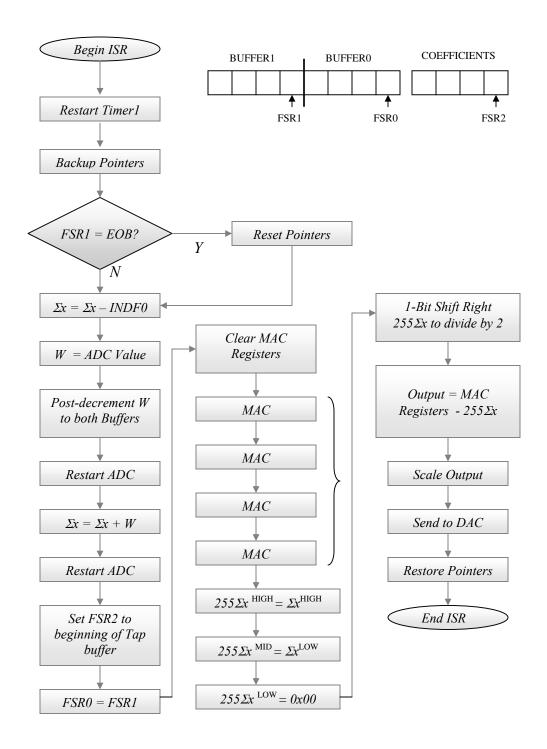

The interrupt service routine for timer1 will also perform all the calculations required of the filter and before exiting the Interrupt Service Routine (ISR) the result of the filter is generated.

#### 3.3.7 Filter Calculations

Three different strategies are used to perform the necessary filter calculations.

- 1. Optimized for maximum Speed

- 2. Optimized to use minimal Ram

- 3. Optimized to generate smallest program size.

All three strategies make use of the same general idea but are different in the way the data is buffered and computation is performed. In general the realization of FIR filters is obtained by the direct computation of the Equation 3.3 [12].

$$y_n = \sum_{0}^{N} x [n - N + 1] * [K_{N-1} + 128] - \sum_{0}^{N} x [n - N + 1] * 128$$

(3.3)

The equation presented above is a variation of the classical FIR filter equation that is presented in most books:

$$y_n = \sum_{n=0}^{N} x[n-N+1] * k_{N-1}$$

(3.4)

In both Equations 3.3 and 3.4, the term  $y_n$  is the output of the filter and is computed by the linear convolution of the coefficient matrix  $K_N$  and the discrete sample vector  $x_n$ . Both equations perform exactly the same computation and produce the same results however Equation 3.3 is far more PIC18F452 architecture-friendly because the signed multiplication operation in Equation 3.4 has been removed. This will allow PIC to maximize the use of the unsigned hardware-multiplier in the PIC hardware.

The only difference between Equation 3.4 and Equation 3.3 is that in Equation 3.3 the tap co-efficient vector  $K_N$ , which contains signed numbers ranging from -128 to +128 are made unsigned by adding to them the integer 128. In order to balance the result from the offset coefficients it becomes necessary to subtract  $128*\Sigma$   $\mathcal{X}_n$  from  $\mathcal{Y}_n$ . To illustrate this point, consider the following analogy. If we wanted to calculate the  $\mathcal{A}$ , which is a product between 8-Bit signed integer  $\mathcal{B}$  and 8-Bit unsigned integer  $\mathcal{C}$ , it will be given by:

$$A = B * C$$

(3.5)

The above computation will require a signed multiplication however if we modified the above equation in the following manner:

$$E = B*(C+128) - B*128$$

(3.6)

then we ultimately achieve the very same result as A and avoid the signed multiplication altogether.

$$A = E \tag{3.7}$$

### 3.3.8 Implementation for Shortest Execution Time

As stated before, three different implementations are possible using the filter design system. The first has the shortest possible execution time and possibly the most attractive implementation of all. The short execution time is achieved at the expense of higher RAM usage, since two adjacent circular buffers are used to store ADC samples instead of one. This doubles RAM use and also produces a much larger program, because to fully make use of the double buffer, the main multiply-accumulate loop is unrolled allowing for program to approach its theoretical minimal computation time, given the data word length constraints that is used by the program [12].

The implementation is split into two routines. The first one is the initialization Routine and the second is the Computation Routine. The initialization routine runs just once when the program begins and it serves only to initialize the buffers and other variables that are required for FIR filter calculations. The computation routine performs all calculation mandated by the filter and runs inside the interrupt service routine of timer1. With the confinement of all filter calculations inside the ISR, we achieve a degree of isolation making it possible for any main application to use the filter and not interfere with its operation or timing.

Memory Usage: The PIC 18F452 chip contains 1536 bytes of RAM and two addressing modes. There is direct-addressing and indirect-addressing. Indirect-addressing uses three pointers — FSR0, FSR1, FSR2

and each pointer is 12-Bit wide, with a 4-Bit select bank and 8-Bit select location within a bank. All memory use for the FIR filter is restricted to a single bank, thereby limiting the available memory for ADC samples and filter coefficients to a total of 256 Bytes. The obvious advantage of limiting all pointers use to a single bank is the speed that is gained because the pointers can be used faster if the bank does not need to be set before every call. Three buffers are used — a static buffer for tap coefficients that is loaded and initialized at start up and two identical adjacent circular buffers for the incoming ADC samples. All three buffers are of the same size and each buffer is given its own hardware pointer. Consider Figure 3.3.32 showing memory footprint

Figure 3.3.32 RAM used by the FIR filtering scheme

The buffers for the tap coefficients and ADC values can be of variable size, since the number of FIR filter coefficients is not fixed. The total memory allocated to the buffers cannot exceed 226 bytes. No buffer can be larger than 75 elements. Hence this design does not allow for FIR filters larger than 75 taps. The MATLAB user interface will generate a

warning if the user specifies a filter that generates more than 75 coefficients and the user is prompted to either accommodate fewer taps or select a different implementation strategy.

#### Filter Processing: (Initialization Routine)

If the filter is to produce an output, then an output port needs to be assigned, the first step of the initialization routine being the setup of an I/O port. Analog to digital converter is set to 8-Bit mode by simply left-shifting the results and reading the ADRESH register (See 3.3.6).

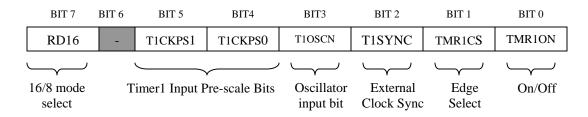

The timer1 interrupt must be set to sample at the user specified sampling rate. All filter processing is conducted in the timer interrupt. There are three registers associated with Timer1. These are T1CON, TMR1H, and TMR2L. The first is the control register the other two are offset registers that are used to initialize the timer. Timer1 can be setup as an 8-bit as well as 16-bit as shown in Figure 3.3.33.

Figure 3.3.33 Description of the T1CON Register

In order to setup the timer bit RD16 = 1, T1CKPSX is calculated in Matlab and set based on user specified sampling rate. T1OSCEN, T1SYNC are not used, TMR1CS = 0 to specify internal clock and TMR1ON is 1 to power on the timer.

The timer offset is calculated using equation discussed in section 3.3.6. The 16-Bit offset is loaded into register pair TMR1L, TMR1H. All

the registers are automatically loaded by code generated by the MATLAB program based on the sampling frequency selected by the user.

Before the timer is engaged the initialization routine loads the coefficients into the coefficient buffers and both the ADC buffers are set up, thereby initializing the pointers. Pointer FSR0 is used to load the coefficient buffer and pointers FSR1, FSR2 are used to address the ADC buffers. ADC buffering method is discussed in detail in section 3.3.5. Once all the buffers are initialized the timer1 is started.

#### Filter Processing: (Computation Routine)

The computation routine involves the real-time implementation of the FIR filtering algorithm given in Equation 3.8.

$$y_{n} = \sum_{0}^{N} x[n-N+1] * [K_{N-1} + 128] - \sum_{0}^{N} x[n-N+1] * 128$$

$$Multiply & Accumulate(Y_{I}) \qquad Accumulate(\Sigma x)$$

(3.8)

In order to compute filter output Yn or Equation 3.8 is broken into three different Equations 3.9, 3.10 and 3.11.

$$y_{1} = \sum_{0}^{N} x[n - N + 1] * [K_{N-1} + 128]$$

Sample vector Tan Coefficients (3.9)

$$\sum x = \sum_{0}^{N} x[n-N+1]*128$$

Sample Sum

(3.10)

$$Y_n = Y_1 - \sum x \tag{3.11}$$

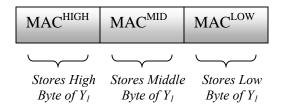

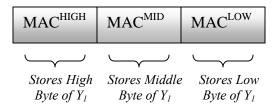

Equation 3.9 is implemented using a fixed-point multiply-accumulate operation block. The MAC block is repeated for N times till  $y_1$  is computed. A 24-Bit register comprised of three 8-bit registers is assigned to hold the MAC result shown in Figure 3.3.34.

Figure 3.3.34 Word space dedicated to storing MAC result

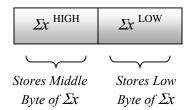

Equation 3.10 computes the sample-sum of all the samples held in the ADC buffers.  $\Sigma x$  is given a 16-Bit unsigned variable comprising to register pair  $\Sigma x^{\text{LOW}}$  and  $\Sigma x^{\text{HIGH}}$ , shown in Figure 3.3.35. It is calculated with minimal computational effort by simply subtracting from the total, the oldest ADC sample and adding the newest one every time a new sample is made. Thus a running total of all the samples in the buffer is constantly maintained without having to add up every value in the buffer each time a new sample is added to it.

Figure 3.3.35 Word space dedicated to storing Sample Sum

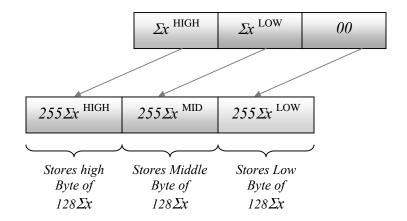

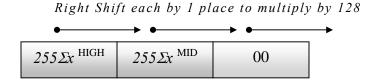

$\Sigma$ x has to be multiplied by 128 and subtracted from  $Y_t$  to obtain final output Yn. An efficient way to multiply by 128 is to copy the sum into another 24-bit variable i.e. moving  $\Sigma x^{LOW}$  to  $255\Sigma x^{MID}$  and  $\Sigma x^{HIGH}$  to

$255\Sigma x^{\rm HIGH}$  and clearing the  $255\Sigma x^{\rm LOW}$  will do an implicit multiply by 255 as shown in Figure 3.3.36.

Figure 3.3.36 Multiply by 256 algorithm

Once moved a single right-shift with carry on all three registers produces the required multiply by 128 shown in Figure 3.3.37.

Figure 3.3.37 Multiply by 128: Single Right shift of each byte

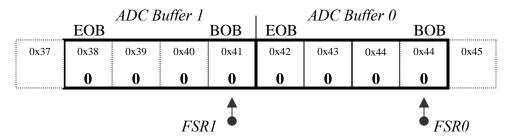

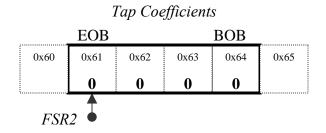

The MAC block for computing Y<sub>1</sub> uses three buffers that are located in RAM. The Buffers shown here are 4 elements long but can extend up to 75 elements depending on filter requirements. All buffers are dynamically scaled depending on filter requirements. A double buffering scheme is used for storing ADC samples and a single static buffer is used to store filter tap coefficients. FSR0, FSR1 and FSR2 pointers dedicated to each buffer as shown in Figure 3.3.38 and Figure 3.3.39.

Figure 3.3.38 Buffer setup for storing ADC samples

Figure 3.3.39 Buffer setup for storing Coefficients

The MAC cycle accumulator occupies three bytes of memory to store a 24-bit number as shown in Figure 3.3.40.

Figure 3.3.40 24-Bit Result store for MAC operation

Given the above constraints of 8-bit unsigned coefficients, 8-bit ADC samples and 24-Bit accumulator the quickest possible MAC on the PIC 18F452 is shown in Figure 3.3.41.

Figure 3.3.41 Multiply-Accumulate Algorithm

The entire MAC cycle lasts 800ns and the assembly code generated for it is as follows:

```

POSTDECO, W

// Move element pointed by FSR0 to (W)

movf

// Multiply FSR2 and Post-increment

mulwf POSTINC2

PRODL, W

// Move Product Low-byte to (W)

movf

// Add (W) to the MAC^{LOW}

addwf output_least

movf

PRODH, W

// Move Product High-Byte to (W)

//Add carry + (W) + MAC^{MID}

addwfc output_middle

// Clear (W)

clrf

WREG

//Add carry + (W) + MAC^{HIGH}

addwfc

output most

```