Graduate Theses, Dissertations, and Problem Reports

2017

## **Data Conversion Within Energy Constrained Environments**

Brandon M. Kelly

Follow this and additional works at: https://researchrepository.wvu.edu/etd

#### **Recommended Citation**

Kelly, Brandon M., "Data Conversion Within Energy Constrained Environments" (2017). *Graduate Theses, Dissertations, and Problem Reports.* 5959.

https://researchrepository.wvu.edu/etd/5959

This Dissertation is protected by copyright and/or related rights. It has been brought to you by the The Research Repository (a) WVU with permission from the rights-holder(s). You are free to use this Dissertation in any way that is permitted by the copyright and related rights legislation that applies to your use. For other uses you must obtain permission from the rights-holder(s) directly, unless additional rights are indicated by a Creative Commons license in the record and/ or on the work itself. This Dissertation has been accepted for inclusion in WVU Graduate Theses, Dissertations, and Problem Reports collection by an authorized administrator of The Research Repository (a) WVU. For more information, please contact researchrepository(a) mail.wvu.edu.

# Data Conversion Within Energy Constrained Environments

Brandon M. Kelly

Dissertation submitted to the

Benjamin M. Statler College of Engineering and Mineral Resources

at West Virginia University

in partial fulfillment of the requirements

for the degree of

Doctor of Philosophy in Electrical Engineering

David W. Graham, Ph.D., Chair Matthew Valenti, Ph.D. Natalia A. Schmid, Ph.D. Vinod Kulathumani, Ph.D. Edward M. Sabolsky, Ph.D.

Lane Department of Computer Science and Electrical Engineering

Morgantown, West Virginia 2017

Keywords: Analog-to-Digital Conversion, Extrema Sampling, Floating-Gate, Reconfigurable Analog, Wearable Devices, Wireless Sensor Networks

Copyright 2017 Brandon M. Kelly

#### Abstract

#### Data Conversion Within Energy Constrained Environments

#### Brandon M. Kelly

Within scientific research, engineering, and consumer electronics, there is a multitude of new discrete sensor-interfaced devices. Maintaining high accuracy in signal quantization while staying within the strict power-budget of these devices is a very challenging problem. Traditional paths to solving this problem include researching more energy-efficient digital topologies as well as digital scaling.

This work offers an alternative path to lower-energy expenditure in the quantization stage – content-dependent sampling of a signal. Instead of sampling at a constant rate, this work explores techniques which allow sampling based upon features of the signal itself through the use of application-dependent analog processing. This work presents an asynchronous sampling paradigm, based off the use of floating-gate-enabled analog circuitry. The basis of this work is developed through the mathematical models necessary for asynchronous sampling, as well the SPICE-compatible models necessary for simulating floating-gate enabled analog circuitry. These base techniques and circuitry are then extended to systems and applications utilizing novel analog-to-digital converter topologies capable of leveraging the non-constant sampling rates for significant sample and power savings.

## Dedication

Marriage is a promise, a potential, made in the hearts of two people who love, which takes a lifetime to fulfill.

- Edmund O'Neil

Dedicated to Erica and the lifetime we will spend fulfilling that promise.

## Acknowledgments

First, thank you to my family for all of the love and support over the years. I'm lucky to have such a large family, and even luckier to feel so close with all of them.

Thank you to Dr. Matthew Valenti, Dr. Natalia Schmid, Dr. Vinod Kulathumani, and Dr. Edward Sabolsky for serving on my committee and thank you Dr. David Graham for leading that committee. I have been lucky enough to have learned from most of you for the past decade. Also, thank you West Virginia University and the WVU Foundation for supporting my research.

I would also like to thank Brandon Rumberg, Kyle Allard, Spencer Clites, Steven Andryzcik, Alex Dilello, Mir Mohammad Navidi, and Haifa Abulaiha. Working on a deadline through the night, through the weekend, or through a blizzard has a funny way of building a strong camaraderie. Working alongside you is what I will miss most about my time at WVU.

A very sincere thank you to anyone who has ever posted a free tutorial or lesson online on anything electronics related. Few get rich by sharing their knowledge online, but many like myself are better engineers for it.

And finally, to my wife Erica. You challenge me, you push me, and you help me discover what I am capable of accomplishing. Thank you.

## Contents

| Dedication    |                                                   |                                                        | iii  |  |

|---------------|---------------------------------------------------|--------------------------------------------------------|------|--|

| A             | Acknowledgments                                   |                                                        |      |  |

| $\mathbf{Li}$ | st of                                             | Figures                                                | viii |  |

| 1             | Intr                                              | roduction                                              | 1    |  |

|               | 1.1                                               | Shannon-Nyquist Sampling                               | 2    |  |

|               |                                                   | 1.1.1 Nyquist-Rate Data Converters                     | 4    |  |

|               | 1.2                                               | Post Quantization Energy Expenditure                   | 6    |  |

|               | 1.3                                               | Analog Signal Conditioning and Pre-Processing          | 7    |  |

|               | 1.4                                               | Example Application: Electrocardiograms                | 8    |  |

|               | 1.5                                               | Summary                                                | 9    |  |

| <b>2</b>      | Technical Challenges in Asynchronous Quantization |                                                        |      |  |

|               | 2.1                                               | Asynchronous/Adaptive Analog-to-Digital Conversion     | 12   |  |

|               | 2.2                                               | Reconfigurable Analog Front Ends                       | 14   |  |

|               |                                                   | 2.2.1 Floating-Gate Transistors                        | 15   |  |

|               | 2.3                                               | Inter-Sample Time Quantization                         | 15   |  |

|               | 2.4                                               | Summary                                                | 17   |  |

| 3             | $\mathbf{A} \mathbf{S}$                           | PICE-Compatible Floating-Gate Macromodel               | 18   |  |

|               | 3.1                                               | Floating-Gate Modeling in SPICE                        | 18   |  |

|               | 3.2                                               | The Floating Gate Structure                            | 20   |  |

|               | 3.3                                               | Reactions of the Floating Node                         | 22   |  |

|               |                                                   | 3.3.1 Tunneling                                        | 23   |  |

|               |                                                   | 3.3.2 Injection                                        | 24   |  |

|               |                                                   | 3.3.3 Reverse-Tunneling                                | 26   |  |

|               |                                                   | 3.3.4 Charge Leakage                                   | 27   |  |

|               | 3.4                                               | Floating-Gate Macromodel                               | 27   |  |

|               |                                                   | 3.4.1 Verilog-A Implementation                         | 30   |  |

|               | 3.5                                               | Tuning the Floating-Gate Model                         | 34   |  |

|               |                                                   | 3.5.1 Calculation of Injection and Tunneling Constants | 34   |  |

|               |                                                   | 3.5.2 Fine-Tuning the Model for Fabricated Devices     | 36   |  |

|               | 3.6                                               | Comparison of Model to Fabricated Designs              | 36   |  |

| CONTENTS | vi |

|----------|----|

|          |    |

|   | 3.7                                                  | 3.6.1 Static Programming3.6.23.6.2 Dynamic Programming3.6.2Conclusion3.6.2                                                                                                                                                                                                                                                                                  |

|---|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4 | 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6               | rema Sampling – An Adaptive Sampling Method         38           Energy-Constrained Sampling         38           Adaptive Sampling         4           4.2.1 Extrema Sampling         4           Reconstruction         4           Results         4           Sampler and Quantizer Implementation         4           Conclusion         4             |

| 5 | Tem<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5               | Introduction                                                                                                                                                                                                                                                                                                                                                |

| 6 | Asy<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7 | Asynchronous Data Conversion 6 System Overview 6 Analog Front-End for Pre-Processing 6 6.3.1 Synthesized Extrema Detection Circuit 6 Successive-Approximation ADC 6 6.4.1 Successive Approximation Register 6 6.4.2 Digital-to-Analog Coverter 6 6.4.3 Non-Overlapping clock 6 6.4.4 Comparator 6 Time-to-Digital Converter 7 System Example 7 Conclusion 7 |

| 7 | Ext. 7.1 7.2 7.3                                     | rema-Enhanced Successive Approximation ADC  Data Converter Efficiency                                                                                                                                                                                                                                                                                       |

|   | 7.4<br>7.5                                           | 7.3.1 FSM Implementation       8         7.3.2 Comparator       8         Results       8         Conclusion       8                                                                                                                                                                                                                                        |

| CONTENTS                  |            | vii                                            |    |

|---------------------------|------------|------------------------------------------------|----|

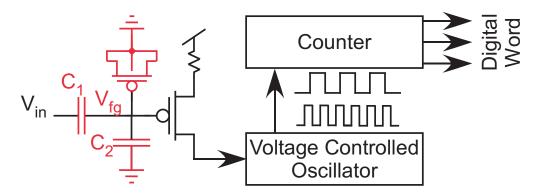

| 8                         | VC         | O-ADC with Floating-Gate Linearization         | 88 |

|                           | 8.1        | Voltage-Controlled-Oscillators as ADC elements | 88 |

|                           | 8.2        | System Overview                                | 90 |

|                           |            | 8.2.1 Principles of the VCO-ADC                | 90 |

|                           |            | 8.2.2 Principles of Floating Gates             | 91 |

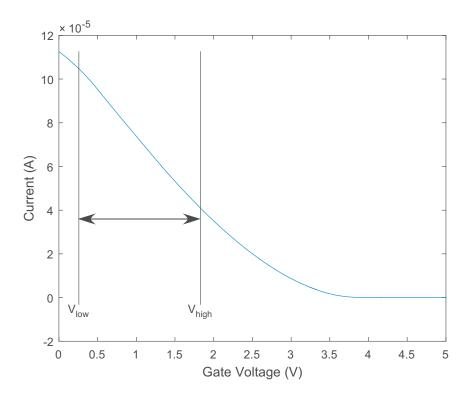

|                           | 8.3        | Linearization Technique                        | 91 |

|                           | 8.4        | Results                                        | 93 |

|                           | 8.5        | Conclusion                                     | 94 |

| 9                         | Sun        | nmary and Future Work                          | 96 |

| $\mathbf{R}_{\mathbf{c}}$ | References |                                                |    |

## List of Figures

| 1.1 | Design compromises in ADC topologies                                 | 4  |

|-----|----------------------------------------------------------------------|----|

| 1.2 | Example of a 'bursty' biological signal                              | 8  |

| 2.1 | Block diagram of an asynchronous quantizer system                    | 12 |

| 2.2 | Block diagrams of common time-to-digital converters                  | 16 |

| 3.1 | Floating-gate schematic and layout                                   | 19 |

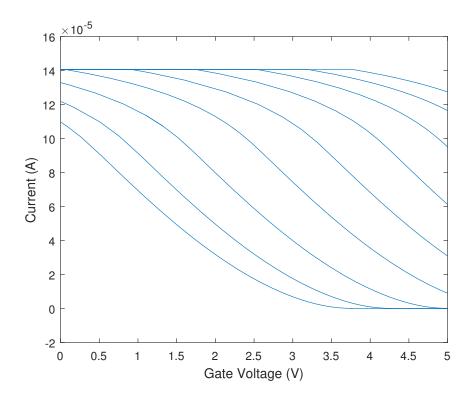

| 3.2 | Control gate voltage to channel current of a Floating-Gate           | 22 |

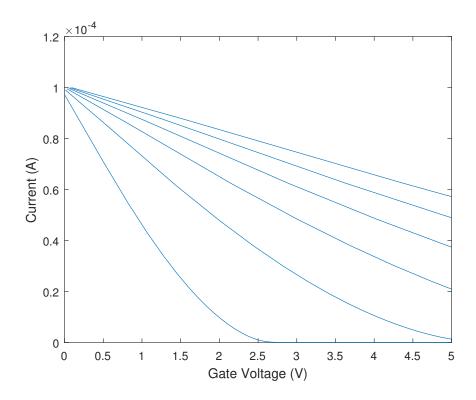

| 3.3 | Tunneling currents across multiple transistor fabrications           | 24 |

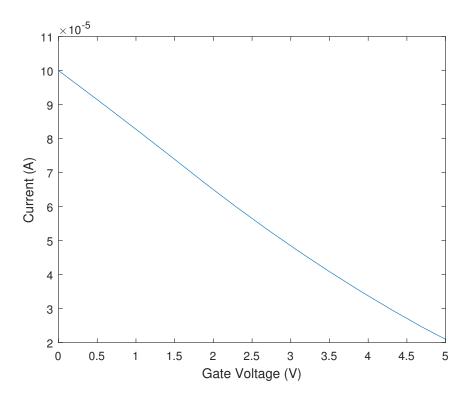

| 3.4 | Injection currents across multiple transistor fabrications           | 25 |

| 3.5 | Demonstration of reverse-tunneling in a floating-gate device         | 26 |

| 3.6 | The floating-gate macromodel                                         | 28 |

| 3.7 | Test-bed for floating-gate charge reprogramming characterization     | 35 |

| 3.8 | Measured vs simulated pulsed-injection data                          | 36 |

| 3.9 | A floating-gate amplifier with simulated and measured waveforms      | 37 |

| 4.1 | Nyquist-rate vs adaptive-rate sampling                               | 40 |

| 4.2 | Block diagram of a signal quantization and transmission system       | 42 |

| 5.1 | Temperature dependence of a floating-gate transistor                 | 51 |

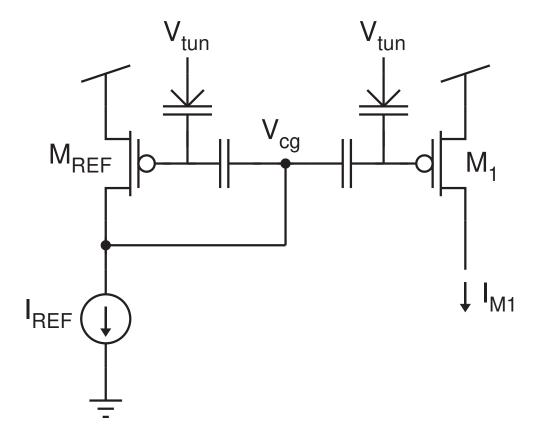

| 5.2 | Floating-gate current mirror                                         | 52 |

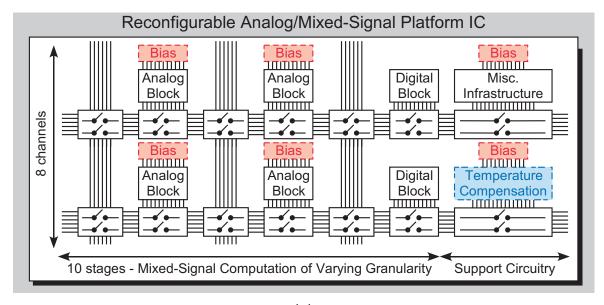

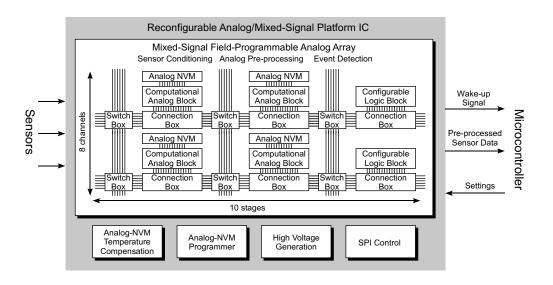

| 5.3 | FPAA block diagram with temperature compensation                     | 53 |

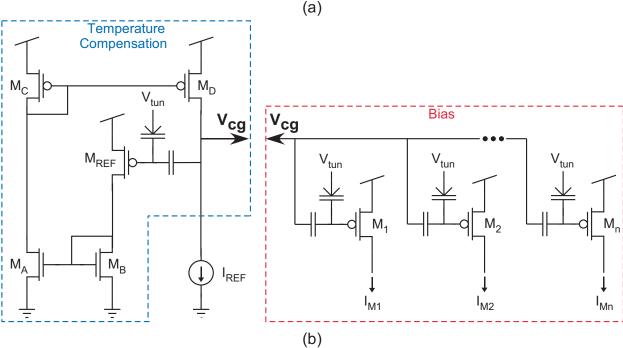

| 5.4 | Floating-gate current vs temperature                                 | 57 |

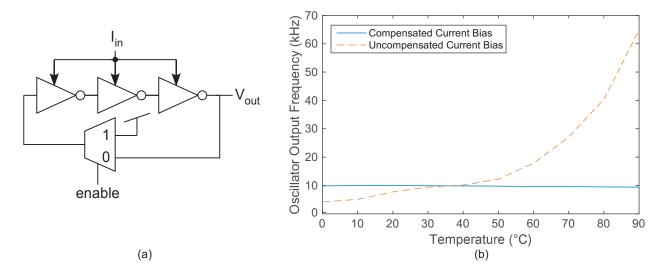

| 5.5 | Ring oscillator performance vs temperature                           | 58 |

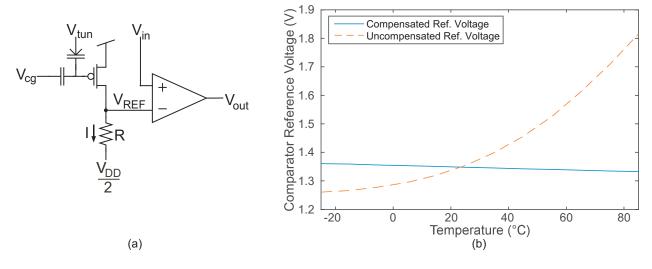

| 5.6 | Comparator performance vs temperature                                | 58 |

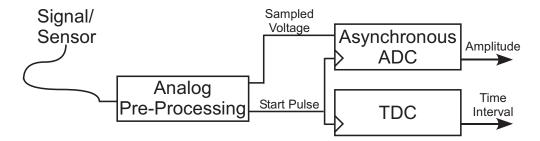

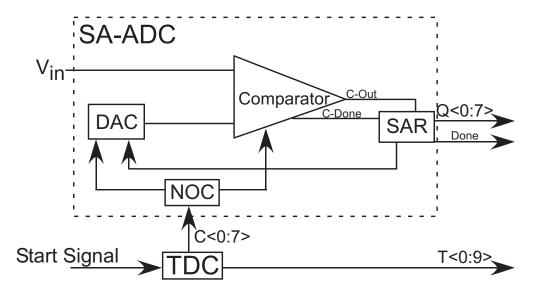

| 6.1 | Block diagram of an asynchronous analog-to-digital conversion system | 61 |

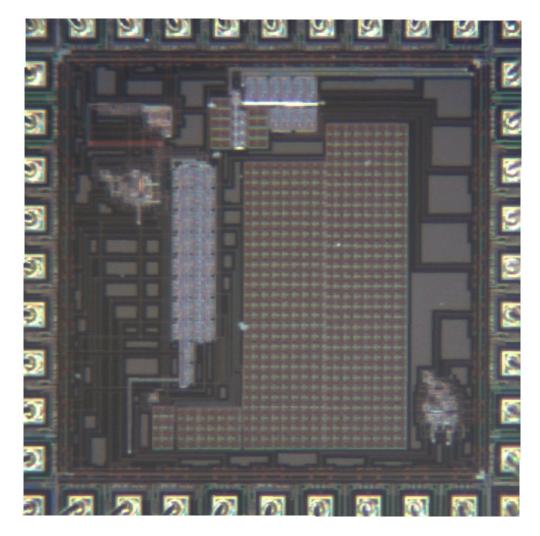

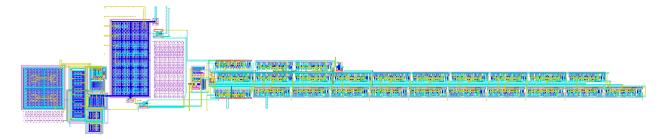

| 6.2 | Die photograph of the $0.5\mu\mathrm{m}$ asynchronous ADC/TDC        | 62 |

| 6.3 | Detailed diagram of the asynchronous ADC/TDC                         | 64 |

| 6.4 | Architecture of the RAMP integrated circuit                          | 64 |

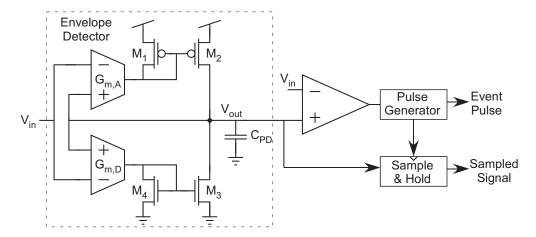

| 6.5 | Extrema detection circuit                                            | 66 |

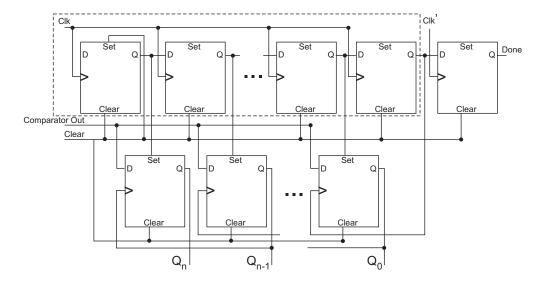

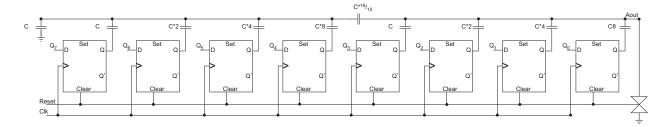

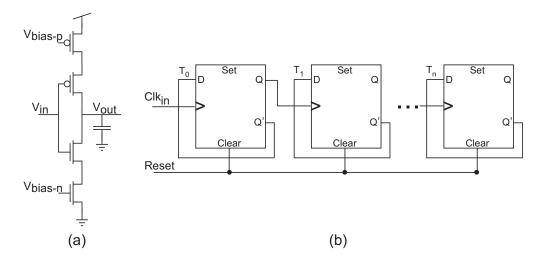

| 6.6 | Scehmatic of a successive approximation register                     | 67 |

| 6.7 | Schematic of a charge-redistribution DAC                             | 68 |

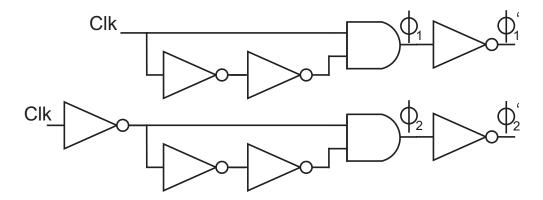

| 6.8 | Schematic of a non-overlapping clock generator                       | 69 |

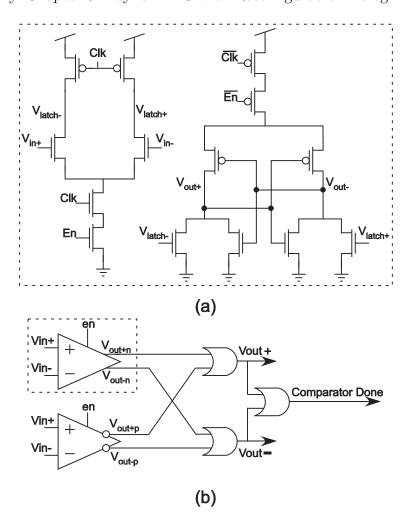

| 6.0 | Schomatic of a full scale range comparator                           | 70 |

| LIST OF FIGURES | ix |

|-----------------|----|

|-----------------|----|

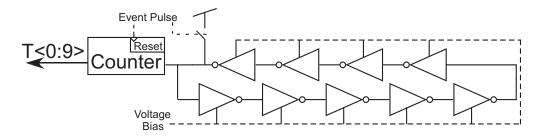

| 6.10 | Block diagram of a time-to-digital converter               | 71 |

|------|------------------------------------------------------------|----|

| 6.11 | Schematic of a delay unit and counter                      | 72 |

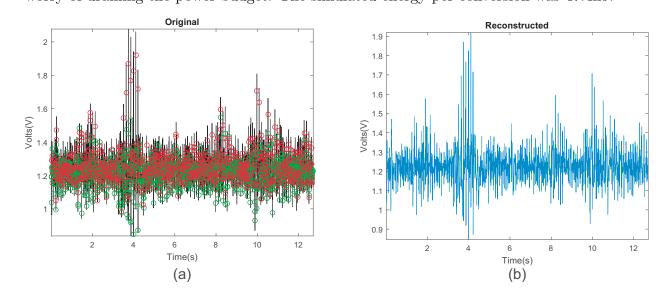

| 6.12 | Results of an EMG extrema capture and quantization         | 73 |

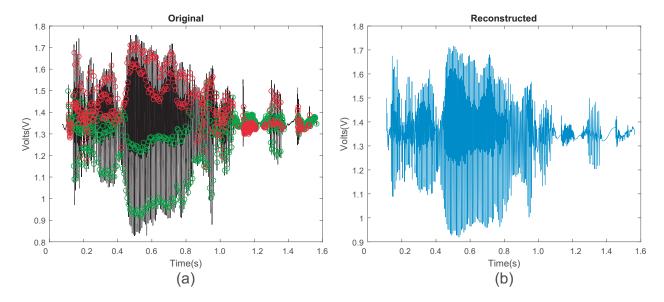

| 6.13 | Results of a vocal signal extrema capture and quantization | 74 |

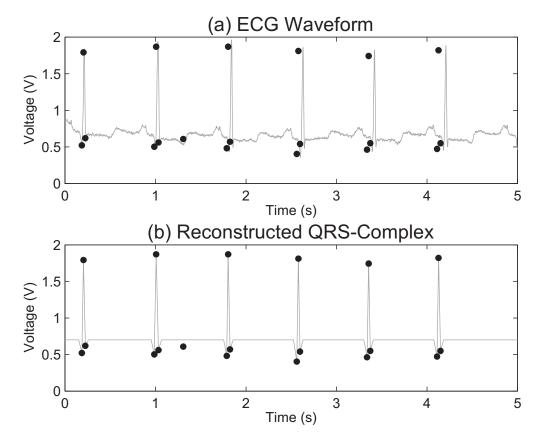

| 6.14 | Results of an ECG extrema capture and quantization         | 75 |

| 7.1  | Successive approximation with extrema samples              | 80 |

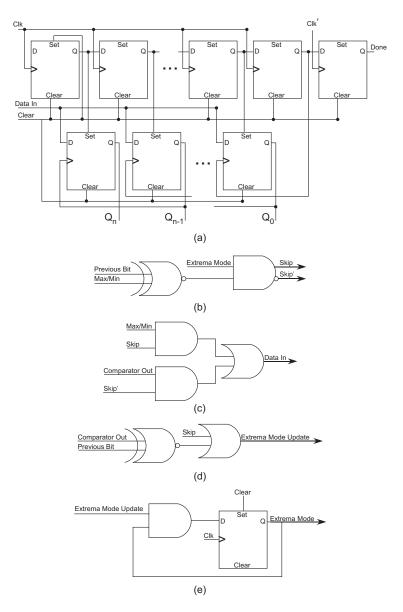

| 7.2  | Extrema-enhanced successive approximation register         | 82 |

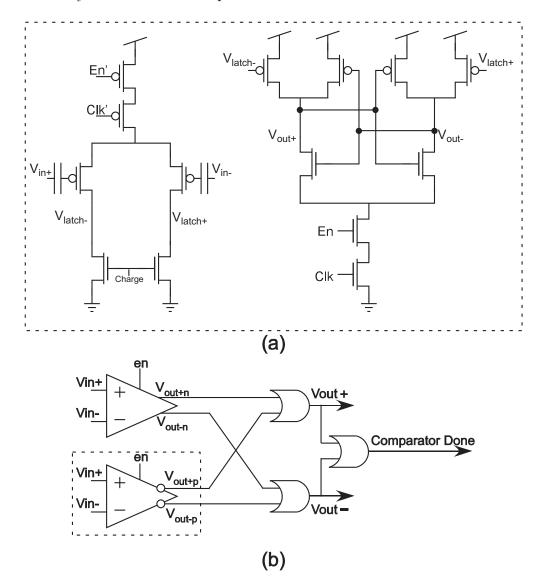

| 7.3  | Floating-gate enabled full-scale range comparator          | 84 |

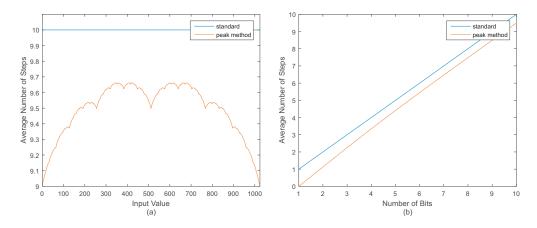

| 7.4  | Steps reduced with extrema-enhancement                     | 85 |

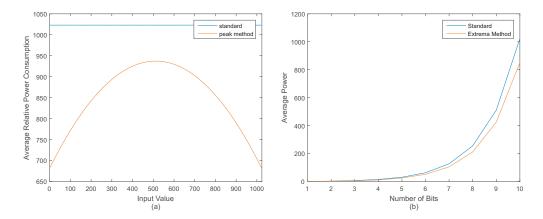

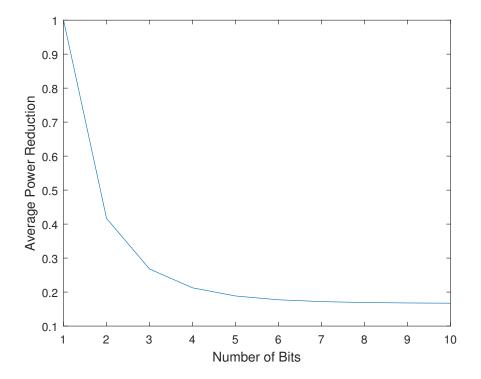

| 7.5  | Power consumption reduced with extrema-enhancement         | 86 |

| 7.6  | Percentage power versus resolution in extrema-enhancement  | 86 |

| 8.1  | VCO-ADC plus the proposed linearization method             | 89 |

| 8.2  | Non-linear input-output in VCO-ADC                         | 92 |

| 8.3  | Effect of charge programming on VCO-ADC                    | 93 |

| 8.4  | Effect of capacitive division on VCO-ADC                   | 94 |

| 8.5  | Result of linearization technique on VCO-ADC               | 95 |

| 8.6  | $0.35\mu\mathrm{m}$ CMOS VCO-ADC layout                    | 95 |

## Chapter 1

## Introduction

It is now common to expect digital devices to be able to interact with our analog environment, but this interaction is really the melding of two different worlds. Watches that monitor our heartbeat, phones that listen for specific commands, roads that monitor themselves for degradation – these are all examples of digital systems interacting with our analog world. Converting analog signals into digital representations is very energy intensive, but it is a necessary prerequisite to our devices performing some useful computation or monitoring task. Despite the complexity involved in this conversion, these sensor interfaced-devices are proliferating at an incredible rate.

Some of these devices take the moniker of wireless sensor networks (WSNs) and are primarily focused on remote monitoring applications. These applications range from monitoring the integrity of roadways and bridges [1] to monitoring cargo in transit [2]. WSNs, as the name implies, form their own network over which to share information and help operators make informed decisions about applications which would usually be to expansive or remote for an individual to monitor. As these networks grow, the primary limitations become the individual power budgets of the individual nodes as well as the growing aggregate of data which must be passed by the entire network.

Another class of discrete-sensor-interfaced devices are bio-wearable technologies. Initially, these applications focused on health and exercise related goals (e.g., monitoring heart-rate during a jog or observing blood pressure over the course of a day), but have been rapidly extended to more clinically-driven applications within physical therapy and sports sciences

[3, 4, 5]. These devices collect incredible amounts and varied types of data, pushing our understanding of our own physiology. As the desire and need for more advanced bio-signal monitoring applications develop, so too does the need for devices which can be adapted to a variety of different processing algorithms, all without exceeding their limited power and data storage budgets.

The most broad class of sensor-interfaced devices are known collectively as the internet of things (IoT). IoT devices number in the tens of billions, and are only expected to keep proliferating. They range from smart-refrigerators and smart-thermostats to more energy constrained applications such as trackers and cell phones. The sheer number of applications and the volume of data processed in the IoT is staggering, and presents a challenge to engineers attempting to make use of it.

For energy-constrained sensor-interfaced devices to continue to proliferate and advance in complexity, new low-power architectures and signal-compressing methods must be developed. This chapter will highlight the traditional paths that have been taken to achieve both energy and sample reduction, while developing the background necessary to understanding the need for the devices and techniques presented by this work.

## 1.1 Shannon-Nyquist Sampling

An analog signal is defined as being continuous in time. Being continuous in time means that, between a start and end time, the signal is defined for any point in time, no matter how fine the time scale. These continuous-time analog signals are different than the discrete-time (i.e., defined only at specific time intervals) digital signals which empower the operation of modern electronics. The challenge in interfacing modern electronics with the real-world is in quantizing analog signals in a way that creates high-quality digital representations with low-power expenditures. This section will discuss the way in which signals are typically sampled and quantized.

One of the influential works that has made the digital age possible is Claude Shannon's "Communication in the Presence of Noise" [6]. In this work, Shannon created a foundation for how we quantize and transmit analog data. The rate, known as the Nyquist rate, was

described succinctly by the following theorem:

If a function f(t) contains no frequencies higher than W cps, it is completely determined by giving its ordinates at a series of points spaced  $\frac{1}{2W}$  seconds apart.

This theorem states that a band-limited signal may be completely reconstructed if sampled at twice its highest frequency component. The band-limiting condition is a necessary prior step to choosing the Nyquist Rate. Intuitively this condition makes sense – it would be difficult to choose a rate based upon the highest frequency content of a signal if you did not limit what that frequency could be. The process yields the following equation:

$$f(x) = \sum_{k \in \mathbb{Z}} f(kT) \operatorname{sinc}(x/T - k) \tag{1.1}$$

As a sampling scheme, Shannon's method is theoretically sound and surprisingly simple to understand. However, the physical implementation is marred by some practical difficulty. Firstly, real-world signals are not bandlimited. Generally, this is both a natural result (feint harmonics in speech for example [7]) as well as an artificial product of high-frequency noise being added to the system. In a similar vein, perfect low-pass filters do not exist. Furthermore, the more stringent your filtering requirements, the longer the required computation – at least for digitally produced filters.

To handle these non-idealities, modern mathematicians have adjusted the definition so that a 'modern' approach to Shannon sampling is one that minimizes reconstruction error, given not-completely-bandlimited functions and non-ideal filters [8]. This reinterpretation has been realized in the form of different approximations, allowing quicker convergence with understood resolution trade-offs through the use of specific mathematical modalities including splines [9] and wavelet theory [10].

These mathematical insights have led to more efficient implementations of the Shannon-sampling paradigm, as well as a more thorough understandings of its limits, but the Nyquist rate remains a limiting factor. Simply put, the sampling and reconstruction algorithms can become increasingly refined, but no matter what, you will still have to sample the signal at twice its highest frequency. The Nyquist rate is a hard minimum on the number of samples required to perfectly represent a signal – at least for traditional Shannon sampling.

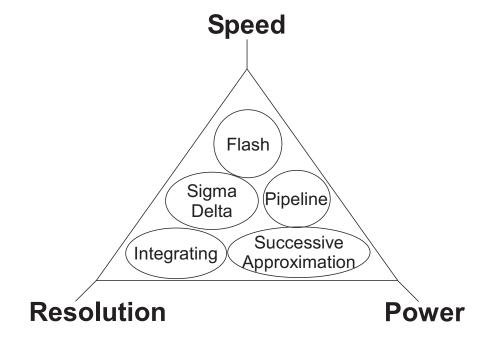

Figure 1.1: There is an intrinsic three-way trade between speed, resolution, and power within ADC design. On the continuum of this trade-off are the five primary ADC types. Speed refers to how quickly an ADC can perform a conversion. Power refers to the power efficiency of a particular topology. Resolution refers to how accurately, or with how many digital bits, an ADC can quantize an analog quantity.

### 1.1.1 Nyquist-Rate Data Converters

There are many topologies within the area of analog-to-digital converters (ADC), but they all tend to trade three quantities: power expenditure, conversion speed, and sample resolution (Fig. 1.1). Typically, advances in one quantity result in some loss in one or both of the other two. While there are examples within individual topologies which stand as outliers, examining the trends within these topologies [11] allows us to make some broad inferences about their optimum application.

The first category of ADCs is comprised of flash and pipeline ADCs. Both are known for their speed, but at the cost of very high power consumption. While this high consumption can be partially mitigate through the use of multiple lower resolution quantizers, with subranging or folding techniques [12, 13], they are still best left to applications which require giga-hertz rate sampling at the cost of milli-watt power consumption [11, 14].

On the other end of the Nyquist-rate ADC spectrum are very high-resolution ADCs –

particularly integrating converters. This topology can reach resolutions up to 20 bits, but is generally limited to sub-kilohertz sampling rates. This technique suffers from linearity and scaling issues and is no longer a popular area in research outside of very application specific circumstances [15].

Somewhere between these two extremes, there is a speed-resolution-power trade-off that is considered ideal for low-power sensor-enabled systems. This region is characterized by the successive-approximation ADC (SA-ADC) topology, which is easily implemented in energy-constrained systems.

SA-ADCs follow a conversion process that is very similar to a binary search. In essence, the SA-ADC has a list of ordered numbers that represent all of the digital values which it is able to estimate an analog signal to be. The SA-ADC finds where in this list the analog sample belongs by first comparing it to the midpoint of its list. If, for example, the analog value is found to be greater than this midpoint, the bottom half of the list is discarded. The top half of the list is then split in half again, and the process repeats itself until the closest approximation within the list to that sample is found. This approximation is then the digital word produced by the SA-ADC.

SA-ADCs are the chosen topology for most cutting-edge ADC research. Many interesting variants of SA-ADCs have been developed, including subranging [16], time-interleaved [17], variable resolution [18], and self-clocking architectures [19]. In addition to demonstrating some of the highest conversion rates among papers submitted to top-tier conferences [11], SA-ADCs have been shown empirically to be the most energy efficient topology. [20] showed that among the many types of ADC architectures, the efficiency of switch capacitor circuits in CMOS technology make SA-ADCs among the most inherently efficient for the low to medium resolution range.

Even though ADCs are not purely digital systems, they have still benefited from both process scaling and from a plethora of research. In [21], Murmann predicted that power expenditure in ADCs would continue to halve every two years, as long as CMOS processes continued to scale in the nano-meter range. And while the area of ADC research has made great strides in reducing power consumption, the ADC itself only represents one part of the energy expended by a discrete sensor-interfaced device.

## 1.2 Post Quantization Energy Expenditure

Within networks of discrete sensor-interfaced devices, there are many forms of power consumption. This work thus far has only discussed the cost of sampling and quantizing analog signals. For these quantized signals to be useful, however, they must normally be processed by a microcontroller and/or transmitted to some other device by a transceiver.

Microcontrollers are digital devices which process and route digital data. They are the necessary step, in traditional systems, for turning digital data into usable pieces of information. Unfortunately, this digital processing comes at a cost. One of the lowest-power microcontroller series on the market, the MSP430, runs on a supply voltage of 1.8 volts and an active current of  $101.25\mu\text{A/MHz}$ . This level of current draw may be low for a microcontroller, but it is too high for an energy constrained system to maintain. It is thus important that as little active processing as possible be performed by the microcontroller so that it can remain in a lower power sleep-state, where it only consumes  $0.5\mu\text{A}$  of current.

Transceivers transmit or receive data in wireless applications. They are necessary for communicating raw signals or processed data from WSN nodes, wearable devices, or IoT devices to more computationally powerful base stations. One example use-case is a wearable pedometer transmitting gait information back to a cell-phone for easier viewing and storage of information. A different use-case might be an IoT device transmitting a speech signal to a more powerful base-station for speaker and command identification. In either case, the number of samples in the signal is related to how long the transceiver(s) must be left in a run-mode. An example of a very low power transceiver is the CC110L series, which operates on a 1.8 volt supply with a 16mA active current draw and a 200nA sleep-state current draw. Clearly, it greatly benefits the power-budget to make the transmitted message as short as possible, thus utilizing the active-state of the transceiver as little as possible.

These components, transceivers and microcontrollers, represent system overhead in discrete sensor-interfaced devices. Reduction of their power consumption can take two forms. The first is simply through improvements in device topology or scaling of process. This form is the most direct method, but requires considerable research and, for process-scaling, increasingly costly fabrication processes. The second way to reduce power consumption is

to reduce the required amount of data points which need to be processed and transmitted. If this reduction of data is not done digitally, then the next logical place for it to occur is within the analog domain, prior-to or during signal quantization. Whatever power is consumed during this data reduction must then be weighed against the power saved by reduced processing and transmission to determine the overall system impact.

## 1.3 Analog Signal Conditioning and Pre-Processing

Prior to the quantization of a signal, it is possible to perform some conditioning and classification operations. Since the signal is analog to begin with, analog electronics offer a natural and power efficient means of doing so [22]. In [23], for example, an analog auditory sensory system was presented that provided a power savings of 3-4 orders of magnitude over a comparable digital system. This power savings was shown to be the equivalent of a 20 year leap in digital fabrication process technology.

Given the pre-requisite of band-limitedness for Shannon-Nyquist sampling, it is no surprise that most data converters include an analog signal-conditioning front end. In this context, signal conditioning typically includes performing some sort of filtering operation to reduce the presence of high-frequency noise within a signal. Intuitively, removal of this noise ensures a more accurate sampling and reconstruction of the target signal.

Another, less common operation is to use analog electronics to perform a classification operation. By taking a signal and breaking it down by frequency spectrum, magnitude, or periodicity, analog electronics are capable of detecting events of interest. These events could include the onset of voice [24, 25], the passing of a certain class of automobile [1], or the onset of a cardiac event within an electrocardiogram [26]. The detection of these events allows the system to selectively turn the quantization stage on only during events of interest.

Unfortunately, analog design does not benefit from process scaling the way that digital design does. In fact, scaling tends to result increased mismatch, noise, and non-linearity in analog circuits. A large part of this is caused by the lower supply voltage, which creates less 'head room' within which the analog circuit can operate. In addition to this problem, analog circuits are often very application-specific, requiring new circuits to be designed on a

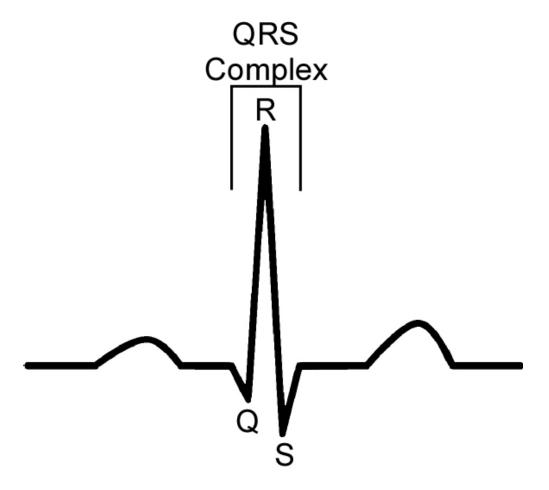

Figure 1.2: A simulated electrocardiogram waveform, illustrating the locations of the Q, R, and S inflection points which form the QRS complex.

per-application basis.

## 1.4 Example Application: Electrocardiograms

Within the domain of wearable devices, systems which monitor biological signals are very popular. Given their prevalence, it is natural to use a bio-signal monitoring device to bring in to context all of the background material presented in this chapter. Our example device will focus on electrocardiogram signals. But we will consider an application which traditionally requires some post-processing in the digital domain – the capture of the QRS complex.

While an analysis of the complete electrocardiogram (ECG) waveform provides the most

data, a great deal of clinically relevant data can be gleaned from just the QRS complex. QRS complexes are useful for a variety of medical purposes ranging from monitoring for hyperkalemia or cardiac hypertrophy to simply extracting heart-beat to estimate perceived exertion [27].

In a traditional system, the analysis of a QRS waveform would begin by utilizing an ADC at a sampling rate dictated by Shannon-Nyquist sampling. Given that the highest rate of change in the QRS waveform of a 60-100 beats per minute heart rate occurs at a frequency of 57 Hz, the accurate reconstruction of the waveform requires a 114 Hz sampling rate. This 114 Hz sampling will result in 68-114 samples per QRS complex.

These 68-114 samples must then be processed by a microcontroller and/or transmitted by a transceiver. The total number of samples could be reduced by using an analog front-end to trigger sampling only when the heart rate is outside of a normal window [26], but this would still result in 68-114 samples per 'interesting' QRS complex. If you consider that this complex is only defined by three requisite data points, then this traditional method results in a thirty eight times potential oversampling. A better method would be to sample these three requisite points directly – avoiding the need of a microcontroller for digital processing and mitigating the use of a transceiver, resulting in system-wide power savings. Achieving this type of data-driven adaptive sampling is the goal of this work.

## 1.5 Summary

Now that the context of traditional sampling within sensor-interfaced devices has been set, this work can demonstrate a potential improvement – adaptive sampling for energy-constrained systems. Chapter 2 will begin by reviewing the requirements of, and the current literature on, adaptive and asynchronous sampling. Chapter 3 will present a SPICE compatible non-volatile analog-memory macromodel while Chapter 4 will present a frequency adaptive sampling scheme. The next half of this work will leverage these mathematical and simulation-based tools to develop full systems realized in physical circuitry. Chapter 5 will utilize the analog-memory model to create a temperature compensation circuit – this will provide a stable platform for data conversion to occur. Chapter 6 will discuss the use of

adaptive sampling within the context of specific, bio-wearable related applications. I will extend this adaptive sampling method in Chapter 7 to outline an ADC architecture which takes further advantage of analog memory and the frequency-adaptive sampling method. Next, in Chapter 8, I will demonstrate the versatility of some of the developed techniques on an entirely different data-converter topology. Finally, Chapter 9 will summarize the key findings of this work and detail possible directions in which this research could be further developed.

## Chapter 2

# Technical Challenges in Asynchronous Quantization

Many energy-constrained sensor-interfaced devices (e.g., WSN nodes, bio-wearables) focus on the capture and analysis of 'bursty' signals. A bursty signal is one which is characterized by long portions of relative inactivity interspersed with shorter periods of high-frequency events. Systems tasked with monitoring bursty signals such as electrocardiogram (ECG), electromyography (EMG), or vocal signals are traditionally required to sample at a constant rate of twice the signal's highest frequency component – known as the Nyquist rate. This fixed sampling rate leads to oversampling during lower-frequency portions of the signal. This oversampling is even more wasteful in applications which do not require a perfect reconstruction of the signal, but instead are attempting to glean some specific information or data point.

Adapting to a signal's changing frequency characteristics or capturing specific points of interest is the primary goal of adaptive and asynchronous sampling systems. This chapter begins with a brief discussion of asynchronous and adaptive conversion systems in Section 2.1. One key difference is the mechanism which triggers these asynchronous systems, which is usually some sort of analog front-end. Section 2.2 will introduce the concept of using reconfigurable analog to alleviate some of the issues associated with using analog-front ends. Finally, Section 2.3 will provide some background on the issue of inter-sample time measurement – a unique challenge in asynchronous quantization.

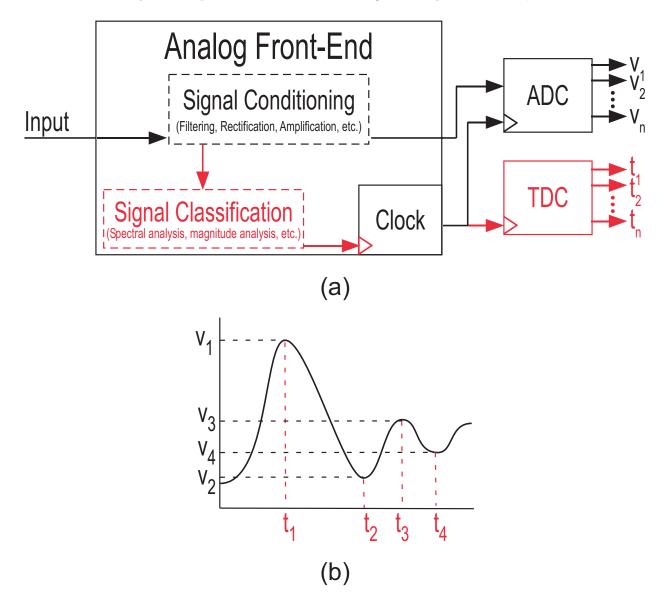

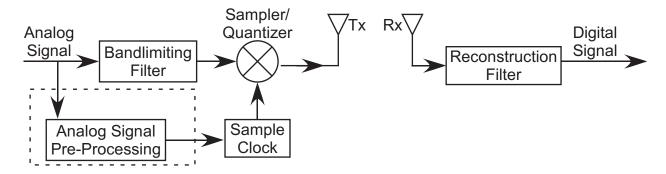

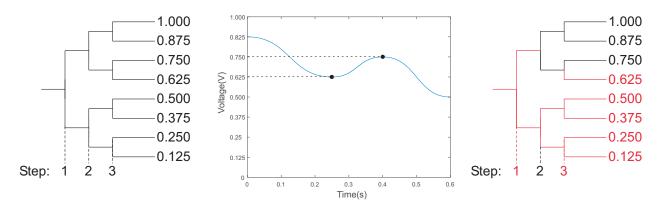

Figure 2.1: (a) A block diagram of a quantization system. The pieces shown in black are common to all quantization systems. The pieces shown in red are unique requirements of asynchronous quantization. The most important distinctions are the explicit time measurement, as well as the signal characteristic-driven clock. (b) A waveform showing example quantization levels. In an asynchronous system, the timing of the samples must be explicitly measured.

# 2.1 Asynchronous/Adaptive Analog-to-Digital Conversion

Besides improving the per-conversion-cycle efficiency of an ADC, the other logical approach to lowering the energy consumption of an ADC is reducing the number of conversions

it performs. Asynchronous ADCs are a class of ADCs which are not clocked at the Nyquist rate, but are instead triggered by some external event – typically some characteristic of the target signal to be converted (Fig. 2.1). These ADCs push against the rate minimum imposed by the Nyquist Rate.

Compressed sampling, for example, is a sparse-signal measurement modality [28, 29] that has been implemented successfully as an asynchronous sampling scheme [30]. Compressed sensing works by creating an array of samples (taken from individual sensors) from a sparse signal. Given that the signal is very sparse, the samples can be represented by a vector of coefficients which are mostly zeros. The sampling rate in this scheme is much smaller than the dimension of the signal being measured, meaning that the quantized array of samples would normally not be sufficient to reconstruct the original signal. However, the additional information that the signal is sparse allows the signal to be reconstructed [28].

Level-crossing ADCs are possibly the most popular type of asynchronous ADCs. The basic idea is that a sample is only converted when the measured signal passes through a bound that would represent a new digital word. By only recording these transitions, periods of relative inactivity are ignored. Ignoring these inactive periods allows energy to be saved through reducing the number of conversions [31]. While this method avoids extraneous conversions during periods of low-activity, it is possible for it to cause oversampling during 'bursty' events. If an event is characterized by a pulse of constant derivative, an electrocardiogram spike for example, it may trigger several threshold crossings. However, at least in the case of constant derivative change, accurate reconstruction could be achieved through the use of only the first and last threshold crossing, making the intermediary crossings extraneous information. Another way to consider this issue, is that as the resolution of the ADC is increased, the frequency bandwidth becomes more limited.

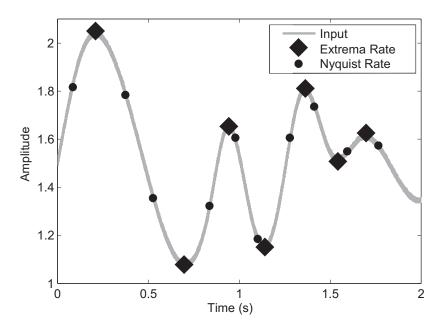

Extrema sampling, otherwise known as peak or min/max sampling, is another implementation of an asynchronous sampling method. Here, only the local minimums and maximums of a signal are sampled. This method is similar to level-crossing sampling in that it adapts itself to the changing spectrum of a signal, but this method leads to fewer sample points. Fewer sample points can mean a loss in signal reconstruction fidelity, but it can also mean a reduction in superfluous samples that may occur in level-crossing sampling when a function

is rapidly changing with a near constant rate of change [32, 24].

## 2.2 Reconfigurable Analog Front Ends

As described in Chapter 1, signal processing in the analog stages is very energy efficient, but carries with it some inherent limitations. Chief among these limitations is the application-specific nature of analog electronics. While an analog front-end might make an excellent conditioning or classification circuit to trigger an asynchronous data converter, it would likely be useful for only a narrow range of applications. For this front-end to be useful in a wide range of applications, particularly for triggering asynchronous data conversion, a certain amount of tunability or reconfigurability is necessary.

The desire to enable reconfigurability in analog electronics has led to the development of a relatively new class of devices, field-programmable analog arrays (FPAAs) [33, 34, 35, 36, 26, 26, 37, 38, 39]. FPAAs are similar to digital field-programmable gate arrays (FPGAs) in that they allow for a system architect to program arbitrary connections of primitives to form larger systems.

FPAA usage varies from trying to solve a single-niche problem, to implementations which try to provide reconfigurability in analog at a level comparable to what FPGAs provide in digital. Ultra focused solutions include an FPAA which is focused on the implementation of a pipeline ADC [40]. In this case, the FPAA allows for both tunable pre-quantization filtering as well as some reconfigurability in the actual quantization stage itself, theoretically enabling the implementation of an entirely different topology – a sigma-delta converter. On the other end of the spectrum is a system that allows reconfigurability at the transistor level [36]. This level of reconfigurability allows a great number of analog designs to be useful, thus making it a useful tool for prototyping or teaching, among other applications.

Somewhere along this spectrum are FPAAs designed for use within energy-constrained applications [26]. These FPAAs implement analog blocks of varying granularity – from single transistor amplifiers up to oscillators and operational amplifiers. This range of granularity strikes a balance between the performance of individual blocks and the reconfigurability of the system as a whole. This variety in available circuitry also allows these systems to focus

on signal classification and event-detection as opposed to simply signal conditioning (e.g., filtering operations). A great deal of the flexibility in both topology and biasing for this and other FPAAs is provided by non-volatile analog memory, otherwise known as floating-gate transistors.

#### 2.2.1 Floating-Gate Transistors

Floating-gate transistors are field-effect transistors characterized by their floating control-gate node. This node has no DC path to ground, and instead relies on capacitive coupling and charge programming to effect the gate potential. These devices are most widely used in digital flash-memory applications, but they have also been shown to be extremely useful in the analog domain. One use of floating-gates is as non-volatile analog memory, in which they are programmed to store a particular charge. By tuning the charge stored on the floating node, they have been used for offset removal in differential pairs [41], threshold definition in flash ADCs [42], or for tuning corner frequencies in filters [43]. The versatility of floating-gate circuits has allowed them to be useful in applications ranging from modeling neurons [44] to measuring cranial impacts caused during collisions in sports [3].

While floating-gate devices are very useful, they are also uniquely challenging to implement. This difficulty largely stems from the fact that the two main sources of programming, Fowler-Nordheim tunneling [45] and hot-electron injection [46], occur with currents on the order of pico-Amperes. This complication is only worsened by the SPICE circuit simulation language's inability to accurately model these device due to their floating-nodes.

## 2.3 Inter-Sample Time Quantization

Unlike traditional ADCs, the asynchronous variety have an unknown and variable amount of time between samples. What is often ignored within the literature, however, is that proper knowledge of this time period is critical for proper reconstruction of the signal [47].

Most of the current literature ignores this timing issue completely [48, 49]. Others utilize a stand-alone data acquisition system to separately monitor the time limits for the sake of prototyping the system [24]. [50] proposes that, instead of explicitly measuring the time

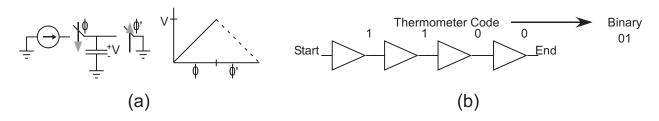

Figure 2.2: (a) A simplified schematic and output of a class-1 TDC. This type of TDC uses a voltage ramp to create a quantity that is proportional to the duration for which it is charged. (b) A simplified schematic and output of a class-2 TDC. This type of TDC uses equal delay units to create a thermometer code which can be converted to binary.

interval of an asynchronous ADC deployed at a WSN node, the time could be interpolated by broadcasting every sample as it is acquired and the base station could measure the time in between samples. This method introduces an entire host of variables involved with the transmission and reception of these signals – making this method very impractical.

A more practical approach would be to use an explicit time to digital converter (TDC). TDCs measure temporal characteristics within a system and convert that quantity to a digital value. TDCs are used in various digital oscilloscopes, they are inherently found in delay-locked loops, and they also appear in positron emission tomography scans (PET scans). Within the context of PET scans, TDCs are used to measure the duration of the annihilation of a positron emitting radioisotope (injected in a subjects body) with an electron. [51] was a sub-nano second TDC developed for the express purpose of use in PET scans.

The class-1 TDCs operate much like an integrating ADC (Fig. 2.2 (a)). In this class, a current source creates a ramping voltage upon a capacitor. This ramp begins at a known voltage and is halted at the end of the period to be measured. The resulting analog voltage is thus proportional to the duration of the asynchronous event and can be converted to a digital word through any traditional ADC technique.

Class-1 TDCs have been utilized in works which require exceptionally low power operation and demand small area [24], but have several severe drawbacks. Like integrating ADCs, class-1 TDCs are not particularly suited for CMOS implementation. It is inherently difficult to build a stable current source that will be reliable in the face of power supply variation or fabrication process variations. This technique also scales poorly as CMOS fabrication processes continue to shrink. Also, an entire ADC unit is required after this initial TDC

stage to convert the analog value to a usable digital word.

The class-2 TDCs (Fig. 2.2 (b)) are most similar to digital delay lines. A start signal is passed to a chain of inverters, buffers, or other generic delay unit. The signal propagates along the line, clocking a flip flop or similar memory element at every node, until a stop signal is received. The result is a thermometer code which is proportional to the duration of the event and can be converted easily to a digital word.

Within class-2 TDCs, certain comparisons can be made to typical ADC design. For instance, the LSB of this circuit is simply the smallest time increment which can be measured – at best this is the smallest delay created by a single delay unit. Another example is instead of defining the dynamic range as the range of analog voltages which can be converted, we can define it as the maximum amount of time which can be measured. In theory, we can then extend the dynamic range to an arbitrary length by extending the delay-line to an arbitrary length. In reality, this technique is limited by non-linearities that either exist in asymmetries within the schematic design or the physical layout. Put another way, eventually the circuit will drift in timing past one least significant bit and some digital correction will be necessary.

Within conventional circuits, TDCs have found a few interesting uses. Time interleaved ADC structures are often used to increase the through-put of slower ADC topologies, but at some point the designer naturally hits a point where process mismatch becomes non-negligible and time-interleaving is no longer feasible. In [52], a TDC was used to automatically detect variation caused by process mismatch and push the resolution of the time-interleaved system past what it could perform at otherwise.

## 2.4 Summary

This chapter has introduced concepts critical to understanding the remainder of this work. These concepts begin by understanding the difference between asynchronous/adaptive conversion systems and synchronous conversion systems. The idea of alleviating the application specific nature of analog prepossessing with reconfigurable analog was then introduced as a mechanism for triggering the event-driven asynchronous conversion. Finally, the concept of inter-sample time quantization was discussed – an issue unique to asynchronous conversion.

## Chapter 3

## A SPICE-Compatible Floating-Gate Macromodel

Despite their usefulness as programmable circuit elements, floating-gate circuit development is hampered by its inability to be modeled in SPICE-compatible environments. The primary challenge in modeling a floating gate FET device is that there is no DC path to the floating node itself – a property which SPICE has difficulty reconciling at compile time. This lack of a DC path makes modeling capacitive coupling onto the node and effecting the charge stored on the floating node impossible without the use of a macromodel. Previous attempts at creating a macromodel have not addressed these issues simultaneously in a manner compatible with AC, DC, and transient analysis. In this chapter, we present a new SPICE-compatible macromodel which includes mechanisms for capacitive coupling onto the floating node as well as mechanisms for programming the charge on the floating node. In addition, this work provides insights into the design and use of floating gates and varies the validity of this model with floating-gate circuits developed over multiple processes.

## 3.1 Floating-Gate Modeling in SPICE

Floating-gate devices are most widely used in digital flash-memory applications, but they have also been shown to be extremely useful in the analog domain. One use of floating-gates is as non-volatile analog memory, in which they are programmed to store a particular charge.

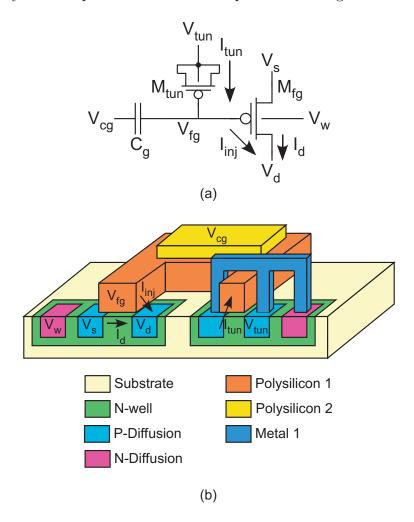

Figure 3.1: The basic structure of a pFET CMOS floating-gate element. (a) Schematic representation of a pFET floating-gate element. Note that the floating node,  $V_{fg}$ , is where charge is stored. It is the lack of a DC path to ground from this node which makes direct SPICE modeling impossible. (b) A model of the layout of a pFET floating-gate element. This layout topology has the advantage of being directly implementable in any double-polysilicon process, without the need for amended fabrication rules.

By tuning the charge stored on the floating node, they have been used in many applications including offset removal in differential pairs [41], threshold definition in flash ADCs [42], or for tuning corner frequencies in filters [43]. The versatility of floating-gate circuits has allowed them to be useful in applications ranging from modeling neurons [44] to measuring cranial impacts caused during collisions in sports [3]. Floating gates have even enabled the creation of field-programmable-analog-arrays, the analog equivalent of digital FPGAs, by providing programmable switches and bias currents [26, 36].

Despite the usefulness of floating-gate devices within a wide variety of applications,

SPICE modeling techniques are incomplete and vary from application to application. The problem with SPICE modeling arises from the unique floating node,  $V_{fg}$  in Fig. 3.1(a), which has no DC path to ground. Without a DC path to ground, SPICE simulations are unable to both set and effect the charge on the node and maintain accurate effects of coupling from explicit and parasitic capacitances. Macromodels have been developed to address these issues, but they address either the charge setting and programming issue [53, 54, 55] or the capacitive coupling issue [56, 57], but never both. While these techniques can be accurate and adequate if applied to specific applications, a macro-model which addresses the complete behavior of a floating-gate would better equip circuit designers to predict the intended and unintended behavior of their systems. In addition, a unified floating-gate model promotes the use and re-use of floating-gate based circuits within other systems.

In this chapter, we will detail a unified macro-model for floating-gate devices which is capable of modeling the DC capacitive coupling characteristics as well as the storage and programming of charge on the floating-node. This work expands and improves upon our previous work [58] by improving the macromodel (more accurate charge modeling equations and adjustments which improves convergence) and by providing better instruction on its implementation as well as better verification for its use across multiple fabrication processes. We will begin by explaining the structure of the floating-gate element in Section 3.2. Next, the theory behind the mechanisms of charge modification and capacitive coupling will be explored in Section 3.3. We will then present the macromodel itself in Section 3.4 before describing empirical and analytical methods of parameter extraction in Section 3.5. Finally, we will provide verification of the static and dynamic characteristics of this model by comparing it to designs fabricated over different fabrication processes in Section 3.6 before concluding in Section 3.7. All simulated data will be compared to real data from devices fabricated in  $0.5\mu$ m and  $0.35\mu$ m standard CMOS processes.

## 3.2 The Floating Gate Structure

Floating-gate elements are most simply characterized as a MOSFET whose gate lacks an explicit resistive path to ground. Instead, a 'control gate' is capacitively coupled onto the

DC isolated node, or 'floating gate' (FG). This FG node stores charge, making it not only useful for digital flash memory, but also for non-volatile reprogrammable analog memory.

Figure 3.1(b) shows the physical layout of a floating gate device. Alternative layouts such as nFET type FG elements, which use double well processes, or stacked capacitor FG elements are realizable, but the demonstrated design can be made in the most common CMOS fabrication processes.

The FG itself is formed through the use of a polysilicon-insulator-polysilicon capacitor. If a double polysilicon process is not available, this structure could still be realized with a MOS capacitor – trading some ease of analog design for some space reduction. When drawing the layout of this particular node, it is best-practice to reduce charge leakage by not creating any connections to metal paths. Instead, it is best to make the connection to the tunneling capacitor via polysilicon, as depicted. The connection of the floating node to nonessential terminals or gratuitous sizing of traces, even within the polysilicon layer, has been reported to cause poor charge retention, or 'leaky' FG nodes – as in the case of [59] where this effect was intentional.

Similar to a standard MOSFET, the channel current of an FG transistor is determined primarily by the potential between the source and gate over top of its channel. What makes the FG transistor unlike a standard MOSFET is the fact that the potential on the gate is determined by both the charge stored on the FG node, as well as any voltages capacitively coupled onto the node. If the charge on the FG is Q and the total capacitance on the FG is CT, then

$$V_{fg} = \frac{Q + C_{cg}V_{cg} + \sum C_x V_x}{C_T} \tag{3.1}$$

where  $C_{cg}$  and  $V_{cg}$  are the drawn capacitance from the FG node to the control node and the voltage placed upon the control node respectively, and  $C_x$  and  $V_x$  are any other drawn or parasitic capcitances to the floating node (e.g. drain-to gate capacitance, source-to-gate capacitance, etc.) and the voltage placed upon them. Typically, the drawn control gate capacitance is much larger than the other capacitances, allowing reasonable approximation with simply the  $C_{cg}$ ,  $V_{cg}$ , and  $C_T$  terms, if computational speed is preferred over accuracy.

Even for the case where we ignore parasitic capacitances and consider only drawn control-

gate capacitances (of which there can be more than one), we can begin to see some interesting properties of FG transistors which can be taken advantage of in the analog domain. The first and most obvious is that the charge placed upon the FG creates a programmable, non-volatile offset. Another way to think about this programmed charge, is to consider it as repositioning the effective threshold voltage (at least from the perspective of a circuit using the floating gate as a black-box). Another advantage is that, particularly with multiple control gates, the FG transistor can be used as a multiple input transistor [60], possibly also taking advantage of the capacitive division to create inputs scaled to particular ratios [61].

## 3.3 Reactions of the Floating Node

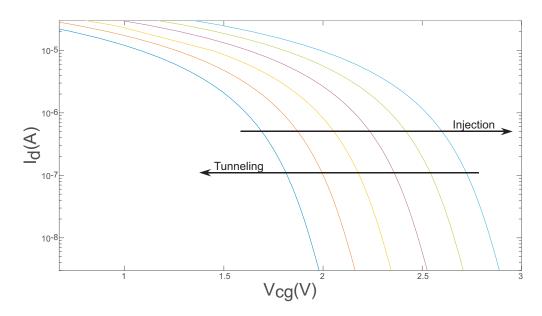

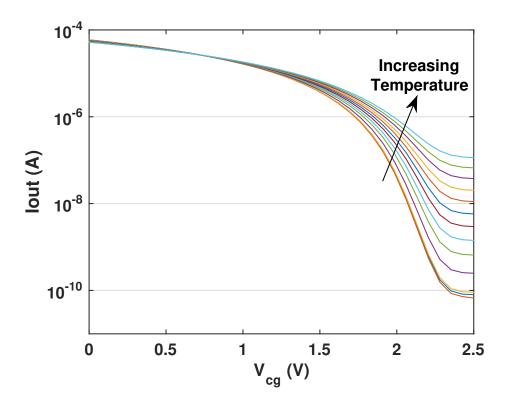

Figure 3.2: The use of Folwer-Norheim tunneling and hot-electron injection allow circuit designers to program FG elements with specific charge – in effect, the threshold voltage can be 'tuned.'

The ability to effect and predict the charge on the floating-node is of paramount importance for the usage of FG devices. Charge is typically programmed through Fowler-Nordheim tunneling and hot-electron injection (Fig. 3.2). For a model to be accurate, it must also account for methods of changing the charge which are typically unintentional or undesired, specifically leakage and a previously un-discussed phenomena we call reverse-tunneling. In this section, we will describe the effects of these mechanisms and the mathematical equations which model them.

#### 3.3.1 Tunneling

Fowler-Nordheim (FN) tunneling is the primary method by which charge is removed from the floating node. FN tunneling can be used for writing or erasure in individual FG elements. For larger arrays of FG elements, it isn't normally applied to individual elements, instead it is most commonly used for global erasure. The reason is due to the relatively high voltages required to induce the phenomena. This phenomena occurs when high voltages are used to distort the energy band of the oxide, allowing electrons to pass through. Generating this high voltage for most systems is a source of inefficiency, particularly if it must be done on a per/write basis.

FN tunneling can be performed on FG nodes made of pFET or nFET transistors. However, we recommend the use of pFet devices for a few reasons. The first reason is that, to protect against reverse breakdown, tunneling junctions are normally isolated by placing them inside a well. Therefore, the use of an nFET necessitates a double-well process. Other reasons are that we have found the pFET tunneling junctions to produce higher levels of current, enabling faster erasure. Also, their erasure time is not voltage dependent. We recommend sizing this tunneling junctions at about 3.1 percent of the total capacitance (drawn and parasitic) of the FG element to maximize current draw while minimizing voltage coupling and oxide degradation. Further elucidation and analysis of these points can be found in [62].

The current induced by FN tunneling can accurately be modeled by the equation:

$$I_{tun} = \alpha \left(\frac{C_{tun}}{\gamma}\right) exp\left[-\frac{\beta t_{ox}}{1 - (Ctun/C_T)V_{tun} - V_{fq,e}}\right]$$

(3.2)

where  $C_{tun}$  is the capacitance of the tunneling junction,  $C_T$  is the total explicit and implicit capacitance seen by the floating node,  $t_{ox}$  is the thickness of the oxide barrier,  $V_{ox}$  is the voltage across the barrier,  $\gamma$  is the unit capacitance  $(aF/m^2)$  of  $C_{tun}$ , and  $\alpha$   $\beta$  are constants related to the fabrication process and junction type [45, 63]. By curve-fitting FN tunneling data from multiple chips and processes, we have found that values of 185.5  $A/m^2$  and 32.8

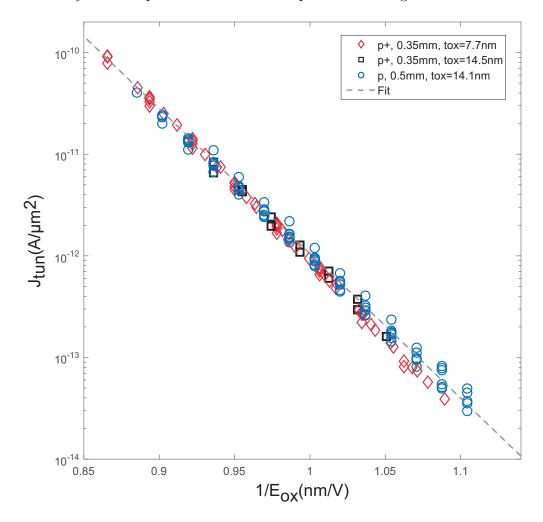

Figure 3.3: Data taken from multiple processes were used to derive the constants used in the calculation of tunneling current.

V/nm, for  $\alpha$  and  $\beta$  respectively, accurately model the current induced by injection across a range of fabricated chips [62] (Fig. 3.3).

## 3.3.2 Injection

Hot-electron injection is the method by which charge is added to the FG element. Hotelectron injection occurs when there is a channel current flowing through the transistor and a drain-to-source potential high enough to cause impact ionization at the drain [46]. A portion of these ionized carriers gain enough energy to pass through the oxide barrier and become trapped on the floating gate. The resultant injection current can be approximated, in the

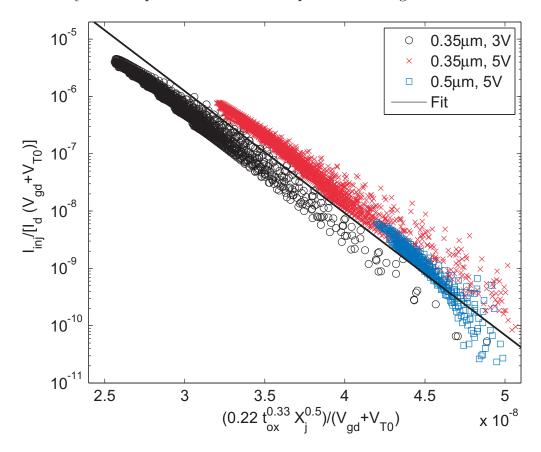

Figure 3.4: Calculated injection rates from this experiment were normalized across processes to find the constants we use in our injection current calculation.

subthreshold region, as:

Brandon M. Kelly

$$I_{inj} = \gamma * I_d * (V_{fg} - V_d + V_t) * exp[-\frac{\gamma \delta}{(V_{fg} - V_d + V_t)}]$$

(3.3)

where  $I_d$  is the channel current,  $V_{fg}$ ,  $V_d$ , and  $V_t$  are the floating gate, drain, and threshold voltages, and  $\gamma$   $\delta$  are device-dependent fits found to be of value 3 and 4.9e8, respectively. [64]. This current can be modeled as flowing from the floating-gate to the drain, resulting in a lowering of the floating-gate potential.

Injection is typically a more practical means of programming compared to tunneling, do to the lower required potential ( $V_{sd} > 3.5 \text{V}$  vs  $V_{tun} > 8 \text{V}$  for  $0.35 \mu \text{m}$  CMOS process). There are generally two categories of injection programming methods: pulsed and continuous time. In pulsed based programming, short pulses of injection are induced with the value of the floating node measured after each pulse [65, 66]. While this method is very accurate, it is also very slow due to the need for read cycles after every pulse. Continuous-time programming,

conversely, implements a feedback structure to stop programming of the FG element once it reaches the desired value. Generally, continuous-time programming is quicker and requires less peripheral circuitry [67].

#### 3.3.3 Reverse-Tunneling

Figure 3.5: Demonstration of the effect of reverse tunneling. In this test, the source of the FG element was held at 6.5 volts, and the FG node was programmed with sufficient charge so that it would be well above the drain. With the FG node held high, we would expect there to be no channel current and consequently no injection current. However, we can see an injection-like effect occurring over a very long time scale. We attribute this to reverse tunneling.

Reverse tunneling is a yet unstudied phenomena that resembles injection at first approximation. This phenomena occurs when the potential of the floating node is sufficiently higher than that placed on the drain node, causing charge to tunnel from the floating node to the drain node. As can be seen in Fig. 3.5, the process is fairly slow, due to the very slight magnitude of current involved. We have found that scaling the Fowler-Nordheim tunneling

equation, Eq. 3.2, to one half of a percent is sufficient for accurate modeling.

In practice, this may occur during programming of an array of FG elements. After writing a value to a FG node using injection, it is common practice to raise the potential of the control gate before moving onto the next FG element, with the intention of completely shutting off the channel current to avoid further programming. However, doing so has the potential to raise the FG node to a high enough voltage to induce reverse tunneling. If this effect is not properly understood and modeled, it may be mistaken for some non-ideality such as charge leakage or some unintended reprogramming through injection.

#### 3.3.4 Charge Leakage

The term 'charge leakage' is used to describe the effect that a, usually unintentional, DC path to the floating node can have. This DC path is usually formed one of two ways. The first and most common is through ill-advised layout practices, contrary to those suggested in Sec 3.2.

The second possible cause of a DC path is oxide degradation. The primary methods of charge manipulation on an FG device, namely injection and tunneling, are inherently destructive processes which have a slight, degrading effect upon the oxide. However, it has been shown in both the digital and analog domains that excellent charge retention can be maintained with loss less than one percent over a decade of use [68]. Thus, for the majority of applications, circuit designers can rely on consistent performance from FG devices, provided that some basic best practices were followed in the layout stage.

#### 3.4 Floating-Gate Macromodel

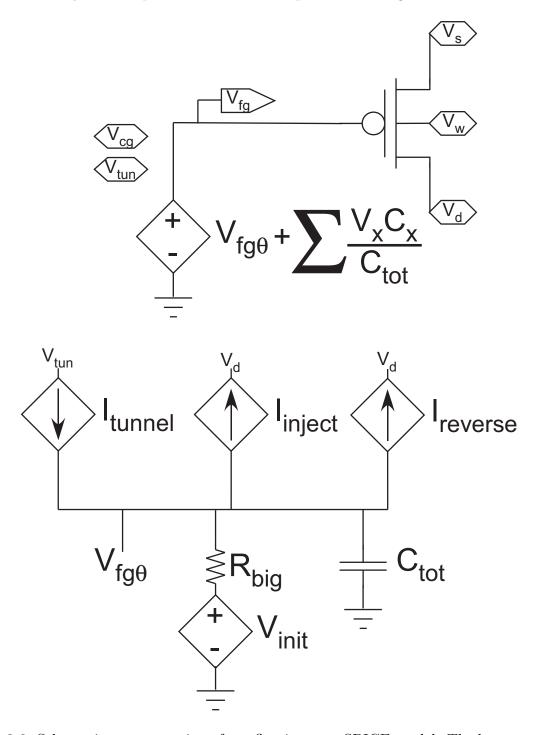

In modeling the floating gate (FG) transistor, as seen in Fig. 3.6, the three details addressed by our model are: modeling the charge stored on the floating node, modeling the means by which charge may be programmed, and modeling the effects of capacitive coupling on the floating node. While previous macromodels have been able to model these effects individually [53, 54, 55, 56, 57], ours is capable of modeling all of these effects in tandem.

The simplest part of the model to understand is the capacitive coupling. Changing the

Figure 3.6: Schematic representation of our floating-gate SPICE model. The bottom portion reflects charge programming techniques as well as non-idealities which may effect charge. This node is combined with the effects of capacitive coupling onto the gate of the transistor in the upper portion of the schematic.

voltage on the floating node through capacitive coupling is achieved through a dependent source attached directly to the floating node.

The dependent source should sum all capacitively coupled potentials individually, through the rule of capacitive division. A complete model of this should include the contributions of all drawn and parasitic capacitance (e.g., drain-to-gate capacitance, source-to-gate capacitance, etc.) but, in practice, the drawn coupling capacitance tends to dominate. Therefore, if computational speed were desired, as in the case of simulating a large array of FG-enabled circuits, one could include only the drawn capacitance and achieve reasonable accuracy.

The other term added through the dependent source is the voltage seen at the 'dummy' node  $V_{fg\theta}$ . This node is used to both set the initial voltage as well as to model the effects of charge programming. The initial voltage is set by an independent source attached to  $V_{fg\theta}$  through a very large resistance. This large resistance allows  $V_{fg\theta}$  to reach the desired value prior to a transient simulation, when the SPICE simulator is searching for a stable DC operating point, but then effectively separates the voltage source's effect during simulation. One caveat to this operation is that one must remember that the capacitively coupled voltages are also being added in during the search for a starting DC operating point. Therefore, the equation to set this initial value should be

$$V_{init} = V_{des} - \frac{\sum C_x V_x}{C_T} \tag{3.4}$$

where  $V_{des}$  is the desired initial floating gate voltages. Alternatively, if one would rather think of the programming of a floating gate as a shifting of threshold voltages, then the voltage source should be set to

$$V_{init} = V_{Tact} - V_{Tdes} \frac{C_{cg} V_{cg}}{C_T} - \frac{\sum C_x V_x}{C_T}$$

(3.5)

where  $V_{Tdes}$  is the desired threshold voltage and  $V_{Tact}$  is the actual, intrinsic, threshold voltage.

Also seen at the dummy node are current sources and a capacitor. The capacitor, set at the value of the total capacitance seen by the FG node, and the current sources create the voltage changes that charge reprogramming would have on the FG node. Included in the illustration are sources which model injection, tunneling, and reverse tunneling (see Sec. 3.3 for specific equations). In addition to these effects, other charge reprogramming effects could

be added to model new behaviors which may arise from newer processes or particularly odd topologies.

#### 3.4.1 Verilog-A Implementation

In certain cases, it may be beneficial to use a SPICE language which does not support the use of arbitrary voltage or current sources. In these cases, it is necessary to model the injection, tunneling, and other charge programming currents with a high-level programming language. The following is the implementation of the tunneling current in Verilog-A:

```

'include "constants.vams"

'include "disciplines.vams"

module TunnelingMod(Vtun, Vfg, Vfg0, Test);

inout Vtun, Vfg, Vfg0, Test;

electrical Vtun, Vfg, Vfg0, Test;

real tun_val;

parameter real tdelay=0 from [0:inf);

parameter real trise=2n from [0:inf);

parameter real tfall=2n from [0:inf);

parameter aT=185.5e12;

parameter bT=32.8e9;

parameter Width=2e-6;

parameter Length=1e-6;

parameter tox=7.754e-9;

analog begin

```

```

@(initial_step)

begin

tun_val=0;

end

if(analysis("ic"))

tun_val=0;

else begin

if(V(Vtun, Vfg) > 8)

tun_val=aT*Width*Length*exp(-tox*bT...

/(V(Vtun,Vfg)));

else

tun_val=0;

end

I(Vtun,Vfg0) <+ transition(tun_val, tdelay, trise,...</pre>

tfall);

V(Test) <+ transition(tun_val, tdelay, trise, tfall);</pre>

end

endmodule

```

Likewise it is possible to model injection in Verilog-A. Implementation of this equation in Verilog-A takes the following form:

```

'include "constants.vams"

'include "disciplines.vams"

module InjectionMod(Vd,Vs,Vfg0,Vfg,Vcur,Test);

inout Vd,Vs,Vfg,Vfg0,Vcur,Test;

```

```

electrical Vd, Vs, Vfg, Vfg0, Vcur, Test;

real inj_val;

real alpha;

real velLen;

real beta;

parameter real tdelay=0 from [0:inf);

parameter real trise=2n from [0:inf);

parameter real tfall=2n from [0:inf);

parameter gamma=3;

parameter delta=4.9e8;

parameter xj=3e-7;

parameter tox=7.754e-9;

parameter Vt=0.6915;

analog begin

alpha=gamma;

velLen=0.22*pow(tox,0.333)*pow(xj,0.5);

beta=delta*velLen;

@(initial_step)

begin

inj_val=0;

end

if(analysis("ic"))

inj_val=0;

```

```

else begin

if(V(Vs,Vd)>3.5)

inj_val=(alpha*V(Vcur)*V(Vfg,Vd)+Vt)...

*exp(-beta/(V(Vfg,Vd)+Vt));

else

inj_val=0;

end

I(Vfg0,Vd) <+ transition(inj_val, tdelay, trise,...

tfall);

V(Test) <+ transition(inj_val, tdelay, trise, tfall);

end

endmodule</pre>

```

In both cases, an important consideration is determining a pre-transient analysis, or DC, operating point for the charge programming currents. The most straight-forward approach to this consideration, is to initialize them to a value of zero. Almost all other approaches will cause the simulator to assume that, for example, the floating-gate has been injecting indefinitely prior to the transient analysis. This faulty assumption will usually result in either a simulation failure or an erroneous result.

In order to set the current sources which model charge reprogramming, certain values from the target CMOS library must be explicitly included. These include threshold voltage, oxide thickness, and junction depth. For complete agreement with fabricated results, these values may need to be 'tuned' to match the actual values of the fabricated device (as described in Sec. 3.5).

#### 3.5 Tuning the Floating-Gate Model

The first step in implementing the floating-gate macromodel is tuning the model to fit the fabricated device. The process amounts to finding the threshold voltage, oxide thickness, and junction depth through the foundry reports available for individual fabrications. These parameters, along with the multi-process parameters presented in Sec. 3.3, can be used to model injection and tunneling currents.

The other necessary component to be analytically derived are the drawn and parasitic capacitances. The coupling capacitance will be by far the largest of these, and is therefore the most crucial to calculate accurately. Foundry reports on the overlap capacitance and area between polysilicon layers can be used to derive this value. Parasitic capacitances can be estimated by the width of the transistor and the reported value of overlap capacitance.

Beyond using foundry reported values, further refinements can be made to tune the model to a given process or even to a specific fabrication run. This section will detail how we characterized the charge programming effects as well as how we tuned the model for specific ICs.

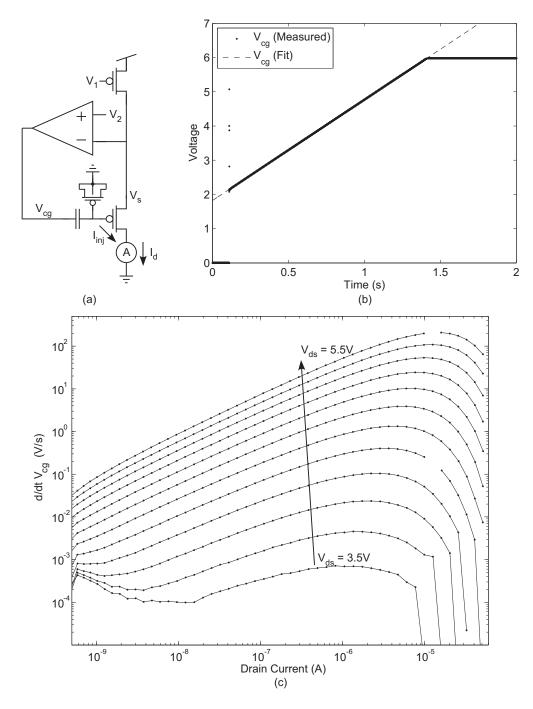

#### 3.5.1 Calculation of Injection and Tunneling Constants

Calculations of the tunneling and injection constants, provided in Sec. 3.3, were made on data taken from multiple processes. These calculations were made by data taken from the circuit in Fig. 3.7. This circuit provides a feedback loop, which was used to measure the effects of both tunneling and injection. The basic operation of the circuit consists of inducing the charge programming effect (i.e., tunneling or injection) and observing the feedback loop's effect on the control-gate while also monitoring the channel current. Injection can be induced with a sufficiently high drain-to-source voltage while tunneling can be induced with a sufficiently high tunneling voltage. The feed-back loop will then cause the control gate to change to compensate for the changing voltage on the floating-node. This effective slope in control gate voltage is then proportional to the injection/tunneling current by a factor of  $C_{ca}$ .

Figure 3.7: Demonstration of acquisition of injection data. (a) This continuous-time programming circuit was used to inject or tunnel the FG element at a set source potential and channel current value. (b) The results of one injection programming. Here we can see the measured  $V_{cg}$  raising at a constant rate to compensate for the lowering of the floating node potential through injection. Measurement of the slope, along with knowledge of the coupling capacitance from the control gate, allows us to calculate the value of injection for this single value of channel current and source voltage. (c) The aggregate of multiple injection programmings for many channel currents and source potentials.

#### 3.5.2 Fine-Tuning the Model for Fabricated Devices

Using the device values found in fabrication-specific foundry reports and the charge programming constants presented in Sec. 3.3 will provide reasonably accurate results, but these results can be refined further for individually fabricated ICs.

For the floating-gate amplifier presented in Sec. 3.6, the simulation model was tuned to match the actual data taken from the circuit. This post-fabrication tuning was achieved by minimizing the error between the simulated data and the actual data in MATLAB. MATLAB was used to control the SPICE simulation of the floating-gate amplifier, and was allowed to tune the values of the coupling capacitance, oxide thickness, junction depth, tunneling voltage, and source voltage. MATLAB was then instructed to tune these parameters until it minimized the error, using the simplex search method presented in [69]. For our example application, we were able to minimize this error with less than 5% change to the voltages and less than 1% change to the device properties.

#### 3.6 Comparison of Model to Fabricated Designs

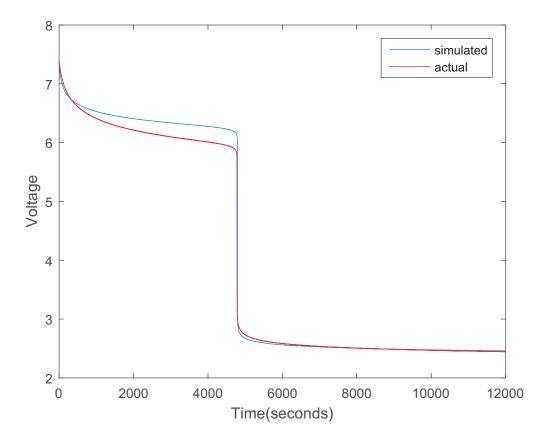

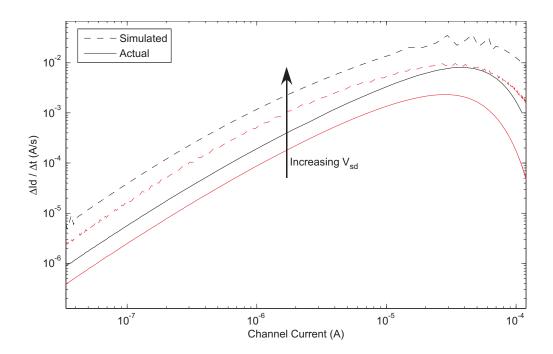

Figure 3.8: Simulated and measured data from a pulse-based injection programming scheme. The source to drain voltages used were 7.5 and 8 volts.

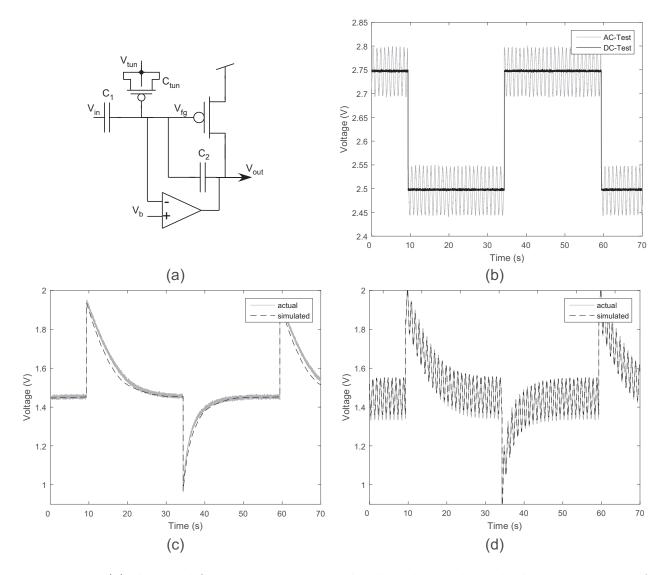

Figure 3.9: (a) The amplifier autozeroes to the level set by  $V_b$  through the constant use of injection and tunneling. The resultant waveform is an amplified version of the input, with the DC component tuned out. (b) The inputs used in our tests of the FG amplifier. (c - D) The fabricated and simulated results of the DC and AC tests. These demonstrate good agreement between the injection and tunneling currents of the fabricated and simulated device.

In this section we will demonstrate both the accuracy as well as the versatility of our macro-model. Data simulated within a SPICE-compatible environment will be compared to data taken from circuits fabricated in a  $0.5\mu m$  process.

#### 3.6.1 Static Programming