Graduate Theses, Dissertations, and Problem Reports

2001

## CMOS fingerprint sensor electrostatic modeling

Praveen Kumar Soora West Virginia University

Follow this and additional works at: https://researchrepository.wvu.edu/etd

#### **Recommended Citation**

Soora, Praveen Kumar, "CMOS fingerprint sensor electrostatic modeling" (2001). *Graduate Theses, Dissertations, and Problem Reports.* 1174. https://researchrepository.wvu.edu/etd/1174

This Thesis is protected by copyright and/or related rights. It has been brought to you by the The Research Repository @ WVU with permission from the rights-holder(s). You are free to use this Thesis in any way that is permitted by the copyright and related rights legislation that applies to your use. For other uses you must obtain permission from the rights-holder(s) directly, unless additional rights are indicated by a Creative Commons license in the record and/ or on the work itself. This Thesis has been accepted for inclusion in WVU Graduate Theses, Dissertations, and Problem Reports collection by an authorized administrator of The Research Repository @ WVU. For more information, please contact researchrepository@mail.wvu.edu.

## **CMOS Fingerprint Sensor Electrostatic Modeling**

Praveen K. Soora

Thesis submitted to the College of Engineering and Mineral Resources at West Virginia University in partial fulfillment of the requirements for the degree of

> Master of Science in Electrical Engineering

Lawrence A. Hornak Ph.D., Chair Biswajit A. Das Ph.D. Stephanie C. Schuckers Ph.D.

**Department of Computer Science and Electrical Engineering**

Morgantown, West Virginia 2000

Keywords: Biometrics, Fingerprint, CMOS Sensor, Parasitic Capacitance Copyright 2000 Praveen K. Soora

## ABSTRACT

## **CMOS Fingerprint Sensor Electrostatic Modeling**

#### **Praveen Soora**

The use of Biometrics in personal identification is an important emerging technology in modern electronic society. Fingerprints are one of the most popular biometric technologies, currently used in majority of biometric applications. In recent years, solid-state capacitive fingerprint sensors which image fingerprints using Silicon CMOS Technology are gaining much acceptance in the market. This research work is carried out to quantify and explore approaches for achieving improved sensitivity of the capacitive imaging process through reduction of parasitic capacitances and sensor cell scaling for future generation devices. Evaluation of sensor cell and array geometries was completed using a commercial 2-D electrostatic field solver. The modeling activities performed include analysis of sensor cell and sensor plate size, their relationships, evaluation of ESD ring coupling, and exploration of cell and array layout approaches for achieving reduced parasitic capacitance.

### **Sponsoring Agency: Veridicom Inc.,** Santa Clara, CA.

#### **Committee:**

Dr. Lawrence Hornak, Chair

Dr. Biswajit Das

Dr. Stephanie Schuckers

## **ACKNOWLDEGEMENT**

I would like to express my sincere gratitude and thanks to my advisor Dr. Lawrence Hornak for providing valuable advice, guidance and encouragement throughout this research work. As my committee chairman his patience, suggestions and reviews certainly made the completion of this thesis possible. I was fortunate to have him as my advisor and as a teacher in the classroom.

I would like to extend my thanks to my committee members Dr. Biswajit Das and Dr. Stephanie Schuckers for their generous time and kind co-operation.

The encouragement and assistance of fellow research students in my lab is greatly appreciated. My heartfelt thanks to my friends for their constant support and encouragement.

Financial support for this research was provided by Veridicom Inc., Santa Clara, CA. Their support is very much appreciated.

Last but not least, my special thanks to my parents without whose love and blessings none of this would have been possible. I would also like to thank my brother Ravi for his encouragement throughout my education. Finally, I wish to thank my sisters for their love and support.

## Dedication

This research work is dedicated to my father the best teacher in my life. Though he passed away 10 years back, I always feel he is still with our family and supports me whenever I need him.

# **List of Contents**

| 1. | Introduction            |                                            |                                                |    |  |

|----|-------------------------|--------------------------------------------|------------------------------------------------|----|--|

|    | 1.1                     | Biome                                      | etrics                                         | 1  |  |

|    |                         | 1.1.1                                      | Personal Identification Systems                | 1  |  |

|    |                         | 1.1.2                                      | Biometric Technologies                         | 3  |  |

|    |                         | 1.1.3                                      | Applications                                   | 5  |  |

|    | 1.2                     | of the art in Biome tric Fingerprint Model | 6                                              |    |  |

|    |                         | Finger print and its Verification          | 6                                              |    |  |

|    |                         | 1.2.2                                      | Principle of fingerprint authentication system | 8  |  |

|    |                         | 1.2.3                                      | Various image sensing devices                  | 9  |  |

|    | 1.3                     | S Review                                   | 11                                             |    |  |

|    |                         | 1.3.1                                      | Complementary MOS transistor                   | 11 |  |

|    |                         | 1.3.2                                      | CMOS process flow and Planarization            | 12 |  |

|    | 1.4                     | citive Fingerprint Scanning Device         | 13                                             |    |  |

|    |                         | 1.4.1                                      | The Veridicom Sensor Cell                      | 14 |  |

|    |                         | 1.4.2                                      | Parasitic Capacitance                          | 18 |  |

|    | 1.5                     | rch Overview                               | 19                                             |    |  |

|    |                         |                                            |                                                |    |  |

| 2. | Simulation and Software |                                            |                                                |    |  |

|    | 2.1                     | Softwa                                     | are Tool                                       | 22 |  |

|    | 2.2                     | Electr                                     | ostatic Field Simulation                       | 23 |  |

|    |                         | 2.2.1                                      | Field Equations                                | 23 |  |

|    | 4                       | 2.2.2                                      | Capacitance                                    | 24 |  |

|    | 4                       | 2.2.3                                      | Capacitance Matrix                             | 25 |  |

|    | 4                       | 2.2.4                                      | Computing Capacitance                          | 27 |  |

|    |                         |                                            |                                                |    |  |

| 3. | Mo                      | escription and Simulation Results          | 29                                             |    |  |

|    | 3.1                     | meters and Materials                       | 31                                             |    |  |

|    |                         | 3.1.1                                      | Parameters Used                                | 31 |  |

|    | •                       | 3.1.2                                      | Materials Assigned                             | 33 |  |

| 3.2 Vii            | 3.2 Virtual Test Objects                                           |    |  |  |  |

|--------------------|--------------------------------------------------------------------|----|--|--|--|

| 3.2.               | 1 Rectangular Block                                                | 35 |  |  |  |

| 3.2.               | 2 Trapezoid Block                                                  | 35 |  |  |  |

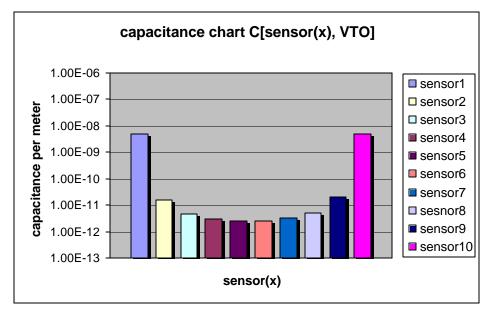

| 3.3 Sen            | sor Model Study                                                    | 36 |  |  |  |

| 3.3.               | 1 Sensor Plate Size Study                                          | 37 |  |  |  |

| 3.3.               | 2 Sensor Cell Size Study                                           | 39 |  |  |  |

| 3.4 Sim            | 3.4 Simulating With Virtual Test Objects                           |    |  |  |  |

| 3.4                | 1 Testing the Model with Trapezoid Object                          | 42 |  |  |  |

| 3.4                | 2 Static Mode                                                      | 42 |  |  |  |

| 3.4                | 3 Swipe Mode                                                       | 46 |  |  |  |

| 3.4                | 4 Vertical Sensitivity                                             | 50 |  |  |  |

| 3.5 Em             | 3.5 Embedding the Sensor Model                                     |    |  |  |  |

| 3.6 We             | ll Structure                                                       | 54 |  |  |  |

| 3.6.               | 1 Theoretical Expectations                                         | 55 |  |  |  |

| 3.6.               | 2 Testing the model and Analyzing the results                      | 56 |  |  |  |

| 3.6.               | 3 Approach suggested                                               | 61 |  |  |  |

| 3.7 ESI            | 3.7 ESD Ring                                                       |    |  |  |  |

| 3.7.               | 1 Controlling the ESD                                              | 61 |  |  |  |

| 3.7.               | 2 ESD Grounded Grid                                                | 62 |  |  |  |

| 3.7.               | 3 Effect of ESD grid on the model                                  | 62 |  |  |  |

| 3.8 Mix            | xed Array Approach                                                 | 66 |  |  |  |

| 3.8                | 1 Linear Array                                                     | 67 |  |  |  |

| 3.8.               | 2 Full Shield Array                                                | 72 |  |  |  |

| 3.9 Ada            | aptive Arrays                                                      | 78 |  |  |  |

| 4 Conclusio        | ons & Future work                                                  | 84 |  |  |  |

| Bibliography       | bliography                                                         |    |  |  |  |

| Appendix A:        | ppendix A: Specification of solid state FPS 100 fingerprint sensor |    |  |  |  |

| <b>Appendix B:</b> | ppendix B: Pictures of specific simulation window geometries       |    |  |  |  |

# List of Figures

| Fig 1.1 Architecture of typical biometric identification system2                          |

|-------------------------------------------------------------------------------------------|

| Fig 1.2 Finger print which shows ending and bifurcation7                                  |

| Fig 1.3 Extracting features of finger print minutiae[9]7                                  |

| Fig1.4 CMOS device cross section11                                                        |

| Fig1.5 The deposition process of various layers on Si substrate in CMOS fabrication12     |

| Fig 1.6 Typical capacitive sensor design14                                                |

| Fig 1.7 Block diagram of the chip15                                                       |

| Fig 1.8 Individual sensor cell with Sample and Hold Logic16                               |

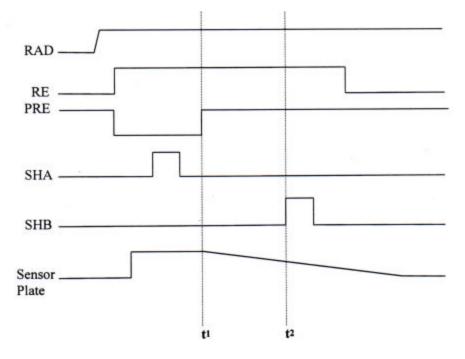

| Fig 1.9 Sensor row access timing diagram 16                                               |

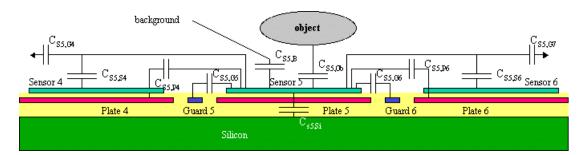

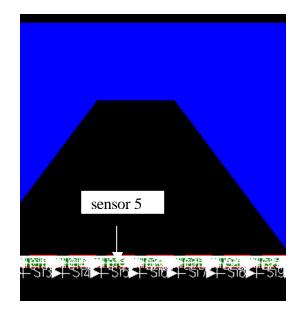

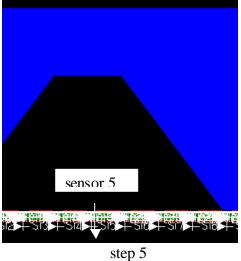

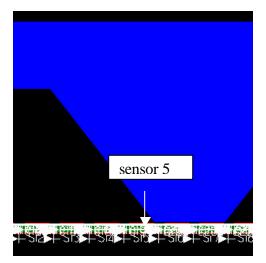

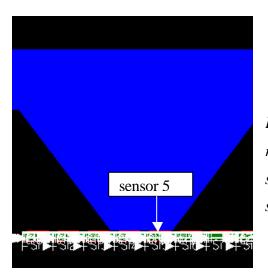

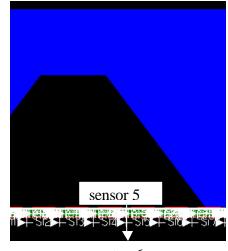

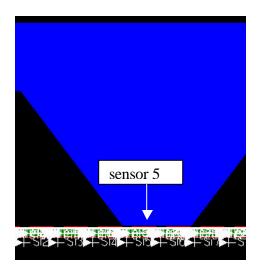

| Fig 1.10 Various capacitances involved for sensor 5 in the sensor geometry setup18        |

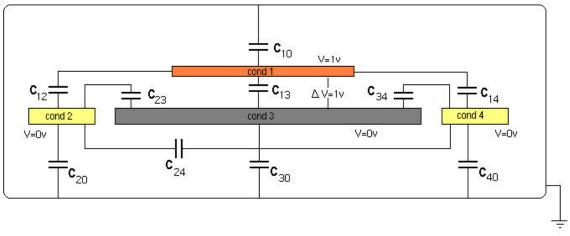

| Fig 2.1 Capacitances between objects26                                                    |

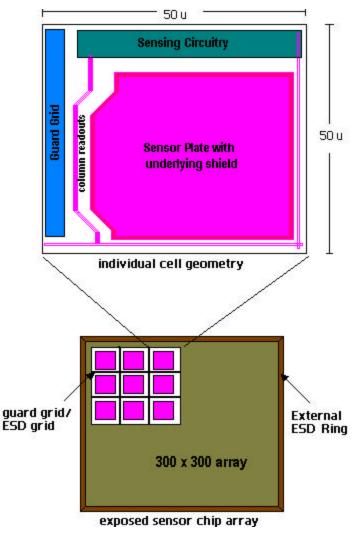

| Fig 3.1 Complete sensor array with enlarged individual cell geometry29                    |

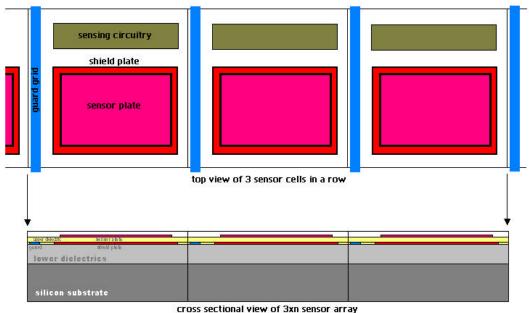

| Fig 3.2 Top and cross sectional view of one partial row of sensor chip 30                 |

| Fig 3.3 The various elements and their assigned materials in a sensor cell31              |

| Fig 3.4 Rectangular Test Object on the sensor model of cell size 50 micrometers35         |

| Fig 3.5 Rectangular Test Object on the sensor model of cell size 200 micrometers 35       |

| Fig 3.6 Trapezoid test object on the sensor model of cell size 200 micrometers 36         |

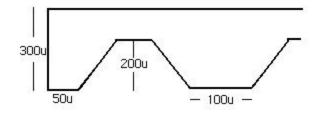

| Fig 3.7 A piece of trapezoid and its internal dimensions 36                               |

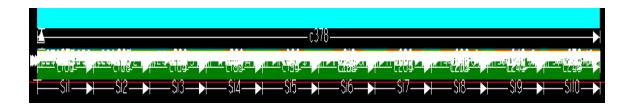

| Fig 3.8 Sensor model, consisting of 10 cells, a 1-D array with rectangular test object 36 |

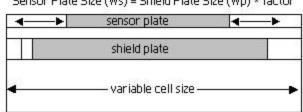

| Fig 3.9 A sensor cell showing how cell size and senor plate size can be varied37          |

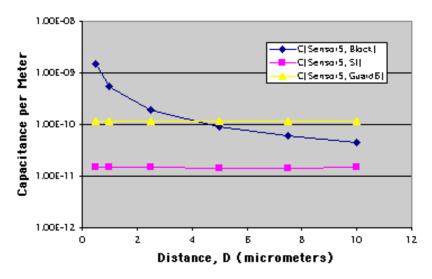

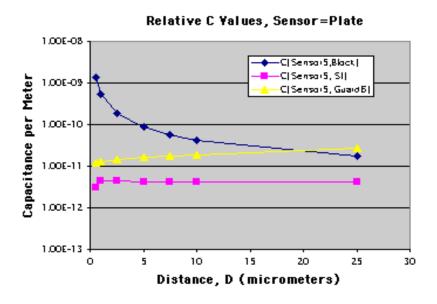

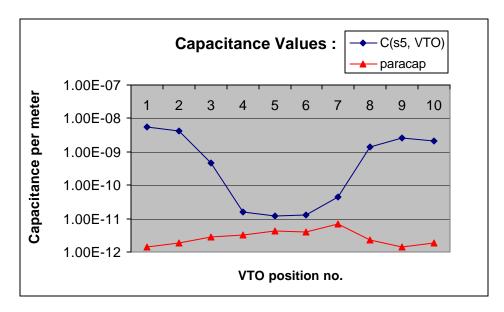

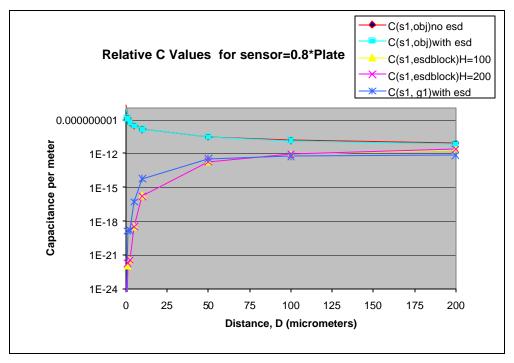

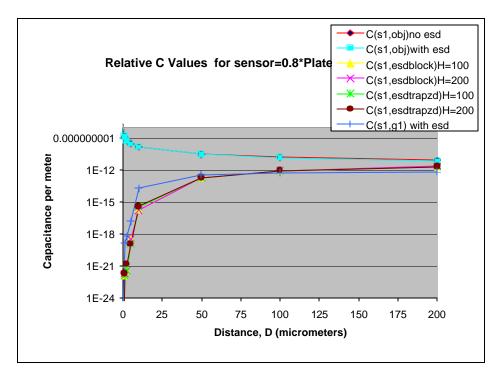

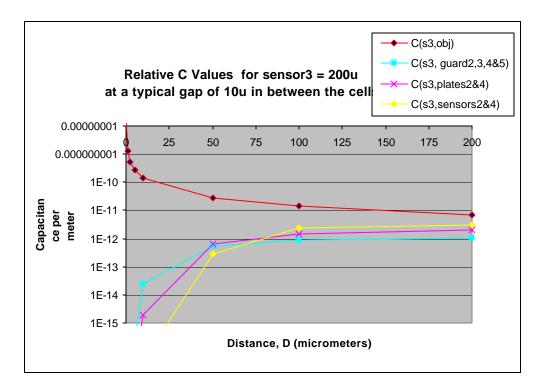

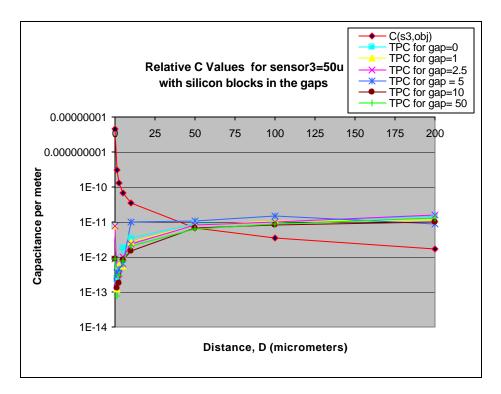

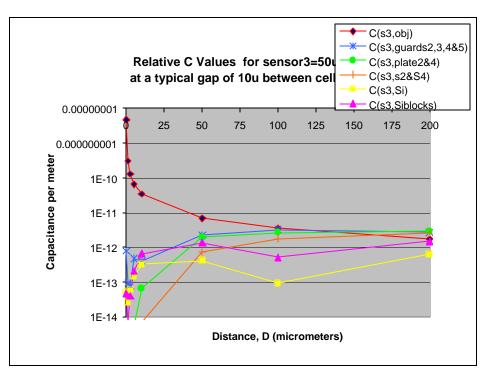

| Fig 3.10 Plot showing typical capacitances with sensor factor =1.137                      |

| Fig 3.11 Plot showing typical capacitances with sensor factor =1.0 38                     |

| Fig 3.12 Plot showing typical capacitances with sensor factor =0.8 38                     |

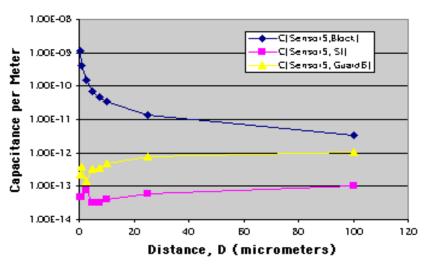

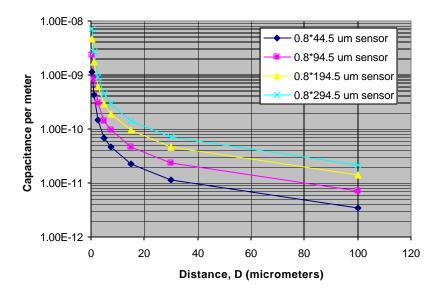

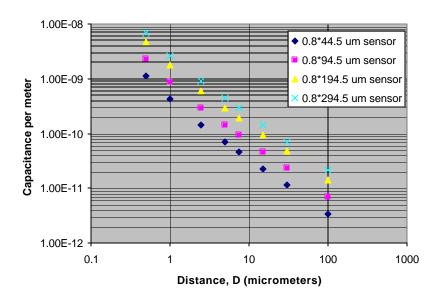

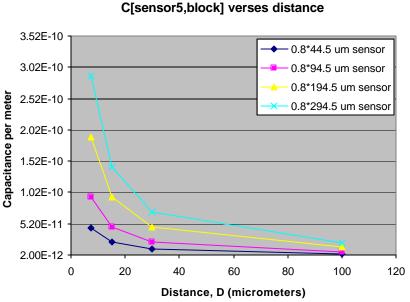

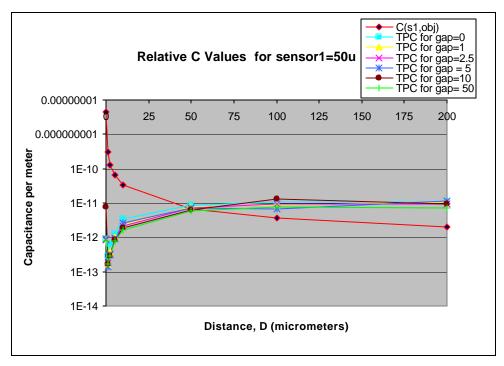

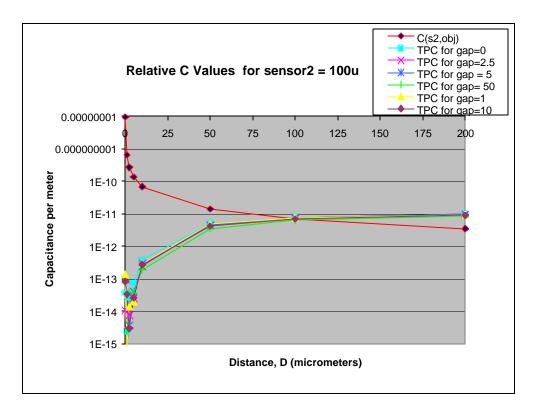

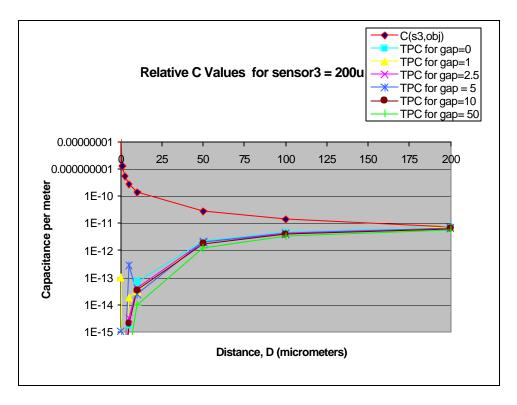

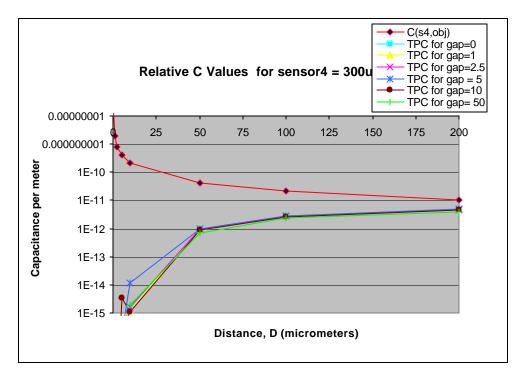

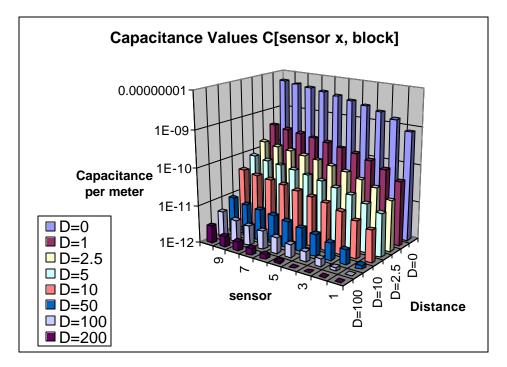

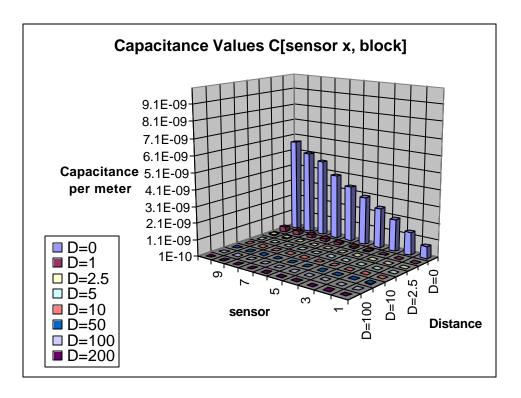

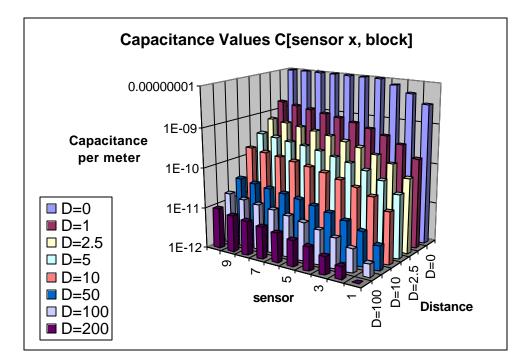

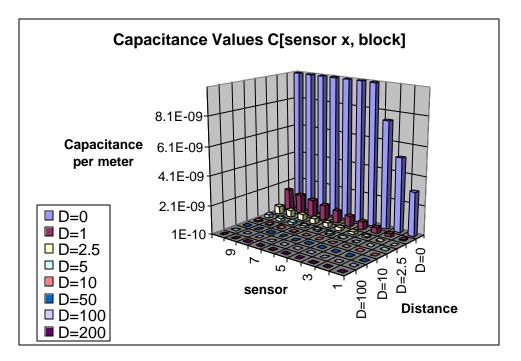

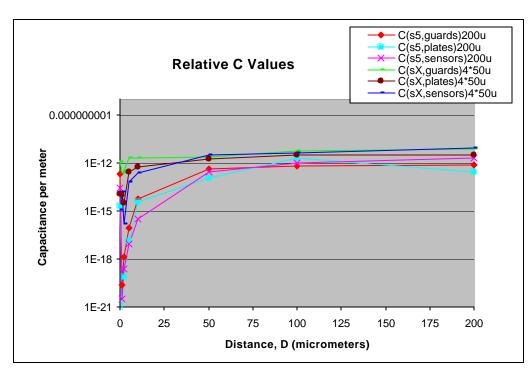

| Fig 3.13 Linear plot of sensor to object capacitance with different cell sizes 40         |

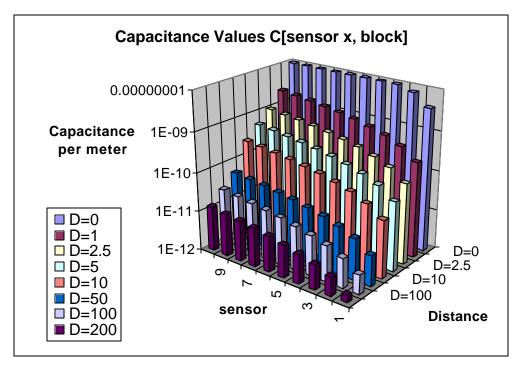

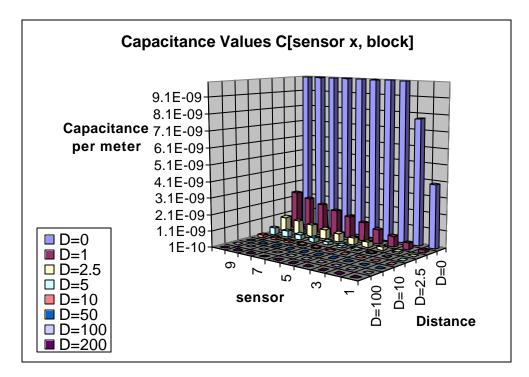

| Fig 3.14 Logarithmic plot of sensor to object capacitance with different cell sizes 40    |

| Fig 3.15 Expanded linear plot of different sensor to object capacitance values41          |

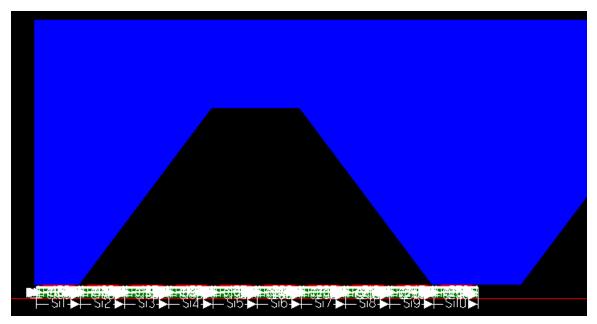

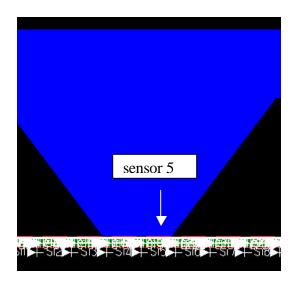

| Fig 3.16 50 micron cell array with VTO in static mode42                                   |

| Fig 3.17 Enlarged view of 50 micron cell array covered by a single period of VTO 43       |

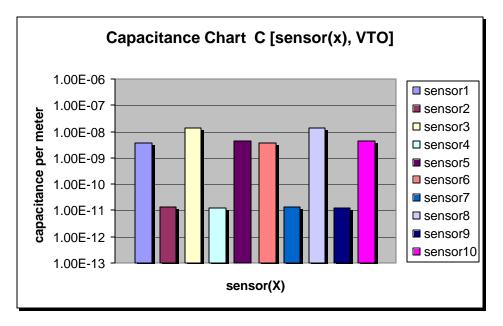

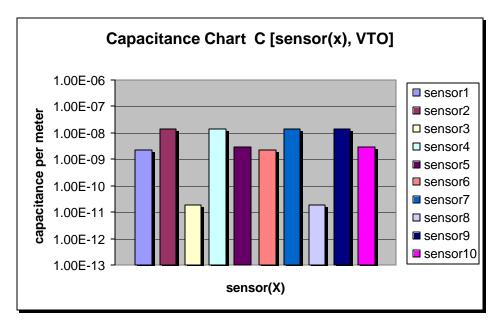

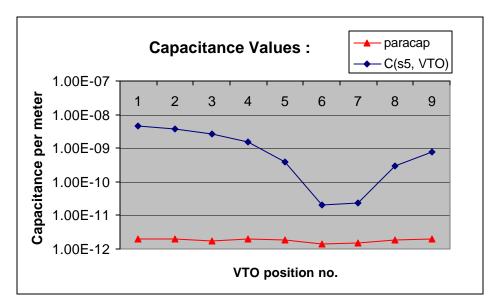

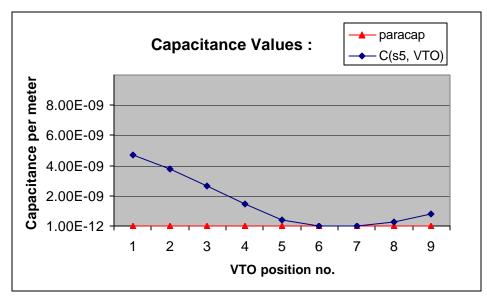

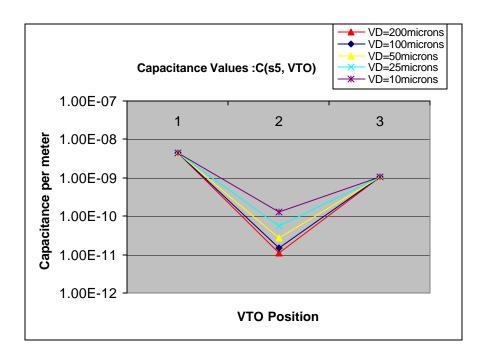

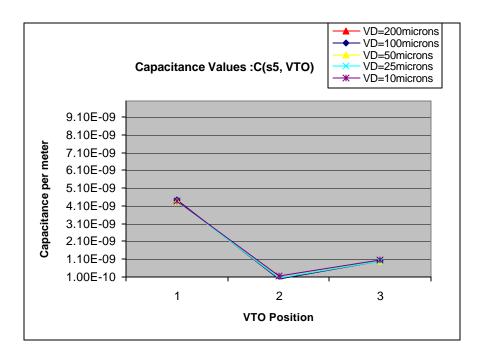

| Fig 3.18 Logarithmic chart for the sensor-VTO capacitances for 50 micron cell size 43     |

| Fig 3.19 200 micron cell array with VTO in static mode 44                                 |

| Fig 3.20 Logarithmic chart for sensor-VTO capacitances for 200 micron cell size45         |

| Fig 3.21 300 micron cell array with VTO in static mode 45                                 |

| Fig 3.22 Logarithmic chart for sensor-VTO capacitances for 300 micron cell size 46        |

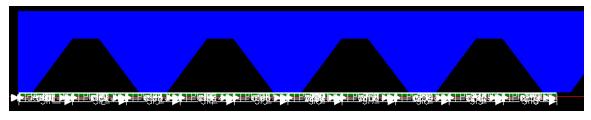

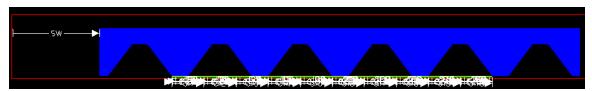

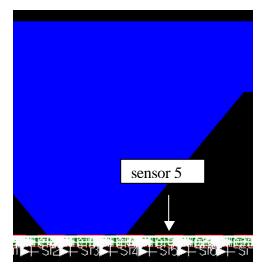

| Fig 3.23 VTO in swipe mode on the sensor model46                                          |

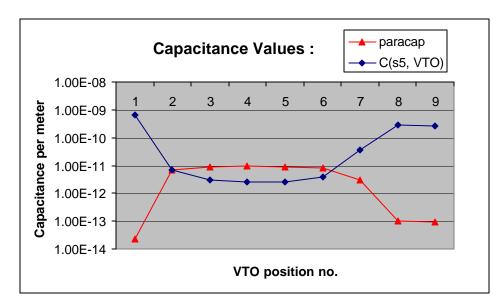

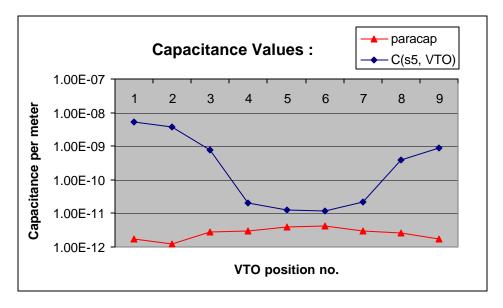

| Fig 3.24 Logarithmic plot for sensor5-VTO capacitance for 50u cell in swipe mode 47       |

| Fig 3.25 Logarithmic plot for sensor5-VTO capacitance for 200u cell in swipe mode48       |

| Fig 3.26 Logarithmic chart for sensor5 to VTO capacitance for 300 micron cell 49          |

| Fig 3.27 Linear chart for the sensor5 to VTO capacitance for 300 micron cell size 49      |

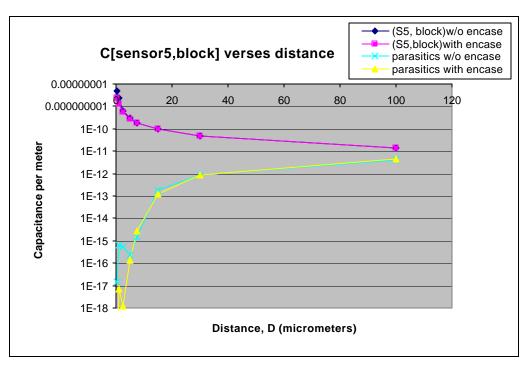

| Fig 3.28 Virtual Test Object with different valley depths to test sensor sensitivity 51   |

| Fig 3.29 Comparing the different valley depth capacitance values in logarithmic plot52    |

| Fig 3.30 Comparing the different valley depth capacitance values in linear plot 52        |

| Fig 3.31 Logarithmic plot which compares the nitride coating effect54                     |

| Fig 3.32 A well-structured underlying shield plate under each sensor55                    |

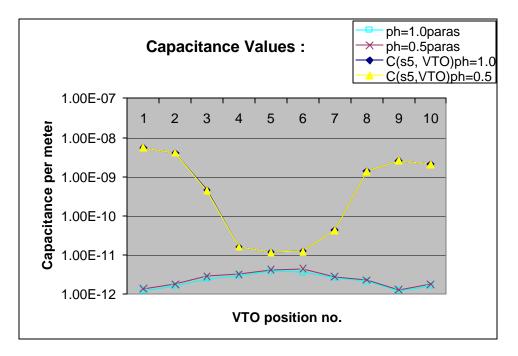

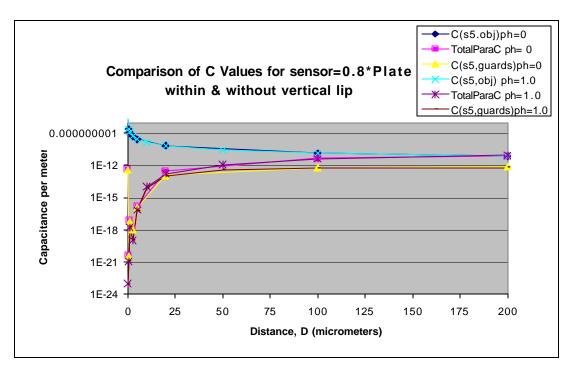

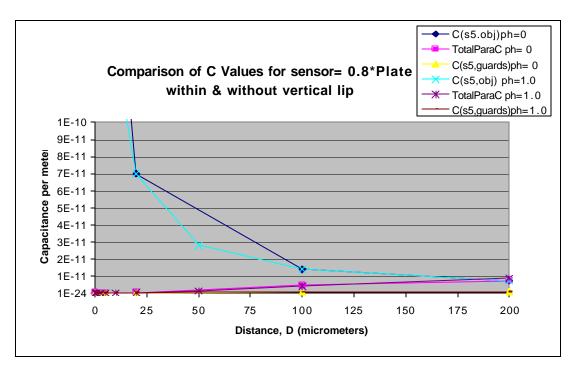

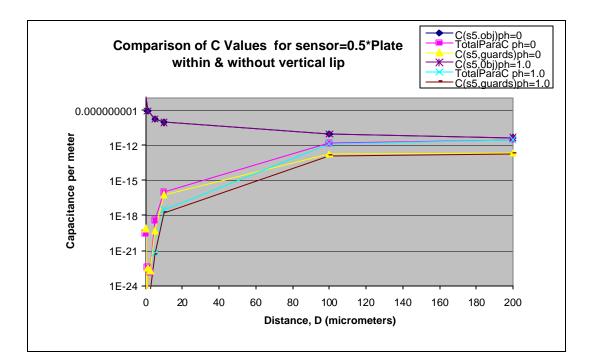

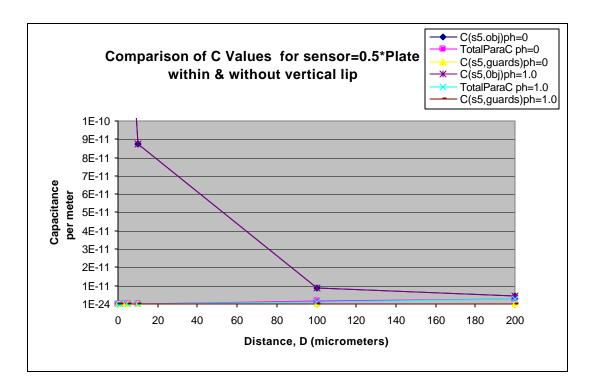

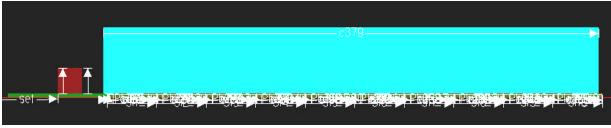

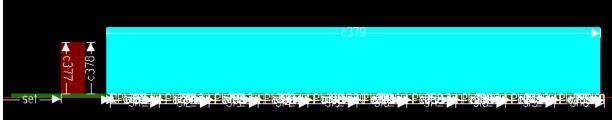

| Fig 3.33 Logarithmic plot showing the capacitance values for plug height factor=1.056<br>Fig 3.34 Logarithmic plot of the capacitance values for plug height factor=1.0&0.5 57<br>Fig 3.35 Logarithmic plot of various capacitance values for plug height factor=0&1.058<br>Fig 3.36 Linear plot of various capacitance values for plug height factor=0&1.058<br>Fig 3.37 Logarithmic plot of sensor factor 0.5 comparing plug height factors 0&1.059<br>Fig 3.39 ESD model with rectangular grounded ring of height 100 microns |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Fig 3.56 Linear plot of individual sensors(200u) to object in full shield array76                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Fig 3.57 Logarithmic plot of individual sensors(300u) to object in full shield array77                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Fig 3.58 Linear plot of individual sensors(300u) to object in full shield array77                                                                                                                                                                                                                                                                                                                                                                                                                                                |

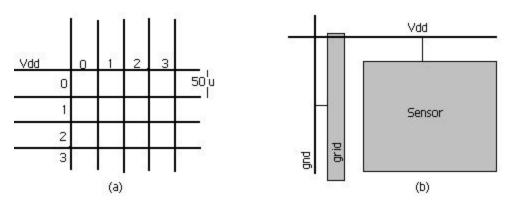

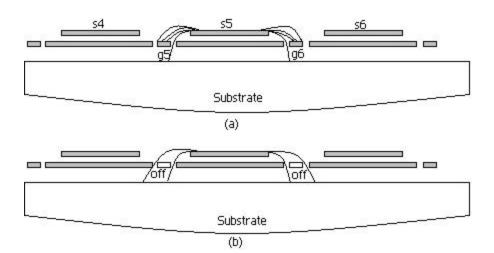

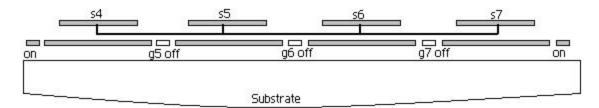

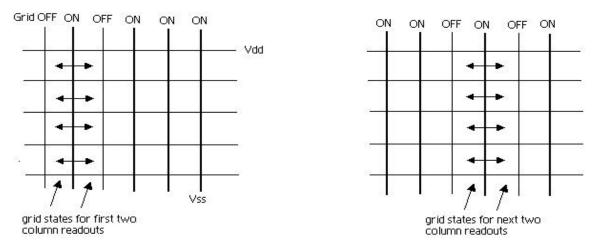

| Fig 3.59 Sensor array with row column addressing79<br>Fig 3.60 Sensor model with guard grid switching79                                                                                                                                                                                                                                                                                                                                                                                                                          |

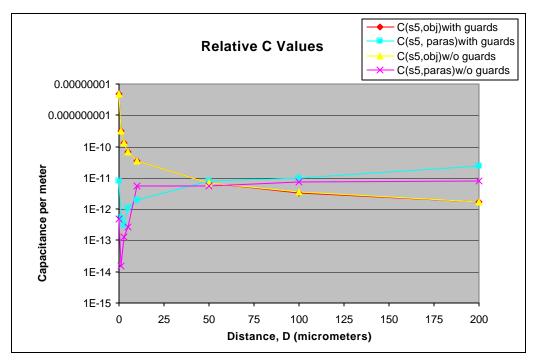

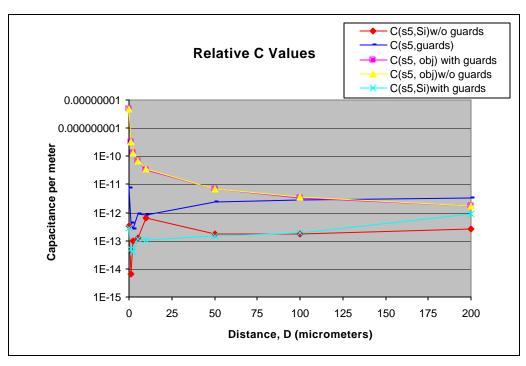

| Fig 3.61 Logarithmic plot of parasitic capacitance with and without guard grids 80                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Fig 3.62 Logarithmic plot of substrate parasitic capacitance with without guard grids80                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Fig 3.63 Adaptive array model in which sensors are interconnected81                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

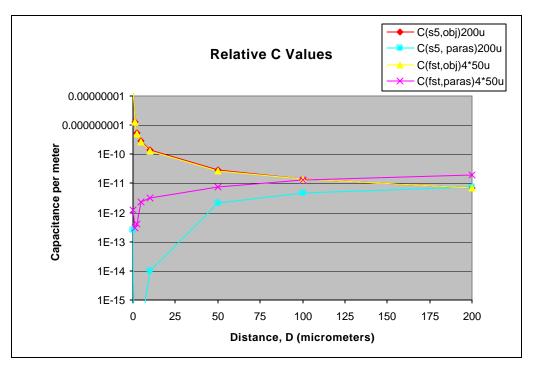

| Fig 3.64 Logarithmic plot of capacitance values of two types of large size cell array82                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Fig 3.65 Logarithmic plot of individual values of two types of large size cell array82                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Fig 4.1 Partial sensor array which change state by switching 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

## Chapter 1 Introduction

#### **1.1 Biometrics**

The automated measurement and identification of biological and behavioral characteristics of an individual is called biometrics [1]. If a human physiological or behavioral characteristic has the following properties, universality: which means that every person should have the characteristic, uniqueness: which means that no two persons should be the same in terms of the characteristic, permanence: which indicates that characteristic should be invariant with time, and collectability: which indicates that characteristic can be measured quantitatively then it could be used as a biometric[1]. As this technology becomes more economically viable, technically mature and the public becomes aware of the applications and strengths, the field of biometrics will play a crucial role in identification technology and the shaping of privacy policies.

#### **1.1.1 Personal Identification Systems**

Automated biometric personal identification systems represent a new and emerging technology. Initially, biometric technologies were considered to be highly technical, high cost systems, and can only be used in forensic and military applications, but with the availability of inexpensive embedded computing, cheaper sensing technologies, and increasing demand for identification, biometrics have emerged as mainstream[1].

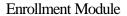

The architecture of an automated identity authentication system is shown in Fig 1.1. It has four components: biometric reader or sensor, system knowledge, enrollment module and authentication module. During enrollment, one of the biometric measurements are captured by the biometric interface and required information is taken by feature extractor and stored in a database. In authentication mode, the person to be authenticated indicates his identity. Next, the system reads the relevant biometric

Fig 1.1 Architecture of typical Biometric Identification System[6]

measurements, extracts features and compares with that of the information stored in the database. Lastly, the system then decides the subject is valid or invalid [6] [1].

There are two types of matching that an authentication module performs: one-toone matching which confirms the subject validity directly, and one-to-many matching which searches whole database and then decides the validity. In other words, if a system is asked to determine the identity of a person who presents himself to the system, the system compares particular biometric feature with the enrolled features. This type of matching is called one-to-many matching. If a person supplies his identity to the system usually by presenting a machine readable identification card and the system is asked to confirm that the person is who he says he is, this type of matching is called one-to-one matching.

#### **1.1.2 Biometric Technologies**

As with any technology, all the biometric technologies have their own strengths and limitations. Though there are a number of biometric technologies, each appeals to a particular identification application.

The following are the few biometric technologies that are currently commercially available[1].

- *Voice*: Voice print is acceptable in almost all societies and voice capture is unobtrusive. To identify a person over the telephone, voice may be the only feasible biometric as most of the other technologies require the individual to be present at the identification system. Though it has the properties of universality and collectability, it lacks permanence and uniqueness properties as it is a behavioral characteristic and is affected by person's health, emotions etc.

- *Infrared facial and hand vein thermograms:* The human body radiates heat and an infrared sensor device could capture an image indicating different levels of heat. Infrared facial thermograms are acceptable since their acquisition is non-contact and has a non-invasive sensing technique. A related technology is to scan the back of a clenched fist to determine the hand vein structure.

- *Fingerprints:* Fingerprints are one of the most popular and oldest biometric technologies used historically in forensic applications for criminal investigations. These are formed on human fingers depending on the initial conditions of embryonic development and therefore they are believed to be unique to each person and it also is permanent, universal and collectable.

- *Face:* Face is considered among the most natural biometrics because this can be used in visual interactions. It is very challenging to develop face recognition techniques because of the effects such as aging, facial expressions, slight

variations in the imaging environment and variations in the pose while taking the image.

- *Iris:* Visual texture of the human iris is considered to be unique for each person and each eye. An iris image is usually captured using a non-contact imaging process.

- *Ear:* The shape of the ear and the structure of the cartilaginous tissue on the pinna are distinctive, but not unique to each individual. No commercial systems are available yet in this field.

- *Gait:* Gait is the peculiar way one walks and not supposed to be unique for each individual. This is a behavioral biometric and can be used in identity authentication.

- *Keystroke Dynamics:* This is a behavioral biometric based on the fact that each person types on a keyboard in a distinct way. It is not unique to each individual but offers sufficient information to be used in some identification applications. Some commercial systems are available in the market in this field.

- *DNA:* Deoxyribo Nucleic Acid is the ultimate unique code for each individual except for the fact that identical twins have the identical DNA patterns. It is currently used mostly in forensic applications after fingerprint images for identification because of its high recognition rate. Identification systems involving this technology currently are not fully automated on the time scales necessary for rapid identification.

- *Signature:* The signature of a person is known to be a characteristic of that individual. It is widely acceptable in many government, commercial and legal transactions as a method of personal identification. Signatures are a behavioral biometrics, which depends on physical and emotional conditions of the persons.

- *Retinal Scan:* The retinal vasculature structure is supposed to be a characteristic of each individual and each eye. It is the most secure biometrics with the qualities of universality, uniqueness, permanence and collectability. The image capture method necessitates cooperation of the subject, entails contact with the eye piece and requires efforts of the user.

- *Hand and Finger Geometry:* Another method of identification is hand geometry, which has captured half of the physical access control market [1]. Finger geometry is related to hand geometry and is a new technology which relies only on geometrical invariants of index and middle fingers. Though this is more accurate than hand geometry, its technology is not as matured as that of hand geometry.

#### **1.1.3 Applications**

It is expected that in the coming years, the rising number of applications may increase the demand for the biometric identification systems. Some of the applications where biometric technology is already in use or would evolve and be used include:

- Transactions via e-commerce

- Search of digital libraries

- Computer Logins

- Access to internet and local networks

- Document encryption

- Credit cards and ATM cards

- Access to office buildings and homes

- Protecting personal property

- Tracking and storing time and attendance

- Law enforcement and prison management

- Automated medical diagnostics

- Access to medical and official records.

#### **1.2 State of the art in Biometric finger print model**

The use of fingerprints as a biometric is the oldest mode of personal identification and also is the most prevalent in use today [9]. However, this technology still is largely limited to law enforcement applications. It is expected that a recent combination of factors such as small and inexpensive fingerprint capture devices, fast computing hardware, recognition rate and speed to meet the rising needs of many applications, and the rapid growth of network and Internet transactions will favor the use of fingerprints as personal identification for the much larger market segment [9].

Currently much research is going on in this area, and the fingerprint technology is becoming very popular in biometric identification systems. This is the main reason behind the selection of fingerprint technology as a primary topic for this research work. Though there are few small sized solid state capturing devices available, they still suffer from low sensitivity, low robustness etc. This research work is concentrated on enhancing the sensitivity of fingerprint capturing device.

The following sections review the state of the art in biometric fingerprint models and future advances in this field, which includes a brief introduction about fingerprint image and the principle of fingerprint identification system.

#### **1.2.1 Finger Print and its Verification**

Fingerprints are graphical flow-like images present on human fingers. The lines that appear are called 'ridges' and the spaces between ridges are called 'valleys'. Fingerprint matching is done by comparing features on these ridges of one fingerprint with that of another.

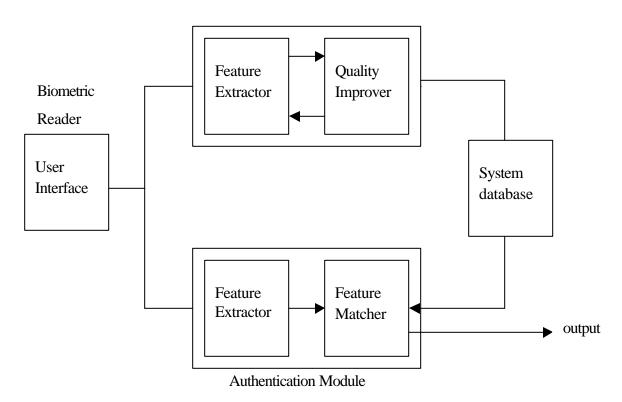

The two most important structures on a fingerprint image which are used for matching are a ridge ending and ridge bifurcation as shown in Fig 1.2. An ending is a feature where a ridge terminates and a bifurcation is a feature where a ridge splits into

6

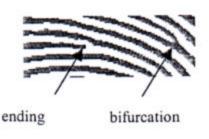

two paths. Both the structures collectively are called minutiae, shown in figure 1.3, which is attributed with features like type which says whether it is an ending or bifurcation, location of the structure determined by (x,y) coordinates, and direction in which the ending and bifurcation appears. These attributes are represented by binary values which combined together called minutiae template which is actually stored for matching purposes. There are other features of the fingerprint that are used in matching. For more information please refer to[9].

Fingerprint matching is done by two methods, *verification* which is based on one-to-one matching or one-to-few matching and *identification* which is based on one-to-many matching.

Fig 1.2 Finger print which shows ending and bifurcation[9]

1.3 (a) minutiae1.3(b) minutiae graphFig 1.3 Extracting features of Finger print minutiae[9]

Verification or one-to-one matching is done by comparing the claimant fingerprint against the enrollee fingerprint to decide the validity of the fingerprint. For this, initially a person enrolls his fingerprint into the system database which is stored in compressed format along with the person's other identity such as his name [9]. For example, to access his account at an ATM, the person would still have to present his card on which his name appears and then he would press his finger against a fingerprint sensor such that the identity can be verified. Verification based on one-to-few matching is done similarly but the person may not need to present his identity as this type of matching is done in a system where access is restricted to few users from which the system can easily determine whether the presented fingerprint matched with one of the fingerprints in the database. Most of the biometric verification systems use one-to-one or one-to-few matching for faster service which would be on the order of a few seconds.

Identification or one-to-many matching is significantly different from one-to-one matching in that it requires comparing the presented fingerprint against a database of many fingerprints. This is the typical fingerprint searching that law enforcement authorities use with the aid of automatic fingerprint-identification systems[3].

#### **1.2.2 Principle of fingerprint authentication system**

An automatic fingerprint identity authentication system consists of four main components, viz; acquisition, representation, feature extraction and matching[6].

*Acquisition:* There are two primary methods of capturing a fingerprint image, inked and live scan. Acquisition of inked fingerprints is laborious. Therefore live scan fingerprint has become popular technology which is done based on the techniques like frustrated total internal reflection, ultrasound total internal reflection, thermal sensing, and sensing of differential capacitance.

*Representation:* Representation of a fingerprint is done based on the unprocessed gray-scale profile, entire ridge structure (ridge-based), and land mark based representation.

8

Though each has its own design constraints, all of the above are used in representation of fingerprint images in different scanning methods. Landmark or minutiae based representation has one important advantage in terms of privacy. One cannot reconstruct the entire fingerprint image from the fingerprint landmark information alone. The American National Standard Institute [ANSI] – National Institute of Standards and Technology [NIST] standard representation of a fingerprint is based on minutiae location and orientation[6]. The typical minutiae of a fingerprint is shown in Fig 1.3 in the previous section.

*Feature Extraction:* A feature extractor finds the ridge endings and bifurcations on the input fingerprint images. The minutiae extraction is not a complicated task if ridges can be perfectly located in the input fingerprint image. Reliable minutiae-extraction algorithms should not assume perfect ridge structures since in practice it is not possible to obtain a perfect ridge image[6].

*Matching:* The matching phase defines a measurement of similarity between test and reference fingerprint representation. The matching module also defines a threshold by which a decision is made about the validity of the fingerprint [6].

#### **1.2.3 Various Fingerprint Image Sensing Devices**

There are primarily three types of image capture devices, optical, solid state and other [9].

Optical fingerprint capture devices have a long history dating back to the 1970's. These devices operate on the principle of frustrated total internal reflection (FTIR). Efforts have been put to reduce the size of these devices. There are also other optical technologies than FTIR such as fiber optics [6]. Some of the new optics-based sensing units offer much lower prices and smaller sizes than did their predecessors [3]. Recently, solid state sensors have become popular in the market. These are made up of microchips which contain a surface that images the fingerprint by one of the following technologies. Capacitive sensor devices incorporate a sensing surface composed of a rectangular array of about 100,000 conductive plates over which a dielectric is placed. The other plate of the capacitor is the skin of the user finger. The ridges of the fingerprint are close to the surface and have high capacitance whereas the valleys have lower capacitance. The other surfaces proposed are pressure sensitive which uses piezoelectric material, and temperature sensitive sensors which respond to the temperature difference between the ridges and valleys [9].

Two major companies which ship solid state sensor chips, SGS-Thomson and Veridicom, use dc capacitive sensors, while Thomson-CSF's finger chip uses thermal sensing. Hughes briefly pursued an RF impedance based array device but did not commercially pursue this device. Harris FingerLoc IC is also a capacitive fingerprint sensor but instead of measuring capacitance with dc, it uses an ac electric field [3].

Low cost and compact size are the two most important factors that decide the future of a product in the large volume personal verification market. Solid state sensors have an edge where their compact size approaches a lower limit of size needed to capture the surface area of finger, about 1x1 inch with a fraction of an inch depth [9]. Target price range for acceptance of solid state sensors in broad application areas is considered to be on the order of \$10 per unit or less.

Optical scanners have the advantage of being able to support larger image capture size. It is costly to manufacture a large solid state sensor due to yield considerations[9]. There is also an assertion that because the finger never directly touches the chip in optical scanning systems, the device is inherently safer than capacitive direct contact sensing devices. But the IC companies have developed a chip coating that even scratching with a diamond scribe cannot damage it[3]. On the whole, solid state finger print capturing devices are dominant in the market place now, having greater flexibility for various applications.

### **1.3 CMOS Review**

Complementary Metal Oxide Silicon (CMOS) technology is at the heart of Silicon solid state fingerprint sensor approaches. In this chapter, a brief explanation of CMOS devices and its various technologies are mentioned. Explaining in detail about CMOS device structure is beyond the scope of this dissertation.

#### **1.3.1 Complimentary MOS Transistor**

Metal Oxide Semiconductor Field Effect Transistor (MOSFET) has become prominent as soon as digital switching circuits have emerged. The fabrication of large scale IC digital circuits became possible with MOS transistors from the fact that its size can be reduced for use in densely packed circuits [10]. The density achievable has recently made large (100k to 300k elements) fingerprint sensor arrays viable.

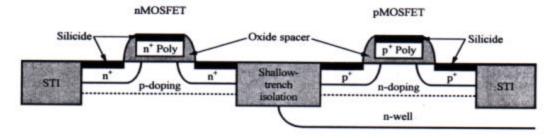

The Complementary MOS device is a combination of n-channel and p-channel MOS transistors integrated on the same chip as shown in Fig 1.4. The CMOS has an unique characteristic of practically zero standby power, which makes them particularly useful in digital and VLSI applications[11].

The main features of CMOS technology are polysilicon gate(n-type for n-channel MOSFET and p-type for p-channel MOSFET), refractory metal silicide on the

Fig1.4 CMOS device cross section [11]

polysilicon gate and on the source and drain diffusion regions, and shallow-trench oxide isolation between the channels [11].

#### **1.3.2 CMOS process flow and planarization**

Fig1.5 The deposition process of various layers on Si substrate in CMOS fabrication

The fabrication process of CMOS involves deposition of various films over the silicon substrate in the order shown in the above figure. It is not appropriate to discuss about each process here, but the films and materials which lie over the oxide coating are a major concern in this work as this is what the plates are made of in a fingerprint sensor. So, a brief description about the planarity of the device, interconnect metals, and dielectrics is given below.

The deposition of both insulating and conducting films on a flat silicon substrate as it proceeds to metallization process results in an increasingly nonplanar structure of the device. This loss of planarity creates two problems. One is local issue, that is maintaining step coverage without breaks in the continuity of fine lines, and another is global, the inability to produce fine line pattern over the substrate with the loss of planarity. The techniques for making the microchip flat are commonly referred to as planarization techniques. There are various techniques available, such as LOCal Oxidation of Silicon(LOCOS), Chemical Mechanical Planarization(CMP), encapsulation etc., to achieve planarity of the device but these are a function of the height and spacing of the features. The features which are narrow and closely spaced are more readily planarized than the features which are wide and spaced apart. This is the most important factor to consider while designing a fingerprint sensor device or any microchip device. Al and Silicide are the most commonly used materials for metallization in VLSI devices. As circuits become more complex, the area utilization of the silicon surface becomes difficult. To avoid these problems, multilevel metallization schemes are used which aids in providing additional surface area and solving topological problems of interconnection. Three layer metallization is often used with thin insulating films deposited which serve as barrier between these layers. These inter metal dielectrics (IMD) should have a reasonably low dielectric constant and a high electric breakdown electric field strength. SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub> are commonly used materials for these intermediate layers in fingerprint sensor devices[5].

#### **1.4 Capacitive Fingerprint Scanning Devices**

Conventional forms of fingerprint sensing devices such as optical detection and pressure detection suffer from the disadvantages of high cost and bulkiness [12].

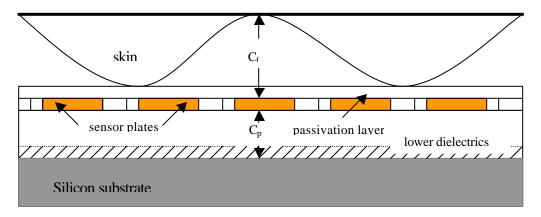

The capacitive fingerprint sensor which avoids the aforementioned problems is composed of 2-D array of sensing elements using standard CMOS processing covered by a thin dielectric layer as shown in fig 1.6. Each sensing element acts as capacitor bottom plate, while the finger surface acts as grounded top plate which is assumed to be an equipotential surface. Each active element detects the change in electric field (and hence change in capacitance) induced by the proximity of the fingerprint valleys and ridges to the cell plates. The different values of these capacitances are measured and an electronic representation of the fingerprint is obtained [12].

The choice of dielectric material and thickness is critical in the design of sensor model. The requirement that the top dielectric or passivation layer be exposed to the external environment is completely foreign to typical IC technology. The finger which is placed on the sensor chip contacts this dielectric material, and therefore the material has to be made chemically rigid enough to resist skin oils, moisture, salts, acids that can migrate to the silicon, electrically isolated to prevent electrostatic discharge, and

Fig 1.6 Typical Capacitive Sensor Design

mechanically strong to avoid surface scratching. Major companies like Veridicom use a special type of coating material as a passivation layer which is 100 times the strength of glass (see Appendix-A for complete specifications). Such a rugged design withstands frequent use of the sensor for commercial applications like cell phones and laptops and for outdoor use in applications such as an access control device for a vehicle or ATM[8]. The sensitivity of the device is directly proportional to the ratio of  $G_f / C_p$ , (see in figure) where  $G_f$  is the capacitance between the finger and the sensor plate and  $G_p$  is the parasitic capacitance associated with each sensor plate, which includes substrate, neighboring plates, grounded grids etc. So, sensitivity can be increased by maintaining a high  $C_f / C_p$  ratio by altering the dielectric constant and thickness of lower dielectrics[8]. In our modeling, high  $C_f / C_p$  ratios are explored by providing shielding to the sensor plate, and changing the size of sensor plates and shields.

### 1.4.1 The Veridicom Sensor Cell

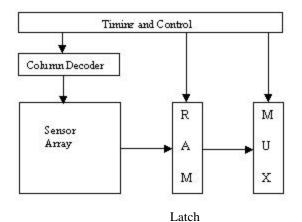

At the time of this research, the family of capacitive fingerprint sensor devices manufactured by Veridicom each consist of a sensor array of 300x300 elements, fabricated using a standard digital 0.5 micrometer CMOS process[8] A block diagram of the fingerprint scanner chip is shown in Fig 1.7.

Fig 1.7 Block diagram of the chip

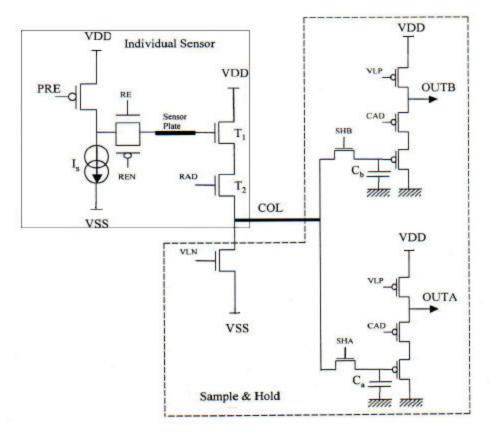

The following Fig 1.8 shows an individual Veridicom FPS 100 sensor cell with associated column read out circuit [8]. A simple sample & hold logic circuit is used to read the measured capacitances through a series of row-column selections.

Basic device operation is described in [8]. The entire read cycle timing diagram is shown in the Fig 1.9. At the beginning of each cycle, sensor plates are activated by row enable signals RE and RAD. Each sensor plate is then pre-charged using PRE. Source follower T<sub>1</sub> buffers the voltage appearing on sensor node and the row select signal RAD gates this voltage onto a column data bus, COL, through source of  $\underline{T}_2$ . C<sub>A</sub> in sample & hold logic stored with precharge voltage V<sub>A</sub> by pulsing SHA. After PRE is released current source Is drains the deposited charge from the plate during a fixed period of interval. Now, this new voltage V<sub>B</sub> is sent to C<sub>B</sub> by pulsing SHB.

A subsequent circuit subtracts  $V_B$  from  $V_A$  to remove pattern noise caused by transistors  $T_1$  and  $T_2$  (due to variations in their threshold voltages) and give an output which is approximately proportional to the gap between the finger and the sensor plate[8].

Fig 1.8 Individual Sensor Cell with Sample and Hold Logic[8]

Fig 1.9 Sensor row access timing Diagram [8]

The calculation for capacitance from this sensed voltages can be illustrated by the following,[13].

$$V_A = V_a + V_{Noise}$$

$V_B = V_b + V_{Noise}$

$V_A$ ,  $V_B$  are the voltages at beginning and end of sample & hold period respectively, which includes noise as well.  $V_a$  and  $V_b$  are voltages at same periods but without noise. We have relationship of charge and voltage as,

$$q = CV$$

Let the charges at above two intervals be  $q_1$  and  $q_2$ .

$\therefore$  Change in the charge or net charge is

$$q_2 - q_1 = C (V_B - V_A)$$

becomes

$q_2 - q_1 = C (V_b - V_a)$  ------(1)

From the timing diagram, we can write as,

$$q_1 - q_2 = I_s (t_2 - t_1)$$

-----(2)

Equating (1) and (2),

$$C (Va - Vb) = Is (t2 - t1)$$

$$C = Is \frac{(t2-t1)}{Va-Vb}$$

Or

$$C \propto \frac{1}{(Va - Vb)}$$

Therefore, the capacitance measured by the capacitive sensor is inversely proportional to voltage sensed which in turn is directly proportional to the distance between the finger and chip.

#### **1.4.2** Parasitic Capacitance

The parasitic capacitance is defined as the unwanted capacitance sensed by the sensor plate from neighboring sensor plates, neighboring underlying shields (which is one of the solutions to reduce the parasitic capacitances explained later), neighboring guard grids and the silicon substrate. All the capacitances involved with each sensor element including the object capacitance are shown in the following Fig1.10. Of all these the main contributor is the grounded guard grids which sit on either side of the sensor plate. The neighboring plates and shields provide secondary contributions.

In order to reduce the parasitic capacitance, the current design of the sensor cell incorporates a shielding plate under the sensor plate in each cell which follows the sensor plate voltage. The underlying shield plate and its size relative to the sensor plate, and the position of both (sensor plate and underlying shield) relative to the grounded grid and neighboring sensor plates are critical to the control of parasitic capacitances.

Fig 1.10 Various capacitances involved for sensor plate 5, all of them except sensor to object capacitance C(s5, obj) contribute towards total parasitic capacitance.

#### **1.5 Research Overview**

Though the capacitive fingerprint sensors are available commercially and are used in many applications, increased performance and device operation understanding is still sought. Approaches for achieving improved depth sensitivity of the capacitive imaging process are of particular interest. This goal is closely tied to the need to understand the role of capacitive parasitics in the device geometry and layout and seek means to reduce their contribution to the total capacitance. In addition, new modes of device operation that may enhance performance or further improve user acceptance represent important avenues of investigation.

The primary objective of this work is to quantify and explore these approaches through the use of appropriate models and simulation software. The results of this work will serve as a guide for future device designs.

The research is composed of a set of related studies. These studies are summarized briefly below.

#### • Vertical sensitivity using structured objects in static and swipe mode:

To start with, most current device designs are not efficient in resolving the capacitance variation when the object distance goes beyond 100 micrometers. To evaluate the ability of existing model to detect and resolve spatial features from capacitance variations, structured objects named here as "Virtual Test Objects(VTO)" are used as test objects. The swipe imaging has become popular in fingerprint capturing devices recently This type of imaging differs from static imaging in that user swipes his finger across a tiny fingerprint scanner instead of just putting over it for more privacy. The parasitic capacitance effect and the row spacing of such a model when different sized sensor cells are used in the array are important factors to be considered. The model is tested in swipe mode and based on the coupling capacitances of this uniform cell array of different cell sizes, the row spacing of linear arrays could be evaluated.

#### • Embedded sensor plate:

The passivation layer overlaying the chip is essential in order to protect the device from chemical and physical wear and tear. The material of this top dielectric layer and its thickness are critical in this regard and must not adversely effect the capacitance measurement ability of the sensing elements. To see the effect of this passivation layer on vertical sensitivity, the model is tested with and without this layer to evaluate the thickness of the layer that could be used.

#### • Well structure of underlying shield plate:

The primary parasitic capacitances impacting a sensor cell are the mutual capacitances of the sensor plate with Si substrate, the guard grid surrounding its cell, and the neighboring plates. Though the flat underlying shield helps in suppressing the sensor to Si substrate coupling, it doesn't isolate the neighboring guards, and plates. To extend the advantage of having the shield under the sensor plate, the design of shield plate is slightly modified by tilting its edges vertically so that it covers the sensor plate on either side as well. The effect of this well-shaped structure was evaluated for its ability to reduce sensor plate coupling to neighboring elements.

#### • Electrostatic Discharge Ring:

With consideration of a linear swipe type device, the impact of bringing the external ESD ring to within close proximity of the linear sensor arrays was raised as a potential concern. The distance of the ring from the last sensing element is greatly depended on the height of the ESD ring. These two factors are evaluated.

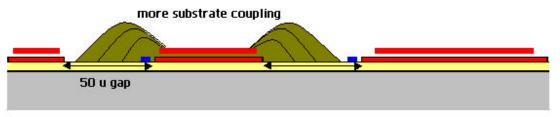

#### • Mixed size cells and sensor plates in the array:

In order to explore row to row spacing in a linear array, an array with different sized cells in one dimension is designed. This one dimensional array can be considered as one single column of a linear array. The effect of capacitive coupling between such cells are evaluated by varying the gaps in between the cells. Reducing the sensor plate size relative to shield plate decreases the

measurement ability of sensor plate, therefore to balance these two issues a mixed array is designed with different size of sensor plates keeping shield plate size fixed. This is done with the intent of reducing electrostatic field coupling, by having many small sized sensor plates in each row.

#### • Adaptive Arrays:

Each sensor plate in the array has grounded grid which is a major contributor towards parasitic capacitance array. If some of the grids in the array are switched off and relative sensors are interconnected then the parasitic capacitance can be reduced to some extent. This experiment is done considering possibility of grid switching and electrical interconnections between the sensors.

The following chapter, describes the sensor physical model, simulation parameters and the software used to perform the electrostatic modeling to obtain the effect of geometry and layout design changes on capacitances. The results and detailed explanation of above mentioned modeling activities are given in Chapter 3. Finally, results are reviewed, approach to be taken for future work is mentioned and conclusions about this work are made in the final chapter.

### Chapter 2 Simulation Theory and Software

A requirement underlying this entire body of work is the need to calculate capacitance. A basic one dimensional ten cell array is used for performing modeling activities in this work.

The capacitance developed between the sensor plates and the finger surface is the desired parameter to be determined in these simulations along with the parasitic capacitances between the sensor plates and other components in the sensor. These capacitances are indicated schematically in Fig1.10. The theory involved in calculating these capacitances considering all the neighboring elements such as guards, shield plates, sensor plates is illustrated in this chapter. Before going into that, a brief introduction is given about the software tool used for this calculations.

#### 2.1 Software Tool

Given the complexity of the geometry of the sensor cell and the need to understand multi-cell interaction analyzing this model analytically will not give sufficient information. Therefore, an electrostatic modeling tool will be used to calculate these capacitance values. This tool must provide flexibility of change in geometry, parameters, materials, excitations, etc., so that different types of designs can be tested in one simulation by performing required number of iterations. The tool must also give accurate results with minimal error and be fast enough to run on a system in a practical time frame.

The Software tool used throughout this work is *Maxwell 2D Field Simulator* from *Ansoft* Corporation. This is an interactive software package that uses finite element analysis to solve two-dimensional static electromagnetic problems [17].

Maxwell 2D quickly obtains critical device parameters such as force, torque, inductance, and *capacitance* from the physical design information.

The changes in geometry, material and electrical parameters are evaluated automatically by the integrated parametric analysis module. This module allows all design options to be thoroughly explored within a simulation. Maxwell 2D uses the finite element method and its adaptive automatic mesh refinement feature ensures accurate, converged solutions. The simple flow of the software along with status monitoring and error checking features provide a structured analysis environment. The executive user interface guides user to specify the appropriate geometry, material properties, and excitations for a device. The software then automatically creates the required finite element method, iteratively calculates the desired electrostatic field solution and quantities of interest such as inductance and *capacitance*. Finally, it allows the user to analyze, manipulate, and display field solutions [18].

In the next section, detailed explanation of electrostatic field equations and capacitance matrix is given .

#### **2.2 Electrostatic Field Simulation**

The electrostatic field simulator computes static electric fields arising from potential differences and charge distributions [18].

#### 2.2.1 Field Equations

The electrostatic field simulator solves for the electric potential,  $\phi(x,y)$ , in this field equation:

$$\nabla \bullet (\varepsilon_{\rm r} \varepsilon_{\rm o} \nabla \phi(\mathbf{x}, \mathbf{y})) = -\rho$$

where,

- $\phi(x,y)$  is the electric potential.

- $\varepsilon_r$  the relative permittivity. It can be different for each material.

- $\varepsilon_{o}$  is the permittivity of free space, 8.854 x 10<sup>-12</sup> F/m.

- $\rho(x,y)$  is the charge density.

This equation is derived from Guass's Law, which indicates that the net electric flux passing through any closed surface is equal to the net positive charge enclosed by that surface. In differential form, Guass's Law is,

$$\nabla \bullet \boldsymbol{D} = \boldsymbol{\rho}$$

where  $\mathbf{D}(x,y)$  is the electric flux density, since  $\mathbf{D} = \varepsilon_r \varepsilon_o \mathbf{E}$ , then:

$$\nabla \bullet (\varepsilon_{\rm r} \varepsilon_{\rm o} \boldsymbol{E}(\mathbf{x}, \mathbf{y})) = \rho$$

In a static field,  $E = -\nabla \mathbf{f}$ . Therefore,

$$\nabla \bullet (\varepsilon_{\rm r} \varepsilon_{\rm o} \nabla \mathbf{f} ({\rm x}, {\rm y})) = -\rho$$

which is the equation that the electrostatic field simulator solves using the finite element method.

After the solution for the potential is generated, the system automatically computes the E-field and D-field using the relations  $\mathbf{E} = -\nabla \mathbf{f}$  and  $\mathbf{D} = \mathbf{\varepsilon}_{\mathrm{r}} \mathbf{\varepsilon}_{\mathrm{o}} \mathbf{E}$ . [18].

#### 2.2.2 Capacitance

Two conductors separated by an insulator are said to form a capacitor. The conductors usually have charges of equal magnitude and opposite sign, so that the net charge on the capacitor as a whole is zero. The electric field lying in between the conductors is proportional to the magnitude of this charge, and it follows that the potential difference 'V' between the conductors is also proportional to the charge magnitude 'Q'.

The Capacitance 'C' of a capacitor is defined as the ratio of magnitude of the charge 'Q' on either conductor to the magnitude of the potential difference 'V' between the conductors.

$$C = \frac{Q}{V}$$

From the definition it follows that the unit of capacitance is one Coulomb per Volt. A capacitance of one coulomb per volt is called one Farad [17].

In a single electric circuit, the capacitance represents the amount of energy stored in the electric field that arises due to a potential difference across a dielectric.

$$U_{\rm e} = \frac{1}{2} \,\mathrm{C} \,v^2$$

where  $U_e$  is the energy stored in the electric field, C is the capacitance, and v is the voltage across the dielectric.

The Maxwell 2D Field Simulator computes the capacitance between two conductors by simulating the electric field that arises when a voltage differential is applied. Then, by computing the energy stored in the field, the corresponding capacitance can be computed.

$$C = \frac{2Ue}{v2}$$

To compute capacitances using this method, the E-field and D-field associated with a given distribution of voltages must first be computed. The electrostatic field simulator, which computes the electric potential at all points in the problem region, performs this task [19].

#### 2.2.3 Capacitance Matrix

A capacitance matrix represents the charge coupling within a group of conductors. This is the relationship between the charges and voltages for the conductors. Given the four conducting objects as shown in Fig 2.1 with the outside boundary taken as a reference, the net charge on each object will be:

$$\begin{split} Q_1 &= C_{10}V_1 + C_{12}(V_1 - V_2) + C_{13}(V_1 - V_3) + C_{14}(V_1 - V_4) \\ Q_2 &= C_{20}V_2 + C_{12}(V_2 - V_1) + C_{23}(V_2 - V_3) + C_{24}(V_2 - V_4) \\ Q_3 &= C_{30}V_3 + C_{13}(V_3 - V_1) + C_{23}(V_3 - V_2) + C_{34}(V_3 - V_4) \\ Q_4 &= C_{40}V_4 + C_{14}(V_4 - V_1) + C_{24}(V_4 - V_2) + C_{34}(V_4 - V_3) \end{split}$$

Fig 2.1 Capacitances between objects

This can be expressed as in matrix form as:

| $\left[ Q_{1} \right]$ |   | $\begin{bmatrix} C10 + C12 + C13 + C14 \end{bmatrix}$ | - <i>C</i> 12                                      | <i>- C</i> 13                                      | - <i>C</i> 14      | $\begin{bmatrix} V1 \end{bmatrix}$ |

|------------------------|---|-------------------------------------------------------|----------------------------------------------------|----------------------------------------------------|--------------------|------------------------------------|

| $Q_2$                  |   | - <i>C</i> 12                                         | <i>C</i> 20+ <i>C</i> 12+ <i>C</i> 23+ <i>C</i> 24 | - <i>C</i> 23                                      | - <i>C</i> 24      | V2                                 |

| Q3                     | = | - <i>C</i> 13                                         | - <i>C</i> 23                                      | <i>C</i> 30+ <i>C</i> 13+ <i>C</i> 23+ <i>C</i> 34 | - <i>C</i> 34      | V3                                 |

| $\lfloor Q4 \rfloor$   |   | - <i>C</i> 14                                         | - <i>C</i> 24                                      | - <i>C</i> 34                                      | C40+ C14+ C24+ C34 | $\lfloor V4 \rfloor$               |

The capacitance matrix above gives the relationship between Q and V for the four conductors and ground. In a device with n conductors, this relationship would be expressed by an  $n \ge n$  capacitance matrix. Capacitance matrix values are specified in Farads (Coulombs/Volt). If one volt is applied to Conductor 1 and zero volts is applied to the other three conductors, the capacitance matrix becomes:

$$\begin{bmatrix} Q_1 \\ Q_2 \\ Q_3 \\ Q_4 \end{bmatrix} = C \begin{bmatrix} 1 \\ 0 \\ 0 \\ 0 \end{bmatrix} = \begin{bmatrix} C10 + C12 + C13 + C14 \\ -C12 \\ -C13 \\ -C14 \end{bmatrix}$$

The diagonal elements in the matrix (such as  $C_{(1,1)}$ ) are the sum of all capacitances from one conductor to all other conductors. These terms represent the self-capacitance of the conductors. Each is numerically equal to the charge on a conductor when one volt is applied to that conductor and the other conductors (including ground) are set to zero volts. For instance,  $C_{(1,1)} = C_{10} + C_{12} + C_{13} + C_{14}$ .

The off-diagonal terms in each column (such as  $C_{(1,2)}$ ,  $C_{(1,3)}$ ,  $C_{(1,4)}$ ) are numerically equal to the charges induced on other conductors in the system when one volt is applied to that conductor. For instance, in column one of the example capacitance matrix,  $C_{(1,2)}$  is equal to  $-C_{12}$ . This is equal to the charge induced on Conductor 2 when one volt is applied to Conductor 1 and zero volts are applied to Conductor 2.

The off-diagonal terms are simply the negative values of the capacitances between the corresponding conductors (the mutual capacitances). In column one of the example capacitance matrix, the off-diagonal terms represent the capacitances between Conductor 1 and the other three Conductors; in column two, the terms represent the capacitance between Conductor 2 and the other conductors; and so forth.

We can observe that the capacitance matrix is symmetric about the diagonal. This indicates that the mutual effects between any two objects are identical. For instance,  $C_{(1,3)}$ , the capacitance between Conductor 1 and Conductor 3 (- $C_{13}$ ), is equal to  $C_{(3,1)}$ , the capacitance between Conductor 3 and Conductor 1[19].

#### 2.2.4 Computing Capacitance

To compute a capacitance matrix for a structure, the Maxwell 2D Field Simulator performs a sequence of electrostatic field simulations. In each field simulation, one volt is applied to a single conductor and zero volts is applied to all other conductors as shown in the Fig 2.1. Therefore, for an n-conductor system, n field simulations are automatically performed. The energy stored in the electric field associated with the capacitance between two conductors is given by the following relation,

$$U_{ij} = \frac{1}{2} \mathbf{W} \mathbf{D}_i \bullet \mathbf{E}_j \, \mathrm{d} \mathbf{W}$$

Where:

- w specifies the volume integral and dW is the unit volume.

- U<sub>i j</sub> is the energy in the electric field associated with flux lines that connect charges on conductor *i* to those in conductor *j*.

- **D**<sub>i</sub> is the electric flux density associated with the case in which one volt is placed on conductor *i*.

- **E**<sub>j</sub> is the electric field associated with the case in which one volt is placed on conductor *j*.

The capacitance between conductors i and j is therefore:

$$\mathbf{C} = 2 U_{ij} / v^2 = \mathbf{W} \int \boldsymbol{D}_i \bullet \boldsymbol{E}_j \, \mathrm{d} \mathbf{W}$$

### Limitations:

Though Maxwell 2D field simulator can compute capacitances with accuracy, it only gives information about capacitance for two dimensional geometries. All the capacitances calculated in this simulations are per unit length, assuming extension of the cross section into the depth of the simulation plane. Maxwell 2D assumes that capacitance lies in the cross-sectional geometry of the sensor model in which 3D effects can be ignored for the purpose of analysis.

# Chapter 3 Model Description and Simulation Results

# Introduction:

In the previous chapters, the physical model of a capacitive fingerprint device is introduced and the procedure to calculate the capacitance matrix is explained. This chapter introduces the geometrical views of sensor chip and sensor cells and motivates the model (in terms of geometry, internal elements, materials etc.), which was developed for actual simulations. The geometrical views of chip and individual cell of the fingerprint sensor is shown in the following Fig 3.1 below.

Fig 3.1 Complete sensor array with enlarged individual cell geometry[8]

A 3 x 3 cell array is highlighted on 300 x 300 cell array from which a single cell is enlarged to show the internal circuit layout of individual cell. Each cell of size approximately 50 x 50 micrometers has primarily a sensor plate, a shield plate, sensing circuitry and a guard grid, with over 60 % of the sensor cell area is devoted to the sensor plate[8]. The sensing circuitry consists of the CMOS circuits including sample and hold circuit which was introduced in the first chapter. The figure also shows the column readout line from the sensing circuit. The guard grid is placed between each cell for proper grounding of the circuit.

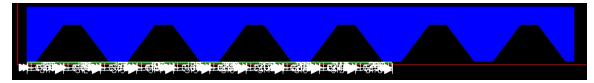

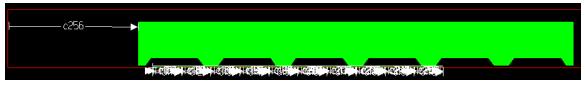

For the purpose of designing the geometry model for simulations a row of 10 cells is selected for modeling. Cells at the center of this row are used to simulate cells far from the actual array edges. It is assumed that all internal elements are similarly located in each cell to generalize the modeling of the device. Fig 3.2 shows a cross-sectional view of a 3-cell section showing the cell features used in the geometry model. The model was formulated keeping in view that future device designs might vary from the basic model. As a result, based on preliminary modeling work only those cell features are reflected in the geometry cross-section which have significant impact on fields. These are shown in the above figure and in Fig 3.5 in the next section.

CLOSS SECTIONAL MEW OF SAIL SENSOL ALL AY

Fig 3.2 Top and Cross sectional view of one partial row of sensor chip

# **3.1 Parameters and Materials**

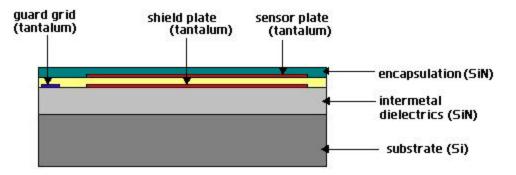

The various sub-elements and their materials of a sensor cell are shown in the Fig 3.3 and are discussed briefly in this section.

Fig 3.3 The various elements and their assigned materials in a sensor cell

The parameters used in the simulations through out this work are given below,

| 1. | Silicon substrate (Si)          | 5. Space                        |

|----|---------------------------------|---------------------------------|

| 2. | Silicon Plate (Sensor)          | 6. Guard Grid                   |

| 3. | Underlying Shield Plate (Plate) | 7. Right                        |

| 4. | Left                            | 8. Inter Metal Dielectric (IMD) |

The materials used in the model generation and simulations are given below,

- 1. Silicon4. Tantalum

- 2. Silicon di oxide 5. Water Sea

- 3. Silicon Nitride

# 3.1.1 Parameters used

# Silicon (Si):

This name is used for the base substrate of the sensor cell in the model. This model consists of ten sensor cells horizontally having flexibility of change in their size. A parametric geometric model has been formulated in order to perform the

simulations and see the impact of sensor cell size on the capacitance. In this work cell sizes tested are 50 u, 100u, 200u, & 300 u. The results of these cells are given in next chapter.

#### Underlying Shield (Plate):

Plate is a 0.2 micron thick underlying shield for each sensor plate in each cell. It is assigned to the same material of that of the sensor plate, and it follows the sensor voltage. This plate is added in the model to reduce the parasitic capacitance with the substrate. This underlying plate relative to the sensor plate and position of both relative to the neighboring guards and shield plates are critical to the reduction of the dominant parasitic capacitances.

#### Sensor Plate (sensor):

Sensor Plate is also a 0.2 micron thick metal which is the actual sensing area in the model. A variable 'factor' is used to vary the size of the sensor plate size relative to the underlying plate. In this work, factors 0.5 to 1.0 are tested and an optimum one is used throughout the remainder work. The mathematical equation for the sensor plate is ,

Sensor plate size = factor \* sensor plate size

## Left:

Left is a 0.25 micron wide constant block on the left side of plate in each cell. This is being kept in the model to isolate the adjacent cells.

#### Space:

Space is another constant 2.25 micron block adjacent to the 'Left'.

# Guard:

Guard is a constant 1.5 micron wide and 0.2 micron thick grounded grid which is of major concern in this work. It acts as circuit ground path for the sensing elements and contributes to parasitic capacitance. These grids are very left of Plate in each cell. In the following chapters some models are given to reduce the capacitance arising from grounded grids.

## **Right:**

Right is a constant 1.5 micron block at the far end of each sensor cell.

# SiN:

These are the rectangular silicon nitride blocks which isolate sensor plate from the underlying shield plates in the model. This nitride film thickness is 0.5 microns.

# IMD:

These are the Inter Metal Dielectrics of thickness 3 microns which isolate the silicon substrate from the other elements of each cell in the model.

# **3.1.2 Materials Used** [16]

# Silicon:

Silicon is used as substrate in the model. Silicon's atomic structure makes it an extremely important semiconductor. Highly purified Silicon, doped with elements such as boron, phosphorus, and arsenic, is the basic material used in computer chips, transistors, silicon diodes, and various other electronic circuits and switching devices.

# Silicon dioxide:

Silicon dioxide is used routinely as inter metal dielectric (IMD). Silicon dioxide is one of the most commonly encountered substances in electronics industry. It has the unique properties such as, the only native oxide of a common semiconductor which is stable in water and at elevated temperatures, an excellent electrical insulator, and capable of forming a nearly perfect electrical interface with its substrate.

# Silicon Nitride:

This material is used as an insulator between the sensor plate and the underlying shield plate. It is also used as passivation layer which encapsulates the sensor plates. "Bulk" silicon nitride, Si3N4, is a hard, dense, refractory material. It's structure is quite different from that of silicon dioxide. CVD silicon nitride is generally amorphous, but the material is much more constrained in structure than the oxide. As a result, nitride is harder, has higher stress levels, and cracks more readily..

#### Tantalum:

Tantalum is used for sensor plates, underlying shield plates and guard grids in the model. It is a very hard metal and almost completely immune to chemical attack at temperatures below 150°C. Tantalum is used to make a variety of alloys with desirable properties such as high melting point, high strength etc. Tantalum has unique electrical, chemical and physical properties that lead to its application in a growing number of new and highly sophisticated applications. This is used as sensor plates because its hardness makes plates less prone to mechanical scratch damage, compression etc.

#### Sea Water:

A "standard" sea water has been defined as one containing 35 grams of salts per kilogram of solution. The human sweat has almost the same properties of sea water, hence this material is assigned to all the test objects in this work in order to get the effect of sweating finger.

### **3.2 Virtual Test Objects**