Graduate Theses, Dissertations, and Problem Reports

2001

# Scenario-based verification and validation of dynamic UML specifications

Alaa El-Sayed Ibrahim West Virginia University

Follow this and additional works at: https://researchrepository.wvu.edu/etd

# **Recommended Citation**

Ibrahim, Alaa El-Sayed, "Scenario-based verification and validation of dynamic UML specifications" (2001). *Graduate Theses, Dissertations, and Problem Reports.* 1114. https://researchrepository.wvu.edu/etd/1114

This Thesis is protected by copyright and/or related rights. It has been brought to you by the The Research Repository @ WVU with permission from the rights-holder(s). You are free to use this Thesis in any way that is permitted by the copyright and related rights legislation that applies to your use. For other uses you must obtain permission from the rights-holder(s) directly, unless additional rights are indicated by a Creative Commons license in the record and/ or on the work itself. This Thesis has been accepted for inclusion in WVU Graduate Theses, Dissertations, and Problem Reports collection by an authorized administrator of The Research Repository @ WVU. For more information, please contact researchrepository@mail.wvu.edu.

# Scenario-based Verification and Validation of Dynamic UML Specifications

Alaa E. Ibrahim

Thesis Submitted to the College of Engineering and Mineral Resources at West Virginia University in partial fulfillment of the requirements for the degree of

> Master of Science in Electrical and Computer Engineering

Hany H. Ammar, Ph.D., Chair Ali Mili, Ph.D. Vittorio Cortellessa, Ph.D.

**Department of Computer Science and Electrical Engineering**

Morgantown, West Virginia 2001

Keywords: Verification and Validation, UML, Simulation, Automated, Timing Analysis, Timing Constraints, Risk assessment, Performance Modeling, Fault Injection

**Copyright 2001 Alaa E. Ibrahim**

#### ABSTRACT

# Scenario-based Verification and Validation of UML Dynamic Specifications

# Alaa E. Ibrahim

The Unified Modeling Language (UML) is the result of the unification process of earlier object oriented models and notations. Verification and validation (V&V) tasks, as applied to UML specifications, enable early detection of analysis and design flaws prior to implementation. In this work, we address four V&V analysis methods for UML dynamic specifications, namely: Timing analysis and automatic V&V of timing constraints, automated Architectural-level Risk assessment, Performance Modeling and Fault Injection analysis. For each we present: approaches, methods and/or automated techniques. We use two case studies: a Cardiac Pacemaker and a simplified Automatic Teller Machine (ATM) banking subsystem, for illustrating the developed techniques.

#### ACKNOWLEDGMENTS

I wish to express my deep gratitude to my research advisor, Dr. Hany Ammar for helping me define my research goals and for providing valuable guidance during this research.

I would also like to thank the members of my committee, Dr. Ali Mili and Dr. Vittorio Cortellessa for their support and review and for their time in serving on my committee.

I would like also to express gratitude to the project team at Averstar Group, especially to Dr. Jim Dabney and Dr. Khalid Lateef for their directions, support and encouragement.

Many thanks to Dr. Sherif Yacoub, who invested from his time, knowledge and effort in this work. He has been an unfailing source of support and encouragement to me during all the research period.

Special thanks to Dr. Vittorio Cortellessa, for his patience, teaching and efforts in sharing his wide knowledge in Performance Modeling.

I also thank my parents for always motivating me to pursue higher education and to expand my scientific knowledge. I offer my sisters and friends heartfelt thanks for their invaluable consideration and moral support.

I am also grateful to all my colleagues in the research lab. Thank you for your help and for creating a very positive atmosphere that makes it easier to withstand the difficulties that sometimes arise.

This work was funded by the Averstar Group research grant to West Virginia University through the Software Engineering Research Center (SERC).

# TABLE OF CONTENTS

| CHAPTER 1 | : INTRODUCTION                                                   | 1  |

|-----------|------------------------------------------------------------------|----|

| 1.1 BAG   | CKGROUND                                                         | 1  |

| 1.2 PRC   | DBLEM STATEMENT                                                  | 2  |

| 1.3 Res   | SEARCH OBJECTIVES                                                | 2  |

| 1.4 The   | ESIS STRUCTURE                                                   | 3  |

| CHAPTER 2 | SIMULATION ENVIRONMENT                                           | 5  |

| 2.1 UM    | IL-RT MODELING AND SIMULATION TOOL                               | 5  |

| 2.2 Loc   | G FILES                                                          | 10 |

| 2.3 TIM   | IING DIAGRAMS                                                    |    |

| CHAPTER 3 | 3: THE CARDIAC PACEMAKER CASE STUDY                              | 13 |

| CHAPTER 4 | I: TEMPORAL V&V                                                  | 19 |

| 4.1 AU    | TOMATED V&V OF TIMING CONSTRAINTS                                | 19 |

| 4.1.1     | The first approach for Automatic timing constraints verification | 19 |

| 4.1.2     | The second approach for timing constraints verification          | 23 |

| 4.1.3     | Results and lessons learned                                      |    |

| 4.2 Thi   | E FOUR TIMING ANALYSIS METHODS                                   |    |

| 4.2.1     | Methods                                                          | 34 |

| 4.2.2     | The Cardiac Pacemaker Example                                    |    |

| CHAPTER 5 | 5: AUTOMATED RISK ASSES SMENT                                    | 42 |

| 5.1 INT   | RODUCTION                                                        |    |

| 5.1.1     | Dynamic Metrics                                                  | 43 |

| 5.1.2     | Component Dependency Graphs                                      |    |

| 5.1.  | 3 The Risk Analysis Algorithm                                          | 45      |

|-------|------------------------------------------------------------------------|---------|

| 5.2   | THE AUTOMATED ENVIRONMENT                                              |         |

| 5.3   | CONCLUSION AND FUTURE WORK                                             |         |

| СНАРТ | ER 6: FAULT INJECTION ANALYSIS                                         | 49      |

| 6.1   | MOTIVATIONS                                                            |         |

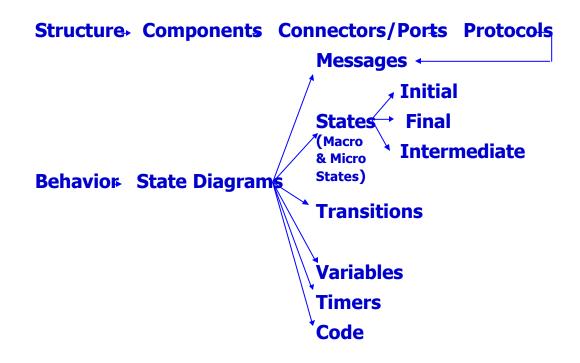

| 6.2   | UML-RT MODEL ELEMENTS                                                  | 50      |

| 6.3   | DOMAIN OF FAULTS IN UML-RT MODELS                                      |         |

| 6.3.  | 1 Structural Faults                                                    | 51      |

| 6.3.  | 2 Behavioral Faults                                                    | 52      |

| 6.4   | THE FAULT MODEL                                                        | 53      |

| 6.4.  | 1 State Selection Process                                              | 54      |

| 6.4.  | 2 State faults                                                         | 54      |

| 6.4.  | 3 State transition faults                                              | 55      |

| 6.4.  | 4 Timing Faults                                                        | 55      |

| 6.5   | PACEMAKER CASE STUDY EXPERIMENTATION                                   | 55      |

| 6.6   | CONCLUSIONS & FUTURE WORK                                              |         |

| СНАРТ | ER 7: PERFORMANCE MODELING                                             | 71      |

| 7.1   | INTRODUCTION                                                           | 71      |

| 7.2   | OUR APPROACH FOR PERFORMANCE MODELING OF CLIENT-SERVER SYSTEMS USING T | HE UML- |

| RT NO | ΓΑΤΙΟΝ                                                                 |         |

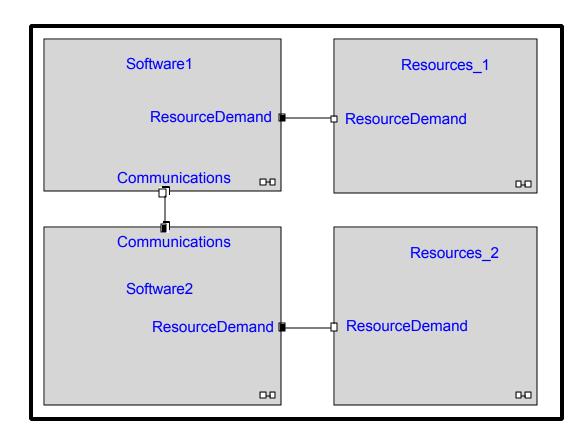

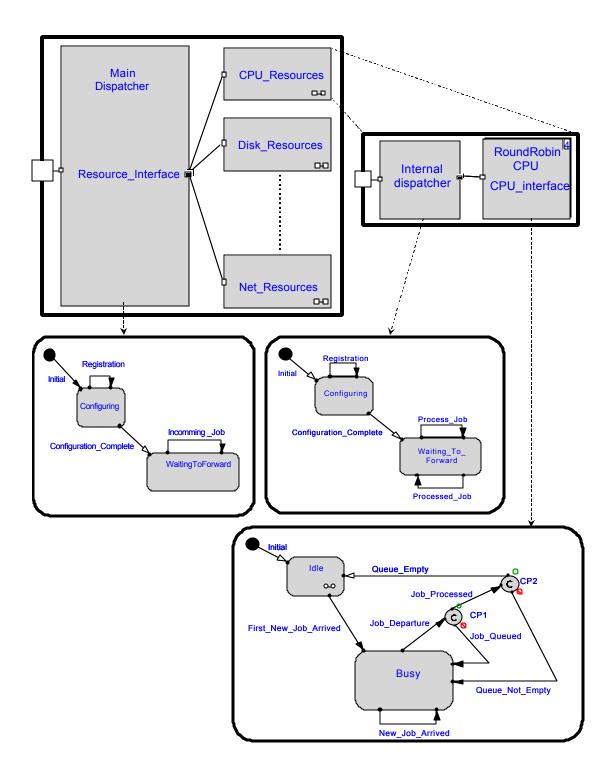

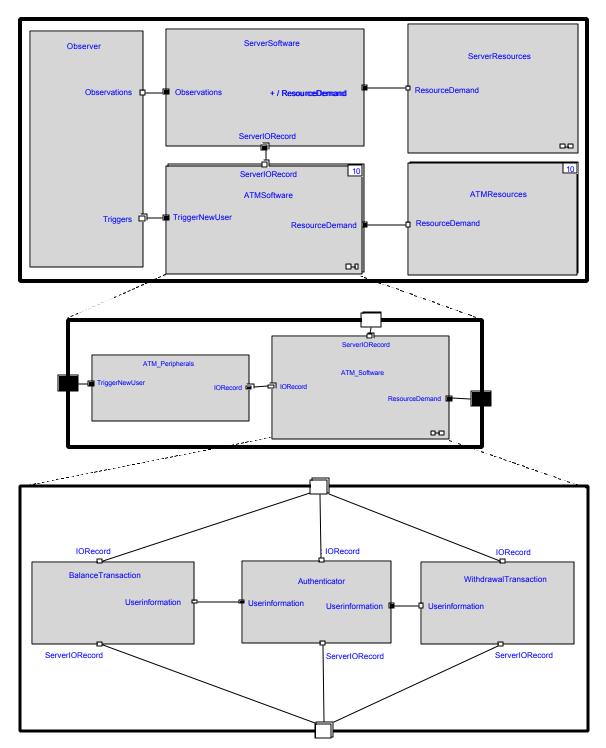

| 7.2.  | 1 A layered software architecture                                      | 72      |

| 7.2.  | 2 Representing the extended software architecture                      | 74      |

| 7.3   | EXAMPLE: SIMPLIFIED AUTOMATIC TELLER MACHINE (ATM) BANKING SUBSYSTEM   |         |

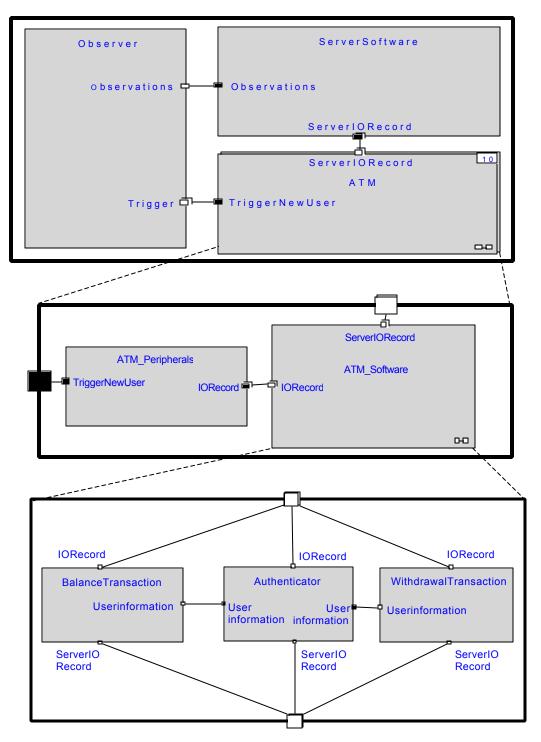

| 7.3.  | 1 ATM Architecture                                                     | 79      |

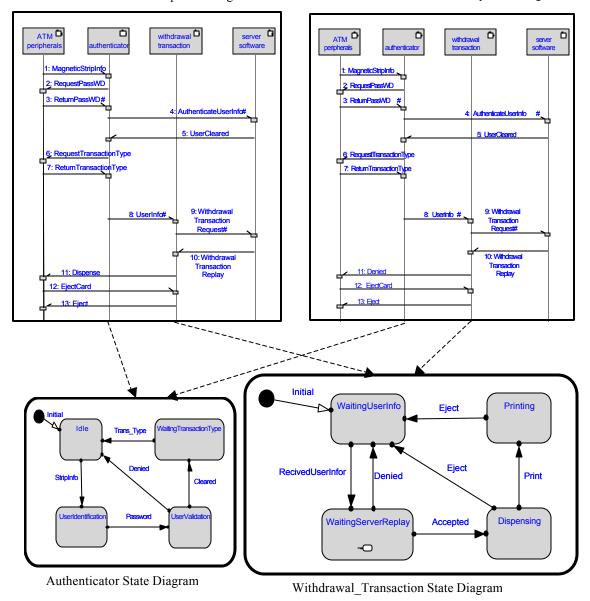

| 7.3.2    | Sequence Diagrams                        |    |

|----------|------------------------------------------|----|

| 7.3.3    | State Diagrams                           |    |

| 7.3.4    | Performance Modeling for the ATM Example |    |

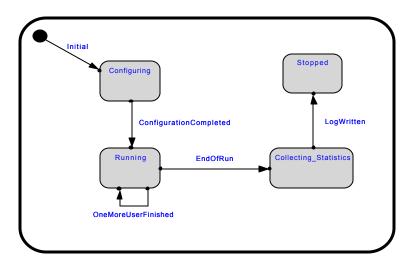

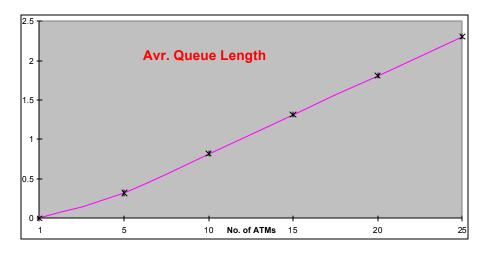

| 7.4      | EXPERIMENTS                              |    |

| 7.5      | CONCLUSION                               |    |

| CHAPTI   | ER 8: CONCLUSIONS AND FUTURE WORK        |    |

| 8.1      | TEMPORAL V&V                             |    |

| 8.2      | AUTOMATED ARCHITECTURAL-RISK ASSESSMENT  |    |

| 8.3      | FAULT INJECTION ANALYSIS                 |    |

| 8.4      | Performance Modeling                     |    |

| BIBLIOG  | RAPHY                                    | 96 |

| APPENDI  | X A VISUAL BASIC MACROS                  |    |

| APPENDIX | X B RISK MACRO                           |    |

| APPENDI  | X C ATM SEQUENCE DIAGRAMS                |    |

# LIST OF FIGURES

| Figure 1.1 | Flow chart of the thesis chapters                                                             | 4 |

|------------|-----------------------------------------------------------------------------------------------|---|

| Figure 2.1 | A Capsule ( <i>Top_Level_Capsule</i> ) and its Structure Diagram                              | 7 |

| Figure 2.2 | State Diagram of <i>First_Capsule</i> (top level)                                             | 8 |

| Figure 2.3 | State Diagram of the macro state <i>S</i> _1                                                  | 8 |

| Figure 2.4 | Environmental overall view                                                                    | 9 |

| Figure 2.5 | A sample-timing diagram                                                                       | 2 |

| Figure 3.1 | Structure diagram for the Pacemaker                                                           | 4 |

| Figure 3.2 | Main Use Case Diagram                                                                         | 7 |

| Figure 3.3 | A sample-timing diagram illustrating the timing constraints                                   | 8 |

| Figure 4.1 | High level view of the Automated Timing Constrains V&V process                                | 0 |

| Figure 4.3 | Constraint Driven Observer Modeling                                                           | 6 |

| Figure 4.4 | Use Case Driven Observer Modeling                                                             | 1 |

|            | Sample of Concurrency-based Timing Analysis for a Cardiac Pacemaker in the AVI erational mode | 8 |

| •          | Sample of the Performance-based analysis for a Cardiac Pacemaker in the AVI erational mode    | 9 |

| -          | Sample of the Timeout-based analysis for a Cardiac Pacemaker in the AVI operational ode       | 0 |

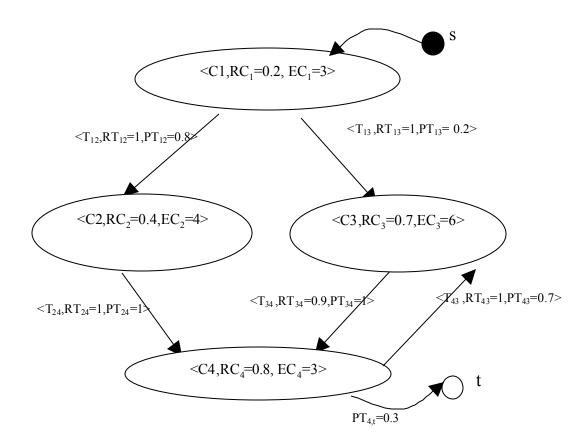

| Figure 5.1 | A Sample CDG 1 (source [33])                                                                  | 4 |

| Figure 5.2 | Risk Aggregation Algorithm (source [33])                                                      | 5 |

| Figure 6.1 | UML-RT model elements                                                                         | 0 |

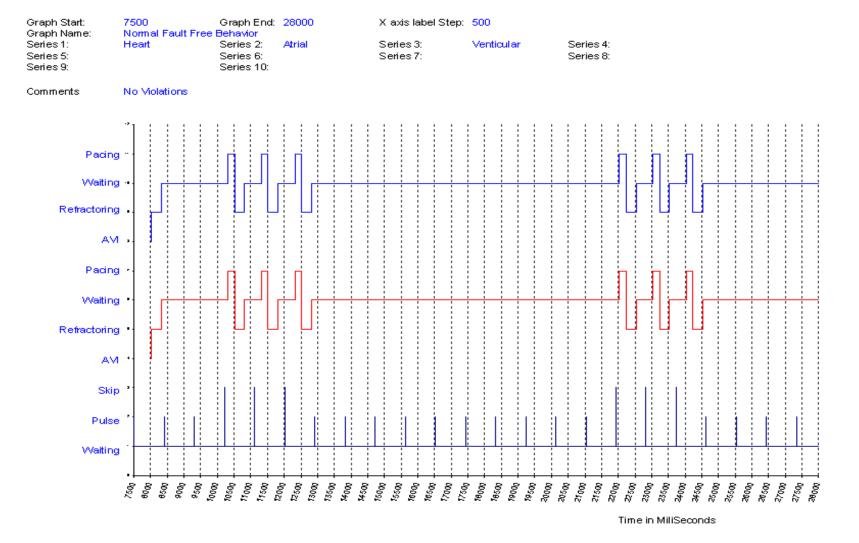

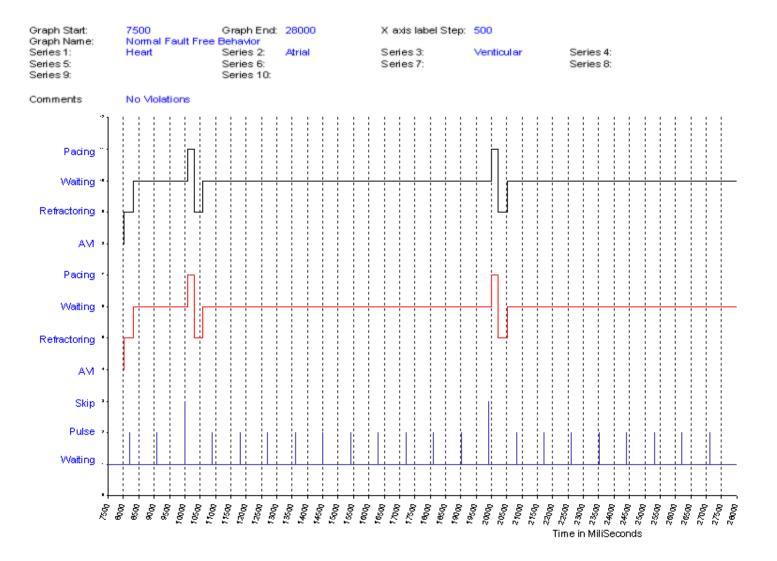

| Figure 6.2 | Pacemaker Expected Behavior (three pulses skipped)                                            | 9 |

| Figure 6.3 | Pacemaker Expected Behavior (one pulse skipped)                                               | 0 |

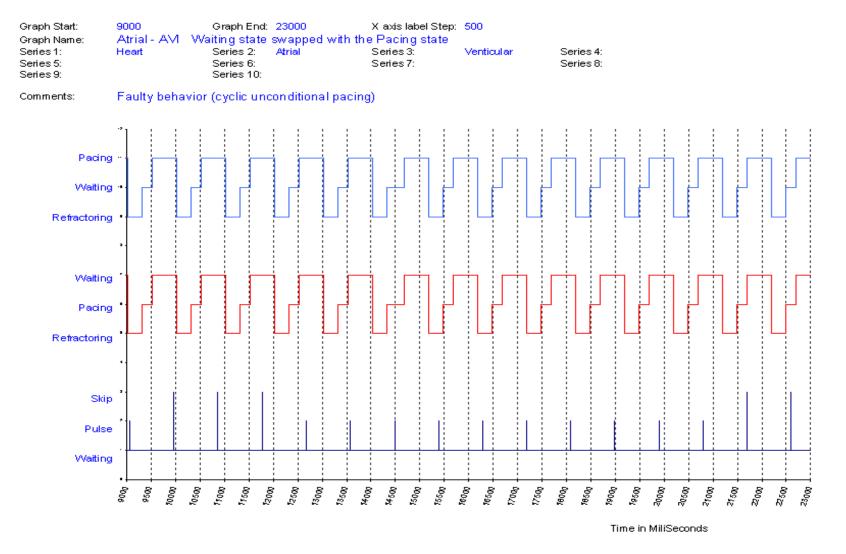

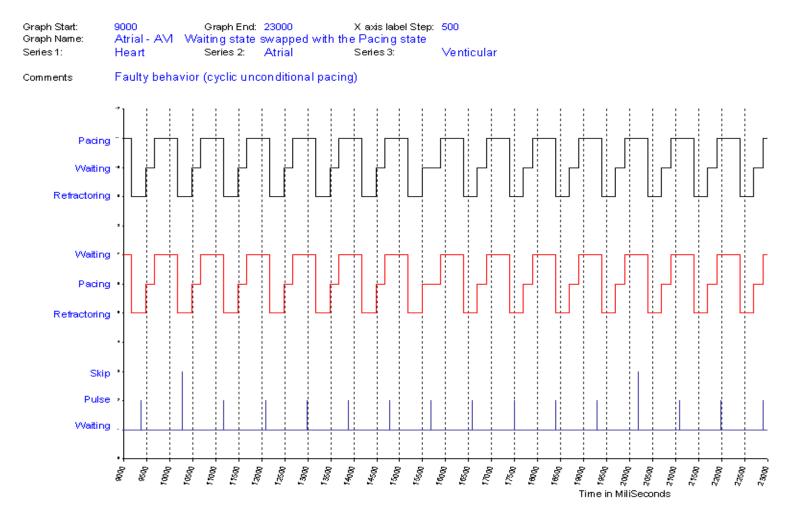

| Figure 6.4 State Swap (three pulses skipped)                                 | 61 |

|------------------------------------------------------------------------------|----|

| Figure 6.5 State Swap (one pulse skipped)                                    |    |

| Figure 6.6 Transition Swap (three pulses skipped)                            |    |

| Figure 6.7 Transition Swap (one pulse skipped)                               | 64 |

| Figure 6.8 Initial Sate Swap (three pulses skipped)                          | 65 |

| Figure 6.9 Initial Sate Swap (one pulse skipped)                             |    |

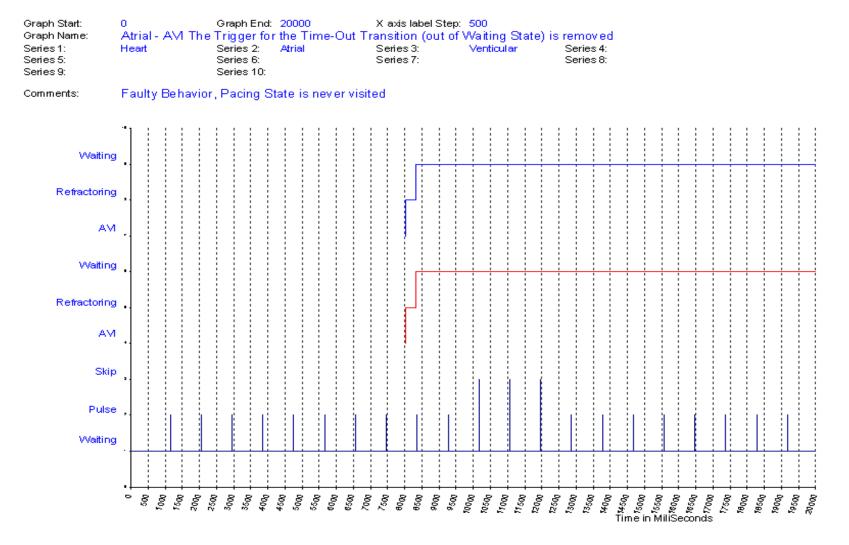

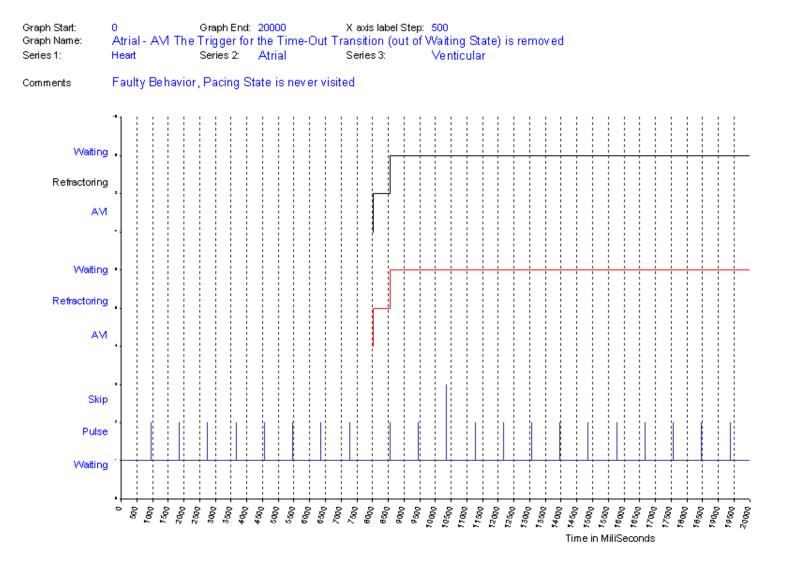

| Figure 6.10 Null Trigger (three pulses skipped)                              | 67 |

| Figure 6.11 Null Trigger (one pulse skipped)                                 |    |

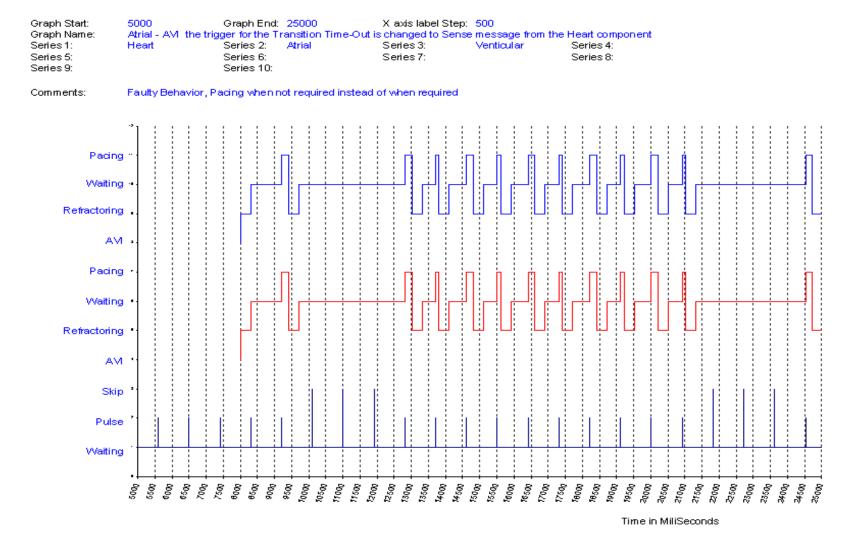

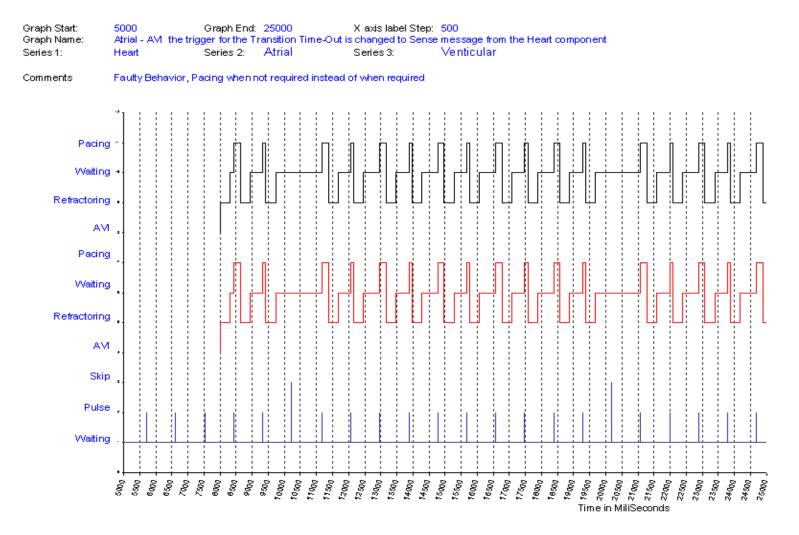

| Figure 6.12 Trigger Swap (three pulses skipped)                              | 69 |

| Figure 6.13 Trigger Swap (one pulse skipped)                                 | 70 |

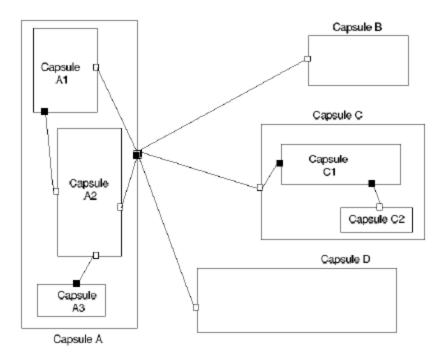

| Figure 7.1 Transparent diagram of Capsules and embedded Capsules             |    |

| Figure 7.2 Generic two-sides Capsule diagram                                 | 75 |

| Figure 7.3 Basic structure (Capsule and State Diagrams) of the resource side |    |

| Figure 7.4 ATM software Architecture (3 level nested view)                   |    |

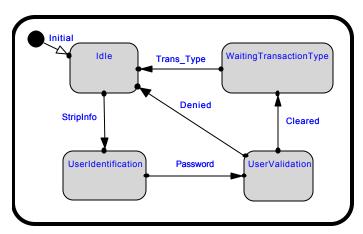

| Figure 7.5 Authenticator Component State Diagram                             |    |

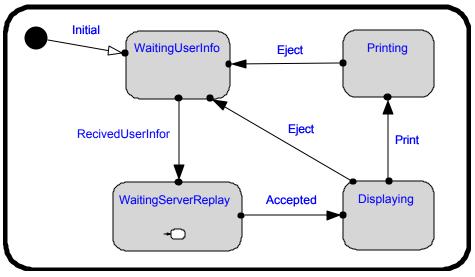

| Figure 7.6 BalanceTransaction Component State Diagram                        | 83 |

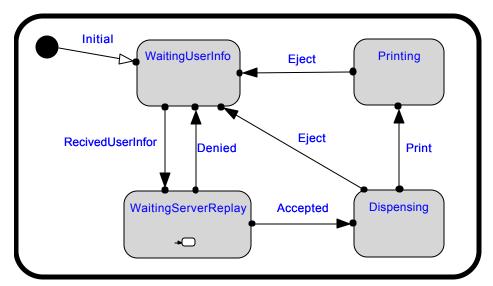

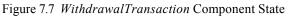

| Figure 7.7 WithdrawalTransaction Component State Diagram                     |    |

| Figure 7.8 Sample of Sequence Diagram to State Diagram translation           |    |

| Figure 7.10 Observer State Diagram                                           |    |

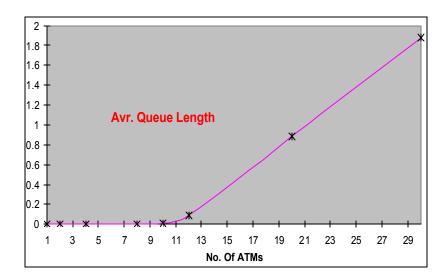

| Figure 7.11 Average CPU Queue Length (first experiment)                      |    |

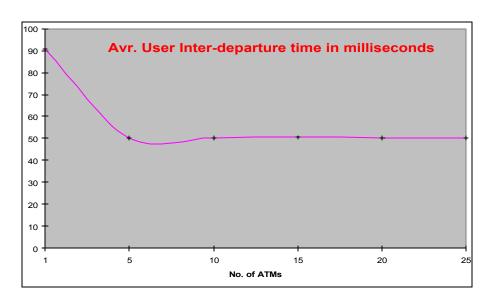

| Figure 7.12 CPU Throughput (first experiment)                                |    |

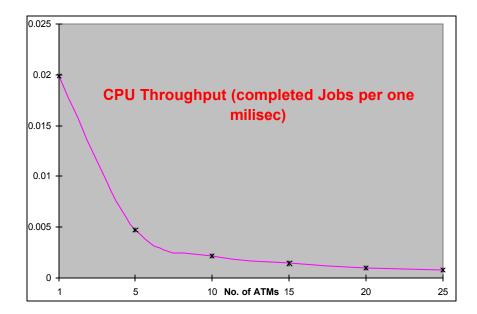

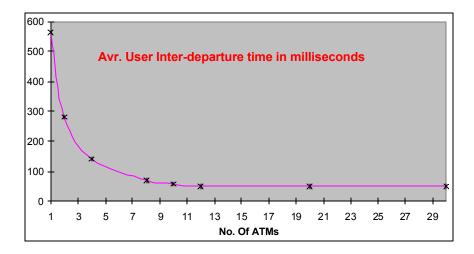

| Figure 7.13 Average User Inter-departure time (first experiment)             | 90 |

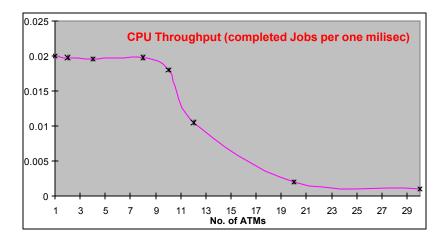

| Figure 7.14 Average CPU Queue Length (second experiment)                     |    |

| Figure 7.15 CPU Throughput (second experiment)                                                   |

|--------------------------------------------------------------------------------------------------|

| Figure 7.16 Average User Inter-departure time (second experiment)                                |

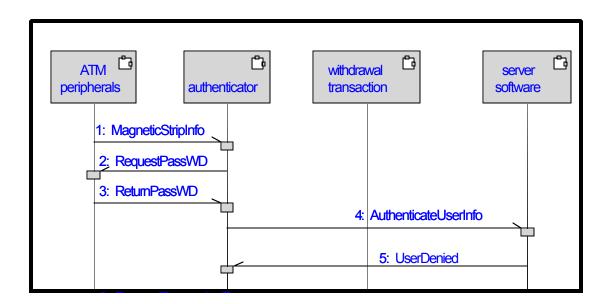

| Appendix C Figure 1 Use_Denied: Sequence Diagram for failed Authentication 134                   |

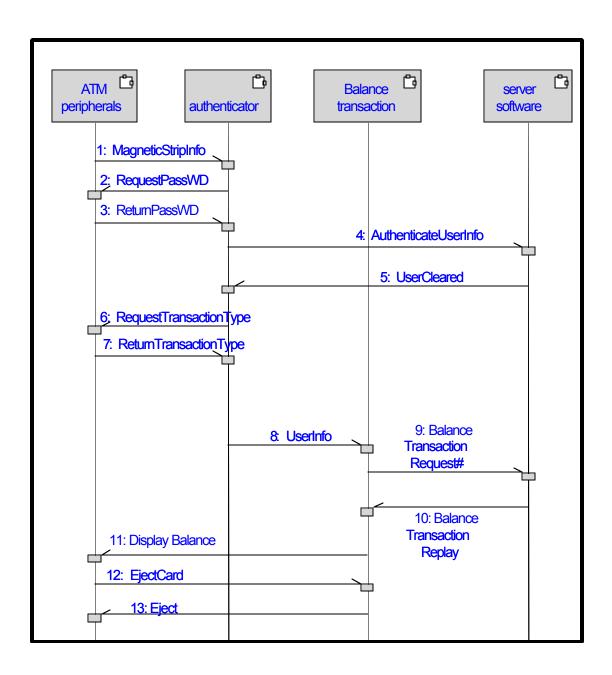

| Appendix C Figure 2 Balance: Sequence Diagram for balance inquiry transaction without            |

| statement printing                                                                               |

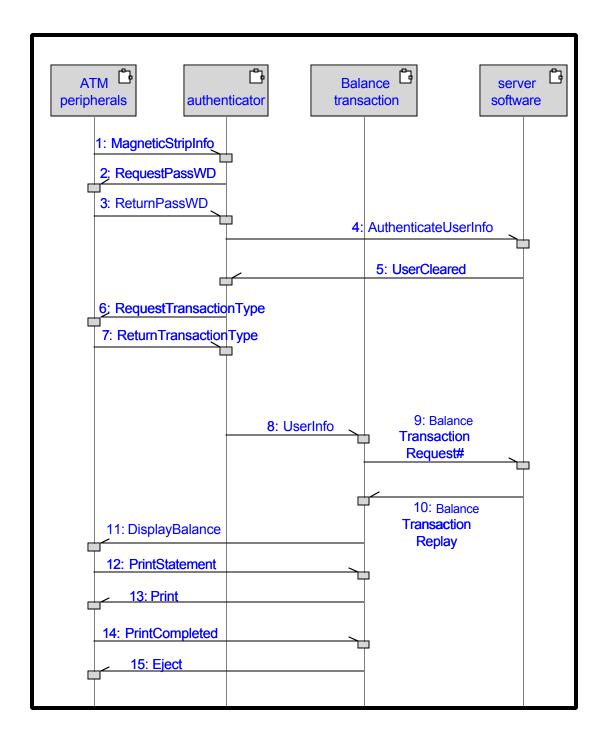

| Appendix C Figure 3 <i>Balance_Print</i> : Sequence Diagram for balance inquiry transaction with |

| statement printing                                                                               |

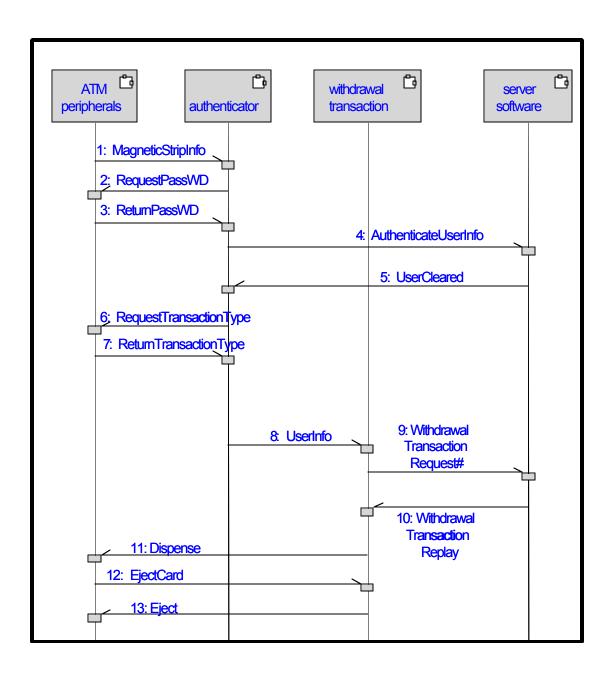

| Appendix C Figure 4 Withdrawal : Sequence Diagram for successful withdrawal transaction          |

| without statement printing                                                                       |

| Appendix C Figure 5 Withdrawal_Print : Sequence Diagram for successful withdrawal                |

| transaction with statement printing                                                              |

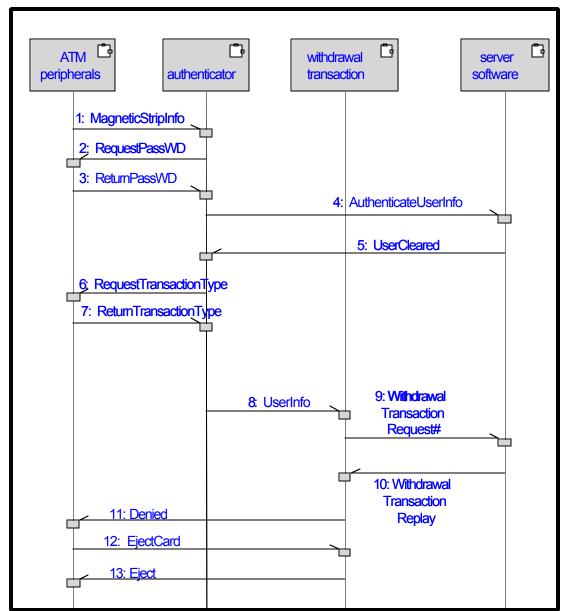

| Appendix C Figure 6 Withdrawal_Denied : Sequence Diagram for unsuccessful withdrawal             |

| transaction without statement printing                                                           |

# LIST OF TABLES

| Table 2.1 Summary of UML Extensions for ROOM, source [25]               | 6                 |

|-------------------------------------------------------------------------|-------------------|

| Table 4.1 Sample of the violation table from simulation with 350milisec | Ventricular_Model |

| Refractory time                                                         |                   |

| Table 4.2 Summery of Timing Analysis Methods                            |                   |

## **CHAPTER 1: INTRODUCTION**

The Unified Modeling Language (UML) is becoming a widely accepted standard notation for modeling software systems. The software development industry is embracing this modeling language for requirement analysis and the subsequent phases of software development lifecycle. Its success mostly relies on few elementary characteristics: different diagrams are provided (in an integrated framework) to represent the software model from different viewpoints, so explicitly specifying software aspects elsewhere hidden; the language is supported by a graphical representation, easy to use, that is not far from the classical diagrams used before introducing UML (e.g., State Diagrams, Class Diagrams, Sequence Diagrams); no standard software development process is coupled to the notation, thus software designers may decide to use whatever subset of diagrams that can better fit their application requirements, and organize an application oriented software process. As a result of the rapid success, Verific ation and Validation (V&V) teams need to devise methods for evaluating UML artifacts. V&V analysis can be categorized as static or dynamic. Static analysis helps V&V teams in reviewing the structure of UML models and generating metrics such as class size, the size of the hierarchy and static complexity measures. The complex dynamic behavior of many applications, especially real-time applications, motivates a shift in interest from traditional static analysis to dynamic analysis. Dynamic analysis is performed to analyze the behavior of objects as expected at run time.

## 1.1 Background

UML was explicitly born as an "open" project [17], with the potential of embedding additional notations and tools to satisfy specific design requisites. Along this trace, Rational Software [21](the UML originator) and ObjecTime Limited [16](the Real-Time Object Oriented Modeling "ROOM" originator) collaborated in defining UML for Real-Time [11,25] (UML-RT), an extension of UML optimized for real-time embedded software development. ROOM was introduced to study the dynamic aspects of applications modeled as concurrently executing objects with complex dynamic behavior. ROOM models are intended for simulating the application execution scenarios and complex object behavior. UML specification provides a State Machine package as a sub package of the behavioral elements package. UML state machines formalism is a

variant of Harel Statecharts and it incorporates several ROOMcharts concepts and ROOMcharts are a valiant of ROOM modeling language [30]. Dynamic analysis can be conducted on executable design models using several tools, such as Rational Rose Real-Time (RRT) from Rational Software Inc. and ObjecTime Developer from ObjecTime Inc., and hence the dynamic behavior of applications can be verified and assessed.

#### 1.2 Problem Statement

V&V can be conducted at various development phases. Early V&V of software specification and analysis artifacts is encouraged before large investment is made in development. V&V of UML specifications can be done at an early development phase - prior to implementation - using scenarios, requirements and simulation models. Although UML is a rich analysis and design modeling language, it does not define how to study the dynamic aspects of the models through simulation, a capability that is required to monitor and assess the expected run-time behavior of software systems. V&V teams being much smaller than development teams must use efficient techniques to perform their analysis. At present mostly manual methods are being used to analyze UML models. Given the size and complexity of the large software systems, the manual efforts are time-consuming, tedious and error prone. Therefore automated techniques for V&V of UML models need to be developed.

#### 1.3 Research Objectives

In this work, techniques are developed to help V&V teams in performing there task in the early development stages of UML dynamic specifications. We develop methods and approaches. We extend tool support for fast and automatic deployment of the developed techniques. Four areas are investigated in this thesis:

Developing automated techniques and methods for the V&V of the temporal characteristics of software systems (more importantly Real-Time software systems). Temporal V&V and timing analysis are not part of UML specifications, thus studying the conformance of the UML model with the timing constraints specified in the requirements is needed.

- 2. The automated generation of software metrics for ordering the components, connectors and subsystems, based on well defined metrics is needed. This will help in allocating the resources during the next development phases and in assessing the software quality. Dynamic component complexity and connector coupling metrics developed in [35] and the Architectural-Risk assessment methodology developed in [33] are selected for this purpose.

- 3. Optimizing the number test-case scenarios required for software testing, and assessing component severity are the motives behind the third area of investigation where we develop and assess a fault model for fault injection analysis.

- 4. Studying the performance of software systems, where queuing networks that model the performance characteristics of software systems have been well investigated. Interest in performance modeling for UML specifications has gained an increasing acceptance in industry standard. In [2] UML sequence diagrams where used as the starting point for performance model generation. In this study we aim to utilize the simulation capabilities in studying the performance characteristics of UML-RT models through resource modeling.

#### 1.4 Thesis Structure

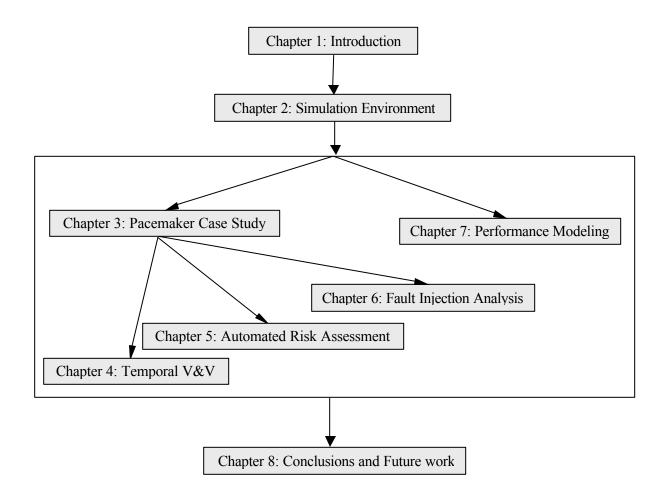

Considering the four areas of investigation mentioned above and two case studies, we structure this thesis as follows (figure 1.4). Chapter 2 introduces our simulation environment and the tool extensions developed and chapter 3 presents the first case study: the software model of a Cardiac Pacemaker device. Chapter 4 discusses automated temporal V&V techniques. Chapter 5 discusses the automatic extraction of dynamic metrics and architectural-level risk. Chapter 6 presents techniques for fault injection analysis. Chapter 7 discusses performance modeling based on UML dynamic specifications in simulation environments (the fourth area of investigation) and we use a simple abstraction of the software of the Automatic Teller Machine (ATM) banking subsystem. Finally we conclude and discuss potential areas for future work.

Figure 1.1 Flow chart of the thesis chapters

## **CHAPTER 2: SIMULATION ENVIRONMENT**

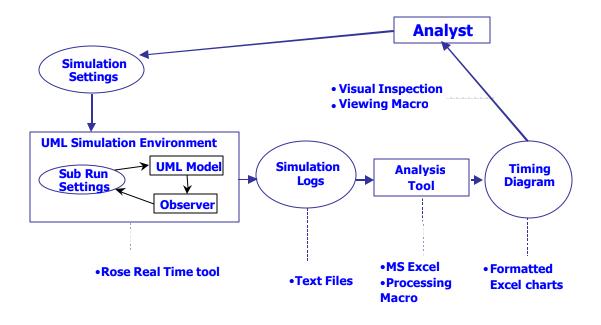

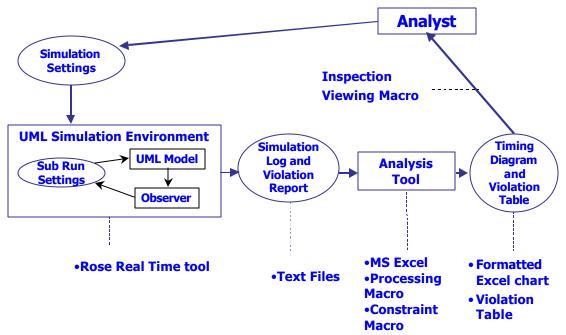

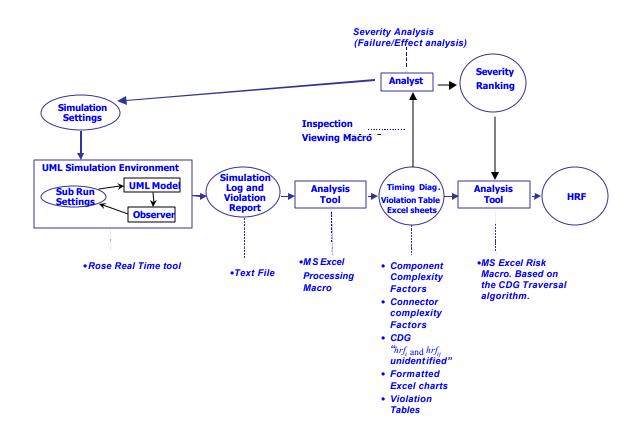

Our general approach for V&V of UML models is based on simulating the dynamic specifications. Figure 2.4 shows an overall view of our environment in which we developed methods and techniques to perform the required tasks. The simulation settings for a particular scenario are adjusted by the analyst and the UML model is executed in a given simulation environment to produce simulation logs for that particular scenario. We generate the timing diagram from processing the simulation log files. The generated timing diagrams are inspected visually to determine and assess the correctness of the developed methods and techniques, and to analyze the logic behind our findings. Elements in our environment are:

- 1. Rational Rose Real-Time 6.0 [22] RRT as the modeling and simulation tool.

- 2. Simulation log files and the log analysis tool that is composed of Microsoft Excel and Visual Basic Scripts that were develop.

- 3. The timing diagrams are charts showing each object as a series of changes in its states versus time.

#### 2.1 UML-RT modeling and simulation tool

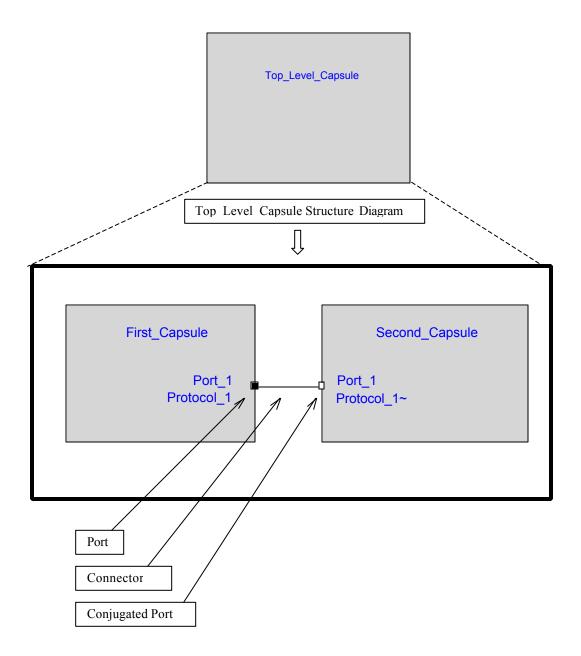

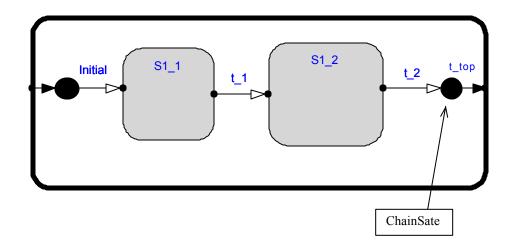

In [25] the derivation of the set of architectural constructs that integrate ROOM notation in UML were presented. These architectural constructs are derived from general UML modeling concepts using UML extensibility mechanisms. Table 2.1 provides a summary for these extensions, as a brief description of the basic constructs used in modeling the system structure and component behavior. Three principal constructs; Capsules, Ports and Connectors, are used to explicitly describe the system structure. In a Capsule collaboration diagram, Capsules and Ports are stereotype roles, and Connectors are association roles. Behavior is modeled using Protocols and state machines. A Protocol specifies the desired behavior over a connector and compromises a set of participants, each participant plays a specific ProtocolRole. A Protocol state machine specifies valid communication sequence and is the standard UML state machine. Capsule behavior is defined in UML state machine where the stereotype (ChainState) is a state that is used in case of

transitions that are split into a transition that terminates on the boundary of the state and a transition that propagated into the state (in case of hierarchical state machines).

| Metamodel Class | Stereotype   |

|-----------------|--------------|

| Collaboration   | Protocol     |

| ClassifierRole  | ProtocolRole |

| Class           | Port         |

| Class           | Capsule      |

| State           | ChainState   |

Table 2.1 Summary of UML Extensions for ROOM, source [25]

Figure 2.1 shows a Capsule named *Top\_Level\_Capsule* and its Structure Diagram. The Structure Diagram of *Top\_Level\_Capsule* contains two Capsules: *First\_Capsule* and *Second\_Capsule*, each with one port named *Port\_1*. *Port\_1* in *First\_Capsule* is assigned a ProtocolRole *Protocol\_1* and *Port\_1* in *Second\_Capsule* is assigned a ProtocolRole *Protocol\_1*~, which is the conjugate of *Protocol\_1*. As mentioned earlier a Protocol defines the flow of messages between ports. Messages are categorized into incoming and outgoing messages. In a conjugated Port the messages defined in the Protocol as incoming messages are defined as incoming messages in the ProtocolRole assigned to the Port. A connector connects the two ports and works as a media for message delivery.

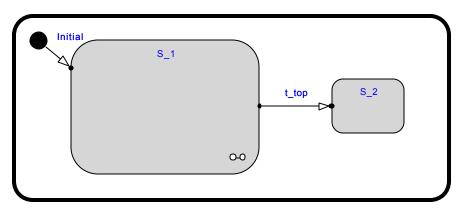

Figure 2.2 shows the State Diagram of *Second\_Capsule*. *Second\_Capsule* has two states *S\_1* and *S\_2*, and two transition;  $t\_top$  and the initial transition that defines the initial state. *S\_1* is a macro state that can be expanded into another State Diagram shown in figure 2.3. S\_1 has two states and three transition,  $t\_1$ ,  $t\_2$  and the initial transition.  $t\_2$  is a transition top a ChainState. Each transition is configured with a message that defines its firing conditions, except transitions from ChainStates like  $t\_top$ .

Figure 2.1 A Capsule (Top\_Level\_Capsule) and its Structure Diagram

Figure 2.2 State Diagram of *First\_Capsule* (top level)

Figure 2.3 State Diagram of the macro state  $S_1$

A typical early model of a software product is known as the software architecture, that is essentially a graph whose nodes represent software components and arcs represent software connectors. In order to provide to a software architecture the potential to represent the same software at different levels of detail, it can be hierarchically structured. In other words, a component can be detailed by describing its internal structure of subcomponents and connectors, while unvarying its external structure consisting of connectors with other components.

UML notation does not explicitly provide a diagram to describe a software architecture, which is in fact not necessary. The RRT tool allows building a diagram of components and connectors, where each component is represented by a Capsule and its Ports as interfaces to which Connectors are associated to exchange messages with other Capsules. The suitable hierarchical structure that such a software architecture should have is also provided, by allowing to detail the internal structure of a Capsule with other Capsules and Connectors.

Figure 2.4 Environmental overall view

The simulative nature of this tool requires as a minimum, in order to run such a scheme, a dynamic description of the behavior of each Capsule belonging to the lowest levels of the hierarchy, that is each Capsule that does not contain other Capsules. This dynamic (behavioral) description is represented in the Capsules State Diagrams as part of the UML specifications.

Figure 2.4 shows an overview of our simulation environment, RRT as the main tool and Visual Basic Scripts running from within Microsoft Excel as tool extensions.

#### 2.2 Log files

The log files are two text files. The first (state log file) contains an entry for each state change in each component during a simulation run, where each entry is composed of: the simulation time of the entry, the object and the new state. The second (message log file) contains an entry for each message sent in the system during a simulation run, where each entry is composed of: the send time of the message, the source object, the destination object and the message name.

#### 2.3 Timing Diagrams

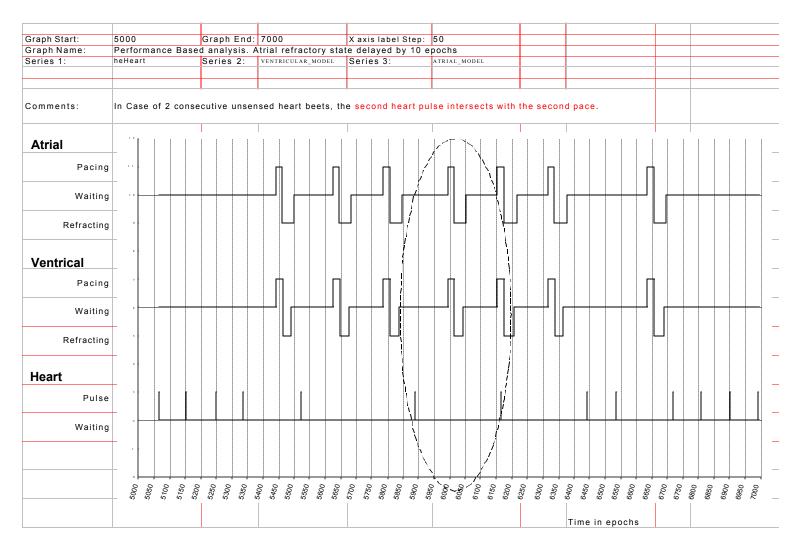

Figure 2.4 shows a sample-timing diagram from the Cardiac Pacemaker case study that will be presented later in chapter 3. The x-axis is a time series of 1 milisec with labels every 100 milisec and on the y-axis are the states of three objects. The first object named "Heart" has two states: Pulse and Waiting, the second and third objects named "Ventricle" and "Atrial" respectively each has three states: Pacing, Waiting and Refractory. For each object a series of the state changes is plotted on the timing diagram. The fields "Graph Start" and "Graph End" are used by the viewing macro to define the starting and ending values of the x-axis, which corresponds to the window of time, in a single simulation run, to be displayed.

For automatic generation of timing diagrams from simulation logs, two Visual Basic macros were developed, Processing macro and Viewing macro, within Microsoft Excel environment. First, the processing macro, which recognizes all executed objects and all their involved states, generates numeric distinct codes for all involved states in each object, adjusts values to enforce continuous vertical and horizontal line representation of state changes, configures x-axis as a time series of milliseconds, y-axis as state codes, and each object as a series, and automatically generates an Excel chart for each simulation run. Appendix A shows the Processing macro as a subroutine named "Processing\_Macro()" in Visual Basic Script. Bellow we show the steps followed by the Processing macro in processing the log file.

- 1. Extract all the Capsules "Objects" in the log file.

- 2. Extract the Object names and their states coded in continuous numeric state codes. i.e. For each Object: extract all states and generate a consecutive state code for each

- 3. For each Object: use the state codes to generate an eleven columns log table with time as the first column and the rest as the states in state code.

- 4. Create continuous lines (horizontal and vertical) from the ten fragmented series representing the state changes (in state codes) of the ten Objects.

- 5. Size the chart and force the start to be 0 milisec and the end to be 20000 milisec.

The second macro is the viewing macro, which enables the analyst to zoom in and out of the timing diagram and adjust the window of time to be viewed. Appendix A shows the Viewing macro as a subroutine named "Viewing\_Macro()" in Visual Basic Script. The basic function is to resize the chart (figure 2.5) based on the start, end and step fields.

|            | 5000 |       |       |        | aph E |      |      |           |        |                 |      | bel Step             |      |      |      |      |       |        |       |      |       |      |      |       |       |      |    |

|------------|------|-------|-------|--------|-------|------|------|-----------|--------|-----------------|------|----------------------|------|------|------|------|-------|--------|-------|------|-------|------|------|-------|-------|------|----|

|            |      | irren | cy ba |        |       |      |      |           |        |                 |      | rial and             |      |      |      | armo | delsa | are de | layed | by 1 | 0 epo | chs  |      |       |       |      |    |

|            |      |       |       | than c |       | sens |      | nsecut    | tive h | eart            |      | s, the ne            | xt h |      | beet |      |       |        |       |      |       |      |      |       |       |      |    |

|            |      |       |       |        |       |      |      |           |        |                 |      | ayed fro<br>t queuin |      |      |      |      |       |        |       |      |       |      |      | delay | ed by | atle | •a |

| Atrial     | 12   |       |       |        |       |      |      |           |        |                 | ;    |                      | +    | 1    |      |      | I     |        |       |      |       |      |      |       |       |      |    |

| Pacing     | n -  |       |       |        |       |      |      | Π         |        | 7               |      |                      | ľ    | •    | Π    |      |       |        |       |      |       |      |      | ]     |       |      |    |

| Waiting    | 10 - |       |       |        |       |      |      | ╵         |        |                 |      |                      |      |      |      |      |       |        |       |      |       |      |      |       |       |      | -  |

| Refracting | 9 -  |       |       |        |       |      |      |           |        |                 |      |                      | ļ    |      | L    | J    |       |        |       |      |       |      |      |       |       |      |    |

| Ventrical  | 8 -  |       |       |        |       |      |      |           |        |                 |      |                      |      |      |      |      |       |        |       |      |       |      |      |       |       |      |    |

| Pacing     | 7 -  |       |       |        |       |      |      | $\square$ |        | $\left \right $ |      | Π                    | ſ    |      |      |      |       |        |       |      |       |      |      | ]     |       |      |    |

| Waiting    | 6 -  |       |       |        |       |      |      |           |        |                 |      |                      |      |      |      |      |       |        |       |      |       |      |      |       |       |      | -  |

| Refracting | s -  |       |       | L      |       |      |      |           |        |                 |      |                      |      |      |      |      |       |        |       |      |       |      |      |       |       |      |    |

| Heart      | 4 -  |       |       |        |       |      |      |           |        |                 |      |                      |      |      |      |      |       |        |       |      |       |      |      |       |       |      |    |

| Pulse      | 3 -  |       |       |        |       |      |      |           |        |                 |      |                      |      |      |      |      |       |        |       |      |       |      |      |       |       |      |    |

| Waiting    | 2 -  |       |       |        | _1    |      |      |           |        | 1               |      |                      | -    |      |      |      |       |        |       | I    |       | 1    |      |       |       |      | -  |

|            | 2000 | 5100  | 5200  | 2300   | 5400  | 5500 | 5600 | 5700      | 5800   | 5900            | 6000 | 6100                 | 6200 | 6300 | 6400 | 6500 | 6600  | 6700   | 6800  | 6900 | 7000  | 7100 | 7200 | 7300  | 7400  | 7500 | -  |

Figure 2.5 A sample-timing diagram

# **CHAPTER 3: THE CARDIAC PACEMAKER CASE STUDY**

We have selected as a case study a cardiac pacemaker (Pacemaker) device [4, pp177] to discuss the applicability of the proposed approaches and methods. The pacemaker is a critical real-time application. An error in the software operation of the device can cause loss of the patient's life. Therefore, it is necessary to model its design in an executable form to validate its temporal behavior. We have used RRT simulation environment [22] and dynamic UML specifications [30] to model and gather simulation statistics.

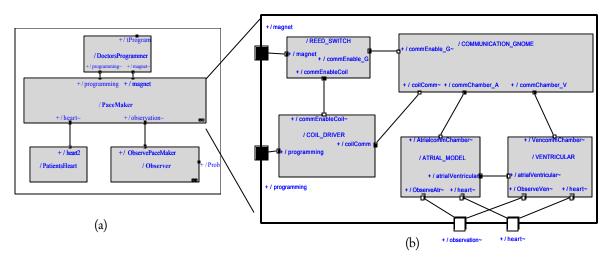

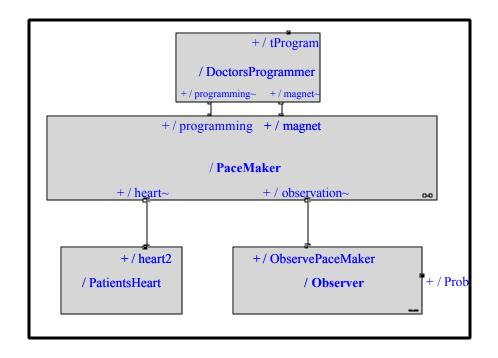

A cardiac pacemaker is an implanted device that assists cardiac functions when the underlying pathologies make the intrinsic heartbeats low. The pacemaker runs in either a programming mode or in one of operational modes. During programming, the programmer specifies the type of the operation mode in which the device will work. The operation mode depends on whether the Atrium, Ventricle, or both are being monitored or paced. The programmer also specifies whether the pacing is inhibited (I) or triggered (T). For the purpose of this paper, we limit our discussion to the AVI operation mode. In this mode, the Atrial portion of the heart is paced (shocked), the Ventricular portion of the heart is sensed (monitored), and the Atrium is only paced when a Ventricular sense does not occur; i.e., inhibited (I). Figure 3.1 shows (a) the system structure diagram of the external components and the pacemaker design model. The external components are modeled for simulation purposes. In the pacemaker example the Programming device (DoctorsProgrammer) is used to configure the pacemaker's operational mode. Therefore it appears as one of the components interacting with the pacemaker components in the Programming scenario only, whereas the heart is represented by the PatientsHeart component and is interacting with the pacemaker in all the operational modes. The Observer component shown in figure 3.1 (a) is the external monitoring component that we discuss in chapter 4. The pacemaker consists of the following components: (shown in figure 3.1 (b))

*Reed\_Switch:* A magnetically activated switch that must be closed before programming the device. The switch is used to avoid accidental programming by electric noise.

Figure 3.1 Structure diagram for the Pacemaker.(a) Pacemaker and all external Capsules (context level).(b) Pacemaker internal Structure Diagram

*Coil\_Driver:* Receives/sends pulses from/to the DoctorsProgrammer. These pulses are counted and then interpreted as a bit of value zero or one. These bits are then grouped into bytes and sent to the communication gnome. Positive and negative acknowledgments as well as programming bits are sent back to the programmer to confirm whether the device has been correctly programmed and the commands are validated.

*Communication\_Gnome:* Receives bytes from the coil driver, verifies these bytes as commands, and sends the commands to the Ventricular and Atrial models. It sends the positive and negative acknowledgments to the coil driver to verify command processing.

*Ventricular\_Model and Atrial\_Model:* These two actors are similar in operation. They both could pace the heart and/or sense heartbeats. The AVI mode is a complicated mode, as it requires coordination between the Atrial and Ventricular models. Once the Pacemaker is programmed the magnet is removed from the Reed\_Switch. The Atrial\_Model and Ventricular\_Model communicate together without further intervention. Only battery decay or some medical maintenance reasons force reprogramming.

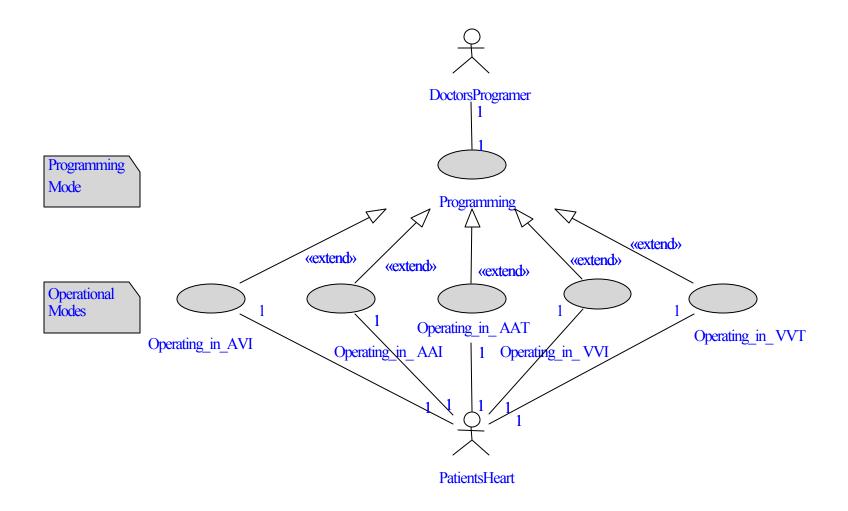

A hierarchical UML state machine models the behavior of each component. As mentioned earlier, a pacemaker can be programmed to operate in one of several modes depending on which part of the heart is to be sensed and which part is to be paced. The analysis of the device operation defines six scenarios. Figure 3.2 show the main Use Case diagram and all the relationships among the six Use Cases and the two actors, DoctorsProgrammer and PatientsHeart. Each scenario, in the pacemaker, maps to a Use Case, one for the programming scenario and five for the operational modes. The AAI operational scenario: in which the Ventricular Model is Idle and the Atrial Model is sensing and pacing the heart when a heartbeat is not sensed. The AAT operational scenario: in which the Ventricular Model is Idle and the Atrial Model is sensing and pacing the heart when a heartbeat is not sensed. The VVI operational scenario: in which the Atrial Model is Idle and the Ventricular Model is sensing and pacing the heart when a heartbeat is not sensed. The VVT operational scenario: in which the Atrial Model is Idle and the Ventricular Model is sensing and pacing the heart when a heartbeat is sensed or not. We only use the AVI Operational scenario: in which the Ventricular Model senses the heart and the Atrial Model paces the heart when a heart beat is not sensed. In all scenarios a refractory period is then in effect after every pace.

Currently UML representation of timing constraints [30] is limited to construction marks on sequence diagrams (common in blueprints), labels, and message transmission and reception on sequence diagrams. We compose the AVI timing constraints from: elements representing the time of a message transmission and reception; elements mapping to the time of entry of a state are represented by the reception of the message that fired the transition. We applied our approaches in chapter 4 to the following two timing constraints of the AVI operational scenario.

The first timing constraint is on the paces generated by the pacemaker in response to unsensed heart pulses. The time to each pace corresponding to an unsensed pulse should be less than 350 milisec.

$\forall s_i \exists p_j \mid T(p_j)$ - $T(s_i) \le \epsilon$  and  $s_i \in S$  and  $p_j \in P$

where S is the set of all unsensed heart beats observed during a simulation run, S={s1, s2, ..., sn}, P is the set of all paces generated by the pacemaker to the heart during a simulation run, P={p1, p2, ..., pm} and  $\varepsilon$  is the maximum permissible delay of pacing after a heart beat is not sensed and is equal to 350milisec. Figure 3.3 shows two cases: in the first  $\varepsilon$  was not exceeded, while in the second it was exceeded and the result was Pacing the patients heart while a pulse is naturally in place.

The second timing constraint is on the refractory period, the time in which the pacemaker stays idle after every pace. The Atrial\_Model refractory time represents this period and is controlled by the Ventricular\_Model refractory state which intern is controlled by the Ventricular\_Model refractory time. The Atrial\_Model refractory time should be less than 350milisec.

$$\forall i_i \exists o_j \mid T(o_j) - T(i_j) < \epsilon \text{ and } i_i \in I \text{ and } o_j \in O$$

where I is the set of all transitions from the Pace state to the Refractory state in the Atrial\_Model, I = {i1, i2, ..., in}, O is the set of all transitions from the Refractory state to the Waiting state in the Atrial\_Model, O = {o1, o2, ..., om}, and  $\varepsilon$  is the maximum permissible refractory time for the Atrial\_Model and is equal to 350milisec.

Figure 3.2 Main Use Case Diagram

Figure 3.3 A sample-timing diagram illustrating the timing constraints

#### CHAPTER 4: TEMPORAL V&V

Capitalizing on the simulation environment (commercial tool "RRT, Microsoft Excel and Visual Basic Scripts" and the tool extensions "logging and automatic generated Timing Diagrams") described in chapter 2, the V&V analyst can inspect the timing diagrams to verify that the timing constraints are met. Moreover, two approaches for automatic V&V of timing constraints [8] are presented in this chapter, together with the results and the lessons learned, using the Pacemaker case study presented in chapter 3. As well as four timing analysis methods, and their deployment procedure to UML artifacts [34] are presented, together with samples of the results from the Pacemaker example.

#### 4.1 Automated V&V of Timing Constraints

The first approach is based of processing the simulation log files in search of constraint violations. While the second approach is based on an Observer component, modeled as an external entity to the modeled system and acting as a monitoring device. Hence two methods for modeling the timing constraints in the Observer Component, namely: Constraint driven and Use Case driven, are developed. The output in both approaches is a violation table, table 4.1 is a sample of a violation table. Figure 4.1 shows a high level view (process/product view) of the Automated Timing Constraints V&V process.

#### 4.1.1 The first approach for Automatic timing constraints verification

In this approach the violation algorithm shown below processes the message log file. The product is the violation table which is a list of violations and their time of occurrence in the simulation run. The violation algorithm consumes the message log file and the timing constraints. Each entry in the message log file contains the time of message occurrence, the message name, and the type of

Figure 4.1 High level view of the Automated Timing Constrains V&V process

occurrence (receive\_by or send\_by). The timing constraints are in the form of Boolean expressions containing elements that correspond to the time of the transmission or reception of a message and a constant to which the evaluated expression is compared. The timing constraints are coded in the algorithm in the form of a two dimensional array where each row represents one timing constraint and contains: the constant time value to which the expression is compared, the total number of elements in the expression, the set of elements which represent the time of a message occurrence ordered by their expected occurrence, the set of corresponding occurrence types (transmission or reception), and the set of operators acting on the corresponding element including the Boolean operator as the last operator. Examples are shown below.

For each constraint the algorithm scans the message log file and searches for the elements in order. For each element detected, the corresponding operator is applied on the temporary variable temp\_time and the element. The Boolean expression is evaluated after the last element is detected

and processed, and if it evaluates to false, an entry in the violation table is recorded in the form of the time and type of the violation.

# <u>Algorithm</u>

#### **Procedure Violation**

## Parameters

Consumes: log\_file\_entry<sub>i</sub>(time, message, occurrence), where  $0 < i < end_of_log_file$ timing\_constrain<sub>k</sub>(constant, no\_of\_elements, element<sub>h</sub>, occurrence<sub>h</sub>, operators<sub>h</sub>(first\_operand, second\_operand)), where 0 < k <=total\_no\_of\_timing\_constrains and 0 < h <= no\_of\_elements Produces: Violation Table(Stack[time,constrainID])

Initialization:

i = k = h = 1

$temp_time = 0$

Algorithm

```

while k \le total\_no\_of\_timing\_constrains do

i = h = j = 1

while h \le no\_of\_elements do

i = j

while i \le end\_of\_log\_file do

if log\_file\_entry_i.message = timing\_constraint_k.element_h AND

log\_file\_entry_i.occurrence = timing\_constraint_k.occurrence

timing\_constraint_k.operator_h(temp\_time, log\_file\_entry_i.time)

j = i

next h

end if

if h = no\_of\_elements AND timing\_constraint_k.operator_h(temp\_time, log\_file\_entry_ktime)

= False

push (log\_file\_entry_i.time, k)

end if

```

next i end while end while next k end while end Procedure Violation

The pacemaker constraints were composed and fed to the above algorithm and the log file, generated for a faulty simulation run in which the waiting time was increased by 50 milisec to be 1050 milisec, was processed. The parameters consumed by the algorithm are:

The two timing constraints:

```

- timing_constrain<sub>1</sub>(constant = 350 milisec, no_of_elements = 2,

```

$[element_1 = Pace, element_2 = Unsensed],$

$[occurrence_1 = Receive\_heart, occurrence_2 = Send\_heart],$

[operators<sub>1</sub>(first\_operand, second\_operand) = "-", operators<sub>2</sub>(first\_operand, second\_operand) = "<"])

- timing\_constrain<sub>2</sub>(constant = 350 milisec, no\_of\_elements = 2,

```

[element<sub>1</sub> = APaceDone, element<sub>2</sub> = VRefractDone],

```

$[occurrence_1 = Receive\_Atrial, occurrence_2 = Receive\_Atrial],$

[operators<sub>1</sub>(first\_operand, second\_operand) = "-", operators<sub>2</sub>(first\_operand, second\_operand) = "<"])

Sample of the log file:

```

log_file_ entry<sub>124</sub> (time = 22152, message = APaceDone, occurrence = Send_Venticular)

log_file_ entry<sub>125</sub> (time = 22152, message = APaceDone, occurrence = Receive_Atrial)

log_file_ entry<sub>126</sub> (time = 22653, message = unsensed, occurrence = Send_heart)

log_file_ entry<sub>127</sub> (time = 23004, message = Pace, occurrence = Send_ Atrial)

log_file_ entry<sub>128</sub> (time = 23004, message = Pace, occurrence = Receive_Venticular)

```

$\log_{file}$  entry<sub>129</sub> (time = 23007, message = Pace, occurrence = Send\_Venticular)  $\log_{file}$  entry<sub>130</sub> (time = 23007, message = Pace, occurrence = Receive heart)

Results showed several violations in the first constraint:

Delayed Pace at: 10015 Delayed Pace at: 22653 Delayed Pace at: 23554 Delayed Pace at: 33469 Delayed Pace at: 34370 Delayed Pace at: 35271 Delayed Pace at: 45185 Delayed Pace at: 46087 Delayed Pace at: 58705

The drawbacks of this approach is in the fact that it resembles an open loop process, i.e. we can not stop the simulation nor change the simulation settings in response to a violation as it occurs, only when the whole simulation run is performed and the logs are available we can detect the violations and start understanding the logic behind them. This fact makes the approach less valuable to the purposes of timing analysis and the sensitivity analysis to a specific variable, delay or operation. This drawback is handled in the second approach discussed next.

#### 4.1.2 The second approach for timing constraints verification

In this approach we designed the Observer component (figure 4.2) to act as an external monitoring object that monitors the timing constraints in the modeled system, and detects and reports all the violations as they occur. The Observer component is not part of the UML specifications nor of the tool used; it is aimed to automate the detection of timing constraints violations as they occur. The Observer responsibilities are: 1) Setting and initiating consecutive simulation runs 2) Detection of timing constraint violations 3) Production of the violation report. These violations represent detected deadline failures during the simulation run. The observer is modeled using UML hierarchical state machine based on timing constraints, use cases, sequence diagrams and the

methods presented in this section. One connector delivers the messages between the modeled system and the Observer. Messages from the system represent all the instances addressed in the timing constraints. There exist no messages from the Observer directly to the system. Several connectors can exist between the Observer and the modeled external systems. Messages from the Observer to the modeled external systems are control messages to initiate and terminate subruns. In [5], requirement verification for timed UML sequence diagrams and timed automata design representation (UML models have to be converted to timed automata), were accomplished by an Observer model within UPPAAL tool that was designed to verify timed automata requirements. The modeled observer branched to a state indicating a specific traceable timing failure, while in our model for the Observer, the reaction to a timing violation is configurable (the sub run can be forced to stop and the next can be consequently configured and started).

Figure 4.2 The Observer as an external object

#### 4.1.2.1 Constraint driven Observer modeling

Our first proposal for Observer modeling is strictly based on timing constraints. Each constraint is modeled using a UML hierarchical State Machine representing the behavior of a subcomponent in the Observer component. The Observer component encapsulates all constraint components as well as an Observer controller component. The controller component is responsible for setting, initiating, terminating sub runs and controlling which set of constraint components is active at each specific time instance. The highest level of the constraint hierarchical State Machine consists of two states; on and off, and is controlled by the Observer controller component.

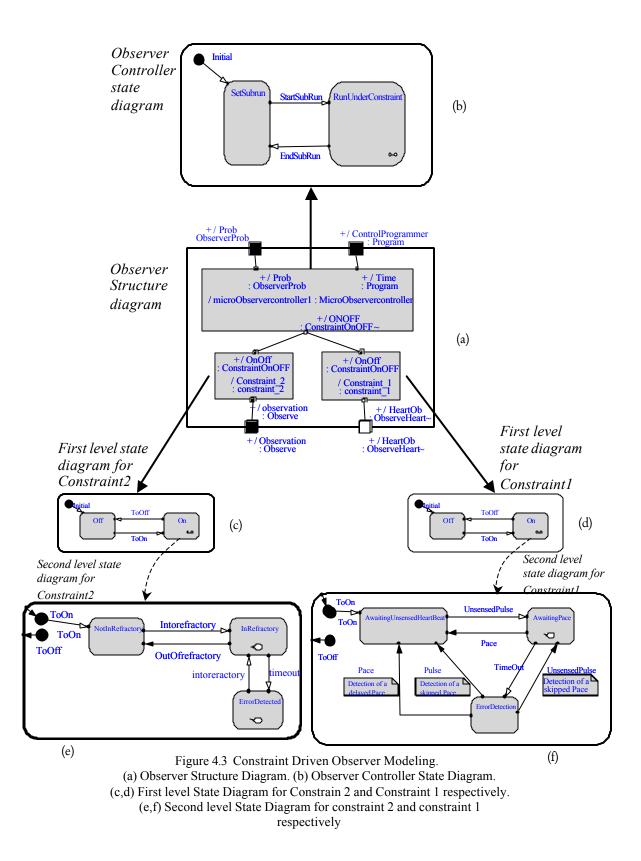

We modeled an Observer for the pacemaker based on the constraint driven Observer modeling and we confirmed the results with the timing diagrams. In this case the two pacemaker timing constraints mentioned in chapter 3 are modeled each in a separate component, namely: Constraint\_1, Constraint\_2. Figure 4.3 shows: (a) Observer component structure diagram for the pacemaker. (b) The state diagram representing the behavior of the Observer Controller (MicroObserverController in figure 4.3 (a)). (c,d) The first level of the state chart representing the behavior of constraint 2 and constraint 1 respectively. Two states are shown "Off" which is equivalent to idle and "On" which is expanded to a second level state machine, shown in (e,f), to represent the constraints.

One of the benefits of Modeling constraints in this manner is the ability to report a categorized violation of a constraint instead of just reporting the violation. This is obvious in the lower state diagram of the first constraint (figure 4.3). The violation of this constraint can imply one of two behavioral errors: a delayed pace or a skipped pace. Modeling the constraint as well as the types of violations, speeds up the analysis process performed by the analyst.

The drawbacks of the constraint driven Observer Modeling is the fact that the amount of effort spent by the analyst is directly proportional to the number of constraints modeled. This fact makes this method limited by the number of constraints to be studied. Our experience with the tool used in this work suggests that this method should only be used for a small number of timing constraints. Thus the number of components in the Observer Capsule is relatively small. This limitation is relaxed in the Use Case driven Observer modeling presented in the next subsection.

#### 4.1.2.2 Use Case driven Observer modeling

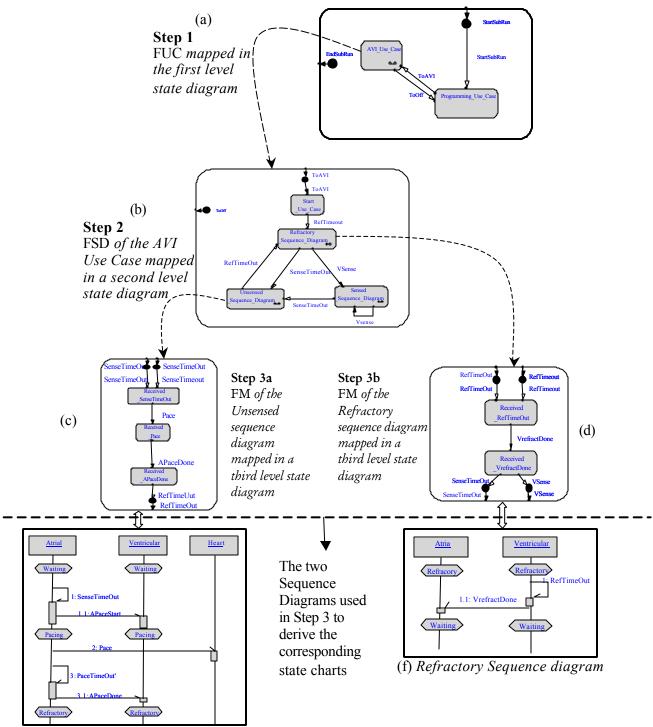

Our second method for Observer modeling is based on timing constraints, use cases and sequence diagrams. In this method an adaptation of the structured sequence diagrams in [12], in which each scenario is represented as a Use Case composed of a set of Sequence Diagrams such that no loops or conditions exist within a sequence diagram, is used. This adaptation serves in mapping the sequence diagrams to state machines. In this representation the decision of the next sequence diagram is made based on the first message in the next sequence diagram. In this representation each Use Case has a set of Sequence Diagrams. For the purpose of timing constraints verification only the messages of the sequence diagram that affect one or more variables in the constraints to be verified as well as the messages on the edges of the Sequence Diagram, are mapped. Modeling the messages on the edge of the sequence diagrams is intended for modeling the messages on which the choice of the next sequence diagram is selected. Bellow we define FUC as a set of Use Cases, subset (filtered from UC) of the set of all use cases in the specification, FSD as a set of Sequence Diagrams, subset (filtered from SD) of the set of Sequence Diagrams in a Use Case that belongs to FUC and FM as the set of messages, subset (filtered from M) to the set of all messages in a sequence Diagram that belongs to FSD. In the following subsection we present the definitions of the sets mentioned above, how the filtration is performed and steps for the modeling process.

### 4.1.2.2.1 Definitions

The system requirements are expressed in a set of Use Cases named "UC" and each Use Case is named "UC<sub>i</sub>" and contains a set of Sequence Diagrams named "SD<sub>i</sub>". Each Sequence Diagram belonging to Use Case UC<sub>i</sub> is named "SD<sub>ij</sub>" and contains of a set of messages named  $M_{ij}$ . The set T is the set of timing constraints, each timing constraint is named  $t_l$  is composed of three sets: a set of messages named  $E_1$ , a set of operators named op<sub>l</sub> and a set of constants named  $C_1$ . The set UC, SD, M and T are presented below

$T = \{ t_l | l \le l \le n \} = \{ t_1, t_2, \dots, t_l, \dots, t_n \}$  where  $1 \le l \le n$

n is the total number of timing constraints

$t_l = < Op_l, E_l, C_l >$

UC = {  $uc_i | 1 \le i \le m$  } = {  $uc_1, uc_2, ..., uc_i, ..., uc_m$  } where  $1 \le i \le m$

m is the total number of Use Cases

$SD_i = \{ sd_{ij} | 1 \le j \le p_i \}$   $SD = _{i=1} \cup^m SD_i$

pi is the total number of Sequence Diagrams in Use Case number i

$M_{ij} = \{ \mu_{ijk} | 1 \le k \le q_{ij} \}$   $M = {}_{i=1} \cup^{m} {}_{j=1} \cup^{pi} M_{ij}$

q<sub>ij</sub> is the total number of messages in Sequence Diagram ij

The set  $FM_{ij}$  is the subset of  $M_{ij}$  that contains the messages that are required for the timing constraints, and if any then, the edge messages in the Sequence Diagram  $SD_{ij}$  are included as well.

$TM_{ij} = \{ \mu_{ijk} \mid \exists 1 (1 \le l \le n) : \mu_{ijk} \in E_l \}$

If

$$(TM_{ij} = \emptyset)$$

then  $FM_{ij} = \emptyset$  Else  $FM_{ij} = TM_{ij} \cup \mu_{ij1}, \mu_{ijqij}$

$FM = _{i=1} \cup^{m} _{j=1} \cup^{pi} FM_{ij}$

The set  $FSD_i$  is the subset of  $SD_i$  that contains the set of Sequence Diagrams that have messages in FM

$$FSD_i = \{ sd_{ij} | 1 \le j \le p_i , FM_{ij} \ne \emptyset \}$$

$FSD = _{i=1} \cup^m FSD_i$

The set FUC is the subset of UC that contains the set of Use Cases that have Sequence Diagrams in FSD

$FUC = \{ uc_i | 1 \le i \le m_i , FSD_i \ne \emptyset \}$

#### 4.1.2.2.2 Step 1

Construct the top level/levels of the Observer state chart from the logical relationships and structure between all the Use Cases in FUC such that:

A- Each Use Case maps to a Macro state: where the Micro states of that state are constructed later in step 2 and each represent a Sequence Diagram.

- B- If a Use Case is contained in another Use Case it is mapped to a Micro State inside the corresponding Macro State representing the containing Use Case.

- C- Each relationship between two Use Cases in FUC is mapped to a transition triggered by the occurrence of a message from the corresponding sequence diagrams.

### 4.1.2.2.3 Step 2

For each element in FUC construct the state diagram that represents the logical relationships and structure between all elements in FSD such that:

- A- Each Sequence Diagram in FSD maps to a Micro state in the corresponding Use Case Macro State in FUC.

- B- Each relationship between two Sequence Diagrams in FSD (consecutive conditional or unconditional execution) is mapped to a transition triggered by the occurrence of the first message in following Sequence Diagram.

- C- Each Use Case in FUC has a "Start\_Use\_Case" state representing its initial starting point from which the selection of the first Sequence Diagram to be executed, is made.

- D- Selection is based on transitions triggered by the occurrence of the first message in the corresponding Sequence Diagrams causing the transition to their corresponding Macro States.

### 4.1.2.2.4 Step 3

For each Sequence Diagram in FSD construct the state diagram that maps all messages in FM into transitions triggered by the occurrences of messages in the observed system such that:

- A- States are named by the message name "Received\_messagename" and are triggered the message reception at the destination Capsule

- B- Mapping is done for messages in FM only: The set FM as defined above does not contain all the messages in each Sequence Diagram in FSD. Only the messages that are related to elements of the timing constraints and the messages on the edge of the Sequence Diagrams are modeled.

- C- Time stamps of messages involved in all concerned timing constraints are collected in variables "RTTimespec" using the system method "RTTimespec::getclock(Variable Name)", as they occur.

- D- Each constraint Boolean expression is evaluated immediately after the collection of the last element (occurrence of the last message related to the constraint). Then the check is performed and the violation (if any) is logged.

#### 4.1.2.2.5 Observer Model for the cardiac pacemaker case study

We modeled an Observer for the pacemaker based on the Use Case driven Observer modeling methodology. The two timing constraints for the AVI operational mode were used to construct the FUC, FSD and FM. Figure 4.4 shows the three level hierarchical state machine of the modeled Observer and the messages mapped from the sequence diagrams, based on the definitions and steps of the Use Case driven Observer modeling. The Programming Use Case and the AVI Use Case formed FUC. The mapping of FUC based on step 1 is shown in figure 4.4 (a). The three sequence diagrams; Refractory, Unsensed and Sensed formed FSD. The mapping of FSD based on step 2 is shown in figure 4.4 (b). Figure 4.4 (c,d) show the State Diagram of the "Unsensed" and "Refractory" Sequence Diagrams (figure 4.4 (e,f)) respectively. The timing constraints span two sequence diagrams only; Refractory and Unsensed. For this reason, the Sensed sequence diagram is modeled. In modeling the Unsensed sequence diagram, the messages "A Pace Start" and "Pace Timeout" are not elements of any of the two timing constraints and hence the are not mapped. While in the Refractory sequence diagram the message "RefTimeOut" is mapped because of being an edge message and the message "VrefractDone" is mapped because of being part of the second constraint.

One of the benefits of Modeling constrains in this manner is the ability to verify sequence diagrams, in a manner that is proportional to the amount of details modeled in the Observer.

(e) Unsensed Sequence diagram

Figure 4.4 Use Case Driven Observer Modeling

### 4.1.3 Results and lessons learned

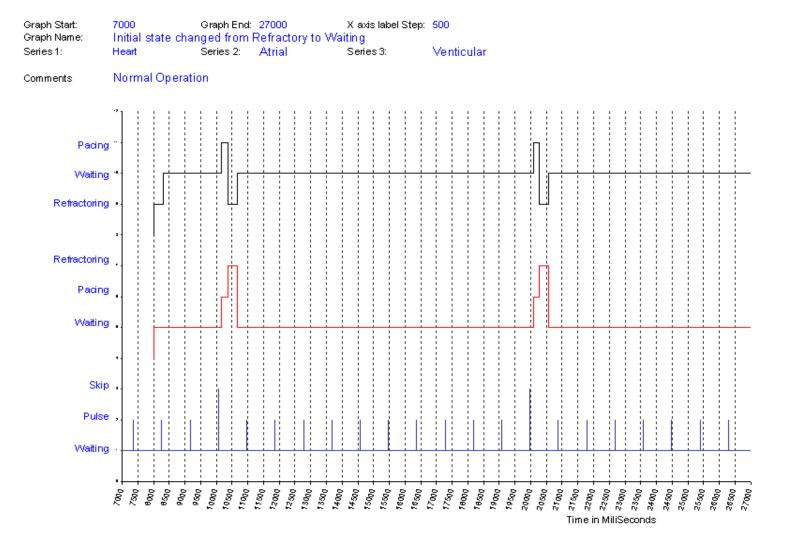

In this section we show our results, from applying the approaches and methods above, and confirming with visual inspection of the timing diagrams, to the AVI scenario of the pacemaker model. We injected timing faults in the pacemaker model in order to force the occurrence of violations based on the analysis methods described later in this chapter and in [34]. The timing diagrams described earlier in chapter 2 were generated and used to verify the expected logics behind the detected violations. The sample that we show below is a Time-out based timing analysis in which we study the effect of the time set for the Ventricular Model Refractory timer (timer controlling the time spent in the Refractory state by the Ventricular\_Model and the exiting transition to the waiting state) on the timing constraints, when increased by 50 milisec to be 350 milisec. We know that the Atrial Model Refractory time (time spent in the Refractory state by the Atrial Model) is directly controlled by the Ventricular Model Refractory time through the messages: ApaceDone and VrefractDone from the Venticular Model to the Atrial Model. Thus we expect the periodic violation of the second constraint. The increase in the Atrial Model Refractory time, being part of the cycle time, causes an increase in the delay between each generated pace and each unsensed pulse. The increase in the accumulated delay becomes significant to the first timing constraint starting from the third consecutive unsensed heart beet. We tested the presented approaches and methods and proved their correctness when the violation tables generated for the same faulty simulation run were identical. An increase in the Ventricular Model Refractory time from 300 milisec to 350 milisec was the selected fault. Table 4.1 shows a sample of the violations from the three simulation runs where the temporal V&V was performed using the presented approaches and methods: the violation algorithm (first approach), constraint driven Observer modeling (first method in the second approach) and Use Case driven Observer modeling (second method in the second approach).

| 22612 | Constraint 2 Violated: Refractory problem     |

|-------|-----------------------------------------------|

| 23664 | Constraint 2 Violated: Refractory problem     |

| 24165 | Constraint 1 Violated: Delayed Pacing problem |

| 24715 | Constraint 2 Violated: Refractory problem     |

| 25216 | Constraint 1 Violated: Delayed Pacing problem |

| 25767 | Constraint 2 Violated: Refractory problem     |

| 26268 | Constraint 1 Violated: Delayed Pacing problem |

| 26818 | Constraint 2 Violated: Refractory problem     |

| 27319 | Constraint 1 Violated: Delayed Pacing problem |

| 27870 | Constraint 2 Violated: Refractory problem     |

| 34339 | Constraint 2 Violated: Refractory problem     |

| 35391 | Constraint 2 Violated: Refractory problem     |

| 35891 | Constraint 1 Violated: Delayed Pacing problem |

| 36442 | Constraint 2 Violated: Refractory problem     |

| 36943 | Constraint 1 Violated: Delayed Pacing problem |

| 37494 | Constraint 2 Violated: Refractory problem     |

| 37994 | Constraint 1 Violated: Delayed Pacing problem |

| 38545 | Constraint 2 Violated: Refractory problem     |

| 39046 | Constraint 1 Violated: Delayed Pacing problem |

| 39597 | Constraint 2 Violated: Refractory problem     |

| 46056 | Constraint 2 Violated: Refractory problem     |

| 47108 | Constraint 2 Violated: Refractory problem     |

| 47608 | Constraint 1 Violated: Delayed Pacing problem |

|       |                                               |

Table 4.1 Sample of the violation table from simulation with 350milisec

Ventricular Model Refractory time

We argue that the three directions for automated verification of timing constraints presented above are independent, yet selecting the most suited direction is specific to the specification to verify and the V&V objectives. The first approach will be the most effective and efficient when the verification objectives do not require any response within a single simulation run. Which we described as an open loop analysis where there is no intention for stopping the simulation nor changing the simulation settings in response to a violation as it occurs. In this case the first approach is the most efficient and we perceive it to be the most scala ble. This limitation is handled in using the second approach, in which a selection of the Observer modeling method should be performed. In the constraint driven Observer Modeling, the amount of effort spent by the analyst in modeling the Observer and the complexity of the Observer model is directly proportional to the number of constraints modeled. This fact makes this method limited by the number of constraints to be studied, thus introducing the limitation on the use of the method in cases where more than four timing constrains are being verified. This limitation is eliminated when using the Use Case Observer modeling, yet the trade off when selecting the constraint driven Observer modeling over the Use Case driven Observer modeling in case of four constraints or less is in the amount of effort spent in modeling the Observer versus the inability (if required) to verify sequence diagrams nor to gather statistics that can be used in other analysis.

### 4.2 The Four Timing Analysis Methods

### 4.2.1 Methods

Using the automatic generation of timing diagrams described in chapter 2, the analyst can inspect the timing diagrams to verify that timing constraints are met. Moreover, the analyst can deploy several timing analysis methods to study the effect of delays in transmission or processing of messages. Table 4.2 summarizes four timing analysis methods that we developed to analyze UML specifications. We discuss each of the proposed methods using a Focus/Purpose/Method template.

| Timing Analysis Method   | Focus                                    | Purpose                                                           |

|--------------------------|------------------------------------------|-------------------------------------------------------------------|

| Concurrency-based        | Links between<br>objects<br>(components) | Study the effect of delays of delivering messages between objects |

| Performance-based        | Objects<br>(components)                  | Study the effect of implementation efficiency                     |

| Timeouts-based           | Objects<br>(components)                  | Study effect of various timeout values.                           |

| Environment-Interactions | External<br>Environment                  | Study effect of delays in recognizing hardware events             |

Table 4.2 Summary of Timing Analysis Methods

# 4.2.1.1 Concurrency-based Timing Analysis:

Focus: Architecture connectors (links between objects)

*Purpose*: Analyze the effect of delays in delivering messages from one component (object) to another.

# Method:

- Augment the model with delays over connectors involved in each scenario.

- Generate timing diagrams for each simulation run.

- Inspect timing diagrams to study the effects of these delays on model behavior and required deadlines.

# 4.2.1.2 Performance-based Timing Analysis

*Focus*: Architecture components (objects)

Purpose: Analyze the effect of inefficient implementation of state activities and actions.

# Method:

- Augment the model with delays in the execution of entry, exit, and activity code segments of all states involved in each scenario.

- Generate timing diagrams for each simulation run.

- Inspect timing diagrams to study the effect of these delays on model behavior and required deadlines.

## 4.2.1.3 Timeouts-based Timing Analysis

Focus: Architecture components (objects)

Purpose: Analyze the effect of timeout values of all user defined timers in the model.

# Method:

- Vary the values of timers used in each scenario.

- Generate timing diagrams for each simulation run.

• Inspect timing diagrams to study the effect of these variations on model behavior and required deadlines.

# 4.2.1.4 Environmental-Interactions Timing Analysis

Focus: Interactions with the environment including hardware devices and sensors.

*Purpose*: Analyze the effect of delay in sensing environmental events, caused by external systems and/or event recognition software (outside system boundaries).

## Method:

- Augment the model with delays in sensing hardware events.

- Produce timing diagrams for each simulation run.

- Inspect timing diagrams to study the effect of these delays on model behavior and required deadlines.

Later in chapter 6 the above methods are used in Fault Injections analysis.

# 4.2.2 The Cardiac Pacemaker Example

# 4.2.2.1 Concurrency-based Timing Analysis

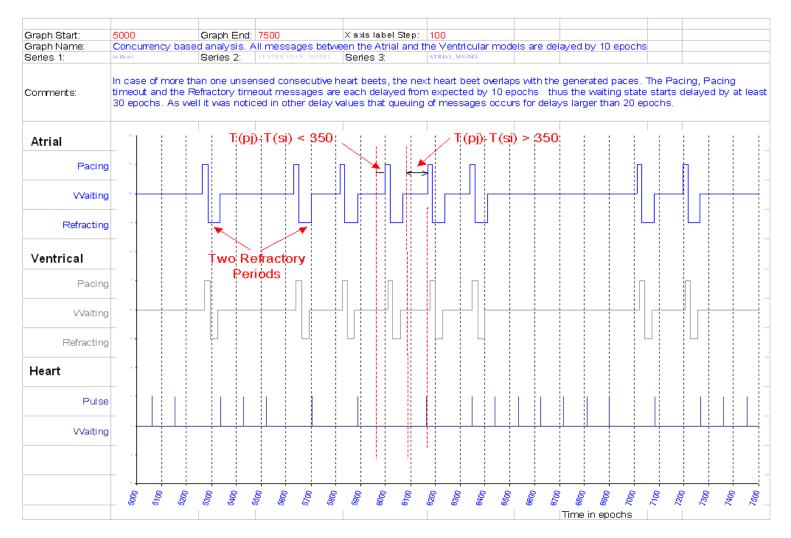

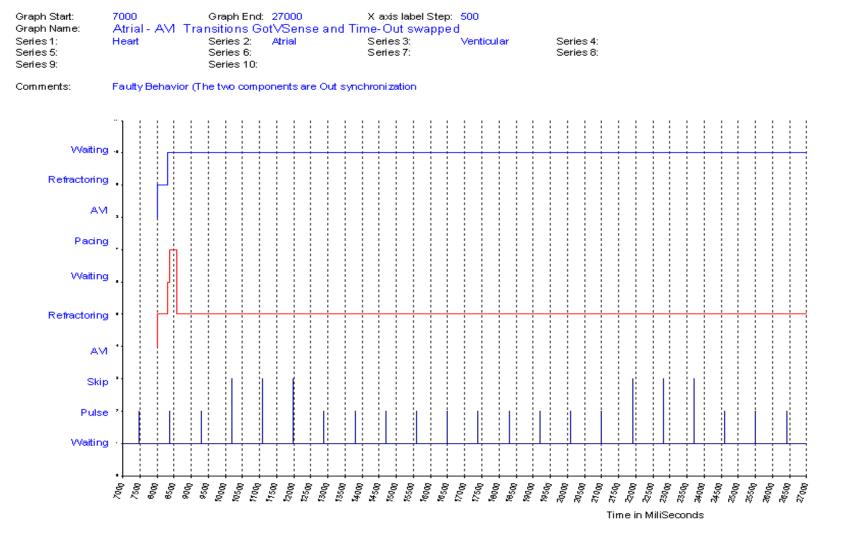

**Focus:** Delay all messages on the connector between the Atrial and Ventricular components. (10 epochs is shown in Figure 4.5)

**Result:** Figure 4.5 shows a sample of the Concurrency-based analysis for a Cardiac Pacemaker in the AVI operational mode where all messages between the Atrial and the Ventricular models are delayed by 10 epochs (100 milliseconds). In case of more than one unsensed consecutive heart beats, the next heart beat overlaps with the generated paces.

**Reason:** Due to message delay, the refractory time for the Atrial increased by at least 20 epochs and the Pacing is delayed from expected by 10 epochs, thus the start of the waiting state was delayed by at least 30 epochs.

Note: We observed that Queuing of messages occurs for delays larger than 20 epochs.

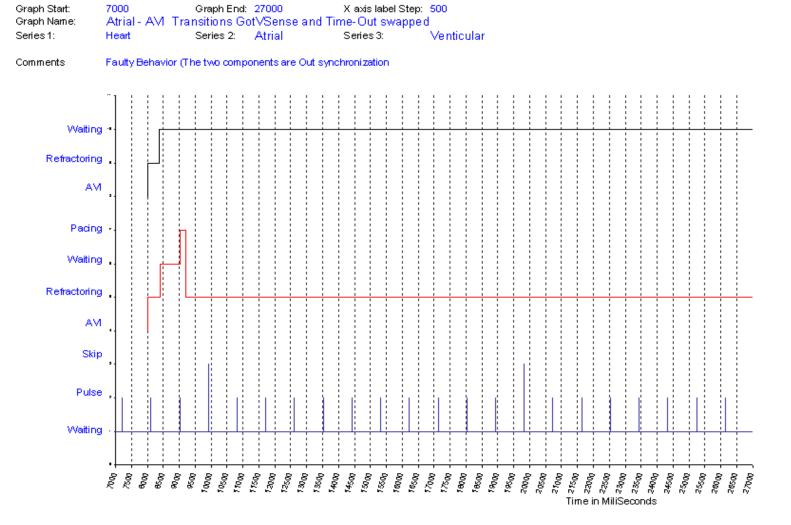

#### 4.2.2.2 Performance-based Timing Analysis

**Focus:** Insert delays in the execution of actions in the refractory state of the Atrial component. (10 epochs is shown)

**Result: :** Figure 4.6 shows a sample of the Performance-based analysis for a Cardiac Pacemaker in the AVI operational mode where the entry actions of the Atrial Refractory state is delayed by 10 epochs (100 milliseconds).In Case of 2 consecutive unsensed heart beats, the second heart pulse overlaps with the second pace.

**Reason:** The inserted delay added to the refractory period of the Atrial, thus causing the start of the waiting state to be delayed.

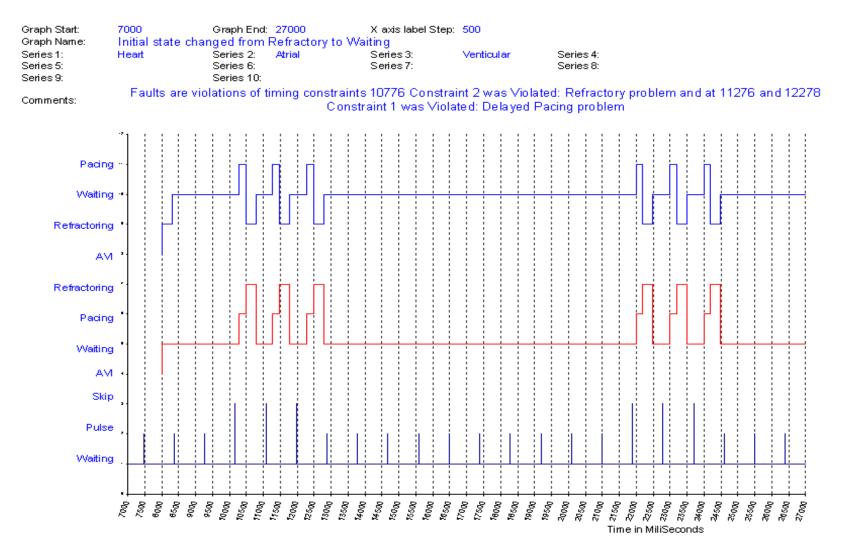

### 4.2.2.3 Timeout-based Timing Analysis

**Focus:** Increase the timeout value of the Ventricular refractory (Vrefract) timer. (5 epochs is shown)

**Result:** Figure 4.7 shows a sample of the Timeout-based analysis for a Cardiac Pacemaker in the AVI operational mode where the Venticular Refractory timer is increased by 5 epochs (50 milliseconds) to be 35 epochs (350 milliseconds). In Case of 2 consecutive unsensed heart beats, the 2nd heart pulse intersects with the 2nd pace.

**Reason:** The Refractory time-out in the Ventricular triggers the change of state to waiting in the Atrial, thus the increase in its value causes a delayed sensation period which accumulates in the in case of consecutive unsensed heart beats.

#### 4.2.2.4 Environmental-based Timing Analysis

**Focus:** Delay the sensation of the heart pulses in the Ventricular component. (30 epoch is shown) **Result:** Figure 4.8 shows a sample of the Environmental-based analysis for a Cardiac Pacemaker in the AVI operational mode where the sensation messages are delayed by 30 epochs (300 milliseconds). After pulse A two pulses were not sensed from the heart, thus two paces were generated but delayed by 30 epochs, this made pulse B to fall between the two paces.

**Reason**: The delay causes a shift in the sensed Heart beats series, thus increasing the chance for pacing while pulsing. The effect is more clear in pulse C where one pace was generated and pulse C fallen in the refractory state.

|              | 5000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0.15.          |                                                   | V auto la ball Ot      | 4.0.0                                                              |                                                                           |                  |              |      |