Graduate Theses, Dissertations, and Problem Reports

2018

## Integrated Circuits for Programming Flash Memories in Portable Applications

Mir Mohammad Navidi

Follow this and additional works at: https://researchrepository.wvu.edu/etd

#### **Recommended Citation**

Navidi, Mir Mohammad, "Integrated Circuits for Programming Flash Memories in Portable Applications" (2018). *Graduate Theses, Dissertations, and Problem Reports.* 6301. https://researchrepository.wvu.edu/etd/6301

This Dissertation is protected by copyright and/or related rights. It has been brought to you by the The Research Repository (a) WVU with permission from the rights-holder(s). You are free to use this Dissertation in any way that is permitted by the copyright and related rights legislation that applies to your use. For other uses you must obtain permission from the rights-holder(s) directly, unless additional rights are indicated by a Creative Commons license in the record and/ or on the work itself. This Dissertation has been accepted for inclusion in WVU Graduate Theses, Dissertations, and Problem Reports collection by an authorized administrator of The Research Repository (a) WVU. For more information, please contact researchrepository(a) mail.wvu.edu.

# Integrated Circuits for Programming Flash Memories in Portable Applications

Mir Mohammad Navidi

Dissertation submitted to the Benjamin M. Statler College of Engineering and Mineral Resources at West Virginia University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy in Electrical Engineering

David W. Graham, Ph.D., Chair Vinod Kulathumani, Ph.D. Parviz Famouri, Ph.D. Jeremy Dawson, Ph.D. Edward M. Sabolsky, Ph.D.

Lane Department of Computer Science and Electrical Engineering

Morgantown, West Virginia 2018

Keywords: Analog, Integrated Circuits, Floating-Gate, Flash Memory, Field Programmable Analog Arrays

Copyright © 2018 Mir Mohammad Navidi

#### Abstract

Integrated Circuits for Programming Flash Memories in Portable Applications

#### Mir Mohammad Navidi

Smart devices such as smart grids, smart home devices, etc. are infrastructure systems that connect the world around us more than before. These devices can communicate with each other and help us manage our environment. This concept is called the Internet of Things (IoT). Not many smart nodes exist that are both low-power and programmable. Floating-gate (FG) transistors could be used to create adaptive sensor nodes by providing programmable bias currents. FG transistors are mostly used in digital applications like Flash memories. However, FG transistors can be used in analog applications, too. Unfortunately, due to the expensive infrastructure required for programming these transistors, they have not been economical to be used in portable applications. In this work, we present low-power approaches to programming FG transistors which make them a good candidate to be employed in future wireless sensor nodes and portable systems. First, we focus on the design of low-power circuits which can be used in programming the FG transistors such as highvoltage charge pumps, low-drop-out regulators, and voltage reference cells. Then, to achieve the goal of reducing the power consumption in programmable sensor nodes and reducing the programming infrastructure, we present a method to program FG transistors using negative voltages. We also present charge-pump structures to generate the necessary negative voltages for programming in this new configuration.

## Dedication

To my advisor and all CESLAB members who have been very helpful.

${\it To my family and the memory of my father.}$

## Contents

| A  | bstra               | $\mathbf{ct}$ |                                                               |     |    | ii        |

|----|---------------------|---------------|---------------------------------------------------------------|-----|----|-----------|

| D  | edica               | tion          |                                                               |     |    | iii       |

| Li | ist of              | Figur         | res                                                           |     |    | viii      |

| Li | ist of              | Table         | es e                      |     |    | xiii      |

| 1  | Intr                | roducti       | ion                                                           |     |    | 1         |

| 2  | Ove                 | erview        | of Floating-Gate Transistors                                  |     |    | 4         |

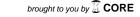

|    | 2.1                 | Flash         | Memory                                                        |     |    | 4         |

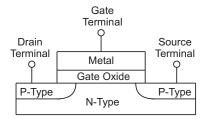

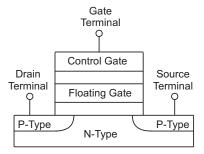

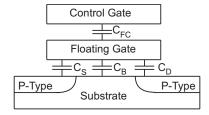

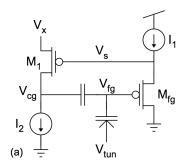

|    | 2.2                 | Floati        | ing-Gate Transistors                                          |     |    | 5         |

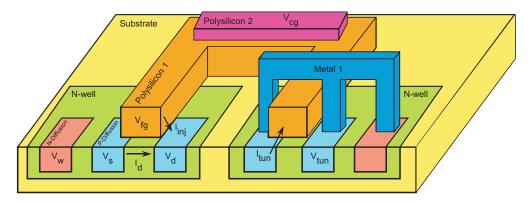

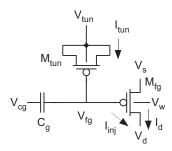

|    |                     | 2.2.1         | Structure of the FG transistors in this report                |     |    | 8         |

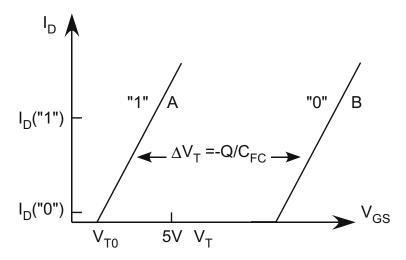

|    |                     | 2.2.2         | Above threshold operation                                     |     |    | 9         |

|    |                     | 2.2.3         | Subthreshold operation                                        |     |    | 10        |

|    | 2.3                 | Readi         | ng Operation                                                  |     |    | 11        |

|    | 2.4                 | Progra        | amming of FG Transistors                                      |     |    | 11        |

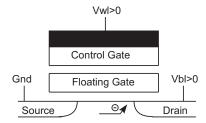

|    |                     | 2.4.1         | Tunneling Processes                                           |     |    | 12        |

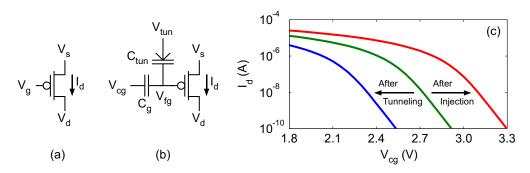

|    |                     | 2.4.2         | Injection Process                                             |     |    | 14        |

|    |                     | 2.4.3         | Injection Methodologies                                       |     |    | 16        |

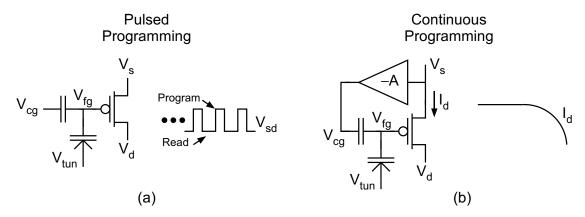

|    |                     |               | Pulsed-Programming                                            |     |    | 16        |

|    |                     |               | Continuous Programming                                        |     |    | 17        |

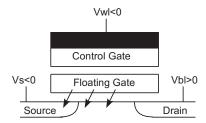

|    | 2.5                 |               | ard Flash Memories                                            |     |    | 18        |

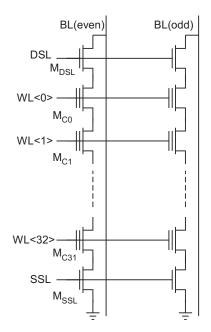

|    |                     | 2.5.1         | NAND Flash Memories                                           |     |    |           |

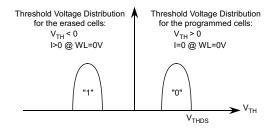

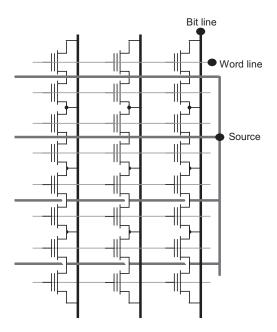

|    |                     | 2.5.2         | NOR Flash Memories                                            |     |    | 19        |

|    |                     | 2.5.3         | NAND Flash vs. NOR Flash                                      |     |    | 21        |

|    | 2.6                 |               | og Applications of FG transistors                             |     |    |           |

|    | 2.7                 | Objec         | etive of the proposed research                                |     | •  | 24        |

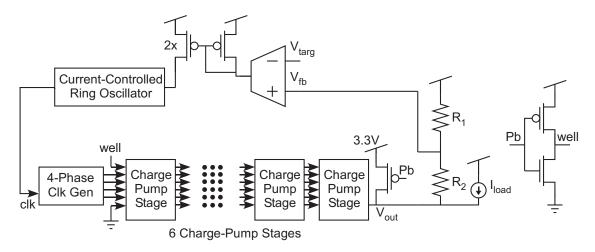

| 3  |                     |               | age Charge Pumps for Tunneling and Injection of Floating-Gate | Tra | n- |           |

|    | $\mathbf{sist}_{0}$ |               |                                                               |     |    | <b>26</b> |

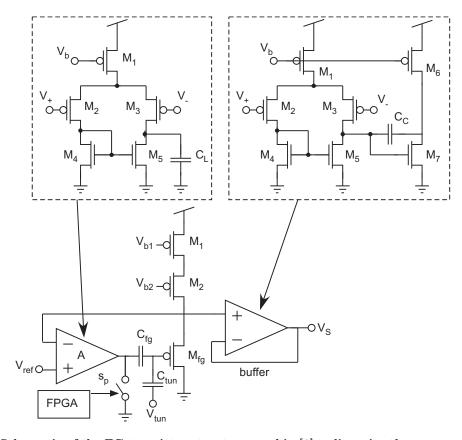

|    | 3.1                 |               | gulated Charge Pump for Tunneling Floating-Gate Transistors   |     |    |           |

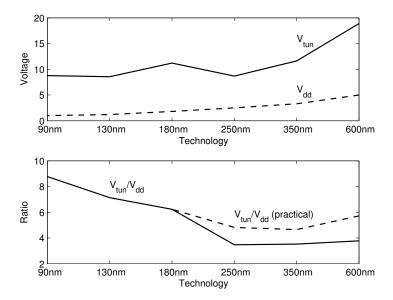

|    |                     | 3.1.1         | Considerations Regarding Tunneling Voltages                   |     |    |           |

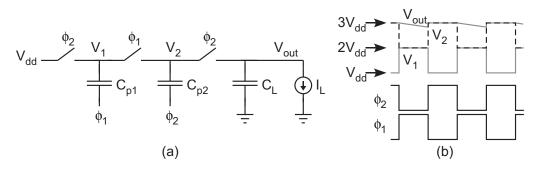

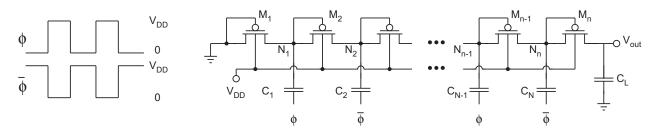

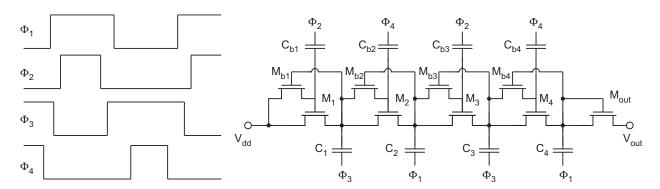

|    |                     | 3.1.2         | Brief Overview of Charge Pumps                                |     |    |           |

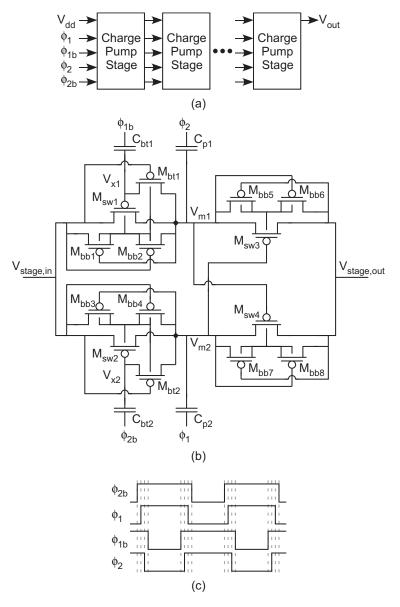

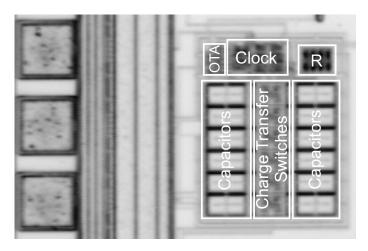

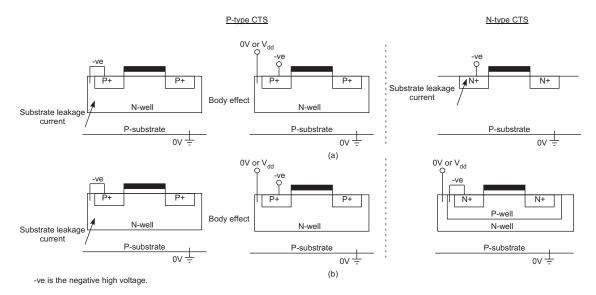

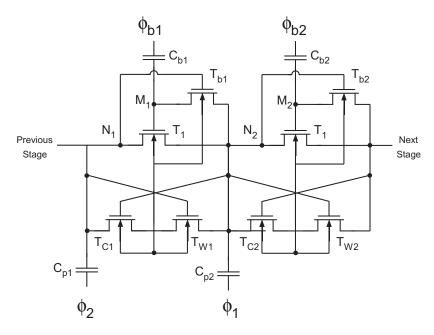

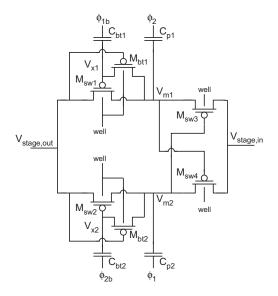

|    |                     | 3.1.3         | Charge-Transfer Switches                                      |     |    | 29        |

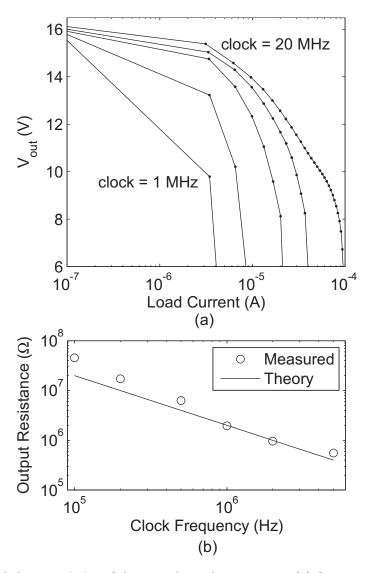

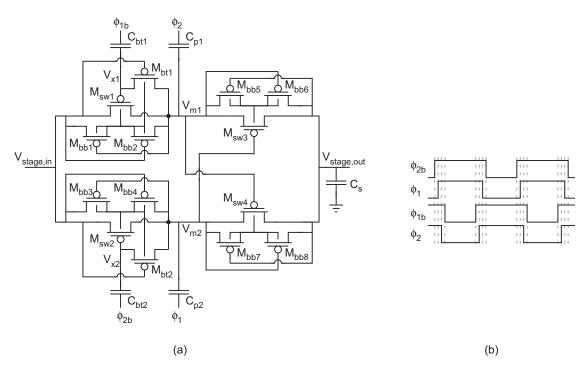

|    |                     | 3.1.4         | Complete Open-Loop Charge Pump                                |     |    | 31        |

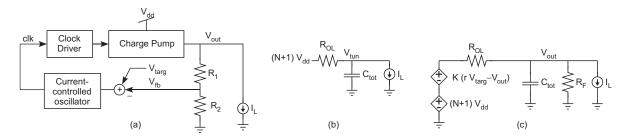

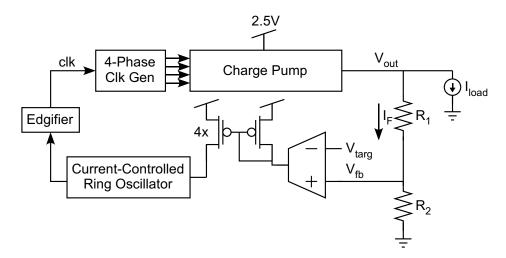

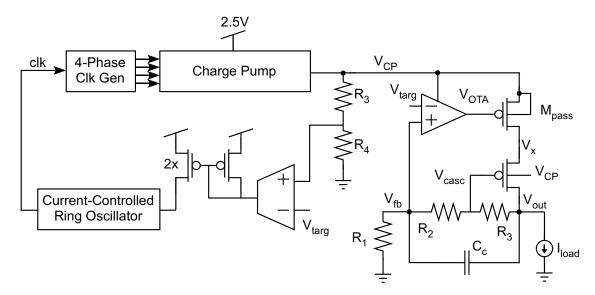

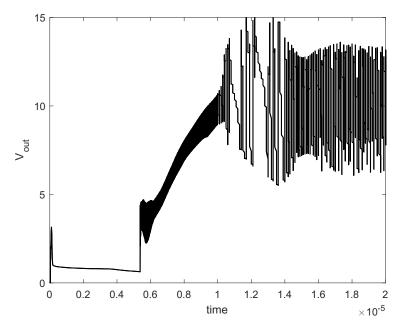

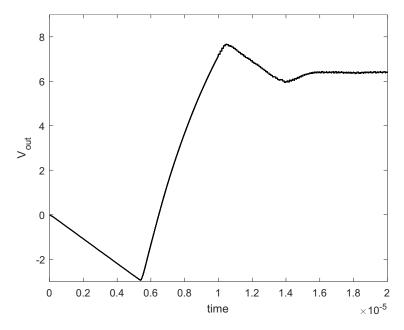

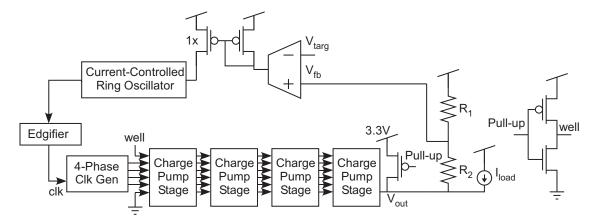

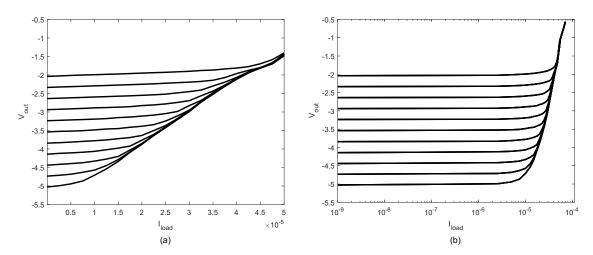

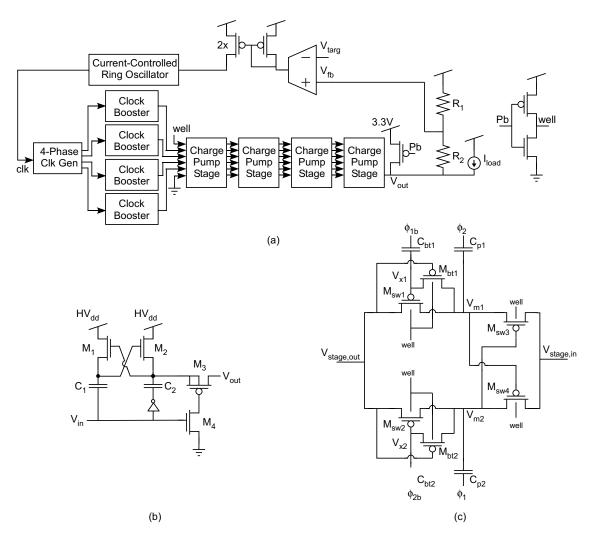

|    |                     | 3.1.5         | Regulation Through Frequency Variation                        |     |    | 32        |

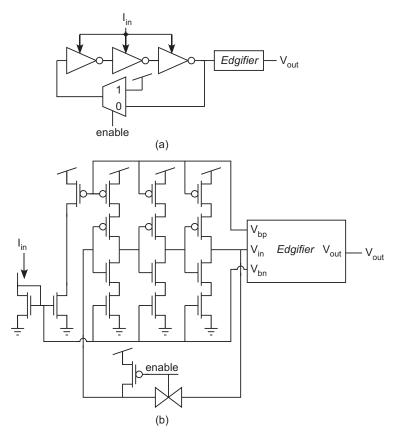

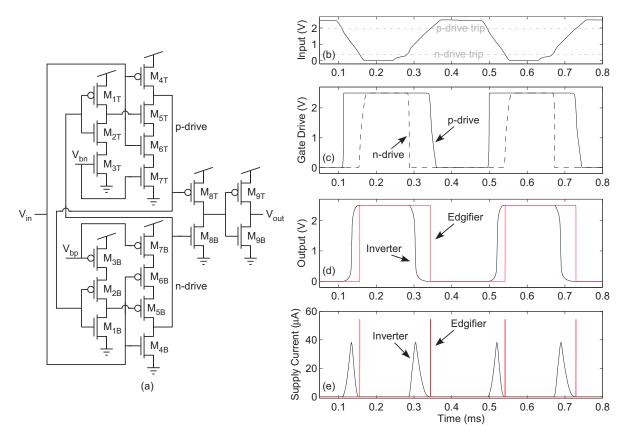

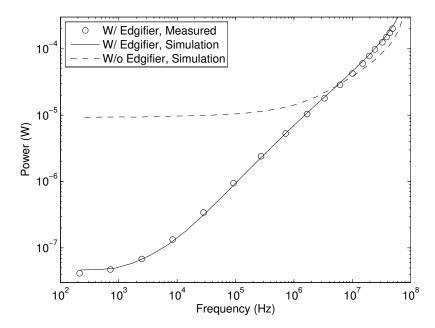

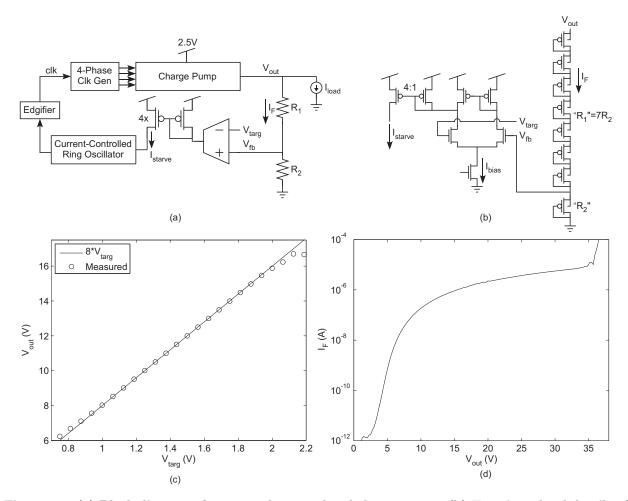

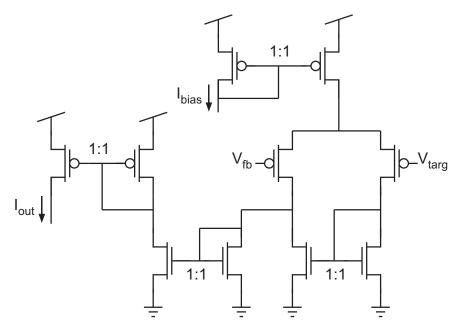

|    |                     | 3.1.6         | Current-Controlled Oscillator and Edgifier                    |     |    | 35        |

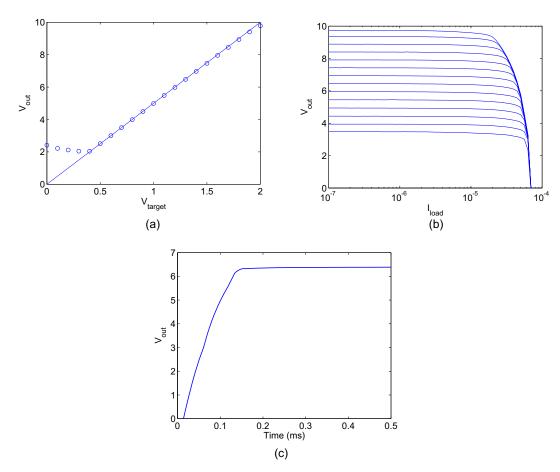

|    |                     | 3.1.7         | The Complete Charge Pump                                      |     |    | 39        |

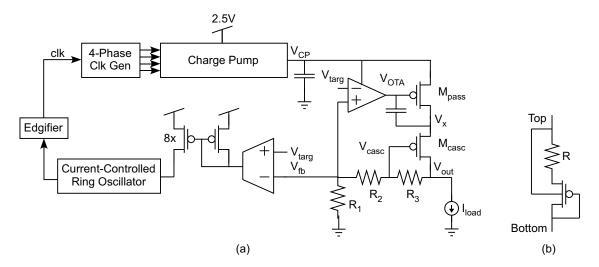

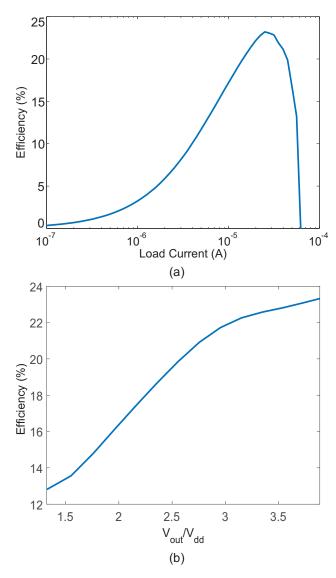

|    | 3.2                 | A Reg         | gulated Charge Pump for Injecting Floating-Gate Transistors   |     | _  | 47        |

CONTENTS vi

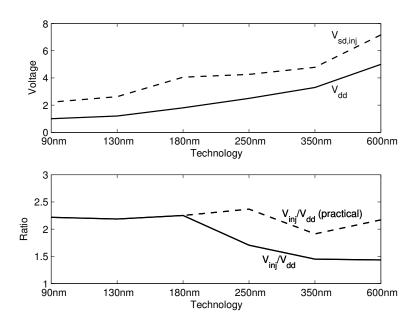

|                                                |                                                         | 3.2.1 Considerations Regarding Injection Voltages and Scaling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 48<br>49                                                             |

|------------------------------------------------|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

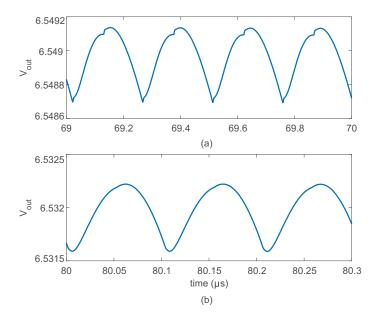

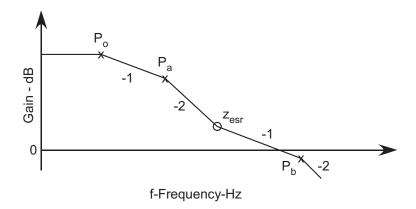

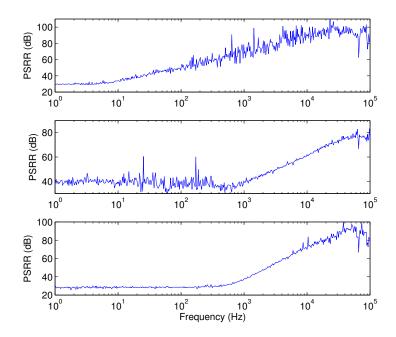

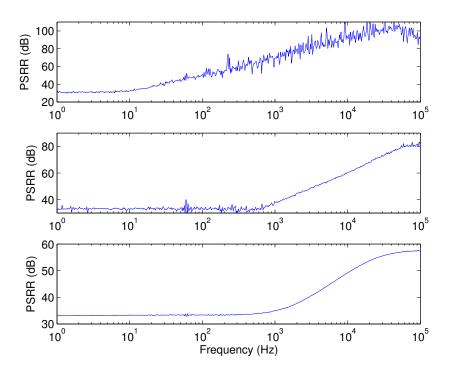

|                                                |                                                         | 3.2.3 PSRR of LDO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                      |

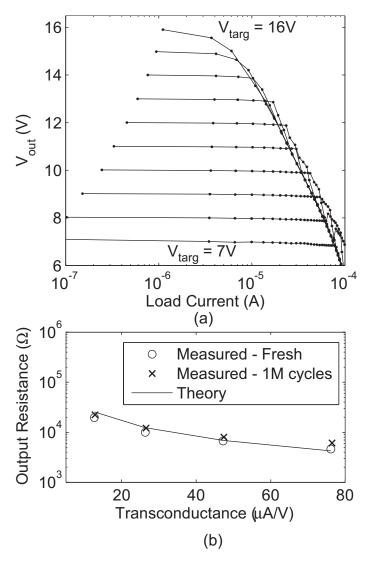

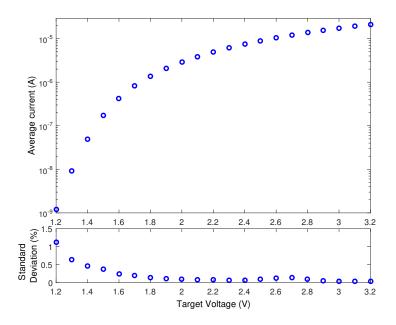

|                                                |                                                         | 3.2.4 Experimental Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                      |

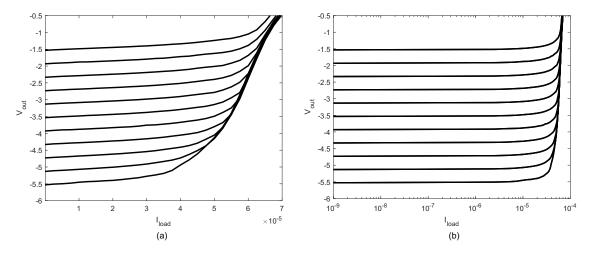

| 5                                              | 3.3                                                     | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 53                                                                   |

|                                                | 0.0                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 55                                                                   |

|                                                |                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 56                                                                   |

|                                                |                                                         | 3.3.3 Experimental Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                      |

| •                                              | 3.4                                                     | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                      |

|                                                | J. 1                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ,                                                                    |

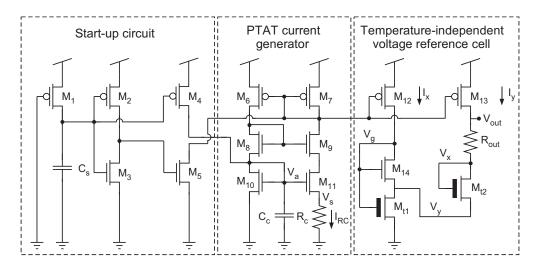

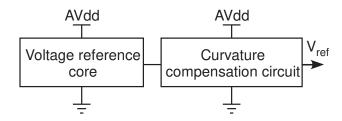

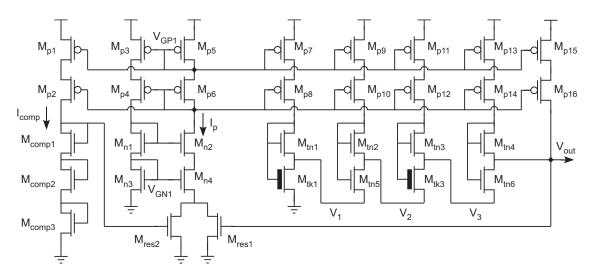

| 4                                              | A L                                                     | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 63                                                                   |

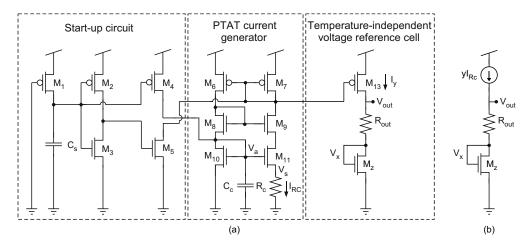

|                                                | 4.1                                                     | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 63                                                                   |

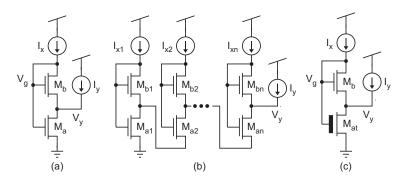

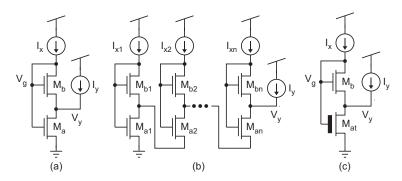

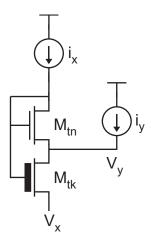

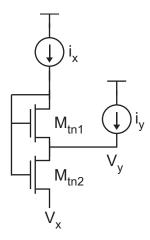

| 4                                              | 4.2                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 64                                                                   |

|                                                |                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 65                                                                   |

|                                                |                                                         | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 66                                                                   |

|                                                |                                                         | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 66                                                                   |

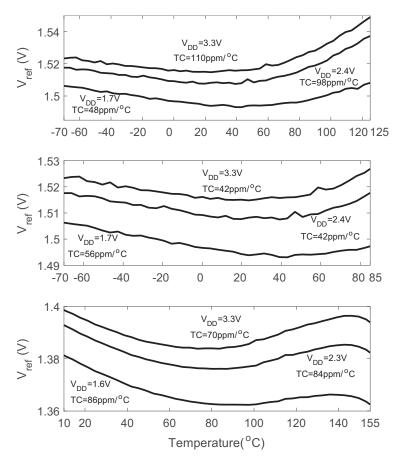

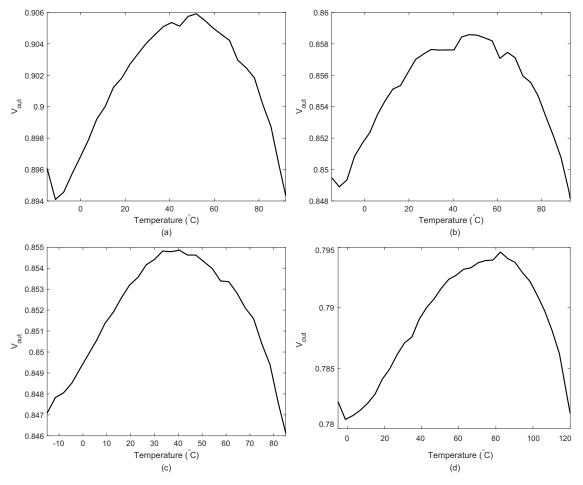

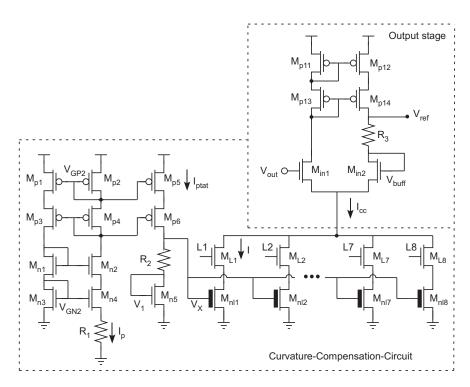

|                                                | 4.3                                                     | Design procedure for low TC $V_{out}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                      |

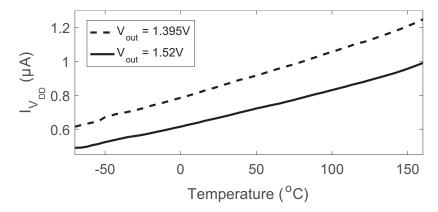

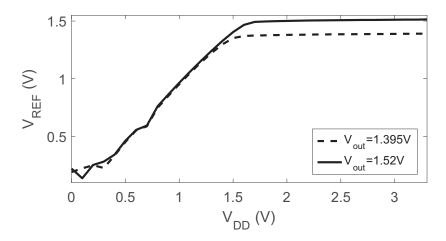

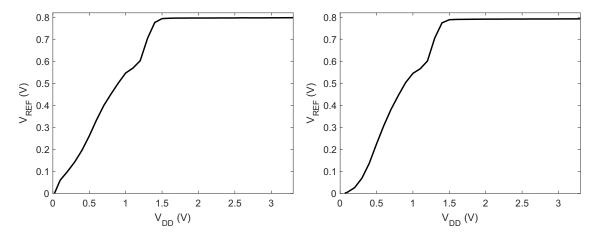

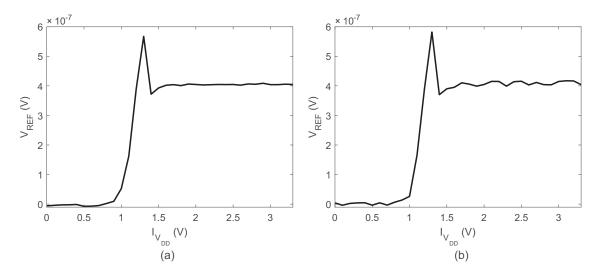

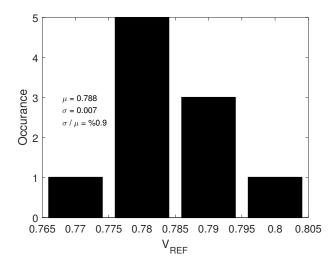

|                                                | 4.4                                                     | Experimental Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                      |

| 4                                              | 4.5                                                     | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 72                                                                   |

| 5 (                                            | On-                                                     | chip Voltage Regulators for Supply and Mid-Rail Voltage References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 73                                                                   |

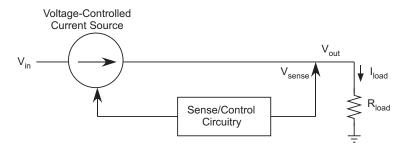

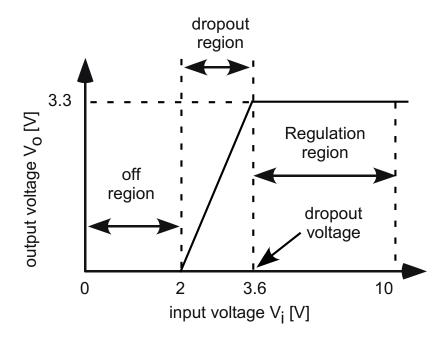

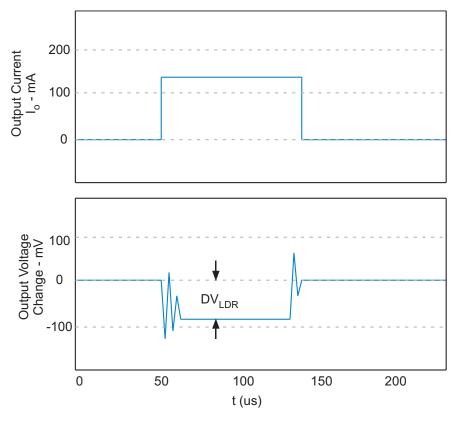

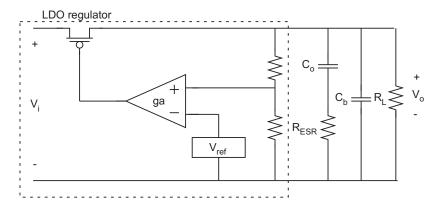

|                                                | 5.1                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 73                                                                   |

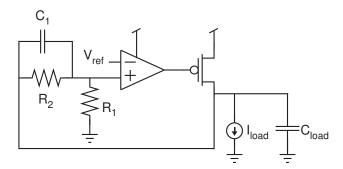

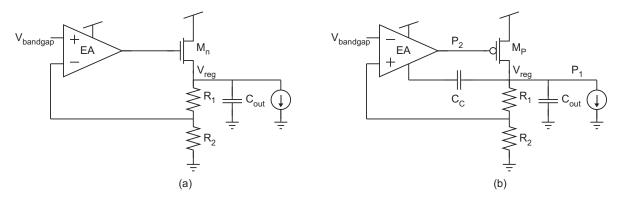

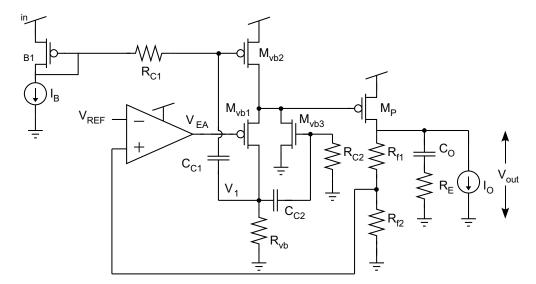

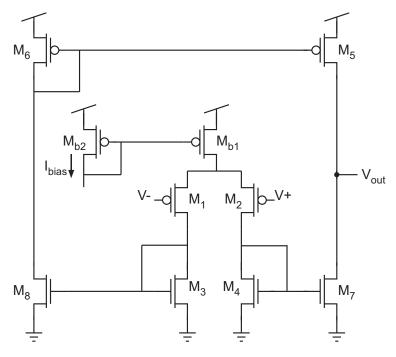

|                                                | 5.2                                                     | Analog/Digital LDO regulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                      |

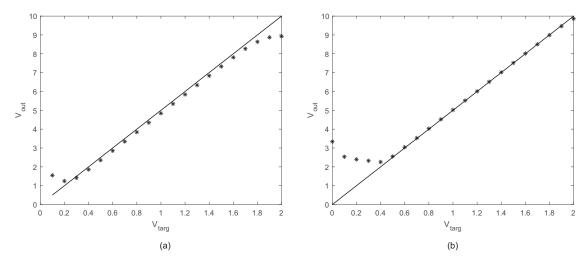

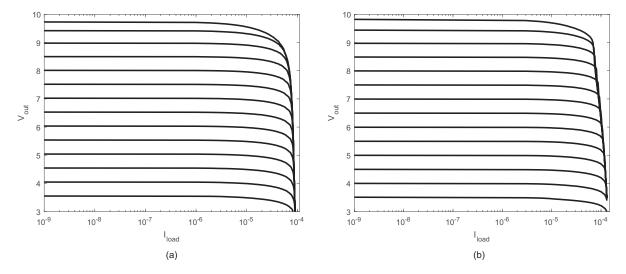

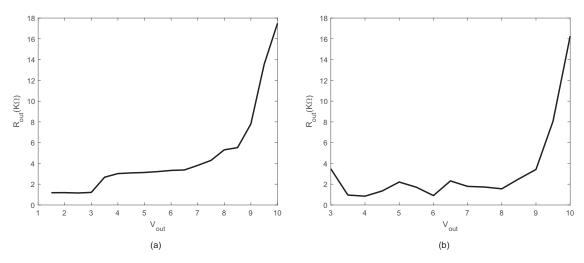

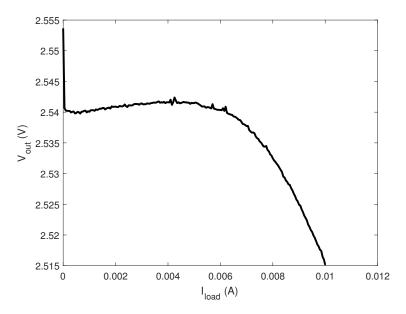

|                                                | 0.2                                                     | 5.2.1 Experimental results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                      |

|                                                |                                                         | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                      |

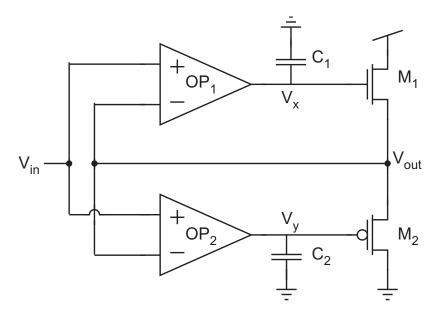

|                                                | 5.3                                                     | Mid-rail Regulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ~ ı                                                                  |

|                                                | 5.3<br>5.4                                              | Mid-rail Regulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                      |

| Ę                                              | 5.4                                                     | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                      |

| Ę                                              | 5.4                                                     | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 84<br>88                                                             |

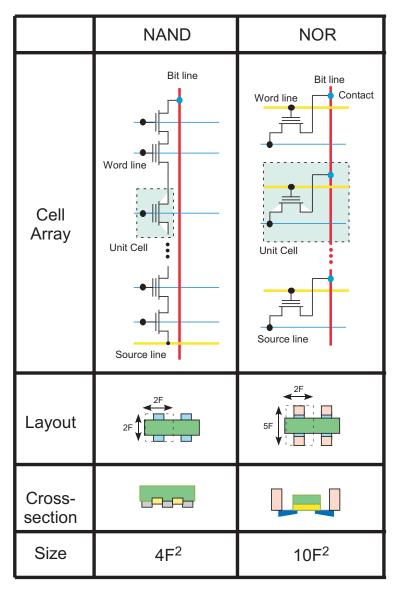

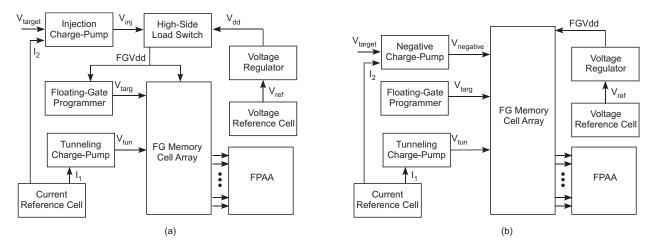

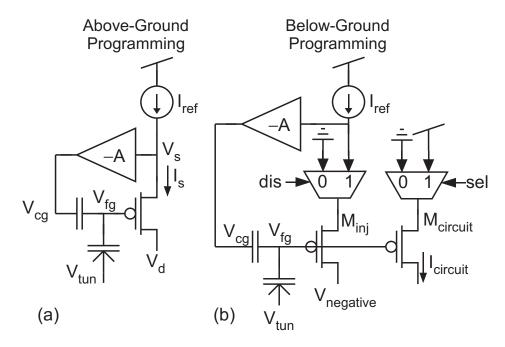

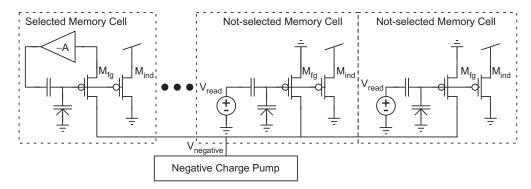

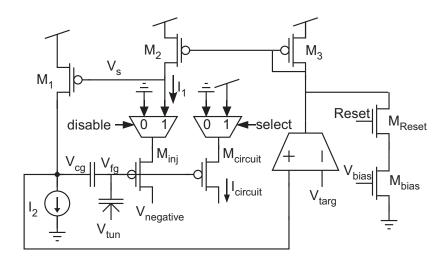

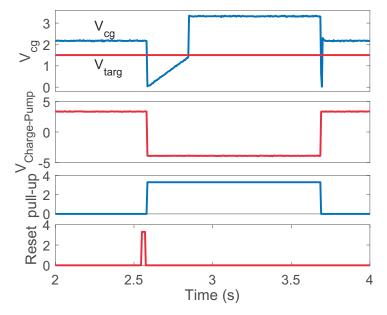

| 6 J                                            | 5.4                                                     | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 84<br>88<br>88                                                       |

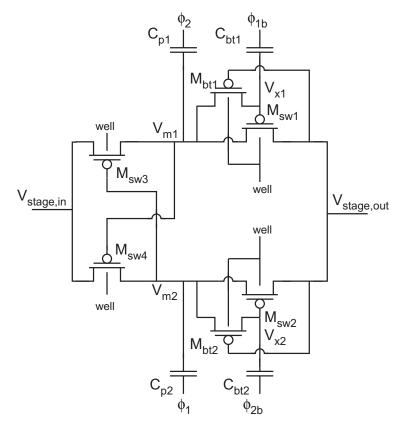

| 6 J                                            | $5.4$ ${f Belo}$                                        | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 84<br>88<br>88                                                       |

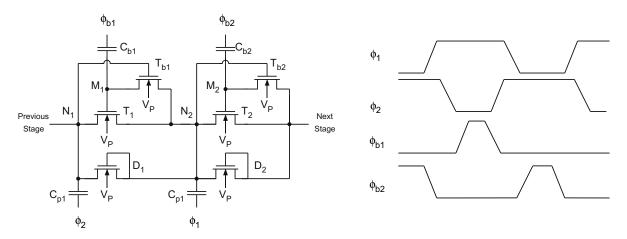

| 6 J                                            | $5.4$ ${f Belo}$                                        | Conclusion  Ow-Ground Injection of FG Transistors for Programmable Analog Circuits  Below Ground Programming  6.1.1 Floating-Gate Memory Cell  6.1.2 Negative Charge Pump                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 84<br>88<br>88<br>90                                                 |