Faculty Scholarship

2003

# Formation of porous silicon through the nanosized pores of an anodized alumina template

Biswajit Das

S. P. McGinnis

Follow this and additional works at: https://researchrepository.wvu.edu/faculty\_publications

#### **Digital Commons Citation**

Das, Biswajit and McGinnis, S. P., "Formation of porous silicon through the nanosized pores of an anodized alumina template" (2003). *Faculty Scholarship*. 171. https://researchrepository.wvu.edu/faculty\_publications/171

This Article is brought to you for free and open access by The Research Repository @ WVU. It has been accepted for inclusion in Faculty Scholarship by an authorized administrator of The Research Repository @ WVU. For more information, please contact ian.harmon@mail.wvu.edu.

University Libraries University of Nevada, Las Vegas

Electrical and Computer Engineering Faculty Publications

**Electrical & Computer Engineering**

2003

# Formation of porous silicon through the nanosized pores of an anodized alumina template

Biswajit Das University of Nevada, Las Vegas, dasb@unlv.nevada.edu

S. P. McGinnis *West Virginia University*

Follow this and additional works at: https://digitalscholarship.unlv.edu/ece\_fac\_articles Part of the <u>Electrical and Computer Engineering Commons</u>

**Repository Citation**

Das, B., McGinnis, S. P. (2003). Formation of porous silicon through the nanosized pores of an anodized alumina template. *Applied Physics Letters*, 83 2904-2906. https://digitalscholarship.unlv.edu/ece\_fac\_articles/375

This Article is brought to you for free and open access by the Electrical & Computer Engineering at Digital Scholarship@UNLV. It has been accepted for inclusion in Electrical and Computer Engineering Faculty Publications by an authorized administrator of Digital Scholarship@UNLV. For more information, please contact digitalscholarship@unlv.edu.

Biswajit Das and S. P. McGinnis

Citation: Appl. Phys. Lett. **83**, 2904 (2003); doi: 10.1063/1.1614842 View online: http://dx.doi.org/10.1063/1.1614842 View Table of Contents: http://apl.aip.org/resource/1/APPLAB/v83/i14 Published by the AIP Publishing LLC.

**Applied Physics**

Letters

### Additional information on Appl. Phys. Lett.

Journal Homepage: http://apl.aip.org/ Journal Information: http://apl.aip.org/about/about\_the\_journal Top downloads: http://apl.aip.org/features/most\_downloaded Information for Authors: http://apl.aip.org/authors

### Formation of porous silicon through the nanosized pores of an anodized alumina template

Biswajit Das<sup>a)</sup>

Department of Electrical and Computer Engineering, University of Nevada, Las Vegas, Nevada 89154-4026

S. P. McGinnis

Lane Department of Computer Science and Electrical Engineering, West Virginia University, Morgantown, West Virginia 26506-6109

(Received 27 May 2003; accepted 11 August 2003)

This letter demonstrates the ability to fabricate porous silicon through the nanoscale pores of an anodized alumina template formed on a silicon substrate. The alumina template acts as a protective coating on the porous silicon surface increasing its mechanical integrity, thus eliminating the need for delicate handling that is usually required for this material system. The optical properties of the porous silicon formed through the template show characteristics similar to that of normally formed porous silicon. In addition, the porous silicon optical properties show very little degradation with time; the alumina coating is believed to contribute to this improved stability. The results are significant and can increase the likelihood of commercial applications of this material. © 2003 American Institute of Physics. [DOI: 10.1063/1.1614842]

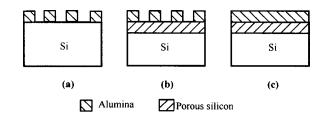

Porous silicon is a promising material for several device applications, including electronic, photonic, sensing, and electromagnetic shielding.<sup>1,2</sup> Porous silicon is formed by the anodization of single-crystal silicon and consists of an interconnected network of nanoscale silicon structures.<sup>1</sup> However, porous silicon is inherently a nonuniform material that has nonuniform optical and electronic properties. In addition, it is also a mechanically fragile material requiring careful material handling. While a number of devices based on porous silicon have been proposed and demonstrated, their applications have been limited by the material's nonuniform properties and its fragile nature.<sup>3</sup> If the material uniformity and mechanical integrity of porous silicon can be improved, it can increase the potential for commercial applications of this material. Towards this goal, we have fabricated porous silicon by anodization through an electrochemically formed porous alumina template on a silicon substrate. The fabrication technique is schematically shown in Fig. 1. A porous alumina template is first created on the silicon substrate by anodizing a thin film of aluminum deposited on the substrate. Next, porous silicon is formed through the template pores. The pores in the template are then sealed using a simple hydrolysis step to form a protective coating on the porous silicon layer.

This structure is expected to have many advantages. Anodized alumina is a mechanically robust material and is expected to increase the structure's mechanical integrity, thus making it more amenable to manufacturing processes including lithography and patterning. The top coating is also expected to protect the porous silicon layer from its surrounding environment, thus reducing the aging effect and increasing the device lifetime. Since anodized alumina is optically transparent over a wide spectral range, it is not expected to affect the optical properties of porous silicon. In addition, there is also some likelihood that the uniform pore spacing in the alumina template can increase the spatial uniformity of the porous silicon.

Anodized alumina is an important material system for the nonlithographic implementation of semiconductor and metal nanostructures.<sup>4</sup> When aluminum is anodized in a suitable acidic electrolyte under controlled conditions, it oxidizes to form anodic aluminum oxide (alumina) containing a two-dimensional hexagonal array of cylindrical nanoscale pores. Anodized alumina has been used as a nanotemplate for the implementation of a variety of metal and semiconductor nanostructures.<sup>4–6</sup>

The fabrication of porous silicon through the nanoscale pores of an anodized alumina template was carried out using the following procedure. The starting substrates were 0.1– 0.3-ohm cm *p*-type  $\langle 100 \rangle$  silicon wafers that were cleaned using a standard technique and were etched in a 1% hydrofluoric acid solution to remove any native oxide. Next, a 0.5- $\mu$ m-thick aluminum layer was deposited by sputtering on the back of the wafers and annealed at 450 °C for 30 min to form a good electrical contact. Following this, for half of the wafers, a 0.4- $\mu$ m-thick aluminum film was deposited on the top polished surface. The top aluminum layers were then anodized in a 20% sulfuric acid solution to form the porous alumina templates. Anodizations were performed at constant

FIG. 1. Schematic representation of the template-based porous silicon formation process. (a) Formation of nanoporous alumina template on silicon, (b) formation of porous silicon through template pores, and (c) sealing of the template pores to form a protective coating.

2904

#### © 2003 American Institute of Physics

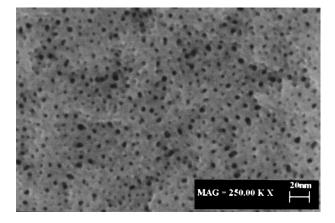

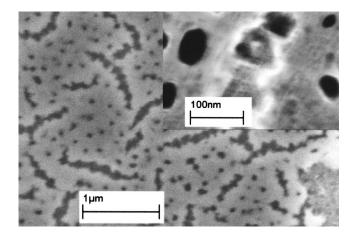

FIG. 2. Field-emission SEM image of a typical porous alumina template used in the experiments.

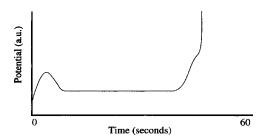

current densities ranging between 10 and 40 mA/cm<sup>2</sup>, corresponding to pore diameters in alumina in the range of 10 to 40 nm. Figure 2 shows the top view of a thin-film alumina template used in the experiments. During the anodization process, voltage-time characteristics were monitored to ensure that pores went all the way down to the silicon substrate. A typical voltage-time characteristic for an aluminum thin film on silicon during constant current anodization is shown in Fig. 3. The initial rise in voltage is due to barrier layer formation, which is followed by a decrease in voltage corresponding to pore initiation. The voltage reaches a plateau when the pores reach their final diameter as determined by the anodization current density. Next, during pore propagation, the voltage remains constant and then increases sharply when the pores reach the silicon surface. For this experiment, the anodization process was stopped when the voltage started increasing, thus ensuring that the silicon substrate was reached. The samples were then pore-widened in phosphoric acid for 3 min to remove any leftover materials and any unetched barrier layer.

Porous silicon was formed by anodization through the template pores in a 49% HF and ethanol solution for 30 s using a current density ranging between 25 and 60 mA/cm<sup>2</sup>. It may be pointed out that the anodization current densities for the template-based samples were calculated in the same way as for the bare silicon samples (i.e., current divided by the total area), and template coverage was not taken into account. This is expected introduce a small error in the estimation of the anodization current density for the template-based samples. The samples were then hydrolyzed to seal the pores by boiling in deionized water for 60 s. For comparison,

FIG. 3. Typical voltage-time characteristics during the formation of a porous alumina template on silicon. The anodization was stopped when the potential started increasing rapidly.

FIG. 4. Field-emission SEM image of the top surface of a porous silicon sample covered with hydrolyzed alumina template.

porous silicon samples were fabricated on substrates without the top aluminum coating (bare silicon) using similar anodization parameters.

A serious concern during this experiment was the survivability of the alumina template during the HF anodization step used to form porous silicon. Although some thinning of the template was expected, it was important that the alumina template at least partially survived the HF anodization step. Scanning electron microscope (SEM) imaging of the surface indicated the presence of the alumina layer, the images are presented in the next section. In addition, we confirmed the presence of the alumina layer through C-V measurements. For this purpose, aluminum electrodes, 0.5  $\mu$ m thick and 2 mm in diameter, were sputter-deposited on the top of the sample to form capacitors. Standard high-frequency C-Vmeasurements were then performed on the samples. From a comparison of the C-V data with that on bare porous silicon and on alumina templates on silicon, the presence of an alumina layer was confirmed. However, a large device-to-device variation was observed in the C-V data, which suggested that the alumina layer was nonuniform over the sample. While an exact determination of the alumina layer thickness could not be made due to the spread in the device data, the average thickness of the alumina layer was estimated to be around 0.1  $\mu$ m.

The field-emission SEM image of the top view of a typical porous silicon sample formed through an alumina template (and hydrolyzed) is shown in Fig. 4. The inset shows the image at a higher magnification. In Fig. 4, the top layer showing pores is hydrolyzed alumina. Closer inspection shows that while some of the pores were sealed by the hydrolysis step, there are quite a few that were not sealed. In Fig. 4, the pore diameters also appear to be larger than those typically obtained for the anodization conditions used to form the alumina template. We believe that the alumina template was partially etched during the HF acid anodization step used to form the porous silicon. This etching caused significant widening of the pores that can be seen in Fig. 4. The pore widening has also caused the pores on grain boundaries to connect with each other, causing the long openings that are observed in Fig. 4 (see Fig. 2 for pore formation on grain boundaries). A closer inspection of long openings in Fig. 4 reveals the edges of the connected pores.

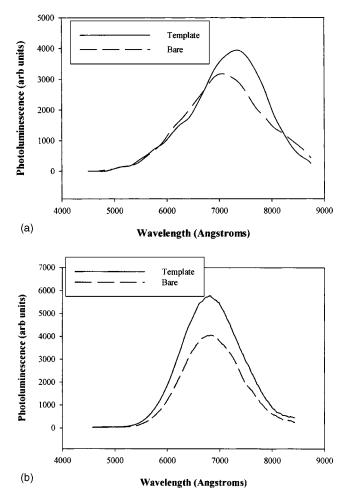

FIG. 5. Room-temperature PL data from porous silicon samples created through alumina template (solid line) and on bare silicon (dashed line) at current densities of (a) 25 and (b) 60 mA/cm<sup>2</sup>. The excitation wavelength for PL measurement was 325 nm.

The room-temperature PL characteristics for the samples fabricated at 25 and 60 mA/cm<sup>2</sup> are shown in Figs. 5(a) and 5(b), respectively. All samples showed luminescence characteristics that are typically observed in porous silicon, with PL peak positions similar to that reported for porous silicon fabricated under similar conditions. However, the following interesting observations are made from the photoluminescence data. (a) Porous silicon samples fabricated through alumina templates show increased luminescence intensity compared to porous silicon formed on bare silicon under identical processing conditions. This was observed to be true for all porous silicon samples fabricated using current densities ranging between 25 and 60 mA/cm<sup>2</sup>. (b) Porous silicon fabricated through alumina templates shows a small redshift in the PL peak position compared to that formed on bare silicon. The redshift was largest for porous silicon fabricated at 25 mA/cm<sup>2</sup> and decreased with increasing anodization current density; no significant shift was observed for porous silicon fabricated at 60 mA/cm<sup>2</sup>. From Fig. 5(a), the redshift was estimated to be around 75 meV. To investigate the aging effect, the samples were stored in closed plastic containers at room temperature and the PL measurements were repeated after a month. The PL characteristics did not show any degradation or variation, and were similar to the PL characteristics observed before.

Our results confirm that porous silicon was formed through the pores of the alumina templates and that the material was of good optical quality. An interesting observation was the increased brightness of the porous silicon formed through the alumina templates compared to that formed on bare silicon. We believe that the alumina top layer acts as a protective coating that improves the porous silicon surface characteristics, thus increasing the luminescence intensity. Another interesting observation was the redshift in PL peak position for the template-based porous silicon formed at lower current densities. The reason for the redshift is not clear at this time; in fact, it is contrary to what was expected. The effective current densities for the template-based samples were expected to be larger, as explained earlier, which should have given rise to a blueshift of the PL peak position. We believe that the following may be a possible explanation for this result. It is expected that for the template-based samples, the porous silicon formation proceeds downwards initially and then spreads laterally. For smaller anodization currents, the lateral spread is expected to be smaller compared to that for higher anodization currents. Thus, the effect of the template, which is to guide the formation of porous silicon downward, is expected to be more prominent for lower anodization currents than for higher anodization currents. Thus, the redshift is expected to decrease with increasing current densities. As for the redshift itself, we believe that it arises due to the formation of arrays of nanosized porous silicon islands for lower anodization current densities. However, we do not have a clear explanation for this at this time and are currently investigating this effect further.

In summary, we have demonstrated the formation of porous silicon through the pores of an anodized alumina template on a silicon substrate. The template, when hydrolyzed, forms a protective layer on top of the porous silicon layer. This protective layer significantly reduces the aging effect in porous silicon and makes the surface mechanically robust, which allows further processing. The photoluminescence properties of the porous silicon formed through templates did not show any degradation after a month. The results are significant and can form the basis for the development of more stable porous silicon devices. In addition, it may be possible to design an anodization process to take advantage of the order provided by the alumina template.

The authors would like to acknowledge Nancy Giles and Pavan Singaraju for their help with device fabrication and characterization.

- <sup>1</sup>R. T. Collins, P. M. Fauchet, and M. A. Tischler, Phys. Today **50**, 24 (1997).

- <sup>2</sup>T. Komoda, X. Sheng, and N. Koshida, J. Vac. Sci. Technol. B **17**, 1076 (1999).

- <sup>3</sup> S. McGinnis, P. Sines, and B. Das, Electrochem. Solid-State Lett. **2**, 468 (1999); K. D. Hirschman, L. Tsybeskov, S. P. Duttagupta, and P. M. Fauchet, Nature (London) **384**, 338 (1996).

- <sup>4</sup>D. Routkevitch, T. Bigioni, M. Moskovits, and X. Jing Ming, J. Phys. Chem. **100**, 14037 (1996).

- <sup>5</sup>B. Das and S. McGinnis, Appli. Phys. A Mater. Sci. Process **71**, 1 (2000).

- <sup>6</sup>H. Masuda, H. Yamada, and M. Satoh, Appl. Phys. Lett. **71**, 2770 (1997).