Missouri University of Science and Technology Scholars' Mine

Electrical and Computer Engineering Faculty Research & Creative Works

**Electrical and Computer Engineering**

01 Sep 2014

## First Demonstration of Ultra-Thin SiGe-Channel Junctionless Accumulation-Mode (JAM) Bulk FinFETs on Si Substrate with PN Junction-Isolation Scheme

DongHyun Kim Missouri University of Science and Technology, dkim@mst.edu

Tae Kyun Kim

Young Gwang Yoon

**Byeong Woon Hwang**

et. al. For a complete list of authors, see https://scholarsmine.mst.edu/ele\_comeng\_facwork/3725

Follow this and additional works at: https://scholarsmine.mst.edu/ele\_comeng\_facwork

Part of the Electromagnetics and Photonics Commons

## **Recommended Citation**

D. Kim et al., "First Demonstration of Ultra-Thin SiGe-Channel Junctionless Accumulation-Mode (JAM) Bulk FinFETs on Si Substrate with PN Junction-Isolation Scheme," *Journal of the Electron Devices Society*, vol. 2, no. 5, pp. 123-127, Institute of Electrical and Electronics Engineers (IEEE), Sep 2014. The definitive version is available at https://doi.org/10.1109/JEDS.2014.2326560

This Article - Journal is brought to you for free and open access by Scholars' Mine. It has been accepted for inclusion in Electrical and Computer Engineering Faculty Research & Creative Works by an authorized administrator of Scholars' Mine. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

Received 23 April 2014; revised 8 May 2014; accepted 15 May 2014. Date of publication 22 May 2014; date of current version 21 August 2014. The review of this paper was arranged by Editor Colin McAndrew.

Digital Object Identifier 10.1109/JEDS.2014.2326560

# First Demonstration of Ultra-Thin SiGe-Channel Junctionless Accumulation-Mode (JAM) Bulk FinFETs on Si Substrate with PN Junction-Isolation Scheme

### DONG-HYUN KIM, TAE KYUN KIM (Student Member, IEEE), YOUNG GWANG YOON, BYEONG-WOON HWANG, YANG-KYU CHOI, BYUNG JIN CHO (Senior Member, IEEE), AND SEOK-HEE LEE (Member, IEEE)

Department of Electrical Engineering, Korea Advanced Institute of Science and Technology, Daejeon 305-701, Korea CORRESPONDING AUTHOR: SEOK-HEE LEE (seokheelee@ee.kaist.ac.kr)

**ABSTRACT** A SiGe-channel junctionless-accumulation-mode (JAM) PMOS bulk FinFETs were successfully demonstrated on Si substrate with PN junction-isolation scheme for the first time. The JAM bulk FinFETs with fin width of 18 nm exhibits excellent subthreshold characteristics such as subthreshold swing of 64 mV/decade, drain-induced barrier lowering (DIBL) of 40 mV/V and high  $I_{on}/I_{off}$  current ratio (>1 × 10<sup>5</sup>). The change of substrate bias from 0 to 5 V leads to the threshold voltage shift of 53 mV by modulating the effective channel thickness. When compared to the Si-channel bulk FinFETs with fin width of 18 nm, Si and SiGe channel devices exhibits comparable subthreshold swing and DIBL. For devices with longer fin width, SiGe channel devices exhibits much lower DIBL, indicating superior top-gate controllability and robustness to substrate bias compared to the Si channel devices. A zero temperature coefficient point was observed in the transfer curves as temperature increases from -120 to  $120^{\circ}$ C, confirming that mobility degradation is dominantly affected by phonon scattering mechanism.

**INDEX TERMS** Junctionless (JL) field-effect transistor (FET), junctionless-accumulation-mode (JAM) FET, SiGe bulk FinFET, junction-isolation.

#### **I. INTRODUCTION**

THE recent scaling down of CMOSFETs poses a challenge to industrial fabrication of ultra-shallow and abrupt source/drain (S/D) junctions [1]. In response, a junction-less (JL) FET was proposed [2] and demonstrated [3] with unique features of a uniformly and homogeneously doped channel from the source to the drain. The JL FET is well known to have stronger immunity against short-channel effect (SCE) than inversion-mode (IM) FETs because it has a longer effective channel length than the physical channel length [4]–[6].

To alleviate the problems arising from the heavily doped channel of JL FET such as increased ionized impurity scattering, random dopant fluctuation, and subthreshold swing (SS), the channel concentration needs to be lowered. Such measures, however, result in an increase of the S/D parasitic resistance and a reduction of the drain current. Therefore, a junctionless accumulation-mode (JAM) FET has been developed by introducing additional S/D implantation into a JL FET [7]–[9].

To obtain a fully-depleted channel at the off state, most JL FETs have been evaluated on an ultra-thin body FET based on either a silicon-on-insulator (SOI) substrate or as a nanowire FET [10]–[12]. Although our group has demonstrated a Si-channel JAM bulk FinFET aimed at attaining threshold voltage (V<sub>th</sub>) control by substrate bias (V<sub>b</sub>), low substrate cost compared to SOI and compatibility with the standard CMOS process [13], isolated junction of Si-channel devices suffered junction breakdown under high substrate bias (V<sub>b</sub> > 3 V).

Meanwhile, there have been some reports on Ge-channel JL FETs upon consideration of higher hole mobility and

improved gate electrostatics owing to higher dielectric constant of Ge in a multi-gate scheme [14]. Despite such merits of Ge channel, reported subthreshold characteristics are severely degraded due to the low quality of Ge epitaxial layer on Si substrate and inferior interface property between dielectric and channel.

In this work, a SiGe-channel JAM bulk FinFET was demonstrated on Si substrate for the first time to make use of the advantages resulting from high mobility and high dielectric constant of SiGe while achieving relatively mitigated density of the interface trap compared to that of Ge. Also, lower diffusivity of boron in SiGe makes SiGe channel a promising PMOS channel candidate beyond Si channel for JAM bulk FinFET from the viewpoints of improved SCE and robustness to substrate bias.

#### **II. DEVICE FABRICATION**

The key fabrication processes have been described including the schematic view of our JAM FET in the previous work [13]. Starting with 8-inch n-type bulk Si substrate, an undoped 15-nm-thick SiGe epi-layer was grown to be Ge composition of 30% using ultra-high-vacuum CVD. Phosphorus ion implantation for a channel-stop was performed to obtain a phosphorus concentration of  $1 \times 10^{17}$  cm<sup>-3</sup> in the uppermost region of the underlying n-type Si. Boron ion implantation was then carried out for SiGe channel doping with a concentration of  $1 \times 10^{18}$  cm<sup>-3</sup>. Both implant energies of the above-mentioned implantations were targeted to make a 15-nm-thick p-type SiGe channel. A photo-resist trimming technique was applied to reduce the fin width and gate length, varied from 12 to 43 nm and from 120 to 1000 nm, respectively. After gate patterning, additional S/D implantation of boron was performed for the formation of heavily doped S/D (> $1 \times 10^{20}$  cm<sup>-3</sup>), followed by spike annealing at 1020°C for 1 second in N<sub>2</sub> ambient. The equivalent oxide thickness of hafnium oxide (HfO<sub>2</sub>) and titanium nitride (TiN) gate stacks was extracted to be  $\sim$ 1.4 nm from a MOS capacitor as described in our previous report [13].

#### **III. RESULTS AND DISCUSSION**

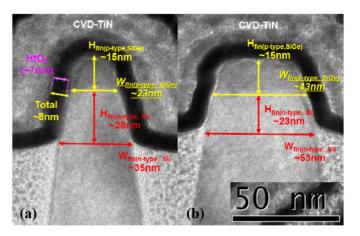

Fig. 1 shows cross-sectional transmission electron microscope (TEM) images of the JAM SiGe bulk FinFETs. When the fin width ( $W_{fin}$ ) was defined as the bottom width of the p-type SiGe fin,  $W_{fin}$  was measured to be ~23 nm and ~43 nm, in Fig. 1(a) and (b), respectively. Partial exposure of the underlying n-type fin was inevitable for tri-gate scheme. The fin height of the underlying n-type Si fin ranges were controlled from ~23 to ~28 nm by the wet dip process of high density plasma oxide. The total physical thickness of ALD-HfO<sub>2</sub> was found to be ~8 nm, comprising the HfO<sub>2</sub> layer of ~7 nm and interfacial oxide of ~1 nm. The secondary ion mass spectroscopy data shows a junction-isolated doping profile with a p-type channel having average boron concentration of 1 × 10<sup>18</sup> cm<sup>-3</sup> and an underlying n-type

**FIGURE 1.** Cross-sectional TEM images of the fabricated JAM PMOS SiGe bulk FinFETs with various fin widths. (a)  $W_{fin} = 23$  nm and (b)  $W_{fin} = 43$  nm.

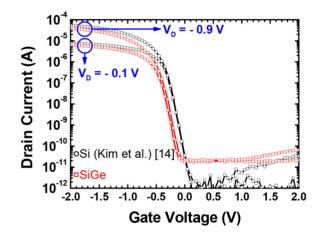

**FIGURE 2.** Transfer curves of the SiGe JAM device with  $W_{fin} = 18$  nm and  $L_G = 180$  nm compared to previously reported Si JAM device with the same physical dimension by Kim *et al.* [13].

Si of phosphorus concentration of  $1 \times 10^{17}$  cm<sup>-3</sup> although it is not shown in this paper.

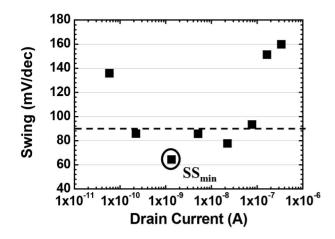

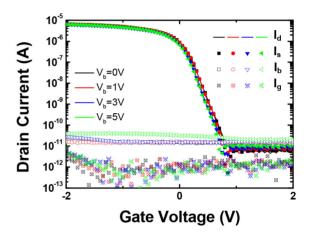

The performance of SiGe-channel JAM FinFETs was measured at room temperature using a semiconductor device analyzer (Agilent Technologies, Model B1500). Fig. 2 shows the transfer curves of the JAM SiGe device with  $W_{fin} = 18$  nm and  $L_G = 180$  nm, providing superior transfer characteristics such as  $SS_{min} = 64$  mV/dec., DIBL = 40 mV/V, and  $I_{on}/I_{off}$  ratio > 1 × 10<sup>5</sup>. The SS extracted from Fig. 2 remains less than ~90 mV/decade over three decades of drain current, as shown in Fig. 3.

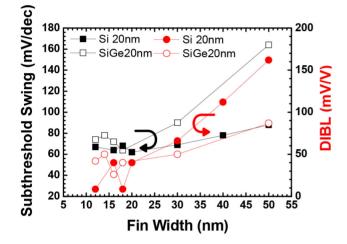

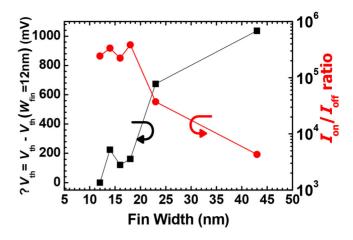

Figs. 4 and 5 show the effect of the channel dimensions on the device characteristics. Here,  $\Delta V_{th} = V_{th} - V_{th}$  (at  $W_{fin} = 12$ nm). The increase of fin width weakened the gate controllability, resulting in the increases of SS and DIBL as shown in Fig. 4. SS was relatively higher in SiGe device, because of relatively higher interface trap density than Si device. Si and SiGe channel devices shows comparable levels of DIBL for small fin width. However, SiGe channel device shows much lower DIBL for larger fin width. Such lower

FIGURE 3. Distribution of SS measured from SiGe JAM device in Fig. 2.

FIGURE 4. Dependency of SS, DIBL, and as a function of fin width at a fixed  $L_{\rm G}$  = 180 nm.

DIBL in SiGe channel is explained by the higher dielectric constant of SiGe than that of Si as a channel material in FinFET structure. Also, the increase of the fin width results in a decrease of PMOS V<sub>th</sub> (i.e. the increase in the amount of positive V<sub>th</sub> shift) and a decrease of the I<sub>on</sub>/I<sub>off</sub> ratio due to an increase of SS and I<sub>off</sub> current as shown in Fig. 5. The JAM devices with fin widths less than 18 nm give I<sub>on</sub>/I<sub>off</sub> ratio >1 × 10<sup>5</sup>. Here, SS<sub>min</sub> was measured at drain voltage (V<sub>d</sub>) = -0.1 V. DIBL has been extracted from the gate voltages corresponding to drain current (I<sub>d</sub>) =  $10^{-9}$  A. V<sub>th</sub> was defined as the gate voltage measured at I<sub>d</sub> =  $10^{-7}$  A. I<sub>on</sub> and I<sub>off</sub> have been measured at V<sub>g,on</sub> = V<sub>th</sub> + 0.7 × V<sub>d</sub> and V<sub>g,off</sub> = V<sub>th</sub> -  $0.3 \times V_d$ , where V<sub>d</sub> = -0.9 V.

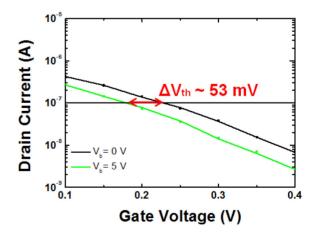

Figs. 6 and 7 show the V<sub>b</sub>-induced behavior of the transfer curves, indicating that the increase of positive V<sub>b</sub> causes an increase of V<sub>th</sub>, reflecting a decrease of the effective channel thickness by widening the depletion width in the SiGe channel isolated by pn junction, unlike SOI or nanowire FETs. The amount of V<sub>th</sub> shift by changing V<sub>b</sub> from 0 V to 5 V is ~53 mV as shown in Fig. 7. Here, the V<sub>b</sub> was applied to the underlying n-type Si substrate by chuck-biasing on the backside of the wafer. The JL FET has been reported to

FIGURE 5. Dependency of  $\bigtriangleup V_{th},$   $I_{on}/I_{off}$  ratio as a function of fin width at a fixed  $L_G$  = 180 nm.

FIGURE 6. Effect of substrate bias (V<sub>b</sub>) on transfer curves of the device with  $L_G$  = 180 nm and  $W_{fin}$  = 45 nm.

FIGURE 7. Enlarged plot of the transfer curves corresponding to  $V_{\rm b}$  = 0, 5 V, respectively in Fig. 6.

be more sensitive to substrate bias than an IM FET because of bulk conduction mechanism [15]. It was observed that both the substrate current (I<sub>b</sub>) and the gate leakage current (I<sub>g</sub>) were negligible in Fig. 6. Given that I<sub>b</sub> was less than  $1 \times 10^{-10}$  A, the partially exposed underlying n-type

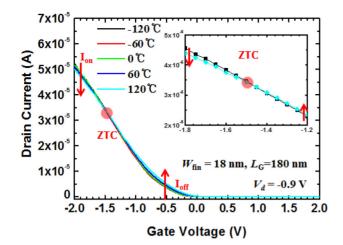

**FIGURE 8.** Transfer curves of the device with  $L_G = 180$  nm and  $W_{fin} = 18$  nm when temperature is varied from -120 to  $120^\circ$ C. Inset shows the transfer curves of the same device at -120 and  $120^\circ$ C for clear presentation of the ZTC.

TABLE 1. Parameters extracted for JAM FinFETs on bulk silicon

| Channel<br>Material | W <sub>fin</sub><br>(nm) | L <sub>G</sub><br>(nm) | SS <sub>min</sub><br>(mV/dec.) | $\int_{at} V_{th} V_b = 2V$ |           |

|---------------------|--------------------------|------------------------|--------------------------------|-----------------------------|-----------|

| Si [13]             | 18                       | 180                    | 68                             | 110 mV                      | Junction  |

| -                   |                          |                        |                                |                             | breakdown |

| SiGe (This          | 18                       | 180                    | 64                             | 20 mV                       | 53 mV     |

| Work)               |                          |                        |                                |                             |           |

Si fin did not form any parasitic channel. When compared to our previous work [13], shown in Table 1, SiGe channel device shows much lower threshold voltage variation at higher substrate bias, indicating superior top-gate controllability of SiGe device because of SiGe channel's higher dielectric constant compared to Si channel in a FinFET structure. Also, the robust junction-isolation of SiGe channel withstands over 5 V of substrate bias, much higher than that of Si channel reported in our previous work [13].

Fig. 8 shows that an increase of temperature leads to both a Vth decrease and SS increase, presenting the existence of a zero temperature coefficient (ZTC) point, contrary to the absence of a ZTC point in previously reported JL FETs [16], [17]. The temperature dependent performance of SiGe channel FinFETs was measured with chamber probe station (MS Probe Station, Model MST-1000B). Here, the ZTC point is the gate voltage where the drain current does not change by varying temperature, and it is important for analog circuit design with temperature stability and reliable circuit operation [17]. The conventional JL FETs with channel doping concentration of more than  $1 \times 10^{19}$  cm<sup>-3</sup> have been reported to show temperature-independent mobility because of enhanced Coulomb scattering comparable to phonon scattering [16]. Meanwhile, the relatively low doping channel concentration  $(1 \times 10^{18} \text{ cm}^{-3})$  of our JAM bulk FinFET was found to give rise to mobility degradation dominated by phonon scattering rather than Coulomb scattering at high temperature.

When compared with JAM Si-channel FinFETs in our previous work [13], JAM SiGe-channel FinFETs in this work show improved DIBL characteristics and low I<sub>b</sub> under high V<sub>b</sub> (5 V) because of their superior top-gate electrostatics and more robustness to substrate bias, respectively. As further works, gate length scaling of our SiGe-channel JAM bulk FinFETs can be reinforced by tuning either the S/D additional implant process conditions or the gate spacer material/sidewall thickness, given that JAM FETs with normal transfer characteristics have been reported down to  $L_G = 20$  nm despite abrupt degradation of SS and DIBL [10], [11].

#### **IV. CONCLUSION**

In conclusion, SiGe-channel JAM bulk FinFETs were successfully demonstrated on Si substrate for the first time. Outstanding transfer characteristics were achieved from the JAM devices with  $W_{\rm fin}$  of less than 18 nm. The JAM devices with various fin width give superior subthreshold characteristics resulted from enhanced top gate controllability and robustness to substrate bias compared to Si-channel-based devices. The substrate bias allowed modulation of  $V_{\rm th}$  owing to the virtue of a body-tied FET with suppressed I<sub>b</sub> of less than 1 × 10<sup>-10</sup> A. A zero temperature coefficient point was observed, confirming that mobility degradation was dominantly affected by phonon scattering mechanism.

#### REFERENCES

- R. H. Dennard, F. H. Gaensslen, V. L. Rideout, E. Bassous, and A. R. LeBlanc, "Design of ion-implanted MOSFET's with very small physical dimensions," *IEEE J. Solid-State Circuits*, vol. 9, no. 5, pp. 256–268, Oct. 1974.

- [2] C. W. Lee *et al.*, "Junctionless multigate field-effect transistor," *Appl. Phys. Lett.*, vol. 94, no. 5, pp. 053511–053512, Feb. 2009.

- [3] J. P. Colinge *et al.*, "Nanowire transistors without junctions," *Nat. Nanotech.*, vol. 5, no. 3, pp. 225–229, Feb. 2010.

- [4] J. P. Colinge *et al.*, "Junctionless nanowire transistor (JNT): Properties and design guidelines," *Solid-State Electron.*, vol. 65–66, pp. 33–37, Nov.–Dec. 2011.

- [5] M. Wu, X. Jin, R. Chuai, X. Liu, and J. H. Lee, "Simulation study on short channel double-gate junctionless field-effect transistors," *J. Semiconductors*, vol. 34, no. 3, pp. 034004–034008, 2013.

- [6] M. H. Han, C. Y. Chang, H. B. Chen, Y. C. Cheng, and Y. C. Wu, "Device and circuit performance estimation of junctionless bulk FinFETs," *IEEE Trans. Electron Devices*, vol. 60, no. 6, pp. 1807–1813, Jun. 2013.

- [7] C.-W. Lee *et al.*, "Performance estimation of junctionless multigate transistors," *Solid-State Electron.*, vol. 54, no. 2, pp. 97–103, 2010.

- [8] R. Rios *et al.*, "Comparison of junctionless and conventional trigate transistors with  $L_g$  down to 26 nm," *IEEE Electron Device Lett.*, vol. 32, no. 9, pp. 1170–1172, Sep. 2011.

- [9] D. Y. Jeon *et al.*, "Low-temperature electrical characterization of junctionless transistors," *Solid-State Electron.*, vol. 80, pp. 135–141, Feb. 2013.

- [10] S. Barraud *et al.*, "Scaling of trigate junctionless nanowire MOSFET with gate length down to 13 nm," *IEEE Electron Device Lett.*, vol. 33, no. 9, pp. 1225–1227, Sep. 2012.

- [11] C. H. Park *et al.*, "Electrical characteristics of 20-nm junctionless Si nanowire transistors," *Solid-State Electron.*, vol. 73, pp. 7–10, Jul. 2012.

- [12] D. I. Moon, S. J. Choi, J. P. Duarte, and Y. K. Choi, "Investigation of silicon nanowire gate-all-around junctionless transistors built on a bulk substrate," *IEEE Trans. Electron Devices*, vol. 60, no. 4, pp. 1355–1360, Apr. 2013.

- [13] T. K. Kim *et al.*, "First demonstration of junctionless accumulationmode bulk FinFETs with robust junction isolation," *IEEE Electron Device Lett.*, vol. 34, no. 12, pp. 1479–1481, Dec. 2013.

- [14] R. Yu *et al.*, "Device design and estimated performance for p-type junctionless transistors on bulk germanium substrates," *IEEE Trans. Electron Devices*, vol. 59, no. 9, pp. 2308–2313, Sep. 2012.

- [15] S. J. Park et al., "Back biasing effects in tri-gate junctionless transistors," Solid-State Electron., vol. 87, pp. 74–79, Sep. 2013.

- [16] C. W. Lee *et al.*, "High-temperature performance of silicon junctionless MOSFETs," *IEEE Trans. Electron Devices*, vol. 57, no. 3, pp. 620–625, Mar. 2010.

- [17] R. D. Trevisoli *et al.*, "The zero temperature coefficient in junctionless nanowire transistors," *Appl. Phys. Lett.*, vol. 101, no. 6, pp. 062101–062103, Aug. 2012.

YANG-KYU CHOI received the Ph.D. degree from the University of California (UC), Berkeley, Berkeley, CA, USA, in 2001. He is currently a Professor with the Department of Electrical Engineering, Korea Advanced Institute of Science and Technology, Daejeon, Korea. His current research interests include exploratory devices and nanofabrication technologies for bioelectronics as well as biosensors. He has authored over 200 papers. He was the recipient of the Sakrison Award for the Best Dissertation from the EECS

Department of the UC-Berkeley, in 2002, and also the recipient of the Scientist of the Month Award for July 2006 from the Ministry of Science and Technology in Korea.

**DONG-HYUN KIM** received the B.S. degree in electrical engineering from the Korea Advanced Institute of Science and Technology, Daejeon, Korea, in 2012, where he is currently pursuing the M.S. degree in electrical engineering. His current research interests include nanometer-scale device fabrication, characterization, and TSV technology.

**BYUNG JIN CHO** (M'97–SM'01) received the B. S. degree in electrical engineering from Korea University, Seoul, South Korea, in 1985, and the master's and Ph.D. degrees in electrical engineering from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea, in 1987 and 1991, respectively. From 1991 to 1993, he was with IMEC, Leuven, Belgium, as a Research Fellow, where he worked on advanced silicon processing. From 1993 to 1997, he joined the Memory Research and Development Division of Hyundai

Electronics, Industrial Corporation (currently SK Hynix Semiconductor), Korea, as a Section Manager, where he led a research team for the process development for 256 M and 1 G DRAM and Flash EEPROM. In 1997, he joined the Department of Electrical and Computer Engineering at the National University of Singapore, as a faculty member. Since 2007, he is with the Department of Electrical Engineering, KAIST, Daejeon, as a faculty member. His current research interests include advanced CMOS device and front-end process technology, memory devices, graphene electronics, thermoelectric devices, and flexible electronics. He has published over 350 technical papers and holds over 30 patents. He has delivered numerous invited talks at international conferences. He is currently the President of Korean Graphene Research Society.

**SEOK-HEE LEE** (M'04) received the B.S. and M.S. degrees from Seoul National University, Seoul, Korea, in 1988 and 1990, respectively, and the Ph.D. degree from Stanford University, Stanford, CA, USA, in 2000, all in materials science and engineering. From 1990 to 1995, he was with the Advanced Semiconductor Development Group, Hyundai Electronics (now Hynix Semiconductor), where he worked in the area of gate oxide scaling and reliability. In 1994, he discovered a new breakdown mechanism, i.e.,

"quasi-breakdown (also known as soft breakdown)," in ultrathin gate oxide regime. The research was reported at the International Electron Devices Meeting (IEDM)'94 and has since developed into a new area of study in oxide reliability. This work has been cited in over 100 research papers since then. From 2000 to 2010, he was with the Portland Technology Development Group, Intel Corporation, Hillsboro, OR, USA, where he worked on process integration and yield on Intel's 130-, 90-, and 65-nm advanced CMOS logic technologies. Most recently, he has managed a process integration team responsible for developing 32-nm logic process technology. Since 2010, he has been with the Faculty of the Department of Electrical Engineering, Korea Advanced Institute of Science and Technology, Daejeon, Korea, as an Associate Professor. His current research interests include nanoscale devices and fabrication. He was a committee member for CMOS devices and technology subcommittee for the 2008-2009 IEEE IEDM and the chair for the same subcommittee in the 2010 IEDM. He is currently the Asian Arrangement Chair for the 2011 IEDM and steering committee member of the 2011 International Conference on Solid State Devices and Materials. He was the recipient of the Intel Achievement Award thrice (Intel's highest recognition for technical achievement) and 11 Intel Divisional Recognition Awards for his technical achievements in transistor and process development.

**TAE KYUN KIM** received the B.S. degree in ceramic engineering from Yonsei University, Seoul, Korea, in 1996 and the M.S. degree in electrical engineering from Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea, in 1998. He is currently pursuing the Ph.D. degree in electrical engineering from KAIST. His current research interests include nanometer-scale novel device fabrication and characterization.

YOUNG GWANG YOON received the B.S. degree in electronic engineering from Inha University, Incheon, Korea, in 2008, and the M.S. degree from the School of Information and Communications, Gwangju Institute of Science and Technology, Gwangju, Korea, in 2010. He is currently pursuing the Ph.D. degree in electrical engineering from the Korea Advanced Institute of Science and Technology, Daejeon, Korea. His current research interests include device physics, process technology, characterization of Si, SiGe, and III-V-based

CMOS devices with the main focus on reliability and low frequency noise.

**BYEONG-WOON HWANG** received the B.S. and M.S. degrees in electrical engineering from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea, in 2010 and 2012, respectively. He is currently pursuing the Ph.D. degree in electrical engineering from KAIST. His current research interests include nanometer-scale device simulation and modeling.