# Scholars' Mine

## Masters Theses

Student Theses and Dissertations

Fall 2018

# Analysis and mitigation of parallel-plate noise for high-isolation applications

Zachary Joel Legenzoff

Follow this and additional works at: https://scholarsmine.mst.edu/masters\_theses

Part of the Electrical and Computer Engineering Commons Department:

## **Recommended Citation**

Legenzoff, Zachary Joel, "Analysis and mitigation of parallel-plate noise for high-isolation applications" (2018). *Masters Theses*. 7828. https://scholarsmine.mst.edu/masters\_theses/7828

This thesis is brought to you by Scholars' Mine, a service of the Missouri S&T Library and Learning Resources. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

## ANALYSIS AND MITIGATION OF PARALLEL-PLATE NOISE FOR HIGH-ISOLATION APPLICATIONS

by

## ZACHARY JOEL LEGENZOFF

## A THESIS

Presented to the Graduate Faculty of the

## MISSOURI UNIVERSITY OF SCIENCE AND TECHNOLOGY

In Partial Fulfillment of the Requirements for the Degree

MASTER OF SCIENCE

in

## ELECTRICAL ENGINEERING

2018

Approved by

James Drewniak, Advisor David Pommerenke Daryl Beetner

#### ABSTRACT

Achieving highs levels of isolation between different functionalities in a PCB can be challenging. One of the major issues is that vertically adjacent planes or area fills in a PCB can form a parallel-plate waveguide with no cutoff frequency and serve as an efficient coupling mechanism between interconnects. Due to the finite size of the conductors, reflections off the edges of these parallel-plate cavities can result in the formation of standing-wave patterns with very high field strengths, resulting in high coupling at certain frequencies. This noise coupling mechanism can be suppressed by connecting the parallel plates together with an adequate amount of vias. However, adjacent power and ground conductors can not be conductively connected together because they are at different DC potentials. As a result, there is no way to eliminate the existence of parallel-plate noise in a power/ground cavity. A fundamental understanding of this problem is needed to determine how it can be mitigated.

The first part of the thesis develops a qualitative understanding of the underlying physics of how noise is coupled to the parallel plates from a variety of interconnects and how the noise can spread throughout the design. This discussion is then expanded to more complex geometries that are representative of what could occur in actual designs. Test vehicles are created to study the noise coupling to various interconnects from noise injected into the power distribution network by an amplifier. Parameters affecting the transfer of noise from an amplifier to the power distribution network, such as the addition of capacitors, are then explored. An expression to predict the noise coupling using S-parameter measurements of the PCB and the amplifier is developed. It is demonstrated that results from full-wave electromagnetic simulation can be used to predict the amount of noise coupling before PCB fabrication. General design recommendations are then presented to improve design robustness to the parallel-plate noise.

#### ACKNOWLEDGMENTS

This work has been funded by the Department of Energy's Kansas City National Security Campus which is operated and managed by Honeywell Federal Manufacturing & Technologies, LLC under contract number DE-NA0002839.

I would like to thank Honeywell FM&T for the opportunity to pursue a master's degree full time through the Technical Fellowship program. I would specifically like to thank Sean Garrison for his technical mentorship throughout the program and for providing direction for the research. I would also like to thank my managers during the program, Belinda Thompson and Jeremy Wilson, for supporting me throughout the process. I would also like to thank Mary Peete for submitting the numerous part orders that were needed to conduct this research.

I would like to thank Dr. Drewniak, my advisor, for his support and guidance of my research work. His guidance and teaching were instrumental in developing the skills necessary to be successful in my research. I would also like to thank Dr. Pommerenke for the wealth of experimental knowledge I have gained through his lab-based classes. I have him to thank for developing my skill and creativity in RF measurements. I would also like to thank Dr. Beetner for serving on my committee with his busy schedule. In addition, I would to thank all the students at the EMC Lab, it has been a privilege to interact with and learn from many bright minds.

Lastly, I would like to thank my family and friends for their support and encouragement while pursuing my master's degree.

## **TABLE OF CONTENTS**

| AE | BSTRACT                                                 | iii  |

|----|---------------------------------------------------------|------|

| AC | CKNOWLEDGMENTS                                          | iv   |

| LI | ST OF ILLUSTRATIONS                                     | viii |

| SE | CTION                                                   |      |

| 1. | INTRODUCTION                                            | 1    |

|    | 1.1. MIXED-SIGNAL DESIGN CONSIDERATIONS                 | 1    |

|    | 1.2. PARALLEL-PLATE WAVEGUIDE                           | 3    |

|    | 1.3. PARALLEL-PLATE CAVITY RESONATOR                    | 8    |

|    | 1.4. PARALLEL-PLATE NOISE IN THE LITERATURE             | 13   |

|    | 1.5. OVERVIEW OF THE REMAINING SECTIONS                 | 15   |

| 2. | BASIC PARALLEL-PLATE COUPLING MECHANSIMS                | 16   |

|    | 2.1. ELECTRIC FIELD AND MAGNETIC FIELD COUPLING         | 16   |

|    | 2.2. VIA TO VIA COUPLING WITHIN A PARALLEL-PLATE CAVITY | 22   |

|    | 2.3. PARALLEL-PLATE CAVITY COUPLING TO CBCPW            | 30   |

|    | 2.4. PARALLEL-PLATE CAVITY COUPLING TO STRIPLINE        | 37   |

|    | 2.5. COUPLING BETWEEN CAVITIES                          | 39   |

| 3. | TEST VEHICLE COUPLING ANALYSIS                          | 44   |

|    | 3.1. OVERVIEW OF TEST VEHICLES                          | 44   |

|    | 3.2. FULL-WAVE EM SIMULATION MODEL                      | 48   |

|    | 3.3. EXCITATION AND FIELDS OF POWER NET CAVITY          | 49   |

|    | 3.4.  | EXCIT  | ATION OF ADDITIONAL CAVITIES THROUGHOUT THE PCB .           | 54  |

|----|-------|--------|-------------------------------------------------------------|-----|

|    | 3.5.  | COUP   | LING TO VIA IN THE POWER CAVITY                             | 61  |

|    | 3.6.  | COUP   | LING TO VIA LOCATED NEXT TO THE POWER CAVITY                | 64  |

|    | 3.7.  | COUP   | LING TO VIA AWAY FROM THE POWER CAVITY                      | 67  |

|    | 3.8.  | COUP   | LING TO STRIPLINE ON SAME LAYER AS POWER NET                | 70  |

|    | 3.9.  |        | LING TO STRIPLINE ROUTED BELOW CIRCULAR APER-               | 73  |

|    | 3.10. |        | LING TO STRIPLINE REFERENCED TO POWER NET AREA              | 76  |

|    | 3.11. | COUP   | LING FROM EDGE LAUNCH COAXIAL CONNECTORS                    | 79  |

| 4. | INTI  | EGRAT  | ION OF ACTIVE AND PASSIVE COMPONENTS                        | 83  |

|    | 4.1.  | NOISE  | E COUPLING FROM IC THROUGH THE PDN                          | 83  |

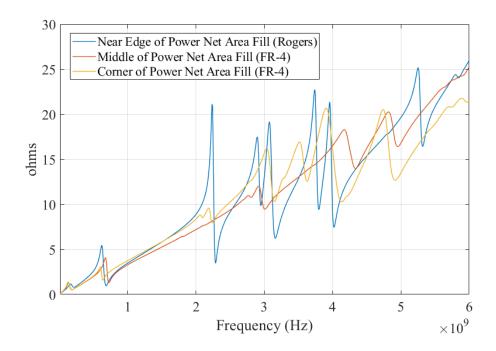

|    | 4.2.  | INPUT  | TIMPEDANCE OF PCB PDN SEEN BY IC                            | 84  |

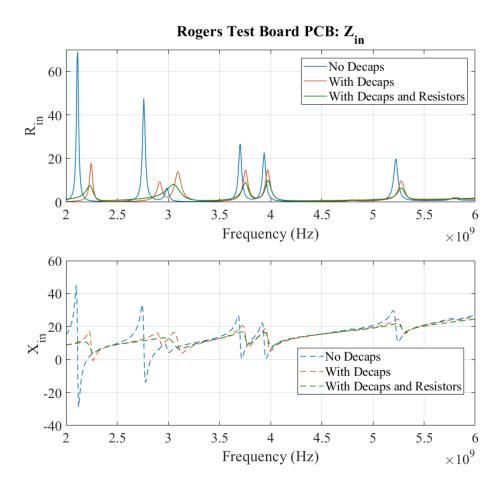

|    | 4.3.  |        | CT OF PASSIVE COMPONENTS ON THE PCB PDN INPUT<br>DANCE      | 91  |

|    | 4.4.  | POWE   | R TRANSFER FROM IC TO PCB PDN                               | 95  |

|    | 4.5.  | COUP   | LING PREDICTION WITH S-PARAMETERS                           | 98  |

|    | 4.6.  | COUP   | LING PREDICTION WITH FULL-WAVE SIMULATION RESULTS           | 108 |

|    | 4.7.  | EFFEC  | CT OF UNTERMINATED INTERCONNECTS                            | 114 |

| 5. | DES   | IGN RE | ECOMMENDATIONS                                              | 117 |

|    | 5.1.  | OVER   | VIEW                                                        | 117 |

|    | 5.2.  | POWE   | R DISTRIBUTION NETWORK DESIGN RECOMMENDATIONS .             | 117 |

|    |       | 5.2.1. | Use of Higher-Loss Dielectric Material for PWR/GND Cavity   | 118 |

|    |       | 5.2.2. | Use of Thin Dielectric Layer for PWR/GND Cavity             | 118 |

|    |       | 5.2.3. | Use of Passive SMT Components                               | 119 |

|    |       | 5.2.4. | Elimination of Power Net Area Fill/Power Plane              | 119 |

|    |       | 5.2.5. | Minimizing Cut-outs and Apertures Above and Below Power Net | 120 |

|        | 5.2.6. | Optimal Location of IC on Power Net for Minimizing Noise Transfer 120              |

|--------|--------|------------------------------------------------------------------------------------|

|        | 5.2.7. | Brief Review of More Complex PWR/GND Noise Suppression<br>Methods                  |

| 5.3.   | SUPPF  | RESSION OF PARALLEL-PLATE NOISE IN GND CAVITIES 121                                |

|        | 5.3.1. | Use of Stitching Vias Throughout the Entire PCB 121                                |

|        | 5.3.2. | Use of Via Fence for Suppressing Parallel-Plate Noise between<br>Two Regions       |

|        | 5.3.3. | Use of Via Ring Around Signal Via for Suppressing Parallel-Plate<br>Noise Transfer |

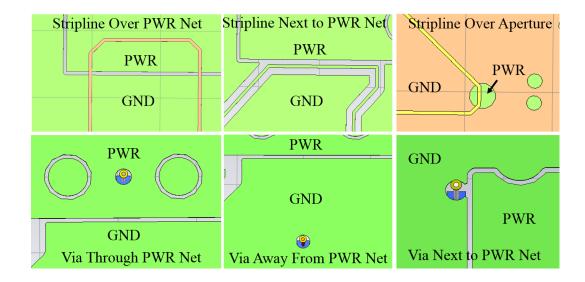

| 5.4.   | ROUT   | ING OF SENSITIVE SIGNALS                                                           |

|        | 5.4.1. | Avoidance of Referencing Transmission Line to Power Net 127                        |

|        | 5.4.2. | Avoidance of Via Placement Through PWR/GND Cavity for Sen-<br>sitive Nets          |

|        | 5.4.3. | Differential Signaling Increased Robustness to Parallel-Plate Noise. 128           |

| APPEN  | DIX    |                                                                                    |

| REFERI | ENCES  |                                                                                    |

| VITA   |        |                                                                                    |

## LIST OF ILLUSTRATIONS

| Figur | re                                                                                                                                       | Page |

|-------|------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1.1.  | A rectangular parallel-plate waveguide                                                                                                   | 3    |

| 1.2.  | Cross-section of a via passing through a parallel-plate pair.                                                                            | 6    |

| 1.3.  | E-field probe locations and normal E-field in cavity                                                                                     | 7    |

| 1.4.  | Comparison of $E_z$ as a function of distance for simulation and analytical solution                                                     | . 8  |

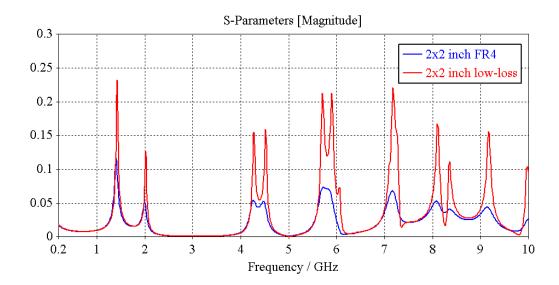

| 1.5.  | Comparison of simulated coupling between vias in a cavity for lossy (FR-4) and low-loss dielectric material.                             | 13   |

| 2.1.  | Electric field source coupling to stripline.                                                                                             | 17   |

| 2.2.  | Magnetic field and surface current density on electric field coupled stripline                                                           | 18   |

| 2.3.  | Magnetic field source coupling to stripline                                                                                              | 19   |

| 2.4.  | Magnetic field source coupling to stripline                                                                                              | 20   |

| 2.5.  | Electric field and surface currents for via passing through cavity with absorbing boundary conditions to prevent standing-wave patterns. | 23   |

| 2.6.  | Test board for measuring coupling between two vias in a cavity.                                                                          | 25   |

| 2.7.  | Measured coupling between vias in 62 mil thick parallel-plate cavity.                                                                    | 26   |

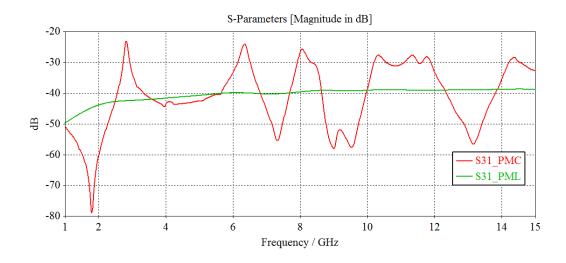

| 2.8.  | Simulated coupling comparison between vias in parallel-plate cavity with PML B.C. and PMC B.C.                                           | 27   |

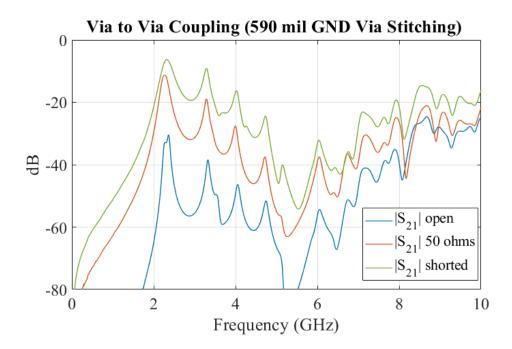

| 2.9.  | Measured coupling between vias: short, open, 50 ohm comparison                                                                           | 28   |

| 2.10  | . Simulated coupling distance comparison between vias in parallel-plate cavity with PML boundary conditions.                             | 29   |

| 2.11  | . Magnitude of $TM_{z0}$ fields as a function of distance.                                                                               | 29   |

| 2.12  | . Electric field cross-section of CBCPW in logarithmic scale.                                                                            | 31   |

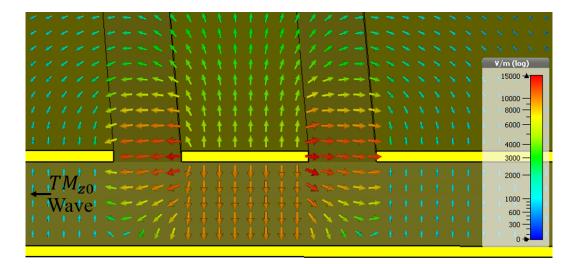

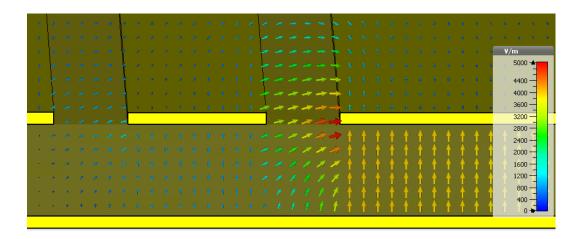

| 2.13  | . Electric field showing parallel-plate mode coupling to CBCPW                                                                           | 32   |

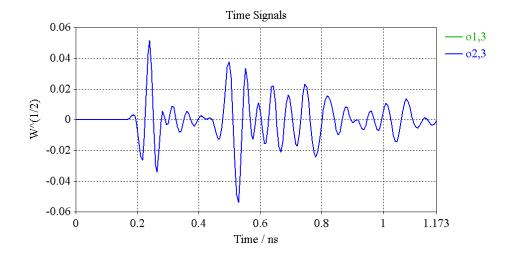

| 2.14  | . Coupled time-domain signals measured at CBCPW ports showing equal mag-<br>nitude and phase.                                            | 32   |

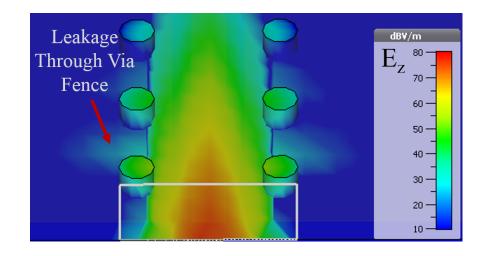

| 2.15  | . $E_z$ around CBCPW showing small field leakage through via fence                                                                       | 33   |

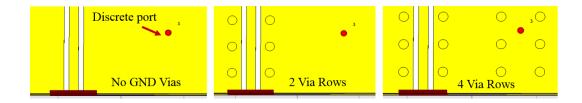

| 2.16. | Geometry comparison of different amount of GND vias for simulation model                          | 34 |

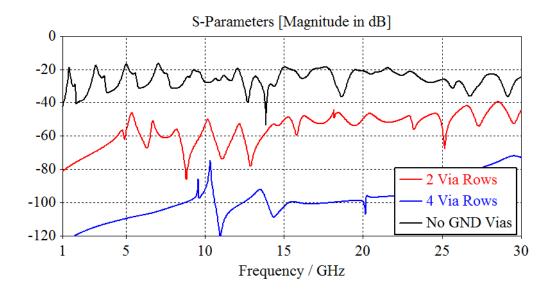

|-------|---------------------------------------------------------------------------------------------------|----|

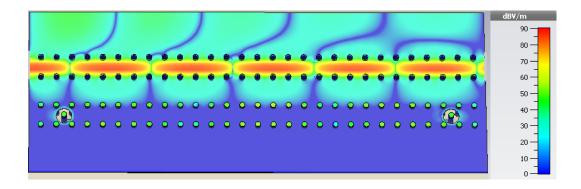

| 2.17. | Comparison of simulated coupling for different amount of GND vias                                 | 34 |

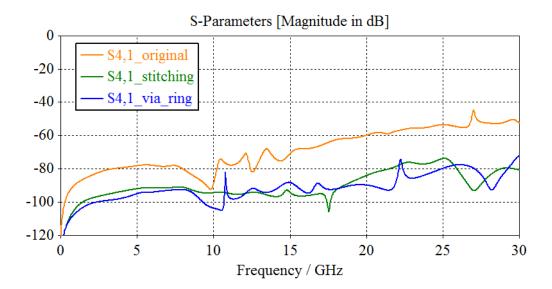

| 2.18. | $E_z$ between Layers 1 and 2 at 15 GHz of test vehicle                                            | 36 |

| 2.19. | Simulated coupling comparison of test vehicle with additional stitching and GND via ring.         | 36 |

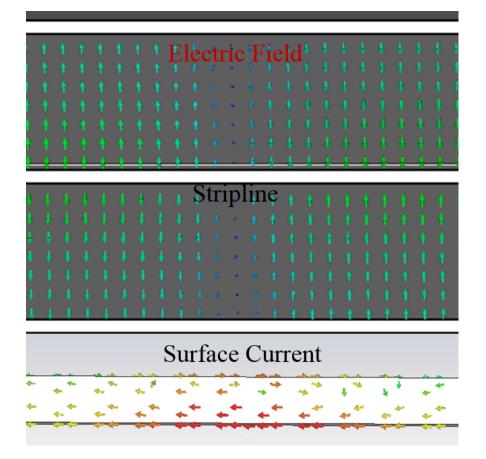

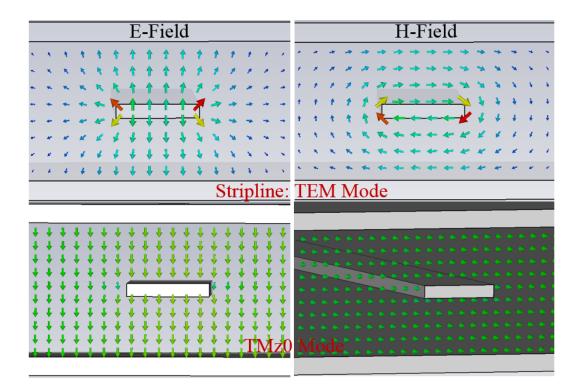

| 2.20. | TEM mode of stripline and stripline surrounded by $TM_{z0}$ fields in cavity                      | 38 |

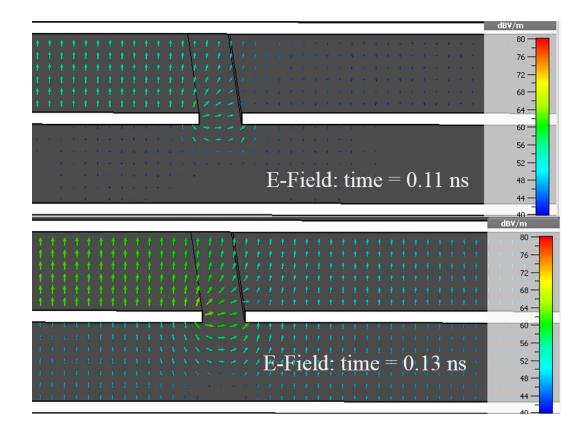

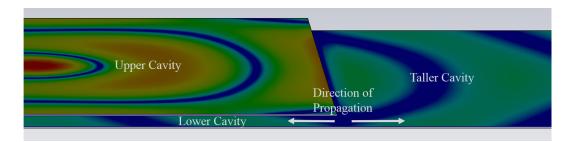

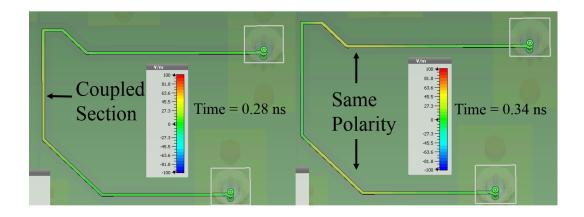

| 2.21. | Time-domain $\vec{E}$ of gapped plane showing excitation of bordering cavities                    | 41 |

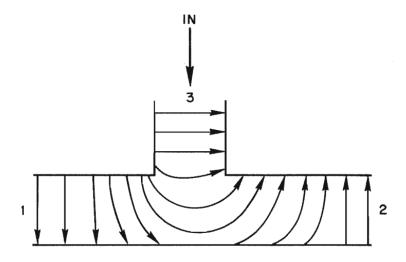

| 2.22. | Electric field lines for a waveguide E-plane tee.                                                 | 41 |

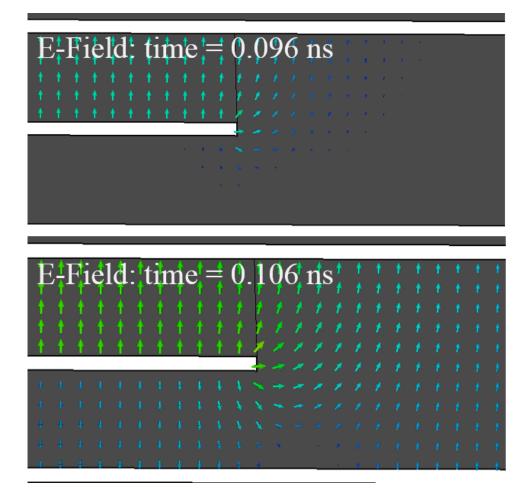

| 2.23. | Time-domain $\vec{E}$ at plane edge showing excitation of bordering cavities                      | 42 |

| 2.24. | Propagation of $TM_{z0}$ waves in two cavities that are excited at the edge of a bordering cavity | 42 |

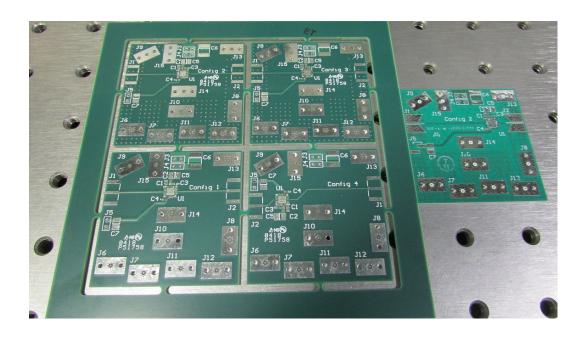

| 3.1.  | Picture of the five different configurations of the test vehicle                                  | 45 |

| 3.2.  | An overview of the victim interconnects included in the test vehicles                             | 45 |

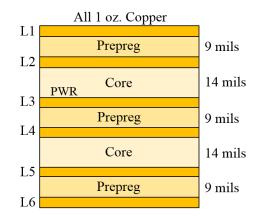

| 3.3.  | Stack-up of 6 Layer FR-4 for configurations 1-4.                                                  | 46 |

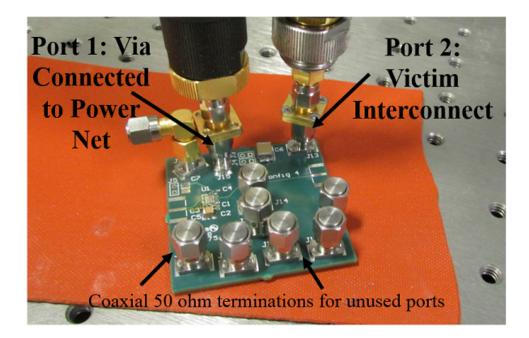

| 3.4.  | Set-up for passive coupling network analyzer measurement                                          | 47 |

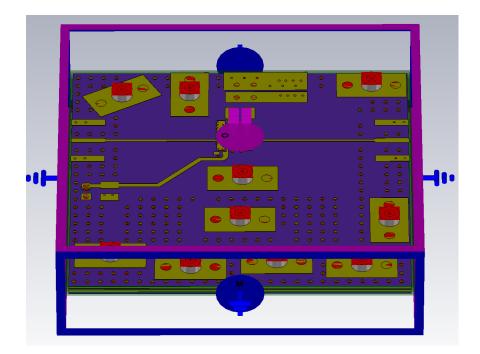

| 3.5.  | Microwave CST simulation model of Configuration 2 test vehicle                                    | 48 |

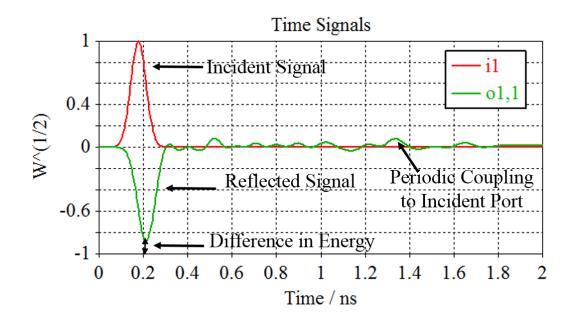

| 3.6.  | Simulated time signals of port exciting the PWR/GND cavity                                        | 50 |

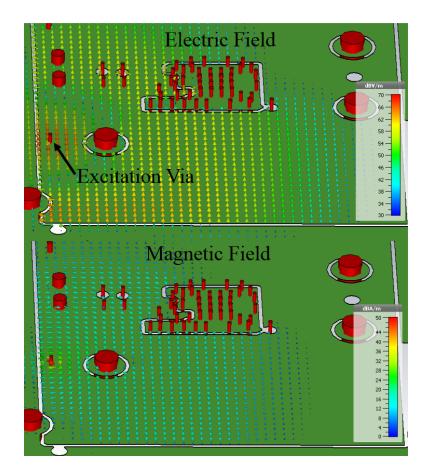

| 3.7.  | Fields in the PWR/GND cavity excited by via.                                                      | 51 |

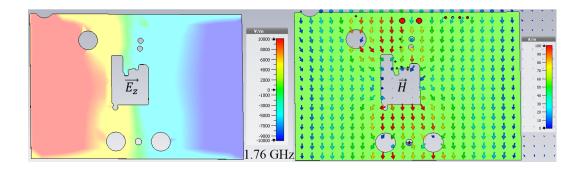

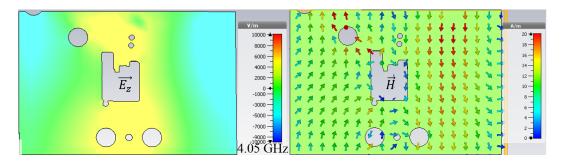

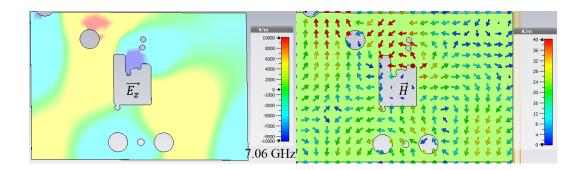

| 3.8.  | $E_z$ and $\vec{H}$ in PWR/GND cavity at 1.76 GHz                                                 | 52 |

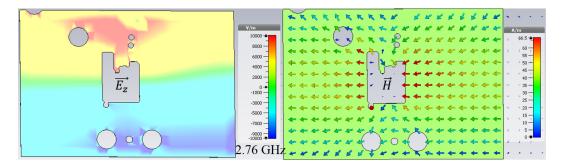

| 3.9.  | $E_z$ and $\vec{H}$ in PWR/GND cavity at 2.76 GHz                                                 | 52 |

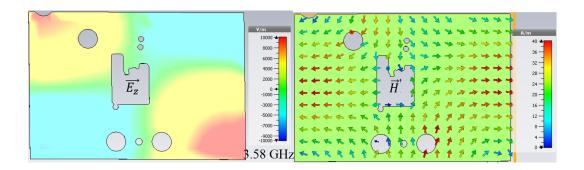

| 3.10. | $E_z$ and $\vec{H}$ in PWR/GND cavity at 3.58 GHz                                                 | 53 |

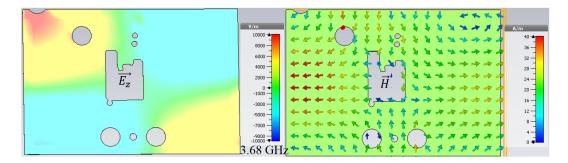

| 3.11. | $E_z$ and $\vec{H}$ in PWR/GND cavity at 3.68 GHz.                                                | 53 |

| 3.12. | $E_z$ and $\vec{H}$ in PWR/GND cavity at 4.05 GHz.                                                | 53 |

| 3.13. | $E_z$ and $\vec{H}$ in PWR/GND cavity at 6.12 GHz.                                                | 53 |

| 3.14. | $E_z$ and $\vec{H}$ in PWR/GND cavity at 7.06 GHz.                                                | 54 |

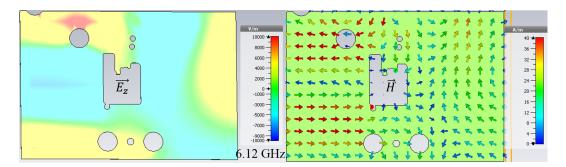

| 3.15. | $\vec{E}$ at gap between PWR and GND area fills                                                   | 55 |

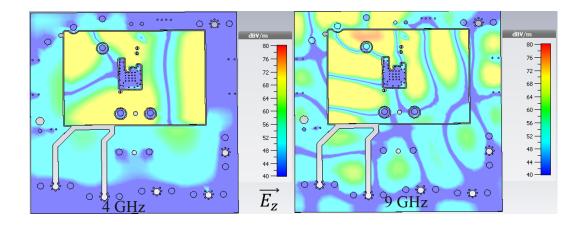

| 3.16. | Electric field distributions in Layer 2-3 GND cavity at 4 GHz and 9 GHz                           | 56 |

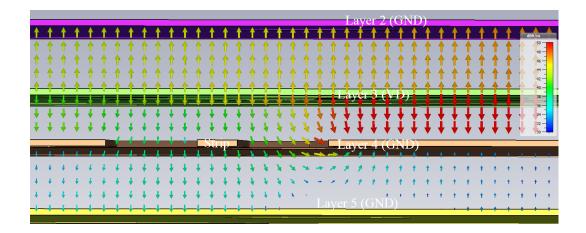

| 3.17. | $\vec{E}$ at gap in Layer 4 showing the excitation of the Layer 4-5 cavity                             | 57 |

|-------|--------------------------------------------------------------------------------------------------------|----|

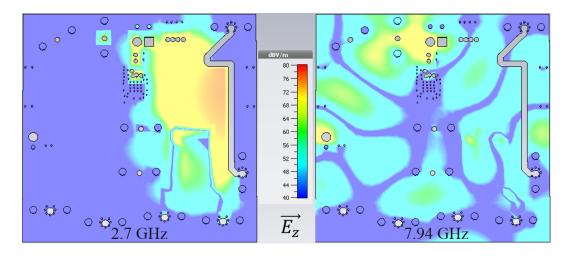

| 3.18. | Electric field distributions in Layer 2-3 GND cavity at 2.7 GHz and 7.94 GHz                           | 57 |

| 3.19. | $\vec{E}$ at gap in Layer 5 showing the excitation of the Layer 5-6 cavity                             | 58 |

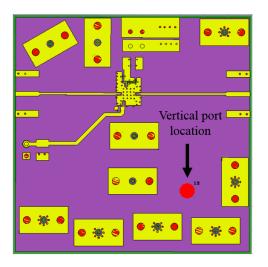

| 3.20. | Location of vertical discrete port for cavity coupling simulation                                      | 59 |

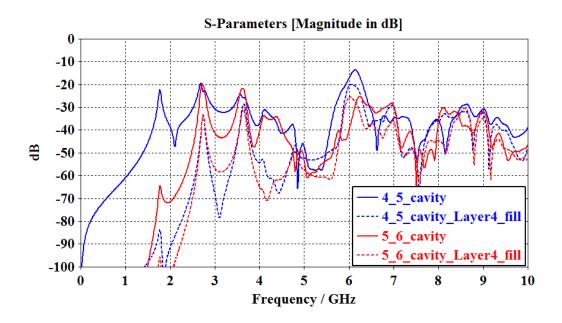

| 3.21. | Simulated cavity coupling comparison with Layer 4 cutout removed                                       | 60 |

| 3.22. | Simulated cavity coupling comparison with PWR via stubs removed                                        | 60 |

| 3.23. | Measured and simulated coupling to the via in the power cavity                                         | 62 |

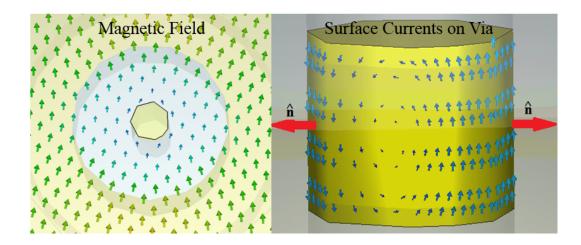

| 3.24. | Uniform magnetic field around via and corresponding surface currents                                   | 63 |

| 3.25. | Cross-section of the electric field at the via anti-pad                                                | 63 |

| 3.26. | Electric field from PWR/GND cavity coupling to via next to cavity                                      | 64 |

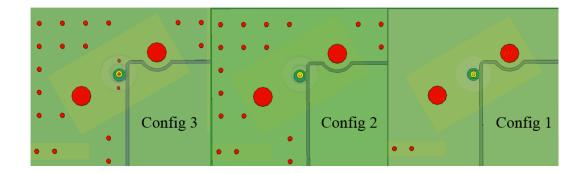

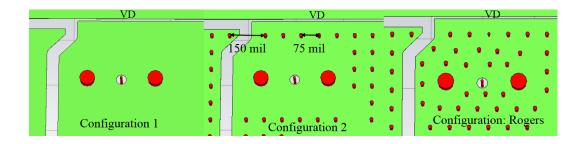

| 3.27. | Comparison of the number of GND vias around the via for the different configurations                   | 66 |

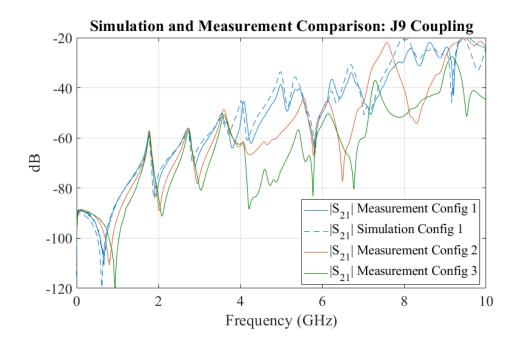

| 3.28. | Measured and simulated coupling to the via next to the power cavity                                    | 66 |

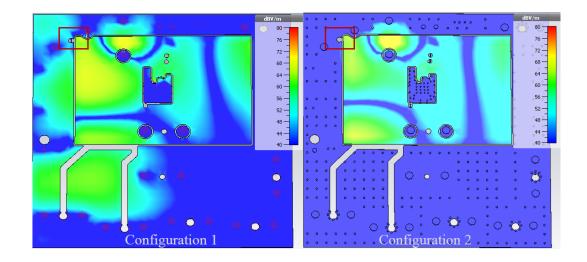

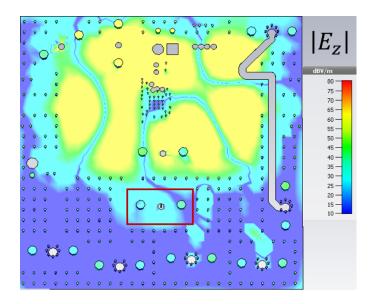

| 3.29. | Comparison of the Layer 2-3 cavity electric field distribution at 5 GHz between Configuration 1 and 2. | 67 |

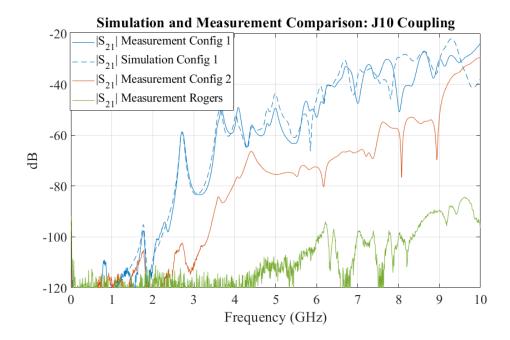

| 3.30. | Measured and simulated coupling to the via away from the power cavity                                  | 68 |

| 3.31. | Configuration comparison of the number of GND vias around the via                                      | 68 |

| 3.32. | Electric field in Layer 4-5 cavity at 10 GHz for Configuration 2                                       | 69 |

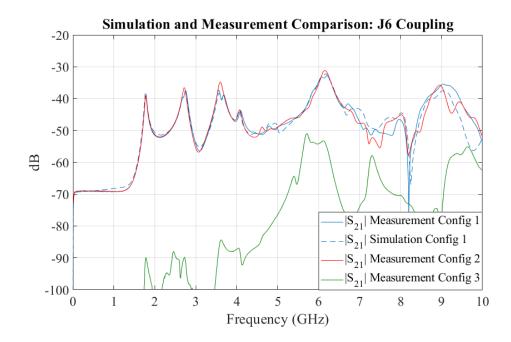

| 3.33. | Measured and simulated coupling to the stripline next to the power cavity                              | 70 |

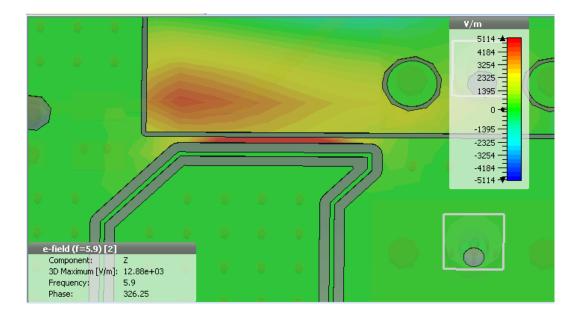

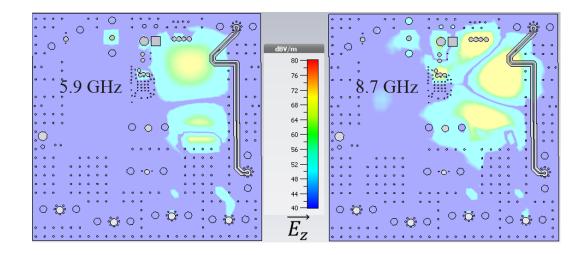

| 3.34. | Electric field at 5.9 GHz for Configuration 3 showing resonant GND segment                             | 71 |

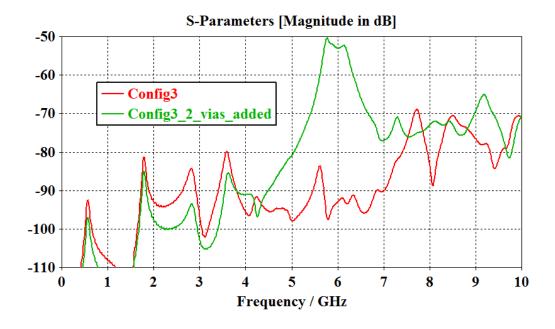

| 3.35. | Configuration 3 simulated coupling comparison for via modification                                     | 71 |

| 3.36. | Fields of PWR/GND cavity next to stripline on same layer                                               | 72 |

| 3.37. | Normal electric field of stripline at two instances in time                                            | 73 |

| 3.38. | Measured and simulated coupling to the stripline routed below an aperture in the power cavity          | 74 |

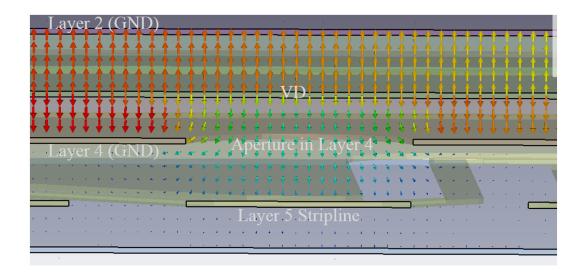

| 3.39. | Electric field coupling to the stripline through aperture.                                             | 74 |

| 3.40. | Electric field distributions in Layer 4-5 cavity at 5.9 GHz and 8.7 GHz for Configuration 3.           | 75 |

| 3.41. | Measured and simulated coupling to the stripline referenced to power net area fill.                                                                   | 76  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.42. | Stripline routed over clearance gap between power and GND area fills                                                                                  | 77  |

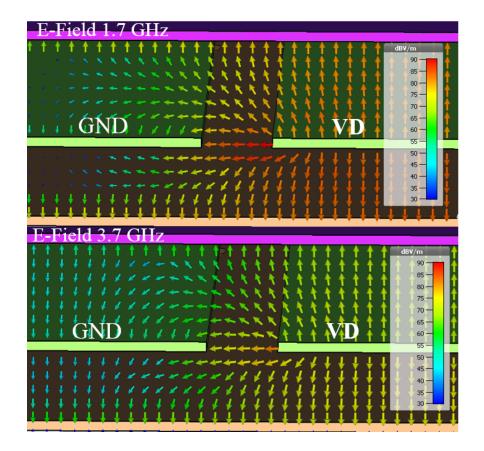

| 3.43. | Electric field cross-sections showing the stripline crossing the gap excite a slotline mode                                                           | 77  |

| 3.44. | Electric field cross-sections showing the stripline crossing the gap excite a slotline mode                                                           | 78  |

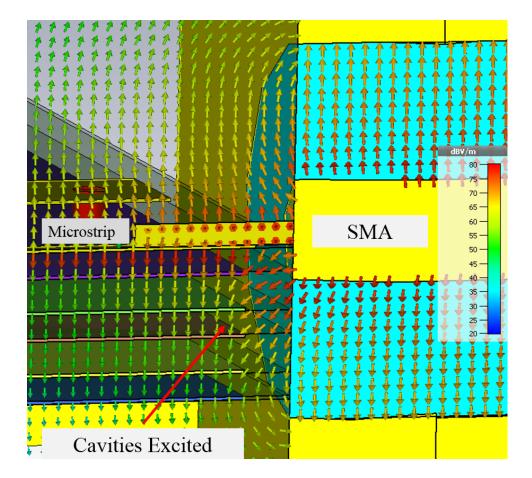

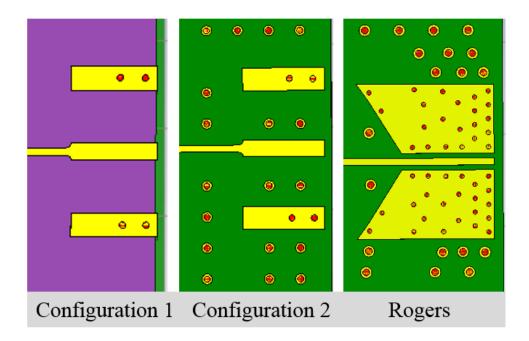

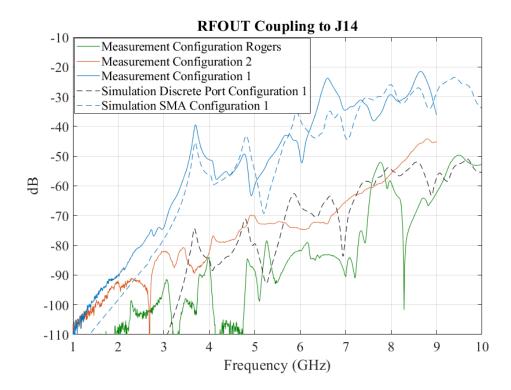

| 3.45. | Electric field of coaxial connector exciting PCB cavities                                                                                             | 80  |

| 3.46. | SMA end launch structure comparison for the different configurations                                                                                  | 81  |

| 3.47. | Measured and simulated coupling from RFOUT to via in PWR/GND cavity                                                                                   | 82  |

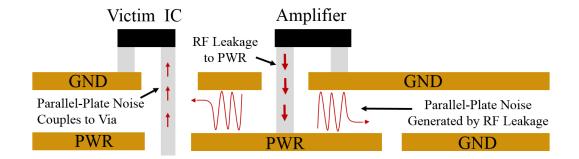

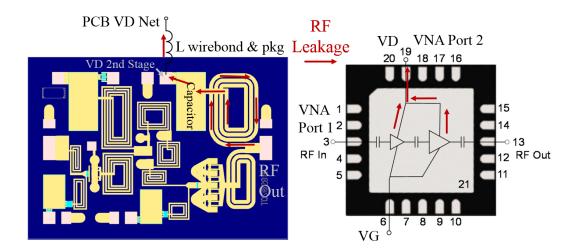

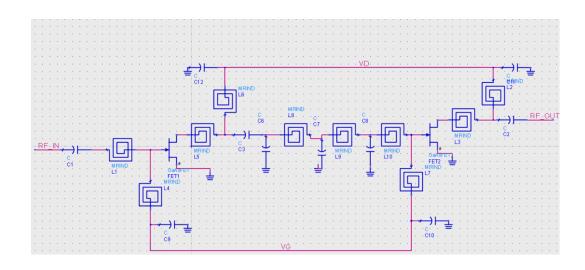

| 4.1.  | Simplified diagram of the noise coupling mechanism studied in this section                                                                            | 83  |

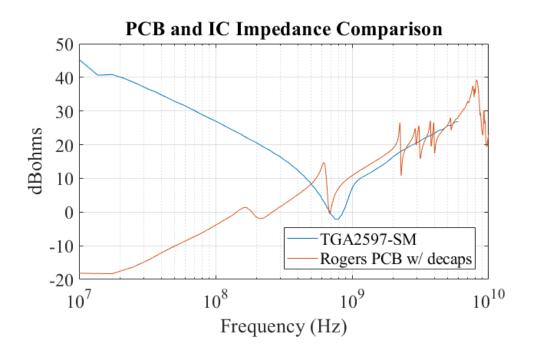

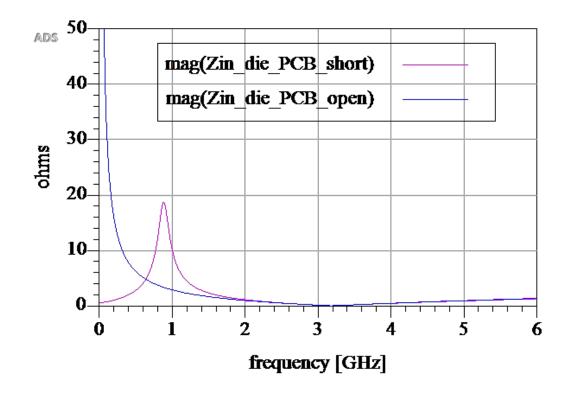

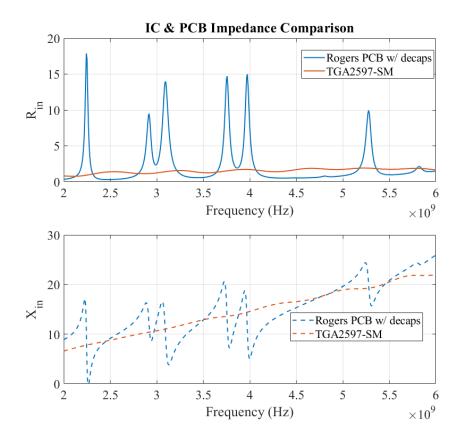

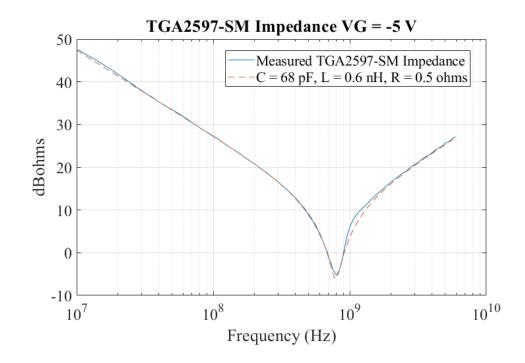

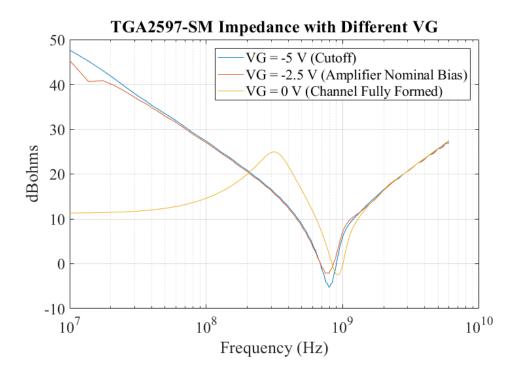

| 4.2.  | Comparison of input impedance of IC and PCB in log scale                                                                                              | 85  |

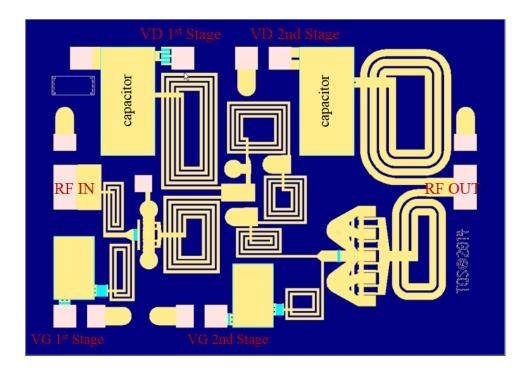

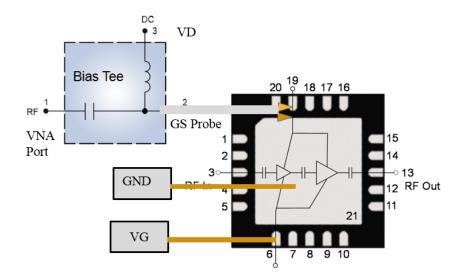

| 4.3.  | Simplified diagram showing the RF leakage to VD in the amplifier                                                                                      | 85  |

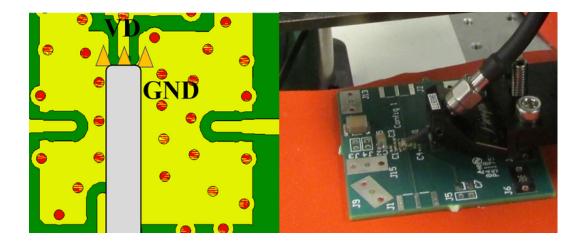

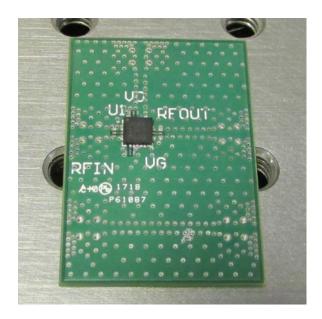

| 4.4.  | Impedance is measured where the IC's VD pin is located once the IC is installed.                                                                      | 86  |

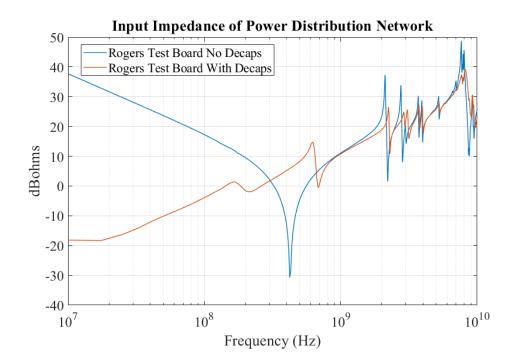

| 4.5.  | Input impedance looking into the PDN with and without decoupling capacitors.                                                                          | 87  |

| 4.6.  | Simplified equivalent circuit model of impedance seen by on-die devices                                                                               | 89  |

| 4.7.  | Comparison of simulated results of impedance seen by on-die capacitance                                                                               | 89  |

| 4.8.  | Input impedance comparison of different configurations where the IC is at different locations                                                         | 90  |

| 4.9.  | Input impedance for the Rogers test board in complex form                                                                                             | 92  |

| 4.10. | Comparison of the IC impedance and PCB impedance in complex form                                                                                      | 96  |

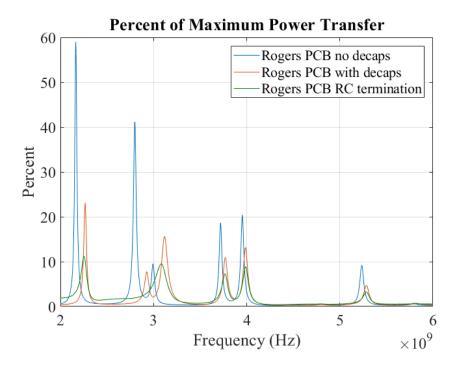

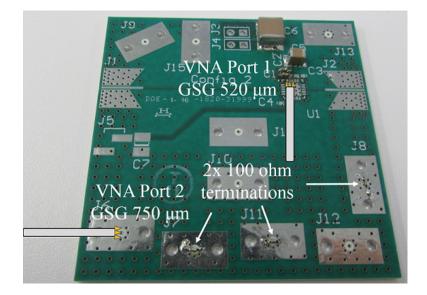

| 4.11. | Power transfer between IC and PCB PDN expressed as percentage of the maximum power transfer possible.                                                 | 97  |

| 4.12. | Measurement set-up for obtaining S-parameters between the IC location and victim interconnect with the measurement reference plane at the IC SMT pads | 98  |

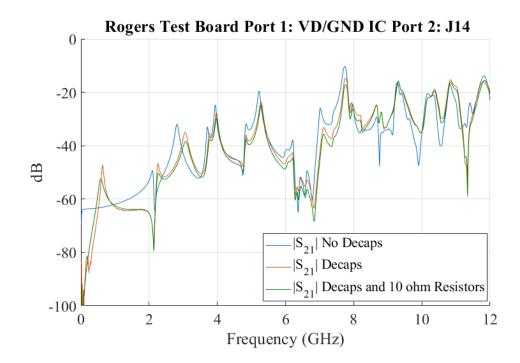

| 4.13. | Measured $ S_{21} $ comparison with and without passive components for port 1 excitation at IC PCB pads.                                              | 99  |

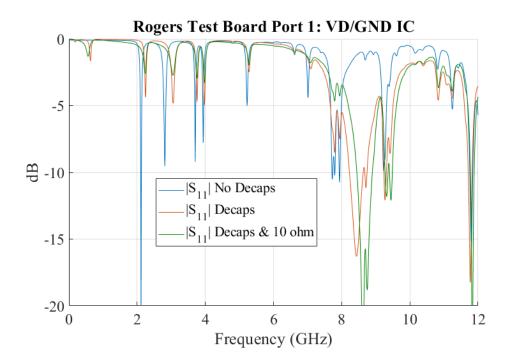

| 4.14. | Measured $ S_{11} $ comparison with and without passive components for port 1 excitation at IC PCB pads.                                              | 100 |

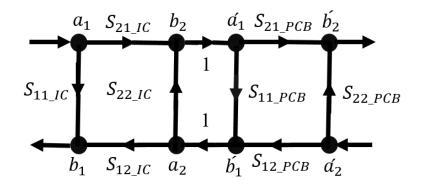

| 4.15. | Signal flow graph of two cascaded two-port networks                                                                                                   | 101 |

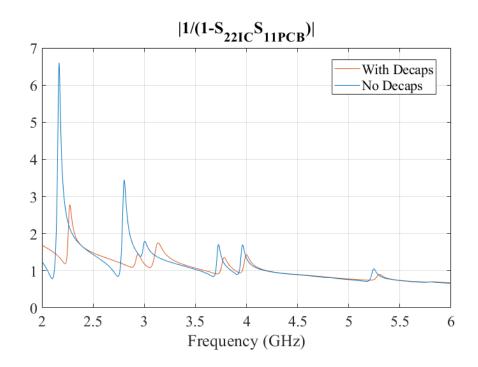

| 4.16. | Magnitude plot of the S-parameter terms that capture the power transfer 102                                                             |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------|

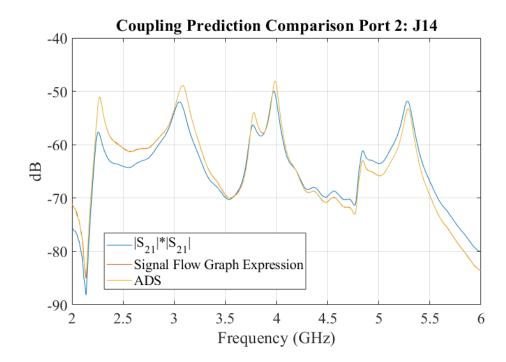

| 4.17. | Comparison of the signal flow graph method and ADS for the coupling prediction. 103                                                     |

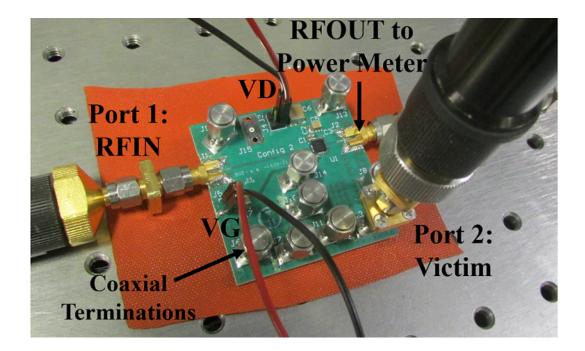

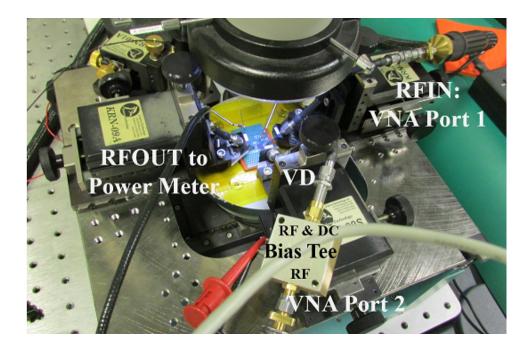

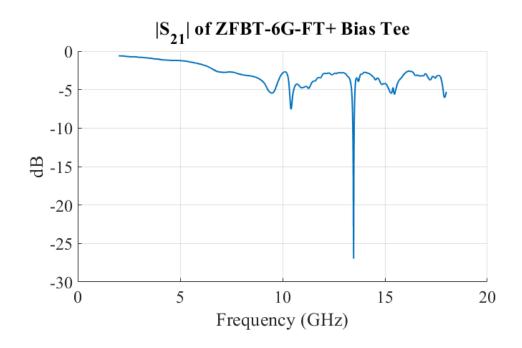

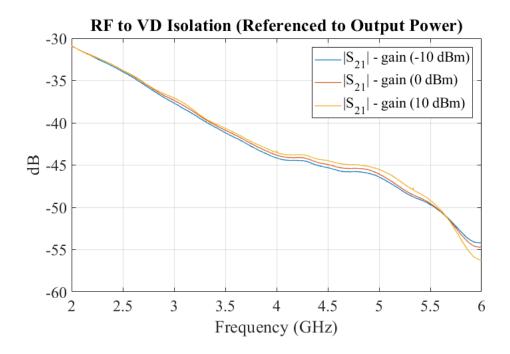

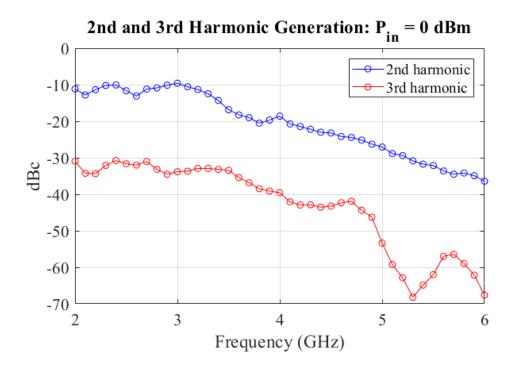

| 4.18. | Active coupling measurement set-up 104                                                                                                  |

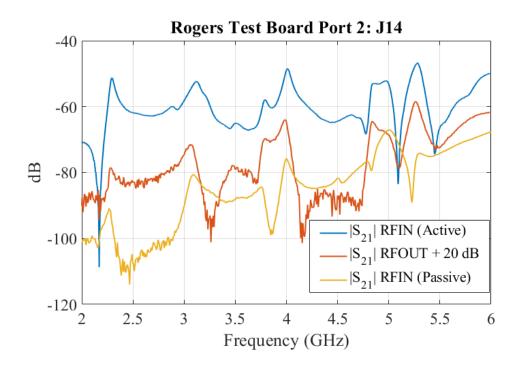

| 4.19. | J14 active coupling comparison with RFIN and RFOUT coupling 105                                                                         |

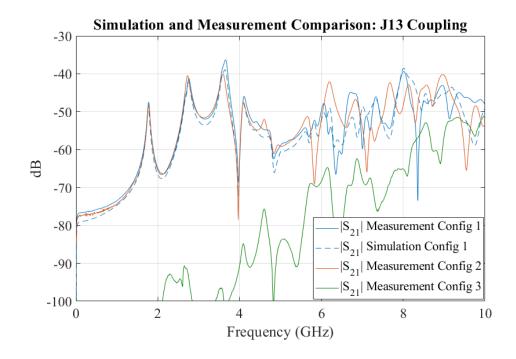

| 4.20. | J13 active coupling comparison with RFIN and RFOUT coupling 105                                                                         |

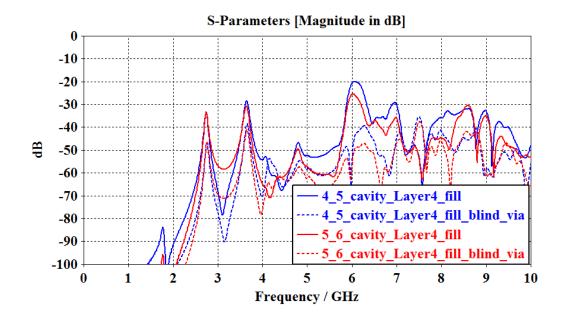

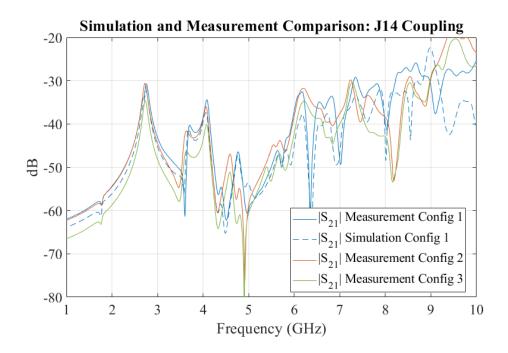

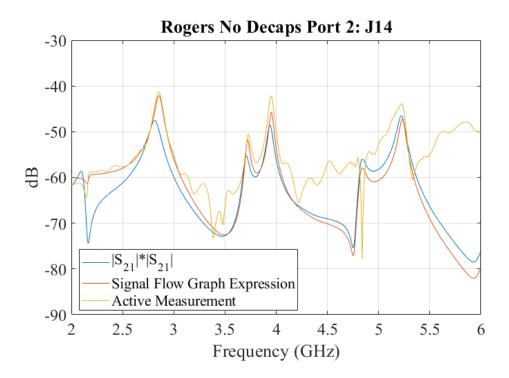

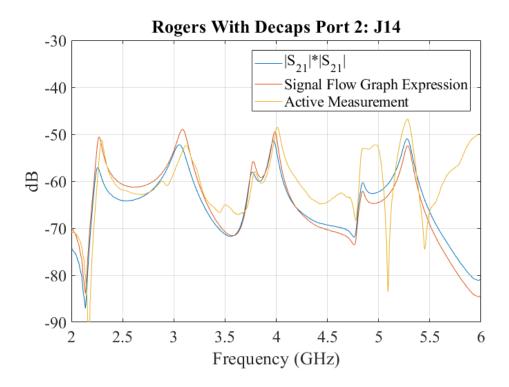

| 4.21. | J14 active coupling measurement with no capacitors compared with prediction 106                                                         |

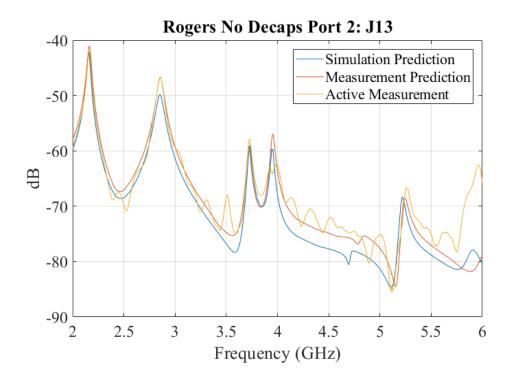

| 4.22. | J14 active coupling measurement with capacitors compared with prediction 107                                                            |

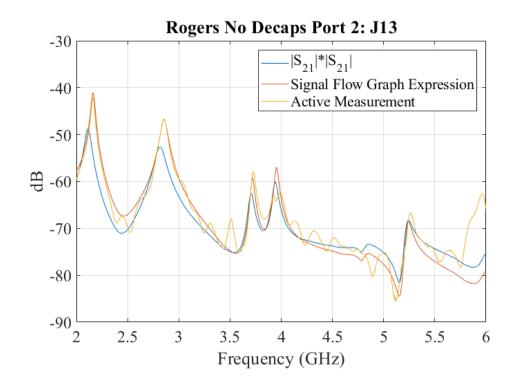

| 4.23. | J13 active coupling measurement with no capacitors compared with prediction. 107                                                        |

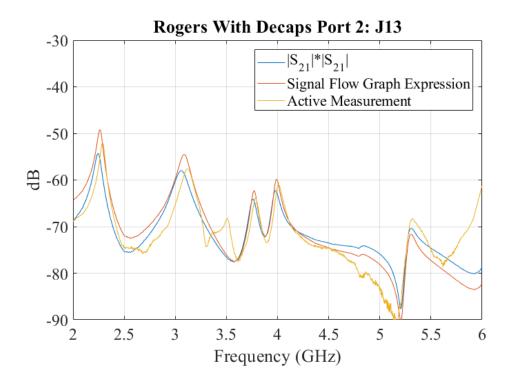

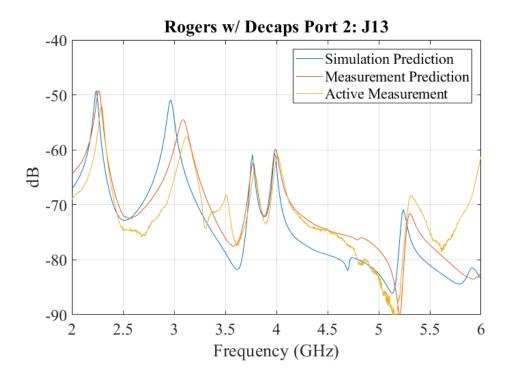

| 4.24. | J13 active coupling measurement with capacitors compared with prediction 108                                                            |

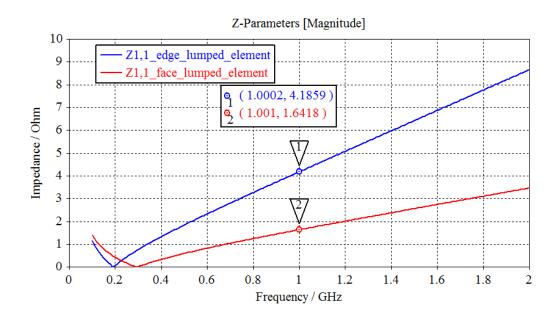

| 4.25. | Impedance comparison of face lumped element and discrete wire lumped element.110                                                        |

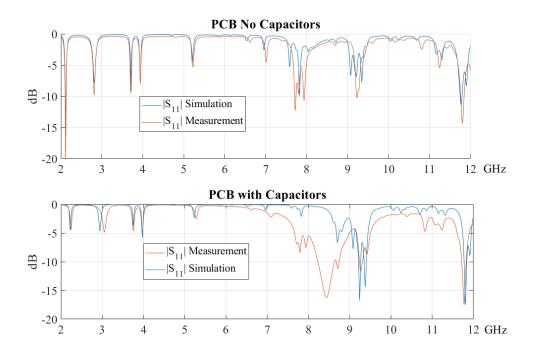

| 4.26. | $ S_{11} $ comparison of measurement and simulation results for Rogers test PCB 111                                                     |

| 4.27. | Comparison between measurement and coupling prediction from simulation results for PCB with no capacitors                               |

| 4.28. | Comparison between measurement and coupling prediction from simulation results for PCB with capacitors                                  |

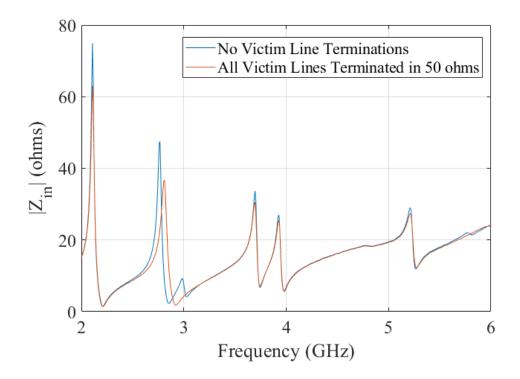

| 4.29. | Change in the PCB PDN input impedance when all victim interconnects are terminated in 50 ohms                                           |

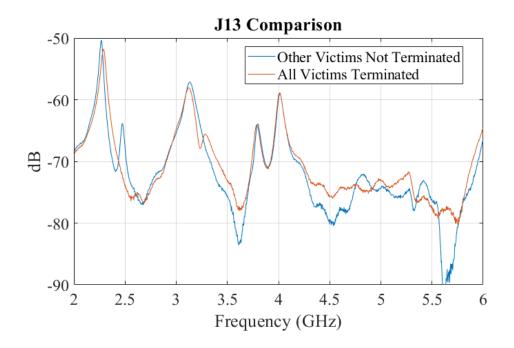

| 4.30. | Active coupling to J13 measurement comparison with and without termination on other victim interconnects                                |

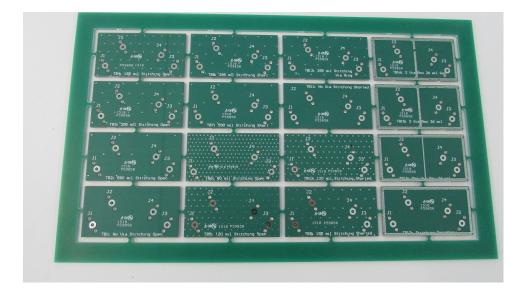

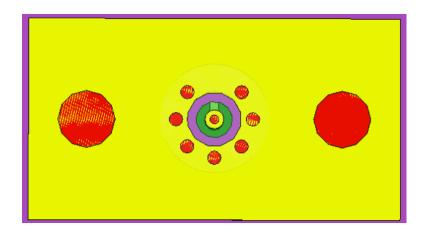

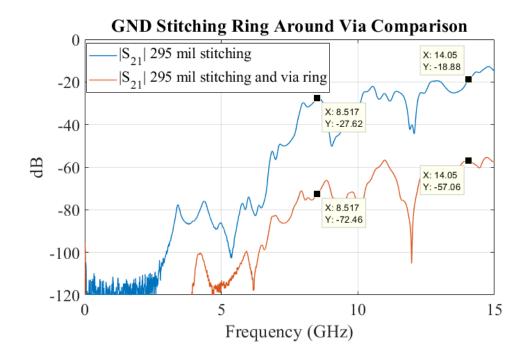

| 5.1.  | Picture of via stitching test vehicle which includes test boards for measuring isolation of global stitching, via fences, and via rings |

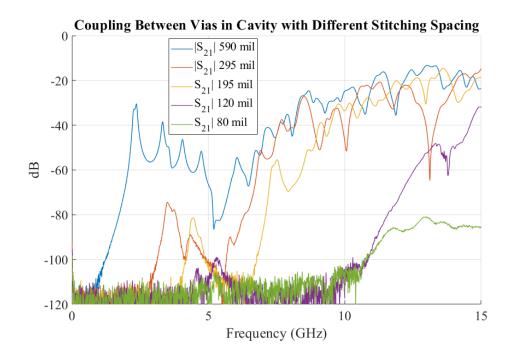

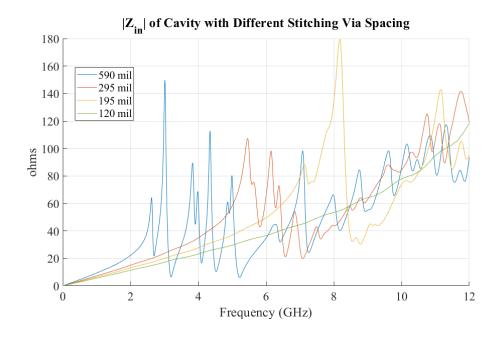

| 5.2.  | Comparison of the coupling between two vias in a cavity with different stitching via spacing                                            |

| 5.3.  | Comparison of the input impedance of a cavity with different stitching via spacing                                                      |

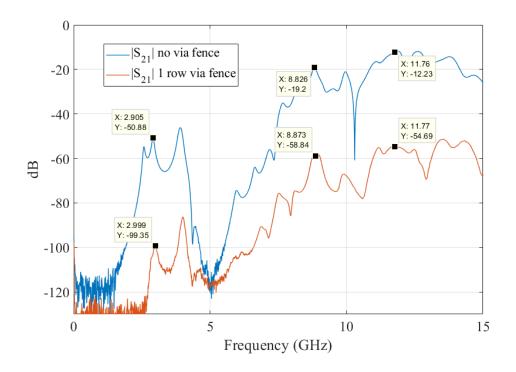

| 5.4.  | Comparison of the coupling between vias with and without a via fence 125                                                                |

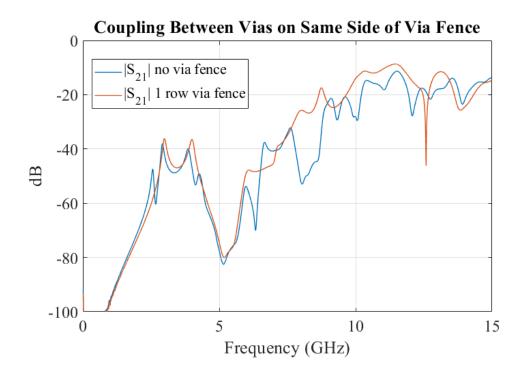

| 5.5.  | Comparison of the coupling between two vias on the same side of the via fence with and without a via fence                              |

| 5.6.  | GND vias added around signal via to minimize coupling to the parallel plates 126                                                        |

| 5.7.  | Coupling comparison with and without ring of GND vias around the signal via. 127                                                        |

## **1. INTRODUCTION**

#### **1.1. MIXED-SIGNAL DESIGN CONSIDERATIONS**

Much of the PCB related research is conducted for high-speed digital designs such as server motherboards. Signal integrity considerations, making sure the ones and zeros can be interpreted at the receiver, are the most important for these designs. Due to the routing density of most high-speed digital products, transmission line crosstalk is unavoidable. Although transmission line crosstalk can be pervasive, it is well understood and easy to identify. It drops off predictably with increasing distance. This type of coupling is sometimes referred to as proximity coupling because it is dependent on how close the two transmission line structures are to each other. Analytical equations are available in references such as [1]. However, in signal integrity applications, coupling or crosstalk between nets only becomes important if it is large enough to increase the bit error rate (BER). The coupling has to be fairly high to change the logic level of the signal. Although the susceptibility to noise can increase with lower voltage levels and multi-level signaling such as PAM4.

Mixed-signal designs contain both digital and analog functionalities. For a low level analog signal, a small amount of coupling from a digital signal may completely dominate the desired analog signal. In addition, a design may contain ICs that are sensitive to noise such as a PLL or VCO. As a result, much lower coupling levels are allowable, i.e. greater isolation is needed. Most designers are aware of standard transmission line coupling and can avoid it by placing potential aggressor signals on a different layer or far away from a sensitive analog signal. Furthermore, often in aerospace or test equipment applications, where less of a cost performance trade-off exists, routing density can be decreased with the use of additional PCB layers. In addition, above the board shields can often be afforded which reduce the coupling between interconnects on the top and bottom layers if properly implemented. For these reasons, it is unlikely that standard transmission line coupling will be an unforeseen issue for these types of high-performance designs.

A common practice in RF PCB design is to place GND area fills to fill all open areas after routing. This practice results in the formation of many parallel-plate cavities throughout the design. Parallel-plate cavities are also formed by power net area fills/planes and neighboring GND fills/planes. It is these parallel-plate cavities that can provide an efficient, but subtle, coupling mechanism between signals in a PCB, even those not in close proximity. A pair of parallel plates is able to propagate a TEM mode with no intrinsic cutoff frequency. Consequently, this coupling mechanism is not associated with higher order waveguide modes that are cutoff before a certain frequency.

Of course, cavities formed by GND area fills should be well connected using vias to prevent the formation of electrically large cavities that can propagate fields. But, if only plated through hole (PTH) vias are used it can be difficult to connect the GND areas adequately due to routing constraints. Further, it is not well defined what the largest allowable spacing between via connections should be to achieve a certain amount of isolation. Parallel-plate cavities formed between PWR and GND obviously cannot be conductively connected so field propagation is unavoidable. The important consideration in this case is to contain the fields to prevent them from coupling through the rest of the design. The parallel-plate noise problem has been occurring for a long time in designs and continues to be an issue. For example, a RF engineer, James Lampen, wrote a poem in the 1990s titled "Ode to GREENTAPE" which a portion of states "The ground design you generate / Can really, truly, resonate. / Scattering a few vias around/ Should, it seems, suffice for ground" [2]. The author of the poem likely had an unfortunate experience of a LTCC design being ruined due to resonances in parallel-plate cavities. The following subsections will provide the theoretical background necessary for understanding the problem.

Figure 1.1. A rectangular parallel-plate waveguide.

#### **1.2. PARALLEL-PLATE WAVEGUIDE**

Transmission lines are used to guide electromagnetic waves. Transmission lines support a TEM mode where the field distribution is uniform along the cross section with no field components in the direction of the propagation. The transverse fields then satisfy Laplace's equation for electrostatics which means the transverse fields are the same as the static fields [3]. This property allows for well-defined voltages and currents. For instance, in electrostatics the potential on a perfect conductor is the same everywhere so calculating the voltage from the electric field is path independent [3]. In contrast, for higher-order modes, such as the  $TE_{01}$  mode of a rectangular waveguide, the electric field varies across the geometry resulting in different voltages depending on the integration path for the electric field. In this case, the voltage is not well-defined. Another consequence of the potential on a perfect conductor being the same everywhere is that two conductors are required for a TEM mode.

A parallel-plate waveguide, shown in Figure 1.1, consists of two conductors so it is capable of transmitting a TEM mode. A parallel-plate waveguide is also capable of supporting higher-order TM and TE modes. The TEM mode solution can be obtained by solving the Helmholtz wave equation or using Laplace's equation. Because it is also important to have knowledge of at what frequencies the higher-order modes can start to occur, the Helmholtz wave equation will be solved. The following derivation follows from [4]. For a TM solution, there is no magnetic field component in the direction of propagation and a non-zero electric field in the direction of propagation. The direction of propagation is assumed to be in the y-direction. If the width of the parallel plate is much larger than the separation then the x-variation, d/dx, can be approximated as zero. As a result, the problem is reduced to a 2-D problem which can be solved with the 2-D Helmholtz wave equation. The wave equation is solved for  $E_y$  and the other field components are obtained by substituting  $E_y$  into the Maxwell's equations:

$$\nabla^2 E_y(x, y, z) + k^2 E_y(x, y, z) = 0$$

(1.1)

$$E_{y} = 0 \ at \ z = 0 \ \& \ z = d \ (PEC) \tag{1.2}$$

Separation of variables is used to solve the homogeneous differential equation. Traveling wave solutions are selected for the y-direction and standing-wave solutions are selected for the z-direction resulting in (1.3).

$$E_{y}(x, y, z) = [A\sin(k_{c}z) + B\cos(k_{c}z)][Cexp^{-j\beta y} + Dexp^{+j\beta y}]$$

(1.3)

In (1.3), A, B, C, and D are unknown constants. Applying the PEC boundary conditions in (1.2) results in B = 0 and  $k_c d = n\pi$  or  $k_c = n\pi/d$ . There are only outgoing waves which results in D = 0. This results in (1.4), where the constants A and C have been combined.

$$E_y(x, y, z) = A_n \sin(\frac{n\pi z}{d}) \exp^{-j\beta y}$$

(1.4)

The remaining field components are obtain by substituting (1.4) back into the Maxwell's equations.

$$E_z = \frac{-j\beta}{k_c} A_n \cos(\frac{n\pi z}{d}) \exp^{-j\beta y}$$

(1.5)

$$H_x = \frac{j\omega\varepsilon}{k_c} A_n \cos(\frac{n\pi z}{d}) \exp^{-j\beta y}$$

(1.6)

$$E_x = H_z = 0 \tag{1.7}$$

The dispersion relation is (1.8) and the cutoff frequency for the higher order modes can be derived from it and is given in (1.9).

$$k_c = \sqrt{k^2 - \beta^2} \tag{1.8}$$

$$f_c = \frac{k_c}{2\pi\sqrt{\mu\varepsilon}} = \frac{nv_p}{2d} \tag{1.9}$$

Equation (1.9) shows that electrical length of the separation between parallel plates must be greater than  $\lambda/2$  for higher order mode propagation. The TEM mode, n = 0, does not have cutoff frequency and only has  $E_z$  and  $H_x$  components. For the case with a dielectric thickness of 10 mils (254  $\mu m$ ) and  $\varepsilon_r = 4$  the cutoff frequency of the first higher-order mode is 295 GHz. As a result, the higher-order modes are not of concern for typical PCB geometries and frequency ranges.

An important result for PCB geometries can be derived by considering a pair of infinite circular plates with a line excitation in the center. This configuration is referred to as a radial waveguide. Obviously no actual PCB geometry has infinite parallel plates, however making this assumption allows for closed-form analytical solutions in the absence of scattering to be obtained. In addition, line excitations are also a mathematical construct, however in PCB geometries the most common excitation is a via that passes through the parallel-plate pair. The size of the via typically much smaller than the parallel plates so the use of a line excitation is reasonable. These closed-form analytical solutions help elucidate the physics of the initial excitation of the parallel plates by a via without becoming too cumbersome. A radial waveguide can support  $TM_z$  and  $TE_z$  modes. The  $TM_z$  modes are of interest in PCB geometries because a TEM mode is possible. The fields of the TMz modes are derived in [5] for the homogeneous differential equation. Equations (1.10-12) are the

Figure 1.2. Cross-section of a via passing through a parallel-plate pair.

case when n = 0, corresponding to the  $TM_{z0}$  mode which is TEM.

$$E_z = -j \frac{\beta_\rho^2 A}{\omega \mu \varepsilon} H_0^{(2)}(\beta_\rho \rho)$$

(1.10)

$$H_{\phi} = -\frac{\beta_{\rho}A}{\mu} H_0^{(2)'}(\beta_{\rho}\rho)$$

(1.11)

$$E_{\phi} = E_{\rho} = H_{\rho} \tag{1.12}$$

With respect to the parallel-plate surfaces, there is a tangential magnetic field and a normal electric field while the propagation is in the radial direction. Consequently, there are no field components in the direction of propagation and  $\vec{E}$  and  $\vec{H}$  are perpendicular to each other, illustrating the TEM property of the fields. The higher-order modes are cutoff and the wave impedance for the cutoff modes is capacitive [5].

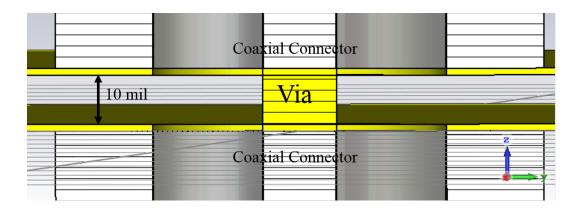

For comparison with the analytical equations, a simulation model is created in CST Microwave Studio of a pair of parallel plates with a via passing through the plates as shown in Figure 1.2. The time-domain solver is used for the simulation. There are coaxial connectors on the top and bottom with waveguide ports that connect to the via. The dielectric between the two plates is lossless. The model uses dimensions representative of typical PCB geometries with a dielectric thickness of 10 mils, a via diameter of 15 mils, and an

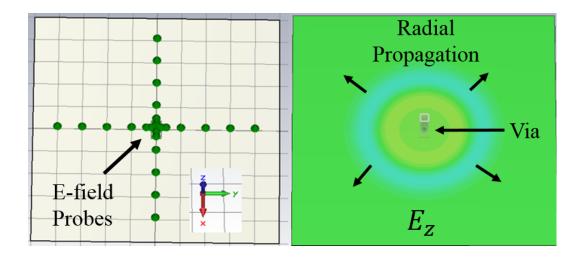

Figure 1.3. E-field probe locations and normal E-field in cavity.

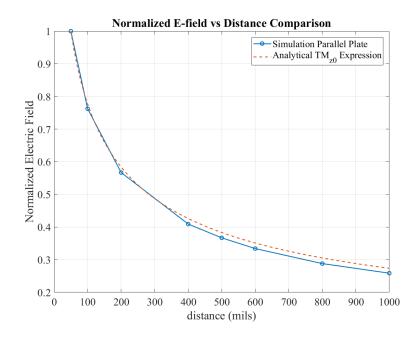

anti-pad diameter of 35 mils. Perfectly Matched Layer (PML) boundary conditions, which absorb the wave incident on the boundary, are used to enforce no scattering (infinite length plates). PML boundary conditions are called "Open" in CST. E-field probes are defined in both the positive and negative x-directions and y-directions as shown in Figure 1.3. The via passing through the parallel plates results in the excitation of a radial wave as seen in the left side of Figure 1.3. As expected from the analytical expressions, the E-field values from the simulation were the same at equidistant points in different directions, indication of the radial propagation. The E-field probe data from the simulation is normalized to one using the E-field value at 50 mils. The simulation data is plotted with the analytical solution to  $E_z$ , (1.10), which is also normalized to the value at 50 mils. The two curves agree well as seen in Figure 1.4. The difference could be attributed to not accounting for the finite via radius, the anti-pad, and if the cutoff higher-order modes are not completely decayed at 50 mils. The field strength drops off rapidly initially, but decays much slower at farther distances.

Figure 1.4. Comparison of  $E_z$  as a function of distance for simulation and analytical solution.

## **1.3. PARALLEL-PLATE CAVITY RESONATOR**

Assuming infinite parallel plates is important for understanding how the fields of a via can couple to a parallel-plate cavity. By invoking reciprocity, the fields in the parallel-plate cavity can then couple to other vias. However, the scattering of the fields in the parallel-plate cavity needs to be accounted for to determine the field distributions that can be present in the cavity. The waves will scatter when they encounter discontinuities such as apertures in the cavity and the open edges of the cavity. In the frequency domain, the incident and reflected waves can combine constructively and destructively resulting in the formation of standing-wave patterns. The standing-wave patterns are dependent on the boundary conditions, material properties, physical dimensions, and where the excitation occurs. For instance, the dielectric constant of a material will determine the speed that waves propagate through the medium. The speed and physical dimensions will determine

the electrical length of a structure, i.e. how many wavelengths long a structure is. At resonant frequencies, where the waves add constructively, the magnitude of the fields becomes very large which can result in greater coupling.

The cavity model, which was originally developed for analysis of patch antennas, can be used to analyze the standing-wave behavior [6]. More recently the cavity model has been used for the analysis of the power distribution network (PDN) of PCBs [7]. Although the cavities formed in PCB geometries are not completely uniform due to cutouts for anti-pads and vias, discussion of the cavity model can still provide insight to the problem. Complex geometries have been successfully studied with the cavity model by using segmentation techniques [8]. For PCB geometries, the electrical length of the thickness of a cavity is usually much less than a wavelength. As a result, the field variation in the z-direction (along the thickness) can be approximated as zero and the problem simplifies to a 2D problem. The propagating wave solutions, Equations (1.4-1.9), derived earlier in this section were obtained by assuming infinite length plates where scattering was ignored, however for this derivation the standing-wave modes resulting from scattering at the boundary conditions are desired. The boundary conditions on the periphery of the cavity are approximated with perfect magnetic conductor (PMC) boundaries. The 2D Helmholtz wave equation for  $E_z$ can be solved and the other field components are obtained by substituting  $E_z$  back into the Maxwell's Equations.

$$\nabla^2 E_z(x, y, z) + k^2 E_z(x, y, z) = 0$$

(1.13)

$$H_x = 0 at y = 0 \& y = b (PMC)$$

(1.14)

$$H_{y} = 0 \ at \ x = 0 \ \& \ x = a \ (PMC) \tag{1.15}$$

The wave equation is solved through separation of variables. Standing wave-solutions are selected for both the x-direction and the y-direction. The boundary conditions are on  $\vec{H}$  which is obtained from  $E_z$  using Faraday's Law.

$$E_z(x, y) = [A\cos(k_x x) + B\sin(k_x x)][C\cos(k_y y) + D\sin(k_y y)]$$

(1.16)

$$H_x(x,y) = \frac{j}{\omega\mu} [A\cos(k_x x) + B\sin(k_x x)] [-Ck_y\cos(k_y y) + Dk_y\sin(k_y y)]$$

(1.17)

$$H_{y}(x,y) = \frac{-j}{\omega\mu} [-Ak_{x}\cos(k_{x}x) + Bk_{x}\sin(k_{x}x)][C\cos(k_{y}y) + D\sin(k_{y}y)]$$

(1.18)

Applying the PMC boundary conditions at y = 0 and y = b (1.14) results in D = 0 and  $k_y = n\pi/b$ , respectively. Applying the PMC boundary conditions at x = 0 and x = a (1.15) results in B = 0 and  $k_x = m\pi/a$  respectively. The remaining constants A and C can be consolidated into a single constant  $A_{mn}$ . The resulting fields are given in (1.19-1.21).

$$E_z(x, y) = A_{mn} \cos(\frac{m\pi x}{a}) \cos(\frac{n\pi y}{b})$$

(1.19)

$$H_{y}(x,y) = \frac{jA_{mn}}{\omega\mu} \frac{m\pi}{a} \sin(\frac{m\pi x}{a}) \cos(\frac{n\pi y}{b})$$

(1.20)

$$H_x(x,y) = \frac{-jA_{mn}}{\omega\mu} \frac{n\pi}{b} \cos(\frac{m\pi x}{a}) \sin(\frac{n\pi y}{b})$$

(1.21)

The dispersion relation is (1.22) and can be rearranged to obtain an expression for the resonant frequencies of the cavities (1.23).

$$k^{2} = k_{x}^{2} + k_{y}^{2} = \omega^{2} \mu \varepsilon = \left(\frac{m\pi}{a}\right)^{2} + \left(\frac{n\pi}{b}\right)^{2}$$

(1.22)

$$f_{mn} = \frac{1}{2\pi\sqrt{\mu\varepsilon}}\sqrt{(\frac{m\pi}{a})^2 + (\frac{n\pi}{b})^2}$$

(1.23)

Equation (1.23) for the resonant frequencies can be used to determine when the first resonance occurs based on the geometry and material properties. If the highest frequency of interest in a design is greater than the first resonant frequency of the cavity, the resonances of the cavity need to be considered. The derivation of the cavity model contained here solves the homogeneous differential equation, but does not solve the inhomogeneous differential equation with the excitation. A Green's function of the 2-D Helmholtz equation can be used to solve the inhomogeneous differential equation. In [7], the inhomogeneous differential equations is solved to obtain the impedance matrix where finite length ports can be placed at different locations. An important result is that the impedance looking into the cavity varies with position, i.e. what modes are excited and how strongly they are excited is position dependent. Conductor and dielectric loss is accounted for with a complex propagation constant that uses the standard low-loss approximation.

The parallel-plate PWR/GND cavity has the same structure as a microstrip-patch antenna which is why the cavity model works well for its analysis. It follows that noise coupled to the parallel-plate cavity can excite resonances and result in radiation [9]. This radiation is primarily an EMC radiated emissions issue, i.e., causes the product to exceed the field strength limit for radiated emissions in EMC compliance testing. But the radiation could cause an inter-system interference issue as well. This radiation is typically mitigated by stitching the sides of PCBs with vias and edge plating [10]. Because this work is concerned with coupling mechanisms within a PCB, the radiation from the PCB edges will not be discussed further in this work.

An important concept with dealing with resonant structures is the quality factor or Q. The Q is a measure of the loss of a resonant circuit and is obtained by dividing the stored energy with the power loss. A high Q corresponds to low loss which results in very high field strength at resonance for a cavity resonator. For unintended resonances, loss is desirable to dampen the resonance or lower the Q. Analytical expressions for the Q of a parallel-plate cavity can be derived from the fields obtained using the cavity model. The

conductor loss is obtained by calculating the power dissipated in the finite resistance of the top and bottom plates where the surface current density is obtained from  $\vec{J}_s = \hat{n} \times \vec{H}$ , by approximating the conductor as a PEC. The dielectric loss is obtained by performing the volume integral of  $\frac{1}{2}\omega\varepsilon''|\vec{E}|^2$  over the structure. The stored magnetic and electric energy are obtained by performing the volume integral of  $\frac{1}{4}\omega\varepsilon''|\vec{E}|^2$  over the structure. The stored magnetic and electric energy are obtained by performing the volume integral of  $\frac{1}{4}\mu|\vec{H}|^2$  and  $\frac{1}{4}\varepsilon|\vec{E}|^2$  over the structure. From the stored energy and the loss of the cavity, equations for the *Q* can be obtained (1.24-26).

$$Q_{conductor} = \frac{d}{\delta_s} \tag{1.24}$$

$$Q_{dielectric} = \frac{1}{\tan \delta} \tag{1.25}$$

$$\frac{1}{Q_{total}} = \frac{1}{Q_{conductor}} + \frac{1}{Q_{dielectric}}$$

(1.26)

The PMC boundary conditions used in the cavity model do not account for the radiation loss which also impacts the overall Q. However, previous research has shown in general for PCB geometries the radiation loss is much less than conductor and dielectric loss [11]. From (1.24) and (1.25) it is clear that two design parameters impact the Q: the tan  $\delta$  of the dielectric material and the thickness, d, of the dielectric material. The skin depth,  $\delta_s$ , of the metal is essentially fixed as only copper is used in standard PCB fabrication. The dielectric thickness is dependent on the number of layers, the desired finish board thickness, and the standard thicknesses of a dielectric material available from the manufacturer. The designer in some cases may have some control in selecting a dielectric thickness between two layers. More often, the dielectric material is a key design parameter. For applications where signal attenuation needs to be minimized, such as in RF designs or high-data rate digital designs, a lower-loss dielectric material is used instead of low-cost FR-4. Low-loss dielectric substrates such as Rogers RO4000 series or Megtron 6 have a much lower tan  $\delta$  resulting in an increase in Q. To provide an illustration, the simulated coupling in linear scale between two vias for a 2"x 2" cavity with FR-4 dielectric (tan  $\delta = 0.025$ ), and a 2"x 2"

Figure 1.5. Comparison of simulated coupling between vias in a cavity for lossy (FR-4) and low-loss dielectric material.

cavity with a tan  $\delta$  of 0.003 is shown in Figure 1.5. The coupling magnitude of the low-loss dielectric cavity is 2-3 times greater at resonant frequencies than the FR-4 cavity coupling magnitude. Therefore, the parallel-plate coupling mechanisms are much more severe in PCBs that use low-loss dielectric materials. In addition, in [12] it was shown that smaller sized cavities resonate stronger. The low-loss materials used in some IC packages can result in even larger Q-factors. For instance, a glass interposer used for 2.5D IC integration resulted in very strong coupling at resonant frequencies due to the very low loss of the glass material [13].

## **1.4. PARALLEL-PLATE NOISE IN THE LITERATURE**

Sometimes, this form of coupling is called parasitic coupling to distinguish it from proximity coupling as it is the result of electromagnetic wave propagation on waveguide structures that were not intentionally designed to do so [14]. This type of coupling related to the PWR/GND structures is often referred to in the literature as simultaneous switching

noise. Simultaneous switching noise is referencing when multiple transistors are switching simultaneously which injects multiple noise sources into a PWR/GND structure. Another related term is ground bounce which is referencing the fact that due to the field distributions that can occur in a cavity there can be locations where the voltage  $(E_z)$  is no longer zero as assumed in circuit theory analysis. Still, these names do not entirely elucidate the physics of how noise is coupled to the cavity and how the fields in the cavity couple to traces or vias. Further, some of the papers discussing this topic do not explicitly explain the physics of these phenomenon. There are still papers that explicitly reference the physics which will be referenced throughout. A review of the relevant literature is included throughout Section 2.

Overall, there is very little literature on obtaining high isolation in PCB designs. Searching the IEEE database for "noise isolation" primarily yields a paper discussing the use of via fences around striplines and microstrips for isolation in RF multi-chip packages [15]. This practice is primarily aimed at minimizing transmission line crosstalk, but also helps suppress parallel-plate cavity noise. Despite the lack of literature for achieving high levels of isolation, there is some literature for how to suppress parallel-plate cavity noise which is often critical for achieving high isolation. However, a majority of the recent literature in this area discusses using Electromagnetic Bandgap (EBG) structures for suppressing parallelplate noise such as [16]. For EBG structures, one of the planes is patterned with narrowly connected patches in such a way to suppress the propagating waves in the parallel-plate cavity which creates a stopband for a range of frequencies. Utilizing more complex EBG patterns can yield stopband bandwidths around 4 GHz and stopband attenuation of about 40 dB [17]. Still, the EBG structures have not been used much in industry for several reasons. For example, the patterning essentially prevents the planes from being used as a reference plane for transmission lines because of the gaps. Consequently, the use of EBGs will likely necessitate an increase in the layer count of a PCB. In addition, the narrow connections may have IR-drop or thermal consequences in high-power applications such as the power net area fill for a power amplifier. Another reason for the lack of adoption is that in most designs the parallel-plate cavity noise is created by switching digital circuits which is broadband noise while the EBG bandwidth is finite. Despite the implementation issues, EBGs may be a potential solution for achieving higher isolation in some applications. There are many topologies and permutations of EBGs which has resulted in numerous publications, dominating the more recent literature on parallel-plate noise. Placement of capacitors is another mitigation strategy that has been studied and suggested in the past for dampening the resonances [18]. The mounting inductance of SMT capacitors typically limits their efficacy at higher frequencies. The effect of capacitors is discussed extensively in Section 4.

#### **1.5. OVERVIEW OF THE REMAINING SECTIONS**

Understanding the noise coupling mechanisms related to the parallel-plate cavities is often critical for obtaining high isolation in RF & mixed signal PCB and package designs. Noise coupling in complex PCB designs can be better understood by breaking up the overall coupling mechanism into smaller portions. For example, a via can couple to a cavity, and then the first cavity can couple to another cavity where a via in that second cavity can be coupled to. This work will first discuss basic coupling mechanisms in Section 2 and then will analyze more complex test vehicles in Section 3. The focus will be on qualitatively understanding the physics underlying the coupling mechanisms. This knowledge can then be exploited in the full-wave EM simulation tools for proper identification and mitigation of this noise coupling mechanism. Section 4 will analyze how the active and passive components influence the coupling and how the coupling can be predicted in the final PCB assembly. Section 5 will provide design recommendations for minimizing the parallel-plate noise in mixed-signal designs.

### 2. BASIC PARALLEL-PLATE COUPLING MECHANSIMS

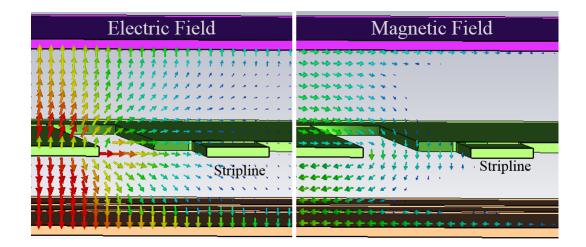

## 2.1. ELECTRIC FIELD AND MAGNETIC FIELD COUPLING

It is important to develop a fundamental understanding of electric field coupling and magnetic field coupling in order to diagnose coupling mechanisms in PCB geometries. The Maxwell equations are linear if the constitutive parameters,  $\mu$  and  $\epsilon$ , are assumed to be linear. For linear systems, superposition applies which allows for the coupling to be analyzed in the absence of other fields. The coupled fields can then be added to the original fields to obtain the final field distribution. Another important principle in the analysis of coupling mechanisms in PCB geometries is that there is typically no field penetration through conductors. At the frequencies of interest, the skin depth of copper is much less than the thickness of the copper layer in a PCB thus there is negligible field penetration through conductors. For example, at 100 MHz the skin depth of copper is about 0.25 mil As a result, a conductor will have two distinct surfaces with two distinct surface currents. To simplify analytical analysis, good conductors such as copper are modeled as Perfect Electrical Conductors (PECs) at high frequencies. For a PEC, free electrical charges are contained in an infinitesimally thin layer on the surface of the conductor.

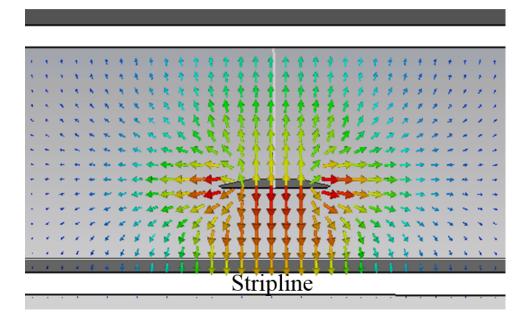

Electric field coupling is derived from the Ampere-Maxwell law where a changing electric field or a conduction current induces a circulating magnetic field. For instance, consider the case where a changing electric field is applied to the middle of a stripline as shown in Figure 2.1. The changing electric field produces a circulating magnetic field where the magnetic field is in different directions on each side of the electric field. If the conductor is approximated as a PEC, the  $\vec{J}_s = \hat{n} \times \vec{H}$  boundary condition can be used find the current density which shows that the current density is traveling in opposite directions from the changing electric field as seen in Figure 2.2. The electric field is in the same direction

Figure 2.1. Electric field source coupling to stripline.

on both sides while the magnetic field is in opposite directions. Therefore, by the Poynting vector energy is flowing in opposite directions. As a result, two propagating TEM waves travelling in opposite directions are being guided on the stripline. Because the electric field is in the same direction the voltage will have the same polarity at both ends of the stripline. If a closed contour was place between the stripline and the reference plane and symmetric about the electric field injection point, the net magnetic flux density through the surface formed by the contour would be zero because the magnetic field is circulating.

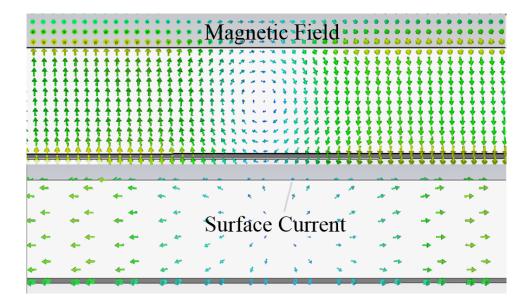

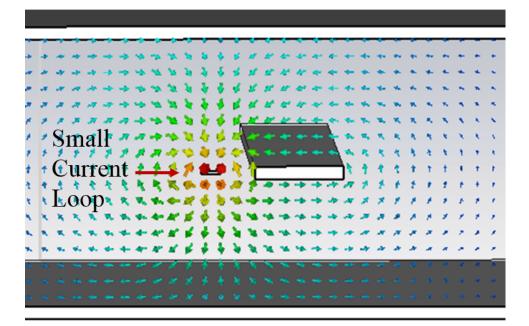

Magnetic field coupling is derived from Faraday's Law which states that a time changing magnetic field induces a circulating electric field. For example, consider the case where a small current loop next to a stripline is excited. The current loop produces a magnetic field with a portion of the magnetic field wrapping the conductor. Consider a closed contour defined between the stripline and the top reference plane. The magnetic field penetrates the surface created by the contour and circulate back on themselves by passing between the bottom of the stripline and the bottom reference plane. As a result,

Figure 2.2. Magnetic field and surface current density on electric field coupled stripline.

there is a time changing magnetic flux density that produces an electric field. Electric fields produced by the time changing magnetic fields must circulate back on themselves. For actual conductors with finite conductivity, there will be a portion of the electric field parallel to the conductor that drives conduction current (emf). The direction of the electric field circulation is such to drive a conduction current to oppose the changing magnetic flux density. If the conductor is modeled as a PEC, the tangential electric field at the conductor surface must be zero. The vertical electric fields on each side of the magnetic field are in opposite directions as seen in Figure 2.4. If the  $\hat{n} \cdot \vec{D} = \rho_s$  boundary condition is applied, the surface charge density on the conductor at the two locations will have opposite polarities showing a difference in potential. The magnetic field is in the same direction while the electric field is in opposite directions. Because the magnetic field is in the same direction the surface current is in the same direction. Applying the Poynting vector, power flow is opposite for the fields on each side of the excitation. The polarity of the voltage drop at each end of the transmission line is opposite. Two propagating TEM waves travelling in opposite directions are being guided on the stripline.

Figure 2.3. Magnetic field source coupling to stripline.

Circuit parameters are more intuitive to most engineers and easier to work with so transmission lines are typically modeled using distributed lumped circuit elements. The transmission line telegrapher's equations solve the wave equation with voltage and current rather than fields. The magnetic field is represented with an inductance and the electric field is represented with a capacitance. As a result of the TEM field structure of a transmission line, these lumped element models can be developed from the Maxwell's equations directly. Another important result of the TEM fields is that static solvers can be used to obtain the capacitance and inductance. Using the lumped element models, electric field coupling is replaced with capacitive coupling where current is injected in to the victim line through the mutual capacitance. If the transmission line structure is uniform, the current will see an equal impedance in both directions so half the current will travel forwards and the other half of the current will travel backwards. This property will result in the same polarity voltage drop across the termination on each end of the structure which as expected agrees with the result from analyzing the fields directly. Magnetic field coupling is replaced with

Figure 2.4. Magnetic field source coupling to stripline.

inductive coupling where a time-changing current induces an emf or series voltage source in the victim. A current will be driven by this series voltage which results in current flowing in one direction. As a result, the polarity of the voltage drop across the termination of each end of a structure will be opposite. This result again agrees with the fields where two waves are propagating with magnetic fields in the same direction and with normal electric fields in opposite directions. The above results can be used to analyze the coupling response to determine if the magnetic field (inductive) coupling or electric field (capacitive) coupling is the dominant coupling mechanism. For instance, if inductive coupling dominates the polarity of the voltage drop at the measurement port on each side of the transmission line will be opposite. In the frequency-domain, the phase of the voltage will be opposite. When the terminations of the transmission line are not matched the coupling response becomes more complicated. This mismatch will introduce reflected waves to satisfy the boundary conditions. At frequencies where the geometry is electrically small, transmission line effects can be neglected and the analysis of the effect of a termination simplifies. For example, for a high impedance termination even a small noise current can create a large voltage drop across the high impedance. Capacitive coupling is then more of an issue for high impedance terminations. In comparison, a series voltage induced by inductive coupling will not drive much current in a high impedance circuit.

For transmission lines in a homogeneous medium, such as a stripline, the inductive coupling and capacitive coupling are equal. Near end cross talk (NEXT) and far end cross talk (FEXT) are used to describe the crosstalk for coupled transmission lines. Because the phase is opposite for the inductive coupling and capacitive coupling they cancel each other out at the far end and add together at the near end where they are in phase. The physics that describe crosstalk are the same physics used to design directional couplers which is why transmission line couplers are reverse couplers (near end is the coupled port). A microstrip is not a homogenous medium as some of the fields travel in air and some travel in the dielectric so the inductive coupling and capacitive coupling do not cancel each other out. The fields travelling in air have a different velocity than the fields traveling in the dielectric which is why there is not cancellation. The fields of the microstrip on the edges fringe out farther compared to the fields of a stripline which are more contained because of the second reference plane. As a result of the fringing fields for the microstrip, the microstrip coupling drops off slower than stripline coupling. These two reasons are why stripline routing is regarded as superior for minimizing crosstalk. Extensive treatment of transmission line coupling can be found in [1] and [3].

#### 2.2. VIA TO VIA COUPLING WITHIN A PARALLEL-PLATE CAVITY

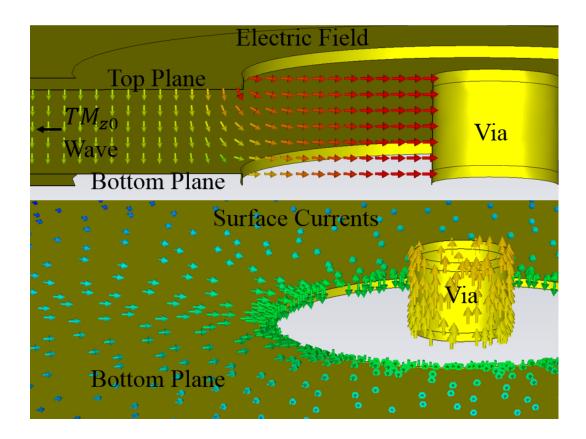

In the introduction section, it was demonstrated that a via penetrating a pair of parallel plates excites a radial TEM wave. By reciprocity, because the vias are able to excite the cavities they are also able to be coupled to by fields in the cavity. Analytical solutions for a radial waveguide or radial transmission line were published in electromagnetics textbooks long before it became an issue for PCB geometries [19]. Publications regarding coupling to the parallel plates and their consequences for PCBs began to appear in the early 1990s. There are many publications covering via coupling and this background is not comprehensive listing of all of them. In 1993, a paper illustrated that at higher frequencies the parallel plates used for power distribution needed to be modeled as a parallel-plate waveguiding system for accurate prediction of "Delta-I noise" [20]. Previously, only inductive effects had been considered. This "Delta-I noise" is another name for the "Simultaneous Switching Noise" (SSN) mentioned in the introduction. The first analytical method for calculating coupling between vias used admittance matrices to describe the parallel-plate modes responsible for the coupling, but was restricted to infinitely large parallel plates as edge reflection was not considered [21]. In 1995, [22] presented field plots from full-wave simulation showing the excitation of the radial TEM waves at a via transition and created a circuit model with dependent sources to capture the mode conversion. Coupling of energy to an undesired mode can be referred to as mode conversion. In [23], analytical expressions for via coupling were developed from radial transmission line theory that accounted for reflections from finite boundaries and time-domain plots were presented to show reflections off the finite boundaries. In [24], analytical expressions were derived that incorporated multiple scattering from other vias in the cavity using the Foldy-Lax equations, although only circular cavities could be used. An excellent analytical treatment of the via and parallel plate geometry is available in [25]. The paper solves the inhomogeneous differential equation using the Green's function and accounts for the finite via radius and incorporates different boundary conditions. The goal of the paper was to obtain analytical formulas for the via

Figure 2.5. Electric field and surface currents for via passing through cavity with absorbing boundary conditions to prevent standing-wave patterns.

plate capacitance that is dependent on the higher order modes. More recently, a physicsbased via circuit models with the via plate capacitance from [25] and impedance matrices for the parallel-plate pair was used to study the effect of different dielectric thicknesses and ground via patterning on the via crosstalk [26]. The parallel-plate impedance matrices captures the coupling between vias due to the dominant  $TM_{z0}$  propagating mode. In [27], the accuracy of the physics-based circuit model was evaluated and found that coupling due to the higher order  $TM_z$  modes only needs to be considered for very closed spaced vias such as those closer than 30 mils for typical dielectric thicknesses. In [28], the intrinsic circuit model for multiple vias was presented which extends the the physics-based via circuit model to accurately model field effects of the higher-order modes for vias in close proximity.

The radial waveguide equations in [5] are derived from the z-component of the vector potential  $\vec{A}$ , assuming a line current source in the z-direction. Therefore, the existence of a current on the via excites the  $TM_z$  fields in the cavity. Alternatively, the fields in the parallel-plate cavity can be obtained from equivalent, fictitious magnetic currents in the coaxial via/antipad aperture, which are dependent on the electric field [25]. The electric field in the coaxial aperture is also an excitation for the  $TM_z$  fields in the cavity. Another way to look at the coupling is in terms of mode conversion: the TEM coaxial mode in the anti-pad aperture is converted into  $TM_z$  modes in the parallel-plate cavity and then converted back into a TEM coaxial mode in the antipad aperture in the next plane [25]. The impedance of the higher-order  $TM_z$  modes that are cutoff is capacitive, representing stored electrical energy [5]. The stored energy associated with the higher-order modes is then converted back to a coaxial TEM mode in the antipad aperture, but some energy is lost as a result of the propagating  $TM_{z0}$  mode. The reason for this excitation is also sometimes explained as a return current path discontinuity [29]. For TEM or quasi-TEM transmission lines, the return current (an image current) flows on the reference plane next to the signal conductor. Figure 2.5 shows the electric field around the via passing through a pair of parallel plates and the surface currents on the via and the bottom plate. The surface currents inside the anti-pad plane aperture are in the opposite direction of the currents on the via. At a via transition (through at least one plate pair), the return current needs to change reference planes and does not have a well-defined conduction current path to do so in most cases. In order to satisfy Maxwell's continuity equation (KCL that includes displacement current), a displacement current must exist between the two plates. Therefore, the existence of the radial wave seen in Figure 2.5 is required to satisfy the continuity of current and is said to be the return current path for the via currents.

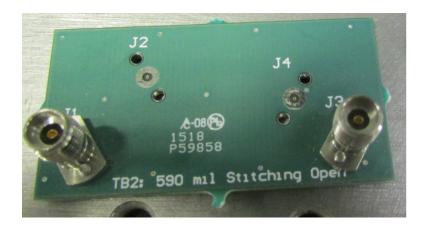

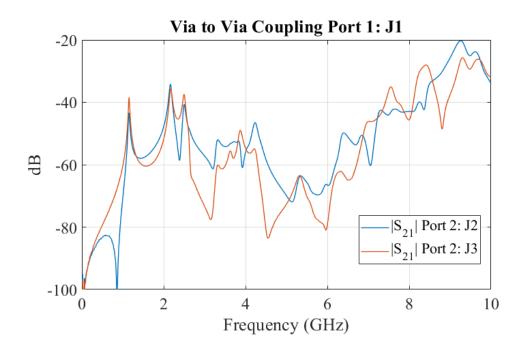

There are multiple factors that influence the strength of the coupling, many of which are clearly illustrated in the background literature. For instance, analytical expressions in [23] show that the magnitude of the coupled  $TM_{z0}$  wave is directly proportional to the

Figure 2.6. Test board for measuring coupling between two vias in a cavity.

height of the parallel-plate cavity, i.e. the dielectric thickness. Parametric studies in [26] agree with the analytical expressions and show the coupling is directly proportional to the dielectric thickness. As shown in the introduction, the dielectric loss affects the magnitude of the field strength at resonant frequencies and is an important factor in the coupling. Basic test vehicles were created to study the coupling among vias in a single parallel-plate cavity. Figure 2.6 shows an example of one of the test vehicles. A 2-layer PCB stack-up is used with a dielectric thickness of 62 mils which is much larger than the typical 5-10 mil dielectric layer thickness of most PCBs. Still, the dielectric thickness is electrically small (less than  $\lambda/10$ ) until about 10 GHz and only the fundamental  $TM_{z0}$  mode is propagating. Because of the larger thickness, the cutoff modes may not be fully decayed until a greater distance compared to a thinner cavity. Overall, the structure of the fields will be the same as a thinner cavity. The measured coupling between one excitation via and two other vias is shown in Figure 2.7. For the blue curve, the victim via is 570 mils away from the excitation and the distance is 1500 mils for the red curve. The coupling to each via is on the same order of magnitude despite the varying distances between the excitation via. The coupling clearly exhibits resonant behavior as there are peaks in the coupling. The modal resonances of the cavity will result in coupling maxima if the excitation via excites that resonance and

Figure 2.7. Measured coupling between vias in 62 mil thick parallel-plate cavity.

the victim via is not located close to a null in the field distribution of that resonance. As a result, when the cavity is electrically large the position of the two vias relative to the modal field distribution is the most important factor for the amount of coupling. To further illustrate this, two full-wave simulation models of the parallel-plate cavity with vias are created: one with absorbing PML boundary conditions and another with PMC boundary conditions that result in total reflection at the open edges. Figure 2.8 shows a comparison of the simulated coupling of the two models. If the resonances are eliminated, as with the PML boundary conditions, the coupling is much lower. Figure 2.9 shows the measurement of a cavity with 590 mil GND via spacing with different termination for the vias that form the measurement ports. In one configuration the vias are not connected to the cavity, in another configuration the vias are shorted to the bottom plane, and in the final configuration the vias are connected to the bottom plane through two 0201 100 ohm resistors to form a 50 ohm termination. The shorted configuration results in the greatest coupling and the open configuration the least coupling. The parallel plate is excited by the current on the

Figure 2.8. Simulated coupling comparison between vias in parallel-plate cavity with PML B.C. and PMC B.C.

via so it is expected that the strength of the excitation and thus the coupling increases with increasing current. At a PEC, the tangential electric field must go to zero so a scattered field must be produced to cancel out the incident electric field. This scattered field results in an increase in the total magnetic field around the via and thus current. The terminated via configuration is most representative of actual geometries as a via is typically connected to a transmission line or IC on where most of the energy is delivered. The vias shorted in the plane is representative of the stronger excitation that occurs for a PWR/GND cavity. Another important consideration in the coupling is how various scatterers, e.g. shorting vias and apertures, within a cavity influence the coupling. Full-wave simulation can be used to analyze the coupling in a specific geometry, but more insight is desired for design guidelines. For the case of parallel-plate cavities formed by two GND area fills, stitching vias can be used to limit the excitation of the cavity. Via stitching is investigated further in Section 5.

It can also be relevant to understand the coupling between vias in the absence of modal resonances. For example, if the frequency of the noise exciting the parallel-plate cavity is below the first resonant frequency of the cavity. As long as the vias are not very

Figure 2.9. Measured coupling between vias: short, open, 50 ohm comparison.

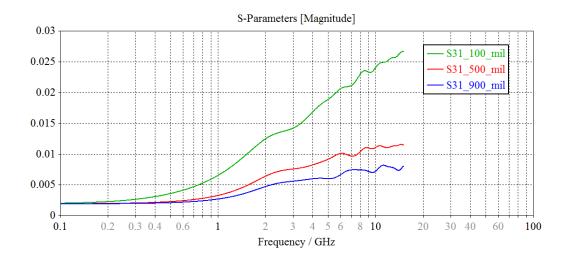

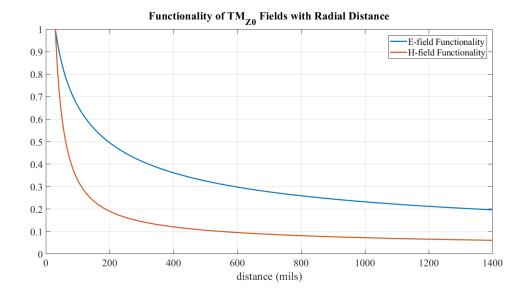

closely spaced, e.g. 30 mils or less depending on the dielectric thickness, the coupling is only due to the propagating  $TM_{z0}$  mode. A simulation model was created to simulate the coupling between two vias at varying distances with scattering off the cavity edges removed via absorbing PML boundary conditions. Figure 2.10 plots the simulated coupling in linear scale for vias with a 100 mil separation, a 500 mil separation, and a 900 mil separation. The coupling for the 100 mil case is about twice the 500 mil case while the reduction in coupling between the 500 mil case and 900 mil case is even less. Overall, the coupling between vias is not strongly dependent on the distance between the two vias. The reason for this is the field strength of the propagating  $TM_{z0}$  fields is dependent on the Hankel function of the 2nd kind which decreases quickly initially, but then decreases at approximately a  $1/\sqrt{x}$  rate subsequently. Figure 2.11 plots the magnitude of the E-field and H-field as a function of distance, where the field strength has been normalized to 1 at 50 mils. As a result, after the quick initial decrease the coupling is only weakly dependent on distance.

Figure 2.10. Simulated coupling distance comparison between vias in parallel-plate cavity with PML boundary conditions.

Figure 2.11. Magnitude of  $TM_{z0}$  fields as a function of distance.

### 2.3. PARALLEL-PLATE CAVITY COUPLING TO CBCPW

A conductor-backed coplanar waveguide (CBCPW) is a transmission line structure that occurs commonly in RF PCBs where GND area fills are often placed on the outer layers. The CBCPW transmission line mode is a combination of a microstrip mode and a CPW mode. CBCPW is also common in MMIC designs and can also be created when a MMIC with no ground plane with coplanar waveguide (CPW) transmission lines is mounted on a metal base. CBCPW is sometimes referred to as ground-backed coplanar waveguide (GBCPW) as well. Coupling or power leakage between a CBCPW and a parallel-plate cavity was first mentioned in the literature in 1986 [30]. Although, the paper did not provide any quantification of the amount of coupling or mitigation strategies. Subsequent papers by other authors elaborated on the coupling mechanism between the CBCPW and the parallel plates including [31]. [32] contains an analysis of using shorting vias as a suppression technique by deriving analytical expressions to evaluate the leakage loss as a function of different design parameters such as the shorting via spacing. Modes that lose energy due to coupling into the substrate are sometimes referred to leaky modes. The use of this term is contingent on the parallel plates being assumed to be infinite. [32] was primarily concerned with minimizing the power leakage loss to the parallel plates and did not incorporate scattering effects from the edges of finite size parallel plates. Other papers considered the effect of the finite size of the parallel plates and its consequences. [33] used test vehicle measurements to demonstrate the efficacy of different via stitching strategies for suppressing resonances associated with finite size of the cavity and showed that the resonances can be predicted analytically by the cavity model. These resonances result in dips or dropouts in the insertion loss.

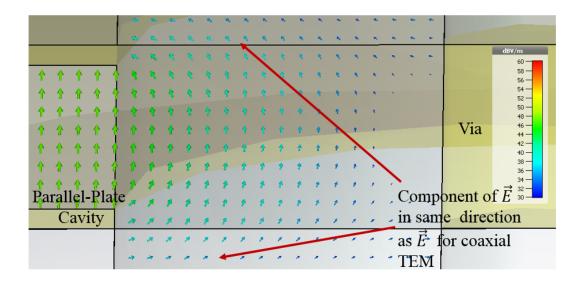

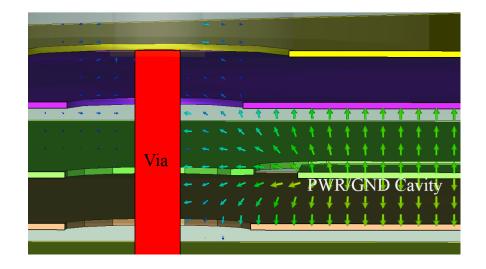

Although it is known that stitching vias can minimize the coupling to parallel-plate modes, to understand the excitation of the parallel plates it is best to analyze the case without vias. As mentioned previously, a CBCPW mode is a combination of the CPW mode and microstrip mode as can be seen in Figure 2.12. Some of the electric field lines terminate

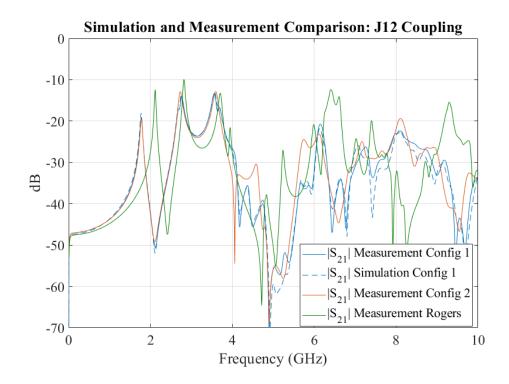

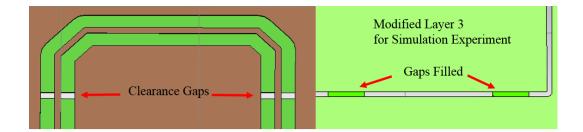

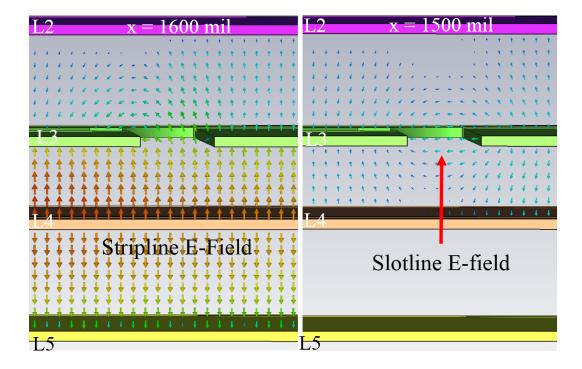

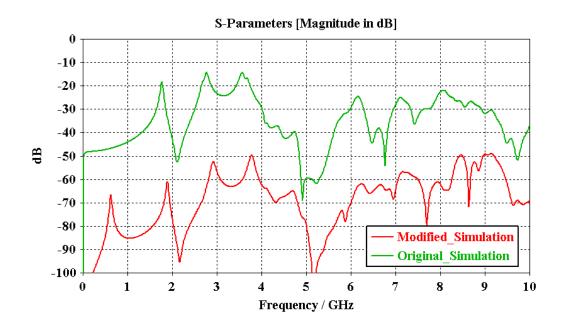

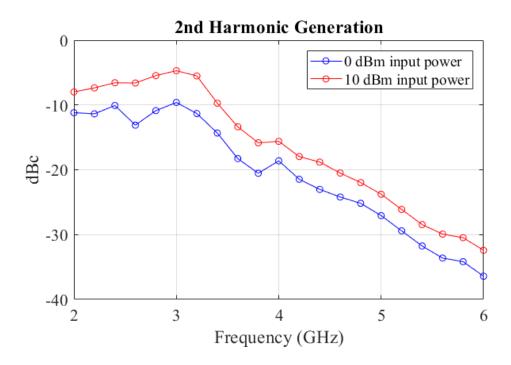

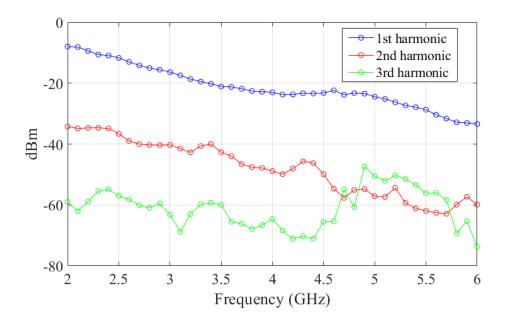

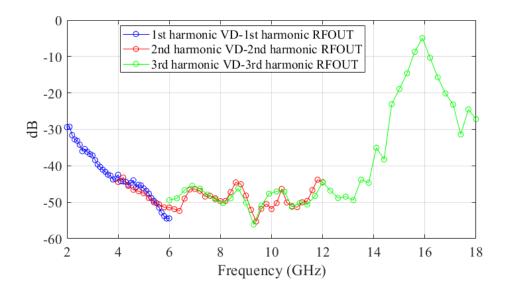

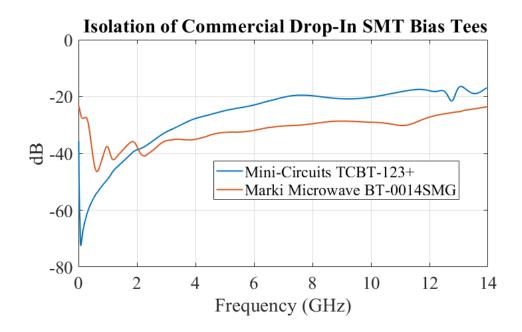

Figure 2.12. Electric field cross-section of CBCPW in logarithmic scale.