## Scholars' Mine

**Doctoral Dissertations**

Student Theses and Dissertations

Fall 2016

## Characterization of an Integrated Circuit with Respect to **Electrostatic Discharge-Induced Soft Failures**

Benjamin J. Orr

Follow this and additional works at: https://scholarsmine.mst.edu/doctoral\_dissertations

Part of the Electrical and Computer Engineering Commons

**Department: Electrical and Computer Engineering**

## **Recommended Citation**

Orr, Benjamin J., "Characterization of an Integrated Circuit with Respect to Electrostatic Discharge-Induced Soft Failures" (2016). Doctoral Dissertations. 2543. https://scholarsmine.mst.edu/doctoral\_dissertations/2543

This thesis is brought to you by Scholars' Mine, a service of the Missouri S&T Library and Learning Resources. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

# CHARACTERIZATION OF AN INTEGRATED CIRCUIT WITH RESPECT TO ELECTROSTATIC DISCHARGE-INDUCED SOFT FAILURES

by

## BENJAMIN J. ORR

## A DISSERTATION

Presented to the Graduate Faculty of the

## MISSOURI UNIVERSITY OF SCIENCE AND TECHNOLOGY

In Partial Fulfillment of the Requirements for the Degree

DOCTOR OF PHILOSOPHY

in

**ELECTRICAL ENGINEERING**

2016

Approved by

David J. Pommerenke, Advisor

Daryl Beetner

Jun Fan

Victor Khilkevich

Harald Gossner

Copyright 2016 BENJAMIN J. ORR

All Rights Reserved

## **PUBLICATION DISSERTATION OPTION**

This dissertation consists of the following articles, formatted in the style used by the Missouri University of Science and Technology.

Paper I on pages 19-44, as well as Paper II on pages 45-71, were published at the 2013 EOS/ESD Symposium in Las Vegas, NV.

Paper III on pages 72-97 was published at the 2015 EOS/ESD Symposium in Reno, NV and an extension to this work is intended for submission to the IEEE Transactions on Electromagnetic Compatibility.

Paper IV on pages 98-128 is intended for submission to the IEEE Transactions on Device and Materials Reliability.

#### **ABSTRACT**

This research proposal presents a methodology whereby an integrated circuit (IC) can be characterized with respect to soft-failures induced by Electrostatic Discharge (ESD)-like events. This methodology uses an exclusively "black-box" approach to determine the response of an IC in a system-level environment, thereby allowing it to be implemented without intimate knowledge of the DUT IC. Results from this methodology can be referenced during system design to raise awareness of specific vulnerabilities of the core system ICs.

During work on this methodology, several sub topics have been explored and developed in the field of system-level ESD. Sections 2 and 3 introduce two topics which were developed to facilitate the generation and expression of IC pin models. Papers 1 and 2 introduce injection methods for characterizing complete systems on an interface-by-interface basis and form the foundation for the following works. Papers 2 and 3 mirror Papers 1 and 2 but instead shift focus away from the system as a whole and outline methods for characterizing the integrated circuits directly. Finally, Section 4 outlines a model method which can be used to describe the failures found in Paper 4 in circuit simulation, rounding out the work. Additional measurements which were unable to be included in Paper 4 are included in Appendices A, B, and C.

## **ACKNOWLEDGMENTS**

I would like to thank my advisor Dr. David Pommetenke, for supporting me from late in my undergraduate all the way through my graduate studies at the MS&T EMC Lab. Thank you also to the rest of my committe here at MS&T, Dr. Daryl Beetner, Dr. Jun Fan, and Dr. Victor Khilkevich, for their insights into this work. I would also like to extend special thanks Harald Gossner, the instigator of my research project. My time working with Harald in Munich was an enormous opportunity that I benefited from academically, professionally, and personally. Finally, I would like to thank my wife Patricia for her patience and support through my graduate work as well as my family for their role in where I am today.

## TABLE OF CONTENTS

|     |       |         | P                                           | age  |

|-----|-------|---------|---------------------------------------------|------|

| PU  | BLIC  | CATION  | DISSERTATION OPTION                         | iii  |

| AE  | STR   | ACT     |                                             | iv   |

| AC  | KNO   | WLEDO   | GMENTS                                      | v    |

| LIS | ST OF | F ILLUS | TRATIONS                                    | xi   |

| LIS | ST OF | F TABL  | ES                                          | kvii |

| SE  | CTIO  | Ν       |                                             |      |

| 1.  | INTI  | RODUC   | TION                                        | 1    |

| 2.  | PIEC  | CEWISE  | E LINEAR IV CURVES                          | 3    |

|     | 2.1.  | INTRO   | DDUCTION                                    | 3    |

|     |       | 2.1.1.  | Circuit Building Blocks                     | 3    |

|     |       | 2.1.2.  | Simulation Using Piecewise Linear IV Models | 5    |

|     |       | 2.1.3.  | Conclusion                                  | 8    |

| 3.  | THR   | EE-TER  | RMINAL PIN MODELING                         | 10   |

|     | 3.1.  | INTRO   | DDUCTION                                    | 10   |

|     |       | 3.1.1.  | Measuring Pins in the Context of a System   | 11   |

|     |       | 3.1.2.  | Benefits of the Three-Terminal Model        | 11   |

|     |       | 3.1.3.  | Conclusion                                  | 16   |

## **PAPER**

| I.  |               | ERED SYSTEM-LEVEL CONDUCTIVE TLP PROBING METHOD FOR EMI HARD FAIL AND SOFT FAIL THRESHOLD EVALUATION | 19 |

|-----|---------------|------------------------------------------------------------------------------------------------------|----|

| ΑE  | BSTR.A        | ACT                                                                                                  | 20 |

| 1.  | INTR          | ODUCTION                                                                                             | 21 |

| 2.  | CON           | DUCTIVE TLP INJECTION CONFIGURATIONS                                                                 | 22 |

|     | 2.1.          | DEVICE LEVEL TESTING                                                                                 | 22 |

|     | 2.2.          | SYSTEM LEVEL TESTING USING HIGH IMPEDANCE PROBES                                                     | 23 |

|     | 2.3.          | RESISTIVE AND CAPACITIVE PROBES                                                                      | 25 |

|     | 2.4.          | TRANSIENT VOLTAGE SUPPRESSOR DIODE PROBE CHARACTER-IZATION                                           | 27 |

|     | 2.5.          | PROBE PARASITICS                                                                                     | 30 |

| 3.  | VER           | IFICATION OF THE DIODE INJECTION ON A FUNCTIONAL SYSTEM                                              | 38 |

| 4.  | CON           | CLUSION                                                                                              | 42 |

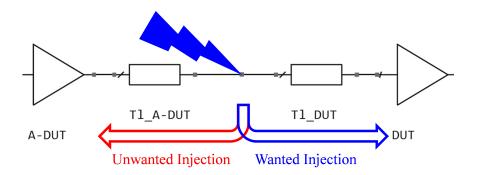

| 5.  | ACK           | NOWLEDGEMENTS                                                                                        | 43 |

| ΒI  | BLIO          | GRAPHY                                                                                               | 44 |

| II. |               | STEMATIC METHOD FOR DETERMINING SOFT-FAILURE ROBUST-SOF A SUBSYSTEM                                  |    |

| ΑE  | BSTR <i>A</i> | ACT                                                                                                  | 46 |

| 1   | INITD         | PODLICTION                                                                                           | 17 |

| 2.  | METHOD OVERVIEW                                                                                          | 49 |

|-----|----------------------------------------------------------------------------------------------------------|----|

| 3.  | SYSTEM, TESTING AND FAILURE DESCRIPTION                                                                  | 51 |

| 4.  | DUT 1: MEASUREMENTS AND OBSERVATIONS                                                                     | 53 |

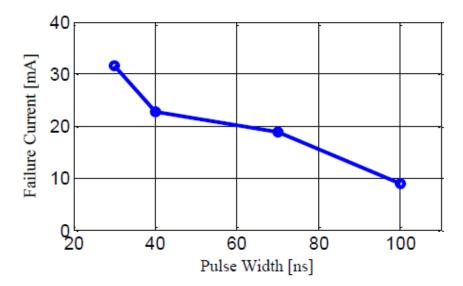

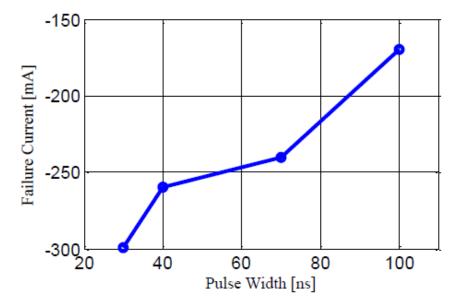

|     | 4.1. PULSE POLARITY                                                                                      | 56 |

|     | 4.2. PULSE RISE TIME                                                                                     | 57 |

|     | 4.3. PULSE WIDTH                                                                                         | 57 |

|     | 4.4. FAILURE ANALYSIS                                                                                    | 57 |

| 5.  | DUT 2: MEASUREMENTS AND OBSERVATIONS                                                                     | 62 |

|     | 5.1. PULSE POLARITY                                                                                      | 63 |

|     | 5.2. PULSE WIDTH                                                                                         | 64 |

|     | 5.3. FAILURE CULPRIT                                                                                     | 64 |

|     | 5.4. SOFTWARE ERROR LOG                                                                                  | 67 |

| 6.  | CONCLUSION                                                                                               | 69 |

| 7.  | ACKNOWLEDGEMENTS                                                                                         | 70 |

| BI  | BLIOGRAPHY                                                                                               | 71 |

| III | . A PASSIVE COUPLING CIRCUIT FOR INJECTING TLP-LIKE STRESS INTO ONLY ONE END OF A DRIVER/RECEIVER SYSTEM | 72 |

| AE  | BSTRACT                                                                                                  | 73 |

| 1.  | INTRODUCTION                                                                                             | 74 |

| 2.  | CIRCUIT DEVELOPMENT                                                                                      | 76 |

|     | 2.1. | TRANSFORMER PARAMETERS                                                           | 76  |

|-----|------|----------------------------------------------------------------------------------|-----|

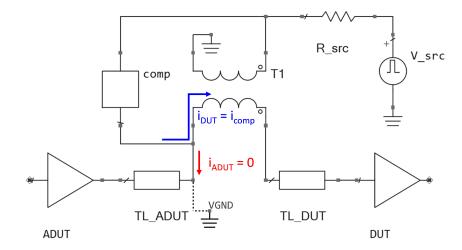

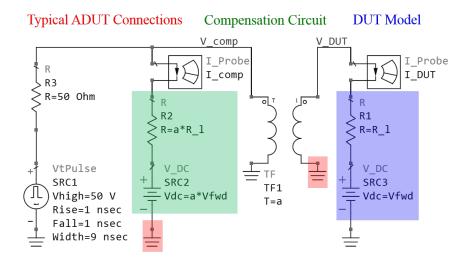

|     | 2.2. | ESTABLISHING THE VIRTUAL GROUND                                                  | 77  |

|     | 2.3. | IDEAL CIRCUIT SIMULATION                                                         | 80  |

| 3.  | CIRO | CUIT IMPLEMENTATION                                                              | 83  |

|     | 3.1. | TEST PCB                                                                         | 83  |

|     |      | 3.1.1. Test PCB Simulation                                                       | 83  |

|     |      | 3.1.2. Test PCB Measurement                                                      | 87  |

|     | 3.2. | IMPLEMENTATION ON A REAL SYSTEM                                                  | 91  |

| 4.  | CON  | ICLUSION                                                                         | 95  |

| 5.  | ACK  | NOWLEDGEMENTS                                                                    | 96  |

| BI  | BLIO | GRAPHY                                                                           | 97  |

| IV. |      | RACTERIZATION OF AN APPLICATION PROCESSOR WITH RESPECT ESD-INDUCED SOFT FAILURES | 98  |

| AE  | BSTR | ACT                                                                              | 99  |

| 1.  | INTI | RODUCTION1                                                                       | 100 |

| 2.  | TES' | T METHODOLOGY                                                                    | 102 |

|     | 2.1. | PRELIMINARY                                                                      | 102 |

|     | 2.2. | INJECTION AND CHARACTERIZATION SETTINGS                                          | 103 |

|     | 2.3. | FAILURE DETECTION                                                                | 105 |

|     | 2.4. | DATA ANALYSIS                                                                    | 107 |

| 3   | СНА  | ARACTERIZATION EXAMPLES                                                          | 110 |

|     | 3.1. CAMERA INTERFACE                                    | 10  |

|-----|----------------------------------------------------------|-----|

|     | 3.2. I <sup>2</sup> C INTERFACE                          | 15  |

|     | 3.3. USB 3.0 INTERFACE                                   | 17  |

| 4.  | SUMMARY AND ANALYSIS                                     | 25  |

| 5.  | CONCLUSION                                               | 27  |

| BII | BLIOGRAPHY1                                              | 28  |

| SEC | CTION                                                    |     |

| 4.  | SOFT-FAILURE CAPABLE SEED MODELS                         | 29  |

| 5.  | CONCLUSION                                               | 42  |

| APl | PENDICES                                                 |     |

| A.  | CAMERA PIN (CSIX) CHARACTERIZATION MEASUREMENT RESULTS 1 | 43  |

| B.  | SENSOR PIN (I2CX) CHARACTERIZATION MEASUREMENT RESULTS 1 | 68  |

| C.  | USB 3.0 (USB3) CHARACTERIZATION MEASUREMENT RESULTS      | 88  |

| BII | BLIOGRAPHY 2                                             | 208 |

| VI  | TA2                                                      | 210 |

## LIST OF ILLUSTRATIONS

| Figur | Figure                                                                                                                      |    |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------|----|--|

| 2.1   | Ideal and negative ideal diode implementations                                                                              | 4  |  |

| 2.2   | Positive and negative resistance unit cell implementations                                                                  | 5  |  |

| 2.3   | DC current swept model                                                                                                      | 6  |  |

| 2.4   | DC current swept IV curve                                                                                                   | 7  |  |

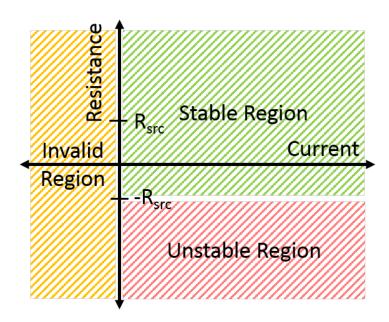

| 2.5   | Regions of stability and validity for the piecewise linear IV SPICE model                                                   | 7  |  |

| 2.6   | Transient simulation of a snapback-positive, diode-negative device                                                          | 9  |  |

| 2.7   | IV curve resulting from a batched transient simulation                                                                      | 9  |  |

| 3.1   | Using a TLP to measure an IV characteristic is a two-terminal technique which ignores the connections made to other IC pins | 10 |  |

| 3.2   | Diagram of the three-terminal IO measurement method                                                                         | 12 |  |

| 3.3   | Three-terminal measurement of an IC IO pin on a wafer-probe station                                                         | 12 |  |

| 3.4   | Three-terminal measurement of an IC IO pin in deadbug configuration                                                         | 13 |  |

| 3.5   | Measured IV curve of a high-speed USB 3.0 differential pin                                                                  | 14 |  |

| 3.6   | A snapshot of a positive transient current waveform pair                                                                    | 15 |  |

| 3.7   | A snapshot of a negative transient current waveform pair                                                                    | 15 |  |

| 3.8   | Split IO IV curves showing currents to VDD and VSS                                                                          | 16 |  |

| 3.9   | Piecewise linear three-terminal IO cell model                                                                               | 17 |  |

| 3.10  | Measurement and model comparison                                                                                            | 18 |  |

| PAPE  | ER I                                                                                                                        |    |  |

| 2.1   | Conductive TLP measurement setup.                                                                                           | 22 |  |

| 2.2   | TLP pulse force probe tip configurations                                                                                    | 23 |  |

| 2.3   | TLP system connected to RF/high-speed data line.                                                                            | 24 |  |

| 2.4  | injection probe concepts.                                                                                       | 26 |

|------|-----------------------------------------------------------------------------------------------------------------|----|

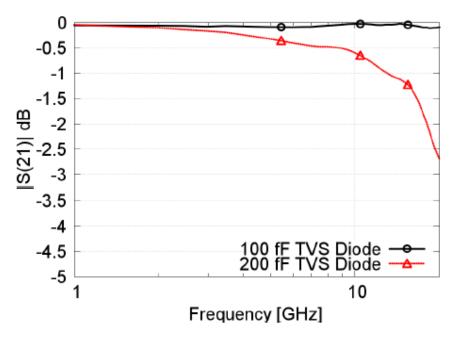

| 2.5  | Insertion Loss of a 0.2 pF and a 0.1 pF TVS Diode                                                               | 28 |

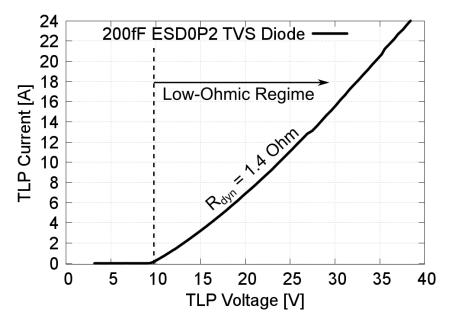

| 2.6  | 200 fF ESD0P2 TVS Diode TLP I/V curve; trigger voltage Vtrig = 10 V, dynamic resistance Rdyn = $1.4~\Omega$     | 29 |

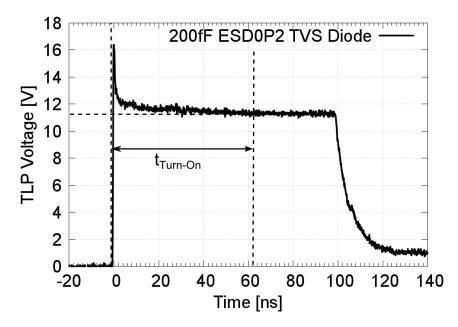

| 2.7  | TLP Voltage waveform of the ESD0P2; Turn-on time tTurn-On = 60                                                  | 29 |

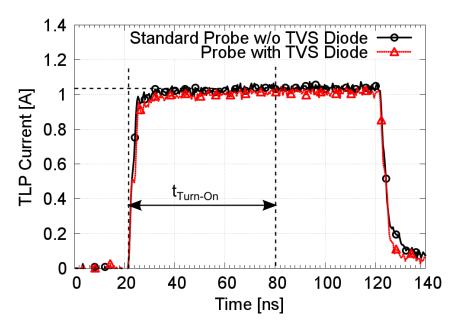

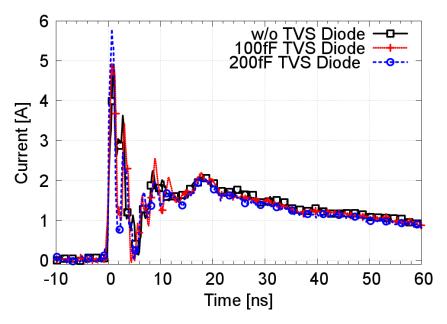

| 2.8  | TLP current wave forms applied into 50 $\Omega$ load using TVS diode probe and standard probe.                  | 30 |

| 2.9  | IEC61000-4-2 1 kV Pulse shape into 2 $\Omega$ target w/o TVS diode, with 100 fF TVS Diode and 200 fF TVS Diode. | 31 |

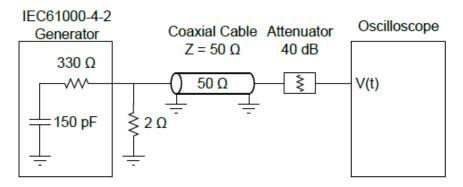

| 2.10 | IEC61000-4-2 pulse source verification setup                                                                    | 31 |

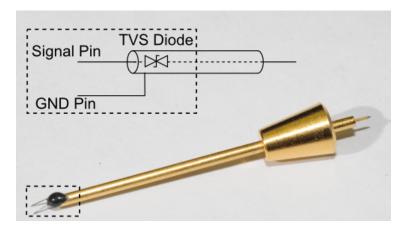

| 2.11 | TVS Diode implemented on GGB PicoProbe Model 10.                                                                | 32 |

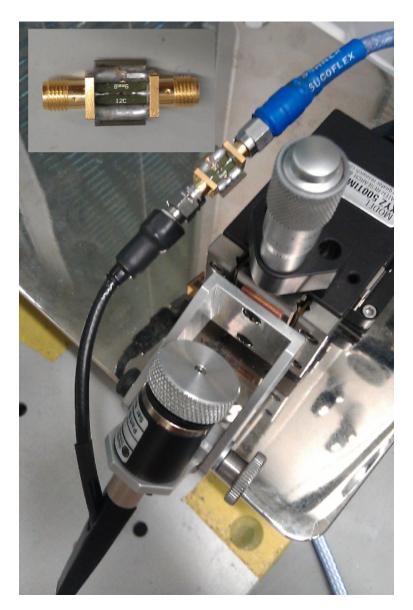

| 2.12 | TVS Diode attached on PCB.                                                                                      | 33 |

| 2.13 | Coax cable equivalent circuit with TVS diode placed at different distance from injection point.                 | 34 |

| 2.14 | Insertion Loss of TVS Diode implemented in GGB PicoProbe Model 10 and TVS Diode attached on PCB                 | 35 |

| 2.15 | Eye Diagram of USB3.0 transmission channel w/o probe attached                                                   | 35 |

| 2.16 | Eye Diagram of USB3.0 transmission channel with TVS diode in PicoProbe head attached.                           | 36 |

| 2.17 | Eye Diagram of USB3.0 transmission channel with PCB mounted TVS diode probe attached.                           | 36 |

| 2.18 | BER of USB3.0 Transmission Channel with TVS diode in PicoProbe head attached.                                   | 37 |

| 2.19 | BER of USB3.0 Transmission Channel with PCB mounted TVS diode probe attached.                                   | 37 |

| 3.1  | MIPI Bus TLP injection setup.                                                                                   | 38 |

| 3.2  | MIPI Bus TLP injection setup.                                                                                   | 39 |

| 3.3  | Measured TLP I/V curve on the MIPI bus with mapped soft failure levels                                          | 40 |

| 3.4  | TLP pulse that arrives between data frames                                                | 41 |

|------|-------------------------------------------------------------------------------------------|----|

| PAPE | ER II                                                                                     |    |

| 4.1  | Measurement and Injection Probes                                                          | 53 |

| 4.2  | Injected Pulse Superimposed on Clock Line                                                 | 54 |

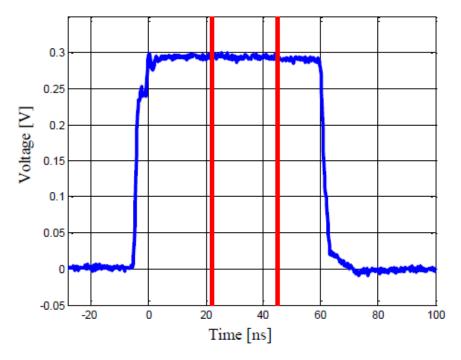

| 4.3  | Measured TLP Pulse with Averaging Window                                                  | 55 |

| 4.4  | Measurement Setup for DUT 1                                                               | 55 |

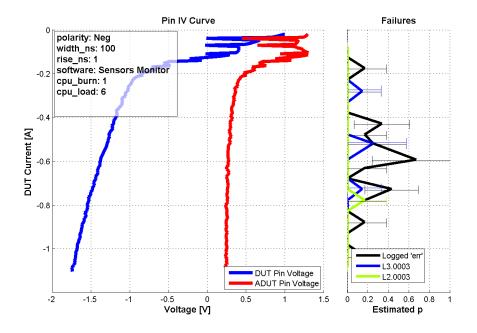

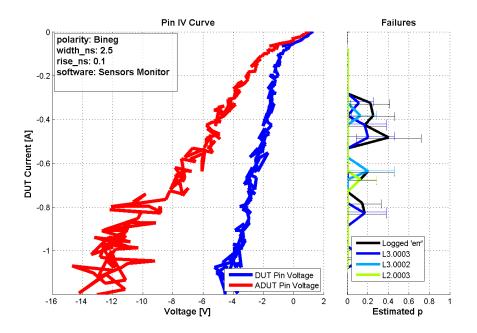

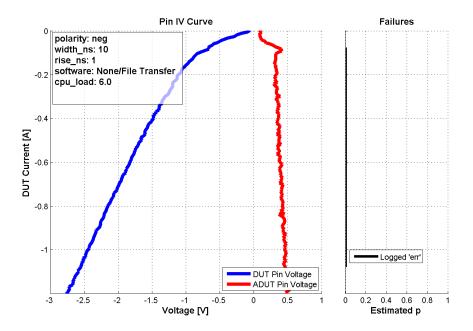

| 4.5  | Negative Quasi-Static IV Curve Truncated due to Multiple Sequential Failures .            | 56 |

| 4.6  | Approximate Failure Current with respect to Pulse Width                                   | 58 |

| 4.7  | Camera Obstruction                                                                        | 59 |

| 4.8  | 5 mm Magnetic Field Probe                                                                 | 60 |

| 4.9  | Screen Tearing on DUT 1                                                                   | 61 |

| 4.10 | Magnetic Field Scan over the Camera on DUT 1                                              | 61 |

| 5.1  | Measurement Setup for DUT 2                                                               | 62 |

| 5.2  | DUT 2 Failure Symptom                                                                     | 63 |

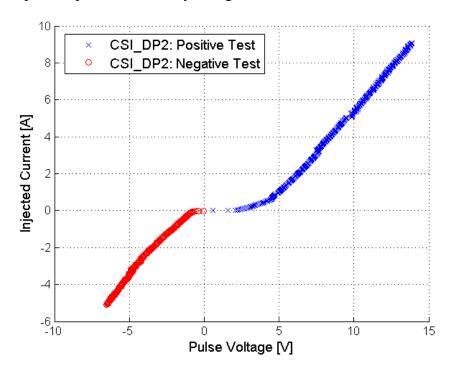

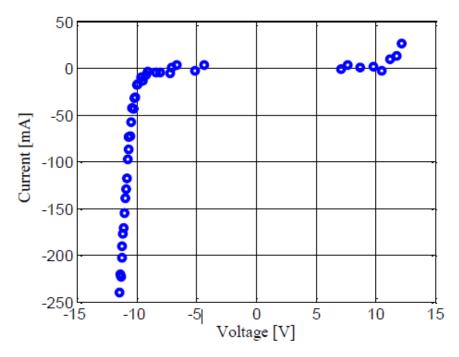

| 5.3  | Quasi-static IV Curve for MIPI_DAT0_N on DUT 2 (70 ns Pulse Width)                        | 65 |

| 5.4  | Approximate Failure Current Dependence for Positive Injection with Respect to Pulse Width | 65 |

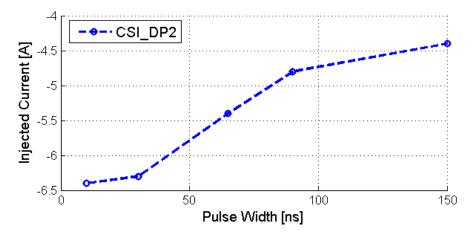

| 5.5  | Approximate Failure Current for Negative Injection with Respect to Pulse Width            | 66 |

| 5.6  | Magnetic Field Scan over Camera on DUT 2                                                  | 67 |

| PAPE | ER III                                                                                    |    |

| 1.1  | Current Injection Problem                                                                 | 75 |

| 2.1  | Compensated Transformer Injection Concept                                                 | 77 |

| 2.2  | Matching the compensation circuit to the load                                             | 78 |

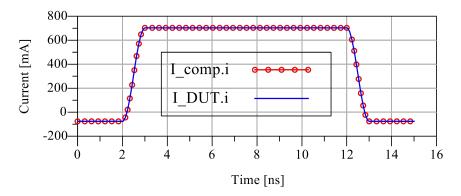

| 2.3  | Comparing the compensation and DUT currents                                               | 79 |

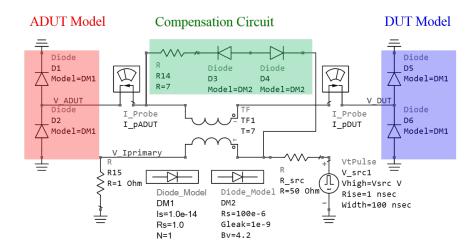

| 2.4  | Ideal injection circuit simulation                                                        | 81 |

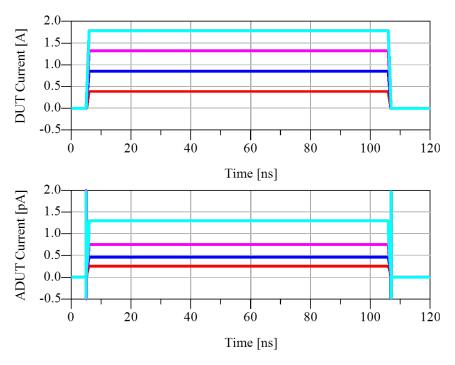

|   | 2.5  | Ideally simulated DUT and ADUT currents for 5 levels of injection                                                                                                                        | 82  |

|---|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

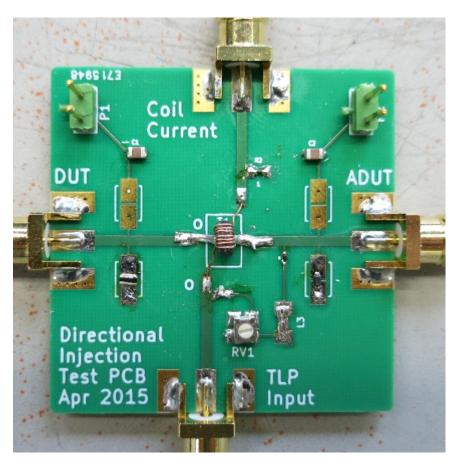

|   | 3.1  | Populated Test PCB                                                                                                                                                                       | 85  |

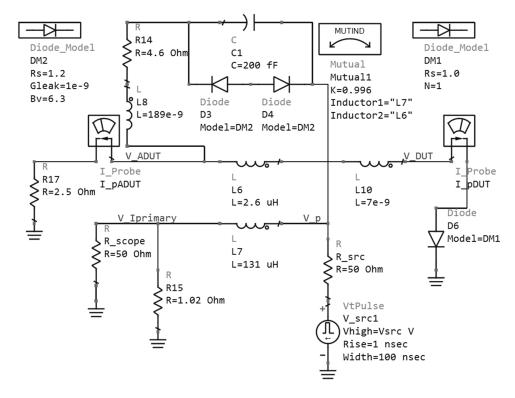

|   | 3.2  | Test PCB equivalent circuit                                                                                                                                                              | 86  |

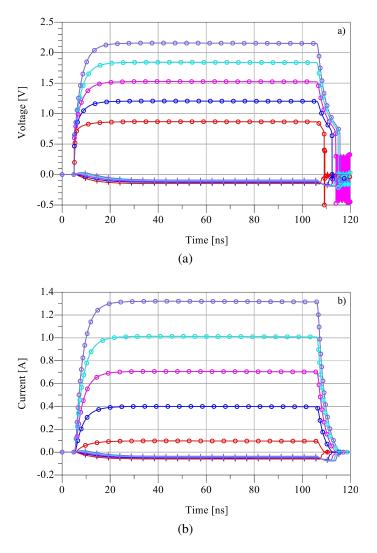

| • | 3.3  | Test PCB simulated DUT ('o' marker) and ADUT ('+' marker) a) voltages and b) currents for five different injection levels                                                                | 87  |

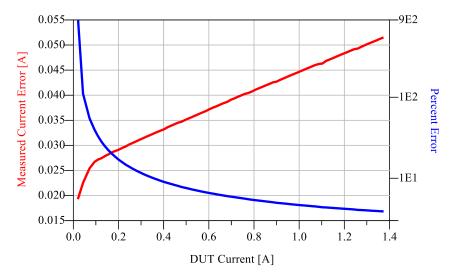

|   | 3.4  | Test PCB simulated current measurement error through sense resistor                                                                                                                      | 88  |

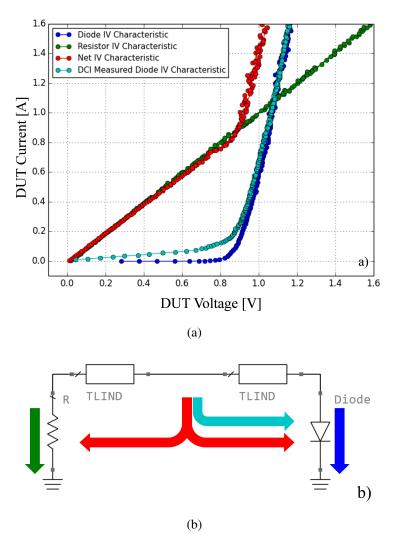

| • | 3.5  | a) IV curve behavior with various measurement configurations; b) Color coded description of IV measurements                                                                              | 89  |

|   | 3.6  | Virtual ground performance during directional measurements                                                                                                                               | 90  |

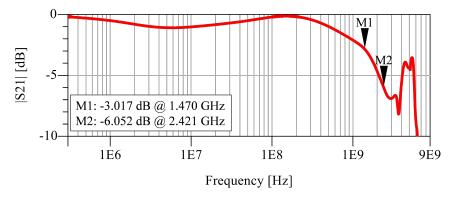

|   | 3.7  | Directional injection circuit insertion loss                                                                                                                                             | 90  |

|   | 3.8  | Fan out test board (camera) installed on functioning SVB                                                                                                                                 | 91  |

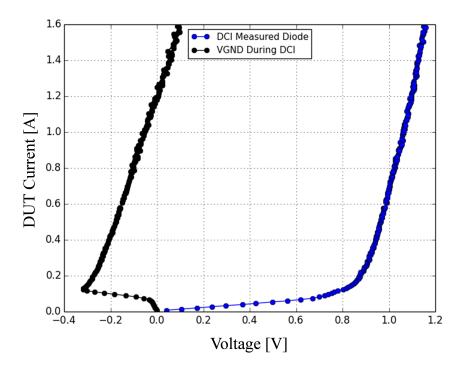

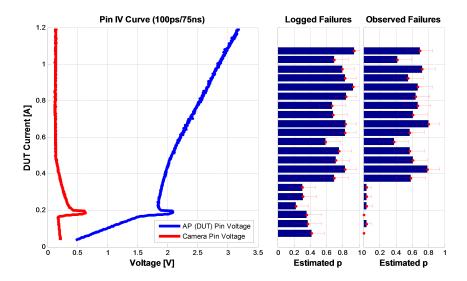

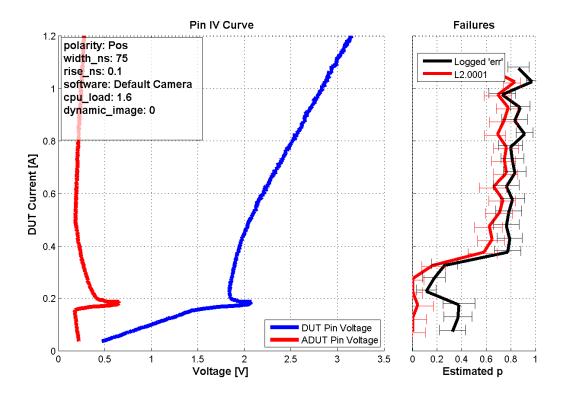

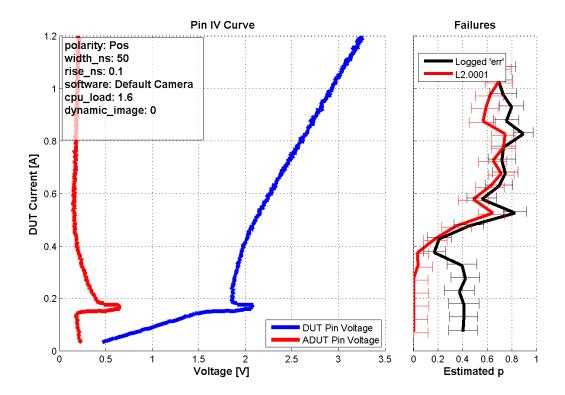

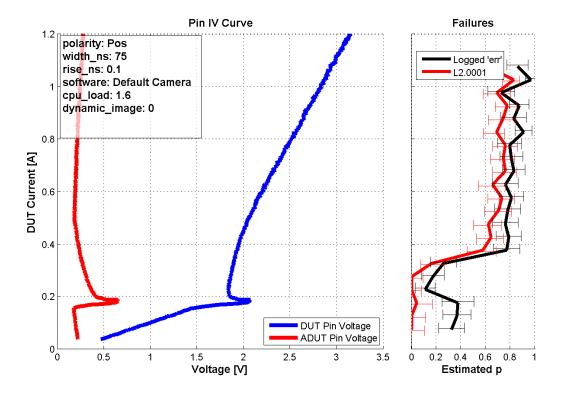

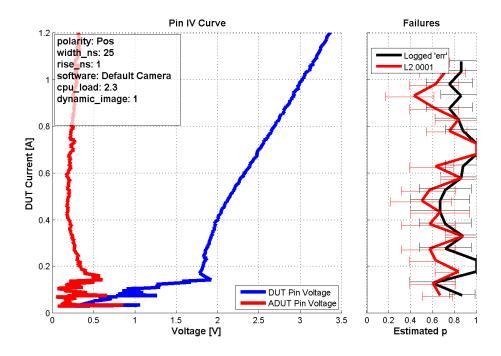

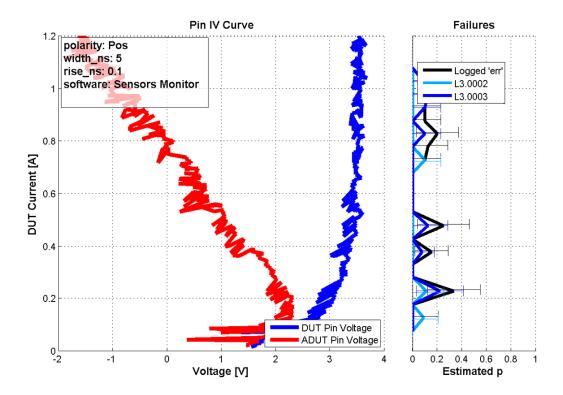

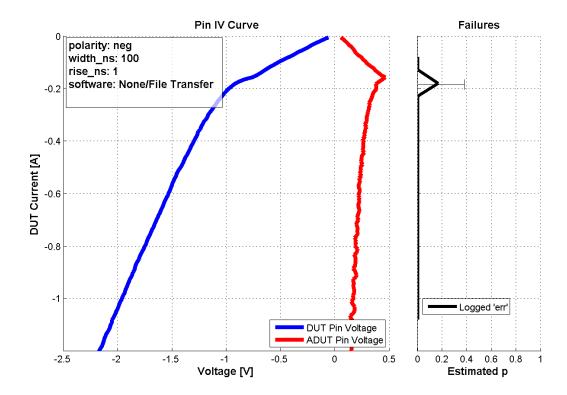

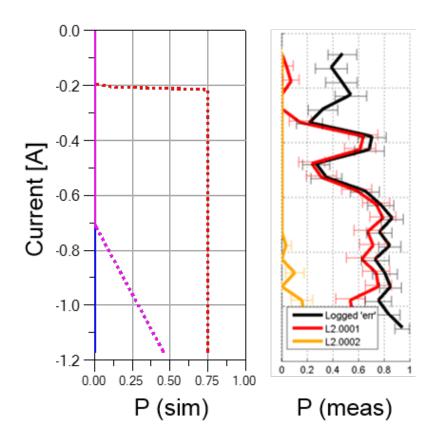

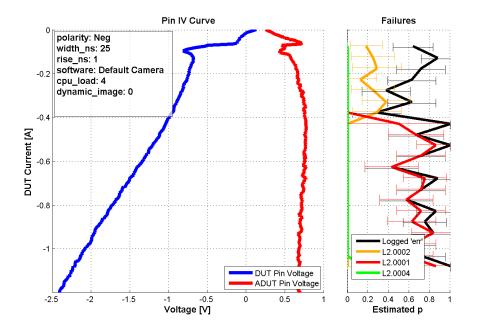

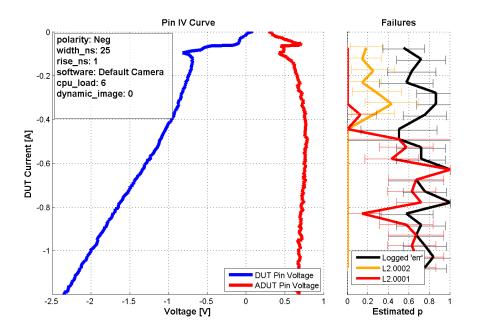

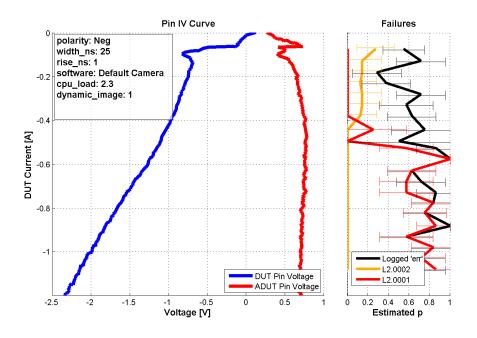

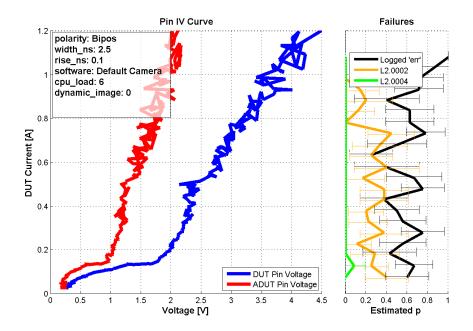

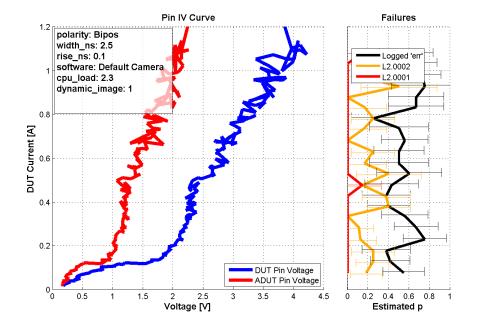

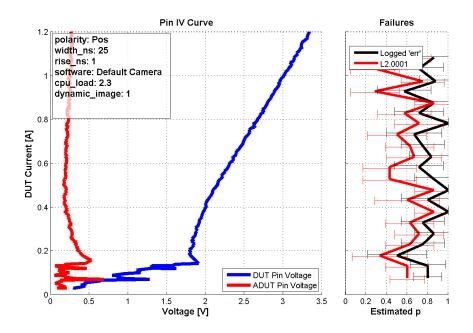

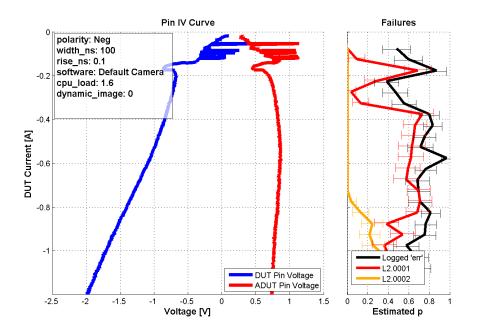

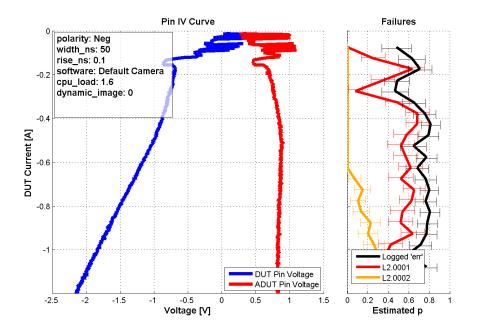

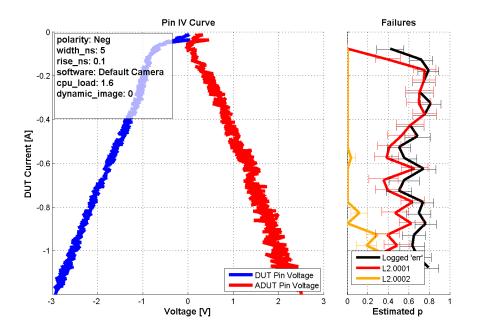

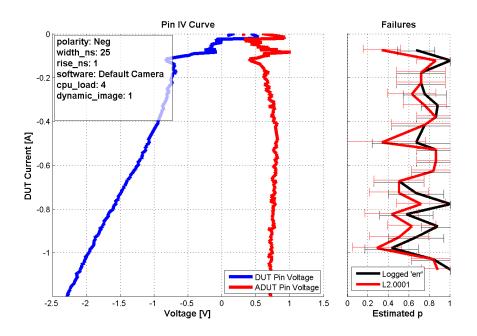

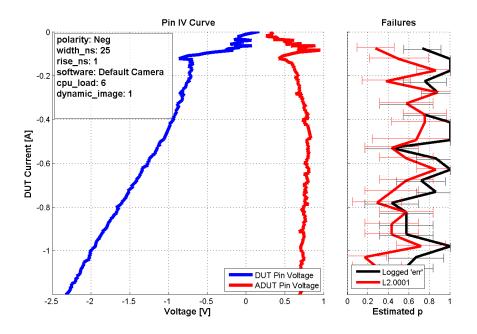

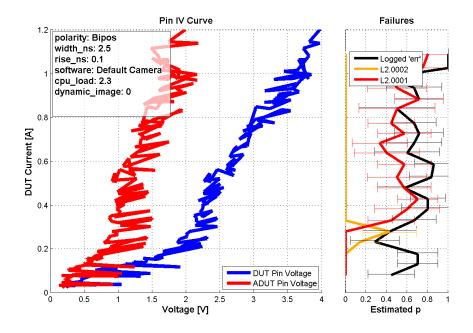

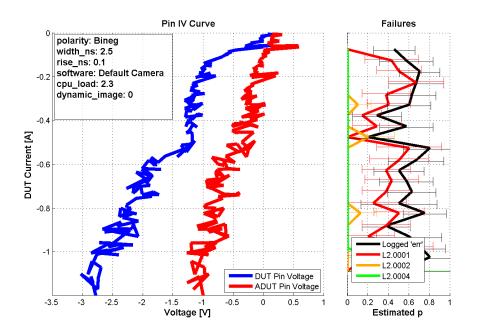

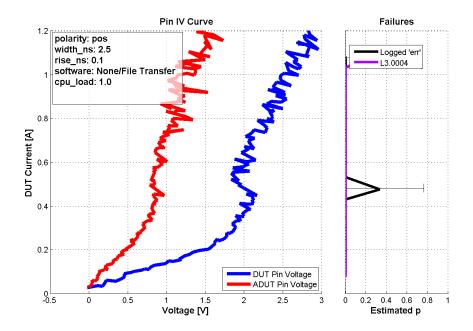

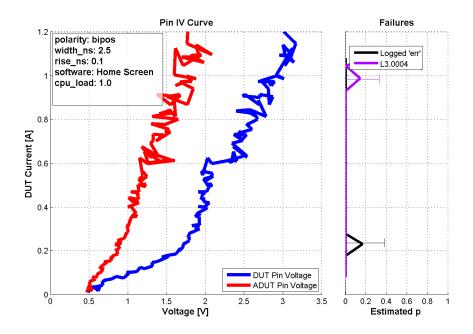

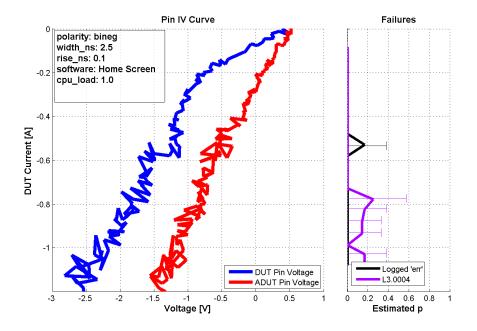

| • | 3.9  | DUT (net:CSI2_CLKN) IV curve for fast 75 ns pulses with VGND performance and soft-failure analysis                                                                                       | 92  |

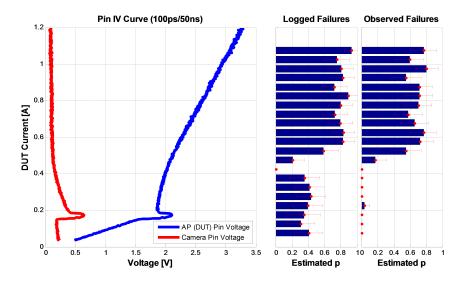

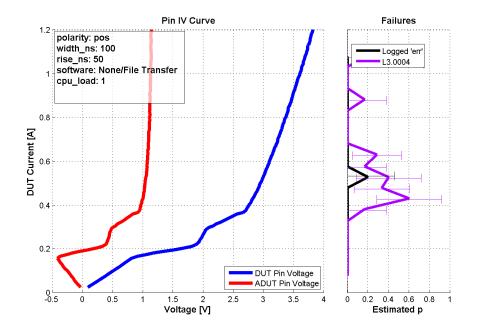

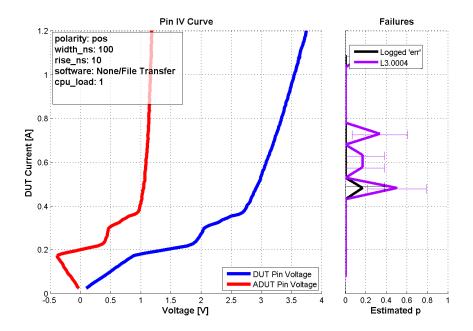

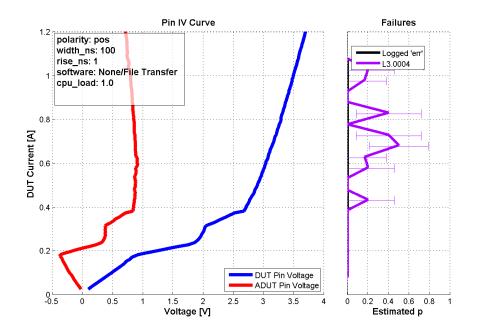

|   | 3.10 | DUT (net:CSI2_CLKN) IV curve for fast 50 ns pulses with VGND performance and soft-failure analysis                                                                                       | 93  |

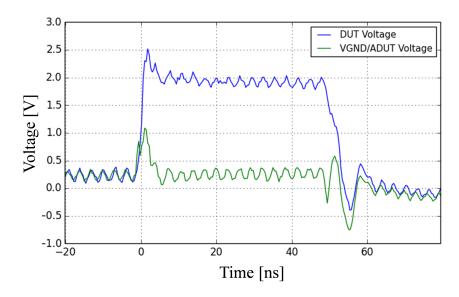

|   | 3.11 | DUT and ADUT transient waveforms                                                                                                                                                         | 94  |

| F | PAPE | R IV                                                                                                                                                                                     |     |

| , | 2.1  | An example system centered on the DUT which is suitable for testing                                                                                                                      | 103 |

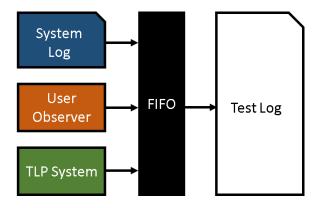

| , | 2.2  | Test log creation                                                                                                                                                                        | 106 |

| , | 2.3  | A log file excerpt                                                                                                                                                                       | 107 |

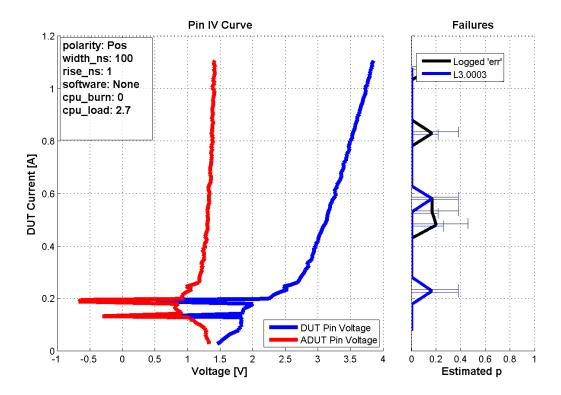

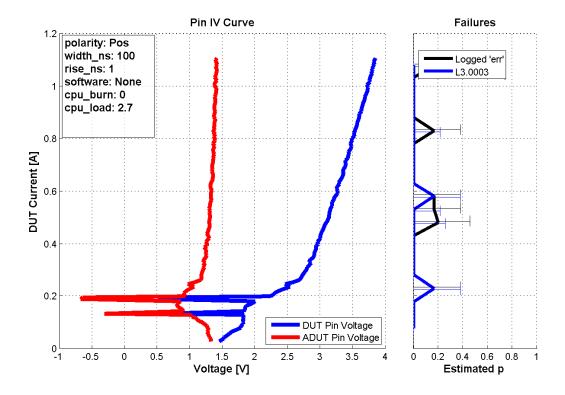

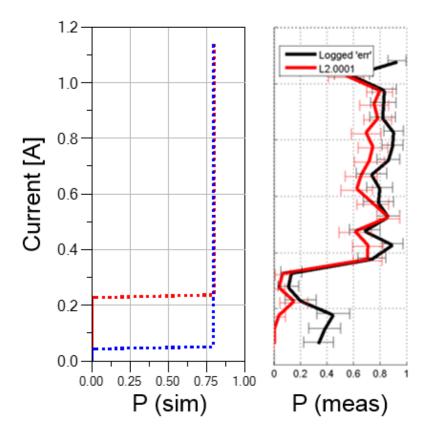

|   | 2.4  | A set of both system-logged and user-observed failure probabilities and confidence intervals as a function of pin current plotted next to the pin IV and virtual ground stability curve. | 109 |

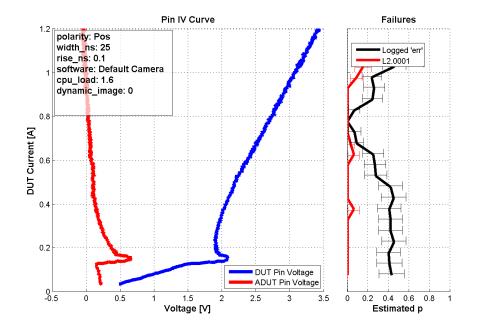

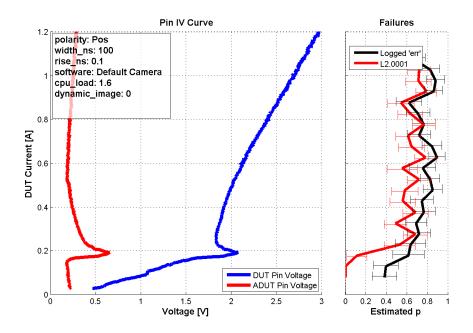

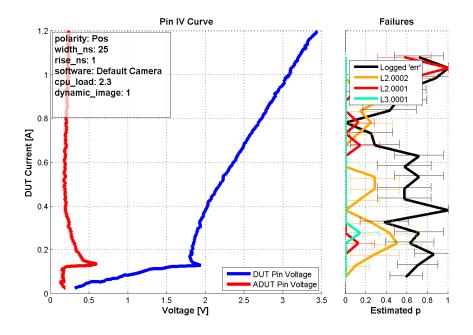

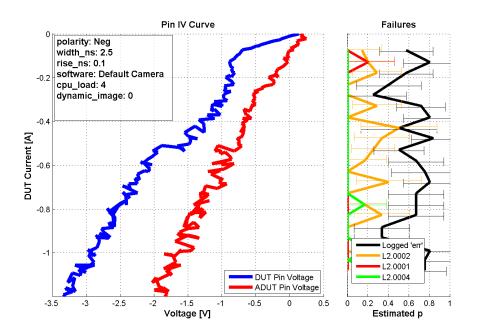

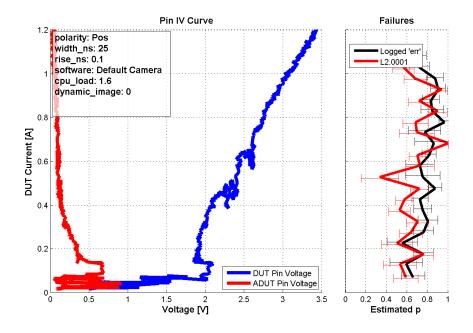

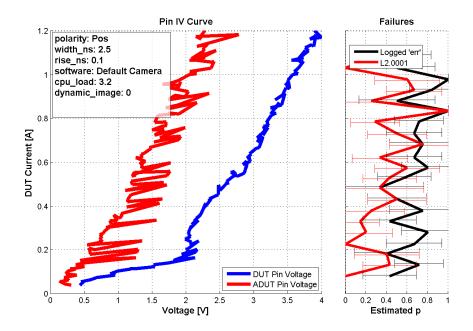

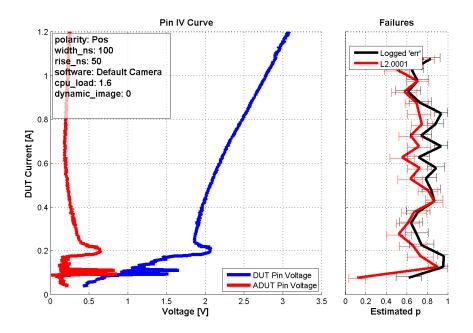

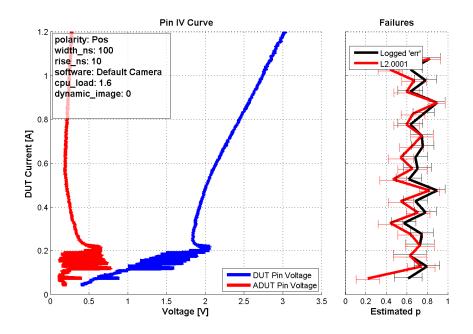

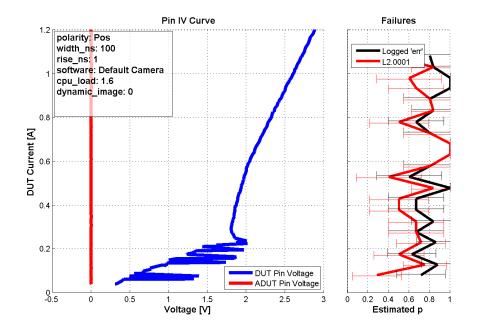

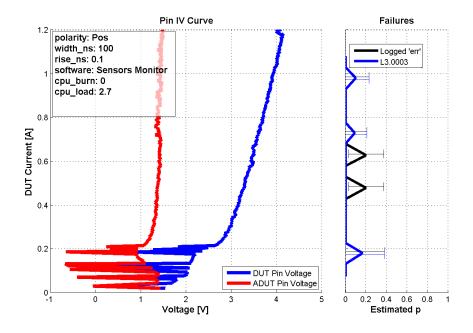

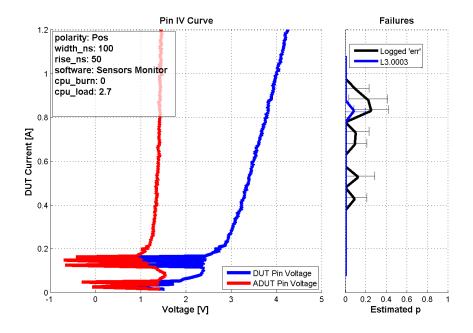

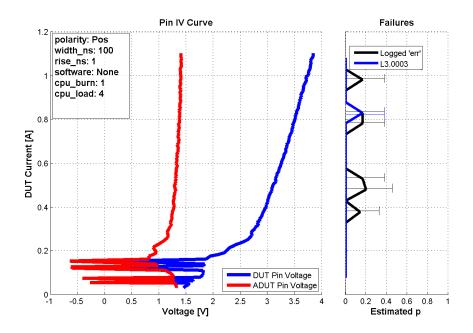

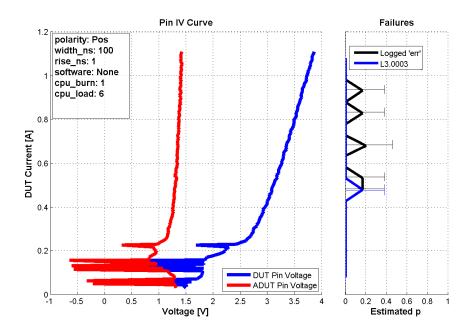

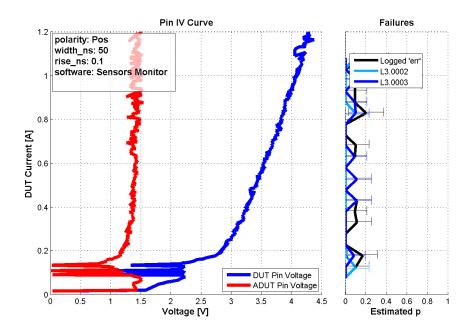

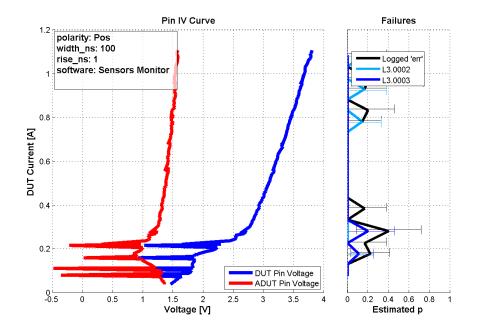

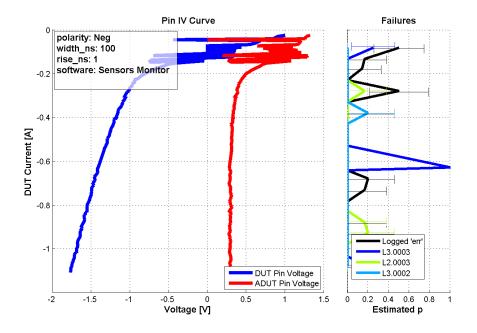

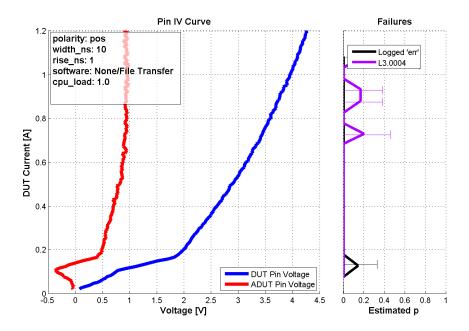

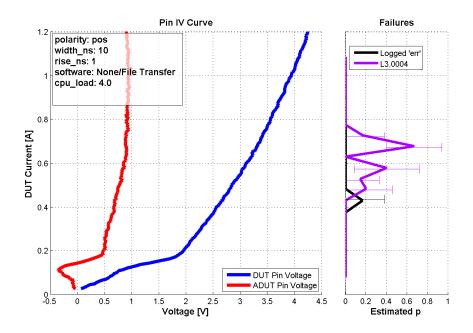

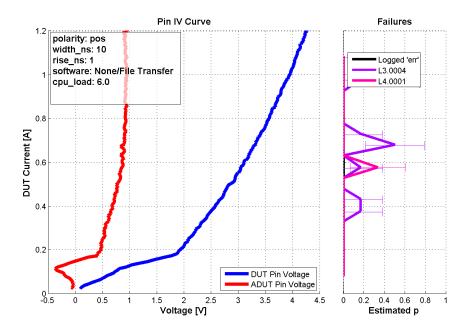

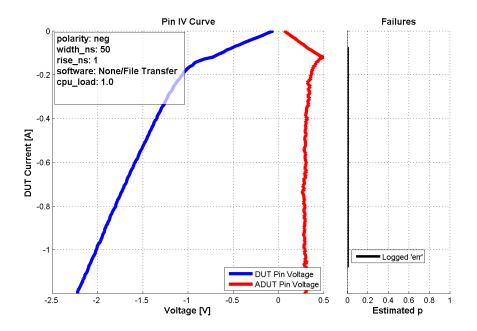

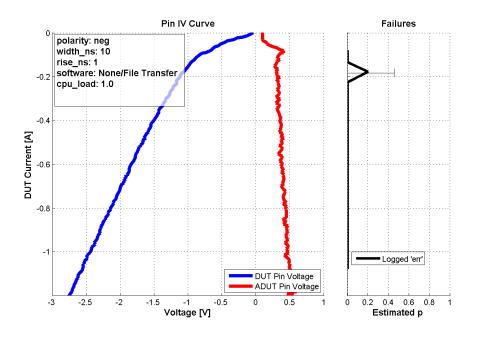

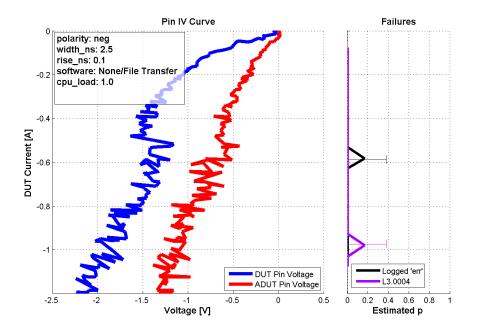

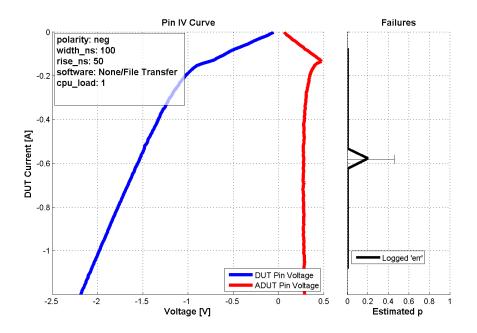

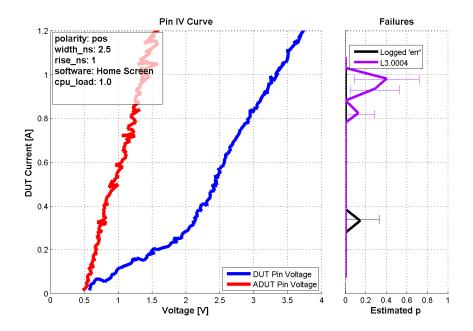

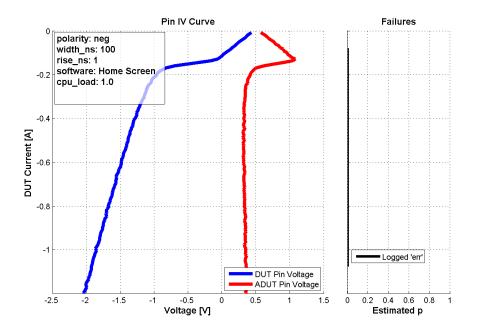

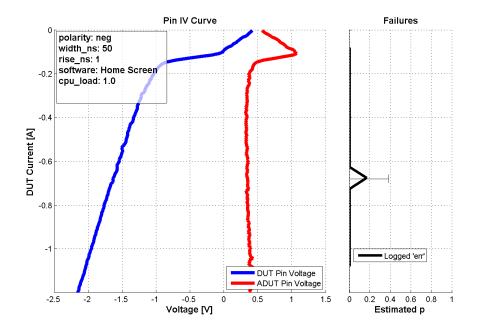

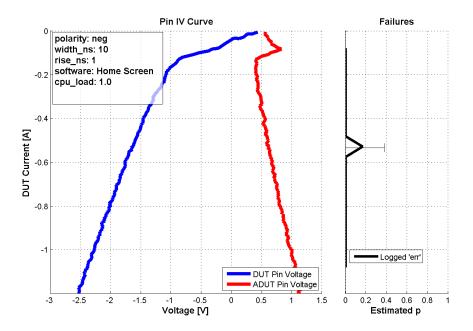

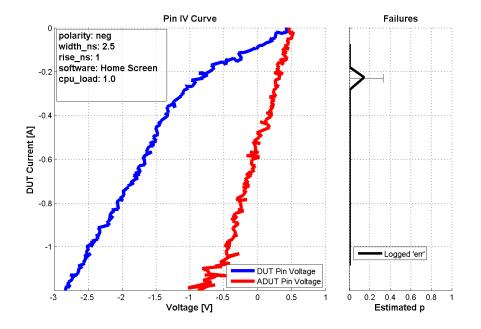

| , | 3.1  | CSI2_DP0 - 75 ns pulse width                                                                                                                                                             |     |

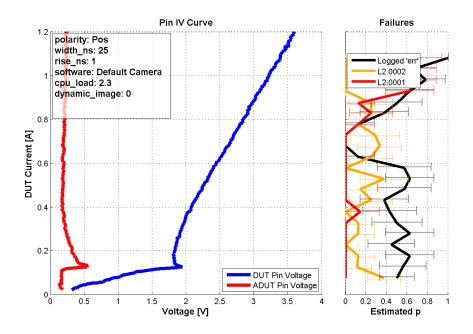

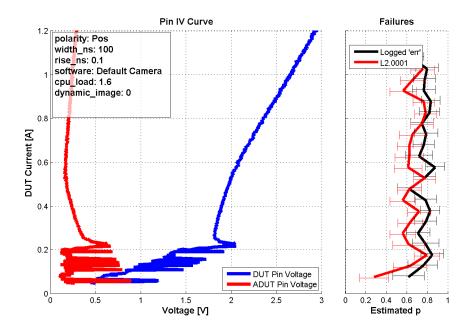

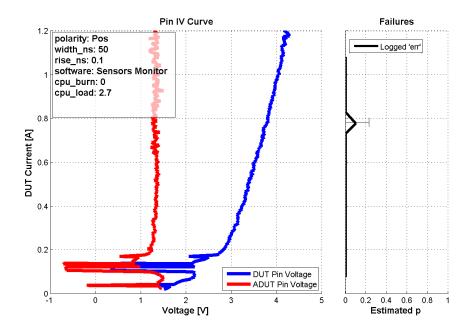

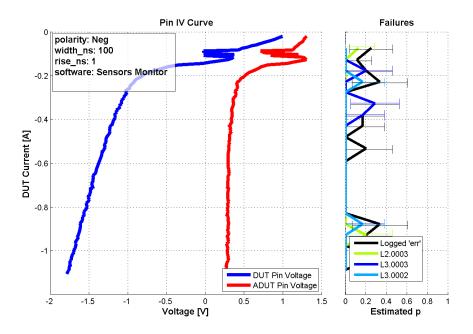

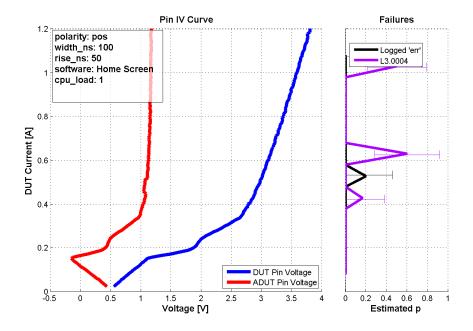

|   | 3.2  | CSI2_DP0 - 50 ns pulse width                                                                                                                                                             |     |

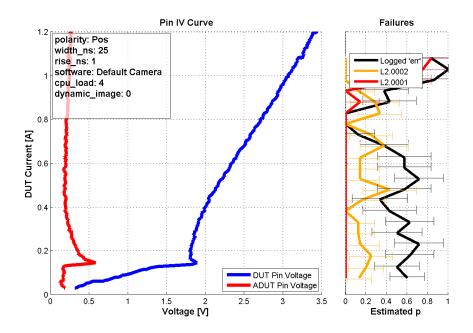

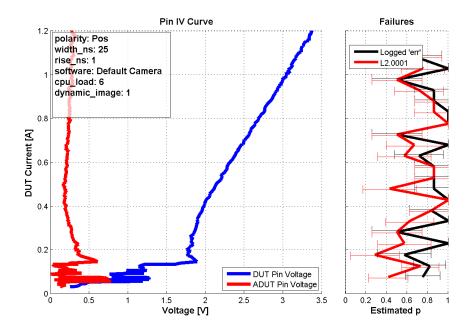

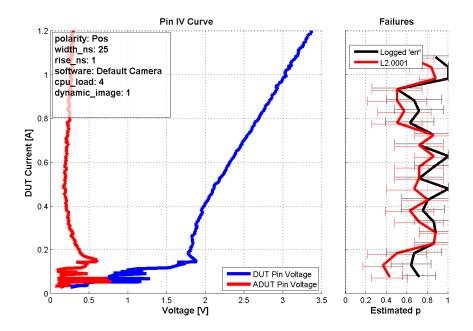

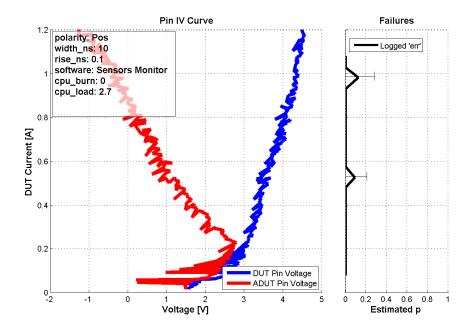

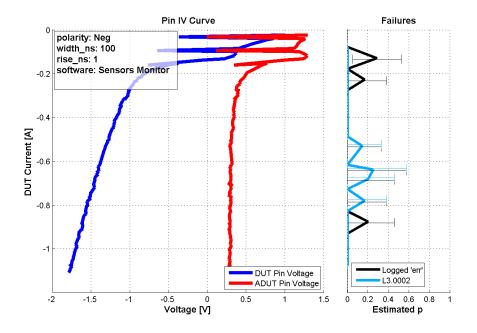

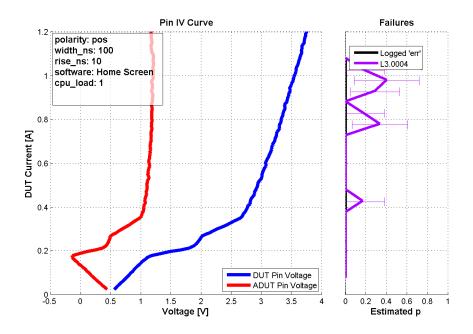

|   | 3.3  | CSI2_DP0 - 25 ns pulse width                                                                                                                                                             |     |

|   | ر. ر |                                                                                                                                                                                          | 114 |

| 3.4  | Two log file entries from before and after the charge-dependent threshold on a CSI2_CLK pin                                    | 114 |

|------|--------------------------------------------------------------------------------------------------------------------------------|-----|

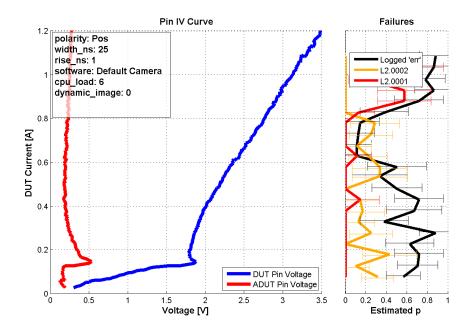

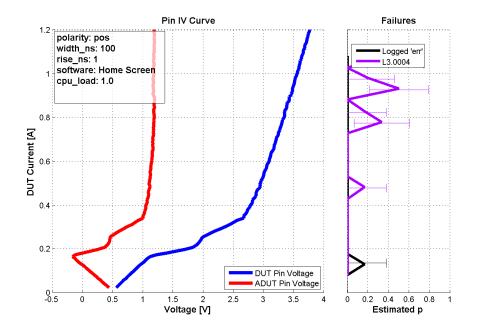

| 3.5  | CSI2_DP0 - 25 ns pulse width                                                                                                   | 115 |

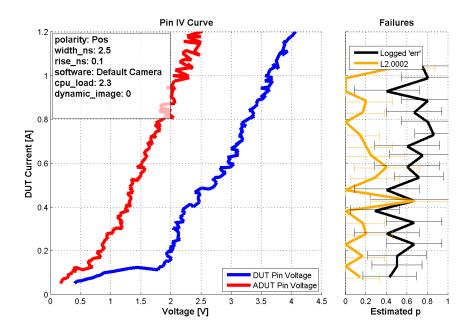

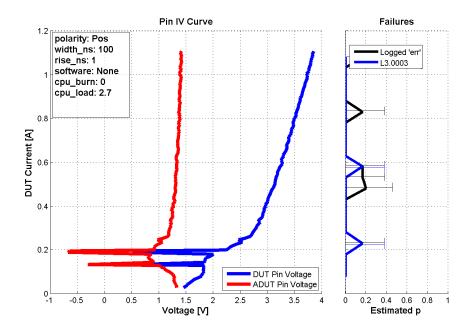

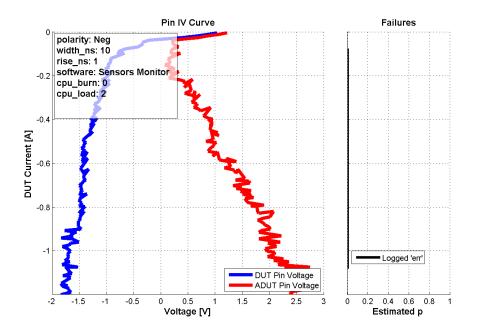

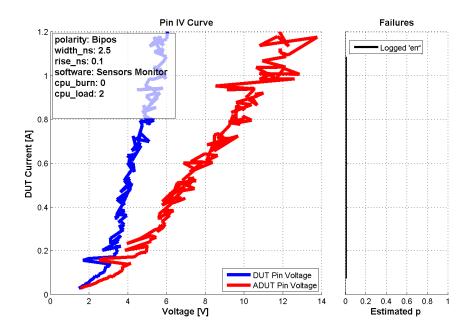

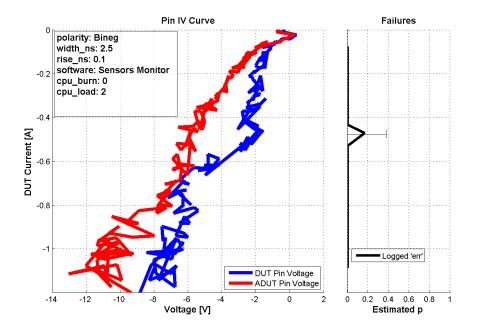

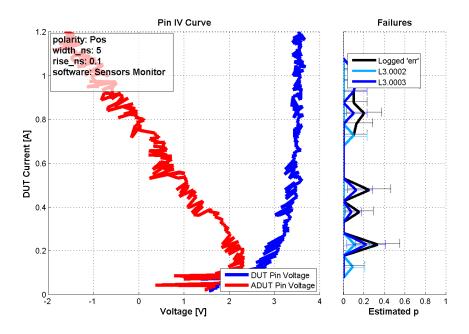

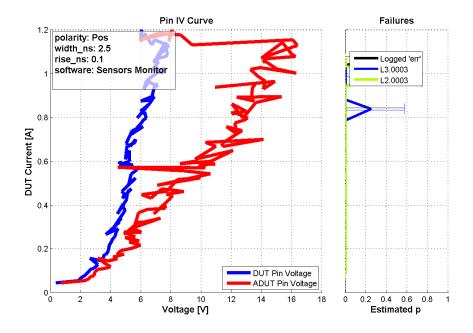

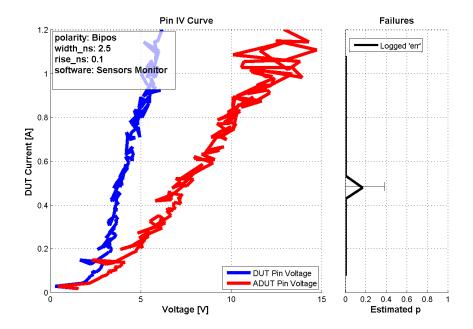

| 3.6  | I2C5_SDA pin test                                                                                                              | 117 |

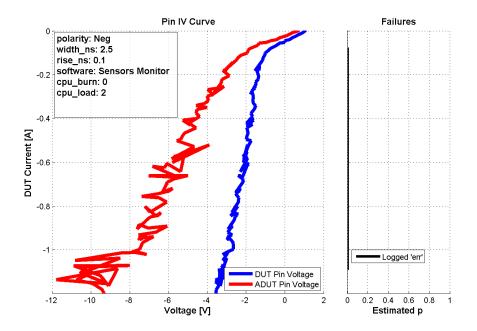

| 3.7  | I2C5_SDA pin test                                                                                                              | 118 |

| 3.8  | I2C5_SDA pin test                                                                                                              | 119 |

| 3.9  | $\label{eq:Kernel-logged} Kernel-logged \ I^2C \ interface \ error \ indicating \ the \ multi-master \ arbitration \ mode \ .$ | 119 |

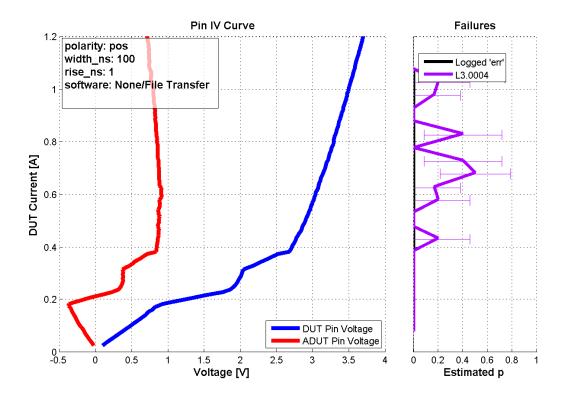

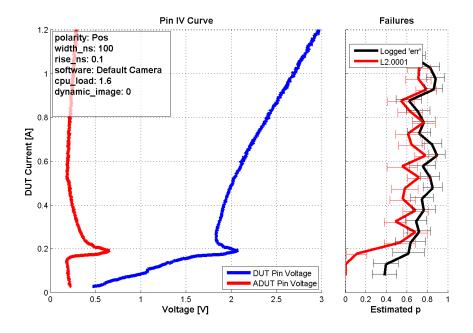

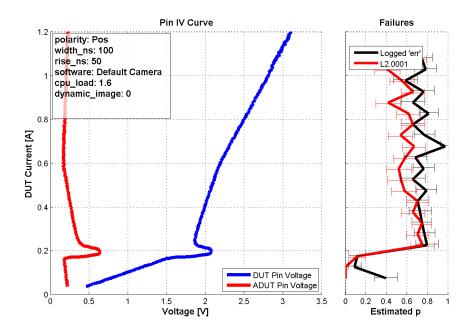

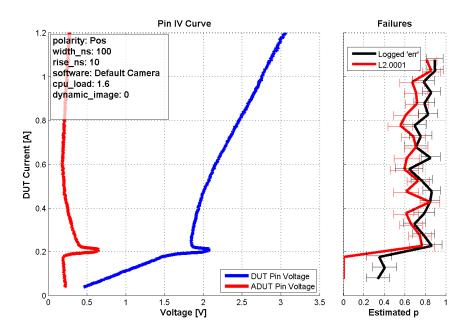

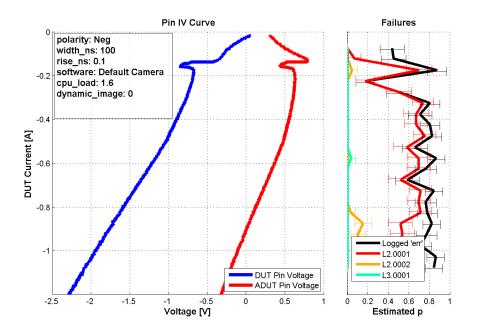

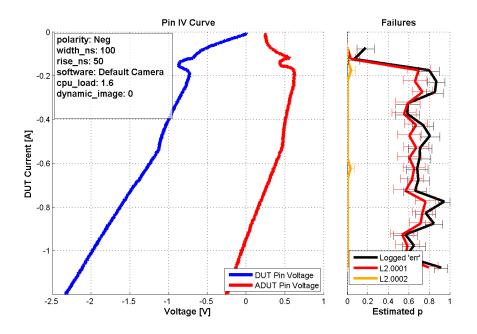

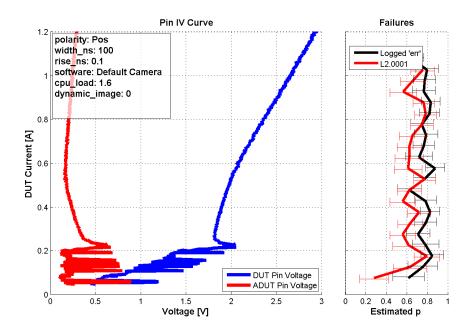

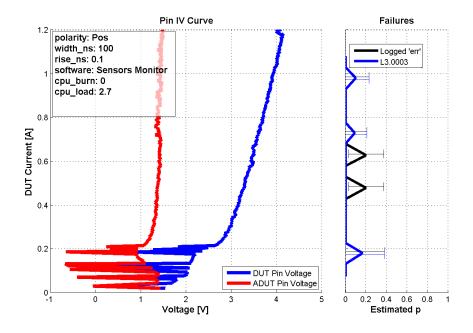

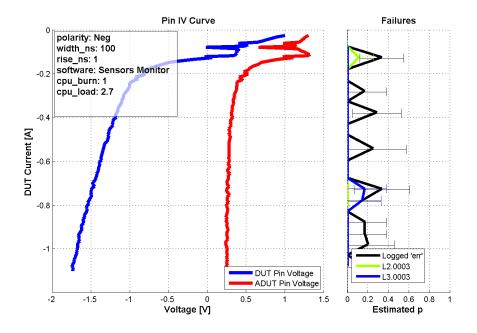

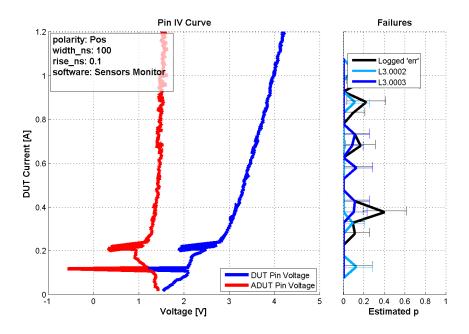

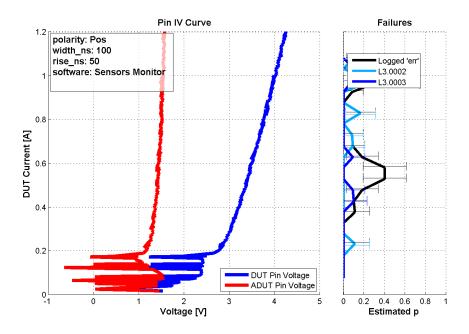

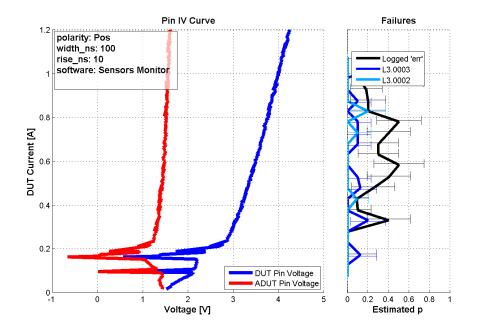

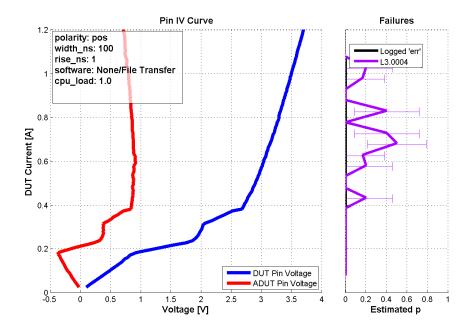

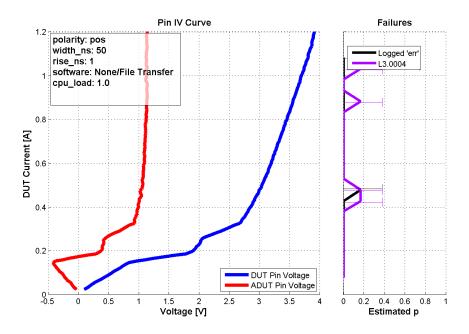

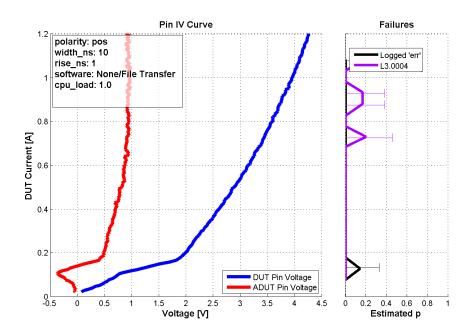

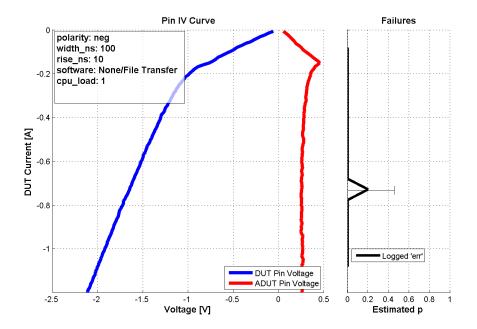

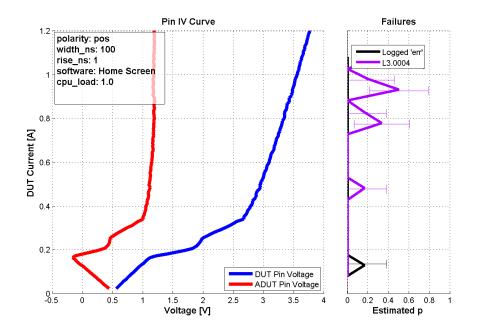

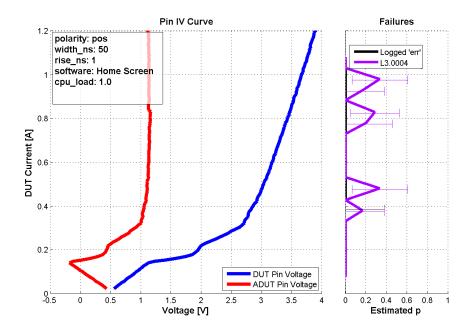

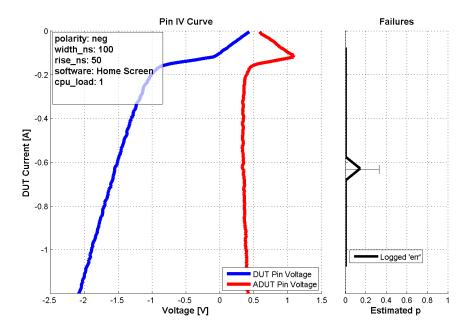

| 3.10 | USB3_RxP - 100 ns pulse width                                                                                                  | 121 |

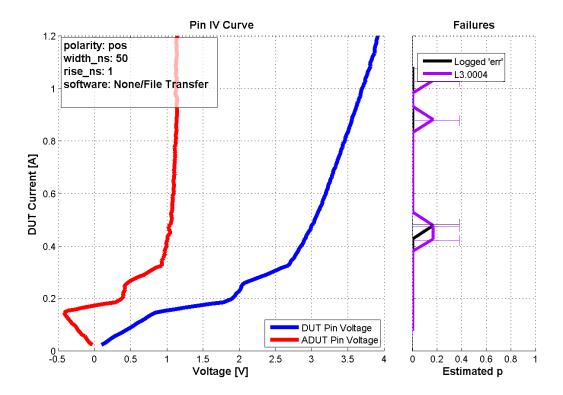

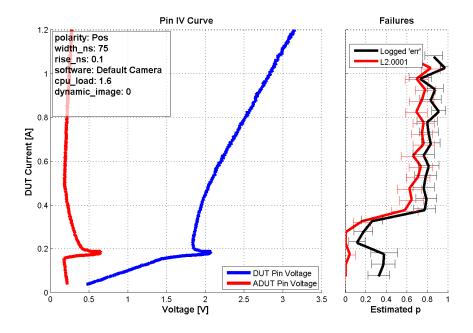

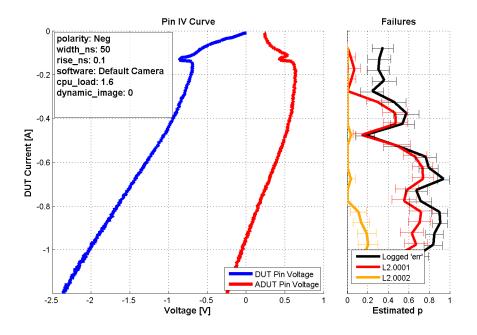

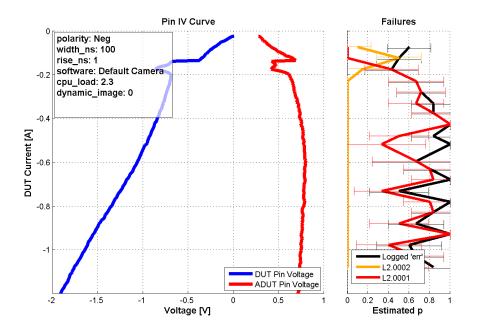

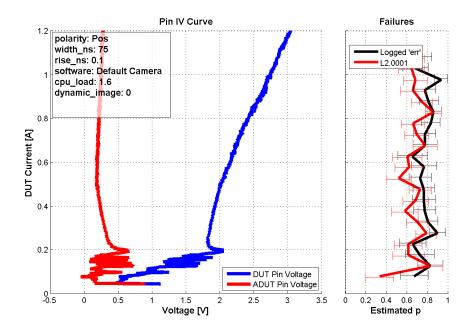

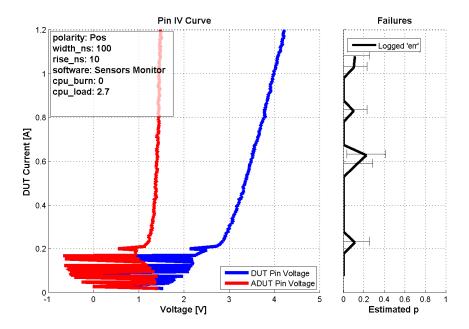

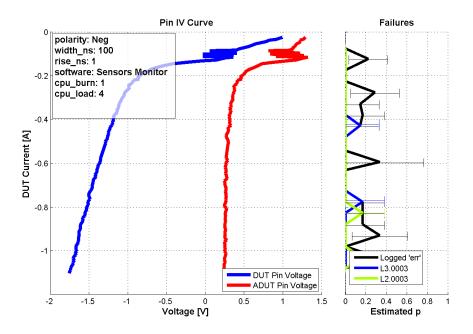

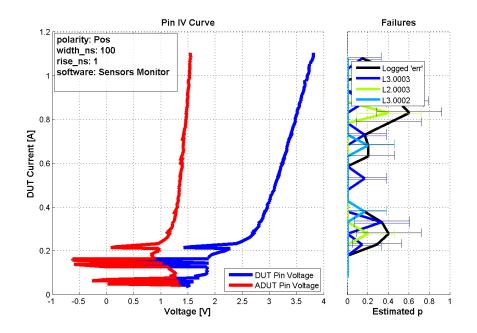

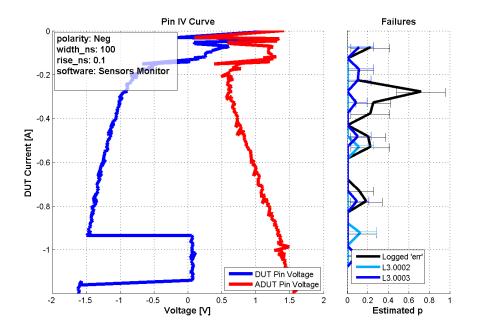

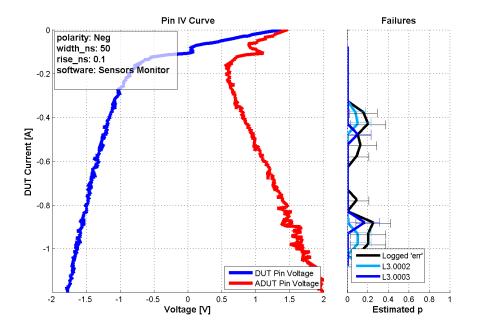

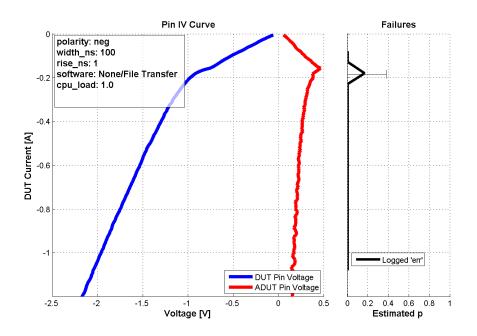

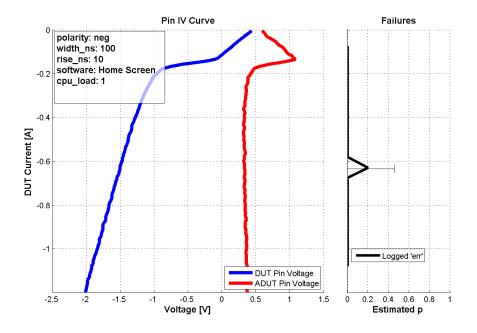

| 3.11 | USB3_RxP - 50 ns pulse width                                                                                                   | 122 |

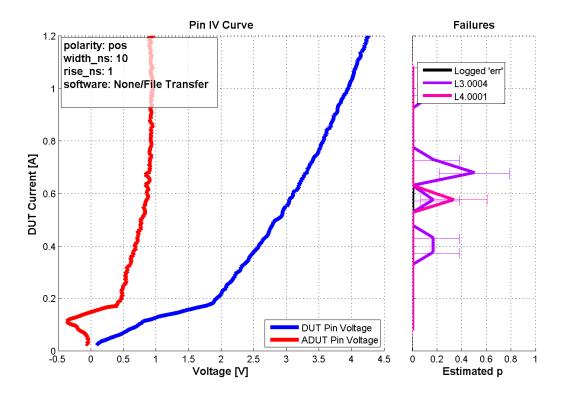

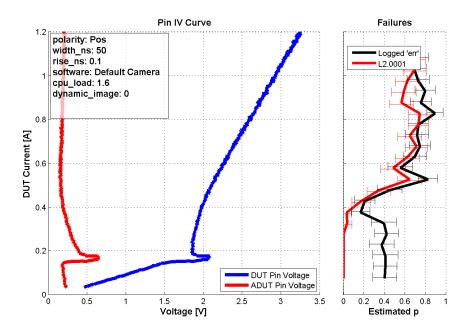

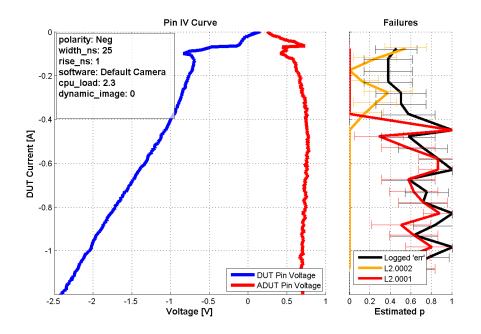

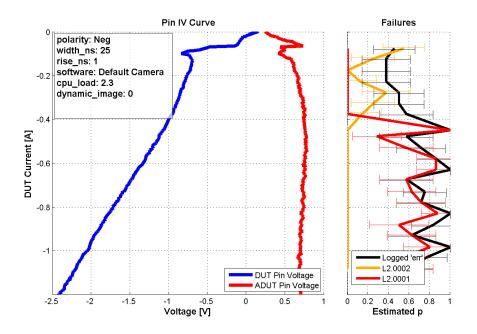

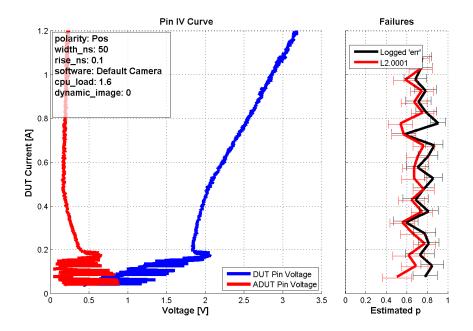

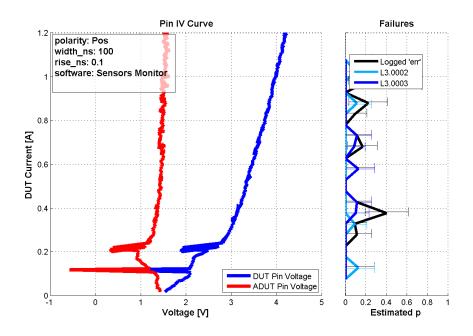

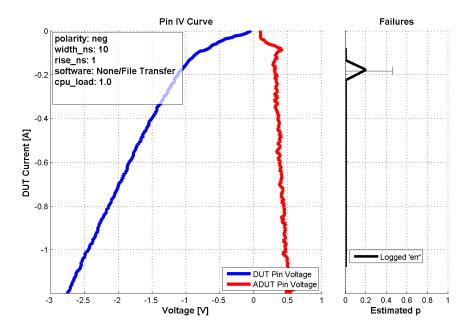

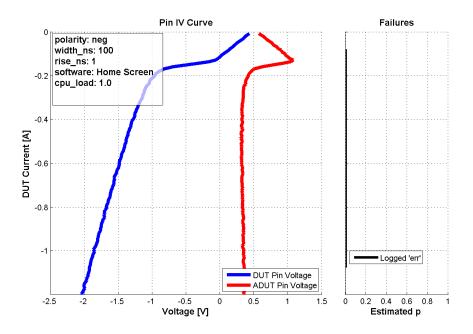

| 3.12 | USB3_RxP - 10 ns pulse width                                                                                                   | 123 |

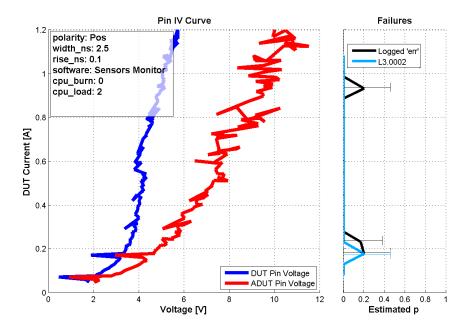

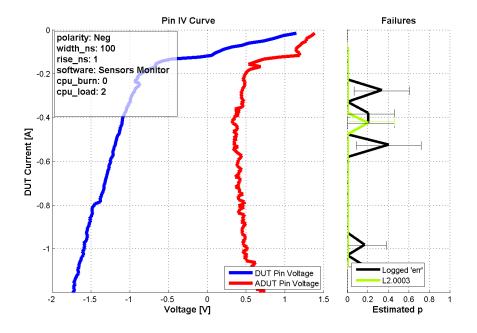

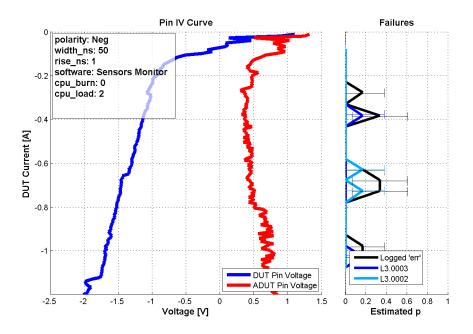

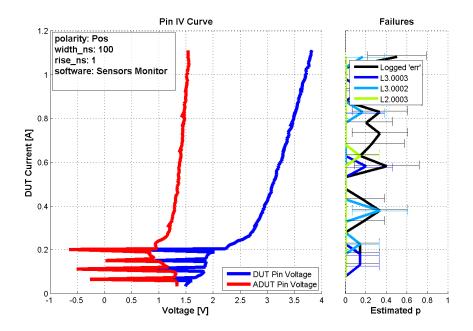

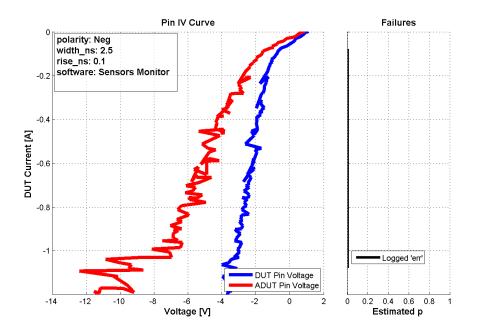

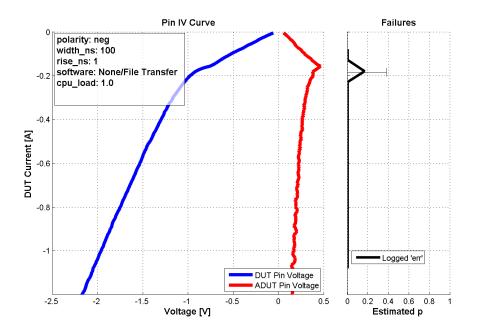

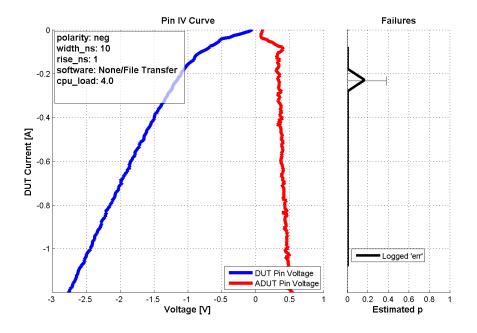

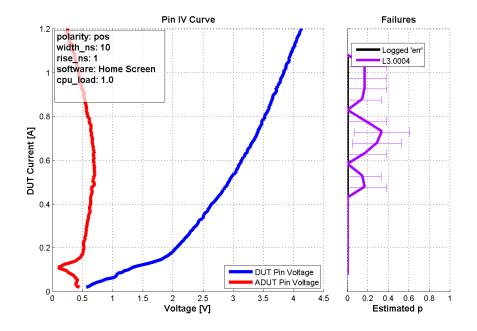

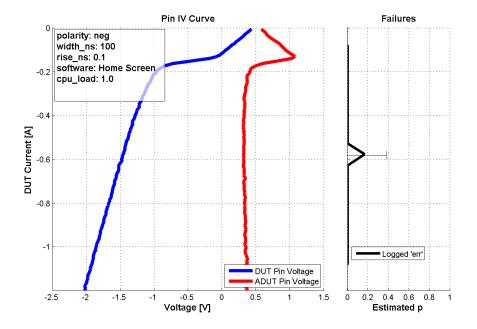

| 3.13 | USB3_RxP - Negative USB injection example                                                                                      | 124 |

| 4.1  | SF-SEED Simulation flow                                                                                                        | 126 |

| SECT | TION                                                                                                                           |     |

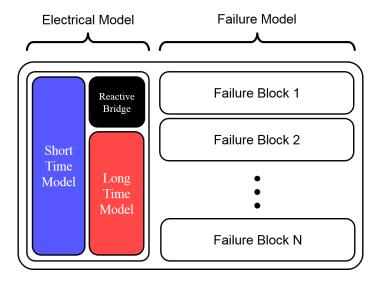

| 4.1  | Pin model overview                                                                                                             | 130 |

| 4.2  | Two and three-terminal electrical model formation                                                                              | 131 |

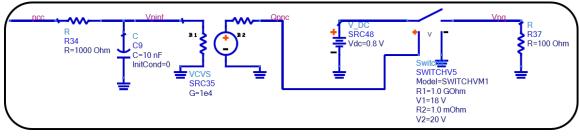

| 4.3  | Example SPICE pin model                                                                                                        | 132 |

| 4.4  | Comparison between three-terminal characterization measurements and simulation of long- and short-time models                  | 133 |

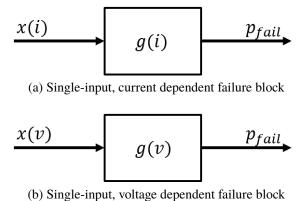

| 4.5  | Failure block forms                                                                                                            | 133 |

| 4.6  | Example failure blocks                                                                                                         | 134 |

| 4.7  | Complete pin model outline                                                                                                     | 135 |

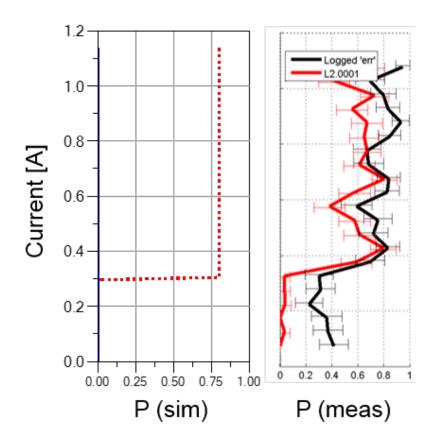

| 4.8  | Measurement and model comparison (positive, 100 ns injection), the blue and red simulated traces indicate L2.0001              | 136 |

| 4.9  | Measurement and model comparison (positive, 75 ns injection), the blue and red simulated traces indicate L2.0001               | 137 |

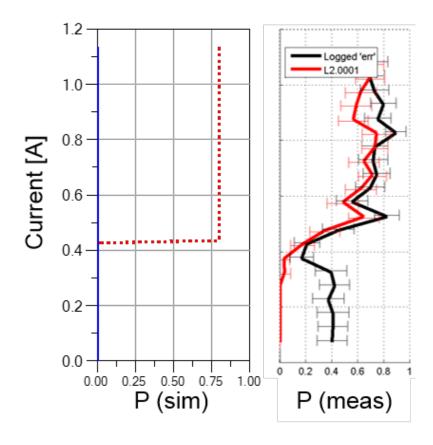

| 4.10 | Measurement and model comparison (positive, 50 ns injection), the blue and red simulated traces indicate L2.0001                                    | 138 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.11 | Measurement and model comparison (positive, 25 ns injection), the blue and red simulated traces indicate L2.0001                                    | 139 |

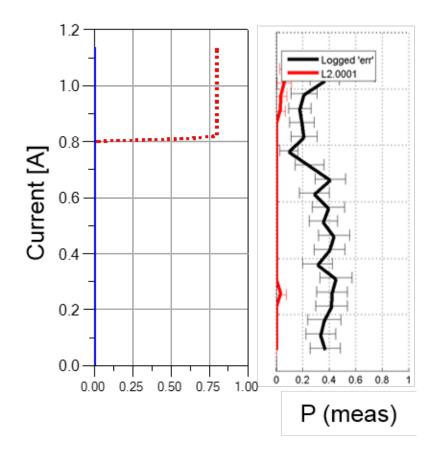

| 4.12 | Measurement and model comparison (negative, 100 ns injection), the blue and red simulated traces indicate L2.0001, the pink trace indicates L2.0002 | 140 |

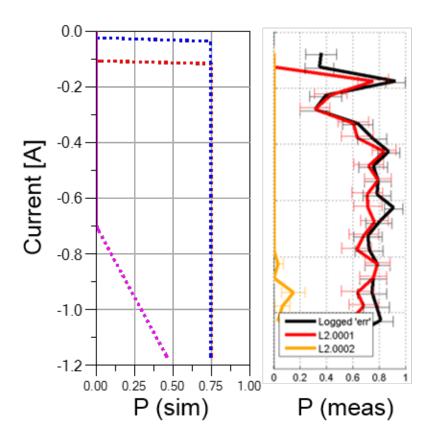

| 4.13 | Measurement and model comparison (negative, 50 ns injection), the blue and red simulated traces indicate L2.0001, the pink trace indicates L2.0002  | 141 |

## LIST OF TABLES

| Table |                                                                         | Page |

|-------|-------------------------------------------------------------------------|------|

| PAPI  | ER I                                                                    |      |

| 2.1   | Impedance of injection probe plus 50 $\Omega$ TLP source at $f = 1$ GHz | 26   |

| PAPI  | ER II                                                                   |      |

| 2.1   | Soft Failure Categorization                                             | 49   |

| PAPI  | ER III                                                                  |      |

| 2.1   | Coupled Inductor Properties                                             | 77   |

| 3.1   | Transformer Parameters for Test PCB                                     | 84   |

| PAPI  | ER IV                                                                   |      |

| 2.1   | Swept Electrical Parameters                                             | 104  |

| 2.2   | Swept Software Parameters                                               | 105  |

| 2.3   | Soft Failure Categorization                                             | 106  |

| 3.1   | Commonly Observed Soft-Failures During Camera Testing                   | 111  |

| 3.2   | Camera Interface Failure Sensitivities                                  | 111  |

| 3.3   | Commonly Observed Soft-Failures During Sensor Interface Testing         | 116  |

| 3.4   | Sensor Interface Failure Sensitivities                                  | 116  |

| 3.5   | Commonly Observed Soft-Failures During USB 3.0 Interface Testing        | 120  |

| 3.6   | USB 3.0 Interface Failure Sensitivities                                 | 120  |

## **SECTION**

#### 1. INTRODUCTION

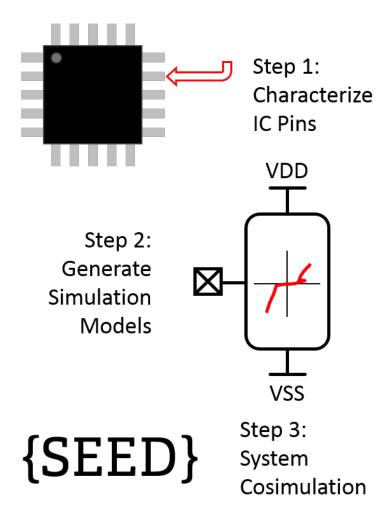

While a general understanding of integrated circuit (IC)-level electrostatic discharge (ESD) has been developed over the last decades, ESD in the scope of whole systems has only relatively recently received similar attention. In 2010 the Industry Council on ESD Target Levels published part one of a white paper [1] which detailed a systematic approach to dealing with system-level ESD, termed System Efficient ESD Design (SEED) which was followed up in 2012 by part two [2]. Since these publications, there have been a number of works which detail implementations of SEED principles on various systems such as [3; 4; 5]. These works have focused on mitigating failures which would lead to device destruction and permanent loss of system functionality, but ESD-induced soft-reliability issues such as data corruption and system upsets are also concerns.

In order to characterize the robustness of a system with respect to soft-failures, a "divide and conquer" approach was developed. This method begins by dividing a system into discrete subsystems such as communication interfaces, IO interfaces, and other peripherals. Once the subsystems have been identified (divide) then each is subjected to various stress pulses to determine their independent robustness levels (conquer). This was first implemented on the scope of a complete system in [6] before being applied directly to the application processor of a similar system in [7]. By splitting the DUT IC into logical pieces and characterizing each interface, models can be generated which are capable of describing the response of the system to a given stimulus on each pin. While similar techniques have been performed for hard failure analysis, this work closes the gap between

the hard- and soft-failure worlds by presenting a methodology whereby soft-failures can be similarly modelled. With these models in hand, system-level simulation can then identify problem areas where targeted fixes can be applied in either hardware or software to counter any potential weaknesses.

In this work the black-box characterization of a highly integrated circuit is presented, as well as both integral and closely related work. In Sections 2-3 and Papers 1-3, several ancillary measurement techniques are presented which describe various aspects of the system setup. Paper 4 contains the characterization methodology and supporting information about the IC under test. Finally, Section 4 integrates the results from Paper 4 into the modelling techniques from Sections 2-3 by proposing a circuit simulation model which is capable of reflecting various failures both hard and soft.

#### 2. PIECEWISE LINEAR IV CURVES

#### 2.1. INTRODUCTION

A key component of SEED is the ability to express measured IV behaviors inside simulation environments such as SPICE. These IV curves are, in general, nonlinear and can often contain apparent negative resistances associated with the phenomenon known as snapback. In reality, snapback is generally not a true negative resistance but traces an IV curve that sees a sudden increase in current and a decrease in voltage. In order to model these curves it is desirable to implement them as a piecewise function of current. Similar piecewise models constructed in VHDL-AMS [8] as well as Verilog-A [9] have been proposed by for both diode and snapback behaviors. Outside of the context of ESD, a purely SPICE-based approach to piecewise linear IV modeling was proposed in [10]. Originally the SPICE-technique was used to implement the real-world negative resistive behaviors of devices such as unijunction transistors and tunnel diodes in a simulation environment for educational purposes. Unfortunately the method relies on the now-deprecated ability of SPICE to accept negative values for the saturation current of a diode. While such a value is not physical, it should be mathematically acceptable by most solution engines. This section serves as an overview of an implementation of the piecewise linear SPICE model in Agilent/Keysight ADS.

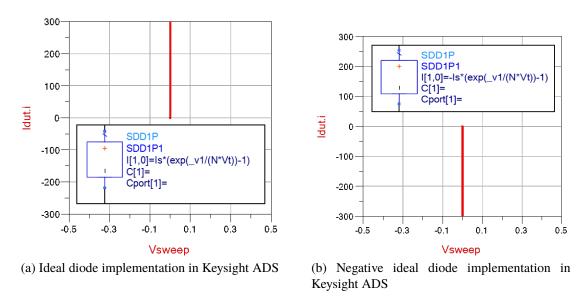

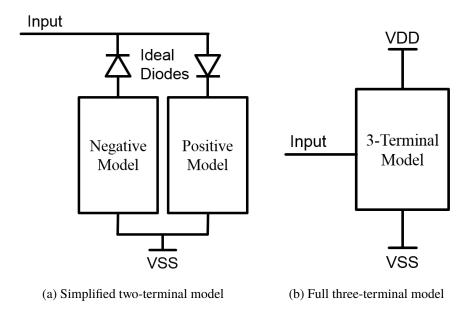

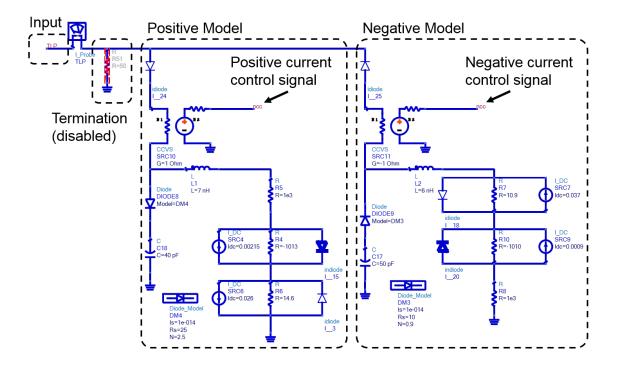

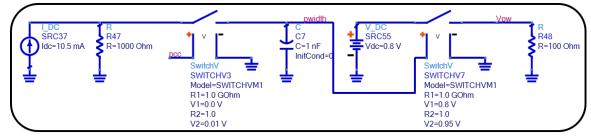

**2.1.1.** Circuit Building Blocks. Implementation of the required circuit elements in ADS is similar to the original implementation. Although, like SPICE, ADS does not accept negative values for the saturation current of a diode, the environment does allow for both implicitly and explicitly defined IV relationships through the use of a 1-port symbolically defined device (SDD1P) [11]. By using these blocks to implement the fundamental diode

equation, sanity checks on the sign of Is are bypassed (Figure 2.1). The exponential relationship between the block current and voltage mimics that of the ideal diode equation as only a callback to the original implementation. Any sufficiently strong exponential relationship could also be used.

Figure 2.1. Ideal and negative ideal diode implementations

Having implemented the positive and negative ideal diodes with equation blocks, the fundamental unit cells can also be created. These unit cells operate on the principle that while the total current is less than Ibreak the cell is shorted. However, once the current exceeds Ibreak, the cell resistance is switched in, and adds to the total resistance of the string of cells. This switching action is achieved by the very small turn-on voltage of the ideal diodes. When the current entering the cell is less than the break current, the remainder of the current (Ibreak âĂŞ I) must then flow through the cell resistance until the cell diode is forward biased. Once the cell diode is forward biased (which occurs at very low voltages due to the near-ideal turn-on behavior), a balance is struck between the current required to keep the ideal diode in conduction, and the current through the cell resistance. The result

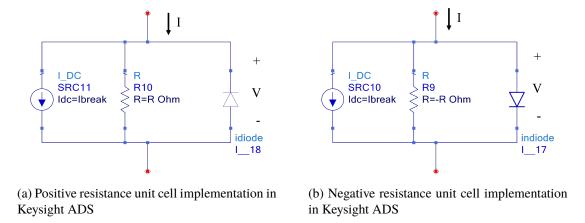

is a vanishingly small positive or negative cell voltage. In essence, a short circuit. The implemented positive and negative cells are shown in Figure 2.2.

Figure 2.2. Positive and negative resistance unit cell implementations

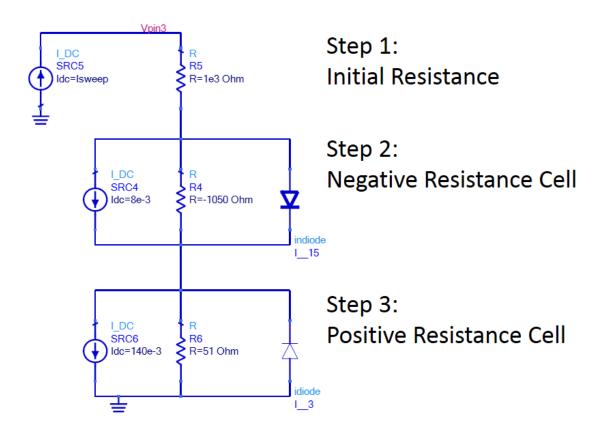

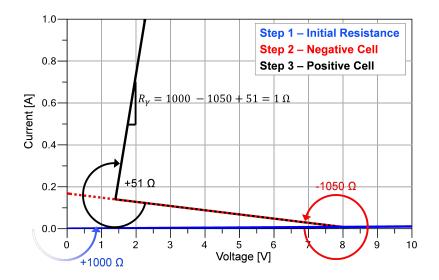

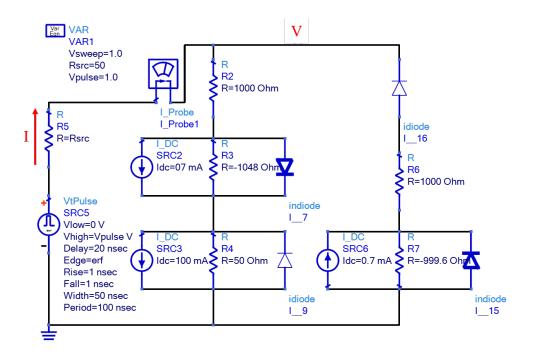

Finally, by cascading these unit cells, arbitrary IV curves can be realized by the network. In Figure 2.3, a DC current source is swept to drive the attached model. The results of the DC simulation are shown in Figure 2.4 by plotting the resultant voltage against the swept current source value.

2.1.2. Simulation Using Piecewise Linear IV Models. Although it is trivial to achieve convergence for these circuits in a DC simulation, a transient solution is more difficult to achieve. After extensive study and experimentation, the primary issue seems to be that if the model, even momentarily, has an apparent resistance equal in magnitude but opposite in sign to the source resistance, then the internal current and voltage derivatives become too high. These rapidly changing values trigger a convergence failure as the internal timestep attempts to decrease below some absolute minimum limit in an attempt to track the current and voltage values. For this reason, the piecewise linear SPICE modeling method is limited to curves which do not exhibit negative resistances with a magnitude larger than the driving source resistance. At first one might believe that the model would only be

Figure 2.3. DC current swept model

incapable of expressing instantaneous resistances of exactly *Rsrc*. However, because the IV curve is not strictly piecewise and is instead a continuous function, even at the corners, in order to express a resistance which is less than *Rsrc*, the model must pass through *Rsrc* at one or more corners resulting in instability. Finally, because the unit cells only function for positive currents, the model is invalid on the entire left hand side of the IV plane, as the only functioning portion of the model is the initial resistance. In order to construct a model which can represent both negative and positive behaviors of a device, two models must be used, each isolated by the previously developed ideal diodes such that one model corresponds to positive current flow and the other to negative. (Figure 2.5).

Figure 2.4. DC current swept IV curve

Figure 2.5. Regions of stability and validity for the piecewise linear IV SPICE model

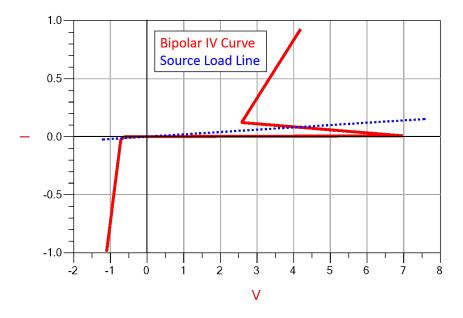

After understanding the constraints on this technique, the device can then be modeled and run through a batched transient simulation to mimic the measurement performed by a TLP system. The positive half of a device IV curve is represented by a chain of an initial resistance, a negative resistance block, and a positive resistance block to create a snapback characteristic. The negative behavior is represented by a second chain of blocks with only an initial resistance and one negative resistance to create a diode-like behavior. An ideal diode is also included in the negative branch to isolate it from positive excitations. This ideal diode is not present in the positive characteristic branch to reduce the overall component count. The omission of this diode places the initial resistance of the positive branch in parallel with the overall negative behavioral branch which has only a negligible effect. The circuit shown in Figure 2.6 was excited by a batch of 77 individual transient simulations of 100 ns duration. Across these simulations, the source voltage *Vpulse* was swept from -50 V to 50 V. The resultant transient voltage and current traces were then window-averaged by the simulator in the same way that a TLP system would in order to generate the resultant IV curve in Figure 2.7.

**2.1.3. Conclusion.** In this section, an easily-implementable method for implementing the piecewise linear IV behaviours commonly used to describe components in the ESD regime is presented. The method is implemented in a SPICE-like engine, the general limitations are outlined, and a bidirectional transient simulation of a device is demonstrated.

Figure 2.6. Transient simulation of a snapback-positive, diode-negative device

Figure 2.7. IV curve resulting from a batched transient simulation

## 3. THREE-TERMINAL PIN MODELING

## 3.1. INTRODUCTION

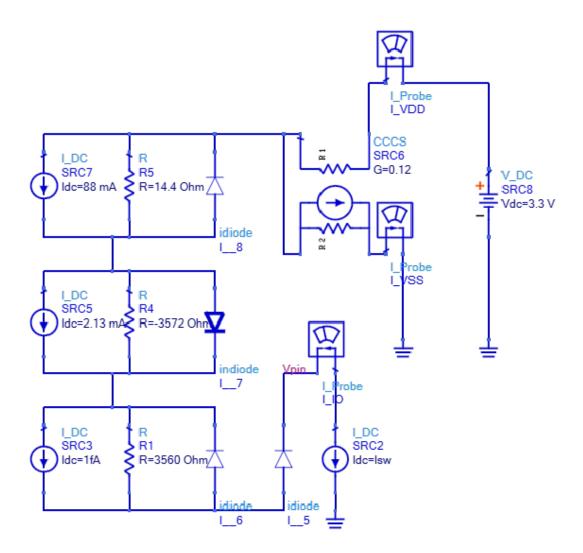

While the TLP is an excellent tool for measuring the IV relationship between two pins, it should be noted that the use of a two-pin characterization system to better understand system-level ESD events is a fundamentally flawed approach Figure 3.1. By its very nature, a system-level ESD event takes place in the context of a system which not only includes the victim IC, but also everything which it is connected to. Common on-chip protection schemes frequently connect the IO to both VSS and VDD [12] and [13]. Furthermore, the behavior of some protection schemes is a function of the voltage between VDD and VSS. Finally, the presence of the off-chip low impedance decoupling network between VDD and VSS such as typically found in systems has also been shown to have a strong effect on the performance of the on-chip ESD protection scheme [14]. For these reasons, the assertion is made that using a TLP alone to perform a two-pin characterization of IO pins should be seen as unrealistic.

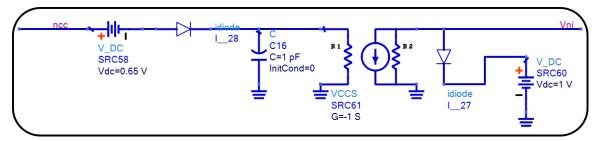

Figure 3.1. Using a TLP to measure an IV characteristic is a two-terminal technique which ignores the connections made to other IC pins

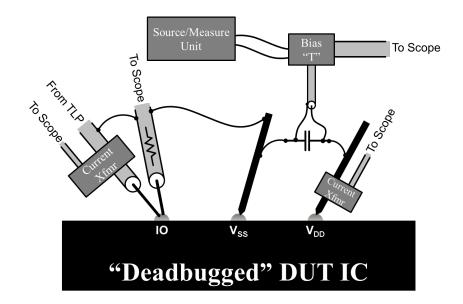

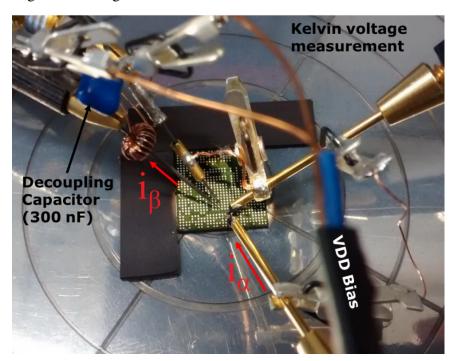

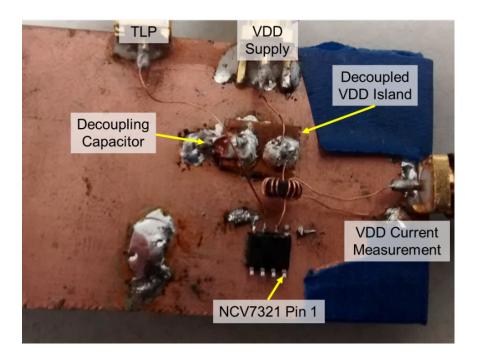

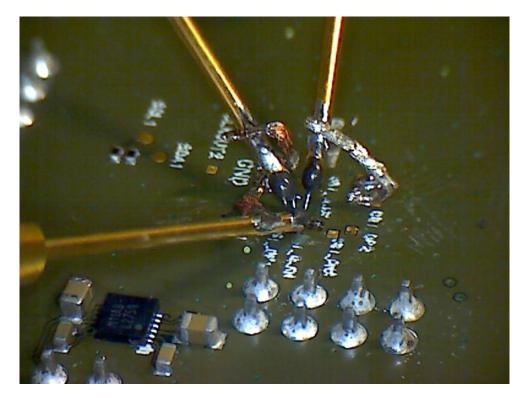

3.1.1. Measuring Pins in the Context of a System. In order to characterize the IO pin of an IC in a more realistic system-level case, the IC is instead placed into a simple circuit which is intended to more closely mimic a realistic system. Such a circuit should include a voltage source to provide a bias between the associated VDD and VSS of the IO under test, adequate decoupling capacitance on the same voltage source, and a second current transformer to measure the current leaving the IC VDD network during IO injection (Figure 3.2). In this way, the IO pin is treated as a three terminal model which includes connections to both VDD and VSS. This measurement technique has been implemented both on a waver probing station with needle probes (Figure 3.3) and by placing the IC in a "deadbug" configuration and forming the circuit by "manhattan construction" [15] (Figure 3.4). The primary application to this body of work is the ability of the technique to predict the amount of current which is shunted to the PCB power distribution network (PDN) during an ESD event. Such a prediction can potentially be used by system designers to ensure the stability of the PDN, or in soft-failure characterization to provide another parameter with which to correlate observed failures during strikes on IO pins.

The validity of this measurement technique is based on the assumption that the system VDD is held relatively stable during the event. This assumption is confirmed by measuring the disturbance on VDD in addition to the IV characteristic of the pin. For cases outside of this assumption, an even more complex nonlinear model must be measured and constructed to account for the effects of VDD perturbations on the IO clamp behavior. This case is considered to be overly complex and is left as potential future work.

**3.1.2. Benefits of the Three-Terminal Model.** The three terminal model provides two potential benefits. The first is accurately understanding the current distribution inside an IO cell under development. Application of the measurement methodology can determine whether the intended device triggers during an event or whether alternate, potentially

Figure 3.2. Diagram of the three-terminal IO measurement method

Figure 3.3. Three-terminal measurement of an IC IO pin on a wafer-probe station

Figure 3.4. Three-terminal measurement of an IC IO pin in deadbug configuration

undersized paths become energized. The second potential benefit is the understanding of the amount of current shunted to the PCB-level PDN during a system-level ESD event. Work on the identification of soft-failures has shown that some errors are not caused directly by a current injected into an IO pin, but instead the resultant disturbance on the power distribution network. During SEED-style simulations, if the amount of current diverted to the voltage supply of the IC is known then such PDN-induced failures can be better addressed.

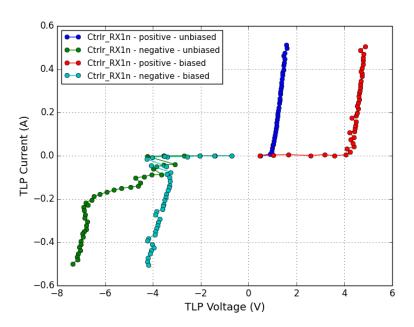

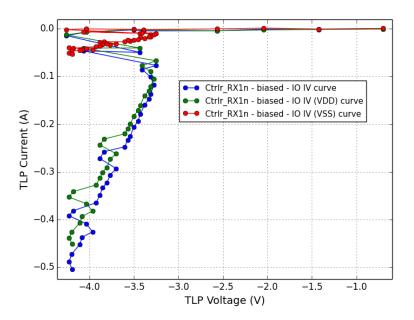

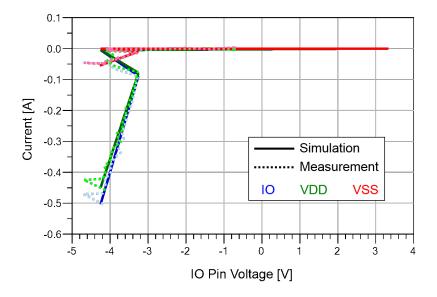

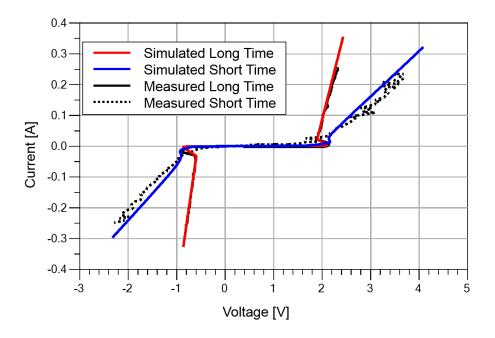

In the first example let us consider the IV curves (taken only to 0.5 A) shown in Figure 3.5. These curves were extracted using the deadbug measurement setup in Figure 3.4. In the positive regime, the device appears to be a simple diode to VDD. By measuring the voltage of the IO pin in both cases with respect to the VSS pins, a clear shift of approximately 3.3 V is visible in the diode characteristic. In contrast, the negative regime is ambiguous. Both curves seem to trigger at the same point, but the slope of the curve above -200 mA

shows a clear difference in behaviors. To investigate this phenomenon further, it is helpful to look at the transient waveforms of the IO pin current and the current leaving VDD.

Figure 3.5. Measured IV curve of a high-speed USB 3.0 differential pin

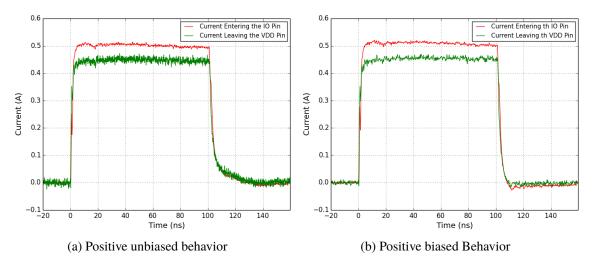

Figure 3.6 and Figure 3.7 show the transient curves measured at the 0.5 A points of the biased and unbiased positive and negative pin behaviors of an example device. In both cases, it is easy to see the similarity in magnitude as well as in the rising edges of the current waveforms between the IO and VDD currents, strongly indicating that both positive- and nevative-going current paths are from IO to VDD.

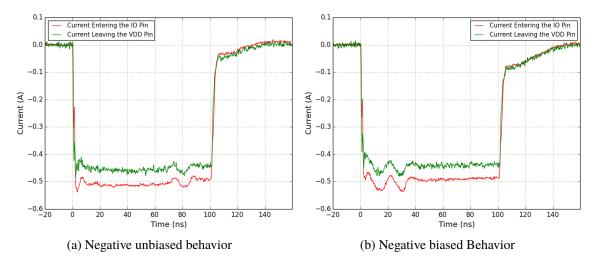

By observing these current waveforms we can see that (for the negative case) nearly all of the current which leaves the IO pin due to a negative injection, is sourced by the IC power distribution network. In reality there is a very small measured difference between the currents. By subtraction, the VSS current can then be calculated, and the IO IV curve can subsequently be visualized three different ways. At the top level, the IO current is plotted

Figure 3.6. A snapshot of a positive transient current waveform pair

Figure 3.7. A snapshot of a negative transient current waveform pair

against the IO voltage. The second two cases plot the IO pin voltage together with the VDD and VSS currents. In this way, the current split inside the IO cell is easily visualized. This is shown in Figure 3.8. By further examining the measurement, it is found that, for this device, the ratio of the current between VDD and VSS is approximately 8.5. This

radio indicates that in spite of the primary connection being to VDD, there is also a small connection to VSS. The generated model can now reflect this by shunting some fraction of the injected current to VSS. An example model is shown in Figure 3.9 and the comparison to the measured IV curve is shown in Figure 3.10.

Figure 3.8. Split IO IV curves showing currents to VDD and VSS

**3.1.3. Conclusion.** Using the presented three-terminal measurements and modeling technique, behaviors of the IC IO pin can be extracted which include connections to VDD as well as VSS. Models designed from these measurements can now include this connection information without any input from the IC manufacturer. Such a model, when used in an accurate SEED simulation, is now capable of affecting the current disturbance of the system VDD network.

Figure 3.9. Piecewise linear three-terminal IO cell model

Figure 3.10. Measurement and model comparison

# **PAPER**

# I. POWERED SYSTEM-LEVEL CONDUCTIVE TLP PROBING METHOD FOR ESD/EMI HARD FAIL AND SOFT FAIL THRESHOLD EVALUATION

Thomas Schwingshackl, Benjamin Orr, Joost Willemen, Werner Simbürger, Harald Gossner, Wolfgang Bösch, and David Pommerenke

# **ABSTRACT**

In this paper an advanced system-level TLP probing technique is presented to evaluate the ESD and EMI performance of a powered system applicable to high speed interfaces. It allows to detect hardware and software fail thresholds to assess the performance of an ESD/EMI protection solution. The method is demonstrated on a Intel mobile phone reference platform.

#### 1. INTRODUCTION

In recent years, system level ESD has become a major focus in the area of ESD testing. At ESD pulse injection levels far below the hardware failure threshold soft-failures can occur. Those soft-failures can cause the shutdown, reboot or hang-up of application software or the whole system. Detecting soft-failure thresholds and investigating their root causes requires the ability to apply ESD pulses into the running system. Normally, system level ESD tests are carried out with a IEC 61000-4-2 ESD generator. In the last couple of years system level testing using Transmission Line Pulse (TLP) generators has become an alternative method for trouble shooting of system level ESD fails [1].

Conductive TLP pulse injection has the benefit that the amplitude of the injected disturbance can be accurately monitored and therefore provides quantitative information of the disturbance levels that can be tolerated or provoke soft and hard fails. When using conductive TLP injection loading of e.g. high-speed data lines by the injection probes and cabling parasitics have to be avoided. The challenge is to connect the DUT to the pulse source through some sort of barrier that isolates the pulse source from the DUT, but still allows the pulse to be delivered to the system. Previously, resistors and capacitors have been used in conductive injection systems to obtain the required isolation. These probes work by placing a relatively high impedance element into a transmission line in order to increase the impedance seen looking in to the TLP system. This impedance effectively isolates the net from the pulse source, but must remain small enough to inject the pulse from the TLP source. In this paper, the authors describe an injection system consisting of ultra-low capacitance bidirectional transient voltage suppressor (TVS) diodes embedded in coaxial injection probes as an alternative to the resistive and capacitive probes.

# 2. CONDUCTIVE TLP INJECTION CONFIGURATIONS

### 2.1. DEVICE LEVEL TESTING

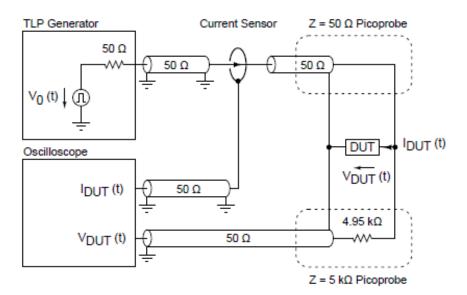

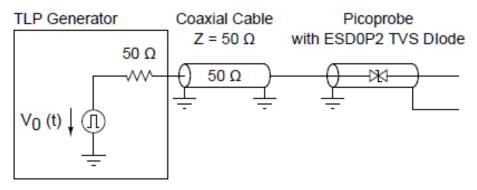

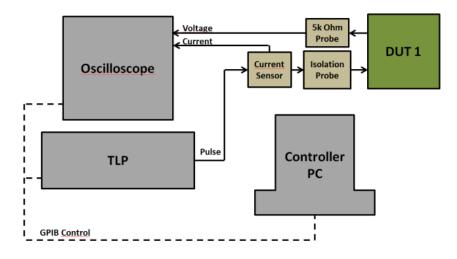

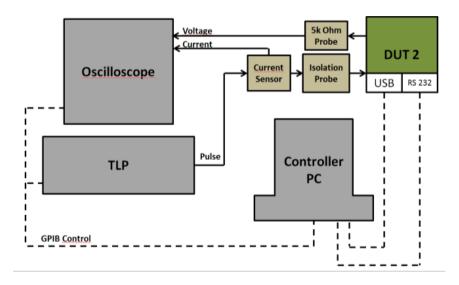

A common method for measuring device level TLP characteristics uses the Kelvin configuration. Figure 2.1 shows a TLP setup using the Kelvin method to measure the TLP IV characteristics of a DUT [2]. Here the current pulse is applied to the DUT over the pulse force probe. The current transient is measured using a current sensor connected to a sampling oscilloscope. At the DUT the voltage transient is measured using e.g. a 5 k $\Omega$  probe connected to a sampling oscilloscope. The same method can be used for system level ESD tests of powered up systems when the pulse force probe, as shown in Figure 2.1, is exchanged with resistive (Figure 2.2a), capacitive (Figure 2.2b) or ultra low capacitance TVS diode probe tip (Figure 2.2c).

Figure 2.1. Conductive TLP measurement setup.

(a) Resistive probe tip.

(b) Capacitive probe tip.

(c) Ultra-low calacitance TVS probe tip.

Figure 2.2. TLP pulse force probe tip configurations.

# 2.2. SYSTEM LEVEL TESTING USING HIGH IMPEDANCE PROBES

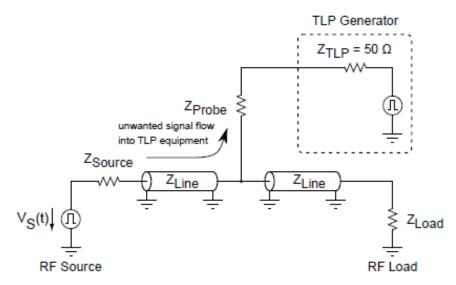

Detecting soft failures caused by ESD/EMI can only be done if the injection test equipment is isolated from the powered operating system. Figure 2.3a shows the configu-

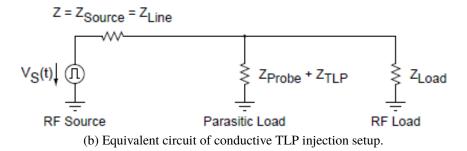

ration of a conductive TLP injection setup for powered system level tests. From the system equivalent circuit in Figure 2.3b it can be seen that the TLP injection setup adds a parasitic shunt impedance

$$Z_{\text{InjectionSetup}} = Z_{\text{Probe}} + Z_{\text{TLP}}$$

(2.1)

to the system connected between the data line and ground.  $Z_{\text{InjectionSetup}}$  is responsible for signal distortion and reflections along the RF/data transmission line. Therefore the signal integrity of the powered system is violated. In order to avoid the unwanted parasitic load a highly isolating solution for  $Z_{\text{Probe}}$  has to be applied.

(a) Conductive TLP pulse force configuration.

Figure 2.3. TLP system connected to RF/high-speed data line.

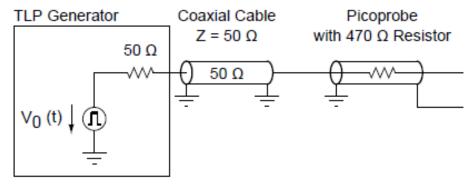

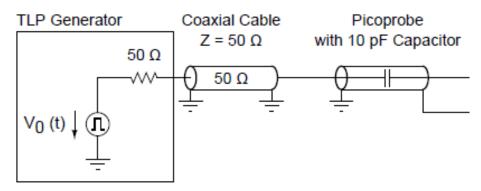

#### 2.3. RESISTIVE AND CAPACITIVE PROBES

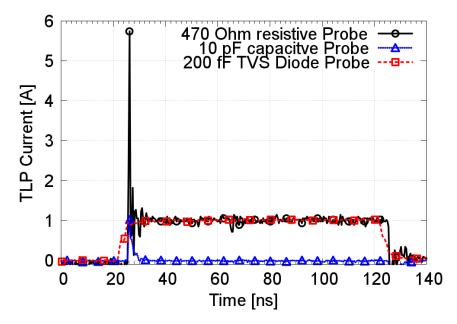

Common approaches for conductive injection in to powered systems are probes with a high nominal value resistor, Figure 2.2a, and probes with a coupling capacitance, Figure 2.2b. Both resistive and capacitive probes have several drawbacks when pulsing in to powered systems, e.g. capacitive and resistive probes deform the applied current pulse, limit the signal bandwidth and limit the maximum TLP current injected to the system.

Figure 2.4 shows a 5 A TLP current pulse in to a 50  $\Omega$  load delivered through a 470  $\Omega$  resistive, a 10 pF capacitive and a 200 fF TVS diode probe as described in Figure 2.2. The capacitive probe is only conductive as long as the voltage across the capacitor changes with time. Therefore according to

$$I(t) = C \cdot \frac{dV}{dt} \tag{2.2}$$

where I(t) is the time dependent current, C is the capacitance and dV/dt the time derivative of the voltage, the square wave TLP current pulse is deformed to a current spike. This leads to a drastically decreased testing and investigation flexibility as the wave form parameters rise time and pulse duration become non-effective. Resistive probes decrease the current capability of the test system due to the increased current source impedance, e.g. for a 470  $\Omega$  probe the current capability of a 50  $\Omega$  TLP pulse source is decreased by a factor of nearly 10.

A further drawback of both resistive and capacitive probe is the lower isolation capability of the test equipment from the net under test when there is no ESD pulse applied. Recalling 2.2 and Eqn. 2.1 the isolation of the test equipment is determined by the impedance added to the data lines.

Figure 2.4. Comparison of 1A TLP current pulse delivered into a 50  $\Omega$  load using different injection probe concepts.

Table 2.1. Impedance of injection probe plus 50  $\Omega$  TLP source at f = 1GHz.

|                  | Capacitive    | Resistive Probe | TVS Diode Probe | TVS Diode Probe |

|------------------|---------------|-----------------|-----------------|-----------------|

|                  | Probe (10 pF) | $(470 \Omega)$  | (200 fF)        | (100 fF)        |

| Impedance        | 65            | 520             | 795             | 1590            |

| in $[\Omega]$ at |               |                 |                 |                 |

| 1 GHz            |               |                 |                 |                 |

The calculated impedance can be directly related to the isolation performance and applicability to different data rates and frequencies. A higher impedance comes with a applicability to higher data rates and higher frequencies.

# 2.4. TRANSIENT VOLTAGE SUPPRESSOR DIODE PROBE CHARACTERIZATION

Using a TVS diode instead of a resistor or a capacitor in the probe has several benefits. To ensure the TVS diode used in the probe isolates the TLP system from the powered application the insertion loss of the TVS diode is determined by measuring its scattering parameters [3].

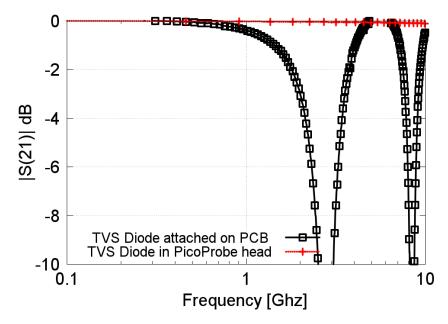

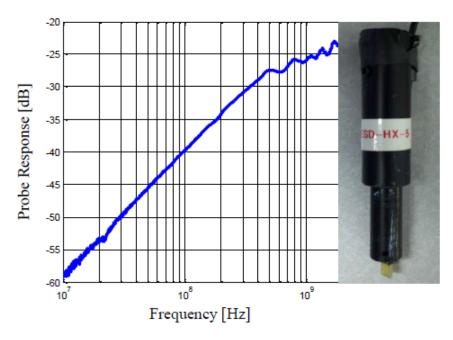

Figure 2.5 shows the insertion loss up to 20 GHz extracted from the scattering parameters of two different TVS diodes. The measurements were taken with a vector network analyzer (VNA) in a configuration according to Figure 2.3a. The diodes were placed instead of  $Z_{\text{Probe}}$ . The VNA was connected to the source and load ports. The junction capacitance, package bond wire and leakage current of the TVS diode mainly determine its frequency dependent impedance in the non conducting state. Due to the low junction capacitances, 100 fF and 200 fF, as well as the low bond wire inductance of 0.4 nH, the signal attenuation, respectively insertion loss, is less than 0.3 dB up to 7 GHz for the 200 fF diode and less than 0.2 dB up to 10 GHz for the 100 fF diode. The DC leakage current for both diodes is in the sub nA regime and is too low to have a significant contribution to the insertion loss. When a current pulse is applied to the system under test the TVS diode triggers, becomes conducting and the current pulse can flow into the system under test. Figure 2.6 shows the TLP I/V curve of the 200 fF TVS diode. The diode triggers at 10 V and then enters its low impedance regime with a dynamic resistance of 1.4  $\Omega$ . The TVS diode is turned on for the time of the applied current pulse and  $Z_{Probe}$  in Figure 2.3a equals the dynamic resistance of the TVS diode.

The time domain transition waveform from off-state to on-state is shown in Figure 2.7. The turn on time in Figure 2.7 and Figure 2.8 is defined as the time when the voltage at and current through the diode has reached steady state. The rapidly decaying

Figure 2.5. Insertion Loss of a 0.2 pF and a 0.1 pF TVS Diode

voltage overshoot in the first 3 ns causes a slight rounding of the current pulse delivered through the TVS diode and in to the system. Figure 2.8 shows comparison between a TLP current pulse delivered through a normal probe in to a 50  $\Omega$  load and through the TVS probe.

Figure 2.9 shows a 1 kV IEC 61000-4-2 pulse in to a 2  $\Omega$  target through two different probe configurations measured using the test setup in Figure 2.10. Both probe configurations, 100 fF and 200 fF TVS diode, hardly disturb the IEC 61000-4-2 current waveform. The higher current peak of the 200 fF TVS diode in Figure 2.10 is caused by the higher capacitance, according to Eqn. 2.2.

Figure 2.6. 200 fF ESD0P2 TVS Diode TLP I/V curve; trigger voltage Vtrig = 10 V, dynamic resistance Rdyn = 1.4  $\Omega$

Figure 2.7. TLP Voltage waveform of the ESD0P2; Turn-on time tTurn-On = 60

Figure 2.8. TLP current wave forms applied into 50  $\Omega$  load using TVS diode probe and standard probe.

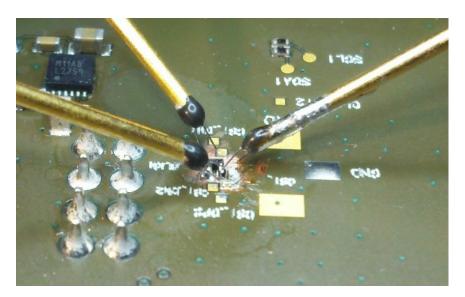

### 2.5. PROBE PARASITICS

The injection probe consists of a TVS diode either implemented in a GGB PicoProbe Model 10 [4] or a TVS diode soldered on a PCB which is placed within the pulse force line. Figure 2.11 shows the TVS diode directly implemented in to the PicoProbe right after the probe tip. In Figure 2.12 the PCB version of the probe is shown.

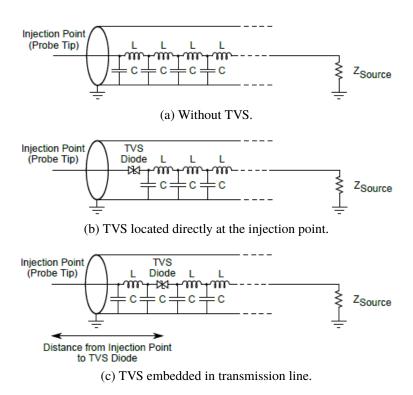

Besides the  $50\,\Omega$  source impedance of the pulse generator further parasitic elements are brought in to the system by the coax cables used to connect the injection point to the pulse source. Figure 2.13a shows the equivalent circuit of a coaxial cable or transmission line. For simplification in Figure 2.13 the resistive elements accounting for power losses in the cable were omitted.

Figure 2.9. IEC61000-4-2 1 kV Pulse shape into 2  $\Omega$  target w/o TVS diode, with 100 fF TVS Diode and 200 fF TVS Diode.

Figure 2.10. IEC61000-4-2 pulse source verification setup.

In Figure 2.13b the TVS diode is mounted directly after the probe tip and all following elements are isolated from the powered system. With increasing distance of the diode from the probe tip the parasitic elements added to the net under test increase. To evaluate the influence of the distance between probe tip and diode the scattering parameters

Figure 2.11. TVS Diode implemented on GGB PicoProbe Model 10.

of a 50  $\Omega$  trace with the probes in Figure 2.11 and Figure 2.12 attached were measured. Figure 2.14 shows the insertion loss of the two configurations.

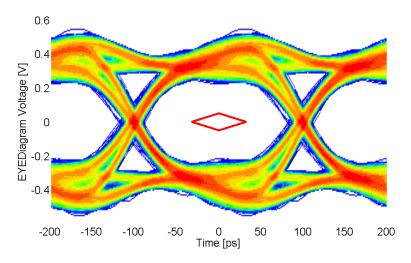

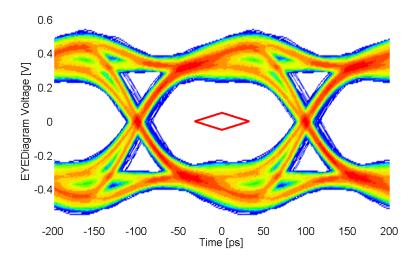

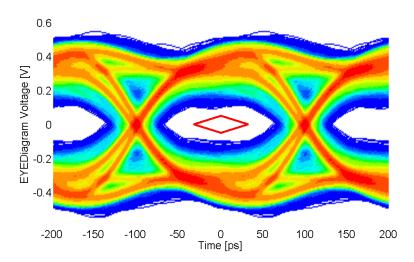

Whereas the probe with TVS diode included in the PicoProbe (blue curve) shows a behavior as expected from the measurement in Figure 2.5, the pcb mounted TVS diode (red curve) indicates a resonance at 2.79 GHz and a 3 dB cut-off frequency of 2 GHz. The resonance at 2.79 GHz is caused by the parasitics of the coaxial cable between probe tip and TVS diode. Even in the undamped region below 1 GHz the probe can have an influence on the transferred signal, e.g. for differential data lines the attached probe can change the electrical length and increase the intra pair skew. A common measure for such effects and in general for characterizing a system's signal integrity is the eye diagram. The eye diagram is an oscilloscope measurement where consecutive bits of a data stream are superimposed over another. Figure 2.15 shows the eye diagram of a USB 3.0 transmission channel without a probe attached. The measurements were done according to the USB 3.0 standard and compliance specification [5]. The red rhombus in the middle is the so called eye mask and indicates the minimum opening of the eye.

Figure 2.12. TVS Diode attached on PCB.

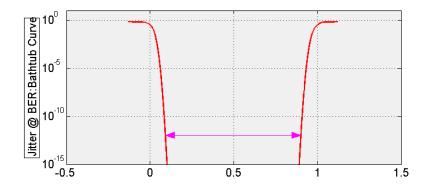

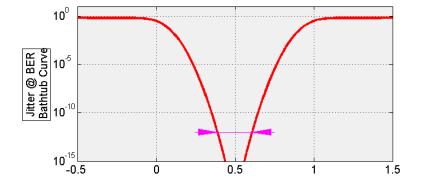

Comparing Figure 2.15 and Figure 2.16 the eye didn't change significantly due to the attached probe. In Figure 2.17 the probe as shown in Figure 2.12 is attached and the eye is almost closed because of the increased distance between injection point and TVS diode. Furthermore the bit error rate (BER) is increased, indicating the USB 3.0 channel is not

Figure 2.13. Coax cable equivalent circuit with TVS diode placed at different distance from injection point.

working within its specifications anymore. The BER is an extrapolated measure from the eye diagram typically plotted in a so called "bathtub" plot, Figure 2.18 and Figure 2.19.

Figure 2.14. Insertion Loss of TVS Diode implemented in GGB PicoProbe Model 10 and TVS Diode attached on PCB.

Figure 2.15. Eye Diagram of USB3.0 transmission channel w/o probe attached.

Figure 2.16. Eye Diagram of USB3.0 transmission channel with TVS diode in PicoProbe head attached.

Figure 2.17. Eye Diagram of USB3.0 transmission channel with PCB mounted TVS diode probe attached.

Figure 2.18. BER of USB3.0 Transmission Channel with TVS diode in PicoProbe head attached.

Figure 2.19. BER of USB3.0 Transmission Channel with PCB mounted TVS diode probe attached.

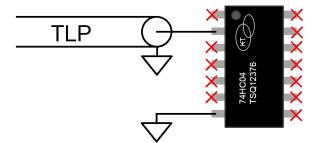

# 3. VERIFICATION OF THE DIODE INJECTION ON A FUNCTIONAL SYSTEM

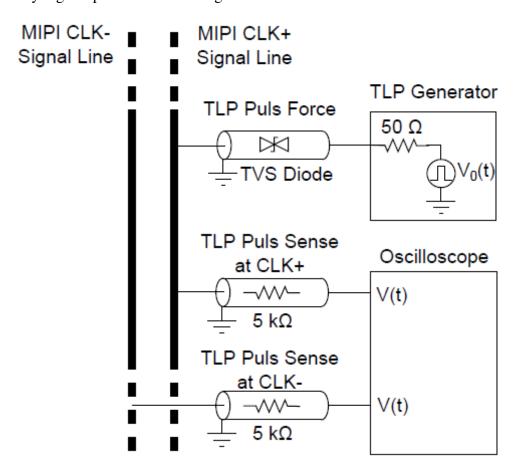

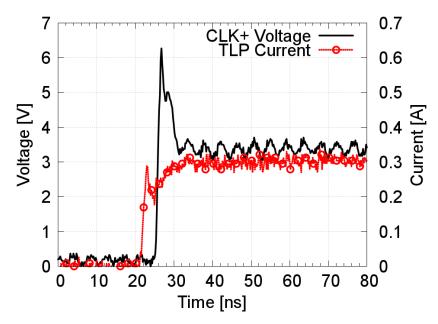

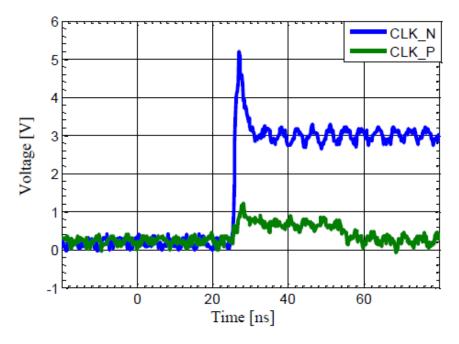

In order to test this new probe, we analyzed a mobile phone's camera subsystem with a MIPI bus using a clock frequency of 250 MHz. The TVS diode probe was used to inject current in to one MIPI data line and to isolate the TLP from the signal path. The measurement setup is shown in Figure 3.1 and Figure 3.2. The waveforms at the lines were measured using a probe with a 4.95 k $\Omega$  attenuating resistor in the probe tip, which has a sufficiently high impedance to avoid signal disturbance.

Figure 3.1. MIPI Bus TLP injection setup.

Figure 3.2. MIPI Bus TLP injection setup.

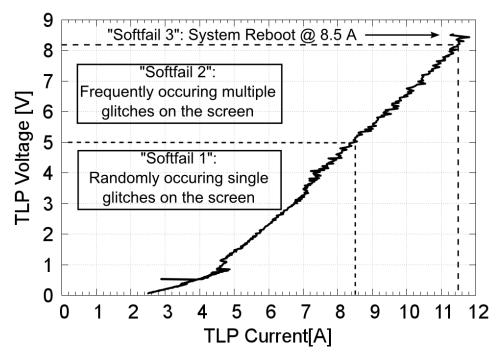

The lines were then evaluated for their susceptibility to pulses that would cause soft failures in the camera system, e.g. glitches on the screen, frozen screen, hang up of the camera software.

By setting the TLP step voltage to a small value (1 V), we created a situation where each pulse was not significantly greater in magnitude from the previous. This allowed us to a) create a very detailed IV curve and b) apply repeated pulses of essentially the same magnitude, reducing the chance that a failure due to a particular amplitude regime would be missed.

Figure 3.3 shows the extracted I/V curve from the captured voltage and current TLP waveforms. The captured waveforms clearly show the presence of a clock signal with

Figure 3.3. Measured TLP I/V curve on the MIPI bus with mapped soft failure levels.

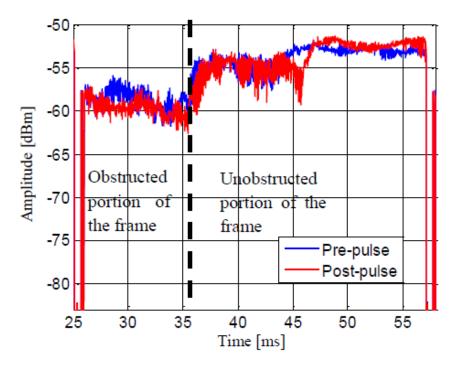

250 MHz on the net when the pulse arrives, Figure 3.4. In comparison, the camera could not even be operated when a 50  $\Omega$  probe was used to pulse in to the MIPI bus.

Figure 3.4. TLP pulse that arrives between data frames.

#### 4. CONCLUSION

A TLP injection test has been presented which allows the assessment of stress pulse susceptibility at high speed data lines by high impedance test probes. In comparison to capacitive and resistive probes the applicability of TVS diode probes by means of data rates, frequency and stress levels is much more flexible. The TVS diode probe does not change the applied wave form independent of the used ESD pulse generator and its source impedance.

The selection criteria for the TVS diode used for the probe is determined by the application data rate and frequency. Scattering parameters and eye diagrams can be used to characterize the TVS diode probe's influence on the signal integrity of the system. As a rule of thumb it can be said that a TVS diode that can be used to protect a certain application can also be used within the TVS diode probe to test the system. Another selection criteria is the diode's trigger voltage as shown in Figure 2.6. The trigger voltage determines the lowest voltage level that can be applied to the system under test. In case lower stress levels are necessary a diode with a lower trigger, respectively breakdown voltage has to be chosen. Care has to be taken on the placement, respectively the distance between TVS diode and injection point. The parasitic capacitance of cabling between injection point and TVS diode can drastically reduce the applicable frequency range of the probe. With the 100 fF TVS diode soldered on a PCB an easy to build probe is realized that can be used for applications below 1 GHz. The GGB PicoProbe Model-10 TVS Diode probe can be used for ultra fast applications as it was shown for USB 3.0 (5 Gbit/s).

# 5. ACKNOWLEDGEMENTS

The authors want to thank GGB Industries for prototyping the customized PicoProbe Model 10 with included TVS diode.

#### **BIBLIOGRAPHY**

- [1] D. Pommerenke and G. Muchaidze and Jayong Koo and Qing Cai and Jin Min, "Application and limits of IC and PCB scanning methods for immunity analysis," in *Electromagnetic Compatibility*, 2007. *EMC Zurich* 2007. 18th International Zurich Symposium on, pp. 83–86, Sept 2007.

- [2] E. Grund and R. Gauthier, "TLP systems with combined 50 and 500-ohm impedance probes and kelvin probes," in *Electrical Overstress/Electrostatic Discharge Symposium*, 2003. EOS/ESD '03., pp. 1–10, Sept 2003.

- [3] B. Franklin and F. Feuerstein and M. Mayerhofer, *High Speed Signal Propagation: Advanced Black Magic.* Prentice Hall Professional, 2003.

- [4] GGB Industries, Inc. http://www.ggb.com/, 2012.

- [5] "Universal Serial Bus 3.0 Specification," November 2012.

# II. A SYSTEMATIC METHOD FOR DETERMINING SOFT-FAILURE ROBUSTNESS OF A SUBSYSTEM

Benjamin Orr, Pratik Maheshwari, Harald Gossner, David Pommerenke, and Wolfgang Stadler

# **ABSTRACT**

A systematic method for evaluating soft fail robustness of a DUT subsystem is presented and demonstrated on a camera MIPI interface. Two different mobile phone platforms are studied under TLP injection while various methods for extracting failure thresholds and localization are applied. The root cause for the soft-failure threshold discrepancy is left for future work.

#### 1. INTRODUCTION

The trend for consumer and industrial electronic devices has led to miniaturization and increased integration, resulting in very small devices with a large number of subsystems [1]. In order to improve the ESD robustness of these highly integrated devices, weak subsystems and points of failure must first be identified. Once they are known, targeted measures such as hardening the hardware and software against ESD events and similar surges can be used to reduce sensitivity of these weak points, thus improving the overall robustness of the system. We propose that System Efficient ESD Design (SEED) [2] can be applied to soft-failures, and is one method to approach this.

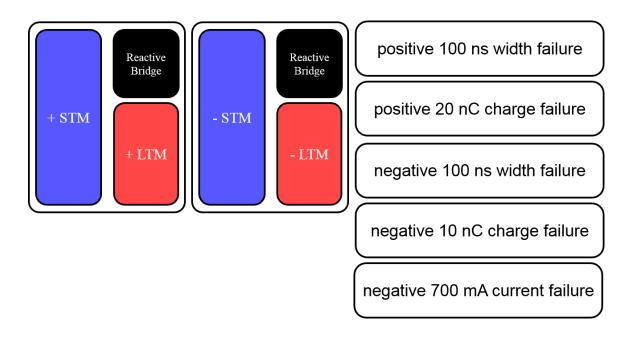

Much work has been done to mitigate hard-failures which would lead to device destruction and permanent loss of system functionality, but ESD-induced soft-reliability issues such as data corruption and system upsets are also concerns. In order to increase device robustness with respect to soft-failures, a "divide and conquer" approach is presented here. This method begins by dividing a device into discrete subsystems such as communication interfaces, IO interfaces, and other peripherals. Once the subsystems have been identified (divide) then each is subjected to TLP characterization in order to determine their independent robustness (conquer). By splitting the overall characterization into pieces and evaluating the susceptibility of these individual subsystems to direct 50  $\Omega$  TLP injection, targeted measures can then be employed to protect vulnerable systems that might exhibit failures during IEC 61000-4-2 testing in the final product. By using this method, an optimization strategy for soft-failures similar to hard failure analysis can be performed as long as the failure can be associated with a pin or pin combination in the susceptible subsystem.

This method is intended to be flexible enough to be applied to any subsystem on a DUT, thus completely characterizing the major IC(s) with respect to soft failure susceptibility. The method is first presented, and then validated on two functionally similar but architecturally different development boards for different mobile phone platforms such as in [3].

#### 2. METHOD OVERVIEW

In order to evaluate a device with respect to its subsystems, failure criteria for each subsystem should be defined. In lieu of enumerating error symptoms and acceptable levels of functionality for all DUTs, the authors have attempted to provide a classification scheme for potential soft-errors which can be applied to many devices. Prior to testing, each subsystem should be identified and assigned an acceptable level of soft failure.

Once the subsystems that are to be tested are identified, specific failure criteria for those subsystems should be described, including their symptoms. This is also a subjective step which requires some consideration of the required device functionality. Note that the very definition of soft-failures precludes hardware symptoms such as DC leakage from being considered. During soft-failure characterization, only software-related symptoms such as a system reset or application crash are considered. Furthermore, the severity of each failure should be considered. For example, the loss of several frames being transmitted from a the video camera of a mobile phone to the main processor may not be considered significant interference, but the same millisecond disturbance on a high speed video camera would cause the loss of valuable information.

Table 2.1. Soft Failure Categorization

| Level 1: | Undetected error, the system recovers without operator intervention        |  |

|----------|----------------------------------------------------------------------------|--|

| Level 2: | Brief but noticeable change in functionality, the system recovers without  |  |

|          | operator intervention                                                      |  |

| Level 3: | Change of functionality, the system requires operator intervention to      |  |

|          | correct                                                                    |  |

| Level 4: | A latent error is introduced into the system that affects an operation not |  |

|          | yet performed, the system requires operator intervention to correct        |  |

After the acceptable failures have been identified, we begin fault-testing the device. This testing is performed by direct electrical stresses to the subsystem nets during normal device operation in search of soft-failures which were previously defined. These stresses are introduced by direct TLP current injection rather than any of the various "real world" ESD models such as HBM or CDM. This controlled injection [4] allows us to build a quasi-static IV curve for the net/subsystem under consideration which can be used when applying mitigation strategies. Furthermore, this injection scheme helps to build a susceptibility model for each pin based on current/voltage, pulse width, and rise time, and polarity.

The final step in determining a subsystem's robustness is to identify the failing device. A subsystem often consists of a communication scheme which involves at least one transmitter and receiver. Even after a failure has been identified, the actual culprit is often still unknown. In order to completely identify the observed failure we need to determine which component of the subsystem is at fault. Again, because of the number of possible subsystems and their varied functions, a complete list of identification techniques cannot be listed here. However, in the following case studies, the methods that the authors used to identify the source of the failure are described in detail.

Once this method has been applied, the results can be easily compared in search of pins or subsystems (often pin groups) which are significantly weaker than the rest. These weak subsystems can then be improved by applying SEED which is a method of system and IC co-design based on high voltage ESD transient characterization of components as in [5], or by hardening the software or firmware against ESD-induced software glitches [6].

## 3. SYSTEM, TESTING AND FAILURE DESCRIPTION

In order to evaluate the effectiveness of the method, we used two development boards, both designed for software development and testing. Documentation was provided with each board pertaining to test points, debug ports, and system layout. Both of these development boards were equipped with cameras driven by the Mobile Industry Processor Interface (MIPI) D-PHY hardware interface and the Camera Serial Interface (CSI) software protocol.

To validate these tests, the camera subsystem was chosen because soft-failures that affected either the camera software or the displayed video were easily identifiable on the screen. Furthermore, camera modules of mobile devices tend to be attached to the system via flex-cables, leaving them very susceptible to IEC system-level testing. These factors make the camera an ideal subsystem to study our characterization methodology.

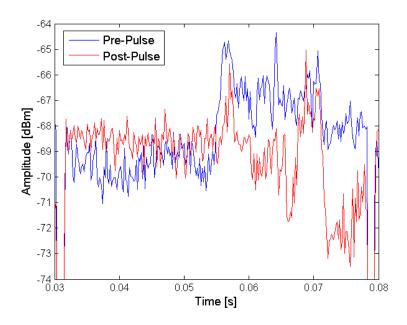

In order to detect soft failures, the camera software on the respective systems was started and placed in 'viewfinder' mode which generated a continuous stream of data from the camera to the processor. Next, we define the acceptable soft failure threshold as Level 3; an error that required user intervention to correct either by restarting the application, or power cycling the device. During testing on DUT 1, the most common failure was found to be screen 'tearing' where multiple frame fragments moved across the screen and obscured the view. For DUT 2, the most common soft failure was a software-reported crash where an error message was presented to the user and the application required a restart. Note that while the errors were symptomatically different, both required the user to restart the viewfinder application, but left the system otherwise unaffected.

Once errors were identified, several methods to determine the actual point of failure in the system were employed. Using these methods the points of failure were tracked to different endpoints on each DUT. Ultimately, these tests would culminate with an identification of the physical mechanism that caused the failure such as latch-up, ground bounce, PDN noise, or crosstalk. However, this is not a trivial task and is left for future work.