# Scholars' Mine

### Masters Theses

Student Theses and Dissertations

Fall 2010

# The study of a model for via transition and the multi-layer via transition tool GUI design

Ketan Shringarpure

Follow this and additional works at: https://scholarsmine.mst.edu/masters\_theses

Part of the Electrical and Computer Engineering Commons Department:

#### **Recommended Citation**

Shringarpure, Ketan, "The study of a model for via transition and the multi-layer via transition tool GUI design" (2010). *Masters Theses*. 4858. https://scholarsmine.mst.edu/masters\_theses/4858

This thesis is brought to you by Scholars' Mine, a service of the Missouri S&T Library and Learning Resources. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

# THE STUDY OF A MODEL FOR VIA TRANSITION AND THE MUTLI-LAYER VIA TRANSITION TOOL GUI DESIGN

by

## KETAN SHRINGARPURE

## A THESIS

Presented to the Faculty of the Graduate School of the

# MISSOURI UNIVERSITY OF SCIENCE AND TECHNOLOGY

In Partial Fulfillment of the Requirements for the Degree

# MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

2010

Approved by

James L. Drewniak, Advisor Jun Fan David Pommerenke

#### ABSTRACT

One of the many challenges faced by engineers working with the present design scenario is to estimate the extent to which a signal, with significant high frequency content, is affected when it is routed on a printed circuit board. The printed circuit board routing will include the transition through the geometries like micro-strip or strip-line transmission lines, via transitions, and irregularities or asymmetries in the aforementioned geometries. One of these discontinuities, the via transition, results in the interaction of the signal on the via and the cavity (plane-pair) through which it passes. The via transition modeling will help characterize a block in the signal path. Section 1 explains the cavity model, and derives an expression for the impedance at a port in a rectangular cavity. The via to cavity connection, and the via capacitance calculation is explained. Then, five practical examples are used to show the model assembly in a circuit fashion, and the results are compared to the measurements.

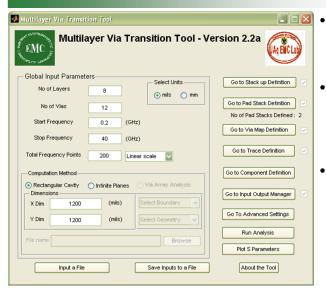

This modeling approach has been automated and integrated into the Multilayer Via Transition Tool, a tool that models all the common PCB geometries and provides the results as network parameters for the user defined ports. This tool is used for performance analysis and design optimization for the high speed PCBs. The tool includes a basic graphic user interface and an engine. Section 2 explains the design methodology for the provided graphic user interface. It explains interface design from the basic set of user inputs required by the engine to run. This section also talks about the difficulties in implementing the interface, and the required improvements for a professional tool.

#### ACKNOWLEDGMENTS

I would like to express my sincere gratitude to my advisor, Dr. James L. Drewniak, for his invaluable support throughout my graduation and his guidance in my research work. I thank Dr. Jun Fan for guiding me through his knowledgeable advice for improvements. I appreciate Dr. David Pommerenke for serving as a member of my thesis committee. I am also grateful to all the members of the "Electromagnetic Compatibility Laboratory" at Missouri University of Science and Technology, for helping me through this learning process. I thank Dr. Giuseppe Selli for his exceptional help with my research work.

I would like to thank my parents, my brother and my entire family for their absolute support and unconditional encouragement throughout my education. I would like to thank my uncle, Mr. Nandkumar Shringarpure, for his constant encouragement to learn more and work towards excellence. I would also like to extend my warm appreciation to all my friends, for their unrelenting support and encouragement. Finally, I thank God Almighty, for making this possible.

# TABLE OF CONTENTS

| Page                                                        |

|-------------------------------------------------------------|

| ABSTRACTiii                                                 |

| ACKNOWLEDGMENTS iv                                          |

| LIST OF ILLUSTRATIONS                                       |

| SECTION                                                     |

| 1. THE VIA MODEL                                            |

| 1.1. CAVITY MODEL                                           |

| 1.2. THE VIA TO CAVITY CONNECTION16                         |

| 1.3. CALCULATING THE VIA TO PLATE CAPACITANCE               |

| 1.4. VIA MODEL FOR MULTILAYERED PCBS                        |

| 1.5. MODELING EXAMPLES                                      |

| 1.6. NEED FOR A TOOL                                        |

| 2. MVTT GRAPHIC USER INTERFACE                              |

| 2.1. INSIGHT INTO GUI DEVELOPMENT FOR MVTT                  |

| 2.2. GUI DESIGN                                             |

| 2.2.1. The Main Window                                      |

| 2.2.2. Stack Up Window                                      |

| 2.2.3. Pad Stack Window                                     |

| 2.2.4. Via Map Window                                       |

| 2.2.5. Trace Definition Window                              |

| 2.2.6. Component Definition                                 |

| 2.2.7. IO Manager Window57                                  |

| 2.2.8. Advanced Settings Window                             |

| 2.2.9. Run Analysis                                         |

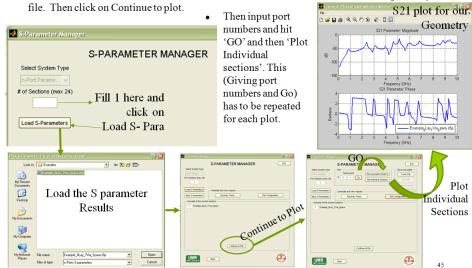

| 2.2.10. Plot S Parameters                                   |

| 2.3. DISCUSSION ABOUT ISSUES IN UI DESIGN AND DEPLOYMENT 61 |

| 2.3.1. Error Checking Necessity And Implementation          |

| 2.3.2. Deployment Of Matlab Based Tool                      |

| 2.4. FUTURE SCOPE FOR TOOL DEVELOPMENT                      |

| APPENDIX     | 67 |

|--------------|----|

| BIBLIOGRAPHY |    |

| VITA         |    |

# LIST OF ILLUSTRATIONS

|  |  | vii |

|--|--|-----|

|  |  |     |

|  |  |     |

|              | Pag                                                                                                                                  | ge |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.1.  | A test board for measurement and modeling designed to study real world<br>PCB layouts                                                | 2  |

| Figure 1.2.  | Electric and magnetic fields in a cavity formed by Plane1 and Plane2 separated by height d.                                          | 5  |

| Figure 1.3.  | PCB geometry showing a signal via connecting two traces and a reference via                                                          | 6  |

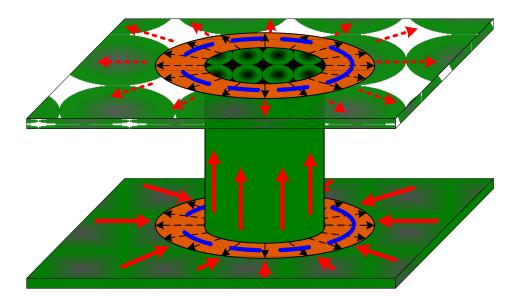

| Figure 1.4.  | The via – cavity geometry with the electric field map and the magnetic field map is shown                                            | 7  |

| Figure 1.5.  | The magnetic field and the surface currents on the planes due to the impressed current source placed in the cavity at a via location | 8  |

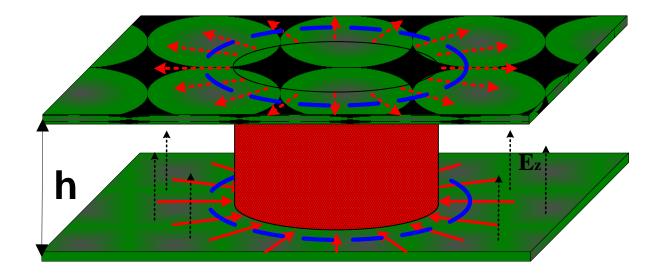

| Figure 1.6.  | Zpp port to via connection is shown for three different geometry configurations                                                      | 20 |

| Figure 1.7.  | Electric flux lines between the via and the planes of the cavity are shown for via without pad and with pad cases                    | 21 |

| Figure 1.8.  | Connecting the cavities stacked vertically                                                                                           | 24 |

| Figure 1.9.  | Common stack up for all test vehicles is shown                                                                                       | 25 |

| Figure 1.10. | A GND via cage is formed by two rows of vias offset by 20 mils 2                                                                     | 26 |

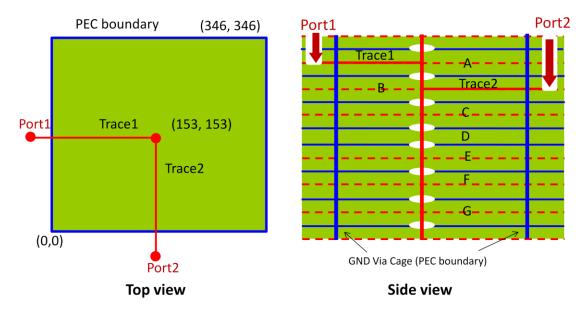

| Figure 1.11. | Example 1 geometry shows one signal via with trace connection in top and bottom cavity                                               | 27 |

| Figure 1.12. | Example 2 geometry shows one signal via connected to traces in first and second cavities                                             | 28 |

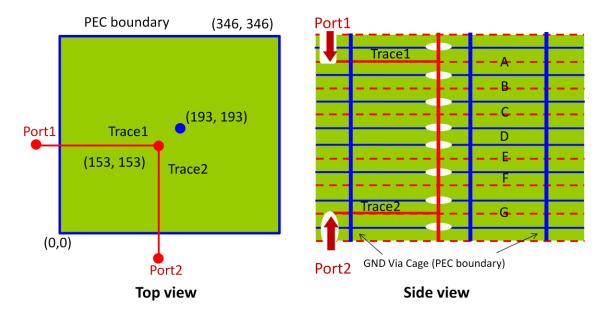

| Figure 1.13. | Example 3 geometry a signal via and a signal return via location                                                                     | 28 |

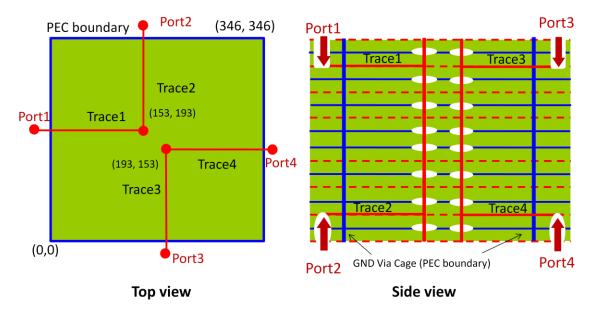

| Figure 1.14. | Example 4 geometry shows two signal vias with trace connection in top and bottom cavities                                            | 29 |

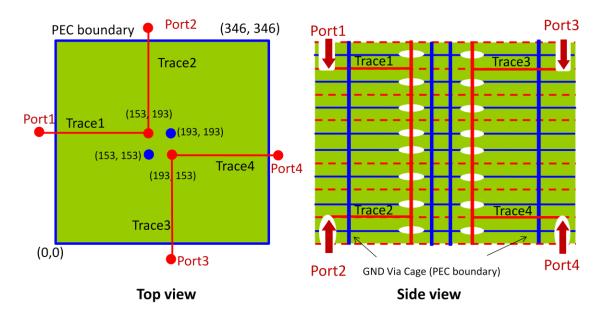

| Figure 1.15. | Example 5 geometry shows the same geometry as Example 4, with two signal return vias                                                 | 29 |

| Figure 1.16. | Dielectric properties of the test vehicles extracted from measurements 3                                                             | 31 |

| Figure 1.17. | Z parameters for Zpp of cavity used in (a)Example 1 and Example 2, (b)<br>Example 3, (c)Example 4, and (d) Example 5                                                                                   | 32 |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

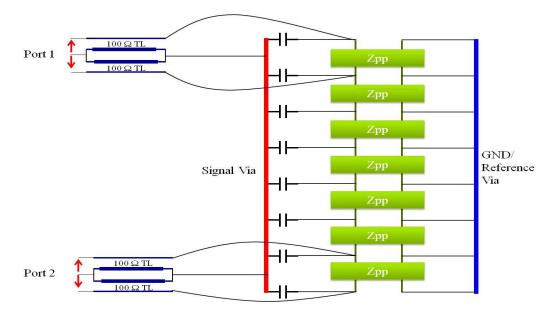

| Figure 1.18. | The circuit model for Example 1 shows Zpp blocks with one port, connected to the via.                                                                                                                  | 33 |

| Figure 1.19. | The circuit model for Example 2 shown is similar to Example 1 circuit except, the trace from bottom cavity is moved up to the second cavity                                                            | 33 |

| Figure 1.20. | The model for Example 3, shown, is the Example 1 circuit model, with the Zpp blocks with two ports                                                                                                     | 34 |

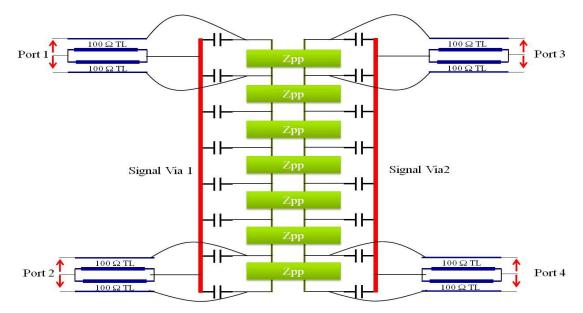

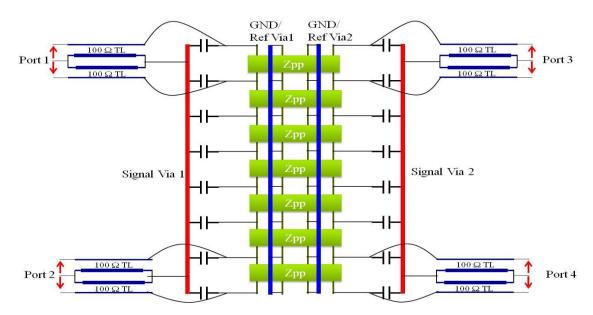

| Figure 1.21. | The circuit model for Example 4 shows Zpp blocks with two ports, connected to two signal vias                                                                                                          | 35 |

| Figure 1.22. | The model for Example 5, shown, has the Example 4 model, with the four port Zpp blocks, where two ports are used to connect to ground vias, and two ports are connected to signal vias as in Example 4 | 35 |

| Figure 1.23. | Example 1 results from measurement and simulation are shown                                                                                                                                            | 36 |

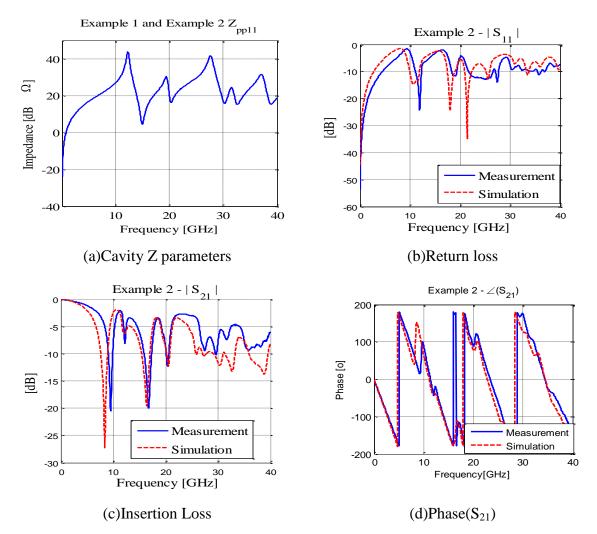

| Figure 1.24. | Example 2 results from measurement and simulation are shown                                                                                                                                            | 37 |

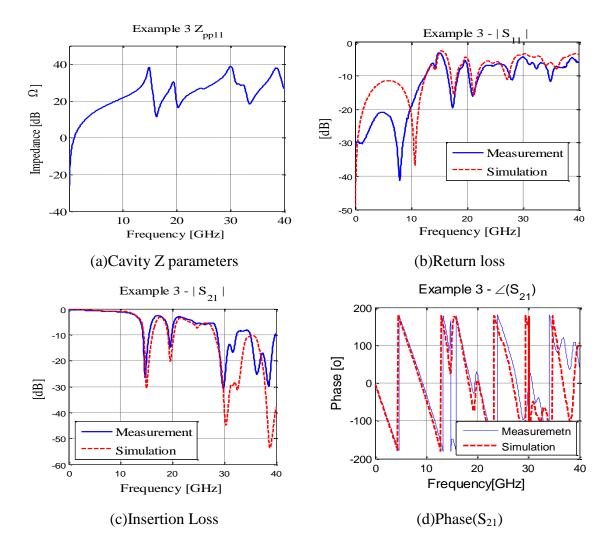

| Figure 1.25. | Example 3 results from measurement and simulation are shown                                                                                                                                            | 38 |

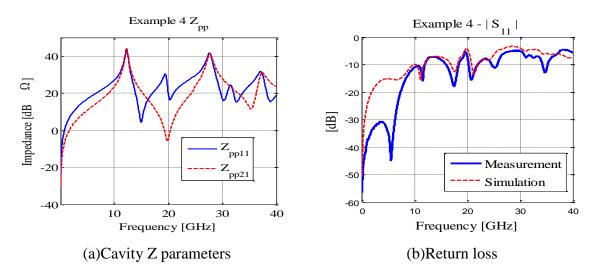

| Figure 1.26. | Example 4 results from measurement and simulation are shown                                                                                                                                            | 39 |

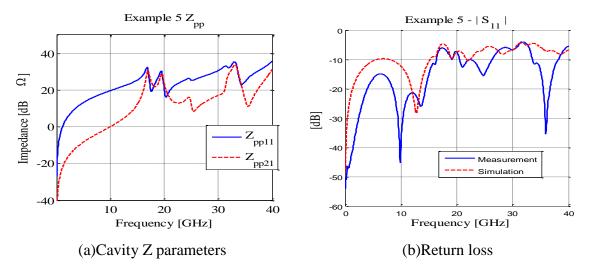

| Figure 1.27. | Example 5 results from measurement and simulation are shown                                                                                                                                            | 41 |

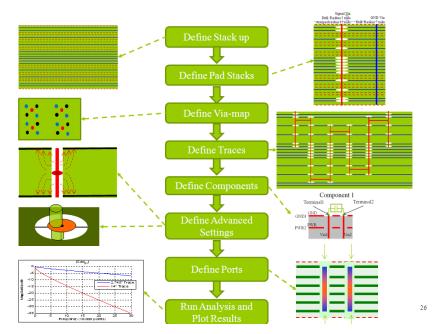

| Figure 2.1.  | Flow used by the MVTT is shown.                                                                                                                                                                        | 46 |

| Figure 2.2.  | Functionality of the MVTT is shown                                                                                                                                                                     | 47 |

| Figure 2.3.  | Ideal flow of the GUI.                                                                                                                                                                                 | 48 |

| Figure 2.4.  | Blank 'Main' Window                                                                                                                                                                                    | 49 |

| Figure 2.5.  | Stack Up Definition Window.                                                                                                                                                                            | 50 |

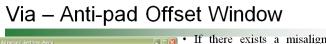

| Figure 2.6.  | Pad Stack Definition Window                                                                                                                                                                            | 52 |

| Figure 2.7.  | Via Map Definition Window                                                                                                                                                                              | 53 |

| Figure 2.8.  | The Trace Definition Window                                                                                                                                                                            | 55 |

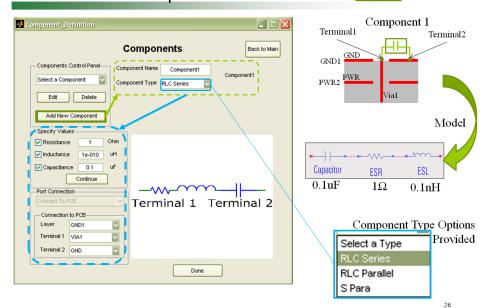

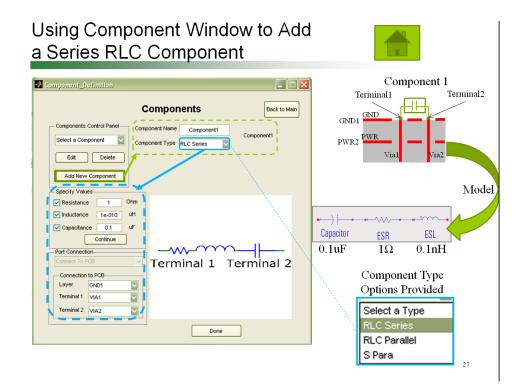

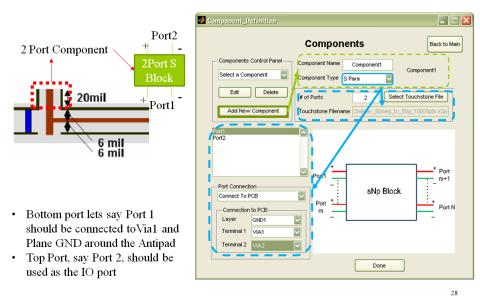

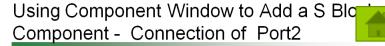

| Figure 2.9.  | Component Window which shows a 50 Ohm resistor definition between<br>the Via 1 and Via 2 at the GND1 layer                                                                                             | 57 |

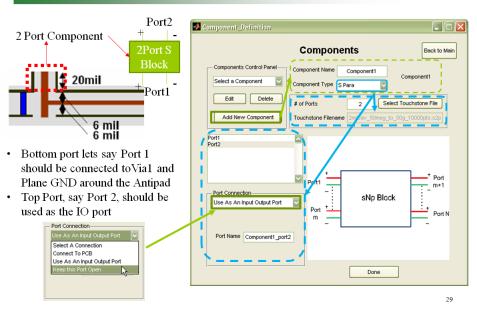

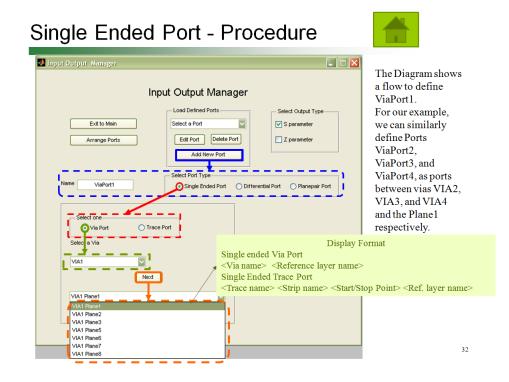

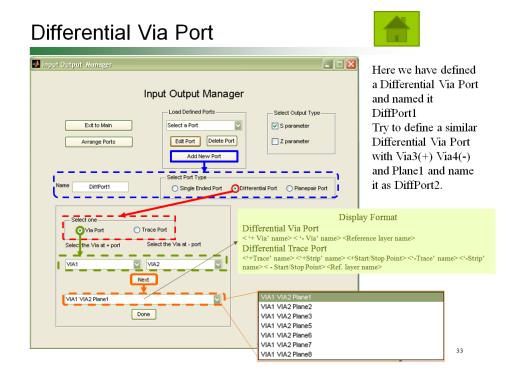

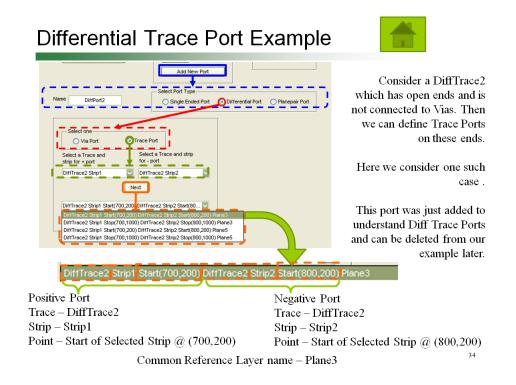

| Figure 2.10. | The Input Output Manager window, showing the definition of a single<br>ended via port using the via and the plane name.  | 58 |

|--------------|--------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.11. | Advanced Settings Window.                                                                                                | 60 |

| Figure 2.12. | Processing complete popup which occurs when engine finishes its processing and writes results into the respective files. | 61 |

| Figure 2.13. | S Manager Window used to plot and compare the results which are given as outputs when the tool finishes processing.      | 61 |

#### **1. THE VIA MODEL**

The performance of the printed circuit boards (PCBs) used in high-speed digital applications, if not carefully designed, may be significantly affected by power integrity and signal integrity issues. The power integrity issues may occur in the power distribution network (PDN) design which deals with providing a clean power and reference rails to the high speed integrated circuits (ICs) placed on the PCB. Recently, most ICs work with clock frequencies of more than several gigahertz. The switching in such ICs leads to fast transient currents on the power and ground rails, causing ripples in the supply voltage. Thus, noise can be introduced into a PDN, very easily. The IO signals of such ICs have to be routed on the same PCB, which may pick up the noise due to the coupling from the other signals or the power/reference rails, causing signal integrity issues too.

The PCBs used in the high-speed applications usually have several layers, many of which are complete planes or large area fills of power or reference nets. Such large metal planes form a parallel plate structure which may act as a waveguide for the high frequency noise coupled into the PDN. The noise in the PDN can cause signal integrity problems when coupled into signal nets, or lead to EMI issues when the noise couples in to a structure that can radiate. Thus, a challenge in PDN design is to make sure noise does not propagate easily along the PDN, and that it does not couple to other nets on the PCB. A common strategy followed by engineers is lowering the input impedance and transfer impedance of the PDN, for all the locations where noise can couple into the PDN.

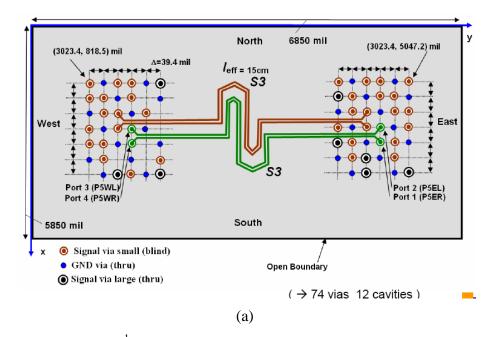

Figure 1.1 shows a test vehicle used to study the performance of the signal links on a high -speed PCB. Top view shows the 74 vias placed in two via fields. The via fields include signal, reference and power net vias. The signal vias in two via fields are connected by the differential links on inner layers of the PCB. This is used as an illustration to show the complexity of high speed PCB designs. Such PCBs have several layers with metal planes or large area fills, which act as reference nets or power nets. The remaining layers are used for routing the signals. Due to the complexity of the implemented circuits and the size constraints, the signals have to be routed on two or more layers. A via is used for this transition of the signal from one layer to another. Also, the via is used to short circuit the reference planes or the power planes lying on different layers. At high frequencies, many such via are required to effectively short circuit the reference planes as the metal plane dimensions become electrically long, i.e., metal planes show distributed behavior. Thus, vias are used for connecting the metal with same net-name lying on different layers. These vias are hollow metallic cylinders, made by drilling holes in the PCB and plating these holes. Section 1.2 will further explain the geometry of the via. To address power integrity and signal integrity concerns, the engineers are required to perform EM analysis of the PCB geometry. For the PCB geometry, several modeling techniques like FDTD, FEM or PEEC, could be used. Many commercial full-wave modeling tools, which use one or more of such modeling techniques are available, e.g., CST Microwave Studio, Ansoft HFSS, Sigrity, etc. But the full-wave simulations require a lot of computational resources and also a very long simulation time.

Figure 1.1. A test board<sup>1</sup> for measurement and modeling designed to study real world PCB layouts: (a) Top view of 74 vias in two via fields connected with differential traces. (b) Cross section of PCB for understanding 24 layer stack up and the via dimensions for different via types.

<sup>&</sup>lt;sup>1</sup> Image and design is courtesy Kevin Gu at IBM research centre and R. Rimolo – Donadio at Technical University Of Hamburg -Harberg.

Figure 1.1. A test board<sup>2</sup> for measurement and modeling designed to study real world PCB layouts (cont.)

This section explains an analytical model for the via transition, using the cavity model technique. The analytical formulation for the via transition, including the behavior of the metal planes, is used to model the common PCB geometries. The required computational time using the analytical formulation, is relatively very small, even for complex geometries, when compared to full-wave modeling techniques.

The model for via transition can be broken down into pieces which can be modeled individually based on the conventional electromagnetic theories and principles.

<sup>&</sup>lt;sup>2</sup> Image and design is courtesy Kevin Gu at IBM research centre and R. Rimolo – Donadio at Technical University Of Hamburg -Harberg.

This section is organized as follows. Section 1.1 explains the cavity mode formulation and finds the solution for rectangular cavity based on Green's function. In section 1.2, the via to cavity connection is explained. The via is modeled as a circuit node connected to the cavity model network parameter block using capacitors for unconnected planes, which represent the via to plane capacitance. The via to plane capacitance is discussed in section 1.3. Section 1.4 explains how the single cavity structure is extended to a complete stack up. The final output of the model is in the form of a network parameters matrix between a given set of ports defined on the geometry. The network parameters help analyze the PCBs as a block in a link path and, allow comparison to measurement and full-wave simulation tool results. Section 1.5 uses a set of example cases for comparing modeling results to measurements. The results are for common geometries, so provide some insight into the physics of via transition. The model requires some effort, when each block is created and assembled in a circuit analysis tool. Section 1.6 explains how the complete process has been integrated into a single tool called the Multilayer Via Transition Tool (MVTT).

#### **1.1. CAVITY MODEL**

The cavity model is a modeling method used for a parallel plane pair geometry using planar circuits [1]. Planar circuits are electromagnetic circuits which are small compared to the wavelength only along one dimension. Based on this assumption, electromagnetic principles are used to find a model for the electric and magnetic fields present in the cavity. The cavity, in this via model, refers to two thin metal layers separated by a small distance. For cavity model application to printed circuit board, the basic structure is that of two arbitrarily shaped metal planes separated by a thin dielectric. Here, essentially, the dielectric thickness has to be smaller compared to the wavelength of electromagnetic waves, in order to form the planar circuit.

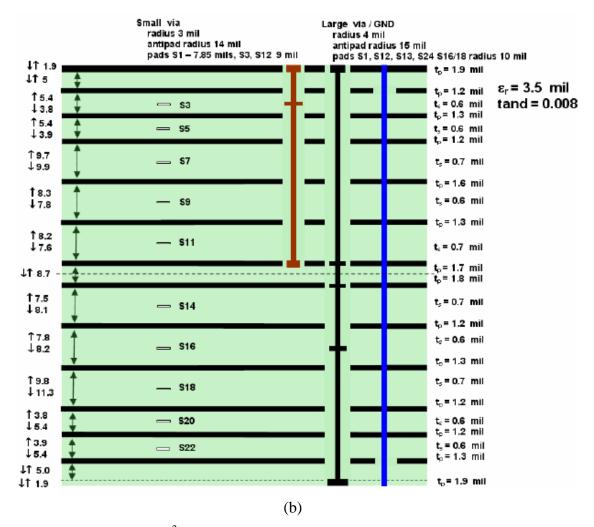

Figure 1.2 shows the cavity under consideration. Plane 1 and Plane 2 form the cavity of arbitrary shape separated by d. The cavity is bounded by the surface S with normal n and tangent t. The dielectric thickness d is small compared to the wavelength (assuming the cavity is a planar circuit). Then, electric field is constant along the z direction. Due to the perfect electric conductor (PEC) boundary condition of top and

bottom conductor surfaces, the electric field only has a z component inside the cavity. Similarly, the tangential magnetic field has only the x and y components, i.e.,

Figure 1.2. Electric and magnetic fields in a cavity formed by Plane1 and Plane2 separated by height d. Surface S forms a boundary along the open edge. A boundary port and impressed source are also shown.

$$E_x = E_y = 0; \ H_z = 0,$$

(1.1)

$$\frac{\partial}{\partial z} = 0. \tag{1.2}$$

The Maxwell's equations for a time harmonic electromagnetic fields are then

$$x\frac{\partial}{\partial y}E_{z} - y\frac{\partial}{\partial x}E_{z} = -j\omega\mu \ xH_{x} + yH_{y} \quad , \qquad (1.3)$$

$$\frac{\partial}{\partial x}H_{y} - \frac{\partial}{\partial y}H_{x} = j\omega\varepsilon E_{z} \quad . \tag{1.4}$$

The wave equation can be obtained using (1.4) in the curl of (1.3), as

$$\left(\frac{\partial^2}{\partial x^2} + \frac{\partial^2}{\partial y^2} + \omega^2 \mu \varepsilon\right) E_z = 0 \quad . \tag{1.5}$$

This is a two dimensional wave equation, which may be represented as

$$\nabla_t^2 + k^2 \ E_z = 0 \ , \tag{1.6}$$

where,

$$\nabla_t^2 = \frac{\partial^2}{\partial x^2} + \frac{\partial^2}{\partial y^2} \quad , \tag{1.7}$$

$$k = \omega \sqrt{\mu \varepsilon} \qquad . \tag{1.8}$$

The boundary of the cavity along its edge, is considered 'open' in the region with no boundary ports. The physical meaning is that there is no current flowing outward from the cavity edge, i.e., from the 'open boundary' where a port is not defined. The current is on the bottom surface of the top conductor and the top surface of the bottom conductor. The magnetic field associated with this current lies in the x-y plane, in a direction normal to the direction of surface current. Along the edge of the cavity, the current normal to the edge is zero (open boundary), so it implies that the magnetic field tangential to the edge is also zero, but the magnetic field can exist in the direction normal to the edge. This condition can be characterized as a perfect magnetic conductor along the boundary or the cavity edge, such that magnetic field can only be perpendicular to the boundary surface. If  $\hat{n}$  is an outward normal to the cavity edge, and  $\hat{t}$  is the tangent to the cavity edge, as shown in Figure 1.2, the open boundary condition can be formulated as

$$\begin{aligned} \mathbf{J}_{\mathbf{n}} &= \hat{n} \times \mathbf{H} \big|_{s} = 0 , \\ \mathbf{H}_{t} &= 0 . \end{aligned}$$

(1.9)

The relationship between the electric field and the magnetic field in the (1.3), Maxwell's equation in differential form for Faraday's law, shows that the gradient of electric field is always normal to the magnetic field, and is related by a non zero constant. Thus if the magnetic field is zero in a particular direction, (1.3) indicates that electric field gradient in that direction is zero, or the electric field remains constant moving in that direction, and vice versa. From this observation and the boundary condition that the tangential magnetic field is zero for the cavity edge, the electric field gradient in the direction normal to the edge of the cavity has to be zero, or

$$\mathbf{H}_{\mathbf{t}} = 0 \Longrightarrow \frac{\partial}{\partial n} E_z = 0 \quad . \tag{1.10}$$

The boundary condition on S enforces tangential electric field and normal magnetic field, with their components in the other direction to be zero. These conditions are enforced at the edge, and as no current is flowing out from the edge, there are no fringing electric field lines. Thus, the cavity model used here does not take into account the fringing field at the boundary.

The electric field is constant along the  $\hat{z}$  direction, inside the cavity, so the potential difference between the top and bottom plates, defined as the integral of the electric field along the z direction at a location in the x-y plane, yields a product of the electric field intensity at that location and the cavity height, as

$$V = -\int \mathbf{E} \cdot \hat{z} \, dz = -E_z d \quad . \tag{1.11}$$

The relationship in (1.11) is important as it relates the field quantity to a circuit quantity, which is useful to define ports in the cavity model.

When the shape of the cavity is irregular, the segmentation approach is used to break down the irregular shape into simple polygons [2], for which the solution to the electric and the magnetic fields can be formulated easily. These simple polygons are connected together using boundary ports. The boundary ports are ports placed along the edge of two cavities to be connected laterally, to enforce current and voltage continuity. The irregular shape is thus stitched together using these boundary ports, which are present on both the cavities at the corresponding locations. They are placed at an electrically small distance apart so that the field variations are contained in the continuity enforced at the ports. As shown in the Figure 1.2, the port current is defined as coming out of the cavity along the normal to the cavity edge on bottom surface of top plane, uniformly distributed across the width  $W_{bp}$  of the port. The return current is uniformly distributed along the width of the port on the top surface of the bottom plane. The voltage is constant along the width of the port. For boundary ports, the current and the voltage expressions in terms of the E field and surface current are

$$I = \int (\mathbf{J}_{s} \cdot n) ds = (\mathbf{J}_{s} \cdot n) \mathbf{W}_{bp}$$

(1.12a)

$$V = -(\frac{d}{W_{bp}}) \int E_z ds \tag{1.12b}$$

The impressed current sources are used to model the vias present in the printed circuit board geometry. The via is a cylindrical PEC boundary inside the cavity, which is replaced by an impressed current source. The impressed current source  $\mathbf{J}_{\mathbf{k}}$  is a uniform current distribution oriented in the  $\hat{z}$  direction, and placed at the via location ( $x_k$ ,  $y_k$ ). For a source with rectangular cross section, the dimensions are  $W_{xk}$  and  $W_{yk}$  along x and y direction respectively. As the current density is uniform for the x-y cross section of the source, the current flowing out of the source is

$$I_{k} = \int_{x_{k}-W_{xk}/2}^{x_{k}+W_{xk}/2} \int_{y_{k}-W_{yk}/2}^{y_{k}+W_{yk}/2} \mathbf{J}_{k} \cdot \hat{z} \, dx dy , \qquad (1.13)$$

$$I_k = \mathbf{J}_k \cdot \hat{z} \quad W_{x_k} W_{y_k} \quad . \tag{1.14}$$

Also, the source voltage can be averaged over the area of the source which gives

$$V_{k} = \frac{1}{W_{x_{k}}W_{y_{k}}} \int_{x_{k}-W_{xk}/2}^{x_{k}+W_{xk}/2} \int_{y_{k}-W_{yk}/2}^{y_{k}+W_{yk}/2} -E_{z}(x,y)d \ dxdy \ .$$

(1.15)

These sources should appear in the Maxwell's equation for time harmonic fields used to find the wave equation. Then, the wave equation (1.6) becomes

$$\nabla_t^2 + k^2 \quad E_z = j\omega\mu \quad \mathbf{J}_k \cdot \hat{z} \quad . \tag{1.16}$$

The solution is found for the open boundary condition, or a short boundary condition. For open boundary, the normal derivative of the electric field intensity in the cavity is zero along the boundary, and for the short boundary, the electric field intensity is zero, as given by

$$\frac{\partial}{\partial n}E_z(x,y) = 0 \quad , \tag{1.17}$$

$$E_z = 0$$

, (1.18)

for open and short boundary conditions, respectively. The solution to the wave equation in (1.16) has been found using the Green's function method. As an example, the solution for the open boundary rectangular cavity using the Green's function in series form is shown. The presented solution follows the standard methodology given in [3].

Consider the rectangular cavity with x, y, and z dimensions as a, b, and d respectively. The Green's function satisfies the auxiliary differential equation and boundary conditions as

$$\nabla_t^2 + k^2 \ G \ x, y; x', y' = \delta(x - x')\delta(y - y') , \qquad (1.19)$$

$$\frac{\partial}{\partial n}G \quad x, y; x', y' = 0 \quad . \tag{1.20}$$

where n is the normal to the boundary. The Green's function is taken to be a series summation of an orthogonal basis function set  $\forall g_{mn} \leq y \geq$ . Each basis function of this set will satisfy the auxiliary differential equation and the boundary condition applicable to the Green's function in equations (1.19) and (1.20) as

$$\nabla_t^2 + k_{mn}^2 \psi_{mn} \ x, y = 0 , \qquad (1.21)$$

$$\frac{\partial}{\partial n}\psi_{mn} \quad x, y = 0 \quad . \tag{1.22}$$

The basis function can be written in the variable separable form by choosing

$$\psi_{mn} \quad x, y = f \quad x \quad g \quad y \quad . \tag{1.23}$$

Using (1.23) in (1.21),

$$\left(\frac{\partial^2}{\partial x^2} + \frac{\partial^2}{\partial y^2} + k_{mn}^2\right) f \quad x \quad g \quad y = 0,$$

$$\frac{1}{f \quad x} \frac{\partial^2}{\partial x^2} f \quad x \quad + \frac{1}{g \quad y} \frac{\partial^2}{\partial y^2} g \quad y = -k_{mn}^2.$$

Since f and g are functions of x and y alone, respectively, the differential equations can be separated out as,

$$\frac{1}{f x} \frac{\partial^2}{\partial x^2} f x = -k_x^2,$$

$$\frac{1}{g y} \frac{\partial^2}{\partial y^2} g y = -k_y^2.$$

(1.24)

Where,

$$k_{mn}^{2} = k_{x}^{2} + k_{y}^{2} \quad . \tag{1.25}$$

The differential equations (1.24), have general solutions

$$f \quad x = A\sin k_x x + B\cos k_x x \qquad (1.26)$$

$$g \quad y = C\sin k_y y + D\cos k_y y \quad . \tag{1.27}$$

To find the constants, the boundary conditions for the basis function set are used. The open boundary conditions are written more explicitly for each edge of the cavity, to solve for each constant. Then, at y = 0 and for x in [0, a],

$$\frac{\partial}{\partial y} \psi_{mn} \quad x, 0 = 0$$

$$\Rightarrow f(x)g'(0) = 0$$

$$g' \ 0 = k_y C \cos \ 0 \ -k_y D \sin \ 0 = 0$$

$$\Rightarrow C = 0 , \qquad (1.28)$$

and at y = b and x in [0, a]

$$\frac{\partial}{\partial y} \psi_{mn} \quad x, b = 0$$

$$\Rightarrow f(x)g'(b) = 0$$

$$g' \ b = -k_y D \sin k_y b = 0$$

$$\Rightarrow k_y = \frac{n\pi}{b}; n = 0, 1, 2... \quad . \tag{1.29}$$

Similarly, for x = 0 and x = b, results in,

$$A = 0$$

, (1.30)

$$k_x = \frac{m\pi}{a}; m = 0, 1, 2 \quad . \tag{1.31}$$

Then, the solution to the auxiliary differential equation (1.21) is

$$\psi_{mn} \quad x, y = BD\cos\left(\frac{m\pi}{a}x\right)\cos\left(\frac{n\pi}{b}y\right) \quad .$$

(1.32)

The basis functions are orthogonal for x in [0, a] and y in [0, b], i.e.,

$$\int_{0}^{a} \int_{0}^{b} \psi_{mn} x, y \psi_{pq} x, y dy dx = \begin{cases} 1 & \forall m = p; n = q \\ 0 & otherwise \end{cases}$$

(1.33)

$$BD^{2} \int_{0}^{a} \left[ \cos\left(\frac{m\pi}{a}x\right) \right]^{2} dx \int_{0}^{b} \left[ \cos\left(\frac{n\pi}{b}y\right) \right]^{2} dy = 1,$$

(1.34)

and

$$\int_{0}^{a} \left[ \cos\left(\frac{m\pi}{a}x\right) \right]^{2} dx = \begin{cases} a \quad ; m = 0 \\ a/2 \quad ; m \neq 0 \end{cases}$$

$$\int_{0}^{b} \left[ \cos\left(\frac{n\pi}{b}y\right) \right]^{2} dy = \begin{cases} b \quad ; n = 0 \\ b/2 \quad ; n \neq 0 \end{cases}$$

Then,

$$BD = \frac{\sigma_m \sigma_n}{\sqrt{ab}} ,$$

and the basis function from (1.32) becomes,

$$\psi_{mn} \quad x, y = \frac{\sigma_m \sigma_n}{\sqrt{ab}} \cos\left(\frac{m\pi}{a}x\right) \cos\left(\frac{n\pi}{b}y\right),$$

(1.35)

where

$$\sigma_{m} = \begin{cases} 1 & ;m = 0 \\ \sqrt{2} & ;m \neq 0 \end{cases}$$

$$\sigma_{n} = \begin{cases} 1 & ;n = 0 \\ \sqrt{2} & ;n \neq 0 \end{cases}$$

(1.36)

The Greens function in series form can then be written using bilinear equation [3]

$$G x, y; x', y' = \sum_{m} \sum_{n} \frac{\psi_{mn} x', y' \psi_{mn} x, y}{k^2 - k_{mn}^2} , \qquad (1.37)$$

or,

$$G x, y; x', y' = \sum_{m} \sum_{n} \frac{\sigma_{m}^{2} \sigma_{n}^{2}}{ab} \frac{\cos k_{x} x' \cos k_{y} y' \cos k_{x} x \cos k_{y} y}{k^{2} - \left[k_{x}^{2} + k_{y}^{2}\right]} .$$

(1.38)

The solution to the differential equation (1.16) and boundary conditions (1.17) for a rectangular cavity can then be found from

$$E_{z} x, y = j\omega\mu \int_{0}^{b} \int_{0}^{a} G x, y; x', y' \quad \mathbf{J}(x', y') \cdot \hat{z} dx' dy' .$$

(1.39)

The solution to electric field in (1.39) can be used to get an impedance relationship between the voltages and the currents. For an N port cavity the Z parameter matrix is found by placing a current excitation at one port at a time and calculating the voltage at all other open circuited port locations, based on the definition of Z parameters for an N port system. Thus, in accordance to impressed source definition, a  $\hat{z}$  directional source  $J_i$ , is placed centered at ( $x_i$ ,  $y_i$ ), and is uniform across the cross section of dimensions  $W_{xi}$  and  $W_{yi}$ . Using (1.14) and (1.15) for the impressed source current and voltage respectively, the  $Z_{ij}$  is

$$Z_{ij} = \frac{V_i}{I_j}\Big|_{I_k=0;\forall k \neq j} = \frac{\frac{1}{W_{x_i}W_{y_i}} \int_{x_i-W_{x_i}/2}^{x_i+W_{x_i}/2} \int_{y_i-W_{y_i}/2}^{y_i+W_{y_i}/2} -E_z(x, y)d \ dxdy}{\int_{x_j+W_{x_j}/2}^{x_j+W_{x_j}/2} \int_{y_j-W_{y_j}/2}^{y_j+W_{y_i}/2} J_j \ \hat{z} \ dx'dy'}$$

(1.40)

The solution for  $E_{\boldsymbol{z}}(\boldsymbol{x},\,\boldsymbol{y})$  with only one source  $J_{j}$  is

$$E_{z} x, y \Big|_{\mathbf{J}=\mathbf{J}_{j}} = j\omega\mu \int_{0}^{b} \int_{0}^{a} G x, y; x', y' \quad \mathbf{J}_{j}(x', y') \cdot \hat{z} \, dx' dy' \quad , \qquad (1.41)$$

$$E_{z} x, y \Big|_{\mathbf{J}=\mathbf{J}_{j}} = j\omega\mu \ \mathbf{J}_{j} \cdot \hat{z} \int_{y_{j}^{-W_{y_{j}}}/2}^{y_{j}^{+W_{y_{j}}}/2} \int_{x_{j}^{-W_{y_{j}}}/2}^{y_{j}^{+W_{y_{j}}}/2} G x, y; x', y' \ dx' dy' .$$

(1.42)

Using Green's function series expression from (1.38) in (1.42),  $E_z$  is

$$E_{z} x, y |_{\mathbf{J}=\mathbf{J}_{j}} = j\omega\mu \mathbf{J}_{j} \cdot \hat{z} \frac{1}{ab} \sum_{m} \sum_{n} \frac{4\sigma_{m}\sigma_{n}}{k_{x} k_{y}} \frac{\begin{bmatrix} \cos k_{x}x \cos k_{y}y \cos k_{x}x_{j} \cdot \\ \cos k_{y}y_{j} \sin\left(\frac{k_{x}W_{xj}}{2}\right)\sin\left(\frac{k_{y}W_{yj}}{2}\right) \end{bmatrix}}{k^{2} - \begin{bmatrix} k_{x}^{2} + k_{y}^{2} \end{bmatrix}}.$$

(1.43)

Using (1.43) in (1.40), the impedance is

$$Z_{ij} = -\frac{j\omega\mu d}{\frac{1}{ab}} \sum_{m} \sum_{n} \left[ \frac{4\sigma_m \sigma_n}{k_x k_y} \right]^2 \frac{\left[ \cos k_x x_i \cos k_y y_i \cos k_x x_j \cos k_y y_j \right]}{\sin\left(\frac{k_y W_{yi}}{2}\right) \sin\left(\frac{k_x W_{xj}}{2}\right) \sin\left(\frac{k_y W_{yj}}{2}\right) \sin\left(\frac{k_y W_{yj}}{2}\right)} \frac{1}{k^2 - \left[ k_x^2 + k_y^2 \right]},$$

$$Z_{ij} = j\omega\mu d \frac{1}{ab} \sum_{m=0}^{m=\infty} \sum_{n=0}^{n=\infty} \frac{\left[ \sigma_m^2 \sigma_n^2 \cos k_x x_i \cos k_y y_i \cos k_x x_j \cos k_y y_j \right]}{\left[ \sin\left(\frac{k_x W_{xi}}{2}\right) \sin\left(\frac{k_y W_{yi}}{2}\right) \sin\left(\frac{k_x W_{xj}}{2}\right) \sin\left(\frac{k_y W_{yj}}{2}\right) \right]}{\left[ k_x^2 + k_y^2 \right] - k^2}, \quad (1.44)$$

where,

$$\sigma_{m} = \begin{cases} 1 & ;m = 0 \\ \sqrt{2} & ;m \neq 0 \end{cases}$$

$$\sigma_{n} = \begin{cases} 1 & ;n = 0 \\ \sqrt{2} & ;n \neq 0 \end{cases}$$

$$k_{x} = \frac{m\pi}{a},$$

$$k_{y} = \frac{n\pi}{b}.$$

The m and n, in the impedance equation (1.44), stand for the  $TM_{z0,mn}$  modes with functional variation in the x and y directions, respectively. The equation for  $Z_{ij}$  shows its dependence on the location of the source and the observation port, and their dimensions, the cavity dimensions, the material properties, and the frequency at which the impedance is calculated. The low frequency behavior of the cavity is like a parallel plate capacitor which is given by the m=0 and n=0 mode. As frequency is increased, the distributed behavior of the cavity can be seen by the standing waves formed from the field reflections from the boundary. These resonances, related to the cavity dimensions appear in the self and transfer impedance as alternating poles and zeros. These are the propagating modes. Depending on the highest frequency of simulation and the cavity dimensions, only a certain set of modes will act as the propagating modes. The remaining modes are the evanescent modes which contribute to the self and mutual inductance. The transfer impedance is less sensitive to these evanescent modes, compared to the self impedance. Apart from rectangular geometry, similar expressions can be derived for triangular and circular shaped cavities as well [4], [5].

#### **1.2. THE VIA TO CAVITY CONNECTION**

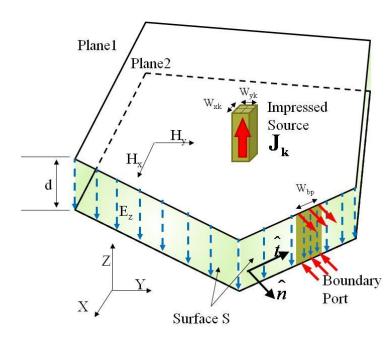

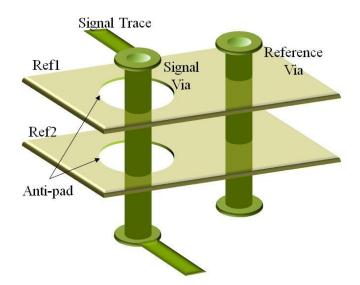

The via is an interconnect used between different layers of a printed circuit board (PCB). It connects or short circuits the copper regions of the same nets, lying on different layers. The geometry of a via is like a hollow metallic cylinder. The via is also known as a plated through hole (PTH). To create the via geometry, as a step in the manufacturing process of a PCB, holes are drilled at the specific locations on the PCB, and then plated with metal. Along the hole, the layers where metal is present in the form of area fills or trace pads, will form a connection to the plating of the hole. For the layers where no connection has to be made, the metal is etched away from the location of the hole. This may be done before the holes are drilled during the etching process, wherein the excess or undesired metal is selectively etched away. This region around the via with metal etched away to avoid connection is known as the anti-pad. A signal via connecting two traces is shown in the Figure 1.3, as it passes through two signal reference planes.

Figure 1.3. PCB geometry showing a signal via connecting two traces and a reference via. The two reference planes shown have anti-pads for signal via and no anti-pads for the reference via, thus controlling the connection to the via.

The metal on the reference layers is etched out at the location of the signal via, to ensure no connection. Thus two anti-pads are formed at the reference layers at the signal via location. Also, at the layer where the via is connected to the trace, pads are placed to ensure the trace-to-via connection while accounting for the drill location tolerance. The reference via has no anti-pads, and the via directly connects to the metal on reference layers.

The printed circuit boards built for RF applications or high-speed digital applications will usually have multiple metal layers, many of which are full plane layers formed of power or reference nets. Multiple vias may pass through these planes, some of which may be connected to the planes, and rest would have anti-pads around them. The high frequency currents on the vias are the surface currents oriented in the vertical or  $\hat{z}$  direction, as shown in the Figure 1.4. When a via and plane are not connected, i.e., an anti-pad is present at the plane layer, then the magnetic fields generated by the via currents will induce radial currents on the unconnected plane. For a via connected to the plane, depending on the current direction, the via current is either spreading into that plane or necking down from the plane into the via. These currents will cause magnetic fields within the parallel plate structure.

Figure 1.4. The via – cavity geometry with the electric field map and the magnetic field map is shown. The antipad has radial electric field and concentric magnetic field like a coaxial transmission line. The magnetic field induces radial current on the cavity planes in opposite directions.

The Figure 1.5 also shows the impressed current source placed in a cavity. The impressed current source forces a radial current on both planes, in opposite directions, and also results in a magnetic field which is concentric with the impressed source. The nature of the fields and the surface currents on the planes for the impressed current source shown in Figure 1.5 is the same as that for and the via geometry shown in Figure 1.4, outside the anti-pad region. Thus, the cavity model with an impressed current source at each via location can be used to model the plane-pair behavior. The expression for self and transfer impedance for any number of impressed current sources placed in a cavity was formulated in Section 1.1. As the Z parameters can be used as a network parameter block with a defined relationship between the voltages and currents for each port, the model including complete plane-pair behavior can be used for circuit analysis. Such an impedance block is referred to as the Zpp block or plane-pair impedance block in a cavity model. The Zpp block will have as many ports as the number of vias in the cavity. To perform circuit analysis, the via has to be connected to the Zpp block.

Figure 1.5. The magnetic field and the surface currents on the planes due to the impressed current source placed in the cavity at a via location. The surface current is shown for bottom surface of top layer and top surface of bottom layer. The magnetic field shown is inside the cavity.

The Zpp block has two terminals for each port. The two terminals of a Zpp port correspond to the terminals of the impressed current source in the cavity model. The terminal is a geometry feature where the voltage and current are defined. The impressed current source is defined between the two planes. The port voltage used in the formulation is the average voltage across the impressed source cross section and the port current is the current through the impressed source, which is the same as the current injected into a plane (spreading current) or the current necking into the source. Thus the terminals of this source lie, one on each plane, at the outer edge of the source, i.e. the circumference of the source, on each plane forms a terminal. The via, an electrically small hollow PEC cylinder, is considered as a single node for the purpose of circuit analysis. When the via is connected to a plane, this node is shorted to the Zpp port terminal for that plane. When an anti-pad is present between the via and a plane, there will be some capacitance between the via barrel and the plane surfaces. In this case, a capacitor is placed between Zpp port terminal for that plane appendix the via to plane capacitance calculation.

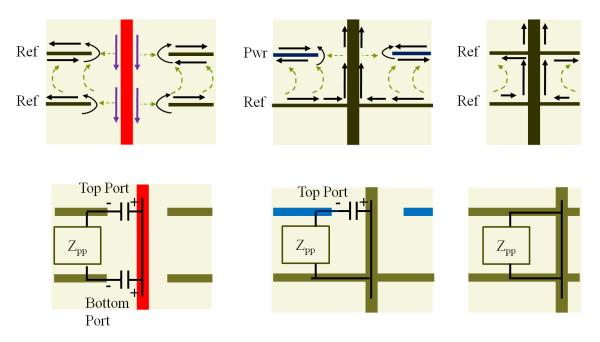

The Figure 1.6 shows three different geometry configurations, from left to right, for a via passing through a cavity, and the circuit connection of the via to the cavity port below the corresponding configuration. In the first configuration, a signal via passes through two reference planes, there is an anti-pad on both layers, and thus Zpp terminal to via node connection has a capacitor for each Zpp terminal. In the second geometry, a reference (REF) via passes through the power (PWR) and reference (REF) cavity, it is connected to the reference plane but has an anti-pad at the power plane. For the circuit model, the Zpp port terminal for reference plane is shorted to via, but the power plane terminal in connected to the via node through a capacitor. The third geometry is a shorting via, connected to both planes of the cavity. The Zpp port terminals are both connected to the via node, and thus short circuited.

All geometries discussed, were single-cavity geometries. This one cavity geometry will form the basic building block for analyzing complex stack ups. In most cases, many cavities are stacked vertically to form a multi-layered structure. Current can flow along the via surface from one cavity to another, where an anti-pad exists. Across the anti-pad, for current flowing along the via outer surface, the electric field is radial

Figure 1.6. Zpp port to via connection is shown for three different geometry configurations. Each geometry with the current map and the circuit model is shown below it. If an anti-pad exists between the via and the plane, then the via is connected to the Zpp port terminal through a capacitor, else the via is short circuited to the Zpp port terminal.

from the via to the anti-pad edge, and the magnetic field goes in concentric circles around the via barrel, as shown in Figure 1.4. The field map represents those of a coaxial transmission line. Thus the voltage across the anti-pad and the current flowing through it can be well defined, allowing a port definition at this location. This port is calle a via port. The positive terminal is the outer surface of via barrel at the anti-pad, i.e., anti-pad inner edge, and the negative terminal is the anti-pad outer edge at the plane. These ports exist at each anti-pad, across the capacitor, e.g., Figure 1.6 shows the model with via ports at each anti-pad. The via port acts as an external port for characterizing the via geometry, and is also used to connect this model to other models by enforcing voltage and current continuity. These ports are used for modeling the multilayered structures, where the cavities are connected vertically at these via ports, as shown in Section 1.4.

#### **1.3. CALCULATING THE VIA TO PLATE CAPACITANCE**

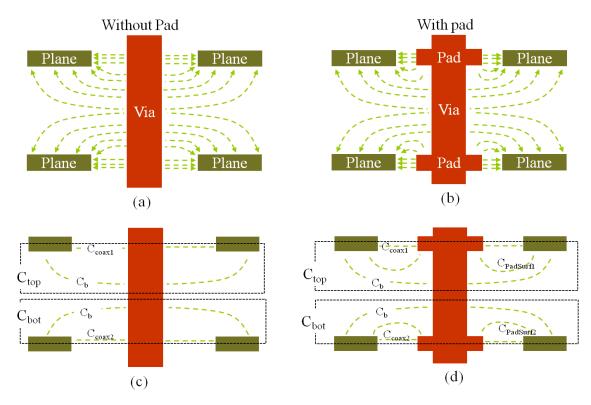

As explained in Section 1.2, the via connection to the cavity model Zpp is through a capacitor, where the anti-pad occurs. The capacitance between the via and the unconnected plane can be divided into different parts as shown in Figure 1.7. The accuracy of the capacitance calculation will affect the final result of the network parameters, depending on the geometry being analyzed. This makes the capacitance calculation important for the entire model.

Figure 1.7. Electric flux lines between the via and the planes of the cavity are shown for via without pad and with pad cases. The capacitance is grouped  $C_{top}$  with top plane and

C<sub>bot</sub> with bottom plane. Both groups have one capacitance from via barrel to plane horizontal surface and another capacitance between the curved surfaces of the anti-pad.

As per Figure 1.7, one part of the capacitance exists between the via barrel and the top plane's bottom surface, and similarly between the via barrel and the bottom plane's top surface, named as C<sub>b</sub>. This part depends on the anti-pad size, via drill size,

and the height of the cavity formed by this plane with other planes above and below it. There is another part of the capacitance in the anti-pad region,  $C_{coax}$ , which can be calculated as coaxial capacitance, which depends on the plane thickness, anti-pad size, and via drill size. When a pad is present on the via at the plane layer, the capacitance from the top and the bottom surfaces of the pad, to the plane surface,  $C_{padsurf}$ , needs to be accounted for.

In Figure 1.7a and Figure 1.7b, the geometry for and electric flux map is shown for case without pad and with pad respectively. In the Figure 1.7c and Figure 1.7d the capacitance is divided into pieces. The capacitances are calculated as individual pieces and then added up to get the value of capacitor to be connected together cavity port and the via. The capacitance between via and top terminal of the cavity port is given in equation (1.45). The capacitance between bottom plane terminal of the cavity port and via is given in the equation (1.46).

$$C_{top} = C_b + \frac{1}{2}C_{coax1}$$

(1.45)

$$C_{bot} = C_b + \frac{1}{2}C_{coax2}$$

(1.46)

The same two capacitances, for the case with pad is given as follows.

$$C_{top} = C_b + \frac{1}{2}C_{coax1} + C_{PadSurf1}$$

(1.47)

$$C_{bot} = C_b + \frac{1}{2}C_{coax2} + C_{PadSurf\,2}$$

(1.48)

The capacitance for the coaxial region is shared by the cavities above and below the plane. There is a capacitor connecting the via to each cavity impedance block. So, half of the anti-pad capacitance value is used in each capacitance. Eventually, they appear in parallel and get added up.

For fast computation an analytical formulation [6] was used. This method provided the required accuracy for via barrel to plane capacitance geometry. However the result was found to be less accurate when a pad would be present on the via, at a plane layer. Also, the capacitance from a signal layer pad to the planes was not accounted for in this formulation. Thus to improve the accuracy of the capacitance calculation, a new approach used. A 2D FEM tool [7] was used. The FEM method, would use cylindrical symmetry to get the capacitance between the via and the planes. This method accounts for the capacitance due to pads on any layers.

#### **1.4. VIA MODEL FOR MULTILAYERED PCBS**

To extend the model to multi-layered structures, segmentation approach is used [2]. The practical PCB has many cavities of irregular shapes and formed over a multilayer stack up. The coupling between vertically stacked cavities is through the voids in the metal planes, like anti-pads or splits (gaps). The voids in the planes may also result in cavities between the non adjacent layers.

The cavities which are stacked vertically couple through the anti-pad region. For connecting cavities in the vertical direction, a via port is defined in every via anti-pad region, between the cavities to be connected. Section 1.2 explains in detail how a via ports is defined at the anti-pad. Corresponding ports from two cavities are connected together, to enforce voltage and current continuity between cavities stacked on top of each other. Due to the current and voltage continuity at the circuit level, there is electric and magnetic field continuity at the field level, as the voltage and currents at the ports are well defined from the fields. As the continuity is enforced the coupling through the antipad is accounted for in the model.

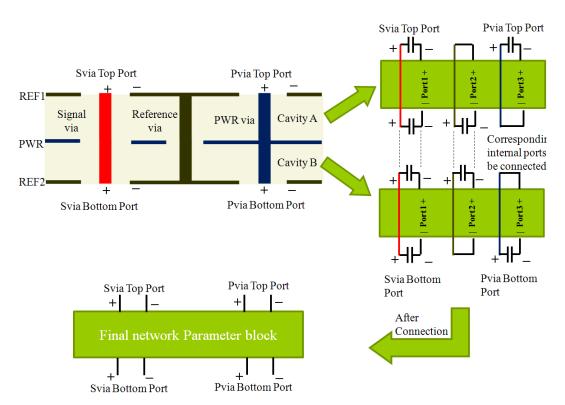

The Figure 1.8 shows the connection of vertically stacked cavities. The geometry shown has two cavities with three vias, one each of the type signal, reference and power. The stack up has a power plane between two reference planes. The circuit model for each cavity is shown to the right of the geometry. The vias are connected to the network parameter block (Zpp) port terminals through a capacitor, where anti-pad is present and short circuited where a connection is present from the via to the plane. Thus individual circuit models of each cavity are formed. These individual circuit models can be connected together at the via ports defined across the same anti-pad, in the geometry.

Then, a final circuit model is obtained for the entire (two cavity) geometry, which can be simulated to get the required network parameter matrix.

Figure 1.8. Connecting the cavities stacked vertically. Geometry shown has two cavities with three vias. The two cavities are modeled individually first and then connected at the corresponding via ports of the same anti-pads to get the complete multilayer model.

The irregular shaped cavities are segmented into regular shapes like rectangles and triangles. There exist closed form expressions for the cavities with regular shapes. Many boundary ports are defined along the boundary of these regular shaped cavities and they are solved for the impedance matrix. These cavities are then assembled together by connecting the corresponding boundary ports defined along the edges of these cavities. Thus continuity is enforced along the edges for these cavities using boundary ports which stitch together the smaller cavities to form the irregular shaped cavity. Thus it is possible to connect the cavities laterally and vertically. These techniques are used together to model the entire multilayered printed circuit board.

#### **1.5. MODELING EXAMPLES**

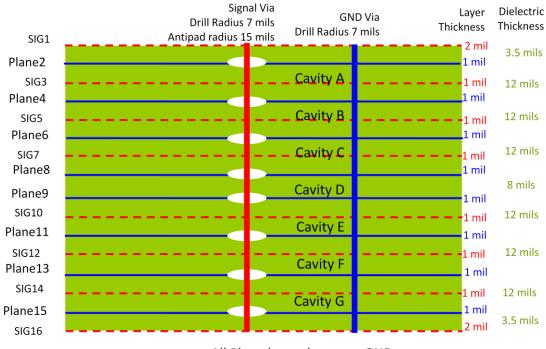

The results of this modeling technique are compared with measurements for practical geometries, designed and implemented by Giuseppe Selli. The geometry structures are multilayered via structures which were designed to model practical PCB scenarios. Following subsection explains the geometry of these test vehicles, the calculation of the impedance matrix and the anti-pad capacitance, the spice like model assembly in ADS, and validation of the modeling results to some practical measurements. Some expectations from the model for the given geometry and inferences from the comparison are also shared. The stack up is shown in Figure 1.9.

All Plane layers have net GND

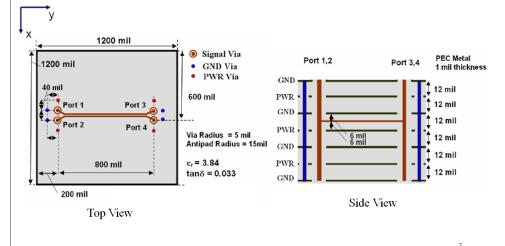

Figure 1.9. Common stack up for all test vehicles is shown. It has eight plane layer forming seven cavities. All cavities are 12 mils thick except center cavity, of 8 mil thickness.

There are 7 cavities, formed by 8 plane layers. Center cavity has 8 mil thickness, and does not contain a signal layer. All other cavities have 12 mil thickness and contain

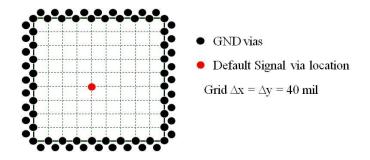

signal layer for trace connection to the signal vias. All plane layers are ground layers and connected by a shorting via cage, as shown in top view of one of the structures in Figure 1.10. The cage is formed by two rows of vias which are offset by half via pitch, i.e., offset by 20 mils. The signal layers include a trace which connects these shorting via rows. Thus, the shorting via cage forms a PEC boundary around the cavities. The PEC boundary will help isolate individual geometries, and help define the spatial simulation domain for the cavity model.

Figure 1.10. A GND via cage is formed by two rows of vias offset by 20 mils. The vias inside the cage lie only the grid locations with pitch 40 mils. The default signal via location is shown by a blue dot.

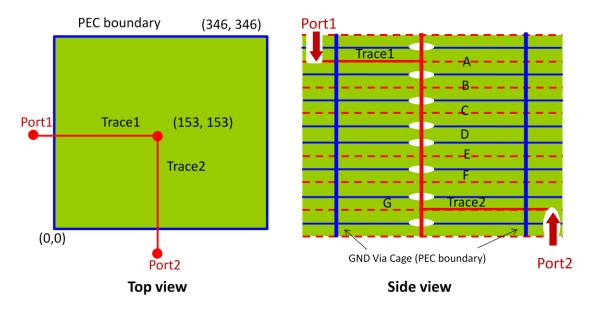

The via structures under study are placed close to the center of this cavity. There are 5 via structures of interest which will be used for simulation and measurement comparison. These will be referred to as Example 1, Example 2, and so on till Example 5. All vias in the geometry are placed on a grid with pitch 40 mils, as shown in Figure 1.10. The geometry for each case is shown from Figure 1.11 onwards. The Example 1 geometry, shown in Figure 1.11, has one signal via placed close to the center of the cavity, with a trace connection in the top cavity, cavity A and the bottom cavity, cavity B. The measurement is across two ports, from a trace port in cavity A to a trace port in cavity G. The Example 2, geometry shown in Figure 1.12, has one signal via as in the case of Example 1 but, the traces are connected to the signal via in the top cavity, cavity A and the second cavity, cavity B. The measurement is performed at two trace ports in cavity A and cavity B. The signal via, in this case, has a long stub, and its effect is

expected to be seen in the simulation results and measurements. The Example 3 geometry is shown in Figure 1.13. This case is the same as Example 1 with a GND via placed close to the signal via. The Example 3 has the same signal via and traces as the Example 1. The results from measurement and simulations show the effect of the GND via placed close to the signal via when compared to Example 1.

Figure 1.11. Example 1 geometry shows one signal via with trace connection in top and bottom cavity.

The Example 4 and 5 are used for four port measurements. In Example 4, shown in Figure 1.14, has two signal vias, placed near the center of the cavity. The signal vias are connected to a trace each in the top cavity, cavity A and the bottom cavity, cavity G. The measurement is performed at the trace ports in the top and bottom cavities. The measurement will give insertion loss and return loss as in the previous cases, and also the near end cross talk (NEXT) and far end cross talk (FEXT). Example 5 geometry is shown in Figure 1.15. The geometry in this case is the Example 4 geometry with two GND vias placed close to the signal vias. The same measurements as in the case of Example 4 are performed.

Figure 1.12. Example 2 geometry shows one signal via connected to traces in first and second cavities. This case has a long stub as compared to Example 1.

Figure 1.13. Example 3 geometry a signal via and a signal return via location. The signal transition is from top cavity to bottom cavity. This is Example 1 geometry with a close signal return via.

Figure 1.14. Example 4 geometry shows two signal vias with trace connection in top and bottom cavities. The traces are orthogonal in orientation.

Figure 1.15. Example 5 geometry shows the same geometry as Example 4, with two signal return vias.

The expression for PEC boundary Zpp is similar to the PMC boundary, except the boundary condition that, E field has to be zero along the boundary. The PEC boundary  $Z_{ij}$  expression is

$$Z_{ij} = -j\omega\mu d \frac{1}{ab} \sum_{m=0}^{m=\infty} \sum_{n=0}^{n=\infty} \frac{\left[ \frac{\sigma_m^2 \sigma_n^2 \sin k_x x_i \sin k_y y_i \sin k_x x_j \sin k_y y_j \cdot \left[ \frac{k_x W_{xi}}{2} \right] \operatorname{sinc} \left( \frac{k_x W_{xi}}{2} \right) \operatorname{sinc} \left( \frac{k_x W_{yj}}{2} \right) \operatorname{sinc} \left( \frac{k_y W_{yj}}{2} \right) \right]}{k^2 - \left[ k_x^2 + k_y^2 \right]}$$

(1.49)

Where,

$$\sigma_m = \begin{cases} 1 & ;m = 0\\ \sqrt{2} & ;m \neq 0 \end{cases}$$

$$\sigma_n = \begin{cases} 1 & ;n = 0\\ \sqrt{2} & ;n \neq 0 \end{cases}$$

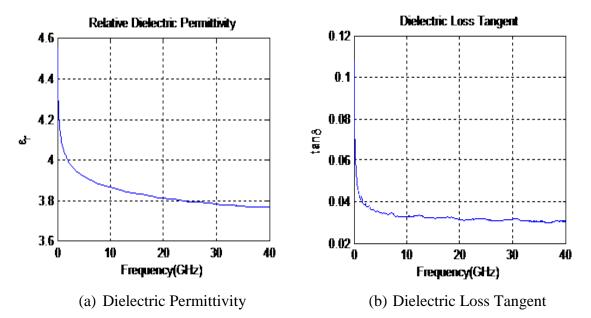

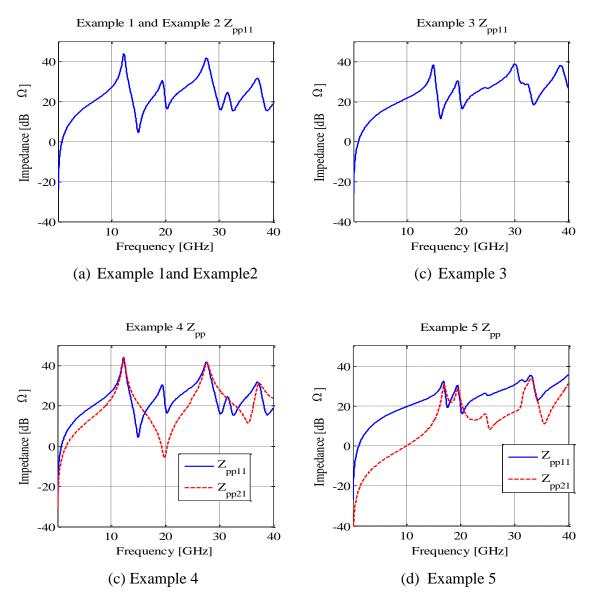

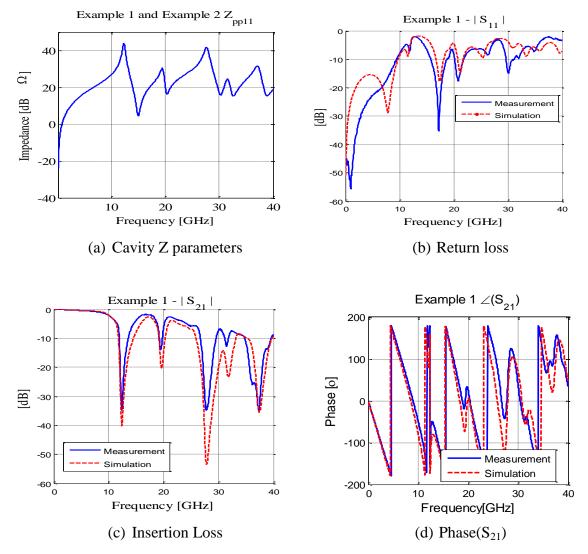

EZPP 118 with PEC boundary is used for Zpp calculation for all models. The boundary is placed at the inner edge of the GND via cage. The dielectric properties of the material were extracted from the measurements by Giuseppe Selli, are plotted in Figure 1.16. These frequency dependent values of relative permittivity and loss tangent are used as input parameters to EZpp during the calculation. The Z parameters for the cavity ports for Example 1 through Example 5 are shown in Figure 1.17. The Zpp is expected to start with an inductive 20dB per decade slope as the boundary is PEC boundary. The  $Z_{11}$  for the Example 1 and Example 3 show the effect of a shorting via, close to observation port. This is seen on comparing the parts (a) and (b) of the Figure 1.17. The inductance at low frequency is reduced when a GND via is placed near the observation port. Example 4 geometry has no GND vias placed close to the signal vias. In Example 5 two GND vias are placed next the signal vias. The self inductance and the transfer inductance at low frequency are both reduced when the two GND vias are placed close to the signal vias.

Figure 1.16. Dielectric properties of the test vehicles extracted from measurements.

The capacitance values for the model are calculated with CST EM studio and Hanfeng Wang's 2D FEM code. The two sets of values are very close and the simulation results were found to be the same for both sets. The capacitors from adjacent cavities are lumped, so only three values of capacitors are required. The capacitors connecting the cavity terminal to via at the top plane and bottom plane have capacitance, due to barrel, pads, and top and bottom stubs, equal to 104fF. The capacitance for the centre cavity port terminals to the via, which is smallest due to the shorter center cavity height, is 89fF. The capacitors connecting the via to all other cavity port terminals is 99fF.

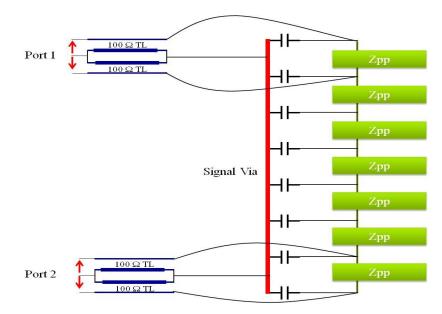

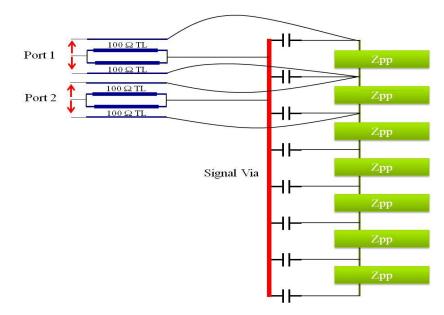

ADS is used for connecting the model together in a network fashion. The circuit model used for each example will change according to geometry being modeled. The Zpp is converted into S parameters, and used as S parameter blocks in the ADS network. As both terminals are needed, a differential design kit is used in ADS to access both the terminals of each port in Spp (derived from Zpp) network block. The model for Example 1 and Example 2 are shown in Figure 1.18 and Figure 1.19, respectively. The Zpp blocks used here have a single port as there is just one via. The model for Example 3 is shown in Figure 1.20, which has the Zpp blocks with two ports. In the model, the second via is a GND via which is modeled by shorting both terminals of that via port.

Figure 1.17. Z parameters for Zpp of cavity used in (a)Example 1 and Example 2, (b) Example 3, (c)Example 4, and (d) Example 5. As the cavity boundary is PEC, the low frequency behavior in inductive. The effect of close shorting via is seen as reduction in low frequency inductance from Example 1 to Example 3 and also from Example 4 to Example 5.

The difference between the Example 1 and the Example 2 models is the shifting of trace connection from last cavity to the second cavity. This is in direct correspondence to the geometry change between the two cases.

Figure 1.18. The circuit model for Example 1 shows Zpp blocks with one port, connected to the via. The traces, implemented using two inverted 100  $\Omega$  microstrips, in top and bottom cavities are connected in the Ad hoc fashion.

Figure 1.19. The circuit model for Example 2 shown is similar to Example 1 circuit except, the trace from bottom cavity is moved up to the second cavity. Like Example 1, the Zpp blocks have one port connected to the signal via and the traces implemented using two inverted 100  $\Omega$  microstrips.

Figure 1.20. The model for Example 3, shown, is the Example 1 circuit model, with the Zpp blocks with two ports. For Example 3, a ground via connected to a second Zpp port.

The Example 4 model, shown in Figure 1.21, also uses a two port network parameter block, but both vias are signal vias and are connected to the traces in the top and bottom cavities. The Figure 1.22 shows the model for Example 5, which has two signal and two GND vias, with the 4 port S parameter block. The port terminals for shorting vias or GND vias are connected together. Signal vias are connected in the same manner as in the Example 4.

The model also contains traces which are transmission line sections used from ADS component library. The stripline model and its connection were implemented by Giuseppe Selli. The stripline is modeled as two inverted microstrip transmission lines. Two ports of microstrips have their positive terminals shorted together, which is the trace terminal, and is connected to the signal via. The reference terminals of the microstrips are the same as the planes of Zpp and so these are connected to respective plane terminals of network parameter block. The signal via has an anti-pad with both planes, so the via is also connected to the planes with capacitors as explained in previous sub-sections. The microstrip traces have an impedance of  $100\Omega$ , so in effect they model the  $50\Omega$  trace. Each microstrip is given the same AC source so as to excite the two traces symmetrically.

Figure 1.21. The circuit model for Example 4 shows Zpp blocks with two ports, connected to two signal vias. Traces are connected to both the signal vias at top and bottom cavities and, implemented in a similar manner as Example1.

Figure 1.22. The model for Example 5, shown, has the Example 4 model, with the four port Zpp blocks, where two ports are used to connect to ground vias, and two ports are connected to signal vias as in Example 4.

The insertion loss for the Example 1, shown in Figure 1.23, and the Example 3, shown in Figure 1.25, match relatively well compared to the Example 2, shown in Figure 1.24. The return loss comparison has not been successful, for low frequencies. It is observed that the impedance of the cavity, shows poles at which the cavity will offer a very high impedance. From the models in Figure 1.18, the Zpp occurs in series for the return current path of the via current.

Figure 1.23. Example 1 results from measurement and simulation are shown: (a)Zpp from cavity model,(b)Return loss, (c)Insertion loss (d)Phase of S21. It shows the dependence of return loss peaks, and insertion loss nulls on the corresponding poles of cavity Zpp.

At the frequencies where a pole occurs in cavity impedance, the signal will see high impedance in the return path, causing a loss in the transmitted signal from one port to another. This is observed by the corresponding nulls in insertion loss. Also, the return loss shows peaks at these frequencies, indicating the reflection of the signal from the high impedance path.

Figure 1.24. Example 2 results from measurement and simulation are shown: (a)Zpp from cavity model,(b)Return loss, (c)Insertion loss (d)Phase of S21. A large stub resonance and less effect of Zpp on results, as compared to Example 1 can be observed. This can be explained by Example 2 geometry having a large stub and signal transition from first cavity to second only, as compared to no stub and top to bottom cavity transition in Example 1.

The measurement and the simulation results agree well at this resonance and confirm the physical reasoning. The Example 2 simulation results and measurements show a very strong null in insertion loss and corresponding peak in return loss, which occurs due to the via stub from present in the geometry. The observation that the poles of cavity impedance cause nulls in the insertion loss, holds true for Example 2. The effect of cavity impedance has reduced in this case, as there are less number of cavities in series path from one port to the other.

Figure 1.25. Example 3 results from measurement and simulation are shown: (a)Zpp from cavity model,(b)Return loss, (c)Insertion loss (d)Phase of S<sub>21</sub>. The Example 3 is the same as the Example 1 geometry with a ground via, and this is seen in the reduced low frequency inductance in Zpp and improved bandwidth seen in the insertion loss, as compared to Example 1 results.

The Example 3 can be compared to the Example 1 as the only difference is the return via placed close the signal via. The Example 1, cavity impedance shows an inductive region in low frequency. This is caused by the conduction current in the cavity travelling along the planes to the PEC boundary, and then returning on the other plane. The return current is conductive till the frequency reaches the first pole in cavity impedance, past which the return current is displacement current through cavity capacitance. When a shorting via is added close to the signal via, majority of the conduction current will use the shorting via as return current path instead of the PEC boundary, thus reducing the return current inductance and pushing the pole to a higher frequency. In terms of link path, this change will increase the bandwidth of the channel, as evident from the results in Figure 1.25.

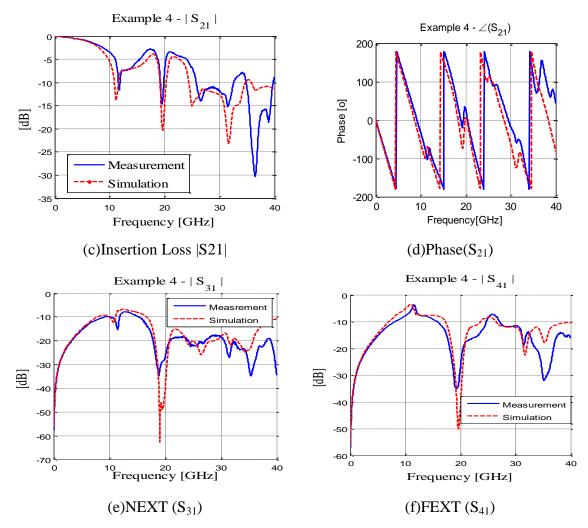

The Example 4 and Example 5 are four port networks and the comparison results for modeling and measurements are shown in Figure 1.26 and Figure 1.27 respectively. The return loss and insertion loss for Example 4 and Example5 will be similar to the Example 1 and Example 3 results. The same trend of improvement in the insertion loss is seen from Example 4 to Example 5 due to the change in the return current path.

Figure 1.26. Example 4 results from measurement and simulation are shown: (a)Zpp from cavity model,(b)Return loss, (c)Insertion loss, (d)Phase of S21, (e)NEXT, (f)FEXT. The insertion and return loss are dependent on the cavity  $Z_{pp11}$ , and the NEXT and FEXT are more dependent on cavity  $Z_{pp21}$ .

Figure 1.26. Example 4 results from measurement and simulation are shown (cont.)

In this case, the improvement is seen easily as there are two close return current vias instead of one. The effect of self impedance of cavity port at the via location, on the return loss and insertion loss is due to the same physics as explained for Example 1 and Example 3.

The geometry in Example 4 and Example 5 is ideal for studying coupling between vias in the cavity. The traces connecting the vias are routed orthogonally to reduce any coupling through the traces. Hence, the NEXT and FEXT will depend on the mutual coupling of the signal vias inside the cavity. The transfer impedance of the cavity, from port at one signal via to another, will dominate the coupling between the two vias. The

results for the Example 4 show that the zeros in the transfer impedance of the cavity, translate into zeros in the NEXT shown by  $S_{31}$  and FEXT shown by  $S_{41}$ . For the poles of transfer impedance, there exist poles in FEXT. On the other hand, NEXT is seen not to depend completely on the transfer impedance, as the poles are not reproduced here. Then as two signal return, or shorting vias are added close to the signal vias, for the Example 5, the self and transfer impedance changes drastically, and so the effect is seen in NEXT and FEXT also

The results of the simulation and measurement show similar trends for all cases. Some differences in return loss are caused for all cases due to the measurement techniques or physical phenomena not accounted for, in this particular modeling technique. The agreement for most cases is proof that the model had accounted for all the relevant physics involved in the via transition.

Figure 1.27. Example 5 results from measurement and simulation are shown: (a)Zpp from cavity model,(b)Return loss, (c)Insertion loss, (d)Phase of S21, (e)NEXT, (f)FEXT. The Example 5 geometry is same as the Example 4 geometry with two close return vias. Thus the improvement in bandwidth and reduced influence of Zpp can be observed when compared to the Example 4 results.

Figure 1.27. Example 5 results from measurement and simulation are shown (cont.)

## **1.6. NEED FOR A TOOL**

The comparison of measurements with modeling results shows that the model can be used to obtain network parameters for complex geometries present on the PCBs. The method is quicker than a full wave model and gives a good comparison to measurement. Thus, it can be used for checking a design before having it built and measured. An accurate model for via and cavities, will find a variety of applications. But the complex calculations and assembly in a spice like software will require some familiarization with the process. To make the via model, available to the design engineers, as a fast calculator or a quick utility to check their designs, a tool called Multilayer Via Transition Tool (MVTT) has been development at the EMC laboratory at Missouri S&T, by Zhenwei Yu and Dr Jun Fan. The tool can read a text file with all geometry information and user requirements. It then calculates the impedance matrix for each cavity, with all the required set of internal and boundary ports. Then the anti-pad capacitance is calculated and vias are connected based on netname information from the text file. The tool then uses voltage and current continuity at the ports to snap together the entire model. At this stage, it is able to connect multi-conductor transmission lines and external components to the model. Thus the whole process of modeling multilayered PCBs with multiple vias, has been automated.

The MVTT has reduced the burden on the user to perform each step of the modeling process. The user has to provide the geometry needed to be modeled. The Section 2 will explain in detail about a graphic user interface of this tool.

#### 2. MVTT GRAPHIC USER INTERFACE

The Multilayer Via Transition Tool (MVTT) is a quick computational utility which can be used to analyze a complex PCB geometry very fast as compared to other tools present in the industry today. The speed and accuracy of the tool are two very important features which give it an advantage over other similar tools. From the user point of view, the time invested in building the geometry in the tool and effectiveness with which the user utilizes the computational ability of the tool are also very important and directly dependent on the design and functionality of the User Interface (UI). Thus the development of the UI becomes very important from the point of view of application and widespread utility of the tool. This section explains the process of designing the graphic user interface (GUI) for the MVTT in Matlab. This section deals only with design and is not intended to serve as a user manual. For this purpose, the 'Quick Start Guide' for the MVTT GUI is placed in the appendix.

#### 2.1. INSIGHT INTO GUI DEVELOPMENT FOR MVTT

As explained in Section 1.6, the MVTT is a fast calculator of network parameters, for a PCB geometry. The MVTT is by itself a design aid, which can replace the full-wave tools for the application with some limitations. To be as successful, the MVTT has to go through an engineered tool development. An integral part of this tool development is User Interface (UI) development, as the usefulness of this tool depends to a great extent on the convenience with which a user can communicate with this tool. There are various options to simplify the communication process. Some tools used command prompt, which is a more primitive user interface. Some tools still use text files, which are mostly the SPICE based tools. But the most user friendly one is the Graphic User Interface (GUI).

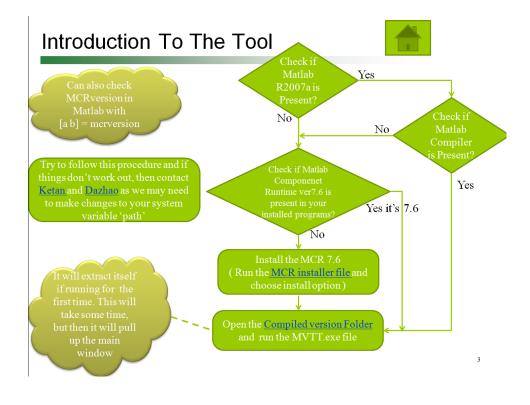

The MVTT engine (also referred to as the 'kernel' which is the main computational part of the tool) was designed to work with a text file input. Thus, the engine is designed to directly run with an input file, without a GUI. The text file is, however, difficult to build from scratch for a new user and thus a GUI would make it more convenient for the user to run the tool. Thus, at this stage, a simple GUI was required, which could easily interpret the user inputs and output a text file, which could be used with the engine. But, a simple GUI would mean it may not support all the features of the engine. Thus, the features deemed too difficult to implement in the basic GUI, would still be accessible through the text file interface, which was considered to be convenient for an advanced user.

The MVTT development was initiated in Matlab. For the computational part, or engine, using the Matlab programming environment is the obvious choice with the numerous scientific toolboxes present in the coding environment. Matlab has a Graphic User Interface Design Environment (GUIDE), a Java based utility, which is helpful in building simple GUIs. It provides some convenience in creating a GUI but does not offer complete control to the programmer. As the engine is Matlab based, having a Matlab based GUI can help overcome any interface issues. Thus, Matlab was chosen to start the GUI development.

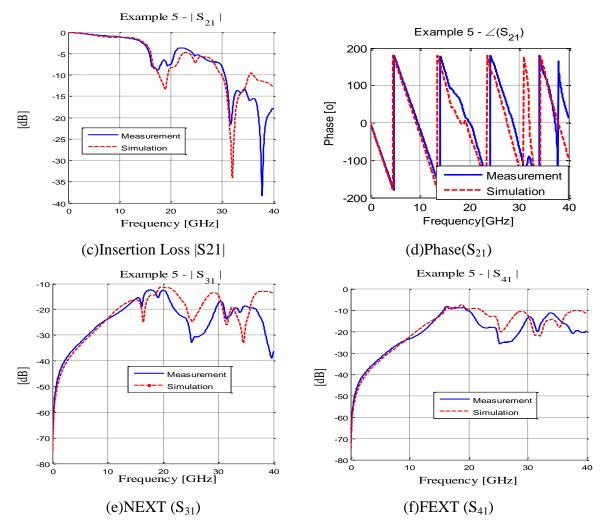

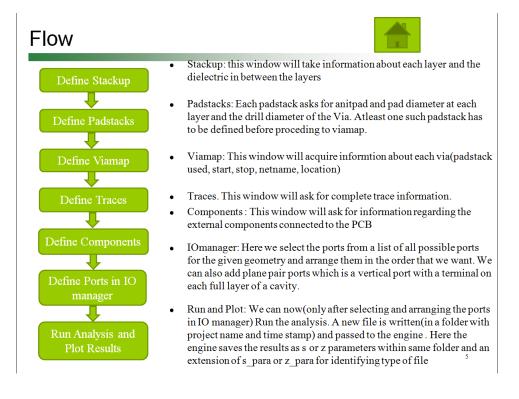

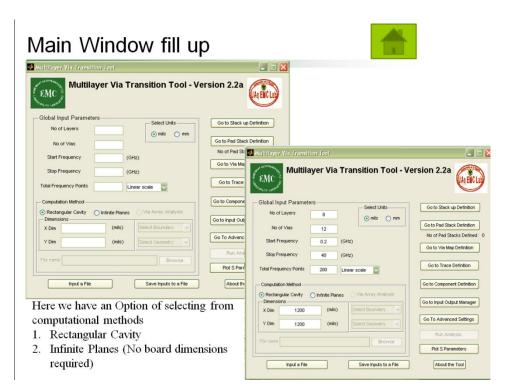

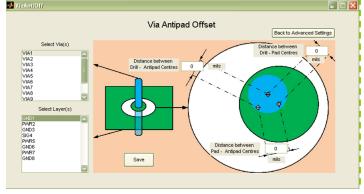

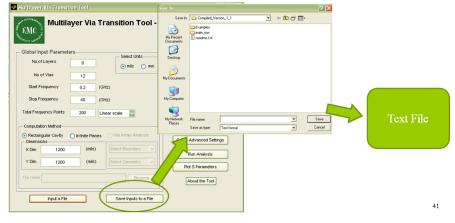

For the MVTT, all the inputs are required up front before any computation can be performed. Then the results are available to the user after the engine finishes its calculations. These results are available for viewing in the GUI. Thus, the tool flow could be represented as shown in Figure 2.1. First the geometry definition is completed by the user. Here the user interacts with the GUI alone. Then in the next step, the GUI generates a text file with the user inputs which is passed on to the engine. The engine then computes the desired results, and outputs the touchstone network parameter files. Then, these results are made available to the user through the GUI. This flow also allows a simple text file interface to the engine.

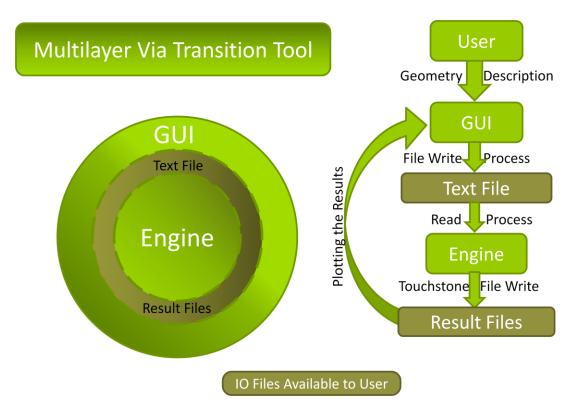

### 2.2. GUI DESIGN

The most basic aim of the GUI is to accept all the inputs (requirements) from the user and then pass them over to engine. This set of requirements can then be arranged into a flow which helps to simplify the process of accepting inputs. To obtain these set of requirements, it is essential to understand the projected functionality of the engine. An understanding of the engine would present a scope of the expected user inputs and the fine tuning required by the user to better control the results from the engine. Figure 2.2 shows the functionality of by the Multilayer via transition tool.

Figure 2.1. Flow used by the MVTT is shown. The tool has an engine and a GUI developed such that they can be independently used. The user provides the geometry description to the GUI, which then generates a text file in a format read by the engine. After processing, the engine writes the network parameter file in touchstone format which user can view using the GUI.

The GUI for such a tool, as MVTT, can become very complicated due to the vast scope of inputs and with the different features of the engine, available to tweak the simulation. The GUI is required to be organized in a manner that the user finds it intuitive while navigating through it. For this reason the organization of the GUI is very close to the physical geometry features and processes involved in the PCB manufacturing.

The inputs can be grouped into sets based on geometry features present in the PCB, which the user wants to simulate, as well as, ports and settings. The grouping of inputs required by the tool is,

- Geometry

- o Stackup

- o Padstack

- o Vias

- o Traces

- o Components

- Port Definitions

- Simulation settings

- Advanced Settings

Figure 2.2. Functionality of the MVTT is shown. The tool can process the listed geometries from a PCB. Results are calculated for the different kinds of user defined ports as shown. It allows for simulation with Open or PML boundary. The engine features, not implemented in the GUI are also listed.