Journal of Engineering and Technology

# OPTIMIZATION OF GATE RECESS STEP AND ELIMINATION OF THE DOME EFFECT FOR HIGHLY RELIABLE AND REPRODUCIBLE NOVEL PHEMT DEVICE

M. Mohamad Isa<sup>1\*</sup>, N. Ahmad<sup>2</sup>, F. Packeer<sup>3</sup> and M. Missous<sup>4</sup>

<sup>1,2</sup> School of Microelectronic Engineering, Universiti Malaysia Perlis, Pauh Putra Campus, 02600 Arau, Perlis, Malaysia.

<sup>3,4</sup> Microelectronics And Nanostructures (M&N) Group, School of E&EE, The University of Manchester, M60 1QD, United Kingdom.

### **ABSTRACT**

We report a comprehensive etching study on the gate recess-processing step in novel pseudomorphic High Electron Mobility Transistor (pHEMT) fabrication. The experiments focused on the etchant composition and elimination of the cap layer residue (Dome Effect) at the etching trenches. The optimised processing flow using highly selective Succinic Acid is aimed for moderate cap layer etching, with an etching rate of 240 Å/min and InGaAs-InAlAs selectivity of 140. The percentage of the Dome height to etching depth is 30%, consistent throughout the etching surface, however, can be further improved by controlling the etching time to the etch-stop layer. The optimised processing steps will enhance the device's robustness, especially in the complete processing steps for Monolithic Microwave Integrated Circuit (MMIC) fabrication, tailored for high-gain and low noise in satellite communication applications.

**KEYWORDS:** PHEMT; schottky contact; ohmic contact; MMIC; 2-DEG; pseudomorphic

## 1.0 INTRODUCTION

Over the past decade, Silicon based devices have served their purposes as the main components in universal electronic gadgets and appliances. However, the demands for better RF and microwave performances in today's applications have shifted the designer and manufacturers' attention to more advanced materials, such as III-V compounds (Lidholm, 2005; T. E. Whall, 1998). InP pseudomorphic High Electron Mobility Transistor (pHEMT) for example, has proven itself to be the best three-terminal device for this purpose, especially for low noise applications at 2 – 1000 GHz (Rodwell et al., 2010). Certainly, the III-V materials are the potential candidates in the post sub-22 nm node (Smith et al., 2001). The excellence in high-speed and low-noise characteristics are the resulting from the progression in consecutive layers of wide and narrow bandgap single crystal material growth using advanced technology such as Molecular Beam Epitaxy (MBE) (Bauer & Schäffler, 2006; Kuech, Jha, Kuan, Babcock, & Mawst, 2009; Osbourn, 1982).

<sup>\*</sup> Corresponding Email: muammar@unimap.edu.my

Similar to other three-terminal field effect transistor family, the pHEMT's gate is used to control the current flow between Source (S) and Drain (D) (Chau, 2007). The control mechanism is done by manipulating the Schottky contact between the gate metal and larger band gap Schottky barrier layer. Such contact is made by etching the gate structure (gate recess process) at the narrow band gap cap layer, which conceal and protect the semiconductor surface. The narrow band gap layer also acts as the metal penetration layer in the formation of Ohmic S-D contacts.

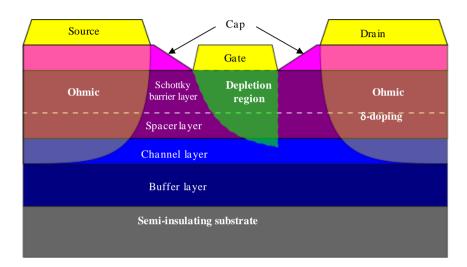

Figure 1. Conventional pHEMT epitaxial layer

Here, the narrow and wide band gap materials are made of lattice matched InGaAs and InAlAs compounds, respectively.

For the conventional pHEMT epitaxial layer as shown in Figure 1, it is important to have a clean and a good gate etching profile at the gate trenches. Incomplete cap layer etching will leave cap layer residue at the gate opening, and subsequently forms an unwanted Ohmic contact at the gate after metal deposition. The consequences of this contact-switch can be seen by the gate leakage current, whereby the carrier in the channel can easily slip to the outside circuit through the unwanted metal-residue contact. Moreover, a previous study has shown that the gate recess depth and width has a substantial effect on the device's threshold voltage  $(V_{th})$ , pinch voltage  $(V_{P})$  and drain-source current  $(I_{DS})$  (Oh et al., 2004).

Due to the importance of this step, it is therefore reported in this paper the comprehensive study on the gate recess process. Even though almost similar experiment has been reported elsewhere (Broekaert & Fonstad, 1992; Fourre, Diette, & Cappy, 1996; Lin, Ma, & Lin, 2011), the information is limited only to the selection of etching agents and etching profiles. Therefore, in this paper, we present an extensive study of the etchant preparation, and the effect of each compound in the mixture on the etching profile. Another significant finding in our work is the formation of "hump" at the etching structure, which directly correlate to the quality of the device's Schottky gate contact.

In order to achieve that, it is also important to choose the suitable etching agent that is highly selective and can give high reproducible results. Even though the successfully fabricated devices have shown excellent DC and RF-performances, the commonly used

Adipic Acid etchant has both process repeatability and reliability issues (Bouloukou, Sohib, Kettle, Sly, & Missous, 2006). In contrast, Succinic Acid (SA) is a more favourable solution due to its high selectivity and highly reproducible result (Lin et al., 2011). Thus, parallel experiments are also being performed to investigate the etch rate and selectivity study of SA, so that the etching process is not affected by time and process variations.

### 2.0 SAMPLES PREPARATION

The initial experiments were conducted using two types of lattice match samples; the bulk cap layer (InGaAs) and bulk Schottky layer (InAlAs), which are labelled as VMBE #1593 and VMBE #1594, respectively. The epitaxial structures for both samples were grown using MBE on a RIBER V100 System at The University of Manchester. The profiles for both epitaxial layers are depicted in Figure 2 and Figure 3. As illustrated in epitaxial layer profiles, the bulk InAlAs layer is protected by 50 Å of cap layer to prevent the Aluminium oxidation in the material compound.

| 8500 Å | In <sub>0.53</sub> Ga <sub>0.47</sub> As undoped | 50 Å   | In <sub>0.53</sub> Ga <sub>0.47</sub> As undoped |  |

|--------|--------------------------------------------------|--------|--------------------------------------------------|--|

| 500 Å  | In <sub>0.52</sub> Al <sub>0.48</sub> As undoped | 8500 Å | In <sub>0.52</sub> Al <sub>0.48</sub> As doped   |  |

|        | InP Substrate                                    |        | InP Substrate                                    |  |

Figure 2. VMBE #1593 Epitaxial Layer Figure 3. VMBE #1594 Epitaxial Layer

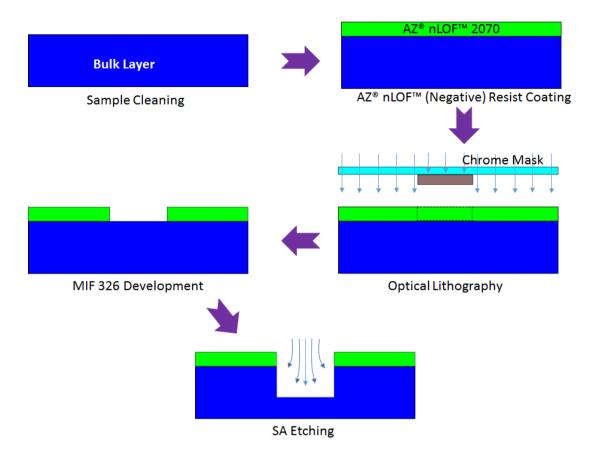

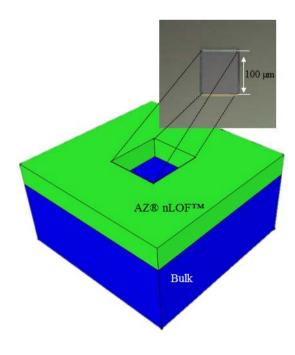

The samples were cleaned separately in an ultrasonic bath for 5 minutes successively with conventional cleaning agents; Trichloroethylene, Acetone and Isopropanol. An extra etching step on bulk InAlAs was used, where the samples are immersed for one minute in a non-selective orthophosporic etch solution (H<sub>3</sub>PO<sub>4</sub>: H<sub>2</sub>O<sub>2</sub>:H<sub>2</sub>O) with 3:1:50 composition for stripping off the cap layer. The steps are followed by rinsing the sample with deionized (DI) water for another one minute for a good surface cleaning. All experiments were conducted at room temperature environment, allowing the chemical compound to be used instantaneously. The etch structures were processed using conventional optical lithography and development. The resist used in this experiment is AZ® nLOF<sup>TM</sup> 2070 followed by development in MIF 326. The etching structures were chosen to be the MESA layer with dimensions of approximately 100 μm. The above processes are depicted in Figure 4, while Figure 5 shows the 100 μm MESA structure before the SA etch.

Figure 4. Processing Steps

Figure 5. The Sketch of  $100~\mu m$  MESA structure. Inset shows a picture of the structure under high power microscope

### 3.0 RESULTS AND DISCUSSION

The experiment begins with the effect of peroxide  $(H_2O_2)$  composition on the semiconductor etch rate. In the mixture,  $H_2O_2$  is needed as the oxidising agent, where the semiconductor surface is first oxidised before this layer is etched by the SA. The etching mixtures are prepared by liquefying 10 g of succinic acid granulates with 50 ml of DI water. Then, the mixture is diluted to pH 6 by Ammonium Hydroxide (NH<sub>4</sub>OH), the same pH value previously used for Adipic Acid etchant (Bouloukou et al., 2008). From this solution, different set of solutions are prepared by adding different  $H_2O_2$  compositions.

At this stage, the etching time is made constant for 5 minutes for all InGaAs samples. Since the etch rate of InAlAs is expected to be lower than 10 Å/min (Fourre et al., 1996), the samples were left for 5 hours in the acid solution. The depth of etching is measured at five random locations using a Taylor Hobson's Talystep profiler (resolution = 2 nm) (Jurzecka-Szymacha, Boszkowicz, & Tkacz-Śmiech, 2011) after the resist layer is stripped-off. In this work, the etch depth is defined as the depth from the substrate surface to the deepest etching distance of the sample over the dedicated etching time. The measurement is taken on both left and right sides of the trenches, and the presented data are the average data from the etch depth on both sides. The graphical representation of etch depth will be depicted in the following section.

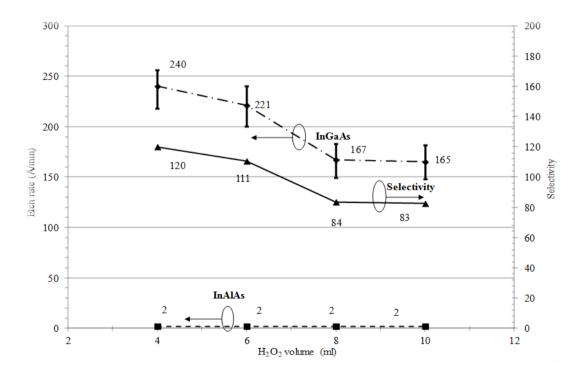

Throughout this work, the etch rate is calculated by the average value of etch depth over the etching time in each solution The resulted etch rate for both InGaAs and InAlAs samples are illustrated in Figure 6.

Figure 6. Etch rate of lattice matched InGaAs and InAlAs and selectivity in different  $H_2O_2$  compositions (DI water volume = 50 ml and pH = 6)

The etch rate of InGaAs in Figure 6 shows decrementing trend with increasing  $H_2O_2$  volume. This trend is in agreement with H. Fourre et al (Fourre et al., 1996) studies where the rate of surface oxidation increases as the peroxide volume increases. Thick oxide layer can hardly be removed, slowing down the second reaction to take place, as shown by the shallower etch depth as peroxide volume increases. The graph also shows a turning point between consistent high and low etch rate region (below 6.0 ml and above 8.0 ml, respectively), where there is a small decrease in etch rate. However, the change is small, around 60 Å/min. Thus, it can be concluded that when the volume is < 6.0 ml and > 8.0 ml, the InGaAs etch rate is not a strong function of  $H_2O_2$  composition. The etch rate for InAlAs is constant at ~ 2 Å/min throughout the first experiment, which confirms the purpose of the Aluminium element in the compound as the chemical etch stop layer. From this relationship, the selectivity of etchant can be calculated as in Equation (1). The selectivity shows a declining trend, and is directly proportional to the InGaAs etching rate.

$$Selectivity = \frac{InGaAs\ etch\ rate}{InAlAs\ etch\ rate} \tag{1}$$

During the step profiling measurement, an important and significant observation has been made particularly on the InGaAs samples. As shown in Figure, there is a "hump" in the middle of the trench caused by the incomplete etching reaction, which is called the Dome Effect. On the contrary, InAlAs shows clean and flat trenches etched profile (Figure ).

Figure 7. Etch profile at InGaAs sample showing 0.01 µm/div

Figure 8. Etch profile at InAlAs sample showing 0.004 µm/div

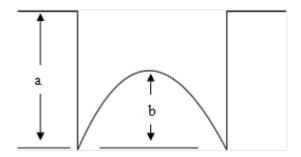

To examine the Dome Effect in the InGaAs layer, the percentage of dome height to etch depth is calculated. Here, the dome height is measured from the bottom of the trenches to the highest point of the hump. Figure 9 illustrates the 'geometry' of the dome profile for the calculation of the percentage of Dome Effect in Equation (2). The persistence of Dome Effect can be viewed as the etchants etch the crystalline materials at different rates depending upon which crystal face is exposed.

Figure 9. Calculation for percentage of dome profile

% of Dome Effect =

$$\frac{Dome \ height, b \ (\mathring{A})}{Etch \ depth, a \ (\mathring{A})}$$

(2)

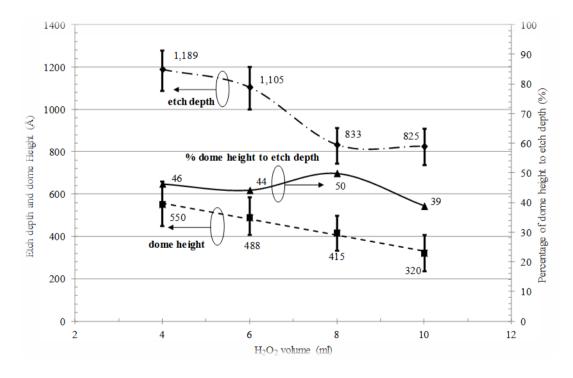

High percentage of Dome Effect in Equation (2) can be seen as the dome height is high relative to the etch depth and thus more prominent to the etching profile. Figure 10 demonstrates the Dome Effect in InGaAs layers for different H<sub>2</sub>O<sub>2</sub> compositions. It can be seen that the dome height is around 40% to 50% over composition after five minutes of etch time. Even though the percentage is stable, it raises a serious processing issue, as it will seriously damage the Schottky contact. Thus, experiments are carried out not only to decide the best etchant composition, but also to address the elimination of "hump" structure in the InGaAs layers.

Figure 10. Etching profile, the Dome Effect percentage of lattice matched InAlAs (DI water volume = 50 ml, pH = 6.0 and etch time = 5 minutes)

All results are summarised in Table 1. The significant finding for etch rate and selectivity experiments are as follows:

- i. H<sub>2</sub>O<sub>2</sub>: Turning point of the InGaAs etch rate at InGaAs samples from high etch rate (~ 230 Å/min) at 6 ml to low etch rate (~ 165 Å/min) at 8 ml. However, only a small change in etch rate is observed (~ 60 Å/min).

- ii. pH: The InGaAs etch rate decays exponentially from 865 to 77 Å/min, while still preserving a low yet decreasing InAlAs etch rate from 9 to 1 Å/min along the pH variations. The result also shows that the pH values do have a strong relationship with the InAlAs etch rate.

- iii. DI water: Significant turning point between high and low etch rate at InGaAs samples at 100 ml and 150 ml. A significant drop in selectivity at high buffering is also observed at 150 ml and 200 ml of H<sub>2</sub>O volumes, where the selectivity drops from 137 to only about 30.

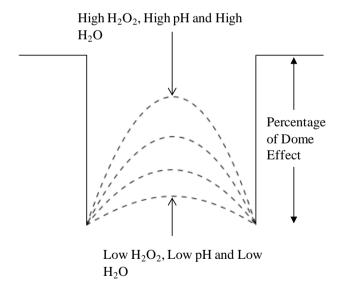

Figure 11 shows the summary of the etchant composition to the % of Dome Effect. It can be concluded that in order to have a low percentage of Dome Effect, a solution with low pH value, low  $H_2O_2$  composition and low volume of DI water must be chosen while maintaining a high InGaAs-InAlAs etching selectivity. Failing to etch the InGaAs cap layer residue is a major cause for the failure in the Schottky contact. Instead of acting as a Schottky barrier, the InGaAs residue will behave increasingly more like an Ohmic contact after heat treatment and thus, deteriorate the device performances.

Figure 11. Summary of chemical composition studies

Table 1. Summary of Results

| Test<br>paramet<br>er                            | pН                                    | H <sub>2</sub> O <sub>2</sub> (ml) | DI<br>water<br>(ml)                    | Etch<br>time                                       | InGaAs<br>trend                                                                            | InAlAs<br>trend                                | Selectivit<br>y                                                                      | % Dome Effect to etch depth                                                                 |

|--------------------------------------------------|---------------------------------------|------------------------------------|----------------------------------------|----------------------------------------------------|--------------------------------------------------------------------------------------------|------------------------------------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| H <sub>2</sub> O <sub>2</sub><br>compositi<br>on | 6                                     | 4 – 10<br>Interval<br>= 2 ml       | 50                                     | 5 min<br>for<br>InGaAs<br>5 hours<br>for<br>InAlAs | Turning point at 6-8 ml at 221 and 167 Å/min  Constant before and after turning point      | Constant<br>s at 2<br>Å/min                    | Turning point at 6-8 ml at 111 and 84  Constant before and after turning point       | 40 - 50                                                                                     |

| pН                                               | 5.0<br>to<br>6.5<br>Interval<br>= 0.5 | 8                                  | 50                                     | 5 min<br>for<br>InGaAs<br>5 hours<br>for<br>InAlAs | Decreased<br>exponential<br>ly from 865<br>to 77 Å/min                                     | Decrease<br>d linearly<br>from 9 to<br>1 Å/min | Peaks at pH 5.5 at 140                                                               | Increased<br>linearly<br>from 10<br>to 62                                                   |

| DI water                                         | 6                                     | 5                                  | 50<br>to<br>200<br>Interval<br>= 50 ml | 5 min<br>for<br>InGaAs<br>5 hours<br>for<br>InAlAs | Turning point at 100 -150 ml at 260 and 68 Å/min.  Constant before and after turning point | Constant<br>at 2<br>Å/min                      | Turning point at 100 -150 ml at 137 and 35.  Constant before and after turning point | Constant<br>at 30 %<br>until 100<br>ml and<br>increase<br>rapidly ><br>60 at high<br>buffer |

Table 2. Final Etching Composition

| Parameter                | Composition/value |  |  |  |

|--------------------------|-------------------|--|--|--|

| Succinic acid granulates | 10 g              |  |  |  |

| $H_2O_2$                 | 5 ml              |  |  |  |

| рН                       | 5.5               |  |  |  |

| H <sub>2</sub> O         | 50 ml             |  |  |  |

The optimised chemical composition is summarised in **Error! Reference source not found.** After considering all factors, these parameters are the best compositions for high selectivity and low Dome Effect percentage. 5 ml of  $H_2O_2$  is used for high InGaAs etch rate and high InGaAs-InAlAs selectivity. Additionally, a pH of 5.5 is chosen in order to have a low InAlAs etch rate and low Dome Effect percentage. Finally, low volume of  $H_2O$  i.e. 50 ml is chosen for high selectivity in addition to low Dome Effect percentage.

### 4.0 CONCLUSION

The effect of etching compounds on the etching rate and consequently the selectivity of InGaAs-InAlAs samples have been successfully presented in this paper. After a series of experiments, the optimal etching composition is chosen to be 5 ml of  $H_2O_2$ , pH of 5.5 and 50 ml of DI water. The etch rate for InAlAs and InGaAs is approximately 2 Å/min and 240 Å/min, respectively, with selectivity of the solution of 140. The percentage of Dome Effect is expected to be consistently 30%. The etching solution is suitable for reliable and highly reproducible pHEMT gate recess process, where the Dome Effect can be further eliminated by controlling the InGaAs etching time to reach the InAlAs etch stop layer.

#### REFERENCES

- Bauer, G., & Schäffler, F. (2006). Self-assembled Si and SiGe nanostructures: New growth concepts and structural analysis. *Physica status solidi (a)*, 203 (14), 3496-3505. Do: 10.1002/pssa. 200622405

- Bouloukou, A., Boudjelida, B., Sobih, A., Boulay, S., Sly, J., & Missous, M. (2008). Very low leakage InGaAs/InAlAs pHEMTs for broadband (300 MHz to 2 GHz) low-noise applications. *Materials Science in Semiconductor Processing*, 11 (5–6), 390-393. doi: 10.1016/j.mssp.2008.11.006

- Bouloukou, A., Sohib, A., Kettle, D., Sly, J., & Missous, M. (2006). Novel High-Breakdown InGaAs/InAlAs pHEMTs for Radio Astronomy Applications. Paper presented at the *4th ESA Workshop on mm-Wave Technology and Applications*.

- Broekaert, T. P. E., & Fonstad, C. G. (1992). Novel, Organic Acid-Based Etchants for InGaAlAs/InP Heterostructure Devices with AlAs Etch-Stop Layers. *Journal of The Electrochemical Society*, 139 (8), 2306-2309.

- Chau, R. (2007, 12-14 Dec. 2007). Challenges and opportunities of emerging nanotechnology for VLSI nanoelectronics. Paper presented at the 2007 *International Semiconductor Device Research Symposium*,.

- Fourre, H., Diette, F., & Cappy, A. (1996). Selective wet etching of lattice matched InGaAs/InAlAs on InP and metamorphic InGaAs/InAlAs on GaAs using succinic acid/hydrogen peroxide solution. *Journal of Vacuum Science & Technology B: Microelectronics and Nanometer Structures*, 14(5), 3400-3402. doi: 10.1116/1.588543

- Jurzecka-Szymacha, M., Boszkowicz, P., & Tkacz-Śmiech, K. (2011). Silicon nitride layers of various n-content: Technology, properties and structure. *Thin Solid Films*, 520 (4), 1308-1312. doi: 10.1016/j.tsf.2011.04.157

- Kuech, T. F., Jha, S., Kuan, T. S., Babcock, S. E., & Mawst, L. J. (2009, 10-14 May 2009). Defect reduction in large lattice mismatch epitaxial growth through block copolymer full wafer patterning. Paper presented at the *IEEE International Conference on. Indium Phosphide & Related Materials*, 2009 (IPRM 2009).

- Lidholm, E. C. a. S. (2005). *Millimeter-Wave Integrated Circuits*. Boston. Springer Science.

- Lin, Y.-S., Ma, Y.-C., & Lin, Y.-T. (2011). Effects of Selective and Nonselective Wet Gate Recess on InAlAs/InGaAs Metamorphic Field-Effect Transistors with Double Delta Doping in InGaAs Channels. *Journal of The Electrochemical Society*, 158 (3), H305-H311.

- Oh, J.-H., Son, M.-S., Lww, B.-H., Baek, Y.-H., Jang, H.-K., Rhee, J.-K., Kim, S.-D. (2004). Effects of the Gate Recess Structure on the DC Electrical Behaviour of 0.1-um Metamorphic High-Electron-Mobility Transistors. *Journal of the Korean Physical Society*, 45 (4), 1004 to 1008.

- Osbourn, G. C. (1982). Strained layer superlattices from lattice mismatched materials. *Journal of Applied Physics*, 53 (3), 1586-1589. doi: 10.1063/1.330615

- Rodwell, M. J. W., Singisetti, U., Wistey, M., Burek, G. J., Carter, A., Baraskar, A., Asbeck, P. (2010, May 31 2010-June 4 2010). *III-V MOSFETs: Scaling laws, scaling limits, fabrication processes.* Paper presented at the 2010 International Conference on Indium Phosphide & Related Materials (IPRM 2010).

- Smith, P. M., Nichols, K., Kong, W., MtPleasant, L., Pritchard, D., Lender, R., Swanson, A. W. (2001). Advances in InP HEMT technology for high frequency applications. Paper presented at the 2001 IEEE International Conference On Indium Phosphide and Related Materials (IPRM 2001).

- T. E. Whall, E. H. C. P. (1998). SiGe heterostructures for FET applications. *Journal of Physics D: Applied Physics*, 31, 1397-1416.