# Scholars' Mine

Masters Theses

Student Theses and Dissertations

1967

# The realization and application of parallel linear feedback shift registers

Ross K. Heitzmann

Follow this and additional works at: https://scholarsmine.mst.edu/masters\_theses

Part of the Electrical and Computer Engineering Commons Department:

#### **Recommended Citation**

Heitzmann, Ross K., "The realization and application of parallel linear feedback shift registers" (1967). *Masters Theses.* 3112. https://scholarsmine.mst.edu/masters\_theses/3112

This thesis is brought to you by Scholars' Mine, a service of the Missouri S&T Library and Learning Resources. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

#### THE REALIZATION AND APPLICATION

#### OF

PARALLEL LINEAR FEEDBACK SHIFT REGISTERS

BY

ROSS K. HEITZMANN - 1936 -

A

#### THESIS

submitted to the faculty of the UNIVERSITY OF MISSOURI AT ROLLA

in partial fulfillment of the requirements for the

Degree of

MASTER OF SCIENC IN ELECTRICAL ENGINEERING

Rolla, Missouri

1967

129481

Approved by

Jones (Advisor) Junk Attens

X16968 A

#### ABSTRACT

Two methods for serial-to-parallel transformation of linear feedback shift registers are briefly discussed. A third method for transformation is rigorously developed using a next-state and output equation representation of the linear feedback shift register. An algorithm is developed for simplifying the parallel machine resulting from serial-to-parallel transformation, where simplification is defined as reduction in the required number of modulo 2 adders. A computer program incorporating serial-toparallel transformation algorithm is provided.

#### ACKNOWLEDGEMENTS

The author wishes to express his appreciation to his major professor, Dr. James H. Tracey, for guidance and for prompt and careful reading of this paper.

The author also appreciates the typing efforts of his wife, Betty.

#### TABLE OF CONTENTS

|       |          |     |                  |             |     |     |     |     |     |     |     |     |     |     |     |     |     |     |            |          |    | Pa | age      |

|-------|----------|-----|------------------|-------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------------|----------|----|----|----------|

| ABST  | RACI     | · • |                  | •           | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •          | •        | •  |    | ii       |

| ACKNO | OWLE     | DG  | EMI              | ENT         | rs  | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •          | •        | •  | t  | ii       |

| LIST  | OF       | FI  | GUI              | RES         | 5   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •          | •        | •  |    | v        |

| LIST  | OF       | TA  | BL               | ES          | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •          | •        | •  |    | vi       |

| I.    | IN       | ITR | ODI              | UCI         | CIC | )N  | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •          | •        | •  |    | 1        |

| II.   | SI       | ERI | AL.              | <b>-</b> TC | )-I | PAF | RAI | LI  | EL  | TH  | RAI | VSI | FOI | RMA | ATI | [0] | 1 1 | ME  | THO        | D        | 5. |    | 11       |

|       | А.<br>В. |     | Two<br>A I<br>1. | Mat         | tri | x   | Me  | eth | ho  | d c | of  | TI  | rai |     | foi | ma  | at: | ioı | <b>n</b> . | od:<br>• | 5. |    | 11<br>17 |

|       |          |     | 2.               | ]           | ir  | iea | ar- | -Se | eqi | uer | nt: | ia. | Lr  | nac | chi | Ine | э.  | •   |            |          |    |    | 17       |

|       |          |     | <i>C</i> •       |             |     |     |     |     |     |     |     |     |     | •   |     |     |     |     |            |          |    |    | 23       |

| III.  | RI       | DU  | CT:              | IOI         | V C | )F  | M   | fCI | HI  | NE  | C   | OM] | PLI | EXI | ETT | ζ.  | •   | •   | •          | •        | •  |    | 35       |

|       |          |     | Is<br>Der        |             |     |     |     |     |     |     |     |     |     |     |     |     |     |     | •          | •        | •  |    | 37       |

|       | Д.       |     | Ma               |             |     |     |     |     |     |     |     |     |     |     |     |     |     |     | •          | •        | •  |    | 42       |

| IV.   | SU       | JMM | IAR              | Y.          | •   | •   | •   | ·   | •   | •   | •   | •   | •   | •   | •   | •   | •   | é   | •          | •        | •  |    | 54       |

| BIBL  | IOGI     | RAF | PHY              | •           | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •          | •        | •  |    | 55       |

| APPE  | NDI      | ζA  | •                | •           | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •          | •        | •  |    | 56       |

| VITA  |          |     | •                | •           |     | •   | •   |     | •   |     |     | •   | •   | •   |     |     | •   | •   | •          |          |    |    | 58       |

# LIST OF FIGURES

|    |                                         | Page |

|----|-----------------------------------------|------|

| 1. | LFSR for Division by g(x)               | . 6  |

| 2. | LFSR for Division by $x^3+x+1$          | . 6  |

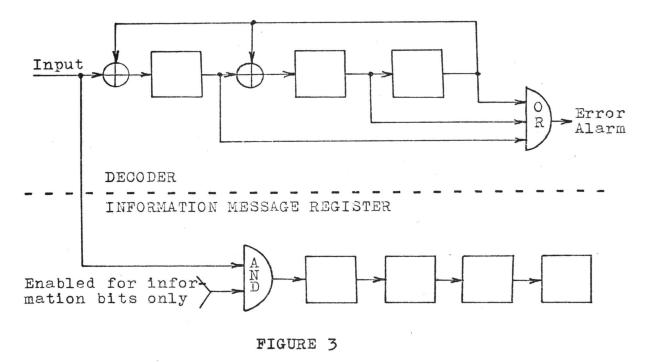

| 3. | Decoder for the (7,4) Code              | . 8  |

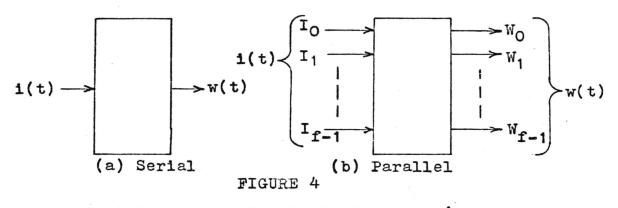

| 4. | Serial and Parallel Equivalent LFSR's   | • 9  |

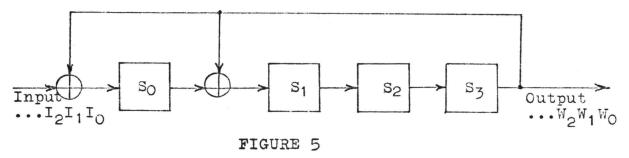

| 5. | LFSR for the Generator $g(x) = 1+x+x^4$ | • 11 |

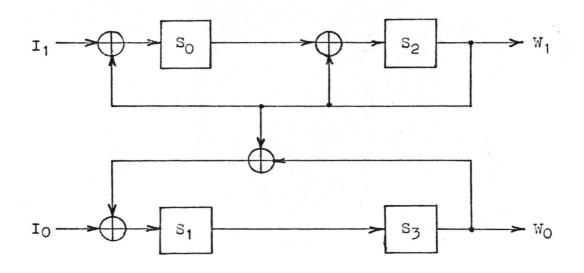

| 6. | Two-Channel Parallel LFSR               | • 13 |

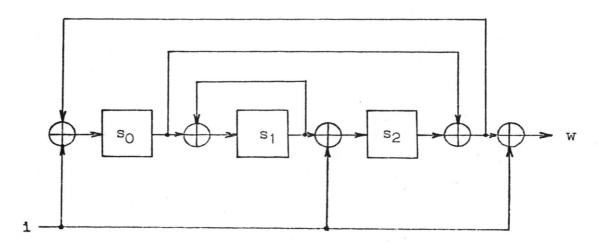

| 7. | A Three-Stage LFSR                      | . 25 |

## LIST OF TABLES

|    |            |                          | Page |

|----|------------|--------------------------|------|

| 1. | Flow Table | for a Serial LFSR        | . 12 |

| 2. | Flow Table | for a Parallel LFSR      | • 14 |

| 3. | Summary of | Results of Computer Runs | • 51 |

#### I. INTRODUCTION

The use of cyclic codes for error detection and correction is well known<sup>1,2</sup>. Cyclic codes are very useful because they are readily constructed using algebraic techniques and because coding and decoding are easily accomplished using linear feedback shift registers. In the past, encoding and decoding has been done serially by shifting messages through registers one bit at a time. This paper presents a method for decreasing the necessary message processing time by using parallel encoders and decoders. The remainder of this introductory section presents the basic ideas of cyclic codes and linear feedback shift registers and relates their characteristics to the serial-to-parallel transformation problem.

A general representation for a binary message of length k is

$M = a_0 a_1 \cdots a_{k-1}$  where  $a_1 = 0$  or 1. The binary digits in the message can be thought of as coefficients of a polynomial m(x) as follows:

$$m(x) = a_0 + a_1 x + \cdots + a_{k-1} x^{k-1}$$

.

The binary operations + and "." are defined as follows:

k-1

| + | 0 | 1 | • | 0 | 1 |  |

|---|---|---|---|---|---|--|

| 0 | 0 | 1 | 0 | 0 | 0 |  |

| 1 | 1 | 0 | 1 | 0 | 1 |  |

It should be noted that "+" is the "modulo 2 addition" operation and "." is ordinary multiplication. These

polynomials are distributive, associative, and commutative under the two operations, and also the polynomials factor uniquely into irreducible factors.

A second polynomial, g(x), is the generator polynomial for a cyclic code. The generator is of degree n-k where the information message is of length k and the coded message of length n. The generator polynomial g(x) is used to generate the code polynomial f(x) from the message polynomial m(x) as follows:

- 1) Multiply m(x) by x<sup>n-k</sup>

- 2) Divide x<sup>n-k</sup>m(x) by g(x) to yield a quotient q(x) and remainder r(x). By the Euclidean Division Algorithm it must be true that

$x^{n-k}m(x) = g(x)q(x)+r(x)$ . Adding r(x) to both sides (modulo 2) yields

$\mathbf{x}^{\mathbf{n}-\mathbf{k}}\mathbf{m}(\mathbf{x})+\mathbf{r}(\mathbf{x}) = \mathbf{g}(\mathbf{x})\mathbf{q}(\mathbf{x})$

where the code polynomial

$f(x) = x^{n-k}m(x) + r(x) = g(x)q(x)$

is of degree n-1.

The code is systematic, that is, the encoding process does not change the information bits. Thus, the information bits are retained as the coefficients of  $x^{n-1}$ ,  $x^{n-2}$ ... $x^{n-k}$  and the check digits are the coefficients of  $x^{n-k-1}$ ... $x^{0}$ . Decoding is therefore a relatively simple task. The first k digits are the information digits, provided that no errors have occurred. Error detecting or correcting is accomplished by dividing the coded polynomial f(x) by the generator polynomial g(x). If

$$f(x) = g(x)q(x)$$

then

f(x)/g(x) = q(x)

provided that no errors have occurred. If a detectable number of errors has occurred, then division by g(x) will yield a nonzero remainder.

The error detection or correction capability of any cyclic code is determined by the generator polynomial for the code. For example, Peterson and Brown<sup>1</sup> prove that the cyclic code generated by the polynomial

$$g(x) = 1 + x$$

is a single-error-detecting code. In addition, of course, the code detects any odd number of errors. Peterson and Brown also develop generator polynomials for double-and triple-error-detecting codes and for burst-error-detecting codes. However, the best known cyclic codes are those for which the generator polynomial is constructed using techniques described by Bose and Chaudhuri. For these codes, given that the desired message length and error-detection capability have been selected, construction amounts to construction of the generator polynomial using the Bose-Chaudhuri algorithm as described by Peterson<sup>2</sup>. Encoding and decoding for the Bose-Chaudhuri codes, as for all cyclic codes, amounts to division by the generator polynomial. If error correction is to be accomplished the remainder must be evaluated at the decoder.

The capability of a cyclic code to detect errors, is shown by the following example which is an information channel for transmission of four binary digits (k = 4). The generator polynomial

$$g(x) = x^3 + x + 1$$

will provide three check digits for the code. It can be shown that this code has minimum (Hamming) distance three so that it can detect any combination of two errors. If the message 1011 is to be encoded, then

$$m(x) = 1+x^{2}+x^{3}$$

$$x^{n-k}m(x) = x^{3}mx = x^{3}+x^{5}+x^{6}$$

$$x^{n-k}m(x) \stackrel{*}{\cdot} g(x) = (x^{3}+x^{5}+x^{6})*(1+x+x^{3})$$

$$= q(x)+r(x) \pmod{2}$$

$$= (1+x+x^{2}+x^{3})*1.$$

Therefore, the coded message polynomial is  $g(x)q(x) = x^{n-k}m(x)+r(x) = 1+x^3+x^5+x^6$ . Thus, the binary coded message to be transmitted is 1001011.

From this example it is obvious that encoding essentially consists of division of the message polynomial by the generator polynomial. At the decoder the coded message polynomial is again divided by the generator polynomial. Therefore it is desirable to find a machine which will efficiently accomplish this division. It is well known that the linear feedback shift register (LFSR) is such a machine.

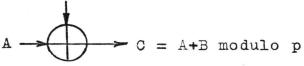

The LFSR is constructed using the three building blocks described below:

1) The modulo-p adder.

- 2) The delay element. The output is the input v(t) v(t) v(t-1) v(t-1) v(t-1)

- 3) The constant multiplier element where D is an element from the residue class ring modulo p. For p = 2 this element is an open circuit for D = 0 and a wire for D = 1.

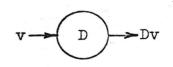

Given a generator polynomial g(x) with coefficients from the GF [2] (i.e. the prime or Galois field having 2 elements) such that

$g(x) = a_r x^r + a_{r-1} x^{r-1} + a_{r-2} x^{r-2} + \cdots a_1 x + a_0$ , the LFSR for dividing by g(x) is as shown in Figure 1. The register is initially set to 0. The (n-1) degree polynomial p(x) which is to be divided by g(x) is shifted, high order first, into the register from the left. After

FIGURE 1 LFSR for Division by g(x)

r-1 shifts, the first coefficient of the quotient appears at the output. After n-1 shifts, the entire quotient has appeared at the output and the shift register retains the remainder.

Example:

The (7,4) code, that is; n = 7, and k = 4, might have a generator polynomial

$g(x) = x^{3}+x+1$ .

The feedback shift register for accomplishing division by g(x) is as shown in Figure 2. If the 4 bit message to be

FIGURE 2 LFSR for Division by  $x^{3}+x+1$

encoded is shifted into this register high order coefficient first, then after three shifts the coefficient will begin

to appear at the output and after seven shifts the remainder will be in the register. Taking a specific example, if m = 1011, then

$$m(x) = 1 + x^2 + x^3$$

and

$$x^{2}m(x) = x^{3}+x^{5}+x^{6}$$

.

This polynomial, divided by

$g(x) = 1 + x + x^3$

yields a quotient

$$q(x) = 1 + x + x^2 + x^3$$

and a remainder r(x) = 1. The flow table below illustrates the operation of the registers

| t      | I | ×o | x <sub>1</sub> | <b>x</b> 2 |

|--------|---|----|----------------|------------|

| 0      | 1 | 0  | 0              | 0          |

| 1      | 1 | 1  | 0              | 0          |

| 2      | 0 | 1  | 1              | 0          |

| 3      | 1 | 0  | 1              | 1          |

| 4      | 0 | 0  | 1              | 1          |

| 5<br>6 | 0 | 1  | 1              | 1          |

| 6      | 0 | 1  | 0              | 1          |

| 7      | 0 | 1  | 0              | 0          |

The message to be sent is

$1+x^3+x^5+x^6 \longrightarrow 1001011.$

At the receiver an identical shift register will divide this coded message polynomial by g(x). After 7 shifts the remainder (O if no errors have occurred) will be in the shift register and an "OR" gate on the outputs of the delay elements must read O after the seven shifts if no error has occurred. Figure 3 shows the decoder.

Decoder for the (7,4) Code

Cyclic codes, as has already been stated, are readily constructed using well defined algorithms the best known of which is the Bose-Chaudhuri algorithm. Also, the codes can be implemented quite simply using linear feedback shift registers. These shift registers were shown to be serial shift registers which required a total of n clock times to perform error checking (i.e. to calculate the remainder) of an n bit message.

In applications where message processing time is a consideration it is desirable to decrease the encoding and

8

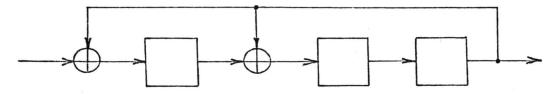

decoding times. Hence the problem of converting a serial feedback shift register to an equivalent machine which is partially parallel presents itself. The serial machine might be described by the diagram of Figure 4a and the equivalent parallel machine by Figure 4b. Suppose for

Serial and Parallel Equivalent LFSR's

the serial machine that the input sequence is  $I_{n-1} I_{n-2} \cdots I_2 I_1 I_0$  and the output sequence is  $W_{n-1} W_{n-2} \cdots W_2 W_1 W_0$ . At time t = 0 the input is  $I_0$  and the output  $W_0$ , at time t = 1 the input is  $I_1$  and the output is  $W_1$ , and so forth. The input is entered one bit per clock time and the output is provided one bit per clock time. In Figure 4b, the f channel parallel machine enters the input data f bits at a time and provides output data f bits at a time. Thus at time t = 0 the input is  $I_{f-1}$ ,  $\cdots$   $I_1$ ,  $I_0$  and the output is  $I_{2f-1}$ ,  $\cdots$   $I_{f-1}$ ,  $I_f$  and the outputs are  $W_{2f-1}$ ,  $\cdots$   $W_f$ . The number of clock times required for the parallel machine is q where q is the smallest integer such that

$$q \leq \frac{n}{f}$$

where q is a parameter which can be selected by the designer. The problem to be investigated may now be stated as:

"Given a serial linear feedback shift register which requires n clock times to accomplish encoding or decoding, find a minimal or near minimal parallel machine which accomplishes the same function in q clock times."

The decrease in message-processing time is, of course, not obtained without a penalty. The penalty is, as is usual for digital machines, an increase in the complexity of the machine. In other words, the decrease in processing time is accompanied by an increase in the amount of hardware necessary to build the encoder and decoder. This will be evident from the example presented in the next section. Thus minimization of the hardware required to realize parallel encoders and decoders is desirable and will be part of the problem treated in this paper.

10

#### II. SERIAL-TO-PARALLEL TRANSFORMATION METHODS

This section presents three methods for transformation of serial LFSR's to f-channel parallel analogs. The first two methods are presented essentially as they appear in a paper by Hsiao and Sih<sup>3</sup>. The third method, which seems to be superior to the first two, is based on a method proposed by Hsiao and Sih and extended by Gill<sup>4</sup>. A. Two Elementary Transformation Methods.

Hsiao and Sih call their first method of serial-toparallel transformation the "Engineering Approach". This method is readily explained by example with the serial LFSR shown in Figure 5. The case in which f = 2 requires

LFSR for the Generator  $g(x) = 1+x+x^4$

that the input data be entered two bits at a time and the output data be provided two bits at a time. From the serial flow table of Table 1, the initial states of the storage elements are  $S_i(0)$ .

#### TABLE 1

Flow Table for a Serial LFSR

| t | In-<br>put     | s <sub>o</sub>     | s <sub>1</sub>                        | <sup>s</sup> 2                        | s <sub>3</sub>     | Out-<br>put |

|---|----------------|--------------------|---------------------------------------|---------------------------------------|--------------------|-------------|

| 0 | IO             | s <sub>o</sub> (0) | s <sub>1</sub> (0)                    | s <sub>2</sub> (0)                    | s <sub>3</sub> (0) | Wo          |

| 1 | I <sub>1</sub> | I0+S3(0)           | s <sub>0</sub> (0)+s <sub>3</sub> (0) | s <sub>1</sub> (0)                    | s <sub>2</sub> (0) | ₩1          |

| 2 |                | 11+S2(0)           | $I_0 + S_3(0) + S_2(0)$               | s <sub>0</sub> (0)+s <sub>3</sub> (0) | s <sub>1</sub> (0) | - C         |

If the inputs are taken in groups of two, then the parallel machine will make a transition from the state at time t = 0 to the state at time t = 2. Therefore the entries in the table for t = 2 describe the feedback connections for the device and the output column describes the output connections. By inspection of Table 1, the next-state equations for the parallel machine are

$$S_{0}(t+1) = I_{1}+S_{2}(t)$$

$$S_{1}(t+1) = I_{0}+S_{2}(t)+S_{3}(t)$$

$$S_{2}(t+1) = S_{0}(t)+S_{3}(t)$$

$$S_{3}(t+1) = S_{1}(t).$$

The output equations for the parallel machine are

$$W_0(t) = S_3(t)$$

$W_1(t) = S_2(t).$

The machine to realize the above sets of equations is shown in Figure 6. Table 2 is a flow table demonstrating the division of  $x^{8}+x^{6}+x^{5}$  by  $g(x) = 1+x+x^{4}$  in the parallel machine. By long division, the quotient is  $x^{4}+x^{2}+1$  and the remainder is  $x^{3}+x^{2}+x+1$  and these results can be verified

FIGURE 6 Two-Channel Parallel LFSR

in Table 2. The input to the parallel machine is

000001101

which is 9 bits. Since 9 is not evenly divisible by two, a zero is affixed in front of the rightmost coefficient to provide

#### 0000011010

where the two rightmost digits are the input at time t = 0, the next two digits are the input at time t = 1, and so forth. This step may be justified by considering the message in polynomial form. Then the rightmost digit is the coefficient of  $x^{n-1}$  and affixing the zero to the right of this coefficient amounts to adding  $(0)x^n$  to the polynomial which obviously does not change the polynomial and therefore cannot change the remainder obtained after division by g(x).

| and the last had been all the second | TA | BI | E | 2 |

|--------------------------------------|----|----|---|---|

|--------------------------------------|----|----|---|---|

| Time | I <sub>1</sub> | IO | s <sub>o</sub> | s <sub>1</sub> | <sup>S</sup> 2 | s <sub>3</sub> | ₩ <sub>O</sub> | W 1 |

|------|----------------|----|----------------|----------------|----------------|----------------|----------------|-----|

| 0    | 1              | 0  | 0              | 0              | 0              | 0              | 0              | 0   |

| 1    | 1              | 0  | 1              | 0              | 0              | 0              | 0              | 0   |

| 2    | 0              | 1  | 1              | 0              | 1              | 0              | 0              | 1   |

| 3    | 0              | 0  | 1              | 0              | 1              | о              | 0              | 1   |

| 4    | 0              | 0  | 1              | 1              | 1              | 0              | 0              | 1   |

| 5    |                |    | 1              | 1              | 1              | 1              |                | 1   |

Flow Table for a Parallel LFSR

The remainder is in the register after the 5th clock time. The coefficients of  $x^3$  is  $S_3$ ,  $x^2$  is  $S_2$ , x is  $S_1$ , and  $x^0$  is  $S_0$ . The quotient is provided as follows: At t = 2 the value of  $W_1$  is the coefficient of  $x^4$ .

At t = 3  $W_0$  and  $W_1$  are the coefficients of  $x^3$  and  $x^2$  respectively.

At  $t = 4 W_0$  and  $W_1$  are the coefficients of x and  $x^0$  respectively.

The method of serial-to-parallel transformation just described is straightforward and intuitively understandable. It does have the major disadvantage of being tedious and unwieldy if g(x) is large or if the desired value of f (the number of parallel channels) is large, because the state of the machine at each clock time must be investigated. Hsiao and Sih present a second method for serial-toparallel conversion which is described below. This technique provides the interconnection between memory elements for the parallel machines but provides neither information about the connection of inputs nor information about connections for providing outputs.

The technique utilizes the property of linear feedback shift registers that, if the register is constructed according to a polynomial g(x) and if  $\prec$  is a root of g(x), then the register will give successive powers of  $\propto$  as it is shifted. (This property is described in detail in Chapter 7 of reference 2). The LFSR described in the preceding section will be used here to demonstrate the procedure for obtaining the interconnection information for a two channel parallel machine. The generator polynomial for this machine is

$g(x) = 1 + x + x^4$ .

Therefore, if  $\propto$  is a root of g(x), it must be true that 1+  $\propto$  +  $\propto^4 = 0$

or, because the addition is modulo-2

$\propto^4 = 1 + \propto$ .

The contents of the four-stage shift register of this example can be described by the polynomial r(x) where

$$r(x) = S_0 + S_1 x + S_2 x^2 + S_3 x^3$$

.

Now if x is replaced by  $\propto$  then it is true that

$$\mathbf{r}(\boldsymbol{\propto}) = \mathbf{s}_0 + \mathbf{s}_1 \boldsymbol{\propto} + \mathbf{s}_2 \boldsymbol{\propto}^2 + \mathbf{s}_3 \boldsymbol{\propto}^3.$$

If a three channel parallel LFSR is to be equivalent to the serial LFSR, then successive shifts of the parallel register must yield successive powers of  $\propto^2$ . Therefore, the contents of this register must be (as shown by Peterson)

$r(\propto^2) = \propto^2 r(\propto) = s_0 \propto^2 + s_1 \propto^3 + s_2 \propto^4 + s_3 \propto^5$ . But, from the preceding paragraph

$$\propto^4 = 1 + \infty$$

so that

$$\infty^5 = \infty (\infty^4) = \infty (1 + \infty) = \infty + \infty^2.$$

Therefore substitution of the values for  $\sim^4$  and  $\sim^5$  into the equation for  $r(\sim^2)$  yields

$$r(\infty^{2}) = s_{0} \propto {}^{2}+s_{1} \propto {}^{3}+s_{2}(1+\infty)+s_{3}(\infty+\infty^{2})$$

=  $s_{0} \propto {}^{2}+s_{1} \propto {}^{3}+s_{2}+s_{2} \propto {}^{+s_{3}} \propto {}^{+s_{3}} \propto {}^{2}$

=  $s_{2}+(s_{2}+s_{3}) \propto {}^{+}(s_{0}+s_{3}) \propto {}^{2}+s_{1} \propto {}^{3}.$

Now,  $r(\sim^2)$  may be rewritten such that

$$r(\infty^2) = s_0' + s_1' \propto + s_2' \propto^2 + s_3' \propto^3$$

.

Then by inspection of coefficients

$$s_0 = s_2$$

$s_1 = s_2 + s_3$

$s_2 = s_0 + s_3$

$s_3 = s_1$

Now the above equations, if properly interpreted and if inputs are ignored, yield the interconnections described by the equations on page 12.

The method described here has two major shortcomings. A very obvious problem is that no information about input or output connections is provided. A second problem is the complexity of solving for coefficients if the generator polynomial is large or if the desired number of parallel channels is large.

B. A Matrix Method of Transformation

The third technique described by Hsiao and Sih uses companion (connection) matrices for the serial-to-parallel transformation. The presentation in the following section was suggested by the work of Hsiao and Sih, but is more general and ultimately results in a method of transformation which is concise and simple, and lends itself to simplification of the transformed circuit.

1. Transformation of the general linear sequential machine.

The description of the LFSR in terms of generalized linear-sequential-machine theory is desirable because the generalized theory permits a concise mathematical description of such machines which in turn provides a foundation for the theory of serial-to-parallel transformation of LFSR's.

Yau and Wang<sup>5</sup> define a finite state sequential machine M as a system with a finite input space  $\overline{I}$ , a finite output space  $\overline{W}$ , a finite internal-state space  $\overline{S}$  and two functions f and g. The functions f and g, called the next-state and output functions respectively, are described by

$$\overline{s}(t+1) = f\left[\overline{s}(t),\overline{1}(t)\right]$$

$$\overline{w}(t) = g\left[\overline{s}(t),\overline{1}(t)\right].$$

where  $\overline{s}(t)$ ,  $\overline{1}(t)$ , and  $\overline{w}(t)$  are, respectively, the internalstate, input and output vectors of M and  $\overline{s}(t+1)$  is the next internal-state vector of M. Furthermore, the machine 17

will be assumed to be deterministic, synchronous, and completely specified. The machine is deterministic if f and g are single valued at every point in their domains, synchronous if every transition is clocked, and completely specified if f and g are defined at every point in their domain. If l, k, and m are the dimensions of the input space, internal-state space, and output space respectively, then  $\overline{s}(t)$  is k-dimensional,  $\overline{I}(t)$  is l-dimensional, and  $\overline{w}(t)$  is m-dimensional.

Let  $\overline{SxI}$  be the Cartesian product of  $\overline{S}$  and  $\overline{I}$  so that, for a general sequential machine, the next-state function f and output function g are mappings among the vector spaces  $\overline{I}$ ,  $\overline{S}$ ,  $\overline{W}$ , and  $\overline{SxI}$ . Then, according to Yau and Wang, a machine M shall be called linear if and only if f is a linear transformation from  $\overline{SxI}$  into  $\overline{S}$ , and g is a linear transformation from  $\overline{SxI}$  onto  $\overline{W}$ .

Yau and Wang<sup>5</sup> prove that a sequential machine M is linear if and only if there exist transformations

$$f_{1}: \overline{S} \longrightarrow \overline{S}$$

$$f_{2}: \overline{I} \longrightarrow \overline{I}$$

$$g_{1}: \overline{S} \longrightarrow \overline{W}$$

$$g_{2}: \overline{I} \longrightarrow \overline{W}$$

such that

$$f(\overline{s},\overline{1}) = f_1(\overline{s}) + f_2(\overline{1})$$

$$g(\overline{s},\overline{1}) = g_1(\overline{s}) + g_2(\overline{1})$$

for every 5 in 5 and every 1 in T. Further, Birkhoff and MacLane<sup>6</sup> prove that there is a one-to-one correspondence

between a linear transformation of the type

$$f_1:\overline{S} \longrightarrow \overline{S}$$

and a kxk matrix A with elements from the field F, where  $\overline{S}$  is a k-dimensional vector space over a scalar field F.

The linear sequential machine M can therefore be described in terms of the equations

$$\overline{\mathbf{s}}(t+1) = \overline{\mathbf{Ts}}(t) + \overline{\mathbf{B1}}(t)$$

$$\overline{\mathbf{w}}(t) = \overline{\mathbf{Cs}}(t) + \overline{\mathbf{D1}}(t)$$

where T is a kxk matrix, B is a kxl matrix, C is an mxk matrix, and D is an mxl matrix.

The serial-to-parallel transformation problem can now be considered in terms of general machine theory. Given a linear sequential machine M with l input terminals and m output terminals, find an f channel analog of M, called M', with  $(f) \cdot (l)$  input terminals and  $(f) \cdot (m)$  output terminals. This means that machine M' must accept f of the l-dimensional input vectors simultaneously and must provide f m-dimensional output vectors simultaneously. If the state vectors for machine M are  $\overline{s}(t)$ ,  $\overline{s}(t+1)$ , . . , then machine M' must transition from  $\overline{s}(t)$  to  $\overline{s}(t+f)$  in a single clock time. From this description it follows that M' will operate f times as fast as M.

The serial-to-parallel transformation of a linear sequential machine is described by the following theorem proved by Gill<sup>4</sup>. The proof of the theorem presented in this paper is an alternate to Gill's proof and is included because it is more easily understood in terms of general linear-sequential-machine theory.

## Theorem

Given a linear sequential machine M described by the set of equations:

$$\overline{\mathbf{s}}(t+1) = \overline{Ts}(t) + \overline{Bi}(t)$$

$$\overline{\mathbf{w}}(t+1) = \overline{Cs}(t) + \overline{Di}(t),$$

the f-channel analog of M, M', is described by the set of equations:

$$\overline{s}'(t+1) = T'\overline{s}'(t)+B'\overline{1}'(t)$$

$\overline{w}'(t) = C'\overline{s}'(t)+D'\overline{1}'(t).$

Where:

$$\overline{\mathbf{s}}'(\mathbf{t}) = \overline{\mathbf{s}}(\mathbf{t})$$

$$\overline{\mathbf{s}}'(\mathbf{t}+1) = \overline{\mathbf{s}}(\mathbf{t}+1)$$

$$\overline{\mathbf{I}}(\mathbf{t}) = \begin{bmatrix} \overline{\mathbf{I}}(\mathbf{t}) \\ \overline{\mathbf{I}}(\mathbf{t}+1) \\ \vdots \\ \overline{\mathbf{I}}(\mathbf{t}+1) \end{bmatrix}$$

$$\overline{\mathbf{w}}'(\mathbf{t}+1) = \begin{bmatrix} \overline{\mathbf{w}}(\mathbf{t}) \\ \overline{\mathbf{w}}(\mathbf{t}+1) \\ \vdots \\ \overline{\mathbf{w}}(\mathbf{t}+1) \end{bmatrix}$$

$$\mathbf{T}' = \mathbf{T}^{\mathbf{f}}$$

$$\mathbf{B}' = \begin{bmatrix} \mathbf{T}^{\mathbf{f}-1}\mathbf{B} & \mathbf{T}^{\mathbf{f}-2}\mathbf{B} & \dots & \mathbf{TB} & \mathbf{B} \end{bmatrix}$$

$$\mathbf{C}' = \begin{bmatrix} \mathbf{C} \\ \mathbf{C}\mathbf{T} \\ \mathbf{C}\mathbf{T}^{2} \\ \vdots \\ \mathbf{C}\mathbf{T}^{\mathbf{f}-1} \end{bmatrix}$$

with each element of D' an mx & matrix. Proof:

The next state equation for M is

$\overline{s}(t+1) = T\overline{s}(t) + B\overline{1}(t)$

By successive substitution, the states at later times in terms of s(t) are

$$\overline{s}(t+2) = T\overline{s}(t+1) + B\overline{i}(t+1)$$

$$\overline{s}(t+2) = T\left\{T\overline{s}(t) + B\overline{i}(t)\right\} + B\overline{i}(t+1)$$

$$\overline{s}(t+2) = T^{2}\overline{s}(t) + TB\overline{i}(t) + B\overline{i}(t+1)$$

$$\overline{s}(t+3) = T\overline{s}(t+2) + B\overline{i}(t+2)$$

$$\overline{s}(t+3) = T\left\{T^{2}\overline{s}(t) + TB\overline{i}(t) + B\overline{i}(t+1)\right\} + B\overline{i}(t+2)$$

$$\overline{s}(t+3) = T^{3}\overline{s}(t) + T^{2}B\overline{i}(t) + TB\overline{i}(t+1) + B\overline{i}(t+2)$$

and, proceeding by induction

$\overline{s}(t+f) = T^{f}\overline{s}(t)+T^{f-1}B\overline{i}(t)+T^{f-2}B\overline{i}(t+1)+ \dots +B\overline{i}(t+f-1).$ Rewriting in matrix form

$$\overline{s}(t+f) = T^{f}\overline{s}(t) + \begin{bmatrix} T^{f-1}B & T^{f-2}B & . & . & B \end{bmatrix} \begin{bmatrix} \overline{i}(t) \\ \overline{i}(t+1) \\ . \\ . \\ \overline{i}(t+f-1) \end{bmatrix}$$

Therefore, by inspection, the above equation can be rewritten

$$\overline{s}'(t+1) = T'\overline{s}'(t)+B'\overline{1}'(t)$$

and the proof is complete for the next state equation. The output equation for M is

$$\overline{\mathbf{w}}(t) = C\overline{\mathbf{s}}(t) + D\overline{\mathbf{i}}(t).$$

Again, by successive substitution, the outputs at later times in terms of  $\overline{s}(t)$  are

$$\begin{split} \overline{w}(t+1) &= C\overline{s}(t+1) + D\overline{1}(t+1) \\ \overline{w}(t+1) &= C\left\{T\overline{s}(t) + B\overline{1}(t)\right\} + D\overline{1}(t+1) \\ \overline{w}(t+1) &= CT\overline{s}(t) + CB\overline{1}(t) + D\overline{1}(t+1) \\ \overline{w}(t+2) &= C\overline{s}(t+2) + D\overline{1}(t+2) \\ \overline{w}(t+2) &= C\left\{T^2\overline{s}(t) + TB\overline{1}(t) + B\overline{1}(t+1)\right\} + D\overline{1}(t+2) \\ \overline{w}(t+2) &= CT^2\overline{s}(t) + CTB\overline{1}(t) + CB\overline{1}(t+1) + D\overline{1}(t+2) \\ \vdots & \vdots \\ \overline{w}(t+f-1) &= C\overline{s}(t+f-1) + D\overline{1}(t+f) \\ \overline{w}(t+f-1) &= C\left\{T^{f-1}\overline{s}(t) + T^{f-2}B\overline{1}(t) + \dots + B\overline{1}(t+f-2)\right\} + D\overline{1}(t+f-1) \\ \overline{w}(t+f-1) &= CT^{f-1}\overline{s}(t) + CT^{f-2}B\overline{1}(t) + \dots + CB\overline{1}(t+f-2) + D\overline{1}(t+f-1). \end{split}$$

Thus, the output equations that have been developed are

$$\overline{w}(t) = C\overline{s}(t) + D\overline{i}(t)$$

$$\overline{w}(t+1) = CT\overline{s}(t) + CB\overline{i}(t) + D\overline{i}(t+1)$$

$$\overline{w}(t+2) = CT^{2}\overline{s}(t) + CTB\overline{i}(t) + CB\overline{i}(t+1) + D\overline{i}(t+2)$$

$$\vdots$$

$$\overline{w}(t+f-1) = CT^{f-1}\overline{s}(t) + CT^{f-2}B\overline{i}(t) + \dots + CB\overline{i}(t+f-2) + D\overline{i}(t+f-1).$$

Rewriting the above set of equations in matrix form yields

$$\begin{bmatrix} \overline{w}(t) \\ \overline{w}(t+1) \\ \overline{w}(t+2) \\ \vdots \\ \overline{w}(t+f-1) \end{bmatrix} = \begin{bmatrix} C \\ CT \\ CT \\ CT^2 \\ \vdots \\ CT^{f-1} \end{bmatrix} \begin{bmatrix} D \\ CB \\ CB \\ CTB \\ CTB \\ CTB \\ CTB \\ CT^{f-2}B \\ CT^{f-3}B \\ CT^{f-3}B \\ CT^{f-3}B \\ CT^{f-1}B \end{bmatrix} \begin{bmatrix} \overline{i}(t) \\ \overline{i}(t+1) \\ \overline{i}(t+2) \\ \vdots \\ \overline{i}(t+f-1) \end{bmatrix}$$

Thus the above equations may be written

$$\overline{w}'(t) = C'\overline{s}'(t) + D'\overline{1}'(t)$$

and the proof is complete.

This theorem is applicable to any linear sequential machine. For the case where the serial machine is an LFSR with only one input and one output the equations are quite simple.

2. Transformation of linear feedback shift registers.

A binary LFSR with a one-dimensional input space and a one-dimensional output space is described by the equations

$$\overline{s}(t+1) = \overline{Ts}(t) + \overline{BI}(t)$$

$$\overline{w}(t) = \overline{Cs}(t) + \overline{DI}(t)$$

If the shift register has k memory elements, then the state vectors form a k-dimensional vector space. Thus  $\overline{s}(t)$  is written as a column vector

$$\overline{s}(t) = \begin{bmatrix} s_0(t) \\ s_1(t) \\ s_2(t) \\ \vdots \\ \vdots \\ s_{k-1}(t) \end{bmatrix}.$$

If the machine has a one dimensional input space the matrix B is a kx1 matrix. A "1" in the i<sup>th</sup> row of B indicates that the input is connected to the ith memory element. Matrix T is a kxk matrix. A "1" in the i<sup>th</sup> row and j<sup>th</sup> column of T indicates a connection from the j<sup>th</sup> memory element to the ith.

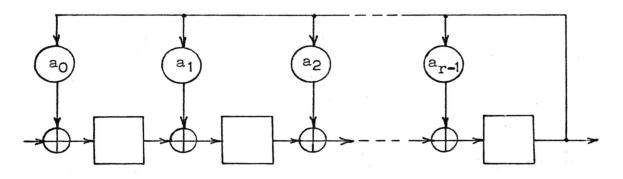

For example, a typical LFSR with three memory elements is described by the next-state equation

|        | s <sub>0</sub> (t+1) |   | 1 | 0 | 1 | s <sub>0</sub> (t) |   |   | Ŧ    |

|--------|----------------------|---|---|---|---|--------------------|---|---|------|

|        | s <sub>1</sub> (t+1) | = | 1 | 1 | 0 | $s_1(t)$           | + | 0 | 1(t) |

|        | s <sub>2</sub> (t+1) |   | 0 | 1 | 0 | $s_{2}(t)$         |   | 1 |      |

| altern | ately                |   |   |   |   | <br>               |   |   |      |

or a

$$s_{0}(t+1) = s_{0}(t)+s_{2}(t)+i(t)$$

$$s_{1}(t+1) = s_{0}(t)+s_{1}(t)$$

$$s_{2}(t+2) = s_{1}(t)+i(t).$$

Again as an example, the output equation for this machine might be

$$w(t) = \begin{bmatrix} 1 & 0 & 1 \end{bmatrix} \begin{bmatrix} s_0(t) \\ s_1(t) \\ s_2(t) \end{bmatrix} + \begin{bmatrix} 1 \end{bmatrix} i(t)$$

which yields

$w(t) = s_0(t) + s_2(t) + i(t).$

It is easily verified by inspection of Figure 7 that the LFSR shown in the figure corresponds to the next-state and output equations given above. It should be noted that the matrices T, B, C, and D contain all the information necessary to construct the LFSR if the matrices are properly interpreted.

The serial LFSR for encoding and decoding is described by a generator polynomial such that each stage of the register except the last one feeds only the succeeding stage. The last stage is fed back to preceding stages according to coefficients of the generator polynomial. A comparison of the serial LFSR of Figure 7 with the serial LFSR shown in Figure 2 on page 6 clearly shows their differences. The connection matrix, T, for the serial LFSR which accomplishes division by a polynomial is formed by constructing the companion matrix of the generator polynomial. According to Birkhoff and MacLane<sup>6</sup> the companion matrix for a polynomial

$g(x) = a_0 + a_1 x + \dots + a_k x^k$

is

$$T_{c} = \begin{bmatrix} 0 & 0 & 0 & \cdots & 0 & -a_{0} \\ 1 & 0 & 0 & \cdots & 0 & -a_{1} \\ 0 & 1 & 0 & \cdots & 0 & -a_{2} \\ \cdots & \cdots & \cdots & \cdots \\ \vdots & \vdots & \vdots & \vdots \\ 0 & 0 & 0 & \cdots & 1 & -a_{k-1} \end{bmatrix}$$

For a binary machine the coefficients  $a_i$  are elements from GF [2] so that

$-a_i \equiv a_i \mod 2$

and therefore each element in the last column of  $T_c$  is either one or zero.

The input for the machine is connected only to the first memory element and the output is the output of the last memory element. Thus the equations describing a serial linear-feedback-shift-register which accomplishes division by the generator polynomial are

$$\begin{bmatrix} s_{0}(t+1) \\ s_{1}(t+1) \\ \vdots \\ s_{k-1}(t+1) \end{bmatrix} = T_{c} \begin{bmatrix} s_{0}(t) \\ s_{1}(t) \\ \vdots \\ s_{k-1}(t) \end{bmatrix} + \begin{bmatrix} 1 \\ 0 \\ \vdots \\ 0 \end{bmatrix} i(t)$$

$$w(t) = \begin{bmatrix} 0 & 0 & \cdots & 0 & 1 \end{bmatrix} \begin{bmatrix} s_{0}(t) \\ s_{1}(t) \\ \vdots \\ s_{k-1}(t) \end{bmatrix} + \begin{bmatrix} 0 \end{bmatrix} i(t).$$

Example:

The companion matrix to the generator polynomial  $g(x) = 1+x+x^4$

is

$$\mathbf{T}_{\mathbf{C}} = \begin{bmatrix} \mathbf{0} & \mathbf{0} & \mathbf{0} & \mathbf{1} \\ \mathbf{1} & \mathbf{0} & \mathbf{0} & \mathbf{1} \\ \mathbf{0} & \mathbf{1} & \mathbf{0} & \mathbf{0} \\ \mathbf{0} & \mathbf{0} & \mathbf{1} & \mathbf{0} \end{bmatrix}$$

Therefore the next-state equation is

$$\begin{bmatrix} s_0(t+1) \\ s_1(t+1) \\ s_2(t+1) \\ s_3(t+1) \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 & 1 \\ 1 & 0 & 0 & 1 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 \end{bmatrix} \begin{bmatrix} s_0(t) \\ s_1(t) \\ s_2(t) \\ s_2(t) \\ s_3(t) \end{bmatrix} + \begin{bmatrix} 1 \\ 0 \\ 0 \\ 0 \end{bmatrix} i(t)$$

and the output equation is

$$\begin{bmatrix} w(t) \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 & 1 \end{bmatrix} \begin{vmatrix} s_0(t) \\ s_1(t) \\ s_2(t) \\ s_3(t) \end{vmatrix} + \begin{bmatrix} 0 \end{bmatrix} i(t) .$$

From these equations

$$s_{0}(t+1) = s_{3}(t)+i(t)$$

$$s_{1}(t+1) = s_{0}(t)+s_{3}(t)$$

$$s_{2}(t+1) = s_{1}(t)$$

$$s_{3}(t+1) = s_{2}(t)$$

and

$$w(t) = s_{z}(t).$$

These equations completely describe the LFSR shown in Figure 2 on page 6.

The serial-to-parallel transformation for the general linear sequential machine applies of course to the LFSR. Thus, if the serial machine is to be transformed to an fchannel analog, the describing equations become

$$\overline{s}'(t+1) = T_c'\overline{s}'(t)+B'\overline{1}'(t)$$

$\overline{w}'(t+1) = C'\overline{s}'(t)+D'\overline{1}'(t)$

where T<sub>c</sub>', B', C', and D' are as described previously for linear sequential machines. Forming these matrices is quite simple as shown in the following example. Example:

Given that a serial LFSR has a generator polynomial

$$g(x) = 1 + x + x^4$$

and that a two-channel analog of this machine is desired (i.e. f = 2), then

|                                                                                 |       | Го  | 0 | 0  | 1   |   | 0   | 0 | 0 | 1 |   | 0 | 0 | 1  | 0 |  |

|---------------------------------------------------------------------------------|-------|-----|---|----|-----|---|-----|---|---|---|---|---|---|----|---|--|

| T <sub>c</sub> ' = 1                                                            | , 2 _ | 1   | 0 | 0  | 1   |   | 1   | 0 | 0 | 1 |   | 0 | 0 | 1  | 1 |  |

| <sup>1</sup> c = 1                                                              | °c =  | 0   | 1 | 0  | 0   |   | 0   | 1 | 0 | 0 | = | 1 | 0 | 0  | 1 |  |

|                                                                                 | Lo    | 0   | 1 | 0_ |     | 0 | 0   | 1 | 0 |   | 0 | 1 | 0 | 0_ |   |  |

| $\mathbf{B}' = \begin{bmatrix} \mathbf{T}\mathbf{B} & \mathbf{B} \end{bmatrix}$ |       |     |   |    |     |   |     |   |   |   |   |   |   |    |   |  |

|                                                                                 | 00    | 0   | 1 | Г  | 1]  | Γ | ٦C  |   |   |   |   |   |   |    |   |  |

| T <sub>c</sub> B =                                                              | 10    | 0   | 1 | 0  |     | . | 1   |   |   |   |   |   |   |    |   |  |

|                                                                                 | 0 1   | 0 ( | b | (  | o = | 0 | o   |   |   |   |   |   |   |    |   |  |

|                                                                                 | 0 0   | 1 ( | 0 | L  | 5   | L | 5 ] |   |   |   |   |   |   |    |   |  |

|                                                                                 |       |     |   |    |     |   |     |   |   |   |   |   |   |    |   |  |

therefore

$$B' = \begin{bmatrix} 0 & 1 \\ 1 & 0 \\ 0 & 0 \\ 0 & 0 \end{bmatrix}$$

$$C' = \begin{bmatrix} C \\ CT \end{bmatrix}$$

$$CT_{c} = \begin{bmatrix} 0 & 0 & 0 & 1 \\ 1 & 0 & 0 & 1 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 \end{bmatrix} = \begin{bmatrix} 0 & 0 & 1 & 0 \end{bmatrix}$$

therefore

$$C' = \begin{bmatrix} 0 & 0 & 0 & 1 \\ 0 & 0 & 1 & 0 \end{bmatrix}$$

$$D' = \begin{bmatrix} D \\ CB & D \end{bmatrix}$$

$$CB = \begin{bmatrix} 0 & 0 & 0 & 1 \end{bmatrix} \begin{bmatrix} 1 \\ 0 \\ 0 \\ 0 \end{bmatrix} = \begin{bmatrix} 0 \end{bmatrix}$$

therefore

$$\mathbf{D}' = \begin{bmatrix} \mathbf{0} & \mathbf{0} \\ \mathbf{0} & \mathbf{0} \end{bmatrix} \cdot$$

Thus, the equations for the parallel analog are

$$\begin{bmatrix} s_{0}'(t+1) \\ s_{1}'(t+1) \\ s_{2}'(t+1) \\ s_{3}'(t+1) \end{bmatrix} = \begin{bmatrix} 0 & 0 & 1 & 0 \\ 0 & 0 & 1 & 1 \\ 1 & 0 & 0 & 1 \\ 0 & 1 & 0 & 0 \end{bmatrix} \begin{bmatrix} s_{0}'(t) \\ s_{1}'(t) \\ s_{2}'(t) \\ s_{2}'(t) \\ s_{3}'(t) \end{bmatrix} + \begin{bmatrix} 0 & 1 \\ 1 & 0 \\ 0 & 0 \end{bmatrix} \begin{bmatrix} i_{0}(t) \\ i_{1}(t) \\ i_{1}(t) \end{bmatrix}$$

where the input  $i_1(t)$  is the input which was described as i(t+1) in the serial machine, and

$$\begin{bmatrix} w_{0}(t) \\ w_{1}(t) \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 & 1 \\ 0 & 0 & 1 & 0 \end{bmatrix} \begin{bmatrix} s_{0}(t) \\ s_{1}'(t) \\ s_{2}'(t) \\ s_{3}'(t) \end{bmatrix}$$

where the output  $w_1(t)$  is the output which was described as w(t+1) in the serial machine. It should be noted that the machine described by the above equations is identical to that shown in Figure 6 on page 13.

The serial-to-parallel transformation of an LFSR, as shown by the previous example, consists of manipulation of four matrices. The techniques for obtaining the matrices for the parallel machine are straightforward but can be tedious for large matrices. Because the transformations are expressed mathematically they may be readily programmed on a digital computer, as indicated by the simplicity of the program in Appendix A. In addition, inspection of the  $T_c$  and B matrices reveals that the matrices  $T_c'$  and B' can be formed very easily.

The f-channel analog of an LFSR having companion matrix  $T_c$  will have an interconnection matrix  $T_c^{i} = T_c^{f}$ . Obviously  $T_c^{f}$  can be found by repeatedly multiplying  $T_c$ by itself, but a simpler way of finding  $T_c^{f}$  will now be developed. If  $T_c$  is a kxk companion matrix with elements  $t_{ij}$  and Q is any kxk matrix with elements  $q_{ij}$ , then the product matrix QT<sub>c</sub> with elements  $(qt)_{ij}$  has the following properties:

1.  $(qt)_{ij} = q_{i(j+1)}$  for j = 1, 2, ..., k-12.  $(qt)_{ik} = q_{i1}t_{1k}+q_{i2}t_{2k}+ \cdots +q_{ik}t_{kh}$ This can be demonstrated by multiplying the matrices:

$$QT_{c} = \begin{bmatrix} q_{11} & q_{12} & \cdots & q_{1k} \\ q_{21} & & & \\ \vdots & & & \\ q_{k1} & \cdots & q_{kk} \\ q_{k1} & \cdots & q_{kk} \end{bmatrix} \begin{bmatrix} 0 & 0 & \cdots & 0 & t_{1k} \\ 1 & 0 & \cdots & 0 & t_{2k} \\ 0 & 1 & & \ddots & \\ \vdots & & & \vdots \\ 0 & 0 & 0 & 1 & t_{kk} \end{bmatrix}$$

It is important to note that

$$t_{ij} = 1 \text{ for } j = i-1 \text{ and } j \neq k$$

$$= 0 \text{ for } j \neq i-1 \text{ and } j \neq k$$

Thus property 1 becomes obvious upon multiplication of the two matrices. Elements of the  $k^{th}$  column of  $T_c$  are coefficients of the characteristic polynomial associated with the companion matrix. Therefore elements of the  $k^{th}$ column of the product matrix are calculated using conventional matrix multiplication.

Matrix  $T_c^2$  can be calculated by application of the two properties as follows:

$$T_c^2 = T_c \cdot T_c = Q \cdot T_c$$

.

Then the first k-1 columns of  $T_c^2$  are formed by shifting columns 2, 3, . . . k of  $T_c$  to the left one place according to property 1. The k<sup>th</sup> column of  $T_c^2$  is formed by observing that  $t_{1k}$ ,  $t_{2k}$ , . . .  $t_{kk}$  are coefficients of the generator polynomial

$g(x) = t_1 + t_2 x + \cdots + t_k x^k$ .

The t<sub>i</sub>'s are either 0 or 1 depending upon the particular generator polynomial. Thus any element  $(qt)_{ik}$  in the last column of  $T_c^2$  is simply the sum of the elements in row 1

of  $T_c$  which are in a column corresponding to a nonzero  $t_i$ . To find  $T_c^3$  the process is repeated so that

$T_c{}^3 = T_c{}^2 T_c$  where now  $T_c{}^2 = Q$ . To obtain  $T^f$ , this process must be repeated for  $T_c{}^4$ ,  $T_c{}^5$  and so on for a total of f-1 iterations.

Example:

If

$$g(x) = 1 + x + x^3 + x^4$$

and  $f = 3$ , then

$$T_c = \begin{bmatrix} 0 & 0 & 0 & 1 \\ 1 & 0 & 0 & 1 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 1 \end{bmatrix}$$

Then column 1 of  $T_c^2$  is column 2 of  $T_c$ , column 2 of  $T_c^2$ is column 3 of  $T_c$ , and column 3 of  $T_c^2$  is column 4 of  $T_c$ . The 4th column of  $T_c$  indicates that the element in row i of the 4th column of  $T_c^2$  is to be a linear sum of the elements in row i and columns 1, 2, and 4 of  $T_c$ . Column 3 is ignored because element 3 in column 4 of  $T_c$  is 0. Thus,  $T_c^2$  is formed by shifting columns to the left, then adding the elements in each row modulo 2 to form each element in the 4th column to obtain

$$T_{c}^{2} = \begin{bmatrix} 0 & 0 & 1 & 1 \\ 0 & 0 & 1 & 0 \\ 1 & 0 & 0 & 1 \\ 0 & 1 & 1 & 1 \end{bmatrix}.$$

Then  $T_c^3$  is formed by iterating the process so that

$$\mathbf{T_{c}}^{3} = \mathbf{T_{c}}^{2}\mathbf{T_{c}} = \begin{bmatrix} 0 & 1 & 1 & 1 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 1 & 1 & 1 & 0 \end{bmatrix}$$

Investigation of properties of the B and B' matrices also reveals a simple method for forming B'. For serial LFSR's where the input is connected only to the first state the B matrix is

$$B = \begin{bmatrix} 1 \\ 0 \\ 0 \\ \vdots \\ 0 \\ 0 \end{bmatrix}$$

Therefore the product of a square matrix Q premultiplying B yields a column matrix which is the first column of Q. This statement can be verified by matrix multiplication. It has been shown that

$B' = \begin{bmatrix} T^{f-1}B & T^{f-2}B & \dots & TB & B \end{bmatrix}$ so that the f<sup>th</sup> column of B' is B, the (f-1)<sup>th</sup> column is the 1<sup>st</sup> column of T, the (f-2)<sup>nd</sup> is the 1<sup>st</sup> column of T<sup>2</sup>,

and so h. Thus if the example used for the T<sub>c</sub> matrix, with

$$g(x) = 1 + x + x^3 + x^4$$

and f = 3, is used, the B matrix can be written by inspe of the matrices  $T_c$  and  $T_c^2$  as

$$B' = \begin{bmatrix} 0 & 0 & 1 \\ 0 & 1 & 0 \\ 1 & 0 & 0 \\ 0 & 0 & 0 \end{bmatrix}.$$

The matrix method of transforming serial LFSR's to equivalent parallel machines requires only a knowledge of the generator polynomial for the serial machine and the number of parallel channels desired in the parallel machine. A computer program, described in Appendix A, has been written such that, if g(x) and f are specified, the resulting T' and B' matrices are supplied by the program. Thus transformation becomes completely automatic to the program user.

If the output equation were also desired, the program could be readily expanded to perform calculation of the C' and D' matrices. It should also be noted here that, for a general linear sequential machine, the transformation program would not be very difficult. However, more computer time would be required because the simplification described earlier applies only to the very special class of LFSR's used for encoding and decoding polynomial codes.

# III. REDUCTION OF MACHINE COMPLEXITY

The next-state and output equations for the parallel LFSR, as derived using the foregoing algorithm, do not necessarily specify the simplest machine. The simplest machine shall be defined as the machine which requires the least number of modulo 2 adders under the following constraints:

- 1) Only two-input adders are to be used

- 2) No adders will be shared.

The first constraint was chosen because most manufacturers of integrated circuits list two-input exclusive-or gates (which are equivalent to modulo 2 adders) as one of their "off-the-shelf" items. There is no apparent pattern to the way in which the adders are shared so that the second constraint seems necessary if some criterion of machine complexity is to be established. It should be noted that the second constraint is meant to imply that sharing of adders is permitted only after the simplest machine, in terms of the above constraints, is obtained.

Under these constraints the number of adders required for realization of a machine can be determined by investigation of the T', B', C', and D' matrices. For example, in the next-state equation the first row of the T' and B' matrices indicate inputs to the first stage (s<sub>0</sub>). More specifically, the input to the first stage is the modulo 2 sum of all feedback connections indicated by "ones" entered in the T' and B' matrices. Clearly, then the number of two-input adders needed for the first stage is one less than the total number of ones in the first rows of matrices T' and B'. The number of adders required for succeeding stages is determined in a similar fashion. It follows that the total number of two-input adders required for realizing the state equation is the total number of ones in both matrices minus the number of rows (k) in the matrices.

From the above it is apparent that some method for reducing the number of ones in the T', B', C', and D' matrices is desirable. This section of the paper presents an algorithm which tends to reduce the number of ones in the T' and B' matrices. However, before a formal algorithm is developed it is necessary to:

- prove that premultiplication of the next-state equation of a linear sequential machine M, by any nonsingular matrix Q, provides a new machine M' isomorphic to machine M,

- demonstrate the usefulness of machine M' as an encoder or decoder, or both,

- 3) demonstrate that premultiplication of the next-state equation of M by matrix Q can result in circuit simplification.

After the three problems listed above have been solved the algorithm will be developed.

# A. Isomorphism in Decoders

It has been shown earlier in this report that a linear sequential machine M is described by the vector spaces  $\overline{S}$ ,  $\overline{I}$ , and  $\overline{W}$  and two linear functions f and g. The vector spaces  $\overline{S}$ ,  $\overline{I}$ , and  $\overline{W}$  are, respectively the next-state, input and output spaces and the functions f and g are, respectively, the input and output functions. Thus, for conciseness it can be said that

$M = (\overline{S}, \overline{I}, \overline{W}, f, g)$

where the symbols are as described above.

Given some linear sequential machine M, the next-state and output equations are

$f(\overline{s},\overline{i}) = \overline{s}(t+1) = \overline{Ts}(t) + \overline{Bi}(t)$  $g(\overline{s},\overline{i}) = \overline{w}(t) = \overline{Cs}(t) + \overline{Di}(t).$

It will be assumed that the state space is k dimensional. Then if the next-state equation is premultiplied by some nonsingular kxk matrix Q the result is

$Q\overline{s}(t+1) = QT\overline{s}(t)+QB\overline{i}(t)$

which can also be written

$$Q\overline{S}(t+1) = QTQ^{-1}Q\overline{S}(t) + QB\overline{I}(t).$$

Then a new state vector  $\overline{\sigma}(t)$  can be defined such that

$$Q\overline{S}(t) = \overline{C}(t)$$

so that

$Q\overline{s}(t+1) = \overline{O}(t+1).$

Then the next-state equation can be rewritten

$$\overline{O}(t+1) = QTQ^{-1} \overline{O}(t) + QB\overline{I}(t).$$

The output equation

$$\overline{\mathbf{w}}(t) = C\overline{s}(t) + D\overline{1}(t)$$

can be written

$$\overline{w}(t) = CQ^{-1}Q\overline{s}(t) + D\overline{i}(t).$$

But

$$Q\overline{s}(t) = \overline{O}(t)$$

so that the output equation becomes

$$\overline{\mathbf{w}}(t) = CQ^{-1} \overline{\mathbf{o}} (t) + D\overline{\mathbf{i}}(t).$$

Thus, as indicated by the next-state and output equations, a new machine M' has been described such that

$$M' = (\overline{S}', \overline{I}', \overline{W}', f', g')$$

where

$$f'(\overline{\sigma},\overline{i}) = \overline{\sigma}(t+1) = QTQ^{-1} \overline{\sigma}(t) + QB\overline{i}(t)$$

$$g'(\overline{\sigma},\overline{i}) = \overline{w}(t) = CQ^{-1} \overline{\sigma}(t) + D\overline{i}(t).$$

It is helpful at this point to consider the physical implications of the process described above. A comparison of the next-state equation for machines M and M' shows that the interconnections between memory elements are described by matrix T for machine M and by matrix  $QTQ^{-1}$  for machine M'. Similarly, the connection of inputs to memory elements is described by matrix B for machine M and by matrix QB for machine M'. A comparison of the output equations reveals different interconnection matrices, C for machine M and  $CQ^{-1}$  for machine M', but identical input-connection (D) matrices. Obviously then the two machines M and M' "look different", but it will be shown that the machines are isomorphic.

Two linear sequential machines are isomorphic if the two machines are identical except for a relabelling of the inputs, internal states and outputs. That is to say, two linear sequential machines  $M = (\overline{S}, \overline{I}, \overline{W}, f, g)$ and  $M' = (\overline{S'}, \overline{I'}, \overline{W'}, f', g')$  are isomorphic if and only if there exist three one-to-one mappings

$$\begin{array}{c} h_1: \ \overline{S} \longrightarrow \overline{S}' \\ h_2: \ \overline{I} \longrightarrow \overline{I}' \\ h_3: \ \overline{W} \longrightarrow \overline{W}' \end{array}$$

such that

Thus to show that machine M', obtained by multiplying the next-state equation of M by Q, is isomorphic to M, the mappings  $h_1$ ,  $h_2$ , and  $h_3$  must first be identified. It will be assumed that the correspondences

$$\begin{array}{c} {}^{h_{1}} \longleftrightarrow \mathbb{Q} \\ {}^{h_{2}} \longleftrightarrow \mathbb{I}_{k} \\ {}^{h_{3}} \longleftrightarrow \mathbb{I}_{k} \end{array}$$

exist where Q is the nonsingular kxk matrix described earlier and  $I_k$  is the kxk identity matrix. Then the mappings must be tested to determine whether they satisfy the relationships

$$h_1 \left[ f(\overline{s}, \overline{i}) \right] = f' \left[ h_1(\overline{s}), h_2(\overline{i}) \right]$$

$$h_3 \left[ g(\overline{s}, \overline{i}) \right] = g' \left[ h_1(\overline{s}), h_2(\overline{i}) \right]$$

Investigation of the next state equation reveals that  $h_{1} \left[ f(\overline{s},\overline{1}) \right] = Q \left[ f(\overline{s},\overline{1}) \right] = QT\overline{s}(t) + QB\overline{1}(t)$

and that

$$f' \left[ h_1(\overline{s}), h_2(\overline{1}) \right] = f' \left[ Q\overline{s}, \overline{1} \right] = QTQ^{-1} \cdot Q\overline{s}(t) + QB\overline{1}(t)$$

$$= QT\overline{s}(t) + QB\overline{1}(t).$$

Inspection of the two equations above verifies that

$$h_1[f(\overline{s},\overline{1})] = f'[h_1(\overline{s}),h_2(\overline{1})].$$

Now, investigation of the output equation reveals that

$$h_3[g(\overline{s},\overline{1})] = g(\overline{s},\overline{1}) = C\overline{s}(t)+D\overline{1}(t)$$

and that

$$g'[h_1(\overline{s}),h_2(\overline{1})] = g'[Q\overline{s},\overline{1}] = CQ^{-1}Q\overline{s}(t)+D\overline{1}(t)$$

$$= C\overline{s}(t)+D\overline{1}(t).$$

Inspection of the above equations verifies that

$h_{\overline{3}}[g(\overline{s},\overline{1})] = g'[h_1(\overline{s}),h_2(\overline{1})].$

Thus, it follows that machine M' is isomorphic to machine M and that the only difference between M and M' is a relabelling of the internal states.

At this point it has been shown that a linear sequential machine M' can be constructed which differs from a linear sequential machine M only in the labelling of its internal states. It remains to be shown that construction of such a machine can lead to realizations which are simpler than the original machine and that a communication system which uses cyclic error-detecting codes can be constructed using the simpler machines.

A communication system in which a cyclic errordetecting code is used will now be defined. The encoder shall be an LFSR which provides a remainder in q clock-times, that is, a parallel LFSR. If the encoder is called machine M, then the decoder shall be denoted M', where M' is the machine obtained by multiplication of the next-state equation of M by a nonsingular matrix Q. Then for the system thus defined, attempts at simplifying the decoder are permitted; but the encoder must not be changed. Justification for defining the communication system in this way requires consideration of the functions of the decoder and encoder.

First, the decoder receives a coded message which shall be called  $m^*(x)$ . The decoder must divide  $m^*(x)$  by g(x) and form a remainder  $r^*(x)$ . If  $r^*(x) = 0$ , then no detectable errors have occurred during transmission; but any nonzero remainder indicates error. It has previously been shown that the coefficients of the remainder are the elements of the state vector of the machine after q clock times. The states of machine M and M' are, respectively,  $\overline{s}(q)$  and  $Q\overline{s}(q)$  after q clock times (assuming the machines are initially in the zero state). Thus if state  $\overline{s}(q)$  is the zero vector, then it follows that state  $Q_{\overline{S}}(q)$  is also the zero vector. This ensures that, if no errors have occurred, either machine will provide a zero remainder. On the other hand, if a detectable number of errors has occurred machine M would provide a nonzero remainder, but machine M' would also have a nonzero remainder so that it is clear that either machine can be used as a decoder.

The function of the encoder is to divide the message polynomial by the generator polynomial and provide a remainder. The encoded message is of the form

$x^{n-k}m(x)+r(x) = g(x)q(x).$

Suppose that machine M is in state  $\overline{s}(q)$  after q clock

times and that the elements of  $\overline{s}(q)$  are correct coefficients of r(x). Then a machine M' with states  $Q\overline{s}(t)$  would be in state  $Q\overline{s}(q)$  after q clock times. In general the elements of  $Q\overline{s}(q)$  are not the correct coefficients of r(x) and therefore machine M' does not provide the desired encoding functions. Therefore, attempts at simplification are restricted to the decoder in the following development. B. Development of an Algorithm for Machine Simplification.

It will now be shown by an example that multiplication of the next-state equation of a machine M by a nonsingular matrix Q can produce a simpler isomorphic machine M'. If the generator polynomial for a decoder is  $x^{5}+x^{4}+x^{2}+1$ , then the companion matrix is

$$\mathbf{T}_{\mathbf{C}} = \begin{bmatrix} \mathbf{0} & \mathbf{0} & \mathbf{0} & \mathbf{0} & \mathbf{1} \\ \mathbf{1} & \mathbf{0} & \mathbf{0} & \mathbf{0} & \mathbf{0} \\ \mathbf{0} & \mathbf{1} & \mathbf{0} & \mathbf{0} & \mathbf{1} \\ \mathbf{0} & \mathbf{0} & \mathbf{1} & \mathbf{0} & \mathbf{0} \\ \mathbf{0} & \mathbf{0} & \mathbf{0} & \mathbf{1} & \mathbf{1} \end{bmatrix}$$

Given that the machine is to have 6 parallel channels, a computer program written for the serial-to-parallel transformation provides the following:

$$T_{c}' = T_{c}^{6} = \begin{bmatrix} 1 & 1 & 0 & 1 & 1 \\ 1 & 1 & 1 & 0 & 1 \\ 1 & 0 & 1 & 0 & 1 \\ 1 & 0 & 1 & 0 & 1 \\ 1 & 1 & 0 & 1 & 0 \\ 1 & 0 & 1 & 1 & 0 \end{bmatrix}; B' = \begin{bmatrix} 1 & 0 & 0 & 0 & 0 & 1 \\ 0 & 0 & 0 & 0 & 1 & 0 \\ 1 & 0 & 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 & 0 & 0 \\ 1 & 1 & 0 & 0 & 0 & 0 \end{bmatrix}$$

In this example the first state requires five adders, the second stage four adders, and so forth, for a total of 20 adders.

Now a machine M' isomorphic to the above machine is to be specified. The nonsingular 5x5 matrix to be used for this example is

|   | 1 |   |   |   |   |   |  |

|---|---|---|---|---|---|---|--|

|   |   | 1 |   |   | 0 |   |  |

|   |   | 0 |   |   | 0 |   |  |

| Q | = | 0 | 0 | 1 | 0 | 0 |  |

|   |   | 0 | 0 | 0 | 1 | 0 |  |

|   |   | 0 | 0 | 0 | 0 | 1 |  |

In this particular case it happens that

$$Q = Q^{-1} .$$

Now the matrices for the next-state equation f' are

|                 | 0  | 1 | 0 | 1 | 0  |   |     |   |   |   |   |   |   | 1 |  |

|-----------------|----|---|---|---|----|---|-----|---|---|---|---|---|---|---|--|

|                 |    |   |   |   | 0  |   |     |   |   |   |   |   |   | 0 |  |

| $QT_c Q^{-1} =$ | 1  | 0 | 0 | 0 | 1  | ; | QB' | = | 1 | 0 | 0 | 1 | 0 | 0 |  |

|                 | 1  | 1 | 0 | 1 | 0  |   |     |   | 0 | 0 | 1 | 0 | 0 | 0 |  |

|                 | _1 | 0 | 0 | 1 | 0_ |   |     |   | 1 | 1 | 0 | 0 | 0 | 0 |  |

Inspection of the above matrices indicates that 16 two-input modulo 2 adders are required. Therefore a reduction of four adders is realized.

The above example has demonstrated that the Q matrix selected for the example did indeed reduce the number of adders necessary to implement the decoder. However the example does not show how to select the Q matrix which results in the simplest machine. For, although some nonsingular matrices lead to simpler machine realizations, there are others which lead to more complex realizations. One method for finding the matrix or matrices which lead to the simplest realization of machine M' is simply to try every possible nonsingular matrix.

Suppose every possible nonsingular kxk matrix is formed, the inverse calculated, and matrix multiplication performed as described in the example. Then inspection of each set of matrices  $QT_cQ^{-1}$  and QB' will yield a simplest realization. But the number of possible nonsingular kxk matrices with elements from the field of integers modulo 2 is very large. Birkhoff and MacLane<sup>6</sup> prove that a kxk matrix over some field is nonsingular if and only if its rows are linearly independent. Thus, if the rows are considered vectors in a k-dimensional space, then a nonsingular matrix must have no two rows alike, and no row which is a vector sum of two or more other rows of the matrix.

These row properties can be used to construct all possible nonsingular matrices. Further, the requirement that the rows be linearly independent leads to a simple expression for the total possible number of different nonsingular kxk matrices,  $N_k$ , with elements from GF [2]. Thus it can be shown that

$$N_k = (2^{k}-1)(2^{k}-2)(2^{k}-4) \dots (2^{k}-2^{k-1}).$$

or

$$N_{k} = \prod_{i=0}^{k-1} (2^{k}-2^{i}).$$

From the above expression it is found that there exist 168 different nonsingular 3x3 matrices, about 20,000 different nonsingular 4x4 matrices, and about 10 million different nonsingular 5x5 matrices. Obviously the total number of nonsingular matrices rises very rapidly with k. The process of finding all nonsingular 5x5 matrices with corresponding inverses would be a formidable task even with a computer. Clearly some method of selecting only a small number of matrices from the millions of possibilities is necessary.

Because nonsingular matrices must be formed and because the inverse of the matrix must be found in each case, two meaningful criteria for selection of the Q matrices are; 1) ease in which the matrix is formed and 2) the ease with which the matrix inverse is formed. Investigation of the properties of square matrices and identity matrices indicates some simple methods for forming nonsingular matrices and inverses. These methods will be developed in the following paragraphs.

Birkhoff and MacLane<sup>6</sup> prove that a kxk matrix has rank k if and only if it is row equivalent to the identity matrix  $I_k$ . By definition a matrix Q is row equivalent to matrix  $I_k$  if Q can be obtained from  $I_k$  by a finite succession of the following elementary row operations:

1) The interchange of any two rows

2) The addition of any row to any other row. Notice that a third operation, multiplication of any row by a nonzero scalar, is omitted because the operation

is trivial in GF [2]. Birkhoff and MacLane also prove that a kxk matrix has rank k and is nonsingular if and only if its rows are linearly independent.

From the above properties it follows that any kxk matrix formed by a finite succession of elementary row operations is a nonsingular matrix. Further, the k linearly independent rows of a nonsingular matrix form a basis for the vector space  $V_k(F)$  (where F is GF [2]). Thus it follows that the set of kxk matrices generated by elementary row operations on  $I_k$  is the set of all possible nonsingular kxk matrices.

To specify the set of nonsingular matrices to be tried for network simplification, some properties of the matrix inverse may be noted. Birkhoff and MacLane prove that if a kxk matrix is reduced to the identity by a sequence of row operations, the same sequence of operations applied to the identity will give the inverse of the kxk matrix. Thus if a nonsingular matrix Q is formed by applying a sequence of elementary row operations on the identity matrix, the easiest method of finding its inverse is to apply the same sequence of row operations to the matrix Q. Now the properties of vectors (or rows) with elements from GF [2] become important. If the identity matrix I<sub>k</sub> is described in terms of the identity vectors  $\overline{e_1}$  as

$$I_{k} = \begin{bmatrix} \overline{e}_{1} \\ \overline{e}_{2} \\ \vdots \\ \vdots \\ \overline{e}_{k} \end{bmatrix}$$

where

| ē <sub>1</sub> = |      |     |   |   |   |    |

|------------------|------|-----|---|---|---|----|

| ē <sub>2</sub> = | 0    | 1 0 | • | • | • | 0] |

| ē <sub>3</sub> = | [o ( | D 1 | • | • | • | 0] |

| •                |      |     |   |   |   |    |

| •                | F    |     |   |   |   | ٦  |

| ē <sub>k</sub> = | Lo ( | 0 0 | • | • | 0 | 1  |

then the result of adding row 1 to row 2 is

It should be noted that to obtain the identity matrix from the above matrix the necessary row operation is addition of row 1 to row 2 because  $\overline{e_1} + \overline{e_1} \equiv 0 \mod 2$ . Thus in this case the matrix is equal to its inverse. From this example it is clear that any matrix formed by adding row 1 of the identity matrix to any other row will be equal to its inverse. Further, if any row of the identity matrix is added to any other row, the resulting matrix will be equal to its inverse. From the above an algorithm can be developed for forming nonsingular matrices having the property that any matrix thus formed is equal to its inverse. The algorithm consists of the following steps:

- 1) Add row 1 to row 2 to obtain matrix  $Q_1$  such that  $Q_1 = Q_1^{-1}$ .

- Add row 1 to row 3 to obtain matrix Q<sub>2</sub>, where

$$Q_2 = \begin{bmatrix} \overline{e}_1 \\ \overline{e}_1 + \overline{e}_2 \\ \overline{e}_1 + \overline{e}_3 \\ \overline{e}_4 \\ \vdots \\ \vdots \\ \overline{e}_k \end{bmatrix}$$

It is apparent that  $Q_2 = Q_2^{-1}$  because the identity is obtained by adding row 1 to rows 2 and 3 of  $Q_2$ .

3) Repeat the process by adding row 1 to rows 4, 5, . . n. Clearly each of the k-1 matrices formed will be of the form  $Q_i = Q_j^{-1}$ . It is apparent that

$$Q_{k-1} = \begin{bmatrix} \overline{e}_1 \\ \overline{e}_1 + \overline{e}_2 \\ \overline{e}_1 + \overline{e}_3 \\ \vdots \\ \vdots \\ \overline{e}_1 + \overline{e}_k \end{bmatrix}$$

4) Reiterate the above process, again successively adding row 1 to each of the other rows. The first matrix formed by step 4 is Q<sub>b</sub> where

$$Q_{k} = \begin{bmatrix} \overline{e}_{1} \\ \overline{e}_{2} \\ \overline{e}_{1} + \overline{e}_{3} \\ \overline{e}_{1} + \overline{e}_{4} \\ \vdots \\ \overline{e}_{1} + \overline{e}_{k} \end{bmatrix}$$

It is easily verified that the sequence of row operations applied to  $I_k$  to form  $Q_k$ , when applied to  $Q_k$ , reduces to the identity  $I_k$ . Thus  $Q_k = Q_k^{-1}$ . Further  $Q_{k+1} = Q_{k+1}^{-1}$  and so forth.

5) At the end of step 4, when  $\overline{e_1}$  is added to  $\overline{e_k}$ , the resulting matrix is again the identity. Thus steps 1 through 4 can be reiterated for rows two through k to form a set of nonsingular matrices having the property that each matrix is its own inverse.

It is apparent that steps 1 through 4 of the algorithm provide 2(k-1) matrices. Thus, because the matrix has k rows, the algorithm provides  $k \cdot 2(k-1)$  different nonsingular matrices for which the inverse is identical to the matrix. Then for the case where k = 5 the

algorithm provides 40 different nonsingular matrices out of a possible 10 million different nonsingular matrices.

The algorithm for simplification can be summarized as a technique for selecting a small sample of nonsingular matrices from a large population of such matrices followed by substitution of each matrix in the sample into the relationship

$$T_{c}^{*} = QT_{c}^{'}Q^{-1}$$

$$B^{*} = QB^{'}$$

where  $T_c^*$  and  $B^*$  are the interconnection matrices for a machine isomorphic to the original machine. The simplest machine from this sample is determined by counting the number of ones in the  $T_c^*$  and  $B^*$  matrices.

A computer program, given in Appendix A, has been written incorporating the serial-parallel transformation algorithm described earlier and the simplification algorithm described in this section. Required inputs to the program are:

- 1) The coefficients of the generator polynomial

- The number of channels (f) desired in the parallel analog.

The program provides the following information to the user:

- 1)  $T_c' = T_c^f$  and B' matrices

- 2) A listing of all Q matrices generated by the simplification algorithm along with the matrices  $QT_c'Q^{-1}$  and QB'corresponding to each Q.

Table 3 summarizes the outcomes of several computer runs using the program discussed above. Selection of the generator polynomials for these trials was arbitrary. The number of gates listed under column A is the number required by the  $T'_c$  and B' matrices as obtained by the serial-parallel transformation algorithm. Columns B and C indicate the best and worst cases respectively obtained in the simplification attempts with Q.

## TABLE 3

| ſ |                                                                                    | -                        | Number of Two Input<br>Adders Required |              |              |  |  |  |

|---|------------------------------------------------------------------------------------|--------------------------|----------------------------------------|--------------|--------------|--|--|--|

|   | Generator                                                                          | Number of                | A                                      | В            | С            |  |  |  |

|   | Polynomial                                                                         | Parallel<br>Channels (f) | No Simpli-<br>fication                 | Best<br>Case | Wors<br>Case |  |  |  |

|   | 1+x <sup>2</sup> +x <sup>4</sup> +x <sup>5</sup>                                   | 6                        | 20                                     | <b>1</b> 6   | 27           |  |  |  |

|   |                                                                                    | 8                        | 26                                     | 22           | 31           |  |  |  |

|   | 1+x+x <sup>2</sup> +x <sup>4</sup> +x <sup>5</sup>                                 | 12                       | 34                                     | 32           | 39           |  |  |  |

|   |                                                                                    | 6                        | 18                                     | 15           | 22           |  |  |  |

|   |                                                                                    | 8                        | 22                                     | 20           | 26           |  |  |  |

|   |                                                                                    | 12                       | 34                                     | 31           | 39           |  |  |  |

|   | 1+x+x <sup>2</sup> +x <sup>4</sup> +x <sup>5</sup> +x <sup>7</sup> +x <sup>9</sup> | 6                        | 34                                     | 29           | 42           |  |  |  |

Summary of Results of Computer Runs

The table indicates that some reduction in the required number of adders was achieved in every case. The reduction ranged from 6 percent to 20 percent with an average for the seven trials of 13 percent. A comparison of the best and

worst cases indicates that, depending upon the original T' and B' matrices, reductions of up to 40 percent of the adders might be realized.

One likely reason for the apparent success of this algorithm is that the matrices constructed all have a low density of ones as elements. The desirability of this property can be demonstrated by looking at the B' matrix for a parallel LFSR. From the properties of the B' matrix described on page 33 it should be evident that the last column of B' is always the identity column  $\begin{bmatrix} 1 & 0 & 0 & \dots & 0 \end{bmatrix}^T$ . Similarly, the second last column is  $\begin{bmatrix} 0 & 1 & 0 & 0 & \dots & 0 \end{bmatrix}^T$ and so forth so that if the B' matrix has k or less columns (k is the size of matrix  $T_c$ ), then all of its columns are identity vectors. Also, if the B' matrix has more than k columns, then its last k columns are identity vectors. Investigation of a particular matrix

$$B' = \begin{bmatrix} 0 & 0 & 1 \\ 0 & 1 & 0 \\ 1 & 0 & 0 \\ 0 & 0 & 0 \end{bmatrix}$$

then shows the effect of the Q matrix on the B matrix. The transformation of the B<sup>i</sup> matrix by the algorithm amounts to calculation of the product

$$QB' = \begin{bmatrix} q_{11} & q_{12} & q_{13} & q_{14} & 0 & 0 & 1 \\ q_{21} & q_{22} & q_{23} & q_{24} & 0 & 1 & 0 \\ q_{31} & q_{32} & q_{33} & q_{34} & 1 & 0 & 0 \\ q_{41} & q_{42} & q_{43} & q_{44} & 0 & 0 & 0 \end{bmatrix}$$

with the result

$$QB' = \begin{bmatrix} q_{13} & q_{12} & q_{11} \\ q_{23} & q_{22} & q_{21} \\ q_{33} & q_{32} & q_{31} \\ q_{43} & q_{42} & q_{41} \end{bmatrix}.$$