# Scholars' Mine

**Masters Theses**

Student Theses and Dissertations

Summer 2010

# A comparative study of capacitor voltage balancing techniques for flying capacitor multi-level power electronic converters

Vennela Yadhati

Follow this and additional works at: https://scholarsmine.mst.edu/masters\_theses

Part of the Electrical and Computer Engineering Commons

Department:

#### **Recommended Citation**

Yadhati, Vennela, "A comparative study of capacitor voltage balancing techniques for flying capacitor multi-level power electronic converters" (2010). Masters Theses. 4790. https://scholarsmine.mst.edu/masters\_theses/4790

This thesis is brought to you by Scholars' Mine, a service of the Missouri S&T Library and Learning Resources. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

# A COMPARATIVE STUDY OF CAPACITOR VOLTAGE BALANCING TECHNIQUES FOR FLYING CAPACITOR MULTI-LEVEL POWER ELECTRONIC CONVERTERS

by

#### VENNELA YADHATI

#### A THESIS

Presented to the Faculty of the Graduate School of the

MISSOURI UNIVERSITY OF SCIENCE AND TECHNOLOGY

In Partial Fulfillment of the Requirements for the Degree

MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

2010

Approved by

Mehdi Ferdowsi, Advisor Badrul Chowdhury Keith A. Corzine

© 2010 Vennela Yadhati All Rights Reserved

#### ABSTRACT

With the advent of multilevel converters for high power applications in industry, a need to develop simpler topologies and control techniques has arisen. The flying capacitor multilevel inverter (FCMLI) is one such topology which is gaining popularity in recent years with many advantages such as extra ride-through capabilities because of the capacitor storage, redundancy in switching states, low common mode voltage ratio, improved power quality, etc. In this thesis, different basic multilevel converter topologies and their advantages and applications are discussed. The thesis mainly focuses on singlephase five-level FCMLI topology. Different control techniques for capacitor voltage regulation like staircase modulation, and PWM techniques including phase disposition PWM (PDPWM), and natural balancing technique are implemented. The disadvantages of these methods are discussed. To overcome these, a new method called the split natural balancing technique which is based on the Unipolar PWM method is proposed in this thesis. In addition, a feedback control technique called amplitude modulation adjustment (AMA) method is devised to regulate the voltage across capacitors around the desired value irrespective of their initial values. Harmonic analysis of the output voltage for all the implemented methods is performed and compared.

#### **ACKNOWLEDGEMENTS**

I thank all the people who have encouraged and inspired me during my graduate study.

I especially would like to thank my advisor, Dr. Mehdi Ferdowsi, for his guidance in academics, research, and career. His energy and enthusiasm in research had motivated not only me, but all his advisees. I would like to specially mention his friendliness and willingness to help without which this thesis would not have been possible.

I want to thank my committee members Dr. Badrul Chowdhury, and Dr. Keith. A. Corzine who also have been world class teachers and mentors. I take this opportunity to thank our Department Secretary, Ms. Regina Kohout for seeing through all my requirements during my study in Missouri University of Science and Technology and for being a mother away from home.

It is a pleasure to thank all my friends in Missouri S & T, particularly Anand Prabhala, Mostafa Khazraei, Hossein Sepahvand and Nishant Chouhan who were always there to answer any question of mine and helped me through some supposedly difficult times of research and academics.

I mention a special thanks to my loveliest sister Pragathi Yadhati who has been a role model and the best counselor to me, and to my dearest friend Amit Thatipalli, for being an ideal friend and human being.

I'm indebted to my parents, Sri. Kasipathi Yadhati and Mrs. Pushpa Latha Yadhati to whom I dedicate this thesis. I owe my deepest gratitude to them for presenting me with this life, and their unconditional love and support throughout it. I cannot ask for more and can never return enough.

## TABLE OF CONTENTS

|                                                              | Page  |

|--------------------------------------------------------------|-------|

| ABSTRACT                                                     | iii   |

| ACKNOWLEDGEMENTS                                             | iv    |

| LIST OF ILLUSTRATIONS.                                       | vii   |

| LIST OF TABLES.                                              | xii   |

| NOMENCLATURE                                                 | xiii  |

| SECTION                                                      |       |

| 1. INTRODUCTION                                              | 1     |

| 1.1 BASIC CONCEPT                                            | 1     |

| 1.2 MULTILEVEL POWER ELECTRONIC TOPOLOGIES                   | 2     |

| 1.2.1. Diode-Clamped Multilevel Inverters                    | 2     |

| 1.2.2. Cascaded H-Bridge Cell Multilevel Inverters           | 4     |

| 1.2.3. Flying Capacitor Multilevel Inverters                 | 6     |

| 1.2.4. Comparison of Different Multilevel Topologies         | 9     |

| 1.3 ADVANTAGES OF MULTILEVEL INVERTERS                       | 12    |

| 1.4. APPLICATIONS OF MULTILEVEL INVERTERS                    | 13    |

| 1.5. MODULATION AND CONTROL STRATEGIES                       | 15    |

| 1.6. THESIS ORGANIZATION                                     | 16    |

| 2. FCMLI WITH NO REDUNDANCY                                  | 18    |

| 2.1. CONVERTER TOPOLOGY                                      | 18    |

| 2.2 THETA CALCULATIONS                                       | 21    |

| 2.3. CAPACITOR VOLTAGE CHARACTERISTICS                       | 23    |

| 2.4 EFFECTS OF MODULATION INDEX, POWER FACTOR AND REDUNDANCY | 30    |

| 3. STAIRCASE MODULATION FOR FCMLI WITH REDUNDANCY            | 31    |

| 3.1 FIVE-LEVEL OPERATION OF THE FCMLI TOPOLOGY               | 31    |

| 3.2 AVAILABILITY OF REDUNDANCY                               | 34    |

| 3.3 CAPACITOR VOLTAGE BALANCING (STAIRCASE MODULATIO         | N).35 |

| 3.4 EFFECTS OF POWER FACTOR                                  | 36    |

| 3.5 OTHER SIMULATION RESULTS                                 | 38    |

| 4. PHASE DISPOSITION AND PHASE SHIFTED SINE TRIANGLE PWM                                          | . 42 |

|---------------------------------------------------------------------------------------------------|------|

| 4.1 PWM CONTROL SCHEMES                                                                           | . 42 |

| 4.2. PD SINE TRIANGLE PWM                                                                         | . 43 |

| 4.3. PHASE SHIFTED PWM (NATURAL BALANCING)                                                        | . 48 |

| 5. SPLIT NATURAL BALANCING TECHNIQUE FOR CAPACITOR VOLTAGE REGULATION                             | . 53 |

| 5.1. DISADVANTAGES OF NATURAL BALANCING                                                           | . 53 |

| 5.2. SPLIT NATURAL BALANCING TECHNIQUE                                                            | . 53 |

| 6. AMPLITUDE MODULATION ADJUSTMENT (AMA) METHOD AND ITS GENERALIZATION TO HIGHER LEVEL TOPOLOGIES | . 62 |

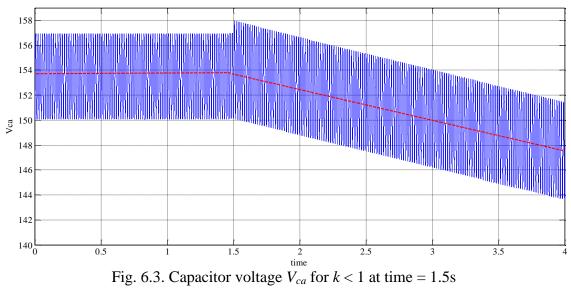

| 6.1. AMPLITUDE MODULATION ADJUSTMENT (AMA) METHOD                                                 | . 62 |

| 6.2. SIMULATION RESULTS                                                                           | . 63 |

| 6.3. ANALYSIS                                                                                     | . 65 |

| 6.4. FEEDBACK CONTROL FOR CAPACITOR VOLTAGE REGULATION                                            | . 66 |

| 6.5. EFFECT OF LOAD CHANGE                                                                        | . 70 |

| 6.6. GENERALIZATION TO HIGHER LEVEL TOPOLOGIES                                                    | . 71 |

| 7. HARMONIC ANALYSIS AND ADVANTAGES OF PROPOSED METHODS.                                          | . 76 |

| 7.1. HARMONIC ANALYSIS OF SINGLE-PHASE FIVE-LEVEL FCML INVERTER                                   | . 77 |

| 7.2. ADVANTAGES OF SPLIT NATURAL BALANCING AND AMA METHODS                                        | . 93 |

| 8. CONCLUSION                                                                                     | . 95 |

| BIBLIOGRAPHY                                                                                      | 96   |

| VITA                                                                                              | 103  |

## LIST OF ILLUSTRATIONS

| Figure                                                                           | age |

|----------------------------------------------------------------------------------|-----|

| 1.1. Five-level diode-clamped inverter.                                          | 3   |

| 1.2. Five-level cascaded H-bridge-cell inverter                                  | 5   |

| 1.3. Single-phase five-level FCMLI topology                                      | 7   |

| 1.4. Five-level generalized multilevel topology.                                 | 10  |

| 1.5. Example for a hybrid multilevel inverter topology                           | 11  |

| 2.1. FCMLI topology.                                                             | 19  |

| 2.2. Seven-level staircase voltage $V_{ab}$                                      | 20  |

| 2.3. Variation of thetas with the modulation index                               | 22  |

| 2.4. Capacitor voltage $V_{ca}$ at M=0.7 and PF=0.8                              | 25  |

| 2.5. Output voltage $V_{ab}$ at M=0.7 & PF=0.8                                   | 25  |

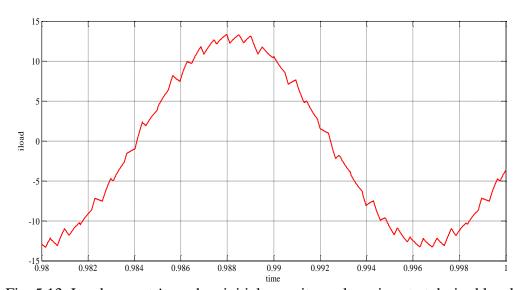

| 2.6. Load current <i>i</i> <sub>load</sub> at M=0.7 & PF=0.8                     | 26  |

| 2.7. Capacitor voltage $V_{ca}$ at M=0.877 & PF=0.8                              | 26  |

| 2.8. Output voltage $V_{ab}$ at M=0.877 & PF=0.8.                                | 27  |

| 2.9. Load current <i>i</i> <sub>load</sub> at <i>M</i> =0.877 & PF=0.8.          | 27  |

| 2.10. Output voltage $V_{ab}$ at M=0.7 & PF=0.7.                                 | 28  |

| 2.11. Load current <i>i</i> <sub>load</sub> at M=0.7 & PF=0.7.                   | 28  |

| 2.12. Output voltage $V_{ab}$ at M=0.877 & PF=0.7.                               | 29  |

| 2.13. Load current <i>i</i> <sub>load</sub> at <i>M</i> =0.877 & <i>PF</i> =0.7. | 29  |

| 3.1. Five-level staircase voltage $V_{ab}$ .                                     | 34  |

| 3.2. Control strategy for staircase modulation technique                         | 35  |

| 3.3. Capacitor voltage $V_{ca}$ at PF=0.9                                        | 36  |

| 3.4. Capacitor voltage $V_{cb}$ at PF=0.9                                        | 37  |

| 3.5. Capacitor voltage $V_{ca}$ at PF=0.3                                        | 37  |

| 3.6. Capacitor voltage $V_{cb}$ at PF=0.3                                        | 38  |

| 3.7. Five level output voltage $V_{ab}$ at power factor 0.9.                     | 39  |

| 3.8. Load current $i_{load}$ at power factor 0.9.                                | 39  |

| 3.9. Five level output voltage $V_{ab}$ at power factor 0.3.                     | 40  |

| 3.10. Load current $i_{load}$ at power factor 0.3.                               | 40  |

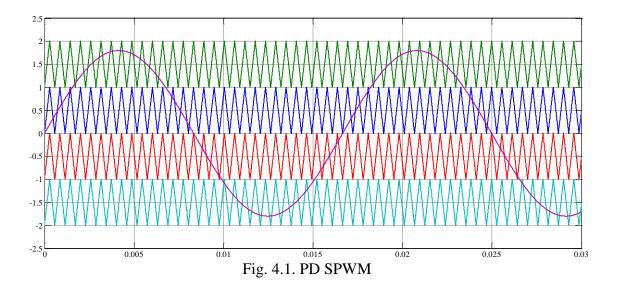

| 4.1. PD SPWM                                                                                                                           | 44 |

|----------------------------------------------------------------------------------------------------------------------------------------|----|

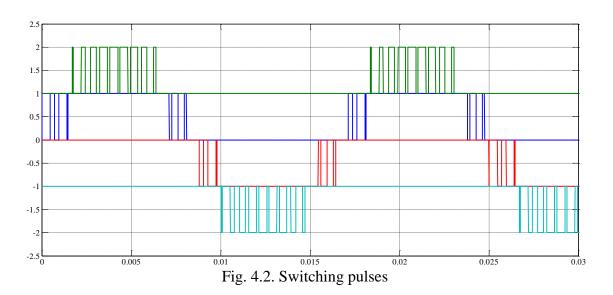

| 4.2. Switching pulses.                                                                                                                 | 44 |

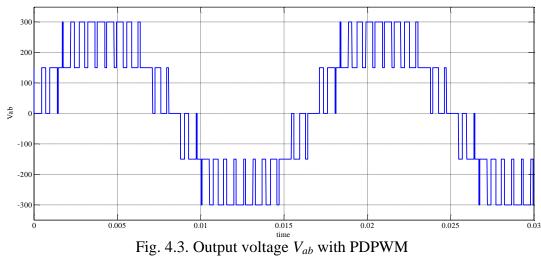

| 4.3. Output voltage $V_{ab}$ with PDPWM                                                                                                | 46 |

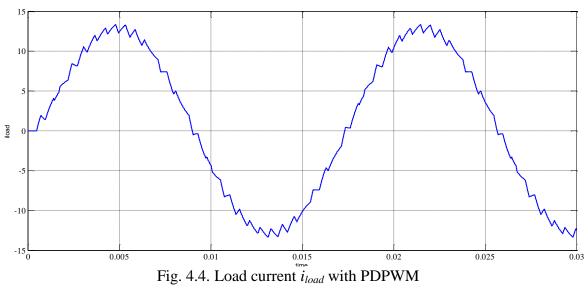

| 4.4. Load current <i>i</i> <sub>load</sub> with PDPWM                                                                                  | 46 |

| 4.5. Capacitor voltage $V_{ca}$ with PDPWM.                                                                                            | 47 |

| 4.6. Capacitor voltage $V_{cb}$ with PDPWM                                                                                             | 47 |

| 4.7. Phase shifted sine triangle PWM for natural balancing technique                                                                   | 49 |

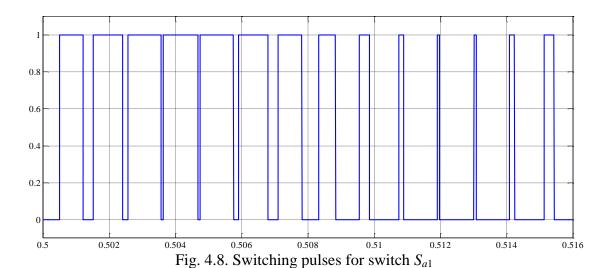

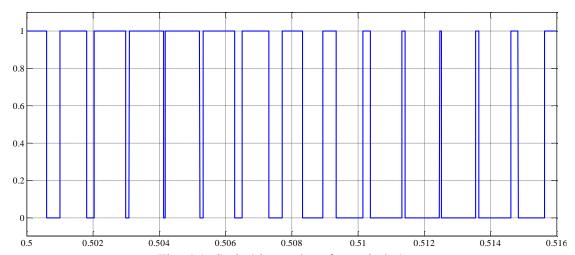

| 4.8. Switching pulses for switch $S_{a1}$                                                                                              | 49 |

| 4.9. Switching pulses for switch $S_{a2}$                                                                                              | 50 |

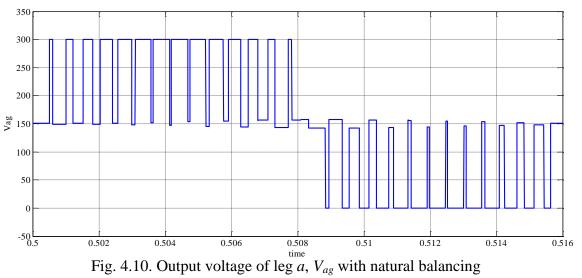

| 4.10. Output voltage of leg $a$ , $V_{ag}$ with natural balancing                                                                      | 50 |

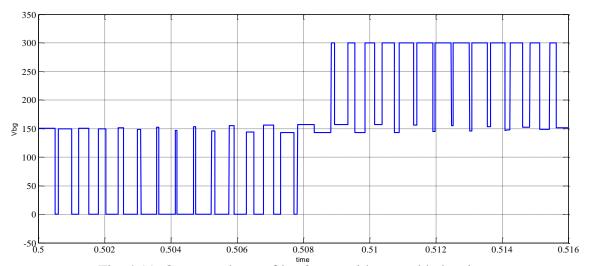

| 4.11. Output voltage of leg $b$ , $V_{bg}$ with natural balancing                                                                      | 51 |

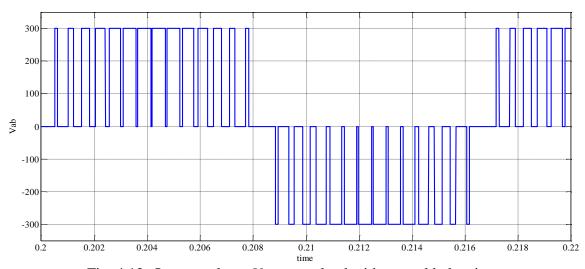

| 4.12. Output voltage $V_{ab}$ across load with natural balancing                                                                       | 51 |

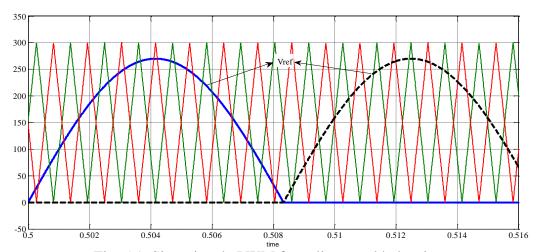

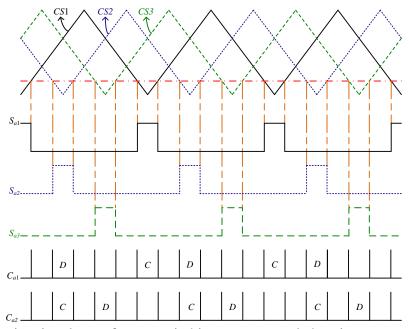

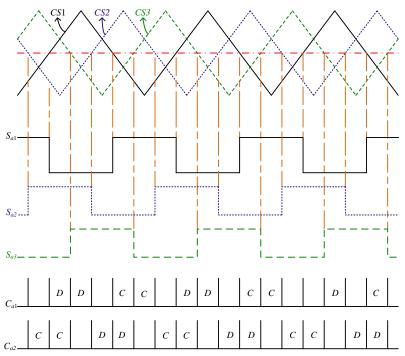

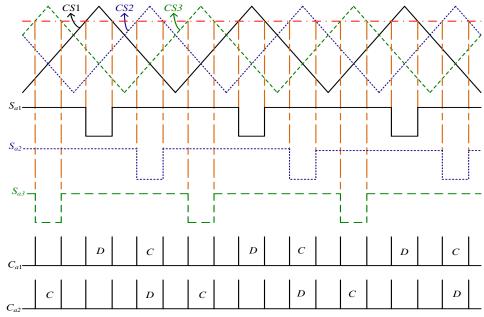

| 5.1. Sine triangle PWM for split natural balancing                                                                                     | 54 |

| 5.2. Switching pulses for switch $S_{a1}$                                                                                              | 54 |

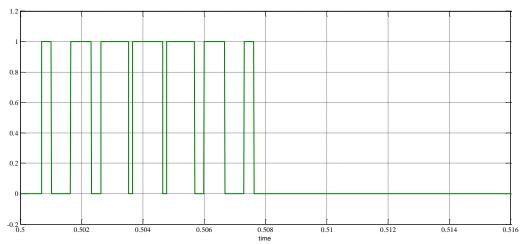

| 5.3. Switching pulses for switch $S_{b1}$                                                                                              | 55 |

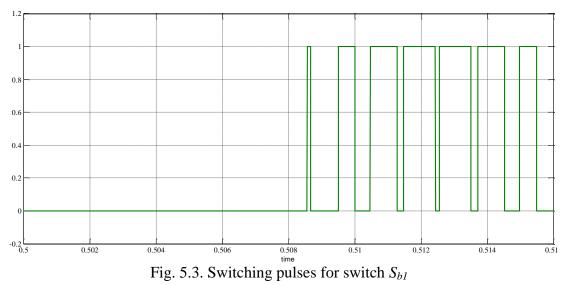

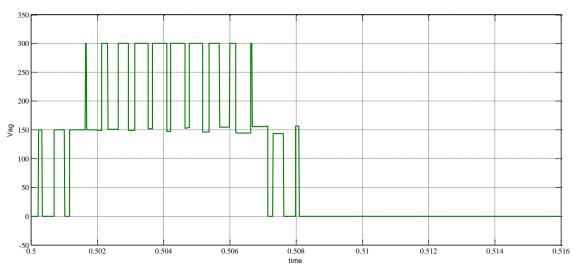

| 5.4. Output voltage on leg $a$ , $V_{ag}$                                                                                              | 55 |

| 5.5. Output voltage on leg $b$ , $V_{bg}$                                                                                              | 56 |

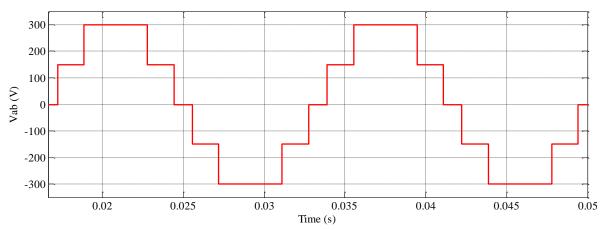

| 5.6. Output voltage $V_{ab}$ with split natural balancing.                                                                             | 56 |

| 5.7. Load current <i>i</i> <sub>load</sub> with split natural balancing                                                                | 57 |

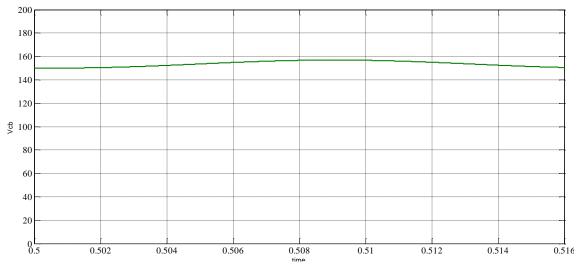

| 5.8. Capacitor voltage $V_{ca}$ with split natural balancing                                                                           | 57 |

| 5.9. Capacitor voltage $V_{cb}$ with split natural balancing                                                                           | 58 |

| 5.10. Capacitor voltage $V_{ca}$ when initial voltage value is 120V                                                                    | 59 |

| 5.11. Capacitor voltage $V_{cb}$ when initial voltage value 160V                                                                       | 59 |

| 5.12. Output voltage $V_{ab}$ when initial capacitor voltage is not at desired level                                                   | 60 |

| 5.13. Load current $i_{load}$ when initial capacitor voltage is not at desired level                                                   | 60 |

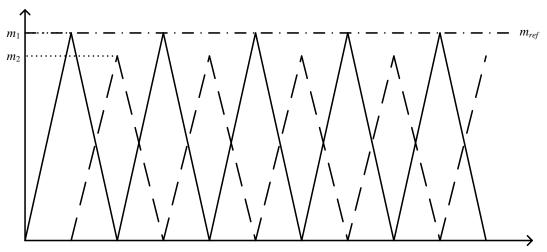

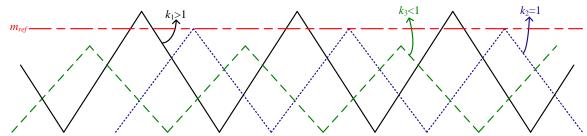

| 6.1. Carrier signal waveforms for $k = (m_2/m_1) < 1$                                                                                  | 62 |

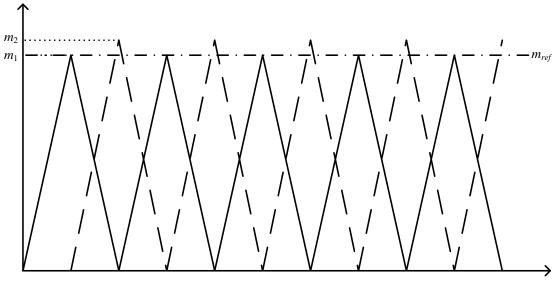

| 6.2. Carrier signal waveforms for $k = (m_2/m_1) > 1$                                                                                  | 63 |

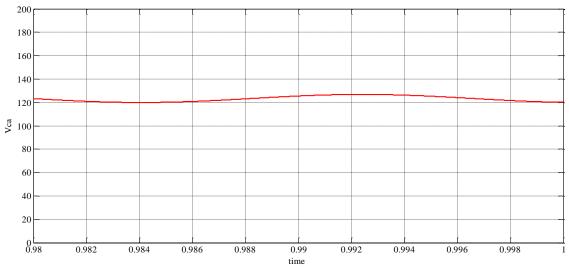

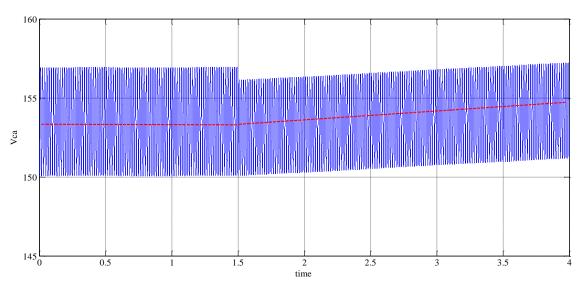

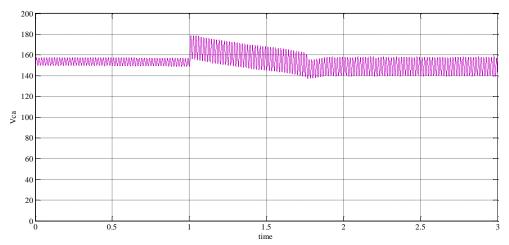

| 6.3. Capacitor voltage $V_{ca}$ for $k < 1$ at time = 1.5s                                                                             | 64 |

| 6.4. Capacitor voltage $V_{ca}$ for $k > 1$ at time = 1.5s                                                                             | 64 |

| 6.5. Waveforms of carrier signals, reference, switching pulses for switches $S_{a1}$ and $S_{a2}$ , output voltage $V_{ag}$ on leg $a$ | 66 |

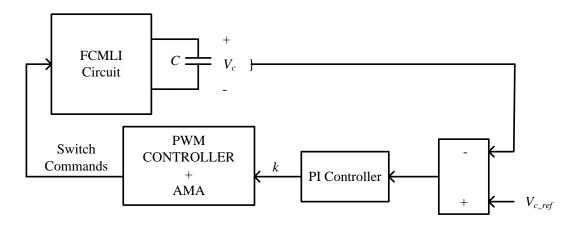

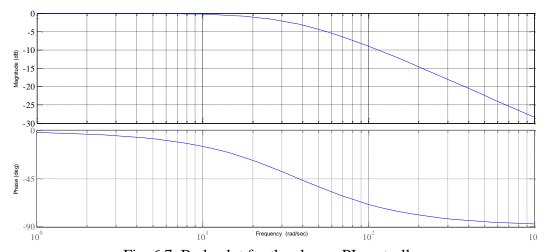

| 6.6. | Feedback control technique.                                                                                            | . 67 |

|------|------------------------------------------------------------------------------------------------------------------------|------|

| 6.7. | Bode plot for the chosen PI controller.                                                                                | . 67 |

| 6.8. | Output voltage $V_{ab}$ , with feedback technique                                                                      | . 68 |

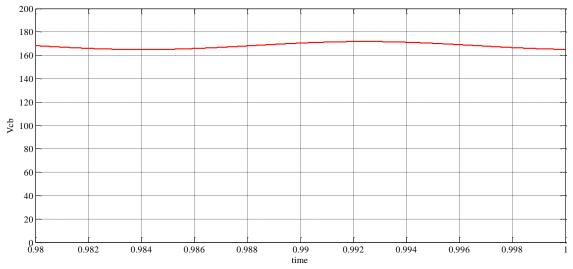

| 6.9. | Load current <i>i</i> <sub>load</sub> , with feedback technique.                                                       | . 69 |

| 6.10 | Capacitor voltage on leg a, $V_{ca}$ , with feedback technique.                                                        | . 69 |

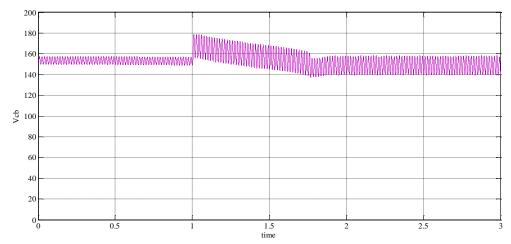

| 6.11 | . Capacitor voltage on leg b, $V_{cb}$ , with feedback technique                                                       | . 70 |

| 6.12 | 2. Effect of sudden change in load on capacitor voltage $V_{ca}$                                                       | . 71 |

| 6.13 | Effect of sudden change in load on capacitor voltage $V_{cb}$                                                          | . 71 |

| 6.14 | Reference amplitude $m_{ref}$ and carrier signal waveforms at different values of $k_i$                                | . 72 |

| 6.15 | Seven-level FCMLI topology                                                                                             | . 73 |

| 6.16 | 6. Carrier signal waveforms, switching patterns and charging states of capacitors with reference signal at low level.  | . 74 |

| 6.17 | Carrier signal waveforms, switching patterns and charging states of capacitors with reference signal at medium level.  | . 74 |

| 6.18 | 8. Carrier signal waveforms, switching patterns and charging states of capacitors with reference signal at high level. | . 75 |

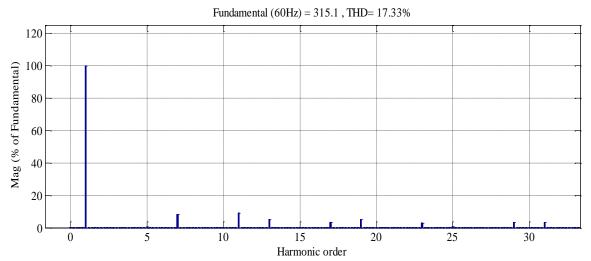

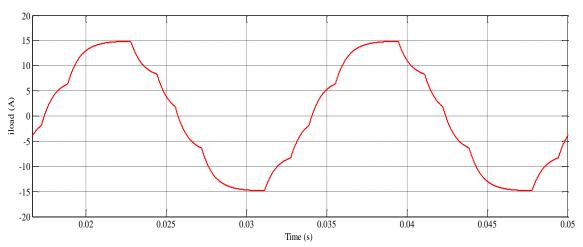

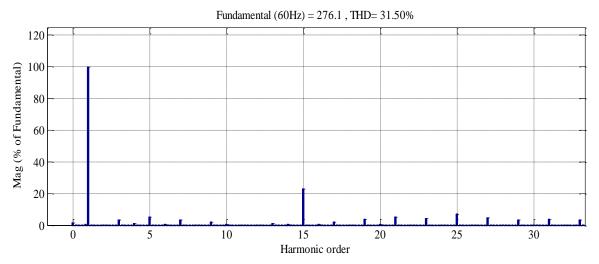

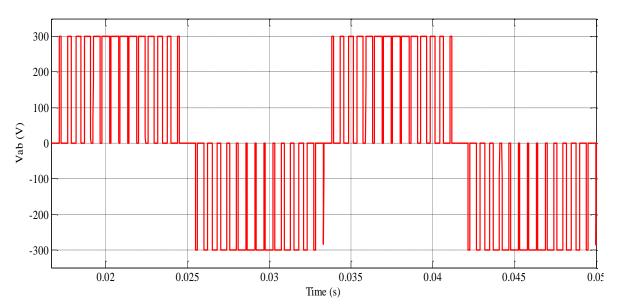

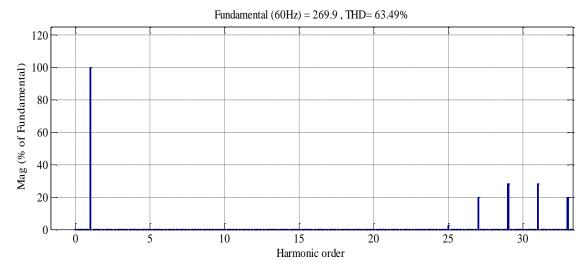

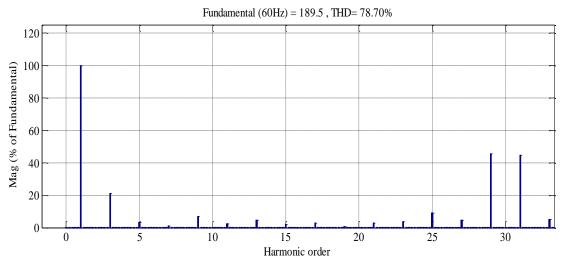

| 7.1. | Output voltage when staircase modulation technique is used for capacitor voltage regulation                            | . 77 |

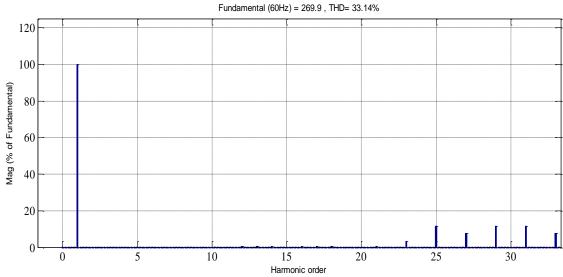

| 7.2. | Voltage harmonic spectrum when staircase modulation technique is used for capacitor voltage regulation.                | . 78 |

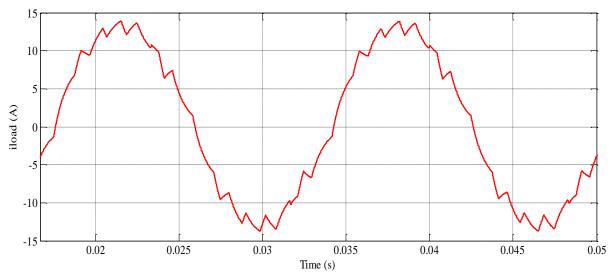

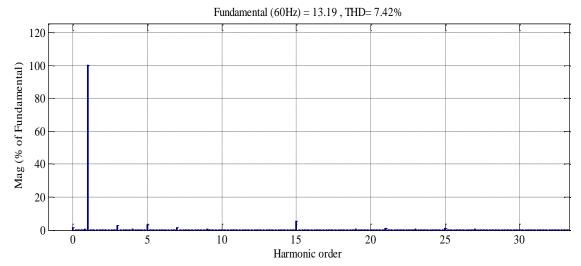

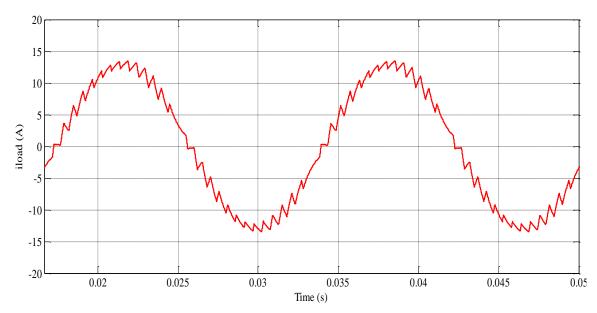

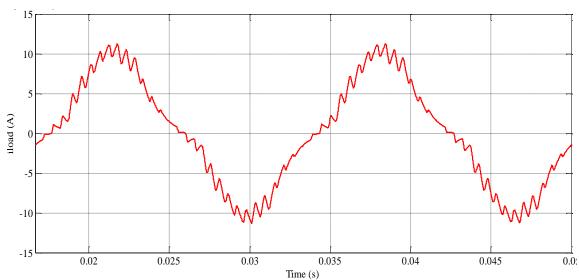

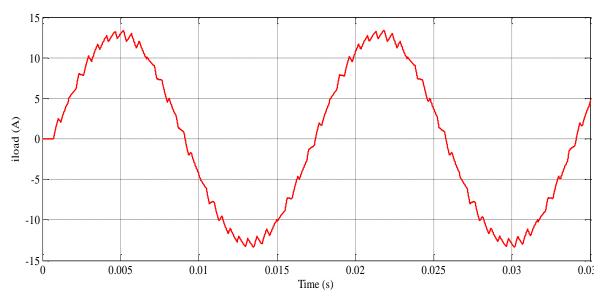

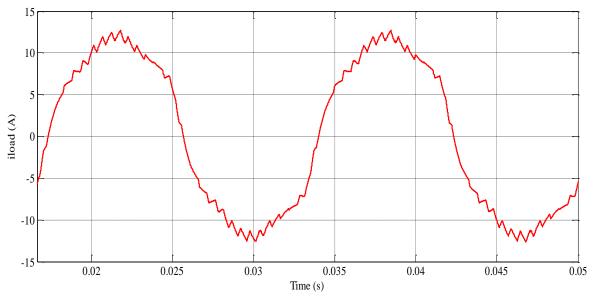

| 7.3. | Load current when staircase modulation technique is used for capacitor voltage regulation.                             | . 78 |

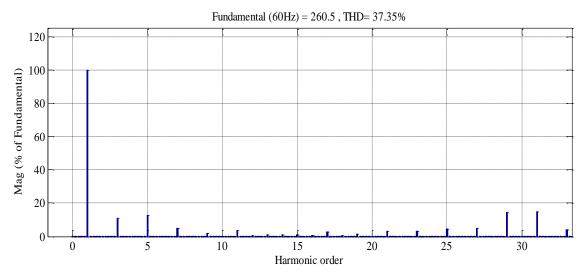

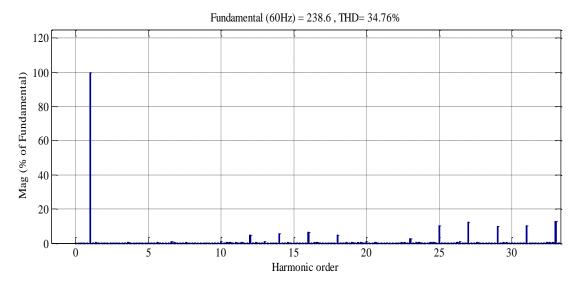

| 7.4. | Current harmonic spectrum when staircase modulation technique is used for capacitor voltage regulation.                | . 79 |

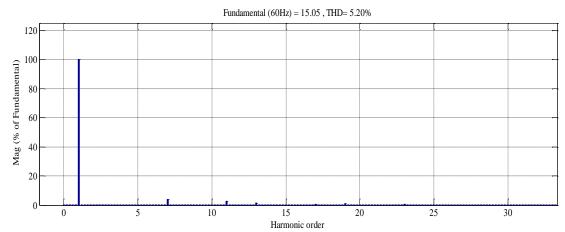

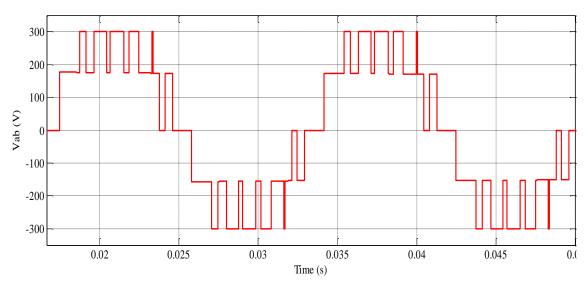

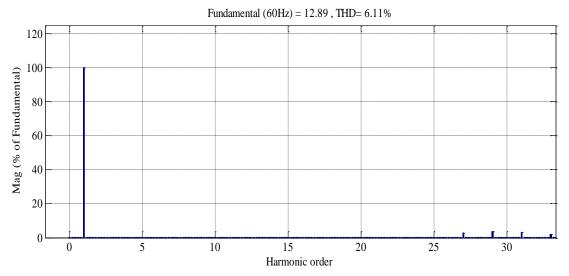

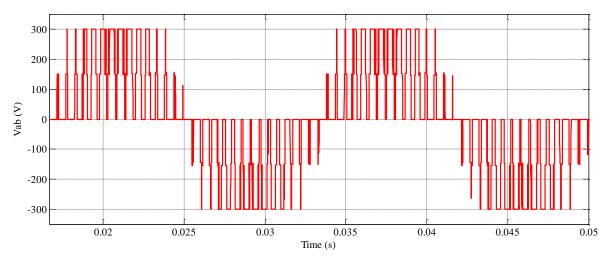

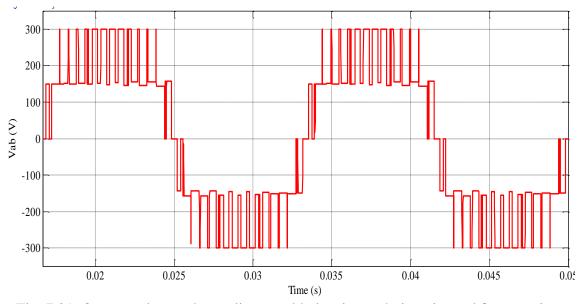

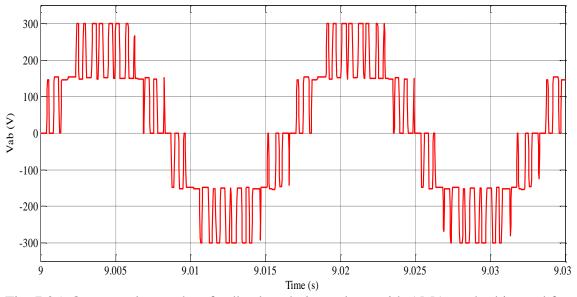

| 7.5. | Output voltage when PDPWM technique is used for capacitor voltage regulation                                           | . 79 |

| 7.6. | Voltage harmonic spectrum when PDPWM technique is used for capacitor voltage regulation                                | . 80 |

| 7.7. | Load current when PDPWM technique is used for capacitor voltage regulation.                                            | . 80 |

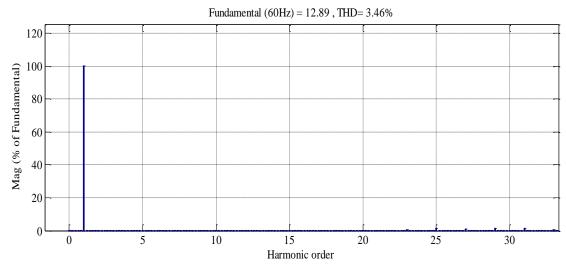

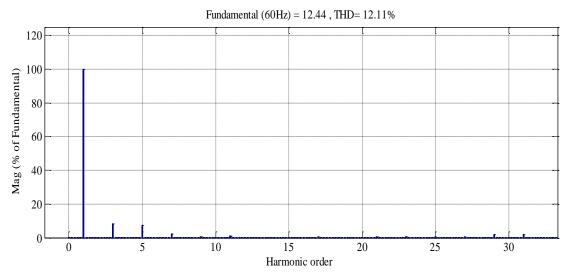

| 7.8. | Current harmonic spectrum when PDPWM technique is used for capacitor voltage regulation                                | . 81 |

| 7.9. | Output voltage when PSPWM (natural balancing) technique is used for capacitor voltage regulation.                      | .81  |

| 7.10.   | Voltage harmonic spectrum when PSPWM (natural balancing) technique                                                                                         | 02 |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

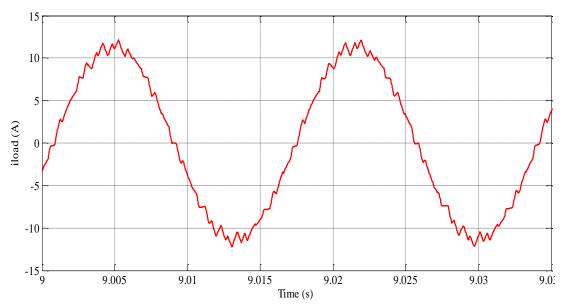

| 7.11.   | is used for capacitor voltage regulation                                                                                                                   | 82 |

| ,,,,,,, | capacitor voltage regulation.                                                                                                                              | 82 |

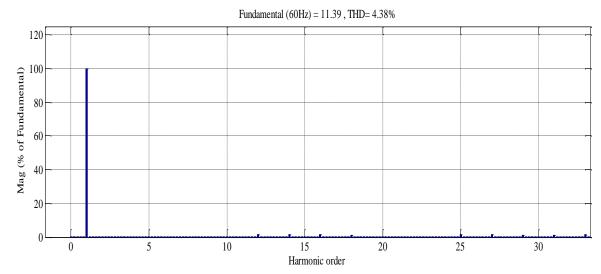

| 7.12.   | Current harmonic spectrum when PSPWM (natural balancing) technique is used for capacitor voltage regulation                                                | 83 |

| 7.13.   | Output voltage when PSPWM (natural balancing) technique is used for capacitor voltage regulation with modified carrier signal described in [75]            | 83 |

| 7.14.   | Voltage harmonic spectrum when PSPWM (natural balancing) technique is used for capacitor voltage regulation with modified carrier signal described in [75] | 84 |

| 7.15.   | Load current when PSPWM (natural balancing) technique is used for capacitor voltage regulation with modified carrier signal described in [75]              | 84 |

| 7.16.   | Current harmonic spectrum when PSPWM (natural balancing) technique is used for capacitor voltage regulation with modified carrier signal described in [75] | 85 |

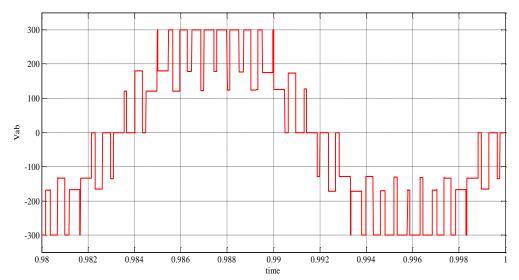

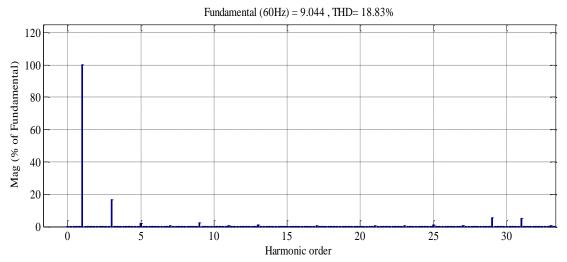

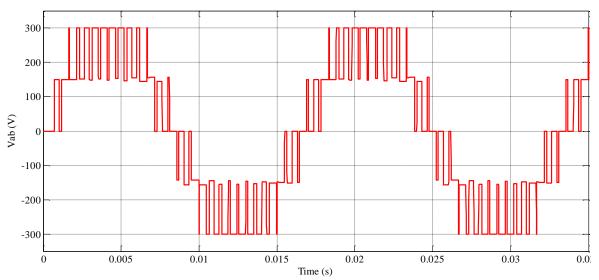

| 7.17.   | Output voltage when split natural balancing technique is used for capacitor voltage regulation                                                             | 85 |

| 7.18.   | Voltage harmonic spectrum when split natural balancing technique is used for capacitor voltage regulation                                                  | 86 |

| 7.19.   | Load current when split natural balancing technique is used for capacitor voltage regulation                                                               | 86 |

| 7.20.   | Current harmonic spectrum when split natural balancing technique is used for capacitor voltage regulation                                                  | 87 |

| 7.21.   | Output voltage when split natural balancing technique is used for capacitor voltage regulation with modified carrier signal described in [75]              | 87 |

| 7.22.   | Voltage harmonic spectrum when split natural balancing technique is used for capacitor voltage regulation with modified carrier signal described in [75]   | 88 |

| 7.23.   | Load current when split natural balancing technique is used for capacitor voltage regulation with modified carrier signal described in [75]                | 88 |

| 7.24.   | Current harmonic spectrum when split natural balancing technique is used for capacitor voltage regulation with modified carrier signal described in [75]   | 89 |

| 7.25.   | Output voltage when feedback technique along with AMA method is used for capacitor voltage regulation                                                      | 89 |

| 7.26.   | Voltage harmonic spectrum when feedback technique along with AMA method is used for capacitor voltage regulation                                           | 90 |

| 7.27. | Load current when feedback technique along with AMA method is used for capacitor voltage regulation              | . 90 |

|-------|------------------------------------------------------------------------------------------------------------------|------|

|       | Current harmonic spectrum when feedback technique along with AMA method is used for capacitor voltage regulation |      |

# LIST OF TABLES

| Tabl | le Pag                                                                                     | ge             |

|------|--------------------------------------------------------------------------------------------|----------------|

| 1.1. | Possible switching states for the diode-clamped inverter                                   | 4              |

| 1.2. | Possible switching states for cascaded H-bridge cell inverter                              | .6             |

| 1.3. | Possible switching states for FCMLI topology                                               | 8              |

| 1.4. | Comparison between various multilevel topologies                                           | 9              |

| 2.1. | Switching states to determine state indicator                                              | 19             |

| 2.2. | Output voltages and capacitor currents                                                     | 20             |

| 2.3. | Thetas when $M=0.7 \& M=0.877$                                                             | 22             |

| 2.4. | Load resistance (R) and inductance (L) at different power factors when $M=0.72$            | 23             |

| 2.5. | Load resistance (R) and inductance (L) at different power factors when M=0.877. $^{\circ}$ | 24             |

| 3.1. | Different voltage levels for five-level operation ( $V_{ca}=V_{cb}=V_{dc}/2$ )             | 32             |

| 3.2. | Switching states for $V_{ag}$ for five-level operation                                     | 33             |

| 3.3. | Switching states for $V_{bg}$ for five-level operation                                     | 33             |

| 4.1. | Simulation parameters.                                                                     | 15             |

| 7.1. | Comparison of various controlling techniques based on voltage harmonic analysis 9          | <del>)</del> 2 |

| 7.2. | Comparison of various controlling techniques based on current harmonic analysis 9          | <del>)</del> 2 |

#### **NOMENCLATURE**

Symbol Description  $V_{dc}$ Input dc voltage  $S_{a1}$ Switch 1 on leg a  $S_{a1}'$ Complementary switch to switch  $S_{a1}$  on leg a $S_{a2}$ Switch 2 on leg *a*  $S_{a2}'$ Complementary switch to switch  $S_{a2}$  on leg aSwitch 1 on  $\log b$  $S_{b1}$  $S_{b1}'$ Complementary switch to switch  $S_{b1}$  on leg bSwitch 2 on leg b  $S_{b2}$  $S_{b2}'$ Complementary switch to switch  $S_{b2}$  on leg b $V_{ca}$ Voltage across the capacitor  $C_a$  on leg a $V_{cb}$ Voltage across the capacitor  $C_b$  on leg bVoltage on leg a  $V_{ag}$  $V_{bg}$ Voltage on leg b Output voltage across the RL load  $V_{ab}$  $i_{load}$ Current through the RL load Current through the capacitor  $C_a$  $i_{ca}$ Current through the capacitor  $C_b$  $i_{cb}$ Ratio of input dc voltage to the capacitor voltage p  $\theta$ Firing angle Modulation index (ratio of amplitude of fundamental M component of output voltage to the input voltage P Output power

$\Phi$  Power factor angle

$f_c$  Carrier frequency

$f_{ref}$  Reference frequency

$m_f$  Frequency modulation index (ratio of carrier frequency to

reference frequency)

$m_a$  Amplitude modulation index (ratio of reference peak to

peak amplitude to dc source voltage)

Number of pairs of complementary switches per leg

$m_{csi}$  Amplitude of carrier signal i

$m_{ref}$  Reference amplitude

Factor by which the amplitude of carrier signal 'i' is

changed (ratio of carrier signal amplitude to reference

amplitude)

#### 1. INTRODUCTION

#### 1.1 BASIC CONCEPT

The need for high power apparatus in industry has increased in recent years. Multilevel converters have developed as easy alternatives for such power requirements [1-4]. Mostly used in medium voltage applications, multilevel converters have gained prominence since it is not feasible to connect a single power semiconductor switch directly to the grid. There are other advantages of multilevel converters such as their capability to be easily interfaced with the renewable energy sources such as solar power, wind power, and fuel cells [5, 6].

Multilevel converters consist of a group of semiconductor switches, like IGBTs, and a set of voltage source components like capacitors or independent sources. The basic concept of these converters depends on using this series of switches and sources to synthesize a stepped or staircase output voltage waveform. Therefore, they reduce the voltage stress on each device or component used [7]. Multilevel converters play a significant role in enhancing the quality of high power distribution networks, power conditioning systems, variable speed drive systems etc because of the availability of higher number of voltage levels at the output. This helps in reducing the size of switching components which can be operated at lower switching frequencies [8].

However, multilevel converters have their own disadvantages. Voltage sharing may not be as desired under all conditions because of the series connection of the switching devices.

#### 1.2 MULTILEVEL POWER ELECTRONIC TOPOLOGIES

The number of switches in a multilevel converter depends on the number of voltage levels required in the output. Based on the arrangement of switches and passive sources, there are four basic types of multilevel converter topologies [9-11]. They are:

- i) Diode-Clamped

- ii) Cascaded H-Bridge Cell

- iii) Flying Capacitor

- iv) Switched Capacitor

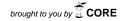

**1.2.1. Diode-Clamped Multilevel Inverters.** Diode-clamped inverters are one of the earliest designed topologies of multilevel inverters [12-14]. Figure 1.1 shows a single-phase five-level diode-clamped inverter. The two capacitors connected in the circuit split input voltage  $V_{dc}$  to obtain the midpoint voltage of the input. In a three level topology, the common point of capacitors is connected to the ground. Therefore, this circuit can also be called the neutral point clamped inverter. Diodes  $D_1$  and  $D_2$  present in the circuit help with clamping dc voltage  $V_{dc}$  to obtain different output voltage levels. There are nine allowable switching states for the given circuit to obtain five different output voltage levels  $+V_{dc}$ ,  $+V_{dc}$ , /2, 0,  $-V_{dc}$ , and  $-V_{dc}$  [5] as shown in Table 1.1. It has to be noted that switch pairs  $S_{a1}$  and  $S_{a1}$ , and  $S_{a2}$  and  $S_{a2}$  are complementary to each other. Similarly, switch pairs  $S_{b1}$  and  $S_{b1}$ , and  $S_{b2}$  and  $S_{b2}$  are complementary to each other.

The number of switches, capacitors, and diodes required in the circuit increases with the number of output voltage levels desired. For every additional level of voltage, it requires an extra pair of complementary switches is required in each limb of the circuit and also additional capacitors and clamping diodes. However, in such cases, voltage

balancing of the capacitors and the cost of diodes become a practical problem [8]. Another disadvantage of diode-clamped multilevel inverters is that they need high voltage rating diodes to block the reverse voltages [9].

Fig. 1.1. Five-level diode-clamped inverter

Table 1.1 Possible switching states for the diode-clamped inverter

| $S_{a1}$ | $S_{a2}$ | $S_{a1}$ | $S_{a2}$ | $S_{b1}$ | $S_{b2}$ | $S_{b1}$ | $S_{b2}$ | $V_{load}$  |

|----------|----------|----------|----------|----------|----------|----------|----------|-------------|

| 0        | 0        | 1        | 1        | 0        | 0        | 1        | 1        | 0           |

| 0        | 1        | 1        | 0        | 0        | 1        | 1        | 0        | 0           |

| 1        | 1        | 0        | 0        | 1        | 1        | 0        | 0        | 0           |

| 0        | 1        | 1        | 0        | 0        | 0        | 1        | 1        | $+V_{dc}/2$ |

| 1        | 1        | 0        | 0        | 0        | 1        | 1        | 0        | $+V_{dc}/2$ |

| 1        | 1        | 0        | 0        | 1        | 1        | 0        | 0        | $+V_{dc}$   |

| 0        | 1        | 1        | 0        | 1        | 1        | 0        | 0        | $-V_{dc}/2$ |

| 0        | 0        | 1        | 1        | 0        | 1        | 1        | 0        | $-V_{dc}/2$ |

| 0        | 0        | 1        | 1        | 1        | 1        | 0        | 0        | $-V_{dc}$   |

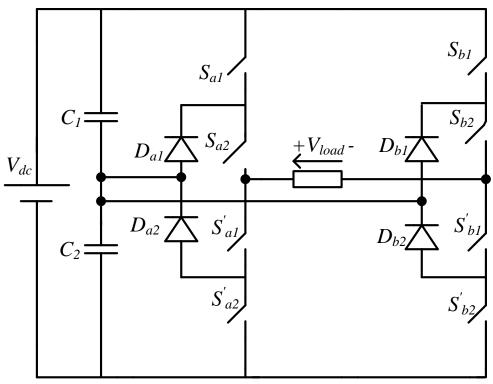

1.2.2. Cascaded H-Bridge Cell Multilevel Inverters. Cascaded H-bridge cell multilevel inverter topology [15-17] is a series connection of two or more individual full-bridge inverters. Figure 1.2 shows a single-phase, five-level cascaded H-bridge cell inverter realized by connecting two three level conventional full bridge inverters in series. Switch pairs  $S_{a1}$  and  $S_{a1}$ , and  $S_{a2}$  and  $S_{a2}$  are complementary to each other. Similarly, switch pairs of the other full bridge inverter  $S_{b1}$  and  $S_{b1}$ , and  $S_{b2}$  are complementary to each other. The switching states are as shown in Table 1.2. The different voltage levels that can be obtained at the output terminals are  $+2V_{dc}$ ,  $+V_{dc}$ , 0,  $-V_{dc}$ ,  $-2V_{dc}$ . If the dc voltage sources in both the inverter circuits connected in series are not equal to each other, then nine levels can be obtained at the output terminals. The

number of levels in the output voltage can be increased by two by adding an identical inverter in series.

Cascaded H-bridge cell inverters use the least number of power electronic devices when compared to any other topology. However, they require isolated power sources in each cell which in turn requires a large isolating transformer [8].

Fig. 1.2. Five-level cascaded H-bridge-cell inverter

Table 1.2 Possible switching states for cascaded H-bridge cell inverter

| $S_{a1}$ | $S_{a2}$ | $S_{a1}$ | $S_{a2}$ | $S_{b1}$ | $S_{b2}$ | $S_{b1}$ | $S_{b2}$ | $V_{load}$ |

|----------|----------|----------|----------|----------|----------|----------|----------|------------|

| 1        | 0        | 0        | 1        | 0        | 1        | 1        | 0        | 0          |

| 1        | 0        | 1        | 0        | 1        | 0        | 1        | 0        | 0          |

| 1        | 0        | 1        | 0        | 0        | 1        | 0        | 1        | 0          |

| 0        | 1        | 0        | 1        | 1        | 0        | 1        | 0        | 0          |

| 0        | 1        | 0        | 1        | 0        | 1        | 0        | 1        | 0          |

| 0        | 1        | 1        | 0        | 1        | 0        | 0        | 1        | 0          |

| 1        | 0        | 0        | 1        | 1        | 0        | 1        | 0        | $+V_{dc}$  |

| 1        | 0        | 0        | 1        | 0        | 1        | 0        | 1        | $+V_{dc}$  |

| 1        | 0        | 1        | 0        | 1        | 0        | 0        | 1        | $+V_{dc}$  |

| 0        | 1        | 0        | 1        | 1        | 0        | 0        | 1        | $+V_{dc}$  |

| 1        | 0        | 0        | 1        | 1        | 0        | 0        | 1        | $+2V_{dc}$ |

| 0        | 1        | 1        | 0        | 1        | 0        | 1        | 0        | $-V_{dc}$  |

| 0        | 1        | 1        | 0        | 0        | 1        | 0        | 1        | $-V_{dc}$  |

| 1        | 0        | 1        | 0        | 0        | 1        | 1        | 0        | $-V_{dc}$  |

| 0        | 1        | 0        | 1        | 0        | 1        | 1        | 0        | $-V_{dc}$  |

| 0        | 1        | 1        | 0        | 0        | 1        | 1        | 0        | $-2V_{dc}$ |

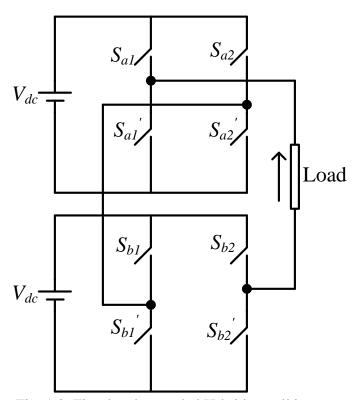

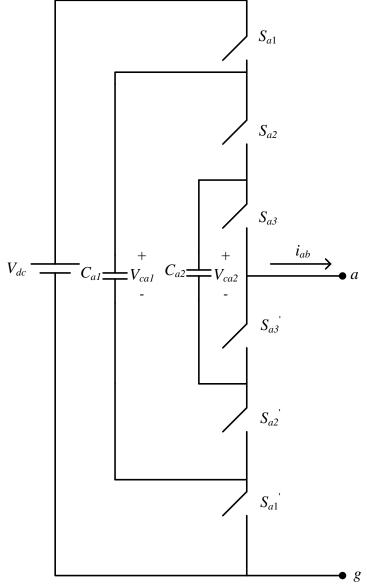

**1.2.3. Flying Capacitor Multilevel Inverters.** The diodes in the diode-clamped topology can be replaced by clamping capacitors or floating capacitors to clamp the voltages. Such a topology is called flying capacitor multilevel inverter (FCMLI). FCMLI topologies are relatively new compared to the diode-clamped or the cascaded H-bridge

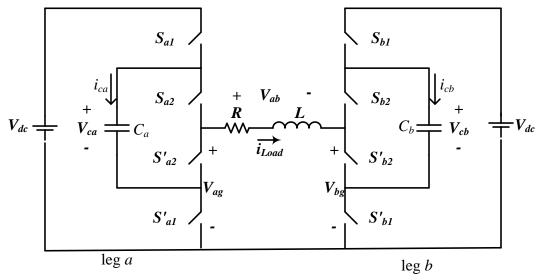

cell inverter topologies [18, 73]. Redundancy in the switching states is available by using flying capacitors instead of clamping diodes. This redundancy can be used to regulate the capacitor voltages and obtain the same desired level of voltage at the output [19]. Figure 1.3 shows a single-phase five-level FCMLI topology. The voltage across the capacitors is considered to be half of Dc source voltage  $V_{dc}$ . The output voltage consists of five different voltage levels +  $V_{dc}$ ,  $V_{dc}/2$ , 0, - $V_{dc}/2$ , and -  $V_{dc}$ . Similar to the other multilevel converter topologies, FCMLI also has complementary switch pairs. In the present considered circuit, switches  $S_{a1}$  &  $S_{a1}$ , and  $S_{a2}$  &  $S_{a2}$  are complementary to each other. Similarly on the other limb, switches  $S_{b1}$  &  $S_{b1}$ , and  $S_{b2}$  &  $S_{b2}$  are complementary to each other. The switching states available for such a topology are higher than that of the diodeclamped which can be observed from Table 1.3. The number of voltage levels at the output can be increased by adding a pair of complementary switches and a capacitor. However, all the capacitors used in such topologies must be rated identically which can prove to be expensive and bulky in size.

Fig. 1.3. Single-phase five-level FCMLI topology

Table 1.3. Possible switching states for FCMLI topology

| $S_{a1}$ | $S_{a2}$ | $S_{a1}$ | $S_{a2}$ | $S_{b1}$ | $S_{b2}$ | $S_{b1}$ | $S_{b2}$ | $V_{load}$  |

|----------|----------|----------|----------|----------|----------|----------|----------|-------------|

| 1        | 1        | 0        | 0        | 1        | 1        | 0        | 0        | 0           |

| 1        | 0        | 1        | 0        | 1        | 0        | 1        | 0        | 0           |

| 1        | 0        | 1        | 0        | 0        | 1        | 0        | 1        | 0           |

| 0        | 1        | 0        | 1        | 1        | 0        | 1        | 0        | 0           |

| 0        | 1        | 0        | 1        | 0        | 1        | 0        | 1        | 0           |

| 0        | 0        | 1        | 1        | 0        | 0        | 1        | 1        | 0           |

| 1        | 1        | 0        | 0        | 1        | 0        | 1        | 0        | $+V_{dc}/2$ |

| 1        | 1        | 0        | 0        | 0        | 1        | 0        | 1        | $+V_{dc}/2$ |

| 1        | 0        | 1        | 0        | 0        | 0        | 1        | 1        | $+V_{dc}/2$ |

| 0        | 1        | 0        | 1        | 0        | 0        | 1        | 1        | $+V_{dc}/2$ |

| 1        | 1        | 0        | 0        | 0        | 0        | 1        | 1        | $+V_{dc}$   |

| 1        | 0        | 1        | 0        | 1        | 1        | 0        | 0        | $-V_{dc}/2$ |

| 0        | 1        | 0        | 1        | 1        | 1        | 0        | 0        | $-V_{dc}/2$ |

| 0        | 0        | 1        | 1        | 0        | 1        | 0        | 1        | $-V_{dc}/2$ |

| 0        | 0        | 1        | 1        | 1        | 0        | 1        | 0        | $-V_{dc}/2$ |

| 0        | 0        | 1        | 1        | 1        | 1        | 0        | 0        | $-V_{dc}$   |

The major challenge in the flying capacitor multilevel inverter topologies is the voltage regulation across the capacitors. The switching states and the polarity of load current cause the capacitors either to charge or discharge since the current can flow

through more than one capacitor. Therefore, the appropriate selection of switching states becomes a priority in FCMLI topologies.

**1.2.4.** Comparison of Different Multilevel Topologies. Table 1.4 shows the basic comparison of various aspects of different multilevel topologies discussed above. It can be observed that for obtaining the same number of levels of voltage at the output, different topologies need different number of sources, diodes, capacitors etc. Other parameters like cost and size of components depend on their rating and requirement. Suitability of topology is mostly application oriented.

Table 1.4 Comparison between various multilevel topologies

| Topology Aspect                        | Diode-<br>clamped<br>Multilevel | Cascaded H-bridge<br>Cell Multilevel | Flying Capacitor<br>Multilevel |

|----------------------------------------|---------------------------------|--------------------------------------|--------------------------------|

| No. of Voltage<br>Levels at the Output | 5                               | 5                                    | 5                              |

| No. of Switches                        | 8                               | 8                                    | 8                              |

| No. of Sources                         | 1                               | 2                                    | 1                              |

| No. of Capacitors                      | 2                               | None                                 | 2                              |

| No. of Clamping<br>Diodes              | 4                               | None                                 | None                           |

| No. of Possible<br>Switching States    | 9                               | 16                                   | 16                             |

More topologies of multilevel inverters can be developed as a combination of one or more of the above mentioned topologies. For example, in [20] F. Z. Peng claims to have developed a generalized multilevel inverter which uses capacitors and diodes in a

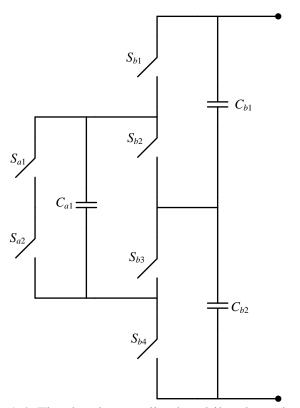

cascaded H-bridge topology. Many other topologies can be derived from such a topology. Figure 1.4 shows the five-level topology of such a generalized multilevel inverter. Such a topology can also be called as a switched capacitor multilevel converter. In this topology, it can be observed that when switches  $S_{b1}$  and  $S_{b3}$  are turned ON, capacitor  $C_{a1}$  is in parallel to capacitor  $C_{b1}$  when switches  $S_{b2}$  and  $S_{b4}$  are turned ON, then capacitor  $C_{a1}$  is in parallel to capacitor  $C_{b2}$ . So, the output available at the terminals of leg b can be a combination of the sum of capacitor voltages  $C_{a1}$ ,  $C_{b1}$ , and  $C_{b2}$ . This topology proves to possess more efficient self balancing capabilities than the other conventional topologies.

Fig. 1.4. Five-level generalized multilevel topology

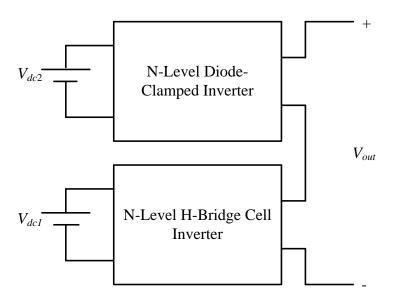

Yet another multilevel topology can be a mixed-level hybrid multilevel converter [21-25]. The full-bridge inverters in a cascaded H-bridge cell inverter can be replaced by diode-clamped or flying capacitor inverters. Such a topology can help in decreasing the number of individual dc voltage sources required in the inverter topology. However, control of such an inverter topology may be difficult because of its mixed-level hybrid structure. As it includes different multilevel inverter topologies incorporated as individual cells of cascaded inverters [5]. An example of a simple hybrid multilevel inverter topology can be shown as a block diagram in Fig. 1.5. It shows an N-level cascaded H-bridge cell multilevel inverter connected in series with an N-level diode-clamped multilevel inverter.

Fig. 1.5. Example for a hybrid multilevel inverter topology

#### 1.3 ADVANTAGES OF MULTILEVEL INVERTERS

The most important aspect of multilevel inverters becomes their ability to produce different levels of output voltage which can be synthesized as a sine waveform. The need for higher power rated switches can be eliminated by using the existing switches in a multilevel topology. The power quality is improved because of the increased number of voltage levels at the output. The common mode voltage is lower in multilevel inverters; therefore, they reduce the stress on the bearings of the motor that is connected to them. In fact, with more advanced control techniques as in [26], the common mode voltage can be completely eliminated in multilevel inverters. Other advantages of multilevel inverters include higher voltage capability, improved electromagnetic compatibility, lower switching losses etc. Specific advantages of different multilevel inverter topologies [9] can be stated as follows:

#### Diode-clamped inverters:

- a) Filters can be avoided because of the increase in the number of voltage levels which reduces the harmonic content of the waveform.

- b) As the devices are all operated at fundamental frequency, efficiency of the circuit is high.

- c) Easy control

#### Cascaded H-bridge cell inverters:

- a) To obtain the same number of voltage levels at the output terminals, cascaded H-bridge cell inverters require the lowest number of components.

- b) Absence of clamping diodes and capacitors allows modularizing the circuit layout.

c) Compatibility to soft switching avoids the usage of bulky snubber circuits which also reduces the losses.

Flying capacitor inverters:

- a) Extra ride through capabilities during power outages is possible because of the presence of storage capacitors.

- b) Redundancy in the switching states is available which helps in regulating the capacitor voltages.

- c) As the number of the levels is increased, filters can be avoided due to low harmonic contents.

#### 1.4. APPLICATIONS OF MULTILEVEL INVERTERS

Several advantages of multilevel inverters as described above make them very promising alternatives in high power and medium voltage applications in industry. Several papers [2, 4, 26, 27] discuss about various industrial applications of multilevel inverters such as input choppers for T13 locomotives in many European countries, medium voltage drives, and adjustable speed drives etc.

Multilevel inverters are becoming popular because of their capability to operate at lower frequencies and therefore, at higher efficiencies. Multilevel inverters also find applications in renewable energy systems [6, 28-32] like fuel cell utilizations, photovoltaic systems, and wind power generation etc for interface with the grid.

Multilevel inverters are also used in aerospace applications where high frequency and low total harmonic distortion (THD) operation is desired. [33] compares the losses in

one such aerospace application and it is observed that there is almost 40% benefit in the losses when an inverter with higher number of voltage levels is used.

An autonomous power generator with diesel engine and permanent magnet synchronous generator which makes use of multilevel inverters is reported in [34]. Usage of multilevel inverters makes the system capable of operating with asymmetrical and non linear three-phase loads.

The next important application of multilevel inverters becomes power conditioning systems [35]. Power conditioning systems are required in almost all renewable energy systems to provide interface with the utility and also to match the characteristics of sources and loads [36]. [37] reports a diode-clamped multilevel inverter connected to the electrical distribution system. This improves the system's ability to control the current demanded and the voltage required to be supplied to the utility and customer respectively. Furthermore, it makes the conditioning system applicable to higher voltage and power levels avoiding the use of bulky transformers.

Applications of multilevel inverters have been extended to low voltage systems as well due to their lower losses and THD. These and reduced voltage derivative dv/dt make them applicable in uninterruptable power supplies (UPS). [38] discusses one such UPS application where a three-level and two four-level multilevel inverters are analyzed and compared for the same purpose.

Most of the major applications of multilevel inverters rest in electric drive systems [17, 26, 39, 40]. These are used in various high speed and voltage traction systems [40-42]. The next area where multilevel inverters are gaining prominence is high power applications like FACTS [3, 43]. Different topologies of multilevel inverters prove

to be more efficient in different applications. For example, cascaded cell multilevel inverters are more used in static compensators (STATCOMs) [44-46] because of their advantages like lower losses, modularity and easier charge balancing techniques. However, diode-clamped and flying capacitor multilevel inverters also proved to be efficient in STATCOM applications because of their larger operating range [47-49]. Diode-clamped inverters are found to be capable in grid connection systems for renewable energy systems [6, 29]. Flying capacitor multilevel inverters find their applications in unified power flow controllers (UPFCs) [50], series and shunt compensation circuits for transmission and distribution systems [51-53], direct torque control (DTC) drives [54] etc because of their various advantages. Diode-clamped inverters are also used in UPFCs [55].

It has to be noted that any multilevel topology may be used in most of these applications though a particular topology might prove to be more efficient for a particular application. Other applications of multilevel inverters include active filters (AFs) [56, 57], dynamic voltage restorers (DVRs), utility adaptors [3], static VAR generators for reactive power control [45, 47], electric vehicle applications [58] and many other medium voltage, high power applications.

#### 1.5. MODULATION AND CONTROL STRATEGIES

Next important thing in multilevel inverters becomes modulation and control strategies for various topologies. Most of these techniques developed may be used as common control methods for any appropriate topology.

To avoid efficiency losses and high switch power dissipation, most of the power electronic converters operate in the switched mode where the switch is either turned OFF, conducting zero current or turned ON, where there is a minimum voltage drop across it. Therefore, power flow control in converters is done by switching between these two transitional states [59].

Several of these controlling strategies are developed from pulse width modulation (PWM) techniques like the phase-shifted PWM, phase-disposition PWM, space vector modulation, etc [36, 60-63]. However, there are other controlling strategies which make use of the redundancy in switching states, delta modulation etc for generating the switching patterns in multilevel inverters [64, 65]. Next sections of this thesis discuss about such modulation and controlling techniques for a single-phase, five-level flying capacitor multilevel inverter modeled as in Fig. 1.3.

#### 1.6. THESIS ORGANIZATION

In this thesis, the concept of multilevel inverters, their basic topologies and applications have been discussed. One such topology, the single-phase five-level flying capacitor multilevel inverter is focused on. Section 2 explains its operation as a seven-level topology with no redundancy and the disadvantages of implementing it in such a mode. To overcome the disadvantages and for availability of redundancy in switching states, the FCMLI considered is operated as a five-level topology in Section 3. It also discusses the staircase modulation technique for capacitor voltage regulation. There are several drawbacks with staircase modulation technique. These are mentioned and the need for simpler techniques as phase disposition sinusoidal PWM and phase shifted

sinusoidal PWM are discussed in Section 4. Section 5 of the thesis discusses the proposed split natural balancing technique for capacitor voltage regulation to avoid the disadvantages associated with PDPWM and natural balancing techniques. Initial voltage of the capacitors if not at the required value, does not provide the desired results. To overcome such a situation, a feedback technique called amplitude modulation technique is discussed in Section 6. This section also talks about the generalization of the proposed methods to higher level flying capacitor multilevel inverter topologies. Harmonic analysis of the output voltage for the implemented control techniques is performed and compared to that of the proposed methods in Section 7. Advantages of the proposed methods are also explained here. Conclusion is presented in Section 8. The units for various parameters shown in the simulation results are seconds (s) for time, volts (V) for output and capacitor voltages, and amperes (A) for load current unless otherwise mentioned.

#### 2. FCMLI WITH NO REDUNDANCY

With some distinct advantages over the other two multilevel topologies such as the absence of clamping diodes and not requiring isolated individual sources, flying capacitor multilevel inverter topologies have gained prominence in industry. Because of the redundancy available to generate the same voltage level in the FCMLI topology, the voltage balancing of capacitors is not an issue. However, some of the redundant states may not be available when the capacitor voltage ratios are changed to increase the number of levels for improving the power quality [66]. A single-phase two-leg FCMLI topology to generate seven levels of voltages is discussed in this section.

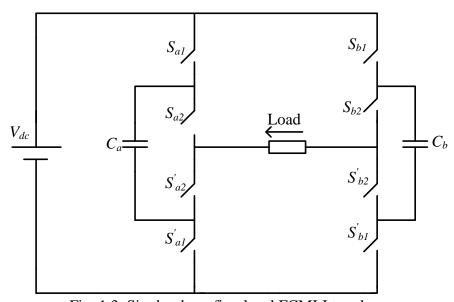

#### 2.1. CONVERTER TOPOLOGY

Figure 2.1 shows the two leg FCMLI topology for obtaining the different levels of voltage across the load. Although the dc source voltage sources are shown to be two, it is basically the same source. Initial values of capacitor voltages are considered to be the same and are given by a ratio of the dc source voltage  $V_{dc}$ . Switches S & S' on each leg are complementary to each other. These switching states are considered as depicted in Table 2.1.

Fig. 2.1. FCMLI topology

Table 2.1 Switching states to determine state indicator

| <b>S</b> 1 | S2  | State |  |

|------------|-----|-------|--|

| ON         | ON  | 3     |  |

| ON         | OFF | 2     |  |

| OFF        | ON  | 1     |  |

| OFF        | OFF | 0     |  |

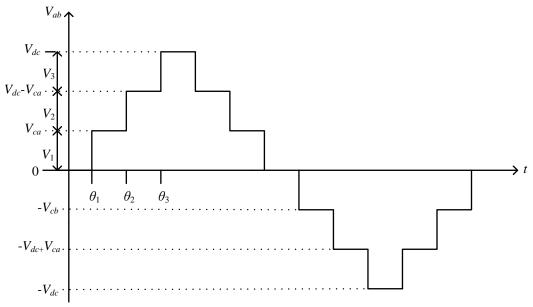

Voltage  $V_{bg}$  on  $leg\ b$  is 180 degrees out of phase with the voltage  $V_{ag}$  on  $leg\ a$ . Hence, the resultant voltage  $V_{ab}$  across the load is a multi level stair case waveform as shown in Fig. 2.2.

Fig. 2.2. Seven-level staircase voltage  $V_{ab}$

Now that different voltage levels are obtained, the capacitor currents in terms of the load current can be tabulated as in Table 2.2.

Table 2.2 Output voltages and capacitor currents

| State | $V_{ag}$            | $V_{bg}$         | $i_{ca}$     | $i_{cb}$    |

|-------|---------------------|------------------|--------------|-------------|

| 3     | $V_{dc}$            | $-V_{dc}$        | 0            | 0           |

| 2     | $V_{dc}$ - $V_{ca}$ | $-V_{dc}+V_{cb}$ | $i_{Load}$   | $-i_{Load}$ |

| 1     | $V_{ca}$            | - $V_{cb}$       | - $i_{Load}$ | $i_{Load}$  |

| 0     | 0                   | 0                | 0            | 0           |

The Fourier series of the staircase output voltage (see Fig. 2.2) can be described

$$V_{ab}(t) = \sum_{n=1,3}^{\infty} \frac{4}{n\pi} (V_1 Cosn\theta_1 + V_2 Cosn\theta_2 + V_3 Cosn\theta_3) Sin(n\omega t) \quad (2.1)$$

Where 'n' is the order of the harmonic and ' $\omega$ ' is the angular frequency. The voltage levels of the dc sources are equal and labeled to be  $V_{dc}$ . Also, the voltage of the capacitors is same and intended to be regulated at  $\frac{V_{dc}}{p}$ . Accordingly, considering Table 2.2, it can be written:

$$V_1 = \frac{V_{dc}}{p}$$

$$V_1 + V_2 = V_{dc} - \frac{V_{dc}}{p}$$

$$V_1 + V_2 + V_3 = V_{dc}$$

The modulation index in general is defined as:

Modulation Index

$$(M) = \frac{V_m}{V_{dc}}$$

(2.2)

where,  $V_m$  is the magnitude of the fundamental component of the output voltage.

### 2.2 THETA CALCULATIONS

Considering only the fundamental component and eliminating the 3<sup>rd</sup> and the 5<sup>th</sup> order harmonics, the following equations are used to calculate  $\theta_1$ ,  $\theta_2$ , and  $\theta_3$  for different values of the modulation index 'M'. Here 'p' is considered to be three.

$$V_{dc} * M = \frac{4}{\pi} \frac{V_{dc}}{3} (Cos\theta_1 + Cos\theta_2 + Cos\theta_3)$$

(2.3)

$$\frac{4}{3\pi} \frac{V_{dc}}{3} (\cos 3\theta_1 + \cos 3\theta_2 + \cos 3\theta_3) = 0 \tag{2.4}$$

$$\frac{4}{5\pi} \frac{V_{dc}}{3} (\cos 5\theta_1 + \cos 5\theta_2 + \cos 5\theta_3) = 0 \tag{2.5}$$

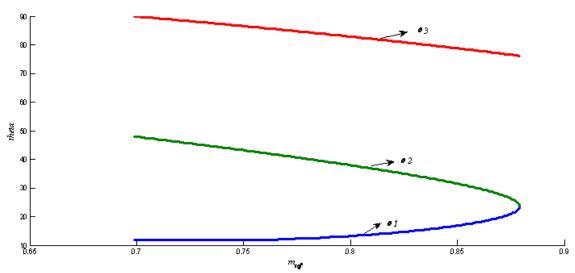

Figure 2.3 shows the graph drawn for the three angles at various modulation indices considering  $V_{dc}$  to be 300 V.

Fig. 2.3. Variation of thetas with the modulation index

Typical values of the angles at M=0.7 & at M=0.877 are as mentioned in Table

Table 2.3 Thetas when M=0.7 & M=0.877

2.3:

| Theta<br>M    | $	heta_1$ | $\theta_2$ | $\theta_3$ |

|---------------|-----------|------------|------------|

| $M_1 = 0.7$   | 12        | 47.92      | 89.95      |

| $M_2 = 0.877$ | 22        | 25.19      | 76.35      |

## 2.3. CAPACITOR VOLTAGE CHARACTERISTICS

With these values of firing angles, the capacitor voltages, the output voltage and the load current at different values of power factor were observed under constant power operation of 200 W by varying the load, using MATLAB Simulink. The values of the load resistance and inductance under different power factor conditions and modulation indices are given in Tables 2.4 and 2.5.

Table 2.4 Load resistance (R) and inductance (L) at different power factors when M=0.7

| Power Factor | R (Ω)  | L (mH) |

|--------------|--------|--------|

| 0.3          | 6.1224 | 3.09   |

| 0.4          | 10.884 | 3.969  |

| 0.5          | 17.006 | 4.68   |

| 0.6          | 24.48  | 5.196  |

| 0.7          | 33.33  | 5.412  |

| 0.8          | 43.537 | 5.196  |

| 0.9          | 55.102 | 4.24   |

$\label{eq:table 2.5} Table \ 2.5 \\ Load \ resistance \ (R) \ and \ inductance \ (L) \ at \ different \ power \ factors \ when \ M=0.877$

| Power Factor | R (\O) | L (mH) |

|--------------|--------|--------|

| 0.3          | 9.623  | 4.87   |

| 0.4          | 17.107 | 6.23   |

| 0.5          | 26.731 | 7.368  |

| 0.6          | 38.492 | 8.168  |

| 0.7          | 52.39  | 8.507  |

| 0.8          | 68.431 | 8.168  |

| 0.9          | 86.608 | 6.676  |

These values are found from the power calculations and the power factor formulae given by,

$$P = \frac{V_m^2}{R^2 + L^2 \omega^2} \frac{R}{2} = 200 \tag{2.6}$$

$$tan\Phi = \frac{L\omega}{R} \tag{2.7}$$

where, 'P' is the output power, ' $\Phi$ ' is the power factor angle and ' $V_m$ ' is the magnitude of the fundamental component of the output voltage obtained from equation (2.1). The fundamental frequency is considered to be 1 kHz.

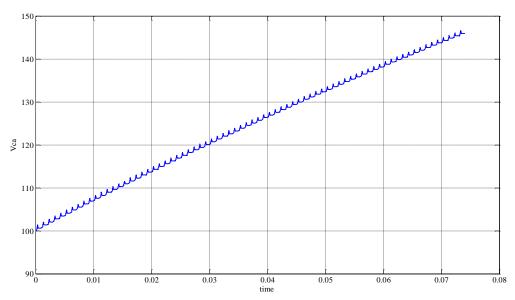

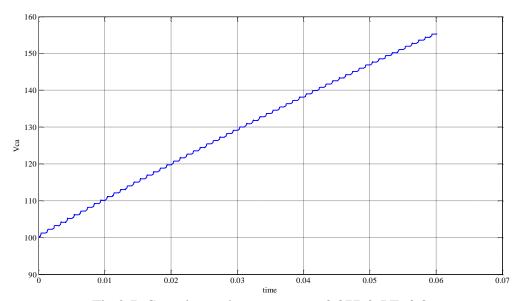

The simulation results showing the capacitor voltages, load current and the output voltage for M=0.7 and M=0.877 at a power factor of 0.8 are shown in Figs. 2.4-2.9, respectively. Capacitor voltage  $V_{cb}$  is similar to that of  $V_{ca}$ , voltage across the capacitor  $C_a$  for both the modulation indices.

Fig. 2.4. Capacitor voltage  $V_{ca}$  at M=0.7 & PF=0.8

Fig. 2.5. Output Voltage  $V_{ab}$  at M=0.7 & PF=0.8

Fig. 2.6. Load current  $i_{load}$  at M=0.7 & PF=0.8

Fig.2.7. Capacitor voltage  $V_{ca}$  at M=0.877 & PF=0.8

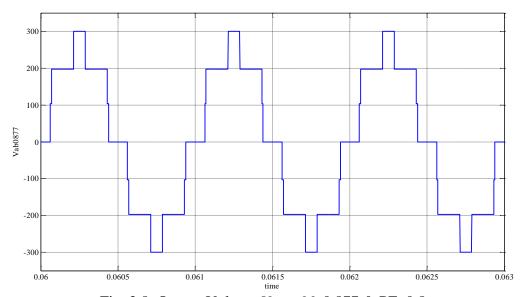

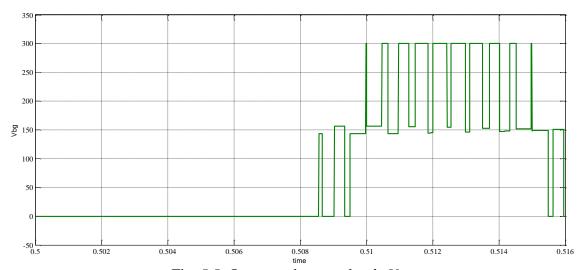

Fig. 2.8. Output Voltage  $V_{ab}$  at M=0.877 & PF=0.8

Fig. 2.9. Load current  $i_{load}$  at M=0.877 & PF=0.8

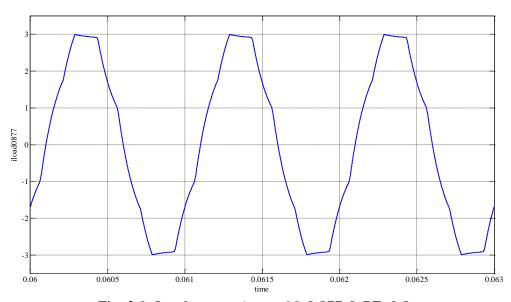

Next aspect that was looked into was the effect of power factor on output voltage and load current. Figures 2.10 to 2.13 show the same at power factor 0.7 for two different modulation indices M=0.7 and M=0.877.

Fig. 2.10. Output voltage  $V_{ab}$  at M=0.7 & PF=0.7

Fig. 2.11. Load current  $i_{load}$  at M=0.7 & PF=0.7

Fig. 2.12. Output voltage  $V_{ab}$  at M=0.877 & PF=0.7

Fig. 2.13. Load current  $i_{load}$  at M=0.877 & PF=0.7

# 2.4 EFFECTS OF MODULATION INDEX, POWER FACTOR AND REDUNDANCY

Figures 2.4-2.13 show the simulation results of the inverter at modulation indices M=0.7 and M=0.877. It can be observed from these that the variation in the modulation index or the power factor does not affect the capacitor voltages. However, variation in the modulation index has noticeable changes on the output voltage and load current characteristics of the FCMLI topology considered.

The main drawback of operating the converter for such higher number of voltage levels is that it does not give the option of redundancy in switching states. This makes the regulation of capacitor voltages difficult. As can be seen in Figs. 2.4 and Fig. 2.7, the capacitor voltages are increasing continuously and are not controlled. Therefore, redundancy plays a vital role in the regulation of the capacitor voltages in a flying capacitor multilevel inverter topology. This calls for reduction in the number of levels in the output voltage. However, it can be an advantage because it makes the capacitor voltage regulation much simpler and easier as Section 3 discusses.

### 3. STAIRCASE MODULATION FOR FCMLI WITH REDUNDANCY

### 3.1. FIVE-LEVEL OPERATION OF THE FCMLI TOPOLOGY

The same FCMLI topology shown in Fig. 2.1 of Section 2 is considered. It is being operated as a full bridge arrangement offering five distinct output voltage levels across the load instead of operating as a seven-level inverter This is to make use of the redundant states available for capacitor voltage regulation. The voltage across the capacitors  $C_a$  and  $C_b$  is going to be regulated at half the dc source voltage  $(V_{ca}=V_{cb}=V_{dc}/2)$ . Switches S & S' on each leg of the converter are still complementary implying only one of them is ON at any instant of time.

The five output voltage levels obtained across the load are  $V_{dc}$ ,  $V_{dc}/2$ , 0, -  $V_{dc}/2$ , -  $V_{dc}/2$ , Table 3.1 shows the different combinations of voltages  $V_{ag}$  and  $V_{bg}$  on each leg of the converter to obtain all five different output voltage levels. It has to be noted that the redundancy in the switching states discussed in this thesis is per leg. Though, the same level of output voltage can be obtained by a combination of  $V_{ag}$  and  $V_{bg}$ , only the redundancy on leg a is used for regulating capacitor voltage  $V_{ca}$  and the redundancy in the switching states of leg b is used to regulate the capacitor voltage  $V_{cb}$

Table 3.1 Different voltage levels for five-level operation ( $V_{ca}=V_{cb}=V_{dc}/2$ )

| $V_{ab}$    | $V_{ag}$            | $V_{bg}$            |

|-------------|---------------------|---------------------|

|             | 0                   | 0                   |

| 0           | $V_{dc}$ - $V_{ca}$ | $V_{dc}$ - $V_{cb}$ |

| 0           | $V_{ca}$            | $V_{cb}$            |

|             | $V_{dc}$            | $V_{dc}$            |

|             | $V_{ca}$            | 0                   |

| V /2        | $V_{dc}$ - $V_{ca}$ | 0                   |

| $V_{dc}/2$  | $V_{dc}$            | $V_{cb}$            |

|             | $V_{dc}$            | $V_{dc}$ - $V_{cb}$ |

| $V_{dc}$    | $V_{dc}$ 0          |                     |

|             | 0                   | $V_{cb}$            |

| $-V_{dc}/2$ | $V_{ca}$            | $V_{dc}$            |

|             | $V_{dc}$ - $V_{ca}$ | $V_{dc}$            |

|             | 0                   | $V_{dc}$ - $V_{cb}$ |

| $-V_{dc}$   | 0                   | $V_{dc}$            |

Circled states in the table are the redundant states to be used. The switching states to obtain these voltage levels on each leg ( $V_{ag} \& V_{bg}$ ) of the converter are shown in Table 3.2 and Table 3.3, respectively.

Table 3.2 Switching states for  $V_{ag}$  for five-level operation

| $S_{a1}$ | $S_{a2}$ | S a2 | $\mathbf{S}^{'}_{a1}$ | $V_{ag}$            |

|----------|----------|------|-----------------------|---------------------|

| 0        | 0        | 1    | 1                     | 0                   |

| 0        | 1        | 0    | 1                     | $V_{ca}$            |

| 1        | 0        | 1    | 0                     | $V_{dc}$ - $V_{ca}$ |

| 1        | 1        | 0    | 0                     | $V_{dc}$            |

Table 3.3 Switching states for  $V_{bg}$  for five-level operation

| S <sub>b1</sub> | $S_{b2}$ | S b2 | S b1 | $V_{bg}$            |

|-----------------|----------|------|------|---------------------|

| 0               | 0        | 1    | 1    | 0                   |

| 0               | 1        | 0    | 1    | $V_{cb}$            |

| 1               | 0        | 1    | 0    | $V_{dc}$ - $V_{cb}$ |

| 1               | 1        | 0    | 0    | $V_{dc}$            |

The five level output voltage thus obtained is shown in Fig. 3.1.

Fig. 3.1. Five-level staircase voltage  $V_{ab}$

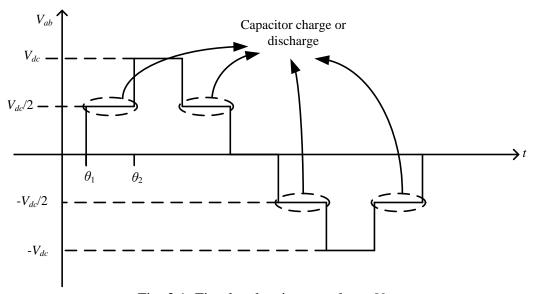

### 3.2 AVAILABILITY OF REDUNDANCY

Maintaining the desired voltage across the capacitors is the main challenge in ensuring proper operation of the inverter. There are several conduction paths that can produce the same voltage levels which will cause charging or discharging of capacitors depending on the overall state of the switches and load current polarity [8]. In the FCMLI topology considered, it can be observed that to obtain the states  $V_{dc}/2$  and  $V_{dc}/2$ , we have redundancy in switching states in which capacitor voltages appear with opposite polarities (see Table 3.2). This redundancy can be used to choose the path that can provide the best balancing characteristics for the capacitor voltages at any point of time. The ratio of the capacitor voltages can be changed to improve the power quality of the output voltage by increasing the number of output voltage levels. However, this requires the sacrificing of the redundancy in the switching states that helps in the capacitor voltage balancing as discussed in Section 2. Therefore, it has to be a tradeoff between power

quality (with increased number of output voltage levels) and capacitor voltage balancing of the FCMLI topology [66].

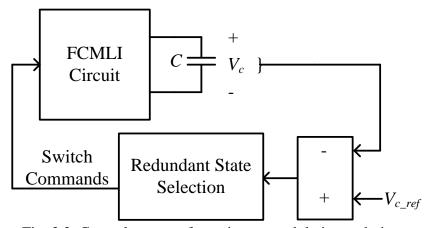

### 3.3 CAPACITOR VOLTAGE BALANCING (STAIRCASE MODULATION)

In order to obtain the desired levels in the output voltage, capacitor voltages should be maintained at a constant voltage level. As seen before, to obtain the same level of output voltage, there is a choice where one state among the available redundant states can be selected. For the topology considered, this can be done by assuming a specific value for the capacitor initial voltage which is equal to the voltage ratio  $V_{dc}/2$ . By comparing the actual voltages of the capacitors to this value, the switching pattern (turning ON and turning OFF of the switches) is decided. This charges and discharges the capacitors accordingly and thus, balances the internal voltage of the capacitors. Figure 3.2 shows the control used for staircase modulation.

Fig. 3.2. Control strategy for staircase modulation technique

### 3.4 EFFECTS OF POWER FACTOR

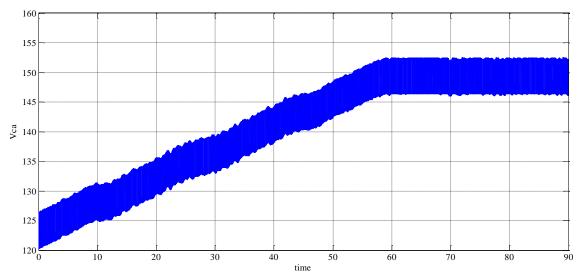

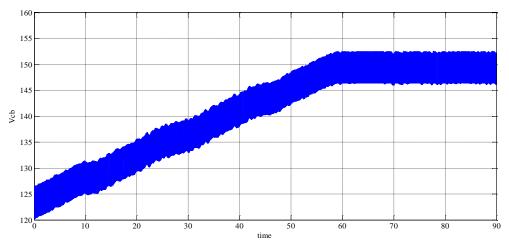

Most of the studies that have been done on FCML converters have assumed the operation at unity power factor or one close to it. Though, power factor has not much effect on the capacitor voltages, it shows a considerable effect on the load current characteristics. At power factors nearing unity, the results are close to the desired results. Figures 3.3-3.6 show the capacitor voltages  $V_{ca}$ , and  $V_{cb}$  at power factors equal to 0.9 and 0.3, respectively. It can be observed from these figures that there is not much difference in the characteristics of the capacitor voltages with the variation in power factor.

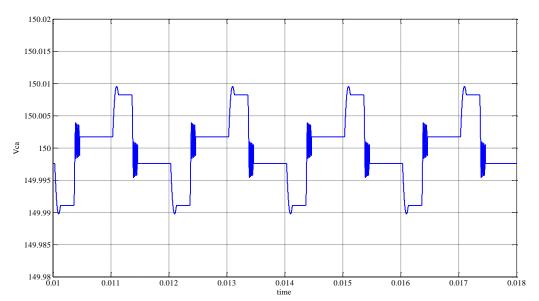

Fig. 3.3. Capacitor voltage  $V_{ca}$  at PF=0.9

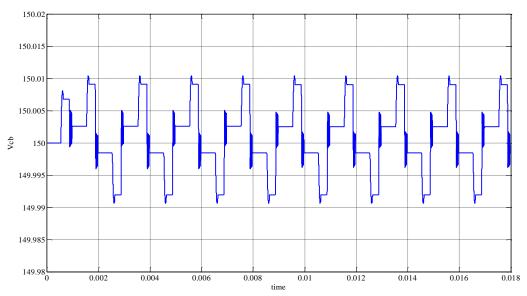

Fig. 3.4. Capacitor voltage  $V_{cb}$  at PF=0.9

Fig. 3.5. Capacitor voltage  $V_{ca}$  at PF=0.3

Fig. 3.6. Capacitor voltage  $V_{cb}$  at PF=0.3

## 3.5 OTHER SIMULATION RESULTS

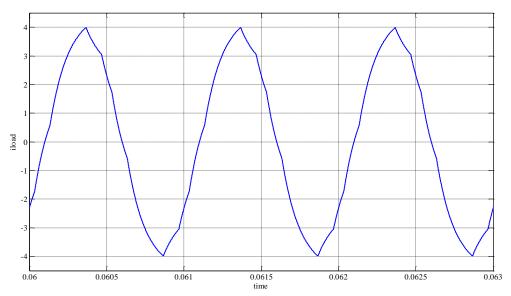

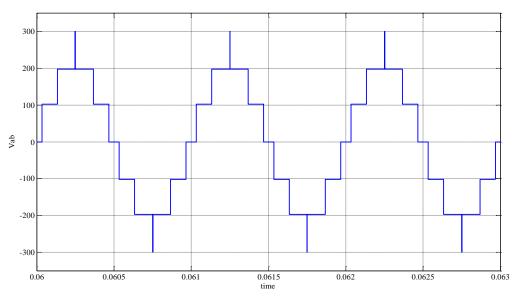

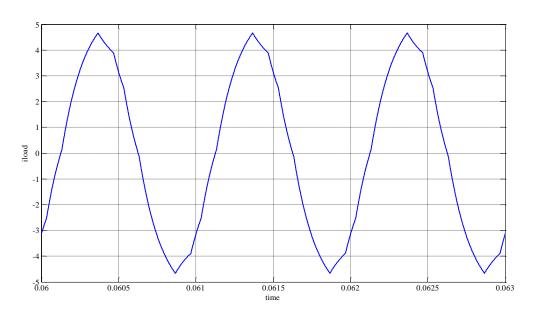

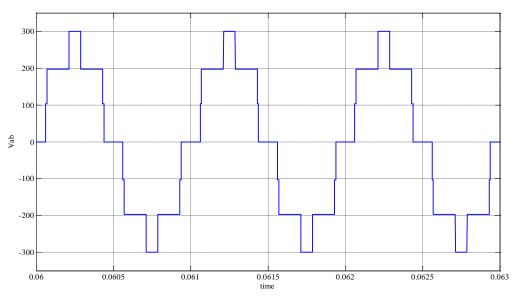

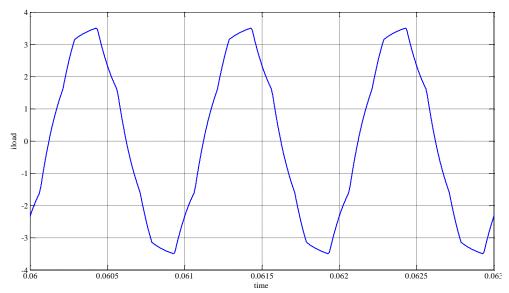

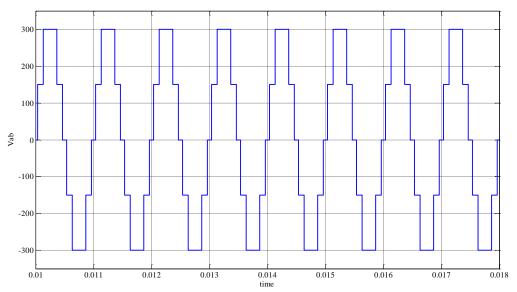

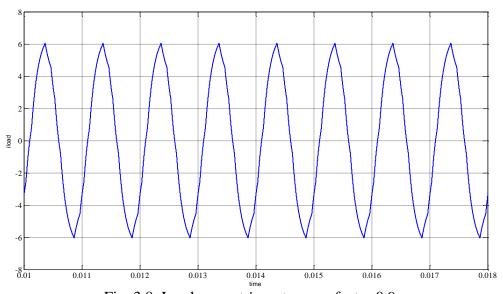

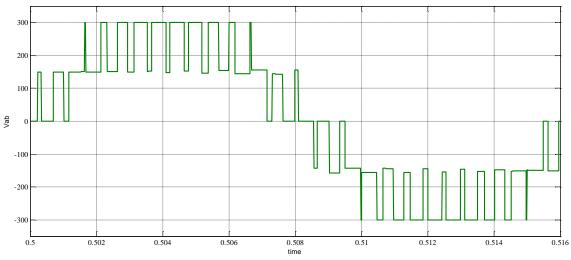

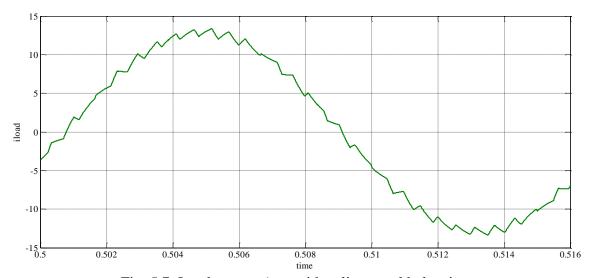

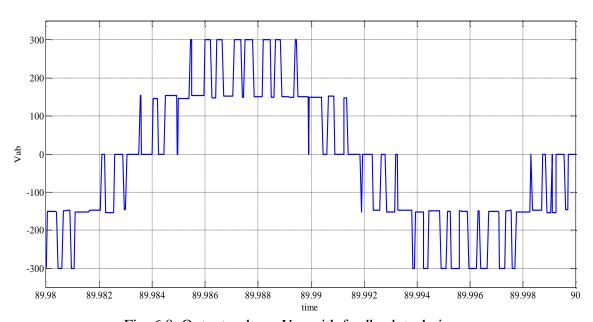

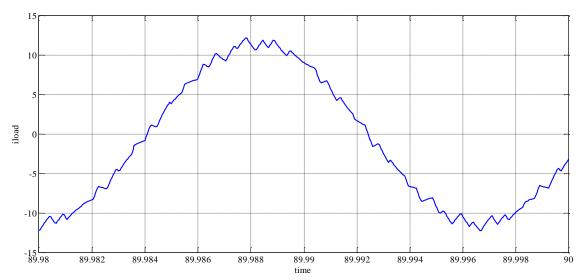

Other important parameters that have to be looked into for the effects of power factor are the output voltage and load current. The simulation results for the five level output voltage  $V_{ab}$  and the load current  $i_{load}$  at power factors 0.9 and 0.3 are shown in Figs. 3.7 - 3.10, respectively.

Fig. 3.7. Five level output voltage  $V_{ab}$  at power factor 0.9

Fig. 3.8. Load current  $i_{load}$  at power factor 0.9

Fig. 3.9. Five level output voltage  $V_{ab}$  at power factor 0.3

Fig. 3.10. Load current  $i_{load}$  at power factor 0.3

It is clear from the figures that there is a change in the amplitude of the load current  $i_{load}$ , with the change in power factor. However, this does not very much affect the capacitor voltages or the output voltage characteristics.

Staircase modulation technique requires measuring the voltages of capacitors and the load current polarity. In order to avoid this, easier and simpler methods have been developed based on the PWM techniques especially, the sine-triangle PWM (SPWM) [67-71]. The next sections talk about such methods as phase disposition SPWM (PDPWM), phase shifted SPWM (PSPWM), etc which do not require any capacitor voltage measurements, and the advantages and disadvantages associated with them.

# 4. PHASE DISPOSITION AND PHASE SHIFTED SINE TRIANGLE PWM

### 4.1 PWM CONTROL SCHEMES

Many controlling techniques have been developed and implemented of which the PWM control is the most widely used. A significant number of publications have been made on the various ways of implementing this technique [71]. PWM control techniques have been the most feasible control methods of all the FCMLI control schemes. There are many ways in which this PWM control can be implemented based on the type of carrier signal used. The most common among these is using a triangular wave as carrier signal and a sinusoidal signal for reference. Such a technique is called the sine—triangle PWM (SPWM).

This can again be implemented in different ways based on its carrier placement strategy [8]. Older methods used Unipolar modulation technique which used a single carrier that is compared to a sinusoidal reference to generate the two firing pulses of opposite polarity. Another strategy which used a single carrier signal and various distinct sinusoidal signals for reference was proposed in [8]. The sine – triangle PWM is done by dividing the sine wave reference into distinct contiguous bands. This reference is now compared to the triangular carrier signal waves. The number of carrier signals is equal to the number of complementary switch pairs in the inverter topology. Since all the carrier signals are in phase and disposed in bands, this carrier placement strategy is called as the phase disposition (PD) sine triangle PWM. The other carrier placement strategy uses the entire reference range. However, the carrier signals are all out of phase with each other. This scheme is called the phase shifted (PS) PWM.

### 4.2. PD SINE TRIANGLE PWM

The switching frequency of generated pulses is based on the carrier frequency, and output amplitude depends on the amplitude of the sinusoidal reference signal. Two important controlling parameters of SPWM are frequency modulation index  $(m_f)$  and amplitude modulation index  $(m_a)$ . They are defined as follows:

$m_f$  – ratio of carrier frequency to reference frequency

$$m_f = \frac{f_c}{f_{ref}}$$

$m_a$  – ratio of reference peak to peak amplitude to dc source voltage

$$m_a = \frac{A_{refpk-pk}}{A_{dc}}$$

The common among the various SPWM techniques is the phase disposition (PD) carrier placement strategy which as mentioned earlier, uses the same number of carrier signals as the number of complementary switch pairs. This set of carrier signals are in phase with each other but at different voltage levels. Such a method is used for balancing the voltages of the capacitors in the considered single phase five level FCMLI topology.

Figure 4.1 shows the four triangular carrier signals and the sinusoidal reference signal. The carrier signals are compared to the reference sinusoidal signal to obtain the required control pulses. Figure 4.2 shows the control pulses thus generated.

The frequency and the amplitude modulation indices for the selected PWM control scheme are chosen to be 15 and 0.9, respectively.

$$m_f = \frac{f_c}{f_{ref}} = \frac{900}{60} = 15$$

$$m_a = \frac{A_{refpk-pk}}{A_{dc}} = \frac{1.8}{2} = 0.9$$

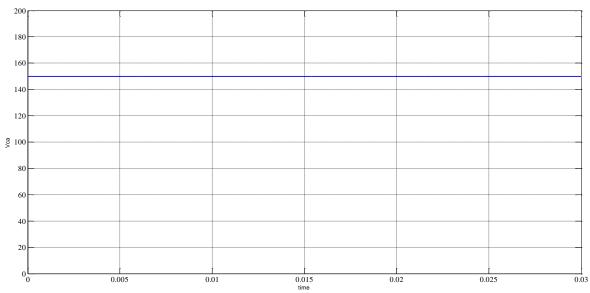

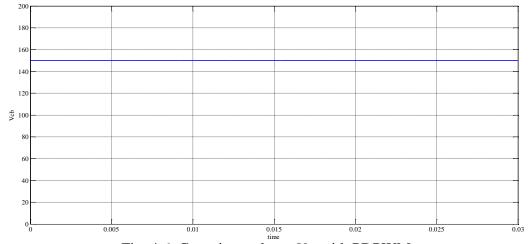

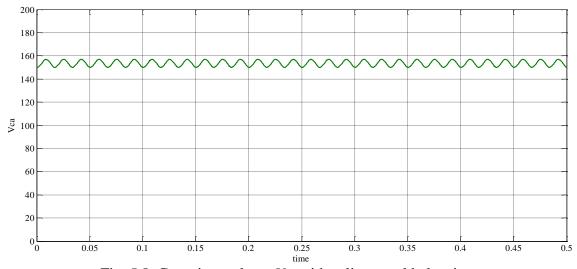

Choosing the frequency modulation index to be a multiple of three eliminates the third multiple harmonics across the load [63]. Hence,  $m_f$  is chosen to be 15. The output voltage  $(V_{ab})$  obtained across the load consists of the desired five levels. Figures 4.3, and 4.4 show the output voltage across the load and the load current  $(i_{load})$ . By using this kind of control technique, the capacitor voltages are very much in balance and regulated over a very small range as can be observed from Figure 4.5 and 4.6. The values for capacitors, and load parameters involved in the FCMLI topology to obtain the simulation results all through this thesis are as mentioned in Table 4.1.

Table 4.1. Simulation parameters

| Parameter | Value     |

|-----------|-----------|

| Ca        | 10 mF     |

| $C_b$     | 10 mF     |

| R         | 20.1087 Ω |

| L         | 15.05 mH  |

Fig. 4.5. Capacitor voltage  $V_{ca}$  with PDPWM

Fig. 4.6. Capacitor voltage  $V_{cb}$  with PDPWM

Although PD SPWM technique works well for capacitor voltage regulation, it is not very easy to implement because of the disposition required in the carrier signals. Hence, we can make use of much simpler techniques of flying capacitor voltage balancing like natural balancing technique which makes use of the phase shifted sine-triangle PWM method. This method which is a self-balancing technique that does not

require the measurement of capacitor voltages or load current polarity is implemented on the considered FCMLI topology.

### 4.3. PHASE SHIFTED PWM (NATURAL BALANCING)

As discussed earlier, capacitor voltage balancing is done by measuring the capacitor voltages and current direction. The appropriate switching states are selected based on the desired output voltage level, capacitor voltages, and current direction. This uses the redundancy in the output voltage levels. Natural balancing method doesn't need these measurements. It is done by using equal duty cycles for every pair of complementary switches in the inverter topology [71-74]. Due to its simplicity, this method has found several applications.

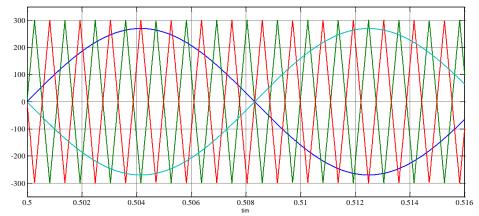

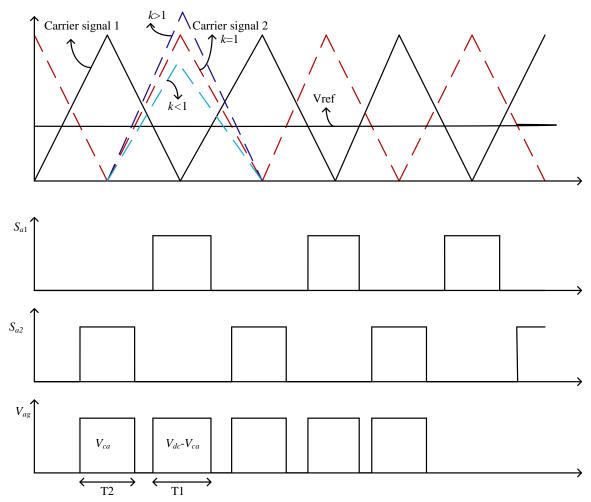

Natural balancing is performed by the phase shifted PWM (PSPWM) in which the carrier waveforms are shifted from each other by a phase equal to  $360^{\circ}/N$ , where N is the number of pairs of complementary switches per leg. The sinusoidal reference is compared to the carrier waveforms and the corresponding switching states are obtained.

For the FCMLI topology considered, since the number of pairs of complementary switches (N) per leg is 2, the two carrier signals are shifted by a phase of  $180^{\circ}$  from each other. When the reference signal is greater than carrier signal 1, switch  $S_{a1}$  is turned ON. Similarly, when the reference signal is greater than carrier signal 2, then switch  $S_{a2}$  is turned ON. A similar PWM method which uses a reference signal with a phase shift of  $180^{\circ}$  to that of the leg a is implemented on leg b on the right hand side of the inverter topology to turn switches  $S_{b1}$  and  $S_{b2}$  ON. The PWM technique used, switching pulses

and output voltages on each leg and across the load are shown in Figs 4.7 to 4.12, respectively.

Fig. 4.7. Phase shifted sine triangle PWM for natural balancing technique

Fig. 4.9. Switching pulses for switch  $S_{a2}$

Fig. 4.11. Output voltage of leg b,  $V_{bg}$  with natural balancing

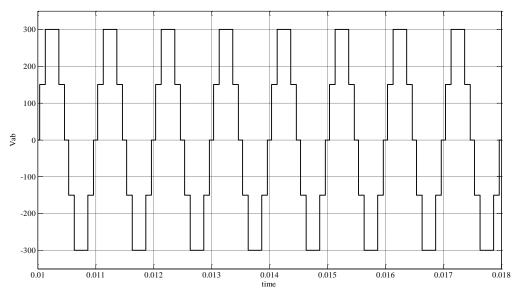

Fig. 4.12. Output voltage  $V_{ab}$  across load with natural balancing

The output voltage is expected to have levels at  $V_{dc}$ ,  $V_{dc}/2$ , 0,  $-V_{dc}/2$ , and  $-V_{dc}$ . However, natural balancing method of capacitor voltage regulation does not generate all the required levels of the output voltage. For the considered topology, levels  $V_{dc}/2$  and  $-V_{dc}/2$  are missing in the output voltage waveform when this technique is used to regulate

the capacitor voltages. This could have been avoided if an even number of positive levels were initially selected. However, it might not be always desirable. In order to solve this problem, a new method called split natural balancing is proposed in the next section. This method is devised using the Unipolar PWM technique.

# 5. SPLIT NATURAL BALANCING TECHNIQUE FOR CAPACITOR VOLTAGE REGULATION

### 5.1. DISADVANTAGES OF NATURAL BALANCING

Natural balancing technique though, the simplest of all voltage regulating methods for an FCMLI, has a few disadvantages. As seen in the previous section, it is not very feasible for any number of voltage levels and moreover, is not very practical in implementation. Though it works well in a simulation where every condition is considered ideal, it doesn't produce the exact desired results when being implemented on real hardware using DSPs etc where the conditions might be different from ideal. This might cause few issues in practical implementation of natural balancing using PSPWM technique. To overcome these issues, split natural balancing technique is proposed by using which the capacitor voltages can either be charged or discharged according to the requirement to maintain a balance.

### 5.2. SPLIT NATURAL BALANCING TECHNIQUE

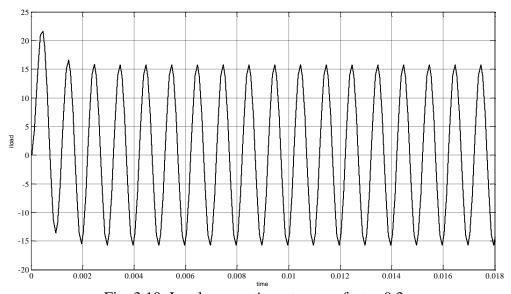

The split natural balancing technique for voltage regulation of capacitors in an FCMLI is similar to the conventional natural balancing technique which produces the switching pulses by comparing a sinusoidal reference signal with triangular carrier signals. In this proposed method, at any instant, only one of the legs of the single-phase inverter produces the output voltage while the other leg produces a zero voltage level. In other words, for one half of the fundamental cycle of the sinusoidal references, only leg a of the inverter operates and for the second half-cycle, leg b of the inverter operates. Figures 5.1 to 5.5 show the sinusoidal reference signal,  $(V_{ref})$  and the triangular carrier

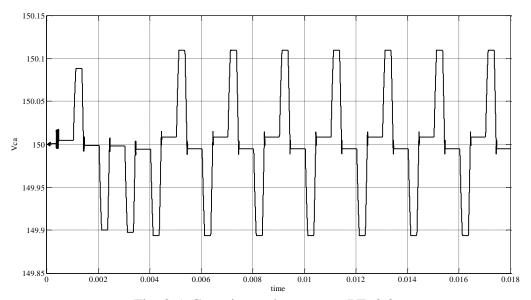

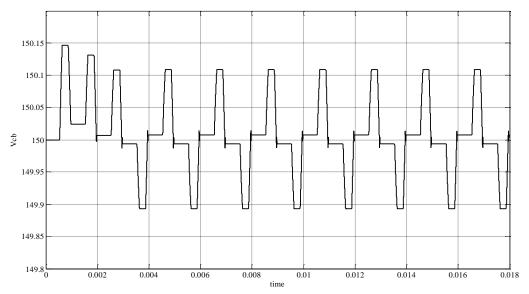

waveforms, switching pulses for the switches  $S_{a1}$  and  $S_{b1}$ , Output voltage  $V_{ag}$  on leg a, and output voltage  $V_{bg}$  on leg b, respectively. Leg a works during the period when  $V_{ref}$  is shown as solid wave and leg b is operating when  $V_{ref}$  is shown as a dashed line waveform.

Fig. 5.1. Sine triangle PWM for split natural balancing