# Scholars' Mine

## Masters Theses

Student Theses and Dissertations

Summer 2010

Prediction of soft error response of integrated circuits to electrostatic discharge injection via simulation field; Package interaction for electrostatic discharge soft error prediction; Full wave model for simulating noise ken electrostatic discharge generator

Argha Nandy

Follow this and additional works at: https://scholarsmine.mst.edu/masters\_theses

Part of the Electrical and Computer Engineering Commons Department:

## **Recommended Citation**

Nandy, Argha, "Prediction of soft error response of integrated circuits to electrostatic discharge injection via simulation field; Package interaction for electrostatic discharge soft error prediction; Full wave model for simulating noise ken electrostatic discharge generator" (2010). *Masters Theses*. 4992. https://scholarsmine.mst.edu/masters\_theses/4992

This thesis is brought to you by Scholars' Mine, a service of the Missouri S&T Library and Learning Resources. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

# PREDICTION OF SOFT ERROR RESPONSE OF INTEGRATED CIRCUITS TO ELECTROSTATIC DISCHARGE INJECTION VIA SIMULATION FIELD PACKAGE INTERACTION FOR ELECTROSTATIC DISCHARGE SOFT ERROR PREDICTION FULL WAVE MODEL FOR SIMULATING NOISEKEN ELECTROSTATIC DISCHARGE GENERATOR

by

## **ARGHA NANDY**

## A THESIS

Presented to the Faculty of the Graduate School of the

## MISSOURI UNIVERSITY OF SCIENCE AND TECHNOLOGY

In Partial Fulfillment of the Requirements for the Degree

## MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

2010

Approved by

David J. Pommerenke, Advisor James L. Drewniak Daryl Beetner

© 2010

Argha Nandy All Rights Reserved

#### ABSTRACT

In the first section, a concept for analyzing soft error response in ICs to ESD via coupling through flex cable structures is presented. Its novelty lies in accounting for the transient electromagnetic fields radiated by the ESD generator that couples to the flex cable PCB thereby causing disturbance on the IC under test. This is accomplished in three stages; first by developing a full wave model of the DUT which includes modeling the PCB and flex cable geometry and validating it in frequency domain with regard to the transfer impedance. This followed by combining the ESD generator with the DUT model to simulate the voltage at the IC input in time domain. Finally the time domain results from full wave simulation are combined with an equivalent IC response model in SPICE to predict soft error failures due ESD.

In the second section, a more detailed modeling of the IC including the lead frame geometry, bond wires and IBIS/ICEM models are incorporated to investigate coupling of fields from three different injection techniques- H field loop probes, TEM cell and ESD generator. For the first time a complete simulation model which includes the ESD generator, passive elements of the DUT structure (PCB) and a detailed model of the IC has been developed to predict interaction of radiated field from the generator to the IC.

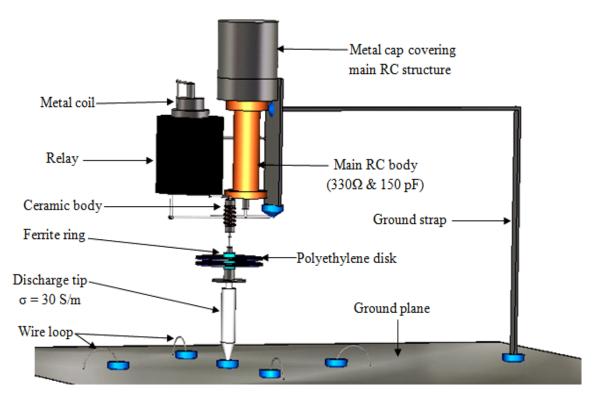

The third section shows a CST MWS model was generated to simulate the discharge current and the transient field of an ESD generator. Individual components of the Noise Ken ESD generator (ESS-2000) were modeled, validated and combined. The complete full wave model was verified by comparing the simulated discharge current waveforms and induced loop voltages with the measured results.

#### ACKNOWLEDGEMENTS

I would like to express my deepest gratitude to my advisor, Dr. David Pommerenke, for providing me the opportunity to pursue graduate studies in UMR/MS&T EMC Laboratory. I am deeply thankful for his patient guidance and support– both professional and personal which has often helped me to tide over difficult times in graduate school.

I would also like to thank Dr. James L. Drewniak and Dr. Daryl Beetner for their continued support throughout my research. Both served on my committee and provided insightful comments.

I am also grateful to Jayong Koo, Weifeng Pan, Fan Zhou, Li Tianqi, Li Zhen and Huang Wei for their support in my projects. I would like to thank Mr. Byong Su Seol, Mr. Jong Sung Lee and Mr. Jae-Deok Lim from Samsung Electronics Ltd for their continued advice and support of my primary research projects.

I would like to thank my friends Sagnik Saha, Shashwatashish Pattnaik, Abhinav Chadda, Andrea Orlando, Nikhil Doiphode, Bharat Gattu, Soumya De, Ram Krishna Rongala, Anup Vader, Julius Heim, Brandon, Naveen Chandrasekaran, Ryan Matthews, Ketan Shringarpure, Amendra Koul, Thomas Matthews, Uttam Chowdhury and many others in the EMC laboratory for making my stay in Graduate school a memorable one.

I owe special thanks to my father who has supported me through my education both financially and emotionally, and to my wonderful mother and my young sister who have always believed in me.

Last, but not the least, I would like to remember my very dear friend Varun Dutt who served for his country and will always be there with me.

## TABLE OF CONTENTS

| ABSTRA  | CT                                                                | iii  |

|---------|-------------------------------------------------------------------|------|

| ACKNOV  | WLEDGEMENTS                                                       | iv   |

| LIST OF | ILLUSTRATIONS                                                     | viii |

| LIST OF | TABLES                                                            | xii  |

| SECTION | 1                                                                 |      |

| 1. INT  | RODUCTION                                                         | 1    |

|         | PERIMENTAL INVESTIGATION OF ESD COUPLING TO IC VIA FLE<br>BLE PCB |      |

| 2.1     | DEFINITION OF TEST PLATFORM                                       | 3    |

| 2.2     | CHARACTERIZATION OF IC                                            | 9    |

|         | 2.2.1 Measurement setup.                                          | 9    |

|         | 2.2.2 Measurement results.                                        | 10   |

| 2.3     | ESD IMMUNITY OF ICs                                               | 13   |

|         | 2.3.1. Measurement setup.                                         | 13   |

|         | 2.3.2. Measurement results.                                       | 15   |

| 3. NU   | MERICAL PREDICTION OF SOFT ERROR ESD UPSET LEVEL                  | 24   |

| 3.1     | FREQUENCY DOMAIN MODEL OF FLEX CABLE PCB                          | 24   |

|         | 3.1.1. Measurement setup.                                         | 25   |

|         | 3.1.2. Full wave simulation model                                 | 27   |

|         | 3.1.3. Challenges in modeling of flex cable structure             | 31   |

| 3.2     | TIME DOMAIN MODEL OF FLEX CABLE PCB WITH ESD GENERATOR            | 33   |

| 3.3     | FULL WAVE MODEL + ESD SOFT ERROR MODEL OF IC                      |      |

| 3.4     | CONCLUSION                                                        | 42   |

| 4. FIE  | LD PACKAGE INTERACTION FOR IC SOFT ERROR PREDICTION.              | 43   |

| 4.1     | ESD FAILURE PARAMETERS                                            | 43   |

| 4.2     | DEFINITION OF TEST PLATFORM                                       | 44   |

| 5. FUI  | LL WAVE MODEL OF MEMORY IC (DDR SDRAM)                            | 49   |

| 5.1     | MODEL OF PHYSICAL GEOMETRY OF IC                                  | 49   |

|        | 5.1.1. Lead frame model of IC                         | 49  |

|--------|-------------------------------------------------------|-----|

|        | 5.1.2. Die and package model of IC                    | 51  |

|        | 5.1.3. Bond wire model of IC.                         | 53  |

| 5.2    | EXTRACTION OF LUMPED PARAMETERS FROM IBIS/ICEM MODELS | 54  |

|        | 5.2.1. Capacitance from VDD to VSS.                   | 54  |

|        | 5.2.2. Capacitance from VDDQ to VSSQ.                 | 58  |

|        | 5.2.3. Capacitance from Input to VSSQ.                | 60  |

|        | 5.2.4. Model of I/O pins (DQ, DQS, DM)                | 60  |

| 5.3    | CONCLUSION                                            | 62  |

| 6. FIE | LD SCANNING OF DDR MEMORY IC                          | 64  |

| 6.1    | MEASUREMENT SETUP                                     | 64  |

| 6.2    | ANALYTICAL ESTIMATION OF MAGNETIC FIELD STRENGTH      | 66  |

| 6.3    | ANALYTICAL ESTIMATION OF INDUCED NOISE VOLTAGE        | 72  |

| 6.4    | MAGNETIC FIELD INJECTION                              | 76  |

|        | 6.4.1. H-field test (5 mm loop).                      | 76  |

|        | 6.4.2. H-field test (1 mm loop)                       | 78  |

|        | 6.4.3. H-field test (0.5 mm loop)                     | 79  |

| 6.5    | MEASUREMENT OF INDUCED NOISE VOLTAGE                  | 80  |

| 6.6    | SIMULATION OF INDUCED NOISE VOLTAGE                   | 82  |

| 6.7    | COMPARISON OF RESULTS                                 | 88  |

| 6.8    | CONCLUSION                                            | 92  |

| 7. FIE | LD INJECTION VIA TEM CELL                             | 94  |

| 7.1    | INTRODUCTION                                          | 94  |

| 7.2    | MEASUREMENT SETUP                                     | 94  |

| 7.3    | MEASUREMENT RESULT                                    | 95  |

| 7.4    | SIMULATION OF INDUCED NOISE VOLTAGE                   | 96  |

| 7.5    | CONCLUSION                                            | 99  |

| 8. SYS | TEM LEVEL ESD GENERATOR TEST                          | 100 |

| 8.1    | INTRODUCTION                                          | 100 |

| 8.2    | MEASUREMENT SETUP                                     | 100 |

|    | 8.3   | MEASUREMENT RESULTS                                  | 102 |

|----|-------|------------------------------------------------------|-----|

|    | 8.4   | SIMULATION OF INDUCED NOISE VOLTAGE                  | 106 |

|    | 8.5   | CONCLUSION                                           | 111 |

|    | 8.6   | COMPARISON OF FIELD INJECTION TECHNIQUES             | 112 |

| 9. | -     | L WAVE MODEL TO SIMULATE THE NOISEKEN ESD<br>IERATOR | 115 |

|    | 9.1   | INTRODUCTION TO ESD GENERATOR                        | 115 |

|    | 9.2   | MODELING OF INDIVIDUAL COMPONENTS                    | 116 |

|    |       | 9.2.1. Modeling of relay                             | 117 |

|    |       | 9.2.2. Modeling of R-C body                          | 120 |

|    |       | 9.2.3. Modeling of ceramic body.                     | 124 |

|    |       | 9.2.4. Modeling of ferrite rings                     | 126 |

|    |       | 9.2.5. Modeling of polyethylene disks                | 129 |

|    | 9.3   | MODELING OF THE WHOLE ESD GENERATOR                  | 130 |

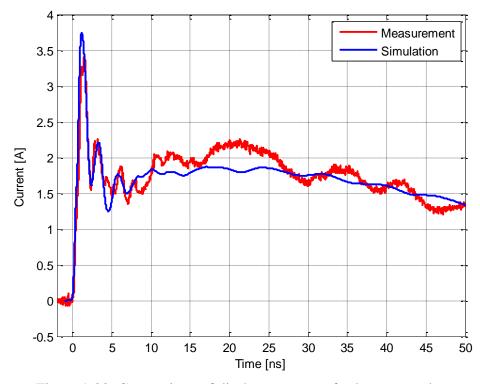

|    | 9.4   | VERIFICATION OF ESD DISCHARGE CURRENT                | 131 |

|    | 9.5   | VERIFICATION OF INDUCED LOOP VOLTAGE                 | 134 |

|    | 9.6   | CONCLUSION                                           | 139 |

| B  | IBLIO | OGRAPHY                                              | 140 |

| V  | ITA   |                                                      | 143 |

## LIST OF ILLUSTRATIONS

| Page                                                                            |

|---------------------------------------------------------------------------------|

| Figure 2.1. Circuit diagram of the slow IC mounted on the PCB                   |

| Figure 2.2. Photo of the IC and various components on the PCB                   |

| Figure 2.3. Circuit diagram of the IC mounted on the PCB7                       |

| Figure 2.4. Photo of the IC and various components on the PCB                   |

| Figure 2.5. Measurement setup for characterization of the IC                    |

| Figure 2.6. Pulses of varying magnitude and pulse width at the slow IC input 10 |

| Figure 2.7. Voltage at the slow IC input vs Pulse width                         |

| Figure 2.8. Pulses of varying magnitude and pulse width at the fast IC input 12 |

| Figure 2.9. Voltage at the fast IC input vs Pulse width 12                      |

| Figure 2.10. Measurement setup with ESD discharge on board                      |

| Figure 2.11. Comparison of voltage at the IC input for discharge onto the board |

| Figure 2.12. Comparison of frequency spectrum of voltage at IC input 17         |

| Figure 2.13. Comparison of voltage at the IC input for discharge onto the board |

| Figure 2.14. Comparison of frequency spectrum of voltage at IC input 20         |

| Figure 2.15. Comparison of discharge current onto board                         |

| Figure 2.16. Comparison of spectrum of the discharge current onto board         |

| Figure 2.17. Transfer impedance for discharge on to the board                   |

| Figure 3.1. Measurement setup for transfer impedance measurement                |

| Figure 3.2. Measured S21 of flex cable board                                    |

| Figure 3.3. CST model of flex cable board                                       |

| Figure 3.4. Comparison of measured and simulated Z11 30                         |

| Figure 3.5. Comparison of measured and simulated S21 30                         |

| Figure 3.6. Comparison of measured and simulated S21                            |

| Figure 3.7. CST model of slow IC with flex cable board and EM TEST DITO         |

| Figure 3.8. Comparison of measured and simulated voltage at the slow IC input   |

| Figure 3.9. Comparison of spectra of voltage at slow IC input                   |

| Figure 3.10. Comparison of measured and simulated discharge current             |

| Figure 3.11. SPICE model to predict crash level of Slow IC in response to ESD   |

| Figure 3.12. Simulated voltage at the Slow IC input in CST MWS                        | 39 |

|---------------------------------------------------------------------------------------|----|

| Figure 3.13. Voltage at the IC input vs Pulse width                                   | 40 |

| Figure 3.14. Comparison of voltage at the IC input and at the input to the switch     | 41 |

| Figure 3.15. Voltage at R_OUPUT indicating that the IC has triggered                  | 41 |

| Figure 4.1. TOP view of the test platform                                             | 47 |

| Figure 4.2. Status of the DDR SDRAM memory                                            | 47 |

| Figure 5.1. Lead frame model of the IC                                                | 50 |

| Figure 5.2. Dimension of lead traces                                                  | 50 |

| Figure 5.3. Die model of the IC                                                       | 51 |

| Figure 5.4. Cross sectional view of the die with the lead frame                       | 51 |

| Figure 5.5. Package model of the IC                                                   | 52 |

| Figure 5.6. Bond wire model of the IC                                                 | 53 |

| Figure 5.7. Experimental setup to measure capacitance                                 | 54 |

| Figure 5.8. Measured Impedance looking into VDD pin                                   | 55 |

| Figure 5.9. CST model to simulate Z11 into VDD pin                                    | 56 |

| Figure 5.10. Distributed lumped modeling of capacitance between VDD and DIE           | 57 |

| Figure 5.11. Comparison of measured and simulated Z11 into VDD pin                    | 58 |

| Figure 5.12. Measured Impedance looking into VDDQ pin                                 | 59 |

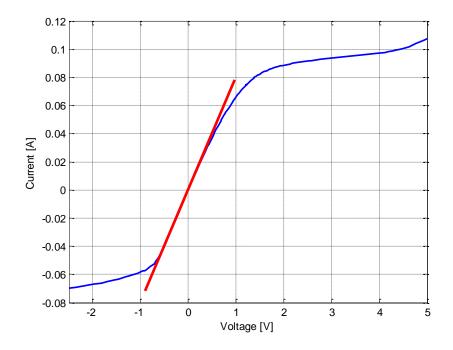

| Figure 5.13. Pullup V-I curve for DQ pins obtained from IBIS model                    | 61 |

| Figure 5.14. Pulldown V-I curve for DQ pins obtained from IBIS model                  | 61 |

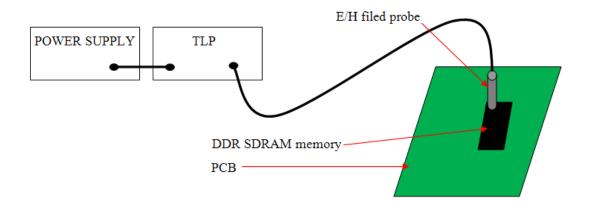

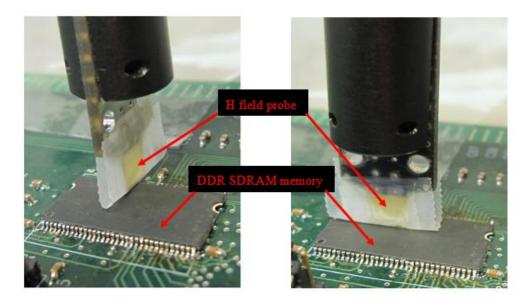

| Figure 6.1. Experimental setup for the test                                           | 64 |

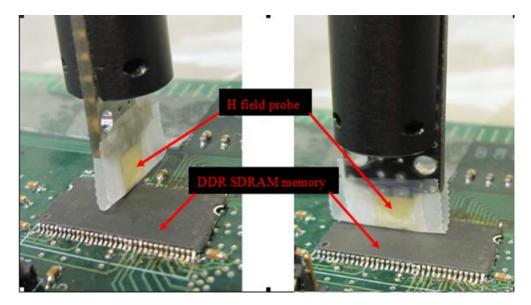

| Figure 6.2. H field probes used for manual scanning                                   | 65 |

| Figure 6.3. Manual scanning of DDR memory with H field probe in dual polarization.    | 66 |

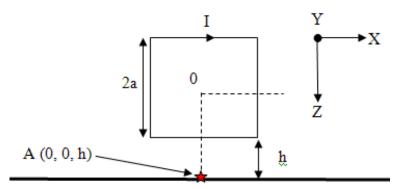

| Figure 6.4. Orientation of the magnetic field loop probe above the GND plane          | 66 |

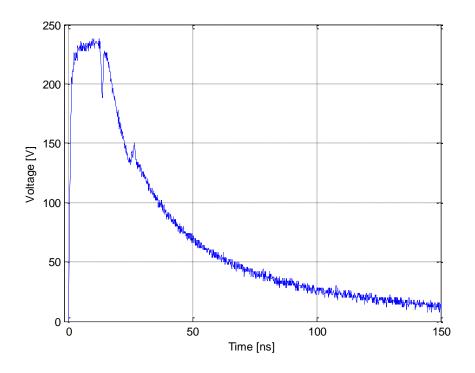

| Figure 6.5. TLP voltage waveform at 500 V charge voltage                              | 68 |

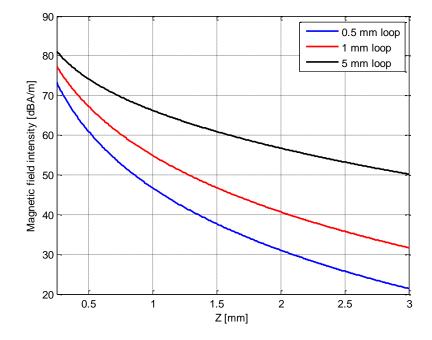

| Figure 6.6. H field strength vs Height above GND plane at TLP voltage of 0.5 kV       | 68 |

| Figure 6.7. Orientation of the magnetic field loop probe above the lead frame (1 mm). | 69 |

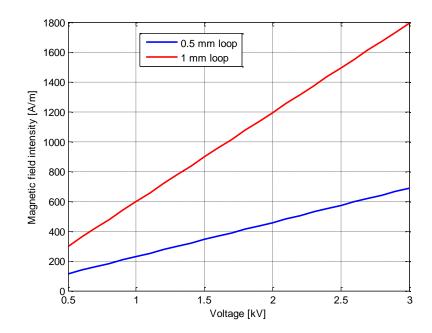

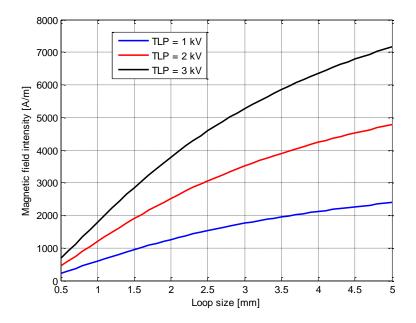

| Figure 6.8. H field strength vs TLP charge voltage at a height of the lead frame      | 71 |

| Figure 6.9. Variation of field strength vs loop size for different TLP voltages       | 71 |

| Figure 6.10. Computation of induced voltage on the lead frame for 0.5 mm loop         | 73 |

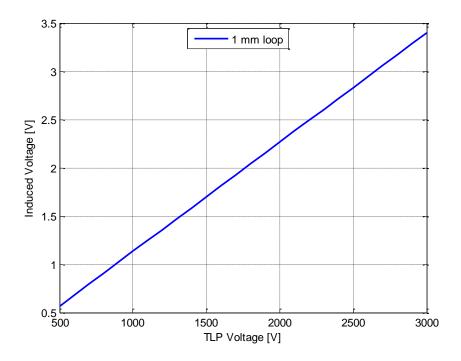

| Figure 6.11. Computation of induced voltage on the lead frame for 1 mm loop           | 73 |

| Figure 6.12. Computation of induced voltage on the lead frame for 5 mm loop74         | 1 |

|---------------------------------------------------------------------------------------|---|

| Figure 6.13. Induced voltage vs TLP voltage for 1 mm loop size                        | 5 |

| Figure 6.14. Manual scanning of DDR memory with H field probe in dual polarization 77 | 7 |

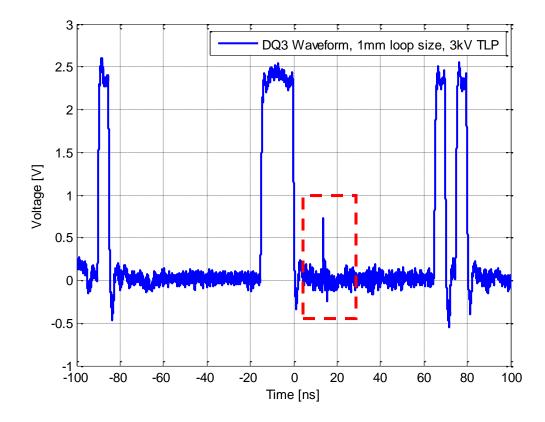

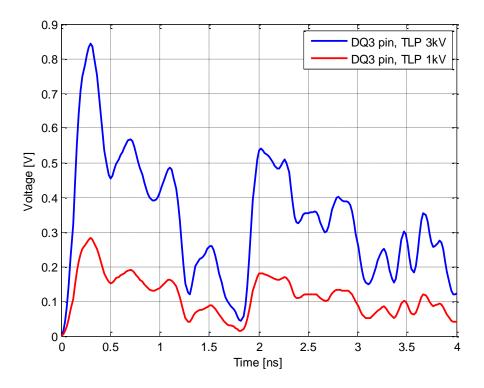

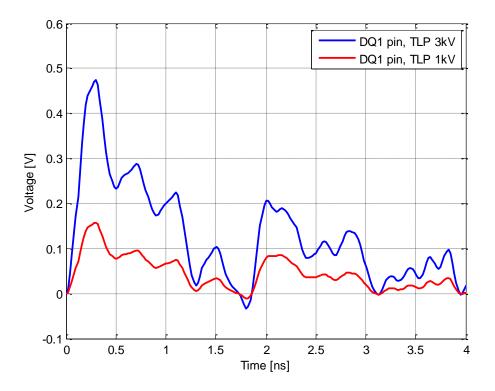

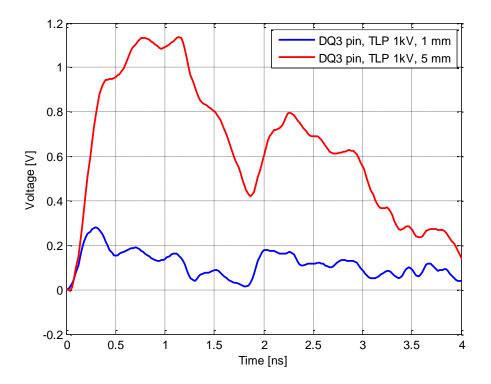

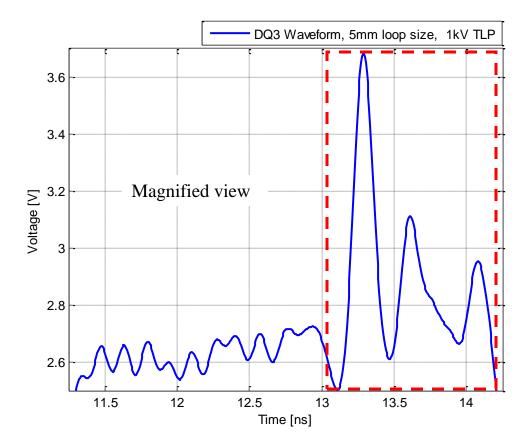

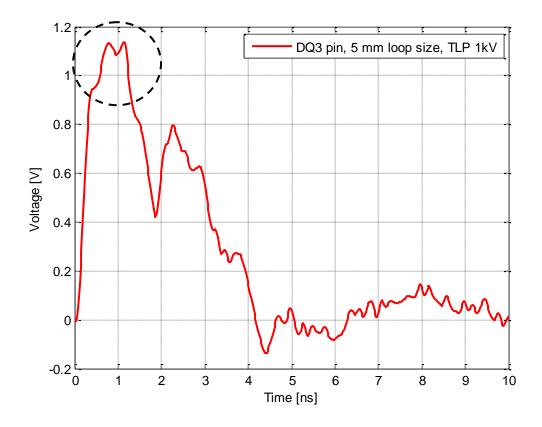

| Figure 6.15. Noise Voltage waveform on DQ3 pin for positive TLP pulse (3 kV)          | ) |

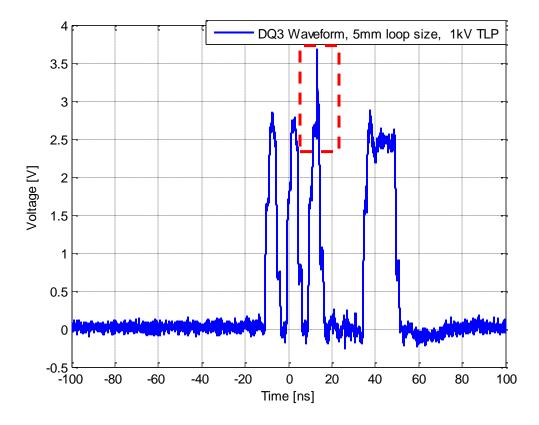

| Figure 6.16. Noise Voltage waveform on DQ3 pin for positive TLP pulse (1 kV)          | 1 |

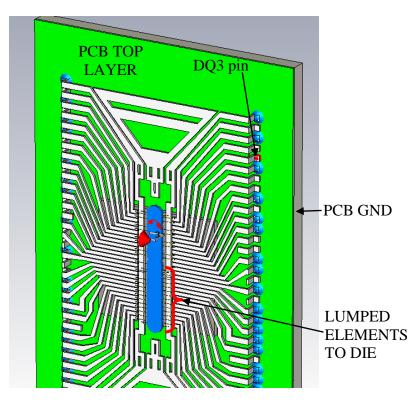

| Figure 6.17. Complete 3D model of the memory IC                                       | 2 |

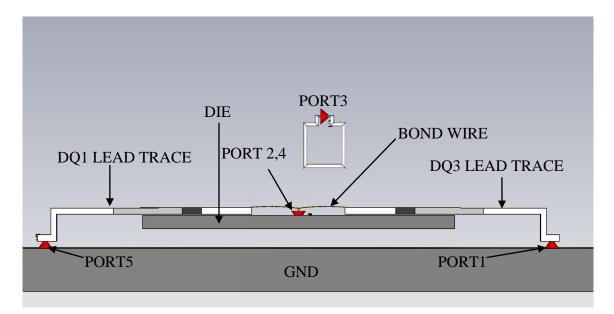

| Figure 6.18. Definition of ports and loop probe83                                     | 3 |

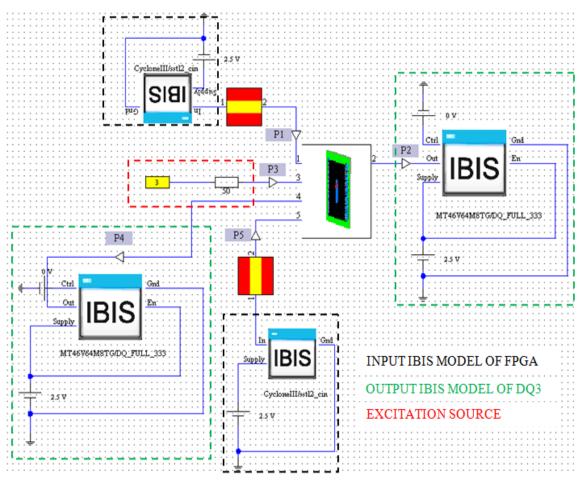

| Figure 6.19. Equivalent circuit in CST DS85                                           | 5 |

| Figure 6.20. Induced noise voltage at Probe 1 (DQ3 pin) of the memory IC              | 5 |

| Figure 6.21. Induced noise voltage at Probe 5 (DQ1 pin) of the memory IC              | 7 |

| Figure 6.22. Comparison of induced voltage at Probe 1 (DQ3 pin) for two loop sizes 88 | 3 |

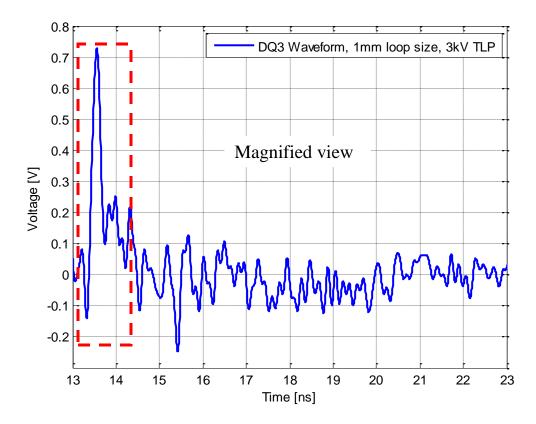

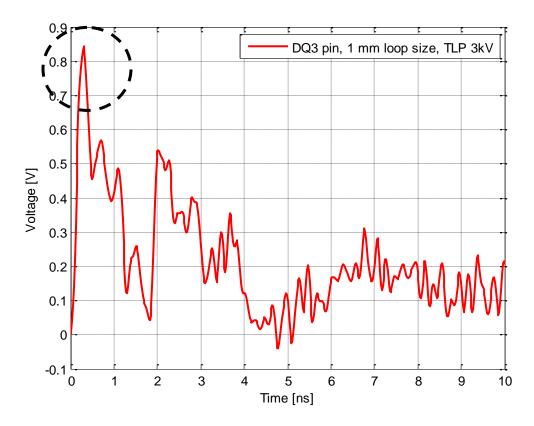

| Figure 6.23. Noise voltage waveform on DQ3 pin for positive TLP pulse (3 kV)          | ) |

| Figure 6.24. Simulated noise signal on the DQ3 pin with 1 mm loop probe               | ) |

| Figure 6.25. Noise voltage waveform on DQ3 pin for positive TLP pulse (1 kV)          | 1 |

| Figure 6.26. Simulated noise signal on the DQ3 pin with 5 mm loop probe               | 2 |

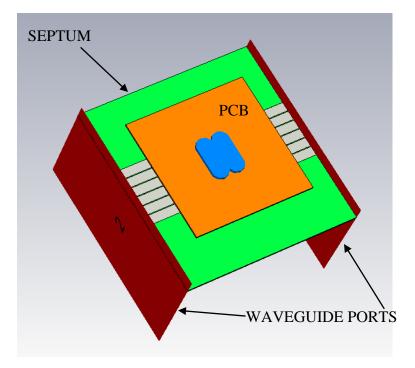

| Figure 7.1. Measurement setup for field injection via TEM cell                        | 1 |

| Figure 7.2. Measured voltage waveform on CKE pin                                      | 5 |

| Figure 7.3. Full-wave simulation model of TEM cell + IC                               | 7 |

| Figure 7.4. Simulated induced noise voltage signal on CKE pin97                       | 7 |

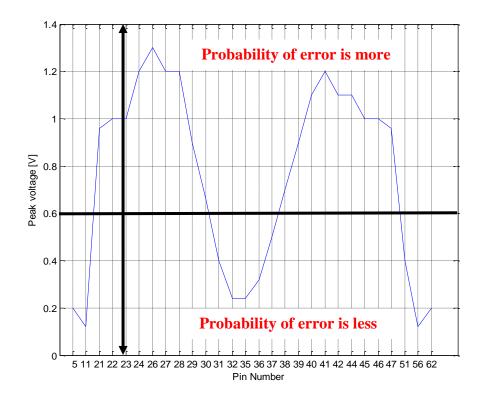

| Figure 7.5. Simulated pin voltage distribution on excitation by TEM cell              | 3 |

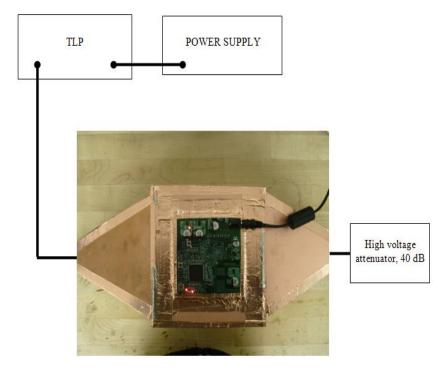

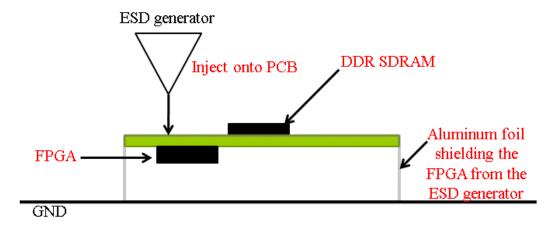

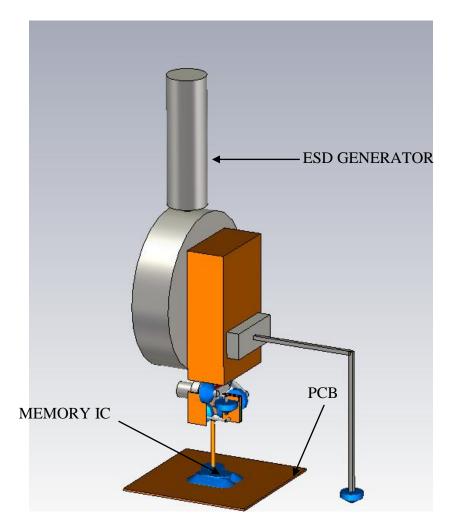

| Figure 8.1. ESD Discharge on the TEM cell board 100                                   | ) |

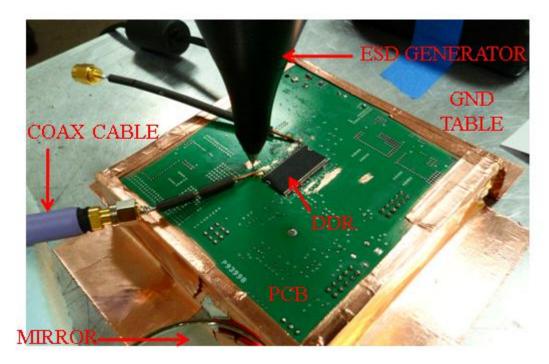

| Figure 8.2. Measurement of Induced noise voltage on DQ3 pin 102                       | 1 |

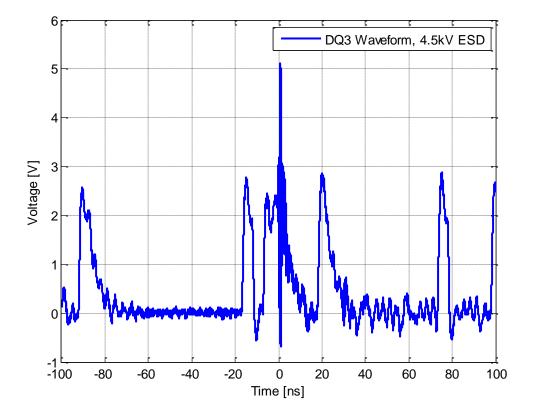

| Figure 8.3. Induced noise voltage on DQ3 pin at positive ESD charge voltage 102       | 2 |

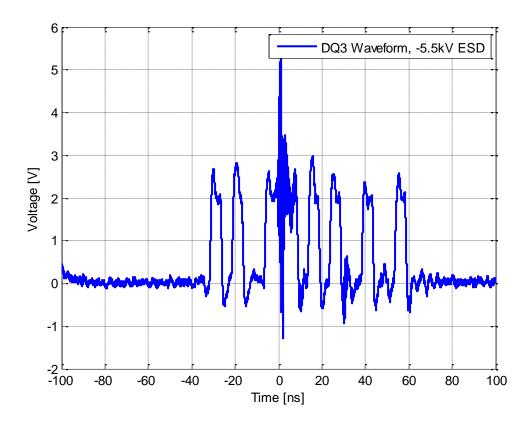

| Figure 8.4. Induced noise voltage on DQ3 pin at negative ESD charge voltage           | 3 |

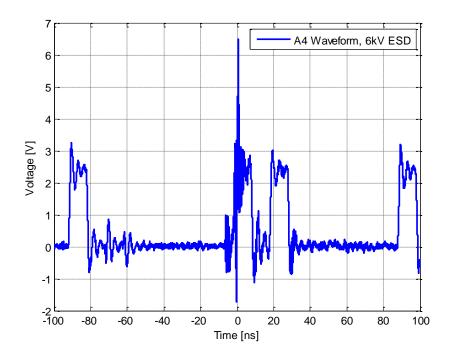

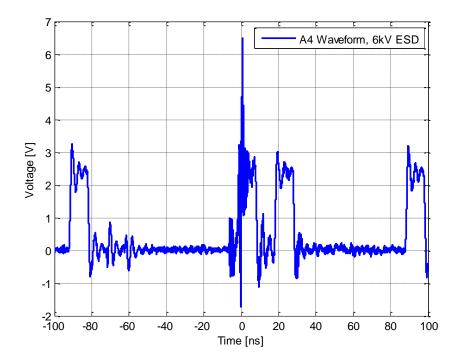

| Figure 8.5. Induced noise voltage on A4 pin at positive ESD charge voltage 104        | 1 |

| Figure 8.6. Induced noise voltage on A4 pin at negative ESD charge voltage 104        | 1 |

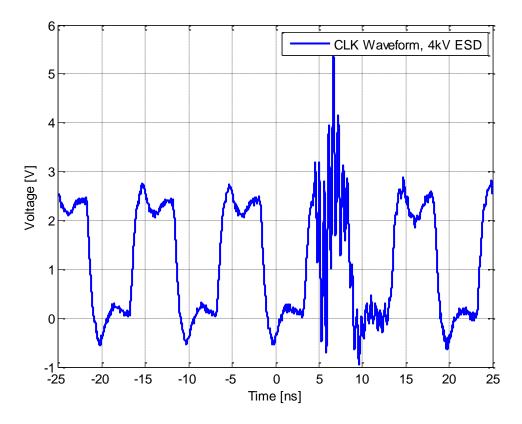

| Figure 8.7. Induced noise voltage on CLK pin at positive ESD charge voltage 105       | 5 |

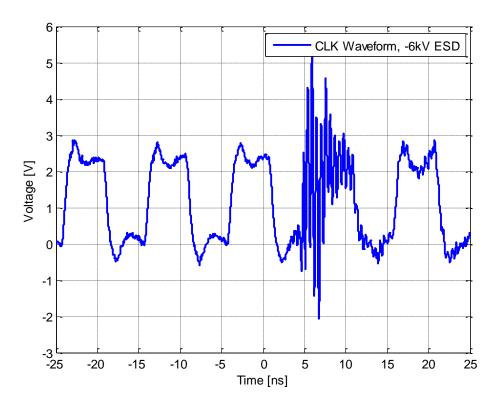

| Figure 8.8. Induced noise voltage on CLK pin at negative ESD charge voltage 106       | 5 |

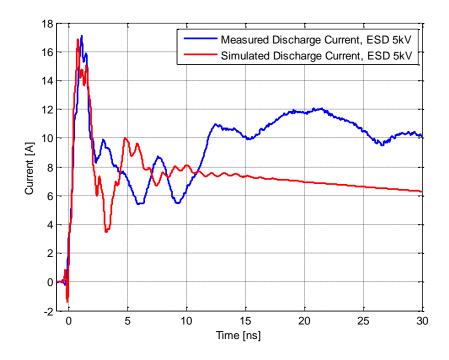

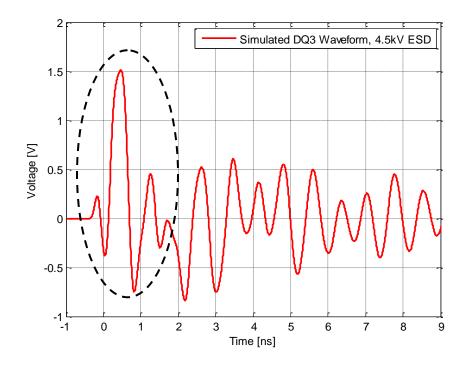

| Figure 8.9. Complete 3D model of the memory IC with the ESD generator 107             | 7 |

| Figure 8.10. Definition of Ports on DQ3 lead trace 108                                | 3 |

| Figure 8.11. Comparison of ESD discharge current at 5kV 109                           | ) |

| Figure 8.12. Simulated induced noise signal on DQ3 pin 109                              |

|-----------------------------------------------------------------------------------------|

| Figure 8.13. Simulated pin voltage distribution on excitation by ESD generator 111      |

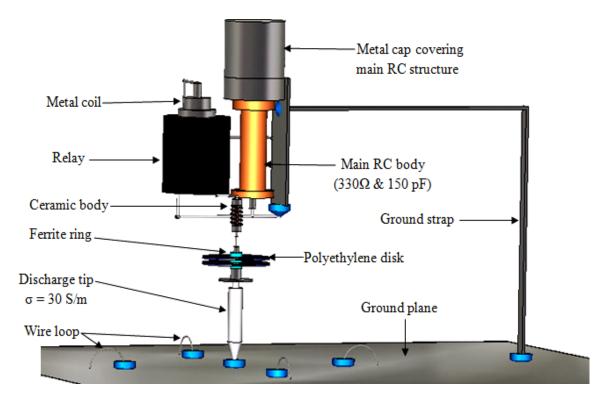

| Figure 9.1. ESD generator geometry in full wave simulation 116                          |

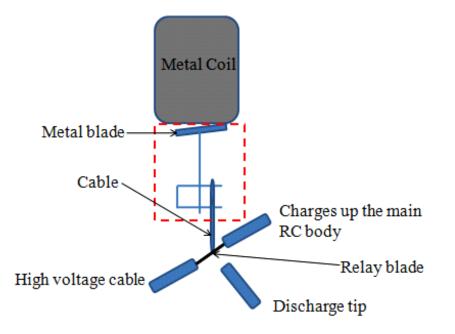

| Figure 9.2. State of the relay during charging process                                  |

| Figure 9.3. State of the relay during discharge process                                 |

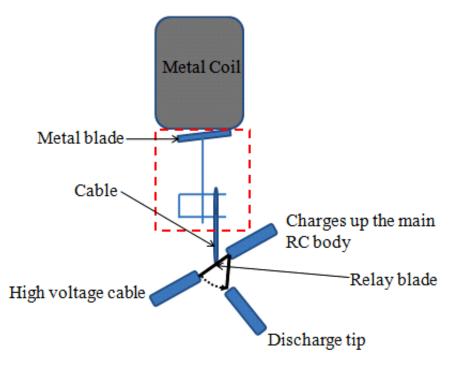

| Figure 9.4. An internal view of the relay                                               |

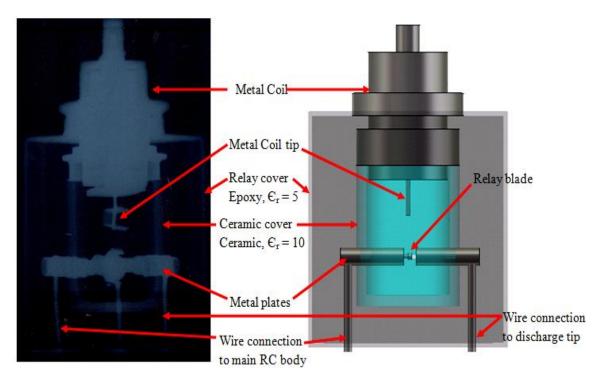

| Figure 9.5. Excitation signal on the port                                               |

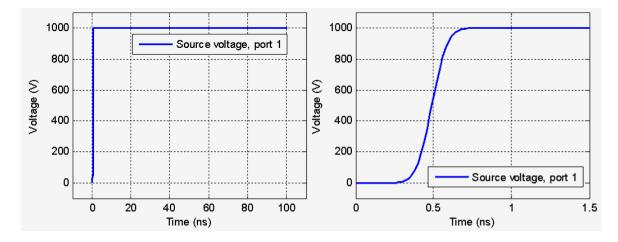

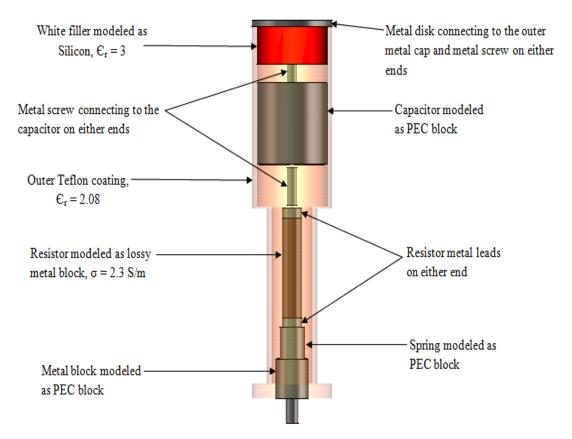

| Figure 9.6. Internal view of the main discharging capacitor and resistor body 121       |

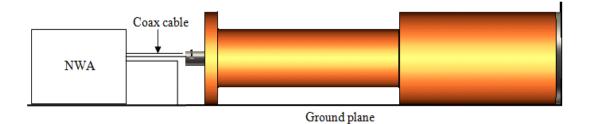

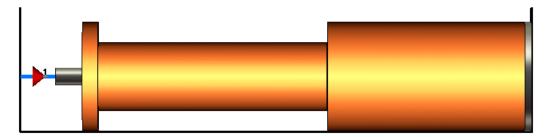

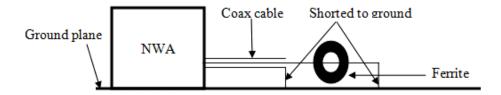

| Figure 9.7. Experimental setup for measuring Z11 of R-C body 122                        |

| Figure 9.8. Frequency domain CST model of the main R-C body 122                         |

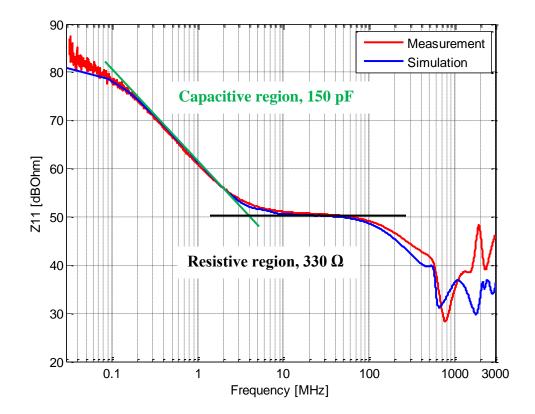

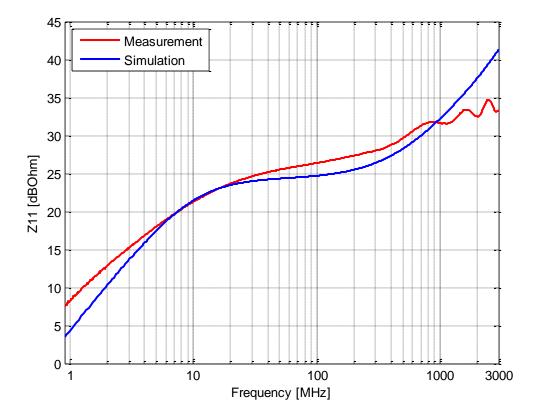

| Figure 9.9. Comparison of measured and simulated Z11 for the main R-C body 123          |

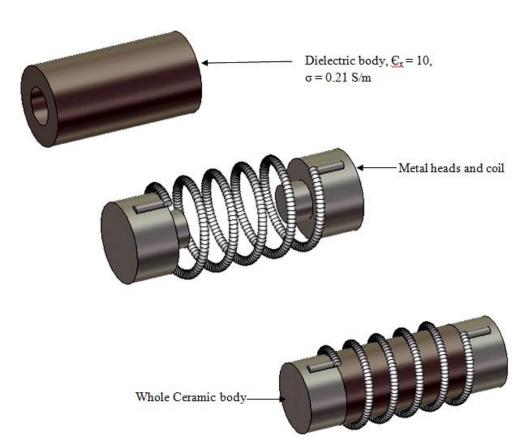

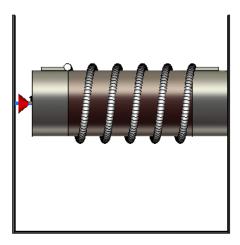

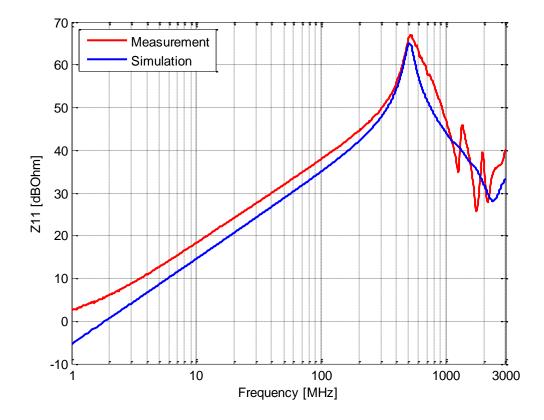

| Figure 9.10. Different parts of the ceramic body developed in multiple steps 124        |

| Figure 9.11. Experimental setup for measuring Z11 of ceramic body 125                   |

| Figure 9.12. Equivalent frequency domain model of the ceramic body in CST 125           |

| Figure 9.13. Comparison of Z11 of the ceramic body 126                                  |

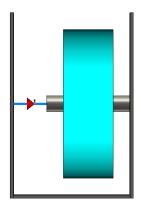

| Figure 9.14. Experimental setup for measuring Z11 of ferrite                            |

| Figure 9.15. Equivalent frequency domain model of the ferrite ring in CST 127           |

| Figure 9.16. Comparison of Z11 of the ferrite ring 128                                  |

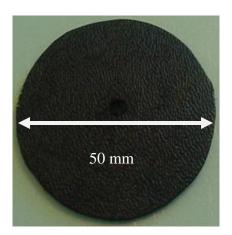

| Figure 9.17. Picture of the polyethylene disk 129                                       |

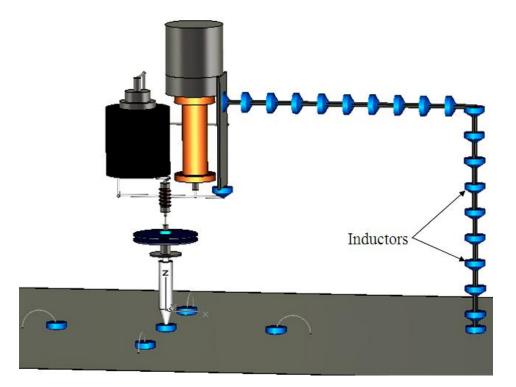

| Figure 9.18. ESD generator geometry in full wave simulation                             |

| Figure 9.19. ESD generator with long ground strap in full wave simulation 131           |

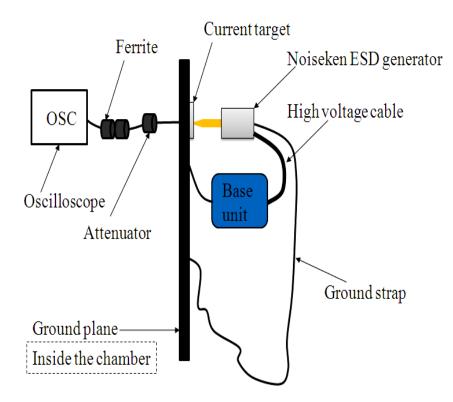

| Figure 9.20. Measurement setup to measure the ESD discharge current                     |

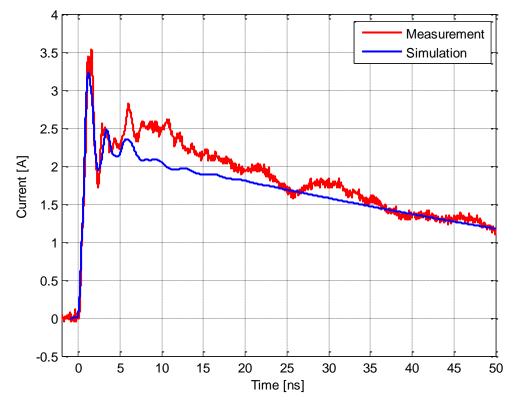

| Figure 9.21. Comparison of discharge current for short ground strap                     |

| Figure 9.22. Comparison of discharge current for long ground strap                      |

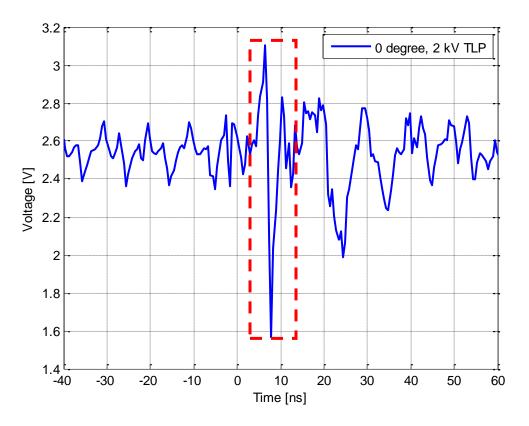

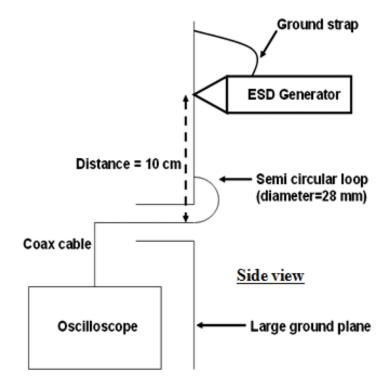

| Figure 9.23. Experimental setup for induced loop voltage measurement                    |

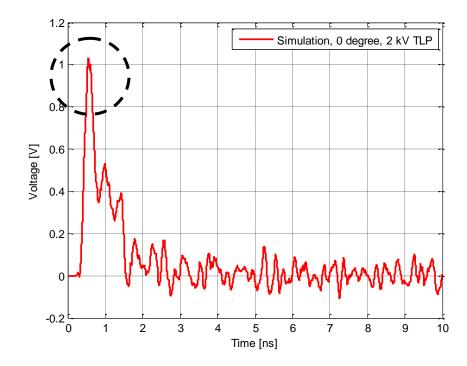

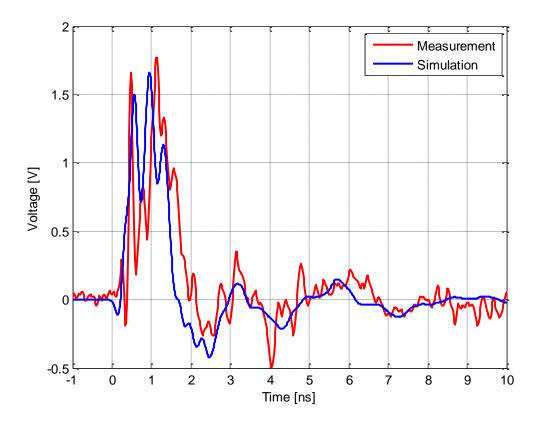

| Figure 9.24. Comparison of induced loop voltage at 10 cm and 0 degree orientation 136   |

| Figure 9.25. Comparison of spectrum of the loop voltage at 10 cm and 0 degree 137       |

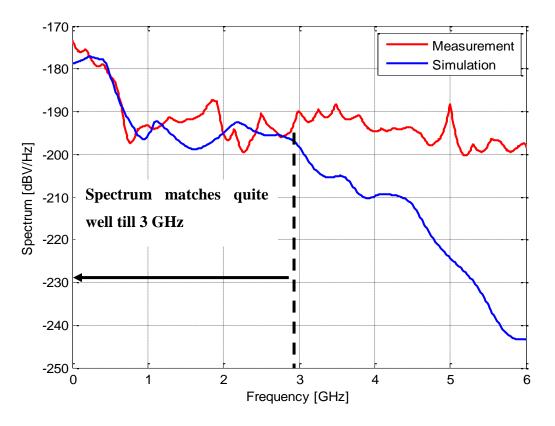

| Figure 9.26. Comparison of induced loop voltage at 40 cm and 270 degree orientation 138 |

| Figure 9.27. Comparison of spectrum of the loop voltage at 40 cm and 270 degree 138     |

## LIST OF TABLES

|                                                                              | Page |

|------------------------------------------------------------------------------|------|

| Table 2.1. Truth table for operation of the IC                               | 5    |

| Table 2.2. Truth table for operation of the IC                               | 8    |

| Table 2.3. Repeatability of ESD test on discharge to board for slow IC       | 15   |

| Table 2.4. Repeatability of ESD test on discharge to board for fast IC       |      |

| Table 3.1: Equivalent modeling of individual components                      |      |

| Table 4.1. Functionality of the LEDs                                         |      |

| Table 6.1. Manual scanning results for 5 mm H field loop probe               | 77   |

| Table 6.2. Manual scanning results for 1 mm H field loop probe               | 78   |

| Table 6.3. Manual scanning results for 0.5 mm H field loop probe             | 79   |

| Table 8.1. Comparison of results for H field loop probe                      |      |

| Table 8.2. Comparison of field strength for three field injection techniques | 113  |

| Table 9.1. Parameters of the ferrite ring modeled in CST                     |      |

## 1. INTRODUCTION

Electrostatic discharge (ESD) can damage or disrupt a system by injecting currents or by their associated transient fields. Getting an understanding of the underlying reason, such as the coupling paths can not only help resolve ESD issues, but can also be used to estimate ESD performance. Study of system level ESD disturbances has been approached from mainly two different directions, circuit modeling [1], [2], [3] or full wave numerical simulation of currents and fields from an ESD generator [4], [5], [6], [7], [8], [11]. Transient fields from ESD events can either couple directly to the lead frame and bond wires in ICs or indirectly through strong coupling structures such as flex cable PCBs therby causing soft errors in ICs. Soft errors are typically defined as logical errors which cause failures in operation of the IC and can be cured at least by resetting the system.

The adopted approach is to develop a complete simulation model which includes the ESD generator model, the passive DUT structure and IC response models to predict ESD related soft errors in ICs caused due of coupling via electromagnetic fields.

This thesis describes two distinct co-simulation strategies whereby a full wave model of the generator is combined with a simple model of an IC represented as a low pass filter to predict voltages and currents via coupling through a passive structure such as a flex cable PCB. The investigation further moves on to modeling the IC in greater detail with the lead frame structure, bond wires and the use of IBIS models to simulate induced noise voltages and currents on the IC pin. The development covers definition of the test platforms; modeling and verification of the of the flex cable and PCB geometry in frequency domain and subsequent combination with the ESD generator model in time domain; combining full wave simulation result with simple IC model in SPICE to predict soft errors; detailed modeling of the IC including geometry and equivalent IBIS models of various pins; correlation of measured and simulated voltages at the IC pins for three different field injection techniques, loop probes, TEM cell and the ESD generator.

The last section of the thesis gives a detailed full wave model of a commercially available ESD generator in CST MWS and verification of the model with regard to discharge current and induced loop voltage waveform.

## 2. EXPERIMENTAL INVESTIGATION OF ESD COUPLING TO IC VIA FLEX CABLE PCB

Real world commercial products often consists of a system of flex cable connected PCBs. The victim IC is maybe mounted on one PCB and is connected via a signal trace on another PCB by a flex cable. The flex cable is a very strong coupling region to ESD. An ESD discharge on the first PCB is not only accompanied by the spread of the discharge current throughout the system but also by the fast changing transient electromagnetic fields. These field components can couple onto the flex cable and drive a common mode current through it thereby leading to a soft error in the IC mounted on the other PCB. The objective of this research concentrates on proposing a simulation strategy to model the flex cable with the interconnected PCBs via a full wave simulation tool and simulate the voltage at the IC input in response to ESD discharge onto the board. This section details the test platform used for our purpose and the soft error failure levels of the IC in response to ESD coupling via the flex cable structure.

### 2.1 DEFINITION OF TEST PLATFORM

The test platform includes an IC mounted on one PCB (Board 2) which is connected to another PCB (Board 1) via a flex cable structure. Two distinct PCB geometries with separate circuit schematics are used for testing two different types of ICs. The test PCB is a 4 layer board. The stack up configuration of the boards are as follows,

•Layer 1: Signal, Power traces and Ground fill

•Layer 2: Solid Ground

## •Layer 3: Empty

## •Layer 4 : Solid Ground

The boards are equipped with SMA connectors and current measurement loops embedded underneath the trace connecting to the CLK pin of the IC to measure the voltages and currents at the IC input. The IC's used for our purpose are D-type flip flops from Potatosemi and ON Semiconductor, thus, they detect noise events that surpass their input low-high transition definition on the CLK pin. They are available in two different speed classes: 600 MHz CMOS and 8 GHz SiGe. The two classes of ICs are classified as slow and fast ICs for identification purpose. The circuit diagram of the slow IC mounted on the board is shown in Figure 2.1.

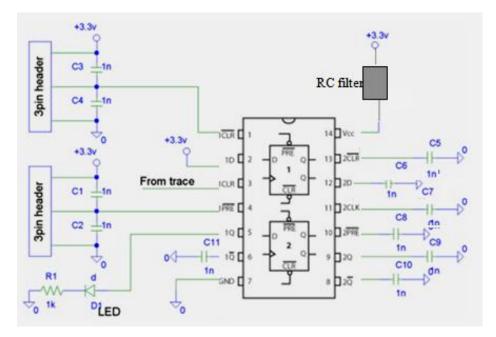

Figure 2.1. Circuit diagram of the slow IC mounted on the PCB

Some of the specifications of the slow IC are as follows,

- Operating frequency is faster than 600MHz

- VCC Operates from 1.65V to 3.6V

- Propagation delay < 2ns max with 15pf load

- Input capacitance: 4pF

- Voltage at input pin for logic high level: 2-5 V

The various operating states of the IC are shown in Table 2.1.

| Table 2.1. Truth table for operation of the IC | Table 2.1. | Truth table | for o | peration | of the IC |

|------------------------------------------------|------------|-------------|-------|----------|-----------|

|------------------------------------------------|------------|-------------|-------|----------|-----------|

| D'  | D   |     |       |  |

|-----|-----|-----|-------|--|

| Pin | Des | cru | otion |  |

|     |     | ~   |       |  |

| [ |     | INPL | JTS |   | OUT              | PUTS | ٦ |

|---|-----|------|-----|---|------------------|------|---|

|   | PRE | CLR  | CLK | D | Q                | ō    | 1 |

|   | L   | н    | х   | х | н                | L    | 1 |

|   | н   | L    | х   | х | L                | н    | I |

|   | L   | L    | х   | х | H <sup>(1)</sup> | H(1) |   |

| Π | н   | н    | î   | н | н                | L    | Τ |

|   | н   | н    | î   | L | L                | н    | T |

|   | н   | н    | L   | х | Q <sub>0</sub>   | ۵o   | I |

The IC is operated in the state marked by the blue box. The layout of the IC on the board is shown in Figure 2.2.

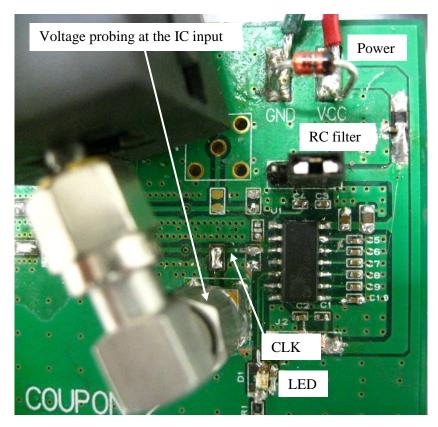

Figure 2.2. Photo of the IC and various components on the PCB

The IC is powered from a DC power supply at 3.3 V. A 3.3 V Zener diode is placed across the power supply to protect the IC against over voltage. An RC filter is also mounted on the power trace to block RF signals propagating into the power pin of the IC. Voltage at the IC CLK input is measured from an SMA connector mounted close to the IC. An SMT LED is mounted to observe state of the output pin in response to voltage pulses on the CLK pin. The circuit diagram of the fast IC mounted on the board is shown in Figure 2.3.

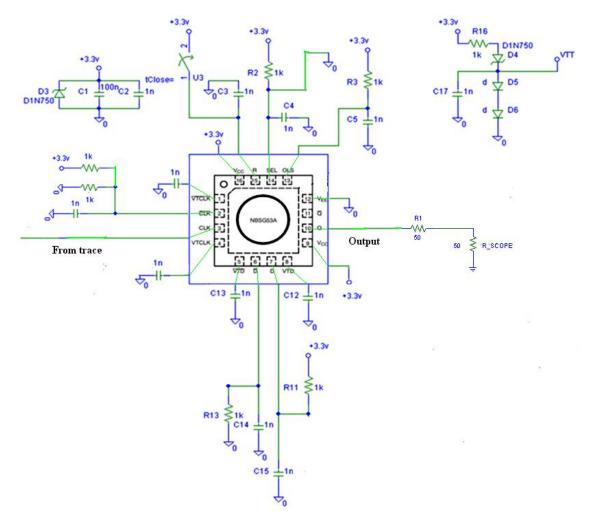

Figure 2.3. Circuit diagram of the IC mounted on the PCB

Some of the specifications of the IC are as follows,

- Operating frequency is faster than 8GHz

- VCC Operates from 2.375V to 3.465V

- D Flip-flop mode, DFF (Active with Select High)

- 50 Internal Input Termination Resistors on all Differential Inputs

- Selectable Output Level, OLS = VCC (800 mV Peak-to-Peak Output)

The various operating states of the IC are shown in Table 2.2.

| R | SEL | D | CLK | Q | Function |  |

|---|-----|---|-----|---|----------|--|

| н | х   | х | х   | L | Reset    |  |

| L | н   | L | Z   | L | DFF      |  |

| L | Н   | Н | Z   | Н | DFF      |  |

| L | L   | х | Z   | α | DIV/2    |  |

Table 2.2. Truth table for operation of the IC

Z = LOW to HIGH Transition

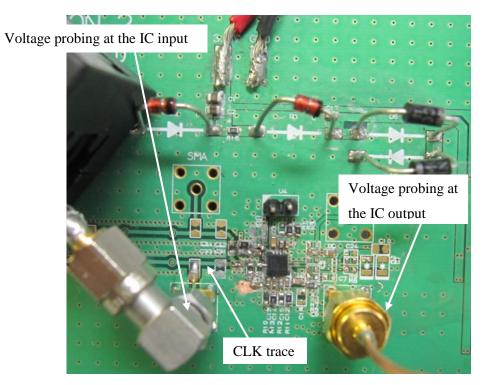

The IC is operated in the state marked by the blue box. The layout of the IC on the board is shown in Figure 2.4.

Figure 2.4. Photo of the IC and various components on the PCB

### 2.2 CHARACTERIZATION OF IC

Characterization of both the ICs is performed with respect to voltage at the IC input vs pulse width. The objective of this test is to determine the speed of response at the IC input. The IC input can then be represented as an equivalent low pass filter followed by a threshold detector in circuit simulation for subsequent co-simulation with full wave simulation results. Both the ICs are mounted on individual PCB test boards and Transmission line pulses (TLP) of varying magnitude and pulse widths are injected into the CLK trace of the IC while observing the response at the output (Q). At the time of failure, the voltage at the IC is measured to obtain the desired curve. The failure threshold curve for the ICs obtained from the above information shows the input response to different pulse widths.

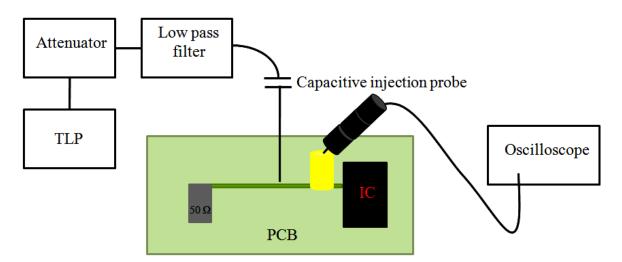

**2.2.1 Measurement setup.** The measurement setup is shown in Figure 2.5.

Figure 2.5. Measurement setup for characterization of the IC

The signal trace on the PCB is terminated with 50  $\Omega$  resistor on one end and the CLK pin of the IC on the other end. The low pass filter following the TLP generator modulates the original TLP pulse and generates pulses of varying magnitude and pulse widths which is injected via a capacitive probe (C = 1pF) onto the CLK signal trace at the input of the IC. At the instant when the IC triggers, voltage pulses at the IC input are recorded on an oscilloscope. A high voltage attenuator of 22 dB is used depending upon the charge voltage of the TLP generator.

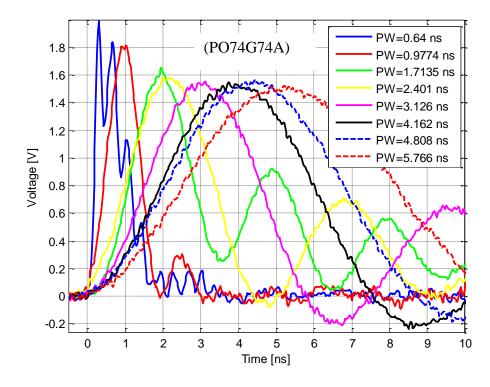

**2.2.2 Measurement results.** Figure 2.6 shows the different voltage waveforms measured at the input of the slow IC (PO74G74A). The failure threshold curve for the slow IC is obtained from Figure 2.6 and is shown in Figure 2.7.

Figure 2.6. Pulses of varying magnitude and pulse width at the slow IC input

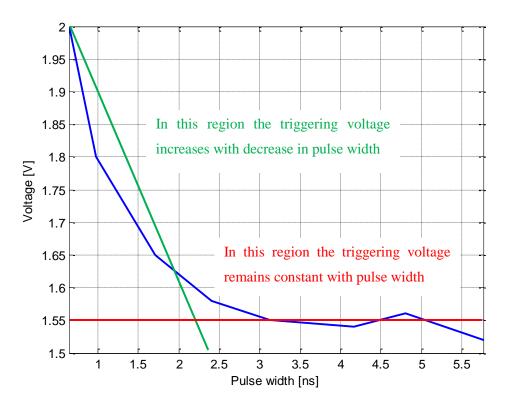

Figure 2.7. Voltage at the slow IC input vs Pulse width

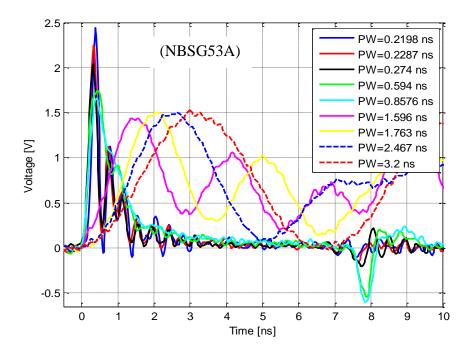

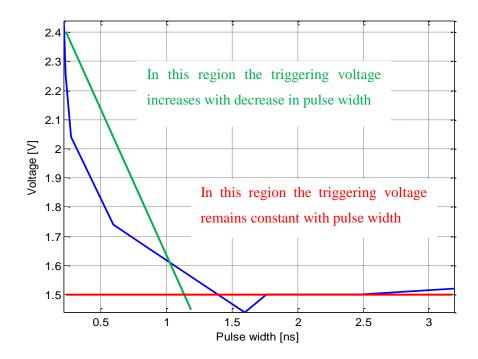

The failure threshold curve is used to model the input structure of the IC in SPICE. From Figure 2.6 and Figure 2.8 one observes that different low pass filters gives rise to different rise times and pulse widths of the injected TLP pulse. The pulse width is defined at 50 % of the magnitude of the pulse. In the region marked by the red line the triggering voltage remains fairly constant with increase in pulse width. However as the pulse width becomes narrow the voltage required to trigger the IC goes up. The same characterization procedure is performed on the fast IC (NBSG53A) as well. Figure 2.8 shows the different voltage waveforms measured at the input of the fast IC. The failure threshold curve is shown in Figure 2.9.

Figure 2.8. Pulses of varying magnitude and pulse width at the fast IC input

Figure 2.9. Voltage at the fast IC input vs Pulse width

Comparing Figure 2.7 and Figure 2.9, the curve for the fast IC starts rising at a much lower pulse width (<1 ns) in comparison to the slow IC (<2 ns). This agrees with the expectation that the faster IC (NBSG53A) is in fact faster than the slower IC (PO74G74A). One would expect to see the speed of response of both the ICs to be in the ratio of  $\sim$  1:10. However it is not reflected exactly from the threshold curves of the ICs. One of the reasons for that could be because of the fact that the speed of response of the ICs may not necessarily correlate to with the speed of the IC due to different technologies associated with both of them.

#### 2.3 ESD IMMUNITY OF ICs

The objective of this experiment is to document the crash levels of both the ICs for different ESD charge voltages. The test case is an IC mounted on one PCB (Board 2) which is connected to another PCB (Board 1) via a flex cable. The crash levels of the IC attached to the CLK trace in flex cable setup is determined experimentally by injecting ESD pulses on PCB Board 1. Simultaneously the voltage at the IC input is recorded at the instant of failure.

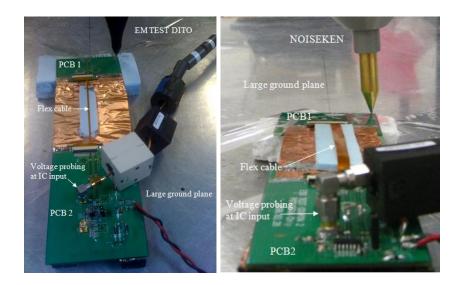

**2.3.1. Measurement setup.** The immunity of the ICs has been determined for two different ESD generator models: EM TEST DITO & NOISEKEN. The ESD generators are discharge on the edge of PCB1. The reason to choose the edge is because in commercial products the chances of an ESD discharge at the edge of PCB structures is relatively more than to the center. The IC is mounted on PCB 2 which is grounded to the large ground plane and PCB 1 is floating above the ground plane. Both the ESD generators are discharged on PCB 1 at a fixed position (2 mm x 2 mm from the edge of

the board, PCB1). On discharge the triggering voltage at the IC input is recorded in an oscilloscope. A 20 dB attenuator and a power limiter is used in front of the oscilloscope as an over voltage protection device. The signal trace on PCB 1 connecting to the CLK trace on PCB2 via the flex cable is terminated with 50  $\Omega$ . The three traces on the flex cable are in SIGNAL-GROUND-FLOATING configuration. Figure 2.10 shows the measurement setup of ESD discharge on to the boards.

Figure 2.10. Measurement setup with ESD discharge on board

The flex cable is mounted on the boards via connectors. The flex cable is a single layer type with 40 traces on it. Only three traces are included in the measurement setup to reduce the complexity of modeling all the traces in the flex cable structure. The whole setup is mounted on an ESD table. The oscilloscope is housed inside a metal chamber to prevent direct coupling of the ESD generator to the ports of the instrument. To further improve shielding from the ESD generator, a semi rigid cable loaded with ferrites is used to measure the voltage at the IC input at the time of discharge.

**2.3.2. Measurement results.** It is a known fact that with ESD measurements there is always an issue with repeatability of results. Hence it is very important to establish the repeatability of test results before moving on further.

| EM-TEST<br>DITO  | 0.7 kV           | 0.8 kV                      | 1 kV                 |

|------------------|------------------|-----------------------------|----------------------|

| NOISEKEN         | 0.7 kV           | 0.8 kV                      | 0.9 kV               |

| 00               | Does not trigger | Triggers, Repeatable        | Triggers, Repeatable |

|                  | Does not trigger | Does not trigger            | Triggers, Repeatable |

| 90 <sup>0</sup>  | Does not trigger | Triggers,<br>Not Repeatable | Triggers, Repeatable |

|                  | Does not trigger | Triggers, Repeatable        | Triggers, Repeatable |

| 180 <sup>0</sup> | Does not trigger | Triggers, Repeatable        | Triggers, Repeatable |

|                  | Does not trigger | Triggers, Repeatable        | Triggers, Repeatable |

| 270 <sup>0</sup> | Does not trigger | Triggers, Repeatable        | Triggers, Repeatable |

|                  | Does not trigger | Does not trigger            | Triggers, Repeatable |

Table 2.3. Repeatability of ESD test on discharge to board for slow IC

From the above table, the crash level for the slow IC is in between 0.8 kV and 1 kV. An interesting observation is the sensitivity of the IC to the orientation of the ESD generator. At lower ESD charge voltage levels the IC triggers for some orientations of the generator and in others not. This suggests that the orientation of the pulse forming

network inside the ESD generator is such that there is more coupling of fields from the generator to the flex cable structure for some orientations making the IC more sensitive with regard to ESD discharge. Hence for reproducibility of results the voltage waveforms at the IC input were measured at 1 kV for both the ESD generators.

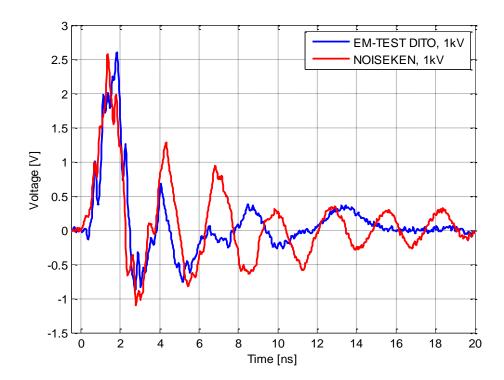

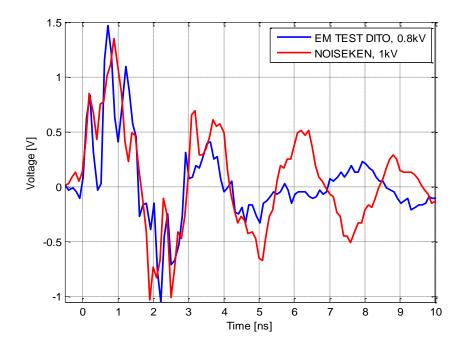

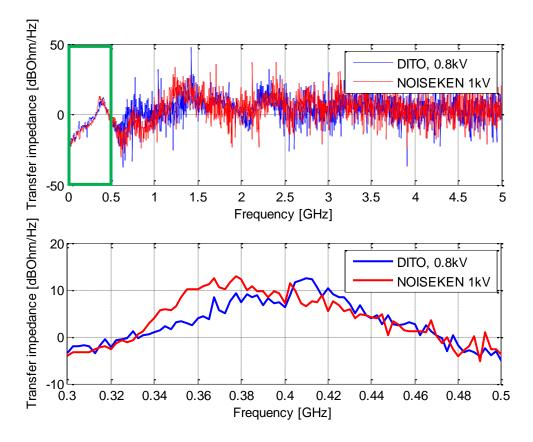

Figure 2.11 shows the voltage waveforms measured at the slow IC input for the two different ESD generators (at  $0^{\circ}$  orientation) when the IC triggers at 1kV.

Figure 2.11. Comparison of voltage at the IC input for discharge onto the board

The data is measured on the oscilloscope with a sampling frequency of 20 GS/s. One notices a ringing a frequency of  $\sim 0.4$  GHz (2.5 ns) in the voltage waveform at the IC

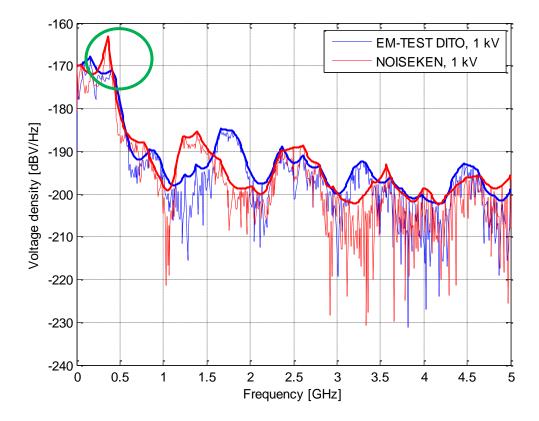

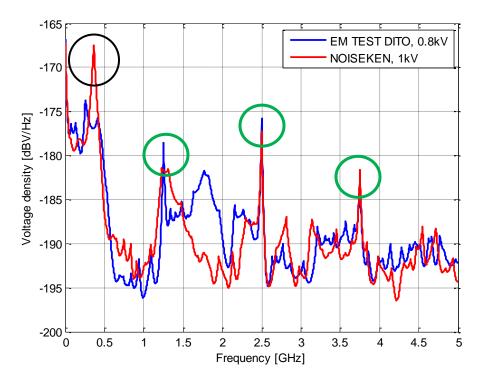

input for the NOISEKEN generator. A spectrum analysis of the above voltage waveform shown in Figure 2.12 also validates that fact.

Figure 2.12. Comparison of frequency spectrum of voltage at IC input

The above figure shows the frequency domain comparison of the voltage waveforms at the IC input from two different ESD generators. The resonance peak at 0.4 GHz (indicated by the green circle) corresponds to the ringing noticed in the time domain voltage waveform. This peak is caused due to the coupling from the flex cable. Above 3 GHz the spectrum does not make any sense and is just noise. The reason one does not see

the resonance peak for the EM TEST DITO generator could be because of the fact that there is a null in the frequency spectrum of the generator which cancels out the resonance from the flex cable coupling.

Table 2.4 shows the repeatability of the ESD test during discharge with both the ESD generator for the fast IC.

| EM-TEST<br>DITO  | 0.6 kV                      | 0.7 kV                      | 0.8 kV               |

|------------------|-----------------------------|-----------------------------|----------------------|

| NOISEKEN         | 0.8 kV                      | 0.9 kV                      | 1 kV                 |

| 00               | Does not trigger            | Triggers,<br>Not Repeatable | Triggers, Repeatable |

|                  | Triggers,<br>Not Repeatable | Triggers,<br>Not Repeatable | Triggers, Repeatable |

| 90 <sup>0</sup>  | Does not trigger            | Triggers,<br>Not Repeatable | Triggers, Repeatable |

|                  | Does not trigger            | Triggers,<br>Not Repeatable | Triggers, Repeatable |

| 180 <sup>0</sup> | Does not trigger            | Triggers, Repeatable        | Triggers, Repeatable |

|                  | Does not trigger            | Triggers,<br>Not Repeatable | Triggers, Repeatable |

| 270 <sup>0</sup> | Triggers, Repeatable        | Triggers, Repeatable        | Triggers, Repeatable |

|                  | Triggers, Repeatable        | Triggers, Repeatable        | Triggers, Repeatable |

Table 2.4. Repeatability of ESD test on discharge to board for fast IC

At intermediate voltages between 0.6 kV and 0.7 kV (for EM-TEST DITO) and 0.8 kV and 0.9 kV (for NOISEKEN), the IC triggers for some orientations of the

generator and in others not. Especially it triggers for the 270 degree orientation, which suggest that the orientation of the pulse generator (inside the ESD generator) at 270 degree is such that there is more coupling of the fields from the generator to the flex cable structure making the IC more sensitive with regard to ESD discharge. So for discharge to board one can say that the ESD failure level of the IC is between 0.7 kV and 0.8 kV when the EM TEST DITO generator is used and 0.9 kV to 1 kV when the NOISEKEN generator is used.

Figure 2.13 shows the voltage waveforms measured at the fast IC input for the two different ESD generators (at  $0^{\circ}$  orientation).

Figure 2.13. Comparison of voltage at the IC input for discharge onto the board

The data is measured on the oscilloscope with a sampling frequency of 10 GS/s. Ideally it is always recommended to take measurements with the sampling frequency set to 20 GS/s or more if available to capture the high frequency components accompanying a discharge. One notices a ringing a frequency of ~0.4 GHz (2.5 ns) in the voltage waveform at the IC input for the NOISEKEN generator. A spectrum analysis of the above voltage waveform validates that fact. The original spectrum of the voltage waveform is processed using a function called "Connect\_extremes". The function is basically a square running average filter which either finds an average of the maximas or minimas of a curve. Figure 2.14 shows the plot of the average of the maximas in the frequency spectrum of the voltage waveform.

Figure 2.14. Comparison of frequency spectrum of voltage at IC input

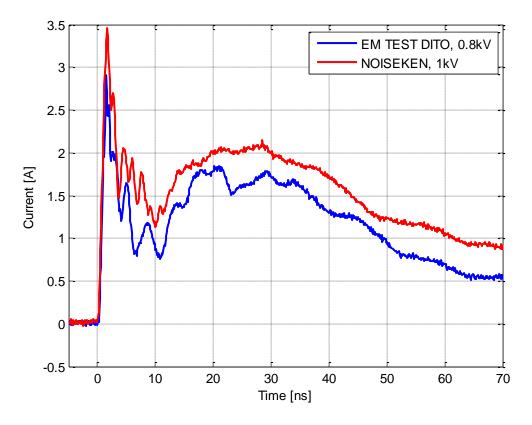

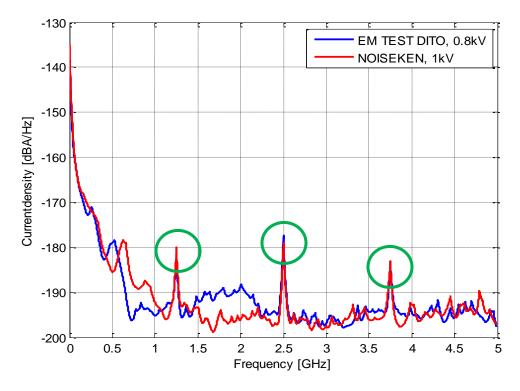

The above figure shows the frequency domain comparison of the voltage waveforms at the IC input from two different ESD generators. We notice resonance peaks at 1.25, 2.5 and 3.75 GHz. These are not actually resonances but artifacts of the AD convertor in the oscilloscope. The artifacts appear in the voltage spectrum for both the ESD generators. The resonance at 0.4 GHz for the NOISEKEN generator is caused due to the coupling from the flex cable. A comparison of the discharge current when the generator is discharged on to the board is measured using an F2000 current clamp and is shown in Figure 2.15. A comparison of the spectrum of the discharge current for the two ESD generators is shown in Figure 2.16.

Figure 2.15. Comparison of discharge current onto board

Figure 2.16. Comparison of spectrum of the discharge current onto board

The artifacts at 1.25, 2.5 and 3.75 GHz appear in the discharge current spectrum for both the ESD generators as well. To formulate an expectation of the peak voltage at the IC input for the frequency of interest one can look at the transfer impedance between the discharge point and the IC input. The transfer impedance ( $Z_T$ ) gives the information on how much of spectral content of the discharge current is transferred to the IC input. It is defined as the voltage at the IC input divided by the discharge current from the ESD generator i.e.

$Z_{T\_Linear}$  ( $\Omega/Hz$ ) = Voltage at IC input (V/Hz)/Discharge current (A/Hz)

$Z_{T\_Log} \left( dB\Omega / Hz \right)$  = Voltage at IC input (dBV/Hz) - Discharge current (dBA/Hz)

Figure 2.17 shows the comparison of the transfer impedance for both the ESD generators when discharged on the board (PCB1). The thing to consider however is, the transfer impedance makes sense only in those regions where both the current density and voltage density spectrum makes sense.

Figure 2.17. Transfer impedance for discharge on to the board

One of the frequencies of interest is the resonance peak at 0.4 GHz caused due to the coupling of the flex cable. In case of the EM-TEST DITO at 0.4 GHz the transfer impedance is 6 dB $\Omega$  which implies that for 1A of ESD current one would expect approximately 2V at the IC input.

#### 3. NUMERICAL PREDICTION OF SOFT ERROR ESD UPSET LEVEL

Investigation of ESD related failures with regard to discharge current and voltages using circuit simulators has been performed with fair degree of success [1], [2], [3]. Circuit simulators have been able to predict the failure levels of ICs to ESD. However they suffer from the major drawback that circuit simulators cannot simulate the fast changing electromagnetic fields accompanying ESD discharge. The transient EM fields are in GHz ranges and can cause soft errors in ICs which is difficult to model in SPICE like simulators. Numerous authors have applied numerical methods for calculating coupling of transient fields from ESD [4], [5], [6], [7], [8]. This is one of the main reasons to include the full wave model of the ESD generator, passive DUT structures and input response models of the ICs to accurately simulate the coupling of the fast changing EM fields to the test structure. This section describes the detailed full wave modelling of the interconnected PCB structure with the flex cable and the ESD generator model to simulate the voltage at the IC input in response to coupling of fields via the flex cable PCB. The results from the full wave simulation are subsequently combined with simple IC response models to predict the occurrence of soft error failures in ICs.

#### **3.1 FREQUENCY DOMAIN MODEL OF FLEX CABLE PCB**

The objective is to model the flex cable board with the IC and the ESD generator in CST MWS and simulate the voltage at the IC input. The IC input is modeled as passive lumped elements in the CST model. To simulate the voltage accurately two distinct models were developed,

- Frequency domain model of the flex cable board where an injection is made from PORT1 of the network analyzer into PCB1 with reference to the large ground plane while S21 is measured on PORT2 at the IC input.

- After verification of the model in frequency domain, the ESD generator model is included with the DUT model in time domain to simulate the voltage at the IC input.

Previous work on modeling of flex cable PCBs have been performed using both full wave simulation tools [9] and analytical methods [10]. In the present test case the flex cable has 40 traces embedded in a dielectric medium. These 40 traces form highly coupled resonators. Accuracy of the simulation is strongly dependent on modeling the resonances correctly. Moreover it is difficult to model the entire flex cable with so many traces because of the small dimension of the traces. To overcome this, the complexity of the problem was reduced to just three traces on the flex cable.

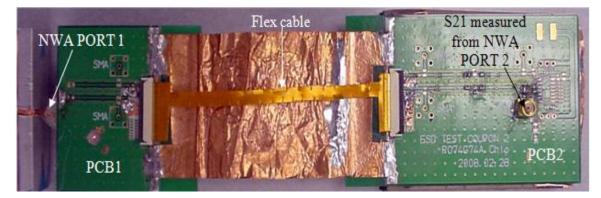

**3.1.1. Measurement setup.** The measurement setup of the flex cable board is shown in Figure 3.1.

Figure 3.1. Measurement setup for transfer impedance measurement

The two PCB boards interconnected via the flex cable PCB is mounted on a metal table top with good electrical connection to earth ground. PCB1 is kept floating above the table top while PCB2 is connected to the system ground plane through gaskets. An injection is made to the ground plane of PCB1 from PORT1 of the network analyzer. S21 is measured from the SMA connector at PORT2. The SMA connector is mounted at the input to the IC. The three traces on the flex cable are in SIGNAL-GROUND-FLOATING configuration. The copper tape connects the ground plane of the both the PCBs. The flex cable is embedded between two Plexiglass plates. The purpose is to change the wave propagation along the flex cable, which would enable us to see which resonances or which behavior is strongly influenced by the flex cable waves. The signal traces on both the PCBs are terminated with 50  $\Omega$  resistors. The transfer impedance measurement is sensitive to the measurement setup and depends on the following factors,

- Height of the flex cable PCB from the copper tape connecting the ground plane of both the boards.

- Orientation of the flex cable meaning whether it is perfectly horizontal or curved to some extent.

- Height of both the boards from the ground plane of the table.

- Reliable connection between the ground planes of the boards through the copper tape.

- Stability at the injection point from PORT1 of the network analyzer to PCB1.

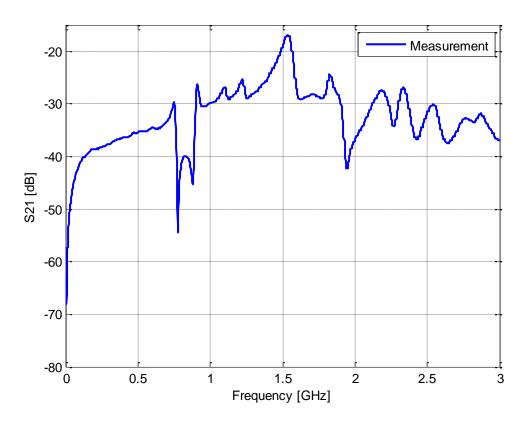

The measured S21 between the injection point and the input to the IC is shown in Figure 3.2.

Figure 3.2. Measured S21 of flex cable board

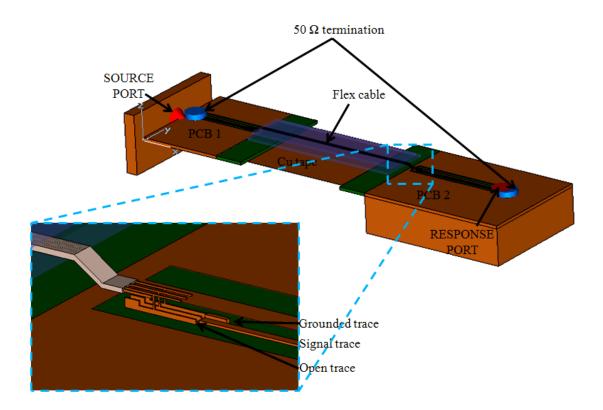

**3.1.2. Full wave simulation model.** An equivalent full wave CST model of the DUT was created and the simulation results were verified with measurement. The CST model is run in frequency domain solver to compute the transfer impedance (S21) and also the input impedance (Z11) looking into the test DUT from PORT1 of the network analyzer. Only three traces are included in the model. The frequency range of simulation is set from 50 MHz to 3 GHz. Figure 3.3 shows the CST model of the flex cable board.

Figure 3.3. CST model of flex cable board

The SOURCE PORT and the RESPONSE PORT are modeled as discrete S parameter ports with 50  $\Omega$  reference impedances to represent the network analyzer ports. A magnified view of the flex cable connector is also shown in the above figure. The flex cable connectors are modeled to scale with the actual geometry. In accordance with the measurement setup the traces on the flex PCB are in SIGNAL-GROUND-FLOATING configuration. The terminations on the signal trace are modeled as 50  $\Omega$  lumped resistor elements to PCB GND. Table 3.1 shows how each element is modeled and the consequences of those modeling strategies.

| Real structure         | Model                         | Consequences                 |

|------------------------|-------------------------------|------------------------------|

| Wall                   | Modeled as Copper             | It is part of the excitation |

|                        |                               | structure and is a metal     |

|                        |                               | block.                       |

| PCB1 & PCB2            | Modeled as copper blocks.     | From previous modeling       |

| Ground layer           | The ground layer of the       | experience one can safely    |

|                        | boards are connected by large | assume this simplification.  |

|                        | number of vias, hence this    |                              |

|                        | assumption.                   |                              |

| PCB1 & PCB2 dielectric | Modeled as FR-4 blocks        | Acceptable solution.         |

|                        | embedded into the ground      |                              |

|                        | layer of the boards.          |                              |

| Flex cable traces      | Modeled as thin sheet of      | The traces are modeled as    |

|                        | Copper.                       | 0.15 mm thick with 0.08      |

|                        |                               | mm of dielectric layer above |

|                        |                               | and below.                   |

| Signal traces on PCB   | Modeled as copper blocks      | Acceptable solution.         |

|                        | with finite thickness.        |                              |

| Copper connect         | Modeled as infinitely thin    | It is not known how the      |

|                        | sheet of PEC to reduce        | results would change if      |

|                        | number of mesh cells.         | modeled with some finite     |

|                        |                               | thickness.                   |

| Extra dielectric       | Modeled as FR-4 blocks.       | Acceptable solution.         |

| Gaskets                | Modeled as copper block.      | Acceptable solution.         |

| Cut traces on the flex | They are ignored in the       | Can be safely ignored.       |

| cable                  | model.                        |                              |

Table 3.1: Equivalent modeling of individual components

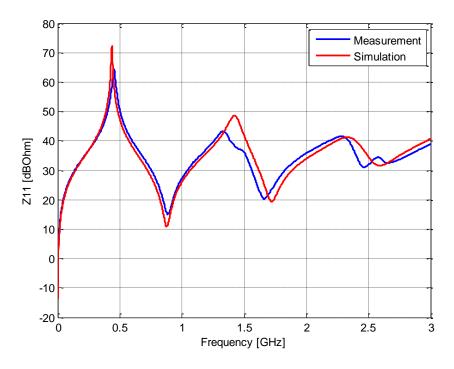

A comparison of the measured and simulated Z11 looking into PCB1 is shown in Figure 3.4. The resonance at 400 MHz matches pretty well. The impedance looking into PCB1 matches quite well over the whole frequency range. A comparison of the measured and simulated S21 is shown in Figure 3.5.

Figure 3.4. Comparison of measured and simulated Z11

Figure 3.5. Comparison of measured and simulated S21

The measured and simulated S21 matches quite well across the whole frequency range up to 3 GHz. There are certain deviations which are minor and have been accepted.

**3.1.3.** Challenges in modeling of flex cable structure. Modeling the flex cable structure in full wave simulation tool proved to be quite a challenge. The main reason for that being the individual traces on the flex cable are so close to each other that they form strongly coupled resonators. So any deviation in the shape or orientation of the flex cable would change the resonances in the S21 curve quite appreciably. Also initially certain assumptions were made with regard to modeling the flex cable PCB which turned out to be wrong. To highlight a few of them,

- Initially the flex cable connector was ignored as it was thought to be not critical to the overall setup since it was very small in comparison to the dimension of the flex cable. However it turned out to be a very crucial element for the simulation model.

- The length of the ground connection was not modeled accurately which added extra inductance to the ground trace thereby leading to mismatch between the measurement and simulation results.

- The air volume between the traces of the flex cable and the copper tape was not modeled accurately which again led to differences between measured and simulated results.

- It was assumed that the thin dimension of the traces on the flex cable could be represented as infinitely thin sheets. Also no attention was paid to modeling the dielectric of the flex cable. These two factors also turned out to be very crucial in getting an accurate model of the flex cable.

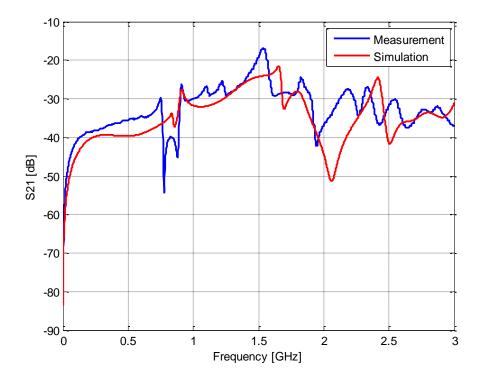

Figure 3.6 shows an initial comparison of the measured and simulated result taking into account the above mentioned assumptions.

Figure 3.6. Comparison of measured and simulated S21

Comparing the curves in the figure above one can see that there are big deviations between the measured and simulated results. This suggests that the assumptions made initially were wrong to begin with. Taking that into consideration some of the important factors during modeling of the flex cable are listed as follows,

- Modeling of the dielectric in the flex cable is crucial for resonance frequency match. The important parameters are dielectric constant and thickness of the traces in the flex cable PCB.

- Distance between the flex cable and the copper tape is critical. It is important to model the air volume between the flex traces and the copper ground accurately.

- Accurate modeling of the connector pins such as width, length, height and pitch is critical.

- Shape and length of the ground trace is important. Modeling the length of the ground connection inaccurately adds extra inductance to the ground trace which can also cause difference between the measurement and simulation results.

## 3.2 TIME DOMAIN MODEL OF FLEX CABLE PCB WITH ESD GENERATOR

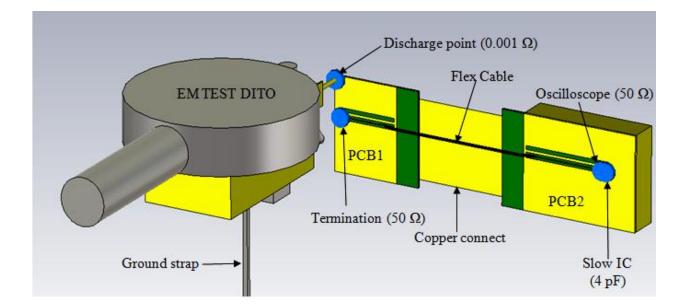

In the previous section the model of the flex cable board was verified in frequency domain. As the next step a complete model of the flex cable board and the IC input with the ESD generator is combined in time domain to simulate the voltage at the IC input at the instance when it crashes. The model of the ESD generator with regard to discharge current and transient electromagnetic fields had been previously verified in [11]. The full wave simulation is carried out in the time domain solver in CST MWS. Figure 3.7 shows the CST model of the flex cable board with the slow IC and the EM TEST DITO generator.

Figure 3.7. CST model of slow IC with flex cable board and EM TEST DITO

From experimental observations it was found that the slow IC triggered at 1 kV when the ESD generator was discharged on the board (PCB1). Hence ESD discharge is simulated at 1 kV. The discharge point is selected 2mm x 2mm from the edge of the board as in the measurement setup. The IC input is modeled as capacitive load of 4 pF obtained from the data sheet. The ground strap of the ESD generator is modeled as a short strap to reduce the size of the discharge current or the peak magnitude of the voltage at the IC input. Discharge tip is modeled as 0.001  $\Omega$  lumped resistive element. Voltage at the IC input is simulated as measured on the oscilloscope which is modeled as a 50  $\Omega$  lumped element to ground of PCB 2. The signal trace on PCB1 is terminated with 50  $\Omega$  in accordance with the measurement setup.

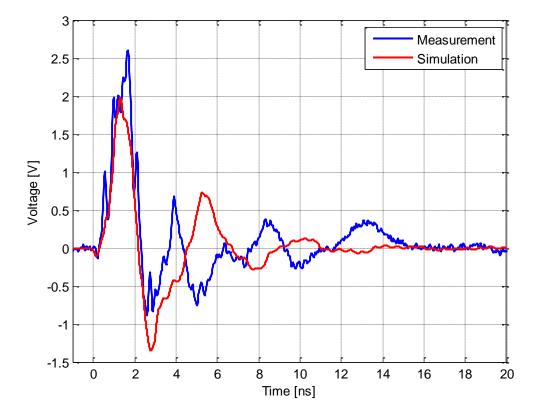

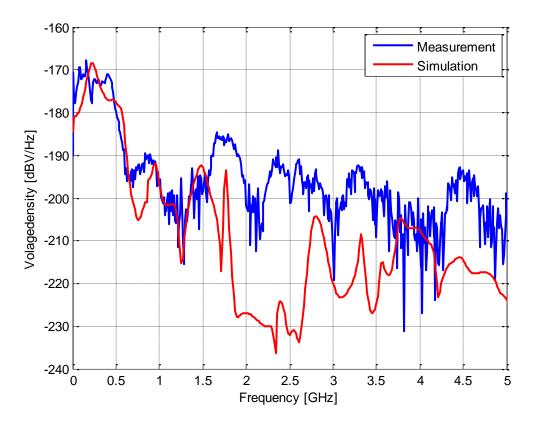

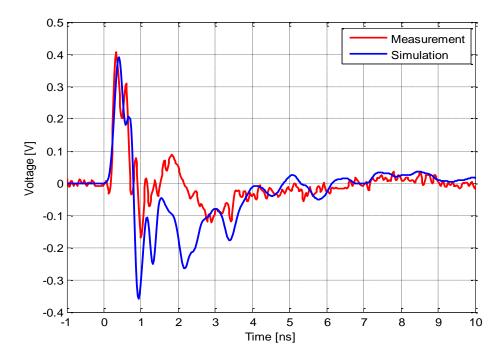

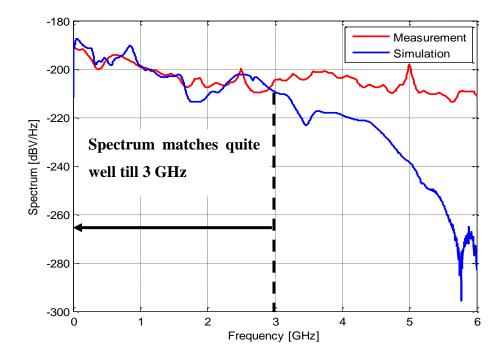

A comparison of the measured and simulated voltage at the slow IC input is shown in Figure 3.8.

Figure 3.8. Comparison of measured and simulated voltage at the slow IC input

The peak value of the simulated voltage deviates around 0.5 V from the measured data. This small difference has been accepted based on measurement uncertainties. A comparison of the spectrum of the voltage waveforms is shown in Figure 3.9.

Figure 3.9. Comparison of spectra of voltage at slow IC input

The spectra of the voltage waveform at the IC input matches fairly well up to about 1.5 GHz. The reason for this could be due to limitations of the ESD generator model to simulate the high frequency content of the measured voltage waveform accurately enough. Also the differences between the measured and simulated S21 for the flex cable boards are not exactly matching which adds to the deviation in the frequency spectrum of the voltage at the IC input. Figure 3.10 shows the comparison of the measured and simulated discharge current onto the board at 1 kV ESD charge voltage.

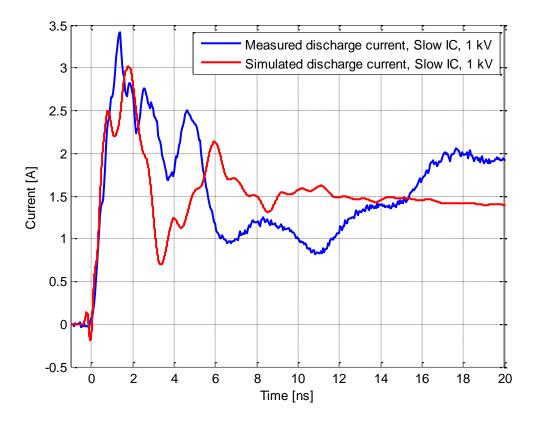

Figure 3.10. Comparison of measured and simulated discharge current

There is a deviation in the peak value of the measured and simulated discharge current. The position of the second peak of the discharge current depends on the length of the ground strap. The longer the ground strap, the farther the second peak is from the first peak. The ground strap length in the simulation model is short which justifies the second peak at 6 ns.

#### 3.3 FULL WAVE MODEL + ESD SOFT ERROR MODEL OF IC

To predict system level ESD failure scenarios the complete simulation model would ideally require the ESD generator model, passive model of the DUT and some form of IC response model. Previous research [11] combines the full wave model of the ESD generator along with passive DUT structure, but no form of IC models. Full wave simulation by itself is not enough to accurately predict the noise voltages at the IC pins in the event of an ESD disturbance. So the ultimate objective is to simulate the time domain voltage waveform in a full wave simulator tool and then combine the simulated result with a soft error upset model of the IC in SPICE to predict the crash levels of the ICs. The next section combines the full wave simulation model (linear) with an equivalent model (non-linear) of the IC to simulate ESD related soft error failure levels.

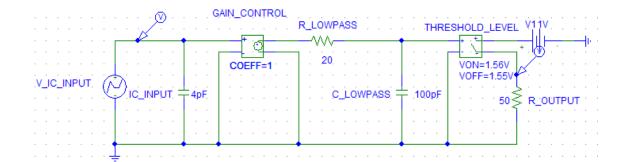

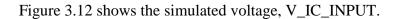

The CST simulation for the slow IC has been successful with regard to the voltage at the IC input. The SPICE model to predict the crash level of the slow IC is shown in Figure 3.11. V\_IC\_INPUT is the voltage at the IC input simulated in CST.

Figure 3.11. SPICE model to predict crash level of Slow IC in response to ESD

Figure 3.12. Simulated voltage at the Slow IC input in CST MWS

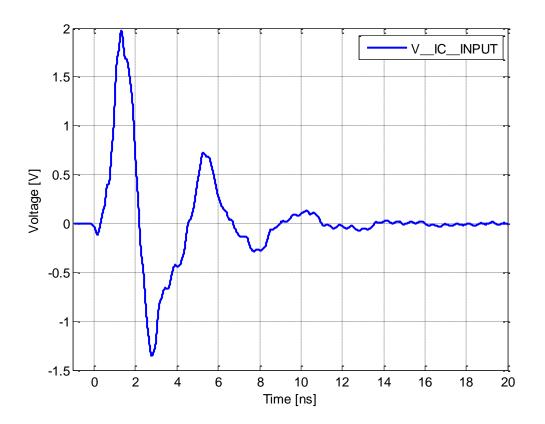

The IC\_INPUT is modeled as a 4 pF capacitor to ground. R\_LOWPASS and C\_LOWPASS form a filter to model the speed of response of the IC. Figure 3.13 shows the speed of response of the slow IC with respect to the peak value of voltage at its input.

Figure 3.13. Voltage at the IC input vs Pulse width

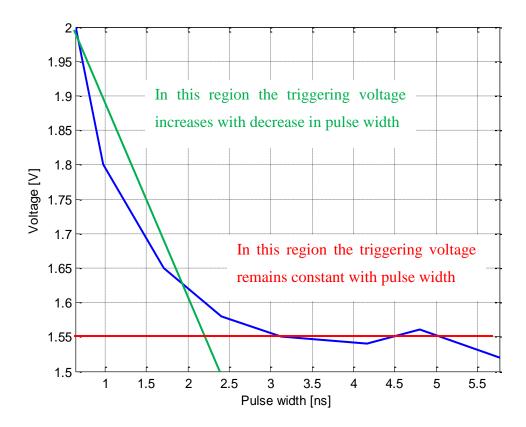

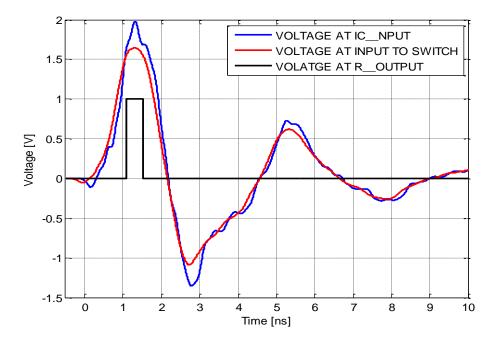

The threshold curve for the slow IC starts to rise at around 2ns. The R\_LOWPASS and C\_LOWPASS components model the 2ns (R\*C = 20\*100 pF = 2\*10-9). The threshold level is 1.55 V and is modeled as a switch. If the peak value of the noise pulse at the input to the switch is greater than the threshold level, a square pulse of magnitude 1 is expected at R\_OUTPUT, which signifies that the IC has triggered. The voltage at the input to the switch (THESHOLD\_LEVEL) is shown in Figure 3.14. Voltage waveform observed at R\_OUTPUT is shown in Figure 3.15.

Figure 3.14. Comparison of voltage at the IC input and at the input to the switch

Figure 3.15. Voltage at R\_OUPUT indicating that the IC has triggered

When the "VOLTAGE AT INPUT TO SWITCH" is greater than the threshold level i.e. 1.55 V, the voltage across "R\_OUPUT" goes to a high (1) indicating that the IC has triggered. This correlates well with the occurrence of soft error in the IC in the event of ESD discharge to the board at a charge voltage of 1 kV.

### 3.4 CONCLUSION

Touch screen features are increasingly being incorporated into small hand held devices such as mobile phones and PDAs. This would likely lead to increased disturbance from ESD related events. An occurrence of ESD either from a human hand or from any metal object on to the LCD might couple through the flex cable and cause soft error failures in an IC mounted on another board inside the product. Moreover with improved IC technology, the threshold levels in ICs are decreasing as well making them more susceptible to different transient phenomena. Hence it is very important for EMC engineers to get an understanding of the coupling mechanism through the flex cable structure and be able to predict system level ESD disturbances occurring in such devices.

The proposed co-simulation strategy models this specific situation and is able to predict ESD related soft errors in ICs via coupling through flex cable PCBs fairly accurately. The simulation method shows a way to build 3D model of flex cable geometries and also points out the important parameters for consideration during modeling. Also for the first time a full wave model of the ESD generator has been combined with an IC response model and the DUT structure to predict system level soft errors.

#### 4. FIELD PACKAGE INTERACTION FOR IC SOFT ERROR PREDICTION

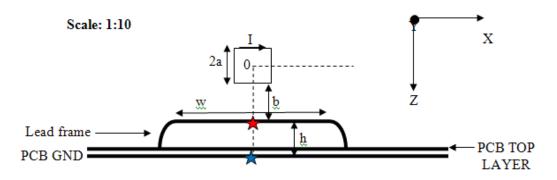

ESD events on commercial products are accompanied by transient electromagnetic fields which can couple onto ICs leading to soft errors. The lead frame structure of ICs along with bond wire connections often form effective loops which couples to the high frequency fields causing induced noise signals on individual pins of the IC. Estimation of the field strengths, derivatives of the field strengths and noise voltages would help understand the coupling mechanism to the IC in much better way.

This section introduces an efficient co-simulation method to predict soft error response in ICs caused by ESD through a combination of full wave modelling and SPICE simulation. The new strategy is able to quantify field strengths and induced noise voltages on pins of the IC for three different field injection techniques – H-field loop probes, field injection via TEM cell and ESD injection. An electromagnetic coupling model for the lead frame structure of the IC is combined with two types of IC models: an IBIS based model and a lumped element model to simulate noise voltages at the IC inputs. The method is verified by comparing simulated and measured noise signals.

#### 4.1 ESD FAILURE PARAMETERS

The failure levels of the IC can be expressed in different ways based on our requirements,

One of the ways to define the failure level is by the TLP charge voltage. However the TLP charge voltage is not a correct representation of the failure levels of the IC. Quantification of the failure levels in terms of the induced currents and voltages would give a much better understanding of the crash levels.

- 2) A better representation of the failure levels is the field strengths on the lead frame of the IC. Estimation of the field from the loop probes must take into account the ratio of the dimension of the loop to the trace on the lead frame, the height of the loop probe above the lead frame, location of the probe with respect to the trace (offset or no offset), variation of the field underneath the probe and how it wraps around the lead frame. All these considerations have to be taken carefully into account since unrealistic assumptions might lead to deviation of the expected results from actual values.

- 3) The derivative of the field or current helps to estimate the induced voltages on the lead frame of the IC. The induced voltage gives qualitative information on the maximum noise voltages the IC can tolerate before it crashes.

- 4) The induced voltages computed from analytical solutions are always a rough estimation of the values. To get accurate results one would need to perform full wave simulation of the lead frame of the IC to determine the field strengths.

#### 4.2 DEFINITION OF TEST PLATFORM

The test bench includes two distinct PCB boards,

Normal board: This PCB board has a dimension of 15x15 cm. It is a 4 layer board. The stack up configuration of the board is as follows,

•Layer 1 (TOP): SIGNAL (Cu)

•Layer 2: GROUND (Cu)

•Layer 3: POWER (Cu)

## •Layer 4 (BOTTOM): SIGNAL TRACE & GROUND (Cu)

This board is primarily used for field scanning, direct injection and system level ESD tests.

TEM Cell board: This PCB board has a dimension of 10x10 cm. It is a 4 layer board. The stack up configuration of this board is as follows,

•Layer 1 (TOP): SIGNAL (Cu)

•Layer 2: POWER (Cu)

•Layer 3: GROUND (Cu)

•Layer 4 (BOTTOM): IC PAD WITH VIAS & GROUND (Cu)

This board is primarily used for TEM cell measurements and also system level ESD tests. On this board the test IC (DDR SDRAM) is mounted on the Layer 4 instead of Layer 1.

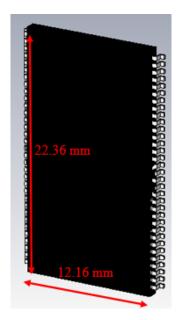

The test platform primarily includes three main ICs,

1) ALTERA EP3C5E144C7N (FPGA IC): The EP3C5E144C7N is a Cyclone III FPGA from ALTERA. It is mounted in a 144 pin Enhanced Quad Flat (EQFP) package. It operates at three voltage levels 1.2V, 2.5V, 3.3V which is supplied to

the IC by a combination of three voltage regulators. The IC pins are housed in 8 different banks.

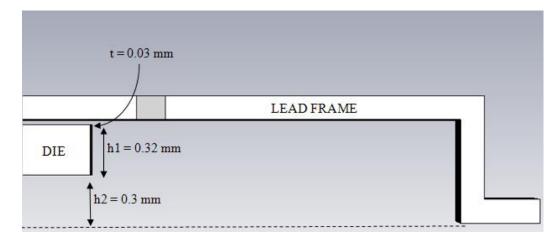

# 2) MICRON MT46V64M8 (DDR-SDRAM MEMORY IC): The MT46V64M8 is a Dual Data rate synchronous high data rate Dynamic RAM organized as 8 x 64 MB, fabricated with MICRON's high performance CMOS technology. The MT46V64M8 uses 8 data lines and 13 address lines. It has 66 pins housed in a TSOP (II) package. The interface for the DDR-SDRAM is SSTL2 and the maximum frequency of operation is 133 MHz. The device requires a supply voltage of typically 2.5 V for its operation.

3) ALTERA EPSC16 (FLASH MEMORY IC): The EPSC16 is a 16-Mbit flash memory device that serially configures the FPGA IC. It is housed in an 8 pin SOIC package. It has a serial interface that can store configuration data for FPGA devices that support active serial configuration and reload the data to the device upon power-up or reconfiguration.

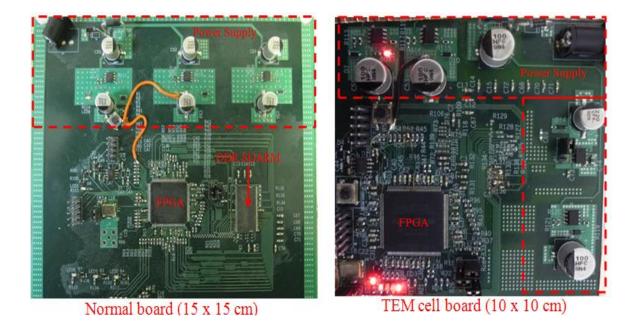

Figure 4.1 shows the top view of both the test boards. The PCB board primarily includes an FPGA (Cyclone III, EP3C5E144C7N), the flash memory IC (EPSC16) and the test IC (DDR SDRAM memory). A simple READ/WRITE operation is performed where the FPGA generates address and random data bits and writes to DDR SDRAM. It concurrently fetches data from the DDR memory and compares the READ and WRITE data.

Figure 4.1. TOP view of the test platform

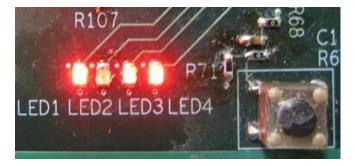

All read & write operations are in burst mode and interleaved with each other. The flash memory is used to program the FPGA so that it can operate in unterhered mode. A group of LEDs indicate the status of operation and the failure of the DDR SDRAM memory as shown in Figure 4.2. Table 4.1 gives the functionality of the LEDs.

Figure 4.2. Status of the DDR SDRAM memory

| LED | STATE    | FUNCTION                   |

|-----|----------|----------------------------|

| 1   | ON       | DDR data error             |

|     | OFF      | No DDR error               |

| 3   | BLINKING | System is running          |

|     | ON/OFF   | System stopped             |

| 4   | ON       | FPGA is comparing data     |

|     | OFF      | FPGA is not comparing data |

Table 4.1. Functionality of the LEDs

#### 5. FULL WAVE MODEL OF MEMORY IC (DDR SDRAM)

In order to accurately estimate the field strengths and induced noise voltages in response to field excitations a full wave model of the lead frame of the IC is required [12]. The following sections show the modeling of the individual components of the memory IC. The primary structural components are as follows:

1) Lead frame geometry of the IC

2) Model of die and package of the IC

3) Model of the bond wires in the IC

4) Modeling the Capacitance to the die for VDD, VDDQ and Input pins of the IC

5) Modeling the resistance to the die for bidirectional Data pins of the IC

Full wave model of the DDR SDRAM memory includes the lead frame geometry along with the distributed lumped elements obtained from a combination of IBIS and ICEM models.

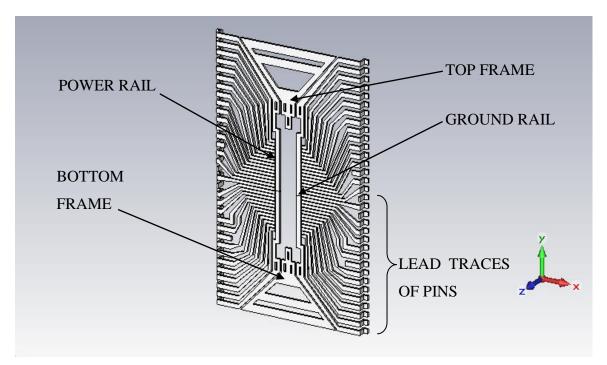

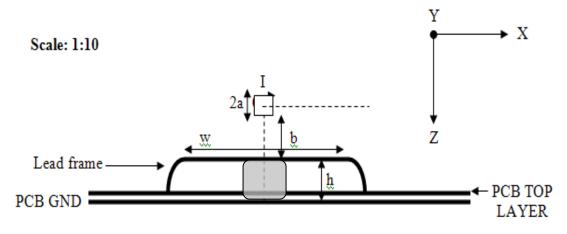

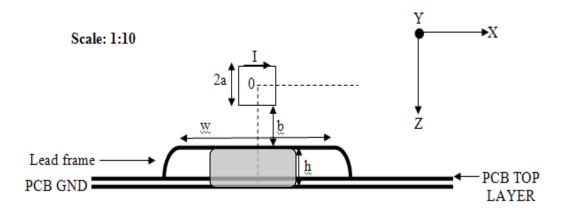

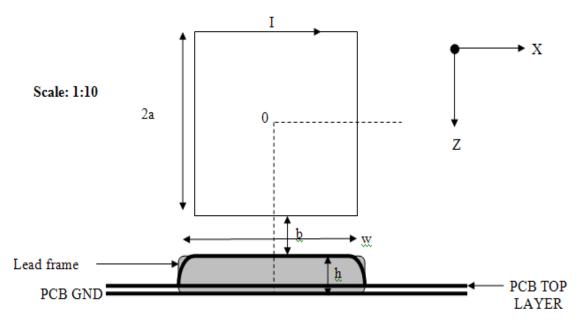

#### 5.1 MODEL OF PHYSICAL GEOMETRY OF IC

**5.1.1. Lead frame model of IC**. The lead frame of the IC was constructed in CST. The lead frame model replicates the exact lead frame structure of the IC. Figure 5.1 and Figure 5.2 shows the lead frame model of the IC. The material property chosen for the lead traces is Alloy42. The reason being for lead frame package, the typical material for the lead frame is Alloy42 (42% Nickel, 58% Iron). The conductivity of alloy42 is  $\sigma = 1.64$  S/m.

Figure 5.1. Lead frame model of the IC

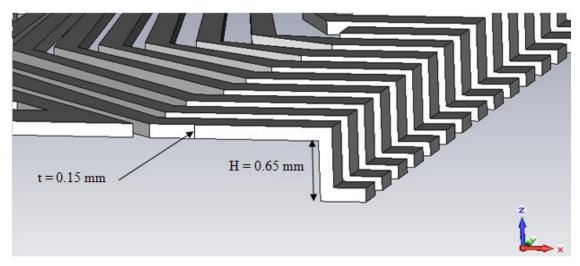

Figure 5.2. Dimension of lead traces

Thickness of the lead traces is 0.15 mm and the height of the lead frame structure is 0.65 mm.

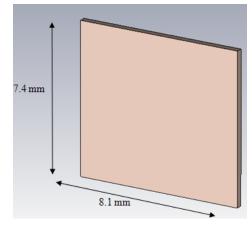

**5.1.2. Die and package model of IC.** The die inside the IC has been modeled as a solid rectangular block as shown in Figure 5.3. Figure 5.4 shows the cross sectional model of the lead frame of the IC along with the die.

Figure 5.3. Die model of the IC

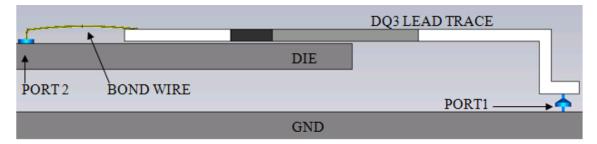

Figure 5.4. Cross sectional view of the die with the lead frame

The distance between the die and the lead frame of the IC is 0.03 mm. In reality the material property of the die is Silicon with varying degree of doping concentrations leading to highly non linear behavior. Hence modeling the die with silicon is improbable in a full wave simulation tool. As a consequence, the die is modeled as a PEC block so that it could be modeled linearly in CST MWS. All the geometries and dimensions have been measured with high degree accuracy. The package for the IC is also modeled as a solid rectangular block as shown in Figure 5.5.

Figure 5.5. Package model of the IC

The material property chosen for the package Epoxy with  $C_r = 4$  according to the default value in CST. The height of the package above and below the lead frame has been measured and modeled accordingly.

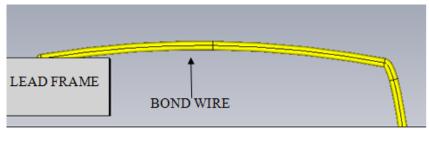

**5.1.3.** Bond wire model of IC. Modeling of the bond wire is very crucial to accurate estimation of the field strength coupling to the IC. The reason being, coupling of transient EM fields to the bond wires is highly dependent on the dimensions, orientation and loop area. Hence inaccurate modeling of the bond wires would lead to over estimation or under estimation of the field components coupling to it. It was difficult to determine the exact diameter and height of the bond wire from the X-ray pictures of the IC. As an alternative typical values (available from commercial ICs) for the height and the diameter were used for our purpose. Typically A-14 type bond wires are used for TSOP type packages. The bond wires are made of gold and have a diameter of 25  $\mu$ m and a height of 160  $\mu$ m. Figure 5.6 shows the bond wire model of the IC.

DIE

Figure 5.6. Bond wire model of the IC

The diameter of the wire is 25  $\mu$ m and the height is 160  $\mu$ m. The material property chosen for the bond wire is gold with a conductivity of  $\sigma = 4.09 \times 10^7$  S/m according to the default value in CST.

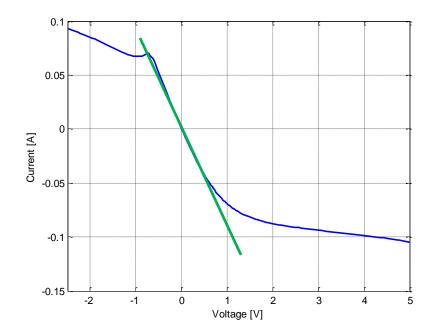

## 5.2 EXTRACTION OF LUMPED PARAMETERS FROM IBIS/ICEM MODELS

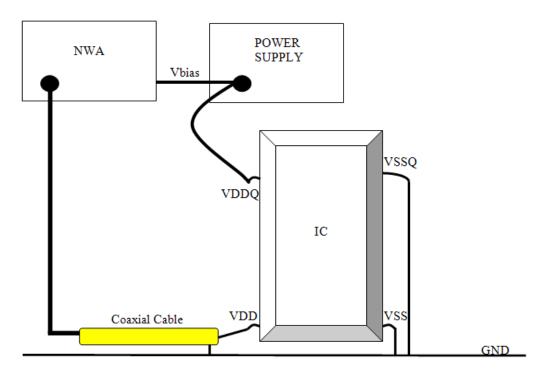

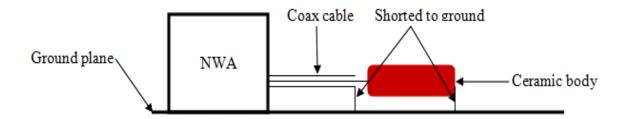

**5.2.1. Capacitance from VDD to VSS**. The ICEM model provides the capacitance value between the power rails. However the IC manufacturer usually does not provide the ICEM models. So in order to get the capacitance value a measurement setup is made to measure this value. The measurement setup is in accordance with the ICEM standard [22]. Figure 5.7 shows the experimental setup.

Figure 5.7. Experimental setup to measure capacitance

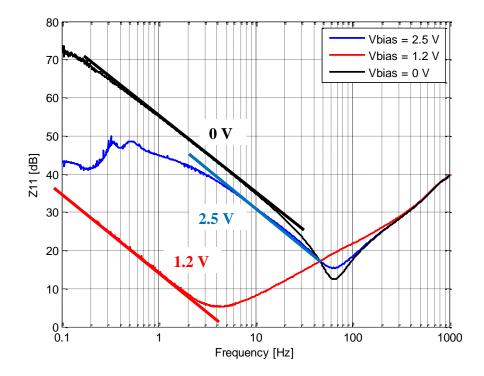

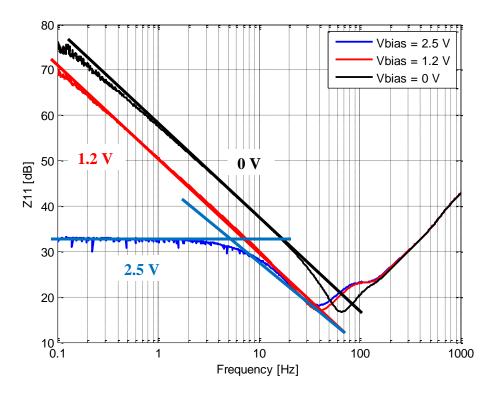

The figure above shows the experimental setup to measure the capacitance value. The VDD pin of the IC is connected via a coaxial cable to PORT 1 of the NWA. Outer conductor of the coaxial cable is connected to GND and the inner conductor is connected to the VDD pin. VSS pin is connected to GND. The VDD pin of the IC is biased to different voltage levels via a power supply which biases PORT 1 of the NWA through the back panel. VDDQ pin is also biased to the same voltage as VDD during the measurement. All the remaining pins of the IC are kept floating. The capacitance value between VDD and VSS is obtained by measuring the input impedance looking into the VDD pin while the IC is biased to VDD/2. The input impedance looking into the VDD pin, for three different bias voltages are shown in Figure 5.8.

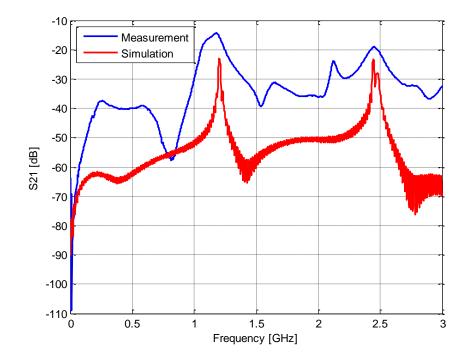

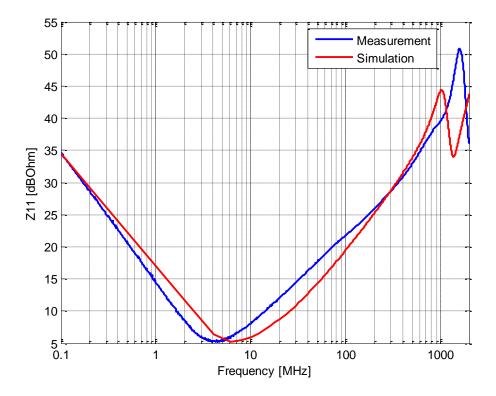

Figure 5.8. Measured Impedance looking into VDD pin

From the above figure, when the bias voltage is 1.2 V i.e. half of the VDD (2.5 V), we observe the capacitance between VDD and VSS. The capacitance value is approximately 30 nF. This capacitance is total capacitance between the VDD and VSS rails in the IC. At 2.5 V bias voltage, non liner switching circuits turn on inside the die which causes the resistive region at lower frequencies. The switching behavior of the non linear circuit is also visible at low frequencies. The rising part of the curve is caused due to the inductance of the path between the VDD and VSS pins.

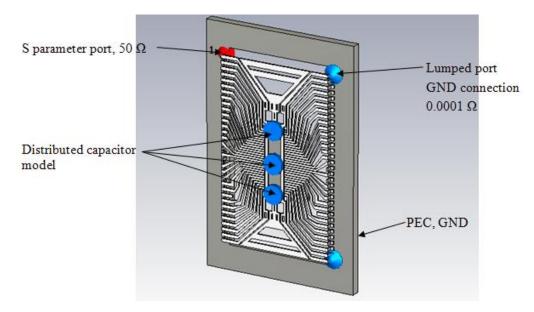

We select the capacitance value corresponding to 1.2 V bias voltage. The capacitance value obtained is 30 nF. From the X-ray model of the memory we see that there are four bond wire connections between VDD power rail and VSS ground rail through the die (the die is modeled as PEC). So this capacitance is modeled as distributed capacitance between the bond wires and the die in the CST model. Figure 5.9 shows the CST model of the IC in accordance to the measurement setup.

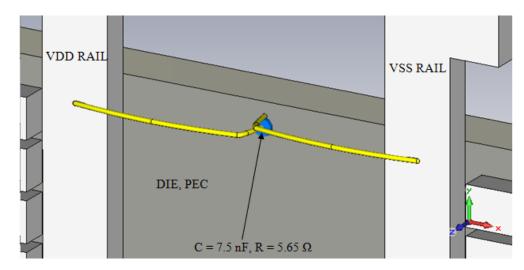

Figure 5.9. CST model to simulate Z11 into VDD pin

The above figure shows the CST model to simulate the impedance looking into the VDD pin of the IC. Going along with the measurement setup, all other pins of the IC model are kept floating. Figure 5.10 shows a magnified view of the distributed lumped capacitor added to the model.

Figure 5.10. Distributed lumped modeling of capacitance between VDD and DIE