# Dickson Charge Pump Rectifier using Ultra-Low Power (ULP) Diode for BAN Applications

Y.C. Wong, P.C. Tan, M. M. Ibrahim, A.R. Syafeeza, N. A. Hamid Faculty of Electronic and Computer Engineering, Universiti Teknikal Malaysia Melaka, 76100 Melaka Malaysia. ycwong@utem.edu.my

Abstract—High power consumption and small battery size severely limit the operating time of devices in Body Area Network (BAN). Radio Frequency (RF) harvesting system can be one of the ways to solve this constraint. Rectifier converts ambient RF into direct current (DC). In a conventional rectifier circuit, Schottky diodes have been considered as an attractive candidate due to their low forward voltage drop and fast switching speed. However, Schottky diodes are not properly modelled in Complementary Metal Oxide Semiconductor (CMOS) technologies which restrict their usefulness in low-cost applications, where high integration levels are desired. Thus, an efficient model of Schottky diode in an integrated circuit (IC) domain is needed. For this reason, Ultra-Low Power (ULP) diode has been proposed in the IC rectifier designs. The performance of ULP diode was compared with diode-connected MOSFET based on Dickson topology and Villard voltage multiplier in 130nm Silterra process technology. The correlation of the design parameters to the performance of voltage rectifier was analysed. The results show that the efficiency of the voltage multiplier has successfully increased more than double based on the optimisation of the design parameters.

*Index Terms*—BAN; RF Rectifier; Ultra-Low-Power Diode; Diode-Connected MOSFET.

## I. INTRODUCTION

Body Area Network (BAN) network is a wireless network of wearable computing devices. It has enormous potential in health monitoring systems as it eliminates the inconvenience of having wires around the patient's body, offering more freedom of movement and comfort, enhanced monitoring and administration of at-home treatment [1]. By using this BAN network, patient's health can be monitored anywhere in real time without the need of wired devices. However, the high power consumption and small battery size restrict the operating time of the devices in BAN. Moreover, the sensors are severely energy constrained. Thus, the demand for batteryfree systems in remote applications raises the interest in radio frequency (RF) energy harvesting.

RF energy harvest is one of the popular types of power harvesting. A block diagram of main functional blocks in RF harvesting system is shown in Figure 1 [2]. The rectifier circuit is one of the important parts that converts the received RF signal voltage into a stable output DC voltage. In a conventional rectifier circuit, Schottky diodes were considered as an attractive candidate to perform the charge transfer task due to their low forward voltage drop and fast switching speed [3]. However, Schottky diodes are not properly modelled in all CMOS technologies, which restrict their usefulness in low-cost applications, where high integration levels are desired [4]. Recently, most researchers have been working towards finding solutions to replicate the low forward voltage drop and leakage current in Schottky diodes through CMOS technology. In BAN application, sensitivity of the rectifier is another key performance parameter [5]. Since the available power given to the rectifier block is too low for traditional rectifiers to operate, most of the recent research work focuses on improving the sensitivity of the rectifier.

Figure 1 : Block Diagram of RF Power Harvesting

The requirement of a high quality rectifier consist of the characteristics of high efficiency, small circuit size, high sensitivity, low threshold voltage, low leakage current, faster rise time and less ripple or noise. Low power consumption rectifier is always preferred in a system to yield higher output power, and a system with higher efficiency is desired. The efficiency of a system has been shown in (1). It takes the ratio of the average of the output voltage over the average of the input voltage during a specific interval of time. Both input voltage ( $V_{in}$ ) and input current ( $I_p$ ) are calculated in RMS values.

$$Efficiency = average clip\left(\frac{V_{out} * I_L}{V_{in} * I_p}\right)$$

(1)

Next, the small circuit size depends on the size of capacitors and transistors used. This determines the size of the chip, effects on the production cost, limitations of its manufacturability, volume, and applications. Smaller capacitance or transistor size leads to an incomplete charge transfer, while larger capacitance and transistor size results in a larger size of the chip. Thus, the trade-off between the size and performance has to be considered. The characteristic of the drain current (I<sub>d</sub>) VS gate to source voltage (V<sub>gs</sub>) is shown in (2), which illustrates that the I<sub>d</sub> is directly proportional to the width of the transistor.

$$I_d = \frac{W}{2L} \left( V_{gs} - V_{th} \right)^2 \tag{2}$$

High sensitivity rectifier that is able to operate in low input voltage condition is preferred. By having high sensitivity, a useful energy level could be harvested by a little ambient RF source. Lower threshold voltage transistor will able to yield higher output. Besides, the undesired leakage current is normally measured at the bulk of the MOSFET. Higher leakage current reduces the efficiency and may lead to latchup in MOSFET. A faster rise time is desired to ensure there is no delay in the system. Lastly, a small ripple in design is to ensure that there will be a smooth and stable DC output supplied to the system.

Therefore, a high quality of charge transfer switches in IC domain which is diode-connected MOSFET and Ultra-Low Power (ULP) diode have been implemented in the Villard voltage multiplier and Dickson rectifier. Their performances in term of leakage current, output voltage and rise time have been observed, analysed and compared. The optimisation has been carried out to improve the efficiency of the rectifier. Next, a high sensitivity rectifier layout has been designed. Lastly, modelling and prototyping on a simple RF energy harvesting have been performed.

The paper is organised as follows. Section II introduces the voltage multipliers topologies. CMOS Charge transfer switches to replicate Schottky diode in rectifier design are described in Section III. Section IV presents the comparison of the simulated result in term of leakage current, output voltage and rises time-based on each of the topologies. The optimisation to the better performance of RF rectifier has been performed and analysed in Section V. High sensitivity rectifier design and layout are shown in Section VI, followed by a conclusion in Section VII.

# II. VOLTAGE MULTIPLIER TOPOLOGIES AND CHARGE TRANSFER SWITCHES

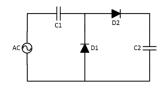

The voltage multiplier rectifier topologies, including the Villard voltage multiplier and the Dickson topology rectifier have been reviewed. The voltage multiplier consists of a cascade of AC-DC voltage doublers. The voltage doubler comprises two capacitors and two diodes, as shown in Figure 2. This circuit serves to change the AC signal into a high DC signal. When the AC signal is in a negative cycle (-Vin), the diode D1 is forward biased and diode D2 is in reverse biased. The current will flow into C1 and charge it until the voltage rise to Vin. Thus, when an AC signal is in a positive cycle (+Vin), the diode D2 is forward biased and diode D1 is in a reverse biased. Then, the current will flow into C2 through D2. The current into C2 is not only derived from the voltage source Vin, but also from C1. Thus, the total voltage generated is twice of the voltage source.

Figure 2: Voltage doubler circuit

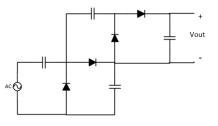

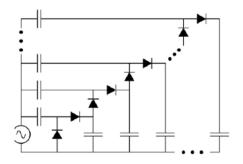

Villard voltage multiplier and Dickson charge pump rectifier, including the diodes [6] are the topologies frequently introduced, as shown in Figure 3 and Figure 4 respectively. Based on both configurations, they look almost similar. They do not have much difference since the Villard voltage multiplier is connected the voltage doubler in a series form, while the Dickson charge pump is connected the voltage doubler in a parallel form. Indeed, Dickson charge pump is a DC to DC converter. With a little modification, in which the clock is replaced by the RF signal, while the leftmost diode is grounded [7], the DC-DC converter could be transformed to a rectifier.

Figure 3: Villard voltage multiplier

Figure 4: Dickson charge pump rectifier

# III. CHARGE TRANSFER SWITCHES IN IC DOMAIN

Due to the high cost and complex process of Schottky diode in the IC fabrication, an efficient model of CMOS transistors to replicate Schottky diode has to be developed. The transistors will act as charge transfer switches to pass charges between stages [8]. The transistor models could be divided to two, namely the diode-connected MOSFET and the ULP diode.

## A. Diode-Connected MOSFET

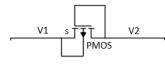

When presenting the diode-connected PMOS transistor as a diode, the transistor will turn on when it is in forward-biased and it will turn off during the reverse-biased, which is similar with a diode. The gate of the diode-connected transistor has been connected to its drain. The bulk or substrate of the NMOS should always connect to the lower voltage terminal, while the substrate of PMOS should connect to the highest voltage terminal [9]. The substrate of diode-connected PMOS transistor that is connected is as shown in Figure 5. There will be a current flow from the source to drain when V1 is higher than V2. This means that the diode is turned on when it is forward-biased. Moreover, when V2 is higher than V1, the voltage of drain is higher than in the substrate. Thus, the drain-body junction starts to conduct. This implies that the diode does not cut-off when it is reversed biased. Thus, this diode-connected PMOS transistor is able to decrease the turn-on voltage compared to the diode when the substrate is connected to the highest voltage terminal. However, this will result in an increase in the threshold voltage due to substrate bias effect and increase the turn-on voltage.

Figure 5: Diode-connected PMOS

## B. Ultra-Low Power (ULP) Diode

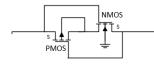

The ULP diode consists of a pair of NMOS and PMOS transistor, as shown Figure 6 [10]. The gate of the PMOS transistor is connected to the source of NMOS transistor and vice versa. The bulk of PMOS connects to higher voltage terminal, while the NMOS connects the bulk to the lower voltage terminal such as ground. The use of a specially designed ULP CMOS diode allows us to improve the characteristics of the rectifier in comparison to rectifiers that use PMOS diodes, and it ensures cheaper fabrication process than the one using Schottky diode [11].

Both transistors are in series and forward biased when ULP diodes are biased positively. The forward current is similar to the standard MOS diodes. However, the ULP diodes become more interested when they are reversed biased. In this case, both transistor sources are connected together and work in weak inversion region with  $V_{gs}$ <0 for NMOS while  $V_{gs}$ >0 for PMOS. If the reverse voltage is increased, the current increases as the drain-source voltage increases. Then, the current decreases exponentially as the cut-off gate-source voltages are increased. This mechanism has strongly reduced the leakage current and maintained a good forward current. Besides, the reduction of the leakage current is due to the creation of a negative impedance in reverse operation, while keeping a forward current almost equal to the one of the equivalent standard MOS diode [12].

Figure 6: Ultra-Low Power (ULP) diodes

#### IV. COMPARISON ON CHARGE TRANSFER SWITCHES

The diode-connected PMOS and ULP diode have been implemented into the 3 stages Villard voltage multiplier and Dickson rectifier in 130nm Silterra process technology. The design parameter of these two topologies was set as shown Table 1. The performances in term of leakage current, rise time and output voltage will be compared and analysed.

#### A. Leakage Current

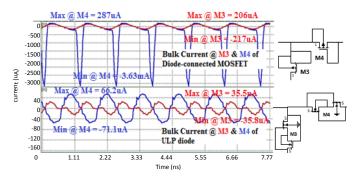

The leakage current of each transistor for the diodeconnected MOSFET and ULP diodes in Villard voltage multiplier and Dickson rectifier was obtained. The more detailed leakage current in Dickson rectifier with different diodes is shown in Figure 7. The bulk current of diodeconnected MOSFET at M4 in the positive cycle was 76.93% higher than in the ULP diode at M4. However, it became worse in the negative cycle. The bulk current of diodeconnected MOSFET at M4 in negative cycle reached 98.04% higher than the bulk current of ULP diode at M4.

Table 1 Parameter setting in Villard voltage multiplier and Dickson charge pump rectifier

| Topology     | Villard Voltage |           | Dickson Charge Pump |           |

|--------------|-----------------|-----------|---------------------|-----------|

| тороюду      | Multiplier      |           | Rectifier           |           |

| Diode        | ULP<br>Diode    | Diode-    |                     | Diode-    |

|              |                 | Connected | ULP Diode           | Connected |

|              |                 | MOSFET    |                     | MOSFET    |

| Technology   | 130nm           |           | 130nm               |           |

| No of stages | 6               |           | 6                   |           |

| Frequency    | 900MHz          |           | 900MHz              |           |

| RF input     | 1Vp             |           | 1Vp                 |           |

| Stages       | 5p              |           | 5p                  |           |

| Capacitance  |                 |           |                     |           |

| Capacitive   | 10p             |           | 10p                 |           |

| load         |                 |           |                     |           |

| W/L (NMOS)   | 10um/           |           | 10um/               |           |

|              | 0.15um          | -         | 0.15um              | -         |

| W/L (PMOS)   | 40um/           | 40um/     | 40um/               | 40um/     |

|              | 0.15um          | 0.15um    | 0.15um              | 0.15um    |

Figure 7: Leakage current of Dickson rectifier using diode-connected MOSFET and ULP

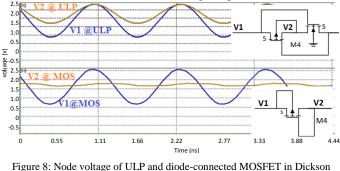

The ULP diode has lower leakage current compared with the diode-connected MOSFET. This is because the bulk of the PMOS in ULP was tied to the terminal, which always has higher voltage, V2 as shown in Figure 8. While in the diodeconnected MOSFET, the bulk was always connected to V1 terminal and the V1 varied as shown in Figure 8. We can observe that the V1 is not always in higher voltage. This means that the substrate of PMOS is not always tied to the higher voltage terminal. The high leakage current was produced in this condition. In order to solve this issue, the auxiliary transistor can be introduced so that the bulk of PMOS can always be tied to a higher voltage terminal. Thus, the leakage current of transistor could be reduced. However, it can lead to undesired effect. By increasing the size with an increase in the number of transistors, it creases the complexity of the circuit and the die size, causing the parasitic effect.

Figure 8: Node voltage of ULP and diode-connected MOSFET in Dicksor charge pump rectifier

# B. Transient Analysis on Output Voltage

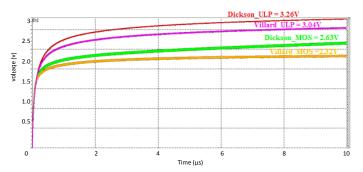

The transient analysis of output voltage for both topologies using diode-connected MOSFET and ULP diode is shown in Figure 9. The result shows that the rectifier using ULP diode has higher output voltage compared to using the diodeconnected MOSFET. Dickson rectifier using ULP diode reached the highest output voltage, which is 3.26V and followed by Villard voltage multiplier using ULP diode with the output voltage of 3.04V in the time duration of 0.01ms. Next, the output voltage of Dickson rectifier and Villard voltage multiplier using diode-connected MOSFET reached 2.63V and 2.32V respectively, although the topologies using the diode-connected MOSFET have faster rise up time in comparison to the same topologies applied with ULP diode. However, ULP diode still has better performance compared to the diode-connected MOSFET in term of the output voltage. The reduction in the leakage current was able to produce higher output voltage.

Figure 9: Transient analysis of output voltage using ULP diode and diodeconnected MOSFET in Villard voltage multiplier and Dickson rectifier

# V. PARAMETER OPTIMISATION ON DICKSON RECTIFIER USING ULP DIODE

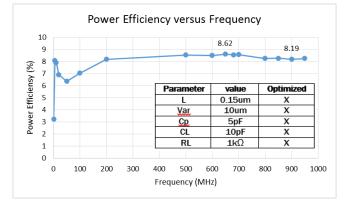

The Dickson charge pump rectifier using ULP diode was employed to the parameter optimisation due to the best performance in terms of the lowest leakage current and highest output voltage obtained. Initially, the Dickson charge pump rectifier using the ULP Diode has been simulated using a parameter set, as shown in Table 1. The input voltage was set at 1Vp. By sweeping the frequency from 1MHz to 950MHz, the graph is as shown in Figure 10. It shows that the maximum efficiency occurred at 650MHz with 8.62%. However, the desired target frequency 900MHz achieved 8.19% efficiency. Thus, an improvement in the efficiency at 900MHz has to be performed.

Figure 10: Power efficiency versus frequency

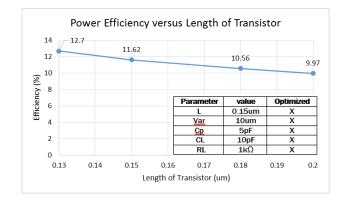

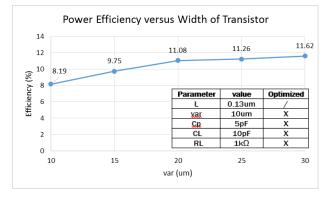

Parameter optimisation has been performed on the width and length of the transistors. It was expected that small load current will be drawn from the rectifier in BAN application, thus the width of NMOS and PMOS was set at 10 $\mu$ m and 40 $\mu$ m respectively. Figure 10 shows the optimisation of the length of the transistor. It shows that the transistor with a shorter length achieved higher efficiency. The optimisation in the length of the transistor at 0.13um increased the efficiency to 12.7%. Figure 11 shows that the increase in the width of the transistor improves the efficiency of the rectifier. The efficiency reached 11.82% with the width of NMOS at 30um and PMOS at120um and the length at 0.15um.

Figure 10: Power efficiency versus length of transistor

Figure 11: Power efficiency versus width of transistor

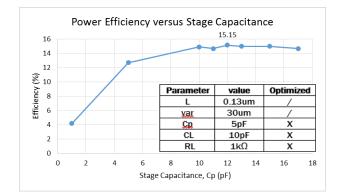

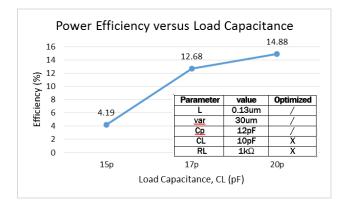

Besides the size of the transistor, the stage capacitance and load capacitance were investigated. Figure 12 and Figure 13 show the optimisation on the stage capacitance and load capacitance respectively. The increase in both capacitances yielded higher efficiency. The stage capacitance at 12pF produced the highest efficiency at the range of 1pF to 20pF. While the load capacitance reached the highest efficiency at 20pF at the range of 15pF to 20pF. The smaller chip is preferred since it will be implemented at BAN devices. Thus, the trade-off between the size of the chip and its performance has been performed.

Figure 12: Power efficiency versus stage capacitances

Figure 13: Power efficiency versus load capacitance

Figure 14: Power efficiency versus load resistance in 900MHz

Figure 15: Power efficiency versus load resistance in 650MHz

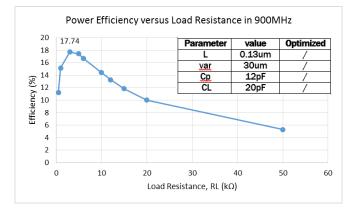

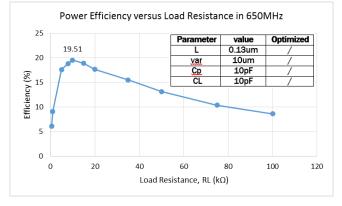

Lastly, by sweeping the load resistance from  $500\Omega$  to  $50k\Omega$ , the  $3k\Omega$  setting yielded the highest efficiency, which is 17.74% as shown in Figure 14. The efficiency has increased from 8.19% to 17.74% in Dickson rectifier using ULP diode. In addition, optimisation was also performed at the frequency of 650MHz, and it was found that the efficiency could achieve 19.51%, as shown in Figure 15.

## VI. HIGH SENSITIVITY RECTIFIER

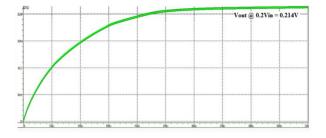

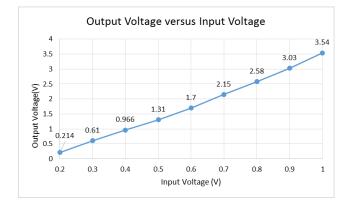

The Dickson charge pump rectifier using ULP diode was investigated using 0.2Vp input voltage. Optimised parameters obtained in the previous section were applied. The transient analysis on output voltage is shown in Figure 16. It shows that the Dickson charge pump using ULP diode was able to produce an output voltage of 0.214V by having an input of 0.2V. This was considered a high sensitivity rectifier since it was able to operate in low input voltage condition. Besides, the input voltage has been swept from 0.2V to 1V, and the relationship between the output voltage and input voltage was observed. Figure 17 shows that the output voltage increases as the input voltage increases.

Figure 16: Transient analysis on output voltage of Dickson charge pump using ULP diode

While comparing among the Villard voltage multiplier and the Dickson rectifier using diode-connected MOSFET and ULP diode, the Dickson rectifier has the best performance in terms of higher output voltage and minimum leakage current. Besides, it is a high sensitivity rectifier, which is able to yield 17.74% efficiency.

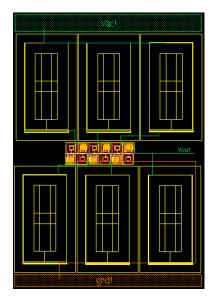

A layout of 3 stages Dickson rectifier using ULP diode has been produced, as shown in Figure 18. It occupies 313mm X 214mm of size. In this layout, the PMOS used eight fingers and the width of each finger was set to 5um, while the NMOS used a total of four fingers with the width of 2.5um.

Figure 17: Output voltage versus input voltage in Dickson charge pump using ULP diode

Figure 18: Layout of 3 stages Dickson charge pump rectifier

#### VII. CONCLUSION

In this work, Villard voltage multiplier and Dickson rectifier using diode-connected PMOS diode and ULP diode have been performed and analysed in terms of its leakage current and output voltage. Dickson rectifier has better performance compared to Villard voltage multiplier. The topologies using ULP diode showed lower leakage current and higher output voltage produced compared to the diode-connected PMOS diode. The Dickson rectifier using ULP diode has the best performance among the others. Thus, it has been proceeded to the parameter optimisation to obtain higher efficiency. The efficiency increased from 8.19% to 17.74%. The Dickson rectifier was also considered as a high sensitivity rectifier since it is able to produce 0.214V with an input voltage of 0.2V.

#### ACKNOWLEDGMENT

The authors acknowledge the financial support by Universiti Teknikal Malaysia Melaka's short term grant No. PJP/2015/FKEKK(5B)/S01424.

#### REFERENCES

- O. Seunghyun, "Energy-efficient Reactive Radio Design in Body Area Networks," pp. 49-68, 2013.

- [2] M. Rastmanesh, "High Efficiency RF To DC Converter With Reduced Leakage Current For RFID Applications," MASc, Department of Electrical and Computer Engineering, Dalhousie University, Halifax, Nova Scotia, 2013

- [3] U. Alvarado, G. Bistué, and I. Adín, Low Power RF Circuit Design in Standard CMOS Technology, 1 ed.: Springer-Verlag Berlin Heidelberg, 2012.

- [4] C. Nguyen, Radio Frequency Integrated Circuit Engineering. Canada: John Wiley & Sons, Inc., Honoken, New Jersey, 2015.

- [5] Z. Hameed and K. Moez, "A 3.2 V -15 dBm Adaptive Threshold-Voltage Compensated RF Energy Harvester in 130 nm CMOS," IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 62, pp. 948-956, 2015.

- [6] L. G. d. Carli, Y. Juppa, A. J. Cardoso, C. Galup-Montoro, and M. C. Schneider, "Maximizing the Power Conversion Efficiency of Ultra-Low-Voltage CMOS Multi-Stage Rectifiers," IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 62, pp. 967-975, 2015.

- [7] G. Gosset, B. Rue, and D. Flandre, "Very High Efficiency 13.56 MHz RFID Input Stage Voltage Multipliers Based On Ultra Low Power MOS Diodes," in IEEE International Conference on RFID, 2008, pp. 134-140.

- [8] Y. C. Wong, N. H. Noordin, A. O. El-Rayis, N. Haridas, A. T. Erdogan and T. Arslan, " An Evaluation of 2-Phase Charge Pump Topologies with Charge Transfer Switches for Green Mobile Technology, " IEEE International Symposium on Industrial Electronics (ISIE), 2011.

- [9] F.-B. L. Dong-Sheng Liu, Xue-Cheng Zou, Yao Liu, Xue-Mei Hui and Xiong-Fei Tao, "New Analysis and Design of a RF Rectifier for RFID and Implantable Devices," 2011.

- [10] C. L. D. Levacq, V. Dessard, D. Flandre, "Composite ULP diode fabrication, modeling and applications in multi-Vth FD SOI CMOS technology," Solid-State Electronics, 48, pp. 1017-1025, 2004.

- [11] B. L. Rue, D; Flandre, D, "Low-Voltage Low-Power High Temperature SOI CMOS Rectifier," IEEE International SOI conference, 2006.

- [12] G. Gosset and D. Flandre, "A very high efficiency ultra-low-power 13.56MHz voltage rectifier in 150nm SOI CMOS," in IEEE International Symposium on Radio-Frequency Integration Technology (RFIT 2009), 2009, pp. 347-350.