# Electrical Test of Resistive and Capacitive Open Defects at Data Bus in 3D Memory IC

Masaki Hashizume<sup>1\*</sup>, Yudai Shiraishi<sup>1</sup>, Hiroyuki Yotsuyanagi<sup>1</sup>,

Hiroshi Yokoyama<sup>2</sup>, Tetsuo Tada<sup>3</sup>, Shyue-Kung Lu<sup>4</sup>

<sup>1</sup>Tokushima University, Tokushima, Japan.

<sup>2</sup>Akita University, Akita, Japan.

<sup>3</sup>Tokushima Bunri University, Shido, Kagawa, Japan.

<sup>4</sup>National Taiwan Univ. of Science and Technology, Taipei, Taiwan3.

tume@ee.tokushima-u.ac.jp

Abstract— We propose an electrical test method of resistive and capacitive open defects occurring at data bus lines between dies, and between dies and I/O pins in 3D memory ICs. The test method is based on supply current of an IC. The number of test vectors for a 3D memory IC made of ND memory dies in the test method is  $10 \cdot ND$  and small. Also, defective interconnects are located by the test method. Feasibility of the tests is examined by some experiments for a circuit made of an SRAM IC on a printed circuit board. The experimental results show that capacitive open defects and resistive open ones whose resistance values are greater than  $200\Omega$  can be detected by the test method.

*Index Terms*— 3D memory IC; Data bus; Open defect; Supply current test.

## I. INTRODUCTION

A lot of attention has been paid to 3D stacked ICs, since low power dissipation and high speed operations are realized in the ICs [1]. 3D stacked ICs are made of known good dies. The dies are stacked and connected with Through Silicon Vias (TSVs) and micro bumps. Defects can occur at interconnects between dies in 3D stacked ICs including 3D stacked memory ones, since the fabricating process is complex. Thus, many kinds of test methods and DfT (design for testability) methods have been proposed for 3D stacked ICs [2-13].

Generally, interconnects between dies in 3D stacked logic ICs are tested by a boundary scan test method. In order to test them by the test method, a testable designed circuit should be embedded to each of the dies in the ICs. However, some speed degradation appears in the testable designed

method based on the test principle of the test method for bidirectional signals [26].

Hard open defects, resistive open defects and capacitive open defects are selected as targeted defects of the test method proposed in [26]. However, hard open defects will be detected by functional test methods. Generally, ICs are tested by functional test methods before shipping to a market. Thus, hard open defects need not be added to targeted defects of electrical tests.

We propose an electrical test method to detect only resistive open defects and capacitive open ones occurring at data bus lines between dies, and between dies and I/O pins in 3D stacked memory ICs. We examined feasibility of our electrical tests with a circuit made of an SRAM IC on a printed circuit board. After proposing the test method in section 2.0, we denote the experimental evaluation results in section 3.0.

# II. ELECTRICAL TEST METHOD

A 3D stacked IC is made by stacking known good dies. Thus, we assume in this paper that dies in 3D memory ICs are known good ones.

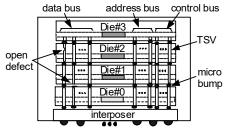

The dies are connected with TSVs and micro bumps. An example of 3D memory ICs is shown in Figure 1.

Open defects can occur in TSVs and at micro bumps in the fabrication process. They can occur at data bus, address one and control one in 3D memory ICs. The open defects occurring at data bus are targeted ones in our test method.

Open defects occurring at the interconnects can be classified into two types: hard open defects and soft ones.

brought to you by CORE ut the Rab per Anniversiti Teknikal Malaysia Melaka: UTeM Open Journal System

As and micro primbs'

I the Bab petmeen the

parts is long, no logical signal will be propagated. The open defect is modeled as a resistive open defect of infinite resistance. When the gap between the parts caused by a hard open defect is short, a high speed signal will be transferred without errors. The hard open defect is modeled as a capacitive open defect. On the other hand, when a soft open defect occurs at TSVs and micro bumps, the output ports of them are connected to the input ports in part. The soft open defect can be modeled as a resistive open defect of finite resistance.

In this paper, we discuss a test method for detecting only capacitive and resistive open defects occurring at interconnects between dies, and between the bottom die and I/O pins of the IC, since hard open defects are detected by

View metadata, citation and similar papers at core.ac.uk

circuit to dies in 3D stacked memory ICs [10].

Since open defects at TSVs may be detected by electrical tests, many kinds of electrical test methods and DfT ones have been proposed [14-24]. However, a testable design is indispensable for the tests and may cause additional delay in defect-free ICs. Thus, a test method of 3D stacked memory ICs, which are abbreviated as 3D memory ICs in this paper, should be developed with no testable design.

We have proposed an electrical test method for TSVs that transmit bi-directional signals [25]. The test method does not request us to add testable designed circuits to an original circuit. Since data bus lines in an SRAM IC are bi-directional signal lines, we proposed an electrical test

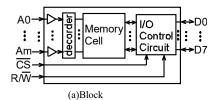

functional test methods. Circuit blocks of typical memory dies are shown in Figure 2(a).

Figure 1: 3D memory IC and targeted defects

Figure 2: Configuration of Memory IC

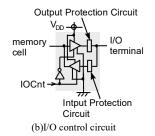

Figure 3: Electrical interconnect test of 3D memory IC

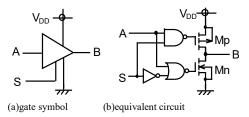

Figure 4: 3-state buffer gate

Memory dies are made of memory cells, an address decoder and input/output control circuits. Memory cells to be accessed are specified by address data. The contents of the accessed memory cells are read out from the die. Also, some data are stored to the memory cells. The input/output operations are controlled by a chip select signal (CS) and a read/write control signal (R/W).

Each of dies in our targeting 3D memory ICs is made of word memories, each of which consists of 8 memory cells and is assigned to an address. By specifying an address, one byte data are read out from a word memory of the address or stored into it.

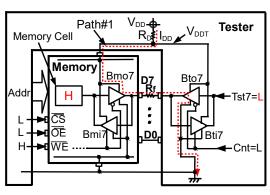

Each memory cell is accessed through an I/O control circuit whose example is shown in Figure 2(b), since data bus lines are bi-directional signal lines.

Test principle of the test method proposed in this paper for a data bus line D7 is shown in Figure 3. At first, a logic value is written into a memory cell. When the value is read out from the cell, a logic signal of the complement value is provided to the bus line from the outside of the IC in our tests. An equivalent circuit of a 3-state buffer gate is shown in Figure 4. A high level signal and low level one are denoted as H and L, respectively, in this paper. When H and L are provided to a data terminal A, an nMOS Mn and a pMOS Mp are turned on, respectively, if H is provided to an I/O control terminal S. Thus, by providing a logic signal of L that is complement to the one in a memory cell from a 3-state gate, a large supply current will flow along a path Path#1 as shown in Figure 3.

If a capacitive open defect and a hard one occur at a data bus line of D7, the supply current will not flow. If a resistive open defect occurs at it, smaller supply current will flow than the defect-free IC. Thus, it is examined whether (1) is satisfied in our tests. If (1) is satisfied, it is judged that an open defect occurs at the targeted data bus line.

$$I_{DDn} - I_{DDc} \ge I_{th} \tag{1}$$

where  $I_{DDn}$  and  $I_{DDc}$  are supply current  $I_{th}$  in the defect-free circuit and in the device under test, respectively. Ith is a threshold value.

If an open defect occurs at a data bus line, the logic value stored in a memory cell is unknown. Thus, in the test method proposed in [26], both H and L are provided to the targeted data bus line. Since test time should be short as possible, we tried to shorten our test time.

Our new test method for data bus lines between dies and between a die and I/O pins in a 3D memory IC is as follows:

- <1> H is stored to all of the memory cells in a word memory inside each of the dies in the 3D memory IC.

- <2> The data stored in the word memory are read out. If L is read out from a memory cell in the word memory, it is determined that an open defect occurs at the data bus line connecting to the memory cell.

<3> L is provided to each of the memory cells of the word memory from a tester and supply current IDD is measured. If (1) is satisfied, it is determined that an open defect occurs at the data bus line connecting to the memory cell. If (1) is not satisfied for all of the memory cells, it is determined that an open defect does not occur at the data bus lines.

The number of test vectors for a 3D memory IC made of ND memory dies in the test method is 10•ND. Supply current measurement is time-consuming. However, since the number of the measurements is 8•ND, test time of the test

method is proportional to ND and acceptable in production tests

In the test method proposed in [26], the process at <1> is not performed and IDD that flows when both H and L are provided to the IC is measured. The current measurement time is extremely longer than a logic signal application to the IC. Thus, the test time of the test method denoted above is shorter than the one proposed in [26].

### III. EXPERIMENTAL EVALUATION

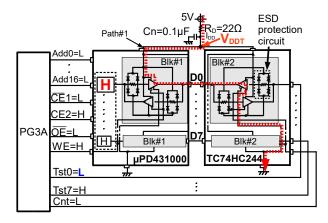

We examine feasibility of our tests with an experimental circuit shown in Figure 5. The circuit is made of a CMOS SRAM IC  $\mu$ PD431000 (1M-bits CMOS Static RAM, 128k-words by 8-bits) and a bus driver IC 74HC244 on a printed circuit board.

Figure 5: Experimental circuit

In our experiments, a resistive open defect, a capacitive one and a hard one are inserted to D0 in Figure 5. The resistive open defect and the capacitive one are inserted by adding a resistor of  $200\Omega$  and a capacitor of 1nF. The hard open defect is inserted by eliminating the signal line of D0 from the experimental circuit.

IDD is measured as the voltage across a resistor RD which is referred to as VDDT. VDDT waveforms are measured with a digital oscilloscope DPO3034. Test signals are provided with a pattern generator PG3A.

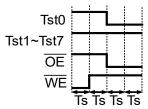

When a data is read out from the SRAM IC, H and L should be provided to it as a write-enable signal ( $\overline{\ }$ WE) and an output enable signal ( $\overline{\ }$ OE), respectively. The waveforms of test signals in our experiments are shown in Figure 6. The signals are provided per Ts=100µsec. When Tst0=L, Cnt=L and  $\overline{\ }$ OE =L, D0 in our experimental circuit can be tested by our test method.

Figure 6: Test signals.

In order to test the data bus line of D0 by our test method, data "11111111" are stored into memory cells whose

address is 000H. After that, a test data "11111110" is provided to the data bus line and L is provided to Cnt. As a result, supply current will flow along a current path denoted as "Path#2". Hence, VDDT will decrease in the defect-free circuit.

When a capacitive open defect occurs at the data bus line, the current will not flow. When a resistive open defect occurs at it, smaller current than the defect-free circuit will flow

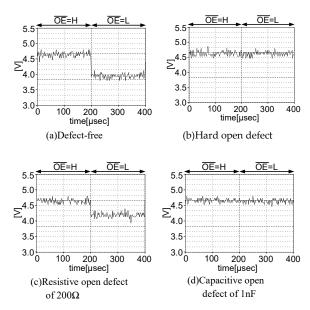

Measured waveforms are shown in Figure 7. In Figure 7(a), a large supply current flows and VDDT decreases when  $^-$ OE=L. When a hard open defect occurs at D0, IDD will not flow and VDDT does not decrease when  $^-$ OE=L as shown in Figure 7(b). When a resistive open defect of 200 $\Omega$  occurs, smaller IDD flows than in Figure 7(a), and VDDT which is larger than in Figure 7(a) appears as shown in Figure 7(c). When a capacitive open defect occurs, IDD does not flow and VDDT does not decrease as shown in Figure 7(d). Thus, the resistive open defect and the capacitive one are detected by our test method.

Test speed of the test method has not been examined. It remains as a future work to examine it.

Figure 6: Measured waveforms of  $V_{DDT}$

# IV. CONCLUSION

We have proposed an electrical test method for detecting resistive open defects and capacitive ones occurring at data bus lines between dies, and between dies and I/O pins in 3D memory ICs. We have examined feasibility of our tests with an experimental circuit made of an SRAM IC on a printed circuit board. It is shown by the experiments that capacitive open defects and resistive open ones whose resistance values are greater than  $200\Omega$  are detected by the test method.

# ACKNOWLEDGMENT

This work was supported by a Collaborative Research

Program between Tokushima University and National Taiwan University of Science and Technology from 2014 to 2015. We wish to thank Tomoaki Konishi, Shoichi Umezu, Kosuke Nambara and Shohei Suenaga in Graduate School of Advanced Technology and Science, Tokushima University for their technical supports and their valuable comments.

### REFERENCES

- Pavlidis, V. F., and E. G. Friedman. 2009. Three-dimensional Integrated Circuit Design. USA: Morgan Kaufman.

- [2] Lee, H-H. S., and K. Chakrabarty. 2009. Test Challenges for 3D Integrated Circuits. IEEE Design & Test of Computers. 26(5):26-35.

- [3] Marinissen, E. J., and Y. Zorian. 2009. Testing 3D Chips Containing Through-Silicon Vias. IEEE International Test Conference (ITC), 2009. Texas, USA. 1-6 November 2009. 1-11.

- [4] Noia, B., K. Chakrabarty, and E. J. Marinissen. 2010. Optimization Methods for Post-Bond Die-Internal/External Testing in 3D Stacked ICs. IEEE International Test Conference (ITC), 2010. Texas, USA. 31 October - 5 November 2010. 1-9.

- [5] Chou, C. W., J. F. Li, J. J. Chen, D. M. Kwai, Y. F. Chou, and C. W. Wu. 2010. A Test Integration Methodology for 3D Integrated Circuits. The 19th IEEE Asian Test Symposium (ATS), 2010. Shanghai, China, 1-4 December 2010. 377-382.

- [6] Huang, Y. J., J. F. Li, J. J. Chen, D. M. Kwai, Y. F. Chou, and C. W. Wu. 2011. A Built-In Self-Test Scheme for the Post-Bond Test of TSVs in 3D ICs. 29th IEEE VLSI Test Symposium (VTS), 2011. CA, USA. 1-5 May 2011. 20-25.

- [7] Aoyagi, M., F. Imura, S. Nemoto, N. Watanabe, F. Kato, K. Kikuchi, H. Nakagawa, M. Hasimoto, H. Uchida and Y. Matsumoto. 2012. Wide Bus Chip-toChip Interconnection Technology Using Fine Pitch Bump Joint Array for 3D LSI Chip Stacking. IEEE CPMT Symposium Japan (ICSJ), 2012. Kyoto, Japan. 10-12 December 2012. 183-186

- [8] Kandalaft, N., R. Rashidzadeh, and M. Ahmadi. 2013. Testing 3-D IC Through-Silicon-Vias (TSVs) by Direct Probing. IEEE Transaction on Computer-Aided Design of Integrated Circuits and Systems. 32(4): 538-546.

- [9] Fkih, Y., P. Vivet, G. D. Natale, M-L. Flottes, and B. Rouzeyre. 2013. A 3D IC BIST for pre-bond test of TSVs using Ring Oscillators. IEEE 11th International New Circuits and Systems Conference (NEWCAS), 2013. Paris, France. 16-19 June 2013. 1-4.

- [10] Taouil, M., M. Masadeh, S. Hamdioui and E. J. Marinisen. 2014. Internconnect Test for 3D Stacked Memory-on-Logic. Design, Automation & Test in Europe Conference & Exhibition (DATE), 2014. Dresden, Germany. 24-28 March 2014. 1-6.

- [11] Chakurabarty, K., M. Agrawal, S. Deutsch, B. Noia, R. Wang, and F. Ye. 2014. Test and Design-for-Testability Solutions for 3D Integrated Circuits. IPSJ Transaction on System LSI Design Methodology. 7:56-73.

- [12] Gambino, J. P., S. A. Adderly, and J. U. Knickerbocker. 2015. An Overview of Through-Silicon-Via Technology and Manufacturing Challenges. Microelectronic Engineering. 135:73-106.

- [13] Kirihata, T., J. Golz, M. Wordeman, P. Batra, G. W. Maier, N. Robson, T. L. Graves-abe, D. Berger, and S. S. Lyer. 2016. Three-Dimensional Dynamic Random Access Memories Using Through-

- Silicon-Vias. IEEE Journal on Emerging and Selected Topics in Circuits and Systems. 6(3):373-384.

- [14] Chen, P. Y., C. W. Wu, and D. M. Kwai. 2009. On-Chip TSV Testing for 3D IC before Bonding Using Sense Amplification. The 18st IEEE Asian Test Symposium (ATS) 2009. Taichung, Taiwan. 23-26 November 2009. 450-455.

- [15] You, J. W., S. Y. Huang, D. M. Kwai, Y. F. Chou, and C. W. Wu. 2010. Performance Characterization of TSV in 3D IC via Sensitivity Analysis. The 19th IEEE Asian Test Symposium (ATS), 2010. Shanghai, China. 1-4 December 2010. 389-394.

- [16] Konishi, T., H. Yotsuyanagi, and M. Hashizume. 2012. Supply Current Testing of Open Defects at Interconnects in 3D ICs with IEEE 1149.1 Architecture. IEEE International Conference on 3D System Integration (3DIC), 2011. Osaka, Japan. 31 January – 2 February 2012. 8-2-1-8-2-6.

- [17] Konishi, T., H. Yotsuyanagi, and M. Hashizume. 2012. Electrical Test Method for Interconnect Open Defects in 3D ICs. Transaction of the Japan Institute of Electronics Packaging. 5(1):26-33.

- [18] Konishi, T., H. Yotsuyanagi, and M. Hashizume. 2012. A Built-in Test Circuit for Supply Current Testing of Open Defects at Interconnects in 3D ICs. 4th Electronics System-Integration Technology Conference (ESTC), 2012. Amsterdam, Netherlands. 17-20 September 2012. PA21.1\_1-PA21.1\_6.

- [19] Hashizume, M., T. Konishi, and H. Yotsuyanagi. 2013. Electrical Testable Design for Open Defects at Logic Signal Lines between Dies in 3D ICs. IEICE Transaction on Electronics. J96-C(11):361-370. (in Japanese).

- [20] Suenaga, S., M. Hashizume, H. Yotsuyanagi, S. K. Lu, and Z. Roth. 2013. DFT for Supply Current Testing to Detect Open Defects at Interconnects in 3D ICs. IEEE Electrical Design of Advanced Packaging & Systems Symposium (EDAPS), 2013. Nara, Japan. 12-15 December 2013. 60-63.

- [21] Hashizume, M., S. Umezu, H. Yotsuyanagi, and S. K. Lu. 2014. A Built-in Supply Current Test Circuit for Electrical Interconnect Tests of 3D ICs. IEEE International Conference on 3D System Integration (3DIC), 2014. Cork, Ireland. 1-3 December 2014. O7-1-O7-6.

- [22] Yotsuyanagi, H., A. Fujiwara, and M. Hashizume. 2015. On TSV Array Defect Detection Method Using Two Ring-oscillators Considering Signal Transitions at Adjacent TSVs. IEEE International Conference on 3D System Integration (3DIC), 2015. Sendai, Japan. 31 August 2 September 2015. TS8.24.1-TS8.24.4.

- [23] Nanbara, K., A. Odoriba, M. Hashizume, H. Yotsuyanagi and S. K. Lu. 2015. Electrical Interconnect Test of 3D ICs Made of Dies without ESD Protection Circuits with a Built-in Test Circuit. IEEE International Conference on 3D System Integration (3DIC), 2015. Sendai, Japan. 31 August 2 September 2015. TS8.22.1-TS8.22.5.

- [24] Odoriba, A., S. Umezu, M. Hashizume, H. Yotsuyanagi, A. A. B. Fara, and S. K. Lu. 2015. A Testable Design for Electrical Interconnect Tests of 3D ICs. 2015 International Conference on Electronics Packaging and iMAPS All Asia Conference 2015. Kyoto, Japan. 14-17 April 2015. 718-722.

- [25] Hashizume, M., M. Akutagawa, S. K. Lu, and H. Yotsuyanagi. 2013. Electrical Test Method of Open Defects at Bi-directional Interconnects in 3D ICs. 2013 International Conference on Electronics Packaging (ICEP) 2013. Osaka, Japan. 10-12 April 2013. 13-18.

- [26] Shiraishi, Y., M. Hashizume, H. Yotsuyanagi, T. Tada, and S. K. Lu. 2014. Electrical Test Method of Open Defects at Data Buses in 3D SRAM IC. 2014 International Conference on Electronics Packaging (ICEP) 2014. Toyama, Japan. 23-25 April 2014. 235-238.