## Scholars' Mine

**Masters Theses**

Student Theses and Dissertations

Summer 2010

# Time-domain thru-reflect-line (TRL) calibration error assessment and its mitigation and modeling of multilayer printed circuit boards (PCB) with complex area fills

Vysakh Sivarajan

Follow this and additional works at: https://scholarsmine.mst.edu/masters\_theses

Part of the Electrical and Computer Engineering Commons

Department:

#### **Recommended Citation**

Sivarajan, Vysakh, "Time-domain thru-reflect-line (TRL) calibration error assessment and its mitigation and modeling of multilayer printed circuit boards (PCB) with complex area fills" (2010). Masters Theses. 6907. https://scholarsmine.mst.edu/masters\_theses/6907

This thesis is brought to you by Scholars' Mine, a service of the Missouri S&T Library and Learning Resources. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

# TIME-DOMAIN THRU-REFLECT-LINE (TRL) CALIBRATION ERROR ASSESSMENT AND ITS MITIGATION

AND

# MODELING OF MULTILAYER PRINTED CIRCUIT BOARDS (PCB) WITH COMPLEX AREA FILLS

by

#### VYSAKH SIVARAJAN

#### A THESIS

Presented to the Faculty of the Graduate School of the

MISSOURI UNIVERSITY OF SCIENCE AND TECHNOLOGY

In Partial Fulfillment of the Requirements for the Degree

MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

2010

Approved by

James L. Drewniak, Advisor

David Pommerenke

Jun Fan

#### **ABSTRACT**

Part 1 for this thesis is on the error assessment of a time-domain (t-TRL) calibration technique. Application of the "Thru-Reflect-Line" (TRL) calibration to time-domain measurements of S-parameters (t-TRL) can be used for the characterization of the printed circuit boards (PCBs). However, t-TRL calibrated results still have deviations from the reference frequency-domain vector network analyzer (VNA) calibrated results. There are two main sources of errors in the t-TRL calibration. They are random errors, such as an additive noise and jitter, and systematic errors associated with cables, connectors, and port mismatches. This work addresses these two types of errors by proper selection of the number of sampling points, waveform averages, and time record. Methods tried out to eliminate or reduce these errors are detailed in this work. Measurements and simulations were performed for implementing these methods, and the results are explained. A t-TRL calibration automation tool based on TDR/TDT measurements has been developed.

Part 2 of this thesis is on the modeling of multilayer PCBs with complex area fills and floating planes. Noise on the power distribution network (PDN) and between the power area fills in multilayer PCBs with complex geometries is a significant concern. Modeling of such PCBs can be done with a cavity model approach. Correlation of a 3D EM solver results with the Multilayer Via Transition Tool (MVTT) results based on cavity model is explained here. Additional modeling and validation was done using the equivalent inductance method.

#### **ACKNOWLEDGMENTS**

I would like to express my utmost gratitude to my advisor, James L. Drewniak, for his constant support and guidance throughout the course of my master's degree program. I also wish to thank my committee members, Dr. David J. Pommerenke and Dr. Jun Fan for their research guidance on my work.

I also thank Brice Achkir at Cisco Systems for his valuable research, and technical input and advice that helped me finish my thesis.

Special thanks go to Dr. Victor Khilkevich for his valuable inputs and research guidance during my masters program. I am also grateful to Abhilash Rajagopal for introducing me to the Signal Integrity world and mentoring me during the early days in the EMC lab.

Finally, I thank my parents and fiancée for their constant emotional support and encouragement. I wish to dedicate this work to them.

### **TABLE OF CONTENTS**

| ABSTRACT                                                     | iii   |

|--------------------------------------------------------------|-------|

| ACKNOWLEDGMENTS                                              | iv    |

| LIST OF ILLUSTRATIONS                                        | . vii |

| SECTION                                                      |       |

| 1. INTRODUCTION TO TIME-DOMAIN CALIBRATION                   | 1     |

| 1.1. ERROR MODELS AND CALIBRATION METHODS                    | 3     |

| 1.2. ERROR ASSESSMENT OF THE T-TRL CALIBRATION TECHNIQUE     | . 11  |

| 1.2.1. Analyzing Random Errors                               | . 20  |

| 1.2.2. Analyzing Systematic Errors                           | . 33  |

| 1.3. TWO TIER CALIBRATIONS                                   | . 40  |

| 1.4. T-TRL CALIBRATION WITH SPLITTERS                        | . 45  |

| 1.5. APPLICATION OF T-TRL CALIBRATION                        | . 55  |

| 1.6. TIME-DOMAIN TRL CALIBRATION AUTOMATED TOOL              | . 59  |

| 1.7. CONCLUSIONS ON t-TRL ERROR ASSESSMENT                   | . 67  |

| REFERENCES                                                   | . 69  |

| 2. INTRODUCTION TO MODELING OF MULTILAYER PCBS               | . 71  |

| 2.1. MULTILAYER PCB STACKUP ANALYSIS                         | . 71  |

| 2.1.1. PCB study                                             | . 72  |

| 2.1.2. Analyzing the stackup in parts                        | . 74  |

| 2.1.3. Identifying return path                               | . 81  |

| 2.1.4. IC pin configuration and connections.                 | . 84  |

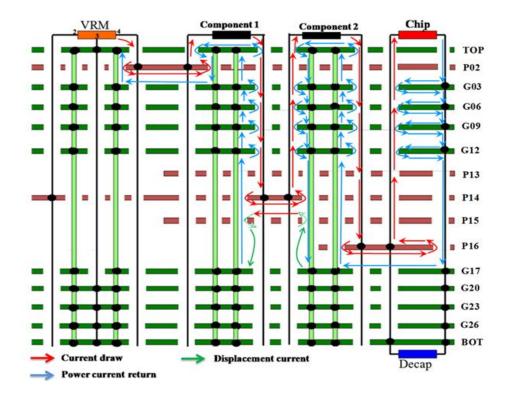

| 2.1.5. Current propagation through PCBs with floating planes | . 88  |

| 2.1.6. Circuit model using equivalent inductance method      | . 91  |

| 2.2. CONCLUSIONS ON PDN MODELING AND DESIGN | 95 |

|---------------------------------------------|----|

| REFERENCES                                  | 97 |

| VITA                                        | 98 |

### LIST OF ILLUSTRATIONS

| Figure 1.1: | Block diagram of different stages of the time-domain calibration                                                                    | 2    |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 1.2: | Block diagram representation of a two-port measurement system                                                                       | 3    |

| Figure 1.3: | Block diagram showing the SOLT calibration reference plane with respect to the DUT for a two port measurement setup                 | 4    |

| Figure 1.4: | Block diagram showing the TRL calibration reference plane with respect to the DUT for a two port measurement setup                  | 4    |

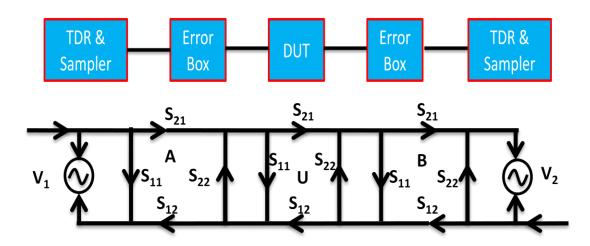

| Figure 1.5: | Block diagram and signal flow graph of a two port time-domain VNA system                                                            | 5    |

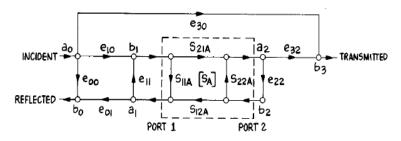

| Figure 1.6: | 12-term error model for the forward measurement direction                                                                           | 6    |

| Figure 1.7: | Error model for forward measurements with excitation on Port 1                                                                      | 7    |

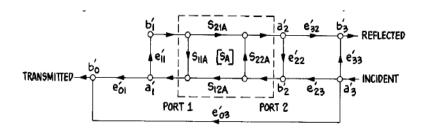

| Figure 1.8: | Error model for reverse measurements with excitation on Port 2                                                                      | 7    |

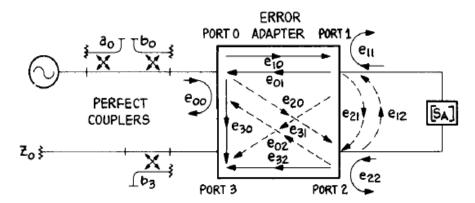

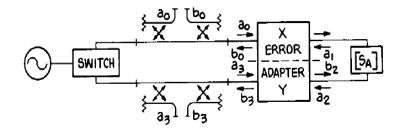

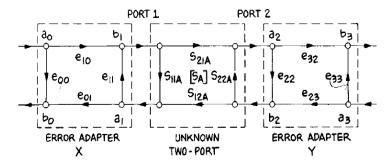

| Figure 1.9: | 8-term error adapter for two port measurements                                                                                      | 8    |

| Figure 1.10 | : Two separate error adapters with 8 error terms in total                                                                           | 8    |

| Figure 1.11 | : 8-term error model for two port measurements                                                                                      | 8    |

| Figure 1.12 | : Setup to measure the directivity, port match and frequency response                                                               | 9    |

| Figure 1.13 | : Setup to measure the leakage term                                                                                                 | 9    |

| Figure 1.14 | : Thru measurement setup                                                                                                            | . 10 |

| Figure 1.15 | : TRL calibration measurement setup using Agilent DCA-J 86100C                                                                      | . 12 |

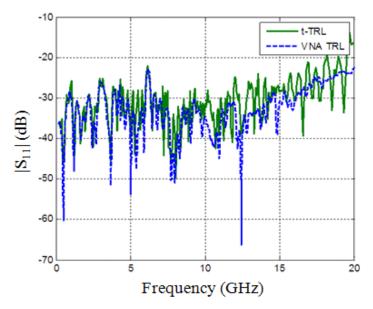

| Figure 1.16 | : S <sub>21</sub> magnitude comparison of the Test Line 1 of the Calibration Kit 1 measured by t-TRL using the TDR 1 and VNA TRL    | 13   |

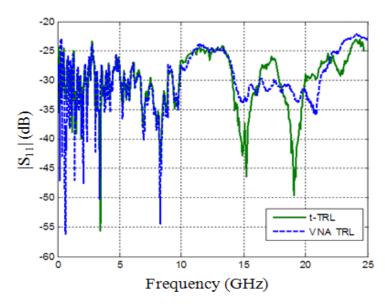

| Figure 1.17 | : S <sub>21</sub> magnitude comparison of the Test Line 1 of the Calibration Kit 2 measured by t-TRL using the TDR 2 and VNA TRL    | 13   |

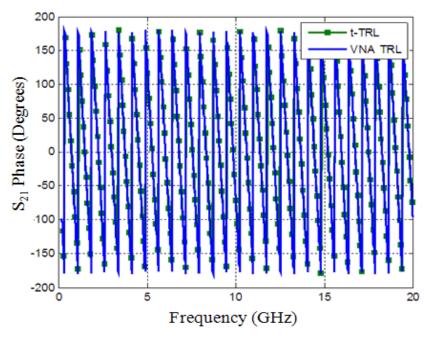

| Figure 1.18 | : Phase of the S <sub>21</sub> comparison of the Test Line 1 of the Calibration Kit 1 measured by t-TRL using the TDR 1 and VNA TRL | 14   |

| Figure 1.19 | : Phase of the S <sub>21</sub> comparison of the Test Line 1 of the Calibration Kit 2 measured by t-TRL using the TDR 2 and VNA TRL | 14   |

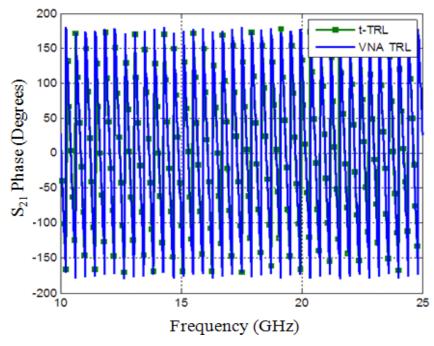

| Figure 1.20 | : S <sub>11</sub> magnitude comparison of the Test Line 1 of the Calibration Kit 1 measured by t-TRL using the TDR 1 and VNA TRL    | 15   |

| Figure 1.21 | : S <sub>11</sub> magnitude comparison of the Test Line 1 of the Calibration Kit 2 measured by t-TRL using the TDR 2 and VNA TRL    | 15   |

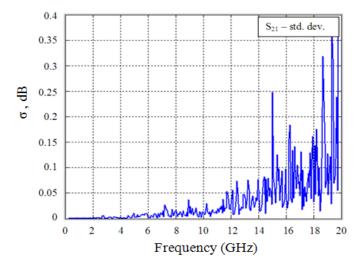

| Figure 1.22 | : Estimation of the standard deviation of the $S_{21}$ measurements                                                                 | . 16 |

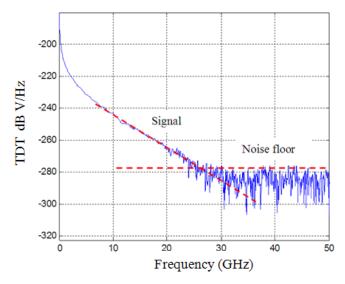

| Figure 1.23: | Spectrum of the TDT signal (TDR 1, 4096 samples, 10 ns time window, 256 averages)   | 17   |

|--------------|-------------------------------------------------------------------------------------|------|

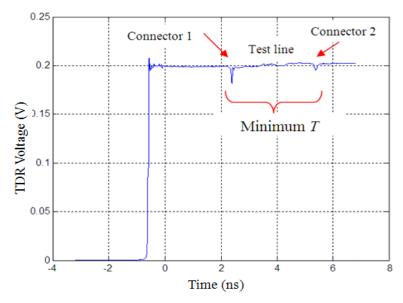

| Figure 1.24: | Minimum time record for TDR measurements                                            | . 18 |

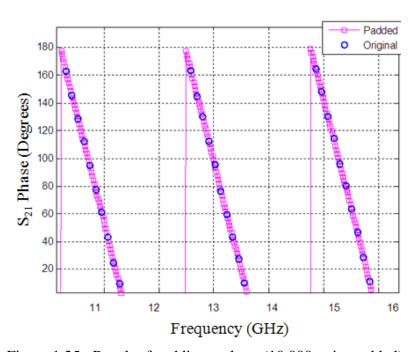

| Figure 1.25: | Result of padding – phase (10,000 points added).                                    | . 19 |

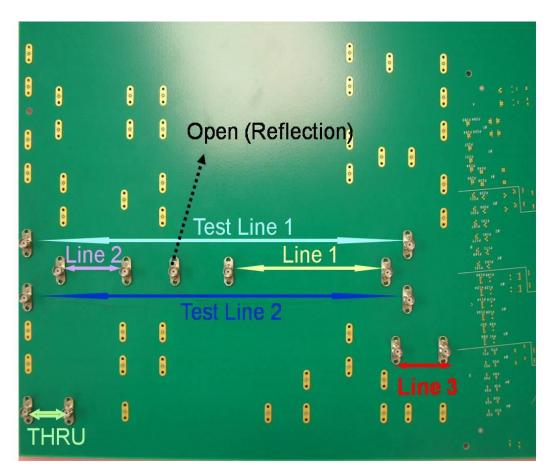

| Figure 1.26: | Test board used for the measurements                                                | . 20 |

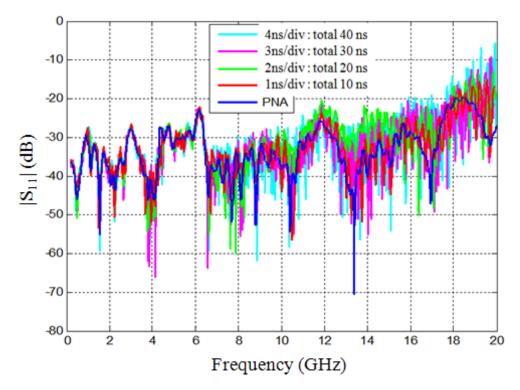

| Figure 1.27: | S <sub>11</sub> magnitude comparison with VNA for different points                  | . 21 |

| Figure 1.28: | S <sub>21</sub> magnitude comparison with VNA for different points                  | . 21 |

| Figure 1.29: | $S_{21}$ magnitude comparison with VNA for different points – zoomed                | . 22 |

| Figure 1.30: | S <sub>11</sub> magnitude comparison for different time record                      | . 23 |

| Figure 1.31: | S <sub>21</sub> magnitude comparison for different time record                      | . 23 |

| Figure 1.32: | Phase of S <sub>21</sub> comparison zoomed                                          | . 24 |

| Figure 1.33: | Increase in time record will increase the frequency resolution                      | . 24 |

| Figure 1.34: | Difference in the $S_{11}$ magnitude for different time record                      | . 25 |

| Figure 1.35: | Difference in the $S_{21}$ magnitude for different time record                      | . 25 |

| Figure 1.36: | Measurement setup for the Tektronix DSA 8200                                        | . 26 |

| Figure 1.37: | S <sub>11</sub> magnitude comparison with VNA                                       | . 27 |

| Figure 1.38: | S <sub>21</sub> magnitude comparison with VNA                                       | . 28 |

| Figure 1.39: | S <sub>21</sub> phase comparison with VNA                                           | . 28 |

| Figure 1.40: | Measurement setup with sampling heads connected directly to the board .             | 29   |

| Figure 1.41: | S <sub>11</sub> magnitude comparison for measurements without cables                | . 30 |

| Figure 1.42: | S <sub>21</sub> magnitude comparison for measurements without cables                | . 30 |

| Figure 1.43: | S <sub>21</sub> phase comparison with VNA for measurement without cables            | 31   |

| Figure 1.44: | S <sub>11</sub> magnitude comparison with VNA                                       | . 32 |

| Figure 1.45: | S <sub>21</sub> magnitude comparison with VNA                                       | . 32 |

| Figure 1.46: | S <sub>21</sub> phase comparison with VNA                                           | . 33 |

| Figure 1.47: | 12-term error model for forward and reverse measurements                            | . 34 |

| Figure 1.48: | Measurement results showing the corresponding generator state                       | . 35 |

| Figure 1.49: | Spectrum of the signal showing diode state error                                    | . 35 |

| Figure 1.50: | Windowing of the TDR/TDT waveforms to eliminate the effect of the diode state error | 36   |

| Figure 1.51: | Improvement by applying waveform windowing                                          | . 36 |

| Figure 1.52: | ADS model for TDR with reflective port                                              | . 37 |

| Figure 1.53: | Simulation results showing higher order reflections                          | 38 |

|--------------|------------------------------------------------------------------------------|----|

| Figure 1.54: | 4 sampler VNA and the measurement of S-parameters                            | 39 |

| Figure 1.55: | Two tier calibration for 3 sampler VNA                                       | 39 |

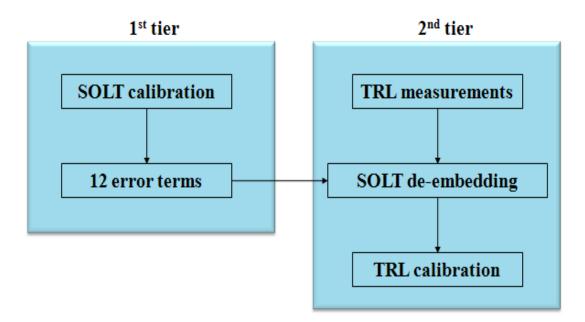

| Figure 1.56: | Two tier calibration block diagram                                           | 40 |

| Figure 1.57: | SOLT calibration comparison of S <sub>11</sub> magnitude with the VNA        | 41 |

| Figure 1.58: | SOLT calibration comparison of $S_{21}$ magnitude with the VNA               | 41 |

| Figure 1.59: | Two tier calibration with 1st tier calibrated by E-calibration               | 42 |

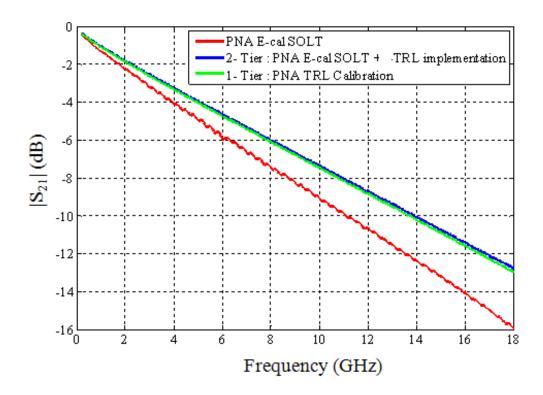

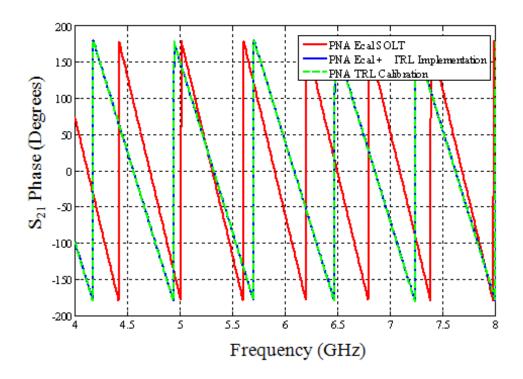

| Figure 1.60: | Two tier calibration on frequency-domain data, $S_{21}$ magnitude            | 43 |

| Figure 1.61: | Two tier calibration on frequency-domain data, $S_{21}$ phase                | 43 |

| Figure 1.62: | Two tier calibration on time-domain data, S <sub>11</sub> magnitude          | 44 |

| Figure 1.63: | Two tier calibration on time-domain data, S <sub>21</sub> magnitude          | 45 |

| Figure 1.64: | ADS model for TDR forward measurement                                        | 46 |

| Figure 1.65: | ADS model for TDR reverse measurement                                        | 46 |

| Figure 1.66: | TDR pulse comparison                                                         | 46 |

| Figure 1.67: | Switching error simulation using the ADS model                               | 47 |

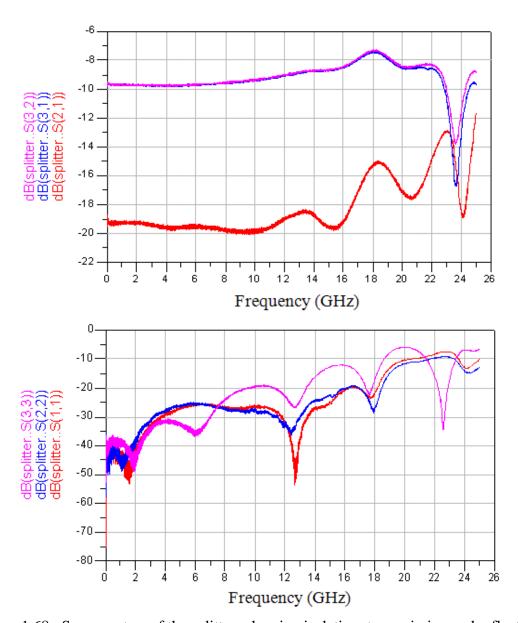

| Figure 1.68: | S-parameters of the splitters showing isolation, transmission and reflection | 48 |

| Figure 1.69: | ADS model for the TDR measurement setup with splitters                       | 49 |

| Figure 1.70: | Simulated results showing fewer undulations with more isolation              | 49 |

| Figure 1.71: | Block diagram for measurement setup 1                                        | 50 |

| Figure 1.72: | Measurement setup 1                                                          | 50 |

| Figure 1.73: | Results from the measurement setup 1                                         | 51 |

| Figure 1.74: | Sampler pulse causing parasitic waveforms                                    | 52 |

| Figure 1.75: | Block diagram for measurement setup 2                                        | 52 |

| Figure 1.76: | Using short cables to connect TDR generators to splitters                    | 53 |

| Figure 1.77: | Results from the measurement setup 2                                         | 53 |

| Figure 1.78: | Block diagram for measurement set up 3                                       | 54 |

| Figure 1.79: | Connecting TDR generators directly to splitters                              | 54 |

| Figure 1.80: | Results from the measurement setup 3                                         | 55 |

| Figure 1.81: | PCB board used for material extraction                                       | 57 |

| Figure 1.82: | Flow-chart for the dielectric parameter extraction procedure                 | 57 |

| Figure 1.83: Dielectric constant extracted comparison                            | 58   |

|----------------------------------------------------------------------------------|------|

| Figure 1.84: Loss tangent extracted comparison                                   | 58   |

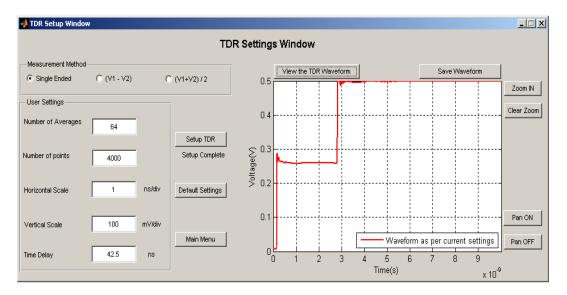

| Figure 1.85: Main Window                                                         | 59   |

| Figure 1.86: TDR setup options                                                   | 60   |

| Figure 1.87: TDR setup with user defined parameters (single ended)               | 61   |

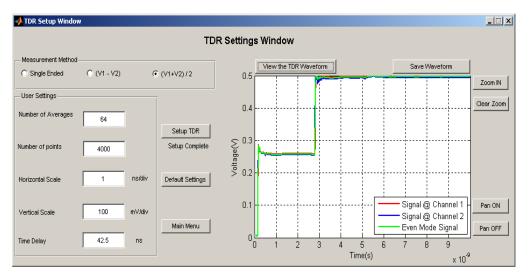

| Figure 1.88: TDR setup with user defined parameters (even mode)                  | 61   |

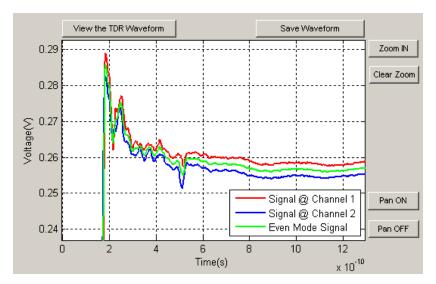

| Figure 1.89: Zoom in and Pan options                                             | 62   |

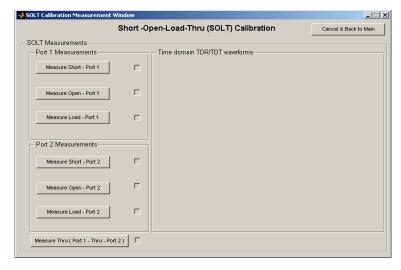

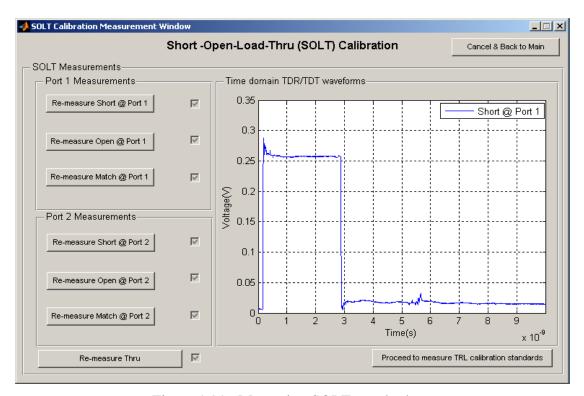

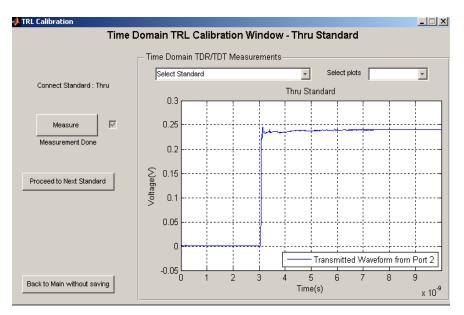

| Figure 1.90: SOLT calibration measurement window                                 | 62   |

| Figure 1.91: Measuring SOLT standards                                            | 63   |

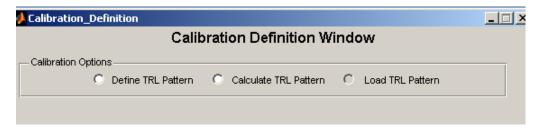

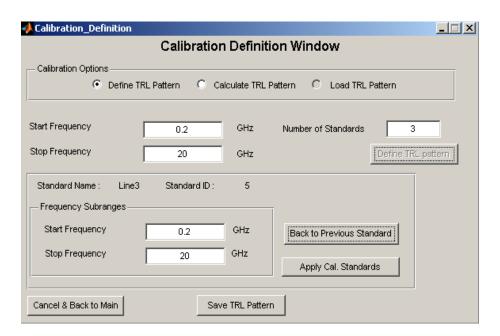

| Figure 1.92: TRL calibration pattern options                                     | . 64 |

| Figure 1.93: Defining a TRL pattern                                              | 64   |

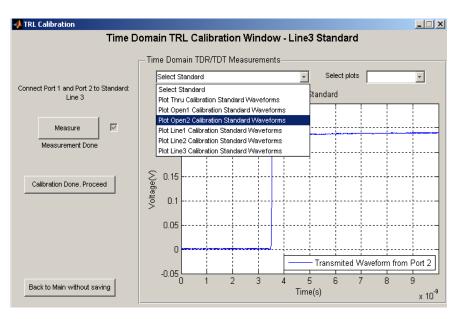

| Figure 1.94: Measuring the TRL standard                                          | 65   |

| Figure 1.95: Options for viewing all the measured time-domain waveforms          | 65   |

| Figure 1.96: Cut point selection/calculation window                              | 66   |

| Figure 1.97: Measuring the DUT once calibration is defined                       | 66   |

| Figure 1.98: Main window giving options to view the calibrated results           | 67   |

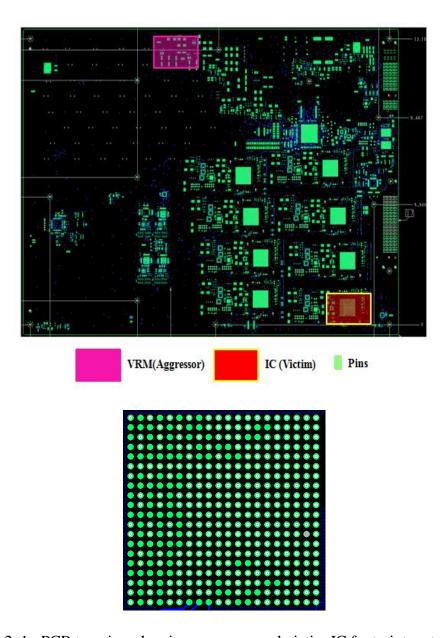

| Figure 2. 1: PCB top view showing aggressor and victim IC footprint on top layer | 73   |

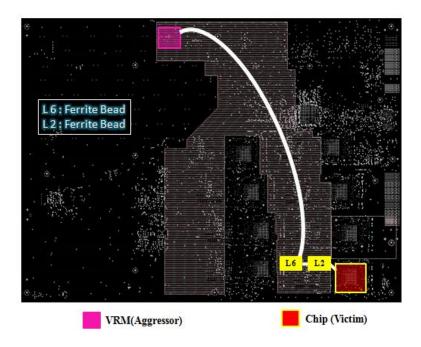

| Figure 2. 2: Current path from the VRM to the chip                               | 74   |

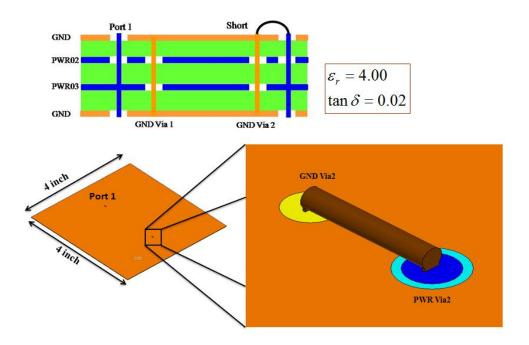

| Figure 2. 3: HFSS model for the 3 layer PCB showing area fill                    | 75   |

| Figure 2. 4: Shapes of the planes modeled in HFSS                                | 76   |

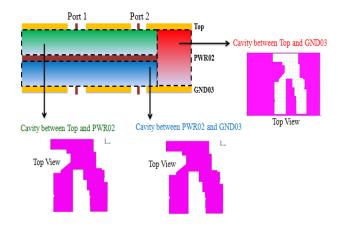

| Figure 2. 5: Cavity formation in the stackup                                     | 77   |

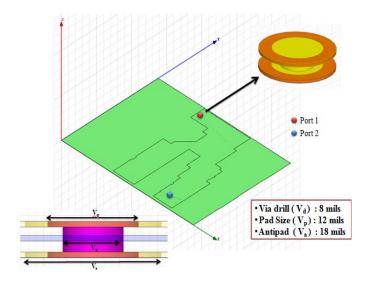

| Figure 2. 6: HFSS model showing ports and padstack                               | 77   |

| Figure 2. 7: MVTT created plane shape and HFSS model                             | 78   |

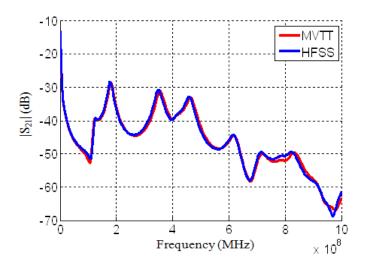

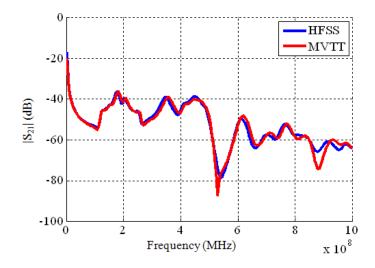

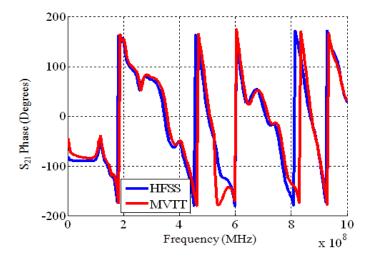

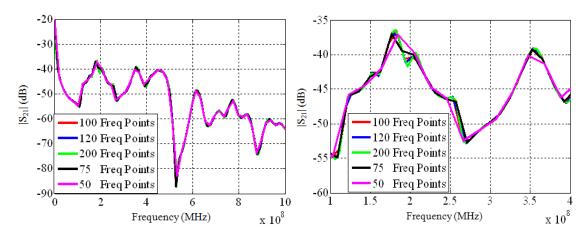

| Figure 2. 8: S <sub>21</sub> Magnitude simulation results comparison             | 78   |

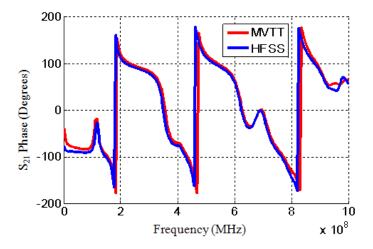

| Figure 2. 9: S <sub>21</sub> Phase simulation results comparison                 | 79   |

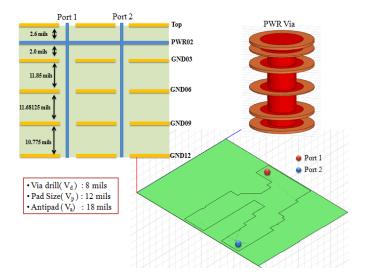

| Figure 2. 10: 12 layer stack and padstack                                        | 79   |

| Figure 2. 11: S <sub>21</sub> Magnitude simulation results comparison            | 80   |

| Figure 2. 12: S <sub>21</sub> Phase simulation results comparison                | 80   |

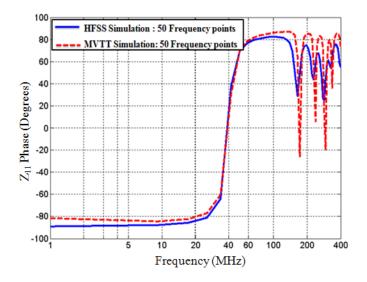

| Figure 2. 13: Simulation with different frequency points                         | 81   |

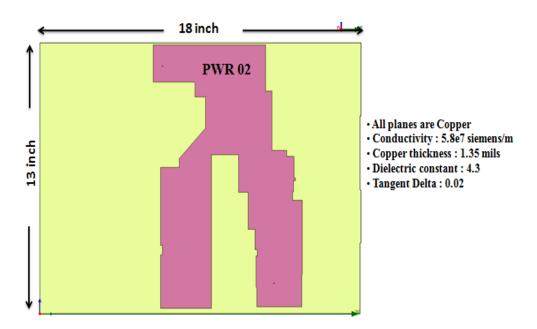

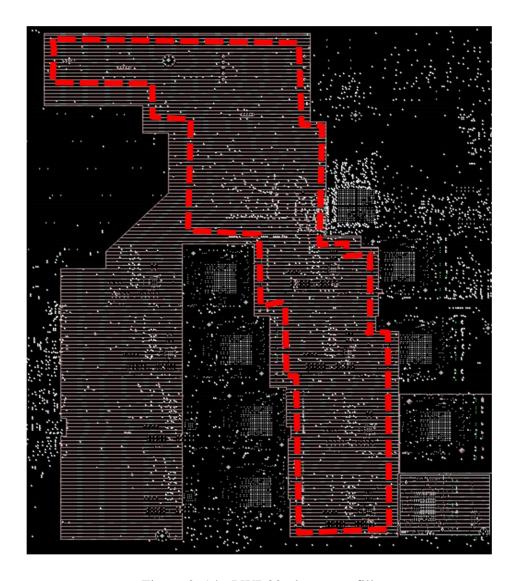

| Figure 2. 14: PWR02 plane area fill                                              | 82   |

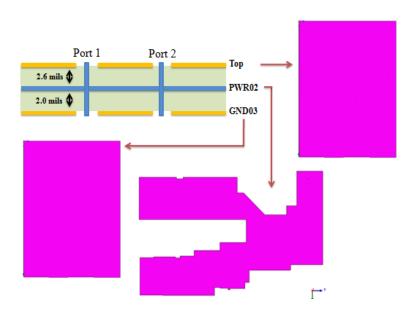

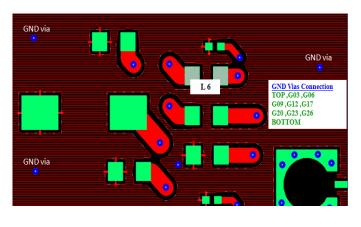

| Figure 2. 15: GND vias nearby ferrite beads                                      | 83   |

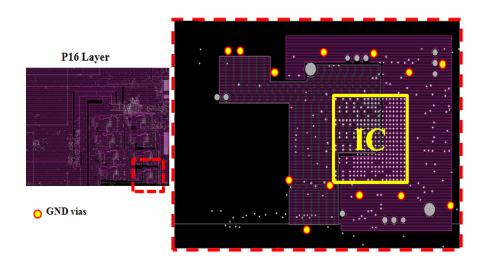

| Figure 2. 16: | P16 Layer area fill and nearby GND vias                        | . 84 |

|---------------|----------------------------------------------------------------|------|

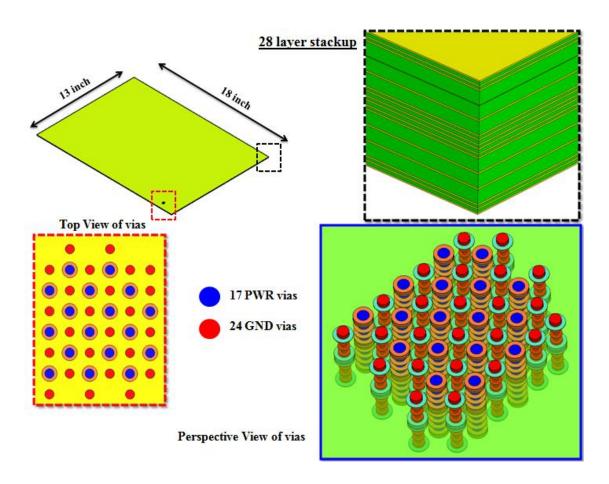

| Figure 2. 17: | HFSS model for the 28 layer PCB with 41 vias                   | . 85 |

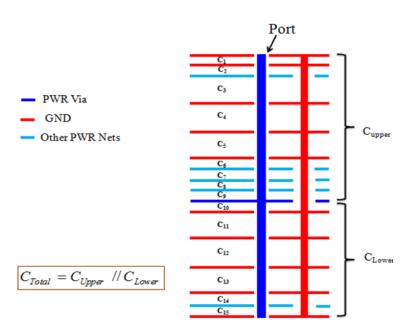

| Figure 2. 18: | Stackup side view and calculation of low frequency capacitance | . 86 |

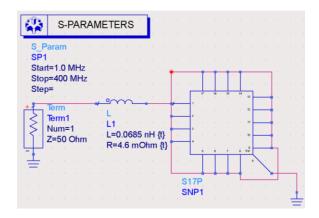

| Figure 2. 19: | ADS model used for post processing                             | . 87 |

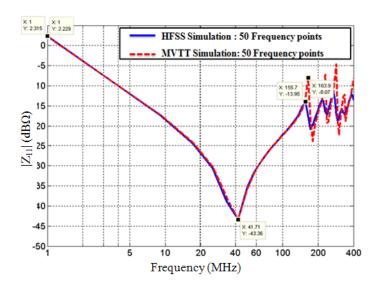

| Figure 2. 20: | Phase of Z <sub>11</sub> comparison                            | . 87 |

| Figure 2. 21: | Phase of Z <sub>11</sub> comparison.                           | . 88 |

| Figure 2. 22: | Tracing current through PCB stackup                            | . 89 |

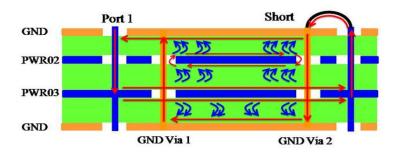

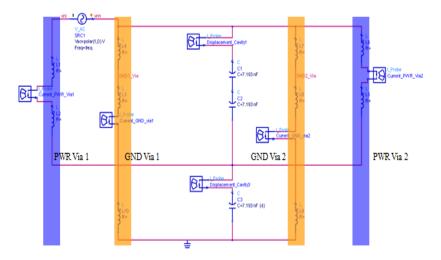

| Figure 2. 23: | 4 layer geometry with floating plane                           | . 90 |

| Figure 2. 24: | Tracing current through 4 layer stackup.                       | . 91 |

| Figure 2. 25: | Circuit model for 4 layer stackup                              | . 91 |

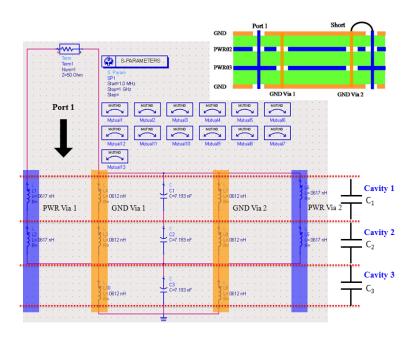

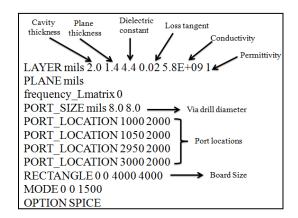

| Figure 2. 26: | EZPP sample input file                                         | . 92 |

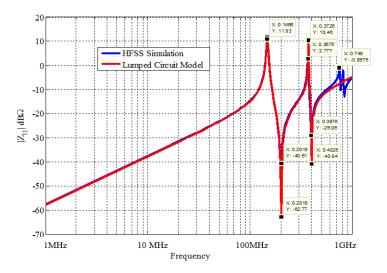

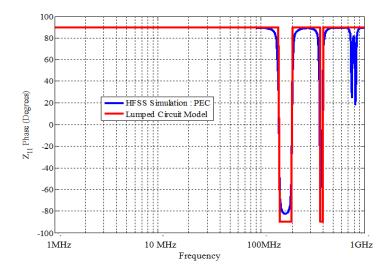

| Figure 2. 27: | Z <sub>11</sub> magnitude comparison                           | . 92 |

| Figure 2. 28: | Z <sub>11</sub> phase comparison                               | . 93 |

| Figure 2. 29: | Calculating current through stackup by circuit model           | . 93 |

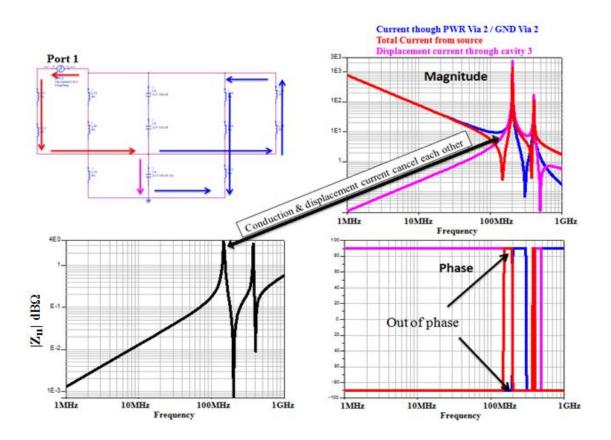

| Figure 2. 30: | 1st parallel resonance                                         | . 94 |

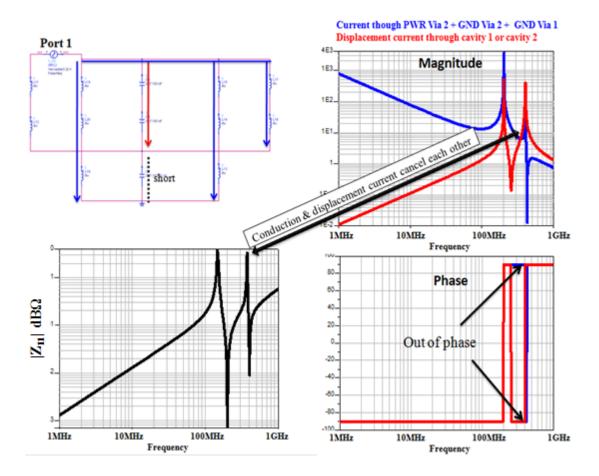

| Figure 2. 31: | 2nd parallel resonance                                         | . 95 |

#### 1. INTRODUCTION TO TIME-DOMAIN CALIBRATION

Measurements are subject to uncertainty. These uncertainties characterize the deviation of the measured values from the actual values. Un-corrected measurements or measurements without any calibration technique applied will have less accuracy but can be very fast and easy. In the case of S-parameter measurements using vector network analyzers (VNA), the device under test (DUT) measured will have the effects of the cables, connectors, measurement errors and port mismatches. The true response of the DUT can be obtained if these effects are removed or characterized.

Interconnect and printed circuit board (PCB) characterization using conventional calibration methods are widely used in high-speed digital systems. Accurate wideband characterization of PCB dielectric materials is becoming increasingly important for the high-speed digital designs as the data rates are raising. The material properties governing the performance of the signal passing through a transmission line are frequency-dependent. The characterization implies measuring S-parameters of the transmission line and extraction of the dielectric substrate parameters, such as relative permittivity or dielectric constant Dk and loss tangent or dissipation factor Df [1]. The measurements can be performed using a conventional VNA in the frequency-domain.

Application of the "Thru-Reflect-Line" (TRL) calibration technique to the VNAs allows for calibrating the instrument to take into account the discontinuities associated with the cable and on-board connectors [2]. However, the cost of a VNA is high. At the same time, time-domain reflection/transmission measurements can be a cheaper alternative to the VNA. Time-domain Reflectometry (TDR) allows for cost effective and faster ways to characterize the PCBs for high-speed digital design. In this work, time-domain calibration using TDR is studied and the errors associated with the calibration is identified. Methods for eliminating these errors are in the literature. These methods were implemented and the results are analyzed.

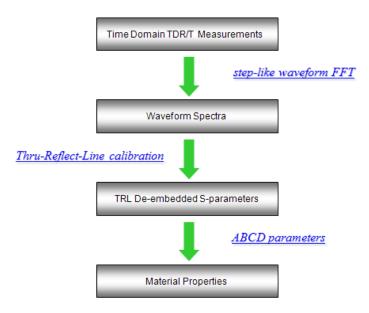

Application of the TRL calibration technique to time-domain measurements (t-TRL) assumes the calculation of TDR/TDT waveform spectra using the complete-fast-

Fourier-transform (CFFT) [4], and application of the TRL algorithm in the frequency-domain.

In reference [5], a complete step-by-step t-TRL calibration procedure has been detailed and compared to VNA measurements up to 25 GHz. It has been shown that the t-TRL technique is widely used for the characterization of the PCBs. However, t-TRL calibrated results still deviate from the reference frequency-domain VNA calibrated results. A block diagram of the time-domain calibration process is shown below in Figure 1.1. In reference [5], design of a complete TRL calibration pattern is explained. The design is based on the requirements of the TRL calibration standards [6].

Figure 1.1: Block diagram of different stages of the time-domain calibration

The errors associated with the time-domain S-parameter measurements are analyzed in this work. The time-domain calibrated results are compared with the corresponding frequency-domain VNA measurements. Also, the material parameter extraction algorithm to the S-parameter measured in the time-domain is applied.

#### 1.1. ERROR MODELS AND CALIBRATION METHODS

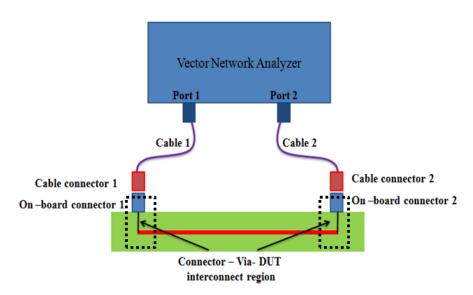

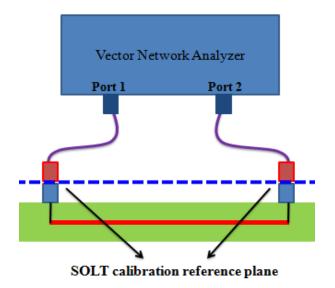

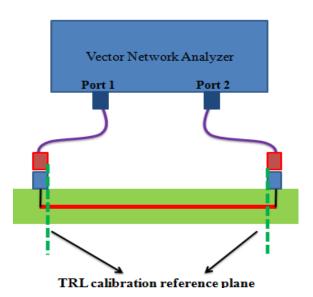

The TRL technique takes into account the discontinuities caused by the connector transitions and the connector-via transitions on the board. Figure 1.2 shows a block diagram of a similar connection to a PCB from a connector. There is cable to connector transition and then a connector to via transition. The DUT which is red in color, is a stripline structure as shown in the Figure 1.2. A Short-Open-Load-Thru (SOLT) calibration which is applied at the cables ends, does not take into account the connector to via transition. This transition is taken as a part of the DUT. The SOLT calibration leads to inaccurate measurement of the DUT. By applying a TRL calibration, the reference plane is shifted as shown in the Figure 1.4 and a more precise measurement can be made.

Figure 1.2: Block diagram representation of a two-port measurement system

The SOLT calibration reference plane is the blue line shown in the Figure 1.3. Here the DUT measurement will include the responses from the DUT along with the response from the unwanted interconnect region. The TRL calibration reference plane with respect to the DUT is shown in Figure 1.4, and will give the response of the DUT alone.

Figure 1.3: Block diagram showing the SOLT calibration reference plane with respect to the DUT for a two port measurement setup

Figure 1.4: Block diagram showing the TRL calibration reference plane with respect to the DUT for a two port measurement setup

The calibration procedures make a marked improvement when measuring two port systems with adaptors, cables and other connectors. Some of the common errors that

are there in the two port calibration are directivity errors, frequency response errors and port mismatch errors. The calibration procedures will combine all the effects caused by the cables, connectors and ports into error terms or boxes. The number of error terms in general is the square of the number of ports. The error terms can be measured and by using the signal flow graph, a complete error model can be obtained. Depending upon the measurement which can be coaxial or non coaxial, and the measurement setup, different error models can be adopted for two port calibration.

It is important to understand the error models adopted. It is easy to explain the error models from a VNA perspective. The error models of the frequency-domain VNAs are similar to that of the time-domain VNAs. It is shown that general VNA calibration techniques apply directly in time-domain VNAs [9]. The difference is only in the internal circuitry of the VNA and TDR that measures the signals. A block diagram for a two port time-domain system and its signal flow graph are shown in Figure 1.5.

Figure 1.5: Block diagram and signal flow graph of a two port time-domain VNA system

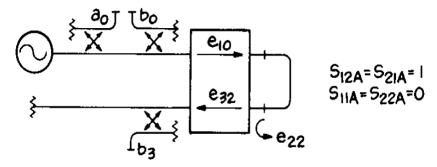

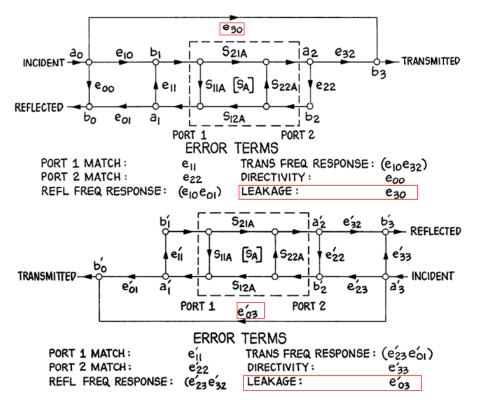

The 12-term error model is widely used in calibration. As seen from Figure 1.6, the error model for the forward and reverse direction measurements has 12 error terms each [12]. There are 24 error terms in total. Out of these error terms, some primary error terms are taken into consideration and the 24-term error model is simplified.

Figure 1.6: 12-term error model for the forward measurement direction

The error terms for the forward direction are:

- Port mismatch e<sub>11</sub> when Port 1 is not terminated with a matched impedance and e<sub>22</sub> when Port 2 is not terminated with a matched impedance

- Directivity e00 which is the ratio of the leakage of the incident signal to the reflected signal.

- Reflection tracking e<sub>10</sub>e<sub>01</sub> and transmission tracking e<sub>32</sub> e<sub>10</sub>

- Leakage e<sub>30</sub>, e<sub>20</sub>, e<sub>02</sub>, e<sub>31</sub>, e<sub>21</sub> and e<sub>12</sub> which are the crosstalk terms between the ports.

There are a total of 12 terms each for forward and reverse direction. Thus there is a sum total of 24 error terms. Certain error terms are not significant in terms of the signal strength when compared to the other terms. These terms can be neglected and a simpler error model with fewer error terms results. After neglecting the insignificant error terms, the 24-term error model reduces to a 12-term error model, with primary error terms:

- Port mismatch e<sub>11</sub> and e<sub>22</sub>

- Directivity e<sub>00</sub>

- Reflection tracking  $e_{10}e_{01}$  and transmission tracking  $e_{32}$   $e_{10}$

- Leakage e<sub>30</sub>

Solving the 12 term error model can give four simultaneous measured S parameter equations [12]. Signal flow graphs for the forward and reverse measurements are shown in Figure 1.7 and Figure 1.8.

Figure 1.7: Error model for forward measurements with excitation on Port 1

Figure 1.8: Error model for reverse measurements with excitation on Port 2

Each actual S-parameter calculated from a DUT measurement needs all four S-parameters as well as the 12 error terms. Two measurements each can be made for the forward where the excitation is on Port 1 and the reverse directions where the excitation is on Port 2. Each of them is a function of the four S-parameters of the DUT as well as the error terms. Error terms can be obtained from the calibration procedure. The signal flow graphs can be solved to get the actual S-parameters of the DUT.

An eight term error model can be derived from the 12-term model. The basic assumption is that the VNA switch is prefect and has same S-parameters for both forward and reverse direction measurements [12]. The error adaptor is separated into an X-error adapter and Y-error adapter as shown in Figure 1.9. There will be no leakage between the adapters. Here the measurement is modified with error adapter X on one side for Port 1

and error adapter Y on the other side for Port 2 as shown in Figure 1.10. The well known calibration using the 8 term error model is the TRL calibration [2]. The eight error terms are  $e_{10}$ ,  $e_{01}$ ,  $e_{00}$  and  $e_{11}$  for Port 1 and  $e_{32}$ ,  $e_{23}$ ,  $e_{22}$  and  $e_{33}$ . The error model of the 8 term model is shown in Figure 1.11

Figure 1.9: 8-term error adapter for two port measurements

Figure 1.10: Two separate error adapters with 8 error terms in total

Figure 1.11: 8-term error model for two port measurements

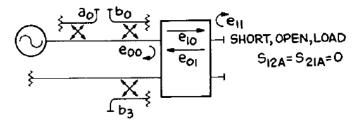

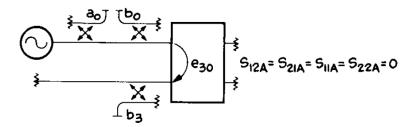

For calculating the error terms, there are different calibration methods. There are mainly two calibration procedures for two port systems. An SOLT calibration, which is fast and has good accuracy but is problematic to use for non-coaxial measurements and the TRL calibration, which is time consuming and has very good accuracy and is suitable for non-coaxial media. The SOLT calibration is a widely used calibration method [12]. One set of measurements is used for the forward direction on Port 1 and same set of measurements is used for reverse direction on Port 2. It is very important to accurately know the terminations used for the measurements. The first set of measurements is done with a Short, an Open, and a Load on Port 1. These measurements allow characterization of these three error terms for one measurement direction which are the equivalent directivity  $e_{00}$ , the port mismatch  $e_{11}$ , and the reflection tracking  $e_{10e01}$  as shown in Figure 1.12. 12-term error model has a leakage term. SOLT calibration allows considering this leakage term too [12]. Leakage term (e30) is measured by placing matched terminations on both ports as shown in Figure 1.13. The final part is connecting port 1 and port 2 together. This is the THRU connection as shown in Figure 1.14.

Figure 1.12: Setup to measure the directivity, port match and frequency response

Figure 1.13: Setup to measure the leakage term

Figure 1.14: Thru measurement setup

These three sets of measurements can yield six error terms for the forward directions. Another set for the reverse directions, then all the 12 error terms can be measured. The SOLT calibration is based on the known short, open and matched standards. One of the main disadvantages of the SOLT calibration is that the standards used are always imperfect to some degree. It is practically difficult to make a perfect open. A short standard will have some inductance associated with it, and the open standard will have some fringing capacitance. These imperfections lead to errors in the measurements. These errors will be significantly larger at higher frequencies.

The TRL calibration does not rely on known standards. It needs three connections such as a Thru, Reflect and Line. The reflect connection can be a short or open which basically has a large reflection coefficient. These connections are applied at the reference plane and the S-parameters are measured. The error boxes are characterized by S-parameters. Using equations obtained from the signal flow graphs; measured S-parameters are obtained at the measurement plane in terms of the S-parameters of the error boxes. S-parameters of the DUT can be measured and then corrected using the TRL error boxes to get the S-parameters at the reference planes. Basic TRL requirements of the standards are noted below. The TRL Calibration standard selection is as follows.

For the Reflect standard, the reflection coefficient ( $\Gamma$ ) magnitude need not be known and the phase of the  $\Gamma$  must be known within  $\pm$  ½ wavelengths. For non-zero length THRU, the characteristic impedance  $Z_0$  of the THRU and LINE must be same, and the attenuation of the THRU is assumed to be zero. For the LINE standard, the Attenuation of the LINE need not be known, the phase need to be specified within ½

wavelengths, the bandwidth of the single THRU/LINE pair is 8:1 and the TRL calibration references the DUT S-parameters to the impedance of the LINE standard. For the Match standard, it assumes matched terminations on both ports.

A network analyzer measures S-parameters as the ratios of complex voltages. The reference plane is at some point inside the VNA, so the measurement will include losses and phase delays caused by the effects of connectors, cables, port mismatch, via transitions etc. A calibration method can include these effects as error boxes placed between the measurement plane and the desired reference plane. A calibration technique can then characterize these error boxes and the error corrected S-parameters of the DUT can be obtained.

#### 1.2. ERROR ASSESSMENT OF THE T-TRL CALIBRATION TECHNIQUE

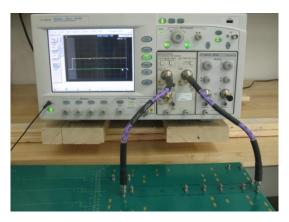

One of the major goals of the t-TRL project is to assess the errors associated with the TRL implementation and the measurement process. The instrument used in the beginning of the work was the Agilent DCA-J 86100C TDR module with 35ps rise time. The receiver bandwidth of this model is 18GHz. The second instrument used was a Tektronix DSA 8200 with E10 TDR modules. The maximum bandwidth of E10 modules is 50GHz. The entire measurement procedure is automated into a calibration wizard tool, which is explained later. A calibration wizard works as a standalone application and lets the user to do the measurement/t-TRL calibration easily.

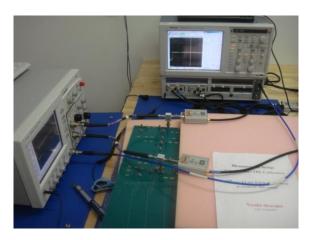

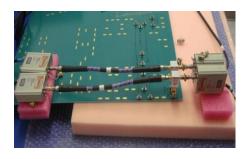

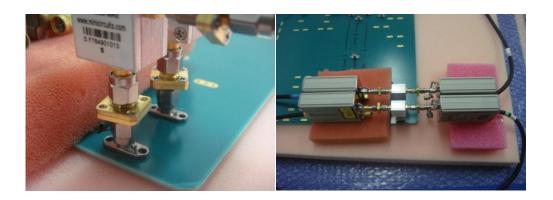

The measurement test setup is shown below in Figure 1.15. The cables used for the measurements are from Gore Associates and are very low loss cables. The connectors are 3.5mmm precision. The connectors on the board are 3.5 mm female SMA Molex connectors. Most of the measurements were taken after one or one and half hours after switching on the instrument. This was done to make sure that the instrument is warmed up and in stable working condition. THE time-domain measurements are performed using t-TRL calibration tool. The tool measures and save the time-domain waveforms and process the waveforms using the TRL calibration technique to give the calibrated S-parameters of the DUT.

Figure 1.15: TRL calibration measurement setup using Agilent DCA-J 86100C

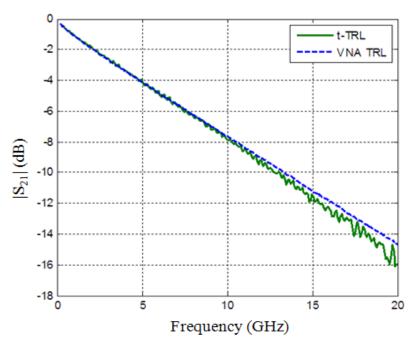

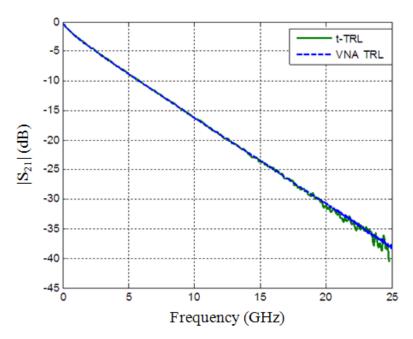

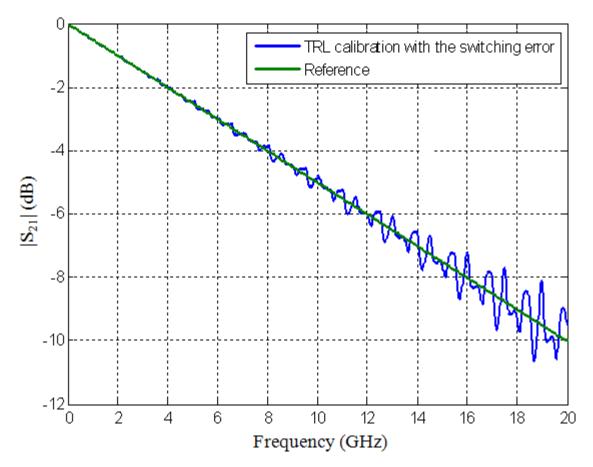

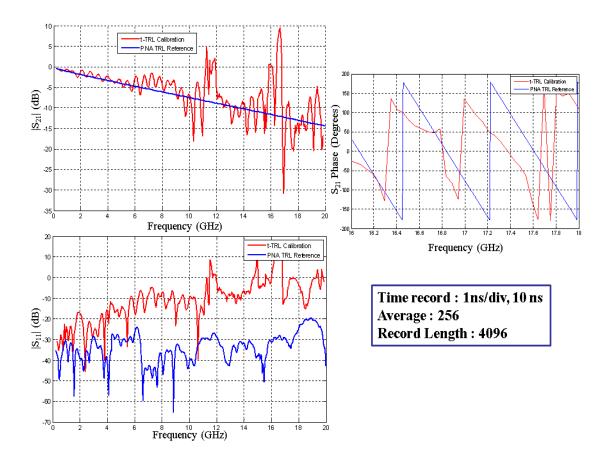

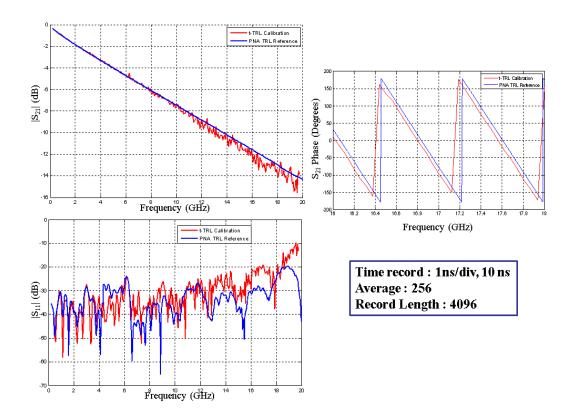

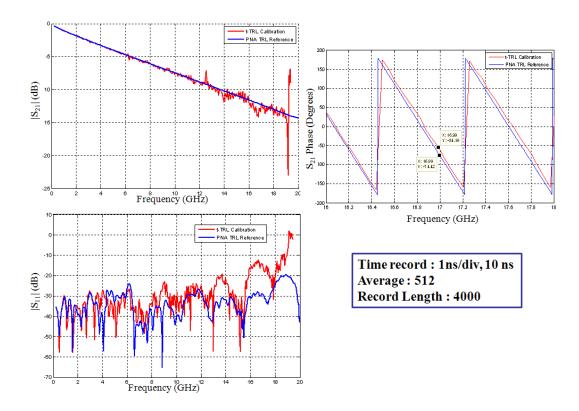

There are two kinds of errors associated with t-TRL measurements. They are random errors and systematic errors. Random errors are due to the noise of the TDR receiver and generator, as well as time jitter and calibration imperfections because of connector inconsistency and cable bend. Systematic errors are caused by cable and connector effects, port mismatches, and nonlinearities of the instrument. These systematic errors, associated with the instrument ports, cables and connectors, can be effectively eliminated by the proper TRL calibration, as VNA measurements show. At the same time, application of the t-TRL calibration to the measurements by two TDR instruments with different bandwidths results in residual errors, illustrated by Figure 1.16 and Figure 1.17. TDR 1 has 18 GHz bandwidth and TDR 2 has 50 GHz bandwidth. Parameters of the TRL kits 1 and 2 applied for calibrating these two TDR instruments and VNAs are explained in the paper [5].

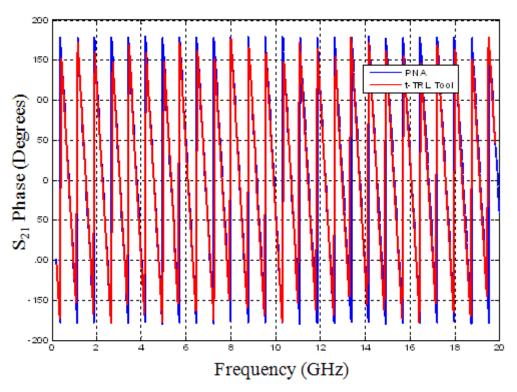

These TRL kits were manufactured using standard PCB technology with copperclad FR-4 type dielectric substrates. The VNA results are used as reference. Magnitude of  $S_{11}$  measured by t-TRL using TDR 1 for calibration Kit 1 and 2 are shown in Figure 1.16 and Figure 1.17. The phase of  $S_{21}$  measured by t-TRL using TDR 1 for calibration Kit 1 and 2 are shown in Figure 1.18 and Figure 1.19 and the magnitude of  $S_{11}$  measured by t-TRL using TDR 1 for calibration Kit 1 and 2 are shown in Figure 1.20 and Figure 1.21.

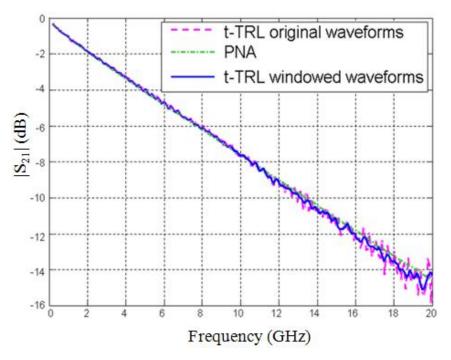

Figure 1.16:  $S_{21}$  magnitude comparison of the Test Line 1 of the Calibration Kit 1 measured by t-TRL using the TDR 1 and VNA TRL

Figure 1.17:  $S_{21}$  magnitude comparison of the Test Line 1 of the Calibration Kit 2 measured by t-TRL using the TDR 2 and VNA TRL

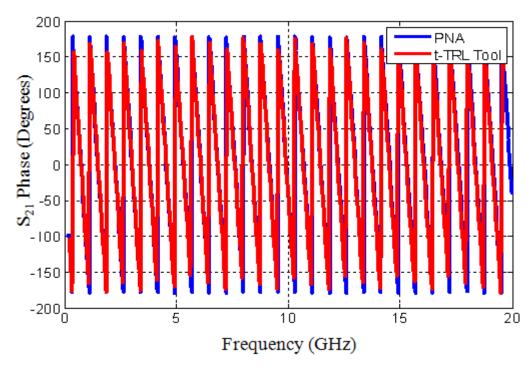

Figure 1.18: Phase of the  $S_{21}$  comparison of the Test Line 1 of the Calibration Kit 1 measured by t-TRL using the TDR 1 and VNA TRL

Figure 1.19: Phase of the  $S_{21}$  comparison of the Test Line 1 of the Calibration kit 2 measured by t-TRL using the TDR 2 and VNA TRL

Figure 1.20: S<sub>11</sub> magnitude comparison of the Test Line 1 of the Calibration Kit 1 measured by t-TRL using the TDR 1 and VNA TRL

Figure 1.21: S<sub>11</sub> magnitude comparison of the Test Line 1 of the Calibration Kit 2 measured by t-TRL using the TDR 2 and VNA TRL

The error in  $S_{21}$  measurement is approximately 1.5 dB for TDR 1 and 1 dB for TDR 2 at 20 GHz. The phase error is 4 degrees for TDR 1 and 7 degrees for TDR 2 at 20 GHz which is a minor value considering the electrical length of the line. The accuracy of

the  $S_{11}$  measurement of the transmission lines is not critical for most applications. A statistical analysis was performed in order to determine the nature of errors in the  $S_{21}$  measurements. Magnitude of  $S_{21}$  of the test transmission line was measured by TDR 1 ten times, and the standard deviation  $\sigma$  was calculated which is shown in Figure 1.22. The discrepancy between the t-TRL TDR measurement and frequency-domain VNA TRL measurement of  $S_{21}$  is about 1.5 dB at 20 GHz as shown in Figure 1.16.

At the same time, the standard deviation  $\sigma$  of t-TRL  $S_{21}$  measurement is less than 0.4 dB at the same frequency. This indicates that the systematic component in the  $S_{21}$  measurement error dominates. The same conclusion can be made by estimating the signal-to-noise ratio (SNR) of the transmitted signal for the test line. The TDT signal was measured for test line 1 of the cal kit 1 using TDR 1. The spectrum of the TDT signal is shown on Figure 1.23. The curve in Figure 1.23 can be used to roughly estimate signal-to-noise ratio in the frequency range of interest. For this purpose, the noise was approximated as having a uniform spectrum in the frequency range, and the signal spectrum was assumed to be a uniformly decreasing function. The estimation gives the value of 0 dB SNR at approximately 25 GHz, which is higher than the highest frequency in Figure 1.16. For this reason, the random noise may be not the dominating factor for the error in the  $S_{21}$  measurement for frequencies below ~25 GHz for the settings of the instrument indicated in the caption for Figure 1.23.

Figure 1.22: Estimation of the standard deviation of the  $S_{21}$  measurements

Figure 1.23: Spectrum of the TDT signal (TDR 1, 4096 samples, 10 ns time window, 256 averages)

Usually it is possible to achieve the SNR of at least 15 dB at 20 GHz for the used DUTs (10 or 16 inch test lines). In fact, the SNR can be further increased by varying the number of averages and the number of sampling points. According to [7], if all random errors are modeled as white noise, and the signal is modeled as an ideal step function, the SNR is defined as the ratio of the power spectral densities of signal and noise

$$SNR(f) = \frac{P_{sig}(f)}{P_{poise}(f)} = \frac{a^2}{2\pi^2} \frac{N_{pts}}{T^2 f^2} \frac{N_{avg}}{n^2},$$

(1)

where  $N_{avg}$  is the number of waveforms averaged,  $N_{pts}$  is the number of samples, a is the signal amplitude, T is the time record, and  $n^2$  is the white noise power. In order to increase the SNR, the number of samples and the number of averages should be increased, while the time record should be decreased. Theoretically,  $N_{pts}$  and  $N_{avg}$  do not have upper limits, and in practice they are limited by technical capabilities of the instrument and the acceptable measurement time. In contrast, the time record T has a lower limit determined by the DUT response. The choice of the minimum time record is illustrated below in Figure 1.24.

Figure 1.24: Minimum time record for TDR measurements

Therefore random noise cannot be a major factor limiting the performance of the t-TRL calibration, and SNR can be easily increased if needed by increasing  $N_{\it pts}$  and  $N_{\it avg}$  .

The interpolation of the frequency-domain results is explained now. The frequency resolution of the discrete Fourier transform is

$$\Delta f_{fft} = 1/N\Delta T_{,} \tag{2}$$

where N is the number of time samples, and  $\Delta T$  is the sampling period. The TDR/TDT signal spectra are computed by CFFT, which uses separate calculation procedures for odd and even frequency samples. Hence, the frequency resolution of the CFFT is doubled [4],

$$\Delta f_{cfft} = \frac{1}{2N\Delta T},\tag{3}$$

For the time record of 10 ns, the frequency resolution of CFFT is 50 MHz. In practice, the part of the signal, which contains the incident TDR pulse and cable

response, is discarded, and the waveforms are windowed to eliminate the diode state error. This results in a reduced frequency resolution (however if the response of the DUT isn't affected by this windowing procedure, the useful information is not lost). At the same time, some applications may require an interpolation of the measured discrete S-parameters, and it can be done prior to the application of the TRL calibration by padding measured waveforms.

The usual way to interpolate discrete spectra is the use of zero-padding [10]. However, since the CFFT is intended to work with step-like functions, the waveform padding with zeros results in an error. To retain the step-like shape of a waveform, it is reasonable to pad it not with the zero, but with the value at its last sampling point. Figure 1.25 illustrates this interpolation technique in frequency-domain for the phase of  $S_{21}$ . The interpolated frequency resolution of the padded waveform is

$$\Delta f_i = \frac{1}{2(N + N_p)\Delta T},\tag{4}$$

where  $N_n$  is the number of added samples.

Figure 1.25: Result of padding – phase (10,000 points added).

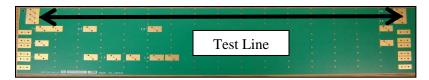

**1.2.1. ANALYZING RANDOM ERRORS.** Experiments were done to analyze random errors. The measurement board used along with the calibration standards is shown below in Figure 1.26. The effect of the number of acquisition points was studied first. A firmware update was done on DCA-J 86100C which increased the number of acquisition points to 16834 points from 4096 points.

Figure 1.26: Test board used for the measurements

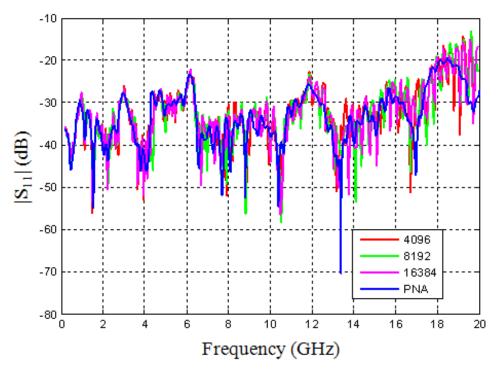

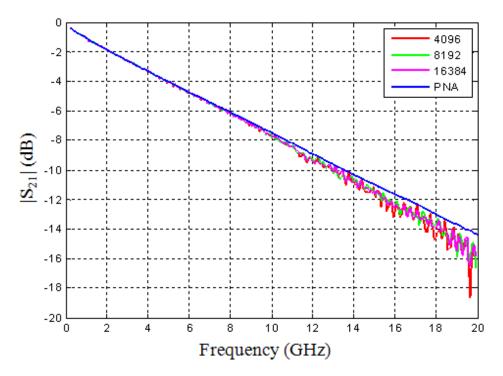

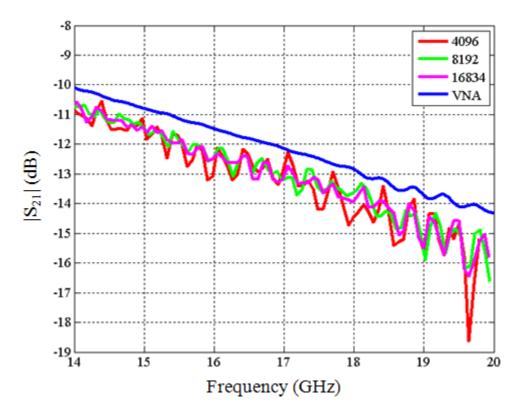

The timespan and the number of averages were fixed and the numbers of points were changed. Timespan was fixed at 1 ns/div or 10 ns in total and the number of averages were 256. Magnitude of  $S_{11}$  and magnitude and phase  $S_{21}$  were plotted for this measurement setup as shown in Figure 1.27, Figure 1.28 and Figure 1.29.

Figure 1.27: S<sub>11</sub> magnitude comparison with VNA for different points

Figure 1.28: S<sub>21</sub> magnitude comparison with VNA for different points

Figure 1.29: S<sub>21</sub> magnitude comparison with VNA for different points – zoomed

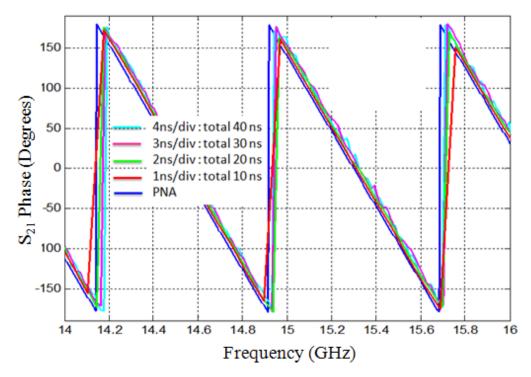

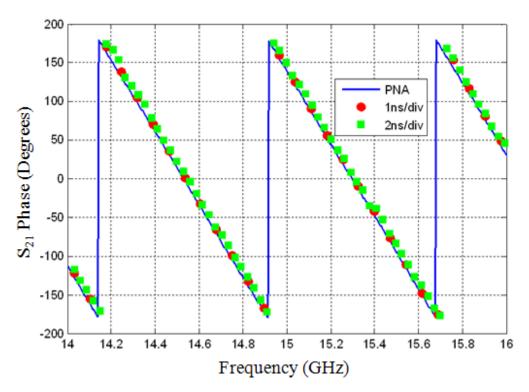

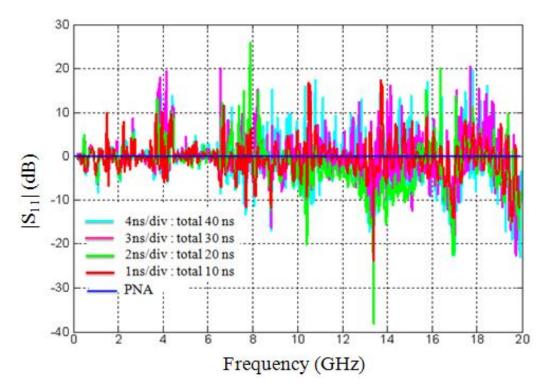

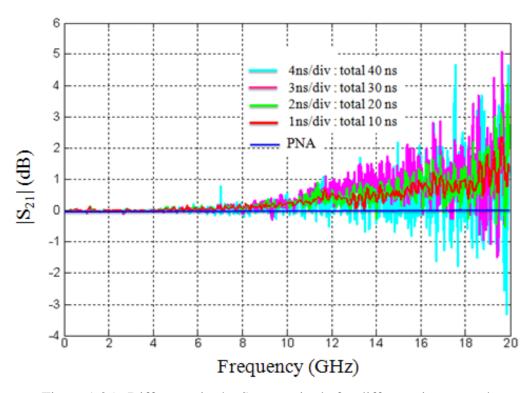

The increase in number of acquisition points in the measurements is preferred as the SNR increases with the number of points/samples especially at higher frequencies. The time record or the timespan of the measurement was changed to study the effect of long waveforms. In this case the averages and the number of points were fixed at 256 and 16834 respectively and the time record was changed. Due to the large number of averages and points, the measurements can take long time. The magnitude of  $S_{11}$  and magnitude and phase of  $S_{21}$  were plotted for this measurement setup as shown in Figure 1.30, Figure 1.31, Figure 1.32 and Figure 1.32. The graphs show that the increase in time record decreases the SNR.  $S_{21}$  graph shows better correlation of the t-TRL result with the VNA measurement for 10ns time record than for the 40ns time record. The phase of  $S_{21}$  shows noise like undulations at higher frequencies. For better understanding of the correlation of the t-TRL results with the frequency-domain VNA for different time record results the difference between the t-TRL and VNA TRL are plotted in dB scale which are shown in figure 1.34 and figure 1.35.

Figure 1.30: S<sub>11</sub> magnitude comparison for different time record

Figure 1.31: S<sub>21</sub> magnitude comparison for different time record

Figure 1.32: Phase of  $S_{21}$  comparison zoomed

Figure 1.33: Increase in time record will increase the frequency resolution

Figure 1.34: Difference in the  $S_{11}$  magnitude for different time record

Figure 1.35: Difference in the  $S_{21}$  magnitude for different time record

From the formula (1), SNR is proportional to the number of points and inversely proportional to the square of the time record. The increase in time record reduces the SNR, but this can be solved by increasing the number of averages. Also by measuring a long time record it is ensured that the multiple reflections that occur at the ports and the connections are always captured. So another method can be considered to improve the measurement results. This method stitches many short waveforms together to create a long waveform. By stitching these waveforms, for each waveform section the SNR is preserved and the higher order reflections are captured. Generally as the time record increases the noise also increases which can be further reduces by taking larger number of averages.

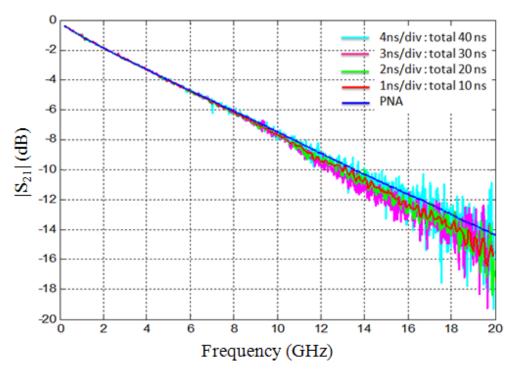

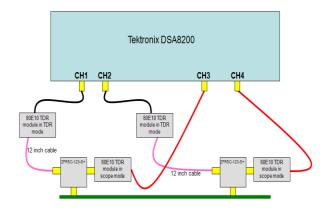

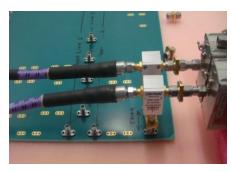

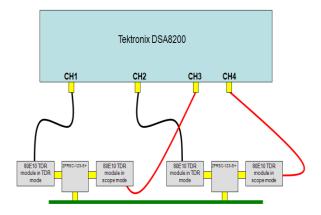

The error assessment and study was now conducted on a new instrument, Tektronix DSA 8200 Digital Serial Analyzer. The measurement setup is similar to the previous setup done for the Agilent TDR. Tektronix has a rise time of 18ps. Here one end of the precision cables was connected to the sampling heads and the other end to the connectors on the boards as shown in Figure 1.36. One of the main advantages of the external E10 sampling heads is that they can be kept away from the instrument mainframe. The t-TRL calibration is performed with the new instrument and  $S_{11}$  magnitude and  $S_{21}$  magnitude and phase were plotted.

Figure 1.36: Measurement setup for the Tektronix DSA 8200

Figure 1.37: S<sub>11</sub> magnitude comparison with VNA

The S<sub>11</sub> magnitude as shown in figure 1.37 has a good correlation with the VNA measurement results at the low frequencies. But after about 6GHz, they graphs tend to fall apart. Random errors and systematic errors were analyzed to understand this effect. The magnitude and phase of S<sub>21</sub> were plotted as shown in Figure 1.38 and Figure 1.39. The Tektronix DSA8200 analyzer is a relatively new instrument with higher bandwidth and faster rise time. Hence it is expected that the results are better than the Agilent DCA-J 86100C. It also has an option for setting the bandwidth to 20GHz or 30GHz or 50GHz. For all the measurements here, the maximum bandwidth of 50GHz was used. The results obtained from Tektronix are better than the ones from the Agilent. This can be due the facts that:

- The Tektronix signals reach steady state earlier due to the faster rise time.

- The Tektronix port connectors seem to be better.

- Faster rise time provides better spatial resolution

Figure 1.38: S<sub>21</sub> magnitude comparison with VNA

Figure 1.39: S<sub>21</sub> phase comparison with VNA

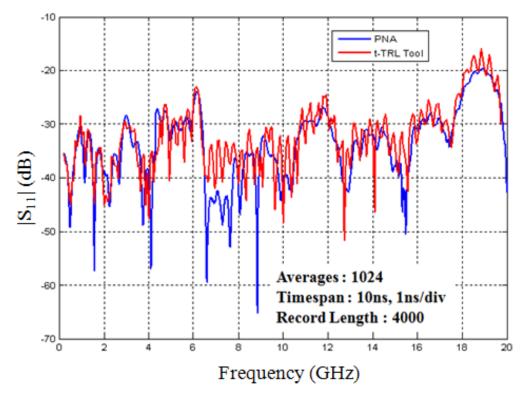

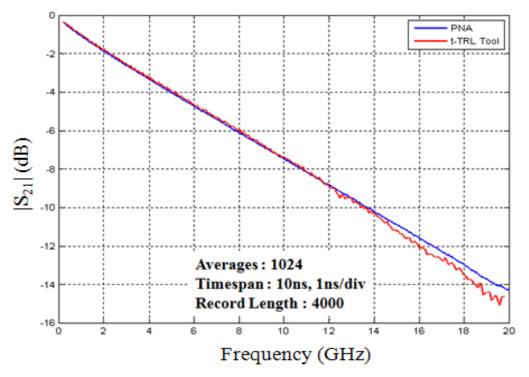

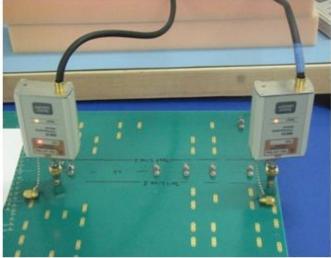

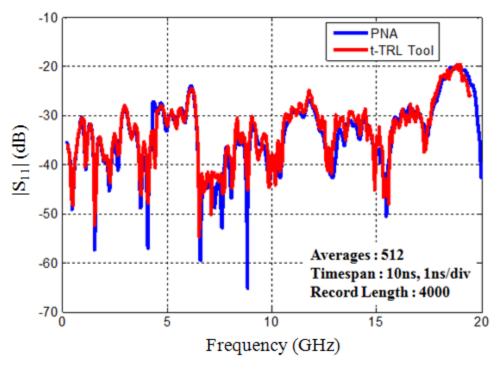

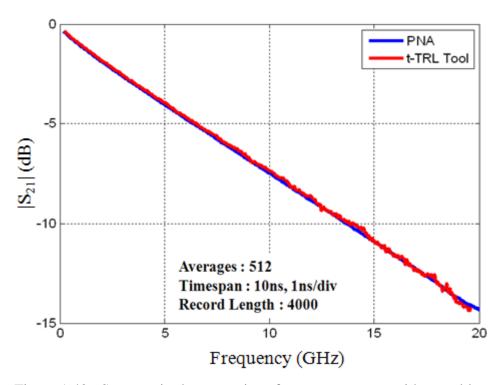

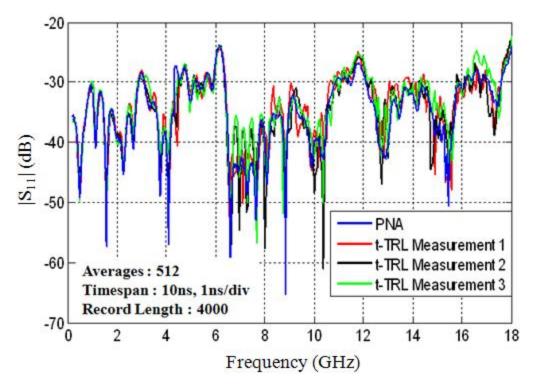

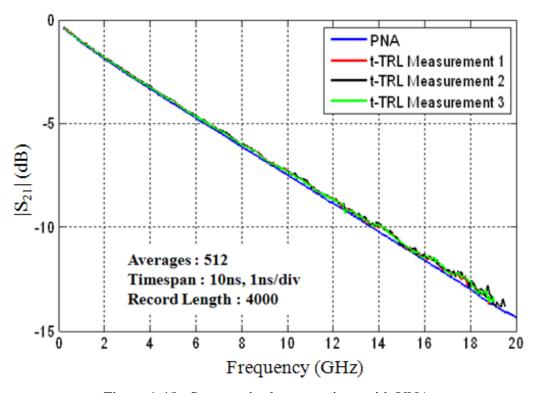

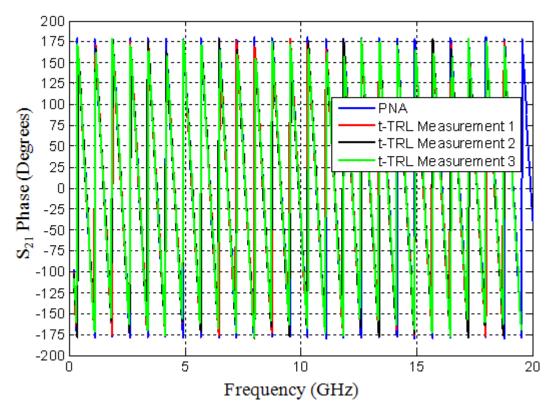

The same process was repeated for a slightly different measurement setup. Here the E10 sampling heads were connected directly to the connectors on the measurement board as shown in Figure 1.40. No cables were used for this setup. Channel 1 was used as port 1 and channel 2 was used as port 2. Time record was fixed at 10ns and 512 averages was used. Also maximum (4000) number of points was used.

Figure 1.40: Measurement setup with sampling heads connected directly to the board

Figure 1.41:  $S_{11}$  magnitude comparison for measurements without cables.

Figure 1.42: S<sub>21</sub> magnitude comparison for measurements without cables

Figure 1.43: S<sub>21</sub> phase comparison with VNA for measurement without cables

The t-TRL calibration results without the cables gave much better results when compared with the ones with the cables. The TRL technique by itself should have taken care of the influence of the cables. Interestingly, the calibration without cables always yielded better correlation with PNA calibration results. The t-TRL calibration effectively reduces reflections caused by the connector mismatches. The ripples in  $S_{21}$  and  $S_{11}$  are caused by extra reflections from the internal TDR load (most likely from the pulse generator of another channel).

Another concern while performing the time-domain TRL calibration was the repeatability of the calibration. It was observed that the t-TRL calibration was very sensitive to the way the measurement is done. Each measurement with respect to the connections and setups should be absolutely identical to get the same results again and again. The t-TRL calibration was done several times on the same DUT to check the repeatability of the measurement.  $S_{11}$  magnitude and  $S_{21}$  magnitude and phase were plotted.

Figure 1.44: S<sub>11</sub> magnitude comparison with VNA

Figure 1.45: S<sub>21</sub> magnitude comparison with VNA

Figure 1.46: S<sub>21</sub> phase comparison with VNA

**1.2.2. Analyzing Systematic Errors.** After analyzing the random errors, systematic errors are studied. The TRL calibration is based on an 8 term error model for two port systems. VNAs with two measurement ports are based on 24 term error models (12 terms for forward and 12 terms for reverse measurements). Taking only the terms that are important this 24 term error model reduces to a 12 term error model as shown in Figure 1.47.

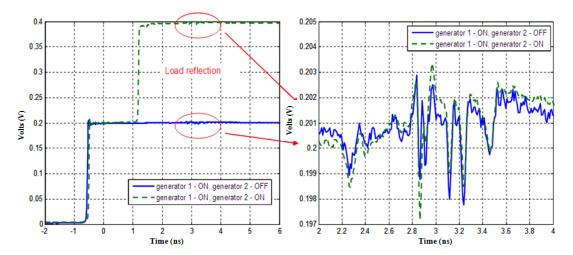

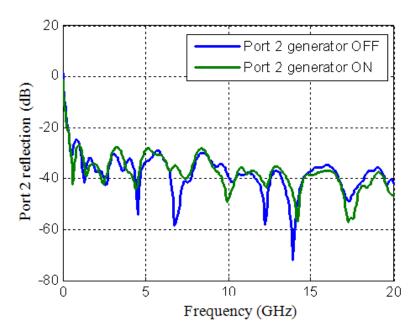

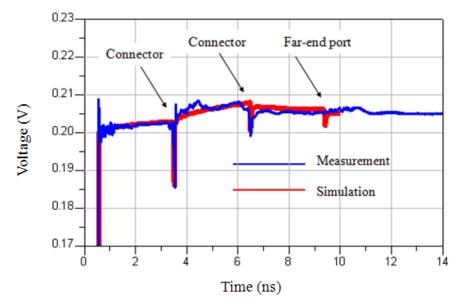

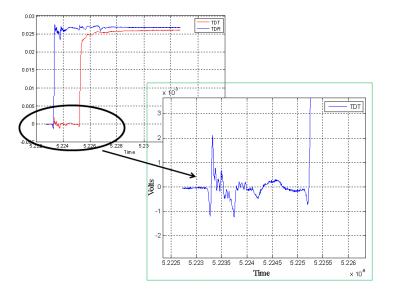

The TRL calibration does not consider the leakage terms. It assumes that the error adapter X and error adaptor Y as shown in figure 1.11 are identical. That means the error adapters are the same for both forward and reverse measurements. One of the requirements for the TRL calibration is that the error terms should be the same for forward and reverse measurements. Unfortunately, this is not true for TDR instruments since their port impedances depend on the state of the port generator, i.e. whether the generator is turned on or switched off. In [8], this effect was described as a diode state error, and is illustrated herein in Figure 1.48[8].

Figure 1.47: 12-term error model for forward and reverse measurements

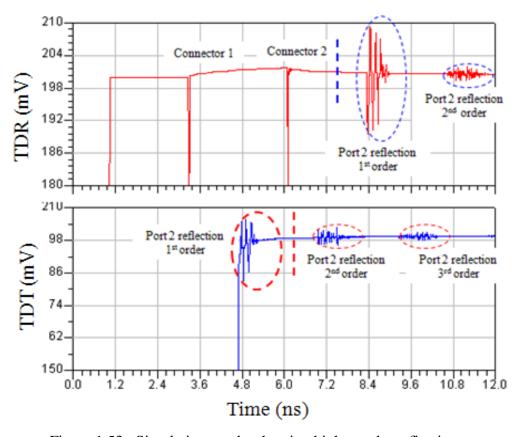

A simple experiment was done to analyze the diode state error. The ports of the TDR 1 were connected with the 12-inch precision cable, and the TDR response of the port 2 was recorded for enabled and disabled generator of the port 2. The left zoomed part of Figure 1.48 shows the difference in TDR responses of the port 2 depending on the state of generator 2. Figure 1.49 shows the spectrum of the signal showing the diode state error.

The difference in reflections from port 2 means that it has different impedance depending on whether the port's generator is "on" or "off" which results in the asymmetry of the system (i.e. dependence of the result from the measurement direction). The diode state error creates a 10 term error model when the isolation terms are not considered. The asymmetry introduces additional term into calibration procedure error model which cannot be compensated by TRL according to [8]. The error can be reduced by windowing waveforms in such a manner that the reflection from the port is excluded, as is seen from figure 1.50[8]. By the windowing procedure, the port reflections are

eliminated after making sure that the response of the DUT is inside the time window selected. The windowing technique was applied to the TDR 1 instrument. It led to the improvement of the transmission coefficient magnitude measurements at 20 GHz, as is indicated in Figure 1.51. In this particular case, the error was reduced from 10% to 5%.

Figure 1.48: Measurement results showing the corresponding generator state

Figure 1.49: Spectrum of the signal showing diode state error

Figure 1.50: Windowing of the TDR/TDT waveforms to eliminate the effect of the diode state error

Figure 1.51: Improvement by applying waveform windowing

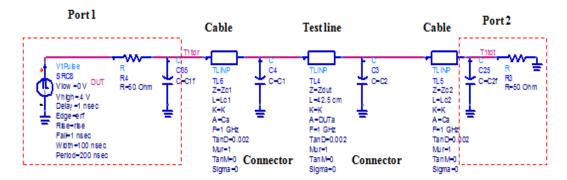

However, the windowing procedure does not allow for eliminating the overall error completely. This is because the reflection form the far-end port in the TDT measurement arrives at the same time at the incident edge of the TDR pulse and they cannot be separated. The circuit model below in the Figure 1.52 illustrates this effect. It contains of the model of the measurement cables, transmission line DUT, on board connectors (modeled by capacitors C1 and C2) and a reflective load.

The reflective load is modeled by a combination of capacitors, inductors and transmission lines. The simulated waveforms are shown in the Figure 1.53. It clearly shows the higher order reflections in both TDR and TDR waveforms. The reflection can be separated from the DUT response only in TDR waveform. In the TDT waveform the reflection and the incident edge overlap.

#### TDR instrument model Port 1 (ideal) DUT Cable 1 Cable 2 Connector 1 Connector 2 TLIN TL1 C1 V bw =0 V Z=Zdet L=42 cm Vigi-.4 V Z=Zc1 L=Lc1 Delay=1 ase o Bikie-enf Fall- 1 use of F=1 GHz Tai D=0 With - 100 a sec Mi i= 1 Tai M=0 Period-200 i sec Tax MH0 Styma-0 Styma=0 R2 R=50 Okm πв C=C3IL6 TL7 L=L3 L=L3 L=L3 Z-Zc2 L=1cm L=1 cm L=1cm A-Ca A=Ca F=1GHz F=1 GHz F=1 GHz F=1 GHz Ta + D=0.002 Tai D=0.002 Tat D=0.002 Tat D=0.002 Tan M-O Tax M=0 Reflective port 2

Figure 1.52: ADS model for TDR with reflective port

Figure 1.53: Simulation results showing higher order reflections

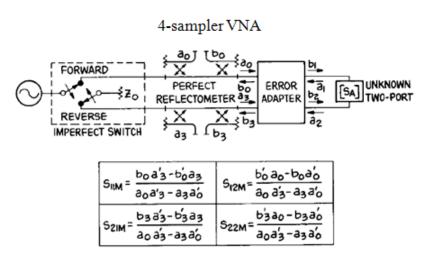

The VNAs with two measurement ports and one source have switching error. This can be very similar to the state error associated with the TDR samplers in the ON and OFF positions. The samplers have diodes which has different impedances in different states. The switching errors can be considered if separate models for forward and reverse measurements are used. This helps to measure the entire incident and reflected signals at the ports. A majority of the modern frequency-domain VNAs are four-sampler instruments, capable of measuring incident and reflected waves on both ports simultaneously. A switch changes direction of the incident power to the unknown 2 port for forward and reverse direction measurements and at the same time terminates the unknown 2 port in impedance  $Z_0$ . In such instruments, the switching error can be compensated in the course of the normal calibration and measurement procedure without the use of any additional calibration standards.

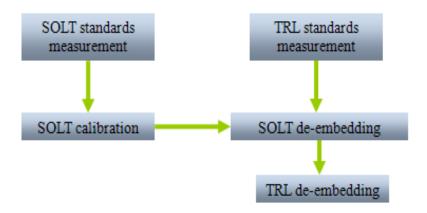

In the frequency-domain VNAs there are two ways of eliminating the switching error. If the VNA has 4 samplers/mixers, then the switching error can be mathematically removed without any additional measurements. Figure 1.54 shows how the S-parameters can be measured from the incident and reflected signals. If the VNA has only 3 receivers, the switching error is removed by applying the SOLT calibration prior to the TRL calibration. This is called the two-tier calibration procedure [12] as shown in figure 1.55. The same approach can be applied to the time-domain VNAs too.

Figure 1.54: 4 sampler VNA and the measurement of S-parameters

# Two-tier calibration

Figure 1.55: Two tier calibration for 3 sampler VNA

### 1.3. TWO TIER CALIBRATIONS

In two tier calibrations [12], SOLT calibration is performed as the 1<sup>st</sup> tier calibration. The SOLT calibration takes into account of the switching error. Time-domain waveforms are measured and SOLT calibration is performed on these waveforms. The SOLT calibrated data is given to the TRL technique to yield two-tier calibrated results. A block diagram below shows the methodology that is used. To make sure that this method works, first the 1<sup>st</sup> tier SOLT calibration is done in the frequency-domain. This is sanity check before doing the experiment in the time-domain. 1<sup>st</sup> tier calibration can be a manual SOLT calibration or an Electronic calibration done in the VNA. Figure 1.56 shows the block diagram representation of two tier calibration.

These frequency-domain results are then compared to the time-domain SOLT calibration results. The measurements for both forward and reverse directions are taken. The correlation between time-domain SOLT calibration and frequency-domain VNA calibration are shown in Figure 1.57 and Figure 1.58.

Figure 1.56: Two tier calibration block diagram

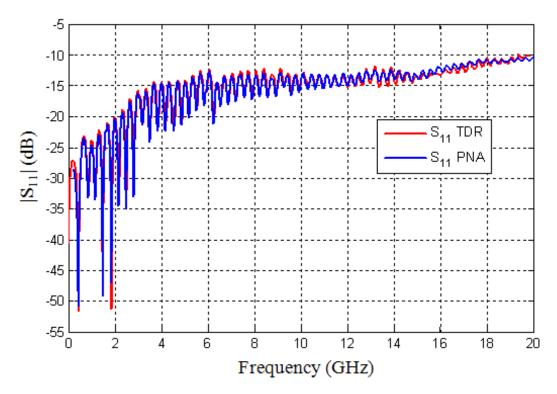

Figure 1.57: SOLT calibration comparison of  $S_{11}$  magnitude with the VNA

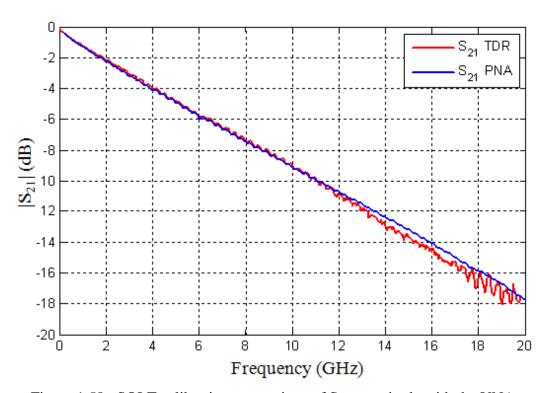

Figure 1.58: SOLT calibration comparison of  $S_{21}$  magnitude with the VNA

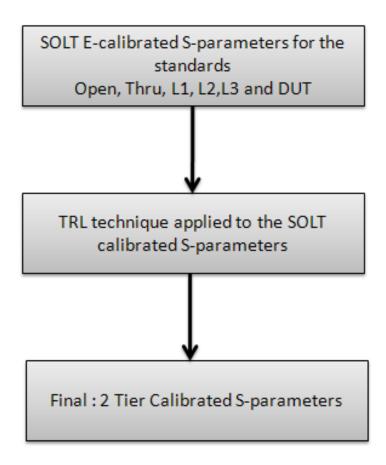

The forward measurements are  $S_{21}$  data and the reverse measurements are  $S_{12}$  data. The VNA S-parameters for forward and reverse measurements are identical. Hence time-domain results are compared to just the forward VNA measurements. Similarly the TRL technique is applied to the SOLT calibrated data from the frequency-domain. All the standards used in the TRL calibration is measured and calibrated using the Agilent VNA. For the particular measurement board three line standards were used. The block diagram of the two tier calibration performed on the frequency-domain data is shown below in the Figure 1.59. The Figure 1.60 and Figure 1.61 show the results of two tier calibrations on frequency-domain data.

Figure 1.59: Two tier calibration with 1st tier calibrated by E-calibration

Figure 1.60: Two tier calibration on frequency-domain data, S<sub>21</sub> magnitude

Figure 1.61: Two tier calibration on frequency-domain data,  $S_{21}$  phase

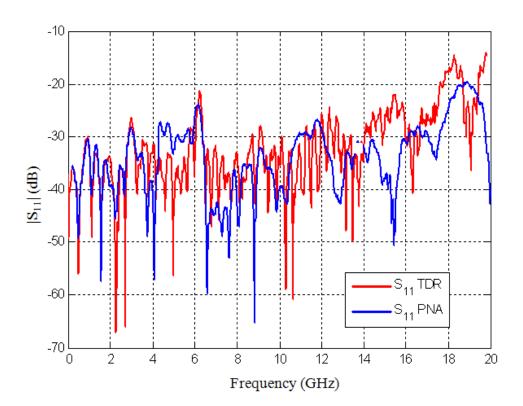

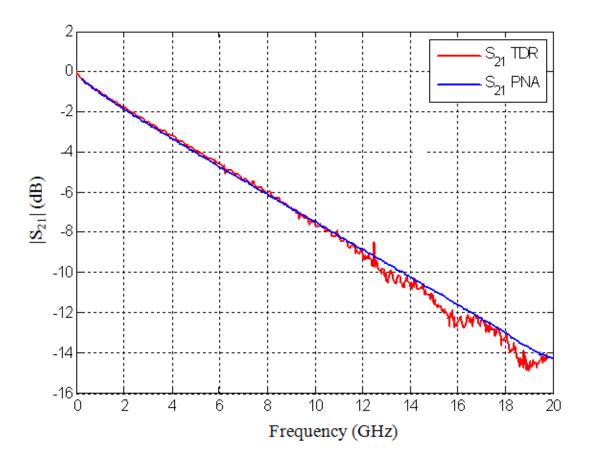

The graphs shows that when the E-calibrated data is given to the TRL technique it gives calibrated results similar to that of the frequency-domain TRL VNA calibrated results. This validates that the two tier calibrations on frequency-domain data works well. This method is now applied to the time-domain waveforms. SOLT calibrated data from the time-domain measurements were fed to the TRL calibration technique and the magnitude of the S<sub>21</sub> and S<sub>11</sub> are plotted as shown in Figure 1.62 and Figure 1.63. The correlation with the reference VNA data is not good as seen from the figures below. The two tier calibration measurements in time-domain were unsuccessful. Even though the 1<sup>st</sup> tier calibration (SOLT) results were comparable to the frequency-domain results, when the 2<sup>nd</sup> tier calibration was applied to the SOLT calibrated S-parameters yielded unsatisfactory results. By theory [12] it is possible to eliminate the switching error by the proposed two tier calibration. One possible reason for the uncorrelated results is that the errors in the 1<sup>st</sup> tier calibration may be exaggerated when the 2<sup>nd</sup> tier calibration is performed.

Figure 1.62: Two tier calibration on time-domain data, S<sub>11</sub> magnitude

Figure 1.63: Two tier calibration on time-domain data,  $S_{21}$  magnitude

# 1.4. t-TRL CALIBRATION WITH SPLITTERS

Another method to eliminate the switching error in time-domain VNA is by the use of splitters in time-domain measurements. The switching error can be simulated using a circuit model for the time-domain VNA. The figure below shows the time-domain model for the TRL calibration in the forward direction (excitation at port 1). The same model is there for the reverse direction too. They are shown in Figure 1.64 and Figure 1.65. The excitation is modeled as a RC circuit. The capacitance of the port models the reflection. The capacitance is given slightly different values for the forward and reverse direction simulations. Simple transmission line models are used for the cables. The connectors on the boards were also modeled as capacitors. The Figure 1.66 shows the correlation of the circuit model with the actual TDR measurement.

Figure 1.64: ADS model for TDR forward measurement

Figure 1.65: ADS model for TDR reverse measurement

Figure 1.66: TDR pulse comparison

This circuit model is used for the TRL calibration. For the forward measurement the capacitance at the port 1 is given a value of 0.1pF and for the reverse measurement this capacitance is given a value of 0.11 pF. This small difference in capacitance can emulate the switching error. Similarly, the same change in capacitor values were made to the port 2 too. Here the values were 0.12 pF and 0.1 pF respectively. Figure 1.67 below shows the simulation results.

Figure 1.67: Switching error simulation using the ADS model

The reference is the frequency-domain VNA results. The Figure 1.67 above shows that the switching error can be visualized by a circuit model. To minimize the switching error a new method was tried. Power dividers were used to reduce the reflected wave. Here by using power dividers, the reflected wave and the transmitted wave are

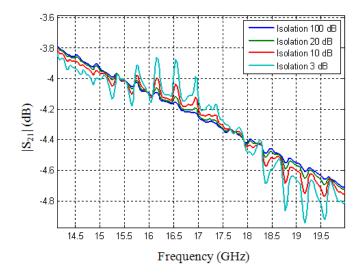

measured separately. The reflections from the ports are attenuated more than the reflections from the DUT. Power dividers from mini-circuits are used for this experiment. The isolation between the inputs is about 20 dB till 10GHz and about 16dB at 20GHz. The transmission is about 10dB at 20GHz. The S-parameters of the splitters are shown in Figure 1.68. Port 1 and 2 are the inputs and port 3 is the output of the splitters.

Figure 1.68: S-parameters of the splitters showing isolation, transmission and reflection

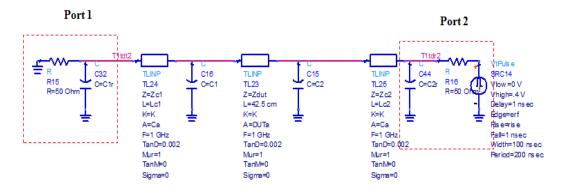

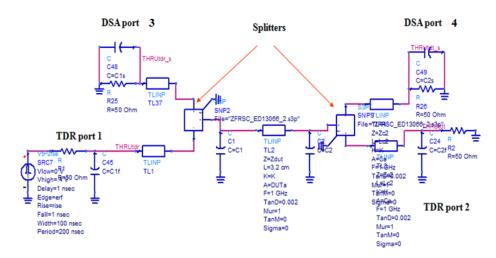

The circuit model for the splitter simulation is shown in Figure 1.69. The excitation at TDR Port 1. The excitation can be given by Agilent DCA-J or Tektronix DSA 8200. In this case the other module is used in the oscilloscope mode to measure the TDR/TDT waveforms. The simulated results are shown below in Figure 1.70. The graph clearly shows with increased isolation, the undulations are greatly reduced. It was decided that 20 dB isolation is enough to get good results.

Figure 1.69: ADS model for the TDR measurement setup with splitters

Figure 1.70: Simulated results showing fewer undulations with more isolation

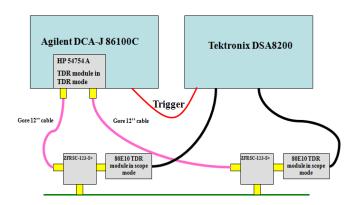

Different configuration were tried to do this experiment. These configurations are shown in the figures below. Setup 1 of the measurement uses Agilent as TDR and Tektronix as scope and is shown in the Figure 1.71 and Figure 1.72. In this setup, DSA 8200 is the TDR and the Agilent DCA-J is in the scope mode. The two instruments must be synchronized to be able to measure the signals properly. Trigger output from the DSA 8200 is given as trigger input to the Agilent scope. The trigger level too was adjusted to enable the measurement. The time-domain waveforms were measured for each port excitation for the entire TRL calibration pattern.

Figure 1.71: Block diagram for measurement setup 1

Figure 1.72: Measurement setup 1

After measuring all the time-domain waveforms, the TRL calibration is applied to the measured waveforms at the scope. The results are shown in Figure 1.73.  $S_{11}$  and  $S_{21}$  magnitude and  $S_{21}$  phase are plotted. The results are not good when compared to the reference VNA results. The reason for this error is the sampling pulse from the generator.

Figure 1.73: Results from the measurement setup 1

The measured TDR and TDT waveforms are shown in Figure 1.74. The TDT waveform clearly shows the parasitic sampler pulse. This pulse arrives at the same time as the incident pulse. It is believed that this parasitic signal may be the reason for the calibration error. To avoid the effect of this unwanted signal due to external trigger, only DSA 8200 is used for the experiment.

Figure 1.74: Sampler pulse causing parasitic waveforms

The setup 2 of the experiment used Tektronix DSA 8200 as both TDR and scope as shown in Figure 1.75. Two channels of the analyzer were used as the TDR generator and the other two channels were used as the receivers. Here twelve inch cables were attached between the generator heads and the splitters as shown in Figure 1.76. The input to the splitters is connected to the sampler heads acting as the scope. Similar time-domain measurements were made using this setup.

Figure 1.75: Block diagram for measurement setup 2

Figure 1.76: Using short cables to connect TDR generators to splitters

Figure 1.77: Results from the measurement setup 2

$S_{11}$  and  $S_{21}$  magnitude and  $S_{21}$  phase are plotted in Figure 1.77. The results shown did not improve the results compared to the measurements without the splitters. The graphs were worse than the measurement without splitters. The setup 3 of the measurement also uses Tektronix DSA 8200 as both TDR and scope. Here no cables are attached between the generator heads and the splitters. The block diagram of this setup is shown in figure 1.78.  $S_{11}$  and  $S_{21}$  magnitude and  $S_{21}$  phase are plotted in Figure 1.80. For connecting the generator heads to the splitters, 3.5 mm precision adaptors were used. Because of the use of many adaptors, the setup is very rigid and good care had to be taken for the getting good proper connections.

Figure 1.78: Block diagram for measurement set up 3

Figure 1.79: Connecting TDR generators directly to splitters

Figure 1.80: Results from the measurement setup 3

The results were not better than the results from the setup 2. The normal t-TRL calibration without cables and splitters gave much better results than the one with splitters and without cables. The entire experiment with power dividers did not give the improvements as expected from the circuit model simulation. Different measurement setups were tried. By theory and by simulation results, the switching errors can be eliminated by the procedures mentioned above. But the measurement done in the time-domain VNA did not give the expected results.

# 1.5. APPLICATION OF T-TRL CALIBRATION

The PCB substrate dielectric characterization tool based on TDR/TDT measurements together with the t-TRL calibration has been developed. This tool allows for efficient and frequency wideband extraction of two major parameters of a PCB FR-4

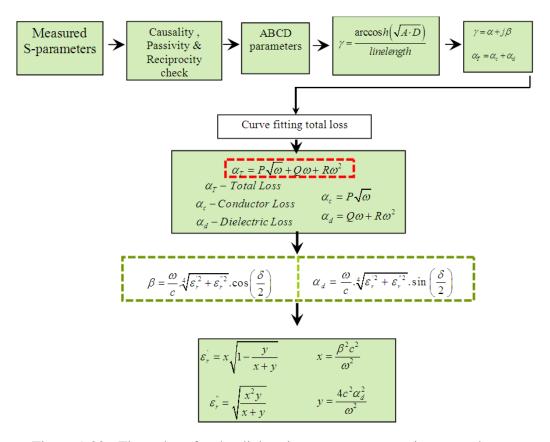

type dielectric substrate: its real part of relative permittivity  $\varepsilon_r'$ , or dielectric constant (Dk), and its loss tangent  $\tan \delta = \varepsilon_r'' / \varepsilon_r'$ , which is also known as a dissipation factor (Df). In the t-TRL tool, the t-TRL calibrated time-domain responses are measured and converted to frequency-domain S-parameters. Then the extraction technique developed in Missouri S&T is applied to determine Dk and Df data. This procedure was initially proposed for frequency-domain measurements obtained using VNA [1], and its flowchart is shown in figure 1.81. However, the same procedure can be successfully used for S-parameters independently whether they were obtained through frequency-domain, or through time-domain measurements [9].

The very first step in this procedure is an application of the MS&T Link Path Analyzer tool to the input S-parameter data for checking the network passivity, causality, and reciprocity. Then the corresponding ABCD transmission matrix parameters are calculated. For a passive and reciprocal system, the complex propagation constant  $\gamma$  is calculated from the known A and D parameters, and the phase  $\beta$  and attenuation  $\alpha$  constants are obtained as the corresponding imaginary and real parts of the complex propagation constant. Dielectric constant and loss tangent are then calculated from these phase and attenuation constants, as is shown in flow-chart. Though conductor surface roughness on the test vehicles substantially affects the extracted dissipation factor (Df) over the frequency range of interest [14, 15], the conductors were considered as smooth, and the conductor frequency behavior was assumed to be as  $\sim P\sqrt{\omega}$ , while dielectric loss behaves as  $\sim Q\omega + R\omega^2$  to follow the Debye-like behavior [1], where P,Q, and R are constant coefficients that depend on the PCB dielectric and copper foil. Once the dielectric loss is determined, the Df values can be calculated [1].

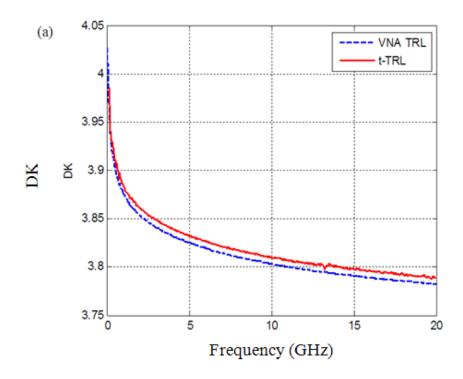

The test board with the TRL calibration pattern was chosen for comparison of the extracted dielectric parameters from the measurements of S-parameters obtained using two different methods - the frequency-domain VNA technique and the t-TRL method using TDR 2. The board has an FR-4 type dielectric with the standard copper foil conductors. The extracted data for Dk and Df parameters using both methods are shown in Figure 1.83 and Figure 1.84.

There is a good agreement between the results obtained using these two methods. The discrepancy for the extracted Dk value does not exceed 0.3%, and the average over the frequency range Df values do not differ more than by 2%, which serves as a validation of the t-TRL calibrated TDR measurements. The PCB used for the material parameter extraction is shown here. It is designed to work till 50GHz. Measurements were taken till 20GHz.

Figure 1.81: PCB board used for material extraction

Figure 1.82: Flow-chart for the dielectric parameter extraction procedure

Figure 1.83: Dielectric constant extracted comparison

Figure 1.84: Loss tangent extracted comparison

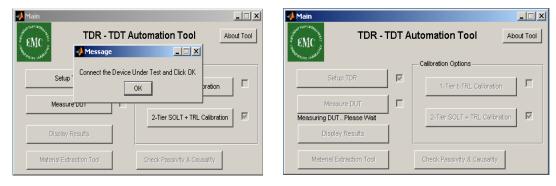

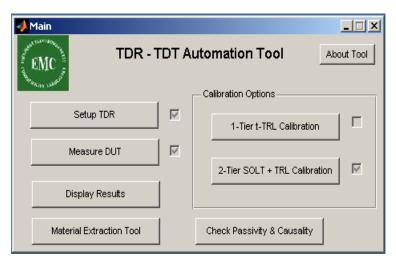

## 1.6. TIME-DOMAIN TRL CALIBRATION AUTOMATED TOOL

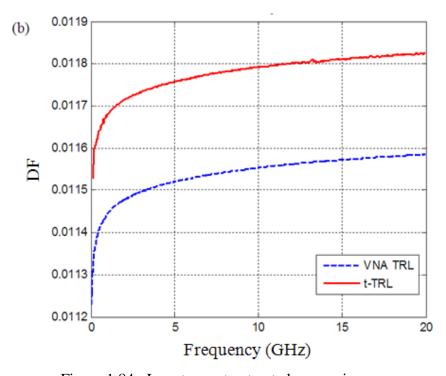

The time-domain calibration is automated into a standalone tool. The tool was developed in Matlab. Graphical user interface (GUI) design is done in Matlab and a complete calibration tool is developed. The calibration tool is designed to work like a calibration wizard in frequency-domain VNAs. The tool is compiled into an executable. User can run the Main window to start the calibration tool. Before running the tool, it should be made sure that the instrument is switched on and it is connected to the computer (where the tool runs) through a GPIB interface. When the Main window is started it opens up as shown in Figure 1.85.

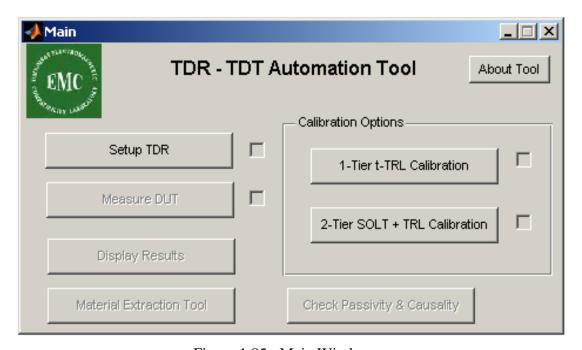

The Main window gives the user the option to setup the TDR and also shows the type of calibration options available in the tool. The user has to setup the TDR instrument properly before proceeding to the calibration methods. Other tabs are grayed out and will appear in time once the user goes through the calibration procedures. The Setup TDR option will call the TDR Setup Window as shown in Figure 1.86.

Figure 1.85: Main Window

Figure 1.86: TDR setup options

The Setup window has the following options to setup the TDR. The number of averages, number of points, horizontal scale, vertical scale and the time delay. The user can use the default settings option in the tool to setup the TDR or can input user defined values. The tool will automatically check any errors in the user input. Once the values are entered the user can setup the TDR. Once the TDR is setup, the tool provides an option to view the TDR waveform as shown in Figure 1.87. This option is useful for the user for observing the DUT transitions. This will give an idea to the user about the connections on the DUT. The user can save the TDR waveform for future use. Tool will retain the values used to set up the TDR each time the user goes to the Setup Window.

Other user friendly options added to this window are the Zoom and Pan option. This helps the user to clearly view the TDR waveform. The figure below shows the TDR setup with an open transition at the port. Once the setup is complete the tool allows the user to go back to the Main window or setup the TDR again.

Figure 1.87: TDR setup with user defined parameters (single ended)

There are 2 more additional options available in the Setup window. The user can also setup the TDR in even mode or odd mode configuration. This option allows the user to view and save the even mode and odd mode waveforms. TDR setup to view the even mode configuration is shown in Figure 1.88. Though, the calibrations using the even mode and odd mode TDR setup is not programmed up in the tool. The Figure 1.89 shows the even mode TDR waveform zoomed in.

Figure 1.88: TDR setup with user defined parameters (even mode)

Figure 1.89: Zoom in and Pan options

Once the setup is complete, the user can go back to the Main window and select either two tier calibration or one tier calibration. If the user wants to do the 2 Tier calibration, SOLT calibration window pops up. This window allows the user to measure the time-domain TDR waveforms of the Short, Open, Load standards for both ports and the THRU standard. The Figure 1.90 shows the initial SOLT waveform measurement window.

Figure 1.90: SOLT calibration measurement window

The user can connect the standards and measure the waveforms. The real time waveforms will be displayed on the window while measurements are taken. Once the standards are measured, the checkboxes will be checked to notify the user about the measurements taken as shown in Figure 1.91. After all the measurements are done, the tool will give an option to go the two tier calibration window.

Figure 1.91: Measuring SOLT standards

The 2<sup>nd</sup> tier t-TRL calibration definition window gives the user two options. One is to input a user defined calibration pattern and the other one is to calculate the TRL pattern. If the user knows the frequency range for TRL calibration Line standards, then the user can define the pattern. If the user knows the frequency range of the measurement only, the tool can calculate the TRL pattern based on the frequency range and the length of the THRU. Loading a pre defined TRL pattern is a future addition to the tool. These options are shown in Figure 1.92.

Figure 1.92: TRL calibration pattern options

While defining the TRL pattern, the user can enter the start and stop frequency and also the number of line standards. Then the user can define the TRL pattern. The tool guides the user to go through the calibration standards one by one as shown in Figure 1.93. Once all the standards are fed to the tool, the control goes to the measurement window for the TRL standards. This window allows the user to make the TRL calibration standard's time-domain TDR/TDT waveform measurements. TDR and TDT waveforms are measured at the ports as shown in Figure 1.94 and saved. The time taken for the measurements depends on the number of averages and the number of points.

Figure 1.93: Defining a TRL pattern

Figure 1.94: Measuring the TRL standard

Figure 1.95: Options for viewing all the measured time-domain waveforms

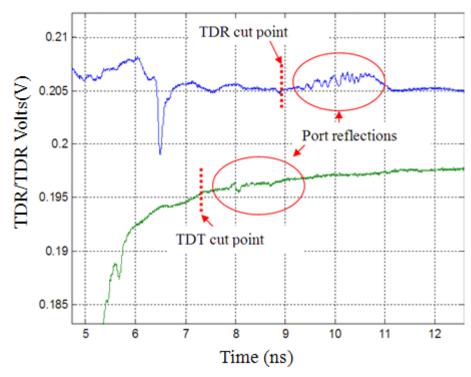

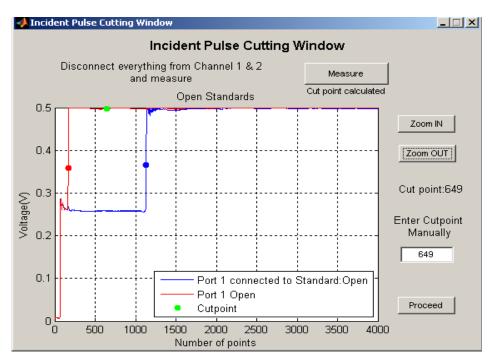

After the measurements, user can view all the time-domain waveforms by selecting the particular calibration standard as shown in Figure 1.95. After all the standards are measured the tool is ask the user to proceed. Tool will pass the control to the Cut point selection window shown in Figure 1.95, where it automatically calculates

the point where the incident pulse is cut away from the waveform. It will ask the user to disconnect all the connections made to the TDR ports and measure. Once measured, the tool will display the Cut point calculated. The user can also input the cut point of his/her choice. The control now passes back the Main window where the tool guides the user to connect the DUT. Once the DUT is connected, user can click the OK button to start the time-domain TDR/TDT measurement of the DUT as shown in Figure 1.97.

Figure 1.96: Cut point selection/calculation window

Figure 1.97: Measuring the DUT once calibration is defined

Tool will process all the time-domain waveforms measurements and apply the TRL calibration technique. Once the calibration is successful the tool displays option for displaying the calibrated results, material extraction tool and also additional option for checking passivity and causality as shown in Figure 1.98.

Figure 1.98: Main window giving options to view the calibrated results

## 1.7. CONCLUSIONS ON T-TRL ERROR ASSESSMENT

The random and systematic errors associated with t-TRL S-parameter measurements on printed circuit boards using TDR/TDT instrument have been assessed. It is shown that the random errors are not the main contributor to the overall error of  $S_{21}$  measurement of practical PCB transmission lines with FR-4 type copper-clad substrates in the frequency range up to  $\sim 20$  GHz. The random errors can be further reduced, if needed, by the proper choice of the number of waveform averaged, the number of samples, and the time record.