# Scholars' Mine

**Doctoral Dissertations**

Student Theses and Dissertations

Summer 2009

# Advanced control techniques for doubly fed induction generatorbased wind turbine converters to improve low voltage ridethrough during system imbalances

Murali M. Baggu

Follow this and additional works at: https://scholarsmine.mst.edu/doctoral\_dissertations

Part of the Electrical and Computer Engineering Commons Department: Electrical and Computer Engineering

## **Recommended Citation**

Baggu, Murali M., "Advanced control techniques for doubly fed induction generator-based wind turbine converters to improve low voltage ride-through during system imbalances" (2009). *Doctoral Dissertations*. 1891.

https://scholarsmine.mst.edu/doctoral\_dissertations/1891

This thesis is brought to you by Scholars' Mine, a service of the Missouri S&T Library and Learning Resources. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

# ADVANCED CONTROL TECHNIQUES FOR DOUBLY FED INDUCTION GENERATOR -BASED WIND TURBINE CONVERTERS TO IMPROVE LOW VOLTAGE RIDE-THROUGH DURING SYSTEM IMBALANCES

by

### MURALI MOHAN BAGGU

## A DISSERTATION

Presented to the Faculty of the Graduate School of the

MISSOURI UNIVERSITY OF SCIENCE AND TECHNOLOGY

In Partial Fulfillment of the Requirements for the Degree

DOCTOR OF PHILOSOPHY

in

### ELECTRICAL ENGINEERING

2009

Approved by

Badrul H. Chowdhury, Co-Advisor Jonathan W. Kimball, Co-Advisor Mariesa L. Crow Mehdi Ferdowsi Mark W. Fitch

© 2009 Murali Mohan Baggu All Rights Reserved

#### ABSTRACT

A doubly-fed induction generator (DFIG) applied to wind power generation is under study for low voltage ride-through application during system disturbances. Conventional dg axis current control using voltage source converters for both the grid side and the rotor side of the DFIG are analyzed and simulated. DFIG operation is investigated under balanced and unbalanced system disturbances. A conventional d-axis and q-axis control applied to a voltage source converter (VSC) during a system imbalance exhibits oscillations in the stiff DC link voltage as well as in the real and reactive powers of the converter. Multiple advanced control methods are explored and compared for imbalance operations. An advanced control technique utilizing both positive and negative sequence domain is evaluated. The approach demonstrates the stabilization of the DC link voltage to a greater extent during a disturbance but is more sluggish than the conventional control. An innovative control strategy that employs the technique of direct power control (DPC) is also investigated. This control achieves real and reactive power stability with simple active and reactive power control variables replacing the current control loops in the conventional case. A modified DPC algorithm is proposed to eliminate the current harmonics created by DPC during system disturbances. The DPC is further extended to the rotor-side converter of the DFIG thus controlling the complete system using this technique. The DPC is implemented using a three-phase converter designed on a PCB using Eagle<sup>®</sup>. A Texas Instruments<sup>®</sup> TMS320F2812 DSP is used to implement the control algorithm. The converter is tested for ride through capability using an industrial power corruptor. The results are compared to the simulation results for compliance with standard grid codes.

iii

### ACKNOWLEDGMENTS

The author is obliged to his co-advisors Dr. Badrul H. Chowdhury and Dr. Jonathan W. Kimball for their diligent guidance and patience all through the dissertation work. Special thanks are due to U.S National Science Foundation (NSF) for funding the research under the Grant ECS-0523897.

The author records his sincere thanks to his committee members Dr. Mariesa L. Crow, Dr. Mehdi Ferdowsi and Dr. Mark W. Fitch for providing support and enthusiasm.

The author would like to appreciate Vamsi Polisetty, Chuan Yan , Keyou Wang, Vivek Appadurai, Nishant S. Chouhan, Deepak B. Somayajula, Rajshekhar Modugu, Jing Huang, Jingsheng Liao, Anand K. Prabala, Vikram R. Surendra and all his friends and roommates who have been equally generous of their time and expertise in helping to complete the research smoothly.

The author is indebted to his fiancée and family who have been a source of encouragement and motivation to complete this work.

# **TABLE OF CONTENTS**

| Е | )- | ~ | ~ |

|---|----|---|---|

| г | a  | y | e |

| ABSTRACTiii                                                            |

|------------------------------------------------------------------------|

| ACKNOWLEDGMENTSiv                                                      |

| LIST OF ILLUSTRATIONS viii                                             |

| LIST OF TABLESxii                                                      |

| NOMENCLATURE                                                           |

| SECTION                                                                |

| 1. INTRODUCTION                                                        |

| 1.1 INTRODUCTION                                                       |

| 1.2 DISSERTATION OUTLINE                                               |

| 1.3 GRID CODES 4                                                       |

| 1.4 LITERATURE REVIEW8                                                 |

| 1.5 SUMMARY11                                                          |

| 2. CONVENTIONAL DFIG CONTROL AND OPERATION DURING GRID<br>DISTURBANCES |

| 2.1 INTRODUCTION12                                                     |

| 2.2 CONVENTIONAL DECOUPLED CONTROL13                                   |

| 2.3 DFIG AND ROTOR-SIDE CONVERTER CONTROL21                            |

| 2.4 DFIG MODEL USING DIgSILENT <sup>®</sup> 27                         |

| 2.5 SUMMARY                                                            |

| 3. ANALYSIS OF UNBALANCED INPUTS AND SEQUENCE CONTROLLERS              |

| 3.1 INTRODUCTION                                                       |

| 3.2 SEQUENCE COMPONENTS D-Q ANALYSIS                                   |

| 3.3 SEQUENCE CONTROLLERS SIMULATION AND SYSTEM IMBALANCE3 | 9  |

|-----------------------------------------------------------|----|

| 3.4 SUMMARY4                                              | 7  |

| 4. DIRECT POWER CONTROL FOR DFIG-BASED WIND TURBINES4     | 8  |

| 4.1 INTRODUCTION4                                         | 8  |

| 4.2 DPC SWITCHING STATES AND DELTA MODULATION4            | 9  |

| 4.3 SIMULATION OF VOLTAGE SOURCE CONVERTER USING DPC5     | 4  |

| 4.4 MODIFIED DIRECT POWER CONTROL                         | 0  |

| 4.5 DPC BASED ROTOR SIDE CONTROL                          | 64 |

| 4.6 SUMMARY7                                              | '4 |

| 5. HARDWARE IMPLEMENTATION OF DPC7                        | '5 |

| 5.1 INTRODUCTION7                                         | '5 |

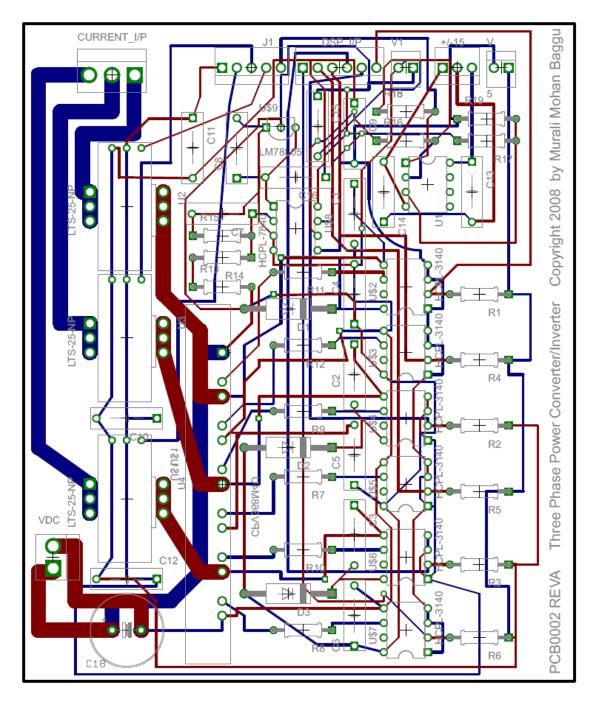

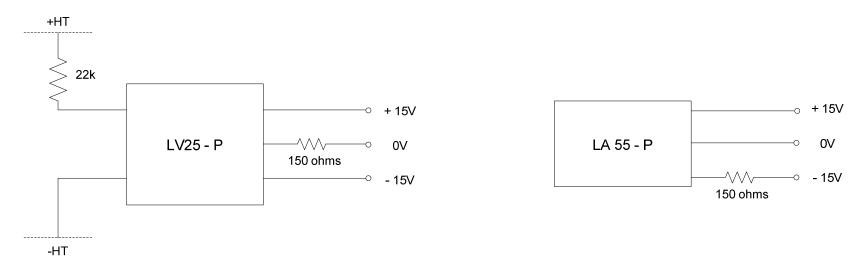

| 5.2 PCB DESIGN7                                           | '6 |

| 5.3 2812 DSP ARCHITECTURE AND PROGRAMMING8                | 1  |

| 5.4 INDUSTRIAL POWER CORUPTOR (IPC)8                      | 4  |

| 5.5 DPC IMPLEMENTATION AND RESULTS8                       | 5  |

| 5.6 SUMMARY10                                             | 0  |

| 6. CONCLUSIONS AND FUTURE WORK10                          | )1 |

| 6.1 SUMMARY AND CONCLUSIONS                               | )1 |

| 6.2 AUTHOR'S CONTRIBUTION10                               | 14 |

| 6.3 FUTURE WORK10                                         | 14 |

| APPENDICES                                                |    |

| A. SIMULATION AND PRACTICAL IMPLEMENTATION PARAMETERS10   | 17 |

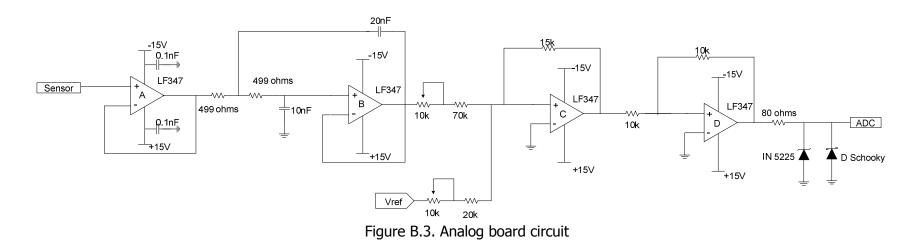

| B. DESIGN LAYOUT AND CIRCUIT DIAGRAMS11                   | .0 |

| C. DSP CODE FOR PRACTICAL IMPLEMENTATION OF DPC           | .3 |

| BIBLI | OGRAPHY | <br> | <br> | 1 | 26 |

|-------|---------|------|------|---|----|

| VITA  |         | <br> |      | 1 | 31 |

# LIST OF ILLUSTRATIONS

| 3.4. | Voltage imbalance simulation for conventional controller42                    |

|------|-------------------------------------------------------------------------------|

| 3.5. | Voltage imbalance simulation for sequence controllers42                       |

| 3.6. | Voltage imbalance simulation for conventional controller43                    |

| 3.7. | Voltage imbalance simulation for sequence controller44                        |

| 3.8. | Single line fault simulation for sequence controllers45                       |

| 3.9. | Single line fault simulation for sequence controller46                        |

| 4.1. | Single line diagram of the PWM converter49                                    |

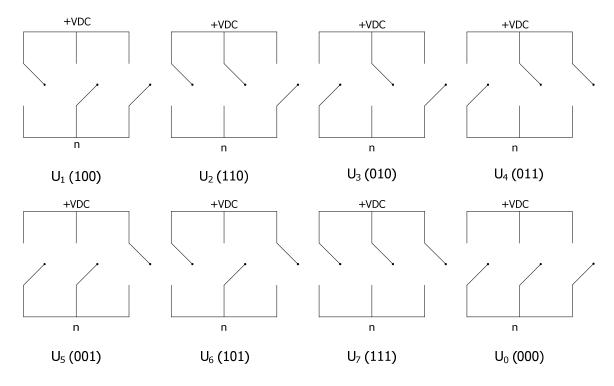

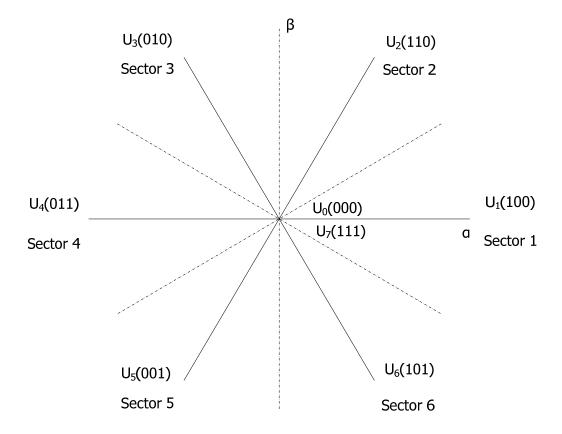

| 4.2. | PWM Converter switching states                                                |

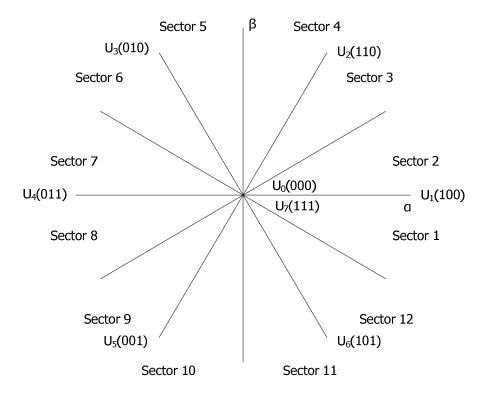

| 4.3. | Voltage vector plane divided into 12 sectors                                  |

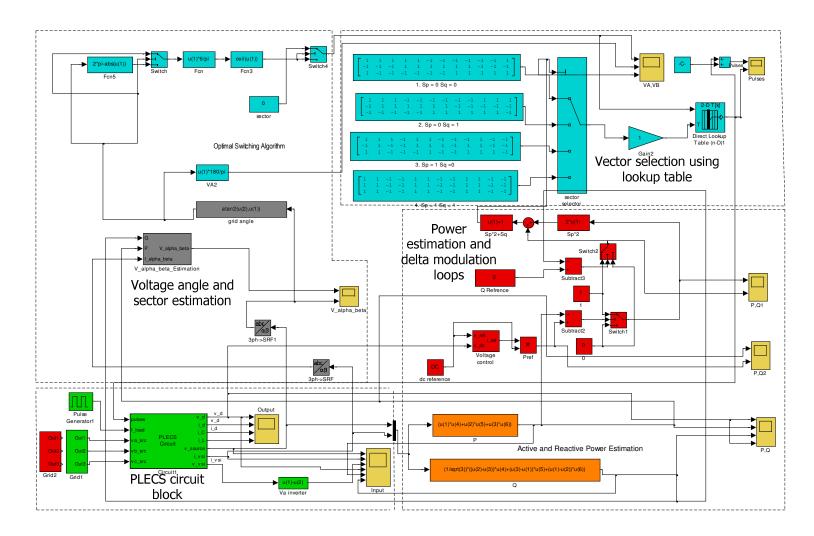

| 4.4. | DPC structure for voltage source converter55                                  |

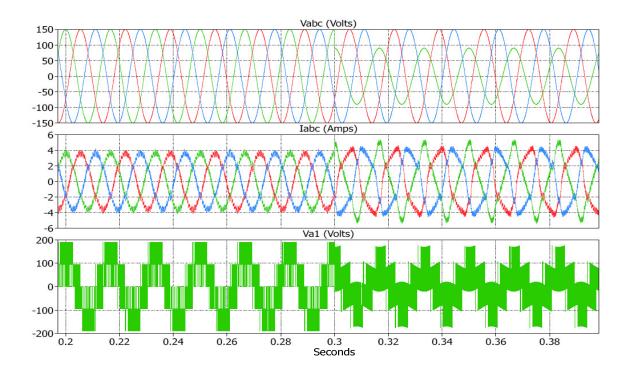

| 4.5. | VSC using DPC for a voltage dip of 60%                                        |

| 4.6. | Simulation of the VSC using DPC for a voltage dip of 60%56                    |

| 4.7. | Simulation of conventional controller for voltage dip of 60%                  |

| 4.8. | Voltage imbalance simulation of VSC for DPC                                   |

| 4.9. | Voltage imbalance simulation of VSC using DPC58                               |

| 4.10 | . Simulation of the voltage source converter using DPC for at 5 KHz60         |

| 4.11 | . Partial simulation diagram for the modified DPC showing unbalanced powers62 |

| 4.12 | . Simulation of the modified DPC for voltage dip of 60%63                     |

| 4.13 | . Simulation of the modified DPC for voltage dip of 60%63                     |

| 4.14 | . Stator flux vector plane divided into six sectors                           |

| 4.15 | . DFIG circuit diagram including the back-to-back converters                  |

| 4.16 | . DPC structure of the grid side and rotor side converter of DFIG             |

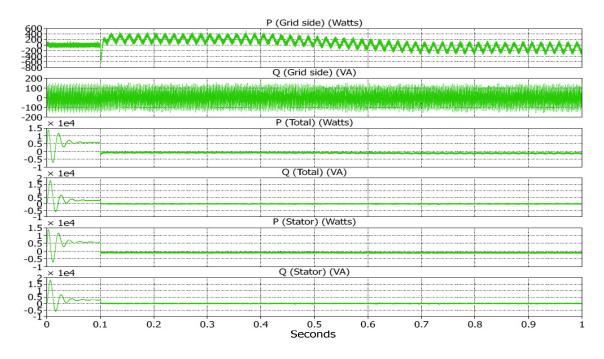

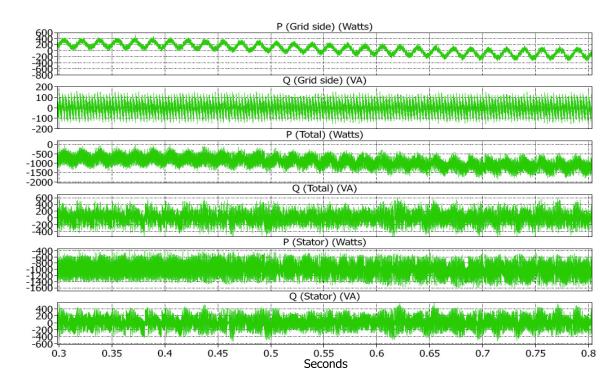

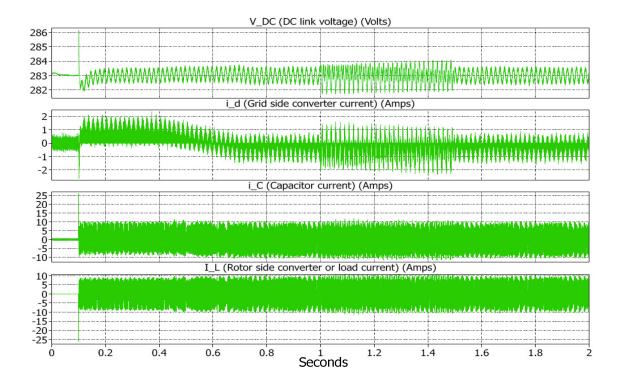

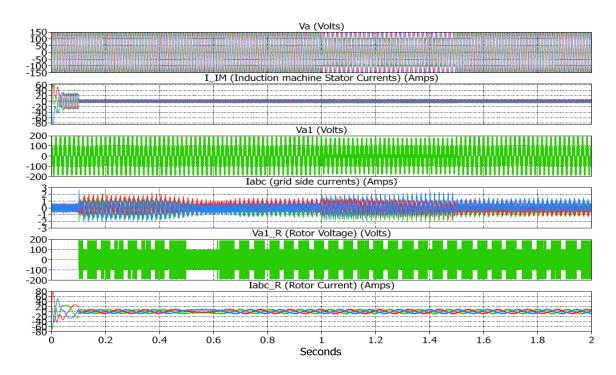

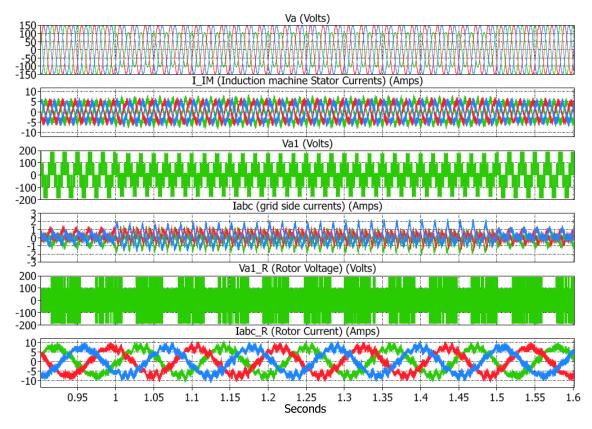

| 4.17 | . DFIG simulation results69                                                   |

| 4.18 | . DFIG simulation results71                                                   |

| 4.19. DFIG simulation results                                           | 71 |

|-------------------------------------------------------------------------|----|

| 4.20. DFIG simulation results                                           | 72 |

| 4.21. DFIG simulation results                                           | 72 |

| 4.22. DFIG simulation results                                           | 73 |

| 5.1. Circuit diagram of the converter for practical implementation      | 75 |

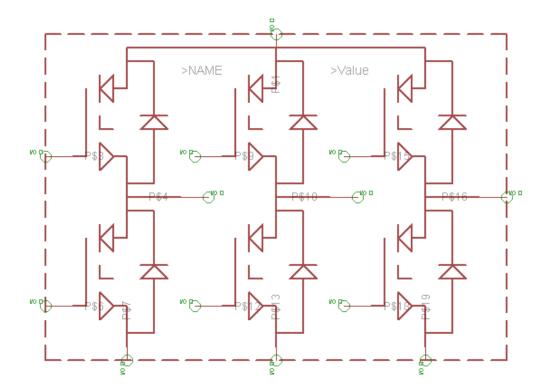

| 5.2. Schematic for the IGBT bridge module using Eagle <sup>®</sup>      | 76 |

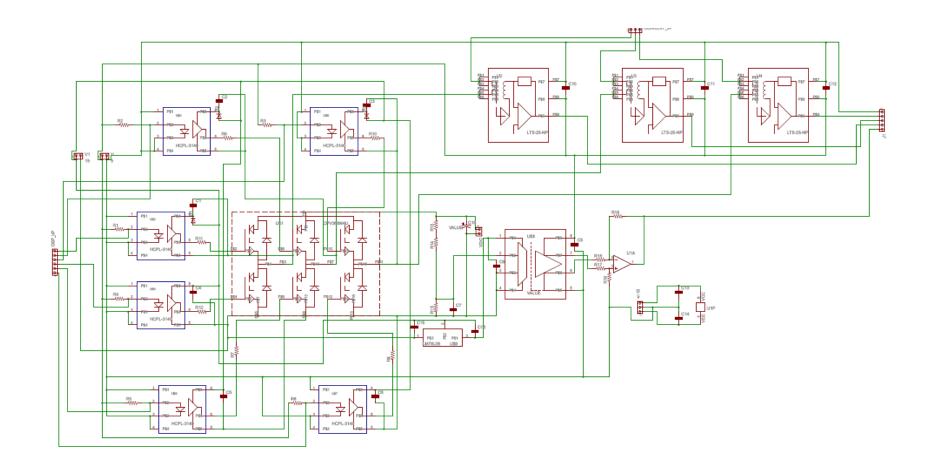

| 5.3. Schematic of the converter designed in Eagle <sup>®</sup>          | 78 |

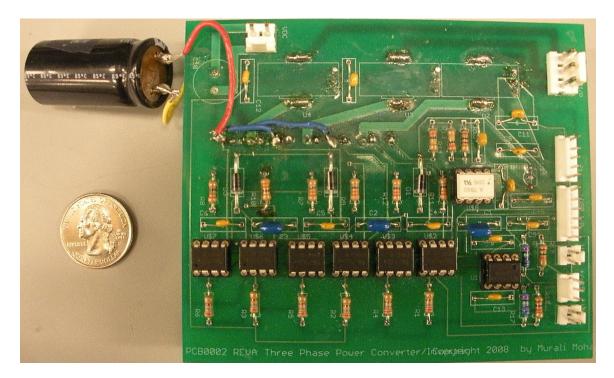

| 5.4. Mounted PCB of the three phase converter                           | 79 |

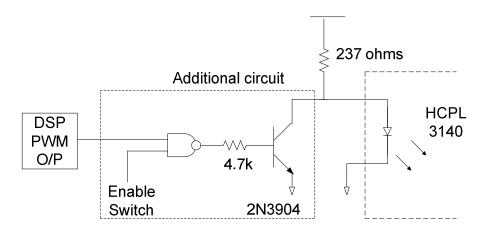

| 5.5. Circuit to convert gate outputs to open collector configuration    | 80 |

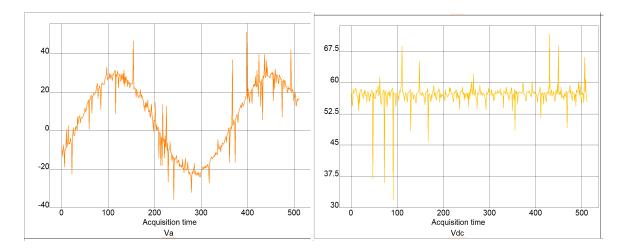

| 5.6. Phase A voltage and DC link voltage sensed by the ADC              | 82 |

| 5.7. Theta and sector values calculated by the ADC                      | 82 |

| 5.8. Front view of the IPC                                              | 85 |

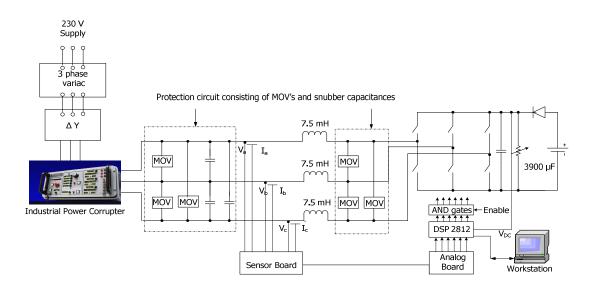

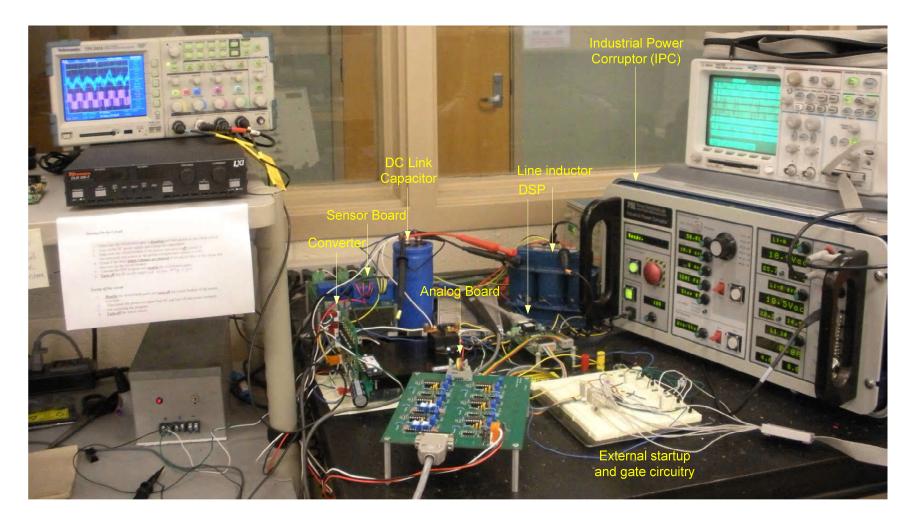

| 5.9. Picture of the experimental setup                                  | 87 |

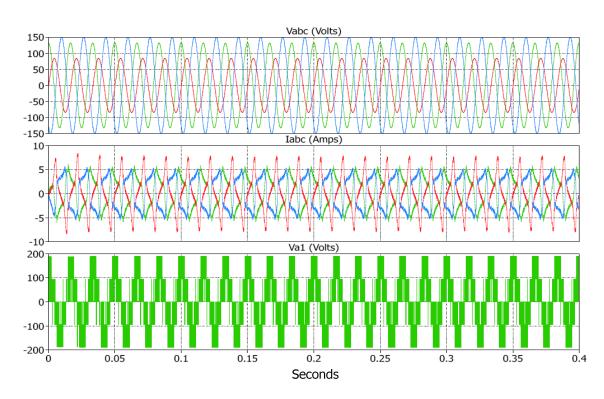

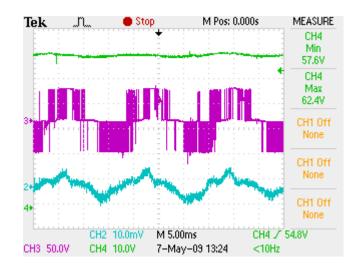

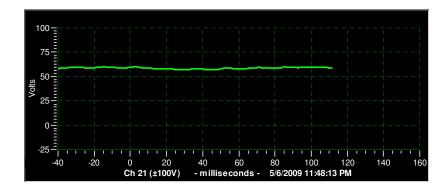

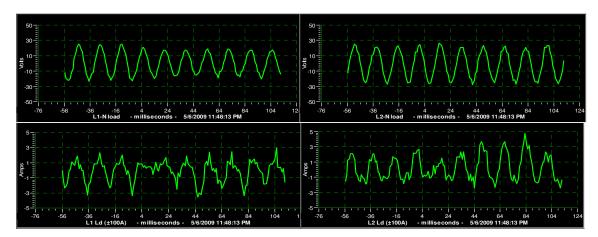

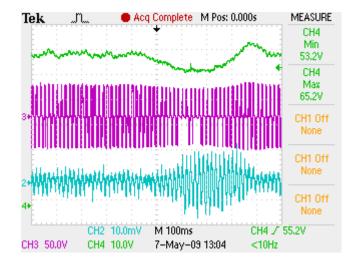

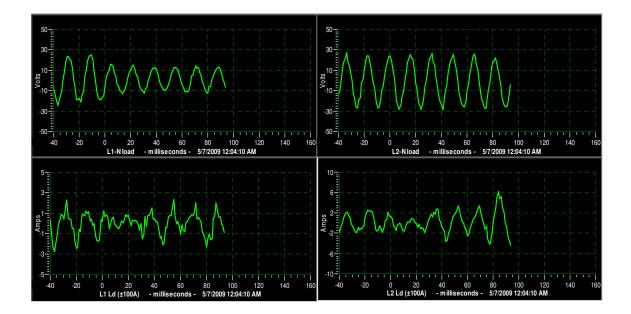

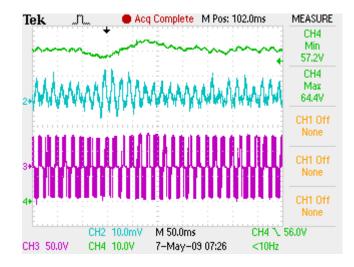

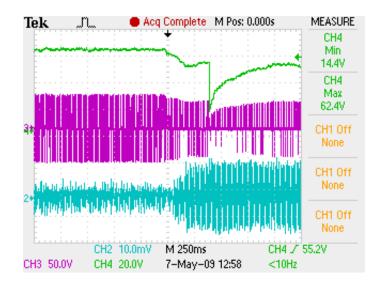

| 5.10. Experimental results for normal operation                         | 88 |

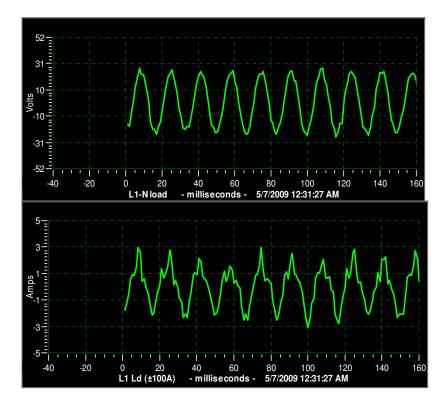

| 5.11. Experimental results for normal operation                         | 89 |

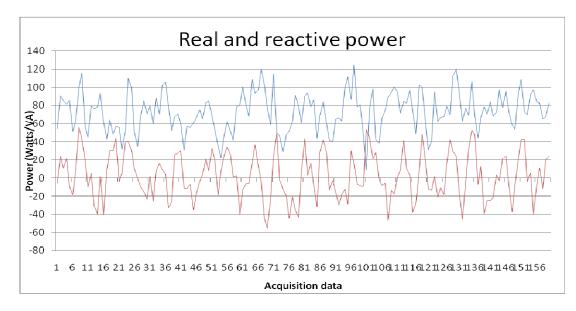

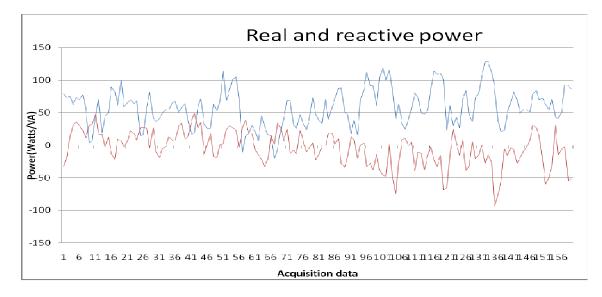

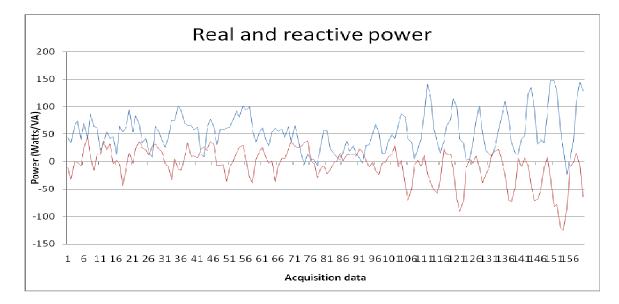

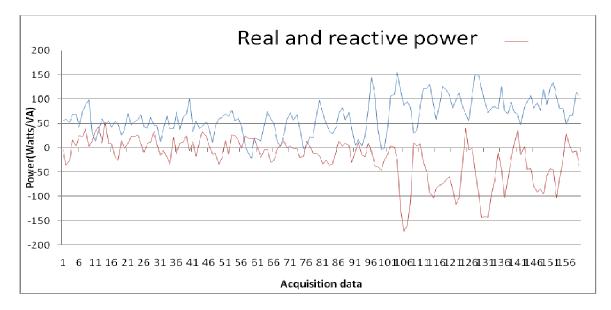

| 5.12. Real and reactive powers for normal operation                     | 89 |

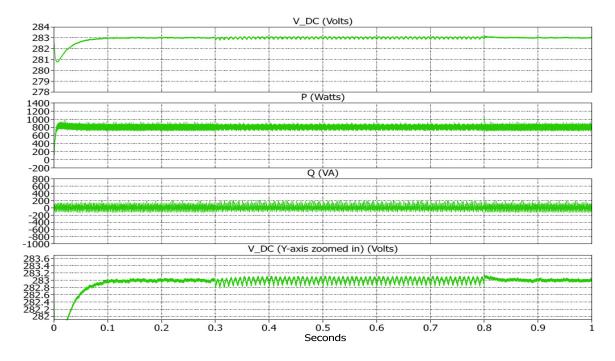

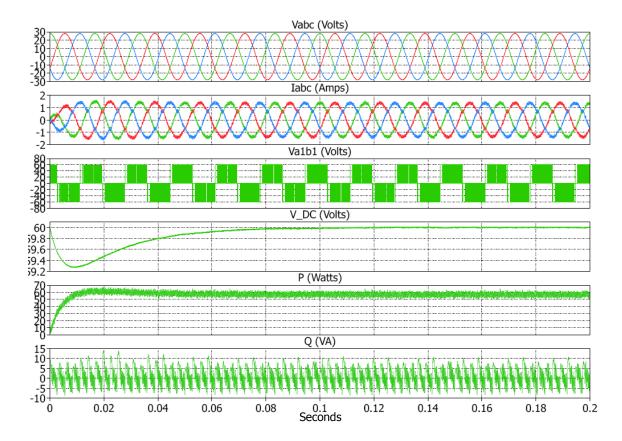

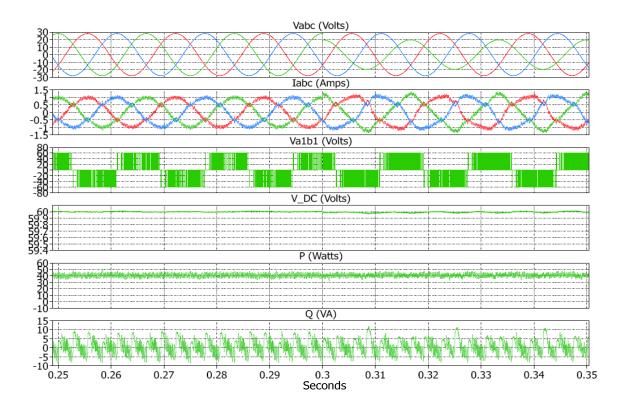

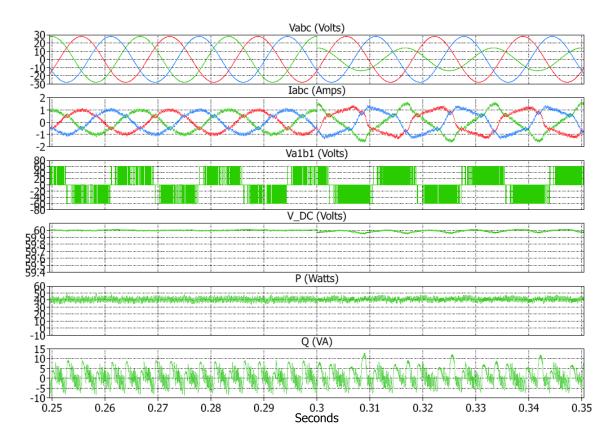

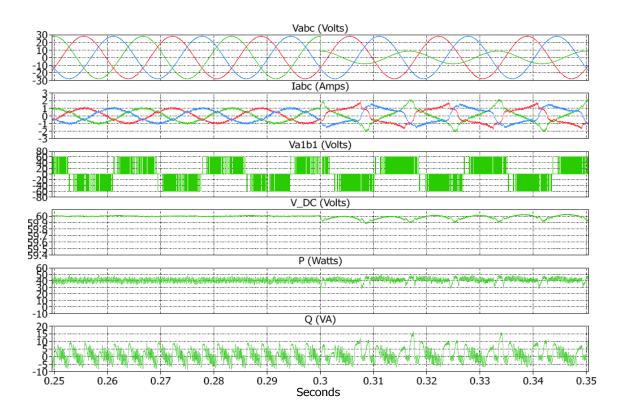

| 5.13. Simulated result for normal operation                             | 90 |

| 5.14. Experimental result for 70% voltage for 2 seconds                 | 91 |

| 5.15. Experimental results for 70% voltage for 2 seconds                | 91 |

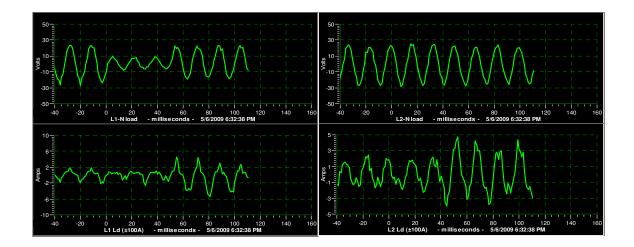

| 5.16. Real and reactive powers for 70% voltage for 2 seconds            | 92 |

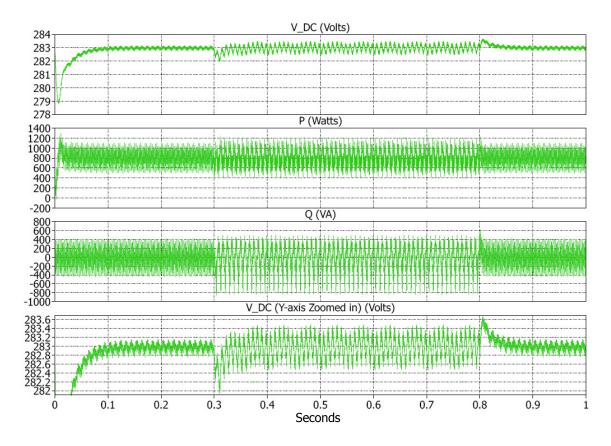

| 5.17. Simulated result for 70% voltage starting at 0.3 s                | 92 |

| 5.18. Experimental result of 50% voltage for 12 cycles                  | 93 |

| 5.19. Experimental results for 50% voltage for 12 cycle starting at 0 s | 94 |

| 5.20. Real and reactive powers for 50% voltage for 12 cycles            | 94 |

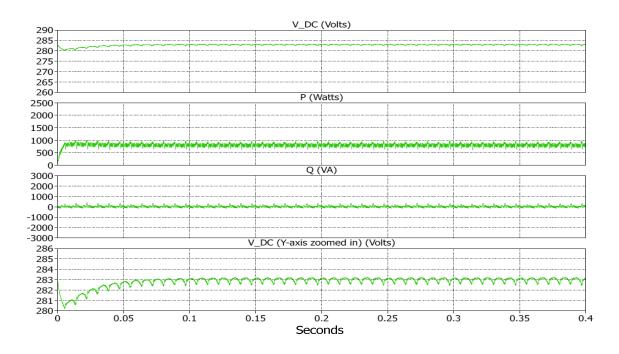

| 5.21. Simulated result for 50% voltage starting at 0.3 s                | 95 |

|-------------------------------------------------------------------------|----|

| 5.22. Experimental result of 30% voltage for 3 cycles                   | 96 |

| 5.23. Experimental results for 30% voltage for 3 cycles starting at 0 s | 96 |

| 5.24. Real and reactive powers for 30% voltage for 3 cycles             | 97 |

| 5.25. Simulated result for 30% voltage starting at 0.3 s                | 97 |

| 5.26. Experimental result of 50% voltage for 1 second                   | 99 |

## LIST OF TABLES

| Table                                                                                                      | Page |

|------------------------------------------------------------------------------------------------------------|------|

| 4.1. Optimal switching table for voltage source converter                                                  | 52   |

| 4.2. Comparison of ripple in DC link Voltage, real power and reactive power for voltage imbalance          | 59   |

| 4.3. Comparison of ripple in DC link Voltage, real power and reactive power for voltage dip                |      |

| 4.4. Optimal switching table for rotor side converter of DFIG                                              | 66   |

| 4.5. Stator, rotor and total real and reactive powers for subsynchronous and supersynchronous operations   | 70   |

| 5.1. Compare registers values of voltage vectors                                                           | 84   |

| 5.2. Comparison of ripple in DC link Voltage, real power and reactive power for different grid code events | 98   |

| 6.1. Summary of the performance of different controllers during system disturbance                         | 103  |

# NOMENCLATURE

| Symbol            | Description                               |

|-------------------|-------------------------------------------|

| $\mathbf{I}_{or}$ | Rotor side current                        |

| I <sub>os</sub>   | Stator side current                       |

| E                 | DC link voltage                           |

| R                 | Series line resistance                    |

| L                 | Series line inductance                    |

| Va                | A phase line to neutral voltage           |

| V <sub>b</sub>    | B phase line to neutral voltage           |

| Vc                | C phase line to neutral voltage           |

| Ia                | A phase line current                      |

| I <sub>b</sub>    | B phase line current                      |

| Ic                | C phase line current                      |

| V <sub>al</sub>   | A phase line to neutral converter voltage |

| V <sub>bl</sub>   | B phase line to neutral converter voltage |

| V <sub>cl</sub>   | C phase line to neutral converter voltage |

| n                 | Neutral point                             |

| V <sub>d</sub>    | d-axis voltage                            |

| Vq                | q-axis voltage                            |

| i <sub>d</sub>    | d-axis current                            |

| iq                | q-axis current                            |

| ω <sub>e</sub>    | Electrical synchronous speed              |

| ω <sub>r</sub>    | Electrical rotor speed                    |

| $\omega_{slip}$      | Electrical slip speed                                     |

|----------------------|-----------------------------------------------------------|

| $\theta_{e}$         | Angular position of the voltage                           |

| ν <sub>α</sub>       | Stationary reference frame alpha voltage                  |

| V <sub>β</sub>       | Stationary reference frame beta voltage                   |

| $\lambda_{s}$        | Stator flux linkages                                      |

| $\lambda_{_{ds}}$    | Stator d-axis flux linkages                               |

| L <sub>o</sub>       | Mutual inductance per phase                               |

| L <sub>s</sub>       | Stator leakage inductance per phase                       |

| L <sub>r</sub>       | Rotor leakage inductance per phase                        |

| L <sub>m</sub>       | Magnetizing inductance per phase                          |

| i <sub>ms</sub>      | Stator magnetizing current                                |

| İ <sub>ds</sub>      | Stator d-axis current                                     |

| İ <sub>dr</sub>      | Rotor d-axis current                                      |

| i <sub>qs</sub>      | Stator q-axis current                                     |

| İ <sub>qr</sub>      | Rotor q-axis current                                      |

| V <sub>dr</sub>      | Rotor d-axis voltage                                      |

| V <sub>qr</sub>      | Rotor q-axis voltage                                      |

| σ                    | Leakage coefficient of induction machine                  |

| R <sub>s</sub>       | Stator resistance                                         |

| R <sub>r</sub>       | Rotor resistance                                          |

| T <sub>e</sub>       | Air gap or electromechanical torque                       |

| $\lambda_{lpha s}$   | Flux linkage of alpha phase in stationary reference frame |

| $\lambda_{ m eta s}$ | Flux linkage of beta phase in stationary reference frame  |

| $V_{\alpha s}$   | Stator alpha voltage in stationary reference frame                 |

|------------------|--------------------------------------------------------------------|

| V <sub>βs</sub>  | Stator beta voltage in stationary reference frame                  |

| $i_{lpha s}$     | Stator alpha phase current                                         |

| $i_{eta s}$      | Stator beta phase current                                          |

| X <sub>a</sub>   | A phase components (voltage/current)                               |

| X <sub>b</sub>   | B phase components (voltage/current)                               |

| X <sub>c</sub>   | C phase components (voltage/current)                               |

| X <sub>mp</sub>  | Positive sequence components (voltage/current)                     |

| x <sub>mn</sub>  | Negative sequence component (voltage/current)                      |

| X <sub>mo</sub>  | Zero sequence component (Voltage/current)                          |

| $lpha_{_p}$      | Positive sequence angle                                            |

| $\alpha_{_n}$    | Negative sequence angle                                            |

| $lpha_0$         | Zero sequence angle                                                |

| $X_{de}$         | d-axis component synchronous reference frame                       |

| $X_{qe}$         | q-axis component synchronous reference frame                       |

| $X_{dpe}$        | Positive sequence d-axis component synchronous reference frame     |

| $X_{qpe}$        | Positive sequence q-axis component synchronous reference frame     |

| $X_{dne}$        | Negative sequence d-axis component synchronous reference frame     |

| X <sub>qne</sub> | Negative sequence q-axis component synchronous reference frame     |

| T <sub>32</sub>  | A, B and C phase to dq transformation                              |

| $X_{abc}$        | A, B and C phase components                                        |

| $X_{qdpe}$       | q-axis sequence components in positive synchronous reference frame |

| $X_{qdne}$       | d-axis sequence components in negative synchronous reference frame |

| R(ωt) | Reference frame transformation |

|-------|--------------------------------|

| κίωι  |                                |

| V <sub>dpe</sub>      | Positive sequence d-axis synchronous reference frame voltage |

|-----------------------|--------------------------------------------------------------|

| V <sub>qpe</sub>      | Positive sequence q-axis synchronous reference frame voltage |

| V <sub>dne</sub>      | Negative sequence d-axis synchronous reference frame voltage |

| V <sub>qne</sub>      | Negative sequence q-axis synchronous reference frame voltage |

| İ <sub>dpe</sub>      | Positive sequence d-axis synchronous reference frame current |

| İ <sub>qpe</sub>      | Positive sequence q-axis synchronous reference frame current |

| İ <sub>dne</sub>      | Negative sequence d-axis synchronous reference frame current |

| İ <sub>qne</sub>      | Negative sequence q-axis synchronous reference frame current |

| Р                     | Real power                                                   |

| P <sub>0</sub>        | Average real power                                           |

| P <sub>c2</sub>       | Real power cosine term coefficient                           |

| P <sub>s2</sub>       | Real power sine term coefficient                             |

| Q                     | Reactive power                                               |

| Q <sub>0</sub>        | Average reactive power                                       |

| Q <sub>c2</sub>       | Reactive power cosine coefficient                            |

| Q <sub>s2</sub>       | Reactive power sine coefficient                              |

| V <sub>a1b1c1</sub>   | Converter A, B and C phase to neutral voltage                |

| İ <sub>abc</sub>      | A, B and C phase source currents                             |

| V <sub>abc</sub>      | A, B and C phase to neutral voltages                         |

| $U_0$ to $U_7$        | space vectors                                                |

| V                     | source phase voltage                                         |

| <b>V</b> <sub>1</sub> | converter phase voltage                                      |

| XL                    | Line inductance                                              |

| $\delta$ Angle between source voltage and converter | voltage |

|-----------------------------------------------------|---------|

|-----------------------------------------------------|---------|

- *P*<sub>*imb*</sub> Real power due to system imbalance

- *Q<sub>imb</sub>* Reactive power due to system imbalance

- $d_p \qquad \qquad \text{digitalized real power output}$

- $d_{\mathsf{q}} \qquad \qquad \text{digitalized reactive power output}$

- p<sub>ref</sub> Real power reference

- q<sub>ref</sub> Reactive power reference

- Theta,  $\theta$  vector position

### **1. INTRODUCTION**

### **1.1 INTRODUCTION**

Wind energy has gained popularity in recent years all over the world, mainly because wind energy is renewable and eco-friendly. There are, however, many challenges associated with harnessing this type of energy for grid application mostly due to its intermittent nature. This dissertation addresses some of the problems associated with the grid integration aspect of wind energy.

Generally, wind power generation uses either fixed speed or variable speed turbines which are classified in to four major types by the Western Electricity Coordinating Council (WECC) to develop industry-standard wind turbine models [1]. These types are briefly described below:

- 1. Pitch regulated squirrel cage induction generator directly coupled to the grid.

- 2. Variable slip squirrel cage induction generator directly coupled to the grid.

- 3. Wound rotor induction generator with an AC/DC/AC power converter connected between the rotor terminals and grid and is pitch regulated.

- 4. Synchronous or asynchronous machine connected to the grid using full rated AC/DC/AC power converter and is pitch regulated.

Type I and II use the simplest topology where the turbine is directly connected to the grid. This type of machine needs a switch to prevent motoring operation during low wind speeds and also suffers a major drawback of reactive power consumption as there is no reactive power control. Type II uses an electronically modulated rotor resistance to effect dynamic changes in the machine torque speed characteristics. Type III is the most common for high power grid applications. This topology allows the complete control of reactive power using rotor and grid side converters and around 25% of the

speed control using rotor side converter. The converters used for this topology need to be rated at only 25% to 30% of overall machine rating as they are used on the rotor side to supply the slip power which is 25% to 30% of the overall machine power. Type IV topology uses a full rated converter with either a synchronous or an asynchronous machine. This type of topology has full control of the reactive power and speed.

The major advantages associated with Type III wind turbines is that it has four quadrant active and reactive power flow capabilities, with constant frequency power output and low power converter ratings making it the most widely used topology. Hence this dissertation focuses attention on the integration of Doubly Fed Induction Generator (DFIG) – Type III based wind turbines to the power grid.

The major issues concerning integration of DFIG wind turbines are that the best wind regimes are located in rural areas and the power grid in these areas is often weak and prone to voltage sags, faults and unbalances. Unbalanced grid voltages can cause many problems for DFIG wind turbines such as torque pulsations, unbalanced currents, and reactive power pulsations. These problems may be attributed to the instability in the power converter's DC link voltage during system disturbances. This issue with the DC link voltage is mainly due to the distorted control in the back to back PWM converters during system unbalance. A review of the pertinent literature reveals several papers addressing the effect of unbalance associated with the DFIG and rotor side converter. This is discussed later in the literature review. The effect of unbalance on the grid side converter is studied in detail in this dissertation and possible remedies for voltage ride through during disturbances are addressed.

### **1.2 DISSERTATION OUTLINE**

The later part of this section deals with major codes followed by US and European grid networks during grid disturbances. A brief literature review of the existing remedies associated with the PWM converters that can be possibly adapted for DFIG based wind turbine generators is also presented in this section.

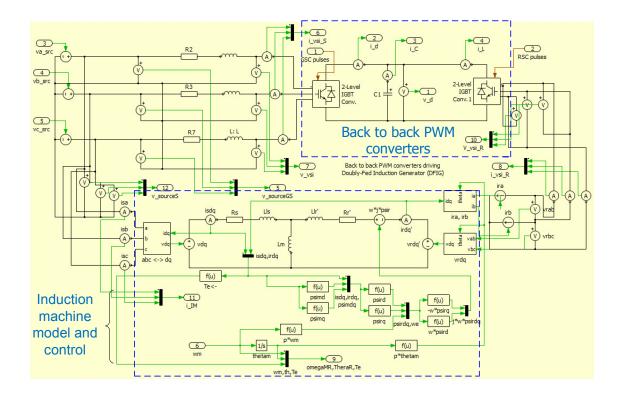

The detailed operation of DFIG control using the conventional current control techniques are discussed in section two using a mathematical model in Matlab Simulink<sup>®</sup> and also with a more detailed model in DIgSILENT<sup>®</sup>. The effect of grid imbalances are also analyzed using these models.

The effect of unbalance on the grid side converter is analyzed in detail in section three. An advanced control technique using sequence controllers to stabilize the operation of the grid-side converter during grid imbalance is also presented in detail in this section.

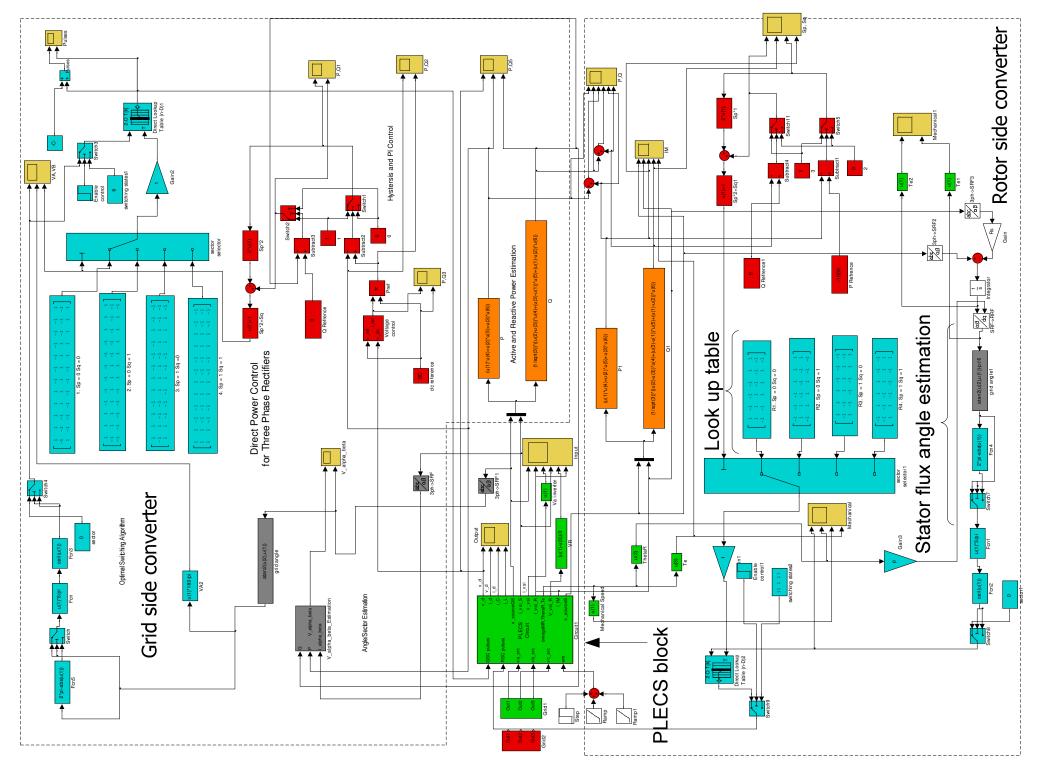

A novel control technique using direct active and reactive power control called Direct Power Control (DPC) is discussed in section four. This controller eliminates the conventional current loops and uses delta modulation comparators, hence has faster response. The switching of the converter is done using a simple optimum switching table. A Grid-side controller is simulated and the results are compared with the conventional and sequence controllers. A complete DFIG including the rotor side and grid-side converters is simulated using DPC and is tested for ride through during system and grid disturbances.

Section five discusses the hardware implementation of a grid side converter using DPC. A 2kW converter is designed using Eagle<sup>®</sup> for PCB design. The control is coded in C and implemented in TMS320F2812 DSP. The converter using DPC is tested for system unbalance conditions created by an Industrial Power Corruptor (IPC) [2] in the laboratory. The laboratory results are compared with the simulation results for accuracy errors and verification.

The concluding remarks and summary of the work along with some future developments are discussed in section six. The Appendix presents the system parameters, circuit diagrams and the C code used for hardware implementation.

### **1.3 GRID CODES**

Grid codes determine the requirement of the wind power systems to stay connected to the grid during grid disturbances. The codes are typically described on a time voltage diagram as in Figure 1.1, Figure 1.2 and Figure 1.3. These diagrams contain safe limits or the border of operation of wind power plants. The system should remain connected during the fault inception and post fault recovery time according to the border limits and the times mentioned in the grid code diagrams.

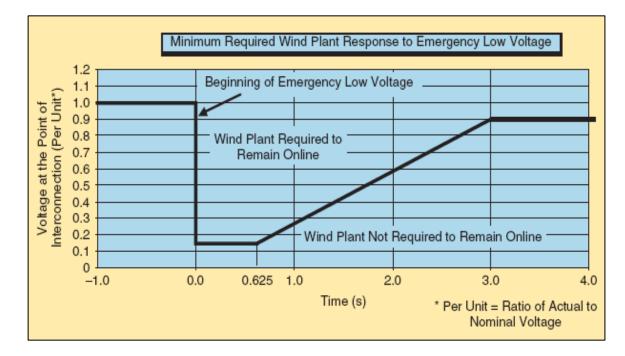

According to the Low Voltage Ride Through (LVRT) requirement for wind generation facilities per Federal Energy Regulatory Commission (FERC) order No. 661 [3] the grid code standard requires that the machine stay connected for emergency low voltages at the terminals for as low as 15% of nominal per unit voltage for approximately 0.6 seconds. This time increases as the terminal voltage requirement increases. For example during the post-fault recovery, the wind power system should be able to withstand a low voltage of 60% at the terminal for a time period of two seconds as shown in Figure 1.1. In practice, the high voltage drop during grid disturbance gives rise to rotor protection which acts to short circuit the dc link capacitor (via a crowbar) in order to protect the converter and the associated components from high currents [4].

Figure 1.1. LVRT requirements for emergency low voltage per FERC order No. 661 [3]

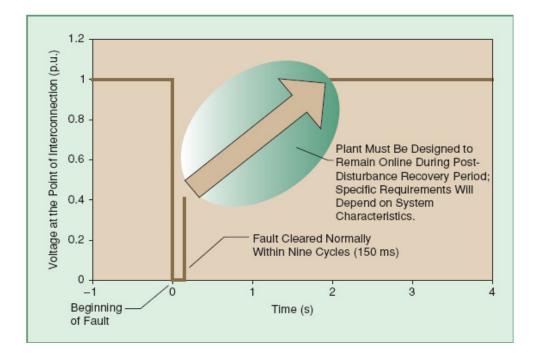

The North American Electrical Reliability Corporation (NERC) and American Wind Energy Association on behalf of FERC had discussions to resolve the issues with FERC order 661 [5]. According to these discussion, "*the new language stated that wind generating plants are required to remain in service during three phase faults with normal clearing (which is a time period of approximately four to nine cycles) and single line to ground faults with delayed clearing, and subsequent postfault voltage recovery to prefault voltage unless clearing the fault effectively disconnects the generator from the system*" [5]. According to this new practice the old voltage versus time curve is no longer applied and the code is to go with post-fault clearing time as show in Figure 1.2.

Figure 1.2. LVRT requirements at the point of intersection FERC Order 661 A [5]

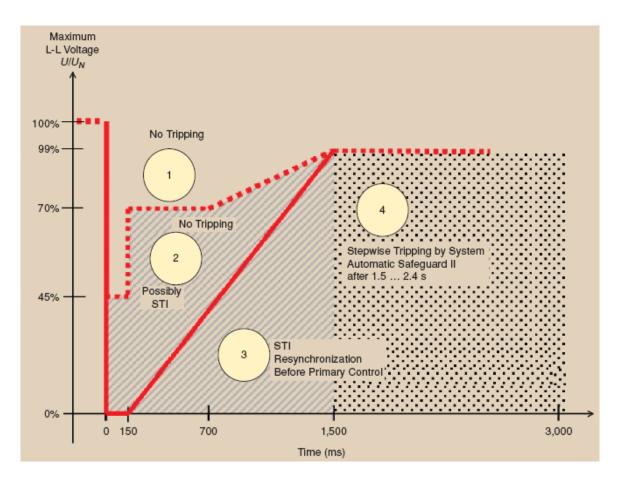

Fault Ride Through (FRT) requirements of Germany are based on the time voltage diagram shown in Figure 1.3 [6]. These requirements state that the wind turbine has to connect to the grid within areas 1 and 2. Possible Short Term Interruption (STI) of less than 2 seconds can occur within area two due to over load or stability concerns or other kinds of technical problems. Short disconnection of the turbine is allowed in area 3 whereas resynchronization of the turbine is necessary after two seconds. Step wise tripping of the wind turbine is allowed in area 4.

Figure 1.3. Definition of Fault ride through (FRT) requirement in Germany [6]

Looking at different grid codes, it can be concluded that DFIG controllers should be capable of overcoming temporary voltage disturbances. Hence, this work deals with the design of controllers that would keep the wind turbine in stable operation during a fault causing a low voltage of up to 40% for two seconds. This type of fault is of importance because the rotor need not be protected by crowbar during this time and the back-to-back PWM converters work normally even with the unbalance. The proposed controllers are tested for different fault conditions for ride through on the grid side as well as the turbine side.

### **1.4 LITERATURE REVIEW**

Advanced control techniques for power converter control are reviewed in this literature review. Some of the controllers are adopted for implementation with DFIG to counter system imbalances. The control techniques are broadly divided into three major methods based on their operation. The first type is based on decomposing the system voltage and currents into symmetrical components and using different controllers in positive and negative sequence components [7] through [13].

Enjeti and Choudhury [7] propose a technique which counter balances the gating signals so that the imbalance in the supply is rectified. The technique is a feed-forward approach where the sequence components of the unbalanced input supply are calculated and are used to counter-unbalance the PWM gating signals of the converter switches to cancel the generated abnormal harmonics. This method is suitable for high power GTO-type PWM ac to dc converters.

Rioual et al. [8] propose a cascade regulation of PWM rectifier in the Park's d-q frame. The system is distributed with unbalanced voltage; the regulation is calculated with a positive sequence network voltage as well as a negative sequence network voltage separately. This control achieves desired positive and negative sequence current commands for a constant dc link voltage and average reactive power.

Kim et al. [9] propose a PWM converter where decomposition into symmetrical components of input voltage is needed. The negative sequence current component is commanded to be zero. It is observed that negative sequence is transformed into the second harmonic component on the synchronous reference frame and the positive sequence can be detected using a band pass filter with center frequency of 120 Hz.

Seok and Nam [10] propose a dual converter scheme where two reference frames are used for measuring the positive sequence in the positive synchronous reference frame (SRF) by eliminating the negative sequence with the 120 Hz and negative sequence in negative SRF. Separately measured currents are used for two feedback PI controllers called as the dual current controller. One regulates the positive sequence current and the other regulates the negative sequence current thus allowing the control of the negative sequence in its own frame.

Giuseppe et al. [11] propose two different controllers to deal with unbalanced conditions. The first controller is implemented in the positive synchronous reference frame. Active and reactive currents are controlled independently of each other with a high bandwidth. The second controller uses a feed forward approach for sequence separation. The DC link voltage controller used in this case is the same as that for the first controller. A third controller similar to the one proposed in [10] is considered; however the transient performance of the controller is not analyzed in [10].

Lie Xu et al. [12] proposed the use of a main controller using decoupled control without positive and negative sequence decomposition and an auxiliary controller in negative sequence with inclusion of cross coupling for negative sequence components. Lie Xu [13] Proposed complete modeling of the DFIG in positive and negative sequence to deal with network disturbances.

The second method proposed by Slavomir et al. [14-15] discusses a finite element modeling (FEM) of the magnetic field in the generator in two dimensions. This model takes into account magnetic saturation of the stator and the rotor leakage inductances. The large difference from the conventional model is that, during an

9

unsymmetrical fault, the FEM model represents unsymmetrical magnetic saturation better than the conventional analytical models.

The third method is based on a novel control technique that directly controls the active and reactive power of the systems. This method more suits the controllers used to connect the utility as this directly achieves the unity power factor requirement of the utility. References [16] to [18] discuss the concept as applied to the grid side and rotor side converters of the DFIG. In references [19] and [20], the authors modify the control and the switching table to accommodate for system disturbance and include the power due to imbalance.

Noguchi et al. [16] propose direct power of a three-phase Pulse Width Modulated (PWM) converter without line voltage sensors. In this control the real and reactive powers are calculated as the sum of power consumed by the inductance and the converter. The voltage angle is calculated from the powers and the currents.

Mariusz et al. [17] propose direct power control of three-phase pulse widthmodulated rectifiers without line voltage sensors. The control is based on assuming the three phase grid as a virtual induction machine and the flux in the virtual machine is defined as virtual flux (VF). It is shown that the VF-DPC exhibits several advantages, particularly providing sinusoidal line current when the supply voltage is not ideal.

Rajib Datta et al. [18] proposed a method of direct decoupled control of active and reactive powers. The algorithm extends the switching logic of Direct Torque Control (DTC) to the rotor side of a doubly-fed wound rotor induction machine. The direct power control algorithm uses only stator quantities for active and reactive power measurements and is inherently position-sensorless. It is computationally simple and does not incorporate any machine parameter. The algorithm can start on the fly and operate stably at synchronous speed.

Geardo Escobar et al. [19] proposed a direct power control where the controller builds upon the ideas of the well-known direct torque control technique for induction motors. The active and reactive powers replace the torque and flux amplitude using the controlled outputs in DPC. A simple modification of the original algorithm utilizing the concept of output regulation subspaces was formalized. A modification was added to the basic controller to deal with disturbances such as unbalance and distortion in the source voltage.

Santos-Martin et al. [20] presented a novel control strategy for a DFIG machine based on direct power control (DPC+) that includes power due imbalance. This method enables DFIG to work under perturbed conditions and achieve optimum results.

### **1.5 SUMMARY**

Sequence controllers and direct power controller techniques would be suitable solutions to address the issue of voltage unbalances for low voltage or fault ride through situations. Sequence controllers are adopted for system stability during disturbances and they are further analyzed in the next two sections. The DPC for wind turbines have been mostly applied to the rotor side converter and the DFIG machine. Hence a similar idea is investigated in this dissertation for grid side converter during disturbances.

# 2. CONVENTIONAL DFIG CONTROL AND OPERATION DURING GRID DISTURBANCES

### **2.1 INTRODUCTION**

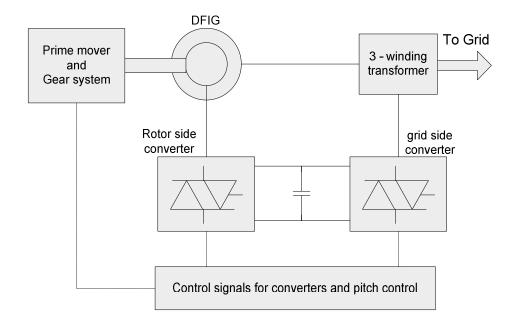

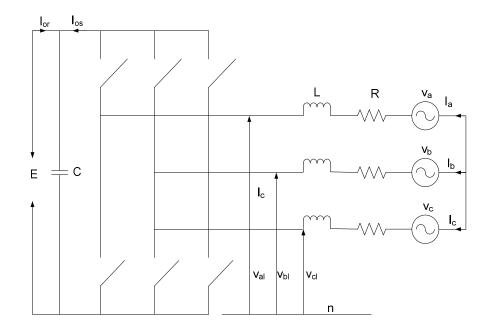

The general operation of a DFIG is discussed in brief by S Muller et al. [21] and a detailed analysis of the control system is discussed by R Pena et al. [22], Vladislav et al. [23] and Nicholas et al. [24]. The DFIG model is shown in Figure. 2.1.

Figure 2.1. DFIG model

The prime mover utilizes a pitch angle controlled wind turbine where the shaft and gear box drive a doubly-fed induction machine. The stator of the machine is connected to the grid. The rotor of the induction machine is fed by self-commutated pulse width modulated converters which control the rotor voltage and angle, thus allowing active and reactive power control. The voltage or the reactive power at the grid terminals, which is dependent on stator flux, is controlled by the reactive power generated or absorbed by the rotor side converter. Hence the current controller operates in a stator-flux oriented reference frame. In this reference frame, the q-axis component of the rotor current directly influences the torque and, hence, is used for active power control. The d-axis component of the rotor current directly influences the reactive power and hence can be used for reactive power control.

The active power dispatch of the wind turbine is by a look-up from power versus mechanical speed graphs or maximum power tracking (MPT) characteristics [22]. Alternatively, the induction machine operates using a reverse control scheme where the mechanical speed is calculated by inverse MPT characteristics.

The grid side controller uses a global reference frame which rotates at reference speed. The direct axis reference of this converter is set by the commanded DC voltage. The model allows using a grid converter to generate or absorb reactive power using a guadrature axis reference. Generally, this reference is kept constant.

#### 2.2 CONVENTIONAL DECOUPLED CONTROL

Controllers used for three-phase PWM converters are generally designed on the assumption that the input voltage is balanced. They are implemented in the synchronous reference frame (SRF) as it eliminates steady state error and the control is decoupled. These controllers do not behave as expected when the input is unbalanced like in the case of voltage sags, Single Line to Ground (SLG) faults, Double Line to Ground (DLG) faults, etc.

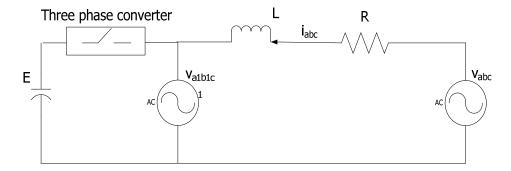

A conventional control scheme based on [22] is implemented first in Matlab Simulink<sup>®</sup> and tested for different unbalanced conditions. The objective of this converter is to regulate the DC link voltage to a constant value irrespective of the disturbances due to the rotor-side converter. A standard design technique used by Pena [22] is used to regulate the DC-link voltage and reactive power. Predictably, the converter does not function well during the imbalance in the system. The PWM converter under analysis for the above schemes is shown in Figure 2.2.

Figure 2.2. PWM converter

In this converter, a stator voltage vector-oriented reference frame is used. This allows the PWM converter to be current regulated; with the direct axis current regulating the DC-link voltage and the quadrature axis current regulating the reactive power. The voltage balance across the inductor is:

$$\begin{pmatrix} v_a \\ v_b \\ v_c \end{pmatrix} = R \cdot \begin{pmatrix} i_a \\ i_b \\ i_c \end{pmatrix} + L \cdot \frac{d}{dt} \begin{pmatrix} i_a \\ i_b \\ i_c \end{pmatrix} + \begin{pmatrix} v_{aI} \\ v_{bI} \\ v_{cI} \end{pmatrix}$$

(1)

L and R are the line parameters. Using the dq transformation rotating at synchronous speed, d-axis and q-axis voltage are:

$$v_d = R \cdot i_d + L \cdot \frac{d}{dt} i_d - \omega_e \cdot L \cdot i_q + v_{d1}$$

<sup>(2)</sup>

$$v_q = R \cdot i_q + L \cdot \frac{d}{dt} i_q + \omega_e \cdot L \cdot i_d + v_{ql}$$

<sup>(3)</sup>

The angular position of the voltage is calculated by (4).

$$\theta_{e} = \int \omega_{e} dt = atan\left(\frac{v_{\beta}}{v_{\alpha}}\right)$$

(4)

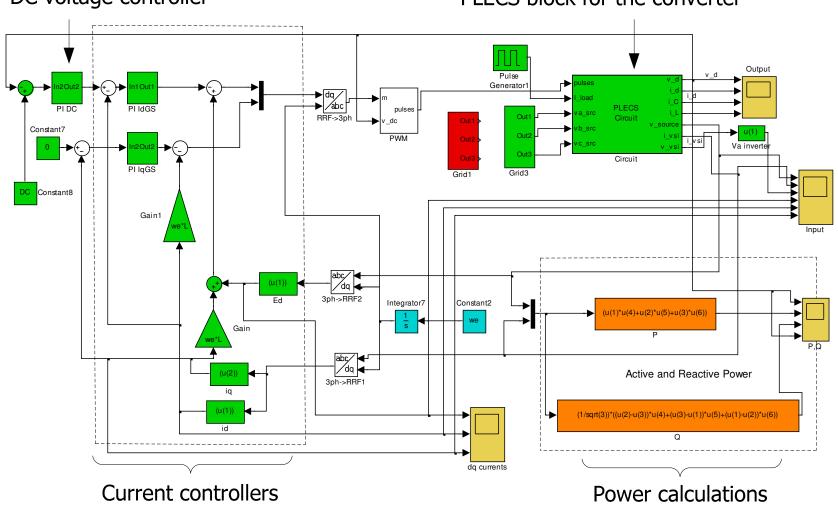

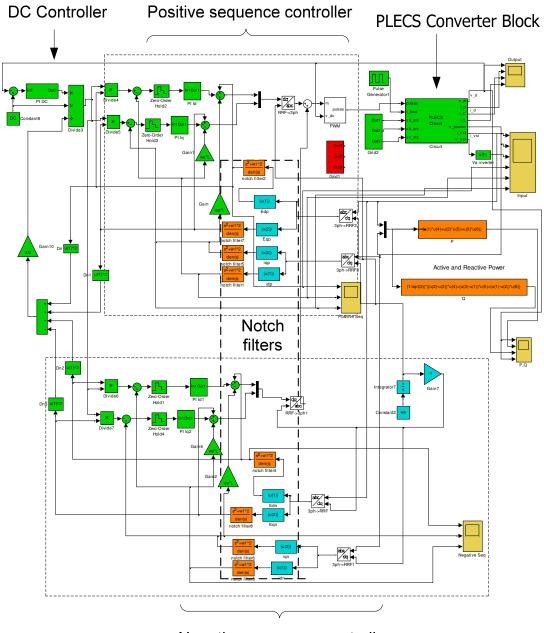

$V_{\alpha}$  and  $V_{\beta}$  are the  $\alpha, \beta$  (stationary 2-axis) stator voltage components. Aligning the daxis along the stator-voltage vector position given by (3) gives  $V_q = 0$  and a constant  $V_d$ . The active and reactive powers are proportional to the d-axis and q-axis current, respectively. Two current loops with PI controllers are independently implemented in these reference frames. The control strategy implemented in Matlab Simulink<sup>®</sup> using PLECS<sup>®</sup> tool box is shown in Figure 2.3 and the circuit is shown in Figure 2.4. The parameters used in the circuit are tabulated in Table A.1 of Appendix A.

(2)

DC voltage controller

PLECS block for the converter

Figure 2.3. Conventional current control block diagram for grid-side converter

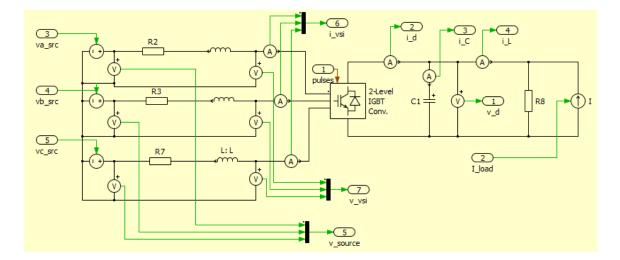

Figure 2.4. PLECS<sup>®</sup> Circuit diagram for grid-side converter

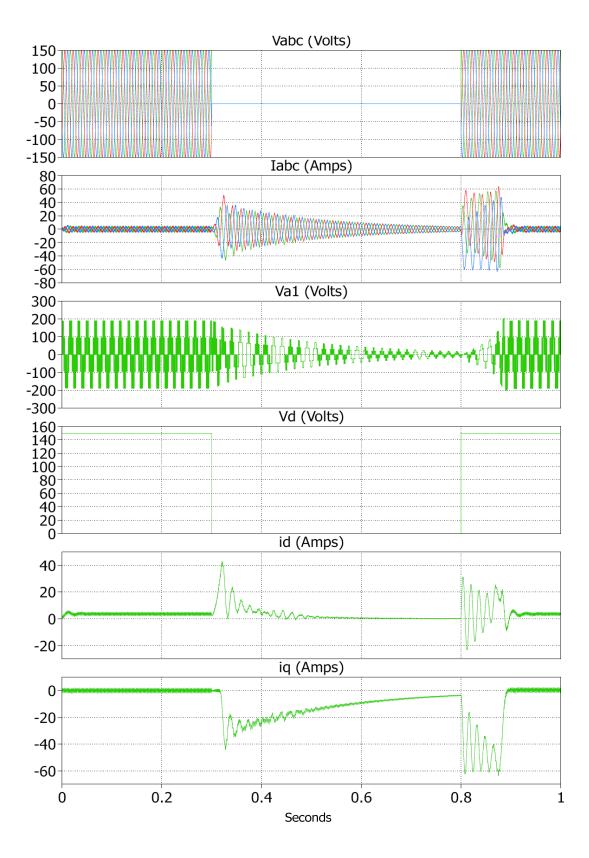

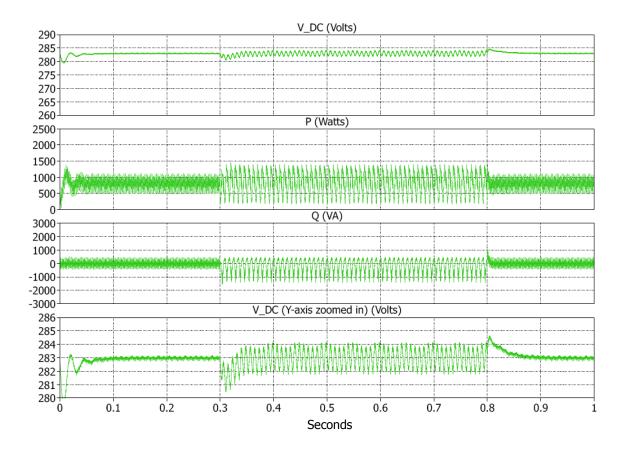

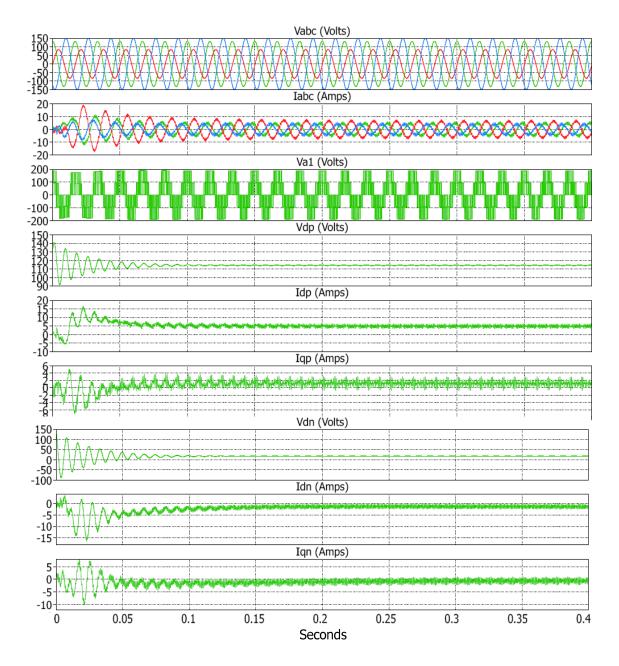

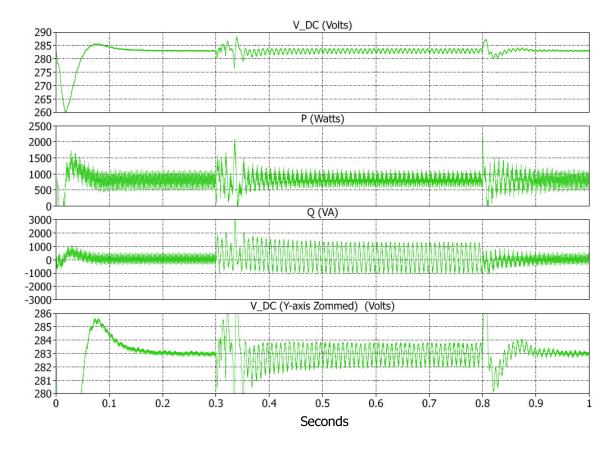

The discrete domain controllers designed by Pena [22] are implemented in the simulation by converting them to the continuous domain equivalent. The simulation is run for two different disturbances - one a three phase fault, shown in Figure 2.5 and Figure 2.6, which is a balanced disturbance, and the other a single line to ground fault, shown in Figure 2.7 and Figure 2.8, which is an unbalanced disturbance.

In the three phase fault case (Figure 2.5 and Figure 2.6), as the three phases are balanced, there is no negative sequence in the input voltage; hence, the disturbance does not affect the conventional control technique based on Park's transforms but the capacitor voltage decays with a time constant of RC circuit due to the load resistance and the dc link capacitance.

Figure 2.5. Simulation of a three phase fault (from top source voltage, source currents, converter voltage, d-axis voltage, d-axis current and q-axis current)

Figure 2.6. Simulation of a three phase fault (from top DC link voltage, real power, reactive power and DC link voltage)

In the single line to ground fault case (Figure 2.7 and Figure 2.8), the source voltage has a negative sequence component and hence there is a ripple in the dc link voltage. A double frequency ripple carries over to the d-axis voltage as well as in real and reactive power. The source currents are also distorted as the commanded voltages are perturbed due to the system disturbance.

Figure 2.7. Simulation of a single line to ground fault (from top source voltage, source currents, converter voltage, d-axis voltage, d-axis current and q-axis current)

Figure 2.8. Simulation of a single line to ground fault (from top DC link voltage, real power, reactive power and DC link voltage Y-axis zoomed)

# 2.3 DFIG AND ROTOR-SIDE CONVERTER CONTROL

The objective of the rotor-side converter is to supply currents to the rotor-side part of the induction machine such that the grid-side active and reactive power is maintained according to the power tracking and desired power factor. The equations associated with the machine are from Leohard [25] and Chellapilla [26]. This converter is controlled in a dq axis reference frame with d-axis oriented along the stator-flux vector position. This reference frame allows a decoupled control between electric torque and rotor excitation. Since the stator is connected to an infinite grid and stator resistance is small, the stator magnetizing current is assumed to be constant. The associated equations are (5)-(14).

$$\lambda_s = \lambda_{ds} = L_o i_{ms} = L_s i_{ds} + L_o i_{dr}$$

<sup>(5)</sup>

$$\lambda_{qr} = \sigma L_r i_{qr} \tag{6}$$

$$\lambda_{dr} = \frac{\left(L_o\right)^2}{L_s} i_{ms} + \sigma L_r i_{dr}$$

<sup>(7)</sup>

$$i_{qs} = \frac{-L_o}{L_s} i_{qr} \tag{8}$$

$$v_{dr} = R_r i_{dr} + \sigma L_r \frac{d}{dr} i_{dr} - \omega_{slip} \sigma L_r i_{qr}$$

<sup>(9)</sup>

$$\omega_{slip} = \omega_e - \omega_r \tag{10}$$

$$v_{qr} = R_r i_{qr} + \sigma L_r \frac{d}{dr} i_{qr} - \omega_{slip} (\sigma L_r i_{dr} + L_m i_{ms})$$

(11)

$$T_e = -3\frac{P}{2}L_m i_{ms} i_{qr} \tag{12}$$

$$L_m = \frac{\left(L_o\right)^2}{L_s} \tag{13}$$

$$\sigma = 1 - \frac{(L_o)^2}{L_s L_r} \tag{14}$$

The reference frame angle is calculated using (4) and (15)-(16). The stator flux speed is obtained from the derivative of the stator flux position ( $\theta_s$ ). Stator flux speed is calculated using the differentiation of the rotor angle. The differentiator function in math

packages like Simulink<sup>®</sup> amplifies the error in the signal to a greater extent. Hence the differentiation is carried by applying the formula of arc tangent as shown in (17).

$$\lambda_{\alpha s} = \int (v_{\alpha s} - R_s i_{\alpha s}) dt \tag{15}$$

$$\lambda_{\beta s} = \int (v_{\beta s} - R_s i_{\beta s}) dt \tag{16}$$

$$\frac{d\theta}{dt} = \frac{\lambda_{\alpha s} (v_{\alpha s} - R_s i_{\alpha s}) - \lambda_{\beta s} (v_{\beta s} - R_s i_{\beta s})}{\lambda_{\alpha s}^2 + \lambda_{\beta s}^2}$$

(17)

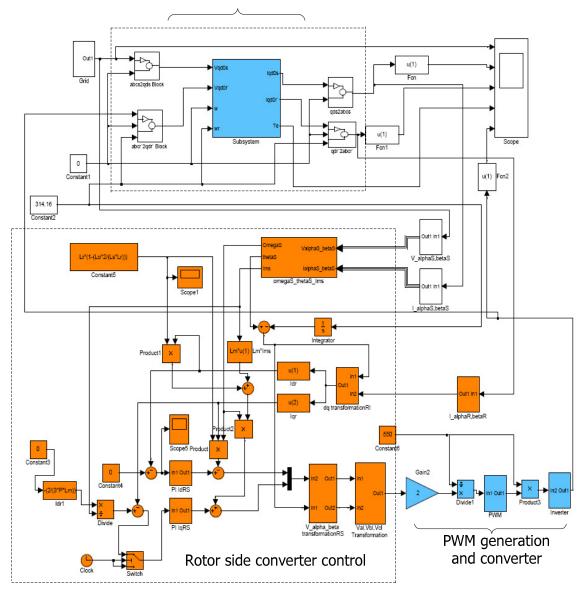

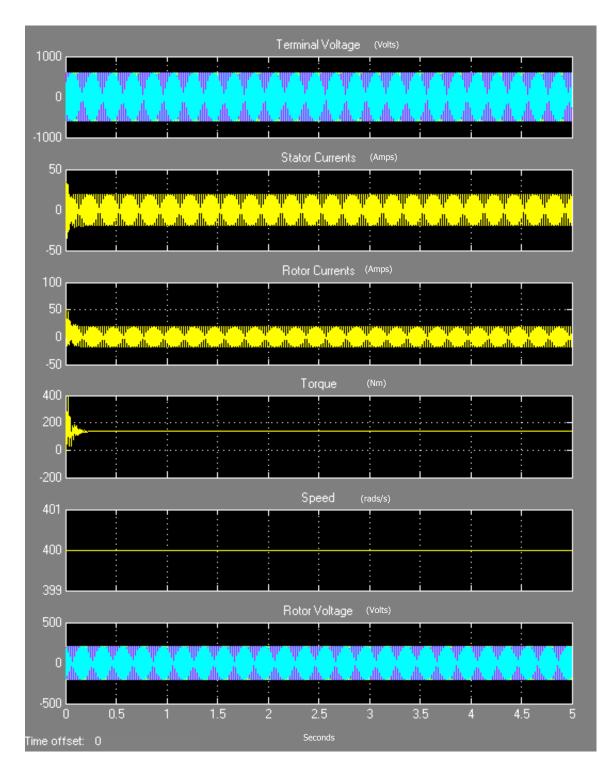

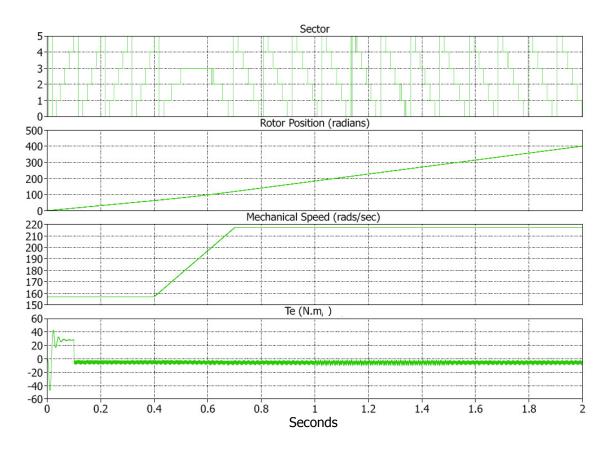

The induction machine is simulated in the stationary reference frame. The control diagram for the induction machine is shown in Figure 2.9. Figure 2.10. shows simulation of induction machine above rated speed (Input - 400 rad/sec). It can be observed that the machine is demanding negative torque which means it is producing power. The second simulation is carried out on the complete DFIG at rated speed demanding zero torque as in Figure 2.11. It can be seen that the rotor torque has an average value of zero but with perceivable oscillations. These are due to approximations and errors in calculating the stator flux speed and reference angle.

Induction machine model

Figure 2.9. Rotor side converter and induction machine implementation

Figure 2.10. DFIG operation above rated speed

Figure 2.11. Rotor Side converter at rated speed

# 2.4 DFIG MODEL USING DIgSILENT<sup>®</sup>

A more robust model needs to be used to simulate the faults on the complete system. Review of various wind turbine models in different platforms are discussed in [27]. DIgSILENT<sup>®</sup> PowerFactory has dynamic models for wind turbine applications as discussed in [28]. Interactions between electric grid phenomena and the wind turbine using these models are discussed in [29]. Hence a dynamic DFIG-based wind turbine model [30] in DIgSILENT<sup>®</sup> mainly intended for stability analysis of large power systems is used in this study. Preliminary simulation with this model for different grid and system disturbances are discussed in [31].

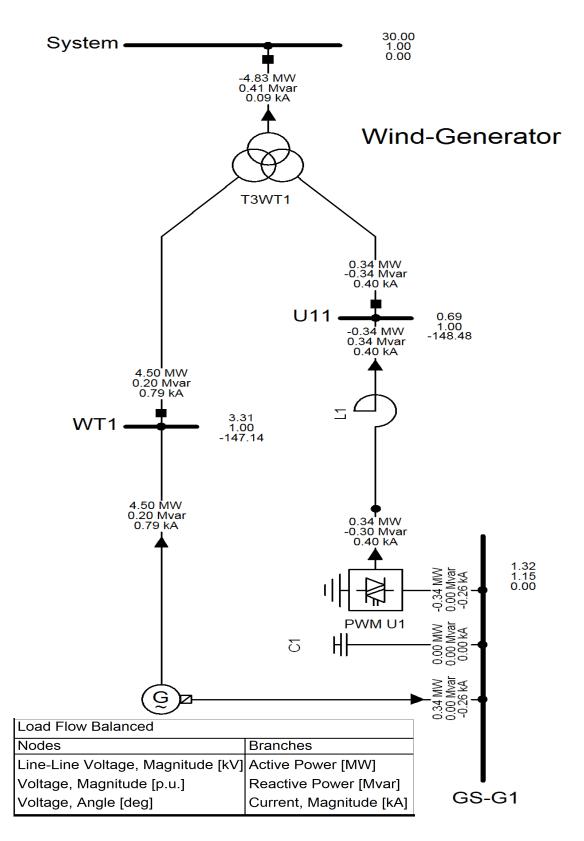

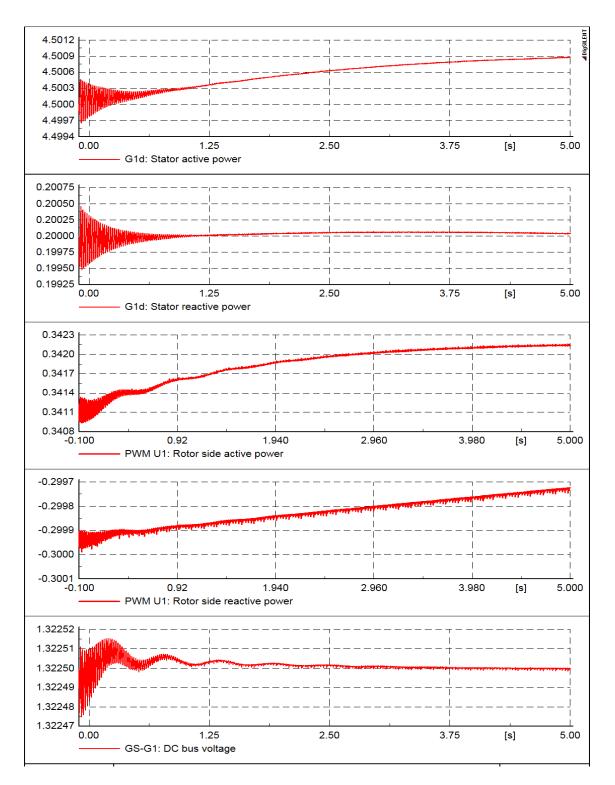

The wind turbine model and power system are initially simulated for typical transient analysis for the rated values of the machine without any disturbance. The setup of the machine along with load flow is shown in Figure 2.12. Typical quantities versus time are shown in Figure 2.13. The simulation is executed for 5 seconds. The wind speed (vw) is assumed to be constant at 13.8 m/s and the output rated power of the wind turbine is 5 MW.

The simulation achieved its steady state after approximately a second. The wind speed (vw) is assumed to be constant at 13.8 m/s and the output rated power of the wind turbine is 5 MW. The simulation achieved its steady state after approximately a second. The real power commanded is 4.5 MW, reactive power is 0.2 MVar, the rotor side dc voltage commanded is 132.25V (1.15 per unit) and the reactive power commanded is -0.3 MVar.

Figure 2.12. DFIG Model in DIgSILENT<sup>®</sup>

Figure 2.13. Normal Operation (Y-axis in pu)

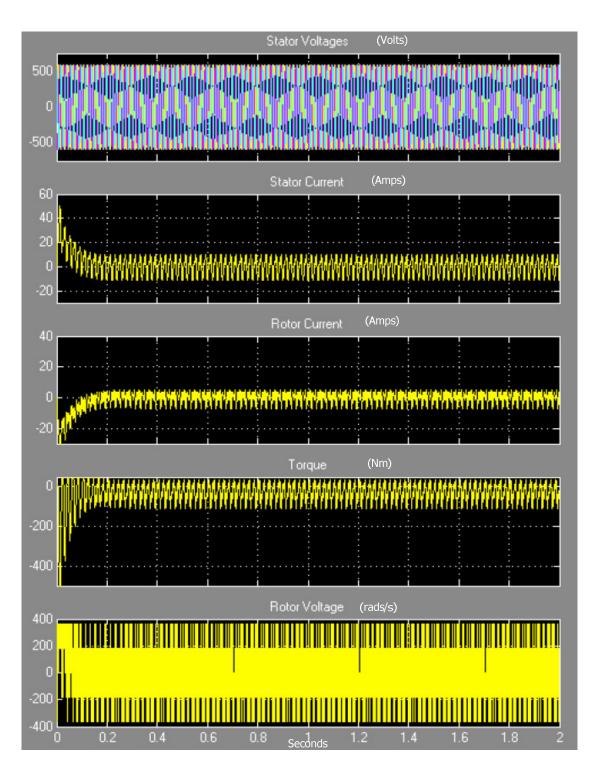

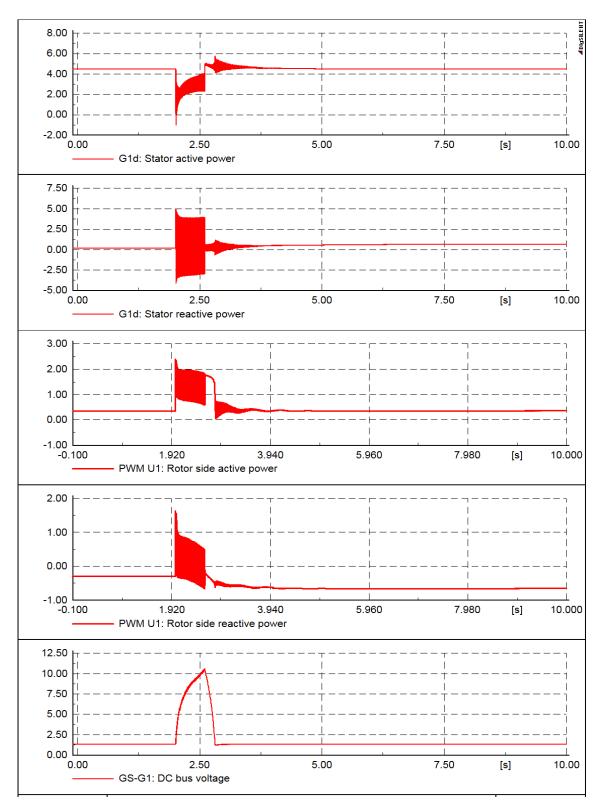

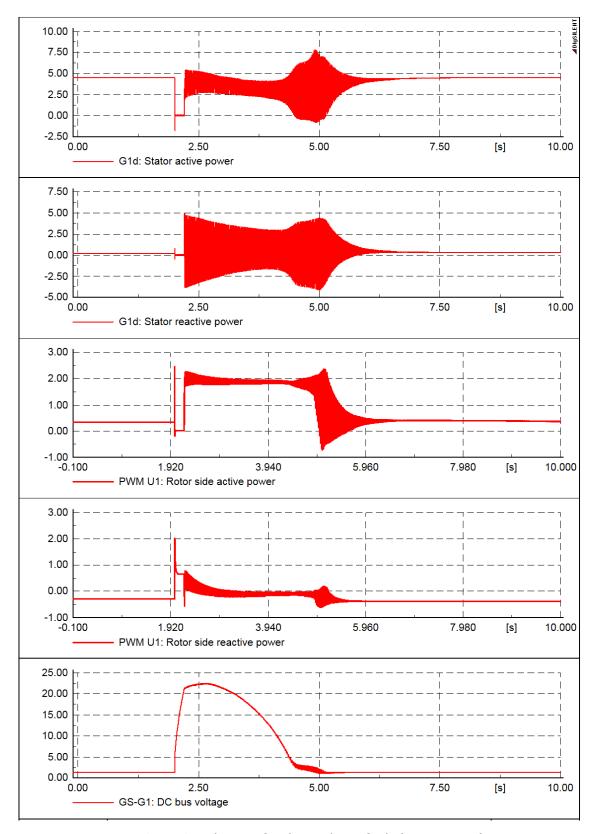

A single line to ground fault is simulated for 600 ms. This fault causes a total voltage depression due to under voltage. The system is simulated for 10 seconds. Figure 2.14 shows the simulation results. It can be observed that the voltage of the dc bus is drastically increased to nine times the nominal voltage. Since this is undesirable, the rotor side system is short circuited during the inception if a fault.

A three phase fault is simulated near the system for 200 ms causing a full voltage collapse. The simulation results are shown in Figure 2.15. In this case it takes a longer time for the simulation to settle back after the fault event. The real power and reactive power takes much longer time to settle back compared the remaining quantities

As in the case of the single line to ground fault, the DC bus voltage increases drastically due to the fault to a value approximately 18 times the nominal voltage value (twice that of the single line to ground fault case). From the above cases it can be concluded that if there was a protection for rotor currents the rotor side converter would be disconnected during the event and the generator speed would increase. The rise in the dc link voltage is attributed to magnetic coupling between stator and rotor. The rise in the stator current induces high current in the rotor that flows through the rotor side converter [32]. The additional energy goes into charging the dc bus capacitor and thus the dc bus voltage rises rapidly, depending on the design of the converter, it is possible to limit the current by current-control on the rotor side of the converter; however this will lead to high voltages at the converter terminals that might also damage the converter. Normal practice is to equip the rotor side converter with crowbar protection during faults and voltage dips [33].

Figure 2.14. Simulation of a SLG fault (Y-axis in pu)

Figure 2.15. Simulation of a three phase fault (Y-axis in pu)

# 2.5 SUMMARY

This section described the operation of conventional back-to-back PWM converters for DFIG based wind turbines. In the operation, the grid side controller uses stationary dq reference frame current loops to control the dc link voltage and the reactive power. The rotor side controller uses stator flux orientation reference frame to control the real and reactive power from the stator according to the speed and wind efficiency curves. Different fault scenarios are analyzed to test the operation of the controllers during disturbances. The Conventional control technique creates oscillations in the DC link voltage and distortion in the source currents during system disturbances.

# **3. ANALYSIS OF UNBALANCED INPUTS AND SEQUENCE CONTROLLERS**

# **3.1 INTRODUCTION**

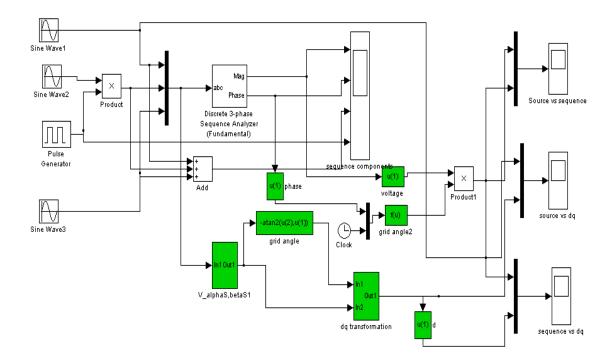

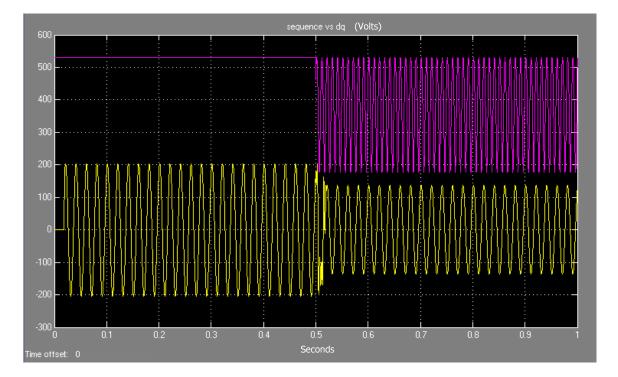

A disturbance on the grid voltage is generally characterized by an imbalance in the voltage or the current, either in magnitude or phase. The nature of the disturbance may be analyzed using symmetrical components theory. Hence, the control of a voltage source converter during a grid disturbance is studied using symmetrical components and multiple reference frame theory. The present work integrates several control and modeling techniques to develop a grid-side controller suitable for low voltage ride through of a DFIG. The change in the voltage dq components during a disturbance is discussed using a simple simulation using Matlab Simulink <sup>®</sup> as shown in Figure 3.1.

Figure 3.1. Sequence components and park's co-ordinates during a voltage imbalance

In the simulation, a line to ground fault is simulated in a balanced set of voltages after 0.5 sec. The simulation is run for 1 second. The simulation of the sequence components shows that the decoupled control during the imbalance gives rise to a negative sequence component in the output which is twice the source frequency. The simulation results are shown in Figure. 3.2. As expected, the negative sequence component appears as a second harmonic component in the synchronous reference frame.

Figure 3.2. Voltage vs. dq components for a voltage disturbance

# **3.2 SEQUENCE COMPONENTS D-Q ANALYSIS**

Any three phase quantities may be represented in sequence components using (18) [9].

$$\begin{pmatrix} X_{a} \\ X_{b} \\ X_{c} \end{pmatrix} = x_{mp} \cdot \begin{pmatrix} \cos(\omega t + \alpha_{p}) \\ \cos(\omega t + \alpha_{p} - \frac{2 \cdot \pi}{3}) \\ \cos(\omega t + \alpha_{p} + \frac{2 \cdot \pi}{3}) \end{pmatrix} + x_{mn} \cdot \begin{pmatrix} \cos(\omega t + \alpha_{n}) \\ \cos(\omega t + \alpha_{n} + \frac{2 \cdot \pi}{3}) \\ \cos(\omega t + \alpha_{n} - \frac{2 \cdot \pi}{3}) \end{pmatrix} + x_{m0} \cdot \begin{pmatrix} \cos(\omega t + \alpha_{0}) \\ \cos(\omega t + \alpha_{0}) \\ \cos(\omega t + \alpha_{0}) \end{pmatrix}$$

(18)

$x_{\partial r} x_{Dr} x_{C}$  are transformed into synchronous d-q axis using (19) and (20).

$$\begin{pmatrix} X_{qe} \\ X_{de} \end{pmatrix} = \frac{2}{3} \begin{pmatrix} \cos(\omega \cdot t) & -\sin(\omega \cdot t) \\ \sin(\omega \cdot t) & \cos(\omega \cdot t) \end{pmatrix} \cdot \begin{pmatrix} 1 & \frac{-1}{2} & \frac{-1}{2} \\ 0 & \frac{-\sqrt{3}}{2} & \frac{\sqrt{3}}{2} \end{pmatrix} \cdot \begin{pmatrix} X_a \\ X_b \\ X_c \end{pmatrix}$$

(19)

$$T_{32}^{T} = \begin{pmatrix} 1 & \frac{-1}{2} & \frac{-1}{2} \\ 0 & \frac{-\sqrt{3}}{2} & \frac{\sqrt{3}}{2} \end{pmatrix}$$

(20)

The simplification of the equation is shown in (21) through (26).

$$\frac{2}{3} \cdot \begin{pmatrix} \cos(\omega \cdot t) & -\sin(\omega \cdot t) \\ \sin(\omega \cdot t) & \cos(\omega \cdot t) \end{pmatrix} \cdot T_{32}^{T} = \begin{bmatrix} \frac{2}{3} \cdot \cos(\omega \cdot t) & \begin{pmatrix} -\frac{1}{3} \cdot \cos(\omega \cdot t) & \dots \\ +\frac{1}{3} \cdot \sin(\omega \cdot t) \cdot \sqrt{3} \end{pmatrix} & -\begin{pmatrix} \frac{1}{3} \cdot \sin(\omega \cdot t) \cdot \sqrt{3} \\ +\frac{1}{3} \cdot \sin(\omega \cdot t) \cdot \sqrt{3} \end{pmatrix} \\ \frac{2}{3} \cdot \sin(\omega \cdot t) & -\begin{pmatrix} \frac{1}{3} \cdot \sin(\omega \cdot t) & \dots \\ +\frac{1}{3} \cdot \cos(\omega \cdot t) \cdot \sqrt{3} \end{pmatrix} & \begin{pmatrix} \frac{-1}{3} \cdot \sin(\omega \cdot t) & \dots \\ +\frac{1}{3} \cdot \cos(\omega \cdot t) \cdot \sqrt{3} \end{pmatrix} \end{bmatrix}$$

(21)

$$\frac{2}{3} \cdot \begin{pmatrix} \cos(\omega \cdot t) & -\sin(\omega \cdot t) \\ \sin(\omega \cdot t) & \cos(\omega \cdot t) \end{pmatrix} \cdot \begin{pmatrix} 1 & \frac{-1}{2} & \frac{-1}{2} \\ 0 & \frac{-\sqrt{3}}{2} & \frac{\sqrt{3}}{2} \end{pmatrix} = \frac{2}{3} \cdot \begin{pmatrix} \cos(\omega \cdot t) & \cos\left(\omega \cdot t - \frac{2\pi}{3}\right) & \cos\left(\omega \cdot t + \frac{2\pi}{3}\right) \\ \sin(\omega \cdot t) & \sin\left(\omega \cdot t - \frac{2\pi}{3}\right) & \sin\left(\omega \cdot t + \frac{2\pi}{3}\right) \end{pmatrix}$$

(22)

$$\begin{pmatrix} X_{qe} \\ X_{de} \end{pmatrix} = \frac{2}{3} \cdot \begin{pmatrix} \cos(\omega \cdot t) & \cos\left(\omega \cdot t - \frac{2\pi}{3}\right) & \cos\left(\omega \cdot t + \frac{2\pi}{3}\right) \\ \sin(\omega \cdot t) & \sin\left(\omega \cdot t - \frac{2\pi}{3}\right) & \sin\left(\omega \cdot t + \frac{2\pi}{3}\right) \end{pmatrix} \cdot \begin{pmatrix} X_a \\ X_b \\ X_c \end{pmatrix}$$

(23)

$$\frac{2}{3} \cdot \begin{pmatrix} \cos(\omega \cdot t) & \cos\left(\omega \cdot t - \frac{2\pi}{3}\right) & \cos\left(\omega \cdot t + \frac{2\pi}{3}\right) \\ \sin(\omega \cdot t) & \sin\left(\omega \cdot t - \frac{2\pi}{3}\right) & \sin\left(\omega \cdot t + \frac{2\pi}{3}\right) \end{pmatrix} \cdot \begin{bmatrix} x_{mp} \cdot \begin{pmatrix} \cos(\omega \cdot t + \alpha_p) \\ \cos\left(\omega \cdot t + \alpha_p - \frac{2\cdot\pi}{3}\right) \\ \cos\left(\omega \cdot t + \alpha_p + \frac{2\cdot\pi}{3}\right) \\ \cos\left(\omega \cdot t + \alpha_n + \frac{2\cdot\pi}{3}\right) \\ \cos\left(\omega \cdot t + \alpha_n - \frac{2\cdot\pi}{3}\right) \end{bmatrix} + x_{m0} \cdot \begin{bmatrix} \cos(\omega \cdot t + \alpha_0) \\ \cos(\omega \cdot t + \alpha_0) \\ \cos(\omega \cdot t + \alpha_0) \\ \cos(\omega \cdot t + \alpha_0) \end{bmatrix} \end{bmatrix}$$

(24)

$$\frac{2}{3} \cdot \begin{pmatrix} \cos(\omega \cdot t) & \cos\left(\omega \cdot t - \frac{2\pi}{3}\right) & \cos\left(\omega \cdot t + \frac{2\pi}{3}\right) \\ \sin(\omega \cdot t) & \sin\left(\omega \cdot t - \frac{2\pi}{3}\right) & \sin\left(\omega \cdot t + \frac{2\pi}{3}\right) \end{pmatrix} \cdot \begin{pmatrix} \cos(\omega \cdot t + \alpha_p) \\ \cos\left(\omega \cdot t + \alpha_p - \frac{2 \cdot \pi}{3}\right) \\ \cos\left(\omega \cdot t + \alpha_p + \frac{2 \cdot \pi}{3}\right) \end{pmatrix} = \begin{pmatrix} \cos(\alpha_p) \\ -\sin(\alpha_p) \end{pmatrix}$$

(25)

$$\frac{2}{3} \begin{pmatrix} \cos(\omega \cdot t) & \cos\left(\omega \cdot t - \frac{2\pi}{3}\right) & \cos\left(\omega \cdot t + \frac{2\pi}{3}\right) \\ \sin(\omega \cdot t) & \sin\left(\omega \cdot t - \frac{2\pi}{3}\right) & \sin\left(\omega \cdot t + \frac{2\pi}{3}\right) \end{pmatrix} \begin{pmatrix} \cos(\omega \cdot t + \alpha_n) \\ \cos\left(\omega \cdot t + \alpha_n + \frac{2\cdot\pi}{3}\right) \\ \cos\left(\omega \cdot t + \alpha_n - \frac{2\cdot\pi}{3}\right) \end{pmatrix} = \begin{pmatrix} \cos(2\omega \cdot t) & -\sin(2\omega \cdot t) \\ \sin(2\omega \cdot t) & \cos(2\omega \cdot t) \end{pmatrix} \begin{pmatrix} \cos(\alpha_n) \\ \sin(\alpha_n) \end{pmatrix}$$

(26)

Simplification of the expression yields (27)

$$\begin{pmatrix} X_{qe} \\ X_{de} \end{pmatrix} = \begin{bmatrix} X_{mp} \cdot \begin{pmatrix} \cos(\alpha_p) \\ -\sin(\alpha_p) \end{pmatrix} + X_{mn} \cdot \begin{pmatrix} \cos(2\omega \cdot t) & -\sin(2\omega \cdot t) \\ \sin(2\omega \cdot t) & \cos(2\omega \cdot t) \end{pmatrix} \cdot \begin{pmatrix} \cos(\alpha_n) \\ \sin(\alpha_n) \end{pmatrix} \end{bmatrix} = \begin{pmatrix} X_{qpe} \\ X_{dpe} \end{pmatrix} + R(2\omega \cdot t) \cdot \begin{pmatrix} X_{qne} \\ X_{dne} \end{pmatrix}$$

(27)

It can be seen from the equation (27) that the positive sequence is expressed as a DC component and the negative sequence as a second harmonic component where Ris the reference frame transformation matrix. The inverse notion of the above equation is shown as (28) and (29)

$$\begin{pmatrix} X_{a} \\ X_{b} \\ X_{c} \end{pmatrix} = T_{32}R(\omega t) \begin{pmatrix} X_{qpe} \\ X_{dpe} \end{pmatrix} + T_{32}R(-\omega t) \begin{pmatrix} X_{qne} \\ X_{dne} \end{pmatrix}$$

(28)

$$X_{abc} = T_{32} \cdot R(\omega \cdot t) \cdot X_{qdpe} + T_{32} \cdot R(-\omega \cdot t) \cdot X_{qdne}$$

<sup>(29)</sup>

In these cases, the current reference is distorted by a second harmonic voltage due to the presence of the negative sequence component. Hence, a more detailed control which takes into account this imbalance needs to be investigated.

#### **3.3 SEQUENCE CONTROLLERS SIMULATION AND SYSTEM IMBALANCE**

The first approach of solving imbalances in source voltages is to use two different reference frames for the positive and the negative sequence components [7-11]. This would decouple the control in the respective sequence frames. A dual control scheme similar to that reported in ref [10] is simulated. Here, the positive sequence is simulated in the positive SRF and the negative sequence is simulated in the negative SRF. A low pass filter or second order notch filter of 120 Hz frequency need to be used to separate the components from the real values. As the imbalance is seen as a 120Hz wave, it is eliminated using the notch filter. As a choice, a low pass filter is excluded due to instability issues with the simulation [10].

The d-q controllers in the positive and negative sequence are commanded based on the real and reactive power equations as shown in (30-32). Equation (30) gives the real power of the system during the presence of both positive and negative sequence components. Equation (31) gives the short form of (30) where the constant terms are the coefficients of average, sine and cosine terms as represented by the subscripts.

$$E \cdot i_{os} = \frac{3}{2} \cdot \left( V_{qpe} \cdot i_{qpe} + V_{dpe} \cdot i_{dpe} + V_{qne} \cdot i_{qne} + V_{dne} \cdot i_{dne} \right) \dots + \frac{3}{2} \cdot \cos(2 \cdot \omega \cdot t) \cdot \left( V_{qne} \cdot i_{qpe} + V_{dne} \cdot i_{dpe} + V_{qpe} \cdot i_{qne} + V_{dpe} \cdot i_{dne} \right) \dots + \frac{3}{2} \cdot \sin(2 \cdot \omega \cdot t) \cdot \left( -V_{dne} \cdot i_{qpe} + V_{qne} \cdot i_{dpe} + V_{dpe} \cdot i_{qne} + V_{qde} \cdot i_{dne} \right)$$

(30)

$$P = E \cdot i_{os} = P_0 + P_{c2} \cdot \cos(2 \cdot \omega \cdot t) + P_{s2} \cdot \sin(2 \cdot \omega \cdot t)$$

(31)

$$Q = Q_0 + Q_{c2} \cdot \cos(2 \cdot \omega \cdot t) + Q_{s2} \cdot \sin(2 \cdot \omega \cdot t)$$

(32)

The DC controller commands the DC link voltage to a constant value thus producing the command for average DC voltage. The q and d controllers in the positive

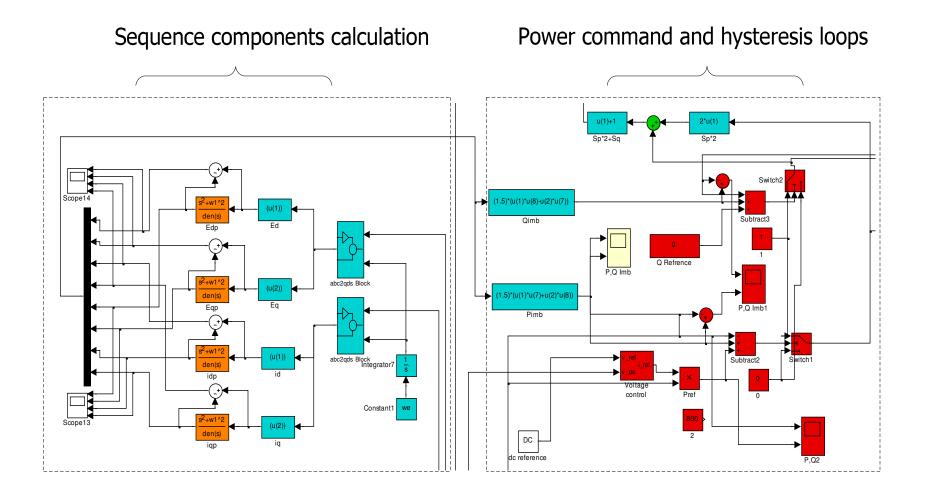

and negative sequence domain control the average real power component, average reactive power component, real power cosine component and real power sine component coefficients to zero [12],[32]. In general the negative sequence current controllers can be commanded to zero [9], [34] but this does not achieve the desired reactive power output. The simulation is done in Matlab Simulink<sup>®</sup> using the PLECS<sup>®</sup> block set. The block diagram is show in Figure 3.3. The circuit diagram is the same as shown earlier in Figure 2.4.

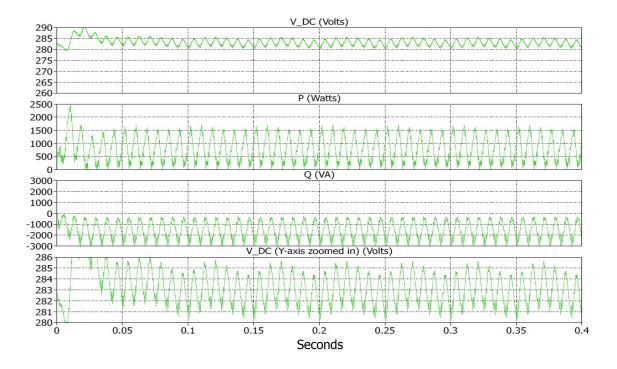

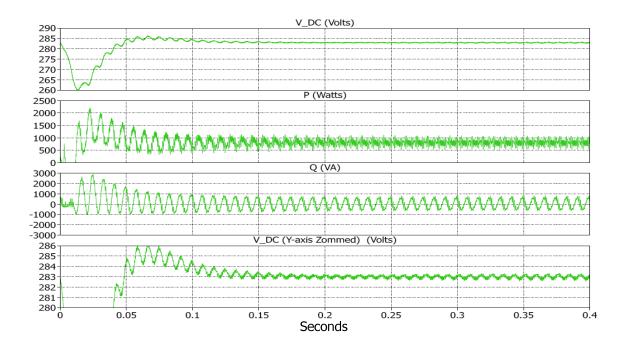

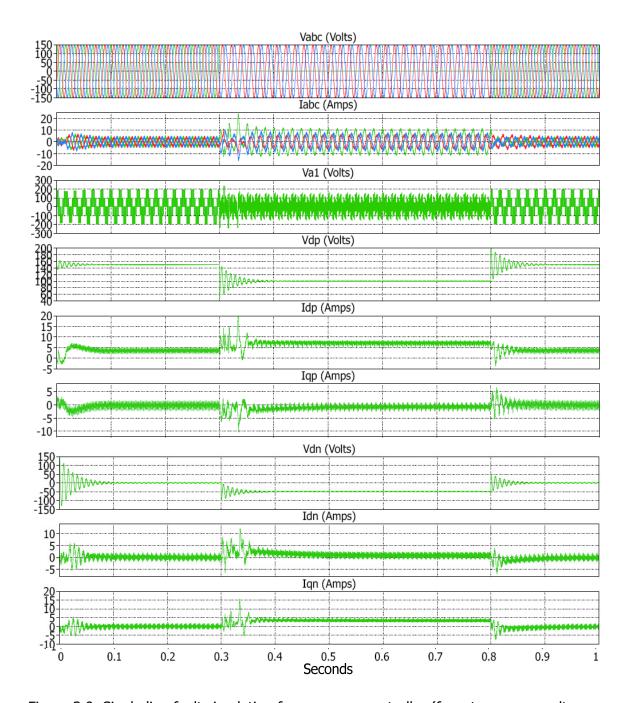

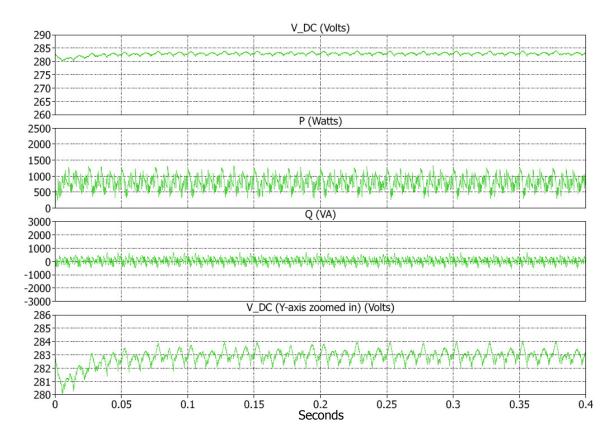

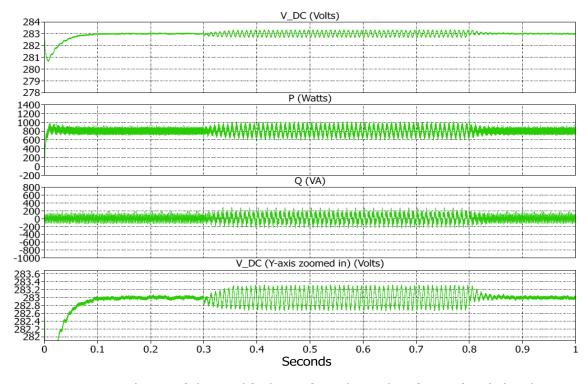

The behavior of the DC link voltage is observed by applying unbalanced voltages to the VSC with conventional control and with the sequence controllers separately. These results are compared with simulation results obtained by the conventional current control technique. It is observed from Figure 3.4 and Figure 3.5 that in steady state the oscillations in the DC link voltage and thus in real and reactive power are less than that obtained by the conventional control. However, the sequence controller takes a longer time to achieve steady state compared to the conventional controller.

Negative sequence controller

Figure. 3.3. Block diagram of the VSC controller using sequence controllers

Figure 3.4. Voltage imbalance simulation for conventional controller (from top DC link voltage, real power, reactive power and DC link voltage Y-axis zoomed)

Figure 3.5. Voltage imbalance simulation for sequence controllers (from top DC link voltage, real power, reactive power and DC link voltage Y-axis zoomed)

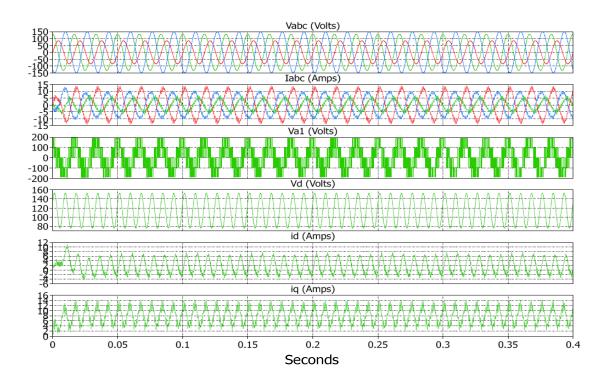

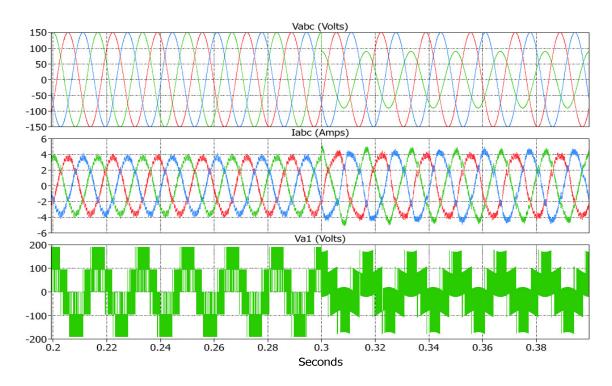

Figure 3.6 and Figure 3.7 compare the dq components of the sequence controller and the conventional controller respectively. In the conventional controller, the d axis voltage is proportional to DC link voltage and is supposed to be a straight line for normal operation. During voltage imbalance, the dc link voltage exhibits double frequency oscillations. In the sequence controller positive d-axis voltage and negative d-axis voltage are approximately straight lines with oscillation of much smaller magnitude. The currents of the sequence controller are smooth compared to the conventional control. The q-axis currents of the conventional controller have an average value. In the general case the q-axis currents should have an average value of zero. This is achieved by the sequence controllers.

Figure 3.6. Voltage imbalance simulation for conventional controller (from top source voltages, source currents, converter voltage, d-axis voltage, d-axis current and q-axis current)

Figure 3.7. Voltage imbalance simulation for sequence controller (from top source voltages, source currents, converter voltage, positive sequence d-axis voltage, positive sequence d-axis current, negative sequence d-axis voltage, negative sequence d-axis current, negative sequence q-axis current)

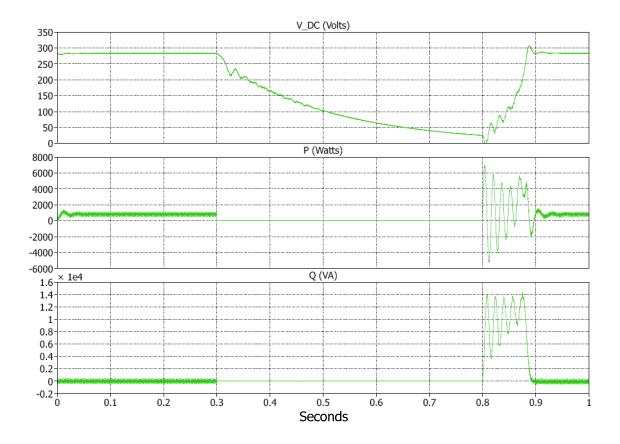

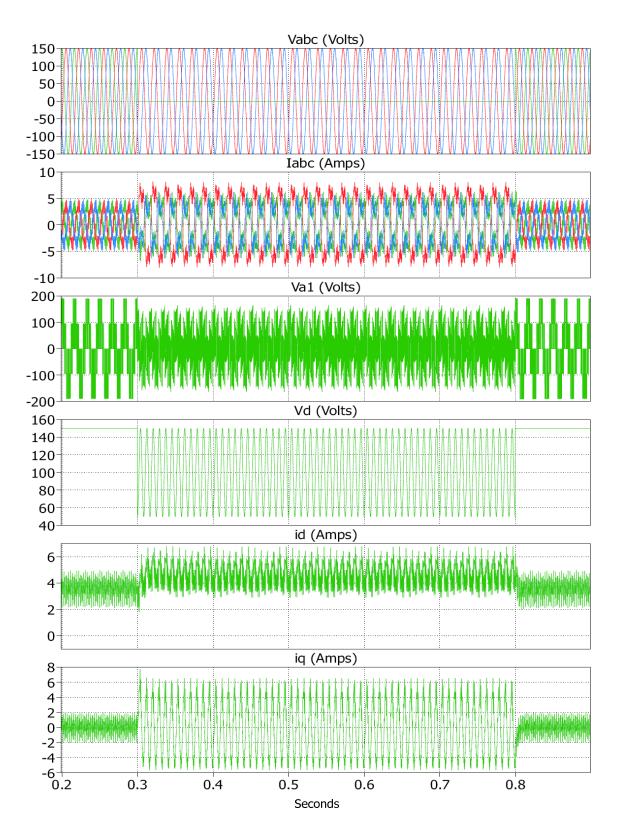

The sequence controllers are tested for a sudden change in the grid condition using a single line to ground (SLG) fault on one of the phases as shown in Figure 3.8 and Figure 3.9. The simulations are run for one second. The fault is applied at 0.3 seconds and removed at 0.8 seconds. The DC link voltage and thus P and Q have lesser oscillations than the conventional controller. It can be observed that the system with sequence controllers have high peak overshoot and their response is more sluggish than with conventional controller. The sluggish response of this control is due to the larger number of PI control loops (five compared to three in conventional control). Hence reducing the number of control loops would make the system respond faster.

Figure 3.8. Single line fault simulation for sequence controllers (DC link voltage, real power, reactive power and DC link voltage Y-axis zoomed)

Figure 3.9. Single line fault simulation for sequence controller (from top source voltages, source currents, converter voltage, positive sequence d-axis voltage, positive sequence d-axis current, negative sequence d-axis voltage, negative sequence d-axis current, negative sequence q-axis current)

Sequence controllers were also used on the rotor side converter of the DFIG by Lie et al. [13]. For rotor side converter analysis a rotor current control strategy based on positive and negative (dq) reference frames was used to provide precise control of the rotor positive and negative sequence currents. Sequence controllers for rotor side uses two PI controllers as well as band trap filters to separate the positive and negative sequence components, increasing the complexity of implementation. It was found that the overall converter ratings of the rotor side converter needed to be increased.

## 3.4 SUMMARY

Sequence control of the VSC acts as a good choice for a prolonged disturbance in the power system as in the case of a weak grid. It achieves stable voltages and currents even in the presence of a disturbance. This technique employs two different PI loops in both positive synchronous and negative synchronous reference frames (one PI loop in the d-axis and the other PI loop in the q-axis). The separation of voltage and currents in these frames is done using two notch filters in each reference frame. There are a total of five PI controllers including the dc link voltage and four notch filters which should be fine-tuned according to the system parameters, thus increasing the complexity of the system implementation. A larger number of controllers makes the system sluggish when compared to the performance of a conventional controller. Hence a fast acting control technique which uses fewer control loops, such as the direct power control technique, is employed for further analysis. This technique is discussed in detail in the next section.

## 4. DIRECT POWER CONTROL FOR DFIG-BASED WIND TURBINES

### **4.1 INTRODUCTION**

A fast acting controller that gets rid of the conventional current control and acts directly upon the real and reactive power of the system is proposed by [14]. As this control acts directly according to the error in the real and reactive powers, this control is called Direct Power Control (DPC). In this control, the power required for the converters are commanded using the instantaneous voltages and currents whether they are balanced or not. The Sequence controller uses more complicated control and is more sluggish than the conventional current control approach. In the present section, DPC is adapted from motor drive applications to grid-side control of a DFIG and integrated with a DPC-based rotor-side converter to achieve fast response. Also, a modified DPC algorithm is derived to reduce current harmonics that occur in the grid-side converter during disturbances.

Figure 4.1 shows the single line diagram of the PWM converter shown earlier in Figure 2.2.  $v_{abc}$  represents the source or the line voltage and  $v_{a1b1c1}$  represents the voltage of the converter that can be controlled by the DC link. The voltage of the converter depends upon the switching sequence of the converter and the magnitude of the DC voltage. The series inductance of the line and the dc bus capacitance provides boost characteristics for the converter from the AC to the DC side. The flow of current from the source to the load is governed by the difference between the source voltage and the converter voltage. The line inductance provides stiff current characteristics to the source whereas the bus capacitance provides stiff voltage characteristics to the dc link. Typically the source voltage is assumed to be constant although this may not be

48

true in case of system imbalance. Hence the flow of the current in the circuit is governed by the magnitude and angle of the converter voltage.

Figure 4.1. Single line diagram of the PWM converter

# 4.2 DPC SWITCHING STATES AND DELTA MODULATION

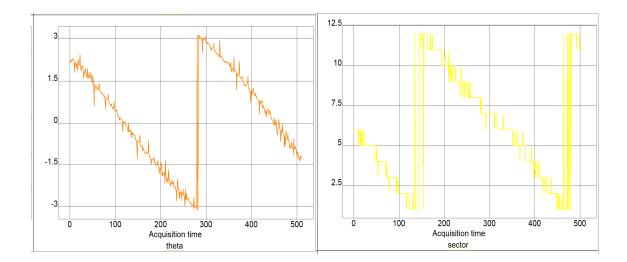

The switching states of a voltage source inverter are based on the space vector modulation approach presented in [35] and discussed in detail in [36]. In this approach, the converter voltages are referred to as space vectors in an  $\alpha$ - $\beta$  reference frame (stationary reference frame). There are eight possible states for these vectors depending on the converter switching possibilities as shown in Figure 4.2. The eight possible vectors are represented on an  $\alpha$ - $\beta$  reference frame as shown in Figure 4.3. Two of the eight cases are zero vectors and hence represented near the origin. An average vector is defined during a switching period. The average vector is assumed to be constant during the switching period and it defines the fundamental nature of the angle and phase of the three converter voltages. A high rate of switching frequency of the vectors is generally necessary to obtain the desired power transfer mechanism; hence the area between the vectors is broadly divided into twelve sectors.

Figure 4.2. PWM Converter switching states

Figure 4.3. Voltage vector plane divided into 12 sectors

The magnitude and angle of the voltage vector can either be increased or decreased by applying appropriate vectors in the  $\alpha$ - $\beta$  plane. Consider for example that the average value of the converter voltage vector falls in sector 2 in a given time period. The magnitude of the vector in this sector can be increased by applying vectors U<sub>6</sub>, U<sub>2</sub> and U<sub>1</sub> and can be decreased by applying vectors U<sub>3</sub>, U<sub>4</sub> and U<sub>5</sub>. Similarly the angle of the voltage can be changed by either advancing the vector in clockwise direction by applying U<sub>1</sub>, U<sub>6</sub> and U<sub>5</sub> or in anticlockwise direction by applying U<sub>2</sub>, U<sub>3</sub> and U<sub>4</sub>. Zero vectors U<sub>0</sub> and U<sub>7</sub> neither change the magnitude nor angle but hold the vector at the same position in real time. Hence an appropriate selection of the vector in a given sector is necessary to change the magnitude and angle of the converter voltage.

The instantaneous real and reactive power, under the assumption of negligible series resistance, flowing between the source or line bus and the converter bus in Figure 4.3, is given in (33) and (34).

$$p = \frac{|v| * |v_1|}{X_L} \sin(\delta)$$

(33)

$$q = \frac{|v_1|}{X_L} (|v| * \cos(\delta) - |v_1|)$$

(34)

$\delta$  is the angle between the line and the converter voltages. As the line voltage is predetermined, the power flow can be varied using the converter voltage. From (33) it is observed that the real power can be increased or decreased either by increasing or decreasing  $\delta$  or the magnitude of the converter voltage. It is important to consider that the effect of change in the angle would be significantly more than the change in the magnitude as the former is a sinusoidal function whereas the latter is just a linear function. Hence appropriate application of zero vectors also change the angle  $\delta$ . The

reactive power is predominantly determined by the magnitude of the converter voltage as it is proportional to the square of the magnitude.

An optimal switching table based on the above analysis as employed by [14] and [15] is used for the instantaneous control of real and reactive power. The switching vectors for different sectors are shown in Table 4.1. While applying the zero vector a choice between  $U_0$  (000) or  $U_7$  (111) depends on the converter legs switching during change of states.

| P / Q     | ↑/↓                  | ↑/↑                  | $\downarrow / \downarrow$ | $\downarrow$ / $\uparrow$ |

|-----------|----------------------|----------------------|---------------------------|---------------------------|

| Sector 1  | U <sub>6</sub> (101) | U <sub>7</sub> (111) | U <sub>6</sub> (101)      | U <sub>1</sub> (100)      |

| Sector 2  | U <sub>7</sub> (111) | U <sub>7</sub> (111) | U <sub>1</sub> (100)      | U <sub>2</sub> (110)      |

| Sector 3  | U <sub>1</sub> (100) | U <sub>0</sub> (000) | U <sub>1</sub> (100)      | U <sub>2</sub> (110)      |

| Sector 4  | U <sub>0</sub> (000) | U <sub>0</sub> (000) | U <sub>2</sub> (110)      | U <sub>3</sub> (010)      |

| Sector 5  | U <sub>2</sub> (110) | U <sub>7</sub> (111) | U <sub>2</sub> (110)      | U <sub>3</sub> (010)      |

| Sector 6  | U <sub>7</sub> (111) | U <sub>7</sub> (111) | U <sub>3</sub> (010)      | U <sub>4</sub> (011)      |

| Sector 7  | U <sub>3</sub> (010) | U <sub>0</sub> (000) | U <sub>3</sub> (010)      | U <sub>4</sub> (011)      |

| Sector 8  | U <sub>0</sub> (000) | U <sub>0</sub> (000) | U4 (011)                  | U <sub>5</sub> (001)      |

| Sector 9  | U4 (011)             | U <sub>7</sub> (111) | U4 (011)                  | U <sub>5</sub> (001)      |

| Sector 10 | U <sub>7</sub> (111) | U <sub>7</sub> (111) | U <sub>5</sub> (001)      | U <sub>6</sub> (101)      |

| Sector 11 | U <sub>5</sub> (001) | U <sub>0</sub> (000) | U <sub>5</sub> (001)      | U <sub>6</sub> (101)      |

| Sector 12 | U <sub>0</sub> (000) | U <sub>0</sub> (000) | U <sub>6</sub> (101)      | U <sub>1</sub> (100)      |

Table 4.1. Optimal switching table for voltage source converter ( $\uparrow$  increase,  $\downarrow$  decrease)

Alternative to (33) and (34) the three phase instantaneous real and reactive power is estimated by the scalar and vector product of the instantaneous voltages and currents as in (35) and (36), respectively.

$$p = \left(v_a i_a + v_b i_b + v_c i_c\right) \tag{35}$$

$$q = \frac{1}{\sqrt{3}} \{ i_a (v_b - v_c) + i_b (v_c - v_a) + i_c (v_a - v_b) \}$$

(36)

The commanded real and reactive powers are compared with the estimated power as in (35) and (36). The difference or error is digitized using a delta modulation as follows:

For reactive power:

$$d_q = 1$$

for  $q < q_{ref}$   $d_q = 0$  for  $q > q_{ref}$

Similarly for active power:  $d_p = 1$  for  $p < p_{ref}$   $d_p = 0$  for  $p > p_{ref}$