# Scholars' Mine

**Doctoral Dissertations**

Student Theses and Dissertations

Fall 2012

# Null Convention Logic applications of asynchronous design in nanotechnology and cryptographic security

Jun Wu

Follow this and additional works at: https://scholarsmine.mst.edu/doctoral\_dissertations

Part of the Computer Engineering Commons

**Department: Electrical and Computer Engineering**

#### **Recommended Citation**

Wu, Jun, "Null Convention Logic applications of asynchronous design in nanotechnology and cryptographic security" (2012). Doctoral Dissertations. 1971. https://scholarsmine.mst.edu/doctoral\_dissertations/1971

This thesis is brought to you by Scholars' Mine, a service of the Missouri S&T Library and Learning Resources. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

# NULL CONVENTION LOGIC APPLICATIONS OF ASYNCHRONOUS DESIGN IN NANOTECHNOLOGY AND CRYPTOGRAPHIC SECURITY

by

#### JUN WU

#### A DISSERTATION

Presented to the Faculty of the Graduate School of the

#### MISSOURI UNIVERSITY OF SCIENCE AND TECHNOLOGY

In Partial Fulfillment of the Requirements for the Degree

DOCTOR OF PHILOSOPHY

in

COMPUTER ENGINEERING

2012

Approved

Dr. Minsu Choi, Advisor

Dr. Daryl G. Beetner

Dr. Sahra Sedighsarvestani

Dr. Yiyu Shi

Dr. Dan Lin

#### ABSTRACT

This dissertation presents two Null Convention Logic (NCL) applications of asynchronous logic circuit design in nanotechnology and cryptographic security. The first application is the Asynchronous Nanowire Reconfigurable Crossbar Architecture (ANRCA); the second one is an asynchronous S-Box design for cryptographic system against Side-Channel Attacks (SCA).

The following are the contributions of the first application:

- 1) Proposed a diode- and resistor- based ANRCA (DR-ANRCA). Three configurable logic block (CLB) structures were designed to efficiently reconfigure a given DR-PGMB as one of the 27 arbitrary NCL threshold gates. A hierarchical architecture was also proposed to implement the higher level logic that requires a large number of DR-PGMBs, such as multiple-bit NCL registers.

- 2) Proposed a memristor look-up-table based ANRCA (MLUT-ANRCA). An equivalent circuit simulation model has been presented in VHDL and simulated in Quartus II. Meanwhile, the comparison between these two ANRCAs have been analyzed numerically.

- 3) Presented the defect-tolerance and repair strategies for both DR-ANRCA and MLUT-ANRCA.

The following are the contributions of the second application:

- 1) Designed an NCL based S-Box for Advanced Encryption Standard (AES). Functional verification has been done using Modelsim and Field-Programmable Gate Array (FPGA).

- 2) Implemented two different power analysis attacks on both NCL S-Box and conventional synchronous S-Box.

- 3) Developed a novel approach based on stochastic logics to enhance the resistance against DPA and CPA attacks. The functionality of the proposed design has been verified using an 8-bit AES S-box design. The effects of decision weight, bitstream length, and input repetition times on error rates have been also studied. Experimental results shows that the proposed approach enhances the resistance to against the CPA attack by successfully protecting the hidden key.

#### ACKNOWLEDGMENT

I would like to thank Dr. Minsu Choi, my advisor and the chairman of my doctoral committee. The present work would not have been completed without his great advice and insightful guidance. It has been a pleasure working in his research group.

I would like to express my sincere gratitude to the remainder of my doctoral committee. Dr. Yiyu Shi and Dr. Daryl G. Beetner provided useful integrated circuit design background for the present work. Dr. Sahra Sedighsarvestani and Dr. Dan Lin has taken time to review this work and has provided useful outside perspectives.

Most of my doctoral research was supported in part by the National Science Foundation under Award Number ECCS-0801362.

Finally, I would like to thank my parents, Zhuanfang Wu and Huimin Su for their continuous encouragement and support. I thank my husband, Hengsi, for his great love.

## TABLE OF CONTENTS

| ABSTRACT                                        | iii |

|-------------------------------------------------|-----|

| ACKNOWLEDGMENT                                  | iv  |

| LIST OF ILLUSTRATIONS                           | vii |

| LIST OF TABLES                                  | ix  |

| SECTION                                         |     |

| 1. INTRODUCTION                                 | 1   |

| 1.1. OVERVIEW OF NCL                            | 2   |

| 1.2. ADVANTAGES OF USING NCL                    | 5   |

| 1.3. WORKS SUMMARY                              | 7   |

| 2. PROJECT I: ANRCA                             | 9   |

| 2.1. BACKGROUND                                 | 9   |

| 2.2. ADVANTAGES OF ANRCA                        | 11  |

| 2.3. DIODE- AND RESISTOR-BASED ANRCA (DR-ANRCA) | 12  |

| 2.4. NUMERICAL ANALYSIS OF DR-ANRCA             | 15  |

| 2.4.1. Area                                     | 15  |

| 2.4.2. Programming Steps                        | 17  |

| 2.4.3. Latency                                  | 18  |

| 2.5. DEFECT/FAULT ISSUES OF DR-ANRCA            | 20  |

| 2.6. MEMRISTOR LOOK-UP-TABLE BASED ANRCA        | 23  |

| 2.7. DEFECT/FAULT ISSUES OF DR-MLUT             | 26  |

| 2.8. COMPARISON BETWEEN DR-ANRCA AND MLUT-ANRCA | 28  |

| 2.9. CONCLUSIONS                                | 31  |

| 3. PROJECT II: NCL S-BOX DESIGN                 | 32  |

| 3.1. BACKGROUND                                 | 32  |

| 3.2. EXISTING COUNTERMEASURES                   | 33  |

| 3.3. NCL AES S-BOX DESIGN                       | 35  |

| 3.4. FUNCTIONAL VERIFICATION                    | 38  |

| 3.5. POWER MEASUREMENT EXPERIMENT               | 41  |

| 3.6. DIFFERENTIAL POWER ANALYSIS                | 42  |

| 3.7. CORRELATION POWER ANALYSIS                 | 45  |

| 3.8. NUMBER OF TRACES                           | 51  |

| 3.9. CONCLUSIONS                                            | 54 |

|-------------------------------------------------------------|----|

| 4. PROJECT III: STOCHASTIC BITSTREAMS COMPUTATION           | 55 |

| 4.1. BACKGROUND                                             | 55 |

| 4.2. STOCHASTIC CRYPTOGRAPHIC DEVICES                       | 57 |

| 4.2.1. MATLAB Simulink Structure                            | 57 |

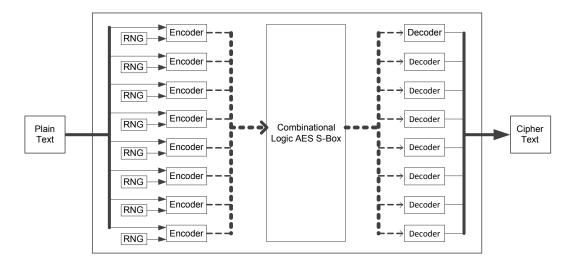

| 4.2.2. Hardware Implementation of Bitstream Based AES S-Box | 60 |

| 4.3. LOGIC VALIDATION                                       | 63 |

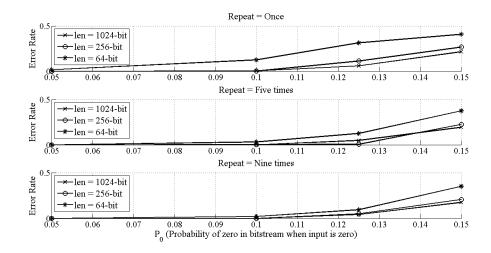

| 4.4. CPA RESULTS                                            | 64 |

| 4.5. CONCLUSIONS                                            | 66 |

| 5. SUMMARY AND CONCLUSIONS                                  | 68 |

| 5.1. SUMMARY OF CONTRIBUTIONS                               | 68 |

| 5.2. FUTURE WORK                                            | 69 |

| BIBLIOGRAPHY                                                | 71 |

| VITA                                                        | 80 |

# LIST OF ILLUSTRATIONS

| Figur | P P                                                                                     | age |

|-------|-----------------------------------------------------------------------------------------|-----|

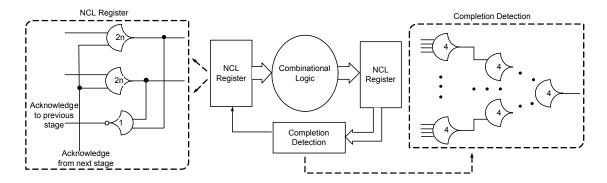

| 1.1   | Block diagram of NCL combinational logic with two DI registers                          | 4   |

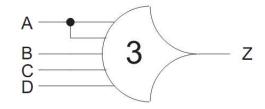

| 1.2   | Threshold gate TH34w2                                                                   | 4   |

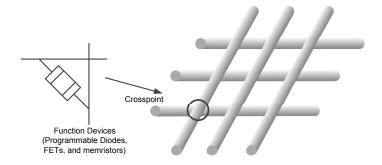

| 2.1   | Typical nanowire crossbar structure                                                     | 10  |

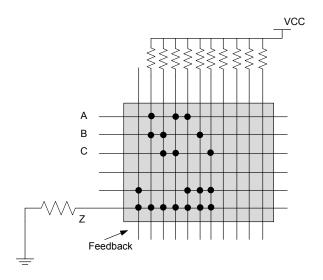

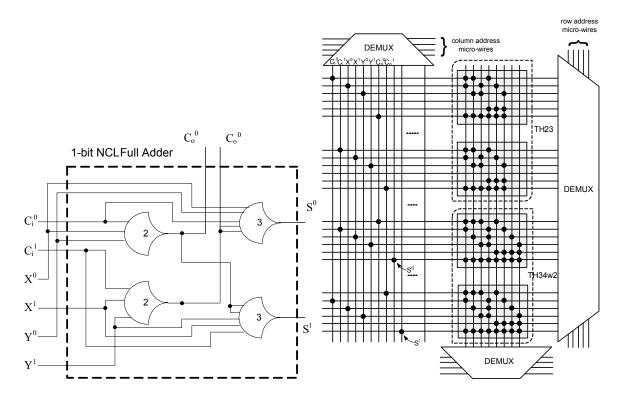

| 2.2   | TH23 gate realized on a programmable gate macro block                                   | 13  |

| 2.3   | NCL full adder implemented in CMOS (left) and CLB-1 (right)                             | 14  |

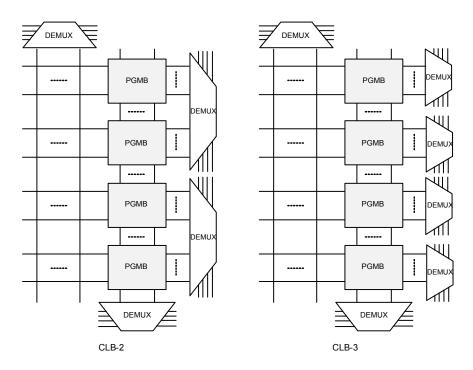

| 2.4   | The second and third variations of (CLB-2 and CLB-3)                                    | 15  |

| 2.5   | 1-bit NCL register implemented in one CLB                                               | 16  |

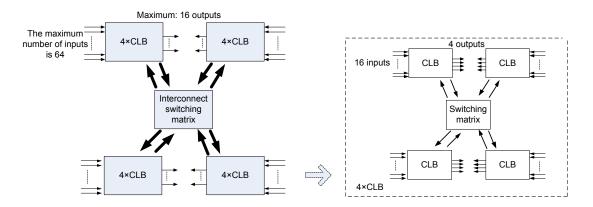

| 2.6   | Two-level hierarchical architecture for the proposed ANRCA                              | 16  |

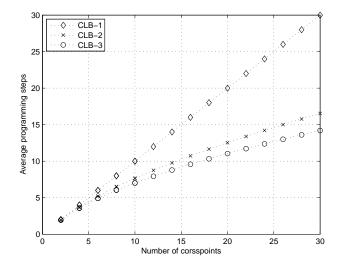

| 2.7   | Curve fitting results of programming steps for various CLBs                             | 18  |

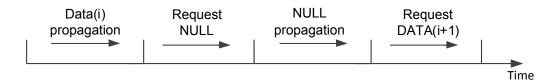

| 2.8   | A single NCL cycle of DATA-to-DATA latency                                              | 19  |

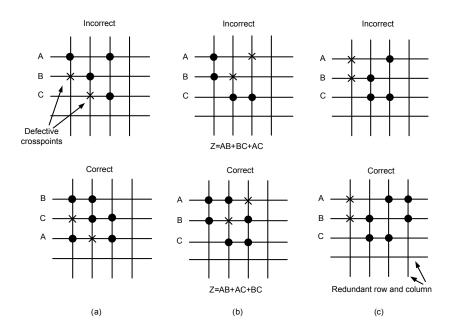

| 2.9   | Demonstration of defect tolerance methods                                               | 21  |

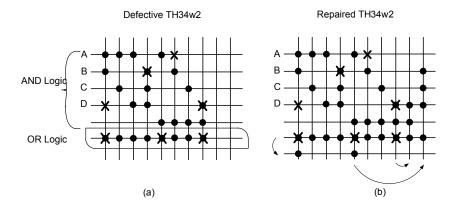

| 2.10  | A case study of successfully realized on a defective DR-PGMB of TH34w2 gate.            | 23  |

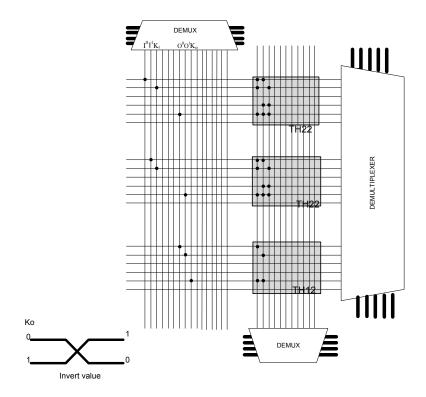

| 2.11  | TH23 gate realized on a MLUT-PGMB                                                       | 25  |

| 2.12  | Waveform of TH23 gate.                                                                  | 26  |

| 2.13  | A defective MLUT-PGMB and a version repaired using the redundancy method.               | 27  |

| 2.14  | Percentage of crosspoints that are programmed to 1 for each TH gate                     | 28  |

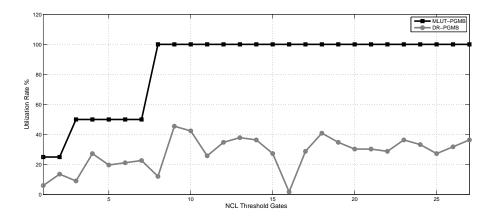

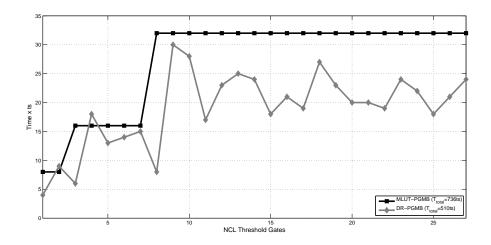

| 2.15  | Crosspoints utilization comparison.                                                     | 30  |

| 2.16  | Programming time comparison.                                                            | 30  |

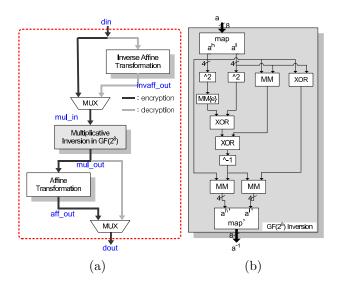

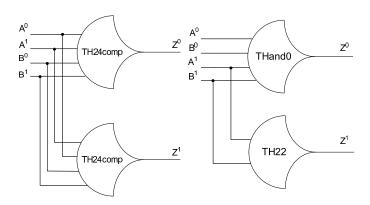

| 3.1   | Block diagram of a combinational S-Box with encryption and decryption datapaths         | 36  |

| 3.2   | An input-complete NCL multiplexer design                                                | 38  |

| 3.3   | Input-complete NCL XOR (left) and NCL AND (right) functions for the proposed NCL S-Box. | 38  |

| 3.4  | ModelSim waveform for the proposed NCL S-Box with input signals changing from 0d to 3d                     |    |  |  |

|------|------------------------------------------------------------------------------------------------------------|----|--|--|

| 3.5  | Power waveform of NCL S-Box design.                                                                        | 41 |  |  |

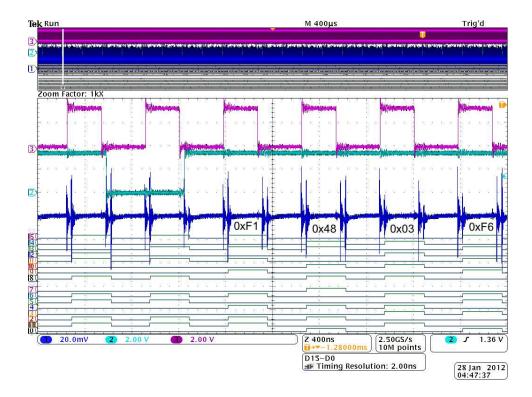

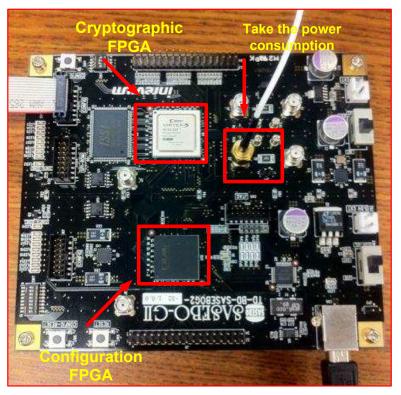

| 3.6  | Specified side channel attack standard evaluation FPGA board (SASEBO-GII)                                  | 43 |  |  |

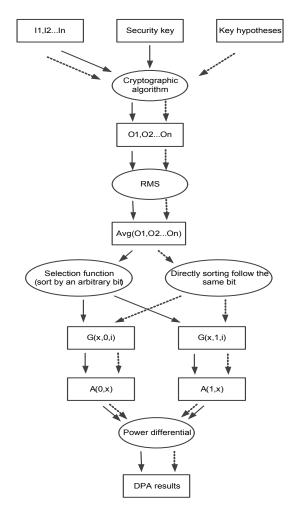

| 3.7  | Block diagram illustrating the DPA attack steps                                                            | 44 |  |  |

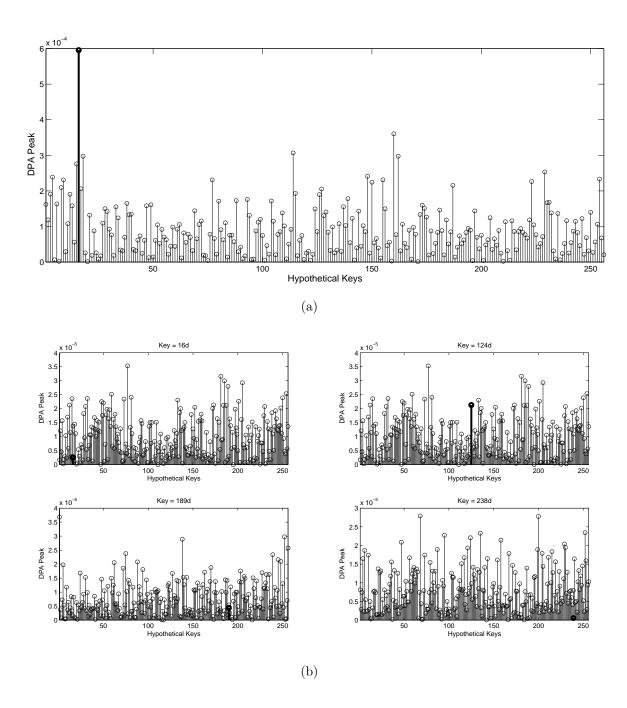

| 3.8  | Power peaks for various key assumptions for a DPA attack on synchronous S-Box design and NCL S-Box design. | 46 |  |  |

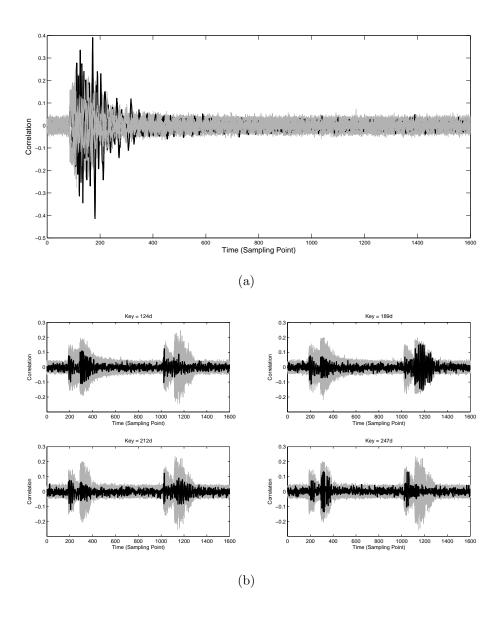

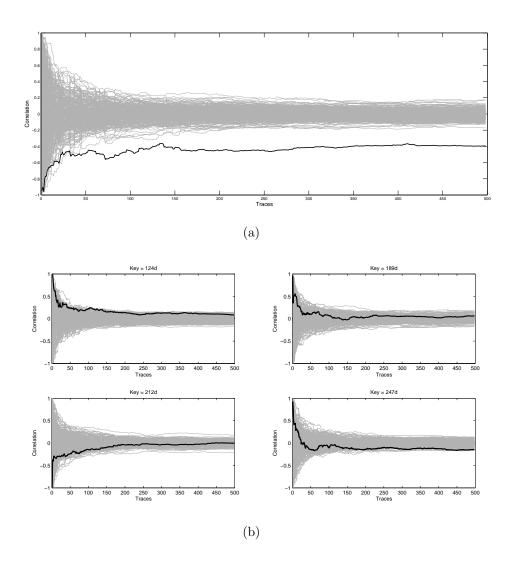

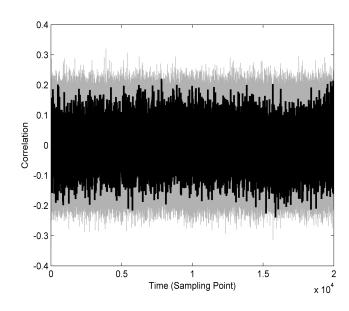

| 3.9  | CPA result for synchronous S-Box design and NCL S-Box design                                               | 52 |  |  |

| 3.10 | The number of traces needed for a successful CPA attack                                                    | 53 |  |  |

| 4.1  | A stochastic bitstream with value 3/8                                                                      | 55 |  |  |

| 4.2  | An AND gate to implement multiplication                                                                    | 56 |  |  |

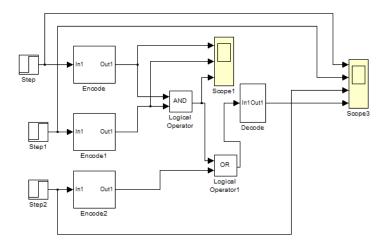

| 4.3  | Stochastic implementation of a combinational logic in simulink                                             | 58 |  |  |

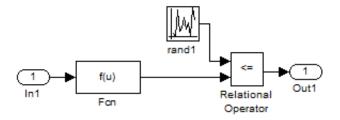

| 4.4  | Encoder block                                                                                              | 58 |  |  |

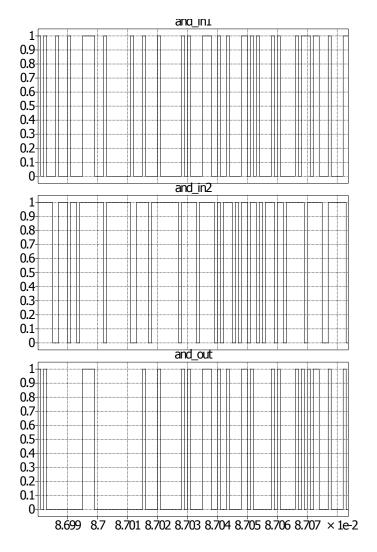

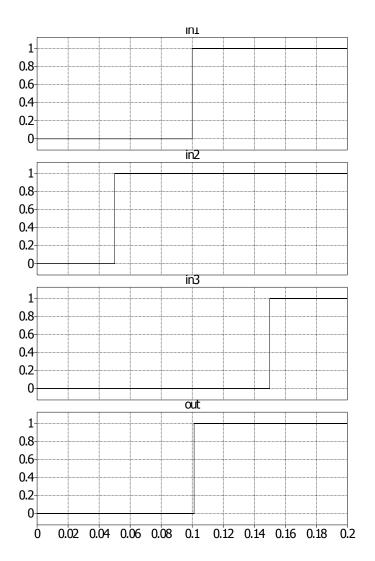

| 4.5  | Generated bitstreams waveform of AND function                                                              | 59 |  |  |

| 4.6  | Decoder block.                                                                                             | 60 |  |  |

| 4.7  | Final output waveform.                                                                                     | 61 |  |  |

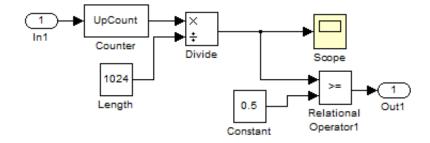

| 4.8  | System diagram                                                                                             | 62 |  |  |

| 4.9  | Error rate of stochastic bitstream S-box                                                                   | 64 |  |  |

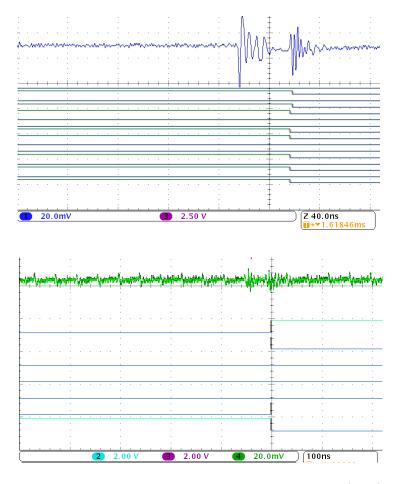

| 4.10 | Power traces comparison between regular S-box (Top) and stochastic S-box (Bottom) design.                  | 65 |  |  |

| 4.11 | CPA results of stochastic bitstream S-box                                                                  | 66 |  |  |

## LIST OF TABLES

| Table |                                                                                                            | Page |

|-------|------------------------------------------------------------------------------------------------------------|------|

| 1.1   | Truth table of NCL TH23 gate                                                                               | 5    |

| 1.2   | Twenty-seven NCL TH gates                                                                                  | 6    |

| 2.1   | Test Tuples for TH34w2 gate                                                                                | 24   |

| 3.1   | Boolean equations for affine transformation and inverse affine transformation components                   |      |

| 3.2   | Simulation results for 10 arbitrary samples from conventional synchronous S-Box and the proposed NCL S-Box |      |

| 3.3   | Power simulation results for synchronous AES S-Box and NCL AES S-Box using Accusim and AdvanceMS.          |      |

#### 1. INTRODUCTION

Synchronous logic with clocked structures has dominated the digital design over the past decades. As the decrease of feature sizes and the increase of the operating frequency of integrated circuits (IC), clock-related issues become more serious, such as clock skews, increased power at the clock edges, extra area, and layout complexity for clock distribution networks, and glitches. These motivate the research of asynchronous (i.e., clockless) logic design which has benefits of eliminating all the clock-related issues listed above.

Null Convention Logic (NCL) is a delay-insensitive (DI) logic that belongs to the category of asynchronous logic. NCL was first proposed by Karl Fant and Scott Brandt in 1994 [1, 2, 3], and further developed by Dr. Scott Smith's research group [4]. NCL initially aimed at designing Application Specific Integrated Circuit (ASIC) and Very-large-scale Integration (VLSI) circuits with lower power, lower noise, and lower electromagnetic interference (EMI). Various NCL based circuits have shown these characteristics. An NCL based Motorola STAR08 processor [5] shows the power and noise reduction up to 40% and 10dB, respectively, comparing to its synchronous counterpart. In [6], an 8-operation NCL ALUs was designed as a benchmark. The simulation result shows that the dual-rail NCL circuit consumes less power but requires a larger area compared with the conventional Boolean logic version. Other designs like NCL divider [7] and NCL multiply-and-accumulate unit [8] have shown the benefits of speed improvement and reduction in power consumption, noise, and EMI.

Designing an NCL circuit is less complex than designing the traditional asynchronous circuit due to the absence of global clock and the property of DI, which does not need worse-case delay analysis and extensive delay matching to synchronize the datapath and control-path without a clock signal. The current research of NCL mainly focuses on the formal design and optimization of NCL, such as the FPGA implementations of NCL[9], Design For Test (DFT) techniques for NCL [10], speed increase of NCL using cycle reduction techniques [11], and timing/gate optimization

methods [12]. However, there is few study at the application level of NCL. And its advantages are not fully investigated.

This dissertation proposes and demonstrates two NCL applications to explore some other benefits of NCL. The first application is the Asynchronous Nanowire Reconfigurable Crossbar Architecture (ANRCA). Potential benefits from ANRCA include enhanced manufacturability, scalability, modularity, and robustness. The second NCL application is an asynchronous S-Box design for cryptographic system to resist side-channel attacks (SCA). This design demonstrates that NCL has the advantage of securing cryptographic devices against various power analysis attacks, including Simple Power Analysis (SPA), Differential Power Analysis (DPA), and Correlation Power Analysis (CPA). In order to enhance security, scholastic bit streams based logics were proposed. The stochastic bit streams method has good scalability and it can be applied to many other devices when they require enhanced security.

#### 1.1. OVERVIEW OF NCL

NCL uses dual-rail or quad-rail signaling methods to achieve the DI [4]. A pair of dual-rail signals  $A^0$  and  $A^1$  could be either 10 (i.e., DATA0), 01 (i.e., DATA1), or 00 (i.e., NULL); as 11 is considered invalid. Same for the quad-rail signaling method but it uses four rails instead of two. The possible sets for quad-rail signaling method would be DATA0 (1000), DATA1 (0100), DATA2 (0010), DATA3 (0001), and NULL (0000). NCL uses two states, DATA (i.e., data representation) and NULL (i.e., control representation) to synchronize itself and control the input and output, eliminating the need of a reference clock signal. To mark the transition between the NULL and DATA states, each NCL combination logic must be bracketed by input and output DI registers, these registers have an input/output acknowledgment signal that alternates between 0s and 1s to provide request-for-NULL (i.e., RFN) and request-for-DATA (i.e., RFD), respectively. An example is shown in Figure 1.1. These signals are used to initiate a delay insensitive handshaking protocol that handles timing locally. The four-phase handshaking protocol includes: 1) The proper conditions are met to provide DATA at the output of the registration element; 2) RFN goes back to its previous state; 3) All of the inputs to the registration element are at NULL state; and 4) RFD is generated and it goes back to the previous state. The completion detection component is used to determine whether the corresponding pipeline stage is ready for another DATA/NULL cycle. It consists a cascade of NCL AND gates at which the output is fed back to the previous register. When it detects the current operation is a complete DATA set or a complete NULL set, the output will be asserted to request the next cycle. Therefore, the period of DATA-to-DATA cycle consists of four stages:

- 1. Time for NULL combinational evaluation  $(T_{Ni} \to T_{RN_{i+1}})$ ;

- 2. Time for NULL completion acknowledgement  $(T_{N_{i+1}} \to T_{RD_i})$ ;

- 3. Time for DATA combinational evaluation  $(T_{Di} \to T_{RD_{i+1}})$ ;

- 4. Time for DATA completion acknowledgement  $(T_{D_{i+1}} \to T_{RNi})$ ;

where  $T_{D_i}$  and  $T_{D_{i+1}}$  represent the propagation time of DATA in the current stage and next stage, respectively. Similarly,  $T_{N_i}$  and  $T_{N_{i+1}}$  represent the propagation time of NULL on the current stage and next stage, respectively.  $T_{RN_i}$ ,  $T_{RD_i}$ ,  $T_{RN_{i+1}}$  and  $T_{RD_{i+1}}$  represent the acknowledge time of request for NULL/DATA on the current or next stage, respectively.

Threshold gates provide the basic building block of NCL designs. There are two types of NCL threshold gates: THmn and  $THmnWw_1..w_R$ , where n represents the number of inputs and m is the threshold value of the gate [13]. This means that at least m of the n inputs must be asserted before the output becomes asserted. Available  $w_1..w_R$  are the integer weights of  $input_1..input_R$ , respectively. For example, a TH34w2 gate has n=4 inputs and its weight of the first input is  $w_1=2$ . In order to assert its output, at least three of the four inputs must be asserted since m=3. Figure 1.2 shows the symbol of a TH34w2 gate [13]. The inputs and outputs of a threshold gate can be one of two states, NULL or DATA. For example, the 1-bit NCL register consists of two TH22n gates and a TH12 gate. A threshold gate starting with its output in an NULL state will remain in the NULL state until the specified number of inputs are placed in the DATA state. Once the gate reaches the DATA state, it remains in this state until all of the inputs return to the NULL state. The hysteresis in the threshold gate provides the threshold needed to keep from switching during intermediate state when the number of inputs in the DATA state is between zero and the threshold limit.

Figure 1.1. Block diagram of NCL combinational logic with two DI registers.

Figure 1.2. Threshold gate TH34w2.

There are twenty-seven fundamental threshold gates (TH gates) with hysteresis capability [13]. Each uses no more than four inputs. The TH gate provides a threshold for the output assertion condition and hysteresis for state-holding behavior. This allows all the inputs to be incorporated before generating the outputs, ensuring a complete transition. Any arbitrary logic(s) can be obtained by using different combinations of these TH gates [4]. For example, the Boolean equation of TH23 gate is  $Z = AB + BC + CA + (A + B + C)Z^*$  where AB + BC + CA is the threshold term, A + B + C is the hold condition, and  $Z^*$  is the previous output. Table 1.1 shows the truth table of this gate. When  $Z^*$  is 0, the updated output is the same result of the threshold equation, but once it becomes 1, the output will remain 1 until all inputs (i.e., A, B, C) become 0 eventually. This principle is designed in all TH gates that are shown in Table 1.2.

| Table 1.1. | Truth | table | of NCL | TH23 | gate. |

|------------|-------|-------|--------|------|-------|

|            |       |       |        |      |       |

| $Z^*$ | АВС   | Z | $Z^*$ | АВС         | $\mathbf{Z}$ |

|-------|-------|---|-------|-------------|--------------|

| 0     | 0 0 0 | 0 | 1     | 0 0 0       | 0            |

| 0     | 0 0 1 | 0 | 1     | 0 0 1       | 1            |

| 0     | 0 1 0 | 0 | 1     | 0 1 0       | 1            |

| 0     | 0 1 1 | 1 | 1     | 0 1 1       | 1            |

| 0     | 100   | 0 | 1     | $1 \ 0 \ 0$ | 1            |

| 0     | 101   | 1 | 1     | 101         | 1            |

| 0     | 1 1 0 | 1 | 1     | 1 1 0       | 1            |

| 0     | 1 1 1 | 1 | 1     | 1 1 1       | 1            |

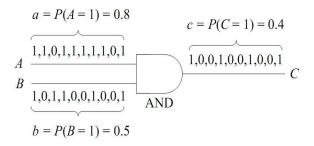

In order to retain DI, NCL circuits should satisfy the condition of input-completeness and observability [14]. Input-completeness requires that the transition of all outputs in a combinational circuit should wait until all inputs have transitioned from either NULL to DATA or DATA to NULL completely. In another word, all outputs cannot transition before all inputs arrive. The observability condition ensures that every gate transition is observable at the outputs, meaning that there is no orphans could propagate through a gate [13]. For example, an incomplete NCL AND function  $(Z = A \bullet B)$  can be designed using a TH12 gate and a TH22 gate, where  $Z^1 = A^1 \bullet B^1$  and  $Z^0 = A^0 + B^0$ . It is incomplete because the output can transfer from NULL to DATA0 without both inputs are DATA, which breaks the condition of input-completeness. To make it complete, the equation for DATA0  $Z^0 = A^0 + B^0$  can be changed to  $Z^0 = A^0(B^0 + B^1) + B^0(A^0 + A^1) = A^0B^0 + A^0B^1 + A^1B^0$ ; Therefore, a complete NCL AND function could be designed using a TH and D0 gate and a D1 gate.

#### 1.2. ADVANTAGES OF USING NCL

NCL is an asynchronous logic, which eliminates the need for a global clock and the clock distribution network. Therefore, timing design is easier than its synchronous counterpart due to the lack of requirement to compensate clock skew, clock jitter, and glitches. Unlike traditional asynchronous design techniques (i.e., Huffman circuits)

Table 1.2. Twenty-seven NCL TH gates.

| NCL TH Gate | Boolean Equation  | NCL TH Gate | Boolean Equation |

|-------------|-------------------|-------------|------------------|

| TH12        | A+B               | TH22        | AB               |

| TH13        | A+B+C             | TH23        | AB+AC+BC         |

| TH33        | ABC               | TH23w2      | A+BC             |

| TH33w2      | AB+AC             | TH14        | A+B+C+D          |

| TH24        | AB+AC+AD+BC+BD+CD | TH34        | ABC+ABD+ACD+BCD  |

| TH44        | ABCD              | TH24w2      | A+BC+BD+CD       |

| TH34w2      | AB+AC+AD+BCD      | TH44w2      | ABC+ABD+ACD      |

| TH34w3      | A+BCD             | TH44w3      | AB+AC+AD         |

| TH24w22     | A+B+CD            | TH34w22     | AB+AC+AD+BC+BD   |

| TH44w22     | AB+ACD+BCD        | TH54w22     | ABC+ABD          |

| TH34w32     | A+BC+BD           | TH54w32     | AB+ACD           |

| TH44w322    | AB+AC+AD+BC       | TH54w322    | AB+AC+BCD        |

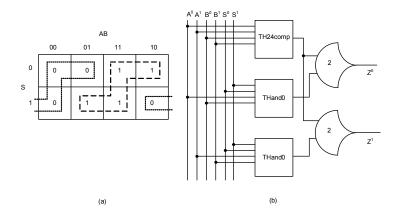

| THxor0      | AB+CD             | THand0      | AB+BC+AD         |

| TH24comp    | AC+BC+AD+BD       |             |                  |

[15] that need timing analysis to achieve the delay matching so as to synchronize the datapath and control path with the absence of a clock. NCL circuits do not need such extensive timing analysis, which makes the design much less complex. In another word, NCL has the potential to process at its maximum frequency due to the fact that the data go through path with minimal delay. This allows a NCL circuit to potentially operate faster than a Boolean asynchronous design.

Another benefit of NCL is the lower power consumption. The demonstration could be found in section 3 that total power consumption of both synchronous S-Box and NCL S-Box is compared based on the measurement results of EDA tools and FPGA simulation. The rational is NCL's monotonic transition between DATA wave and NULL wave, creating an idle power state and eliminating the glitch power [13]. NCL circuits only switch when useful work is being performed, not every clock edge like Boolean circuits. NCL systems also distribute the demand for power over time and area, reducing the occurrence of hot spots, system noise, and peak power demand [16]. According to [2], because of the DI, NCL is insensitive to the changes of physical implementations and parameters, such as the scale changes, variations in propagation delay, aging issues, temperature, manufacturing variations, and so on. Therefore, a NCL circuit is anticipated to operating at a lower voltage with fast speed when the high performance is not required. As discussed in later sections, the NCL's power

consumption characteristic has the benefit of increased security for cryptographic devices.

This dissertation have explored more advantages of using NCL in two application areas. They are: 1) NCL based nanowire crossbar architectures, which have the benefit of enhanced manufacturability, scalability, modularity, and robustness. 2) NCL based AES S-Box design that could successfully resist various SCAs, including DPA and CPA. More specific explanations will be presented in Section 2 and Section 3, respectively.

#### 1.3. WORKS SUMMARY

This dissertation consists of three projects.

The NCL-based nanowire crossbar reconfigurable architectures are presented in Section 2. It studies two implementations of ANRCA and discusses the advantages of using asynchronous logic for nanoscale crossbar structure. The proposed ANRCAs are unique for two reasons: 1) It is based on asynchronous NCL, clock-related failures can be removed; 2) It addresses design, test, and manufacturing issues in nanowire crossbar architecture by designing hierarchical structure, introducing function test, and presenting fault-tolerance and repair strategies. Part of Section 2 comes from the following publications:

- Advances in Nanowire-Based Computing Architectures, a book chapter published in Cutting Edge Nanotechnology, 2010.

- Latency/Area Analysis and Optimization of Asynchronous Nanowire Reconfigurable Crossbar System, Nano Communication Network 2010.

- Asynchronous Nanowire Reconfigurable Crossbar Architectures, submitted to IEEE Transaction on Nanotechnology 2011.

- Area and Latency Measurement and Optimization of Clock-Free Nanowire Reconfigurable Crossbar Systems, IEEE I2MTC 2010.

- Memristor Lookup Table (MLUT)-Based Asynchronous Nanowire Crossbar Architecture, IEEE Nanotechnology 2011.

- Post-Configuration Repair Strategy for Asynchronous Nanowire Crossbar System, IEEE MWSCAS 2012.

- Configurable Logic Block (CLB) Design for Asynchronous Nanowire Crossbar System, IEEE MWSCAS 2012.

Section 3 focuses on the development of NCL based AES S-Box. The objective is to demonstrate NCL S-Box could effectively resist various SCAs and has lower total power consumption than its synchronous counterpart. The hardware implementation of NCL S-Box is designed in VHDL and simulated using both EDA tools and a SCA evaluation FPGA board (SASEBO-GII). Part of Section 3 comes from the following publications:

- Measurement and Evaluation of Power Analysis Attacks on Asynchronous S-Box, accepted for publication in IEEE Transaction on Instrumentation and Measurement 2012.

- FPGA-based Measurement and Evaluation of Power Analysis Attack Resistant Asynchronous S-Box, IEEE I2MTC 2011.

- Asynchronous Nanowire Reconfigurable Crossbar Architectures, GLSVLSI 2010.

Section 4 presents a novel implementation of S-Box design that is based on stochastic logic. By involving probabilistic bit streams in logic implementations, power traces become more unpredictable and data independent. This highly randomness property is helpful for cryptographic devices against power analysis attacks. However, such nondeterministic encoding scheme might generate logic errors. Therefore, different factors that would improve the accuracy have been analyzed in this section, including the length of bit streams, the decision weight, and the repetition times of the inputs. The enhanced security of stochastic logic-based AES S-Box has been experimentally verified on the same SASEBO-GII board. Part of section 4 will be submitted to IEICE Electronics Express (ELEX) 2012.

Finally, Section 5 discusses the contribution of this dissertation and suggestions for future works.

#### 2. PROJECT I: ANRCA

#### 2.1. BACKGROUND

Many challenges have arisen with continued scaling of Complementary Metal-Oxide-Silicon (CMOS) technology, including the increase of integrated circuit complexity, increase in frequency, power density, non-recoverable expenses, and so on. These difficulties have made it troublesome to further progress with, leading nanotechnologies to take the forefront of continuing the technological advancement. One of the most promising nanotechnologies is the nanowire crossbar-based architecture: a two-dimensional array formed by the intersection of two orthogonal sets of parallel and uniformly-spaced synthesized nanowires such as carbon nanotubes (CNTs) and silicon nanowires (SiNWs) [17, 18, 19]. These wires can be aligned to construct an array with nanometer-scale spacing and formed crosspoints of nanoscale wires that can be used as functional logic devices. These devices include programmable diodes, field-effect transistors (FETs), and memristors, depending on the nature of nanowires and interlayer material. The resulting structures act like programmable logic arrays to implement conventional logics. The memristors based nanowire crossbar could also be used to build memories due to its non-volatile characteristic. A typical nanowire crossbar structure is shown in Figure 2.1. Nanowire crossbars offer both opportunities and challenges. One of the opportunities is to achieve ultra-high density which has never been achieved by photolithography (a density of 10<sup>11</sup> crosspoints per square centimeters has been reported in [20]). The most important challenge is to make them reliable enough in computational applications because of the high fabrication defect densities (as high as 10\%, are expected [21]).

Synthesizing nanowires can be done efficiently through bottom-up fabrication paradigm, meaning that the CNTs and SiNWs are synthesized first, then assembled into functional devices. The traditional top-down lithographic manufacturing would not be practical [22]. Combined with fluidic flow techniques by Langmuir-Blodgett (LB) [23], these wires can be aligned to construct arrays that can be used multiple times to yield complex hierarchically assembled nano-systems. Unfortunately, this

Figure 2.1. Typical nanowire crossbar structure.

technique can lead to random breaks between the ends of the nanowires from rearranging them to scale down the size. Thus, a hierarchical structure is better than a monolithic structure for integrated nano-systems due to the fact that small amount of defects would not cause system failure. Hewlett-Packard (HP)'s lab have successfully fabricated 8 × 8 (i.e., 64 bits) crossbar memory arrays by using a fabrication technique of nanoscale crossbar called nano-imprint lithography [24, 25]. The fabrication process reveals that the amount of defects increases proportionally to the decrease in the size of the memory arrays. Challenges still arise with the enhancement of lithographic resolutions and defect tolerance even though these fabrication techniques produce results that are quite favorable for synthesizing nanowires efficiently.

Until now, various nanowire crossbar structures have been proposed: Dehon et al. [26] have developed an operational reconfigurable computing system, known as NanoPLA, utilizing these nanowires and molecular-scale devices. HP [27, 28] announced a computational structure with a decoder scheme for addressing nanowires with micro-scale wires. They have also recently demonstrated a nanoscale crossbar-based memristor array [29]. An analysis of diode-resistor based nanoPLA was present in [30]. Other nanoscale reconfigurable homogeneous architectures, such as NanoFabric [31, 32, 33]; follow a similar principle; grouping multiple crosspoints together to

serve as a memory device or logic element, and the CMOS/Nano hybrid structure has been used to configure the interface.

#### 2.2. ADVANTAGES OF ANRCA

Unlike those proposed nano-structures that are all based on synchronous operation, the presented work proposes Asynchronous Nanowire Reconfigurable Crossbar Architectures (ANRCA). They have a distinct feature of asynchronous operation, which is based on the NCL, a delay-insensitive data encoding and self-timed logic[14]. Potential benefits of using NCL for nanowire crossbar design include:

- 1. Easy for manufacturing because of the clock-less characteristic, eliminating all clock-related hardware.

- 2. ANRCAs are designed in a bottom-up manner and integrated without the trouble of synchronizing each module, which indicates better scalability and modularity than its clocked counterparts because the timing complexity remains the same as the circuit size increases.

- 3. The complemented primary inputs (e.g.,  $\overline{A}$ ,  $\overline{B}$ ,  $\overline{C}$  and  $\overline{D}$ ) used in NanoFabric [31] and the Field Effect Transistor (FET) based inverters used in NanoPLA [26, 18] are no longer needed because they can be implemented simply by crossing over the NCL dual-rail signals.

- 4. Due to non-determinism in the bottom-up self-assembly approach, exhibiting variations in physical parameters in nanowire crossbar structures. These variations would have negative effects on the timing behavior of circuits. ANRCAs are independent of timing issues, thus they are anticipated to have better robustness over the design parameter variations.

- 5. Stuck-at-1 faults are easy to detect, which relatively reduces testing complexity. Once a fault has occurred, the NCL circuit will be halted because it interferes with the transition from DATA (either 01 or 10) to NULL (00). Also, the dual-rail signal 11 is invalid in NCL; therefore, any permanent or transient fault that results in this invalid state can be easily detected.

This section presents two implementations of ANRCA. One uses crosspoints as programmable diodes that create AND/OR planes to implement logic gates (Section 2.3). The other uses configurable memristors to realize nanoscale lookup tables (LUTs)(Section 2.6). Discussions of defect issues and repair strategies for these two optimization models are comprehensively studied. Comparisons between these two optimization models have been analyzed in terms of area, programming steps, crosspoints utilization rate, and defect tolerance(Section 2.8). The above contributions of this project are particularly beneficial in designing an optimized reconfiguration hardware fabrication and in efficiently mapping any given complex logic.

#### 2.3. DIODE- AND RESISTOR-BASED ANRCA (DR-ANRCA)

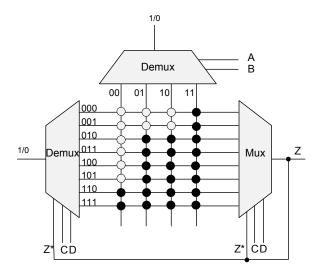

The primitive unit of DR-ANRCA is the Programmable Gate Macro Block (PGMB), DR-PGMB for short. A single DR-PGMB is made of six horizontal nanowires that cross over eleven vertical nanowires to form sixty-six crosspoints. These crosspoints are formed by programmable diodes to create an AND/OR logic plane. The use of pull-up resistors on the vertical nanowires create the AND-plane, and pull-down resistors on the horizontal wires create the OR-plane, enabling each DR-PGMB to be programmed to realize any given NCL threshold gate function in sum-of-product (i.e., SOP) form. For example, Figure 2.2 shows a DR-PGMB implementing a TH23 NCL gate, whose boolean expression is  $Z = AB + BC + CA + (A + B + C)Z^*$ , where  $Z^*$  represents the previous output value of the TH23 gate, which is fed back to the input nanowire.

For the purpose of efficiently reconfiguring the given DR-PGMB as one of the 27 arbitrary NCL threshold gates, three configurable logic block (CLB) structures were designed: CLB-1, CLB-2, and CLB-3. Figure 2.3 shows that the CLB-1 structure consists of four DR-PGMBs which are surrounded by nanowires and demultiplexers. The demultiplexers are used as the interface between microwires and nanowires since they can use a small number of microwires to control a relatively large number of nanowires. The input lines for addressing the demultiplexers are microwires, which can be implemented on a CMOS substrate [34]. The output lines are nanowires that are used to control crosspoints in DR-PGMBs. The number of input microwires (M) and output nanowires (N) is expressed as  $N=2^M$ . The demultiplexers must be placed

Figure 2.2. TH23 gate realized on a programmable gate macro block.

on the side of the rows and columns to program all the crosspoints to ON/OFF states by applying positive or negative voltages. Assuming that the unselected outputs are driven by ground, then the intersection of driven nanowires would have a voltage drop that is different from other unselected crosspoints. This would allow the configuration of crosspoints sensitivity to voltage to drop across them. For example, driving a positive voltage on one of the column nanowires and a negative voltage on one of the row nanowires, the rest of nanowires would be driven with ground, the selected crosspoint is defined as the intersection of driven nanowires.

The CLB-1 shown in Figure 2.3 is configured to function as a NCL full adder. Two TH23 gates and two TH34w2 gates are implemented in four PGMBs, then, interconnected in the configurable interconnection grid. Three inputs X, Y, Ci and two outputs S, Co are represented by  $X^0, X^1, Y^0, Y^1, Ci^0, Ci^1, Co^0, Co^1, S^0, S^1$  encoded in dual-rail logic. The top demultiplexer is used to decode the input signals from DR-PGMB to determine which nanowires are selected. The other demultiplexers are used to select different DR-PGMBs to receive those input signals. The following steps are used to program logic onto the CLB: 1) Use the top and right demultiplexers to choose input crosspoints; 2) Use the bottom and right demultiplexers to map the selected crosspoints to each DR-PGMB; 3) Program each DR-PGMB to the required threshold gate. 4) Retrieve the generated output from the designated DR-PGMB.

Figure 2.3. NCL full adder implemented in CMOS (left) and CLB-1 (right).

The three CLBs are distinguished by the number of demultiplexers on the right side: CLB-1 has one, while CLB-2 and CLB-3 (Figure.2.4) have two and four, respectively. The microwire address lines may be shared among multiple demultiplexers to allow multiple crosspoints to be simultaneously accessed.

NCL delay-insensitive registers are needed to bracket the combinational logic design to achieve the transition between DATA and NULL state. An 1-bit NCL register can be implemented on a single CLB using two TH22 gates and a TH12 as shown in Figure 2.5. The schematic of an 1-bit NCL register has been shown in Figure 1.1.  $I^0$ ,  $I^1$ ,  $O^0$  and  $O^1$  represent input and output data rails, respectively.  $K_i$  and  $K_o$  are the handshaking signals. The complemented value of  $K_o$  can be designed by crossing over the wires due to its dual-rail property. For the full adder design, an 3-bit input register (i.e., three CLBs) and 2-bit output register (i.e., two CLBs) are needed to provide the appropriate number of input/output signals. Thus, an FPGA-like hierarchical architecture was proposed to implement the higher level logic that requires a large number of DR-PGMBs, such as multiple bits full adder. Figure

Figure 2.4. The second and third variations of (CLB-2 and CLB-3).

2.6 shows the structure of the two-level hierarchical architecture that can be used for implementing a 4-bit adder. Compared with the nanowire crossbar 3-bit adder design that was introduced in [35], although the proposed DR-ANRCA consumes more area, it is relatively easier to reconfigure and unaffected from any timing variations because of its delay-insensitivity.

#### 2.4. NUMERICAL ANALYSIS OF DR-ANRCA

2.4.1. Area. The area-efficient demultiplexer designs reported in [36] are used in the proposed CLB designs. Thus, the demultiplexers selected by the DR-PGMB on the right are assumed to be allocated on the same column-wise area of the substrate. According to the NanoPLA assembly parameters provided by Dehon[26], the lithographic interconnect pitch can be estimated as 105nm for the 45nm node. A 10nm nanowire pitch is acceptable for assembling the crosspoints between each pair of crossed nanowires. Nanowire with 3nm diameters has been demonstrated. Microwires have diameters of around 45nm [26]. The pitch between microwires and nanowires is assumed to be a median of  $P_n$  and  $P_m$ , which is around 60nm. Thus, as

Figure 2.5. 1-bit NCL register implemented in one CLB.

Figure 2.6. Two-level hierarchical architecture for the proposed ANRCA.

shown in Figure 2.3, the overall area of each CLB can be estimated as the product of the width and height ( $Area = Width \times Height$ ):

$$Width = P_n \times (N_v - 1) + P_m \times (M_v - 1) + P_{mn} + N_v \times D_n + M_v \times D_m$$

(1)

$$Height = P_n \times (N_h - 1) + P_m \times (M_h - 1) \times 2 + P_{mn} \times 2 + N_h \times D_n + M_h \times D_m \times 2 \quad (2)$$

where:  $N_v$  and  $N_h$  represent the number of nanowires in vertical and horizontal direction, respectively;  $M_v$  and  $M_h$  represent the number of microwires for demultiplexers in vertical and horizontal direction, respectively;  $P_n$  and  $P_m$ ,  $D_n$  and  $D_m$  are the pitch and diameter of the nanowires and microwires, respectively; and  $P_{mn}$  is the pitch between microwires and nanowires. Thus, in calculating their areas using the above equations, the estimated areas of the proposed CLB-1, CLB-2, and CLB-3 are  $1.477um^2$ ,  $1.265um^2$ , and  $1.053um^2$ , respectively.

**2.4.2.** Programming Steps. The complexity of the logic mapping operation is another factor that should be considered to optimize the design. A programming step is defined as selecting and programming a specific crosspoint in a given CLB. The average programming step count is defined as the estimated number of steps needed to program a given number (i.e., 2, 4, 8, or 10) of randomly distributed crosspoints among DR-PGMBs. For example, say there are four crosspoints need to be programmed and they are randomly distributing on the crossbar. If they are programmed by the design of CLB-1, each point would be selected one by one since there is only one PGMB select demultiplexer. Thus the programming step count in this case is four. For CLB-2 and CLB-3, actual programming step count depends on the geometric distribution of crosspoints being programmed because different demultiplexers are controlling the selection of rows. One extreme case is that the four crosspoints happen to locate on the same column of each PGMB controlled by the four demultiplexers of CLB-3. The total step of programming these four points is one since four demultiplexers can select them simultaneously in this case. However, other distributions should be considered too. Therefore, a numerical analysis program for calculating the average steps has been implemented in MATLAB. A probabilistic algorithm and a square curve fitting algorithm were developed to derive the average number of steps. Figure 2.7 shows the relationship between the number of crosspoints to be programmed and the average number of steps required to fully program them.

Figure 2.7. Curve fitting results of programming steps for various CLBs.

2.4.3. Latency. Latency is defined as the total time required to process input to generate output. System latency for the proposed ANRCA consists of two parts: the cycle of combinational logic implemented by the CLBs and the cycle of NULL and DATA handshaking feedback signal propagation. A single cycle in one DR-PGMB of CLB evaluates both input (i.e., in AND-plane) and output (i.e., in OR-plane). The total time for a single input/output plane is estimated based on the following equations: the latency for the input plane and output plane can be estimated as

$$T_{inPlane} = N_{ci} \times T_d \tag{3}$$

$$T_{outPlane} = N_{co} \times T_d \tag{4}$$

and the latency for a demultiplexer is estimated as

$$T_{propagation} = N_p \times T_p \tag{5}$$

thus the overall latency is

$$T_{cycle} = T_{inPlane} + T_{outPlane} + T_{propagation}$$

=  $(N_{ci} + N_{co}) \times T_d + N_p \times T_p$  (6)

where:  $N_{ci}$  and  $N_{co}$  represent the number of input and output crosspoints of an DR-PGMB, respectively;  $T_d$  is the processing time of demultiplexers;  $T_p$  is the propagation delay of programming one crosspoint on its DR-PGMB.  $N_p$  represents the total number of crosspoints on an DR-PGMB. The comparison for the latency of different CLBs, is dependent on the logic that is implemented on it. A full adder design is used as a benchmark to make a simple comparison of the latency among three CLBs: CLB-1, CLB-2, and CLB-3 is  $18T_d + 90T_p$ ,  $10T_d + 54T_p$ , and  $5T_d + 37T_p$ , respectively.

Generally, a single NCL cycle comprises the propagation delay of NULL/DATA and the acknowledge time of a request for DATA/NULL [37] as Figure 2.8 shows.

Figure 2.8. A single NCL cycle of DATA-to-DATA latency.

The proposed ANRCA also follows this rule since it is based on NCL. Therefore, the DATA-to-DATA latency is given by:

$$T_{D_i to D_{i+1}} = T_{D_i} + T_{RNi} + T_{N_i} + T_{RD_{i+1}}$$

(7)

where  $T_{D_i}$  and  $T_{N_i}$  represent the propagation time of DATA and NULL in the current stage, respectively;  $T_{RN_i}$  is the acknowledge time of request for NULL in the current stage;  $T_{RD_{i+1}}$  is the acknowledge time of request for DATA in the next stage.

#### 2.5. DEFECT/FAULT ISSUES OF DR-ANRCA

One of the main problems with nanoscale crossbar architecture is the high inherent defect density that is caused by the bottom-up self-assembly fabrication technique[38]. The conventional fault-tolerance and reliable design are not adequate in nanoscale integration because of the increased defect and fault rates. Therefore, fault-tolerance techniques for nanowire crossbar structure is critically needed. Several test algorithms have been developed by our research group, including defect-unaware, defect-aware, and function test algorithm (FTA) [39, 40]. This dissertation uses FTA to detect defective crosspoint locations, focuses on the development of post-configuration repair technique, and fault-tolerance techniques to increase the reliability of the proposed ANRCAs. The fault-tolerance approaches include permutation, commutative method, and redundancy. There are three ways to tolerate defects in a DR-PGMB:

- 1. Reconfigure the order of primary inputs utilizing the demultiplexer that is designated to select inputs. The number of combinations for rearranging the order of inputs can be determined from factorial of the number of inputs.

- Rearrange the order of columns of the given DR-PGMB base on the commutative law since the product terms in the sum-of-product (SOP) of TH gates can be rearranged.

- 3. Include redundant rows and columns in each DR-PGMB to increase the chances of generating the correct output by forcing the desired logic.

Using a TH23 gate (i.e.,  $Z = AB + BC + AC + (A+B+C)Z^*$ ) as an example, the above defect tolerance methods are demonstrated in Figure 2.9. It shows a side-by-side comparison of a defective DR-PGMB with a corrected DR-PGMB that is based upon the respective methods described above. Figure 2.9(a) shows the matrix implementation of a TH23 gate on a DR-PGMB with defects on the intersection of

Figure 2.9. Demonstration of defect tolerance methods.

(2,1) and (3,2). To avoid these defective crosspoints, the input order can be simply changed from A,B,C to B,C,A. Figure 2.9(b) shows the defective crosspoints located at (2,2) and (1,3); in this case, the SOP can be rearranged from  $Z = AB + BC + AC + (A + B + C)Z^*$  to  $Z = AB + AC + BC + (A + B + C)Z^*$ . Figure 2.9(c) shows the defective crosspoints located at (1,1) and (2,1). The product term of the TH23 gate can not be mapped on the first column without using extra rows. Therefore, the solution is to use extra rows or columns. If the number of defective crosspoints are too large to be tolerated by the selected DR-PGMB, the worst-case scenario is to discard the selected DR-PGMB and use another one to reprogram the given TH gate function.

FTA uses a test tuple that combines the input patterns and the previously asserted output patterns to list all possible faults for the mapped TH gate. Based on FTA, a new post-configuration repair technique was derived to provide a balanced combination of tolerable repair time and acceptable repair performance [39, 40]. Test tuples having one-to-one correspondence with defective crosspoints are applied first to detect and then isolate DR-PGMB rows and columns that are needed to be repaired.

Consider a TH34w2 gate shown in Figure 2.10. The black dots represent programmed-ON crosspoints and crosses represent defective crosspoints. The combination of both symbols represents defective crosspoints that affect the functionality of the gate. To implement a TH34w2 gate on a DR-PGMB, a total of 25 crosspoints must be programmed on the specific locations. In this case, there are 7 defective crosspoints among a total of 66 crosspoints. The defect rate is approximately 10% and five of the defective crosspoints, (2,4), (4,8), (6,1), (6,5), (6,8) affect the functionality of the TH34w2 gate and three of them are located on the OR plane. Thus, according to the functionality of TH34w2 (i.e.,  $Z = AB + AC + AD + BCD + (A + B + C + D)Z^*$ ) and its specific coordinates shown in Figure 2.10 part (a), a test tuple table (see Table 2.1) was generated for TH34w2 to sort the test vectors for related defective crosspoints. The OR plane takes the priority because it reflects the various results from the AND plane [40]. The initial state of input is assumed to be 0000 so that the output Z will be 0 as well. Any stuck-at-1 crosspoints in the OR plane could be tested using this test vector. Although test tuple 0000 could be used to test all the required crosspoints, it takes a long time to go through all the required crosspoints (i.e., 25 in this example). Therefore, a combinations of various inputs could make the testing more efficient. For example, the input 0001 with  $Z^* = 0$  (i.e.,  $Z^*$  is the previous output) could be used to test the defective crosspoints with coordinates (1,3), and (5,8). According to the functionality of TH34w2, the correct result would be 0 when input is 0001 and  $Z^*$  is equal to 0. However, it becomes 1 since the crosspoints (1,3) is defective. A similar testing algorithm could be used for other crosspoints required to implement a TH34w2 gate. Thus the fault location has been detected whenever the observed output does not match the desired one. Using this method, all 25 required crosspoints could be covered within 20 steps.

Once the location of the defective crosspoints have been confirmed, the repair strategy could be developed to avoid the defective crosspoints by either rearranging the mapping or using extra rows or columns. As Figure 2.10 part (b) shows, with column 4 moved to column 10 and column 8 moved to column 9, the remaining two defective crosspoints with initial locations (6,1) and (6,5) are moved to (7,1) and (7,5), respectively. The existing defective crosspoints could be avoided. However, another round of FTA should be used to test the new location of these crosspoints to ensure

Figure 2.10. A case study of successfully realized on a defective DR-PGMB of TH34w2 gate.

the functionality of TH34w2 would work property. The algorithm could be modified to test other TH gates on the DR-PGMB.

#### 2.6. MEMRISTOR LOOK-UP-TABLE BASED ANRCA

Memristor, another promising technology for nanoscale computation systems, is considered as the fourth fundamental circuit element [41]. It is expected to have advantages in building nanoelectronic memories, computer logic, and neuromorphic computer architectures [42]. It is also capable of replacing programmable resistors or rectifying devices to yield configurable crossbar junctions (i.e., crosspoints). There are two important properties of memristors[43]: (a) as a memory storage element, each memristor crosspoint can be programmed independently into a low-conductance (Logic 0) or a high-conductance (Logic 1) as normal resistive switching elements. (b) as a switche, low-conductance (OFF-state) and high-conductance (ON-state) refer to the unconnected state and the connected state, respectively. Various research papers describe the way to write/read memristor based nanowire crossbar[44, 45, 46]. A tutorial of using memristor-based crossbars has been presented in [47]. Using the properties of memristors, this work proposes another implementation of ANRCA that relies on configurable memristors to realize nanoscale look-up-tables (LUTs).

Table 2.1. Test Tuples for TH34w2 gate.

| Test Tuples (input bits) | Required Crosspoints Coordinates         |

|--------------------------|------------------------------------------|

| 0000                     | OR Plane and F(1,5), (2,6), (3,7), (4,8) |

| 0001                     | F(1,3), F(5,8)                           |

| 0010                     | F(1,2), F(5,7)                           |

| 0011                     | F(2,4), F(1,3), F(1,2)                   |

| 0100                     | F(1,1), F(5,6)                           |

| 0101                     | F(1,1), F(1,3), F(3,4)                   |

| 0110                     | F(1,1), F(1,2), F(4,4)                   |

| 0111                     | F(1,1), F(1,2), F(1,3)                   |

| 1000                     | F(2,1), F(3,2), F(4,3), (5,5)            |

| 1001                     | F(2,1), F(3,2)                           |

| 1010                     | F(2,1), F(4,3)                           |

| 1011                     | F(2,1), F(2,4)                           |

| 1100                     | F(3,2), F(4,3)                           |

| 1101                     | F(3,2), F(3,4)                           |

| 1110                     | F(4,4), F(4,3)                           |

| 1111                     | N/A                                      |

The basic unit of MLUT-ANRCA is the MLUT based PGMBs, MLUT-PGMB for short. A single MLUT-PGMB consists of eight horizontal nanowires crossing over four vertical nanowires that are surrounded by column/row demultiplexers and a multiplexer (see Figure 2.11). It can be programmed to realize any given NCL gate by directly implementing the truth table of the given gate function using MLUT with the hysteresis (i.e., state-holding behavior) that is required to achieve the proposed delay-insensitivity via a feedback interconnect.

Figure 2.11 shows the implementation of a MLUT-PGMB programmed to function as an NCL TH23 gate. The demultiplexers located at the row and column

Figure 2.11. TH23 gate realized on a MLUT-PGMB.

of the MLUT-PGMB are utilized to select a programmable memristor junction. Lightcolored dots represent the memristor crosspoints programmed as 0, while the darkcolored dots are 1. A feedback signal is sent to provide  $Z^*$  to the row demultiplexers for hysteresis behavior. If  $Z^*$  is equal to 0, then the top half of the LUT is selected to provide the output setting logic. If  $Z^*$  is equal to 1, the bottom half of the LUT is selected to provide the output resetting logic. An equivalent circuit simulation has been presented in [48]. As shown in this example, a single MLUT-PGMB can be programmed to function as a TH gate. Likewise, multiple MLUT-PGMBs can be programmed and interconnected via a reconfigurable interconnection network to form a higher level circuit in nanoscale. This is similar to the hierarchal architecture presented in DR-ANRCA section. Another benefit of the MLUT-PGMB design is that it simplifies the reading procedure by assuring that the memristors at each crosspoints are required to be programmed either ON or OFF state (i.e., 1 or 0 in Boolean) so that the LUT could be setup. This eliminated the need of using the adaptive measurement algorithm proposed in [43]. Because the comparison of two different states is only necessary. Also, for any TH gate, the initial crosspoint (1,1) (i.e., all inputs are 0) is always programmed to 0 and the last crosspoint (8,4) (i.e., all inputs are 1) is always programmed to 1, therefore they are used as references to determine the value of a selected output.

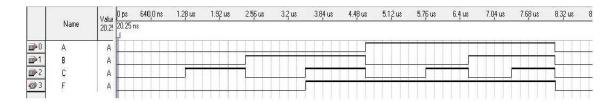

The functionality of the proposed MLUT-PGMB's threshold and hysteresis behaviors were verified by implementing a structural model in VHDL. A timing simulation is also performed using the design automation tool. The simulation waveform is shown in Figure 2.12. Output F becomes '1' when ABC becomes '011' (i.e., threshold behavior), then maintains this value until ABC resets back to '000' (i.e., hysteresis behavior). The results demonstrate that the structural model's functionality accurately matches the logic of the TH23 gate.

Figure 2.12. Waveform of TH23 gate.

#### 2.7. DEFECT/FAULT ISSUES OF DR-MLUT

To address the high inherent defect density in the context of MLUT-ANRCA design, this study focuses on a MLUT-PGMB as a basic unit of MLUT-ANRCA to realize the proposed defect-tolerance methods. There are three states in which a defective crosspoint can be detected: nonprogrammable, stuck-at-1, or stuck-at-0. A crosspoint in a non-programmable state can not be changed to an ON or OFF state. A comparison method is used to detect whether or not a crosspoint is in this a state. This method utilizes the initial crosspoint (1,1) and the last crosspoint (8,4) as references for comparing a selected crosspoint. If the selected crosspoint does not match either of the reference values, it can be considered as a nonprogrammable crosspoint. This method is based on the assumption that the reference crosspoints are programmed properly. The crosspoints with stuck-at-0 or stuck-at-1 faults can be simply detected by programming opposite values on them and then utilize the proposed comparison method to determine whether it is reconfigurable.

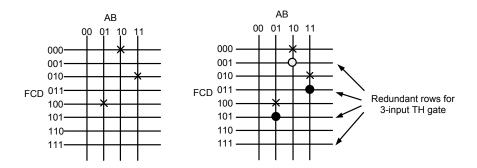

Tolerance for these defective crosspoints can be attained by the use of redundancy, replacement, or a passive approach. Redundancy is the basic method in the fault-tolerance system, it involves the use of spare wires to reprogram copies of selected logic. The area provided by the MLUT-PGMB allows crosspoints on specific rows to be available for redundancy based on the number of inputs for the mapped TH gate. For example, consider the worst case scenario of a 10% defect rate. The left part of Figure 2.13 shows a defective MLUT-PGMB implementing a given TH23 function. The crosspoints (1,3), (3,4), and (5,2) are crossed out to indicate that there are defects. The right part of Figure 2.13 shows a repaired version of the same gate. Crosspoints (2,3), (4,4), (6,2) have been used to replace those defective crosspoints. The same method can be applied to other four inputs TH gates by adding extra wires to increase the number of rows/columns. Relatively high defect rates can be tolerated using this method, especially for the three/two inputs TH gates which require a lower number crosspoints to be programmed on a  $8 \times 4$  MLUT-PGMB. Defect rates of 50% or even 75% can be tolerated without increasing the size of the MLUT-PGMB.

Figure 2.13. A defective MLUT-PGMB and a version repaired using the redundancy method.

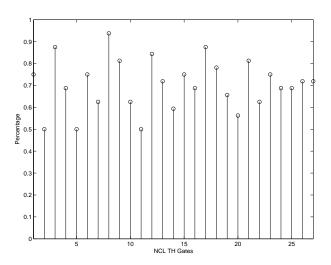

The hysteresis function of NCL determines that the number of crosspoints programmed to 1 is more than the number of crosspoints programmed to 0, because the asserted output will become 0 only when all inputs become 0. Based on this observation, we can use a passive approach to deal with stuck-at-1 faults. If these faults occur at the crosspoints that are originally going to be programmed to 1, they

can be ignored because the desired functionality can still be achieved. Figure 2.14 shows a bar graph that indicates the percentage of crosspoints that are programmed to 1 for each TH gate. It shows that more than 50% of the crosspoints on TH gates are programmed to 1. Thus, this method can be used to tolerate most of stuck-at-1 faults on MLUT-PGMBs. The same method can be applied to stuck-at-0 faults, however, the number of crosspoints that are programmed to 0 for each TH gate is relatively low. To deal with the faults that cannot be ignored, the wires can be rearranged by changing the switching function of the demultiplexer to tolerate them. This approach rearranges the programmed crosspoints to a position where the faults do not interfere with the functionality of the desired TH gate. Alternatively, redundant rows can be used to replace the defective row.

Figure 2.14. Percentage of crosspoints that are programmed to 1 for each TH gate.

#### 2.8. COMPARISON BETWEEN DR-ANRCA AND MLUT-ANRCA

The two designs introduced in this dissertation present novel implementations of ANRCA that achieve the goal of eliminating the dependency of a global clock by implementing the NCL on nanowire crossbar architectures. The DR-ANRCA utilizes

crosspoints as programmable diodes that create an AND/OR plane to implement TH gates. MLUT-ANRCA, on the other hand, uses configurable memristors to realize nanoscale lookup tables (LUTs) to represent each TH gate. The comparison of both in terms of structure, control method, and defect-tolerance analysis are introduced in this section to realize the pros and cons of each method.

The structure of a DR-PGMB consists of  $6 \times 11$  nanowires to create a total of 66 crosspoints to implement any TH gate, whereas a MLUT-PGMB consists of  $8 \times 4$  nanowires to create a total of 32 crosspoints to perform the same functionality. Clearly, MLUT-PGMB requires fewer crosspoints to provide the same functionality. Another benefit of the MLUT-PGMB structure is that it has a better utilization rate of crosspoints than DR-PGMB when implementing the same TH gate function. For example, to program a TH23 gate on both designs, a DR-PGMB requires 18 out of 66 crosspoints, whereas a MLUT-PGMB requires 16 out of 32. The utilization rate is 27.3% versus 50%. Figure 2.15 shows the comparison of crosspoints utilization rate between these two designs for all TH gates. This work also compares the two ANRCAs in terms of area, programming latency, and defect tolerance. The structure of these two designs are different. DR-ANRCA utilizes a combination of three or more demultiplexers to effectively control and program DR-PGMBs in a CLB. Each MLUT-PGMB needs two demultiplexers and one multiplexer to program a TH gate. Similar to DR-ANRCA, it can be managed by a switching matrix to communicate with other MLUT-PGMBs in a CLB. Therefore, a DR-ANRCA uses fewer demultiplexers to implement a CLB, making it relatively easier to be reconfigured than MLUT-CLBs do. According to the NanoPLA assembly parameters provided in [26], 10nm nanowire pitch is acceptable for assembling the crosspoints between each crossed nanowire and 3nm nanowire diameters have also been demonstrated. The area of a single DR-PGMB nano-array and a MLUT-PGMB nano-array is  $9,044nm^2$  and  $7,276nm^2$ , respectively. As Figure 2.15 shows, for most of the TH gates that are implemented in MLUT-PGMB, the crosspoints utilization rate is 100% since all 32 crosspoints will be programmed to achieve its functionality, where the same TH gates require fewer crossponits (up to 50%) to be implemented on a DR-PGMB. Therefore, assuming the latency of programming a crosspoint is the same for both PGMBs (i.e., ts), the total time required to program a MLUT-PGMB would be considerably greater than that

needed to program a DR-PGMB. Figure 2.16 demonstrates a scatter graph that plots the propagation time of programming each TH gate on both PGMBs. The order of TH gates on the x-axis are done in ascending order according to the number of inputs.

Figure 2.15. Crosspoints utilization comparison.

Figure 2.16. Programming time comparison.

Introducing redundancy is a common method that has been widely used in the field of fault-tolerance and reliability. Usually there are two types of redundancy methods: spatial redundancy and temporal redundancy [27]. This work utilized the spatial redundancy method for tolerating these defective crosspoints in the proposed ANRCAs. The cost of spatial redundancy is that larger areas will be consumed when the crossbar scales up. In this regard, MLUT-PGMBs are more flexible in the replacement of a defective crosspoints than DR-PGMBs are because the latter must rely on the AND/OR functions when using the redundancy crosspoints, and the defective crosspoints cannot be fully replaced without increasing the size of each PGMB. However, the defective crosspoints in MLUT-PGMB, especially when it is implementing a two- or three-input TH gate, can be ignored or replaced by adjacent crosspoints, as explained in section 2.7. The comparison made here are based on theoretical designs; a more detailed comparison can be made by evaluating the performance of diodes and memristors.

#### 2.9. CONCLUSIONS

This section has presented two different implementations of ANRCA: DR-ANRCA and MLUT-ANRCA. Both of them are based on NCL that intrinsically eliminate many clock-related issues caused by complex clock distribution networks. Synthesizing nanowires is based on bottom-up fabrication paradigm. The integrated nano-systems prefer using a hierarchical structure over monolithic structure. The studies of ANRCAs start with its primitive configurable logic unit (PGMB), then three versions of CLB for reconfiguration, and finally an FPGA-like hierarchical architecture. With all these features, ANRCAs are anticipated to have the advantages of improved manufacturability, scalability, modularity, and robustness.

Comparisons between different designs are discussed in terms of area, programming steps, and latency. Due to the high inherent defect density in nanowire crossbar caused by the self-assembly fabrication techniques, the conventional fault-tolerance methods are not adequate for ANRCAs. This research have proposed some defect-tolerance and repair strategies for both ANRCAs, including FTA based post-configuration, permutation and commutative method, spatial redundancy, replacement, and passive strategy.

#### 3. PROJECT II: NCL S-BOX DESIGN

#### 3.1. BACKGROUND

In relation to the market of digital information security, crypto-hardware devices that have enhanced security measures while being energy efficient are in high demand. The growth of innovation for these devices can be seen in today's mobile phones and portable devices and computer/network security in industrial control systems [49]. In order to reach this demand of low powered devices with high security features, researchers generally focus around the actually cryptographic algorithm implemented in the hardware itself to encrypt and decrypt information. Thus, securing cryptographic devices against various side channel attacks (SCA) has become a very attractive research topic in recent years along with the developments of information technologies. SCAs explore the security information (i.e., secret key) by monitoring the emitted outputs from physical cryptosystems. These outputs include execution timing, power consumptions, electromagnetic leaks, and even thermal/acoustic emanations [50]. Accurate measurement and estimation of these outputs is the key point of a successful attack. The measurement should be based on the hardware gate-level approach rather than the software instruction-level estimation [51, 52, 53, 54]. Also, for the power consumption measurement, the focus would be the dynamic power consumption that is dissipated during the transistors switching rather than static leakage power consumption [55]. Advanced Encryption Standard (AES) was announced with the intention of being a faster and more secure encryption algorithm over others since its algorithm is comprised of multiple processes used to encrypt information with supports of up to 256 bits key and block sizes, making an exhaustive search impossible to check all  $2^{256}$  possibilities. Usually the hardware AES implementation has a higher reliability than software since it is difficult to be read or modified by attackers and less prone to reverse engineering. Unfortunately, AES is still vulnerable to SCA [56, 57]. The published SCA include simple power analysis (SPA), differential power analysis (DPA), correlation power analysis (CPA) [50, 58], collision attack[59], and leakage power analysis (LPA) [60]. Among them, DPA and CPA are the most popular and effective attack that has been reviewed by numerous researchers on various crypto-systems during these years [50]. In the meantime, many countermeasures for resisting SCA attacks were proposed as well. Most of the countermeasures designed for hardware implementations of AES are based on securing the logics cells to balance the power consumption of the system and make it independent of the processing data. This process of adjusting the basic units of the system makes the overall design less vulnerable to attacks. The hardware implementation of AES essentially has higher reliability than software because it is difficult to be read or modified by the attackers and less prone to reverse engineering [61]. These countermeasures can be separated into two categories based on the framework of the circuit they are implemented on, synchronous and asynchronous.

#### 3.2. EXISTING COUNTERMEASURES

The countermeasures for synchronous circuits include Sense Amplifier Basic Logic (SABL) [62], an improved two-spacer alternating dual rail circuit [63], Wave Dynamic Differential Logic (WDDL) [64], a dynamic voltage and frequency switching approach [65], masked logic styles [66, 67], using Fourier Transform [68], Random Switching Logic (RSL) [69] with its simplified version Dual-rail random-switching logic [70], and recently proposed Masked Dual-Rail Pre-charged Logic (MDPL) and its improved version [71, 72]. These works are centered around resisting DPA attacks and introduce methods on how to effectively reduce the impact of DPA attack. However, they are fundamentally based on synchronized circuits, which either requires a precise control of timing or suffer from some timing related issues, such as glitches [71, 73], hazard, and early propagation [73, 72, 74], which still could leak some side-channel information to the attackers.

Asynchronous circuits, on the other hand, have natural advantages in terms of SCA resistance. The clock-related information leakage can be either eliminated or significantly reduced, which extensively increases the difficulties of attack due to the lack of timing references. The countermeasures based on asynchronous circuits include Balanced delay insensitive method [75], GALS module [76], and 1-of-n data encoded speed independent (SI) circuit [77, 78]. However, the increased security does

not come for free. The area required to implement them are potentially larger than their synchronized counterparts. The benefits in terms of total power consumption and speed are still questionable. In addition, some of the countermeasures are based on the EDA tool simulation results or theoretical analysis, which may not effectively prove that these methods could resist real SCA attacks experimentally.

From these existing countermeasures, the dual-rail encoding [63, 79], with the pre-charge method, spacers, or return to zero (RTZ) protocols are frequently used in both synchronous and asynchronous designs. The dual-rail encoding provides better data independence with the power consumption since the Hamming weights of each data set are the same. A RTZ, spacer, or pre-charge method is used to achieve the monotonic transition to enhance the security. Our proposed Null Conventional Logic (NCL) based S-Box design essentially matches all these important security properties: asynchronous, dual-rail encoding, and an intermediate state (i.e., NULL). Unlike other asynchronous designs, NCL adheres to the monotonic transitions between DATA (i.e., data representation) and NULL (i.e., control representation), which utilizes dual-rail and quad-rail signaling methods to achieve the delay-insensitivity [9]. This would significantly reduce the design complexity. With the absence of a clock, the NCL system is proved to reduce the power consumption, noise, and electromagnetic interference [80, 81]. Furthermore, this work has demonstrated that NCL could also resist SCA without worrying about the glitches and power supply variations [82]. This work provides an extension to what has been presented in [82]. Besides the DPA attack, a CPA attack has been also applied to both synchronous and NCL S-Box design to demonstrated that the proposed NCL S-Box is capable of resisting CPA attack as well.

Usually, there are four methods to conduct the power measurement experiments: 1) use computer-aided design (CAD) tools [61], 2) use regular FPGA board [64], 3) use the SASEBO-GII FPGA board, and 4) use a taped-out ASIC chip. The procedures of taping out a chip include the front-end verification using CAD tools and FPGA board. They are complicated, time consuming, and expensive. Therefore, in order to prove the proposed idea in a more effective way, the first three methods have been tried and the experimental results show that the third method is the most effective one among these three methods. The rational behind lies as follows: 1) while

CAD-tool-based simulation shows the synchronous S-Box design is indeed vulnerable to the DPA attacks, the DPA attacks could not be successfully implemented on the NCL S-Box by such simulation due to too much regularity in the simulated power traces. The reason is that the CAD tools approximate the simulation results. 2) There are many constraints on using regular FPGA board for this experiment. All the decoupling capacitors related to the core power supply should be removed to increase the chance of successful attacks. Also, a current probe is needed to measure the current consumed by the core of the FPGA chip. However, the bandwidth of current probes is usually lower than that of voltage probes, which might not be able to capture the high-frequency AC current variations caused by data transients. 3) A stable power supply is critically important for power analysis experiments. Therefore, using the SASEBO-GII FPGA board is the most effective way because it is designed for the purpose of SCA experiment and it solves all the issues that a regular FPGA board has. In summary, this work provides a general testing procedure to do SCA attacks on the SASEBO-GII FPGA board.

# 3.3. NCL AES S-BOX DESIGN

AES algorithm consists of a number of rounds that are dependent on the key size. For both cipher and decipher of AES algorithm, each round consists of linear operation (i.e., AddRoundKey, ShiftRows, and MixColumns steps) and non-linear operation (i.e., SubBytes step). SubBytes step is the first step of AES round. Each byte in the array is updated by an 8-bit substitution box (S-Box), derived from the multiplicative inverse over  $GF(2^8)$ . AES S-Box is constructed by combining the inverse function with an invertible affine transformation in order to avoid attacks based on mathematics. The S-Box is one the of most critical components in the implementation of AES hardwares. It consumes the majority of power and is also the most vulnerable component to SCAs. A block diagram of AES S-Box is shown in Figure 3.1. The block diagram of multiplicative inversion over  $GF(2^8)$  component where MM is modular multiplication, and XOR is exclusive-or operation [83].

The hardware implementation of AES S-Box adapted in this research follows the combinational logic circuit architecture presented in [83], but uses NCL gates

Figure 3.1. Block diagram of a combinational S-Box with encryption and decryption datapaths.